# DESIGN AND PERFORMANCE ANALYSIS OF AN IMPROVED LOW-POWER 8T SRAM CELL FOR ENHANCED WRITABILITY

A Thesis Submitted

In Partial Fulfillment of the Requirements

For the Degree of

# **MASTER OF TECHNOLOGY**

in VLSI Design & Embedded System

by

### AKHILESH VISHWAKARMA 2K23/VLS/15

Under the Supervision of **Prof. POORNIMA MITTAL** Delhi Technological University

To the Department of Electronics & Communication Engineering

#### **DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering) Shahbad Daulatpur, Main Bawana Road, Delhi-110042. India

MAY, 2025

#### **ACKNOWLEDGMENTS**

I want to intimate my heartfelt thanks to my project guide, Dr. Poornima Mittal, Professor of Department of Electronics and Communication Engineering of Delhi Technological University, for his tremendous support and assistance base on their knowledge. I am so grateful to them for assisting me with the all the necessary tools for the completion of the project. I also want to extend my heartfelt gratitude to all those who have supported my research. I am grateful to the open-source community for developing and maintaining user friendly deep learning frameworks for simplifying the implementation of the research. I specially feel very thankful for our parents, friends, and classmates for their support throughout my project period. Finally, I express my gratitude to everyone for supporting me directly or indirectly in completing this project successfully. Your support and inspiration have been truly invaluable, which encourages me.

Akhilesh Vishwakarma

2K23/VLS/15

VLSI Design and Embedded System (2023-2025)

**DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering)

Shahbad Daulatpur, Main Bawana Road, Delhi-42

**CANDIDATE'S DECLARATION**

I, Akhilesh Vishwakarma (2K23/VLS/15) hereby certify that the work which

is being Presented in the thesis entitled "Design and Performance Analysis of

an Improved Low-Power 8T SRAM Cell for Enhanced Writability" in

partial fulfillment of the requirement for the award of the Degree of Master of

Technological, submitted in the Department of Electronics and Communication

Engineering, Delhi Technological University is an authentic record of my own

work carried out during the period from August 2023 to June 2025 Under the

supervision of **Prof. Poornima Mittal**.

The matter presented in the thesis has not been submitted by me for award of any

other degree of this or any other Institute.

Place: Delhi

Date: 31<sup>th</sup> May, 2025

Akhilesh Vishwakarma

2K23/VLS/15

iii

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Shahbad Daulatpur, Main Bawana Road, Delhi-42

**CERTIFICATE' BY THE SUPERVISOR**

Certified that Akhilesh Vishwakarma(2K23/VLS/15) has carried out their work

presented in this thesis entitled "Design and Performance Analysis of an

improved Low-Power 8T SRAM Cell for Enhanced Writability" for the

award of Master of Technology from Department of Electronics &

Communication Engineering, Delhi Technological University, under my/own

supervision. The thesis embodies results of original works, and studies are

carried out by the student himself and the contents of the thesis do not form the

basis for award of any other degree to the candidate or to anybody else from this

or any other University/Institution.

Place: Delhi

Prof. Poornima Mittal

Date: May 31, 2025

Supervisor, ECE, DTU

iv

#### **ABSTRACT**

In modern electronics, memory is a core component that enables data storage and retrieval, but cache memory is even more critical due to its direct connection to the CPU. Cache memory is designed to provide the processor with quick access to frequently used data and instructions. It relies on millions of SRAM cells, which must be highly efficient to maintain performance. These cells are required to operate with low power both static and dynamic while ensuring data remains stable and accessible. Fast read response times are also essential so that the processor is not bottlenecked during execution.

This review discusses the core elements of SRAM cell design and how they impact performance. It starts by explaining why SRAM matters in computing systems and how each cell functions. The focus is placed on data stability, speed during read and write operations, and minimizing power consumption. The review explores different cell architectures and the trade-offs they involve. It addresses key design challenges, including sensitivity to noise and issues caused by manufacturing variations. It also covers improvements such as assist techniques and feedback loops. The impact of shrinking technology nodes on these cells is reviewed in detail.

The performance of SRAM cells is evaluated by analyzing factors like read and write delay, write margin, stability, and power usage. This review explores how variations in design elements such as transistor sizes, supply voltage, and output loading affect these characteristics. It also looks into how process fluctuations impact the reliability and yield of SRAM cells and outlines possible solutions to enhance long-term performance and stability. This work presents a detailed Monte Carlo analysis of various 7T and 8T SRAM cell topologies at the 45nm technology node, simulated using the Cadence Virtuoso tool. The primary focus is to evaluate and compare the static and dynamic characteristics of these designs against a newly proposed 8-transistor SRAM cell, named 8TSEDPP. The analysis encompasses critical design metrics such as Hold Static Noise Margin (HSNM), Read Static

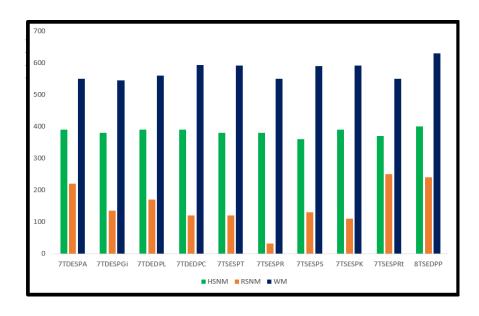

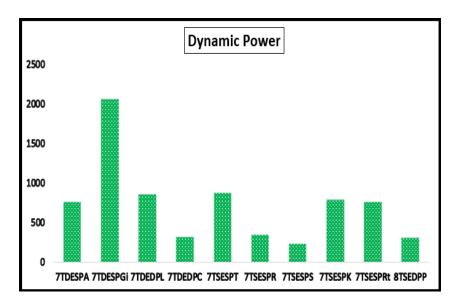

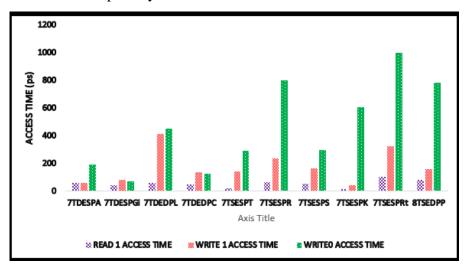

Noise Margin (RSNM), Write Margin (WM or N-Curve), dynamic power consumption, and access times for read and write operations. The proposed 8TSEDPP circuit stands out with significant improvements in stability, power efficiency, and performance balance. In terms of RSNM, the proposed cell achieves 205 mV, outperforming all other designs, including 7TDESPP and 7TSESPK, with an average improvement of over 45%. The Write Margin also shows a notable enhancement, reaching 510.41 mV, which represents a 13.5% increase over traditional 7T cells like 7TDESPC and 7TDESPL. Despite being a more complex circuit, the dynamic power consumption of the proposed 8TSEDPP is just 317.8 nW, which is a remarkable 67.6% reduction compared to the baseline 7TDESPT design. This makes the proposed cell highly suitable for low-power applications without sacrificing stability.

Timing analysis further strengthens the case for 8TSEDPP. The Write '0' access time is measured at 205 ps, while Write '1' access time is 291.6 ps, both of which remain within acceptable limits for high-performance applications. Although some 7T cells exhibit slightly faster access times, they lag significantly in power and noise margin performance. The Read Access Time of 510.41 ps, although not the fastest, offers a balanced trade-off given the robustness in other areas. Overall, the 8TSEDPP SRAM cell demonstrates the best overall balance across all performance, stability, and power metrics, validating its suitability for energy-sensitive and high-reliability memory applications. The proposed design is particularly promising for next-generation VLSI circuits used in portable, embedded, and IoT-based devices, where low leakage, reliable write operations, and immunity to process variations are critical. The results obtained through extensive simulations confirm that 8TSEDPP is a strong candidate for replacing or complementing traditional SRAM architectures in future semiconductor designs.

# **LIST OF PUBLICATIONS**

#### SCOPUS INDEXED CONFERENCES

A. Vishwakarma and P. Mittal, "Trade-offs in 7T SRAM Cells for Low-Power VLSI: A Quantitative Analysis", International Conference on Electrical, Electronics & Automation (E2ACON - 2025), Jalandhar, India, March 2025 (Scopus Indexed)

Status of Paper: Presented in the conference on 8st March 2025

# **CONTENTS**

| Ackı                    | nowled                                                            | gment                                    | ii   |

|-------------------------|-------------------------------------------------------------------|------------------------------------------|------|

| Candidate's Declaration |                                                                   |                                          | iii  |

| Cer                     | Certificate by The Supervisor<br>Abstract<br>List of Publications |                                          |      |

| Abs                     |                                                                   |                                          |      |

| List                    |                                                                   |                                          |      |

| Con                     | tent                                                              |                                          | viii |

| List                    | of Tab                                                            | oles                                     | xi   |

| List                    | of Fig                                                            | ures                                     | xii  |

| List                    | of Abl                                                            | previations                              | xiv  |

|                         |                                                                   | CHAPTER 1 INTRODUCTION                   | 1    |

| 1.1                     |                                                                   | SRAM Array                               | 1    |

|                         | 1.1.1                                                             | Conventional Six Transistor Cell         | 2    |

|                         | 1.1.2                                                             | Data Hold Operation                      | 3    |

|                         | 1.1.3                                                             | Write Operation                          | 4    |

|                         | 1.1.4                                                             | Read Operation                           | 6    |

| 1.2                     |                                                                   | Motivation                               | 7    |

| 1.3                     |                                                                   | Objectives                               | 8    |

| 1.4                     |                                                                   | Methodology                              | 9    |

| 1.5                     |                                                                   | Thesis Organization                      | 9    |

|                         |                                                                   | CHAPTER 2 LITERATURE REVIEW              | 12   |

| 2.1                     |                                                                   | Comprehensive Summary of Past Work       | 12   |

| 2.2                     |                                                                   | Research Gap                             | 20   |

|                         |                                                                   | CHAPTER 3 CHARACTERISTIC COMPARISON      | 22   |

|                         |                                                                   | FOR DIFFERENT EXISTING 7T SRAM CELLS     |      |

| 3.1                     |                                                                   | Overview of SRAM Cells                   | 23   |

| 3.2                     |                                                                   | Different 7T SRAM                        | 24   |

|                         | 3 2 1                                                             | Differential Ended and Differential Port | 24   |

|     | 3.2.2 | Differential Ended 7T SRAM Bit cells with the Isolated Read Port | 25 |

|-----|-------|------------------------------------------------------------------|----|

|     | 3.2.3 | Single Ended Dual Port 7T SRAM Bit Cells                         | 26 |

|     | 3.2.4 | Single Ended and Single Port 7TSRAM Bit Cells                    | 26 |

| 3.3 |       | Cell Sizing                                                      | 27 |

| 3.4 |       | Transient Analysis                                               | 27 |

|     | 3.4.1 | Supply Voltage Scaling                                           | 28 |

|     | 3.4.2 | Stability Analysis                                               | 29 |

|     |       | 3.4.2.1 HSNM Analysis                                            | 29 |

| a = |       | 3.4.2.2 RSNM Analysis                                            | 30 |

| 3.5 |       | Timing Analysis                                                  | 31 |

| 3.6 |       | Power Consumption Analysis                                       | 32 |

| 3.7 |       | Important Results                                                | 33 |

|     |       | CHAPTER 4 PROPOSED SINGLE ENDED DUAL PORT 8T SRAM CELL           | 33 |

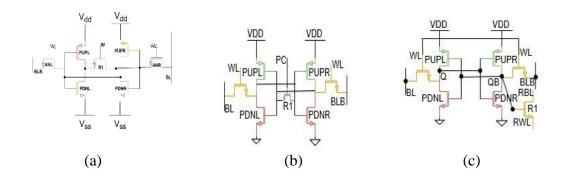

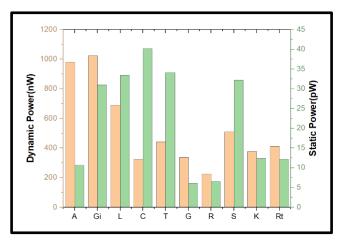

| 4.1 |       | Architecture and Working of Proposed 8T cell                     | 35 |

| 4.2 |       | Dimensions In the Proposed 8T SRAM Bit Cell                      | 36 |

| 4.3 |       | Working of Proposed 8T SRAM Cell                                 | 37 |

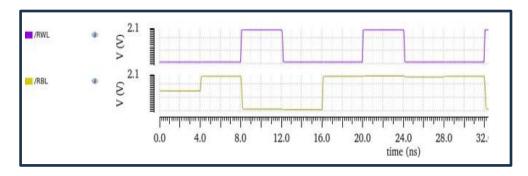

| 4.4 |       | Transient Analysis                                               | 38 |

| 4.5 |       | Data Stability                                                   | 40 |

|     | 4.5.1 | Hold Static Noise Margin                                         | 42 |

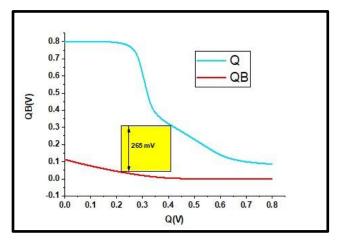

|     | 4.5.2 | Read Static Noise Margin                                         | 43 |

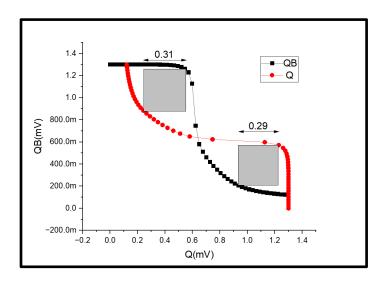

|     | 4.5.3 | Write Static Noise Margin                                        | 45 |

|     | 4.5.4 | N-Curve                                                          | 46 |

| 4.6 |       | Monte Carlo Analysis                                             | 48 |

| 4.7 |       | Important Results                                                | 49 |

|     |       | CHAPTER 5 PERFORMANCE COMPARISON OF                              | 50 |

|     |       | PROPOSED CELL WITH OTHER EXISTING CELLS                          |    |

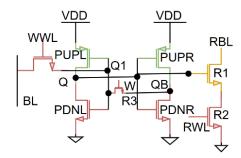

| 5.1 |       | Comparison of proposed cell with different 7T SRAM cells         | 51 |

|     | 5.1.1 | Data Stability                                                   | 51 |

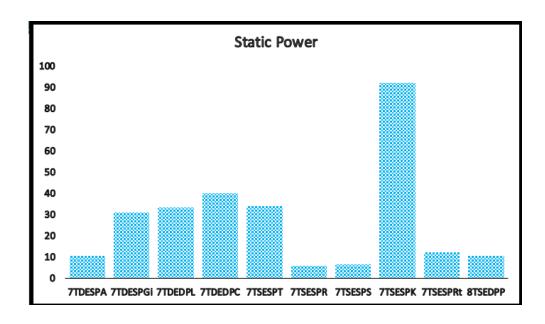

|     | 5.1.2 | Power consumption                                                | 52 |

|     | 5.1.3 | Read and Write Access Delay                                      | 55 |

| 5.2 | Important Results                     |    |

|-----|---------------------------------------|----|

|     | CHAPTER 6 CONCLUSION AND FUTURE SCOPE | 59 |

| 6.1 | Conclusion                            | 61 |

| 6.2 | Future Scope                          | 63 |

| 6.3 | Social Impact                         | 68 |

|     | REFERENCES                            | 65 |

|     | PURLICATION LIST                      | 67 |

# LIST OF TABLES

| Table No. | Caption of Table                                   |     |

|-----------|----------------------------------------------------|-----|

|           |                                                    | No. |

| Table 3.1 | Dimension of Various 7T SRAM cells                 | 27  |

| Table 3.2 | HSNM/RSNM at Voltage 1.1V for Various 7TSRAM Cells | 30  |

| Table 3.3 | Timing Analysis of Read and Write Access time      | 32  |

| Table 3.4 | Static and Dynamic Power for Various 7TSRAM Cells  | 33  |

| Table 4.1 | Dimensions for Proposed 8T cell                    | 37  |

# LIST OF FIGURES

| Fig. No. | Caption of Figure                                                                                                                                           | Page No   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Fig. 1.1 | Typical arrangement of an SRAM array, showing the periphery (in yellow) and the cells (in red), with one row of cells accessed (dark red)                   | 2         |

| Fig. 1.2 | Typical 6T SRAM cell                                                                                                                                        | 3         |

| Fig. 1.3 | Transfer curves of the two inverters in an SRAM cell                                                                                                        | 4         |

| Fig. 1.4 | Transient simulation of a write operation in SRAM cell                                                                                                      | 5         |

| Fig. 1.5 | Modified transfer curves of the inverter while writing                                                                                                      | 5         |

| Fig. 1.6 | Transient simulation of a read operation                                                                                                                    | 6         |

| Fig. 1.7 | Modified transfer curves during a read operation                                                                                                            | 7         |

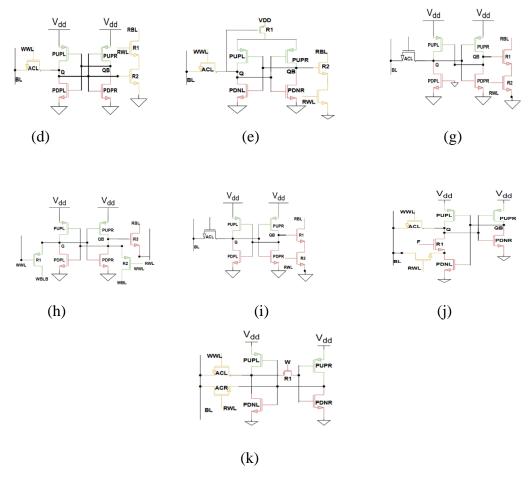

| Fig. 3.1 | Schematic Diagram For (a) 7TDESPA, (b) 7TDESPGi, (c) 7TDEDPL, (d) 7TDEDPC, (e) 7TSEDPT, (f) 7TSEDPG, (g) 7TSEDPR, (h) 7TSEDPS, (i) 7TSESPK, (j) 7TSESPRt    | 25-<br>26 |

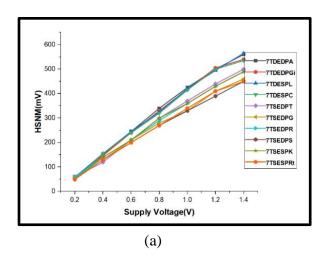

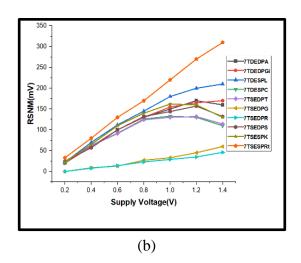

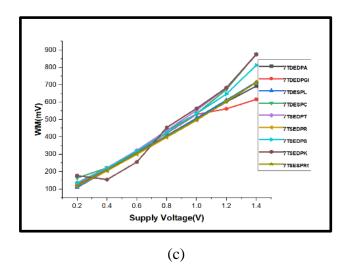

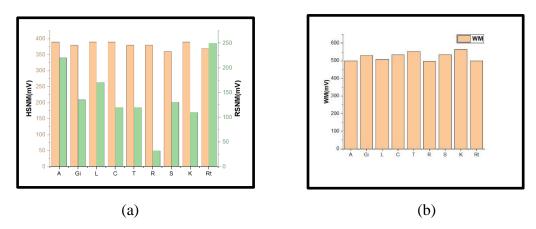

| Fig. 3.2 | Graphical comparison for various 7TSRAM Cells (a) HSNM, (b) RSNM, (c) WM for all different 7T SRAM bit cells for supply voltage varying from 0.2 V to 1.4 V | 24        |

| Fig. 3.3 | Comparison of (a) HSNM and RSNM, (b) WM for various 7T SRAM cells                                                                                           | 30        |

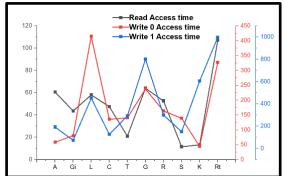

| Fig. 3.4 | Graphical comparison of read time access, write 0 time                                                                                                      | 32        |

| Fig. 3.5  | Graphical comparison of static power and dynamic power                                                                                                                                  | 33            |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Fig. 4.1  | Schematic of Proposed 8T SRAM cell                                                                                                                                                      | 36            |

| Fig. 4.2  | A conventional 6T cell illustrating SRAM sizing                                                                                                                                         | 37            |

| Fig. 4.3  | Proposed 8T SRAM during Hold Operation                                                                                                                                                  | 39            |

| Fig. 4.4  | Proposed 8T SRAM (a) Read 0 and (B) Read 1 operation                                                                                                                                    | 40            |

| Fig. 4.5  | Proposed 8T SRAM (a) Write 1 and (B) Write 0 operation                                                                                                                                  | 40            |

| Fig. 4.6  | Transient analysis of the Proposed 8T cell                                                                                                                                              | 41            |

| Fig. 4.7  | Butterfly curve for HSNM of Proposed 8T cell                                                                                                                                            | 44            |

| Fig. 4.8  | Butterfly curve for RSNM of Proposed 8T cell                                                                                                                                            | 45            |

| Fig. 4.9  | N- Curve for Proposed 8T SRAM cell                                                                                                                                                      | 48            |

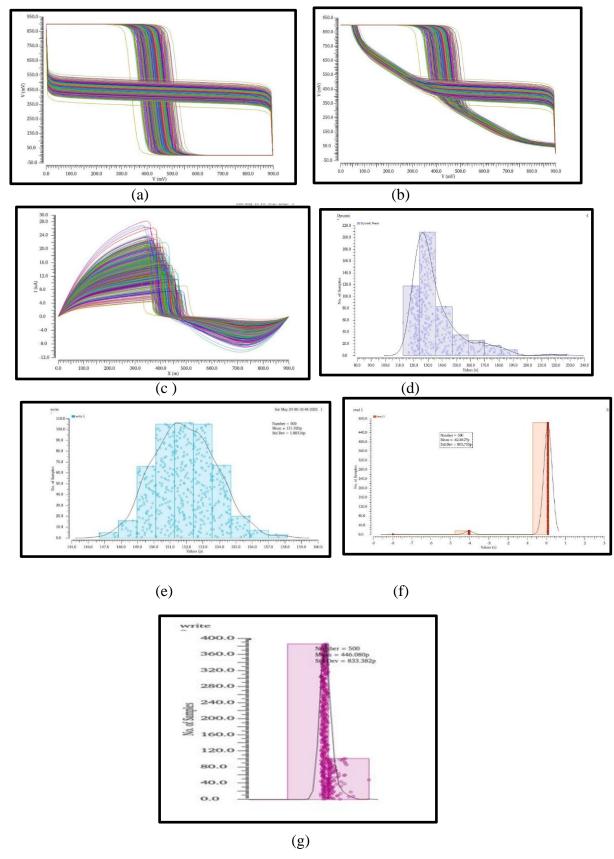

| Fig. 4.10 | Monte Carlo simulation of (a) HSNM (b) RSNM (c) N-Curve, (d) Dynamic Power, (e) Write 1 Access time, (f) Read 1 Access Time, (g) Write 0 Access Time for 500 sample of proposed 8T cell | 49<br>-<br>50 |

| Fig. 5.1  | Comparison of HSNM, RSNM and WM                                                                                                                                                         | 55            |

| Fig. 5.2  | Comparison of Dynamic Power Consumption for various 7T and proposed 8T cells                                                                                                            | 56            |

| Fig. 5.3  | Comparison of Static Power Consumption for various 7T and proposed 8T cells                                                                                                             | 57            |

| Fig.5.4   | Comparison of Delay for various 7T and Proposed 8T cells                                                                                                                                | 58            |

# LIST OF ABBREVIATIONS

| S. No. | Abbreviation | Full Name                            |

|--------|--------------|--------------------------------------|

| 1.     | SRAM         | Static Random Access Memory          |

| 2.     | BL           | Bit Line                             |

| 3.     | BLB          | Bit Line Bar                         |

| 4.     | WL           | Word Line                            |

| 5      | WLB          | Word Line Bar                        |

| 6.     | SNM          | Static Noise Margin                  |

| 7.     | HSNM         | Hold Static Noise Margin             |

| 8.     | RSNM         | Read Static Noise Margin             |

| 9.     | DEDP         | Differential Ended Differential Port |

| 10.    | EN           | Enable                               |

| 11.    | MOS          | Metal Oxide Semiconductor            |

| 12.    | IC           | Integrated Circuit                   |

| 13.    | SA           | Sense Amplifier                      |

| 14.    | P            | Power                                |

| 15.    | T            | Transistor                           |

| 16.    | ROM          | Read Only Memory                     |

| 17.    | DRAM         | Dynamic Random Access<br>Memory      |

| 18.    | SoC          | System on Chip                       |

| 19. | ІоТ  | Internet of Things                          |

|-----|------|---------------------------------------------|

| 20  | GND  | Ground                                      |

| 21. | CMOS | Complementary Metal Oxide-<br>Semiconductor |

| 22. | PMOS | P-type Metal Oxide Semiconductor            |

| 23. | NMOS | N-type Metal Oxide Semiconductor            |

| 24. | WL   | Word Line                                   |

| 25  | WLB  | Word Line Bar                               |

| 26  | DESP | Differential Ended Single Port              |

| 27  | SEDP | Single Ended Deferential Port               |

| 28  | SESP | Single Ended Single Port                    |

| 29  | VDD  | Supply Voltage                              |

| 30  | VTH  | Threshold Voltage                           |

| 31  | TEFT | Tunnel Field-Effect Transistor              |

| 32  | WWL  | Write Word Line                             |

| 33  | RWL  | Read Word Line                              |

| 34  | RBL  | Read Bit Line                               |

| 35  | PUPL | Pull Up PMOS left                           |

| 36  | PUPR | Pull Up PMOS Right                          |

| 37  | PDNL | Pull Up NMOS left                           |

# CHAPTER 1 INTRODUCTION

SRAM (Static Random-Access Memory) cell is a fundamental building block of computer memory systems. It is a type of volatile memory that can store data as long as power is supplied to the system. The SRAM cell is known for its high speed and low power consumption, making it an essential component in various electronic devices, such as microprocessors, cache memories, and graphics cards. As the demand for faster and more efficient computing continues to rise in the future, SRAM cells are expected to play a crucial role in meeting these requirements. With the increasing adoption of artificial intelligence, Internet of Things, and edge computing applications, the demand for SRAM cells is expected to grow even further, driven by the need for high-speed data processing, low-latency access, and power efficiency. Additionally, emerging technologies such as self-driving cars, smart cities, and advanced robotics will also contribute to the increased demand for SRAM cells in the future, making them a vital component in the evolving landscape of computing and information technology.

This chapter is structured into five distinct sections. The first section (1.1) introduces the SRAM array, a fundamental element of memory architecture composed of numerous SRAM cells arranged in a matrix format. It also includes several subsections that briefly explain the conventional 6T SRAM cell along with its hold, read, and write operations. The second section (1.2) outlines the motivation behind this study, emphasizing why this area continues to attract significant research interest. Section three (1.3) states the main goals and objectives of the research. The fourth section (1.4) describes the approach and techniques used to carry out the study. Finally, the fifth section provides a comprehensive overview of how the thesis is organized.

#### 1.1 SRAM ARRAY

An SRAM array refers to the organization and structure of static random access memory cells within a memory module or chip. The SRAM array is responsible for storing and retrieving data in a random access manner, allowing for fast read and write operations.

The basic building block of an SRAM array is a single SRAM cell, which typically consists of six transistors [1]. These transistors form a flip-flop circuit that can store one bit of data. The SRAM array is constructed by arranging multiple SRAM cells in a grid-like pattern, with rows and columns forming the addressable locations of the memory.

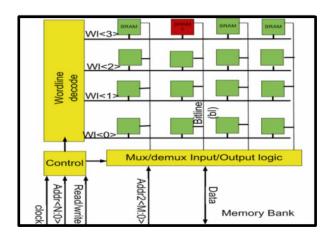

**Fig. 1.1** Typical arrangement of an SRAM array, showing the periphery (in yellow) and the cells (in red), with one row of cells accessed (dark red)

The size of an SRAM array is defined by the number of rows and columns of SRAM cells. Each row represents a word line, and each column represents a bit line. The intersection of a row and column represents a specific memory location, where data can be stored or retrieved.

To read data from an SRAM array, the desired address is provided, activating the corresponding word line and allowing the stored data in the selected column to be accessed and read out. Similarly, writing data involves providing the address and data to be written, and activating the appropriate word line and bit line to store the new data in the desired memory location.

The organization and design of the SRAM array play a crucial role in determining the overall capacity, speed, and power consumption of the SRAM chip. Various techniques, such as hierarchical organization, pipelining, and multiplexing, can be employed to optimize the performance of the SRAM array and meet the requirements of different applications [3].

#### 1.1.1 Conventional Six-transistor Cell

The design of the cell includes multiple vertical and horizontal control lines for each memory unit. In a typical 6-transistor SRAM, each cell requires one horizontal control line called the word line and one vertical line referred to as the bit line.

The traditional 6T memory cell plays a vital role in contemporary memory architectures and is commonly found in processors, cache units, and various digital circuits. It is made up of six transistors arranged in a cross-coupled latch setup. This configuration creates a feedback loop through the inverters, enabling the cell to hold data steadily without requiring continuous refreshing.

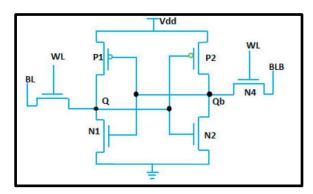

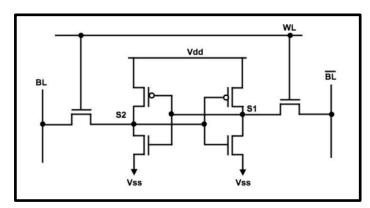

Fig. 1.2 Typical 6T SRAM cell

The 6T SRAM cell comprises a pair of intricately cross-coupled inverters, where the output of each inverter is routed to the input of the other, as depicted in Figure 1.2. This interconnected architecture establishes two complementary internal storage nodes, commonly referred to as bitline and bitline\_bar. Each inverter is constructed using one PMOS transistor, known as the pull-up device, and one NMOS transistor, termed the pull-down device. Complementing this setup, two additional NMOS transistors function as passgates, facilitating a controlled connection between the internal nodes and the corresponding bit lines, enabling efficient data read and write operations.

The 6T SRAM cell offers key benefits such as fast access, low power use, and data retention with continuous power. However, it requires more chip area than some alternatives and is more prone to noise and process variations. Despite this, it remains essential in digital systems for its speed, reliability, and adaptability.

#### 1.1.2 Data Hold Operation

The data storage capability of an SRAM cell relies on its two cross-coupled inverters. When the word line (WL) is low, the pass-gates are disabled and effectively disconnected. If the bit line holds a 1, the top inverter drives bit\_bar to 0, and the bottom inverter reinforces the 1 on bit, confirming data retention. A similar process occurs if the stored value is 0, maintaining stability through feedback.

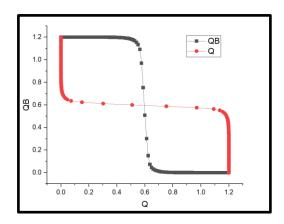

Fig. 1.3 Transfer curves of the two inverters in an SRAM cell

As shown in Figure 1.3, plotting the transfer curves reveals three intersection points. The central point is unstable, while the other two represent the stable states of the cell, corresponding to stored values of either 0 or 1.

The 6T SRAM cell primarily utilizes two transistor-based inverters to retain data, a configuration that minimizes its area footprint. However, the conventional inverters can be replaced with alternative, more advanced designs that can also store the two possible logical states. These alternative designs may involve altering the dimensions of the pull-up and pull-down transistors, or employing more complex circuits, such as inverters incorporating additional transistors like Schmitt triggers. Such modifications can significantly enhance the cell's performance by improving key attributes, including noise immunity, stability, and overall reliability under varying operating conditions.

#### 1.1.3 Write Operation

The two-looped inverters at the core of the cell can accumulate both probable data. The need to trigger the wanted value to behold in the cells, which is called as the write operation.

The write operation begins by setting the word line to  $V_{DD}$ , which stimulates the pass gates. In the meantime, the edge on the top of Figure 1.1 sets the bitlines to the value to be written in the interior nodes of the cell. When an inverse value is written than the one being kept, the pass gate is imposing a value while the inverter is trying to hold the opposite one. The transistors must be sized so that the pass gate surpasses the inverter in order to attain a effective write.

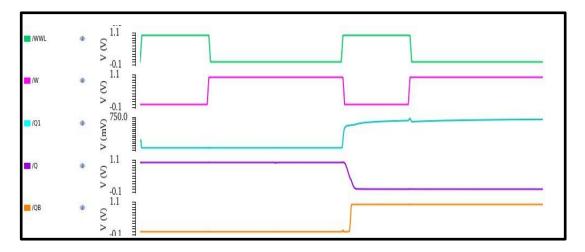

Fig. 1.4 Transient simulation of a write operation in a 6T SRAM cell

Fig. 1.5 Modified transfer curves of the inverter while writing

A transient simulation showcasing the write operation is depicted in Figure 1.4. Initially, the SRAM cell is storing a logic high ('1'), as indicated by the voltage levels at its internal nodes—bit is at VDD, and bit\_bar is at 0 V. To write a new value (the opposite of the stored one), the bit lines are driven to bitline = 0 V and bitline\_bar = VDD. At t = 1 ns, the word line is raised from 0 V to VDD, activating the access (pass) transistors. This action enables the data on the bitlines to overwrite the contents of the storage nodes, effectively flipping the voltages of bit and bit\_bar.

Once the write operation is completed, and the word line is pulled back to ground, the new data remains latched within the cell due to the regenerative feedback of the inverters. The enabled pass transistors during the write operation alter the inverter transfer characteristics, as illustrated in Figure 1.4, resulting in a single stable operating point at the intersection of the curves. This unique crossing point ensures the cell retains the newly written logic state once the word line is deactivated.

The voltage levels on the bit lines during the write operation dictate the stable state that the cell adopts. When the bitline is grounded and bitline\_bar is set to VDD, the cell is forced into storing a logic '0', as demonstrated in Figure 1.5(a). Conversely, applying the opposite condition bitline = VDD and bitline\_bar = 0 V causes the cell to store a logic '1', as seen in Figure 1.5(b).

#### 1.1.4 Read Operation

After a value has been successfully written and retained by the cell, the next crucial step is to read the stored data. While accurately retrieving the data is essential, it is equally important that the read operation does not disturb or modify the contents of the cell. Ensuring data integrity during read access is a key requirement for reliable memory performance.

Fig.1.6 Transient Simulation of a Read Operation

In a 6T SRAM cell, the read operation begins by raising the word line voltage from ground to VDD, which turns on the pass transistors. Instead of driving the bit lines to specific logic levels, they are precharged to VDD and then left floating. The pass transistor connected to the internal node held at ground will draw current from the corresponding bit line, causing it to discharge gradually, as illustrated in Figure 1.6.

The read circuitry at the bottom of Figure 1.1 detects the voltage difference between the two bit lines and amplifies it to recover the data stored in the cell. This circuit, known as the sense amplifier, typically requires only a small voltage difference around 10% of the supply voltage to accurately sense the stored value.

Fig.1.7 Modified transfer curves during a Read Operation

During the read operation, the inverter transfer curves change as depicted in Figure 1.7. The curves intersect three times, resulting in two stable points, which ensures that the stored data remains unchanged. However, compared to the curves shown in Figure 1.3, these curves are closer together, indicating reduced stability and increased susceptibility to noise. This effect is also visible in Figure 1.6, where the voltage at the internal node bit\_bar shifts during the read access.

#### 1.2 MOTIVATION

The motivation behind research in 8T SRAM cells arises from the growing need for high-performance, low-power memory in modern computing systems. With the increasing demand for data-intensive technologies such as AI, virtual reality, and big data, traditional 6T SRAM cells face limitations in stability, leakage, and power efficiency. The 8T SRAM cell design offers a promising solution by incorporating extra transistors that improve stability, reduce leakage, and enhance read and write performance. Understanding the characteristics of 8T SRAM cells will help identify their potential advantages and limitations, ultimately advancing the development of more efficient and reliable memory systems.

The exploration of 8T SRAM cells is driven by the need to tackle the scaling issues faced by traditional SRAM and 7T SRAM designs. As technology nodes continue to shrink, scaling down 6T SRAM cells becomes increasingly challenging due to a range of physical and electrical constraints. By adding extra transistors, the 8T SRAM architecture offers improved

scalability and performance for advanced technology nodes. Through static and dynamic analysis, circuit simulations, and characterization, we can evaluate the feasibility of 8T SRAM cells for future technology generations. The research aims to overcome the limitations of current memory technologies and create more reliable solutions.

#### 1.3 OBJECTIVE

The objective of this study is to investigate and evaluate the performance of SRAM cells, which are essential for memory storage and data retrieval in modern digital systems. With the rising demand for high-speed and energy-efficient memory solutions, it is vital to understand the behaviour of advanced cell architectures. By concentrating on 8T SRAM cells, this research aims to examine their strengths, weaknesses, and potential uses. Through rigorous experimentation and analysis, the goal is to provide critical insights and contribute to the progression of SRAM technology for future systems.

#### Primary objectives of this research project are as follows:

- To Compare multiple SRAM designs for the same technology nodes, power supply, and transient time. This also helped to determine the trend of SRAM being used for low-power applications.

- To understand the working of SRAM cell and which one out performs the others, a comparison is done between existing structures and modified SRAM cell structure.

A mathematical calculation is also performed for the PDP analysis. To establish which circuit had the best performance, SRAMs are compared, and their findings are illustrated.

- To design and analyze a modified SRAM cell structure that includes a back-to-back inverter, buffer transistors, and access transistors. For optimal performance, power analysis, delay analysis, and the data stability are all performed.

The emphasis of this research is to create an up-to-date better SRAM cell structure that uses low-energy and low-power components and may be used in low-power applications. Multiple SRAM cell topologies on the same technology node, with the same aspect ratios and transient times, were compared for this. Then, for the best performance, the existing SRAM cell designs are compared to the modified design.

#### 1.4 METHODOLOGY

A comparative performance analysis has been carried out between various 7T SRAM cells and the proposed 8T SRAM cell. The evaluation includes key parameters such as data stability, power consumption, read delay, and write delay. In most aspects, the proposed 8T SRAM cell demonstrates improved stability and significantly lower power consumption; however, it exhibits a slightly higher write access time compared to conventional 7T SRAM cells.

The proposed 8T design has been implemented and analyzed through various simulations. It consists of a total of eight transistors—two PMOS and six NMOS—which are categorized into pull-up, pull-down, and access transistors. The analysis covers critical factors such as data stability, power dissipation, read delay, and write delay. This research focuses on developing low-power and high-stability SRAM architectures. Additionally, various sense amplifier parameters and stability metrics such as HSNM, RSNM, and WSNM have been investigated across different voltage levels.

The proposed 8T SRAM cell outperforms traditional 6T and 7T SRAM structures in terms of noise immunity and energy efficiency. However, the increased write access time is a trade-off. Therefore, the selection of an SRAM cell architecture should depend on the specific design requirements and the balance between power, area, speed, and stability.

#### 1.5 THESIS ORGANIZATION

This thesis is organized into five main chapters. Chapter 1 serves as the introduction, providing an overview of the SRAM array and the traditional 6T SRAM cell. It also covers the motivation behind the study, outlines the research objectives, explains the adopted methodology, and describes the structure of the thesis. Chapter 2 presents a comprehensive review of existing literature and identifies the existing gaps in current technology. Chapter 3 offers an in-depth comparative evaluation of various 7T SRAM cells. In Chapter 4, the design and analysis of the proposed 8T SRAM cell are discussed in detail, along with its performance metrics and parameter assessment. Chapter 5 builds on this by comparing the earlier reviewed SRAM designs from Chapter 3 with the modified 8T cell, highlighting its performance improvements over previously reported architectures. Finally, Chapter 6 summarizes the findings and outlines potential directions for future work.

**CHAPTER 1 -** This chapter offers a fundamental introduction to SRAM arrays and cells, emphasizing their integral role in memory systems and their functionality under low-power and low-voltage conditions. It also outlines the research objectives, the motivation behind the study, the methodology employed, and the overall structure of the thesis.

**CHAPTER 2 -** This chapter presents an in-depth overview of previous research related to SRAM. It critically examines various parameters discussed in the existing literature and consolidates key academic studies and publications concerning SRAM cells. The literature review aims to build a thorough understanding of the current knowledge landscape, highlight gaps or contradictions in prior research, and establish a solid groundwork for the present study.

**CHAPTER 3 -** This chapter presents a comparative analysis of various 7T SRAM cells, emphasizing their structure, functionality, and performance characteristics. The evaluation was conducted at the 45nm technology node using a range of supply voltages from 0.2V to 1.4V. Depending on their architectural configurations, key parameters such as static noise margin, read/write delay, and power consumption were assessed and compared.

**CHAPTER 4 -** This chapter presents the proposed design of the 8T SRAM cell, detailing its architecture and operational principles. Key performance metrics such as data stability, read/write delay, and power consumption are thoroughly evaluated. Additionally, Monte Carlo simulations are conducted to assess the reliability and robustness of the proposed cell under process variations. These comprehensive analyses serve to demonstrate the overall effectiveness and performance advantages of the proposed design.

CHAPTER 5 - This chapter presents a detailed comparative analysis between the proposed 8T SRAM cell and four existing 7T SRAM cell designs to demonstrate the superior performance of the proposed architecture. The comparison is carried out based on three key parameters: static noise margins, access delays, and power consumption. Additionally, the analysis includes an evaluation of Read Static Noise Margin (RSNM) and Hold Static Noise Margin (HSNM) under both constant and varying supply voltages. This voltage variation study highlights the robustness and stability of the proposed design across a wide operating range.

**CHAPTER 6 -** This chapter concludes the dissertation by summarizing the overall findings and results obtained from the research. It also discusses potential future improvements and directions related to the research topic.

Additionally, the chapter includes a list of publications resulting from the work conducted in this thesis. Following that, a comprehensive list of references is provided, citing previous studies that helped guide and support the present research.

# CHAPTER 2 LITERATURE REVIEW

A thorough review of the existing literature is essential for any research endeavor. The purpose of conducting a literature review is to:

- Build a comprehensive foundation of understanding regarding the subject matter

- Recognize established areas of expertise to avoid redundancy and properly acknowledge the contributions of previous scholars

- Identify contradictions in prior studies, uncover research gaps, highlight key areas of conflict within the existing literature, and address unresolved issues or questions that warrant further investigation

This chapter is divided into two parts. Section 2.1 provides a comprehensive summary of previous research, while section 2.2 addresses the existing technical gaps identified in the literature.

#### 2.1 COMPREHENSIVE SUMMARY OF PAST WORK

• Low-power cache design using 7T SRAM cell, 2007

R Ramy E. Aly and Magdy A. Bayoumi [15] proposed a novel 7-transistor (7T) SRAM cell architecture aimed at reducing power consumption in cache memory applications. The design introduces an additional transistor to decouple the read and write paths, thereby enhancing read stability and reducing the risk of read disturbances. By utilizing only one bit line during write operations, the cell significantly reduces dynamic power consumption. HSPICE simulation results demonstrate that the proposed 7T SRAM cell achieves at least 49% reduction in write power compared to conventional 6T designs, along with improved static noise margins and no performance degradation. Although the addition of a seventh

transistor leads to a slight increase in silicon area (approximately 12.25%), the overall tradeoff favors energy-efficient cache implementations.

#### • A 7T security oriented SRAM bitcell, 2019

R. Giterman, O. Keren, and A. Fish [16] proposed a novel 7-transistor (7T) SRAM bitcell architecture aimed at enhancing security against side-channel attacks, particularly power analysis (PA) attacks. The design incorporates an additional transistor to the conventional 6T SRAM cell and introduces a two-phase write operation. This approach significantly reduces the correlation between the stored data and the power consumption during write operations, thereby mitigating the risk of information leakage through power analysis. Implemented in a 28 nm CMOS technology, the proposed 7T SRAM cell demonstrates over 1000× lower write energy standard deviation between writing '1' and '0' compared to a standard 6T SRAM cell. Additionally, it achieves a 39%–53% reduction in write energy and a 19%–38% decrease in write delay relative to other power analysis-resistant SRAM designs. These improvements make the 7T SRAM cell a promising candidate for secure memory applications in cryptographic and embedded systems.

# • Differential Read/Write 7T SRAM with Bit-Interleaved Structure for Near-Threshold Operation, 2021

J. Sang Oh, J. Park, K. Cho, Tae Woo Oh, and Seong Ook Jung [17] introduced a differential 7-transistor (7T) SRAM bitcell optimized for near-threshold voltage (V<sub>th</sub>) operations, aiming to reduce energy consumption while maintaining high read stability and write ability. The design incorporates an additional row-based control signal and an nMOS transistor between the pull-up and pull-down transistors on one side of the cross-coupled inverter. This configuration enhances the cell's resilience to V<sub>th</sub> variations, which are more pronounced in near-V<sub>th</sub> operations. Furthermore, the proposed SRAM bitcell supports a bit-interleaved structure without encountering the half-select issue, thereby improving reliability. Compared to differential 10T and 12T SRAM designs, the proposed 7T SRAM achieves 5% and 6% higher operating frequencies, 70% and 23% lower operation energy consumption, and 33% and 49% smaller bitcell areas, respectively. These improvements make it a promising candidate for energy-efficient memory applications in advanced CMOS technologies.

### A Near-Threshold 7T SRAM Cell with High Write and Read Margins and Low Write Time for Sub-20 nm FinFET Technologies, 2015

M. H. Ansari, H. Kusha, B. Ebrahimi, Z. Navabi, A. Kusha, and M. Pedram [18] proposed a 7-transistor (7T) SRAM cell optimized for near-threshold operation in sub-20 nm FinFET technologies. The design modifies a previously introduced 5T cell by incorporating an additional access transistor and appropriately setting the threshold voltages of the transistors to enhance both read and write stability. The cell employs differential write and single-ended read operations, achieving high write and read margins, low write time, and ultra-low leakage power in the hold "0" state. HSPICE simulations using 20 nm, 16 nm, 14 nm, 10 nm, and 7 nm FinFET technologies at a supply voltage of 500 mV demonstrate that the proposed 7T cell outperforms conventional 5T, 6T, 8T, and 9T SRAM cells in terms of Ion/Ioff ratio, write speed, and leakage power. Additionally, the cell maintains stability across a temperature range from −40 °C to 100 °C and under process variations at supply voltages of 400 mV and 500 mV, meeting the required 6σ yield criteria. These characteristics make the proposed 7T SRAM cell a promising candidate for high-performance and low-power applications in advanced CMOS technologies.

# A Near-Threshold Soft Error Resilient 7T SRAM Cell with Low Read Time for 20 nm FinFET Technology, 2017

R. N. Asli and S. Taghipour [19] proposed a 7-transistor (7T) SRAM cell optimized for near-threshold operation in 20 nm FinFET technology, focusing on enhancing soft error resilience and reducing read time. The design builds upon a previously proposed 5T cell by incorporating an additional transistor, enabling single-ended read and differential write operations. This configuration improves read speed without compromising write performance. HSPICE simulations at a supply voltage of 0.5 V demonstrate that the proposed 7T SRAM cell achieves high write speed, improved read and write margins, and low leakage power in the hold "0" state compared to the 5T cell. Furthermore, the cell exhibits robust performance under process and environmental variations, including aging effects, making it a promising candidate for reliable low-power applications in advanced CMOS technologies.

# • Low-Power Circuit Analysis and Design Based on Heterojunction Tunneling Transistors (HETTs), 2013

Y. Lee, D. Kim, J. Cai, I. Lauer, Leland Chang, Steven J. Koester, Dennis Sylvester, and David Blaauw [20] proposed a novel low-power circuit design approach utilizing Si/SiGe Heterojunction Tunneling Transistors (HETTs). These transistors exhibit a subthreshold swing below the 60 mV/decade limit of conventional MOSFETs, enabling steeper subthreshold characteristics and improved low-voltage operation. The authors developed a Verilog-A device model based on Technology Computer-Aided Design (TCAD) simulations to evaluate HETT-based circuits. Their analysis demonstrated that a HETT-based ring oscillator achieves a 9–19× reduction in dynamic power compared to a CMOS ring oscillator. Additionally, they proposed a 7-transistor HETT-based SRAM cell, which leverages the asymmetric current flow characteristics of HETTs to achieve a 7–37× reduction in leakage power compared to conventional CMOS SRAM cells. This work highlights the potential of HETTs in enabling ultra-low-power circuit designs for future nanoelectronics.

# • A comprehensive analysis of different 7T SRAM topologies to design a 1R1 W bit interleaving enabled and half select the free cell for 32 nm technology node, 2022

B. Rawat and P. Mittal [13] presented a comprehensive study analyzing various 7T SRAM topologies to design a single-ended, dual-port 1R1W bit cell with interleaving capability and half-select-free operation for the 32 nm technology node. The proposed design aims to mitigate half-select disturb issues by separating the read and write paths and implementing a bit-interleaved structure. This approach enhances stability, write-ability, and read reliability under concurrent access conditions. Simulation results showed improved static noise margin, enhanced read/write performance, and reduced power dissipation, indicating that the cell is well-suited for low-power and high-density SRAM applications in advanced CMOS technologies.

#### • TFET-Based Robust 7T SRAM Cell for Low Power Application, 2019

Sayeed Ahmad, Syed Afzal Ahmad, Mohd Muqeem, Naushad Alam, and Mohammad Hasan [1] proposed a novel 7-transistor (7T) SRAM cell utilizing Tunnel Field-Effect Transistors (TFETs) to achieve ultra-low power consumption. The design incorporates a dual-pocket double-gate TFET (DP-DGTFET) structure, enhancing drive current and reducing ambipolarity compared to conventional TFETs. This configuration improves read and write stability, achieving a significant increase in read static noise margin (RSNM) and write static noise margin (WSNM). Additionally, the proposed cell demonstrates reduced write delay and lower leakage power, making it suitable for energy-efficient memory applications in advanced CMOS technologies. Simulation results indicate that the DP-DGTFET-based 7T SRAM cell outperforms traditional 6T SRAM cells in terms of power consumption and stability metrics, highlighting its potential for low-power electronic devices.

### A 2T1C Embedded DRAM Macro with No Boosted Supplies Featuring a 7TSRAM-Based Repair and a Cell Storage Monitor, 2012

Ki Chul Chun, Wei Zhang, Pulkit Jain, and Chris H. Kim [21] introduced a logic-compatible embedded DRAM (eDRAM) macro that operates without the need for boosted supplies. The design utilizes a 2T1C gain cell comprising an asymmetric 2T cell and a coupling PMOS capacitor, ensuring proper operation even without a boosted supply by leveraging beneficial coupling for read and preferential boosting for write. To enhance reliability, a repair scheme based on a single-ended 7T SRAM is employed, featuring local differential write and shared control with the main 2T1C array. Additionally, a storage voltage monitor is proposed to track the retention characteristics of the gain cell eDRAM under process, voltage, and temperature (PVT) variations, allowing for adaptive adjustment of the refresh rate. A 128 kb eDRAM test chip implemented in a 65 nm low-power process operates at a random access frequency of 714 MHz with a static power dissipation of 161.8  $\mu$ W per megabit for a 500  $\mu$ s refresh rate at 1.1 V and 85°C.

#### Low Power and Robust 7T Dual-Vt SRAM Circuit, 2008

S. A. Tawfik and V. Kursun [33] proposed a dual-threshold voltage (Vt) 7-transistor (7T) SRAM cell designed to enhance read stability and reduce leakage power consumption. The design employs a dual-Vt scheme, utilizing low-Vt transistors in critical paths to improve performance and high-Vt transistors in non-critical paths to reduce leakage. This approach effectively balances the trade-off between speed and power consumption. Simulation results demonstrate that the proposed 7T SRAM cell achieves improved read static noise margin (RSNM) and write static noise margin (WSNM) compared to conventional 6T SRAM cells, while also reducing leakage power. The design is suitable for low-power applications requiring high data stability and reduced leakage currents.

#### • A 32-nm Subthreshold 7T SRAM Bit Cell with Read Assist, 2017

S. Gupta, K. Gupta, and N. Pandey [22] proposed a 7-transistor (7T) SRAM cell optimized for subthreshold operation at the 32 nm technology node. The design addresses the limitations of conventional 6T SRAM cells, which suffer from read-write conflicts and degraded performance at low supply voltages. The proposed 7T cell incorporates a read-assist mechanism to enhance read stability and performance in the subthreshold region, operating reliably down to 0.4 V. This architecture achieves improved dynamic write ability and reduces power consumption by lowering the data retention voltage. The cell occupies an area of  $0.254 \, \mu\text{m}^2$  per bit, making it suitable for low-power and area-constrained applications.

### Power-Aware Source Feedback Single-Ended 7T SRAM Cell at Nanoscale Regime, 2017

C. Roy and A. Islam [23] proposed a low-power and highly stable single-ended 7-transistor (SE7T) SRAM cell incorporating a source feedback mechanism. This design aims to address the challenges of increased leakage power and reduced stability in nanoscale CMOS technologies. By introducing a source feedback transistor, the cell enhances read stability and write ability without significantly increasing the area. Monte Carlo simulations demonstrate that the proposed SE7T SRAM cell achieves improved static noise margins and reduced leakage power compared to conventional 6T and 7T SRAM cells. These characteristics make it a promising candidate for low-power and reliable memory applications in advanced CMOS technologies.

# • A Stable 2-Port SRAM Cell Design Against Simultaneously Read/Write-Disturbed Accesses, 2008

Suzuki et al. [24] addressed the critical challenge of maintaining stability in 2-port SRAM cells during simultaneous read and write operations, which can lead to read/write-disturbed accesses and compromise data integrity. To mitigate this issue, the authors proposed an innovative cell biasing technique that controls the cell's ground level (VSSM) using a dual-V<sub>DD</sub> approach combined with a reduced write bit-line (WBL) precharge scheme. This design was implemented in an 8-transistor (8T) 2-port SRAM cell using 65 nm CMOS technology.

# Schmitt Trigger-Based Single-Ended 7T SRAM Cell for Internet of Things (IoT) Applications, 2018

Sanapala, Sakthivel, and Yeo [25] proposed a Schmitt trigger-based single-ended 7T SRAM cell specifically designed for ultra-low voltage (ULV) applications in the Internet of Things (IoT) domain. The design employs a Schmitt trigger inverter to improve noise immunity and incorporates dynamic body biasing to optimize threshold voltages under varying conditions. Operating at 0.3 V using 45 nm CMOS technology, the cell demonstrates enhanced read static noise margin (RSNM), achieving over 22% improvement compared to conventional 6T, 7T, 8T, and 11T SRAM designs. Furthermore, the proposed cell exhibits more than 44% and 63% reductions in write and read energy consumption, respectively. Its single-ended architecture allows for energy-efficient operation while maintaining stability across different process, voltage, and temperature (PVT) variations. The authors also introduced a new performance evaluation metric, SNM per unit Area to Energy Ratio, with the proposed cell outperforming others in this regard, making it highly suitable for low-power and stable memory operations in IoT applications.

Single-Ended Boost-Less (SE-BL) 7T Process Tolerant SRAM Design in Subthreshold Regime for Ultra-Low-Power Applications, 2016 C. B. Kushwah, S. K. Vishvakarma, and D. Dwivedi [26] introduced a novel 7-transistor (7T) SRAM cell architecture, termed Single-Ended Boost-Less (SE-BL), tailored for ultra-low-power applications operating in the sub-threshold regime. This design eliminates the need for boosted supply voltages, thereby reducing power consumption and simplifying the power delivery network. The SE-BL SRAM cell employs a single-ended read/write mechanism, which not only conserves energy but also enhances read stability and write ability. Comprehensive simulations demonstrate that the SE-BL design exhibits superior performance metrics, including reduced read power consumption and lower standard deviation in read access times, compared to conventional SRAM cells. These attributes make the SE-BL 7T SRAM cell a promising candidate for energy-efficient memory solutions in nanoscale technologies, particularly for applications where power efficiency is paramount.

Single Bit Line Accessed High-Performance Ultra-Low Voltage Operating 7T SRAM Bit Cell with Improved Read Stability, 2021

B. Rawat and P. Mittal proposed a 7-transistor (7T) static random-access memory (SRAM) bit cell designed for ultra-low voltage operation, specifically at 300 mV, using a 32 nm technology node. The design utilizes a single bit-line for both read and write operations, which simplifies the peripheral circuitry and reduces the activity factor during memory access. This single-ended architecture contributes to lower power consumption and improved energy efficiency.

• Single Bit-Line 7T SRAM Cell for Near-Threshold Voltage Operation with Enhanced Performance and Energy in 14nm FinFET Technology, 2016

Y. Yang, H. Jeong, Seung Chul Song, Joseph Wang, Geoffrey Yeap, and Seong-Ook Jung [27] introduced a 7-transistor (7T) SRAM cell optimized for near-threshold voltage (NTV) operation, implemented in 14 nm FinFET technology. The design employs a single bit-line for both read and write operations, simplifying the peripheral circuitry and reducing power consumption. A key innovation is the disconnection of the read path from the internal storage

nodes, effectively eliminating read disturbances and enhancing read stability. This architecture allows for reliable operation at reduced supply voltages, achieving significant improvements in energy efficiency and performance. The proposed cell demonstrates enhanced static noise margins and reduced variability, making it highly suitable for low-power applications in advanced technology node.

#### 2.2 RESEARCH GAP

Over the years, 7T SRAM cells have emerged as strong candidates for ultra-low-power and high-stability memory design in advanced CMOS and emerging device technologies. The reviewed literature spans a broad spectrum, including performance enhancement techniques (Rawat et al., 2021), security features (Giterman et al., 2019), low-voltage operation (Ansari et al., 2015; Asli & Taghipour, 2017), FinFET integration, and novel device-level technologies like TFETs (Ahmad et al., 2019) and HETTs (Lee et al., 2013). Despite these advancements, several significant research gaps remain.

Firstly, power and energy efficiency continue to be major challenges. While several designs introduce single-ended access (e.g., Yang et al., 2016; Kushwah et al., 2016) and boosted-less architectures to reduce dynamic and leakage power, these often suffer from trade-offs such as reduced read/write speed or increased area overhead. The integration of energy-efficient features like power gating (as in Chun et al., 2012) still lacks universal compatibility across multiple operating regimes. There remains a need for standardized, scalable methods to achieve consistent energy reductions in both active and standby modes without degrading performance.

Secondly, stability under near-threshold and sub-threshold operation is another open area. Near-threshold designs (e.g., Oh et al., 2021; Sanapala & Yeo, 2018) show promise but often struggle to simultaneously maintain high read/write margins and low latency. Read-disturb issues are partially addressed through decoupling techniques and read-assist circuits, but in many cases, this increases complexity or adds transistors, affecting area and yield. Techniques such as Schmitt Trigger integration (Sanapala & Yeo, 2018) or security-focused cell layouts (Giterman et al., 2019) provide local improvements, but a holistic approach that balances speed, energy, and robustness under voltage scaling is still missing.

Thirdly, process variation and technology scaling pose enduring challenges. Designs in sub-32nm nodes (e.g., Gupta et al., 2017; Rawat & Mittal, 2021) are heavily impacted by

threshold voltage fluctuations and manufacturing inconsistencies. Though some cells use dual-Vt strategies (Tawfik & Kursun, 2008) or FinFET architectures (Ansari et al., 2015) to address these, variation-aware assist schemes and adaptive body biasing remain underexplored for the 7T topology.

Fourth, device-level innovation using emerging technologies like TFETs and HETTs (Ahmad et al., 2019; Lee et al., 2013) presents new opportunities but also introduces new issues. While such devices promise steep subthreshold swings and low leakage, they often suffer from limited current drive, leading to write failures or increased delay. Moreover, the circuit-compatibility and variability of these novel devices under practical conditions are not yet fully understood.

Finally, scalability and integration into large memory arrays is another underdeveloped area. Though several papers focus on individual cell behavior and bit-level performance, few explore how these designs behave at macro-scale integration. Problems such as half-select disturbance (Suzuki et al., 2008), bit-interleaving complexity (Oh et al., 2021), and write-line contention are yet to be fully addressed. Integration with repairability features (Chun et al., 2012) and peripheral circuit co-design is an avenue still requiring deeper exploration.

# CHAPTER 3 CHARACTERISTIC COMPARISON FOR DIFFERENT 7TSRAM CELLS

The performance and characteristics of 7T SRAM cells vary depending on the specific design, process node, and application requirements. However, 7T SRAM cells are generally designed to offer improvements over conventional 6T cells by addressing limitations in power consumption, stability, and leakage. The key modification in a 7T SRAM cell is the addition of a seventh transistor, typically used to decouple the read path from the storage nodes. This enhances read stability by preventing read disturbance. Additionally, single-ended or gated write mechanisms are often employed to reduce dynamic power during write operations. The 7T SRAM cell tends to offer better read stability and lower power consumption compared to the traditional 6T cell, albeit at the cost of a slight area overhead. Because it typically has only one bit line and more complex control logic, write speed can be slightly lower in some implementations. Overall, 7T SRAM cells are especially suitable for low-power and sub-threshold applications where stability and energy efficiency are more critical than access speed.

The 7T SRAM cell includes an additional transistor compared to the standard 6T design, which introduces some complexity and a slight impact on write speed. This extra transistor mainly serves to decouple the read path from the storage nodes, significantly improving read stability by reducing read disturbances common in 6T cells. While the write speed can be somewhat slower due to single-ended write operations, the 7T cell benefits from lower power consumption through reduced leakage currents and selective bit line switching. Although the added transistor increases the silicon area slightly, this trade-off is justified by enhanced stability and improved energy efficiency, making 7T SRAM cells suitable for low-power and sub-threshold applications.

This chapter is organized into seven sections. The first section (3.1) provides an overview of SRAM cells, discussing conventional 7T SRAM cells alongside the proposed 8T SRAM cell. The second section (3.2) details the dimensions of all the cells, highlighting the technology node used and the differing sizes of pull-down, pull-up, and access transistors. Section 3.3 focuses on transient analysis, evaluating the dynamic behavior of the SRAM cells during read and write operations. The fourth section (3.4) addresses data stability,

presenting butterfly curves for HSNM, RSNM, and WSNM to assess noise robustness and ensure reliable functioning. The fifth section (3.5) compares the power consumption of each cell. Finally, the sixth section (3.6) analyzes and compares the read and write delays of the cells.

#### 3.1 OVERVIEW OF SRAM CELLS

SRAM cells are a kind of semiconductor memory commonly used in computers, microprocessors, and various digital electronics. Unlike dynamic RAM (DRAM), which needs constant refreshing to maintain data, SRAM holds information as long as it receives power. SRAM is recognized for its quick access speeds, low energy use, and ability to retain data without needing to be refreshed continuously.

An SRAM cell usually comprises transistors organized in a flip-flop structure. A concise summary of its components and how it operates is shown below:

- a) Cross-Coupled Inverter Pair: At the core of an SRAM cell are two cross-coupled inverters that create a flip-flop. Each inverter is made up of a PMOS (P-channel Metal-Oxide-Semiconductor) transistor and an NMOS (N-channel Metal-Oxide-Semiconductor) transistor.

- **b) Bitlines:** The flip-flop is linked to two bitlines, called the "bitline" and the "bitline bar" (its complement). These bitlines facilitate reading from and writing data to the SRAM cell.

- **c) Wordlines:** The wordline controls access to the SRAM cell. When activated, it allows data to be transferred between the bitlines and the flip-flop.

- d) Access Transistors: Access transistors are key components of SRAM, widely used for fast, volatile data storage in electronic devices. They act as switches controlling the connection between storage nodes and bitlines, enabling reading and writing of data. During a read operation, access transistors link the stored data to the bitlines so voltage levels can be sensed. In a write operation, they provide a path for current to update the storage nodes. These transistors are designed for rapid switching and low leakage, ensuring reliable and efficient data access.

SRAM cells are arranged in arrays to form larger memory banks. The cell size depends on the technology node and design needs—smaller cells increase memory density but may raise challenges in power use and stability. Due to their fast and efficient random access, SRAM cells are ideal for cache memory, register files, and other speed-critical, low-power application.

#### 3.2 Different 7T SRAM cells

Various 7T SRAM Architectural Configurations" examines many 7-transistor (7T) Static Random-Access Memory (SRAM) cell designs optimized for enhanced stability, performance, and power efficiency in modern electronic systems. This configuration aims to solve critical concerns such as leakage currents, read stability, and write access times. 7T SRAM architectures exhibit greater resilience to noise and unpredictability compared to conventional 6T systems because to their utilization of more transistors, making them suitable for low-power, high-speed applications. This paper provides a comparative analysis of SRAM configurations to aid designers in selecting optimal designs for certain applications, highlighting trade-offs in space, energy consumption and reliability.

#### 3.2.1 Differential Ended and Differential Port

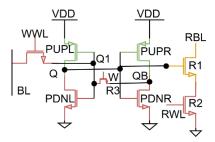

The transistor-level circuit for a differential-ended, single-port 7T cell (7TDEDPA) reported by Aly and Bayoumi in 2007 [6]. It uses an inverter pair (PUPL-PDNL, PUPR-PDNR) with an NMOS transistor (R1) controlled by signal W to enable write operation by connecting/disconnecting the feedback. The cell supports differential read and single-ended write operations.

**Fig. 3.1** Schematic Diagram For (a)7TDESPA, (b)7TDESPGi, (c)7TDEDPL, (d)7TDEDPC, (e)7TSEDPT, (f)7TSEDPG, (g)7TSEDPR, (h)7TSEDPS, (i)7TSESPK, (j)7TSESPRt

The 7TDESPGi bit cell, proposed by Giterman et al. (2018), features a PMOS transistor (R1) controlled by the EQ signal for equalization during write operations [8]. The write process has two stages: removing VDD and activating R1 for voltage equalization and charge sharing, reducing power usage, followed by activating access transistors (ACL and ACR) to complete the write.

#### 3.2.2 Differential Ended 7T SRAM Bit Cell with the Isolated Read Port

In 2017, Liu et al. introduced asymmetric 7T SRAM (7TDEDPL) with an additional read port linked to the QB node via NMOS transistor R1 [9]. This design improves read stabilization but reduces drive current, impacting write performance. The read process involves QB enabling RBL discharge through R1 to the RWL.

In 2012, Chun et al. introduced the 7TDEDPC [10] bit cell using PMOS transistors as access transistors to reduce write power losses. However, PMOS requires a negative bias voltage,

increasing variability and silicon area due to the large charge pump, making PMOS access transistors less favourable for practical applications

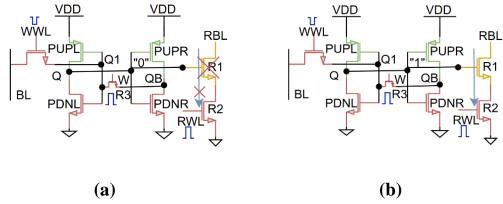

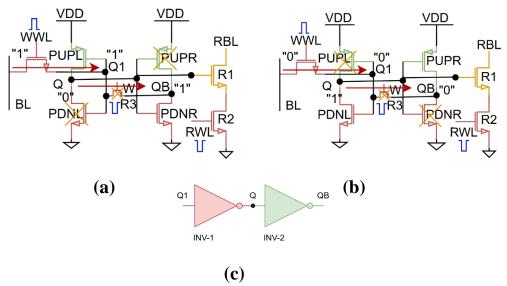

#### 3.2.3 Single-Ended Dual Port 7T SRAM Bit Cells

In light of the increasing need for portable devices, the ability to integrate circuits with ultralow power is a major focus. Therefore, it has now become critical to cut back on both active power and leakage power. Two key methods of power minimization are: (1) The supply voltage (VDD) is decreased, which has a squared effect on the active power, and (2) The activity factor is reduced; hence, the dynamic power of the circuit is also reduced. The 7TSEDPT memory cell in Figure 1e uses a cross-coupled inverter pair with three HVTH and one LVTH MOS transistor. It suffers from reduced write performance due to single-ended write mechanisms [12]. Gupta et al. introduced the 7TSEDPG [13] cell in 2017, which features a dual-port architecture to resolve read-write conflicts and improve write stability at the cost of reduced read stability, requiring a read-assist circuit. In 2017, Roy et al. proposed the 7TSEDPR [14] bit cell, optimizing dynamic power by reducing bit-line activity. Its isolated read path with PMOS (R2) and NMOS (R3) en-hances stability and resists soft errors. Supply feedback lowers write power, but the negatively biased PMOS requires a charge pump, increasing silicon area. In 2008, Suzuki et al. introduced the 7TSEDPS SRAM bit cell, which shares a similar architectural design to the 7TSEDPT bit cell [12]. Figure 1h illustrates the transistor-level schematic of the 7TSEDPS [16] design. How-ever, a key drawback of this approach is its challenge in maintaining strong write ability for logic '1' due to using a pass-transistor-based single-ended port.

#### 3.2.4 Single-Ended Single Port 7T SRAM Bit Cell

In some cases, the main goal of the circuit design is to economize cost, and parallelism is not the aim. Then, using a multi-port bit cell will only increase the area and the power overheads. In such a case, the single-ended, single port bit cell is more effective due to the reasons: (1) the on-chip area is smaller, (2) there is less activity factor, and (3) less circuit capacitance, which in turn reduces the total power dissipation, of the cell. In 2015, Kushwah et al. introduced the 7TSESPK [17] SRAM cell with a single bit-line and feedback disconnection for improved write ability. Controlled by WWL and NMOS transistors, it features a cross-coupled inverter core. However, disconnecting the left inverter causes the Q node to float, increasing susceptibility to write errors and disturbances. In 2021, Rawat and Mittal

introduced the 7TSESPRt [18] cell with a single-ended, single-port topology. Its core uses coupled inverters with an NMOS transistor (R1) to disconnect feedback. Access transistors (ACR, ACW) manage read/write operations. Despite its design, 7TRt is prone to read errors due to read current discharging through the data node.

#### 3.3 CELL SIZING

The table presents the transistor sizing (in nm) for various 7T SRAM cell designs categorized by their configurations: Differential-Ended Single Port (DE-SP), Differential-Ended Dual Port (DE-DP), and Single-Ended Single Port (SE-SP). Each cell is labeled (e.g., 7TDESPA, 7TSESPK), and key transistors are sized: pull-up (PUPL/PUPR), pull-down (PDNL/PDNR), and access transistors (ANL/ANR/ANW). Some cells include additional transistors (R1, R2) for enhanced read stability or write performance. For instance, the 7TDESPGi cell uses larger ANL and ANR to improve access, while the 7TSESPK features a wide write-access transistor (ANW = 480 nm), optimizing write ability. Missing values (indicated as "----") reflect design simplifications or inactive paths. The variation in transistor sizing across cells indicates targeted optimizations for read stability, write ability, and power efficiency, depending on application needs. Overall, this table supports comparative analysis of 7T SRAM topologies to guide design decisions in low-power and high-performance memory applications.

**Table 3.1** Dimension of Various 7T SRAM cells

| CTD 4 T | CDITO    | DIIDI | DDATE | DIIDD | DDAID |     | 4.375 | 4.37 | - To 4 |     |

|---------|----------|-------|-------|-------|-------|-----|-------|------|--------|-----|

| SRAN    | I CELLS  | PUPL  | PDNL  | PUPR  | PDNR  | ANL | ANR   | AN   | R1     | R2  |

|         |          |       |       |       |       |     |       | W    |        |     |

| DE-DP   | 7TDESPA  | 120   | 310   | 120   | 395   | 240 | 120   |      | 240    |     |

|         | 7TDESPGi | 120   | 240   | 120   | 240   | 480 | 240   |      | 120    |     |

| DE-SP   | 7TDEDPL  | 120   | 310   | 120   | 180   | 480 | 240   |      | 240    |     |

|         | 7TDEDPC  | 120   | 310   | 120   | 240   |     |       |      | 240    | 240 |

| SE-DP   | 7TSESPT  | 120   | 180   | 180   | 180   | 480 |       |      | 240    | 240 |

|         | 7TSESPR  | 120   | 240   | 120   | 240   | 180 |       |      | 120    | 240 |

|         | 7TSESPS  | 120   | 310   | 120   | 180   | 366 |       |      | 240    | 240 |

|         | 7TSESPSa | 120   | 180   | 120   | 180   | 240 | 240   |      | 240    |     |

| SE-SP   | 7TSESPK  | 120   | 310   | 360   | 240   |     | 240   | 480  | 120    |     |

|         | 7TSESPY  | 120   | 180   | 120   | 180   | 180 |       |      | 120    | 120 |

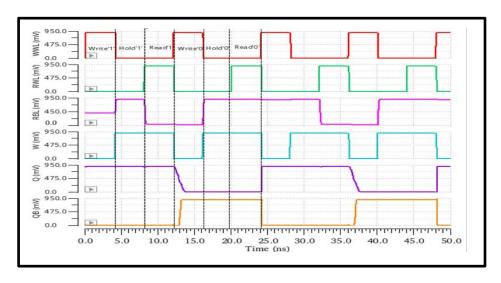

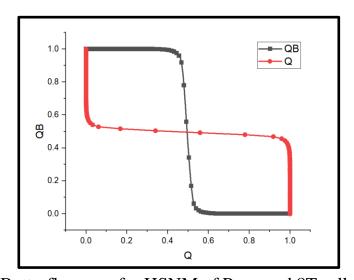

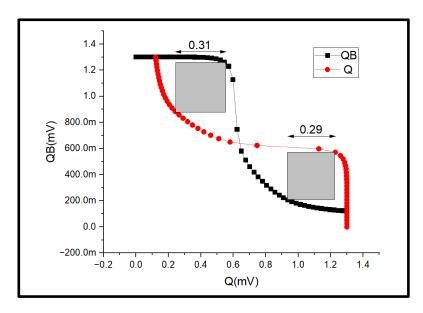

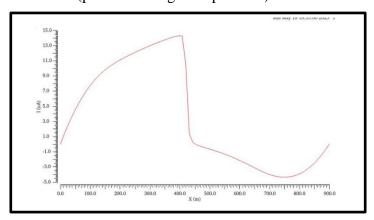

To verify the correct execution of hold, read, and write operations, transient (time-domain) simulations were carried out on all three SRAM models. The simulations utilized consistent read/write control signals, uniform input data patterns, and identical precharge signals for both read and write bitlines. This uniformity ensured a fair basis for comparison. Moreover, the same sense amplifiers, precharge circuits, and write drivers were integrated across all models to guarantee the reliability and consistency of the performance evaluation. The simulation outcomes are illustrated in Fig. 3.5.