# GRID SYNCHRONIZATION AND OPERATION OF PARALLEL INVERTERS

### DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE AWARD OF THE DEGREE OF

# **DOCTOR OF PHILOSOPHY**

Submitted by:

Aditya Narula

(Roll no. 2K16/PhD/EE/07)

Under the supervision of

Prof. Vishal Verma

# DEPARTMENT OF ELECTRICAL ENGINEERING

# DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

# GRID SYNCHRONIZATION AND OPERATION OF PARALLEL INVERTERS

### DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE AWARD OF THE DEGREE OF

# **DOCTOR OF PHILOSOPHY**

Submitted by:

Aditya Narula

(Roll no. 2K16/PhD/EE/07)

Under the supervision of

Prof. Vishal Verma

# DEPARTMENT OF ELECTRICAL ENGINEERING

# DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042 **DECLARATION**

I, ADITYA NARULA (2K16/PhD/EE/07) hereby declare that the work, which

is being presented in the project report entitled, "GRID SYNCHRONIZATION

AND OPERATION OF PARALLEL INVERTERS" submitted for partial

fulfillment of the requirements for the award of the degree of Doctor of

Philosophy is an authentic record of my own work carried out under the able

guidance of Dr. VISHAL VERMA, Professor, EED, DTU. The matter embodied in

the dissertation work has not been plagiarized from anywhere and the same has

not been submitted for the award of any other degree or diploma in full or in part.

Submitted by: -

ADITYA NARULA

(2K16/PhD/EE/07)

**Electrical Engineering Department**

ii

#### DEPARTMENT OF ELECTRICAL ENGINEERING

### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

# **CERTIFICATE**

This is to certify that the thesis entitled, "GRID SYNCHRONIZATION AND OPERATION OF PARALLEL INVERTERS", submitted by Mr. ADITYA NARULA, Roll No. 2K16/PhD/EE/07, student of Doctor of Philosophy in Electrical Engineering Department from Delhi Technological University (Formerly Delhi College of Engineering), is a dissertation work carried out by him under my guidance during session 2016-2024 towards the partial fulfillment of the requirements for the award of degree of Doctor of Philosophy.

The uniqueness of the thesis pertains to the incorporation of impedance on the DC link of the inverter to limit the circulating current among the inverters, additionally the synchronization and resynchronization algorithm with superior dynamic performance, which has not been reported elsewhere. I wish him all the best in his endeavors.

(Dr. VISHAL VERMA)

Professor, EED, DTU

SUPERVISOR

## ACKNOWLEDGMENT

It is my pleasure to be indebted to various people, who directly or indirectly contributed to the development of this work and who influenced my thinking and behavior during study. Firstly, I would like to express my deep gratitude to my esteemed supervisor **Prof. Vishal Verma** for his invaluable guidance, constant encouragement with praise, effective criticism by example and for creating an environment so conducive for learning. His ability to manage students amidst his administrative work is something which puzzles so many people around. He showed me different ways to approach a research problem and the need to be persistent to accomplish any goal. His wide knowledge and his logical way of thinking have been of great value for me. His understanding, encouraging and personal guidance have provided a good basis for the present thesis.

I thank my comprehensive examination and DRC committee members: Prof. Bhim Singh (IIT Delhi), Prof. Sukumar Mishra (IIT Delhi), Prof. Pragati Kumar, for guiding me throughout my research work.

I am extremely grateful to authorities of Delhi Technological University (DTU) for providing me cutting edge technology and valuable resources to carry out my research work.

I would like to extend thanks to my colleagues Dr. Amritesh Kumar, Dr. Ramesh Singh, Dr. Ritika Gour, Ms. Vandana Arora, Mr. Shirish Raizada and Mr. Anil Butola for their support and cooperation from time to time during my Ph.D tenure. I would also like to thank Mr. Tarun, Mr. Sarthak for their kind assistance throughout my Ph.D.

My heartfelt thanks to my father and mother for their constant motivation and support during various phases of Ph.D. It is very difficult to find the right words to express my gratitude towards my wife, Pankhuri Asthana, their support without any complaint or

regret has enabled me to complete this Ph.D. thesis. I extend my very sincere and

special thanks to the two of them for their love, understanding, support, endless

patience, tolerance during the writing of this thesis and encouragement when it was

most required.

And last, but certainly not least, my sincere thanks to all people who have helped

directly or indirectly towards the completion of this thesis.

Above all, I thank God for everything.

Above all, I wish to deeply thank God for his blessings and providing me the strength

to complete my Ph.D.

Mr. Aditya Narula Delhi Technological University

New Delhi

V

# GRID SYNCHRONIZATION AND OPERATION OF PARALLEL INVERTERS

## **ABSTRACT**

With rapid industrialization in developing nations, the power demand from the end consumer has exponentially grown. To support the conventional power generation sources (based on fossil fuels) in meeting the rising power demand, power generation based on Distributed Energy Resources (DER's) enacting as small power sources are gaining popularity. The microgrid architecture with local energy generating sources like photovoltaic, wind, battery systems have opened the pathway for small scale smart distribution grids interfacing the sustainable and clean energy sources with the grid through a voltage / current controlled voltage source inverter. Interfacing a voltage sourced inverter with the grid additionally allows the inverter to support the power quality of grid during grid sag and swell condition. Further based on the power demand at the consumer end the number of interfacing inverters can be added or reduced allowing a scale up or scale down approach in the connected network. The response and dynamics of the microgrid are governed by three major factors -1) The dynamics of the renewable energy source at the DC side, 2) the synchronization dynamics of the interfaced inverter, 3) Control technique of the interfacing inverter and 4) Effect of high penetration of the low inertial inverters with high switching frequency.

The interfacing voltage source inverter is vulnerable to disturbance from both grid side and the renewable energy source or input side, with common intermittencies like partial shading of the photovoltaic panel, different wind speeds, low battery voltages etc. The disturbances at the grid side can be controlled through the control technique of the interfacing inverter or a synchronization algorithm with fast tracking capability. On the DC side the conventional practice is to use a non-isolated boost or buck converter based upon the series parallel combination of the installed solar panels. Conventional converters like buck converter or boost converter struggle with the operating duty requirement at time of partial shading, with the operating duty reaching the nonlinear region, thereby compromising on the operating efficiency. Also, addition of the natural output impedance network through the interfacing

converter will help in mitigating the spike and transients in the DC link and the control signals during intermittencies at either grid side or input side. This would result in smooth running of the inverter.

A VSI interfaced with the renewable energy source typically has low inertia due to lack of moving parts unlike a synchronous generator. As a result, the system remains sensitive towards grid frequency variations. With multiple injection of VSI in the system, the inertia of the system would not increase making the system vulnerable unless and until a fast control on frequency change is not incorporated or virtual inertia is embedded, even though such arrangement provides better reliability. With paralleled VSI having different situations on the connected nodes the response to the change of voltage or frequency often lead to issues of circulating current and large variations during transients due to lack of inertia or damping system. For parallel combination of inverters aligned with the stringent grid codes, synchronization algorithm plays a crucial role. Noncompliance of the code would result in outage of the inverter. The stability of synchronization algorithm dictates the capability dictates the capability of the parallel operation of the inverter especially during off grid mode of operation in master slave configuration. The synchronization algorithms like zero crossing detection (ZCD), voltage unit template-based algorithms and SRF - PLL provide the requisite tracking but suffer immensely during grid disturbances. SOGI adaptive filter based PLL with filtering capability has a superior tracking and filtering capability when compared to conventional PLL. Moreover, the capability of the SOGI filter to generate orthogonal signals eliminates the requirement of Clarke's transformation reducing the complexity and computation of the algorithm.

The work proposes impedance based continuous input current converters for photovoltaic and battery charging applications. The same have been modelled; simulated and experimentally validated under various test conditions. The impedance network allows auxiliary boost supporting the system under severe conditions like partial shading, irradiance change and battery deep discharge. Additionally, the impedance network installed at the input side of the inverter limits the flow of circulating current within the system.

Synchronization algorithm based on Second Order Generalized Integrator (SOGI) resonating at 100Hz is proposed and experimentally validated for severe grid disturbances. The synchronization algorithm enhances the fault bearing capability of the inverter allowing it to remain synchronized with the grid with minimum transients. A resynchronization algorithm embedded in the Second Order Generalized Integrator Phase Locked Loop (SOGI – PLL) is proposed in the work working with adaptive droop filter. The resynchronization algorithm seamlessly transfers the inverter from grid forming mode to grid connected mode and vice versa while limiting the circulating current among the inverters. The resynchronization algorithm limits the transitional spikes besides administering fast dynamics with prominent signal filtering.

The development of algorithm and hardware including development of various control and interface cards have been indigenously done. The simulation and hardware results are presented which show good agreement with the theoretical modeling and analysis.

# TABLE OF CONTENTS

| Declaration       | ü                                                            |

|-------------------|--------------------------------------------------------------|

| Certificate       |                                                              |

| Acknowledgmen     | tiv                                                          |

| Abstract          | vi                                                           |

| Table of Content  | isix                                                         |

| List of Figures   | xxi                                                          |

| List of Tables    | xxxi                                                         |

| List of Abbreviat | ionsxxxii                                                    |

| CHAPTER-1         | INTRODUCTION1                                                |

|                   | 1.1 General                                                  |

|                   | 1.2 Solar Photovoltaic System: Issues and Opportunities      |

|                   | 1.3 PV String and Arrays : Challenges                        |

|                   | 1.4 Converter/Inverter Configurations for the PV System 5    |

|                   | 1.5 DC – DC Converter                                        |

|                   | 1.6 Voltage Sourced Converter                                |

|                   | 1.6.1 Voltage Sourced Inverter - Configurations9             |

|                   | 1.6.2 Control Techniques of the Voltage Sourced Inverter 10  |

|                   | 1.6.2.1 Hysteresis Current Control                           |

|                   | 1.6.2.2 Pulse Width Modulated Control11                      |

|                   | 1.7 Parallel Operation of Inverters                          |

|                   | 1.8 Synchronization and Resynchronization                    |

|                   | 1.9 Scope of the work:                                       |

|                   | 1.9.1 Wide Operating impedance Converter for Photovoltaic 17 |

|                   | 1.9.2 Bidirectional Impedance Source Converter for ESS 17    |

|                   | 1.9.3 Interfacing Impedance Converter with the Distribution  |

|                   | Grid and Impact of Impedance Converter on the Grid           |

|                   | Disturbances                                                 |

|               | 1.9.4 Fast Tracking Synchronization Algorithm for Grid       |      |

|---------------|--------------------------------------------------------------|------|

|               | Synchronization                                              | 18   |

|               | 1.9.5 Resynchronization Algorithm                            | 18   |

|               | 1.10 Organization of Thesis                                  | 19   |

| CHAPTER – 1I  | LITERATURE REVIEW                                            | 21   |

|               | 2.1 General                                                  | 21   |

|               | 2.2 Survey of the Literature for PV Fed System               | 22   |

|               | 2.2.1 Solar PV Balanced System                               | 22   |

|               | 2.2.2 MPPT Techniques for PV system                          | 23   |

|               | 2.2.3 MPPT Charge Controllers                                | 23   |

|               | 2.2.4 Bi – Directional Converter                             | 25   |

|               | 2.3 Grid Connected Voltage Source Inverters                  | 26   |

|               | 2.3.1 Synchronization Algorithm                              | 26   |

|               | 2.3.2 Resynchronization Algorithm                            | 28   |

|               | 2.3.3 Two / Single Stage Grid Connected PV Inverters and the | heir |

|               | Parallel Operations                                          | 29   |

|               | 2.4 Research Gap                                             | 30   |

| CHAPTER – II1 | WIDE OPERATING DC – DC IMPEDANCE CONVERTER FOR               |      |

|               | PHOTOVOLTAIC APPLICATION                                     | 34   |

|               | 3.1 Problem Formulation                                      | 34   |

|               | 3.2 Proposed Wide Operating Range Continuous Input Current   |      |

|               | Impedance Network Converter                                  | 35   |

|               | 3.3 Operating Modes                                          | 35   |

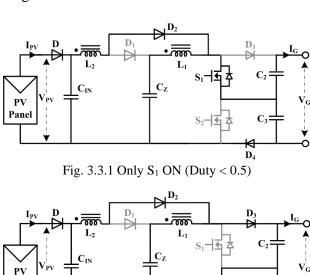

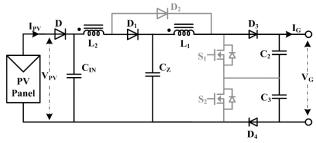

|               | 3.3.1 Operating Duty < 0.5                                   | 35   |

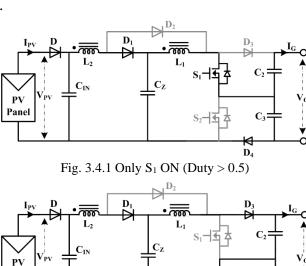

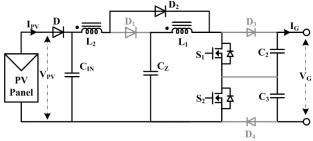

|               | 3.3.2 Operating Duty > 0.5                                   | 37   |

|               | 3.4 Converter Analysis – Voltage and Current Mode            | 39   |

|               | 3.4.1 Converter Analysis for Voltage Mode                    | 39   |

|               | 3.4.2 Converter Analysis for Current Mode                    | 40   |

|               | 3.4.3 Efficiency Analysis                                    | 42   |

|               | 3.5 MATLAB Based Simulation of Impedance Converter           | 43   |

|               | 3.5.1 Performance During Irradiance Change                   | 44   |

|               | 3.5.2 Performance During Partial Shading                     | 46   |

|              | 3.6 Experimental Analysis of Impedance Converter              | 47    |

|--------------|---------------------------------------------------------------|-------|

|              | 3.6.1 Experimental Performance During Irradiance Change       | and   |

|              | Partial Shading                                               | 47    |

|              | 3.7 Performance Analysis                                      | 50    |

|              | 3.8 Conclusion                                                | 52    |

| CHAPTER – IV | BI – DIRECTIONAL WIDE OPERATING MULTI PORT IMPEDAN            | ICE   |

|              | CONVERTER                                                     | 53    |

|              | 4.1 Problem Formulation                                       | 53    |

|              | 4.2 Proposed Bi – Directional Multiport Impedance Network .   | 53    |

|              | 4.3 Operating Modes                                           | 54    |

|              | 4.3.1 Discharging Mode                                        | 54    |

|              | 4.3.2 Charging Mode                                           | 56    |

|              | 4.4 Converter Analysis: Current Mode and Voltage Mode         | 57    |

|              | 4.4.1 Converter Analysis: Current Mode                        | 57    |

|              | 4.4.1.1 Discharging Mode                                      | 57    |

|              | 4.4.1.2 Charging Mode                                         | 59    |

|              | 4.4.2 Converter Analysis: Voltage Mode                        | 59    |

|              | 4.4.2.1 Discharging Mode                                      | 59    |

|              | 4.4.2.2 Charging Mode                                         | 60    |

|              | 4.5 Control Algorithm                                         | 61    |

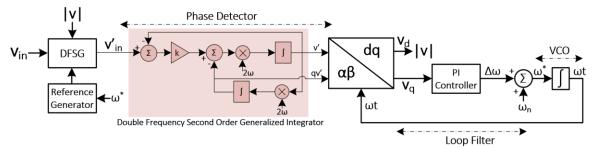

|              | 4.6 Stability Analysis of Impedance Converter                 | 62    |

|              | 4.7 MATLAB Based Simulation of Bi – Directional Impedance     | e     |

|              | Converter                                                     | 66    |

|              | 4.7.1 Transition from Discharging to Charging State           | 66    |

|              | 4.7.2 Charging Discharging at Different SoC                   | 67    |

|              | 4.8 Experimental Analysis of Bi – Directional Multiport Imped | lance |

|              | Converter                                                     | 70    |

|              | 4.8.1 Experimental Response – Discharging to Charging         | 70    |

|              | 4.8.2 Experimental Response – Different SoC                   |       |

|              | 4.9 Performance Analysis                                      |       |

|              | 4.10 Conclusion                                               |       |

|              |                                                               |       |

| CHAPTER-V    | DOUBLE FREQUENCY PHASE LOCKED LOOP FOR GRID                                                         |        |

|--------------|-----------------------------------------------------------------------------------------------------|--------|

|              | CONNECTED INVERTER                                                                                  | 76     |

|              | 5.1 Problem Formulation                                                                             | 76     |

|              | 5.2 Proposed Double Frequency Phase Locked Loop                                                     | 76     |

|              | 5.2.1 Control                                                                                       | 77     |

|              | 5.3 Analysis of Double Frequency Synchronization Algorithm                                          | 78     |

|              | 5.3.1 Stability Analysis                                                                            | 79     |

|              | 5.3.2 Transient Response                                                                            | 80     |

|              | 5.4 Experimental Analysis of Proposed Synchronization Algor                                         | ithm   |

|              |                                                                                                     | 83     |

|              | 5.4.1 Grid Perturbation – Step Frequency Change of 5Hz                                              | 83     |

|              | 5.4.2 Grid Perturbation – Step Phase Change of +30 <sup>0</sup>                                     | 83     |

|              | 5.4.3 Grid Perturbation – Step Voltage Sag of 80%                                                   | 83     |

|              | 5.4.4 Response for Pulsed Voltage Signal                                                            | 84     |

|              | 5.5 Performance Analysis                                                                            | 95     |

|              | 5.6 Conclusion                                                                                      | 97     |

| CHAPTER – VI | ADAPTIVE DROOP BASED RESYNCHRONIZATION ALGORITHM MITIGATING TRANSIENTS AND CIRCULATING CURRENTS FOR |        |

|              | GRID CONNECTED INVERTER                                                                             | 98     |

|              | 6.1 Problem Formulation                                                                             | 98     |

|              | 6.2 Proposed Adaptive Droop Control Re – Synchronization                                            |        |

|              | Algorithm for Grid Connected Inverter                                                               | 100    |

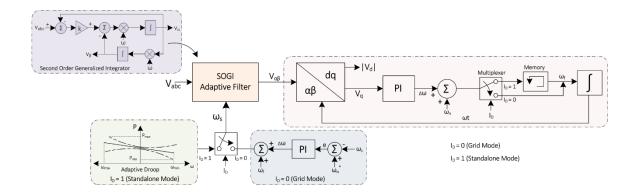

|              | 6.2.1 Control Algorithm                                                                             | 101    |

|              | 6.2.1.1 Grid Connected to Islanded                                                                  | 101    |

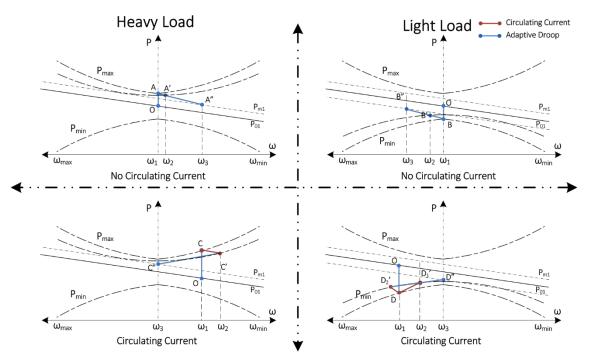

|              | 6.2.1.1.1 Heavy Loading with No Circu                                                               | lating |

|              | Current                                                                                             | 102    |

|              | 6.2.1.1.2 Light Loading with No Circulating                                                         |        |

|              | Current                                                                                             | 102    |

|              | 6.2.1.1.3 Heavy Loading in Presence Circula                                                         | ting   |

|              | Current                                                                                             | 103    |

|              | 6.2.1.1.4 Light Loading in Presence of Circul                                                       | lating |

|              | Current                                                                                             | 104    |

|              | 6.2.1.2 Islanded to Grid Connected Mode                                                             | 104    |

|                    | 6.2.2 Performance Analysis                          | 104        |

|--------------------|-----------------------------------------------------|------------|

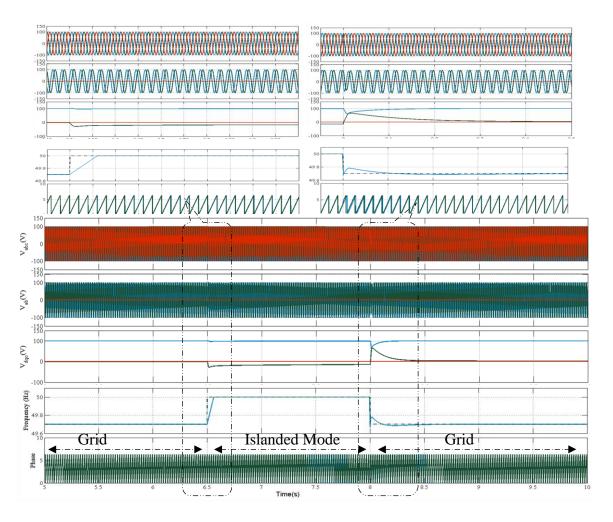

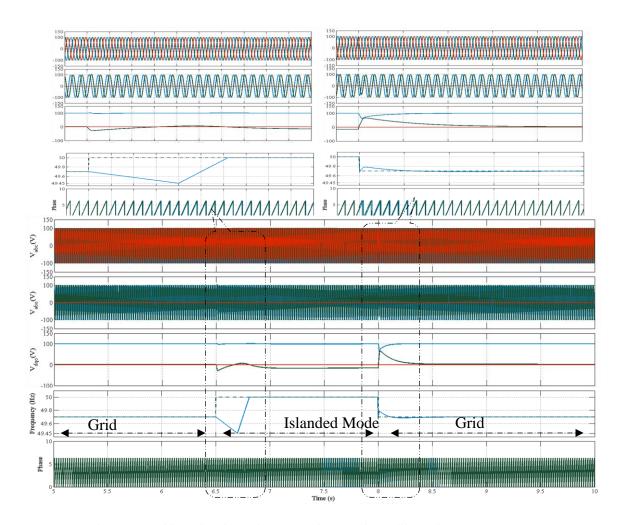

|                    | 6.2.2.1 Dynamic Response Without Circulatin         | g Current  |

|                    |                                                     | 104        |

|                    | 6.2.2.2 Dynamic Response with Circulating C         | urrent 106 |

|                    | 6.3 Conclusion                                      | 107        |

| CHAPTER – VII      | SIMULATION AND EXPERIMENTAL VALIDATION OF GR        | ID TIED    |

|                    | INVERTER                                            | 108        |

|                    | 7.1 Introduction                                    | 108        |

|                    | 7.2 Impedance Based Converter Fed Grid Connected In | verter 108 |

|                    | 7.3 Control Technique                               | 109        |

|                    | 7.4 MATLAB Based Simulation and Control             | 110        |

|                    | 7.5 Prototype – Grid Connected Inverter             | 113        |

| CHAPTER – VII      | I MAIN CONCLUSION AND SUGGESTION FOR FURTHER V      | Work 121   |

|                    | 8.1 Main Conclusion                                 | 121        |

|                    | 8.2 Future Scope of Work                            | 122        |

| REFERENCES         |                                                     | 124        |

| Bibliography       |                                                     | 131        |

| List of Publicatio | ns                                                  | 132        |

# LIST OF FIGURES

| Fig. No.   | Figure Name                                                           | Page No. |

|------------|-----------------------------------------------------------------------|----------|

| Fig. 1.1   | PV Characteristics of Photovoltaic Panel with variation of irradiance | 2        |

| Fig. 1.2   | IV Characteristics of Photovoltaic Panel                              | 3        |

| Fig. 1.3   | Photovoltaic Panel Configuration and Partial Shading                  | 4        |

| Fig. 1.4   | PV Characteristic during Partial Shading                              | 4        |

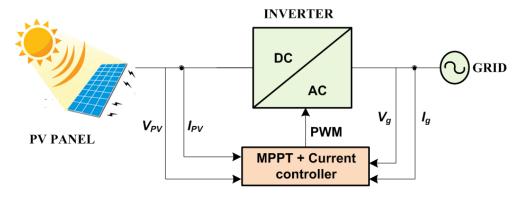

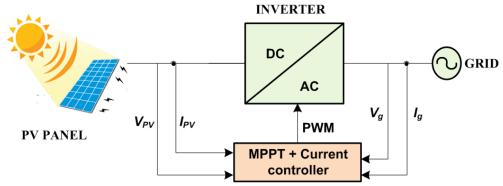

| Fig. 1.5   | Single Stage Configuration interfacing DER to Grid                    | 5        |

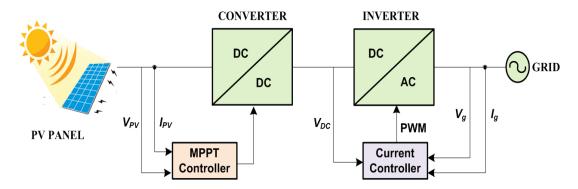

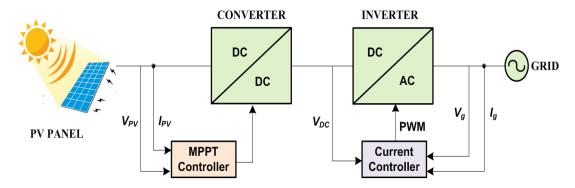

| Fig. 1.6   | Double Stage Configuration interfacing DER to Grid                    | 5        |

| Fig. 1.7   | Single Stage Configuration interfacing DER to Grid                    | 8        |

| Fig. 1.8   | Double Stage Configuration interfacing DER to Grid                    | 8        |

| Fig. 1.9   | Half Bridge Inverter Configuration                                    | 9        |

| Fig. 1.10  | 3 Phase Full Bridge Inverter Configuration                            | 10       |

| Fig. 1.11  | Hysteresis Current Control (HCC) Technique                            | 11       |

| Fig. 1.12  | SPWM Control of VSI                                                   | 12       |

| Fig. 1.13  | SPWM Control Technique                                                | 12       |

| Fig. 1.14  | Parallel Operation of Inverters                                       | 13       |

| Fig. 3.1.1 | 2/3rd Panel Shaded                                                    | 34       |

| Fig. 3.1.2 | 1/3rd Panel Shaded                                                    | 34       |

| Fig. 3.1.3 | Normal Operation                                                      | 34       |

| Fig. 3.2   | Continuous Input Current Impedance Converter                          | 35       |

| Fig. 3.3.1 | Only $S_1$ ON (Duty $< 0.5$ )                                         | 36       |

| Fig. 3.3.2 | Only $S_2$ ON (Duty $< 0.5$ )                                         | 36       |

| Fig. 3.3.3 | $S1$ and $S_2$ OFF (Duty < 0.5)                                       | 36       |

| Fig. 3.4.1 | Only $S_1$ ON (Duty $> 0.5$ )                                         | 37       |

| Fig. 3.4.2 | Only $S_2$ ON (Duty $> 0.5$ )                                                                                                                                                                                                            | 37 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 3.4.3 | $S_1$ and $S_2$ ON (Duty > 0.5)                                                                                                                                                                                                          | 37 |

| Fig. 3.5   | Inductor currents and voltages during normal operating condition                                                                                                                                                                         | 38 |

| Fig. 3.6   | Inductor currents and voltages during shoot through condition                                                                                                                                                                            | 38 |

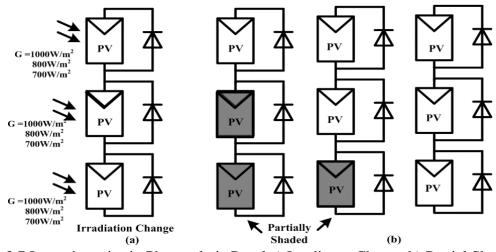

| Fig. 3.7   | intermittencies in photovoltaic panel a) Irradiance<br>Change b) Partial Shading                                                                                                                                                         | 44 |

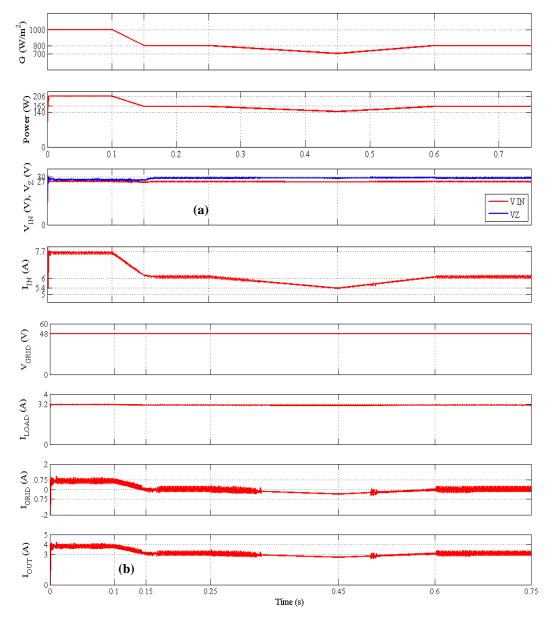

| Fig. 3.8.1 | i) Maximum Power ii) Input Voltage $(V_{IN})$ , iii) Capacitor Voltage $(V_Z)$ iv) Input Current $(I_{IN})$ under Irradiation Change                                                                                                     | 45 |

| Fig. 3.8.2 | i) Grid Voltage ii) Load Current iii) Grid Current iv)<br>Output Current under irradiation change                                                                                                                                        | 45 |

| Fig. 3.9.1 | i) Maximum Power ii) Input Voltage $(V_{IN})$ , iii) Capacitor Voltage $(V_Z)$ iv) Input Current $(I_{IN})$ under Partial Shading                                                                                                        | 46 |

| Fig. 3.9.2 | i) Grid Voltage ii) Load Current iii) Grid Current iv)<br>Output Current under Partial Shading                                                                                                                                           | 46 |

| Fig. 3.10  | Hardware Prototype of Proposed Impedance Converter                                                                                                                                                                                       | 48 |

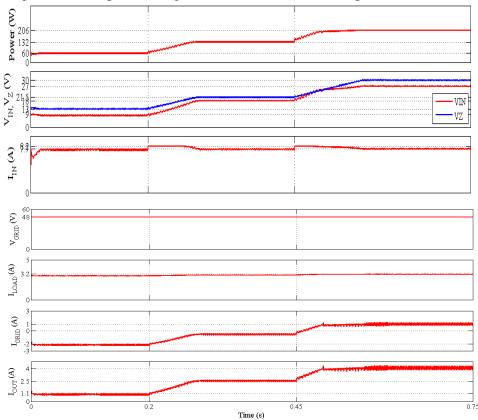

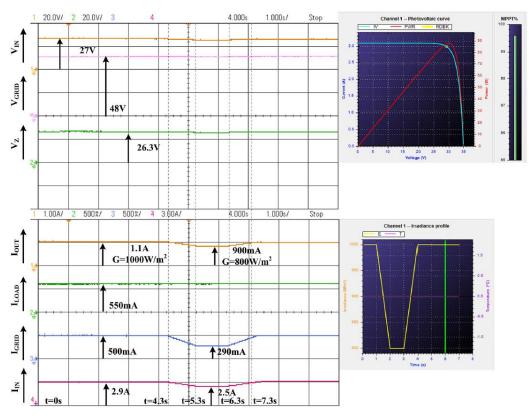

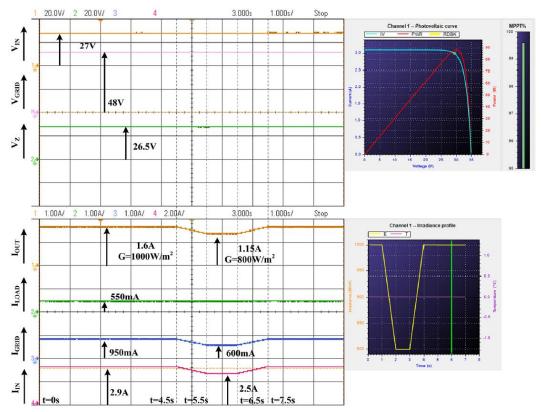

| Fig. 3.11  | a) i ) Input Voltage $(V_{IN})$ ii) Grid Voltage $(V_{G})$ iii) Capacitor Voltage $(V_{Z})$ b) i) Output Current $(I_{OUT})$ ii) Load Current iii) Grid Current iv) Input Current $(I_{IN})$ for irradiation change (strong grid)        | 48 |

| Fig. 3.12  | a) i ) Input Voltage $(V_{IN})$ ii) Grid Voltage $(V_{G})$ iii) Capacitor Voltage $(V_{Z})$ b) i) Output Current $(I_{OUT})$ ii) Load Current iii) Grid Current iv) Input Current $(I_{IN})$ for irradiation change (Weak grid)          | 49 |

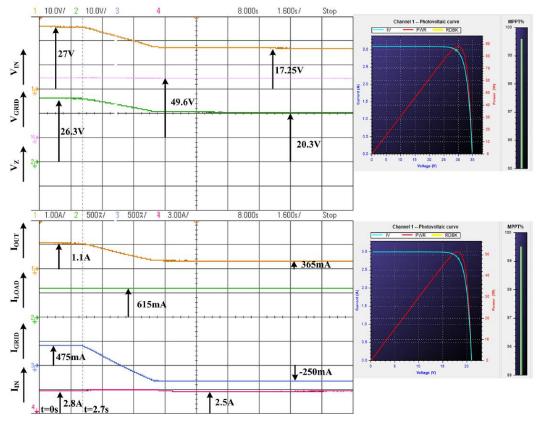

| Fig. 3.13  | a) i ) Input Voltage $(V_{IN})$ ii) Grid Voltage $(V_{G})$ iii) Capacitor Voltage $(V_{Z})$ b) i) Output Current $(I_{OUT})$ ii) Load Current iii) Grid Current iv) Input Current $(I_{IN})$ for partial shading $(27V \text{ to } 18V)$ | 50 |

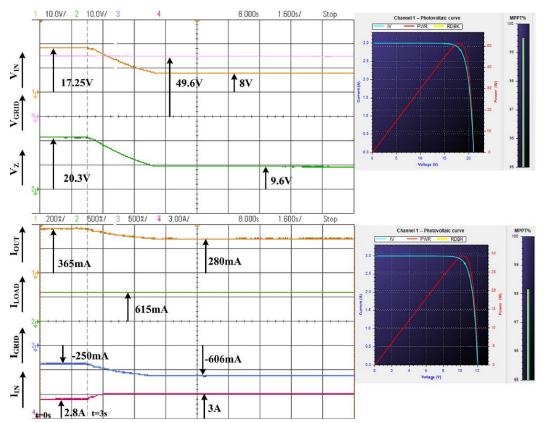

| Fig. 3.14  | a) i ) Input Voltage $(V_{IN})$ ii) Grid Voltage $(V_G)$ iii) Capacitor Voltage $(V_Z)$ b) i) Output Current $(I_{OUT})$ ii) Load Current iii) Grid Current iv) Input Current $(I_{IN})$ for partial shading $(18V \text{ to } 9V)$      | 51 |

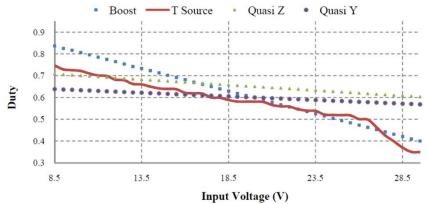

| Fig. 3.15  | Performance Comparison of Impedance Converter                                                                                                                                                                                            | 51 |

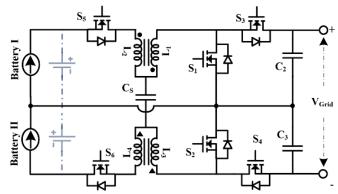

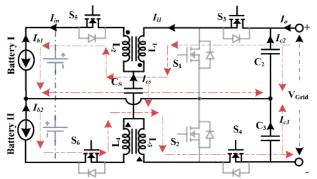

| Fig. 4.1   | Bidirectional Multiport Impedance Converter                                                                                                                                                                                                                              | 54 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

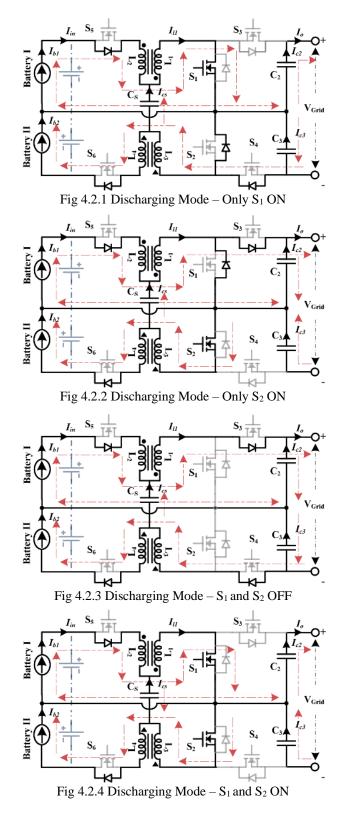

| Fig. 4.2.1 | Discharging Mode - Only S <sub>1</sub> ON                                                                                                                                                                                                                                | 55 |

| Fig. 4.2.2 | Discharging Mode - Only S <sub>2</sub> ON                                                                                                                                                                                                                                | 55 |

| Fig. 4.2.3 | Discharging Mode - S <sub>1</sub> and S <sub>2</sub> OFF                                                                                                                                                                                                                 | 55 |

| Fig. 4.2.4 | Discharging Mode - S <sub>1</sub> and S <sub>2</sub> ON                                                                                                                                                                                                                  | 55 |

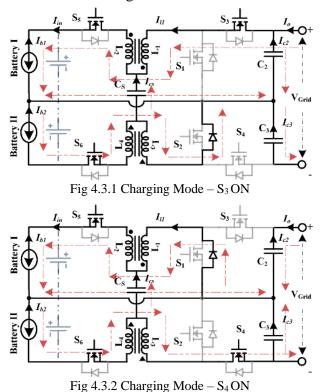

| Fig. 4.3.1 | Charging Mode - S <sub>3</sub> ON                                                                                                                                                                                                                                        | 56 |

| Fig. 4.3.2 | Charging Mode - S <sub>4</sub> ON                                                                                                                                                                                                                                        | 56 |

| Fig. 4.3.3 | Charging Mode - S <sub>3</sub> and S <sub>4</sub> ON                                                                                                                                                                                                                     | 57 |

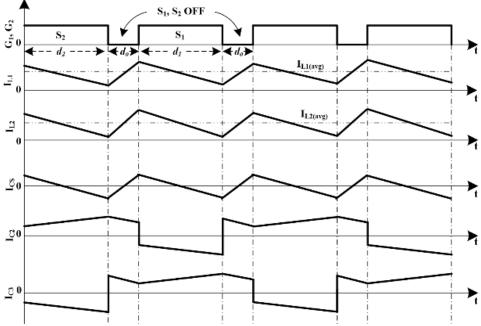

| Fig. 4.4.1 | Discharging Mode with Operating Duty < 0.5                                                                                                                                                                                                                               | 57 |

| Fig. 4.4.2 | Discharging Mode with Operating Duty $> 0.5$                                                                                                                                                                                                                             | 58 |

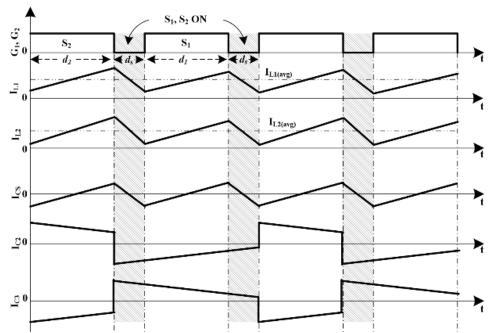

| Fig. 4.4.3 | Charging Mode                                                                                                                                                                                                                                                            | 58 |

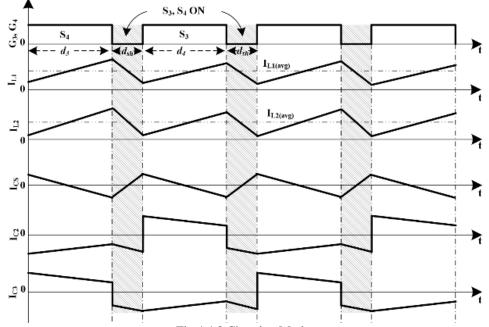

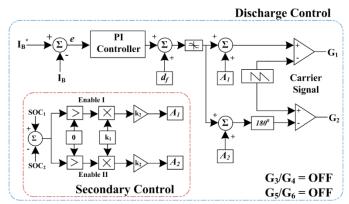

| Fig. 4.5   | Control Algorithm for Discharging Mode                                                                                                                                                                                                                                   | 61 |

| Fig. 4.6   | Control Algorithm for Charging Mode                                                                                                                                                                                                                                      | 62 |

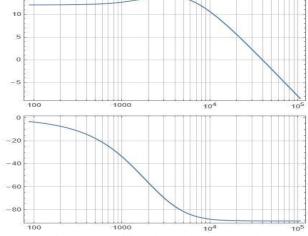

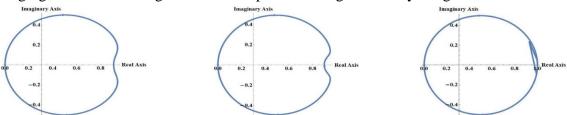

| Fig. 4.7.1 | Stability Plot - Discharging Mode                                                                                                                                                                                                                                        | 65 |

| Fig. 4.7.2 | Stability Plot - Charging Mode                                                                                                                                                                                                                                           | 65 |

| Fig. 4.8.1 | Discharging Mode (Normal Operation)                                                                                                                                                                                                                                      | 66 |

| Fig. 4.8.2 | Discharging Mode (Shoot Through)                                                                                                                                                                                                                                         | 66 |

| Fig. 4.8.3 | Charging Mode                                                                                                                                                                                                                                                            | 66 |

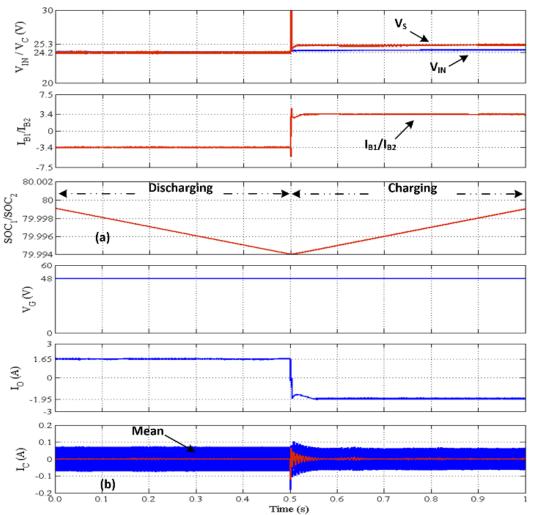

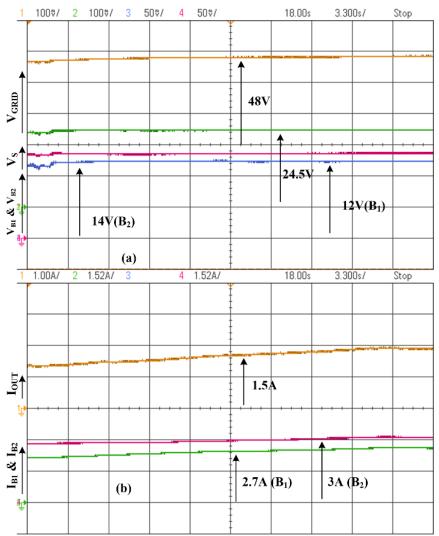

| Fig. 4.9   | Discharge to charge mode $-$ a) i)Input & capacitor voltage ( $V_{IN}$ & $V_{C}$ ) ii) Battery currents( $I_{B1}$ & $I_{B2}$ ) iii)SoC (SoC <sub>1</sub> & SoC <sub>2</sub> ) b) iv) Grid Voltage ( $V_{G}$ ) v) Grid Curr ( $I_{G}$ ) vi) Converter current ( $I_{C}$ ) | 67 |

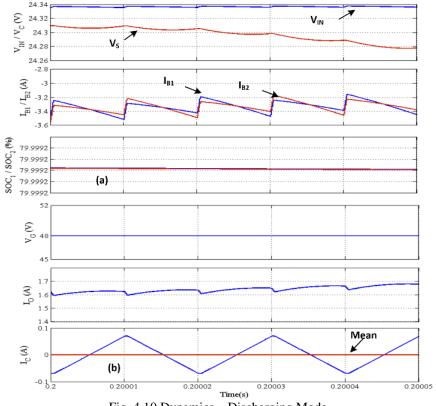

| Fig. 4.10  | Dynamics - Discharging Mode                                                                                                                                                                                                                                              | 68 |

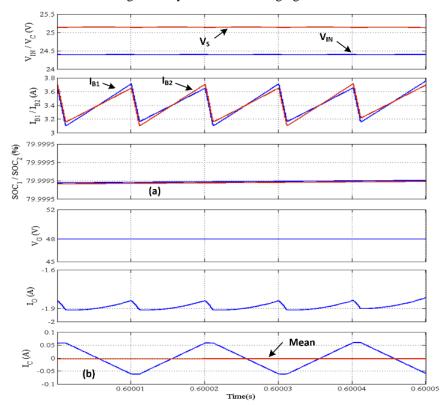

| Fig. 4.11  | Dynamics - Charging Mode                                                                                                                                                                                                                                                 | 68 |

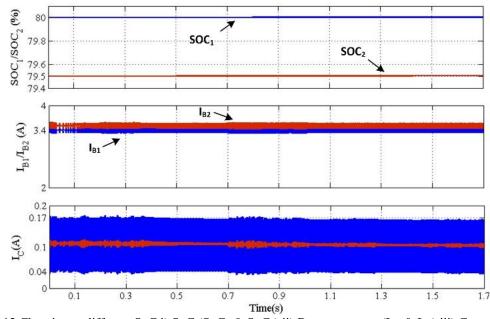

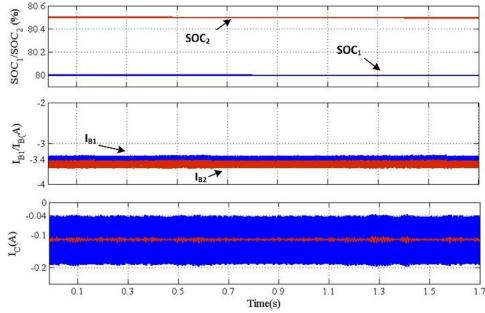

| Fig. 4.12  | Charging at different SoC i) SoC (SoC <sub>1</sub> & SoC <sub>2</sub> ) ii) Battery current (I <sub>B1</sub> & I <sub>B2</sub> ) iii) Conv. Current                                                                                                                      | 69 |

| Fig. 4.13  | Discharging at different SoC i) SoC (SoC <sub>1</sub> & SoC <sub>2</sub> ) ii) Battery current (I <sub>R1</sub> & I <sub>R2</sub> ) iii) Conv. current                                                                                                                   | 69 |

| Fig. 4.14.1 | Charging at Different Rates                                                                                                                                                                                                                                  | 70 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 4.14.2 | Discharging at Different Rates                                                                                                                                                                                                                               | 70 |

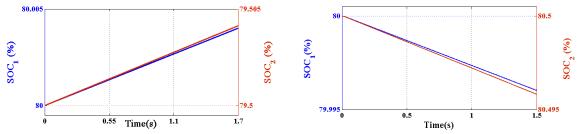

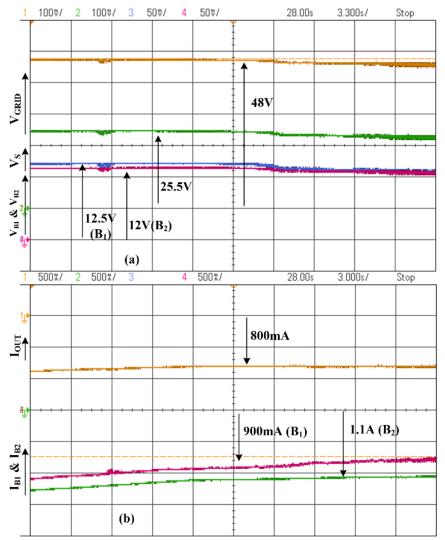

| Fig. 4.15   | Discharge to charge $-i$ ) Grid Voltage $(V_G)$ $ii$ ) capacitor voltage $(V_S)$ $iii$ ) Battery Voltage $(V_{B1})$ $iv$ ) Battery Voltage $(V_{B2})$ $v$ ) Converter current $(I_O)$ $vi$ ) Battery currents $(I_{B1})$ $vii$ ) Battery currents $(I_{B2})$ | 71 |

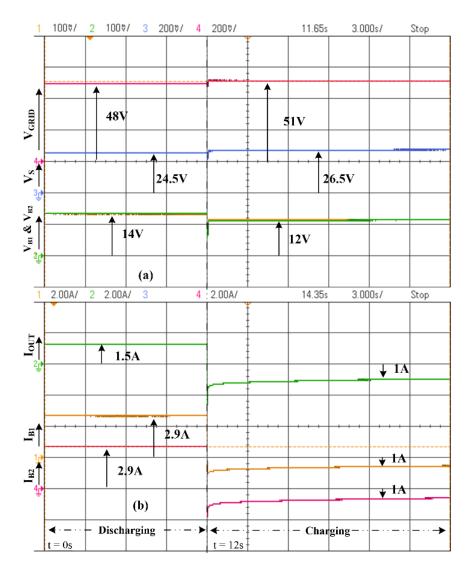

| Fig. 4.16   | Discharge at different $SoC - i$ ) Grid Voltage $(V_G)$ ii) capacitor voltage $(V_S)$ iii) Battery Voltage $(V_{B1})$ iv) Battery Voltage $(V_{B2})$ v) Converter current $(I_O)$ vi) Battery currents $(I_{B1})$ vii) Battery currents $(I_{B2})$           | 72 |

| Fig. 4.17   | Charge at different $SoC - i$ ) Grid Voltage $(V_G)$ ii) capacitor voltage $(V_S)$ iii) Battery Voltage $(V_{B1})$ iv) Battery Voltage $(V_{B2})$ v) Converter current $(I_O)$ vi) Battery currents $(I_{B1})$ vii) Battery currents $(I_{B2})$              | 73 |

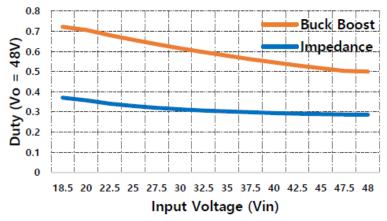

| Fig. 4.18   | Performance comparison conventional buck boost converter and impedance converter                                                                                                                                                                             | 74 |

| Fig. 4.19.1 | Gain Curve (Buck Mode)                                                                                                                                                                                                                                       | 75 |

| Fig. 4.19.2 | Gain Curve (Boost Mode)                                                                                                                                                                                                                                      | 75 |

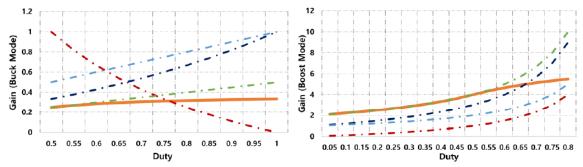

| Fig. 5.1    | Proposed Double Frequency Synchronization<br>Algorithm                                                                                                                                                                                                       | 77 |

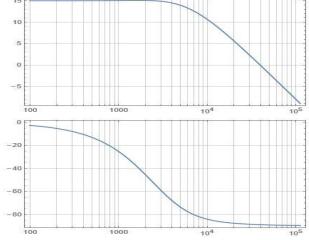

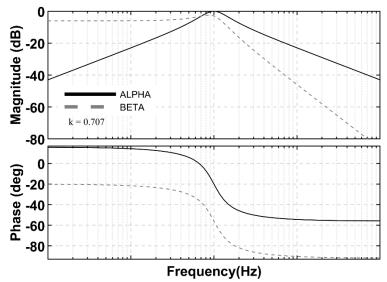

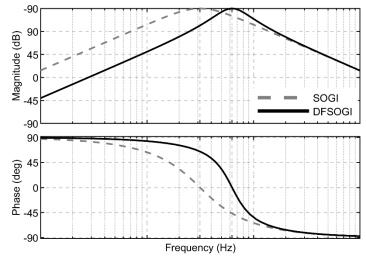

| Fig. 5.2    | Frequency response of $v'$ and $qv'$ of DFSOGI – PLL                                                                                                                                                                                                         | 79 |

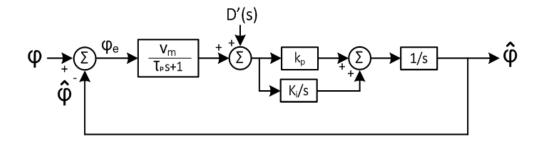

| Fig. 5.3    | Linear Model of DFSOGI – PLL                                                                                                                                                                                                                                 | 80 |

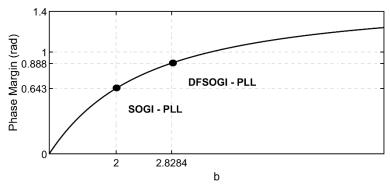

| Fig. 5.4    | Phase margin vs b for DFSOGI – PLL and SOGI – PLL                                                                                                                                                                                                            | 81 |

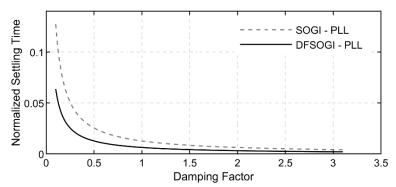

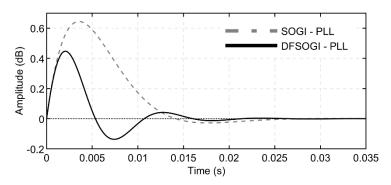

| Fig. 5.5    | Normalized settling time of DFSOGI – PLL and SOGI – PLL                                                                                                                                                                                                      | 81 |

| Fig. 5.6    | Bode Plot of DFSOGI – PLL and SOGI - PLL                                                                                                                                                                                                                     | 82 |

| Fig. 5.7    | Bode Plot of DFSOGI – PLL and SOGI – PLL                                                                                                                                                                                                                     | 82 |

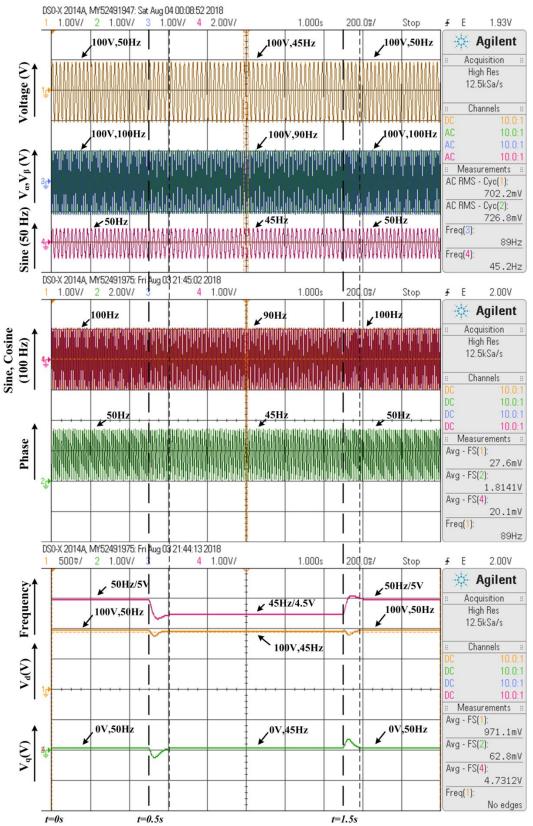

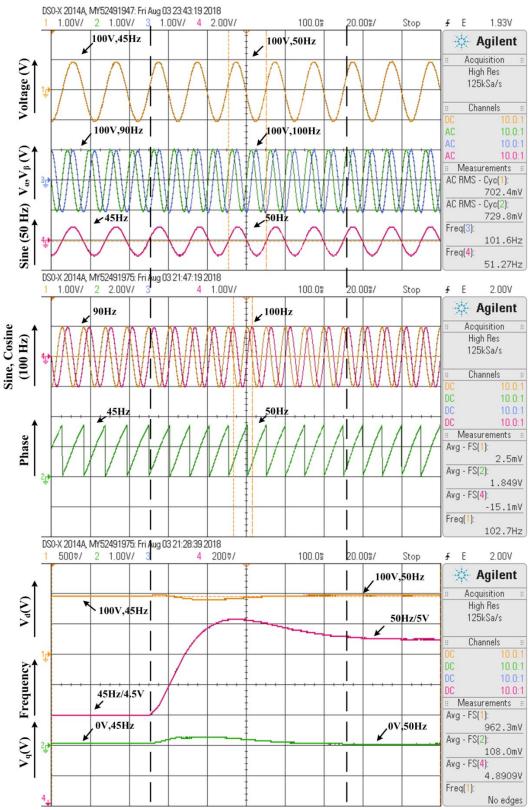

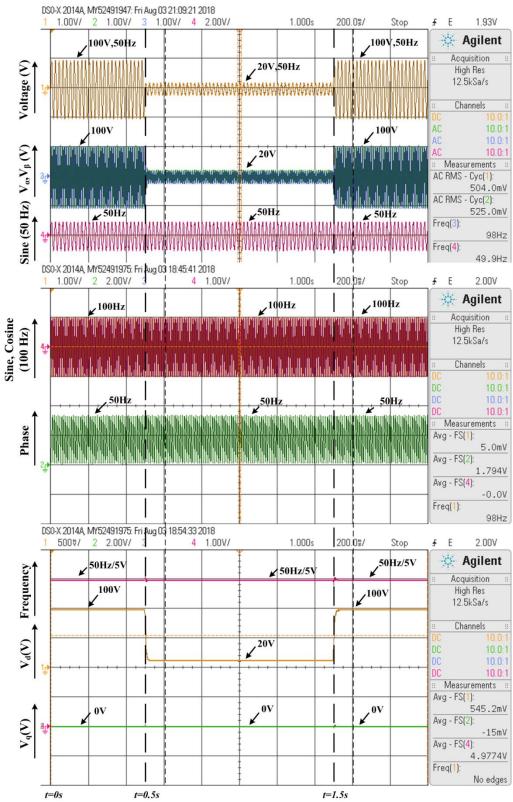

| Fig. 5.8    | Response – Frequency change a) i) input voltage ( $V_{IN}$ ) ii) $v_{\alpha}$ and $v_{\beta}$ iii) sine reference (50 Hz) b) i) sine and cosine reference (100Hz) ii) phase c) i) frequency iv) $v_{d}$ v) $v_{q}$                                           | 85 |

| Fig. 5.9    | Zoomed (t = 0.5s) - Response – Frequency change a) i) input voltage ( $V_{IN}$ ) ii) $v_{\alpha}$ and $v_{\beta}$ iii) sine reference (50 Hz) b) i) sine and cosine reference (100Hz) ii) phase c)                                                           | 86 |

|           | i) frequency iv) $v_d$ v) $v_q$                                                                                                                                                                                                          |    |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 5.10 | Zoomed (t = 1.5s) - Response – Frequency change a) i) input voltage ( $V_{IN}$ ) ii) $v_{\alpha}$ and $v_{\beta}$ iii) sine reference (50 Hz) b) i) sine and cosine reference (100Hz) ii) phase c) i) frequency iv) $v_{d}$ v) $v_{q}$   | 87 |

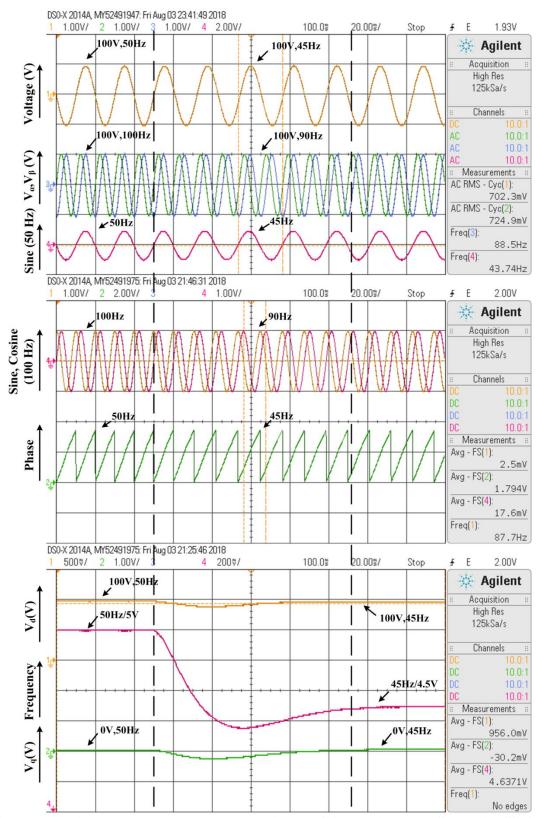

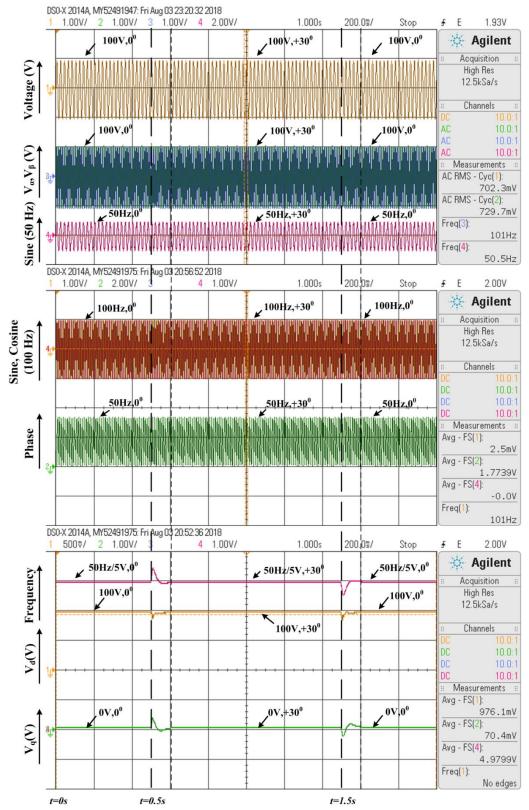

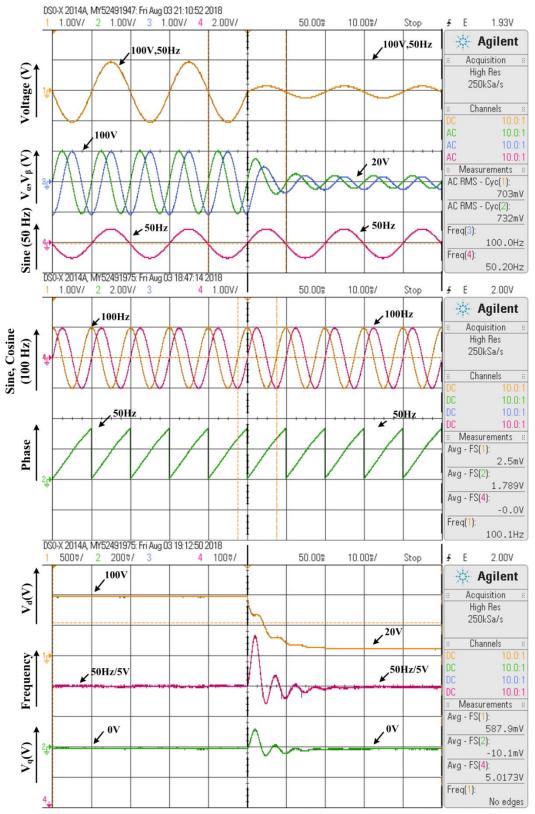

| Fig. 5.11 | Response – Phase Change a) i) input voltage $(V_{IN})$ ii) $v_{\alpha}$ and $v_{\beta}$ iii) sine reference (50 Hz) b) i) sine and cosine reference (100Hz) ii) phase c) i) frequency iv) $v_{d}$ v) $v_{q}$                             | 88 |

| Fig. 5.12 | Zoomed (t = 0.5s) – Response – Phase Change a) i) input voltage ( $V_{IN}$ ) ii) $v_{\alpha}$ and $v_{\beta}$ iii) sine reference (50 Hz) b) i) sine and cosine reference (100Hz) ii) phase c) i) frequency iv) $v_{d}$ v) $v_{q}$       | 89 |

| Fig. 5.13 | Zoomed (t = 1.5s) – Response – Phase Change a) i) input voltage ( $V_{IN}$ ) ii) $v_{\alpha}$ and $v_{\beta}$ iii) sine reference (50 Hz) b) i) sine and cosine reference (100Hz) ii) phase c) i) frequency iv) $v_{d}$ v) $v_{q}$       | 90 |

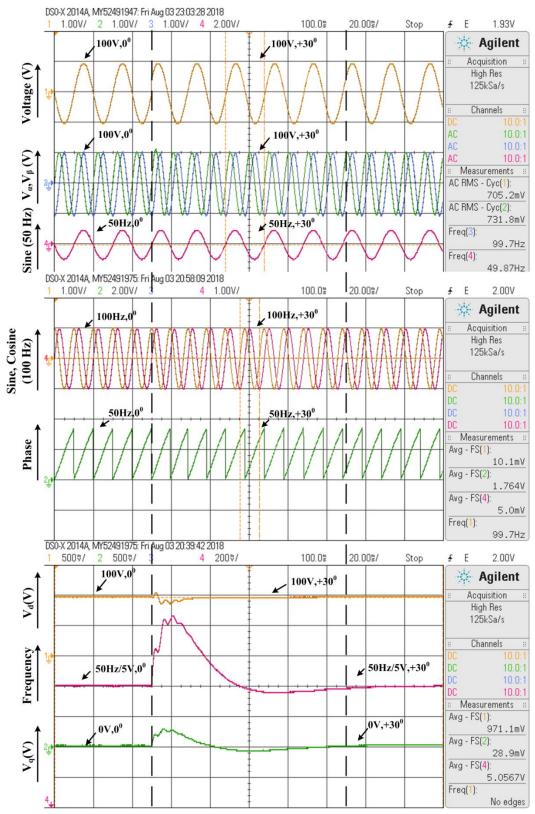

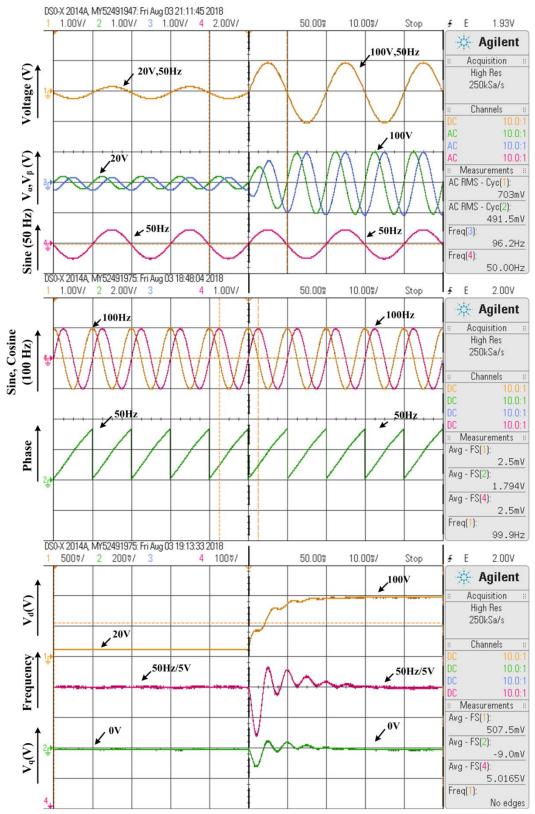

| Fig. 5.14 | Response – Voltage sag a) i) input voltage ( $V_{IN}$ ) ii) $v_{\alpha}$ and $v_{\beta}$ iii) sine reference (50 Hz) b) i) sine and cosine reference (100Hz) ii) phase c) i) frequency iv) $v_{d}$ v) $v_{q}$                            | 91 |

| Fig. 5.15 | Zoomed ( $t$ = 0.5 $s$ ) – Response – Voltage sag a) i) input voltage ( $V_{IN}$ ) ii) $v_{\alpha}$ and $v_{\beta}$ iii) sine reference (50 Hz) b) i) sine and cosine reference (100Hz) ii) phase c) i) frequency iv) $v_{d}$ v) $v_{q}$ | 92 |

| Fig. 5.16 | Zoomed ( $t=1.5s$ ) – Response – Voltage sag a) i) input voltage ( $V_{IN}$ ) ii) $v_{\alpha}$ and $v_{\beta}$ iii) sine reference (50 Hz) b) i) sine and cosine reference (100Hz) ii) phase c) i) frequency iv) $v_{d}$ v) $v_{q}$      | 93 |

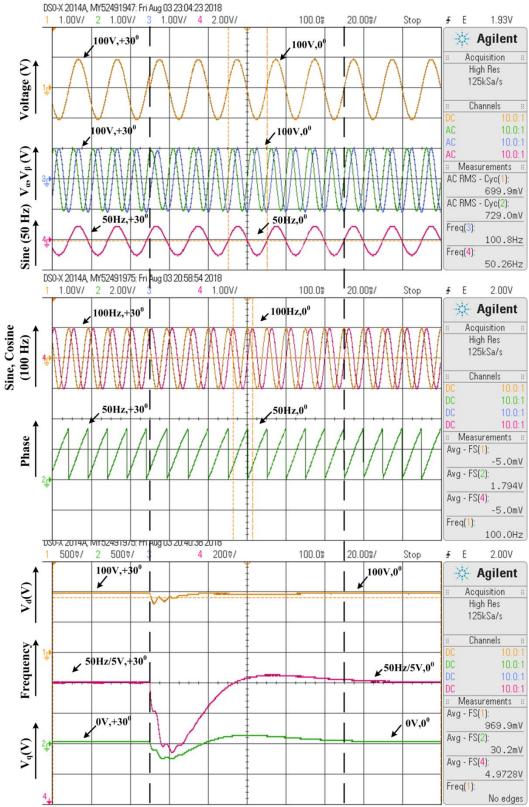

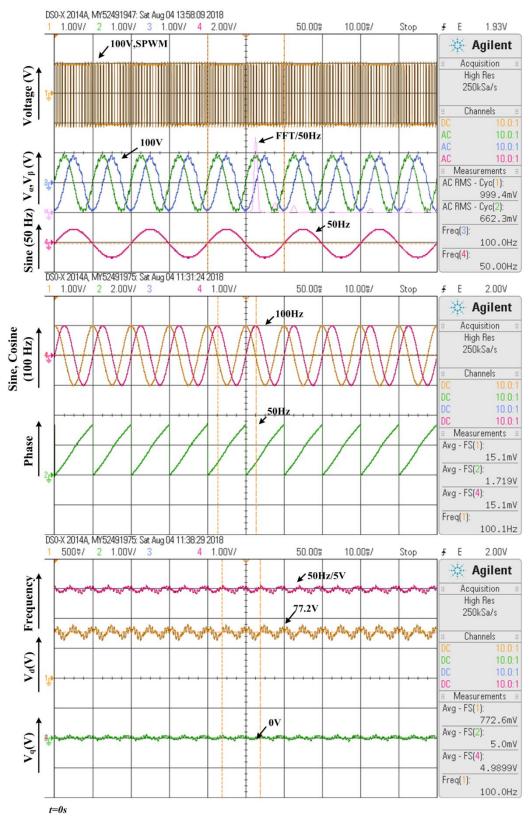

| Fig. 5.17 | Response – Pulsed input voltage a) i) input voltage $(V_{IN})$ ii) $v_{\alpha}$ and $v_{\beta}$ iii) sine reference (50 Hz) b) i) sine and cosine reference (100Hz) ii) phase c) i) frequency iv) $v_{d}$ v) $v_{q}$                     | 94 |

| Fig. 5.18 | Comparison of DFGOSI – PLL and SOGI – PLL for step frequency change of 5Hz                                                                                                                                                               | 95 |

| Fig. 5.19 | Comparison of DFGOSI – PLL and SOGI – PLL for step phase change of 300                                                                                                                                                                   | 96 |

|           |                                                                                                                                                                                                                                          |    |

96

100

$Comparison\ of\ DFGOSI-PLL\ and\ SOGI-PLL\ for\ step\ voltage\ sag\ of\ 80\%$

System Configuration

Fig. 5.20

Fig. 6.1

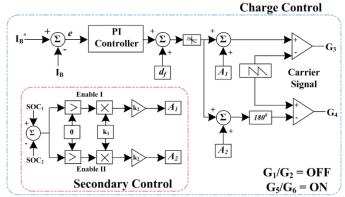

| Fig. 6.2  | Proposed Adaptive Re - Synchronization Algorithm                                                                                                                                                                                                                     | 102 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 6.3  | Adaptive Droop Control                                                                                                                                                                                                                                               | 103 |

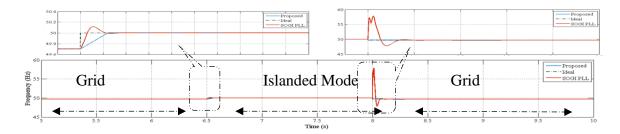

| Fig. 6.4  | Transition with no circulating current i) $V_{abc}$ ii) $V_{\alpha\beta}$ iii) $V_{dq}$ iv) Frequency v) Phase                                                                                                                                                       | 105 |

| Fig. 6.5  | Transition with circulating current i) $V_{abc}$ ii) $V_{\alpha\beta}$ iii) $V_{dq}$ iv) Frequency v) Phase                                                                                                                                                          | 106 |

| Fig. 6.6  | Comparison with conventional SOGI – PLL                                                                                                                                                                                                                              | 107 |

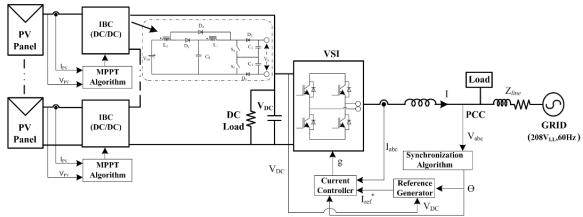

| Fig. 7.1  | System Architecture                                                                                                                                                                                                                                                  | 109 |

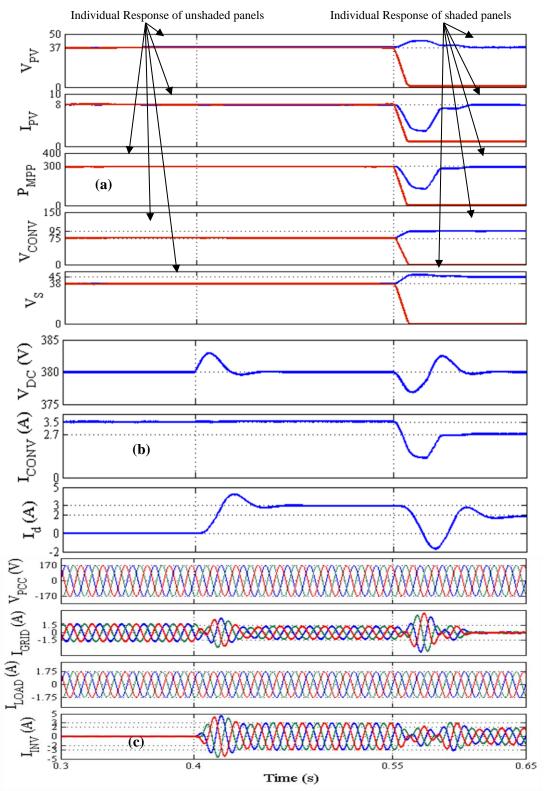

| Fig. 7.2  | a) i) Input Voltage ii) Input Current iii) Input Power iv) Output Voltage v) Shunt capacitor voltage b) i) DC link voltage ii) Converter output current iii) $I_d$ c) i) $V_{PCC}$ ii) Grid Current iii) Load Current iv) Inverter current under outage of one panel | 112 |

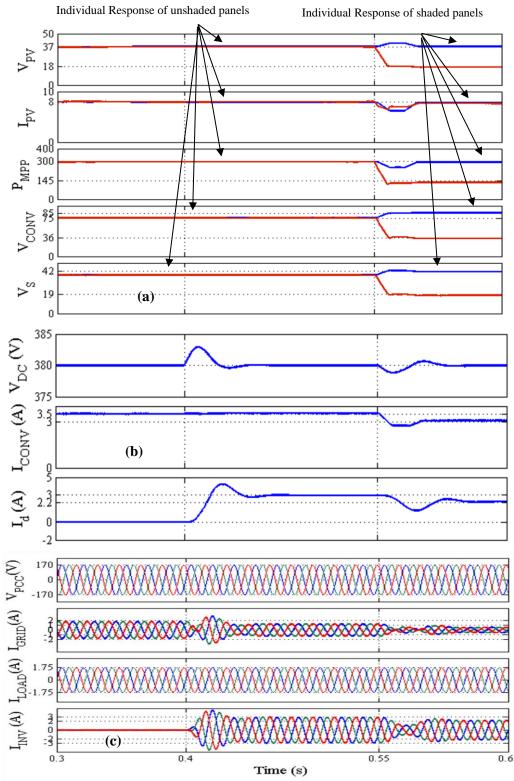

| Fig. 7.3  | a) i) PV Voltage ii) PV Current iii) Max. Power iv) Output Voltage v) Shunt capacitor voltage b) i) DC bus voltage ii) MT - IBC output current iii) $I_d$ c) i) $V_{PCC}$ ii) Grid Current iii) Load Current iv) Inverter current under partial shading condition    | 113 |

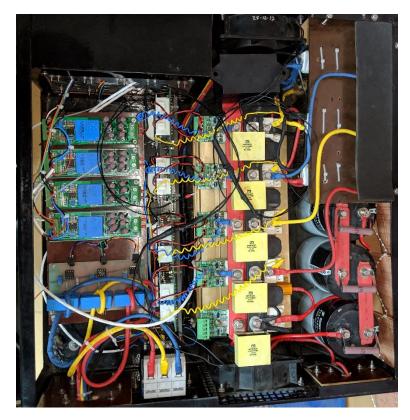

| Fig. 7.4  | Experimental Setup of Grid Tied Inverter                                                                                                                                                                                                                             | 114 |

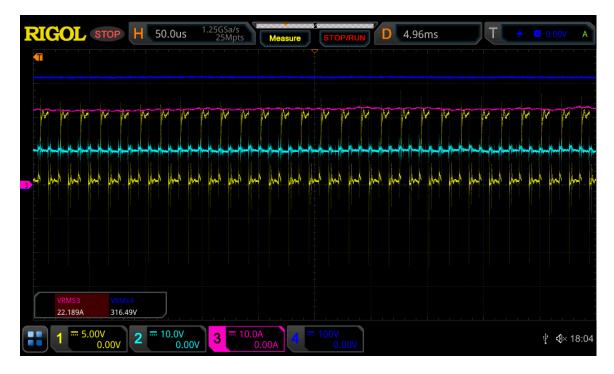

| Fig. 7.5  | Sinusoidal Pulse Width Modulation of Voltage Source<br>Inverter                                                                                                                                                                                                      | 115 |

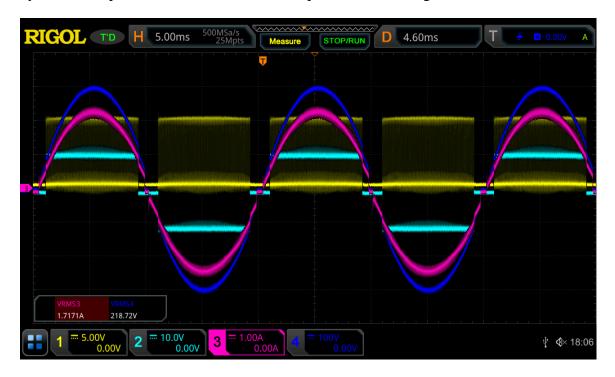

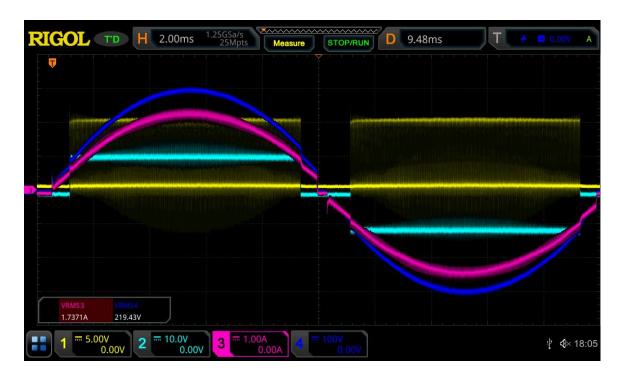

| Fig. 7.6  | Grid Voltage: Grid Current and Pulse Width<br>Modulation of Voltage Source Inverter (Grid Tied<br>Operation)                                                                                                                                                         | 116 |

| Fig. 7.7  | Peak value of Grid Voltage and Grid Current                                                                                                                                                                                                                          | 116 |

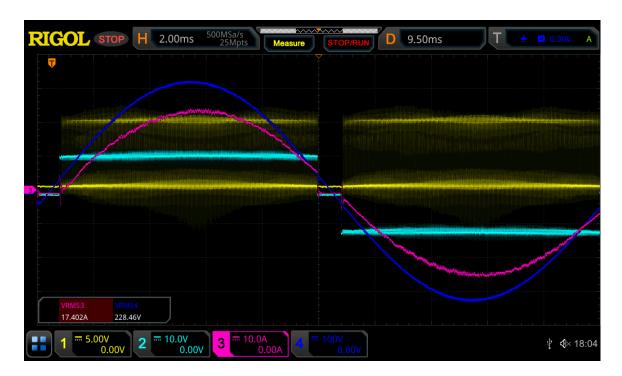

| Fig. 7.8  | Grid Voltage; Grid Current and Pulse Width<br>Modulation of Voltage Source Inverter (Off Grid<br>Operation)                                                                                                                                                          | 117 |

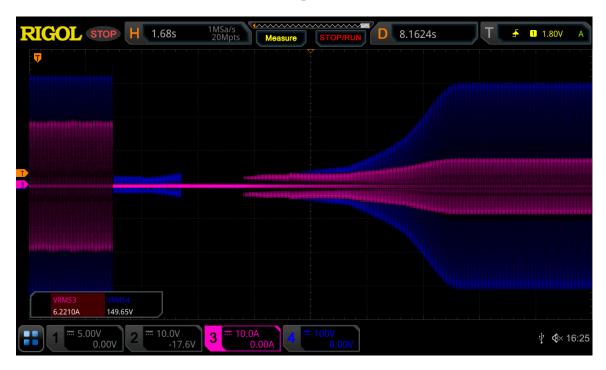

| Fig. 7.9  | Transition from Grid Connected Mode to Off Grid Mode of Operation                                                                                                                                                                                                    | 117 |

| Fig. 7.10 | Soft Start (Off Grid Mode)                                                                                                                                                                                                                                           | 118 |

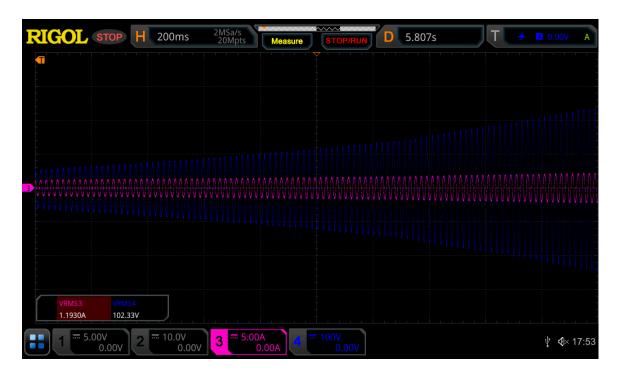

| Fig. 7.11 | Soft Start (Off Grid Mode)                                                                                                                                                                                                                                           | 118 |

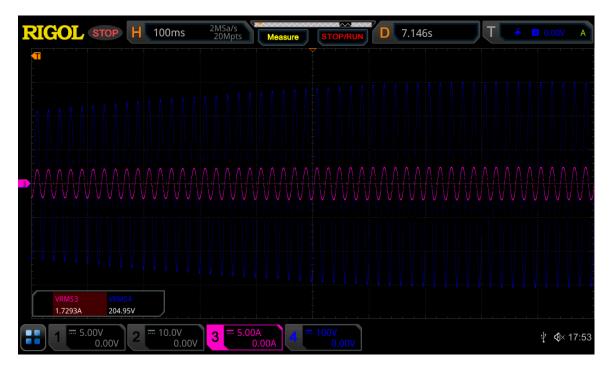

| Fig. 7.12 | Transition from Off Grid Mode to Grid Connected                                                                                                                                                                                                                      | 119 |

# LIST OF TABLES

| Table No.  | Table Name                              | Page No. |

|------------|-----------------------------------------|----------|

| TABLE I    | Simulation Parameters                   | 44       |

| TABLE II   | Hardware Parameters                     | 47       |

| TABLE III  | Performance Analysis                    | 52       |

| TABLE IV   | Simulation Parameter                    | 66       |

| TABLE V    | Comparative Analysis                    | 74       |

| TABLE VI   | RESPONSE OF DFSOGI - PLL AND SOGI - PLL | 97       |

| TABLE VII  | Simulation Parameters                   | 110      |

| TABLE VIII | Experimental Setup                      | 114      |

# **ABBREVIATIONS**

**Abbreviations Full-Form**

PV Photovoltaic

AC **Alternating Current**

DC Direct Current

P&O Perturb And Observe

InC Incremental Conductance **MPP Maximum Power Point**

**MPPT** Maximum Power Point Tracking

$I_{SC}$ Short-Circuit Current  $V_{OC}$ Open-Circuit Voltage

$V_{DC}$ Dc Link Voltage

**VSI** Voltage Source Inverter

MIC Module Integrated Converter

**Total Harmonic Distortion THD**

Current Mode Control **CMC**

**EMI** Electromagnetic Interference

Static Compensator

**STATCOM**

**PWM** Pulse Width Modulation

Direct-Quadrature d-q G2V Grid To Vehicle V2G Vehicle To Grid SoC State Of Charge Electric Vehicles **EVs**

**LVRT** Low Voltage Ride Through

HF High Frequency

Voltage Source Converter **VSC**

**SPWM** Sinusoidal PWM

**BESS** Battery Energy Storage System SRF Synchronous Reference Frame

**SOGI** Second Order Generalized Integrator

PLL Phase Locked Loop

**PCC** Point Of Common Coupling PI Proportional Integral

PQ Power Quality

THD Total Harmonic Distortion

V/F Voltage/Frequency

kHz Kilo Hertz

DSO Digital Storage Oscilloscope

I/O Input / Output

ADC Analog to Digital Converter

## INTRODUCTION

#### 1.1. General

With rapid industrialization in developing nations the power demand from the end consumer is growing exponentially increasing the stress over the fuel reserves. With the limitations imposed because of environmental concerns and depleting fuel reserves the generation from conventional power sources based on fossil fuels, has been slowly migrating towards renewable energy sources for sustainable growth. In contrast to centralized generation system, the distributed generation system includes many generating and storage units, facilitating energy efficiency due to vicinity with the load centers, reduction in the pollution due to the use of renewable sources and good power quality due to quick response and more reliability [1-2]. Further energy efficient devices, different converter configurations have facilitated extraction of maximum power from the renewable energy sources like photovoltaic and wind and reduce the burden on the grid. High efficiency power electronics converters have helped boost the efficient power generation from renewable sources. Among all the renewable energy sources photovoltaic energy source has seen growth at much faster rate due to drop in capital costs. To support this high penetration of Distributed Energy Sources (DER's) the governing bodies are coming up with stringent grid codes to improve the grid stability.

The power electronic converter interfacing with the renewable energy source and the grid should be reliable, efficient, and configurable for which multiple control techniques, topologies or converter configurations must be explored to extract the maximum power. Also, the interface converter must be capable of bidirectional energy transaction as and when required. Many configurations interfacing the distributed energy sources to the grid with different control techniques are possible with the system operation in either, grid connected mode or off grid mode.

In this thesis the study is done to investigate the means and methods for enhance the dynamic performance of the grid interfacing inverters along with studying the influence of connected DC – DC converter on DC bus of the inverters for the transient dynamics, and issues of synchronization / resynchronization of inverters to grid and interventions of DC side converters and adaptive control to offer effective parallel operation of inverters.

The following sections and sub sections gives an insight of the state-of-the-art photovoltaic converter interfaced with the grid through a converter / inverter topology. In addition, the issues of synchronization and resynchronization of the inverter with the grid are presented. Further the dynamic performance of grid connected parallel inverters is also investigated.

# 1.2. Solar Photovoltaic System : Issues and Opportunities

The photovoltaic energy source is abundantly available clean source of energy; however, the panels have very low efficiency when it comes to the conversion of solar energy to electrical energy. It is essential to extract the maximum possible power from the solar panel using an MPPT charge controller using algorithms like Perturb & Observe (P&O) and Incremental Conductance (InC) algorithm.

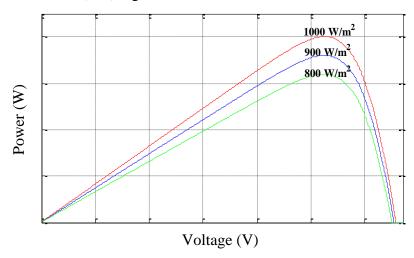

Fig. 1.1 PV Characteristics of Photovoltaic Panel with variation of irradiance

A few topologies have been studied upon and published over the years, be it isolated or non – isolated with focus on cost, efficiency, and reliability of operation. Isolated

converters offer galvanic isolation with capabilities of high gain through interfacing transformer but at an additional component count and cost. The conventional non isolated converters on the other hand lack the isolation and high gain capability but are less complex and easy to execute. For effective use the developed power is further inverted from DC to feed power into the AC load, the microgrid, the distribution network, and or to the entire fed through the national grid connected, islanded mode operation in off grid configurations as shown in Fig. 1.1 and Fig. 1.2.

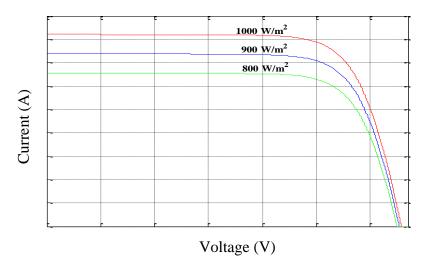

Fig. 1.2 IV Characteristics of Photovoltaic Panel

The following sections deals with challenges encountered, configurations they are connected and added to provide requisite DC voltage to enable the inverters for grid coupling at an appropriate voltage.

# 1.3. PV String and Array: Challenges

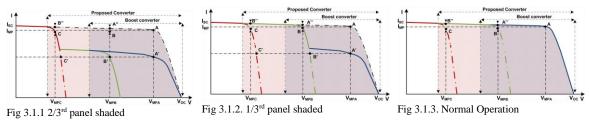

PV panels exhibits a typical non-linear I-V and P-V characteristics as shown in Fig.1.1 and Fig. 1.2 respectively. With the output power varying with variation in irradiance and temperature conditions, the output current of the panel being dependent on the irradiance varies and the output voltage being dependent on the panel temperature varies, a typical variation as shown in Fig. 1.3 and Fig. 1.4. The PV panel being comprised of many single solar cells units connected in series and in parallel to offer power at requisite voltage and

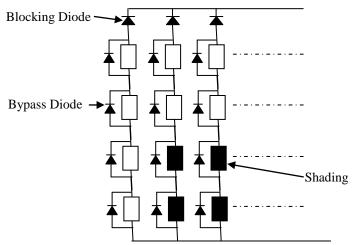

Fig. 1.3 Photovoltaic Panel Configuration and Partial Shading

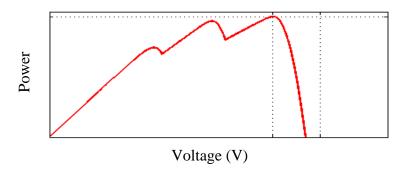

current levels, thereby panels are made by connecting these cells in series and parallel. And to match the upfront connected power electronic converters and inverters PV panels are connected in series and parallel to form an array to offer adequate DC voltage and current. If number of panels is increased in series, it leads to increase in open circuit voltage and when paralleled it increases the short circuit current of the PV arrays. For extracting maximum power and maximize the utilization of the solar panels, various global MPPT (GMPPT) are advocated in literature for operation at GMPPT under partial shading and shading of PV panels in strings since the power generated by the string under shading of panel / partial shading of the panel a voltage drop is witnessed at the terminals of string / parallel, appropriate voltage gain of the string MPPT controller would be a requisite to avoid knocking out of string from the PV array.

Fig. 1.4 PV Characteristic during Partial Shading

# 1.4. Converter/Inverter Configurations for the PV System

Power Electronic converter and inverters are the enablers for transacting PV power into the grid. The conventional grid integration is based on centralized inverters which interfaces many PV modules placed in the form of an array to form a DC link appropriate for directly coupling to the grid through inverter acting in current control mode and voltage control mode respectively in single stage or two stage configurations as shown in Fig. 1.5 or 1.6 [3]. Parallel strings of PV panels are connected to generate sufficiently high voltage to avoid the requirement of amplification by converters in single stage configuration. But the main problems associated with these centralized single stage inverters lies with high-voltage dc cables between the PV modules and the inverter, power losses due to a centralized MPPT, mismatch losses between the PV modules and losses in the string diodes, partial shading / shading of panels in the string.

Fig. 1.5 Single Stage Configuration interfacing DER to Grid

Fig. 1.6 Double Stage Configuration interfacing DER to Grid

Sometimes in the absence of sufficient number of panels and or deliberately for increasing the reliability against shading / partial shading the requisite voltage, is built up through DC-DC boost type converters between the sub sections of string of PV panels with separate MPPT controllers and the inverter making them operate in the two-stage configuration while all such modified string connected to grid in parallel as shown in Fig. 1.6. In double stage mainly isolated or non-isolated DC-DC converters are used in conjunction with voltage source inverter (VSI). Isolated topology though enhances the overall cost of the system, but provides an additional advantage in terms of isolation, which avoids leakage current, preventing occurrence of hazardous situations. For the low wattage off grid PV systems, low-cost non-isolated converters are often preferred.

Recently module integrated converters (MIC) have gained popularity, where in the generated power is transformed to grid coupling compatible, thereby making them capable of avoiding the mismatch losses between PV modules in the string since there is only one PV module to which it caters to, and it also facilitates the individual MPPT, thus enhancing the efficiency and reliability. However, MIC for single PV module is being used; it requires high amplification to match the grid voltage making it a slightly costly proposition.

2 – Level / 3 - Level multi-string / single string inverters are popularly deployed in the field. The topology for multistring inverter consists of several PV strings, each connected with separate DC – DC converters to a common DC – AC inverter [4 – 5]. This topology features several advantages such as the independent tracking of the MPP of each string and the possibility to scale the system by plugging more strings to the existing plant. But the power output suffers a lot under partial shading condition. Further the losses and stresses on switches are quite high due to the high voltage condition prevailing on single DC link capacitor. Due to the heavy power transaction across common capacitor, its capacitance is generally kept being at very high value which due to large stress deteriorates early causing lessening life of the PV system. The classical two-level VSIs is mainly limited to low- or medium power level applications due to the limits of the power-semiconductor switches used in the configuration.

### 1.5. DC – DC Converter

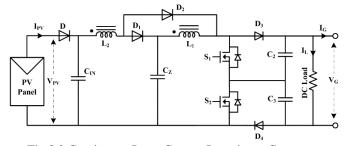

The interfacing DC – DC converter plays a vital role in extracting the power from the photovoltaic panels and feeding it to the DC bus of the inverter, which in turn feeds it to the distribution grid. A simple and cost-effective converter mostly interfaced with a PV system is boost converter, however the conventional boost converter may witness more than the allowable stress under partial shading conditions leading to failure or breach of design [6-7].

To improve the efficiency of the converter and reducing the stress over the components interleaving of converters have been reported, while for high gain requirement, incorporation of multiplier cells or cascading of converter topologies are proposed. Such modifications enhance the operating band of the converter. Isolated topologies provide an alternative for with boosting capabilities by altering the turns ration of the isolating transformer. Non isolated boost converters based on impedance converters have also been investigated with the capability to operate during shoot through and providing auxiliary boost [8].

# 1.6. Voltage Sourced Inverter

The output power generated from the PV panel is low voltage DC in nature, which is scaled up to maintained at the required level of voltage and power by appropriately connecting them in parallel / series. The inverter in the single stage configuration can be interfaced with the distribution grid directly [9], while in two stage configurations through an interface converter. In single stage application the DC bus voltage level need to be maintained at a higher value by PV string, and the inverter in turn to performs the maximum power tracking and power transfer to the distribution grid by appropriately controlling the current drawn from the PV string as shown in Fig. 1.7. Though single stage configuration eliminates the need for extra DC – DC converter, but during voltage sag condition the instantaneous increase in the PV system current momentarily decrease in the DC link voltage and thereby shifts the operating point towards  $I_{SC}$ , leading to collapse of power generation from the string, unless and until DC link is provided with adequate hold up capacitor / STATCOM connection at the PCC.

Fig. 1.7 Single Stage Configuration

In two stage configurations as shown in Fig. 1.8, the photovoltaic voltage is either stepped up or stepped down through the interfacing DC – DC charge controller as per the requirement of the system [10-11]. The DC power is converted into AC using an inverter interfacing the DC output of the charge controller with the grid. The interfacing inverter pushes the power generated from PV panel / PV string to the AC distribution grid and in turn to the connected loads.

Fig. 1.8 Dual Stage Configuration

In addition to power transfer from DC link to AC distribution grid the interfacing inverter is often entrusted for multitasking. Some of the additional tasks carried out are [12–13] -

- Active Filtering –it can act as an active filter injecting a specific current at the PCC for mitigation of harmonics and thereby improving the power quality of the complete system working on the remaining capacity of hardware.

- ii. Power Conditioning The inverter helps in a controlled exchange of energy between two electrical units. The control of the inverter switching sequence is to ensure that

parameters like voltage magnitude, frequency, current magnitude, power factor and Total Harmonic Distortion (THD) are maintained as per the requisite specifications and standards.

iii. Compensator – the voltage source inverter acting as a power compensator helps increase the power transfer capability, efficiency of power transfer, efficiency of power transfer in distribution grid. The inverters can be used series compensators or Static Synchronous Compensator (STATCOM).

Inverter interfacing unit converting the DC to AC helps in increasing the depth of penetration of renewable distributed energy sources in an efficient and reliable way with the existing power infrastructure.

# 1.6.1. Voltage Sourced Inverter - Configurations

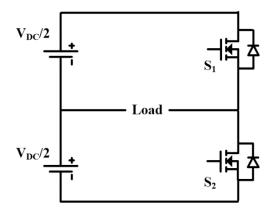

The basic inverter configuration is the half bridge inverter as shown in Fig. 1.9, consisting of an upper and lower switch with an antiparallel diode and interfacing inverter for connection to the grid. The DC voltage is maintained by the DC link capacitors at the input side which is in turn fed from the MPPT charge controller, energy storage system (ESS). The fundamental component of the output voltage of the inverter is controlled by the switching sequence of the inverter. However, such configuration is mainly used for coupling it with the grid, since it requires very high voltage to be maintained at the DC link, and possibilities of injection of DC components to the grid.

Fig. 1.9 Half Bridge Inverter Configuration

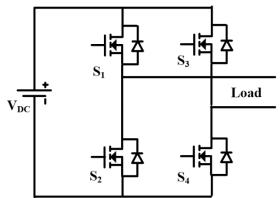

Two half bridges connected in parallel at the input DC side constitutes the full bridge configuration of inverter, also known as full bridge / H bridge inverter having two legs. An extension of H – bridge inverter with  $3^{rd}$  leg is presented for  $3\phi$  systems and is shown in Fig. 1.10. The three-phase voltage sourced inverter interfaces the input DC link to the 3-phase grid through interfacing inductors. If the configuration required is that of a 4-wire system, the neutral wire is attached to the midpoint of the series side capacitor on the input side.

Fig. 1.10 3 Phase Full Bridge Inverter Configuration

# 1.6.2. Control Techniques of the Voltage Sourced Inverter

The interfacing voltage source inverter (VSI) can operate in either grid connected mode or off grid mode. In off grid mode the inverter output is not connected to the grid, and thus need to operate in voltage control mode to control the voltage and frequency fed to the load.

While. in the grid connected mode, the configuration can be master slave mode where the distribution grid acts as master and governs the voltage and frequency at the Point of Common Coupling (PCC) while the VSI injects the current, or in all master mode, where the VSI also acts as a voltage source and transfer by altering the lead angle with respect to voltage at PCC. Generally, the inverter is employed as current controlled VSI, thereby pushing current equivalent to the power generated by the photovoltaic panels or while witnessing near constant voltage at AC side. The most common control technique for switching of VSI in grid connected mode are Hysteresis Current Control (HCC) in master

slave mode and Sinusoidal Pulse Width Modulation (SPWM) for connection of VSI as voltage controlled VSI [14].

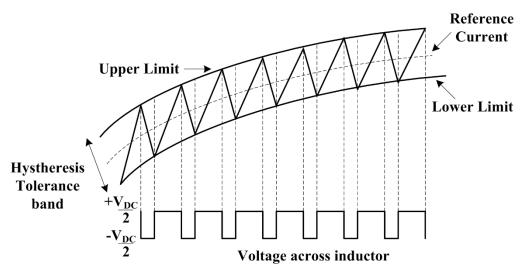

# **1.6.2.1.** Hysteresis Current Control (HCC)

The hysteresis current control compares the reference sinusoidal current with a tolerance band having an upper and lower limit as shown in Fig. 1.11, the switch transitions from ON state to OFF state and vice versa based upon the current waveform reaching the upper and lower thresholds. The switches in a leg of VSI are turned ON and OFF based on the corresponding current threshold. The operating state is reversed when the actual current reaches the other threshold. The control algorithm is simple to implement with very less computation required. However, the transition of the switches from ON state to OFF state is dependent on the slope change of slope of current transition and threshold limits set, thus resulting in operation of the inverter at a switching frequency which may vary with change of the slope if current in sinusoidal and / or parametric variations.

Fig. 1.11 Hysteresis Current Control (HCC) Technique

## 1.6.2.2. Pulse Width Modulated Control –

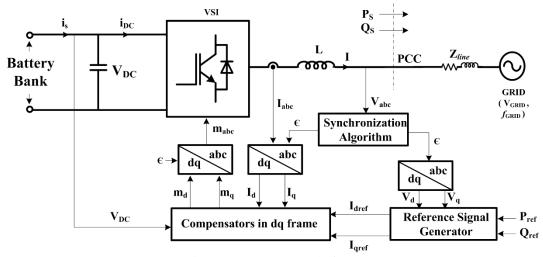

Pulse width modulation technique employ control on the modulation index to control the output magnitude of voltage and phase level by a corresponding modulating signal as given by (1).

$$v_t = mV_{DC} \tag{1}$$

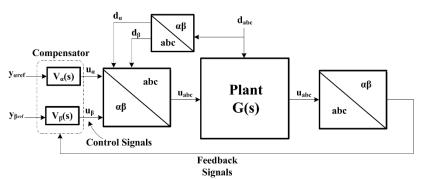

The sinusoidal waveform acts as the modulating signal and is compared with the high frequency carrier signal. The reference current is compared to the actual current and the error is compensated using a PI controller. The reference current for the control is governed by the power generated from the distributed energy source at the DC side. The compensator output after decoupling is converted to switching pulses as per desired modulation index based on (1). The feed forward component also helps in establishing robust response of the control loop. The control technique maintains the switching frequency equivalent to the carrier frequency but suffers from the control complexity and computation requirement as shown in Fig. 1.12 and Fig.1.13.

Fig. 1.12 SPWM Control of VSI

Fig. 1.13 SPWM Control Technique

# 1.7. Parallel Operation of Inverters

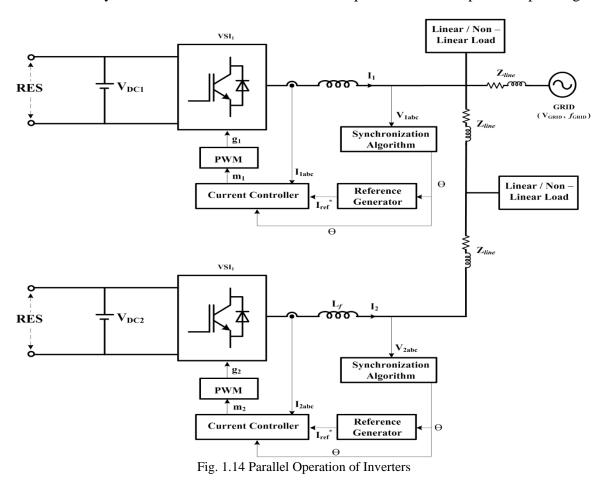

To meet the increasing load demand with aim to reduce the carbon footprint, power generated based on DER's is gaining importance. To meet the load demand, parallel operation of inverters in a microgrid is essential. The parallel operation of the inverters can be investigated separately into operation during off grid mode or grid connected mode.

During off grid mode the voltage and frequency at the connected loads are maintained by the interfacing inverter, with the master inverter operating in voltage control mode maintaining the voltage and frequency at Point of Common Coupling (PCC). Other interfacing inverters are synchronized with the master inverter and are attached to the PCC as current controlled sources behaving as slaves following the frequency and voltage set by the master. The most critical component for interfacing of multiple inverters in parallel is the robust synchronization of the inverters. It is requisite that all the parallel operating

inverters should operate in synchronization, maintaining the output parameters within the required standards. Parallel operation of inverters during off grid mode may experience

circulating currents among themselves due to differences in the response of PLL, hardware parameters and / or the switching sequences.

In grid connected mode, all the connected multiple inverters generally operate in slave mode, pushing the power generated at their input sides to the connected grid in terms of equivalent current where the grid is acting as master and maintaining the voltage and frequency at their respective PCC's as shown in Fig. 1.14. However, during disturbances either at the grid side or at the DC input side, high transients and circulating current flows amongst the inverter bridges. This high di/dt and high dv/dt transients damage the switching devices of the inverters leading to collapse of the system. High circulating current can also be experienced if one of the inverters goes out of synchronization, leading to its failure.

An investigation is therefore due for impedance source based MPPT charge controller at the DC side which can act as an impedance network, which can enhance the transient performance of the system. In addition to limiting the flow of circulating current by imposing an additional impedance at the DC link.

## 1.8. Synchronization and Resynchronization

The phase locked loop ensures precise synchronization of the interfaced inverter with the grid along with providing ride through capability, and accordingly plentiful attention is requisite for investigation into synchronization algorithms. Unit template-based synchronization algorithm determines the sine and cosine synchronizing signals for balanced grid conditions. However, under perturbations the grid voltage and frequency change, making loss of synchronization among inverters is found inevitable and thereby compromising the current references and the control algorithm of the concerned inverter. Conventional synchronization algorithms like Synchronous Reference Frame Phase Locked Loop (SRF – PLL) based on inverse park transformation show fast synchronization response only under balance conditions. To improve the dynamic performance of SRF – PLL, Amplitude Normalization Scheme (ANS) is integrated in the algorithm while to improve the filtering capability by modifying the integrator of low pass filter (PI controller). While, to improve the filtering capability of the PLL, Moving Average Filter

(MAF) is also investigated in the algorithm. Second Order Generalized Integrator (SOGI) acting as a Quadrature Signal Generator (QSG) in addition to its capability of providing infinite gain at a particular frequency with robust performance put the algorithm, in a class apart.

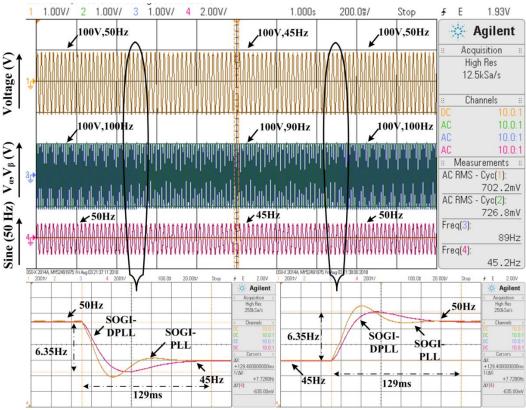

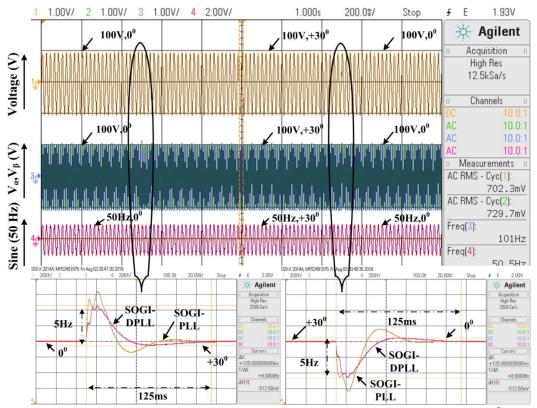

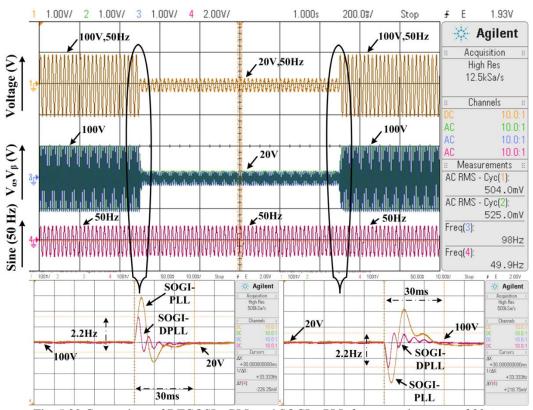

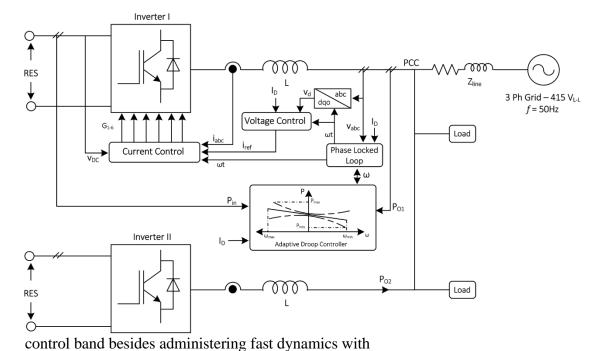

It is important that that the synchronization algorithm should be capable of detecting and adapting to curbing the intermittent conditions on the grid in least possible time, besides exhibiting the capability of accurate transient tracking i.e., the response of the synchronization algorithm should match the fast dynamics of the low inertia inverter assuring the ride through capability in addition to complying with the grid codes. Furthermore, the frequency adaptive algorithms should also allow co – operative synchronization of inverters having different dynamics (due to type of hardware/type of controllers), generating distortion free reference, and nullifying the circulating current flow between the inverter modules.