# Thesis.pdf

Delhi Technological University

---

## Document Details

**Submission ID****trn:oid::27535:120998001****154 Pages****Submission Date****Nov 12, 2025, 1:50 AM GMT+5:30****42,862 Words****Download Date****Nov 12, 2025, 2:38 AM GMT+5:30****227,337 Characters****File Name****Thesis.pdf****File Size****4.0 MB**

# 5% Overall Similarity

The combined total of all matches, including overlapping sources, for each database.

## Filtered from the Report

- ▶ Bibliography

- ▶ Small Matches (less than 14 words)

## Exclusions

- ▶ 159 Excluded Matches

## Match Groups

-  103 Not Cited or Quoted 5%

Matches with neither in-text citation nor quotation marks

-  1 Missing Quotations 0%

Matches that are still very similar to source material

-  0 Missing Citation 0%

Matches that have quotation marks, but no in-text citation

-  0 Cited and Quoted 0%

Matches with in-text citation present, but no quotation marks

## Top Sources

- 2%  Internet sources

- 3%  Publications

- 2%  Submitted works (Student Papers)

## Integrity Flags

### 0 Integrity Flags for Review

No suspicious text manipulations found.

Our system's algorithms look deeply at a document for any inconsistencies that would set it apart from a normal submission. If we notice something strange, we flag it for you to review.

A Flag is not necessarily an indicator of a problem. However, we'd recommend you focus your attention there for further review.

## Match Groups

-  103 Not Cited or Quoted 5%

Matches with neither in-text citation nor quotation marks

-  1 Missing Quotations 0%

Matches that are still very similar to source material

-  0 Missing Citation 0%

Matches that have quotation marks, but no in-text citation

-  0 Cited and Quoted 0%

Matches with in-text citation present, but no quotation marks

## Top Sources

- 2%  Internet sources

- 3%  Publications

- 2%  Submitted works (Student Papers)

## Top Sources

The sources with the highest number of matches within the submission. Overlapping sources will not be displayed.

| Rank | Source Type     | Source                                                                            | Percentage |

|------|-----------------|-----------------------------------------------------------------------------------|------------|

| 1    | Publication     | Pushpa Raikwal, Ambika Prasad Shah, Vaibhav Neema. "A Low Leakage Variation-...   | <1%        |

| 2    | Internet        | www.researchgate.net                                                              | <1%        |

| 3    | Internet        | link.springer.com                                                                 | <1%        |

| 4    | Publication     | R. Krishna, Punithavathi Duraiswamy. "Low leakage 10T SRAM cell with improved ... | <1%        |

| 5    | Internet        | dspace.thapar.edu:8080                                                            | <1%        |

| 6    | Submitted works | Symbiosis International University on 2018-07-22                                  | <1%        |

| 7    | Submitted works | Uttar Pradesh Technical University on 2025-07-01                                  | <1%        |

| 8    | Submitted works | M S Ramaiah University of Applied Sciences on 2025-01-06                          | <1%        |

| 9    | Publication     | Kim, Young Bae. "A Novel CNFET SRAM-Based Computing-In-Memory Design and ...      | <1%        |

| 10   | Submitted works | PEC University of Technology on 2022-06-22                                        | <1%        |

## 11 Publication

Tripti Tripathi, Durg Singh Chauhan, Sanjay Kumar Singh. "A Novel Approach to D... <1%

## 12 Publication

Jitendra Kumar Mishra, Lakshmi Likhitha Mankali, Kavindra Kandpal, Prasanna K... <1%

## 13 Internet

pdffox.com <1%

## 14 Internet

assets.researchsquare.com <1%

## 15 Submitted works

Rochester Institute of Technology on 2014-09-22 <1%

## 16 Submitted works

nith on 2022-06-08 <1%

## 17 Internet

hdl.handle.net <1%

## 18 Internet

spectrum.library.concordia.ca <1%

## 19 Publication

Pushpa Raikwal, Ambika Prasad Shah, Vaibhav Neema. "A Low-Leakage Variation... <1%

## 20 Submitted works

M S Ramaiah University of Applied Sciences on 2025-02-12 <1%

## 21 Publication

Upadhyay, Prashant, Rajib Kar, Durbadal Mandal, and Sakti Prasad Ghoshal. "Cha... <1%

## 22 Submitted works

nith on 2022-06-02 <1%

## 23 Publication

Mann, Randy W. "Interactions of Technology and Design in Nanoscale SRAM", Pro... <1%

## 24 Internet

ebin.pub <1%

25 Publication

"Advances in Communication, Devices and Networking", Springer Science and Bu... <1%

26 Publication

"Embedded Memories for Nano-Scale VLSIs", Springer Nature, 2009 <1%

27 Publication

Halupka, D. "Effects of Silicon Variation on Nano-Scale Solid-State Memories ", Pr... <1%

28 Publication

Kumar, Satyendra, Kaushik Saha, and Hariom Gupta. "Run time write detection in... <1%

29 Internet

aranne5.bgu.ac.il <1%

30 Submitted works

Birla Institute of Technology on 2018-07-07 <1%

31 Internet

hal.inria.fr <1%

32 Publication

Jitendra Kumar Mishra, Bharat Bhushan Upadhyay, Prasanna Kumar Misra, Mani... <1%

33 Publication

Moradi, Farshad, and Jens K. Madsen. "Improved read and write margins using a ... <1%

34 Submitted works

National Institute of Technology, Rourkela on 2020-05-06 <1%

35 Submitted works

Panjab University on 2014-02-19 <1%

36 Publication

Vinod Kumar, Ram Murti Rawat. "Low Power Swing Restoration Circuit Reduce Th... <1%

37 Internet

ictactjournals.in <1%

# **DESIGN AND ANALYSIS OF SRAM CELLS UNDER STABILITY, POWER AND SPEED CONSTRAINTS**

**A Thesis Submitted

In Partial Fulfillment of the Requirements

for the Degree of**

**DOCTOR OF PHILOSOPHY**

**by**

**Ram Murti Rawat

(2K19/PHDCO/13)**

**Under the Supervision of

Prof. Vinod Kumar**

**Professor**

**Department of Computer Science and Engineering

Delhi Technological University, Delhi**

**Department of Computer Science and Engineering

DELHI TECHNOLOGICAL UNIVERSITY**

**(Formerly Delhi College of Engineering)**

**Shahbad Daulatpur, Main Bawana Road**

**Delhi-110042, India**

**November, 2025**

## CANDIDATE'S DECLARATION

I, **Ram Murti Rawat (Roll No. 2K19/PHDCO/13)** student of Ph.D., hereby declare that the Dissertation titled "**Design and Analysis of SRAM Cells under Stability, Power and Speed Constraints**" which is submitted by me to the Department of Computer Science and Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of **Doctor of Philosophy**, is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma, Associateship, Fellowship, or other similar title or recognition.

Place: DTU, Delhi

Date: 10-November-2025

**Ram Murti Rawat**

This is to certify that the student has incorporated all the corrections suggested by the examiners in the thesis, and the statement made by the candidate is correct to the best of our knowledge.

**Signature of Supervisor**

**Signature of External Examiner**

## CERTIFICATE

Certified that **Ram Murti Rawat** (2K19/PHDCO/13) has carried out their research work presented in this thesis entitled **“Design and Analysis of SRAM Cells under Stability, Power and Speed Constraints”** for the award of **Doctor of Philosophy** from Delhi Technological University, Delhi, under my supervision. The thesis embodies results of original work, and studies are carried out by the student himself, and the contents of the thesis do not form the basis for the award of any other degree to the candidate or to anybody else from this or any other University/Institution.

Place: DTU, Delhi

Date: 10-November-2025

**Prof. Vinod Kumar**

Supervisor

Department of CSE

Delhi Technological University

Delhi, India

## ABSTRACT

Memory plays a vital role in most of the electronic devices used in embedded systems. The increasing processing workload has led to a growing demand for low-power, high-performance SRAM cells. The memories are formed by an array of SRAM cells for data storage and their peripheral circuits. The peripheral circuit comprises row-column decoders and pre-charge circuitry. The 6T SRAM cell was the industry standard, but with decreasing technology node and  $V_{DD}$  scaling, the performance of the 6T SRAM cell was deteriorating. This has motivated researchers to design other SRAM cells. SRAM cells play a crucial role in the design of system-on-chips (SoCs), constituting a substantial portion of the die area and thereby contributing to increased power consumption. Despite significant advancements in SRAM performance in finer technologies, concerns persist regarding cell stability in the deep sub-micron domain.

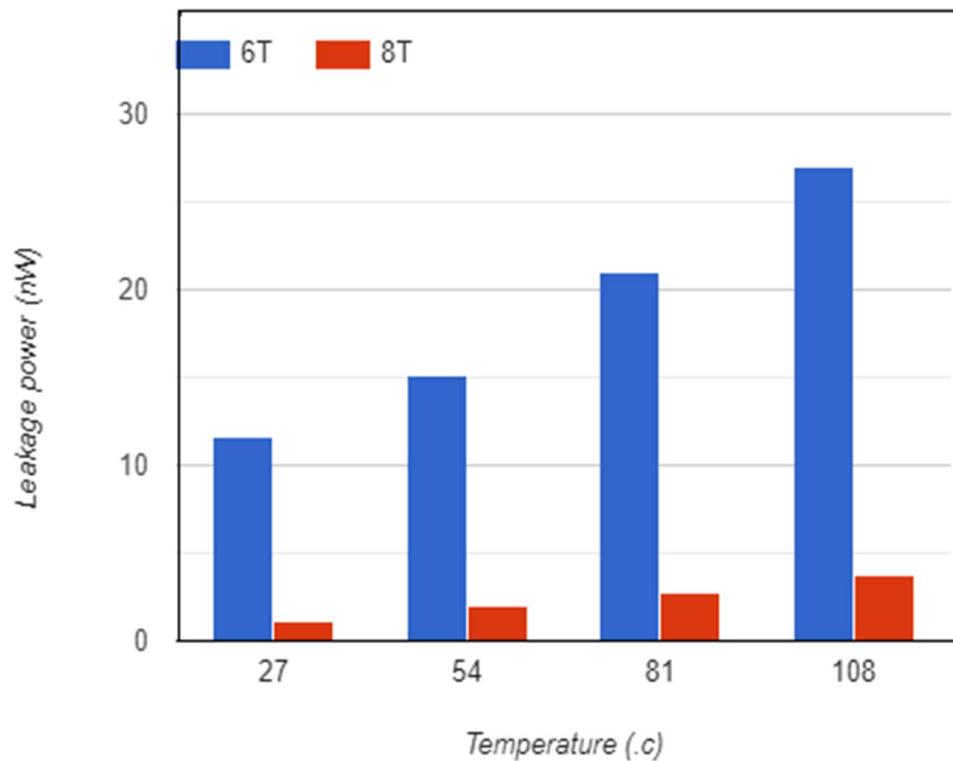

This **thesis** introduces an innovative approach to address these issues by proposing a low-power SRAM cell based on swing restoration inverter (SRI). The swing restoration inverter (SRI) addresses the challenge of swing voltages in finer technologies by integrating two additional transistors to act as swing-restored elements. This innovation results in an impressive 67% reduction in leakage power at 27°C for the 90 nm technology. To evaluate the effectiveness of the proposed SRI-based SRAM cell, performance metrics such as delay and power delay product are calculated. In the context of a 6T SRAM cell in the 90 nm technology, the conventional inverters are replaced with the swing restoration inverter (SRI). The implementation of SRI in an 8T SRAM cell leads to a substantial 91% reduction in leakage power at 30°C and an impressive 91.22% reduction at 27°C compared to the conventional 6T SRAM cell. The SRI technique proves instrumental in enhancing stability, resulting in the proposed 8T SRAM cell outperforming its 6T SRAM counterpart. However, it's important to note that the heightened performance of the proposed 8T SRAM cell comes at the expense of four additional transistors. Simulations are conducted using the 90 nm technology and the Cadence Virtuoso simulator to validate the effectiveness of the swing restoration inverter (SRI) technique in mitigating power consumption and enhancing stability in SRAM cells.

This **thesis examines** the factors that affect the Static Noise Margin (SNM) of Static random-access memories. find the equivalent time, improve hold, read, and write operation of the low power 8T SRAM cell, which is better than 6T SRAM and standard

8T SRAM cells using swing restoration dual node voltages for hold, read, and write operation, and improve stability analysis. This circuit or architecture-level SRAM technique is required to improve hold, read, and write SNM. **This thesis**, Comparative Analysis of 6T SRAM, standard 8T SRAM, and low power 8T SRAM cells with improved read and write noise margin, is completed for nanometer technology.

The typical memory for very large-scale integrated (VLSI) circuits has traditionally been static random-access memory (SRAM) because it has offered faster speeds compared to other alternatives. However, SRAM has been associated with a high-power consumption rate. Researchers have recognized the importance of lowering the power consumption of SRAM cells due to their critical role in memory architecture. This literature review has aimed to provide innovative and effective strategies for designing low-power SRAM cells. Several circuit topologies and methodologies have been introduced to compute stability, leakage current, delay, and power, and novel techniques for designing SRAM cells based on eight transistors (8T) have been proposed. SRAM has frequently been chosen over dynamic random-access memory (DRAM) because it has demonstrated faster speeds and lower power consumption. It has been named "static" because no modification or action, such as refreshing, has been required to maintain data intact. However, leakage current in SRAM has often increased and impaired its performance as technology nodes have been scaled down. Voltage scaling has been adopted as a solution to this issue, although it has also affected the stability and latency of SRAM. A separate (isolated) read port has been employed to enhance read stability, while a negative bit-line (NBL) write-aid circuit has been implemented to improve write capability. The proposed design has been evaluated against cutting-edge approaches based on criteria such as write static noise margin (WSNM), write stability, read static noise margin (RSNM), and other performance metrics. Future research has been directed toward exploring novel circuit topologies and methodologies to further enhance stability, reduce leakage current, and minimize delay and power consumption. Researchers have also investigated the performance of SRAM cells at smaller technology nodes to develop new techniques for maintaining stability and performance at these scales. Additional efforts have been made to explore new approaches to voltage scaling and to develop methods that improve the read and write capabilities of SRAM cells.

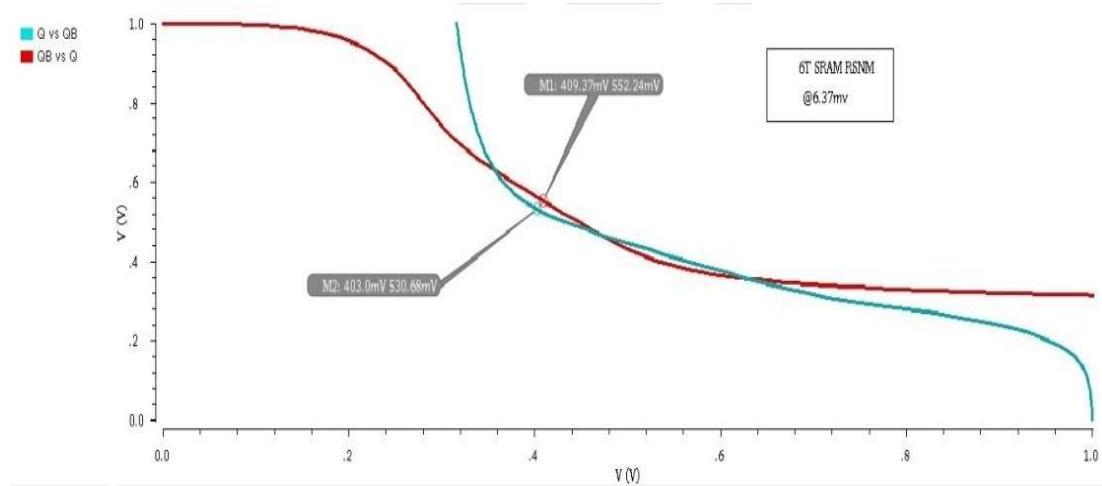

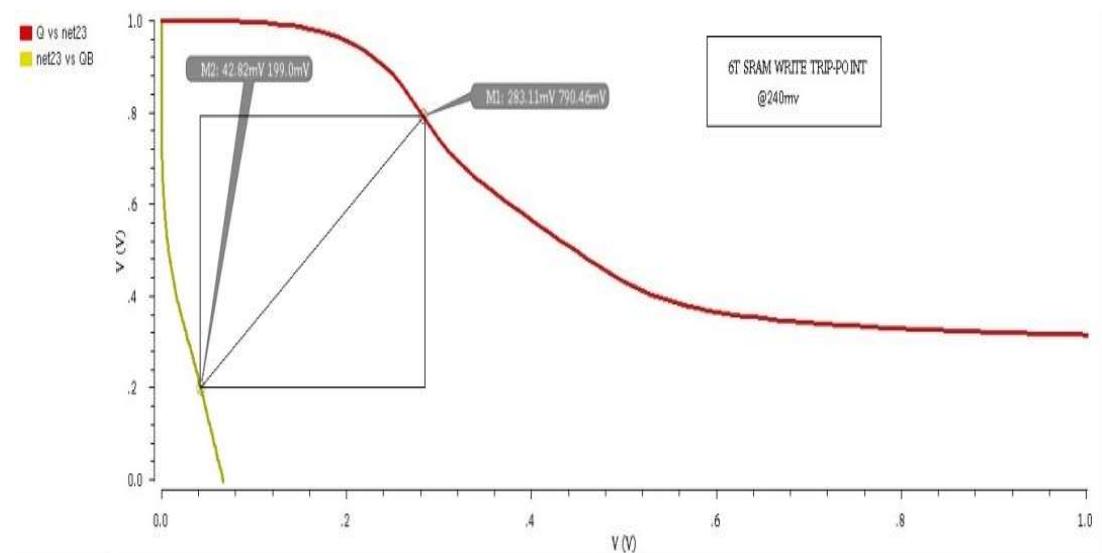

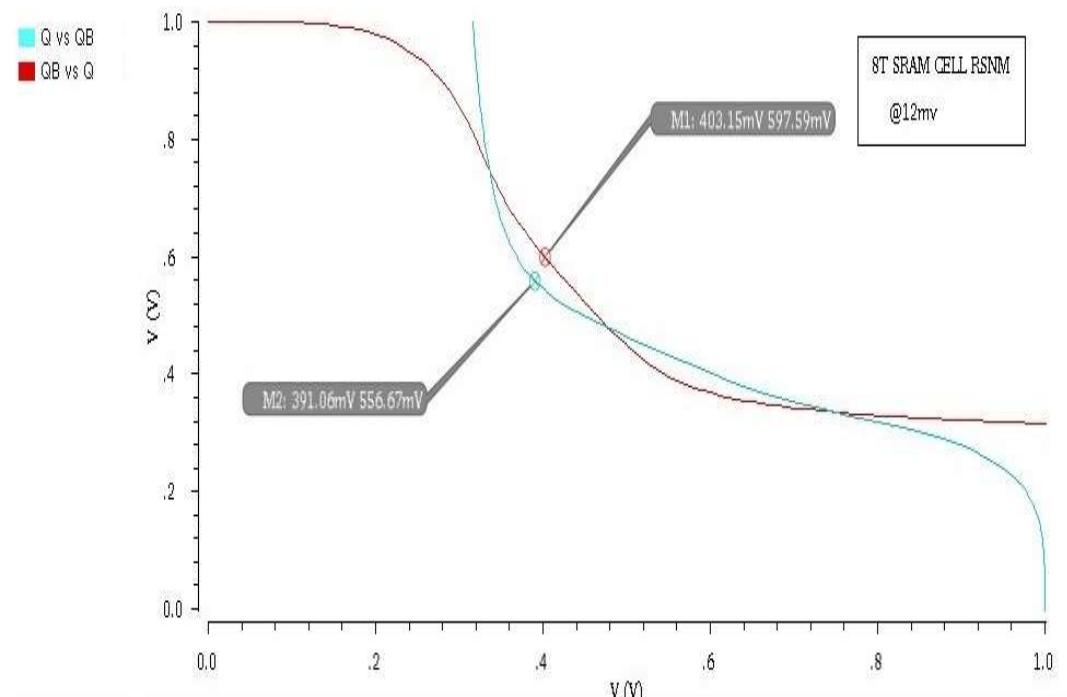

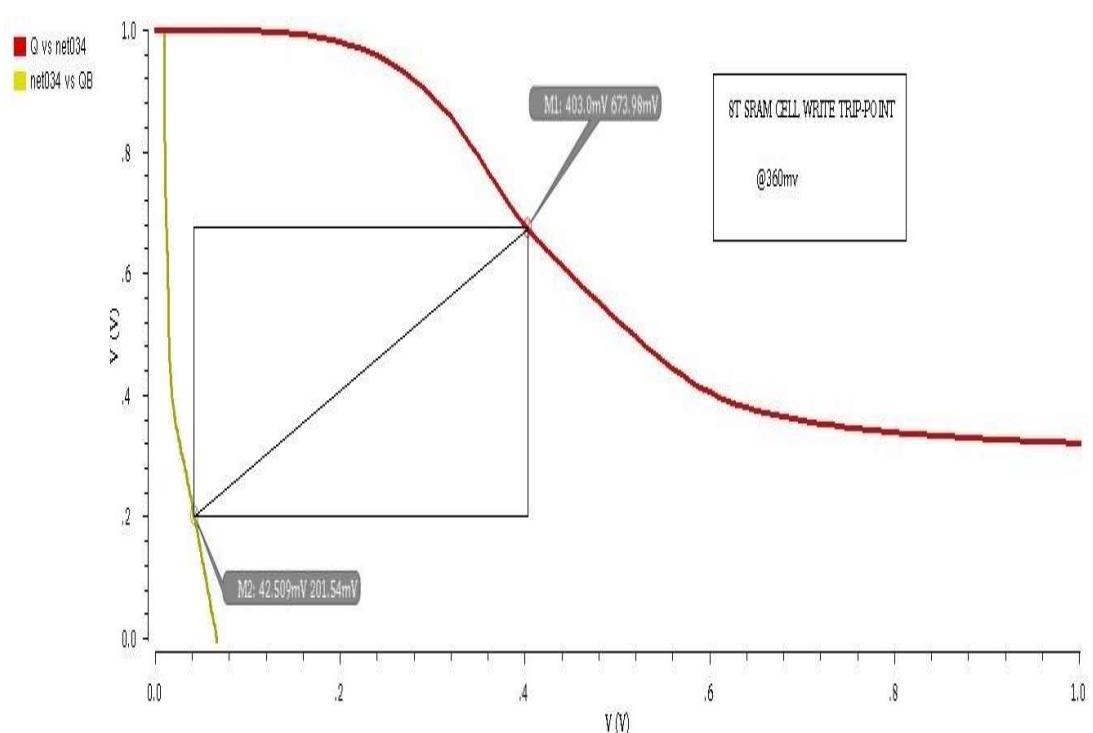

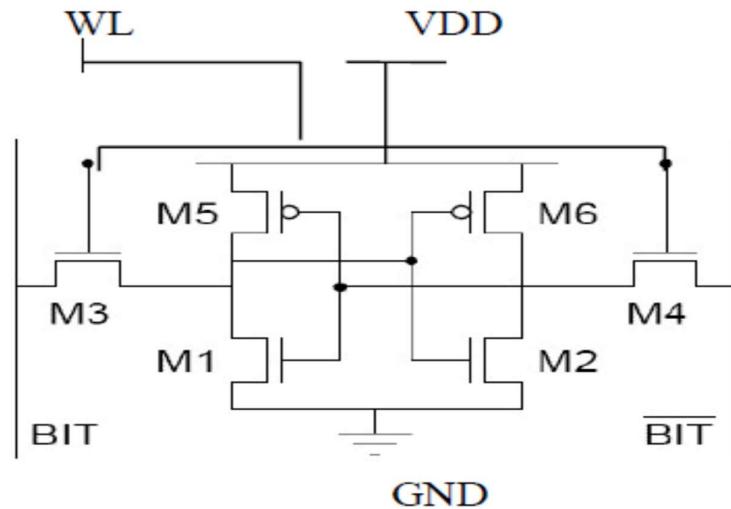

In this thesis, we introduce a proposed 8T SRAM cell that incorporates an isolated read path to enhance read stability compared to the conventional 6T SRAM cell. To address leakage power, two PMOS transistors are integrated into the read and write circuitry, effectively minimizing leakage current induced by stacking effects. The proposed 8T SRAM cell design demonstrates a substantial reduction in leakage current, exhibiting a decrease of 61.11% compared to the 6T SRAM cells, respectively. Moreover, the read operation for the newly proposed 8T SRAM cell is significantly improved, showcasing a 53.08% improvement compared to the 6T SRAM cell, respectively. The results also indicate noteworthy speed enhancements during write operations, boasting a 66.66% improvement compared to the 6T and 8T SRAM cells, respectively. The Read Static Noise Margin (RSNM) and write trip point (WTP) of the proposed cell measure at 12 mV and 360 mV, respectively, signifying an improvement over the conventional 6T SRAM cell measures at 6.37 mV and 240 mV. The effectiveness of the proposed cell is validated through comprehensive simulation analyses conducted in the Cadence Virtuoso environment at the 90 nm technology node.

All the proposed cells are of a double-ended nature owing to their better performance at lower power and high speed. This growing demand for double-ended cells has also generated the need for a swing restoration inverter (SRI) and negative bit line (NBL) circuits that are compatible with the array of double-ended SRAM cells. Conventionally, sense amplifiers were designed with differential-ended SRAM cells. These SRAM cells are usually voltage-based in nature, owing to their low power and high speed with low operational  $V_{DD}$ . Thus, this generates a need for double-ended SRAM cells that have low power consumption.

## ACKNOWLEDGEMENTS

I would like to express my deepest gratitude and sincere appreciation to all those who have contributed to the completion of my doctoral thesis. Their guidance, support, and encouragement have been invaluable throughout this journey.

First and foremost, I am immensely grateful to my supervisor, Prof. Vinod Kumar, Department of Computer Science and Engineering, Delhi Technological University, Delhi, India. I am greatly thankful for his unwavering commitment, patience, and expertise. His guidance and insightful feedback have been instrumental in shaping the direction of my research and enhancing the quality of my work. I am truly fortunate to have had such a dedicated mentor who consistently challenged and inspired me to reach new heights.

I express my sincere gratitude towards the distinguished faculty members who have, time and again, helped me at different stages. I extend my sincere regards to Prof. Manoj Kumar, HoD, (Department of Computer Science and Engineering), for his constant support. I wish to express my gratitude towards the DRC chairperson, the distinguished DRC members. Their expertise, constructive criticism, and valuable suggestions have significantly contributed to the refinement of my thesis. I am deeply grateful for the time and effort they invested in reviewing and evaluating my work.

I am indebted to the esteemed faculty members of the Department of Computer Science and Engineering, Delhi Technological University, Delhi, who provided me with a rich academic environment and facilitated my intellectual growth. Their lectures, seminars, and discussions have expanded my horizons and shaped my research interests.

I express my deepest regards for Prof. V. N. Mishra, Department of Electronics Engineering, IIT (BHU), Varanasi, India, and Dr. Deva Nand, Department of ECE, DTU, Delhi, India, for investing their valuable time and efforts in providing deep and insightful remarks.

Lastly, I would like to thank my family for their kindness, support, and patience throughout my journey. Their belief in me has kept my spirits and motivation high during this process. Their understanding, love, and encouragement have been a constant source of motivation, and I am truly grateful for their presence in my life.

Finally, I would like to acknowledge the financial support provided by Delhi Technological University, Delhi. Their assistance enabled me to carry out my research effectively and ensured that I had the necessary resources to complete my thesis.

To all those who have directly or indirectly contributed to my doctoral thesis, I extend my deepest gratitude. Your support, whether big or small, has played a significant role in shaping my academic and personal growth. I am profoundly grateful for your presence in my life and for the impact you have had on my journey as a researcher.

**Ram Murti Rawat**

(2K19/PHDCO/13)

## TABLE OF CONTENTS

|                                   | <b>Page No.</b> |

|-----------------------------------|-----------------|

| Candidate's Declaration           | ii              |

| Certificate                       | iii             |

| Abstract                          | iv              |

| Acknowledgement                   | vii             |

| List of Tables                    | xiii            |

| List of Figures                   | xiv             |

| List of Symbols and Abbreviations | xvii            |

## **CHAPTER 1: INTRODUCTION AND MOTIVATION** **1 – 12**

|     |                                                   |    |

|-----|---------------------------------------------------|----|

| 1.1 | INTRODUCTION TO SEMICONDUCTOR PROCESS             | 1  |

| 1.2 | INTRODUCTION TO MEMORY                            | 2  |

|     | 1.2.1 Primary Storage                             | 3  |

|     | 1.2.2 Secondary Storage                           | 3  |

|     | 1.2.3 Tertiary Storage                            | 4  |

|     | 1.2.4 Offline Storage                             | 4  |

| 1.3 | CLASSIFICATION OF CMOS MEMORIES                   | 4  |

|     | 1.3.1 Volatile Memories                           | 4  |

|     | 1.3.1.1 Dynamic Random Access Memory              | 4  |

|     | 1.3.1.2 Static Random Access Memory               | 5  |

|     | 1.3.2 Non-Volatile Memories                       | 5  |

|     | 1.3.2.1 Read-Only Memory                          | 5  |

|     | 1.3.2.2 FLASH Memory                              | 5  |

| 1.4 | MEMORY ORGANIZATION                               | 5  |

| 1.5 | MOTIVATION AND OBJECTIVES                         | 8  |

|     | 1.5.1 Low Power and High-Speed SRAM Cell          | 8  |

|     | 1.5.2 Improved Stability of SRAM Cell             | 8  |

|     | 1.5.3 Low-Leakage and High-Stability of SRAM Cell | 8  |

| 1.6 | THESIS ORGANIZATION                               | 10 |

**CHAPTER 2: LITERATURE REVIEW** **13 – 35**

|       |                                        |    |

|-------|----------------------------------------|----|

| 2.1   | INTRODUCTION TO THE PROCESSOR          | 13 |

| 2.2   | LITERATURE SURVEY                      | 14 |

| 2.2.1 | Definition of the Research Questions   | 14 |

| 2.2.2 | Conduct Search                         | 14 |

| 2.2.3 | Screening of Papers                    | 14 |

| 2.3   | REVIEW OF DIFFERENT SRAM CELLS DESIGNS | 15 |

| 2.4   | SUMMARY OF RESEARCH REVIEW             | 23 |

| 2.5   | RESEARCH GAPS                          | 35 |

| 2.6   | RESEARCH OBJECTIVES                    | 35 |

**CHAPTER 3: LOW POWER SRAM CELL USING SWING

RESTORATION INVERTER (SRI)** **36 – 55**

|       |                                                                  |    |

|-------|------------------------------------------------------------------|----|

| 3.1   | INTRODUCTION TO SYSTEM ON CHIP (SoC)                             | 37 |

| 3.2   | SWING RESTORATION INVERTER (SRI)                                 | 41 |

| 3.2.1 | Transfer Characteristics                                         | 43 |

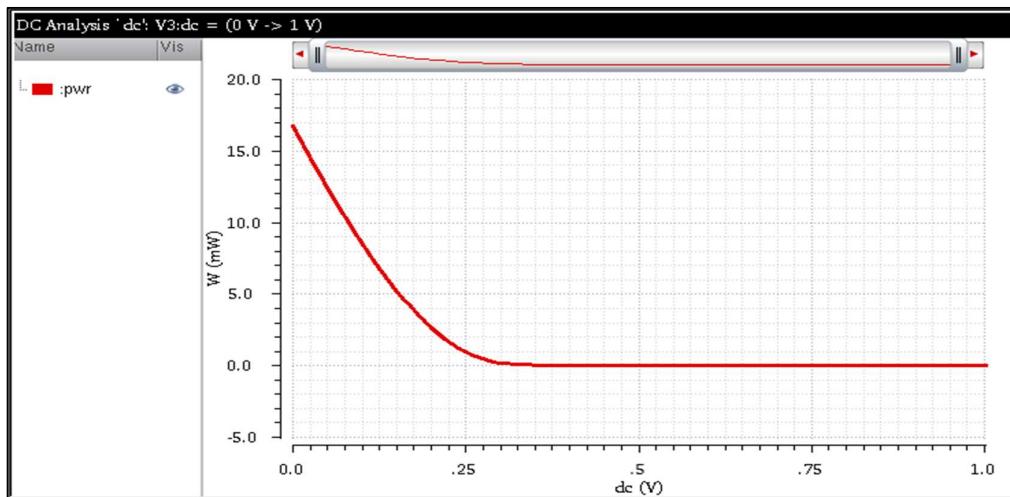

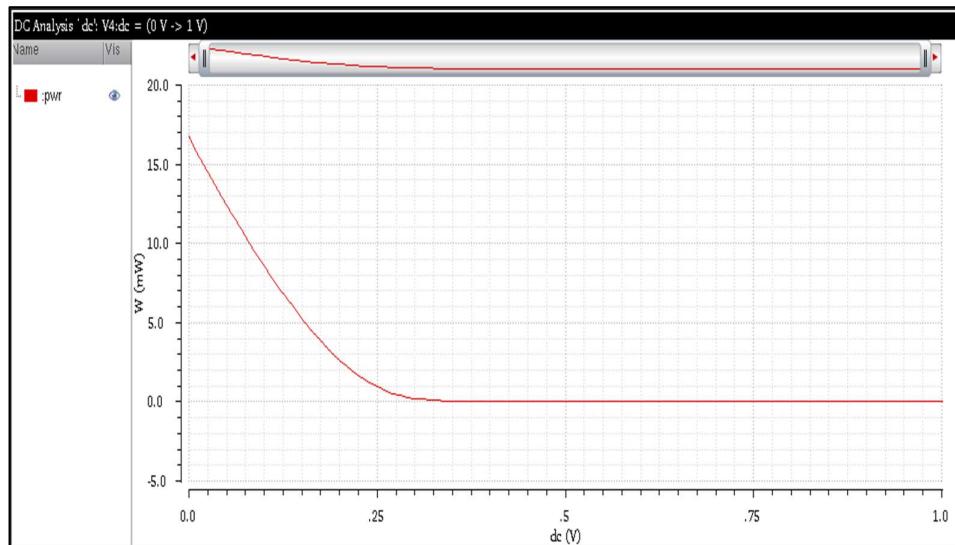

| 3.2.2 | Leakage Power                                                    | 44 |

| 3.2.3 | Dynamic Power                                                    | 44 |

| 3.2.4 | Power Delay Product (PDP)                                        | 45 |

| 3.3   | CONVENTIONAL 6T SRAM CELL VERSUS PROPOSED 8T<br>SRAM CELL DESIGN | 45 |

| 3.4   | PROPOSED 8T SRAM CELL MODE OF OPERATIONS                         | 50 |

| 3.5   | IMPROVED STABILITY                                               | 50 |

| 3.5.1 | Read Stability                                                   | 50 |

| 3.5.2 | Write Stability                                                  | 50 |

| 3.5.3 | Hold Stability                                                   | 50 |

| 3.6   | RESULTS AND DISCUSSIONS                                          | 51 |

| 3.7   | SUMMARY                                                          | 55 |

**CHAPTER 4: IMPROVED STABILITY OF LOW POWER SRAM

CELL** **56 – 68**

|       |                                              |    |

|-------|----------------------------------------------|----|

| 4.1   | INTRODUCTION TO LOW-POWER SRAM IN VLSI CHIPS | 57 |

| 4.2   | SIX-TRANSISTOR SRAM CELL                     | 58 |

| 4.3   | STANDARD 8T-SRAM CELL                        | 59 |

| 4.4   | EVALUATION OF VARIOUS PERFORMANCE PARAMETERS | 60 |

| 4.5   | LOW POWER 8T SRAM CELL                       | 61 |

| 4.6   | RESULTS AND DISCUSSIONS                      | 62 |

| 4.6.1 | Hold Stability                               | 62 |

| 4.6.2 | Read Stability                               | 64 |

| 4.6.3 | Write Stability                              | 66 |

| 4.7   | SUMMARY                                      | 68 |

**CHAPTER 5: LOW-LEAKAGE, HIGH-STABILITY SRAM CELL

FOR IoT APPLICATIONS** **69 – 93**

|       |                                                 |    |

|-------|-------------------------------------------------|----|

| 5.1   | INTRODUCTION TO THE INTERNET OF THINGS (IoT)    | 70 |

| 5.2   | PREVIOUS WORKS                                  | 72 |

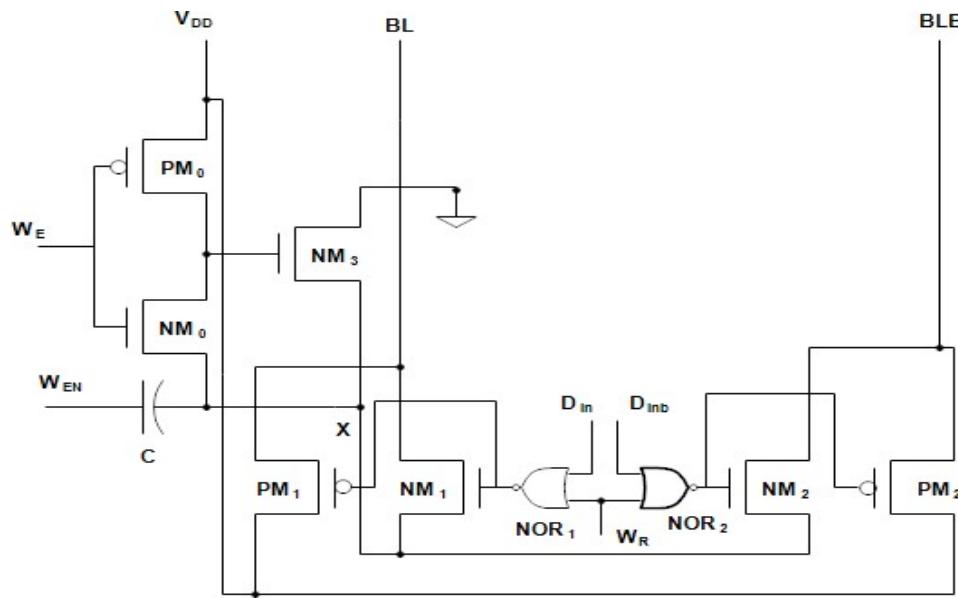

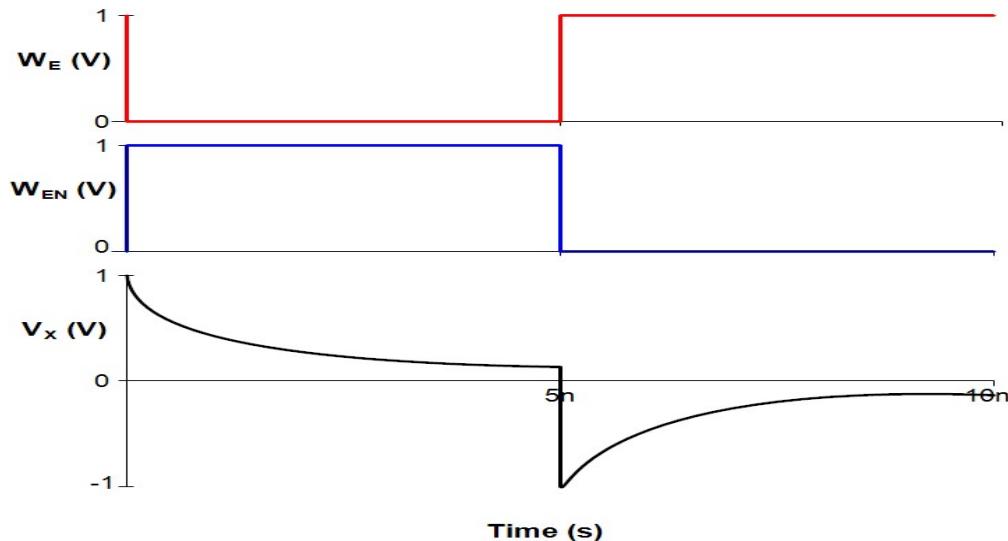

| 5.3   | NEGATIVE BIT-LINE GENERATOR CIRCUIT (NBL)       | 74 |

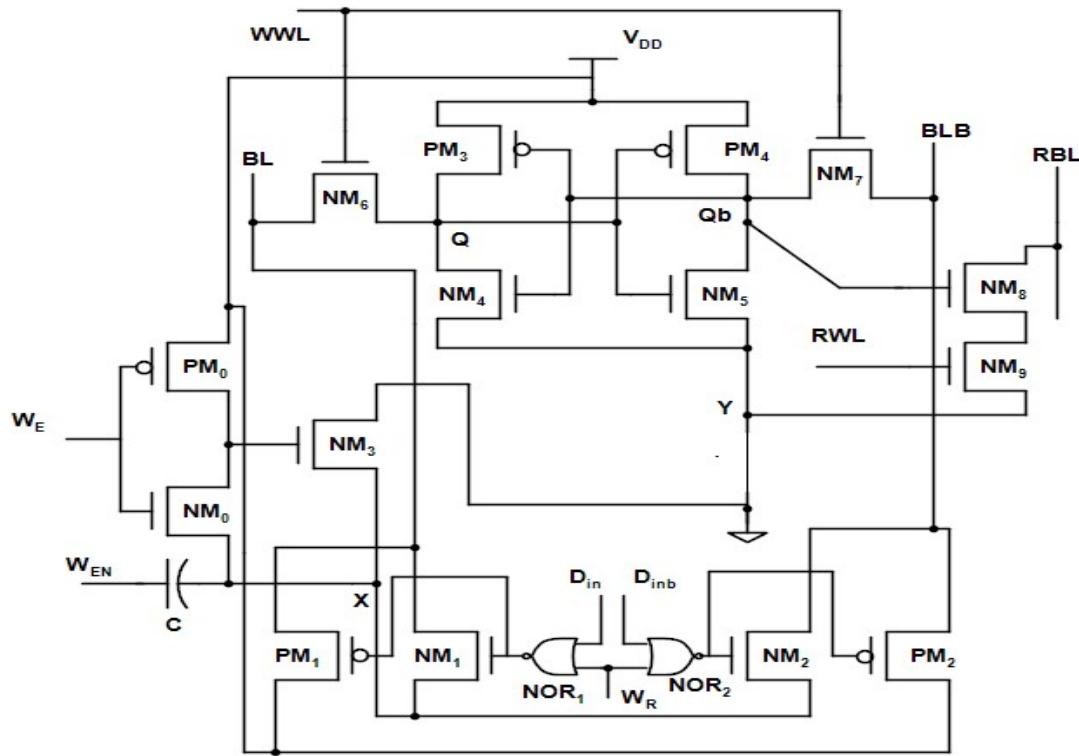

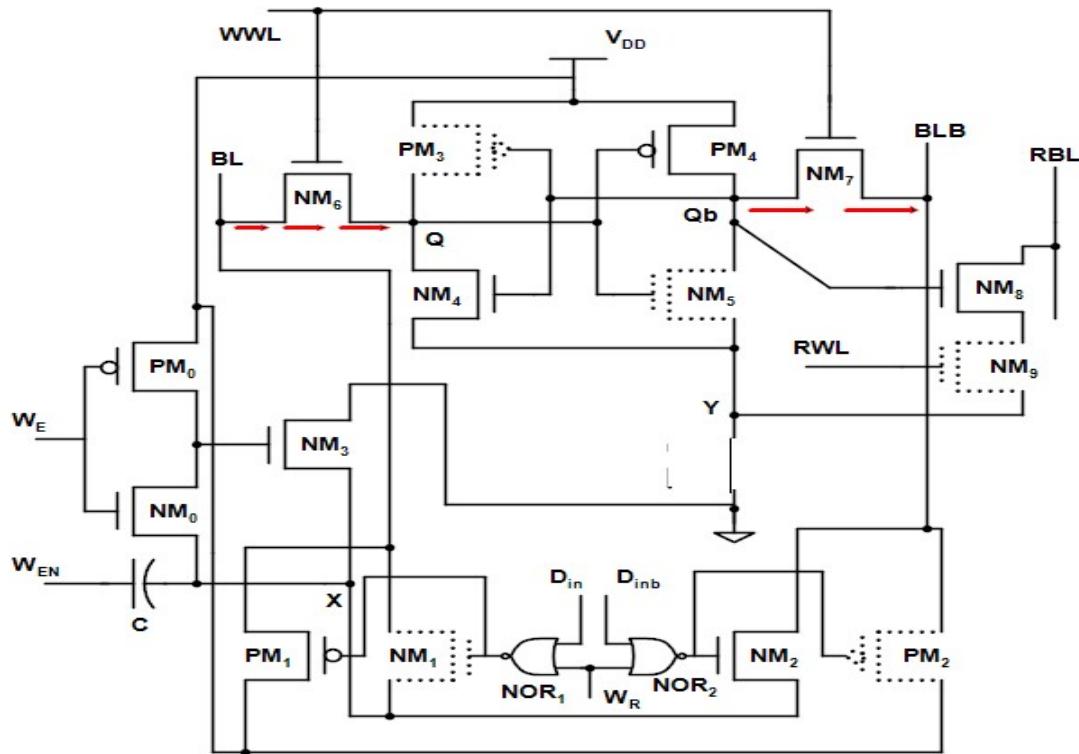

| 5.4   | PROPOSED DESIGN (NBL CIRCUIT WITH 8T SRAM CELL) | 77 |

| 5.4.1 | Write Operation                                 | 77 |

| 5.4.2 | Read Operation                                  | 79 |

| 5.4.3 | Hold Operation                                  | 79 |

| 5.5   | RESULTS AND DISCUSSIONS                         | 80 |

| 5.5.1 | Write-ability                                   | 80 |

| 5.5.2 | Read stability                                  | 83 |

| 5.5.3 | Hold stability                                  | 86 |

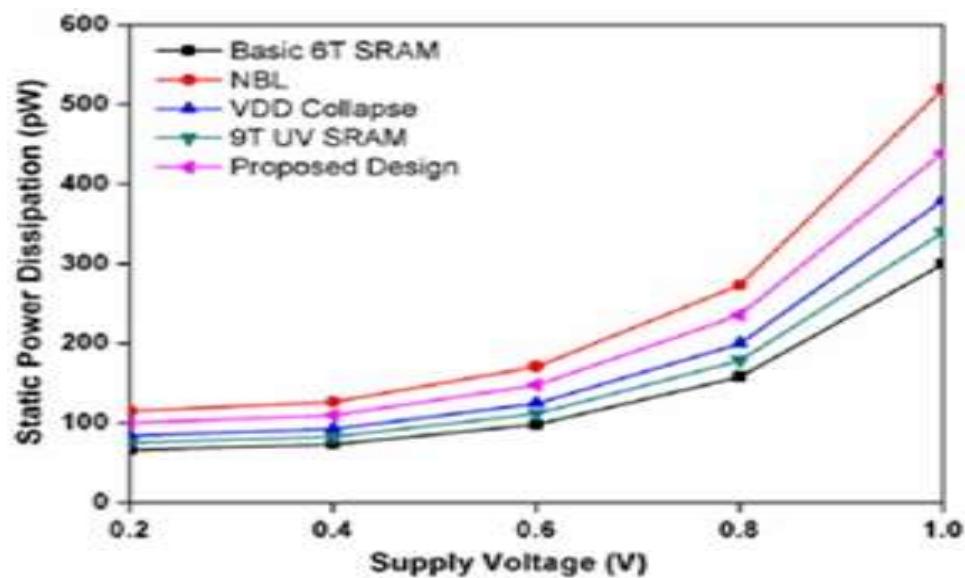

| 5.6   | STATIC POWER DISSIPATION                        | 87 |

| 5.7   | WRITE DELAY                                     | 89 |

| 5.8   | READ DELAY                                      | 90 |

| 5.9   | DYNAMIC POWER DISSIPATION                       | 91 |

| 5.10  | SUMMARY                                         | 93 |

**CHAPTER 6: ENERGY EFFICIENT SRAM CELL** **94 - 113**

|         |                                              |     |

|---------|----------------------------------------------|-----|

| 6.1     | LOW POWER ENERGY EFFICIENT 8T SRAM CELL      | 95  |

| 6.1.1   | Proposed methodology                         | 98  |

| 6.1.1.1 | Problem statement                            | 98  |

| 6.1.1.2 | Rationale for undertaking this research work | 99  |

| 6.1.1.3 | Our research contribution                    | 99  |

| 6.2     | 8T SRAM WITH VOLTAGE DEVIATE-DOMINO LOGIC    | 100 |

| 6.3     | 6T SRAM CELL VERSUS PROPOSED 8T SRAM CELL    | 103 |

| 6.4     | EVALUATION OF VARIOUS PERFORMANCE PARAMETERS | 105 |

| 6.4.1   | Stability                                    | 105 |

| 6.4.1.1 | Read static noise margin (RSNM)              | 105 |

| 6.4.1.2 | Write margin (WM)                            | 107 |

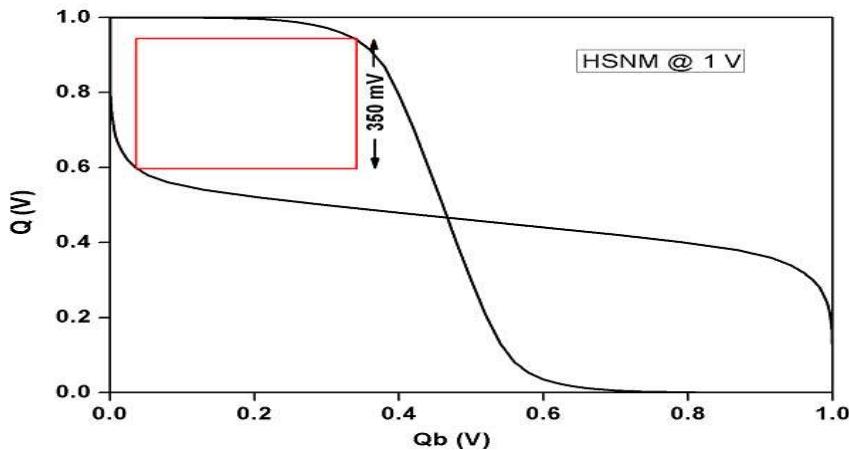

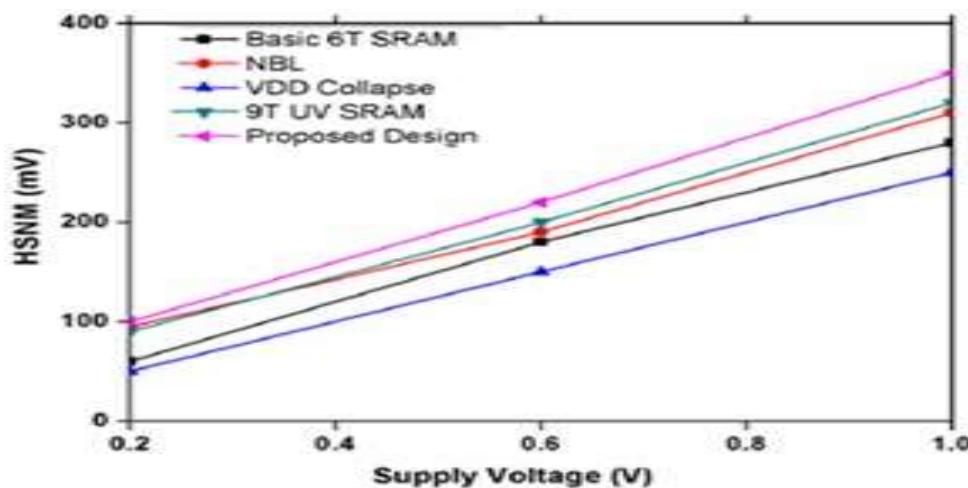

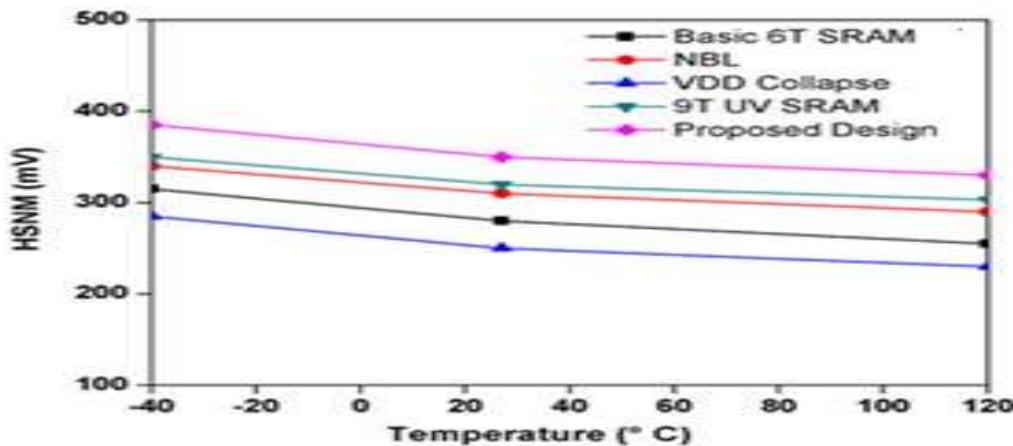

| 6.4.1.3 | Hold static noise margin (HSNM)              | 108 |

| 6.5     | POWER CONSUMPTION                            | 108 |

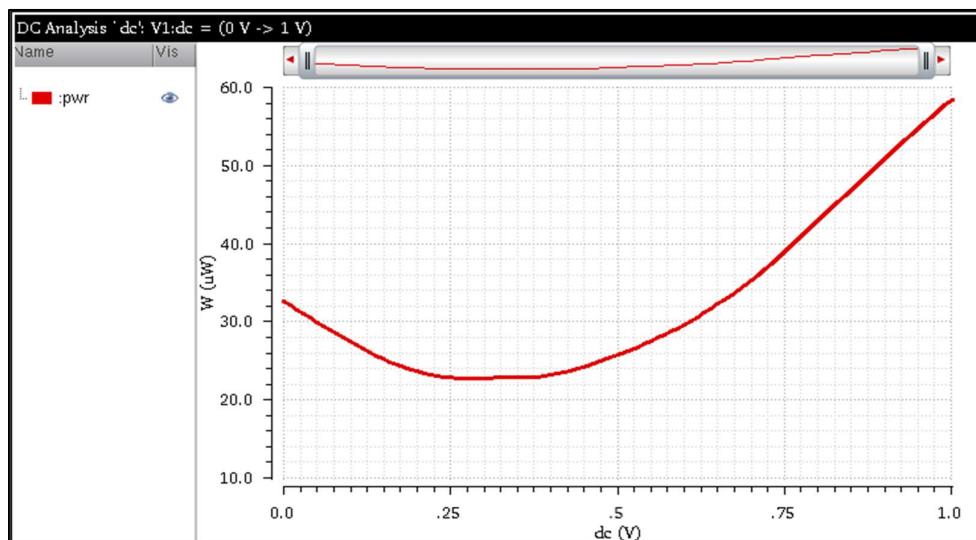

| 6.5.1   | Read power consumption                       | 109 |

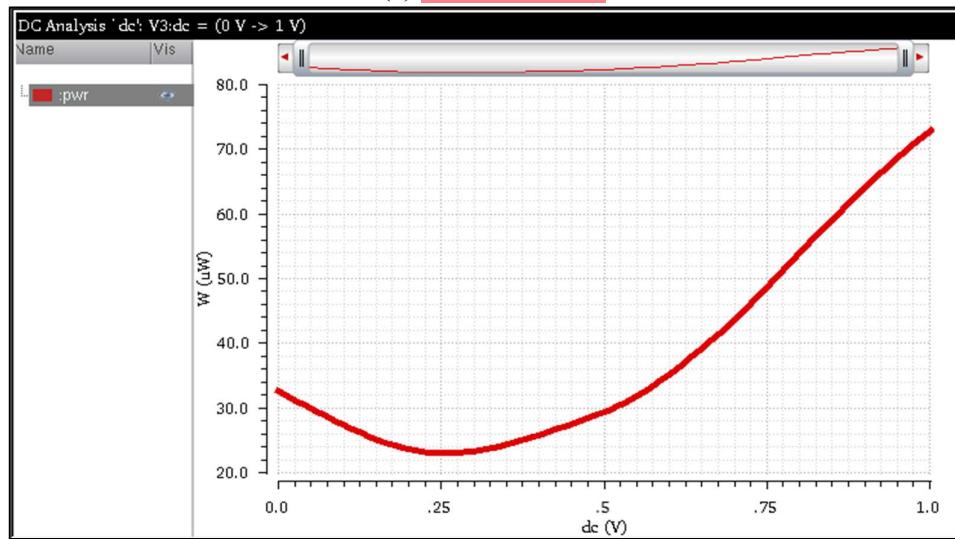

| 6.5.2   | Write power consumption                      | 110 |

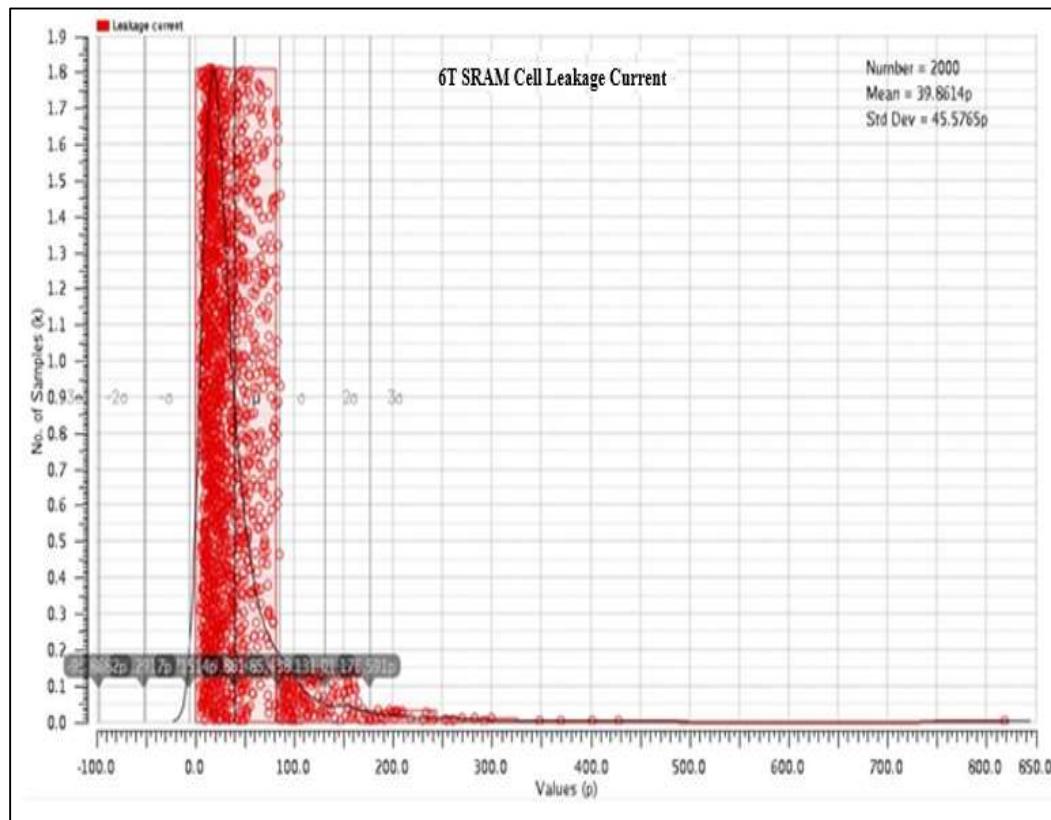

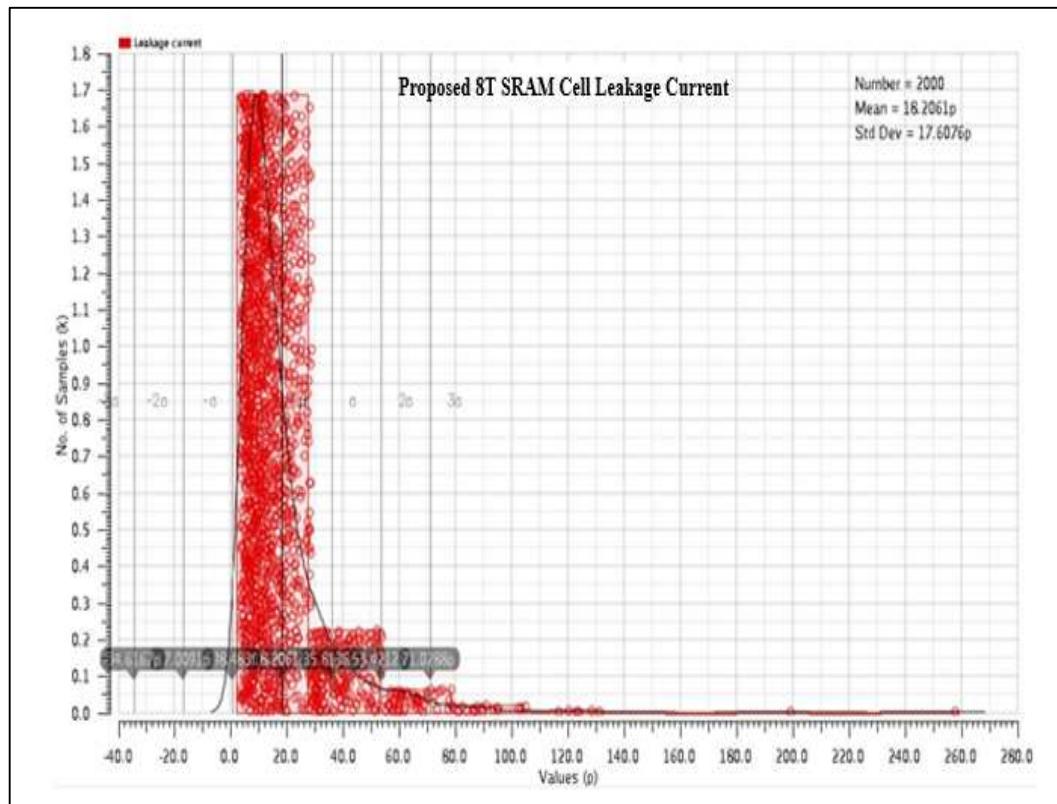

| 6.6     | LEAKAGE POWER CONSUMPTION                    | 111 |

| 6.7     | SUMMARY                                      | 113 |

**CHAPTER 7: CONCLUSIONS AND FUTURE SCOPE** **114 - 118**

|     |              |     |

|-----|--------------|-----|

| 7.1 | CONCLUSIONS  | 114 |

| 7.2 | FUTURE SCOPE | 117 |

**LIST OF PUBLICATIONS** **119 - 120****REFERENCES** **121 - 136**

## List of Tables

| S. No.           | Table Caption                                                                                       | Page No. |

|------------------|-----------------------------------------------------------------------------------------------------|----------|

| <b>Table 2.1</b> | Inclusion and exclusion criteria.                                                                   | 15       |

| <b>Table 2.2</b> | Summary of research review.                                                                         | 24       |

| <b>Table 3.1</b> | Comparison of dynamic power.                                                                        | 47       |

| <b>Table 3.2</b> | Time domain response.                                                                               | 47       |

| <b>Table 3.3</b> | Comparison of delay and power delay product (PDP).                                                  | 47       |

| <b>Table 3.4</b> | Comparison of Conventional 6T SRAM and Proposed 8T SRAM Leakage power.                              | 49       |

| <b>Table 3.5</b> | Characterization of SRAM cells.                                                                     | 53       |

| <b>Table 3.6</b> | Read operation word line voltage drop.                                                              | 53       |

| <b>Table 3.7</b> | Write operation word line voltage boost.                                                            | 53       |

| <b>Table 3.8</b> | Comparison of various SRAM cell design techniques.                                                  | 54       |

| <b>Table 4.1</b> | Comparison of Read SNM and Hold SNM.                                                                | 65       |

| <b>Table 4.2</b> | Comparison for write trip point (WTP) of 6T SRAM and standard 8T SRAM, and low power 8T SRAM cells. | 67       |

| <b>Table 5.1</b> | Comparison of the proposed design with other state of the art work.                                 | 91       |

| <b>Table 5.2</b> | Read and write power at different supply voltages.                                                  | 92       |

| <b>Table 5.3</b> | Dynamic power consumption comparison                                                                | 92       |

| <b>Table 6.1</b> | Comparison of various performance parameters of the SRAM cells.                                     | 112      |

## List of Figures

| S. No.            | Figure Caption                                                                                                     | Page No. |

|-------------------|--------------------------------------------------------------------------------------------------------------------|----------|

| <b>Fig. 1.1.</b>  | Types of computer data storage.                                                                                    | 3        |

| <b>Fig. 1.2.</b>  | <b>Classification of CMOS memories</b>                                                                             | 4        |

| <b>Fig. 1.3.</b>  | Organization of memory system.                                                                                     | 6        |

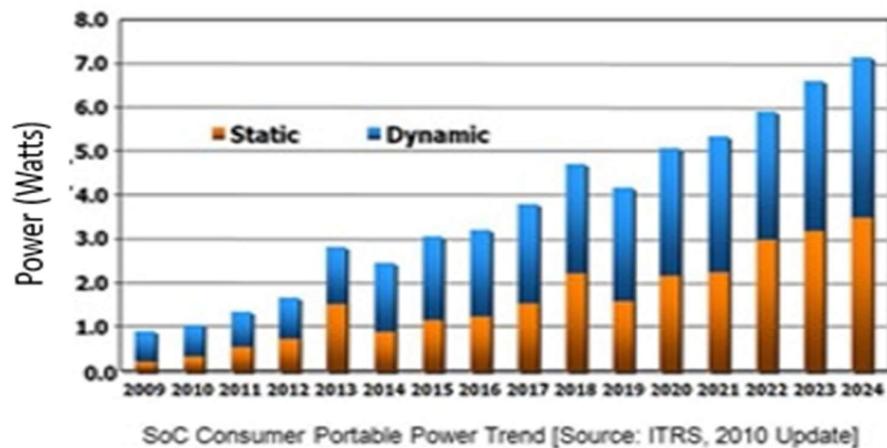

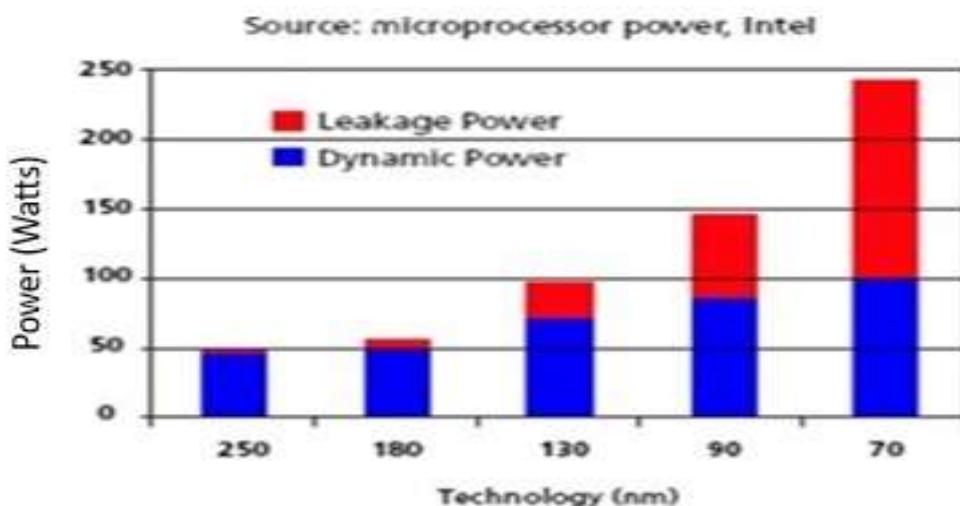

| <b>Fig. 3.1.</b>  | Evolution of leakage power for (a) Power trend in SoC and (b) Power consumption in various technology.             | 37<br>38 |

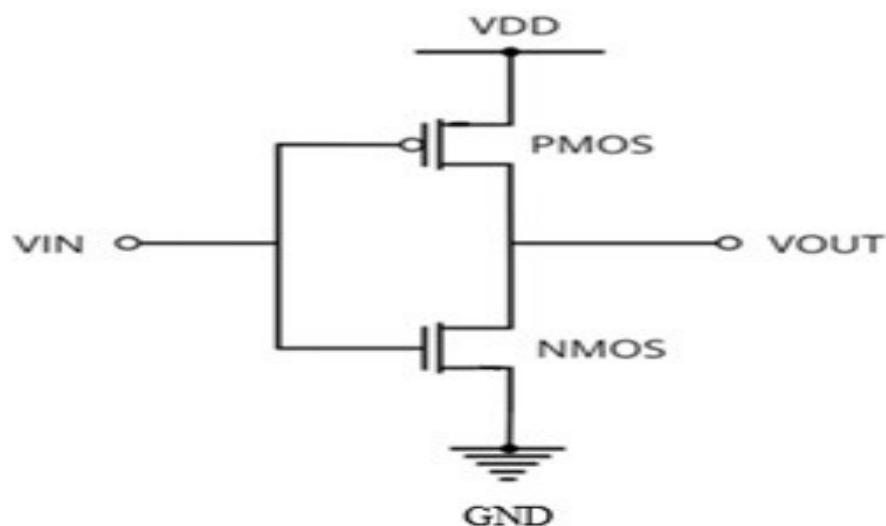

| <b>Fig. 3.2.</b>  | Circuit schematics for (a) Conventional inverter and (b) Swing restoration inverter (SRI).                         | 42<br>43 |

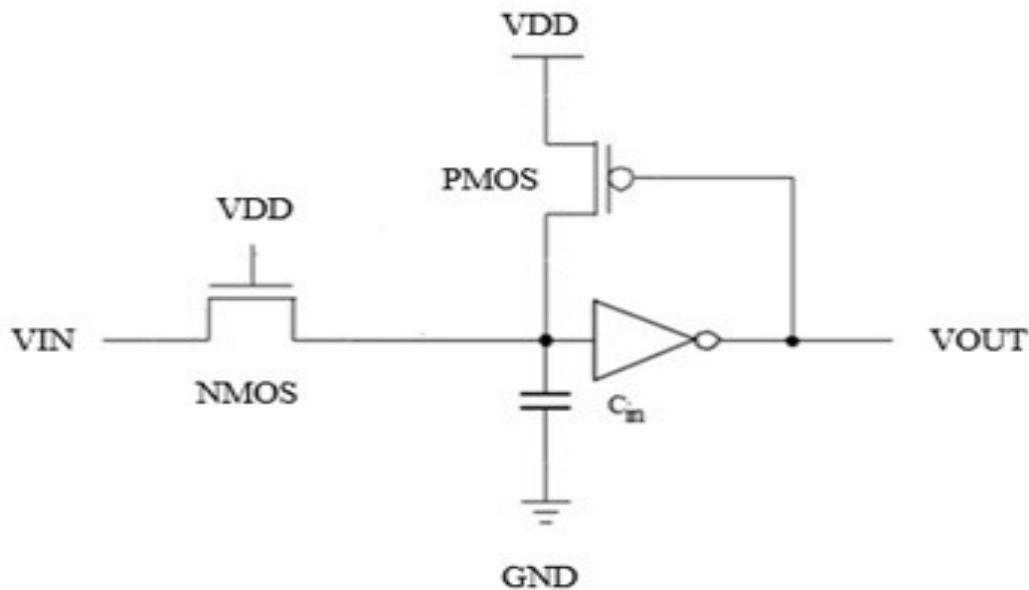

| <b>Fig. 3.3.</b>  | Dependency of node (Q) voltage on width of M6 (nm).                                                                | 43       |

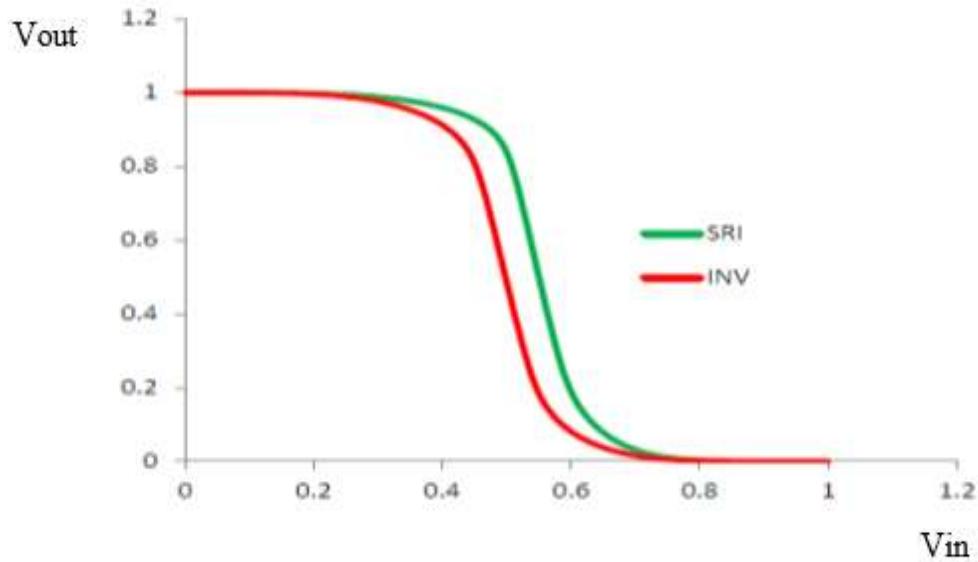

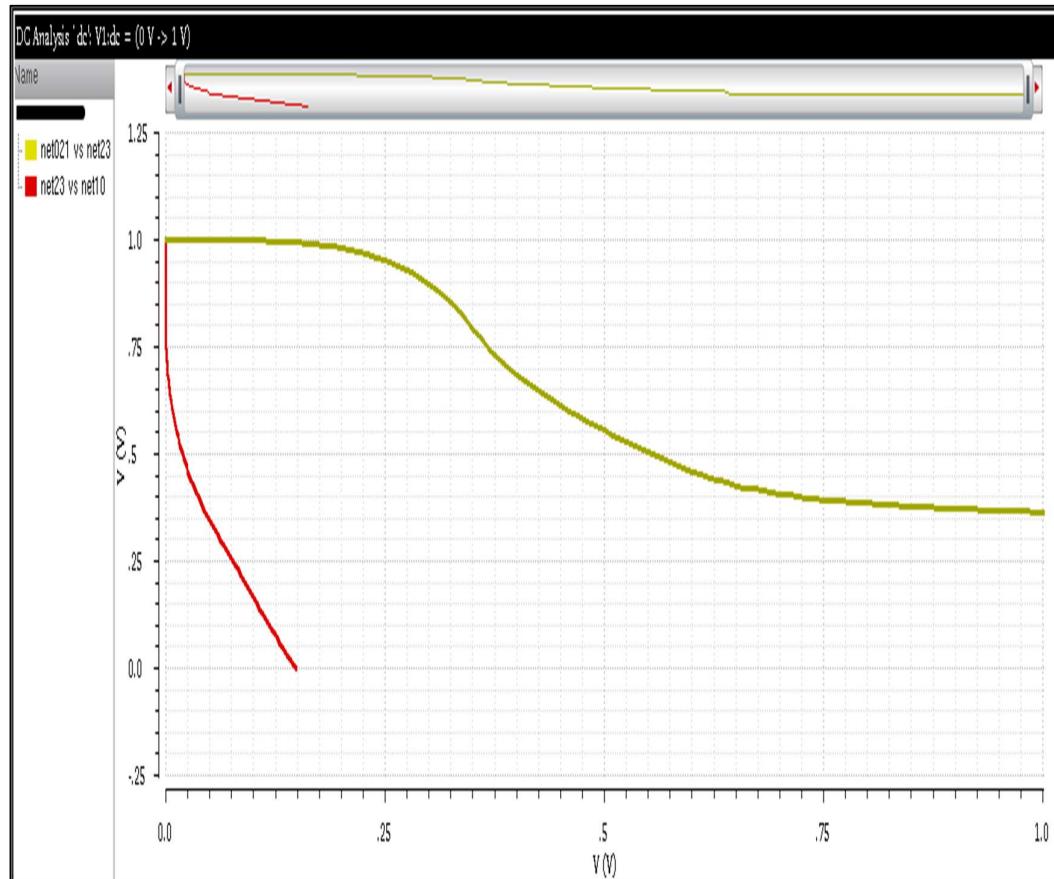

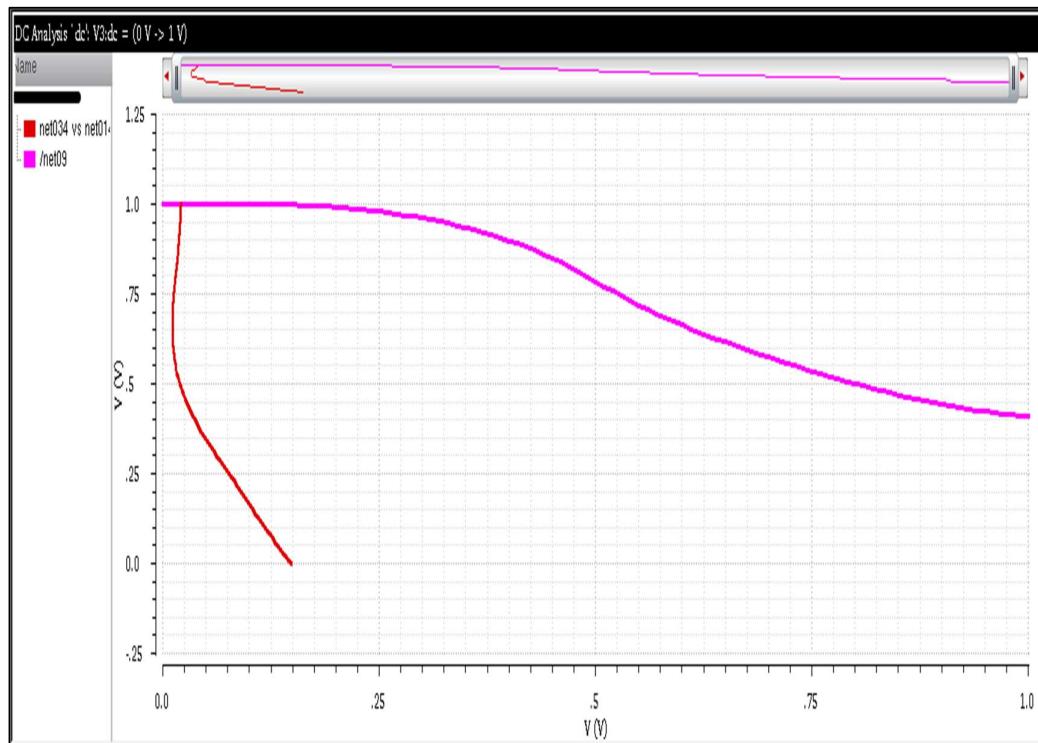

| <b>Fig. 3.4.</b>  | Inverter characteristics.                                                                                          | 44       |

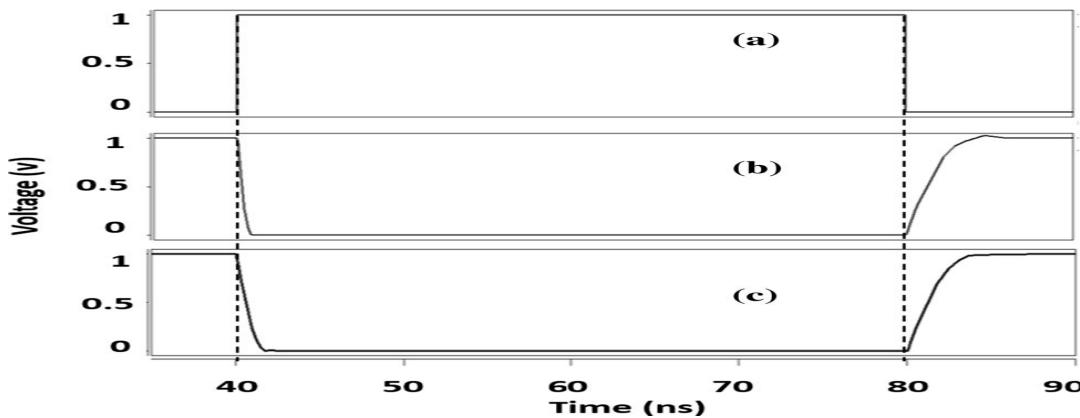

| <b>Fig. 3.5.</b>  | Time domain responses. (a) Inverter input. (b) Output of inverter. (c) Output of swing restoration inverter (SRI). | 46<br>46 |

| <b>Fig. 3.6.</b>  | Conventional 6T SRAM cell (W/L is in nanometers).                                                                  | 48       |

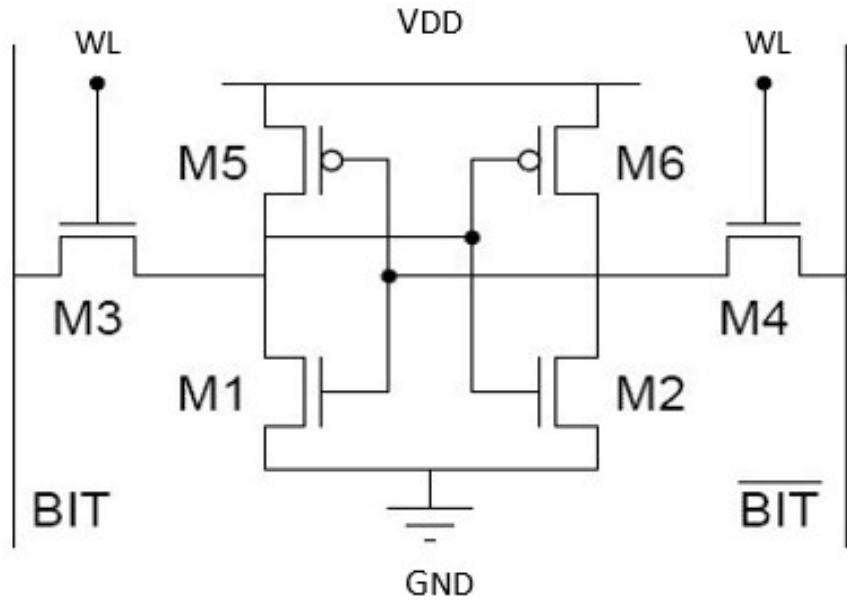

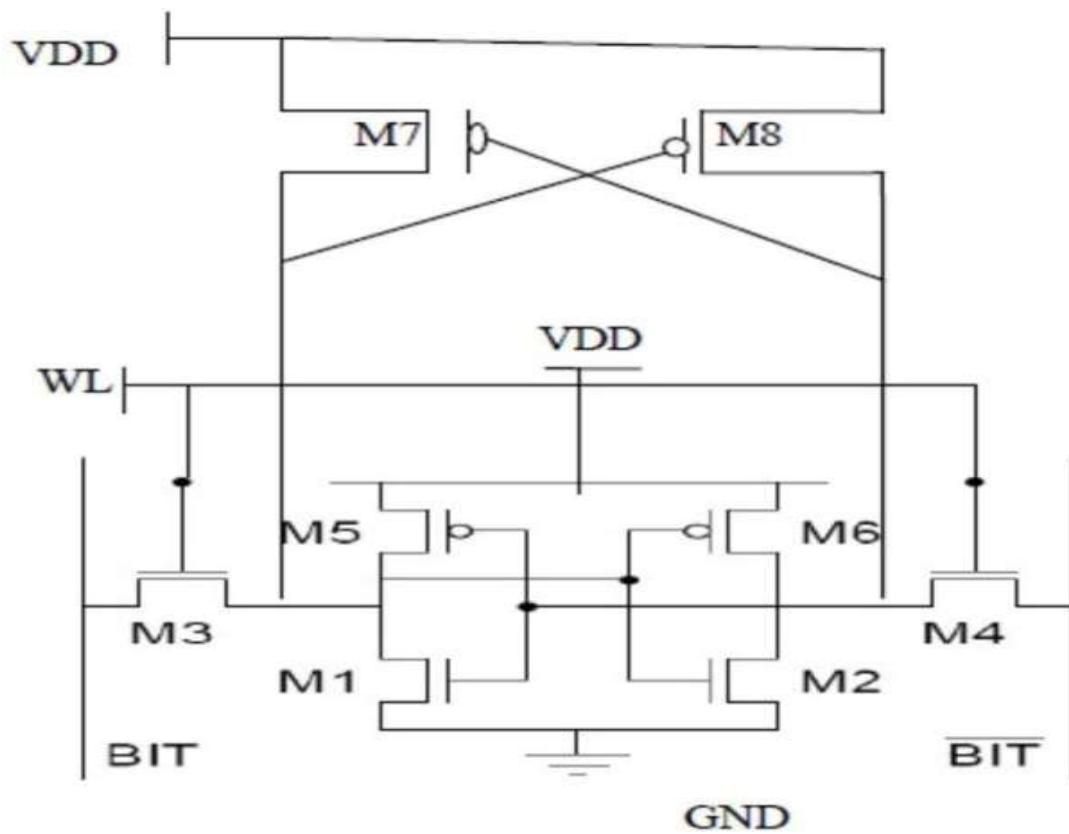

| <b>Fig. 3.7.</b>  | Proposed 8T SRAM cell (W/L is in nanometers).                                                                      | 48       |

| <b>Fig. 3.8.</b>  | Temperature dependency of leakage power.                                                                           | 49       |

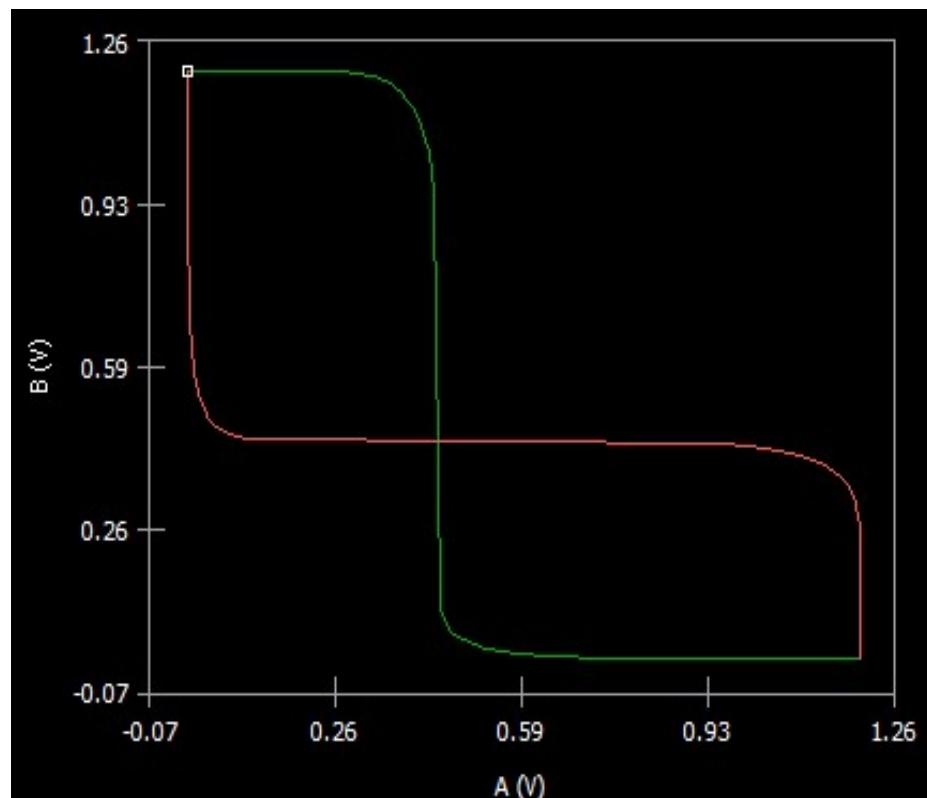

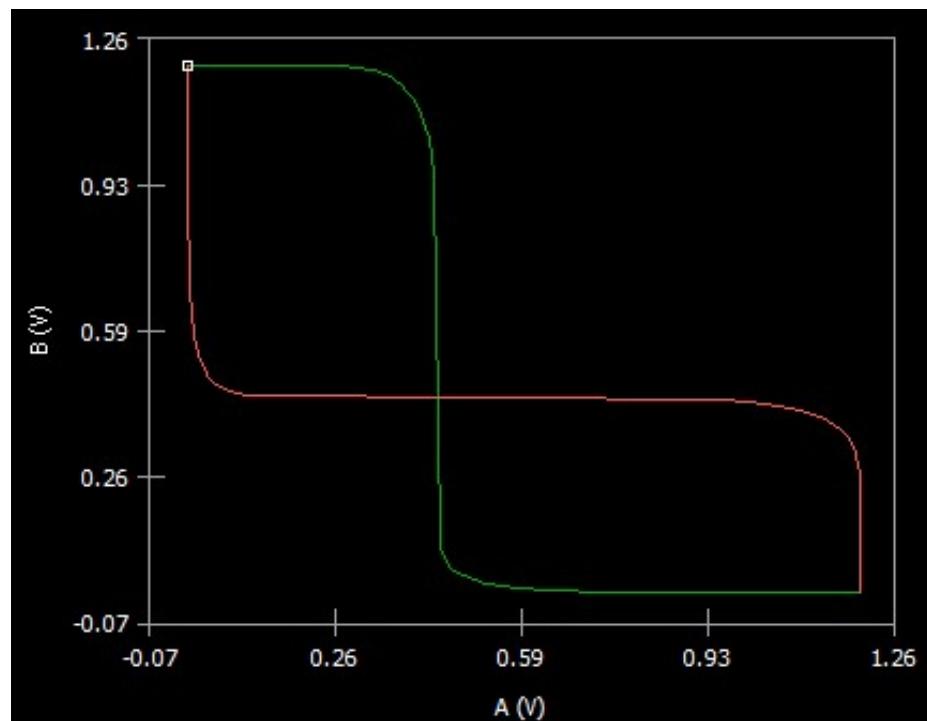

| <b>Fig. 3.9.</b>  | Characterization of conventional 6T SRAM cell for (a) RSNM and (b) WSNM.                                           | 51<br>51 |

| <b>Fig. 3.10.</b> | Characterization of proposed 8T SRAM cell for (a) RSNM and (b) WSNM.                                               | 52<br>52 |

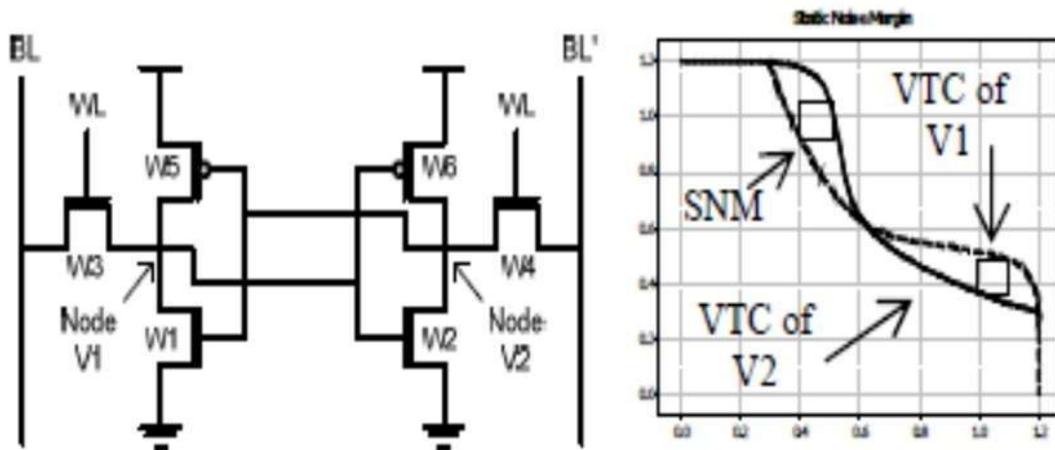

| <b>Fig. 4.1.</b>  | Schematic of a 6T SRAM bit cell with noise voltage sources for measuring SNM.                                      | 57       |

| <b>Fig. 4.2.</b>  | Schematic of a 6T SRAM bit cell and sample the side of the largest square fitted inside the graph.                 | 58       |

| <b>Fig. 4.3.</b>  | Conventional 6T SRAM cell.                                                                                         | 59       |

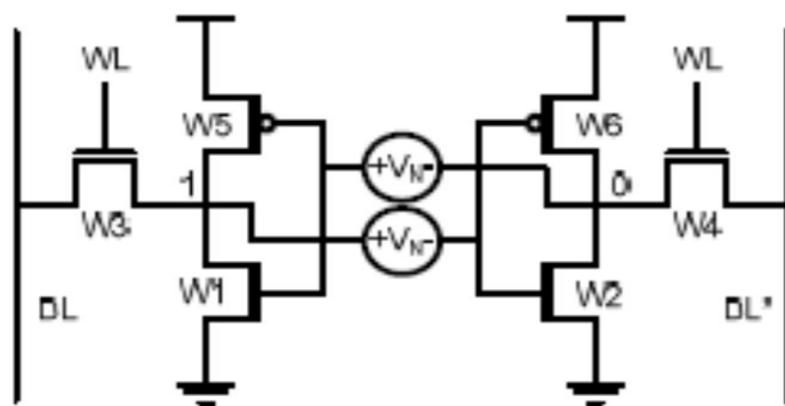

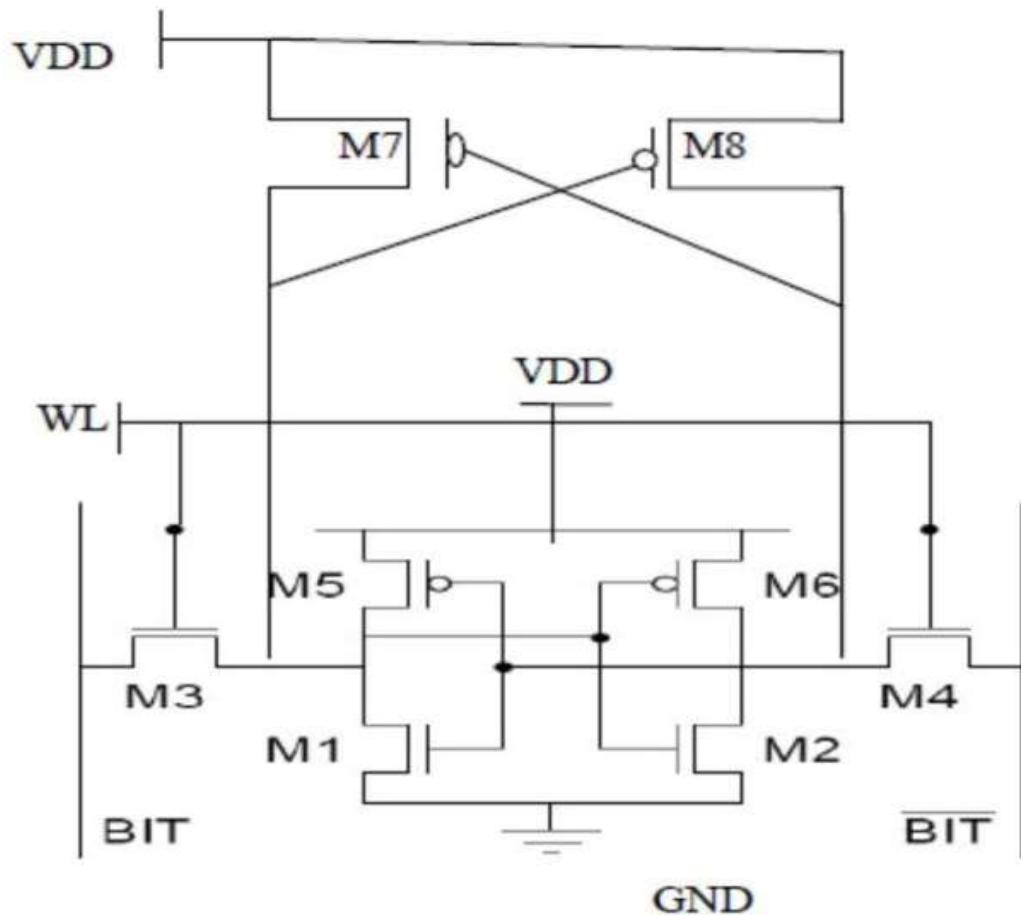

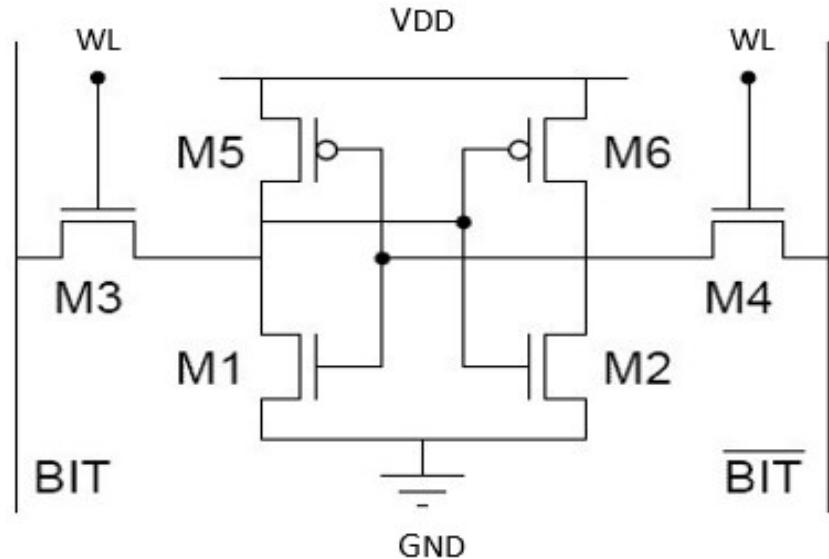

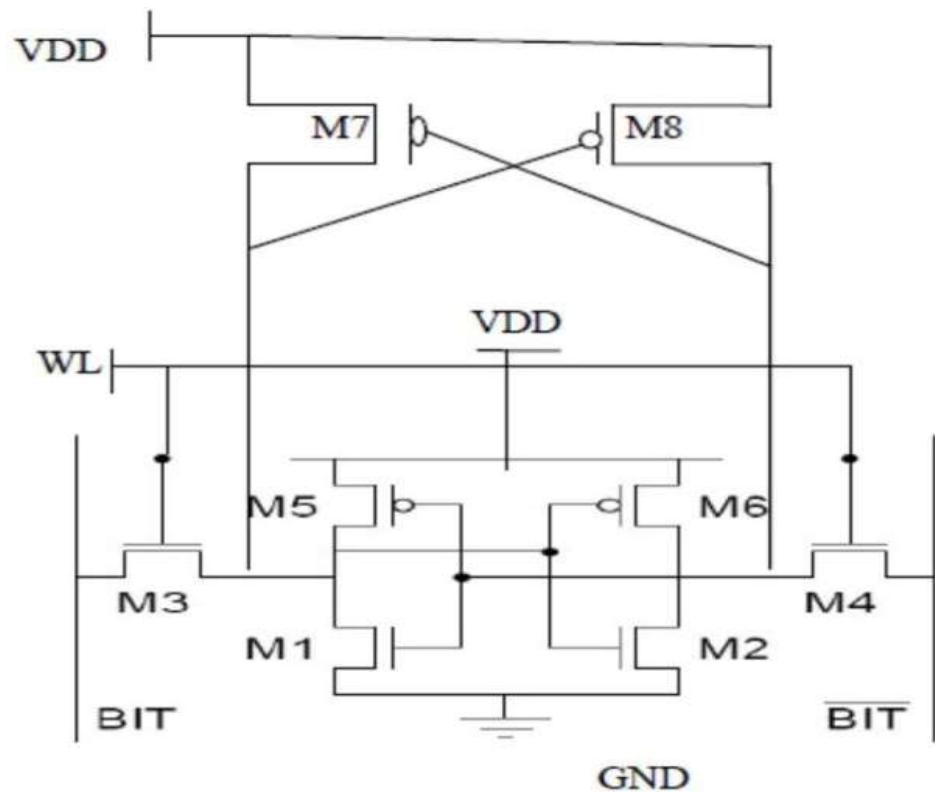

| <b>Fig. 4.4.</b>  | Standard 8T-SRAM cell.                                                                                             | 59       |

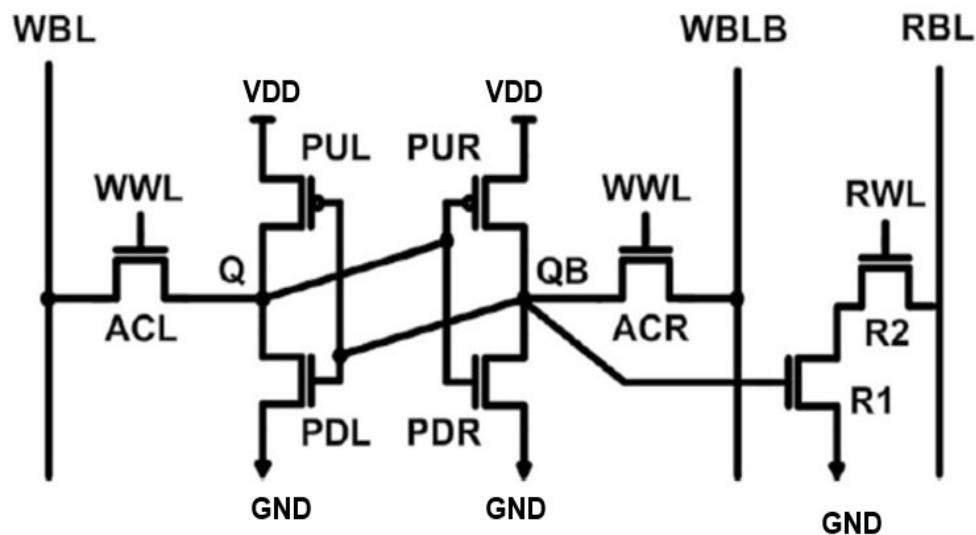

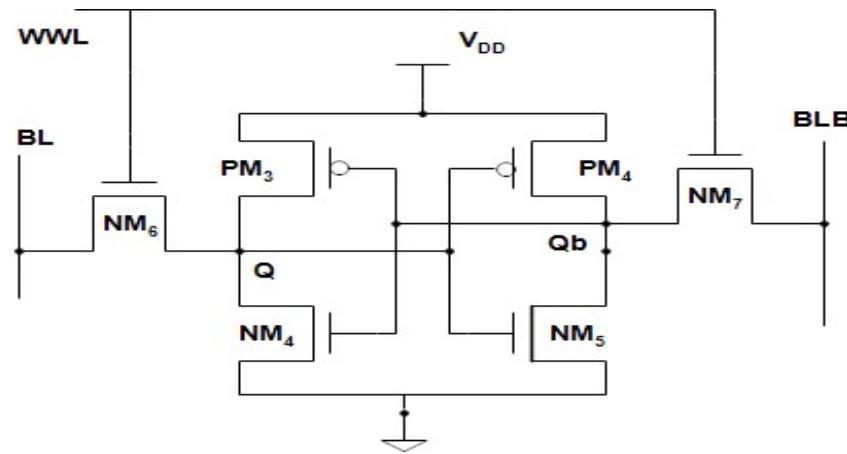

| <b>Fig. 4.5.</b>  | Low power 8T SRAM cell.                                                                                            | 61       |

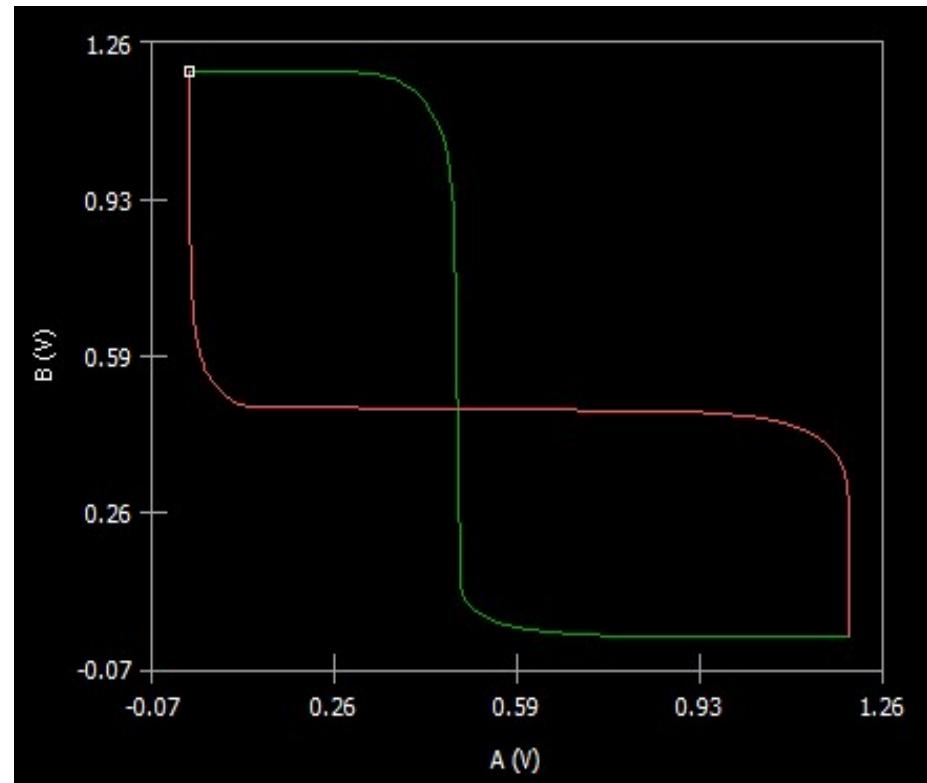

| <b>Fig. 4.6.</b>  | HSNM 6T SRAM cell.                                                                                                 | 62       |

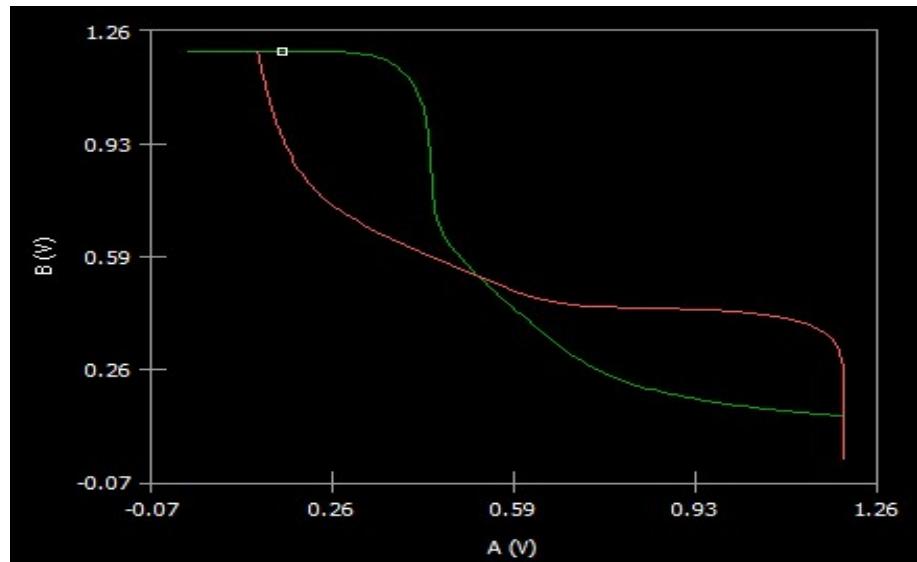

| <b>Fig. 4.7.</b>  | HSNM standard 8T SRAM cell.                                                                                        | 63       |

| <b>Fig. 4.8.</b>  | HSNM proposed 8T SRAM cell.                                                                                        | 63       |

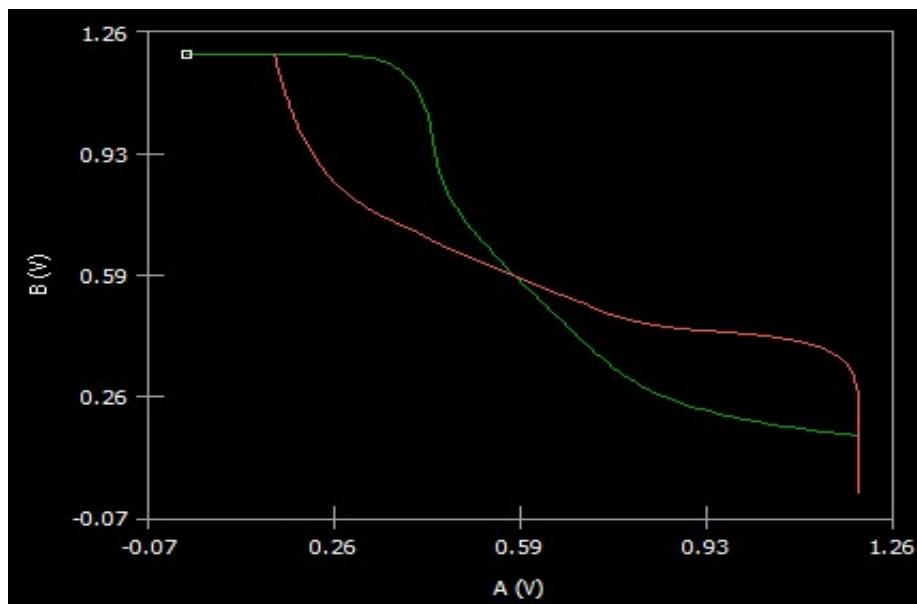

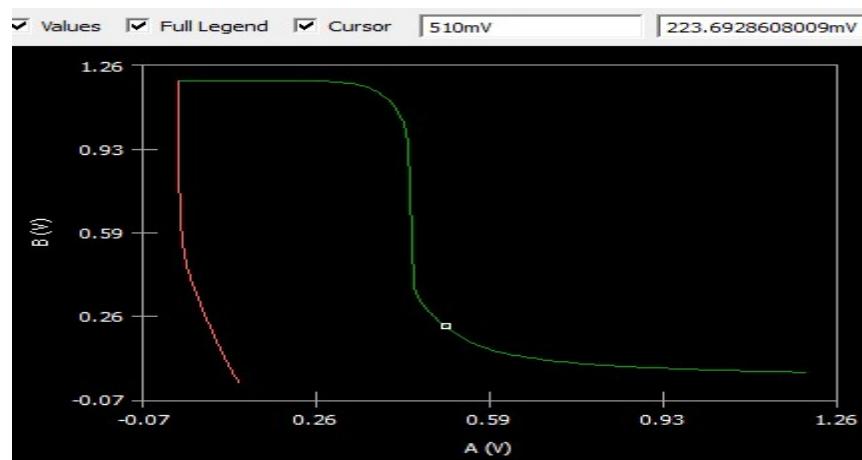

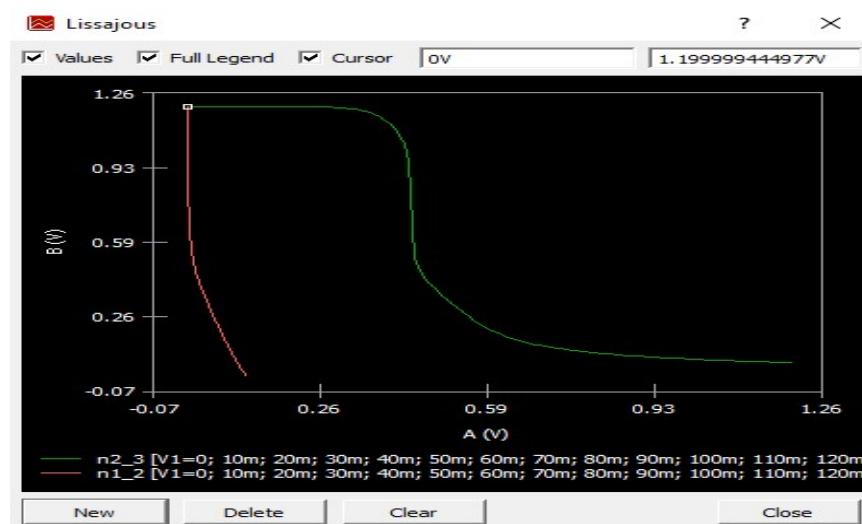

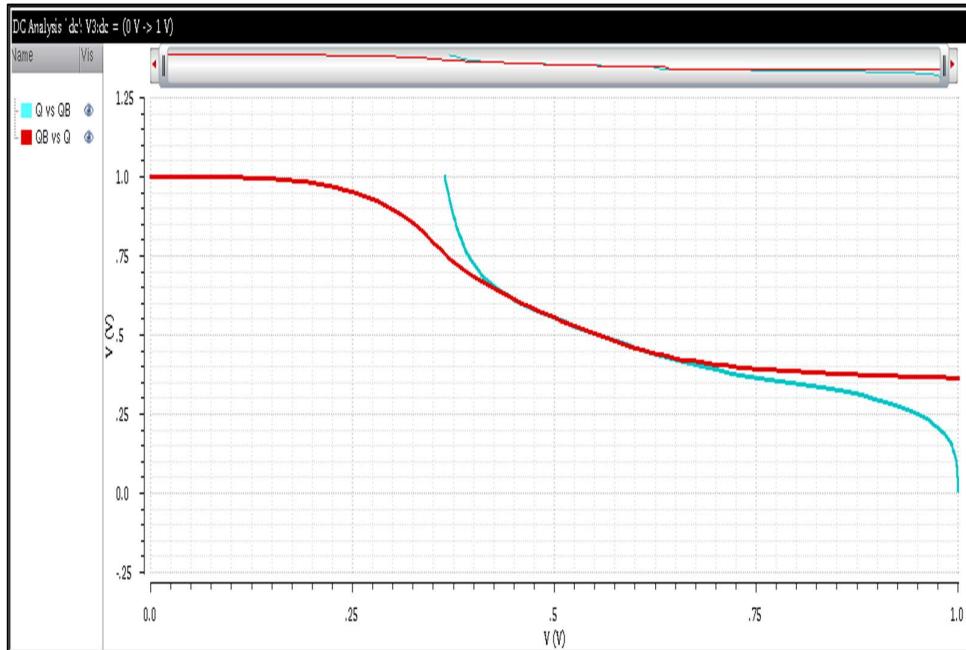

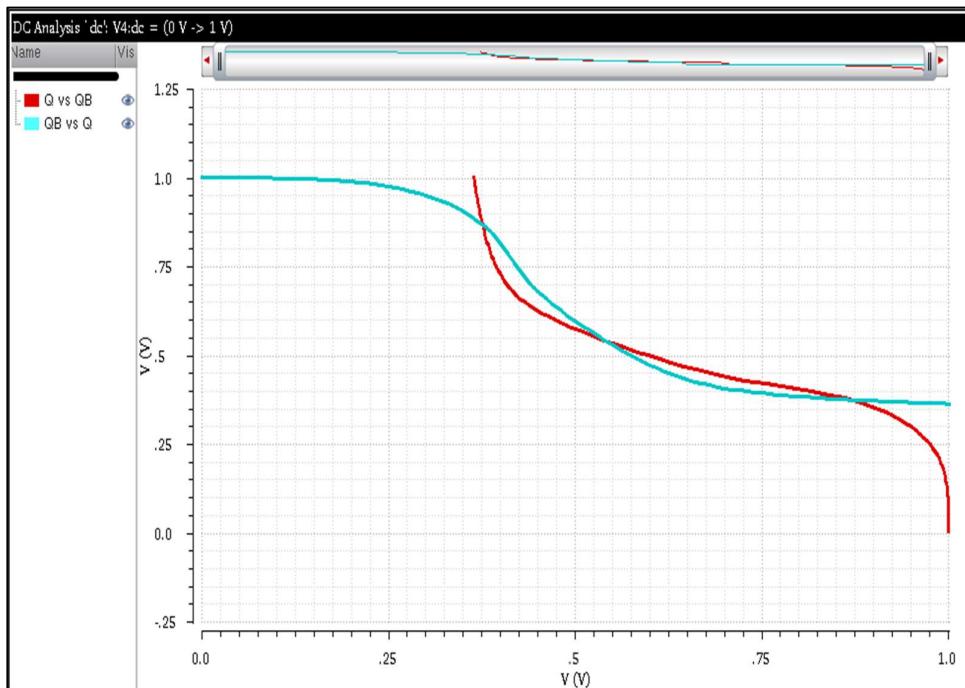

| <b>Fig. 4.9.</b>  | RSNM 6T SRAM cell.                                                                                                 | 64       |

| <b>Fig. 4.10.</b> | RSNM standard 8T SRAM cell.                                                                                        | 64       |

|                   |                                                                                              |     |

|-------------------|----------------------------------------------------------------------------------------------|-----|

| <b>Fig. 4.11.</b> | RSNM proposed 8T SRAM cell.                                                                  | 65  |

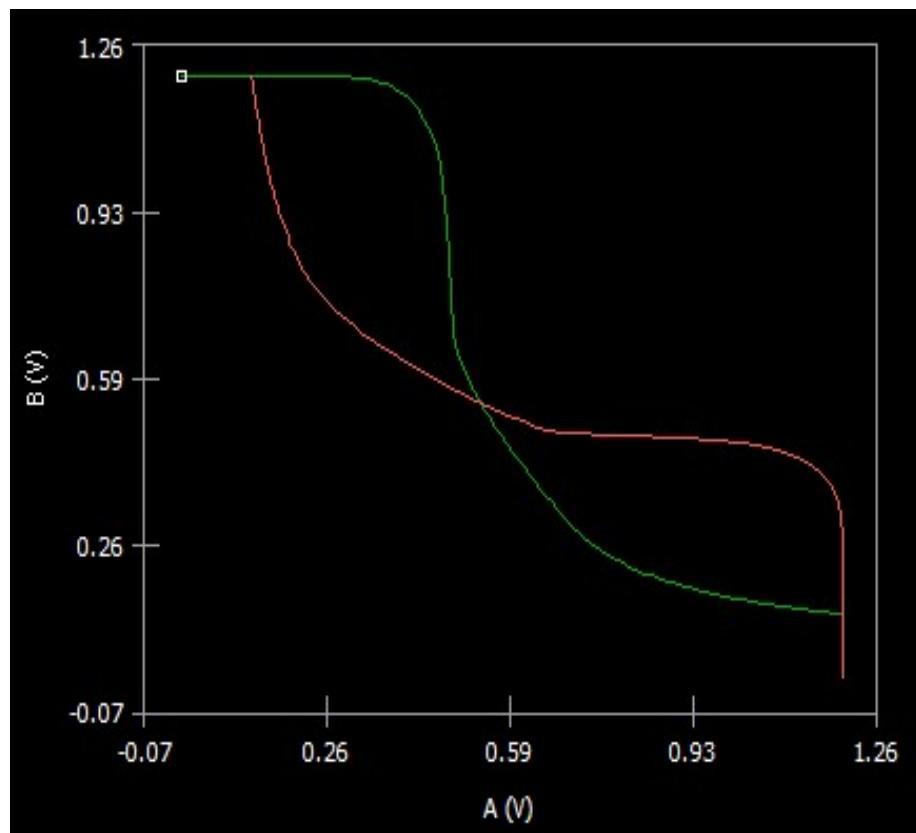

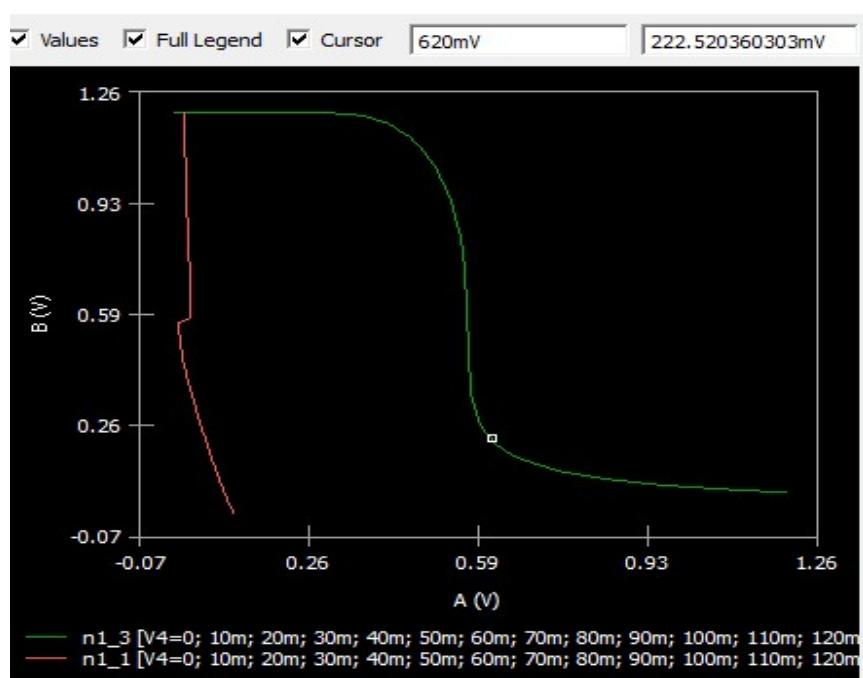

| <b>Fig. 4.12.</b> | 6T SRAM write trip point (WTP).                                                              | 66  |

| <b>Fig. 4.13.</b> | Standard 8T SRAM write trip point (WTP).                                                     | 66  |

| <b>Fig. 4.14.</b> | Low power 8T SRAM write trip point (WTP).                                                    | 67  |

| <b>Fig. 5.1.</b>  | Basic 6T SRAM cell.                                                                          | 72  |

| <b>Fig. 5.2.</b>  | (a) Circuit of negative bit-line generator and<br>(b) Output voltage at node X.              | 75  |

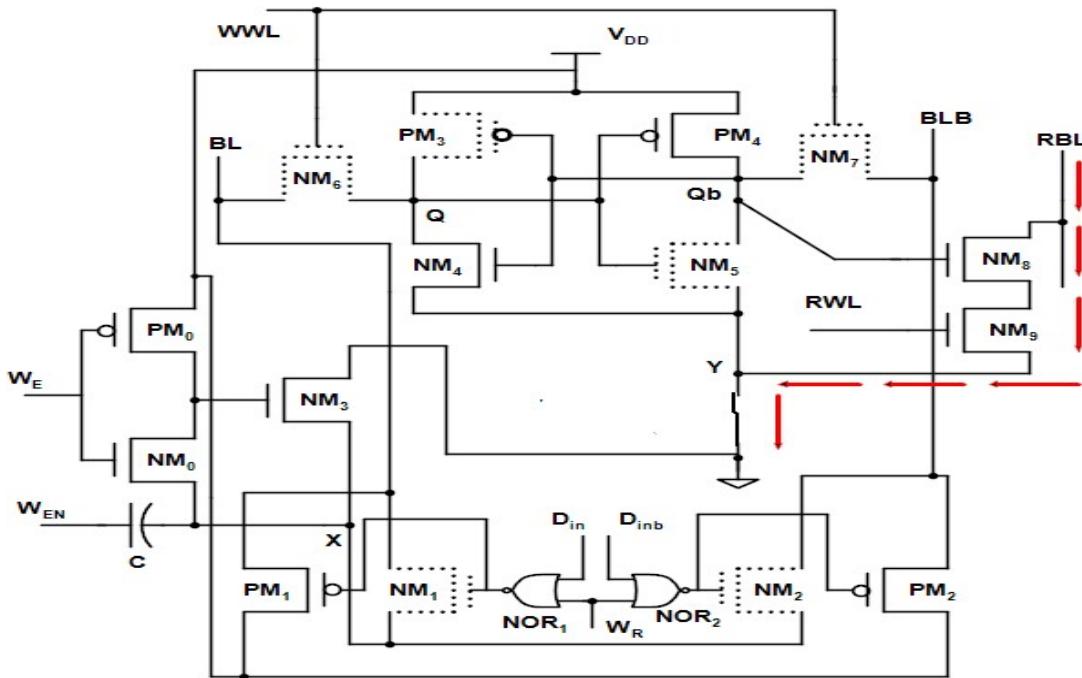

| <b>Fig. 5.3.</b>  | Proposed design.                                                                             | 78  |

| <b>Fig. 5.4.</b>  | (a) Proposed design during write operation and<br>(b) Proposed design during read operation. | 78  |

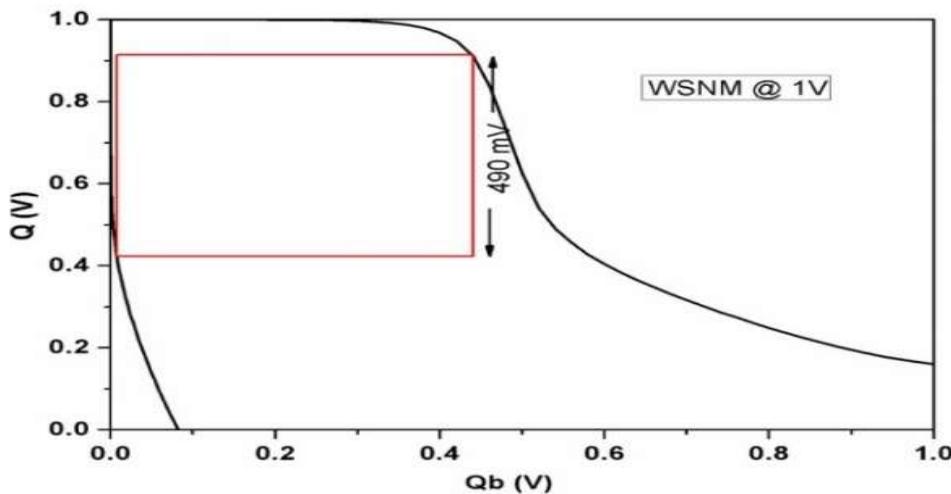

| <b>Fig. 5.5.</b>  | Butterfly curve for write stability.                                                         | 81  |

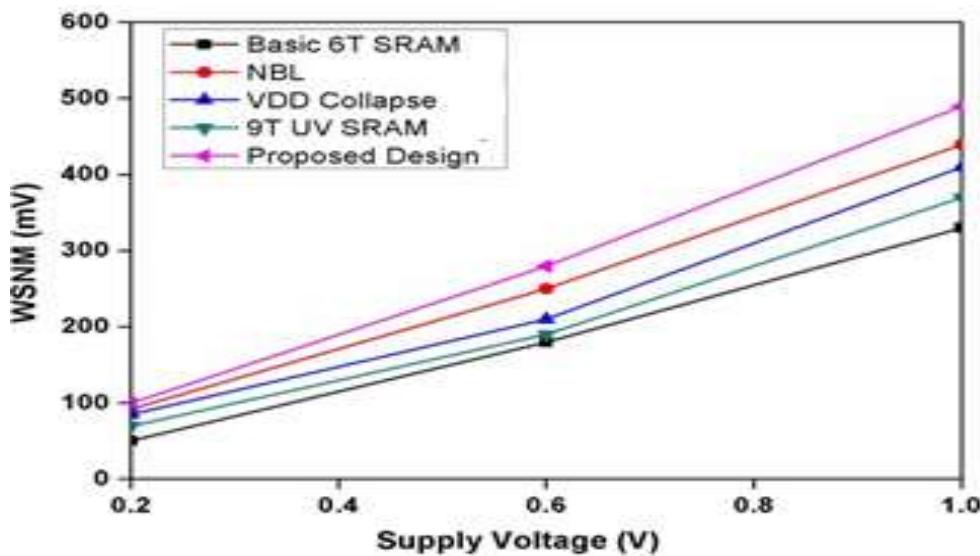

| <b>Fig. 5.6.</b>  | Variation in WSNM Vs. supply voltage.                                                        | 82  |

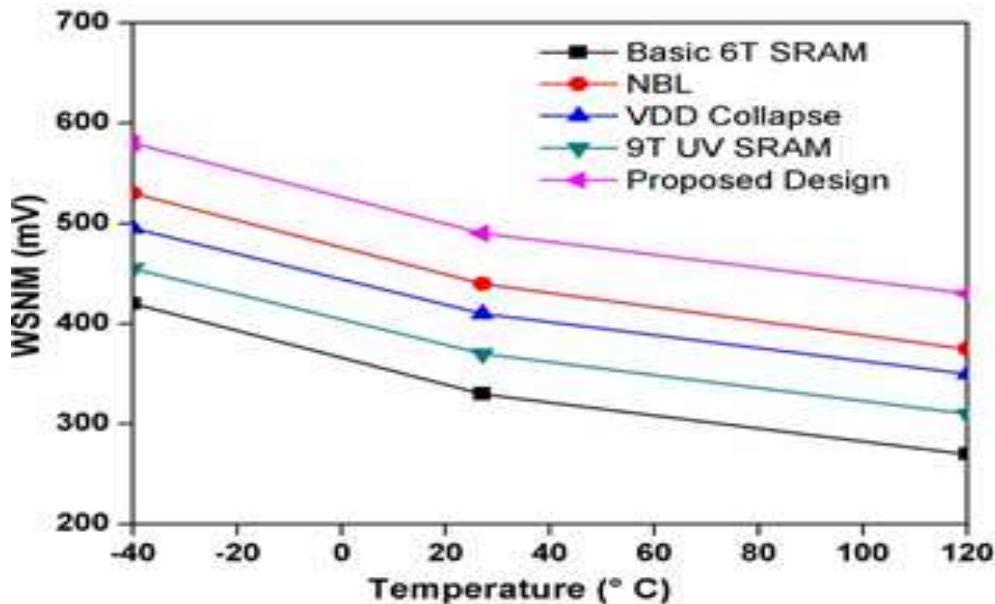

| <b>Fig. 5.7.</b>  | Variation of WSNM Vs. temperature.                                                           | 82  |

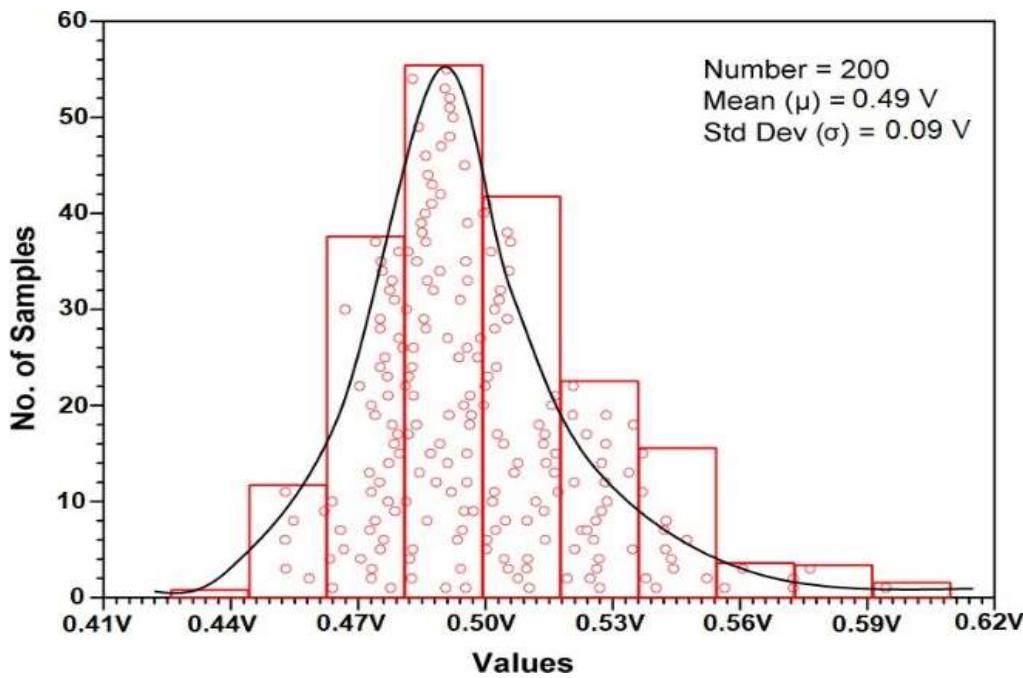

| <b>Fig. 5.8.</b>  | Monte Carlo of WSNM for proposed design.                                                     | 83  |

| <b>Fig. 5.9.</b>  | Butterfly curve for read stability.                                                          | 84  |

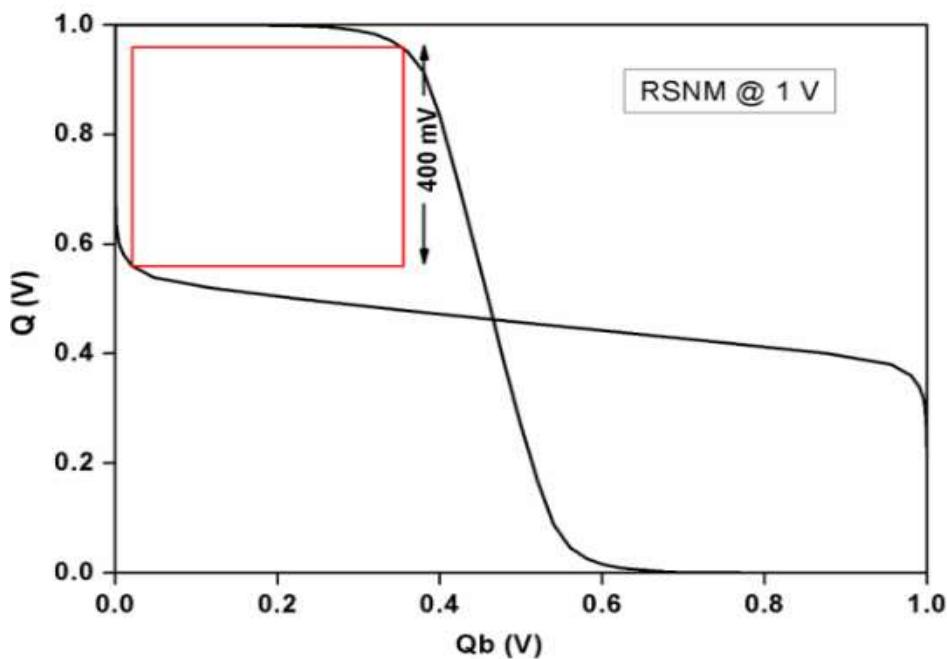

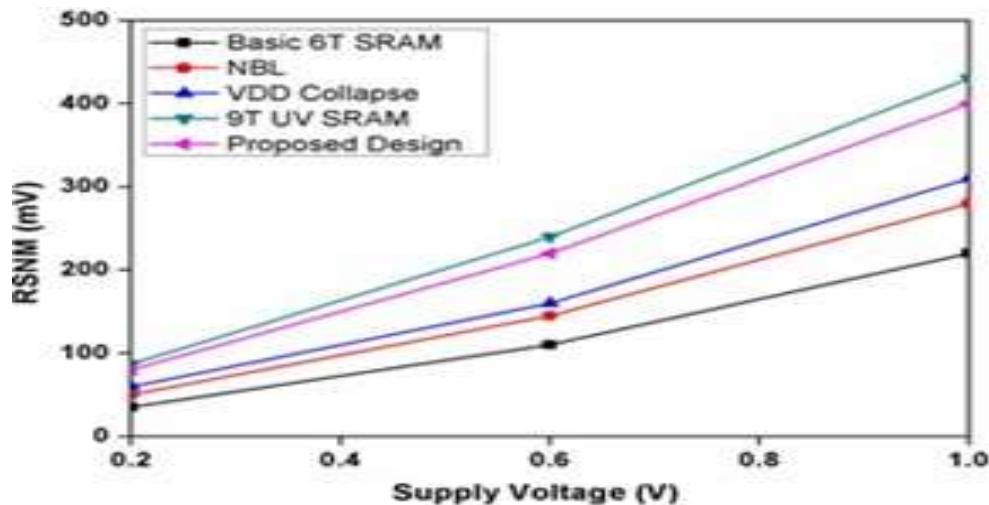

| <b>Fig. 5.10.</b> | Variation in RSNM Vs. supply voltage.                                                        | 85  |

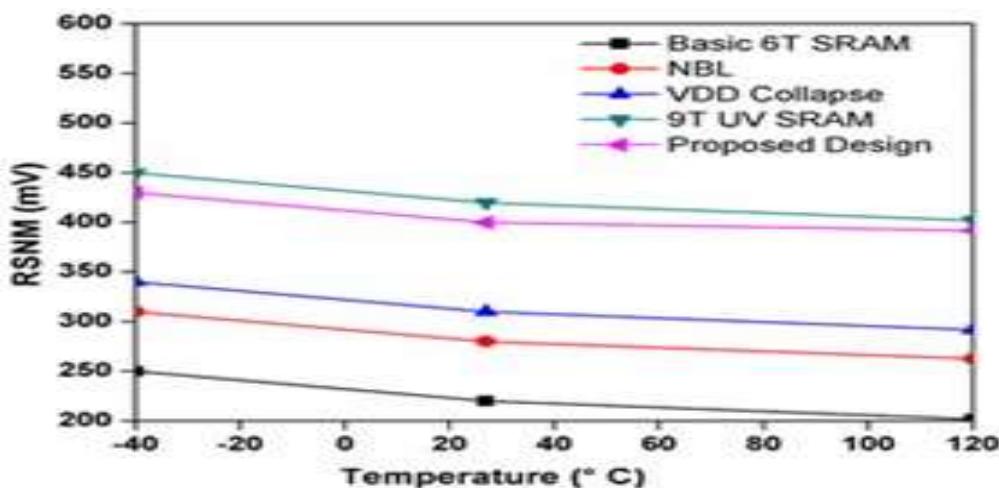

| <b>Fig. 5.11.</b> | Variation of RSNM Vs. temperature.                                                           | 85  |

| <b>Fig. 5.12.</b> | HSNM of proposed design.                                                                     | 86  |

| <b>Fig. 5.13.</b> | Variation of HSNM Vs. supply voltage.                                                        | 87  |

| <b>Fig. 5.14.</b> | Variation of HSNM Vs. temperature.                                                           | 87  |

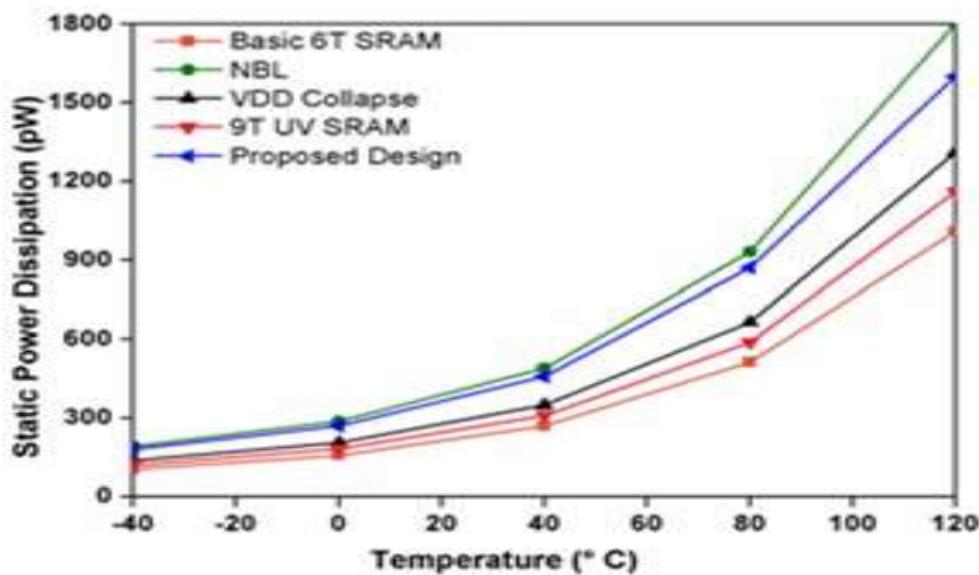

| <b>Fig. 5.15.</b> | Static power dissipation at various VDD.                                                     | 88  |

| <b>Fig. 5.16.</b> | Variation of static power dissipation Vs. temperature.                                       | 88  |

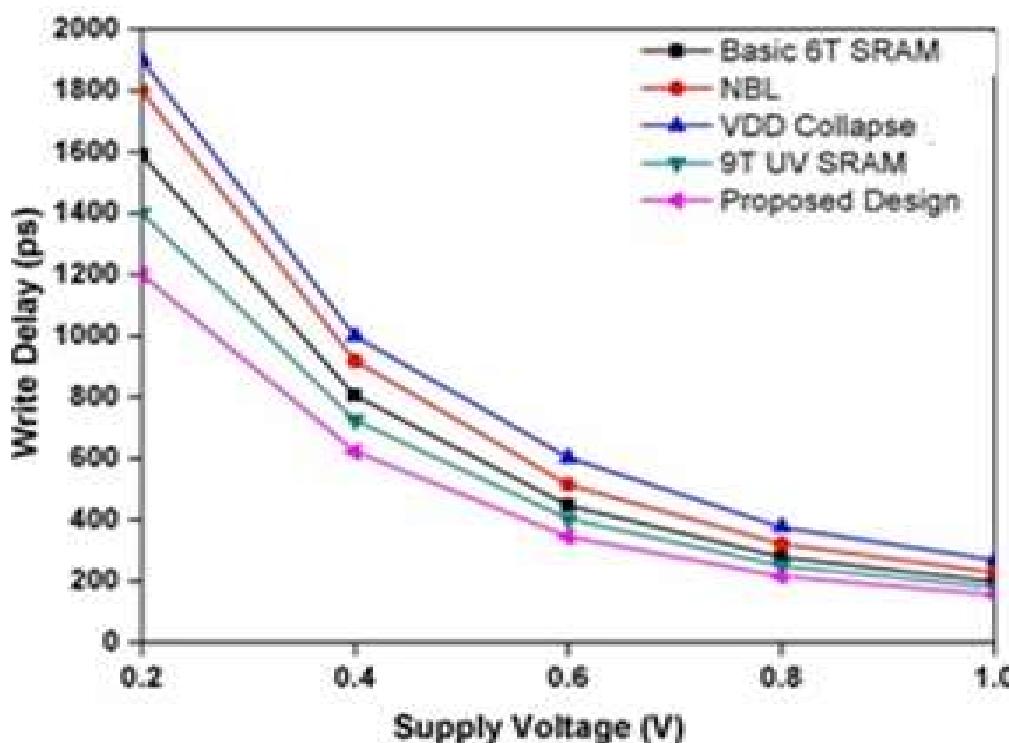

| <b>Fig. 5.17.</b> | Variation of write delay Vs. supply voltage.                                                 | 89  |

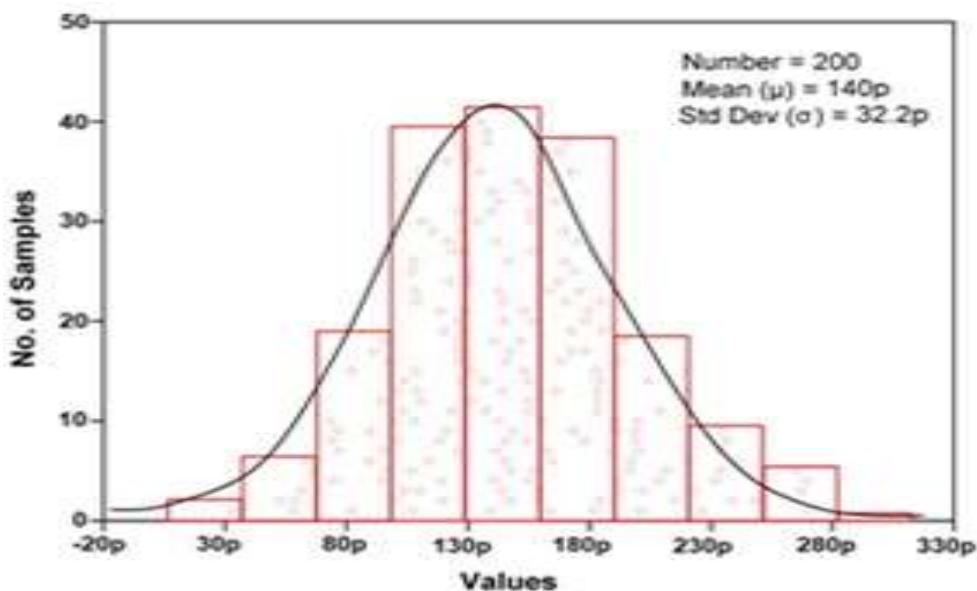

| <b>Fig. 5.18.</b> | Monte Carlo of write delay for a proposed design.                                            | 90  |

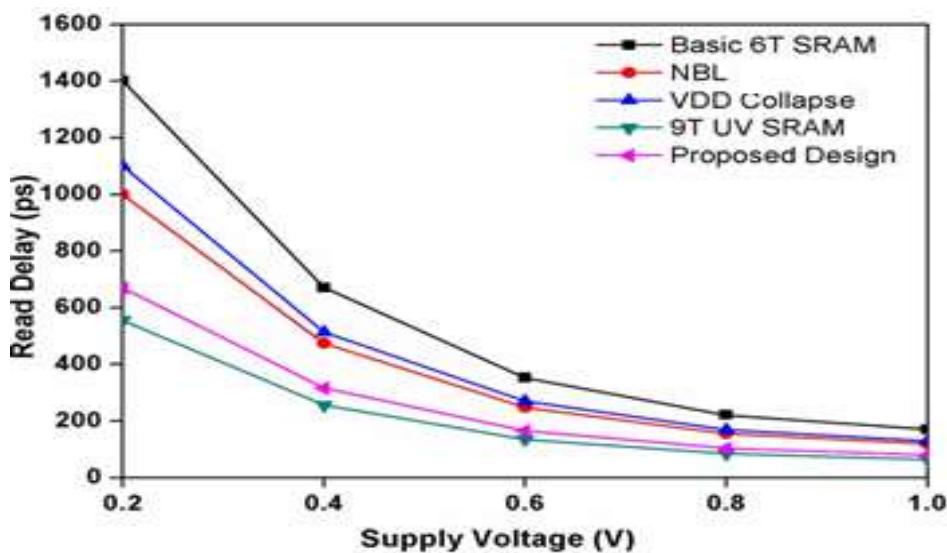

| <b>Fig. 5.19.</b> | Variation of read delay Vs. supply voltage.                                                  | 90  |

| <b>Fig. 6.1.</b>  | Static Random Access Memory (a) 6T SRAM cell and<br>(b) Proposed 8T SRAM cell.               | 104 |

| <b>Fig. 6.2.</b>  | RSNM of the SRAM cells (a) 6T SRAM cell and<br>(b) Proposed 8T SRAM cell.                    | 106 |

| <b>Fig. 6.3.</b>  | WTP of the SRAM cells (a) 6T SRAM cell and<br>(b) proposed 8T SRAM cell.                     | 107 |

| <b>Fig. 6.4.</b>  | Read power consumption of the SRAM cells (a) 6T SRAM<br>cell and (b) Proposed 8T SRAM cell.  | 109 |

**Fig. 6.5.** Write power consumption of the SRAM cells (a) 6T SRAM cell and (b) Proposed 8T SRAM cell. 110

**Fig. 6.6.** 2000 Monte Carlo simulations for leakage current distribution (a) 6T SRAM cell and (b) Proposed 8T SRAM cell. 111

## List of Symbols and Abbreviations

| Symbol/Abbreviation | Full Form                               |

|---------------------|-----------------------------------------|

| IC                  | Integrated Circuit                      |

| VLSI                | Very large-scale integration            |

| PMOS                | P-type metal-oxide semiconductor        |

| NMOS                | N-type metal-oxide semiconductor        |

| CMOS                | Complementary metal-oxide semiconductor |

| RAM                 | Random Access Memory                    |

| ROM                 | Read Only Memory                        |

| SRAM                | Static Random Access Memory             |

| DRAM                | Dynamic Random Access Memory            |

| RWM                 | Read Write Memory                       |

| VTC                 | Voltage Transfer Characteristic         |

| BL                  | Bit line                                |

| BLB                 | Bit line Bar                            |

| INV                 | Inverter                                |

| SRI                 | Swing Restoration Inverter              |

| NBL                 | Negative Bit-line                       |

| DSA                 | Domain-specific architecture            |

| V <sub>ds</sub>     | Drain-to-source voltage                 |

| V <sub>gs</sub>     | Gate-to-source voltage                  |

| C <sub>L</sub>      | Load Capacitance                        |

| HSNM                | Hold Static Noise Margin                |

| RSNM                | Read Static Noise Margin                |

| WSNM                | Write Static Noise Margin               |

| WTP                 | Write-trip-point                        |

| IoT                 | Internet of Things                      |

| K <sub>T</sub>      | Thermal Noise = 26 mV                   |

|                  |                                   |

|------------------|-----------------------------------|

| W                | Width                             |

| L                | Length                            |

| W/L              | Width-to-length ratio             |

| PVT              | Process, Voltage, and Temperature |

| Q                | Data Node                         |

| QB               | Data Node Bar                     |

| RWL              | Read word line                    |

| RBL              | Read Bitline                      |

| SA               | Sense Amplifier                   |

| PD               | Proposed Design                   |

| V <sub>t</sub>   | Threshold Voltage                 |

| SNM              | Static Noise Margin               |

| SoC              | System on Chip                    |

| V <sub>DD</sub>  | Supply Voltage                    |

| GND              | Ground Voltage                    |

| V <sub>OH</sub>  | High Level of Output Voltage      |

| V <sub>OL</sub>  | Low Level of Output Voltage       |

| V <sub>th</sub>  | Threshold Voltage                 |

| D <sub>in</sub>  | Data input                        |

| D <sub>inb</sub> | Data input bar                    |

| WL               | Word line                         |

| WM               | Write Margin                      |

| WWL              | Write Word line                   |

| μ                | Mean                              |

| σ                | Standard deviation                |

| n                | Number of Rows                    |

| m                | Number of Columns                 |

| C <sub>ox</sub>  | Oxide Capacitance                 |

# CHAPTER 1

## INTRODUCTION AND MOTIVATION

The growing dependence of civilization on digital devices has opened up a new world of processing and data. This plethora of data and its processing are dependent on various types of powerful digital devices. These devices comprise a microprocessor or a group of microprocessors. An essential component of these microprocessors is the memory circuits that enable their fast operation. In this chapter, a detailed introduction to the memory and its building blocks is presented. It is essential to understand the classification of CMOS memories so as to identify the different aspects that can be worked upon to improve their performance.

This chapter is divided into six different sections, including an introduction to semiconductor process, Section 1.1. It is followed by section 1.2, which is an introduction to memory. Based on the brief introduction of the classification of CMOS memories in section 1.3. Thereafter, in section 1.4, Memory organization. The motivations are used to achieve each desired objective in section 1.5. Finally, in section 1.6, the thesis organization is summarized.

### 1.1. INTRODUCTION TO SEMICONDUCTOR PROCESS

Semiconductor process technology has been scaling for over four decades. Process technology advancements are the driving force behind the semiconductor industry's growth. In response to increasing consumer demand for improved performance and functionality at a lower cost, the semiconductor industry has developed a new process technology generation every two to three years over the last four decades [1]. Memory is widely employed in all electrical systems, including mainframe computers, microcomputers, and cellular phones. Energy-efficient processors are becoming increasingly important as the need for portable battery-powered computers grows. These gadgets' performance is restricted by their size, weight, and battery life. Serious reliability issues, increased design costs, and battery-operated applications prompted the IC design community to seek out new approaches and methodologies that produce more power-efficient designs, resulting in significant power consumption reductions for the same level

of performance. Memory circuits, such as dynamic RAMs, static RAMs, Ferroelectric RAMs, ROMs, or Flash memories, are an essential component of any system architecture and contribute significantly to system power consumption. Reducing power dissipation in memories can enhance the system's power efficiency, performance, reliability, and total costs. RAMs have been fast growth in low-power, low-voltage memory design in recent years, owing to rising demand for notebooks, laptops, handheld communication devices, and IC memory cards. Various techniques are employed to reduce power dissipation, including power supply voltage scaling through circuit design, power gating, and the use of sleepy systems. Reducing the power supply voltage lowers dynamic power consumption quadratically, but it also increases leakage power exponentially. However, scaling down the supply voltage also decreases the noise margin. Many SRAM arrays are designed to minimize active capacitance and reduce voltage swing. In technologies below 100 nm, leakage currents mainly stem from gate leakage and sub-threshold leakage. Gate leakage can be mitigated with high-k (high dielectric constant) gate materials, while sub-threshold leakage is reduced through methods like forward body biasing and dual-threshold voltage (dual-V<sub>t</sub>) designs. In sub-threshold SRAMs, the supply voltage (V<sub>DD</sub>) is lower than the threshold voltage (V<sub>t</sub>) of the transistors, making sub-threshold leakage the dominant operating current [2].

## 1.2. INTRODUCTION TO MEMORY

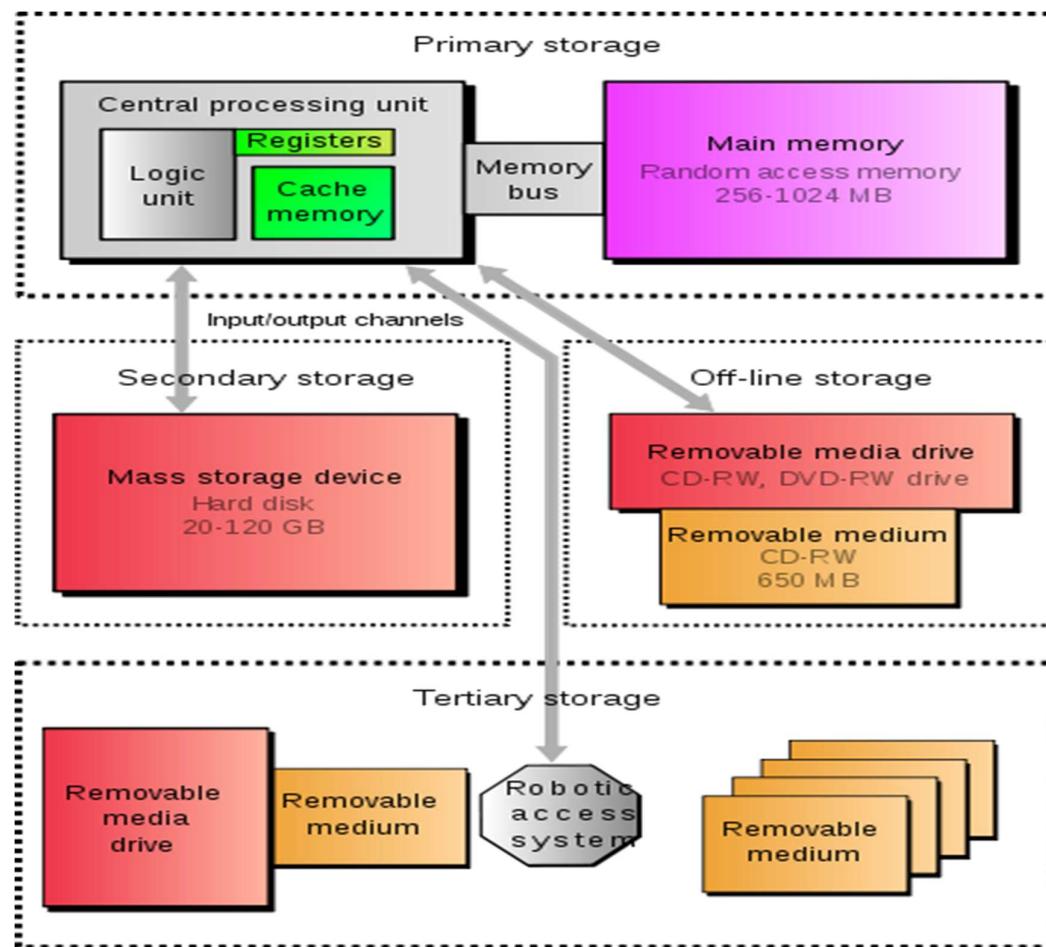

Computer data storage, often called storage or memory, refers to computer components and recording media that retain digital data used for computing for some interval of time. The main purpose of storage is that without a significant amount of memory, a computer would merely be able to perform fixed operations and immediately output the result [3]. It has to be reconfigured every time an operation needs to be performed. The hierarchy of storage is as shown in Figure 1.1.

**Figure 1.1.** Types of Computer data storage [3].

### 1.2.1 Primary Storage

Primary storage (or main memory or internal memory), often referred to simply as memory, is the only one directly accessible to the CPU. The CPU continuously reads instructions stored there and executes them as required. Any data actively operated on is also stored there in uniform manner.

### 1.2.2 Secondary Storage

Unlike primary storage, secondary storage (also known as external memory) is not directly accessible by the CPU. The computer typically transmits the needed data via an intermediate area in primary storage and accesses secondary storage through its input/output channels. Since secondary storage is non-volatile, data is not lost when the device is turned off. Additionally, the cost per unit is usually two orders of magnitude lower than that of primary storage. As a result, secondary storage is usually two orders of magnitude larger than primary storage in current computer systems, and data is stored there for extended periods of time.

### 1.2.3 Tertiary Storage

Tertiary storage or tertiary memory provides a third level of storage. Typically, it involves a robotic mechanism that will mount (insert) and dismount (removable) mass storage media into a storage device according to the system's demands; this data is often copied to secondary storage before use.

### 1.2.4 Offline Storage

Offline storage is used to transfer information, since the detached medium can be easily physically transported. Additionally, in case a disaster, for example a fire, destroys the original data, a medium in a remote location will probably be unaffected, enabling disaster recovery. Offline storage increases general information security.

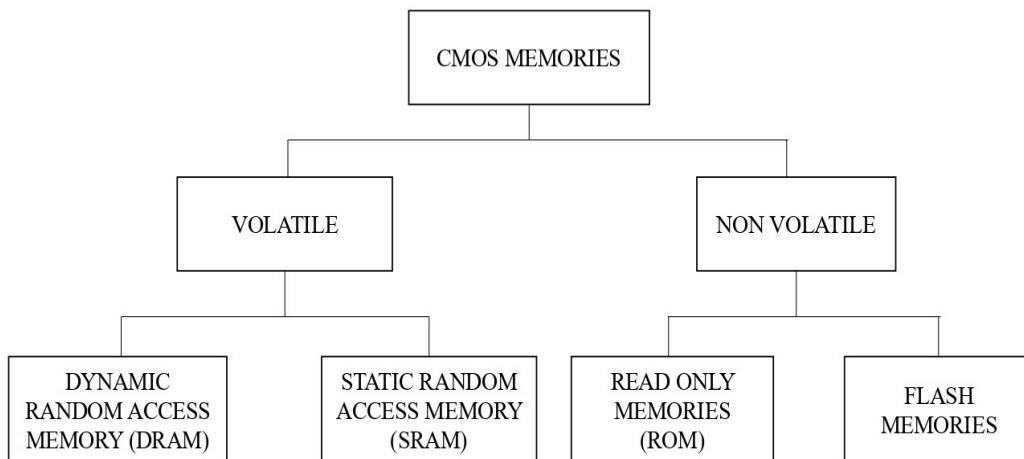

## 1.3. CLASSIFICATION OF CMOS MEMORIES

This section explains the different types of CMOS memories and the given figure 1.2 explains the memory can be classified as volatile and non-volatile memories [4].

**Figure 1.2.** Classification of CMOS memories.

### 1.3.1 Volatile memories

Power is necessary for this memory to preserve the data they contain. Computer data can be stored in random access memory (RAM). It takes the shape of integrated circuits, which provide arbitrary order access to stored data. The concept of randomness states that every item of data, regardless of its physical location or relationship to the preceding piece of data, can be returned in a fixed amount of time.

#### 1.3.1.1 Dynamic Random Access Memory

One kind of random-access memory that keeps each bit of information in a different capacitor inside an integrated circuit is called dynamic random-access memory (DRAM).

The information gradually fades unless the capacitor charge is routinely updated, since real capacitors leak charge. Unlike SRAM and other static memories, it is a dynamic memory because of this refresh requirement. DRAM's structural simplicity is a benefit over SRAM, which requires six transistors per bit, whereas DRAM just requires one transistor and a capacitor.

### 1.3.1.2 Static Random Access Memory

Because it stores each bit using bistable latching circuitry, static random-access memory (SRAM), a form of semiconductor memory, does not require periodic refreshes like dynamic random-access memory (DRAM). Although SRAM may recall data, it is nevertheless volatile in the traditional sense that when the memory is not powered on, data eventually disappears.

## 1.3.2 Non-Volatile memories

Non-volatile memory, NVM, or non-volatile storage, is computer memory that can retain the stored information even when not powered. Examples of non-volatile memory include read-only memory, flash memory, and most types of magnetic computer storage devices.

### 1.3.2.1 Read-Only Memory

ROM is a class of storage that is fabricated with desired data permanently fixed in it, thus it cannot be modified.

### 1.3.2.2 FLASH Memory

FLASH is a non-volatile computer storage technology that can be electrically erased and reprogrammed. Since flash memory is non-volatile, no power is needed to maintain the information stored in the chip.

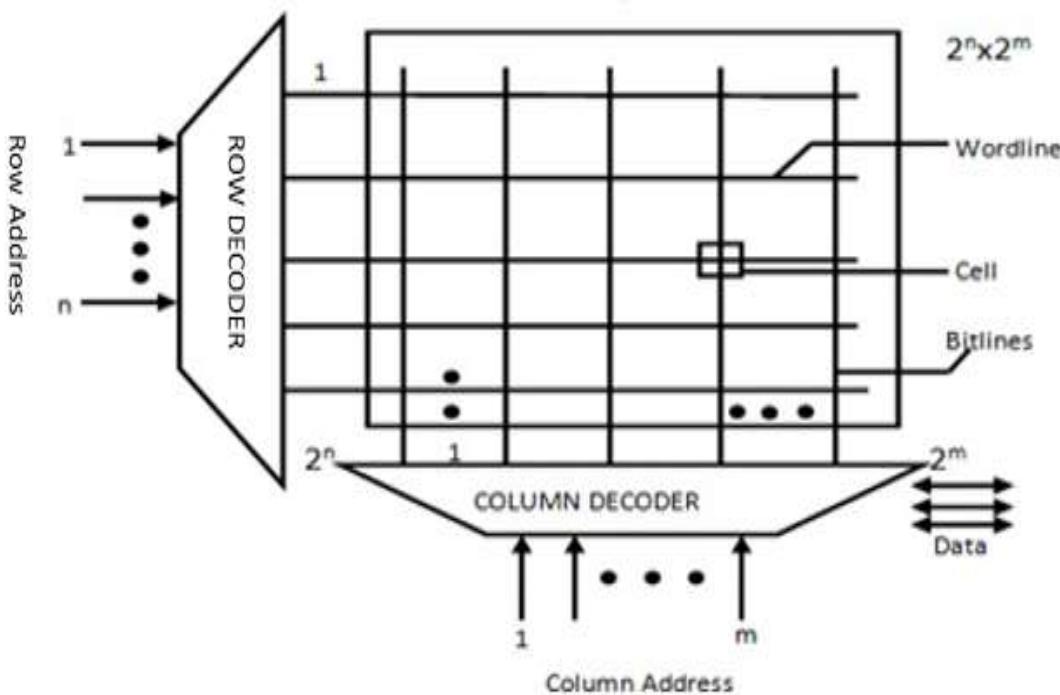

## 1.4. MEMORY ORGANIZATION

Figure 1.3 illustrates how a memory system is organized. Random-access architecture is the name given to this structure. The ability to access memory addresses in constant time and in a random order, regardless of the actual location for reading or writing, is the source of the name. In the storage array or core, the basic cell circuits are arranged so that they share connections in horizontal rows and columns. Word lines are the horizontal lines that are only driven from the external storage array, whereas bit lines are the vertical lines that carry data as it enters and exits the cells. A cell's specifically chosen row and column can be read or written to. Either "0" or "1" can be stored in each cell. Depending on the operation, memories can simultaneously select 4, 8, 16, 32, or 64 columns per row. The specific rows and columns are identified by decoding the dual address data [5].

**Figure 1.3.** Organization of memory system [5].

Read-Write Random-Access Memory (RAM) is the term for the data that is stored in flip-flop circuits or, more simply, as charge on capacitors. Due to its volatility, the reading or writing data experiences roughly the same latency. Because read-write memories store data in an active circuit, they lose their stored data in the event of a power failure. Because Read-Write Random-Access Memory is often referred to as RAM, it would make sense for Read-Write Memory to be abbreviated as RWM. The two most popular kinds of RAMs are dynamic RAM (DRAM) and static RAM (SRAM). The static RAM stores the stored value in flip-flop circuits when the power is on. SRAMs are typically high-speed memory for clock cycles between 5 and 50 ns. The values on the capacitor are stored in dynamic RAM. Compared to SRAMs, they are slower and more susceptible to leakage and noise issues. While SRAMs have roughly a quarter of the density of DRAM in a given technology generation, DRAMs can pack significantly more memory into the same area. This arrangement is also used by ROMs, which have read speeds similar to those of read-write memories (see figure 1.3). Although each ROM writes data in a unique way, they are all non-volatile. Since the most basic type of ROM is programmed during manufacturing by creating physical patterns on the chip, it is difficult to make modifications to the stored data later.

on with mask-programmed ROMs. In order to demonstrate the distinction, programmable read-only memory (PROM) is constructed with a data channel between each row and column that stores "1" in each data location. Storage cells are primarily switched to the "0" state when manufacture is complete, and "0" cannot be written as "1" once it has been programmed or blown, thanks to the provision of suitable electrical pulses that selectively open the row-column data channels. Similar to PROMs, Erasable Programmable Read-Only Memories (EPROMs) are electrically programmed, but exposure to ultraviolet (UV) light has the potential to erase all of the data. All of their bits are initially in a single binary state. To allow UV light to reach the packages, these parts feature a clear window over the chip. The most sophisticated and costly types of PROMs are Electrically Erasable Programmable Read-Only Memories (EEPROMs). Electrical methods can also be used to write and erase them. In contrast to EPROMs, E<sup>2</sup>PROMs can be overwritten to alter even a single bit and can be completely or selectively deleted. Since all PROMs are able to keep data even when the power is turned off, they are referred to as non-volatile. The processes of writing and erasing data for all types require time intervals that can range from microseconds to milliseconds. The more modern version of EPROM and E<sup>2</sup>PROM is called flash memory. The memory blocks in flash memory can be wiped out all at once. The hot electron effect, which is produced by applying a strong field in the channel region, is used to write data in the EPROM form's flash memory. These electrons then penetrate the oxide region and boost the device's threshold voltage. In contrast, the data in E<sup>2</sup>PROM flash is written using Fowler Nordheim (FN) tunnelling, where a device with a higher threshold voltage represents a stored "1" while one with a lower threshold voltage signifies a stored "0". This storage mechanism involves electron tunneling through a thin insulating layer such as a gate-connected thin oxide allowing current to pass by overcoming the energy barrier. Memories like FRAM (or FeRAM) utilize ferroelectric materials and can retain data even after power is removed. These memory cells are built using perovskite crystals, which can be polarized in either direction to store information. This creates a non-volatile memory structure, as the polarization remains intact without power. Despite the availability of alternative memory technologies, semiconductor memories remain the preferred choice in VLSI design, offering superior performance in terms of cost, speed, energy efficiency, and compactness.

5

## 1.5. MOTIVATION AND OBJECTIVES

### 1.5.1 Low-power and High-speed SRAM Cell

Their research introduced an effective, stable cell selection method to identify SRAM cells that exhibit strong bias, resistance to circuit noise, and resilience to voltage, temperature fluctuations, and aging. Despite these advancements, the study concluded that additional endeavors are required to achieve more promising outcomes.

1. To solve the issue of SRAM stability and delay, a novel Swing Restoration Inverter (SRI) circuit is developed and implemented utilizing the proposed 8T SRAM cell.

2. A Swing restoration Inverter (SRI) is used to improve the cell's stability during read and write operations.

3. By adding two more transistors, the leakage power is minimized by increasing the node voltages and decreasing the threshold voltages.

4. As a result of the recommended enhancement, SRAM's stability and latency have improved.

### 1.5.2 Improved Stability of SRAM Cell

There were a number of approaches because early electronic systems were extremely slow due to memory speed not being proportional to CPU performance. Therefore, the cache memory is employed to increase the system's overall speed. At the moment, static random-access memory (SRAM) serves as the foundation for the cache memory. However, the technique's reduction in cell supply voltage disrupts the stored node voltage, which causes data loss during read, write, and hold operations. By raising the word-line voltage in the enhanced word-line write assist technique [18], access transistors' gate to source voltage rises as well, increasing static power dissipation. As a result, low-voltage operation is likewise not appropriate for this approach. Furthermore, S. Kamineni and B. H. Calhoun [21] introduced techniques aimed at minimizing static power dissipation and enhancing the efficiency of read/write operations.

1. To improve the stability of the SRAM cell for low power and high speed.

2. To design an 8T SRAM cell for improved read and write margins.

3. Analyze the proposed 8T SRAM cell and validate it against the conventional 6T SRAM cell.

### 1.5.3 Low-leakage and High-stability of SRAM Cell

The world's technology has been rapidly moving toward the nano regime as consumers' demands for improved electronic device performance are also growing. Consumers want affordable, high-performing gadgets. On-chip circuits have become essential in all areas

of technology, including wireless sensors, the internet, and portable handheld gadgets [22]. On-chip memories play a crucial role in high-performance applications, as the superior speed of SRAM renders it particularly well-suited for such purposes [23]. SRAM memory faces significant challenges, including high leakage power and operational instability, which have been exacerbated by the continued downscaling of process technology [24]. However, to decrease power consumption, the supply voltage was lowered, which in turn caused a proportional decrease in the threshold voltage of the devices. However, this lower threshold voltage results in an exponential rise in subthreshold leakage current. Since the SRAM cell must be able to store its data in all read and hold scenarios, stability is the most crucial design criterion [25]. Data loss could occur if the SRAM cell is not stable. The lowest noise voltage values that can potentially push the cell into an undesirable state during a hold or a read operation, respectively, are known as these static noise margins [26]. By taking into account the static voltage transfer characteristics (VTCs) of the two inverters that comprise the cross-coupled pair, it is possible to examine the stability of the SRAM cell during a hold operation [27]. However, the results obtained are not promising.

1. To address stability and delay difficulties in SRAM, a unique negative bit-line (NBL) circuit is proposed, then put into action using an 8T SRAM cell.

2. In the recommended architecture, one of the bit lines produces a negative voltage during the write operation (due to the NBL circuit), which enhances the access transistors' driving capacity and, as a result, the writing ability.

3. To increase the cell's stability during read operation, a separate or isolated read port is employed.

4. As a consequence, the suggested improvement has improved SRAM's stability and decreased its latency.

## OBJECTIVES

The growing demand for low-power and high-speed memory with low leakage the need for re-designing memory and its peripheral components for performance enhancement. Also, the cumulative aftermath of a reduction in technology node, scaling  $V_{DD}$ , and increased process variation may result in augmented memory failure. Thus, the following three objectives were formulated to improve the performance of SRAM.

**Objective 1:** To design SRAM Cell for low power and High speed.

**Objective 2:** To develop an improved stability of low power SRAM cell.

**Objective 3:** To develop a low-leakage SRAM cell.

## 1.6. THESIS ORGANIZATION

The organization of the thesis is presented in this section, which comprises seven chapters listed below:

**Chapter 1 is Introduction and Motivation:** The simplest and most crucial component for memory is the SRAM cell. The 6T SRAM cell was the industry standard for a very long duration, but its performance deteriorates with the decreasing technology node and scaling  $V_{DD}$ . The literature review has helped identify the proposed 8T SRAM cell as a potential successor, as it has low power and high speed.

**Chapter 2 Literature Review:** The literature survey forms a key part of this review, providing detailed insights into current techniques and research developments. In particular, the review of SRAM cells focuses on three critical aspects: stability, energy efficiency, and power constraints.

**Ram Murti Rawat, Vinod Kumar, "Literature review on SRAM cells under Stability, Energy, and Power Constraints,"** 2025 International Conference on Intelligent Control, Computing and Communications (IC3), pp. 1340-1344, during 13-14 February 2025. **Held at GL BAJAJ Group of Institutions, Mathura, India.** doi: 10.1109/IC363308.2025.10956626. **(Scopus) (Published).**

**Chapter 3** deals with the **Low power SRAM Cell using Swing Restoration Inverter (SRI)** for low-power applications. In this chapter, proposed 8T SRAM cell is proposed, and its performance is analyzed. The proposed cell is based on a swing restoration inverter (SRI), dual-port in nature. This particular configuration is chosen for its low power and high speed.

**Ram Murti Rawat and Vinod Kumar, "Design and analysis of SRAM cell using swing restoration inverter for low power applications",** International Journal of Electronics vol. 1, pp. 1–19, 2025. doi: 10.1080/00207217.2025.2450733. **(SCIE, IF: 1.1) (Published).**

**Ram Murti Rawat and Vinod Kumar, "Low Power Pre-charge Voltage Level and Low Swing Logic Based 8T SRAM Cell for High Speed CMOS Circuits,"** 2021 IEEE 32nd International Conference on Microelectronics (MIEL), pp. 243–246, 12-14 Sep. 2021, **held at Nis University, Serbia.** doi: 10.1109/miel52794.2021.9569198. **(Scopus) (Published).**

**Vinod Kumar** and Ram Murti Rawat, “**Low Power Swing Restoration Circuit Reduce Threshold Voltages of SRAMs Improve Read and Write Operations**,” 2021 IEEE International Symposium on Smart Electronic Systems (iSES), pp. 23–26, 18-22 Dec. 2021, held at MNIT, Jaipur. doi: 10.1109/ises52644.2021.00018. (Scopus) (Published).

**Chapter 4** details the **Improved stability of low power SRAM cell**. The cell stability analysis of the sensitivity of the memory cell using Low Power VLSI. The stability of a Static Random access memory cell in the presence of DC noise is measured by the static noise margin (SNM). Static Noise Margin is the amount of voltage noise required at the output nodes to flip the state of the cell. This can be obtained using the voltage transfer characteristic (VTC) of the two cross-coupled inverters of the SRAM cell.

**Ram Murti Rawat** and Vinod Kumar, “**Restoration circuits for low power reduce swing of 6T and 8T SRAM cell with improved read and write margins**”, International Journal of Reconfigurable and Embedded Systems (IJRES), vol. 10, no. 2, p. 130, Jul. 2021, doi: 10.11591/ijres.v10.i2.pp130-136. (Scopus) (Published).

**Ram Murti Rawat** and Vinod Kumar, “**A Comparative Study of 6T and 8T SRAM Cell With Improved Read and Write Margins in 130 nm CMOS Technology**”, WSEAS TRANSACTIONS ON CIRCUITS AND SYSTEMS, vol. 19, pp. 13–18, Feb. 2020, doi: 10.37394/23201.2020.19.2. (Scopus) (Published).

**Vinod Kumar** and Ram Murti Rawat, “**Low Power Restoration Circuits Reduce Swing Voltages of SRAM Cell With Improved Read and Write Margins**”, International Journal of Security and Privacy in Pervasive Computing, vol. 13, no. 2, pp. 16–28, Apr. 2021, doi: 10.4018/ijspc.2021040102. (Published).

**Chapter 5** In this chapter the **Low-leakage, High-stability SRAM cell for IoT Applications**. The design and characterization of a low-leakage, high-stability SRAM cell for IoT applications is crucial for the development of portable electronic devices. This study proposes a negative bit-line (NBL) write assist circuit and a separate (isolated) read port to improve the write and read stability of the SRAM cell, respectively. The proposed design has been compared to previous state-of-the-art work, and it has been shown that the WSNM has improved significantly, while the write latency has decreased and faster operation.

**Ram Murti Rawat, Vinod Kumar, “Design and Characterization of a Low-Leakage, High-Stability SRAM Cell for IoT Applications”, Indian Journal of Engineering and Materials Sciences (IJEMS), Vol. 31 No.5, pp. 627-640, 2024. <https://doi.org/10.56042/ijems.v31i5.6683>. (SCIE, IF: 0.9) (Published).**

**Chapter 6** In this chapter the **Energy Efficient SRAM Cell**. An energy efficient 8T SRAM cell is also proposed to ensure easy integration for the components of SRAM. Therefore, for performance energy efficient SRAM cell configuration is also proposed mechanisms to lower power consumption and high speed. While ensuring that the designed proposed 8T SRAM cell for low leakage.

**Ram Murti Rawat, Vinod Kumar, “Energy Efficient 8T SRAM Cell for Enhancing Read/Write Assist Performances with Stability,” 2025 14th IEEE International Conference on Communication Systems and Networks Technologies (CSNT 2025), pp. 663-667, during 7 - 9 March 2025. Held at VIT, Bhopal, Madhya Pradesh, India. doi: 10.1109/CSNT64827.2025.10968320. (Scopus) (Published).**

Finally, **Chapter 7 Conclusions and future scope**: SRAM is an essential component for microprocessors. The decreasing technology node and increasing demand for portable devices with longer battery life has generated the need for re-designing SRAM for performance enhancement. Thus, in this thesis double ended, dual port bit cell designs are proposed, that have the ability to achieve the same. Also, a new concept for a dual mode operational cell and its functioning is also explained. Thereafter, for performance energy efficient SRAM cell configuration is also proposed.

The chapters are followed by the list of publications and references. All the papers published for the completion of this work are listed in – List of Publications. While all the books and papers that were referred to during the study to form the basis for this work are listed in the reference section.

## CHAPTER 2

### LITERATURE REVIEW

Memory has been the center of attention for performance enhancement for a very long time. Researchers have proposed various techniques and designs for improving the performance of single or multiple components of memory. SRAM cells are designed to have received special attention from researchers, as the bit cell is the heart of SRAM. Attempts have also been made to modify sense amplifier designs for better compatibility. While array configuration optimization is a fairly recent domain. Thus, a detailed review of pre-existing designs, configurations, and topologies is essential to understand the different challenges that need to be overcome while designing a new proposed and improved cell, sense amplifier, and array for performance enhancement. Thus, in this chapter, a detailed review of the different memory cells, technology, and a summary and observations are presented.

#### **“Literature review on SRAM cells under Stability, Energy, and Power Constraints.”**

The chapter is divided into six different sections, starting with an introduction to the processor, Section 2.1. It is followed by section 2.2, literature survey. This section helps identify the definition of research questions and conduct a search. Thus, the next section 2.3 reviews of different SRAM cell designs, their characterization based on technique and technology, and performance analysis. Further in section 2.4, a summary of the research review based on the literature review, and their performance is commented upon. While in section 2.5, research gaps based on different approaches for array implementations are explained. Finally, based on the research gaps, the identified research objectives are elaborated upon in Section 2.6.

#### **2.1. INTRODUCTION TO THE PROCESSOR**

The key feature of a microprocessor is its multi-core architecture and fast operation. The optimal functioning of a processor is reliant on the performance of the internal memory. This internal memory for the processor is formed by a matrix of SRAM cells. Consequently, improving the performance metric for an SRAM cell improves the performance of the memory array. The overall power consumption for a cell is the sum

of its static and dynamic power components; the charging and discharging event accounts for 60% of the latter component. Therefore, limiting the charging/discharging event for a cell reduces its dynamic power consumption. Consequently, to reduce switching power consumption, double-ended cell topologies are gaining popularity. Various other researchers have also reported other SRAM cell configurations to rectify the abovementioned problems. Therefore, in this chapter, a detailed review of different SRAM cells, technologies, and a summary and observations are presented to understand the different topologies and techniques reported over time to improve the performance of each SRAM cell. It is essential to develop a deep understanding of the different techniques to design and develop new proposed SRAM cells to improve performance.

## 2.2. LITERATURE SURVEY

The literature survey is one of the main focuses of the literature review. It also provides detailed information about current area techniques. The survey is divided into the following sections.

### 2.2.1 Definition of the Research Questions

In this step, this study formulates the Research Questions (RQs) that will guide our work.

RQ1: What are the various designs for stability analysis of low-power SRAM cells?

RQ2: What are the different low-power SRAM architectures?

RQ3: What are the various designs for energy and power-efficient SRAM cells?

RQ4: What are the various parameters for SRAM cell analysis?

### 2.2.2 Conduct Search

The objective of searching is to find the journal and conference papers that investigated the low-power SRAM cells. The search is normally based on some keywords. The keywords used [in this study](#) to search for research articles are listed below: Low power SRAM, static noise margin (SNM), swing restoration inverter (SRI), leakage power, energy-efficient, and power consumption

### 2.2.3 Screening of Papers

To ensure that all the papers included in the review were clearly related to the research questions, detailed inclusion and exclusion criteria were defined. Table 2.1 describes the inclusion and exclusion criteria chosen for our research.

**Table 2.1:** Inclusion and Exclusion Criteria

| Criteria for Inclusion                                                                             | Criteria for Exclusion                               |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Studies that focus on the improved stability of SRAM cells                                         | Studies not in English                               |

| Studies focusing on various approaches for energy-efficient, leakage power, and stability analysis | Studies not related to any of the research questions |

| Studies that conduct High-performance SRAM Cell analysis of their research                         | Studies whose findings are unclear and ambiguous     |

### 2.3. REVIEW OF DIFFERENT SRAM CELLS DESIGNS

Several methods have been proposed for improved stability and energy efficiency for SRAMs in the present low-power analysis. Below is a summary of the work done on SRAMs that are more stable and energy-efficient. Noted that traditional static random-access memory (SRAM) cells often experience internal data instability because the read operations involve direct access to the data storage nodes. Memory cell noise margins in scaled CMOS technologies decrease with increasing power supply voltage and variability. This work presents memory architectures featuring six, seven, eight, and nine transistors, and evaluates them based on key parameters such as area, data stability, write voltage margin, access speed, active power usage, idle leakage current, and minimum operating voltage. To compare these memory cells, a comprehensive electrical performance metric is employed, which considers both manufacturing variations and supply voltage fluctuations. Triple-threshold-voltage 8T and 9T SRAM cells demonstrate up to 2.5 times lower data stability but offer 765.9 times better overall electrical performance than conventional 6T SRAM cells when implemented using TSMC 65 nm CMOS technology [28].

This study proposes a gated ground SRAM design based on a seven-transistor (7T) bit-cell. Under varying process, voltage, and temperature (PVT) conditions, the proposed cell shows superior data stability and yield in comparison to the conventional 6T cell. A single-ended sensing amplifier is also presented for reading from the proposed cell, and a novel write mechanism is employed to reduce write power to less than half that of the 6T cell. The proposed cell is designed and simulated to use a similar silicon area and

leakage power to the 6T cell using a commercial 65 nm CMOS technology. Ground gating is achieved by selectively controlling the column virtual ground (CVG) of consecutively accessed words. By adopting multiple words per row and significantly reducing leakage power consumption, the design minimizes multi-bit data upsets caused by radiation-induced single-event disturbances or soft errors. Additionally, because of its intrinsic 30% greater soft error critical charge, the recommended cell's soft error rate (SER) is less than half that of the 6T cell [29]. According to [30], speed, power consumption, and area are among the key considerations in modern memory design, especially as this study advances toward deep sub-micron technologies; the problems of leakage current, noise, and cell stability caused by changes in physical characteristics become more apparent. In this work, an 8T read-decoupled dual-port SRAM cell with dual threshold voltage was built, and its leakage current, data retention voltage, read-write delay, and read-write noise margins were all assessed. Through read decoupling, dual-V<sub>t</sub> transistors are used to boost the read noise margin and decrease static power dissipation. The results show the benefit of the proposed design in comparison to existing 6T, 8T, and 9T SRAM Cells. The cell in TSPICE is designed and simulated using 90 nm CMOS technology. The reduction of leakage current and data retention are two of the primary problems with modern CMOS technology. In this study, 6T, 8T, and 9T SRAM cells' read and write latency, read and write margins, **data retention voltage (DRV)**, **layout, and parasitic capacitance** are compared. Through **statistical simulation of the noise margin** and corner analysis, the effects of intrinsic parameter modifications have been investigated. When compared to 6T SRAM cells, 8T and 9T SRAM cells have a greater read noise margin (about four times the RSNM). The 9T SRAM cell offers greater write stability despite being around 1.35 times larger than the 8T SRAM cell. **The 8T SRAM cell's write stability is significantly impacted by single-ended bit line sensing.** The write '1' noise margin of the 8T SRAM cell is nearly three times lower than that of the 9T SRAM cell. The data retention voltages for the 8T, 9T, and 6T SRAM cells are 93.64 mV, 84.5 mV, and 252.3 mV, respectively. In terms of read delay, the 9T SRAM cell shows a delay of 98.85 ps, compared to 72.82 ps for the 6T cell and 77.72 ps for the 8T cell. The higher read delay is caused by dual threshold voltage technology, which was employed in the 9T SRAM cell to reduce the leakage current. The write delay was 10 ps for 9T SRAM cells, 45.47 ps for 8T SRAM cells, and 8.97 ps for 6T SRAM cells. The simulation was conducted at 90 nm with CMOS technology [31]. Leakage power constitutes a significant portion of the total active power, particularly in scaled-down

15

16

CMOS technologies. It is estimated that 20–50% of the average power loss during normal operation is caused by leakage. This issue is even more critical for mobile devices, where battery life and precise timing are essential. This study introduces a low-leakage SRAM cell and array architecture aimed at delivering high performance with low power consumption for embedded memory applications. Compared to the traditional 6-transistor (6T) SRAM cell, the proposed revolutionary 7-transistor (7T) based memory offers 50% less leakage power and 30% faster access time. Additionally, its area is 20% greater than that of the small 6T cell. All comparisons are based on low-power process technologies from 28 nm foundries [32]. This study provides a low-power SRAM design with a quiet-bit line architecture by integrating two important methodologies. First, to prevent excessive full-swing charging of the bit lines, the authors initially use a single-ended driving approach for the write operation. Second, to maintain constant low voltages for all bit lines, they employ a pre-charge free pulling method for the read operation. An important 84.4% power reduction over a self-designed baseline low-power SRAM macro can result from such an architecture, according to SPICE simulation on a 2K-bit SRAM macro [33]. In order to overcome the inherent read stability and write margin trade-off and scaling functional restrictions, large-scale 6T SRAM beyond 65 nm will increasingly rely on assist technologies. Improved read or write margin has been the main goal of circuit assistance techniques, with little consideration paid to performance issues. In this study, they demonstrate the direct effects on voltage-sensitive yield and present margin sensitivity and delay analysis tools for evaluating the functional efficiency of bias-based assist approaches. A margin and delay analysis demonstrates how bias-based circuit assistance techniques influence functionality, stability, and performance characteristics. A framework is established to evaluate these assistance methods, providing a basic understanding of their underlying mechanisms. The study covers four generations of low-power technologies to illustrate trends and assess the long-term effectiveness of circuit assistance strategies in future low-power bulk technologies [34]. This study proposes a low-power write technique based on charge-sharing. By minimizing the voltage swing on the bit lines, the dynamic power consumption of the bit lines is effectively reduced. The static noise margin (SNM) of the memory cell concept is discussed in order to illustrate its viability. According to simulation data, this SRAM saves more than 20% dynamic power during the write cycle when compared to traditional SRAM [35]. A significant portion of the entire chip is occupied by on-chip cache, which is predicted to grow in advanced technologies. A significant amount of the power used

2 during a write operation is represented by the capacitance of charging and discharging bit lines. This study provides a brand-new write mechanism that can execute a write operation using just one of the two-bit lines. Consequently, to execute a write operation, the suggested 7T SRAM cell lowers the activity factor of discharging the bit line pair.