# Phd Thesis Ms. Tanvika Garg

*by* Sumit kale

**Submission date:** 11-Dec-2025 01:09PM (UTC+0530)

**Submission ID:** 2843240310

**File name:** Thesis\_writing\_final.pdf (4.95M)

Word count: 34529 Character count: 192764

# DESIGN AND PERFORMANCE IMPROVEMENT OF GALLIUM NITRIDE HIGH ELECTRON MOBILITY TRANSISTORS FOR POWER ELECTRONICS APPLICATIONS

Thesis Submitted

In Partial Fulfilment of the Requirements

for the Degree of

# **DOCTOR OF PHILOSOPHY**

in

**Electronics and Communication Engineering**

by

TANVIKA GARG (Roll No.: 2K21/PHDEC/06)

Under the supervision of

Dr. SUMIT KALE

Assistant Professor, ECE Department, DTU, Delhi

To the

Department of Electronics and Communication Engineering

#### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Shahbad Daulatpur, Main Bawana Road, Delhi-110042, India December, 2025

i

| UNIVERSITY, DEL | HI, |

|-----------------|-----|

| UNIVERSITY, DEL | HI, |

|                 |     |

|                 |     |

|                 |     |

|                 |     |

|                 |     |

|                 |     |

#### ACKNOWLEDGEMENTS

I am deeply grateful to those who have supported me throughout this journey, making it both meaningful and fulfilling. This dissertation marks not just an achievement but the beginning of a new chapter.

First and foremost, I thank the Almighty for His blessings, strength, and guidance. My heartfelt gratitude goes to my supervisor, **Dr. Sumit Kale**, from the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, for his invaluable mentorship, encouragement, and insightful guidance. His patience and belief in my work have been instrumental in my research.

I extend my sincere appreciation to my doctoral committee members for their valuable feedback and to **Prof. Neeta Pandey**, Head of the Department of Electronics and Communication Engineering and **Prof. O. P. Verma**, Former Head of the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, along with the faculty and staff, for their continuous support. I am also thankful to **Delhi Technological University** for providing essential resources and a conducive research environment.

A special thanks to my colleagues and friends — Dr. Shivani, Mr. Vishal, Dr. Palak, Mr. Rohit, Ms. Aparna, and Ms. Shabana —for their encouragement and support.

This thesis is dedicated to my parents, **Mr. Ramesh Garg** and **Mrs. Neeta Garg**, and my twin sister, **Ms. Tulika Garg**, whose unwavering love and support have been my greatest strength. Lastly, my sincere gratitude to all friends, mentors, and well-wishers who have contributed to this journey.

Tameka Gar

Tanvika Garg

# DELHI TECHNOLOGICAL UNIVERSITY

Formerly Delhi College of Engineering Shahbad Daulatpur, Main Bawana Road, Delhi –42

#### CANDIDATE'S DECLARATION

I. Tanvika Garg, hereby certify that the work which is being presented in the thesis entitled Design and Performance Improvement of Gasjum Nitride High Electron Mobility Transistors for Power Electronics Applications in partial fulfillment of the requirements for the award of the Degree of Doctor of Philosophy, submitted in the Department of Electronics and Communication Engineering, Delhi Technological University is an authentic record of my own work carried out during the period from August 2021 to June 2025 under the Operation of Dr. Sumit Kale.

The matter presented in the thesis has not been submitted by me for the award of any other degree of this or any other Institute.

Candidate's Signature

This is to certify that the student has incorporated all the corrections suggested by the examiners in the thesis and the statement made by the candidate is correct to the best of our knowledge.

Signature of Supervisor Signature of External Examiner

## DELHI TECHNOLOGICAL UNIVERSITY

Formerly Delhi College of Engineering Shahbad Daulatpur, Main Bawana Road, Delhi –42

## **CERTIFICATE** BY THE SUPERVISOR

Certified that Tanvika Garg (Enrollment No.: 2K21/PHDEC/06) has carried out their research work presented in this thesis entitled "Design and Performance Improvement of Gilium Nitride High Electron Mobility Transistors for Power Electronics Applications", for the award of Doctor of Philosophy from the Department of Electronics and Communication Engineering, Delhi Technological University, under my guidance and supervision. The thesis embodies results of original work, and studies are carried out by the student herself and the contents of the thesis do not form the basis for the award of any other degree to the candidate or to anybody else from this or any other University/Institution.

Dr. Sumit Kale

Supervisor

Department of ECE

Delhi Technological University,

Delhi –110042, India

Place: New Delhi Date:

# DESIGN AND PERFORMANCE IMPROVEMENT OF GALLIUM NITRIDE HIGH ELECTRON MOBILITY TRANSISTORS FOR POWER ELECTRONICS APPLICATIONS

#### TANVIKA GARG

#### ABSTRACT

Gallium Nitride High Electron Mobility Transistors (GaN HEMTs) have emerged as a pivotal technology in power electronics due to their superior material properties, including a wide bandgap, high electron mobility, and excellent thermal stability. Despite their advantages, key challenges such as gate leakage current, breakdown voltage limitations, and high on-resistance hinder their widespread adoption in high-power applications. This thesis systematically presents novel structural and material engineering approaches to optimize GaN HEMTs for high performance in power electronics applications.

In this thesis, we have designed novel device design techniques for GaN HEMT to improve performance by minimizing gate leakage current, reducing on-resistance, and enhancing breakdown voltage. To reduce gate leakage current, we have introduced MIS and p-GaN structures, Gaussian-doped p-GaN HEMT, and Omega  $(\Omega)$ -shaped gate p-GaN MIS-HEMT. Additionally, we have presented p-GaN HEMTs with an AlInN/AlN/GaN double heterostructure and an InAlGaN back-barrier to improve on-resistance, as well as stepped AlGaN hybrid buffer GaN HEMTs to enhance breakdown voltage. We have also investigated an analytical model to examine the effects of buffer traps on 2DEG density and gate leakage current, particularly at cryogenic temperatures.

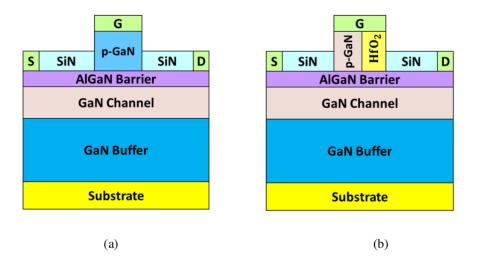

To suppress gate leakage current, an enhancement-mode GaN HEMT with an MIS and p-GaN structure has been designed. By integrating a high-k  $HfO_2$  dielectric layer, this device reduces tunneling effects and improves the threshold voltage while maintaining high drain current performance. In addition, we have introduced a Gaussian-doped p-GaN that incorporates a controlled doping profile in the GaN channel to minimize electric field variations. This approach significantly reduces gate leakage current while improving transconductance and current drive capability. Furthermore, an Omega  $(\Omega)$ -shaped gate has been introduced in p-

GaN MIS-HEMT, demonstrating a significant reduction of gate leakage, enhanced breakdown voltage, and improved reliability. This is achieved through optimized dielectric stress distribution.

The on-resistance has been reduced by implementing a p-GaN HEMT with an AlInN/AlN/GaN double heterostructure and an InAlGaN back-barrier. The AlInN/GaN interface increases 2DEG density, improving current handling, while the InAlGaN back-barrier confines electrons, enhancing efficiency.

Breakdown voltage and BFOM are enhanced by integrating a stepped AlGaN hybrid buffer into the p-GaN HEMT. The optimized lower aluminum concentration reduces surface defects, improves breakdown voltage, and decreases leakage current. The design outperforms conventional HB-HEMTs with higher breakdown voltage, improved BFOM, enhanced transconductance, and lower small-signal capacitances.

We have developed an analytical model to examine buffer trap effects and cryogenic temperature on 2DEG density and gate leakage in p-GaN HEMT. It incorporates thermionic emission, Poole-Frenkel emission, and thermally-assisted tunneling to describe leakage mechanisms and analyzes buffer trap influence on Schottky barrier potential drop and electric field distribution. The findings offer key insights for optimizing device structures to suppress leakage current.

The proposed device architectures have been extensively validated using numerical simulations, ensuring their feasibility for real-world power electronics applications. The findings of this thesis contribute to the ongoing evolution of GaN HEMT technology, providing a strong foundation for future research in high-efficiency, high-reliability power semiconductor devices.

#### LIST OF PUBLICATIONS

#### **SCIE/SCI Indexed Journals**

- 1. **T. Garg** and S. Kale, "Optimization of structural parameters in Omega( $\Omega$ ) Shaped gate p-GaN MIS-HEMT for performance improvement", **Micro and Nanostructures**, vol. 188, Feb. 2024, doi: 10.1016/j.micrna.2024.207793.

- T. Garg and S. Kale, "A novel p-GaN HEMT with AlInN/AlN/GaN double heterostructure and InAlGaN back-barrier," Microelectronics Reliability, vol. 145, 2023, doi: 10.1016/j.microrel.2023.114998.

- T. Garg and S. Kale, "A novel stepped AlGaN hybrid buffer GaN HEMT for power electronics applications," Microelectronics Reliability, vol. 149, 2023, doi: 10.1016/j.microrel. 2023.115232.

- T. Garg and S. Kale "Analytical Modeling of Buffer Trap Effects on 2DEG Density and Gate Leakage Current in p-GaN HEMT at Cryogenic Temperatures," Micro and Nanostructures (Revision Submitted)

#### **International Journal**

T. Garg and S. Kale, "Recent Developments, Reliability Issues, Challenges and Applications of GaN HEMT Technology," in IEEE Electron Devices Reviews, vol. 1, no. 1, pp. 16-30, Oct. 2024, doi: 10.1109/EDR.2024.3491716.

#### **IEEE Scopus Indexed Conference**

- T. Garg and S. Kale, "A Novel Enhancement Mode GaN HEMT with MIS and p-GaN structure," 2024 IEEE 9th International Conference for Convergence in Technology (I2CT), Pune, India, 2024, pp. 1-3, doi: 10.1109/I2CT-61223.2024.10543334.

- T. Garg and S. Kale, "A Gaussian Doped p-GaN HEMT for Power Electronics Application," 2024 IEEE Third International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), Delhi, India, 2024, pp. 1007 1010, doi: 10.1109/ICPEICES62430.2024.10719370.

#### Patent

Tanvika Garg et al., "A Novel Dual-k Double-Sided Dielectric p-GaN MISHEMT for Power Electronics Application" (Patent Published)

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                        | iii        |

|---------------------------------------------------------|------------|

| CANDIDATE'S DECLARATION                                 | iv         |

| CERTIFICATE BY THE SUPERVISOR                           | v          |

| ABSTRACT                                                | vii-viii   |

| LIST OF PUBLICATIONS                                    | ix         |

| TABLE OF CONTENTS                                       | x-xiii     |

| LIST OF TABLES                                          | xiv        |

| LIST OF FIGURES                                         | xv-xviii   |

| LIST OF ABBREVIATIONS                                   | xix-xxi    |

| LIST OF SYMBOLS                                         | xxii-xxiii |

| CHAPTER 1: INTRODUCTION                                 | 1          |

| 1.1 Motivation                                          | 2          |

| 1.2 Objectives                                          | 3          |

| 1.3 Thesis Organization                                 | 4          |

| 1.4 References                                          | 6          |

| CHAPTER 2: LITERATURE SURVEY                            | 8          |

| 2.1 Introduction                                        | 8          |

| 2.2 Types of GaN HEMT Technology                        | 9          |

| 2.2.1 GaN HEMT Technology Based on Orientation          | 9          |

| 2.2.1.1 A Lateral GaN HEMT Technology                   | 9          |

| 2.2.1.2 A Vertical GaN HEMT Technology                  | 9          |

| 2.2.2 GaN HEMT Technology Based on Mode of Operation    | 10         |

| 2.2.2.1 Normally-on                                     | 10         |

| 2.2.2.2 Normally-off                                    | 10         |

| 2.3 Working Principle of GaN HEMT                       | 12         |

| 2.3.1 Wide Bandgap Compound Semiconductor: GaN          | 12         |

| 2.3.2 Crystal Structure and Polarization of GaN         | 13         |

| 2.3.3 The Formation and Calculation of the 2DEG Density | 14         |

| 2.3.3.1 Formation of the 2DEG in AlGaN/GaN Hetero-      | 14         |

| structure                                               |            |

Х

| 2.3.3.2 Calculation of the 2DEG Density in AlGaN/GaN          | 16 |

|---------------------------------------------------------------|----|

| Heterostructure                                               |    |

| 2.4 Early Advancements in GaN HEMT Technology                 | 18 |

| 2.5 GaN HEMTs for High-Power Applications                     | 19 |

| 2.5.1 p-GaN HEMTs                                             | 20 |

| 2.5.1.1 Gate Engineered p-GaN HEMTs                           | 20 |

| 2.5.1.2 Buffer Engineered p-GaN HEMTs                         | 21 |

| 2.5.1.3 Passivation Engineered p-GaN HEMTs                    | 21 |

| 2.5.2 GaN MISHEMTs                                            | 22 |

| 2.6 Applications of GaN HEMT Technology                       | 23 |

| 2.7 Literature Review                                         | 25 |

| 2.8 Research Gaps                                             | 38 |

| 2.9 Summary                                                   | 38 |

| 2.10 References                                               | 39 |

| CHAPTER 3: OPTIMIZATION AND SUPPRESSION OF GATE               | 51 |

| LEAKAGE CURRENT                                               |    |

| 3.1 Introduction                                              | 51 |

| 3.2 An Enhancement Mode GaN HEMT with MIS and p-GaN Structure | 52 |

| 3.2.1 Device structure, Calibration, and Simulation setup     | 52 |

| 3.2.2 Results and Discussion                                  | 54 |

| 3.3 A Gaussian Doped p-GaN HEMT                               | 58 |

| 3.3.1 Device structure, Calibration, and Simulation setup     | 58 |

| 3.3.2 Results and Discussion                                  | 59 |

| 3.4 Omega ( $\Omega$ ) – Shaped gate p-GaN MIS-HEMT           | 61 |

| 3.4.1 Device structure, Simulation setup, Calibration, and    | 62 |

| Fabrication                                                   |    |

| 3.4.2 Results and Discussion                                  | 64 |

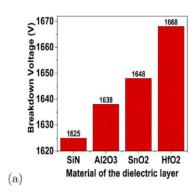

| 3.4.2.1 Effects of variation in the gate dielectric material  | 64 |

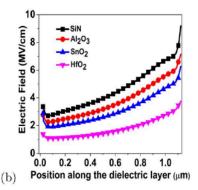

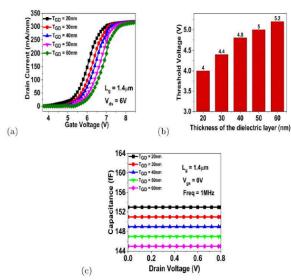

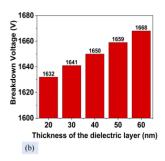

| 3.4.2.2 Effects of scaling the thickness of the gate          | 65 |

| dielectric                                                    |    |

| 3.4.2.3 Effects of variation in the gate dielectric length    | 67 |

| 3.5 Summary                                                   | 68 |

| 3.6 I    | References                                                       | 72  |

|----------|------------------------------------------------------------------|-----|

| CHAPTER  | 4: MINIMIZING ON-RESISTANCE FOR ENHANCED                         | 75  |

| DEVICE P | ERFORMANCE                                                       |     |

| 4.1 I    | Introduction                                                     | 75  |

| 4.2 I    | Device structure, Simulation setup, Calibration, and Fabrication | 76  |

| 4.3 I    | Results and Discussion                                           | 79  |

|          | 4.3.1 DC and AC behavior of the proposed device for different    | 80  |

|          | InAlGaN thicknesses                                              |     |

|          | 4.3.2 Optimized performance parameters of the proposed device    | 81  |

| 4.4 \$   | Summary                                                          | 83  |

| 4.5 I    | References                                                       | 86  |

| CHAPTER  | 2 5: ENHANCING BREAKDOWN VOLTAGE FOR                             | 90  |

| IMPROVE  | CD EFFICIENCY AND PERFORMANCE                                    |     |

| 5.1 I    | Introduction                                                     | 90  |

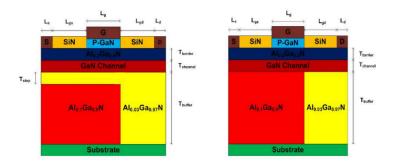

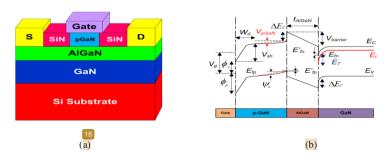

| 5.2 I    | Device structure, Simulation setup, Calibration, and Fabrication | 91  |

| 5.3 I    | Results and Discussion                                           | 94  |

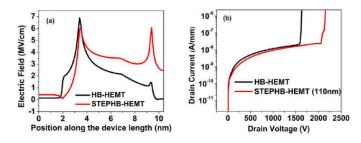

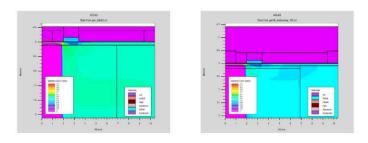

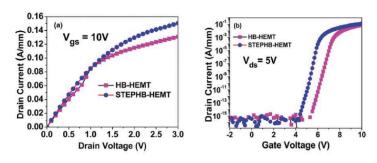

|          | 5.3.1 Comparison of the DC behavior of conventional HB-HEMT      | 94  |

|          | and proposed STEPHB-HEMT                                         |     |

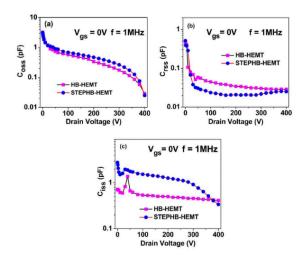

|          | 5.3.2 Comparison of the AC behavior of conventional HB-HEMT      | 97  |

|          | and proposed STEPHB-HEMT                                         |     |

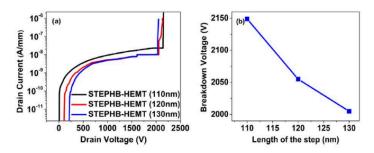

|          | 5.3.3 Optimization of the Device Design Parameters               | 97  |

| 5.4 \$   | Summary                                                          | 98  |

| 5.5 I    | References                                                       | 100 |

| CHAPTER  | 6: ANALYTICAL MODELING OF BUFFER TRAP EFFECTS                    | 103 |

| ON 2DEC  | G DENSITY AND GATE LEAKAGE CURRENT AT                            |     |

| 15       | NIC TEMPERATURES Introduction                                    | 103 |

|          | Device Schematic and Energy Band Diagram                         | 103 |

|          | Model Formulation                                                | 105 |

| 0.51     | 6.3.1 Model Electronics for Buffer Traps at Cryogenic            | 105 |

|          | Temperatures                                                     | 100 |

| 6.3.2 Model Electronics for Potential Variations at Cryogenic   | 108 |

|-----------------------------------------------------------------|-----|

| Temperatures including Buffer Traps                             |     |

| 6.3.2.1 Schottky Barrier Potential Drop                         | 108 |

| 6.3.2.2 AlGaN Barrier Potential Drop                            | 109 |

| 6.3.3 Equation for Potential Balance and Fermi Dirac Statistics | 109 |

| 6.3.4 Model Electrostatics for Gate Leakage Mechanism at        | 110 |

| Cryogenic Temperatures including Buffer Traps                   |     |

| 6.3.4.1 Thermionic Emission                                     | 110 |

| 6.3.4.2 Thermally Assisted Tunneling                            | 111 |

| 6.3.4.3 Poole Frenkel Emission                                  | 111 |

| 6.4 Results and Discussion                                      | 112 |

| 6.5 Summary                                                     | 117 |

| 6.6 References                                                  | 119 |

| CHAPTER 7: CONCLUSION, FUTURE SCOPE AND SOCIAL IMPACT           | 125 |

| 7.1 Conclusion                                                  | 125 |

| 7.2 Future Scope and Social Impact                              | 127 |

| 7.2.1 Research Directions                                       | 128 |

| 7.2.2 Social Impact                                             | 128 |

# LIST OF TABLES

| Table 2.1 | Literature on breakdown voltage in GaN HEMT                              | 25-3 |

|-----------|--------------------------------------------------------------------------|------|

| Table 2.2 | Literature on on-resistance in GaN HEMT                                  | 34-3 |

| Table 2.3 | Literature on gate leakage in GaN HEMT                                   | 39-4 |

| Table 2.4 | Literature on analytical modelling of gate leakage in GaN HEMT           | 44-4 |

| Table 3.1 | The structural parameters of the proposed MG-HEMT                        | 65   |

| Table 3.2 | Comparison of performance parameters of the proposed device              | 70   |

|           | with the reported literature                                             |      |

| Table 3.3 | The structural parameters of the proposed GD-HEMT                        | 72   |

| Table 3.4 | Comparison of performance parameters of the proposed GD-                 | 75   |

|           | HEMT with the reported devices                                           |      |

| Table 3.5 | Performance Comparison of the Proposed Device for Varying                | 83   |

|           | Gate Dielectric Thicknesses                                              |      |

| Table 3.6 | Performance Comparison of the Proposed Device for Varying                | 83   |

|           | Gate Dielectric Lengths.                                                 |      |

| Table 3.7 | Performance comparison of the proposed device with the state-of-         | 84   |

|           | the-art devices in the literature.                                       |      |

| Table 4.1 | Performance Comparison of the Proposed Device for Varying InAlGaN        | 98   |

|           | Thicknesses.                                                             |      |

| Table 4.2 | The parameter comparison of the proposed and state-of-the-art            | 98   |

|           | devices                                                                  |      |

| Table 5.1 | The main structural parameters of the proposed STEPHB-HEMT               | 105  |

|           | device                                                                   |      |

| Table 5.2 | The values of breakdown voltage at different values of T <sub>step</sub> | 113  |

| Table 5.3 | Performance comparison of the proposed STEPHB-HEMT with                  | 113  |

|           | state-of-the-art devices                                                 |      |

| Table 6.1 | Comparison of parameters derived from the models presented in            | 130  |

|           | this chapter                                                             |      |

| Table 7.1 | Comparative analysis of parameters across the devices proposed           | 137  |

|           | in this thesis                                                           |      |

## LIST OF FIGURES

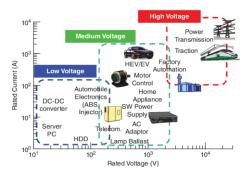

| Fig. 1.1 | GaN HEMT applications by voltage range: Low Voltage (10 V-100                        | 2  |

|----------|--------------------------------------------------------------------------------------|----|

|          | V) - Consumer Electronics and Automotive; Medium Voltage (100                        |    |

|          | $V\!-\!1000\;V) - Electric\;Vehicles, Industrial\;and\;Telecom; High\;Voltage$       |    |

| 9        | (1000 V-10,000 V)- Power Transmission, Rail and Automation.                          |    |

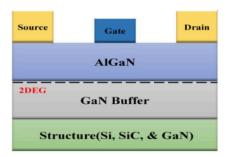

| Fig. 2.1 | Schematic of lateral GaN HEMT                                                        | 9  |

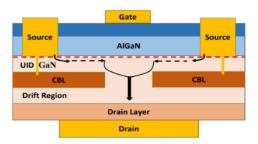

| Fig. 2.2 | Schematic of vertical GaN HEMT                                                       | 10 |

| Fig. 2.3 | Schematic of depletion mode GaN HEMT                                                 | 10 |

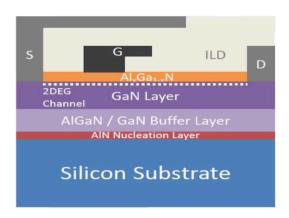

| Fig. 2.4 | Schematic of enhancement mode GaN HEMT                                               | 12 |

| Fig. 2.5 | Considering an n-doped AlGaN film freestanding but strained                          | 15 |

|          | equivalently to an AlGaN/GaN heterostructure, the polarization field                 |    |

|          | causes electrons to traverse from one side to the other. Consequently,               |    |

|          | the energy bands bend and fixed positive charges accumulate in the                   |    |

|          | AlGaN layer                                                                          |    |

| Fig. 2.6 | Energy-band diagram of an n-doped AlGaN/GaN heterostructure.                         | 16 |

|          | Upon contact, electrons transfer into the GaN side, accumulate at the                |    |

|          | interface, and form a two-dimensional electron gas (2DEG)                            |    |

| Fig. 2.7 | Charge distribution profile of an AlGaN/GaN heterostructure                          | 17 |

| Fig. 2.8 | Conductive band diagram of an AlGaN/GaN heterostructure                              | 17 |

| Fig. 3.1 | The schematic diagram of (a) the conventional device and (b) the                     | 64 |

|          | proposed MG-HEMT.                                                                    |    |

| Fig. 3.2 | Calibration of the p-GaN HEMT                                                        | 65 |

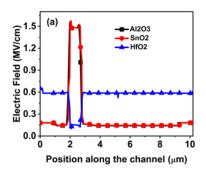

| Fig. 3.3 | The comparison of the proposed device with respect to the dielectric                 | 66 |

|          | constant of the insulating layer (a) the electric field and (b) the gate             |    |

|          | leakage current.                                                                     |    |

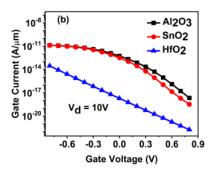

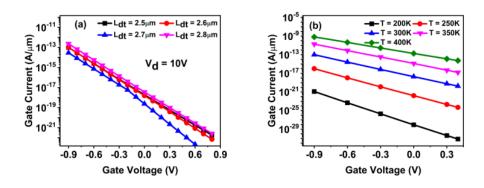

| Fig. 3.4 | (a) The gate leakage current for different values of length of the $\mbox{HfO}_2$    | 67 |

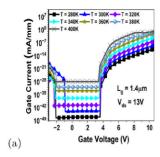

|          | dielectric layer (L_{dt}), and (b) The temperature-dependent $I_g\text{-}V_g$ curves |    |

|          | of the proposed device from 200 K to 400 K.                                          |    |

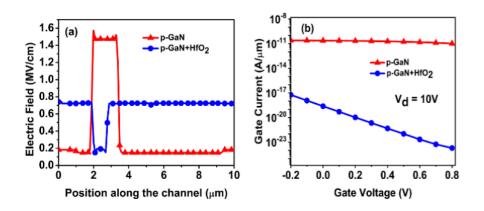

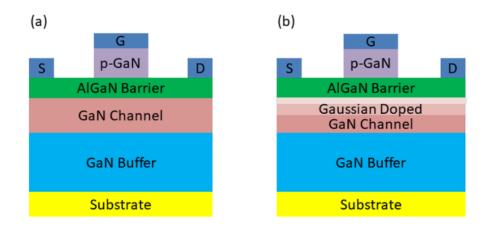

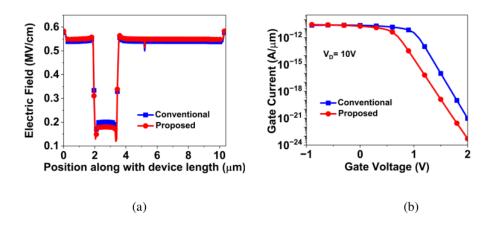

| Fig. 3.5 | (a) The electric field and (b) the gate leakage current comparison of                | 67 |

|          | the proposed and conventional device.                                                |    |

| Fig. 3.6 | (a) Gate capacitance and (b) transconductance comparison of the                      | 68 |

|          | proposed and conventional device.                                                    |    |

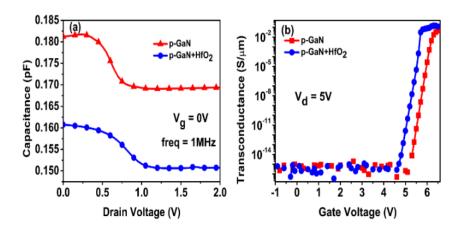

| Fig. 3.7  | (a) $I_d\text{-}V_d$ and (b) $I_d\text{-}V_g$ characteristics comparison of the conventional      | 68 |

|-----------|---------------------------------------------------------------------------------------------------|----|

|           | and proposed device                                                                               |    |

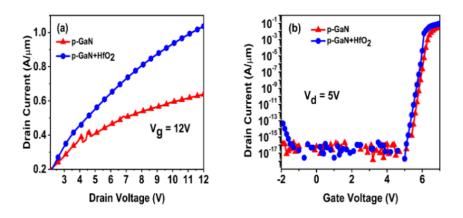

| Fig. 3.8  | The schematic diagram of (a) the conventional device and (b) the                                  | 70 |

|           | proposed GD-HEMT.                                                                                 |    |

| Fig. 3.9  | The comparison of the proposed GD-HEMT with respect to dopant                                     | 71 |

|           | concentration (a) the electric field and (b) the gate leakage current.                            |    |

| Fig. 3.10 | (a) The electric field and (b) the gate leakage current comparison of                             | 72 |

|           | the proposed and conventional device.                                                             |    |

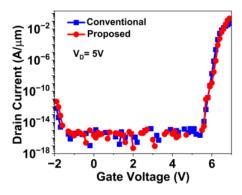

| Fig. 3.11 | $I_d$ - $V_g$ comparison of the proposed GD-HEMT and the conventional device                      | 73 |

| Fig. 3.12 | I <sub>d</sub> -V <sub>d</sub> comparison of the proposed GD-HEMT and the conventional            | 74 |

| 28        | device                                                                                            |    |

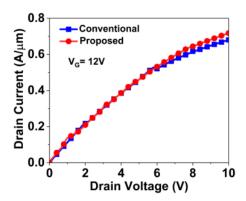

| Fig. 3.13 | The structure of the proposed device                                                              | 76 |

| Fig. 3.14 | The fabrication process for the proposed device                                                   | 77 |

| Fig. 3.15 | Impact of different gate dielectric materials on (a) breakdown voltage                            | 78 |

|           | and (b) electric field of the proposed device                                                     |    |

| Fig. 3.16 | Impact of different gate dielectric thicknesses on (a) transfer                                   | 79 |

|           | characteristics, (b) threshold voltage and (c) c-v characteristics of the                         |    |

|           | proposed device                                                                                   |    |

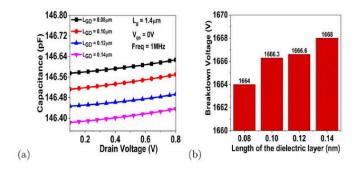

| Fig. 3.17 | Impact of different gate dielectric thicknesses on (a) Ig-Vg                                      | 80 |

|           | characteristics and (b) electric field of the proposed device.                                    |    |

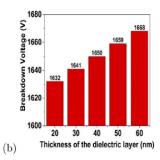

| Fig. 3.18 | (a) Ig-Vg characteristics of the proposed device with respect to                                  | 80 |

|           | temperature and (b) Impact of different gate dielectric thicknesses on                            |    |

|           | breakdown voltage of the proposed device                                                          |    |

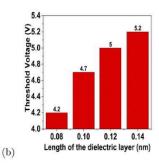

| Fig. 3.19 | Impact of different gate dielectric lengths on (a) I <sub>d</sub> -V <sub>g</sub> characteristics | 82 |

|           | and (b) threshold voltage of the proposed device.                                                 |    |

| Fig. 3.20 | Impact of different gate dielectric lengths on (a) C-V characteristics                            | 82 |

|           | and (b) breakdown voltage of the proposed device                                                  |    |

| Fig. 4.1  | Schematic of the proposed structure                                                               | 88 |

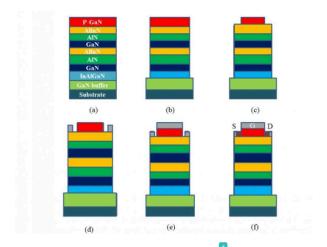

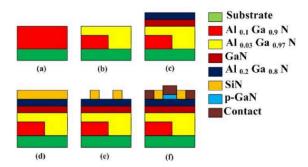

| Fig. 4.2  | Fabrication steps of the proposed device (a) Starting wafer (b) mesa                              | 89 |

|           | isolation by dry etching (c) p- GaN layer etching (d) ohmic contact                               |    |

|           | formation of source-drain(e) gate contact formation (f) passivation                               |    |

|           | with deposited SiN layer                                                                          |    |

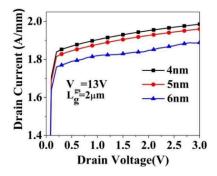

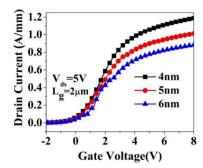

| Fig. 4.3  | I <sub>d</sub> -V <sub>d</sub> characteristics of the proposed device for different values of                              | 90  |

|-----------|----------------------------------------------------------------------------------------------------------------------------|-----|

|           | InAlGaN thickness.                                                                                                         |     |

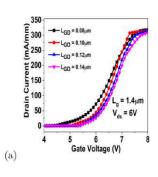

| Fig. 4.4  | I <sub>d</sub> -V <sub>g</sub> characteristics of the proposed device for different values of                              | 91  |

|           | InAlGaN thickness                                                                                                          |     |

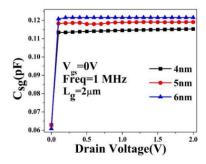

| Fig. 4.5  | The capacitance-voltage characteristics of the proposed device for                                                         | 92  |

|           | different values of InAlGaN thickness                                                                                      |     |

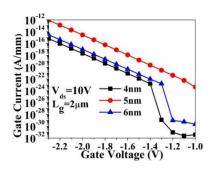

| Fig. 4.6  | The gate leakage current with respect to gate voltage of the proposed                                                      | 93  |

|           | device for different values of InAlGaN thickness                                                                           |     |

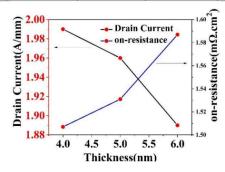

| Fig. 4.7  | Optimization of the proposed device for InAlGaN thickness of 4 nm,                                                         | 94  |

|           | 5 nm and 6 nm with respect to on-resistance and drain current.                                                             |     |

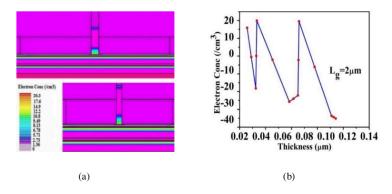

| Fig. 4.8  | The electron concentration in the proposed device (a) Contour plot and                                                     | 94  |

|           | (b) Graphical representation.                                                                                              |     |

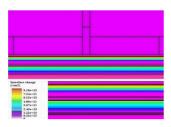

| Fig. 4.9  | Contour plot of the interface charge for the proposed device                                                               | 95  |

| Fig. 4.10 | Contour plot of the electron current density for the proposed device.                                                      | 96  |

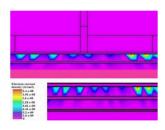

| Fig. 4.11 | The electric field in the proposed device (a) Contour plot and (b)                                                         | 96  |

|           | Graphical representation.                                                                                                  |     |

| Fig. 4.12 | On-state energy band diagram of the proposed device                                                                        | 97  |

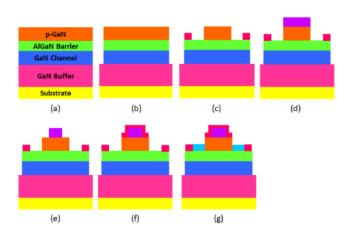

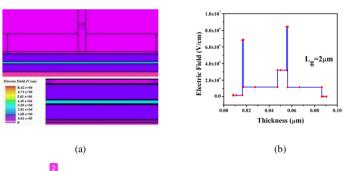

| Fig. 5.1  | The structure of (a) Proposed STEPHB-HEMT and (b) HB-HEMT                                                                  | 104 |

| Fig. 5.2  | Fabrication steps of the proposed STEPHB-HEMT (a) Starting wafer                                                           | 105 |

|           | (b) partial etching of Al <sub>0.1</sub> Ga <sub>0.9</sub> N (c) Growth of the GaN channel layer                           |     |

|           | and the Al <sub>0.2</sub> Ga <sub>0.8</sub> N barrier layer over Al <sub>0.03</sub> Ga <sub>0.97</sub> N (d) deposition of |     |

|           | the SiN passivation layer (e) selective plasma etching of a p-GaN layer                                                    |     |

|           | (f) metallization of ohmic contacts.                                                                                       |     |

| Fig. 5.3  | Comparison between HB-HEMT and proposed STEPHB-HEMT with                                                                   | 107 |

|           | respect to (a) Electric field distribution and (b) Breakdown voltage                                                       |     |

| Fig. 5.4  | Contour plot of electron concentration in (a) HB-HEMT and (b)                                                              | 107 |

|           | Proposed STEPHB-HEMT                                                                                                       |     |

| Fig. 5.5  | The I-V characteristics of HB-HEMT and proposed STEPHB-HEMT                                                                | 108 |

|           | (a) Output characterictics and (b) Transfer characteristics                                                                |     |

| Fig. 5.6  | The C-V characteristics of HB-HEMT and proposed STEPHB-HEMT                                                                | 110 |

|           | with (a) C <sub>oss</sub> (b) C <sub>rss</sub> and (c) C <sub>iss</sub>                                                    |     |

| Fig. 5.7 | The breakdown voltages of the STEPHB-HEMT with different values                                  | 111 |

|----------|--------------------------------------------------------------------------------------------------|-----|

| 9        | of the T <sub>step</sub> and (b) Optimization of the STEPHB-HEMT at different                    |     |

|          | values of T <sub>step</sub> with respect to breakdown voltage                                    |     |

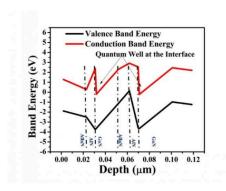

| Fig. 6.1 | (a) Schematic and (b) Energy band diagram for the p-GaN HEMT at                                  | 118 |

|          | ON-state.                                                                                        |     |

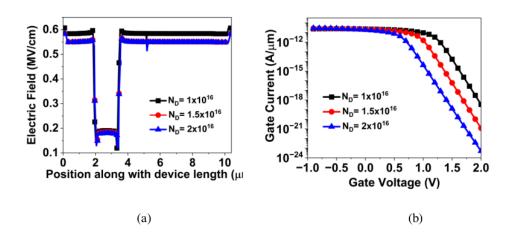

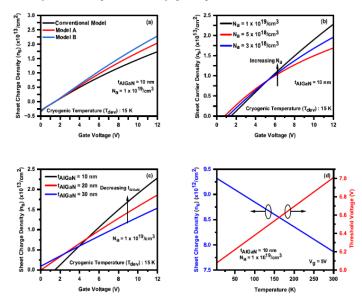

| Fig. 6.2 | (a) Comparison of $n_s$ across the conventional model [17], Model A and                          | 125 |

|          | Model B. (b) Comparison of $n_s$ with varying acceptor concentration in                          |     |

|          | the p-GaN gate layer for the proposed model B. (c) Comparison of $n_{\text{s}}$                  |     |

|          | with respect to AlGaN barrier layer thickness for model B, and (d) Plot                          |     |

|          | showing the variation of ns and threshold voltage with temperature.                              |     |

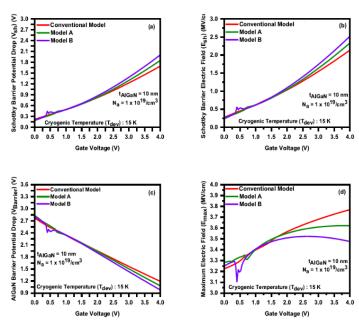

| Fig. 6.3 | Comparison of (a) $V_{sh}$ , (b) $E_{sh}$ , (c) $V_{barrier}$ , and (d) $E_{max}$ across the     | 127 |

|          | conventional model [17], Model A and Model B.                                                    |     |

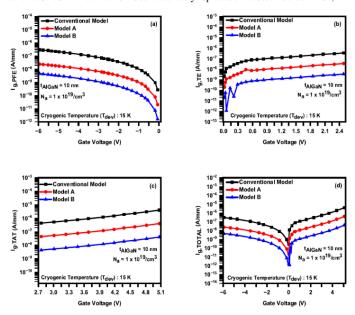

| Fig. 6.4 | Comparison of gate leakage current components (a) $I_{\text{g,PFE}},$ (b) $I_{\text{g,TE}},$ (c) | 128 |

|          | $I_{\rm g,TAT}$ ,and (d) total gate leakage current $(I_{\rm g,TOTAL})$ across the               |     |

|          | conventional model [17], Model A and Model B.                                                    |     |

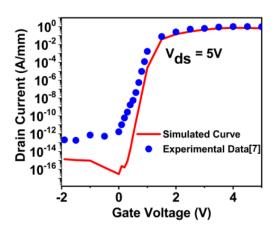

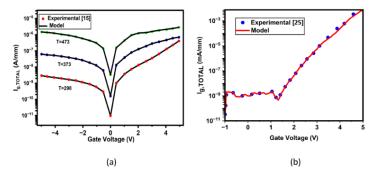

| Fig. 6.5 | Experimental results validating the calibration of gate leakage current                          | 128 |

|          | over the entire bias range.                                                                      |     |

# LIST OF ABBREVIATIONS

2DEG 2-Dimensional Electron Gas

2DHG 2-Dimensional Hole Gas

AC Alternating Current

AI Artificial Intelligence

Al Aluminium

Al<sub>2</sub>O<sub>3</sub> Aluminium Oxide

AlGaN Aluminium Gallium Nitride

AlInN Aluminium Indium Nitride

AIN Aluminium Nitride

ASM Advanced Spice Model

Au Gold

BD Built-in Diode

BFOM Baliga Figure of Merit

CMOS Complementary Metal Oxide Semiconductor

D2DEG Dual 2-Dimensional Electron Gas

DC Direct Current

D-FP Drain Field Plate

EMI Electro-Magnetic Interference

E-mode Enhancement mode EVs Electric Vehicles

Fe Iron

$\begin{array}{lll} F\text{-graphene} & Fluorinated Graphene \\ GaON & Gallium Oxynitride \\ Ga_2O_3 & Gallium Oxide \\ GaO_xN_{1-x} & Gallium Oxynitride \\ \hline GaN & Gallium Nitride \\ \end{array}$

GD-HEMT Gaussian Doped High Electron Mobility Transistor

GGFP Grated Gate Field Plate

GTE Gate Termination Extension

GW GigaWatt

HB-HEMT Hybrid Buffer High Electron Mobility Transistor

xix

High Electron Mobility Transistor HEMT

Hybrid Electric Vehicles HEVs

$HfO_2$ Hafnium Oxide

ICP-RIE Inductively Coupled Plasma Reactive Ion Etching

InAlGaN Indium Aluminium Gallium Nitride IO-pGaN Island Ohmic p-type Gallium Nitride

IoT Internet of Things I-graphene Intrinsic Graphene IPA Isopropyl Alcohol ITO Indium Tin Oxide

Lanthanum Lutetium Oxide  $LaLuO_3$

Mg Magnesium

MG-HEMT Metal Insulator Semiconductor and p-type Gallium

Nitride High Electron Mobility Transistor

Modulation-Doped Field-Effect Transistor MODFET

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

MOCVD Metal-Organic Chemical Vapor Deposition

MIS Metal Insulator Semiconductor

MIS-HEMT Metal Insulator Semiconductor High Electron Mobility

Transistor

NCD Nanocrystalline Diamond Gated

Ni Nickel

n-type Gallium Nitride n-GaN

p-AlGaN p-type Aluminium Gallium Nitride

PECVD Plasma-Enhanced Chemical Vapor Deposition

PFE Poole-Frenkel Emission p-GaN p-type Gallium Nitride

**PSAG** p-type Gallium Nitride Stripe Array Gate

RF Radio Frequency

Silicon Si

Silicon Carbide SiCSiNSilicon Nitride

SOI Silicon on Insulator

SnO<sub>2</sub> Tin Oxide

SRH Shockley-Read-Hall

STEPHB-HEMT Stepped Hybrid Buffer High Electron Mobility

Transistor

SuFP Super Field Plate

TaN Tantalum Nitride

TAT Thermally Assisted Tunneling

TCE Trichloroethylene

TE Thermionic Emission

TUG Thin Upward Graded

UCCM Unified Charge Control Model

WBG Wide Band Gap

#### LIST OF SYMBOLS

$\Delta V_{AlGaN}$  Potential Drop

$\begin{array}{ccc} \sigma_{AIGaN} & & Sheet \ \, \hbox{Charge Density} \\ n_s & & Sheet \ \, \hbox{Density of 2DEG} \end{array}$

$\begin{array}{lll} q & & & & & & & \\ Electron \ Charge & & & & & \\ \epsilon & & & & & & \\ b_b & & & & & \\ Surface \ Barrier \ Height \\ E_f & & & & \\ Fermi \ Level \ Position \end{array}$

ΔE<sub>C</sub> Conduction Band Discontinuity

f<sub>max</sub> Cutoff Frequency

$V_{ds} \hspace{1cm} Drain-to\text{-}Source \hspace{0.1cm} Voltage$

$\begin{array}{cc} R_{ON} & & ON\text{-Resistance} \\ THz & & Terahertz \end{array}$

$V_{th}$  Threshold Voltage  $R_{ep.sp}$  Specific ON-Resistance

V<sub>G</sub> Gate Voltage

$\mu$  micro

V<sub>GS</sub> Gate-to-Source Voltage

$\begin{array}{lll} ^{\circ}C & & Degree \ Celsius \\ I_g & & Gate \ Current \\ I_d & & Drain \ Current \\ V_d & & Drain \ Voltage \end{array}$

$I_{ds,max} \hspace{1.5cm} Maximum \hspace{1.5cm} Drain \hspace{1.5cm} Current$

g<sub>m</sub> Transconductance

MHz Megahertz

$C_{gs}$  Gate-to-Source Capacitance  $C_{gd}$  Gate-to-Drain Capacitance  $C_{ds}$  Drain-to-Source Capacitance

$\begin{array}{lll} E_t & Trap \ Energy \ Level \\ E_C & Conduction \ Band \ Edge \\ n_{trap} & Trap \ Electron \ Density \\ E_T & Trap \ Activation \ Energy \end{array}$

xxii

| $N_{\mathrm{T}}$                          | Trap Concentration           |  |

|-------------------------------------------|------------------------------|--|

| $\beta\text{-}(Al_xGa_{1\text{-}x})_2O_3$ | Beta-Aluminium Gallium Oxide |  |

| $\Omega$ -shaped                          | Omega-shaped                 |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           |                              |  |

|                                           | xxiii                        |  |

# CHAPTER 1

#### INTRODUCTION

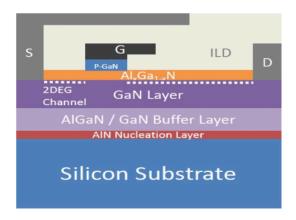

Gallium Nitride High Electron Mobility Transistors (GaN HEMTs) have attracted considerable interest in recent years owing to their outstanding material characteristics, which make them ideal for high power applications [1]. These transistors utilize a heterostructure composed of GaN and AlGaN layers, enabling the creation of a two-dimensional electron gas (2DEG) at their interface, which provides high electron mobility and excellent electrical performance [2]. This high electron mobility significantly reduces resistance, thereby minimizing conduction losses and enabling faster switching speeds compared to conventional semiconductor technologies. As a result, GaN HEMTs offer advantages such as higher power density, and improved efficiency, making them an excellent choice for power electronics where power handling capabilities are essential [3], [4]. Additionally, GaN HEMTs exhibit superior thermal and voltage endurance, allowing them to function effectively in extreme environments, including high-temperature and highpower conditions [5], [6]. Their robustness and ability to maintain efficiency under harsh operating conditions further enhance their suitability for advanced power conversion, and aerospace applications. The continued development of GaN-based power devices has led to innovations in energy-efficient systems. Figure 1.1 depicts the diverse range of applications for GaN HEMT across various voltage levels, highlighting their significance in modern semiconductor technology [7], [8]. Over the years, significant research efforts on GaN HEMTs have resulted in notable advancements in their efficiency, reliability, and overall performance. However, despite these improvements, their widespread commercialization remains hindered by a critical challenge-their inherently normally-on operation, which raises concerns related to safety and cost-effectiveness. To enhance fail-safe functionality, improve system reliability, and simplify circuit design, achieving normally-off

1

operation has become a crucial objective in GaN power electronics. Various techniques have been explored to address this issue, including fluoride plasma treatment, gate recessing, and the incorporation of p-GaN gate structures. Among these methods, the integration of p-GaN gates has emerged as the most practical and commercially viable approach, offering an optimal balance between performance and reliability. This technique involves modifying the epitaxial structure to control the polarization-induced 2DEG. This approach not only ensures enhanced device safety but also facilitates seamless integration into power electronics applications, making GaN HEMTs a promising solution for next-generation power semiconductor technologies.

Fig. 1.1: GaN HEMT applications by voltage range: Low Voltage (10 V-100 V) – Consumer Electronics and Automotive; Medium Voltage (100 V-1000 V) – Electric Vehicles, Industrial and Telecom; High Voltage (1000 V-10,000 V)– Power Transmission, Rail and Automation.

#### 1.1 Motivation

The increasing demand for energy-efficient power electronics across various sectors—including renewable energy, electric vehicles, data centers, and advanced industrial systems—has highlighted the need for next-generation semiconductor technologies. Although silicon-based power devices are well-established and commonly used, they are constrained by limitations in efficiency, thermal tolerance,

and voltage capability, making them less suitable for meeting the stringent requirements of modern power applications. In contrast, GaN HEMTs have emerged as a promising alternative due to their superior properties, including a wider bandgap, enhanced breakdown voltage, increased electron mobility, and excellent thermal management. These advantages make GaN HEMTs a pivotal technology for future power electronics, enabling greater efficiency, higher switching speeds, and more compact and lightweight system designs compared to silicon devices. Despite their potential, the adoption of GaN HEMT in high power electronics is still limited by several challenges, including issues related to device design thermal management, material quality, and cost-effective fabrication techniques. Addressing these challenges requires a deeper understanding of the physical phenomena governing device operation, as well as innovative design approaches and simulation frameworks that can accurately predict device behavior under high power conditions. Additionally, optimizing GaN HEMTs for various power electronics applications demands a thorough investigation of their performance metrics under real-world operating conditions. These research efforts are critical for bridging the gap between the theoretical advantages of GaN HEMTs and their practical implementation in power systems. This research is motivated by the opportunity to contribute to the advancement of GaN HEMT technology through comprehensive design and simulation studies. The outcomes of this research aim to advance the design and simulation of GaN HEMT, enhancing its performance and reliability for power electronics applications. This research has significant potential in contributing to more efficient and sustainable energy systems, supporting global efforts to improve energy utilization and reduce environmental impact.

# 1.2 Objectives

The primary aim of this research is to design and simulate GaN HEMTs tailored for power electronics applications. Given the increasing demand for efficient and reliable power devices, this study focuses on addressing key performance challenges associated with GaN HEMTs, such as breakdown voltage, ON-resistance, and gate leakage. Through comprehensive design and simulation efforts, this research seeks to

develop optimized GaN HEMT structures that can offer enhanced performance, contributing to the advancement of power electronics. The specific objectives outlined in this study aim to tackle these challenges systematically, ultimately improving the efficiency of GaN HEMTs for high power applications. Objectives are listed as below:

- 1. Improvement of the reliability of GaN HEMT by reducing gate leakage.

- Reduction and optimization of the on-resistance of GaN HEMT for improved performance.

- Enhancement of the breakdown voltage of GaN HEMT to withstand high voltages.

- Development of an analytical model for gate leakage optimization of GaN HEMT structure.

#### 1.3 Thesis organization

The thesis comprises seven chapters, which are organized as follows:

**Chapter 1: Introduction** This chapter presents an overview of GaN HEMTs, discussing their properties, applications, and key challenges. The motivation behind the research and its significance in power electronics applications are elaborated. The chapter also outlines the objectives of the research and provides a brief description of the adopted methodologies.

Chapter 2: Literature Review This chapter provides a comprehensive review of existing GaN HEMT technologies, focusing on advancements in device architectures, buffer layer optimizations, and gate engineering techniques. Key performance metrics such as gate leakage current, on-resistance, and breakdown voltage, are analyzed. Various approaches, including p-GaN gate technology and dielectric engineering, are reviewed to highlight their impact on improving device performance.

Chapter 3: Optimization and Suppression of Gate Leakage Current This chapter focuses on structural and material engineering approaches to suppress gate leakage current and enhance device reliability. Three advanced device architectures are proposed and analyzed:

- An enhancement-mode GaN HEMT integrating an MIS and p-GaN structure, which employs a high-k HfO<sub>2</sub> dielectric layer to suppress tunneling effects, improve threshold voltage stability, and enhance current handling capabilities.

- A Gaussian-doped p-GaN HEMT, which utilizes a controlled doping profile in the GaN channel to minimize electric field variations, leading to a 27% reduction in gate leakage current, a 7% improvement in maximum drain current, and a 67% enhancement in transconductance.

- An Omega (Ω)-shaped gate p-GaN MIS-HEMT, which reduces gate leakage through optimized dielectric stress distribution, achieving a 14% reduction in gate leakage and a 20% increase in maximum drain current.

Extensive numerical simulations are performed to validate the proposed designs, ensuring their feasibility for power applications. The chapter provides an in-depth analysis of electric field distribution, tunneling suppression, and doping optimization strategies to improve device performance.

# Chapter 4: A p-GaN HEMT with AlInN/AlN/GaN Double Heterostructure and InAlGaN Back-Barrier

This chapter investigates strategies for reducing on-resistance to enhance current drive capability in GaN HEMTs. A novel p-GaN HEMT design featuring an AlInN/AlN/GaN double heterostructure and an InAlGaN back-barrier is proposed. The simulation results indicate significant improvements in R<sub>ON</sub> and maximum drain current, with a reduction of 85% in R<sub>ON</sub> and an increase of 231% in drain current compared to conventional designs. The chapter also examines the impact of these optimizations on power loss reduction.

#### Chapter 5: A Stepped AlGaN Hybrid Buffer GaN HEMT

To address the challenge of low breakdown voltage in GaN HEMTs, this chapter explores novel device architectures incorporating a stepped hybrid AlGaN buffer layer. The impact of step thickness and electric field distribution on breakdown voltage improvement is analyzed. Simulation results demonstrating a 20% enhancement in breakdown voltage are presented, along with a discussion on Baliga's Figure of Merit (BFOM) improvements.

# Chapter 6: Analytical Modeling of Buffer Trap Effects on 2DEG Density and Gate Leakage Current at Cryogenic Temperature

This chapter presents a physics-based analytical model to examine buffer trap effects on p-GaN HEMTs at cryogenic temperatures. Incorporating key trap parameters and solving the Schrödinger-Poisson equations, the model evaluates 2DEG density and gate leakage mechanisms. A comparison with experimental data confirms its accuracy, showing a 33% increase in 2DEG density and a 99% reduction in gate leakage. These findings highlight the model's potential for optimizing p-GaN HEMTs in cryogenic power applications.

# Chapter 7: Conclusion, Future Scope, and Social Impact

This chapter summarizes the key findings of the research, emphasizing the advancements achieved in GaN HEMT technology for power electronics applications. Potential future research directions, including further optimizations in gate engineering, buffer layer modifications, and experimental refinements, are discussed. The chapter also highlights the broader impact of the research in advancing high-efficiency and high-reliability power semiconductor devices, contributing to sustainable energy solutions.

#### 1.4 References

[1] Tian, Jiangbo, Chunyan Lai, Guodong Feng, Debmalya Banerjee, Wenlong Li, and Narayan C. Kar., "Review of recent progresses on gallium nitride transistor in

power conversion application" International Journal of Sustainable Energy, vol.9, no.1, pp. 88--100, Aug. 2020, 10.1080/14786451.2019.1657866.

- [2] Roccaforte, Fabrizio, Giuseppe Greco, Patrick Fiorenza, and Ferdinando Iucolano, "An overview of normally-off GaN-based high electron mobility transistors." Materials, vol.12, no.10, 1599, May. 2019, 10.3390/ma12101599.

- [3] Greco, Giuseppe, Ferdinando Iucolano, and Fabrizio Roccaforte., "Review of technology for normally-off HEMTs with p-GaN gate." Materials Science in Semiconductor Processing, 78, pp. 96--106, May. 2018, 10.1016/j.mssp.2017.09.027.

- [4] T.Garg and Sumit Kale, "Optimization of structural parameters in Omega-Shaped gate p-GaN MIS-HEMT for performance improvement", Micro and Nanostructures, (2024).

- [5] He, Jiaqi, Wei-Chih Cheng, Qing Wang, Kai Cheng, Hongyu Yu, and Yang Chai, "Recent Advances in GaN-Based Power HEMT Devices." Advanced Electronic Materials, vol.7, no.4, Jan. 2021, 10.1002/aelm.202001045.

- [6] Ranjan, Ravi, Nitesh Kashyap, and Ashish Raman., "Effects of gate width variation on the performance of Normally-OFF dual-recessed gate MIS AlGaN/GaN HEMT." International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, vol.35, no.2, Sep. 2021, 10.1002/jnm.2960.

- [7] Letellier, Juliette. (2019). Diamond Schottky diodes improvement to pave the way to high power electronic application.

- [8] Sumit Verma, Sajad A. Loan, Abdullah G. Alharbi, "Polarization engineered enhancement mode GaN HEMT: Design and investigation, Superlattices and Microstructures, vol. 119, 2018, pp. 181-193, doi.: 10.1016/j.spmi.2018.04.041.

#### **CHAPTER 2**

#### LITERATURE SURVEY

#### 2.1 Introduction

The evolution of semiconductor technology has witnessed a paradigm shift with the emergence of GaN HEMTs, a promising solution to the limitations of traditional silicon-based devices. This chapter delves into a comprehensive literature review of GaN HEMTs, addressing their working principles, material properties, and technological advancements. Beginning with an overview of wide bandgap semiconductors and the role of GaN, the discussion progresses through the fundamental principles underlying the device's operation, particularly the critical role of polarization effects and 2DEG formation. The review further explores early milestones in GaN HEMT development, followed by recent innovations tailored for high-power applications, such as p-GaN HEMTs, MIS-HEMTs, and advancements in device engineering.

This review also comprehensively highlights the critical performance metrics that dictate the operational efficiency and reliability of GaN HEMTs, particularly emphasizing gate leakage current, on-resistance, and breakdown voltage. These parameters serve as fundamental indicators for assessing the suitability of GaN HEMTs in power applications. The breakdown voltage determines the device's capacity to tolerate high electric fields without failure, while the on-resistance influences conduction losses and directly impacts power efficiency. On the other hand, gate leakage current is crucial for evaluating device robustness, particularly under high-voltage and high-temperature stress conditions.

To facilitate a systematic understanding, the review presents a detailed comparative analysis of recent advancements in GaN HEMT technologies through structured tabular summaries. These tables consolidate key findings from contemporary

literature, allowing for a clear evaluation of how various device architectures and fabrication techniques have influenced performance improvements.

#### 2.2 Types of GaN HEMT Technology

#### 2.2.1 GaN HEMT Technology based on Orientation

#### 2.2.1.1 A Lateral GaN HEMT Technology

A lateral GaN HEMT uses the wide-bandgap semiconductor material GaN, as the channel material [8], [9]. The lateral structure of the device means that the current flows in a horizontal direction along the surface of the semiconductor material. The basic structure of a lateral GaN HEMT is depicted in Fig. 2.1.

Fig. 2.1: Schematic of Lateral GaN HEMT

A gate electrode is placed between the drain and source regions. When the gate voltage is applied, an electric field is formed, which controls the electrons flowing in the channel. The high electron mobility in the channel results in high current density and high switching speeds.

#### 2.2.1.2 A Vertical GaN HEMT Technology

A vertical GaN HEMT utilizes a vertical current flow path. The device typically consists of a thin layer of GaN semiconductor material grown on a substrate, with a metal contact layer on top of the GaN layer. A gate electrode separated from the GaN layer by a dielectric layer is presented in Fig. 2.2. In a vertical GaN HEMT, the current flows from top to down. The vertical structure of the device provides several

advantages over lateral GaN HEMTs [9]. For example, it allows for a larger active area and lower on-resistance, as the current flows through the entire thickness of the GaN layer.

Fig. 2.2: Schematic of Vertical GaN HEMT

#### 2.2.2 GaN HEMT Technology Based on Mode of Operation

#### 2.2.2.1 Normally-on

A Normally-On GaN HEMT is engineered to remain in the ON state even when no gate bias is applied. This behavior is enabled by a specific structure that includes an AlGaN/GaN heterojunction, as illustrated in Fig. 2.3. The heterojunction is central to the device's functionality [10], as it gives rise to a 2DEG channel at the channel interface. This 2DEG channel enables efficient current conduction. The AlGaN with a wider bandgap than GaN serves as a barrier that confines electrons within the 2DEG and prevents their diffusion into the depletion region. As a result, the device conducts without needing an external gate voltage. Normally-On GaN HEMTs exhibit key performance benefits, including low on-resistance, high drain current capability, fast switching, and high breakdown voltage. These advantages make them suitable for power electronics applications where default conduction is beneficial, such as in power supplies, inverters, and motor control systems.

#### 2.2.2.2 Normally-off

A normally-off GaN HEMT is specifically designed to remain in the OFF state when no gate bias is applied. These transistors are known for their higher breakdown voltage, lower leakage current, and rapid switching capabilities, making them ideal for applications in power electronics where default-off behavior is preferred. Various techniques have been developed to achieve normally-off behavior in GaN HEMTs [11], [12], including (a) the cascode configuration, (b) employing thin or ultra-thin barrier layers combined with fluorine ion implantation, (c) utilizing a p-GaN gate structure (as illustrated in Fig. 2.4), and (d) implementing a recessed gate design.

Fig. 2.3: Schematic of Depletion mode GaN HEMT

In the cascode approach, a series connection of transistors is used, where one device modulates the gate voltage of the other. Typically, a normally-on GaN HEMT operates in saturation with increased drain-source and gate-source voltages, which in turn controls the switching behavior of an additional MOSFET in the configuration. This setup effectively enables normally-off functionality.

Another method involves fluorine implantation in conjunction with thin or ultra-thin barrier layers. This technique introduces fluorine atoms at the gate-channel interface, which lowers the barrier height and decreases the electron concentration in the channel. As a result, the device becomes easier to turn off, achieving the desired normally-off operation. In a GaN HEMT featuring a p-GaN gate, the gate region is doped with acceptor elements such as magnesium (Mg), creating a depletion zone at

the gate-channel interface. This depletion region modulates the 2DEG, enabling effective control of the channel current. In contrast, a GaN HEMT incorporating a recessed gate involves etching the gate electrode into the device surface, forming a trench within the GaN layer. This recessed structure reduces the gate length and increases the electric field across the gate, leading to improved switching speed and enhanced breakdown voltage.

Fig. 2.4: Schematic of Enhancement mode GaN HEMT

## 2.3 Working Principle of GaN HEMT

#### 2.3.1 Wide Bandgap Compound Semiconductor: GaN

Due to the limitations in performance of silicon-based devices and the increasing demand for advanced capabilities, alternative semiconductor materials are being explored for next-generation electronics. WBG semiconductors such as GaN, SiC and β-Ga<sub>2</sub>O<sub>3</sub>, have emerged as strong candidates due to their outstanding electrical characteristics [1]–[4]. Unlike silicon, which has a relatively narrow bandgap, WBG materials provide improved performance, including higher breakdown voltage, greater efficiency, enhanced reliability, and better thermal management. GaN, for example, has a bandgap two to four times greater than silicon, resulting in transistors with reduced leakage currents and increased stability under elevated temperatures.

Additionally, WBG materials exhibit superior thermal conductivity, reduced power dissipation, and substrate leakage, which make them advantageous for applications like high-power amplifiers [5], [6].

### 2.3.2 Crystal Structure and Polarization of GaN

GaN is a wide-bandgap semiconductor crystallizing in the hexagonal wurtzite form. Its lattice comprises two interleaved face-centered hexagonal sublattices stacked vertically to produce the three-dimensional crystal [7]. The wurtzite unit cell consists of two overlapping tetrahedra, each containing four gallium and four nitrogen atoms. Due to the asymmetric atomic arrangement, the wurtzite lattice exhibits polarity along the axis perpendicular to the hexagonal planes, commonly referred to as the caxis. This intrinsic polarization arises from the electronegativity difference between Ga and N atoms, yielding a dipole moment along the c-axis.

The operation of a GaN HEMT relies fundamentally on the GaN/AlGaN heterojunction and the polarization phenomena present at that interface. These piezoelectric and spontaneous polarization effects are pivotal for forming the 2DEG, which underpins the device's superior electron mobility and overall performance. In a standard GaN HEMT architecture, the epitaxial growth of AlGaN atop GaN, establishing a heterointerface. Due to the different lattice constants and material properties of GaN and AlGaN, large polarization fields develop at this junction.

Two distinct polarization contributions govern the heterojunction behavior: piezoelectric polarization and spontaneous polarization. Spontaneous polarization is inherent to materials lacking centrosymmetry—such as GaN and AlGaN—and manifests as a built-in dipole moment even in the absence of external stress. While both layers possess this intrinsic polarization, it is generally more pronounced in AlGaN due to its higher aluminum fraction. Piezoelectric polarization emerges when the AlGaN layer is strained by the mismatched lattice of the GaN. Depending on the Al composition, the AlGaN film experiences either tensile or compressive strain when grown on GaN, inducing an additional polarization component. The superposition of spontaneous and piezoelectric polarizations generates a strong

electric field at the heterointerface. This field causes band bending, forming a quantum well where electrons from the AlGaN layer are drawn into and confined, giving rise to the 2DEG. Because these electrons reside in a potential well spatially separated from ionized donors, scattering is reduced, enabling exceptionally high mobility [8].

## 2.3.3 The Formation and Calculation of the 2DEG Density

#### 2.3.3.1 Formation of the 2DEG in AlGaN/GaN heterostructure

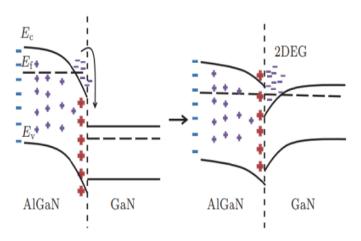

The AlGaN layer induces polarization charges, resulting in positive charges at the AlGaN/GaN interface and negative charges on the AlGaN surface. This polarization creates an internal electric field within the AlGaN layer, which in turn affects the energy band profile and shifts the Fermi level toward the AlGaN/GaN interface. This effect is similar to applying an external voltage across a thin, isolated AlGaN layer, resembling a planar capacitor with the AlGaN acting as the dielectric, as illustrated in Fig. 2.5. The electric field present in the AlGaN layer, along with its n-type doping, causes conduction electrons to move toward the positively charged region, resulting in electron accumulation. This accumulation generates positive space charges within the AlGaN, leading to band bending. As this process continues, the Fermi level eventually reaches a stable, flat state. The inherent electric field in the AlGaN is neutralized by the opposing built-in field, which flattens the previously tilted energy band. Since GaN has a lower Fermi level compared to AlGaN (as shown on the left side of Fig. 2.6), electrons flow from the AlGaN into the GaN when the two materials are brought into contact, forming a two-dimensional electron gas (2DEG). This electron transfer proceeds until the Fermi levels in both AlGaN and GaN align, achieving equilibrium, as illustrated on the right side of Fig. 2.6 [9].

### 2.3.3.2 Calculation of the 2DEG density in AlGaN/GaN heterostructure

Figure 2.7 depicts the charge distribution in an AlGaN/GaN heterostructure, revealing the formation of three distinct dipoles. The first dipole,  $\pm \sigma_{AlGaN}$ , results from polarization charges within the AlGaN layer, while the second,  $\pm \sigma_{GaN}$ , is due to

polarization effects in the GaN layer. The third dipole, linked to the two-dimensional electron gas (2DEG), corresponds to the ionized surface charge  $\pm \sigma_S$ . These dipoles are modeled as planar plate capacitors labeled  $C_1$ ,  $C_2$ , and  $C_3$ . Although these capacitors do not influence electrons beyond their internal boundaries, they sustain a finite electric field between their parallel plates. The magnitude of this electric field is determined by the equation  $E = \sigma/\epsilon$ , where  $\sigma$  is the surface charge density on the opposing plates and  $\epsilon$  is the dielectric constant of the material separating them. In areas where multiple pairs of charged planes overlap, the resulting electric field is determined by the algebraic sum of their charges. As a result, the electric field intensity within the AlGaN layer is influenced by the contributions of charges from  $C_1$  and  $C_2$ , which correspond to the polarization-induced charges in the AlGaN layer and the charge associated with the 2DEG, respectively.

$$\frac{\Delta V_{AIGAN}}{d} = \frac{\sigma_{AIGAN}}{\epsilon} - \frac{qn_s}{\epsilon}$$

$$E_c$$

$$E_t$$

$$E_v$$

$$(2.1)$$

Fig. 2.5: Considering an n-doped AlGaN film freestanding but strained equivalently to an AlGaN/GaN heterostructure, the polarization field causes electrons to traverse from one side to the other. Consequently, the energy bands bend and fixed positive charges accumulate in the AlGaN layer [9].

where  $\Delta V_{AlGaN}$  is the potential drop across the conductive band of the AlGaN surface and the AlGaN/GaN interface as shown in Fig. 2.8, d is the thickness of the AlGaN

layer,  $\sigma_{AlGaN}$  is the sheet charge density that is induced by AlGaN polarization,  $n_s$  is the sheet density of 2DEG, q is the electron charge, and  $\epsilon$  is the dielectric constant of AlGaN. The potential drop  $\Delta V_{AlGaN}$  can be expressed as

$$q\Delta V_{AlGaN} = q\mathbb{Z}_b + E_f - \Delta E_C \tag{2.2}$$

Fig. 2.6: Energy-band diagram of an n-doped AlGaN/GaN heterostructure. Upon contact, electrons transfer into the GaN side, accumulate at the interface, and form a 2DEG [9].

Fig. 2.7: Charge distribution profile of an AlGaN/GaN heterostructure [9].

where  $\mathbb{Z}_b$  is the surface barrier height,  $E_f$  is the Fermi level position with respect to the GaN conduction-band edge at the AlGaN/GaN interface, and  $\Delta E_C$  is the conduction band discontinuity between GaN and AlGaN as shown in Fig. 2.8. Therefore, based on Eqs. (2.1) and (2.2), the sheet density of 2DEG can be expressed as [9].

$$n_{s} = \frac{\sigma_{AlGaN}}{q} - \left(\frac{\epsilon}{q^{2}d}\right) \left(q \, \Box_{b} + E_{f} - \Delta E_{C}\right)$$

$$q \Delta V_{AlGaN}$$

$$\Delta E_{c}$$

$$(2.3)$$

GaN

Fig. 2.8: Conductive band diagram of an AlGaN/GaN heterostructure [9].

# 2.4 Early Advancements in GaN HEMT Technology

The emergence of GaN HEMT technology in the early 1990s marked a revolutionary step forward in semiconductor advancements. In 1993, M. Asif Khan and his team introduced the n-GaN/AlGaN heterojunction HEMT, showcasing remarkable characteristics such as a 28 mS/mm transconductance at 300 K and 46 mS/mm at 77 K [10]. In 1994, they presented a GaN HFET with a 0.25  $\mu$ m gate length, achieving a cut-off frequency of 11 GHz and an oscillation frequency of 35 GHz. The exceptionally high fmax was attributed to the low parasitic output conductance in the saturation regime, establishing its suitability for millimeter-wave and microwave applications [11]. In 1996, Y.F. Wu et al. developed GaN HFETs and MODFETs, achieving significant channel current densities and high power outputs. The

MODFET demonstrated a channel current density exceeding 300 mA/mm and exhibited excellent large voltage I-V characteristics up to  $V_{ds}$  = 60V, enabling a FWS class A amplifier power output exceeding 2 W/mm [12]. Further progress was made in 1999 when Lester F. Eastman demonstrated enhanced GaN HFETs grown on ptype SiC substrates, which outperformed sapphire substrates [13]. His work achieved a power-added efficiency of 78% on SiC compared to 50% on sapphire.

In 2001, Karmalkar and colleagues proposed a systematic approach for optimizing field plate device designs to enhance performance while minimizing the impact on on-resistance and frequency response. They identified increasing the insulator's dielectric constant beneath the field plate as a promising technique to enhance device performance [14]. Saito et al., in 2006, introduced a recessed gate structure for GaN HEMTs, allowing for gate threshold voltage adjustment without increasing on-resistance. This was accomplished by the selective reduction of the 2DEG density under the gate [15]. Two years later, Wong et al. demonstrated an N-face MIS-HEMT with excellent DC and RF characteristics at specific optical gate lengths. Using AlN for electron confinement eliminated alloy scattering and provided a robust back-barrier mechanism, addressing short-channel effects in highly scaled sub-micrometer devices [16].

In 2011, Hilton et al. reported normally-off GaN HEMT tailored for power electronics application by employing p-GaN gate alongside a GaN buffer doped with carbon. The addition of an AlGaN back-barrier in conjunction with the buffer effectively suppressed early off-state punch-through, yielding low  $R_{ON}$  and a robust  $V_{th}$  of 1.1 V for dependable switching. These devices demonstrated a breakdown capability of 1000 V with a gate drain spacing of 6  $\mu$ m [17]. Such achievements represented pivotal steps in advancing GaN HEMT technology and catalyzed further R&D efforts to push its performance limits.

## 2.5 GaN HEMTs for High-Power Applications

Recent developments on GaN HEMTs highlight their strong potential for high-power applications, driven by GaN's superior material properties like wide bandgap, high

breakdown field, and thermal stability. Research increasingly aims at device innovations that enhance power density, efficiency, and reliability, critical for high-power performance in challenging environments. Key developments include p-GaN gate engineering, GaN MIS-HEMTs, field-plated GaN HEMTs, Fluorine implanted GaN HEMTs, and gate-recessed GaN HEMTs to mitigate issues such as premature device failure in power electronics applications.

## 2.5.1 p-GaN HEMTs

The p-GaN HEMT has emerged as a promising device for power electronics applications, leveraging GaN's inherent qualities such as its wide bandgap, high electron mobility, and robust breakdown characteristics. Unlike conventional GaN HEMTs, p-GaN HEMTs employ a p-GaN layer under the gate to deplete the underlying 2DEG at the zero gate voltage. This configuration allows for normally-off behavior, a desirable feature in power electronics for safety and energy efficiency.

#### 2.5.1.1 Gate Engineered p-GaN HEMTs

Recent advancements in gate engineering have significantly enhanced the performance of p-GaN HEMTs by modifying the gate region to improve the control over the 2DEG density and reduce gate leakage currents. Techniques such as incorporating dielectric layers, varying gate lengths, and adjusting the p-GaN cap layer thickness have been explored to improve device reliability, minimize power losses, and ensure stability under high-stress conditions. For instance, the integration of fluorinated and intrinsic graphene as gate insertion layer in p-GaN HEMT has demonstrated improvements in device performance, including better ON/OFF current ratios, increased threshold voltage, and reduced gate leakage, while also enhancing thermal stability due to an improved Schottky barrier height and interface quality [18]. Similarly, the use of indium—tin—oxide gate electrodes in p-GaN HEMT has shown superior gate stability under forward bias, coupled with improvements in current handling and transconductance compared to conventional Schottky gate materials [19]. To address surface damage caused by selective etching, the introduction of a p-AlGaN layer between the p-GaN and AlGaN layers has proven

effective in minimizing plasma damage through low-damage etching processes, resulting in enhanced threshold voltage stability and reduced ON-resistance [20]. Additionally, the adoption of a fin-gate structure with tri-gates and fin trenches extending into the gate-to-drain region has significantly improved on-state resistance, saturation current, and threshold voltage stability by effectively managing carrier traps [21]. These advancements in gate engineering techniques highlight their potential in overcoming challenges such as gate leakage suppression, surface damage reduction, and threshold voltage stability.

## 2.5.1.2 Buffer Engineered p-GaN HEMTs