# REALISATION OF SIMULATED IMMITTANCES USING MODERN ACTIVE BUILDING BLOCKS

A Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of

### DOCTOR OF PHILOSOPHY

in

Department of Electrical Engineering

by

Meghana Shrivastava

(Roll No. 2K21/PHDEE/15)

Under the Supervision of

Prof. Pragati Kumar & Prof. Data Ram Bhaskar

Department of Electrical Engineering

Department of Electrical Engineering

Delhi Technological University, Delhi-110042, India

December, 2025

#### ACKNOWLEDGEMENTS

First and foremost, I sincerely acknowledge my most sincere gratitude to my supervisors Prof. Pragati Kumar and Prof. Data Ram Bhaskar for their valuable guidance, support, and motivation throughout this research work. They have been outstanding mentors and working with them has been a remarkable experience. The valuable hours of discussion that I had with them undoubtedly helped in supplementing my thoughts in the right direction for attaining the desired objectives. I consider it my proud privilege to have worked with them, ever ready to lend a helping hand. I am forever thankful to them for all their wise words and inspiring thoughts.

I am also thankful to my Head of Department Prof. Rachana Garg for her moral support in completion of this thesis and also, I am thankful to Prof. Ram Bhagat and Dr. Garima Mann, Department of Electrical Engineering, Delhi Technological University, Delhi, for rendering valuable help throughout the present work.

I would like to express my heartfelt gratitude to Dr. Ajishek Raj for their invaluable guidance and support throughout my work. I truly appreciate the time and effort you dedicated to helping me, and I am thankful for your constant motivation and willingness to share your knowledge.

I would like to extend my deepest thanks to my best friend and roommate, Rahma Aman, for being my constant source of support, laughter, and strength throughout this journey. Your companionship has made even the most stressful days manageable and your unwavering encouragement has meant the world to me. Thank you for always being there not just as a friend, but as family.

I am sincerely grateful to my friends and colleagues especially, Sakshi Gupta, Kirti Kaharwar, Sudeep Sharan, Deepak Kumar, Vivek Kumar, Devanshu Saxena, Suwaiba Mateen, Qayam Uddin, Gopal Singh and Amitabh Srivastava for their constant motivation and for reminding me to complete my work at the earliest. The assistance of the valuable staff in the Linear Integrated Circuit Lab of Delhi Technological

University is gratefully acknowledged. I am especially thankful to Mr. Jagvir Singh, and Mr. Abhishek for their substantial assistance during my research.

I want to take this opportunity to thank my parents, from the bottom of my heart for everything that they have done and continues to do for me. They never lost their faith in me and sacrificed a great lot in their life to help me come this far. I also want to thank my brothers Shashank Khare, Shivank Khare and Nitin Srivastava for being a constant source of support. I am wholly indebted to ALMIGHTY who is omnipotent and superpower of the universe.

(Meghana Shrivastava)

#### CANDIDATE'S DECLARATION

I Meghana Shrivastava hereby certify that the work which is being presented in the thesis entitled "Realisation of Simulated Immittances Using Modern Active Building Blocks" in partial fulfillment of the requirements for the award of the Degree of Doctor of Philosophy, submitted in the Department of Electrical Engineering, Delhi Technological University is an authentic record of my own work carried out during the period from 1.08.2021 to 31.07.2025 under supervision of Prof. Pragati Kumar and Prof. Data Ram Bhaskar. The matter presented in the thesis has not been submitted by me for the award of any other degree of this or any other Institute.

(Meghana Shrivastava)

This is to certify that the student has incorporated all the corrections suggested by the examiners in the thesis and that the statement made by the candidate is correct to the best of our knowledge.

Signature of Supervisor(s)

Signature of External Examiner

### CERTIFICATE BY THE SUPERVISOR(s)

This is to certify that the thesis entitled Realisation of Simulated Immittances Using Modern Active Building Blocks submitted by Ms. Meghana Shrivastava (2K21/PHDEE/15) for the award of degree of Doctor of Philosophy in the Department of Electrical Engineering, Delhi Technological University, Delhi, is the record of students own work carried out by her under our supervision. The contents of this research work have not been submitted in part or fully to any other institute or university for the award of any degree.

Prof. Pragati Kumar

Department of Electrical Engineering, Delhi Technological University Prof. Data Ram Bhaskar

Department of Electrical Engineering, Delhi Technological University

#### ABSTRACT

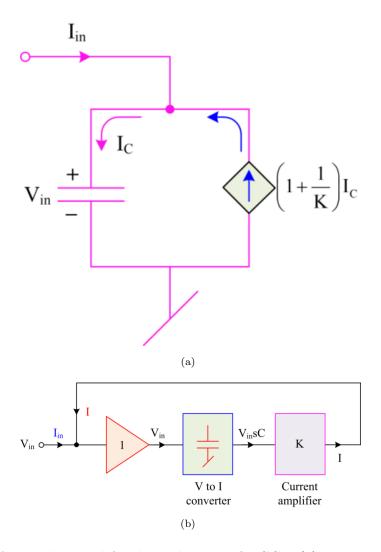

The simulation of passive components, including resistors, capacitors, and inductors, is essential in the design of compact and adjustable analog signal processing/generation circuit applications. Conventional passive components frequently need substantial chip area and lack electronic tunability, make them less appropriate for integrated circuit (IC) applications. This work addresses these limitations by implementing simulated immittances employing active building blocks (ABBs), specifically the Current Feedback Operational Amplifier (CFOA), Current Follower Differential Input Transconductance Amplifier (CFDITA), and Second Generation Voltage Conveyor (VCII). These ABBs provide benefits including low-voltage functionality, good linearity, electronic tunability, and straightforward integration. Various immittance simulator circuits, both grounded and floating, are developed and validated by simulation utilizing macro model and CMOS technology. These circuits are utilized in analog filters, oscillators, impedance matching networks, sensors, biomedical circuits, and signal production systems. The proposed circuits are validated using simulation tools like PSpice and Cadence Virtuoso utilizing 180nm CMOS technology. Practical results are also obtained to verify the performance of the circuits and to confirm their feasibility for hardware implementation. The proposed designs exhibit enhanced performance regarding compactness, power efficiency, and frequency response, making them suitable for application in analog integrated circuits.

# Contents

| A            | BST   | RACT   |            |                                                       |      | vii       |

|--------------|-------|--------|------------|-------------------------------------------------------|------|-----------|

| L            | IST ( | OF TA  | BLES       |                                                       |      | X         |

| L            | IST ( | OF FIG | GURES      |                                                       | X    | xiii      |

| $\mathbf{L}$ | IST ( | OF SY  | MBOLS      |                                                       | X    | xiv       |

| $\mathbf{L}$ | IST ( | OF AB  | BREVI      | ATIONS                                                | X    | xvi       |

| 1            | Intr  | oduct  | ion        |                                                       |      | 1         |

|              |       | 1.0.1  | Current    | feedback operational amplifiers                       |      | 4         |

|              |       | 1.0.2  | Current    | follower differential input transconductance amplifie | er   |           |

|              |       |        | (CFDIT     | TA)                                                   |      | 10        |

|              |       |        | 1.0.2.1    | Advantages of CFDITA Over Other Modern ABBs           |      | 11        |

|              |       |        | 1.0.2.2    | CMOS Realization of CFDITA                            |      | 12        |

|              |       | 1.0.3  | Second     | generation voltage conveyor (VCII)                    |      | 14        |

|              |       |        | 1.0.3.1    | CMOS implementation of VCII $\pm$                     |      | 16        |

|              | 1.1   | Resea  | rch Objec  | etives                                                |      | 22        |

|              | 1.2   | Orga   | nisation o | of Thesis                                             |      | 24        |

| 2            |       |        |            | el Realisation of Capacitance Multiplier and Flo      | oat- |           |

|              |       |        | tance C    |                                                       |      | <b>26</b> |

|              | 2.1   |        |            |                                                       |      | 26        |

|              | 2.2   |        | _          | Negative Grounded Capacitance Multiplier Circuits     |      | 30        |

|              |       | 2.2.1  |            | al Analysis                                           |      | 33        |

|              |       | 2.2.2  |            | tion results                                          |      | 34        |

|              |       |        | 2.2.2.1    | Frequency responses                                   |      | 35        |

|              |       |        | 2.2.2.2    | Temperature variation analysis                        |      | 38        |

|              |       |        | 2.2.2.3    | Monte-Carlo simulations                               |      | 38        |

|              |       |        | 2.2.2.4    | Noise and power supply rejection ratio analysis .     |      | 43        |

|              |       | 2.2.3  | Experin    | nental results                                        |      | 44        |

|              | 2.3   | Floati | ng immit   | tance simulator circuits using CFOAs                  |      | 49        |

|   | 2.4  |        |                                                                      | 55  |

|---|------|--------|----------------------------------------------------------------------|-----|

|   |      | 2.4.1  | Non-Idealities of CFOAs on the proposed immittance simulator circuit | 57  |

|   |      | 2.4.2  |                                                                      | 59  |

|   |      |        |                                                                      | 59  |

|   |      |        |                                                                      | 60  |

|   |      |        | 2.4.2.3 First-Order High-pass Filter                                 | 62  |

|   |      |        | 2.4.2.4 Realization of 4th order Butterworth LPF                     | 64  |

|   |      | 2.4.3  | Simulation results                                                   | 65  |

|   |      |        | 2.4.3.1 Results for parallel R-L circuit                             | 66  |

|   |      |        | 2.4.3.2 Results for parallel R-C circuit                             | 68  |

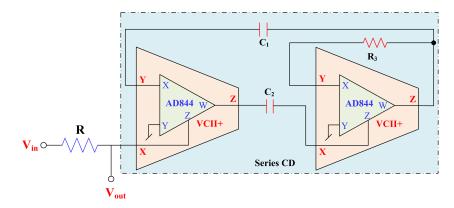

|   |      |        | 2.4.3.3 Results for parallel C-D configuration                       | 70  |

|   |      |        | 2.4.3.4 Results for floating capacitance multiplier circuit          | 72  |

|   |      | 2.4.4  | Experimental Results                                                 | 78  |

|   |      |        | 2.4.4.1 Lag compensator                                              | 80  |

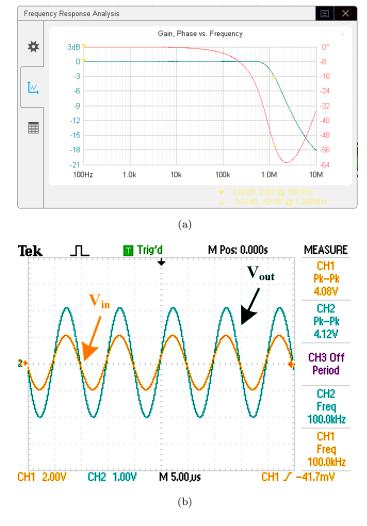

|   |      |        | 2.4.4.2 Lead compensator                                             | 81  |

|   |      |        | 2.4.4.3 First-order high pass filter                                 | 82  |

|   | 2.5  | Floati | ng lossless immittance simulator                                     | 83  |

|   |      | 2.5.1  | Simulation results                                                   | 85  |

|   |      |        | 2.5.1.1 Results for floating inductance simulator                    | 86  |

|   |      |        | 2.5.1.2 Results for capacitance multiplier circuits                  | 88  |

|   |      |        | 2.5.1.3 Results for FFDNR                                            | 93  |

|   | 2.6  | Floati | ng Series immittance simulator                                       | 96  |

|   |      | 2.6.1  | Simulation results                                                   | 98  |

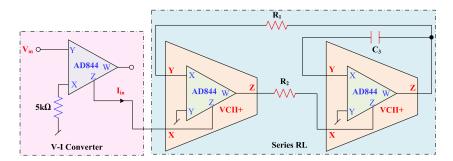

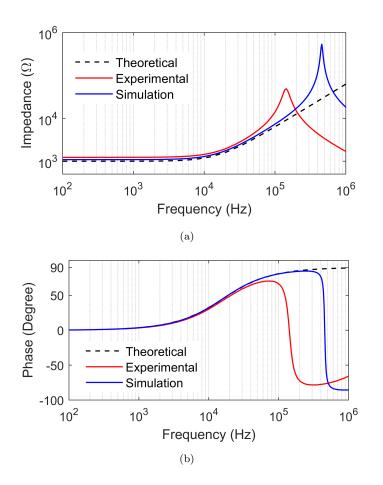

|   |      |        | 2.6.1.1 Results for series R-L circuits                              | 98  |

|   |      |        | 2.6.1.2 Results for series R-C circuit                               | .00 |

|   |      |        | 2.6.1.3 Results for series C-D configurations                        | 02  |

|   |      |        | 2.6.1.4 Results for floating capacitance divider circuit 1           | 04  |

|   | 2.7  | Concl  | iding remarks                                                        | 07  |

| 3 | Sing | gle CF | DITA based Grounded Capacitance Multiplier Circuits 10               | 09  |

|   | 3.1  | Introd | uction                                                               | 09  |

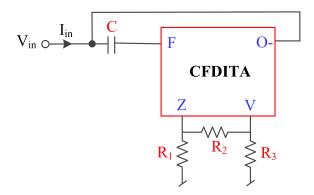

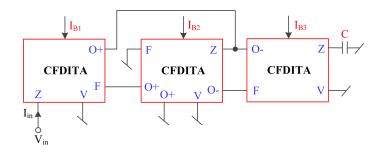

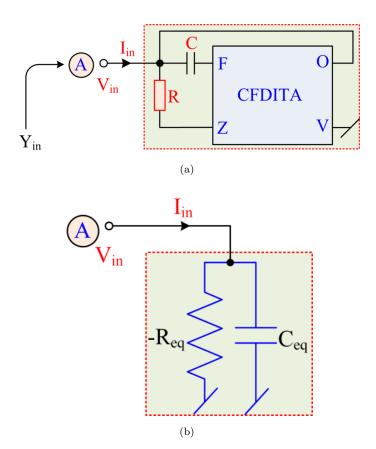

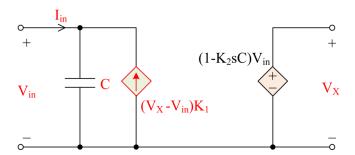

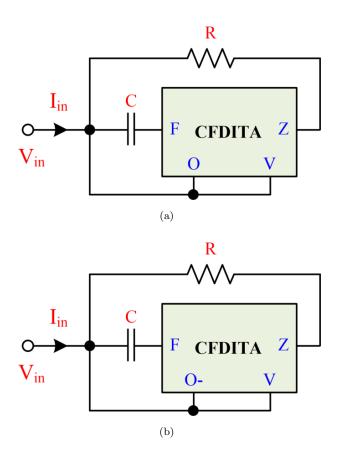

|   |      | 3.1.1  | Lossy capacitance multiplier                                         | 10  |

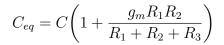

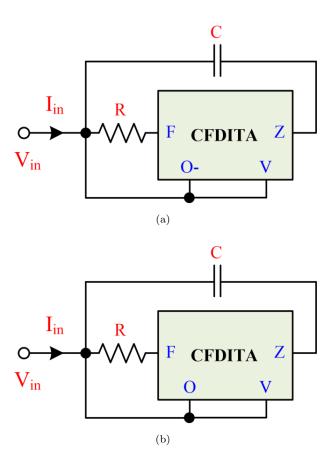

|   |      | 3.1.2  | Lossless capacitance multiplier                                      | 12  |

|   | 3.2  | Groun  | ded Lossy Capacitance Multiplier                                     | 17  |

|   |      | 3.2.1  | Non-ideal Analysis                                                   | 17  |

|   |      | 3.2.2  | SPICE Simulation Results                                             | 20  |

|   |      | 3.2.3  | Layout Simulation Results                                            |     |

|   |      | 3.2.4  | Experimental Results                                                 |     |

|   | 3.3  | Groun  | ded Lossless Capacitance Multiplier Circuit                          |     |

|   |      | 3.3.1  | Non-ideal Analysis                                                   |     |

|   |      | 3.3.2  | Simulation Results                                                   |     |

|   |      | 3.3.3   | Experimental Results                                        | . 140 |

|---|------|---------|-------------------------------------------------------------|-------|

|   |      | 3.3.4   | Application examples                                        |       |

|   | 3.4  | Concl   | uding remarks                                               |       |

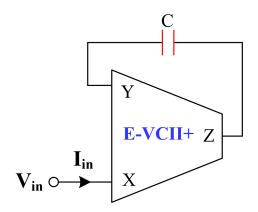

| 4 | VC   | II-base | ed Immittance Simulator Circuits                            | 149   |

|   | 4.1  | Introd  | $\operatorname{luction}$                                    | . 149 |

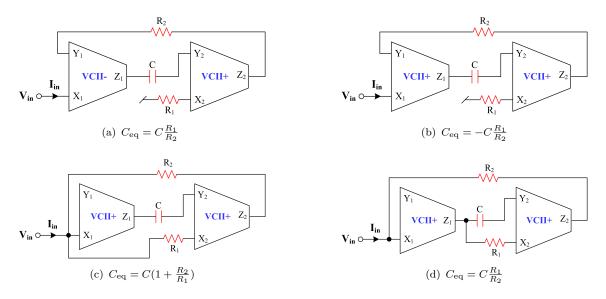

|   | 4.2  | Groun   | nded series type immittance simulators using VCII           | . 155 |

|   |      | 4.2.1   | Non-ideal analysis                                          | . 157 |

|   |      | 4.2.2   | PSPICE simulation results using CMOS VCIIs                  | . 158 |

|   |      |         | 4.2.2.1 Results for Circuit-1                               | . 158 |

|   |      |         | 4.2.2.2 Results for Circuit-2                               | . 165 |

|   |      |         | 4.2.2.3 Results for Circuit-3                               | . 170 |

|   |      |         | 4.2.2.4 Results for Circuit-4                               | . 174 |

|   |      | 4.2.3   | Pre and Post layout simulations                             | . 180 |

|   |      | 4.2.4   | Experimental results                                        |       |

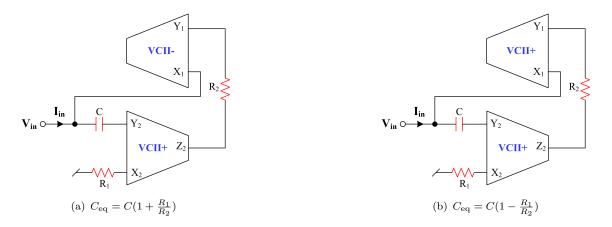

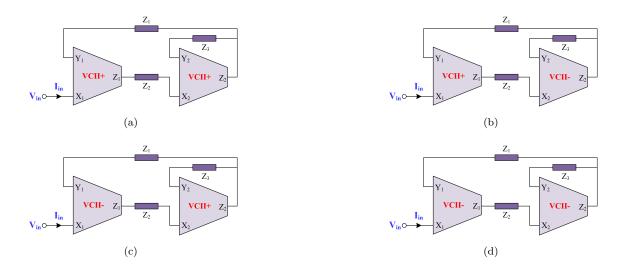

|   | 4.3  | Groun   | nded parallel type immittance simulators using VCII         | . 187 |

|   |      | 4.3.1   | Non-ideal and parasitic analyses                            | . 188 |

|   |      | 4.3.2   | Simulation results using CMOS VCII                          | . 192 |

|   |      |         | 4.3.2.1 Results for Circuit-1                               | . 192 |

|   |      |         | 4.3.2.2 Results for Circuit 2                               | . 199 |

|   |      |         | 4.3.2.3 Results for Circuit-3                               | . 207 |

|   |      |         | 4.3.2.4 Results for Circuit-4                               | . 212 |

|   |      | 4.3.3   | Pre and Post layout simulations                             | . 221 |

|   |      | 4.3.4   | Exemplary application of proposed parallel immittance simu- |       |

|   |      |         | lator circuits                                              |       |

|   |      | 4.3.5   | Experimental results                                        |       |

|   |      | 4.3.6   | Concluding remarks                                          | . 226 |

| 5 | Cor  | ıcludin | ng Remarks and Future Scope of Work                         | 227   |

|   | 5.1  | Concl   | uding Remarks                                               | . 227 |

|   | 5.2  | Future  | e Scope $\dots$                                             | . 229 |

|   | 5.3  | Societ  | al Impact                                                   | 231   |

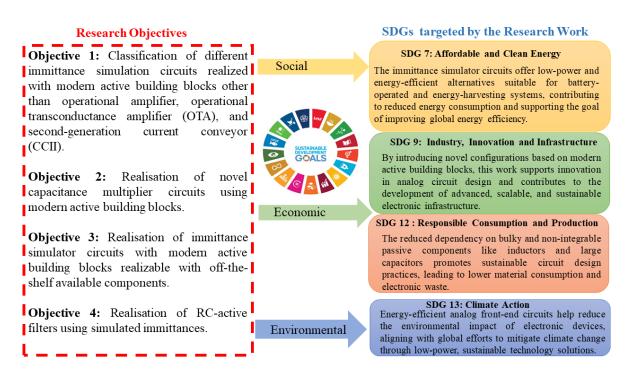

|   |      | 5.3.1   | Linking Research Objectives with SDGs for Societal Impact . | 232   |

|   | Ribl | iograph | nv.                                                         | . 262 |

# List of Tables

|     | Parameters of AD844 [64]                                                            |     |

|-----|-------------------------------------------------------------------------------------|-----|

| 2.1 | Statistical data obtained from Monte-Carlo simulations                              | 43  |

|     | Parasitic resistances and capacitances values of CFDITA                             |     |

|     | Generalized Table for Circuits and Realization Types                                | 156 |

|     | 4.65                                                                                | 188 |

| 4.3 | Transfer functions and cut-off frequencies obtained from the circuits of Fig. 4.133 | 223 |

# List of Figures

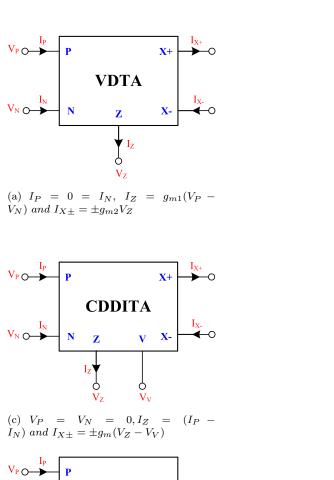

| 1.1  | Functional block diagrams and port characteristics of (a) VDTA [50]        |    |

|------|----------------------------------------------------------------------------|----|

|      | (b) CDTA [51] (c) CDDITA [50] (d) CFTA [52] (e) OTRA [53] (f)              |    |

|      | CDBA [54] (g) FTFN [55] (h) VDBA [50]                                      | 5  |

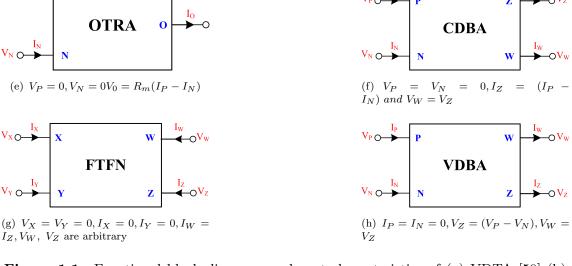

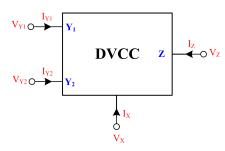

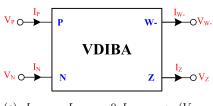

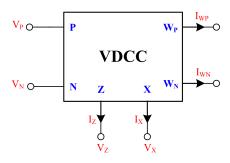

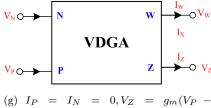

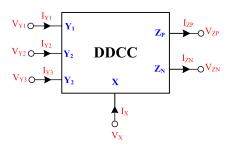

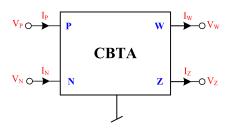

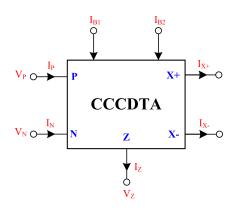

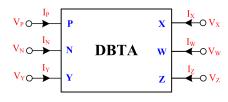

| 1.2  | Functional block diagrams and port characteristics of (a) DVCC [56]        |    |

|      | (b) DDCC [57] (c) VDIBA [58] (d) CBTA [59] (e) VDCC [50] (f)               |    |

|      | CCCDTA [60] (g) VDGA [61] (h) DBTA [62]                                    | 6  |

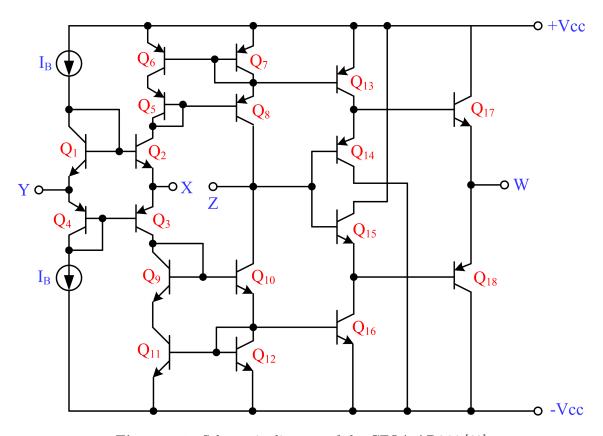

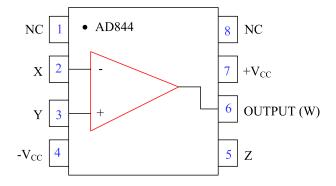

| 1.3  | Schematic diagram of the CFOA AD844 [63]                                   | 7  |

| 1.4  | Pin diagram of AD844 [64]                                                  | 7  |

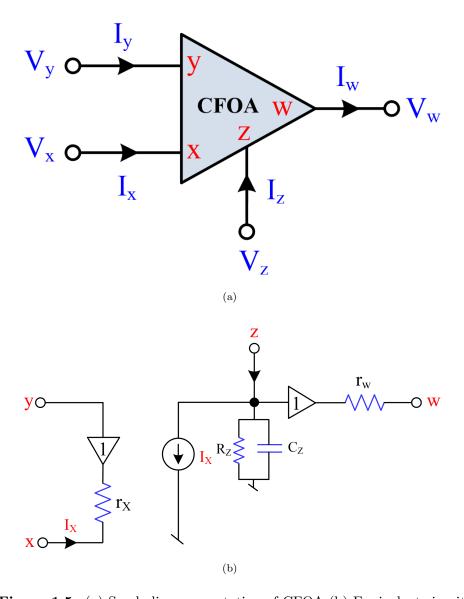

| 1.5  | (a) Symbolic representation of CFOA (b) Equivalent circuit                 | 9  |

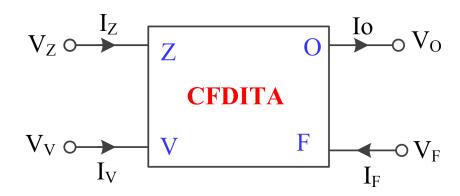

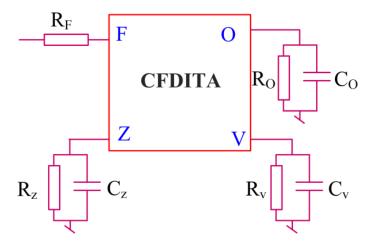

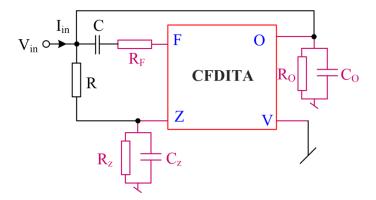

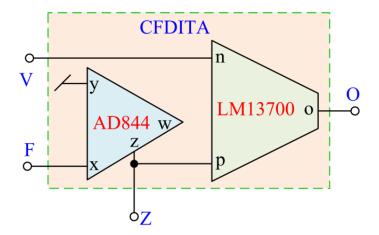

| 1.6  | Symbol of CFDITA                                                           | 11 |

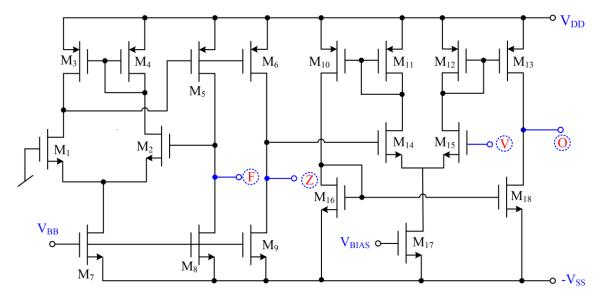

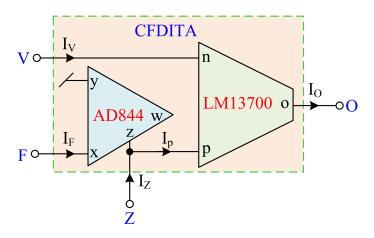

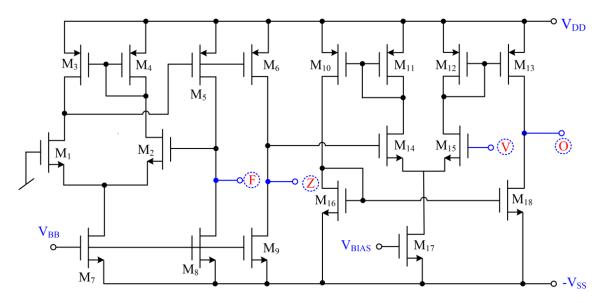

| 1.7  | Proposed CMOS implementation of CFDITA                                     | 13 |

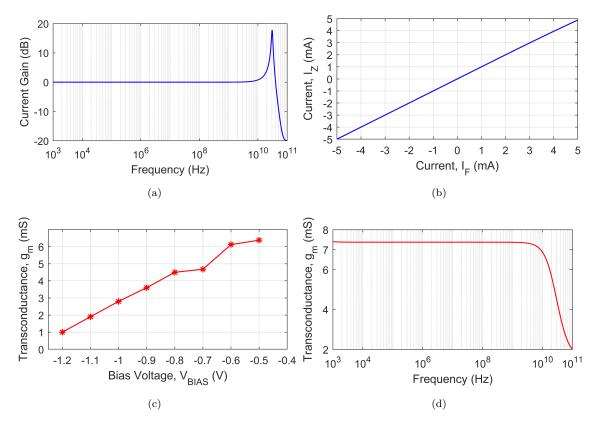

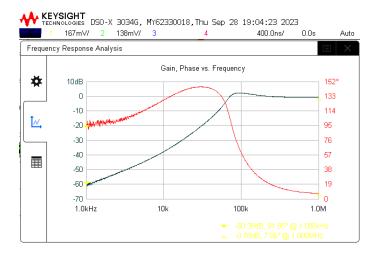

| 1.8  | (a)Frequency response of current gain (b) DC current transfer char-        |    |

|      | acteristic (c) Variation of transconductance with $V_{BIAS}$ (d) Variation |    |

|      | of transconductance with frequency                                         | 15 |

| 1.9  | Implementation of CFDITA using commercially available ICs                  | 15 |

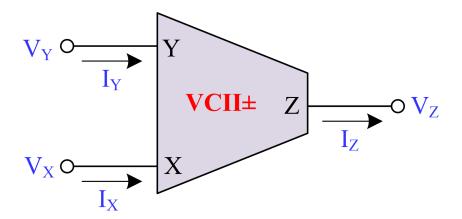

| 1.10 | Symbol of VCII                                                             | 16 |

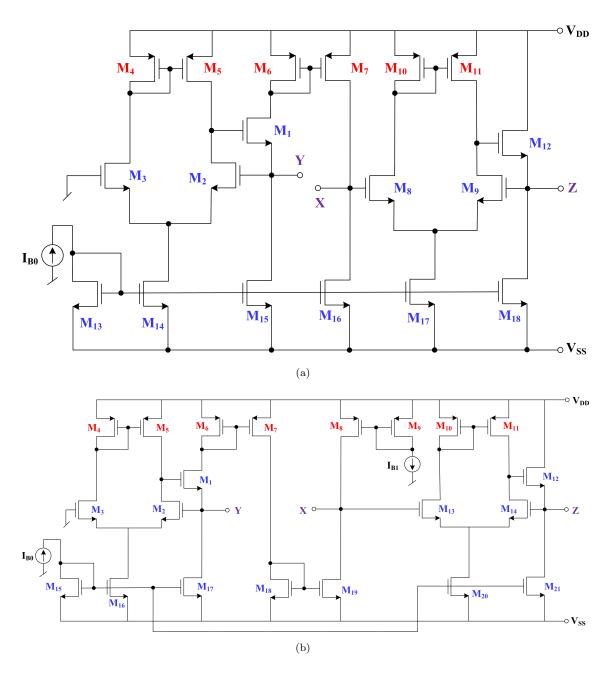

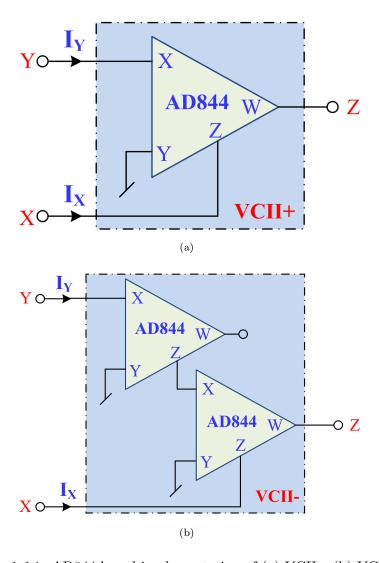

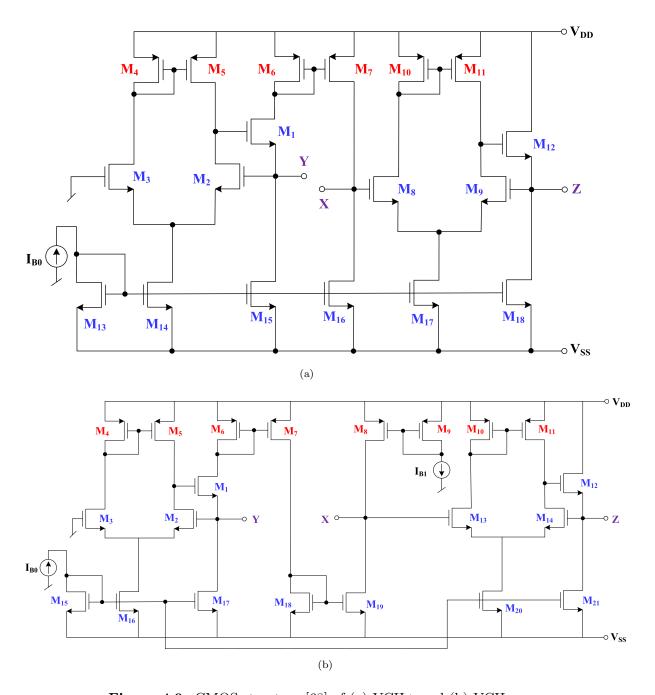

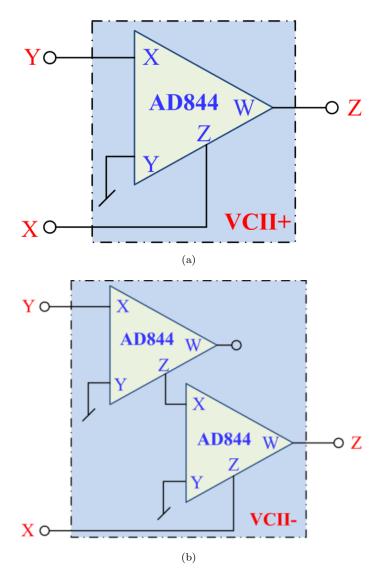

| 1.11 | CMOS structure [68] of (a) VCII+ and (b) VCII                              | 18 |

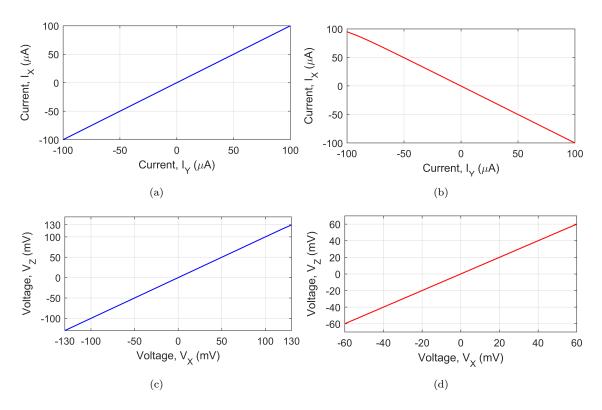

| 1.12 | (a) DC current transfer characteristic of VCII+ (b) DC current trans-      |    |

|      | fer characteristic of VCII- (c) DC voltage transfer characteristic of      |    |

|      | VCII+ (d) DC voltage transfer characteristic of VCII                       | 19 |

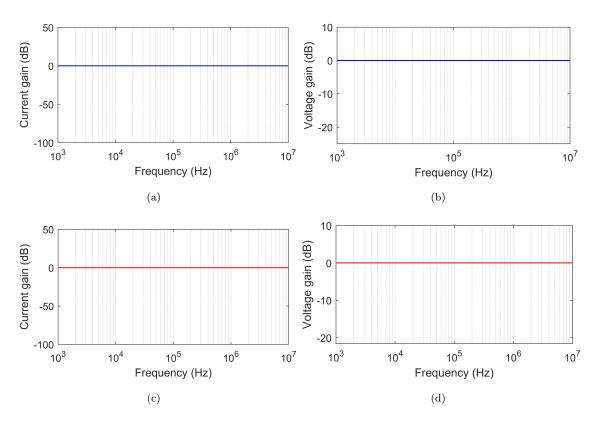

| 1.13 | (a) Frequency response of current gain of VCII+ (b) Frequency re-          |    |

|      | sponse of voltage gain of VCII+ (c) Frequency response of current          |    |

|      | gain of VCII- (d) Frequency response of voltage gain of VCII               | 20 |

| 1.14 | AD844-based implementation of (a) VCII+ (b) VCII- [68]                     | 21 |

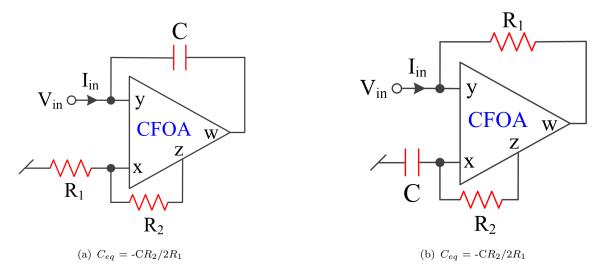

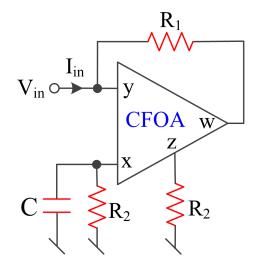

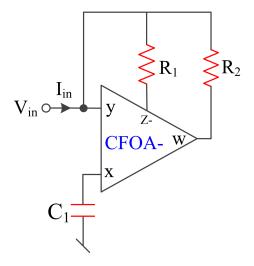

| 2.1  | Negative grounded capacitance multiplier circuits reported in [131]        | 28 |

| 2.2  | Negative capacitance multiplier circuit proposed in [132], $C_{eq} = -$    |    |

|      | $CR_2/R_1$                                                                 | 28 |

| 2.3  | Grounded capacitance multiplier circuit proposed in [133], $C_{eq} =$      |    |

|      | $C_1(1+R_2/R_1)$                                                           | 29 |

| 2.4  | Grounded capacitance multiplier proposed in [136]                          | 29 |

| 2.5  | Proposed negative grounded capacitance multiplier circuits employing       | -0 |

|      | grounded capacitor                                                         | 31 |

| 2.6  | Approaches used for the realization of NGCM (a) current mode ap-                                                                       |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | proach [164] (b) voltage mode approach [165]                                                                                           | 32  |

| 2.7  | Complete proposed NGCMs with parasitic elements of CFOA                                                                                | 34  |

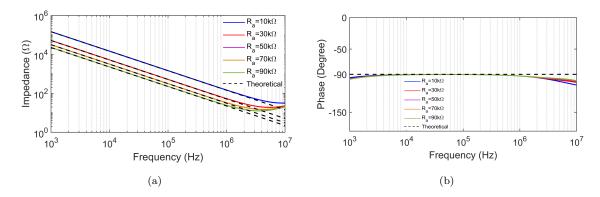

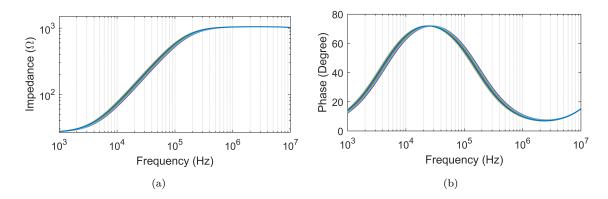

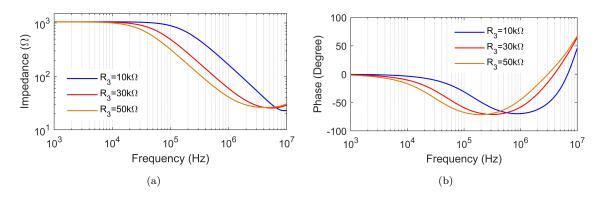

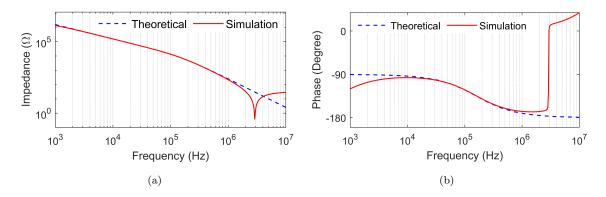

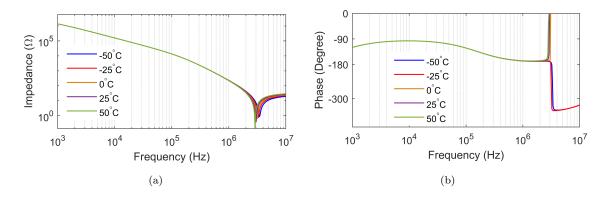

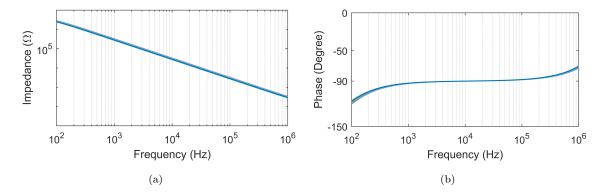

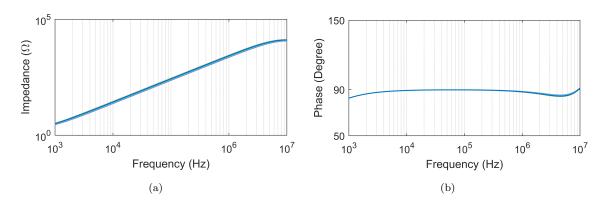

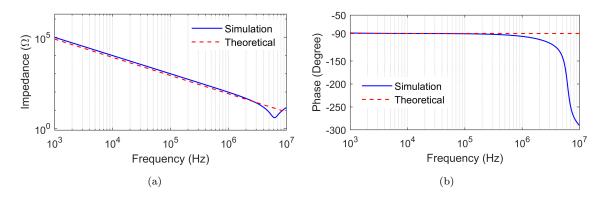

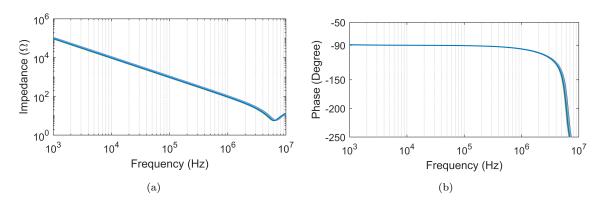

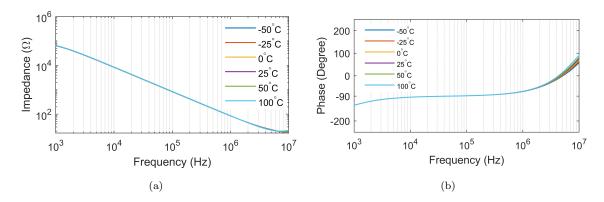

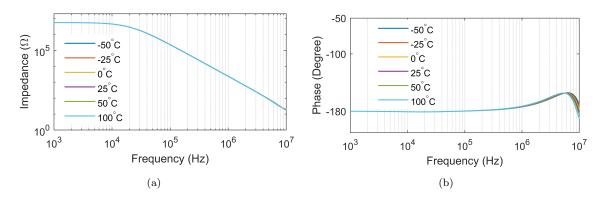

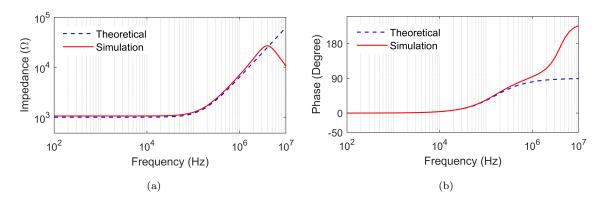

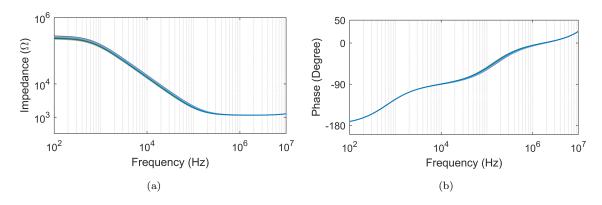

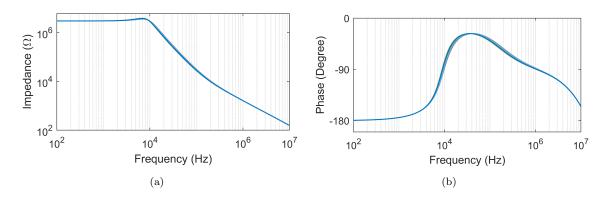

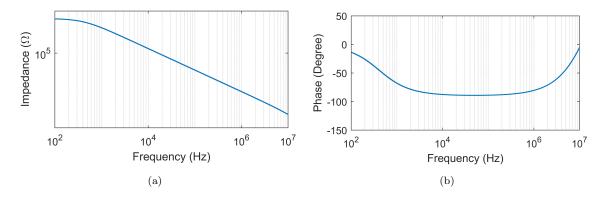

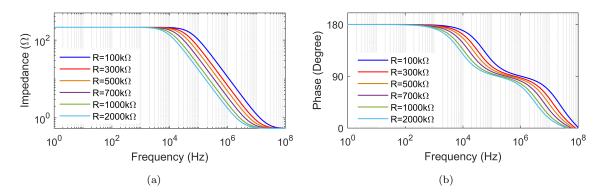

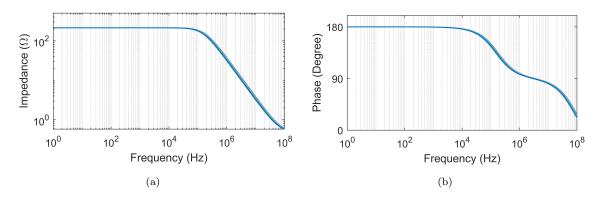

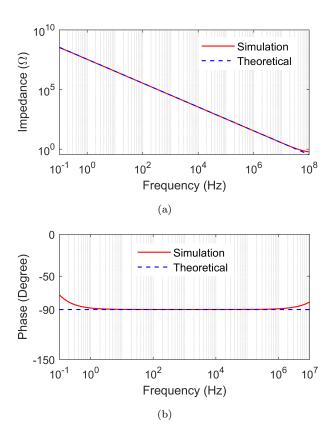

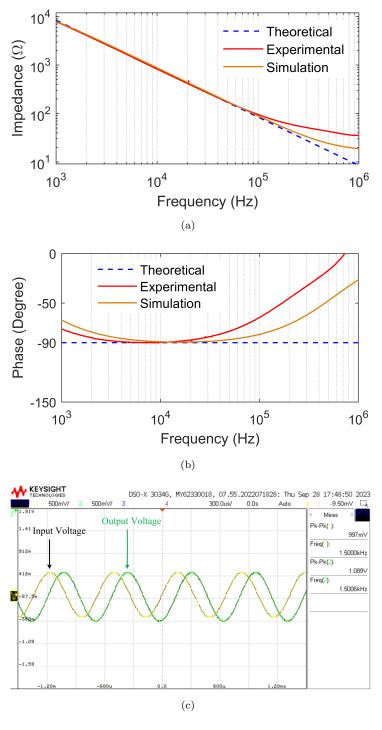

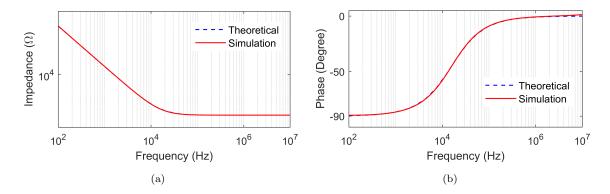

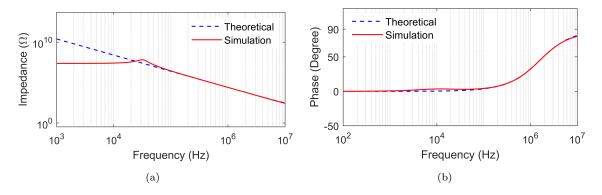

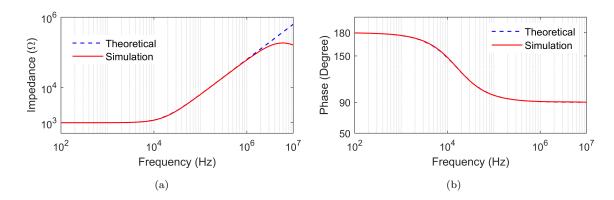

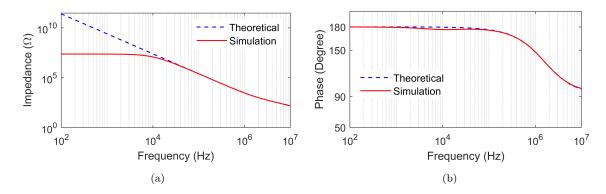

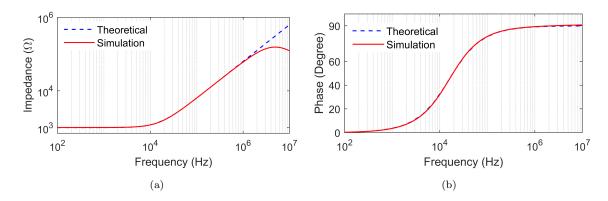

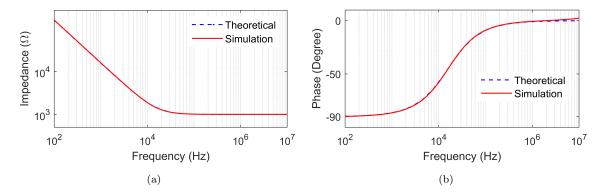

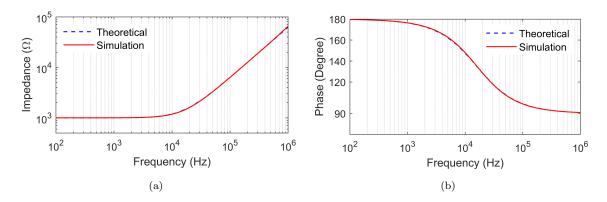

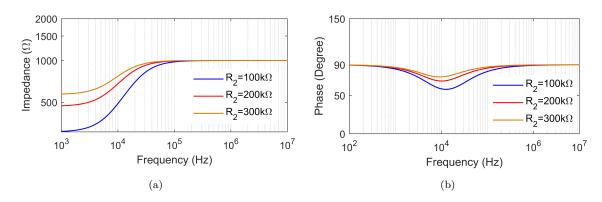

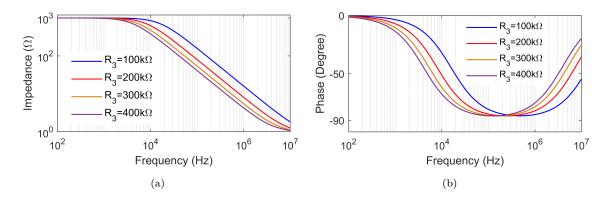

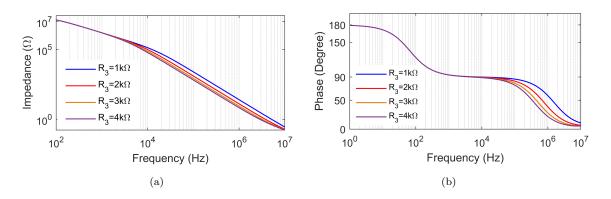

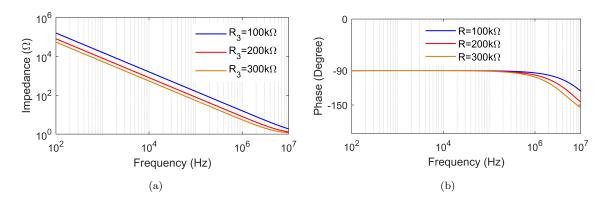

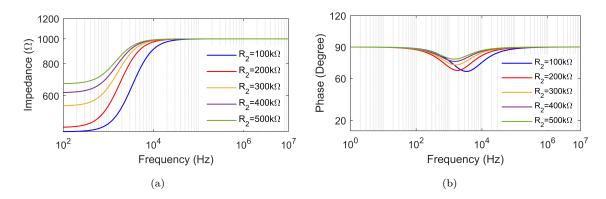

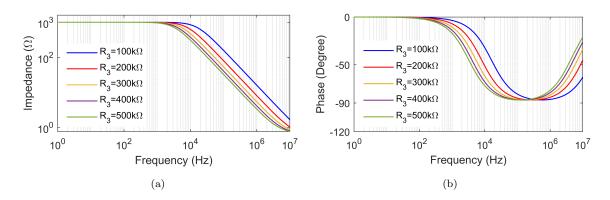

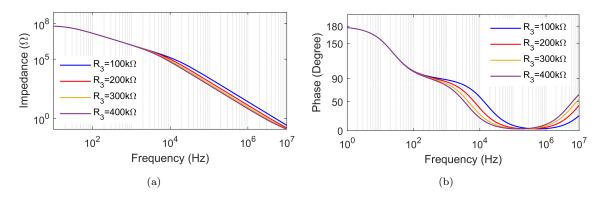

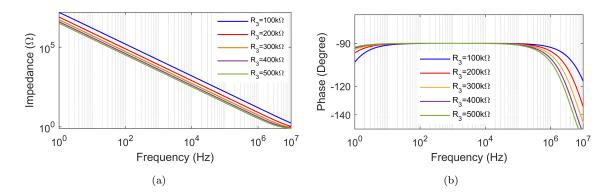

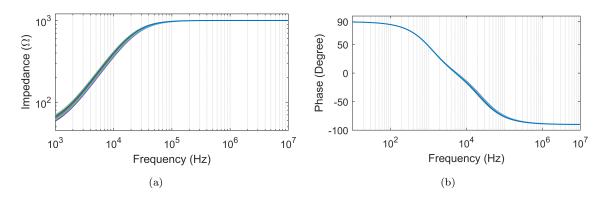

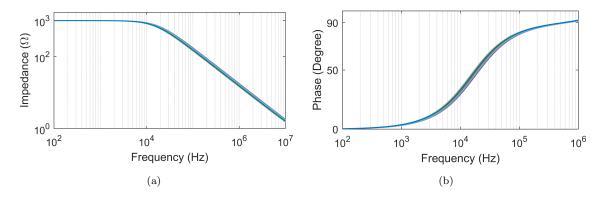

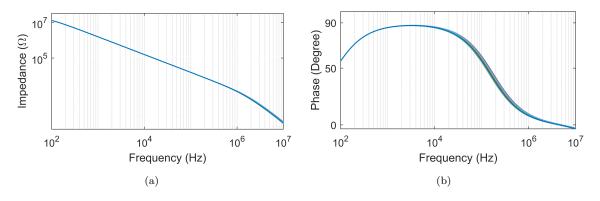

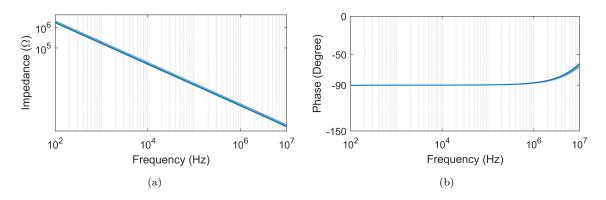

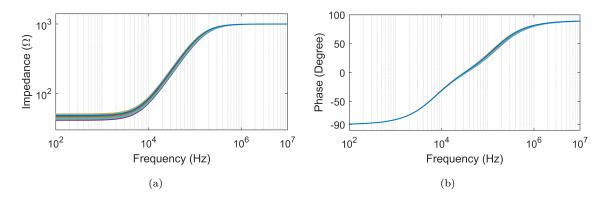

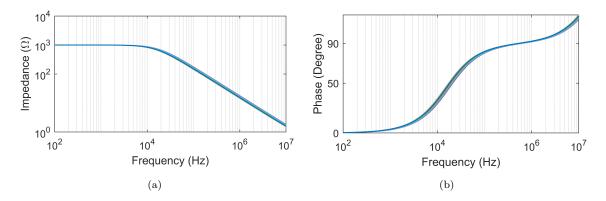

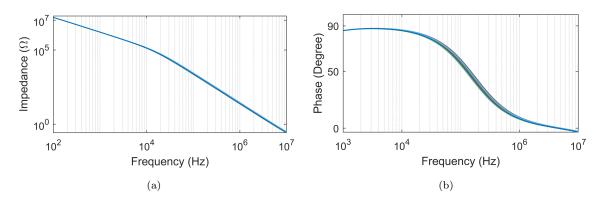

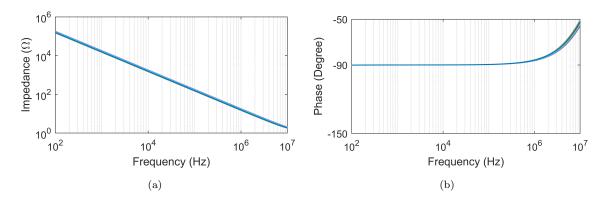

| 2.8  | Frequency responses of (a) impedance and (b) phase of proposed ca-                                                                     |     |

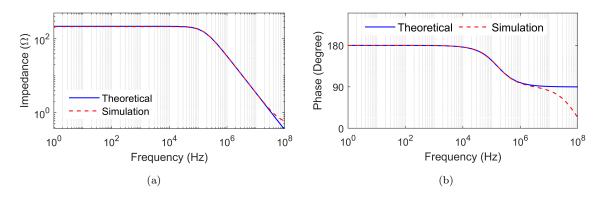

|      | pacitance multiplier of Fig. 2.5(a)                                                                                                    | 35  |

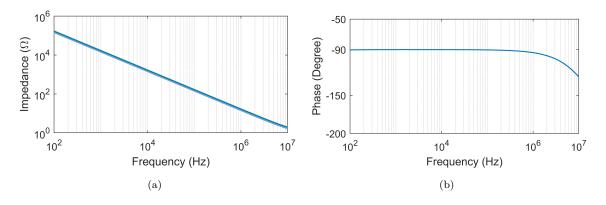

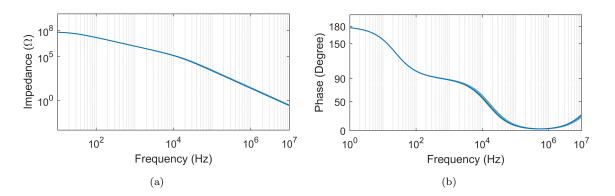

| 2.9  | Frequency responses of (a) impedance and (b) phase of proposed ca-                                                                     |     |

|      | pacitance multiplier of Fig. 2.5(b)                                                                                                    | 36  |

| 2.10 | Frequency responses of (a) impedance and (b) phase of proposed ca-                                                                     |     |

|      | pacitance multiplier of Fig. 2.5(c)                                                                                                    | 36  |

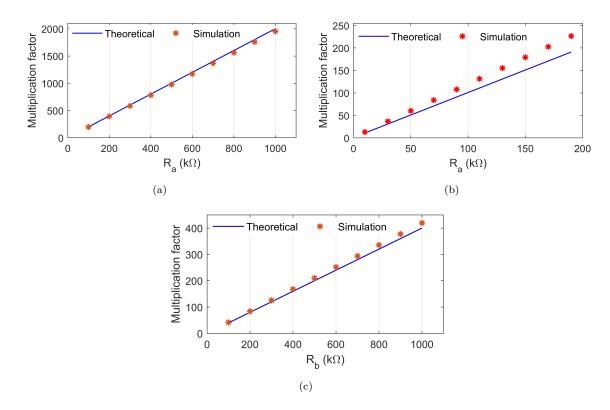

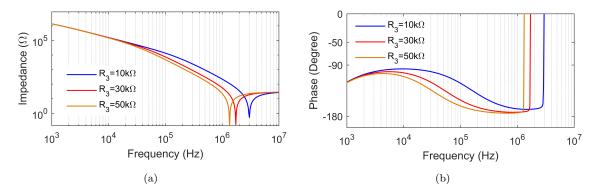

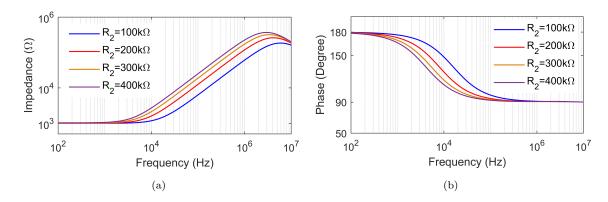

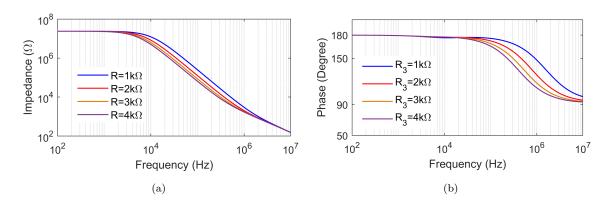

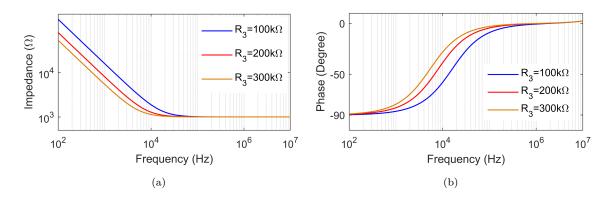

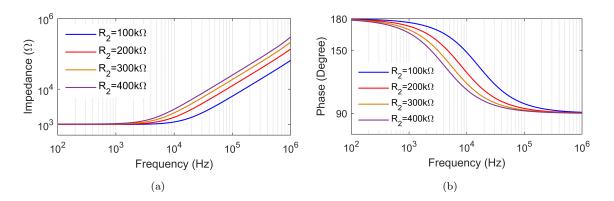

| 2.11 | Variation of multiplication factor for different values of tuning resistor                                                             |     |

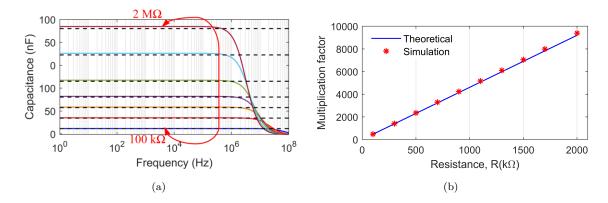

|      | (a) Fig. 2.5 a (b) Fig. 2.5 b (c) Fig. 2.5 c                                                                                           | 37  |

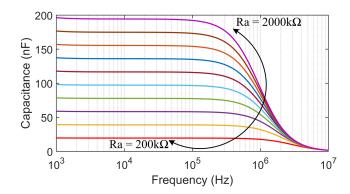

| 2.12 | Variation in capacitance with frequency by varying resistor $R_a$ of Fig.                                                              |     |

|      | 2.5(a)                                                                                                                                 | 37  |

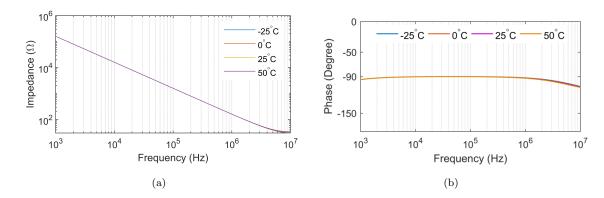

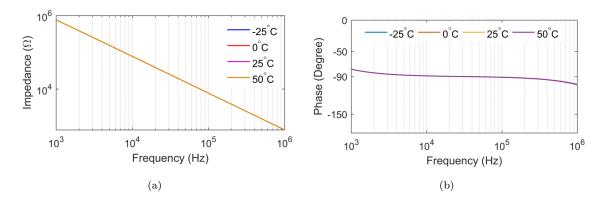

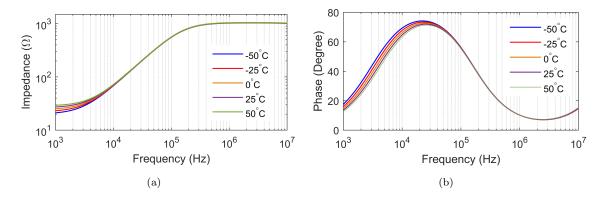

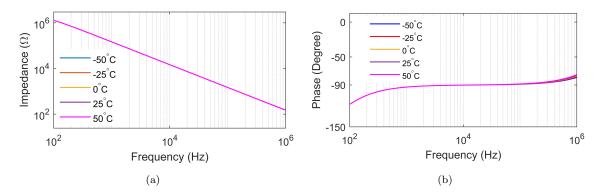

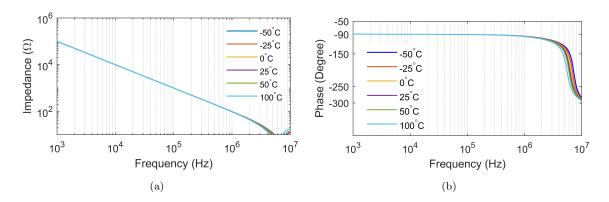

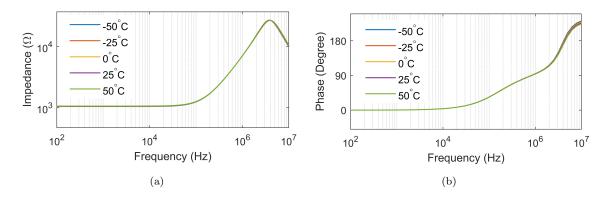

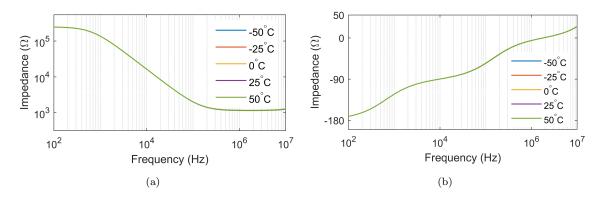

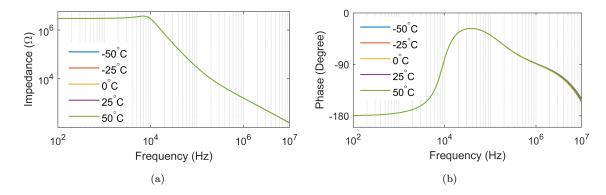

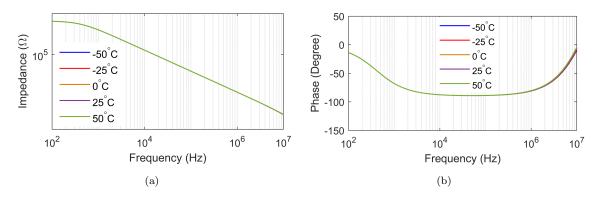

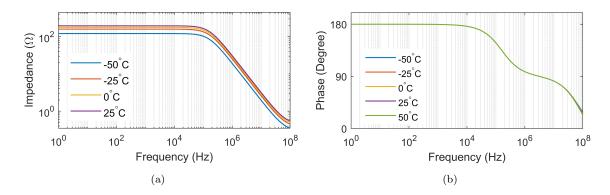

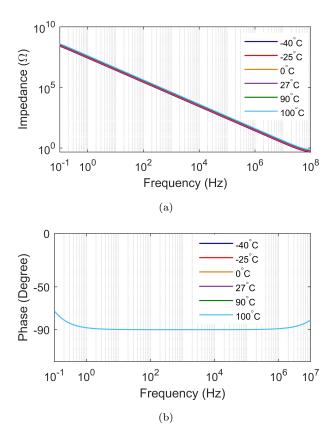

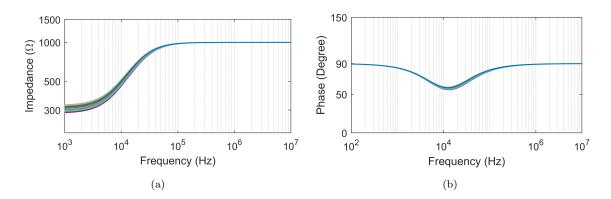

| 2.13 | Frequency responses of impedance and phase of capacitance multipli-                                                                    | 0.0 |

|      | ers at different temperatures for Fig. 2.5(a)                                                                                          | 38  |

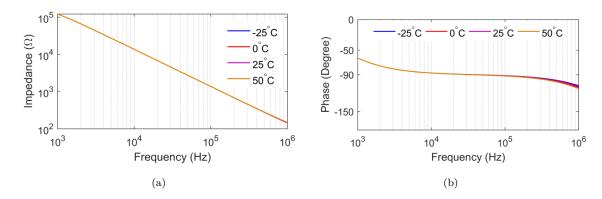

| 2.14 | Frequency responses of impedance and phase of capacitance multipli-                                                                    | 0.0 |

| 0.45 | ers at different temperatures for Fig. 2.5(b)                                                                                          | 39  |

| 2.15 | Frequency responses of impedance and phase of capacitance multipli-                                                                    | 0.0 |

| 0.46 | ers at different temperatures for Fig. 2.5(c)                                                                                          | 39  |

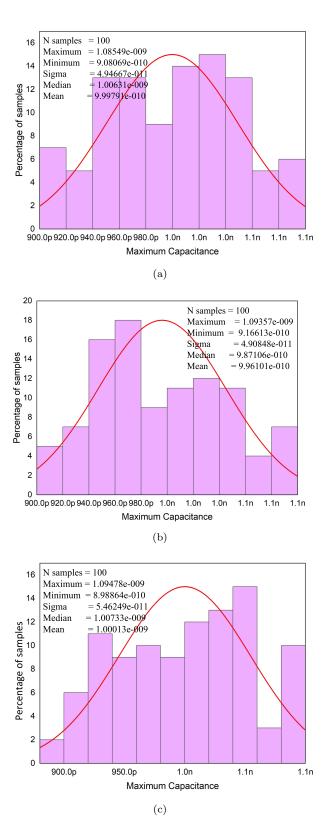

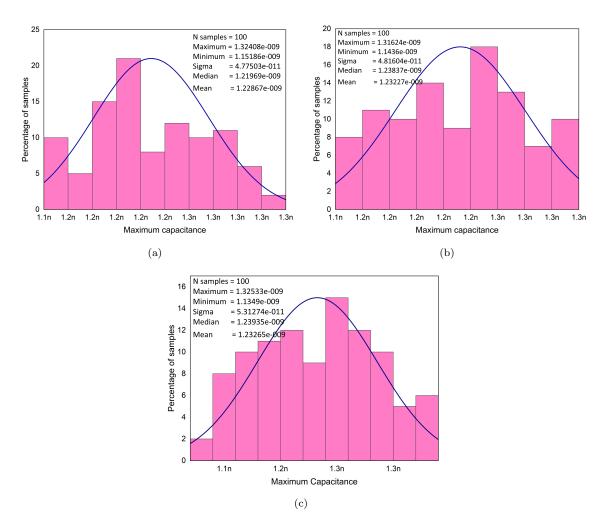

| 2.16 | Histograms of the circuits of Fig. 2.5(a) obtained through Monte-                                                                      | 40  |

| 0.15 | Carlo simulations                                                                                                                      | 40  |

| 2.17 | Histograms of the circuits of Fig. 2.5(b) obtained through Monte-                                                                      | 11  |

| 0.10 | Carlo simulations                                                                                                                      | 41  |

| 2.18 | Histograms of the circuits of Fig. 2.5(c) obtained through Monte-                                                                      | 40  |

| 0.10 | Carlo simulations                                                                                                                      | 42  |

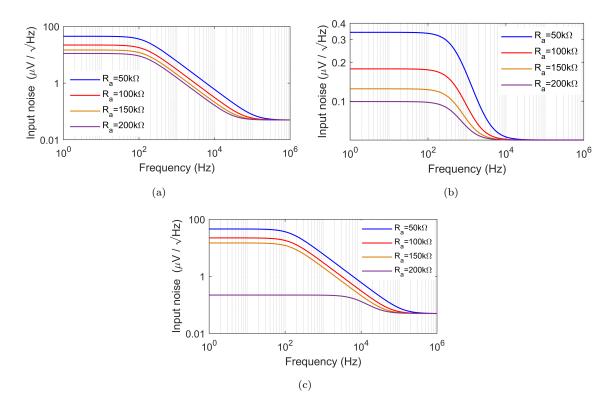

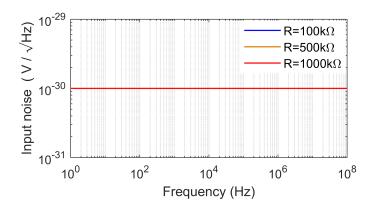

| 2.19 | Effect of noise on proposed NGCM circuits for different values of                                                                      | 4.4 |

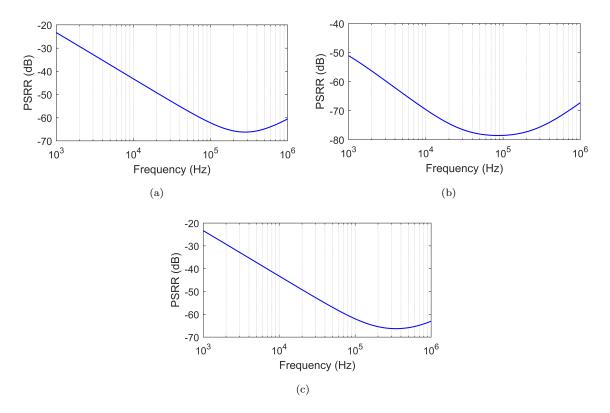

| 2.20 | resistors $R_a$ for (a) Fig. 2.5(a), (b) Fig. 2.5(b), (c) Fig. 2.5(c) Simulated PSPR of the proposed NCCM singuity for (a) Fig. 2.5(a) | 44  |

| 2.20 | Simulated PSRR of the proposed NGCM circuits for (a) Fig. 2.5(a), (b) Fig. 2.5(b) (c) Fig. 2.5(c)                                      | 45  |

| 2 21 | Complete circuit realization of current excited negative capacitance                                                                   | 40  |

| 2.21 | multiplier circuit of Fig. 2.28(a)                                                                                                     | 46  |

| 2 22 | Experimental setup of circuit of Fig. 2.5(a)                                                                                           | 46  |

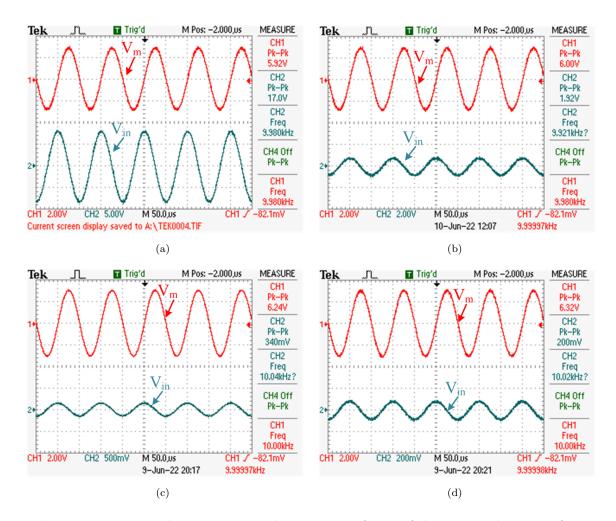

|      | Time domain input and output waveforms of the proposed circuit of                                                                      | 40  |

| 2.20 | Fig. 2.5(a) for different values of MFs                                                                                                | 47  |

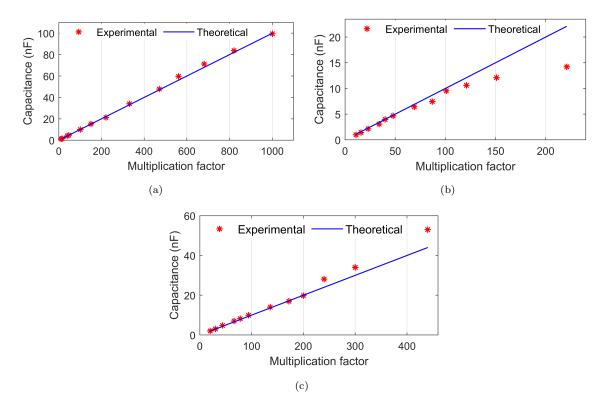

| 2 24 | Time domain waveforms for the circuits (a) Fig. 2.5(b) (b) Fig. 2.5(c)                                                                 | 48  |

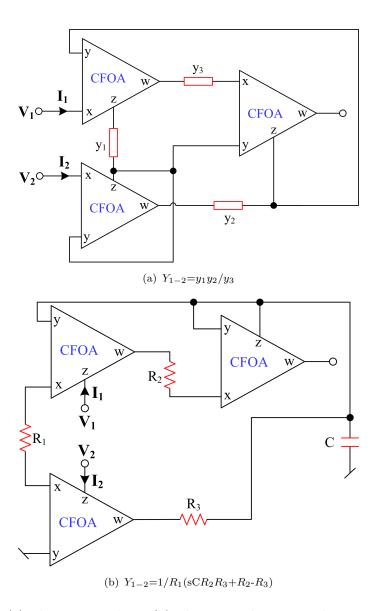

|      | Variation in capacitance value for different multiplication factors                                                                    | 49  |

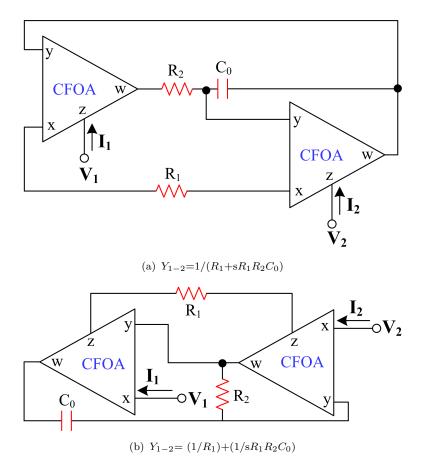

|      | Generalized impedance converter circuit proposed in [140], $Z_{1-2}=Z_2Z_3Z_4$                                                         |     |

| 2.20 | Generalized impedance converter circuit proposed in [140], $Z_{1-2} = Z_2 Z_3 Z_4$                                                     | 51  |

| 2 27 | Floating inductor proposed in [141], $Y_{1-2} = (R_2 - R_1 / R_1 R_2) + 1/sC_1 R_1 R_2$                                                | 51  |

|      | (a) Floating simulator (b) Floating inductor simulator proposed in [145]                                                               | 52  |

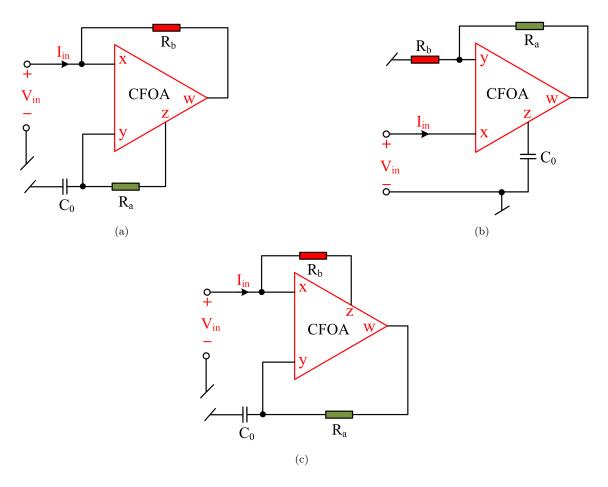

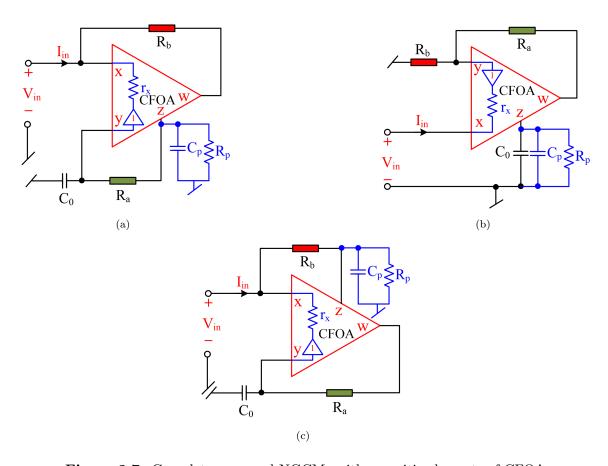

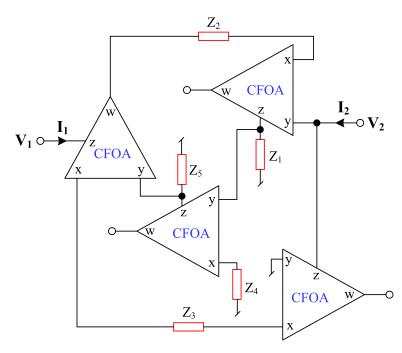

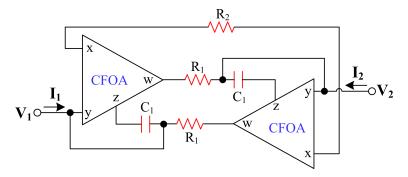

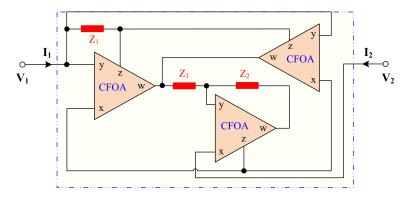

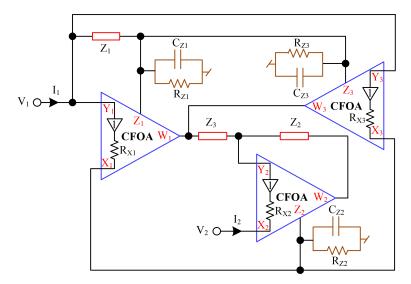

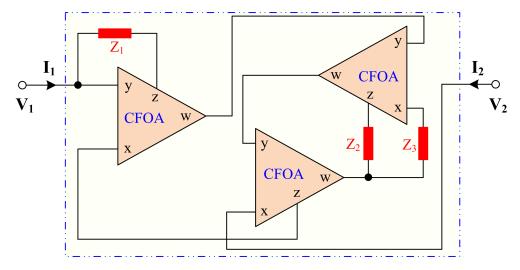

| 2.29 |                                                                                                                                        | 54  |

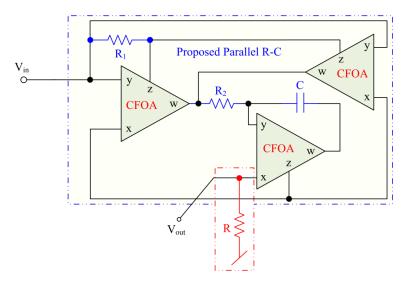

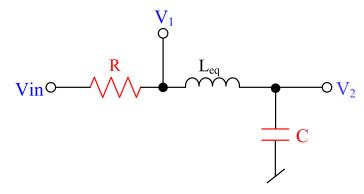

|      | Proposed floating immittance simulator circuit                                                                                         | 55  |

| ⊿.∪∪ | Troposou noaung minipuanoo simulaudi diloliti                                                                                          | 55  |

| 2.31  | Complete proposed immittance simulator circuit with parasitic elements of CFOAs                              | 5 |

|-------|--------------------------------------------------------------------------------------------------------------|---|

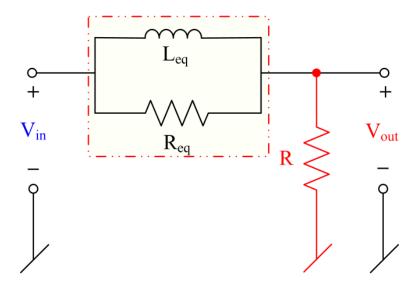

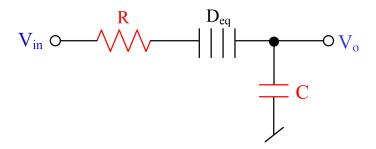

| 2.32  | Circuit model for the design of lag compensator                                                              | 5 |

|       | CFOA-based lag compensator using proposed floating parallel R-L                                              |   |

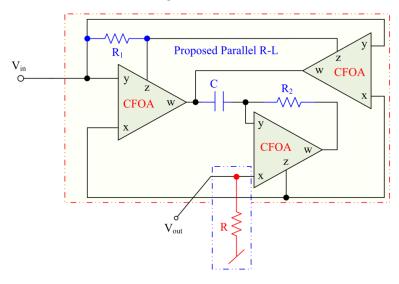

| 2.00  | simulator circuit                                                                                            | 6 |

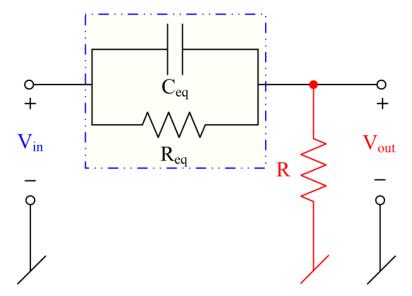

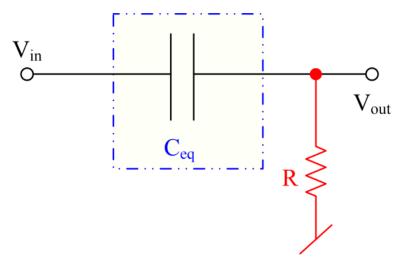

| 2.34  | Circuit model of the lead compensator using parallel floating R-C simulator circuit                          | 6 |

| 2.35  | Lead compensator using proposed floating parallel R-C simulator circuit                                      | 6 |

|       | Circuit model for the realization of first-order HPF                                                         | 6 |

| 2.37  | First-order high-pass filter circuit as an application example of pro-                                       |   |

|       | posed lossless FCM simulator circuit                                                                         | 6 |

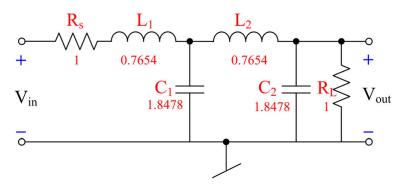

| 2.38  | Normalized fourth-order Butterworth filter                                                                   | 6 |

| 2.39  | Transformation of the passive RLC circuit of 4th order Butterworth                                           |   |

|       | Filter shown in Fig. 2.38                                                                                    | 6 |

| 2.40  | 4th order Butterworth LPF circuit using parallel RL, parallel RC and                                         |   |

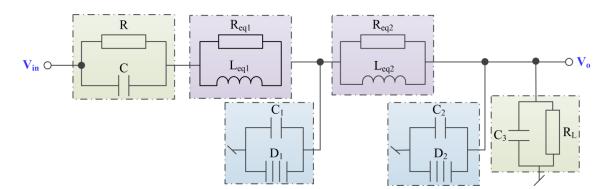

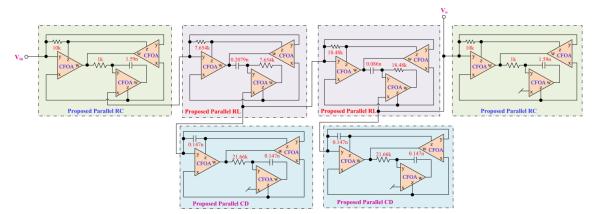

|       | parallel CD circuits [145]                                                                                   | 6 |

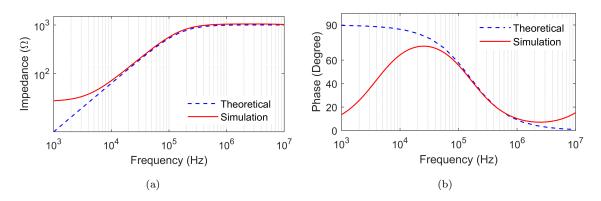

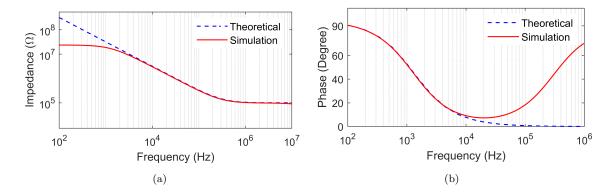

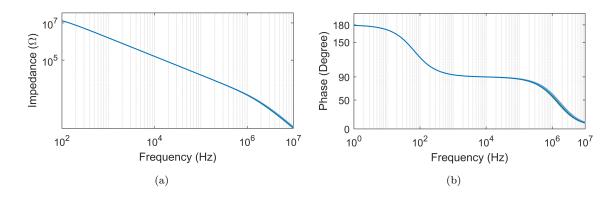

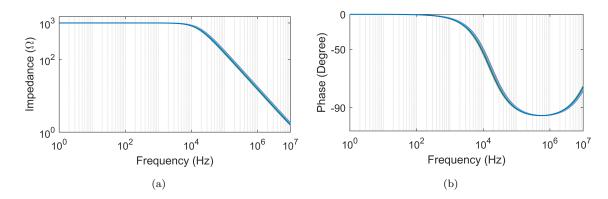

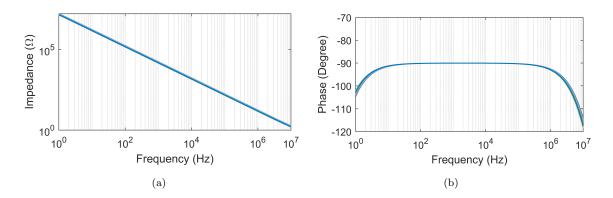

|       | Frequency responses of impedance and phase of the circuit of Fig. 2.30                                       | 6 |

| 2.42  | Frequency responses of parallel R-L simulator showing tunability of                                          |   |

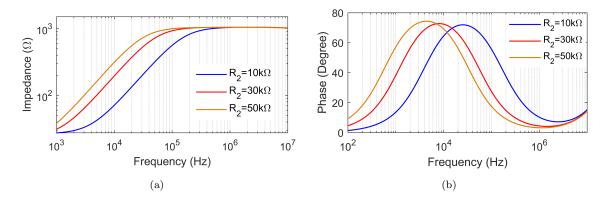

|       | (a) magnitude (b) phase                                                                                      | 6 |

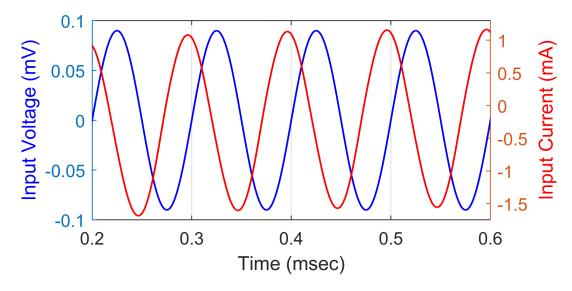

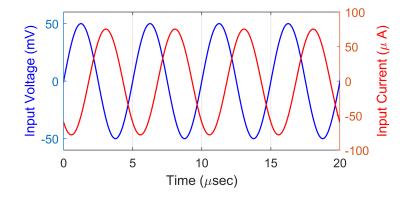

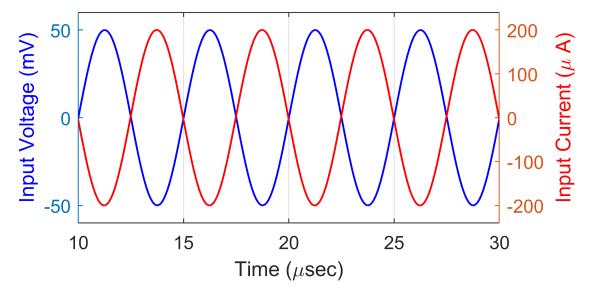

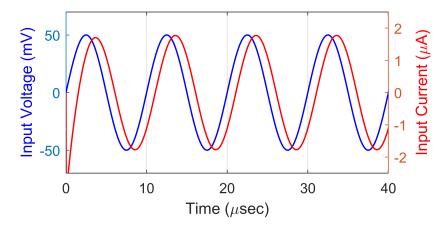

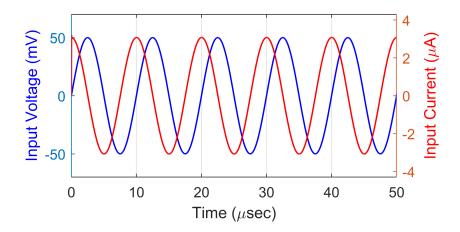

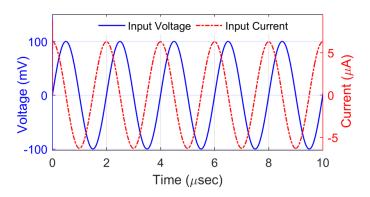

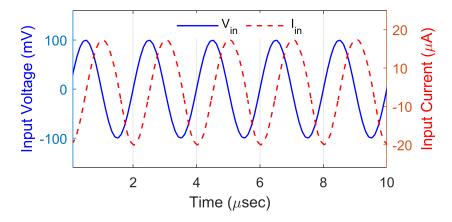

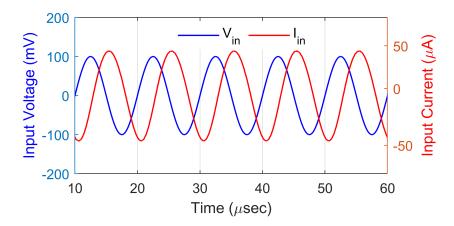

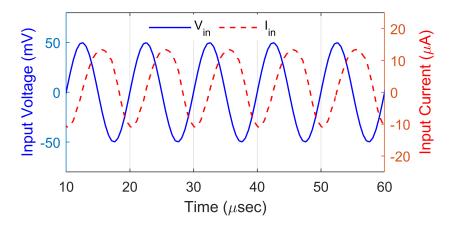

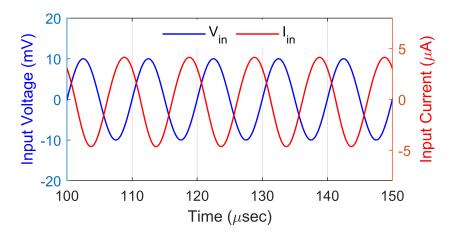

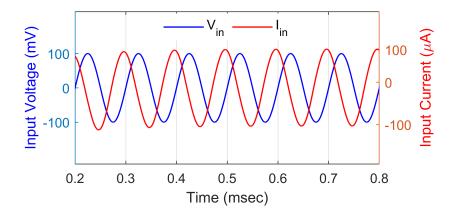

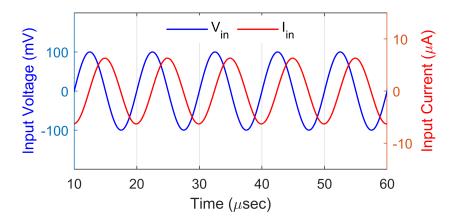

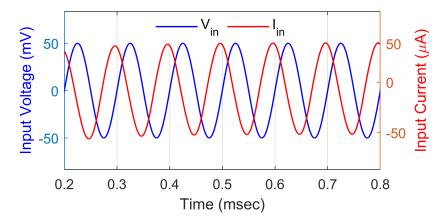

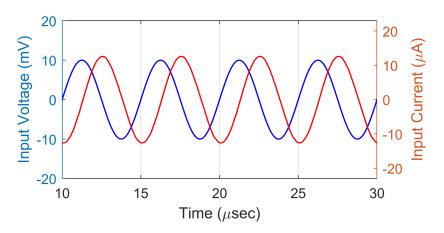

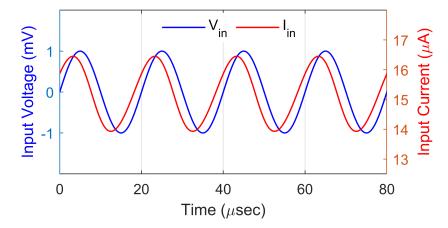

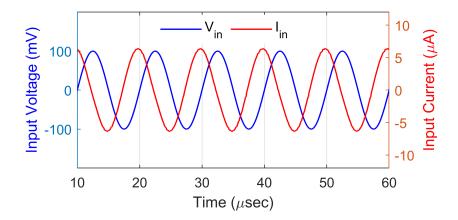

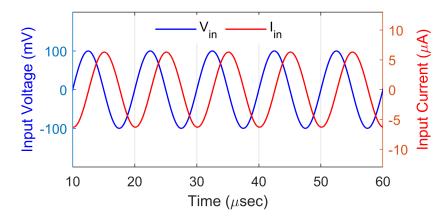

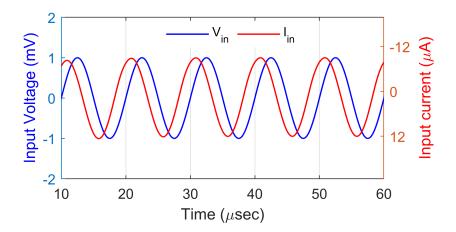

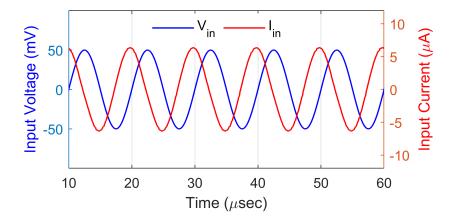

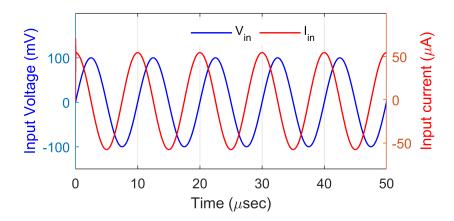

| 2.43  | Transient responses of input voltage and current for parallel R-L sim-                                       |   |

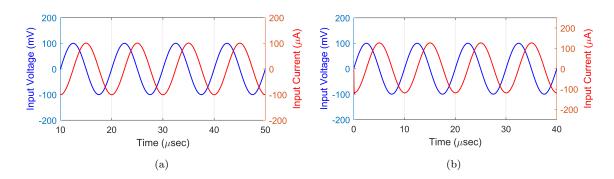

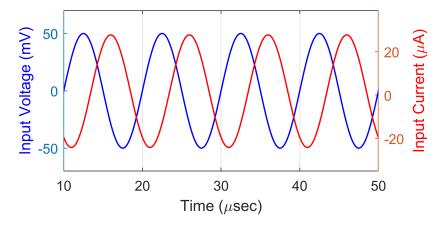

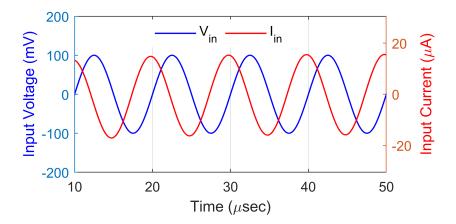

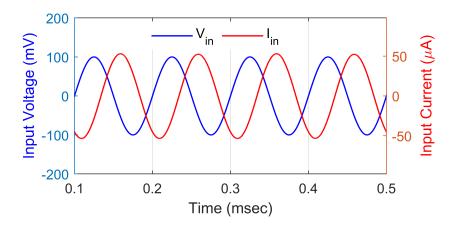

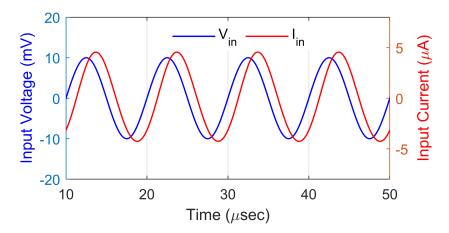

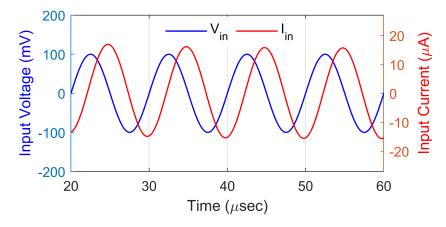

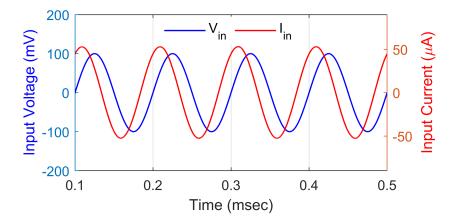

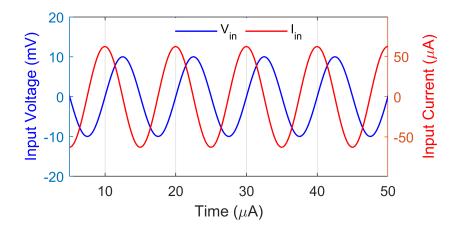

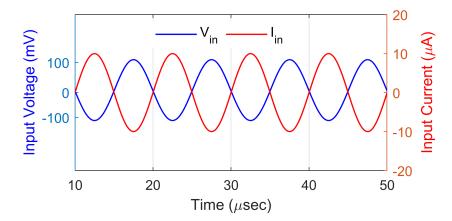

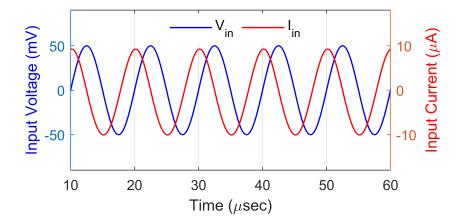

|       | ulator circuit                                                                                               | 6 |

| 2.44  | Monte-Carlo results with 5% Gaussian distribution in R deviation (a) magnitude responses (b) Phase responses | 6 |

| 2.45  | Frequency responses of impedance for variation in temperature (a)                                            |   |

|       | magnitude (b) phase                                                                                          | 6 |

| 2.46  | Frequency responses of impedance for parallel R-C simulator circuit                                          |   |

|       | (a) Magnitude and (b) phase                                                                                  | 6 |

|       |                                                                                                              | 6 |

| 2.48  | Input voltage and current of the impedance of parallel R-C simulator                                         |   |

|       | circuit                                                                                                      | 6 |

| 2.49  | Monte-Carlo results of (a) magnitude (b) phase with 10% deviations                                           |   |

|       |                                                                                                              | 7 |

| 2.50  | Magnitude and phase responses of parallel R-C circuit for different                                          | _ |

| 0 = 1 | temperature (a) magnitude (b) phase                                                                          | 7 |

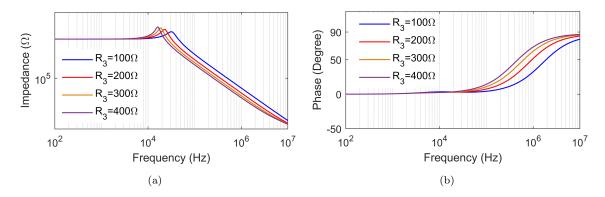

| 2.51  | Frequency responses of (a) magnitude and (b) phase of parallel C-D                                           | _ |

| 0.50  |                                                                                                              | 7 |

| 2.52  | Frequency responses of impedance of parallel C-D simulator (a) magnitude and (b) phase                       | _ |

| 0.50  | nitude and (b) phase                                                                                         | 7 |

| 2.53  | Transient responses of input voltage and current of parallel C-D simulator circuit                           | 7 |

| 2 5/  | Monte-Carlo simulations results for 10% Gaussian deviation in resis-                                         | 1 |

| ∠.04  | Monte-Carlo simulations results for $10\%$ Gaussian deviation in resistor $R_3$                              | 7 |

|       | 101 163                                                                                                      | 1 |

| 2.55 | Frequency responses of impedance of parallel C-D simulator showing variation in temperature (a) magnitude and (b) phase                | 73 |

|------|----------------------------------------------------------------------------------------------------------------------------------------|----|

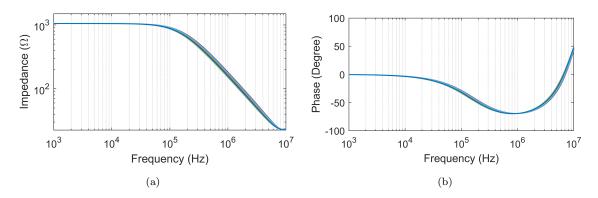

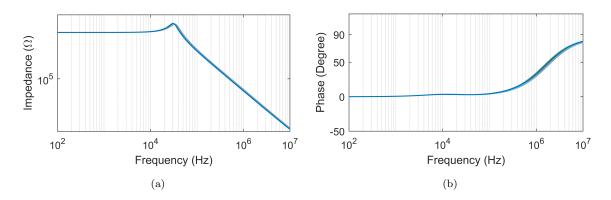

| 2.56 | Frequency responses of the proposed floating capacitance multiplier                                                                    |    |

|      | (a) magnitude and (b) phase                                                                                                            | 73 |

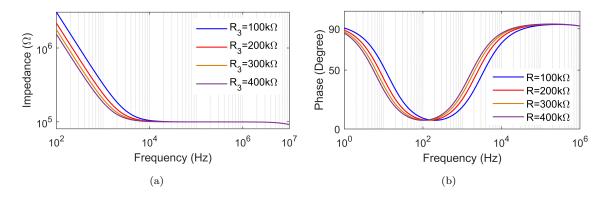

| 2.57 | (a) Variations in capacitance with frequency by varying resistor $R_3$ of                                                              |    |

|      | Fig. 2.30 (b) Variation of multiplication factor for different values of                                                               |    |

|      | tuning resistor $R_3$                                                                                                                  | 74 |

|      | Time responses of input voltage and current of FCM                                                                                     | 74 |

| 2.59 | Monte-Carlo simulation results of the proposed FCM (a) magnitude                                                                       |    |

|      | (b) phase                                                                                                                              | 75 |

| 2.60 | Histograms obtained through Monte-Carlo simulations for circuit of                                                                     |    |

| 0.04 | Fig. 2.30                                                                                                                              | 76 |

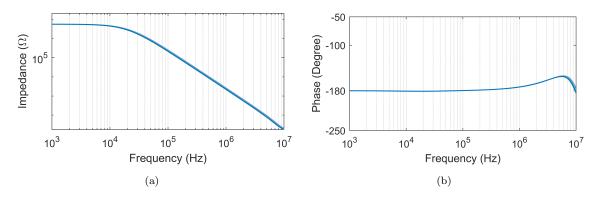

| 2.61 | Frequency responses of (a) impedance and (b) phase of FCM at dif-                                                                      | 7  |

| 0.00 | ferent temperatures                                                                                                                    | 76 |

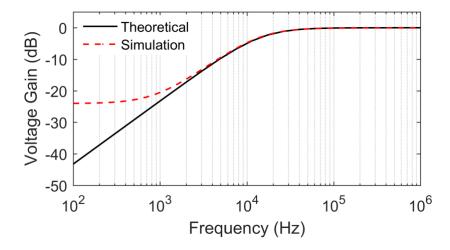

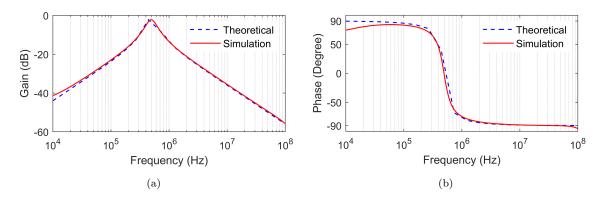

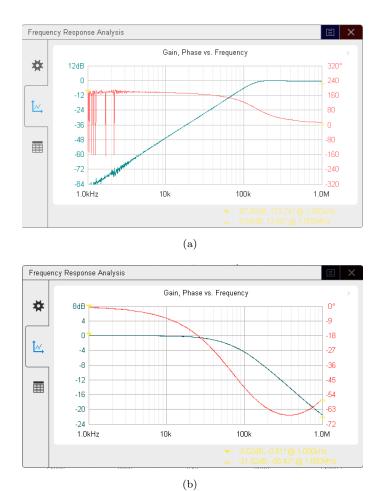

|      | Frequency responses of first order HPF circuit                                                                                         | 77 |

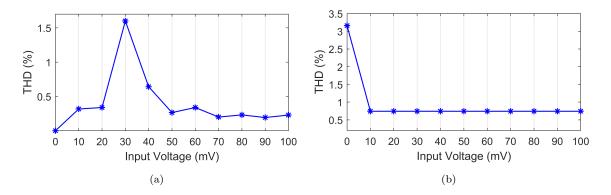

| 2.03 | THD variation with respect to input voltages of the (a) FCM and (b) HPF                                                                | 77 |

| 2.64 | HPF                                                                                                                                    | 77 |

|      | Frequency responses of 4th order Butterworth inter shown in Fig. 2.40  Frequency response of input impedance and phase seen from (a-b) | 11 |

| 2.00 | port 1 (c-d) port 2                                                                                                                    | 79 |

| 2 66 | Experimental test circuit for the FCM                                                                                                  | 79 |

|      | Experimental test circuit for the FCM                                                                                                  | 80 |

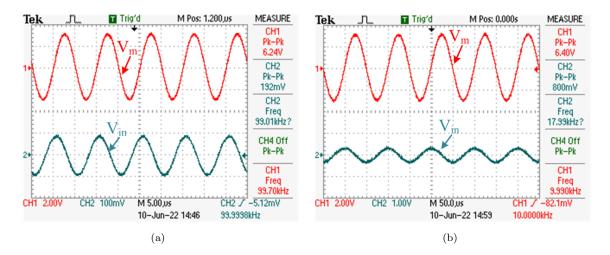

|      | The input and output voltages of the test circuit shown in Fig. 2.66.                                                                  | 80 |

|      | (a and b) Frequency responses of magnitude and phase (c) Input and                                                                     |    |

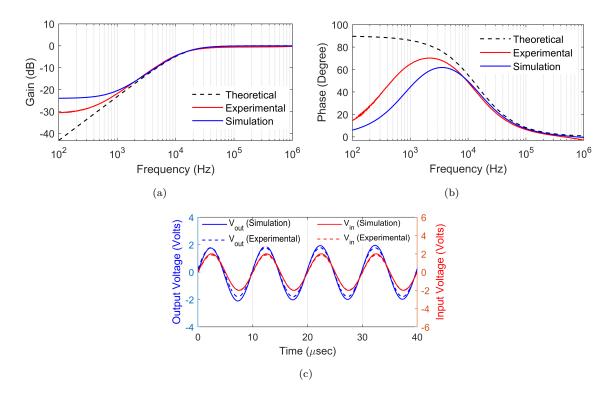

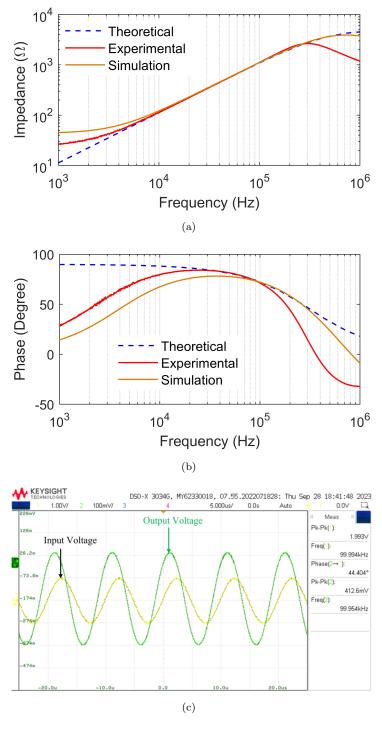

|      | output voltages of lag compensator                                                                                                     | 81 |

| 2.70 | (a and b) Frequency responses of magnitude and phase (c) Input and                                                                     |    |

|      | output voltages of lead compensator                                                                                                    | 82 |

| 2.71 | (a and b) Experimental frequency responses and (c) transient re-                                                                       |    |

|      | sponses of first-order high-pass filter                                                                                                | 83 |

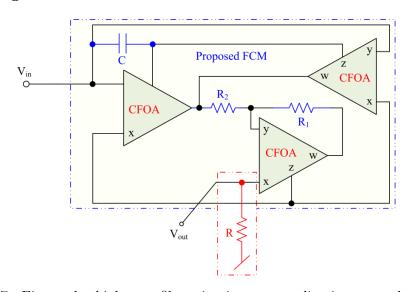

|      | Modified floating lossless immittance simulator circuit                                                                                | 84 |

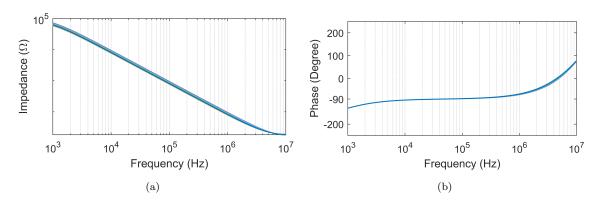

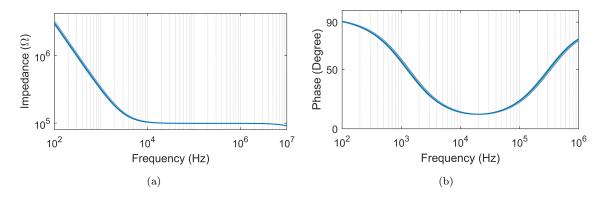

| 2.73 | Frequency responses of (a) impedance and (b) phase of proposed loss-                                                                   |    |

|      | less floating inductor of Fig. 2.72                                                                                                    | 86 |

| 2.74 | Frequency responses of floating inductor simulator showing tunability                                                                  |    |

|      | of (a) magnitude (b) phase                                                                                                             | 87 |

| 2.75 | Monte-Carlo results with 5% Gaussian distribution in R deviation (a)                                                                   | 0. |

| 0.70 | magnitude responses (b) Phase responses                                                                                                | 87 |

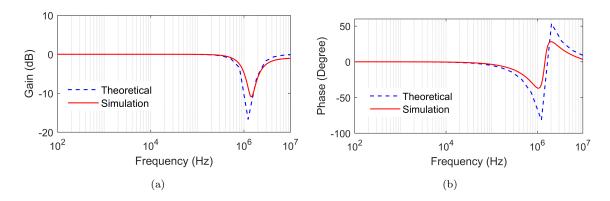

|      | NF and LPF as an application example of floating inductor simulator                                                                    | 87 |

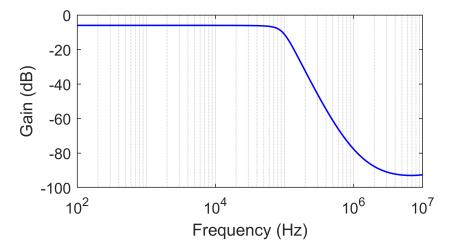

|      | Frequency responses of NF (a) gain (b) phase                                                                                           | 88 |

|      | Frequency responses of LPF (a) gain (b) phase                                                                                          | 89 |

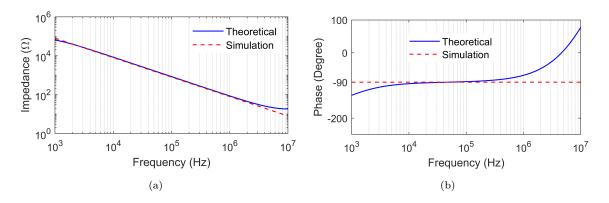

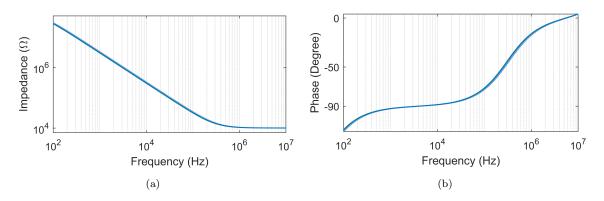

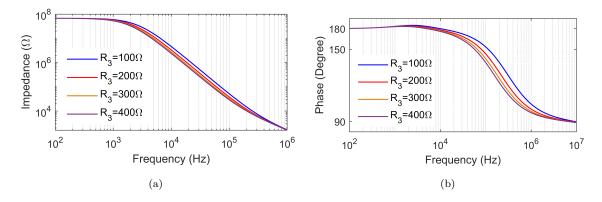

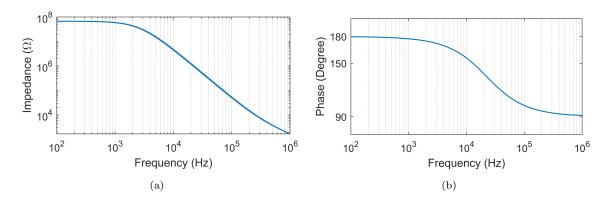

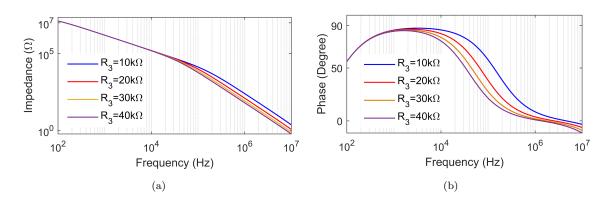

|      | Frequency responses of FCM-1 circuit (a) magnitude and (b) phase.                                                                      | 89 |

| 2.80 | Frequency responses of FCM-2 circuit (a) magnitude and (b) phase .                                                                     | 89 |

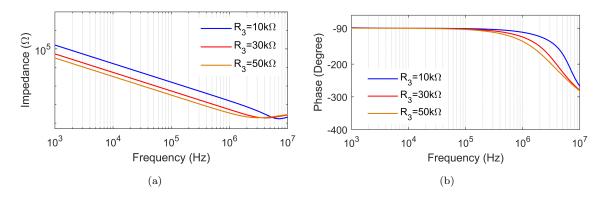

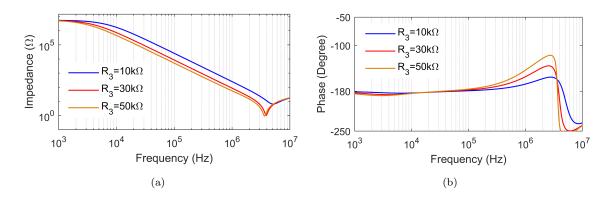

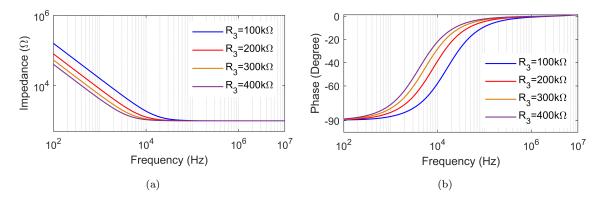

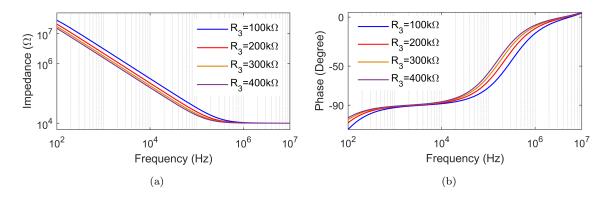

| 2.81 Frequency responses of FCM-1 circuit at different values of resistor                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| $R_3$ (a) Magnitude and (b) phase                                                                                                          |

| $R_3$ (a) Magnitude and (b) phase                                                                                                          |

| 2.83 Transient responses of (a) FCM-1 circuit (b) FCM-2 circuit 91                                                                         |

| 2.84 Monte-Carlo simulations results of FCM-1 for 10% Gaussian deviation                                                                   |

| in resistor $R_3$                                                                                                                          |

| 2.85 Monte-Carlo simulations results of FCM-2 for 10% Gaussian deviation                                                                   |

| in resistor $R_3$                                                                                                                          |

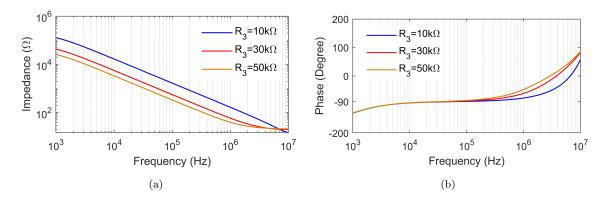

| 2.86 Frequency responses of (a) impedance and (b) phase of FCM-1 at                                                                        |

| different temperatures                                                                                                                     |

| 2.87 Frequency responses of (a) impedance and (b) phase of FCM-2 at                                                                        |

| different temperatures                                                                                                                     |

| 2.88 Frequency responses of (a) magnitude and (b) phase of floating FDNR                                                                   |

| circuit                                                                                                                                    |

| 2.89 Frequency responses of impedance of floating FDNR (a) magnitude                                                                       |

| and (b) phase                                                                                                                              |

| 2.90 Monte-Carlo simulations results for 10% Gaussian deviation in resis-                                                                  |

| $tor R_3 \dots \dots$                |

| 2.91 Frequency responses of impedance of floating FDNR showing varia-                                                                      |

| tion in temperature (a) magnitude and (b) phase                                                                                            |

| 2.92 BPF as an application example of FFDNR                                                                                                |

| 2.93 (a) Magnitude (b) phase response of BPF                                                                                               |

| 2.94 Floating series-type lossy immittance simulator circuit 96                                                                            |

| 2.95 Frequency responses of floating series R-L circuit (a) magnitude and                                                                  |

| (b) phase                                                                                                                                  |

| 2.96 Frequency responses of floating series R-L circuit at different values                                                                |

| of resistor $R_2$ (a) magnitude and (b) phase                                                                                              |

| 2.97 Time responses of floating series R-L circuit                                                                                         |

| 2.98 Monte-Carlo simulations results for 10% Gaussian deviation in resis-                                                                  |

| $\operatorname{tor} R_2 \dots \dots$ |

| 2.99 Frequency responses of floating series R-L showing variation in tem-                                                                  |

| perature (a) magnitude and (b) phase                                                                                                       |

| 2.100Frequency responses of series R-C circuit (a) magnitude and (b) phase 101                                                             |

| 2.101Frequency responses of series R-C circuit at different values of resistor                                                             |

| $R_3$ (a) magnitude and (b) phase                                                                                                          |

| 2.102Time responses of series R-C circuit                                                                                                  |

| 2.103Monte-Carlo simulations results for 10% Gaussian deviation in resis-                                                                  |

| $\operatorname{tor} R_3 \dots \dots$ |

| 2.104Frequency responses of floating series R-C showing variation in temperature (a) magnitude and (b) phase                               |

| perature (a) magnitude and (b) phase                                                                                                       |

| - 2. DOFFECUEUCV TEODOLOGO OF OCHGO V-D CHCUIL TAL HIARHITHUE AHU TDT DHASC 100                                                            |

| 2.106Frequency responses of series C-D circuit at different values of resist                                                         | or  |

|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| $R_2$ (a) magnitude and (b) phase                                                                                                    | 103 |

| 2.107Time responses of series C-D circuit                                                                                            | 104 |

| 2.108Monte-Carlo simulations results for $10%$ Gaussian deviation in res                                                             | is- |

| tor $R_3$                                                                                                                            | 104 |

| 2.109Frequency responses of floating series C-D showing variation in ten                                                             | m-  |

| perature (a) magnitude and (b) phase                                                                                                 |     |

| 2.110Magnitude and phase responses of the proposed floating capacitan                                                                |     |

| divider circuit                                                                                                                      |     |

| 2.111AC Monte-Carlo simulation results of magnitude and phase of pr                                                                  |     |

| posed floating Capacitance divider circuit                                                                                           |     |

| 2.112Time responses of input voltage and current of floating capacitan divider circuit                                               |     |

| 2.113Impedance and phase responses of Floating capacitance divider circu                                                             | uit |

| at different temperatures                                                                                                            | 106 |

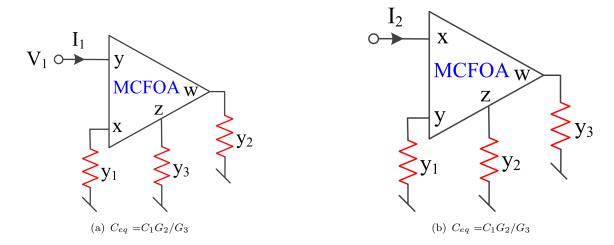

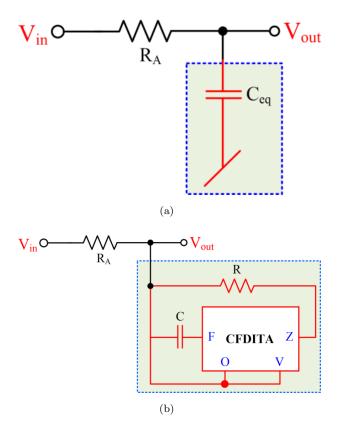

| 2.1 C                                                                                                                                | 115 |

| 3.1 Capacitance multiplier circuit proposed in [151]                                                                                 |     |

| 3.2 Grounded capacitance multiplier circuit proposed in [152]                                                                        |     |

| 3.3 Capacitance multiplier circuit proposed in [153]                                                                                 |     |

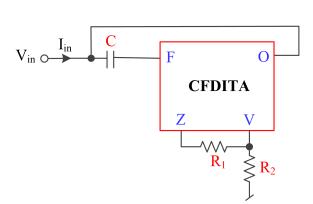

| 3.4 (a) Proposed lossy grounded capacitance multiplier circuit (b) Equivalent circuit                                                |     |

|                                                                                                                                      |     |

| 01                                                                                                                                   |     |

|                                                                                                                                      |     |

| 1                                                                                                                                    |     |

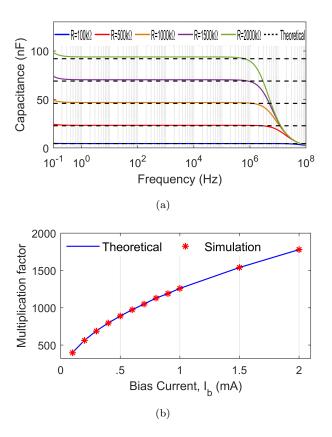

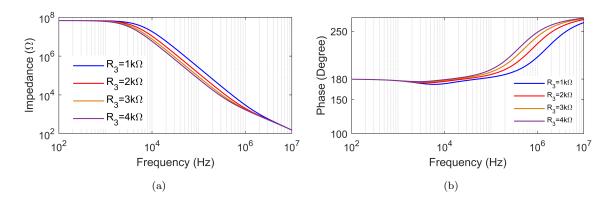

| 3.8 (a) Magnitude and (b) phase responses of proposed circuit 3.9 Frequency responses of the proposed lossy capacitance multiplier ( |     |

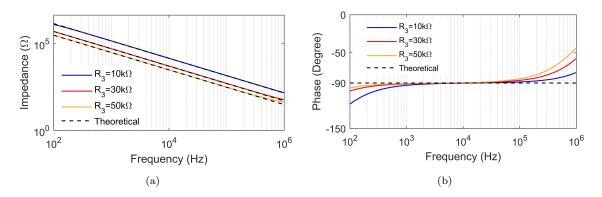

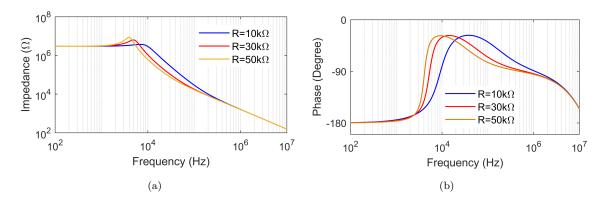

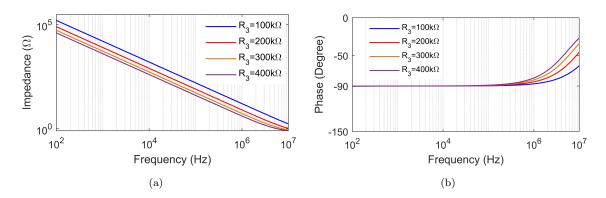

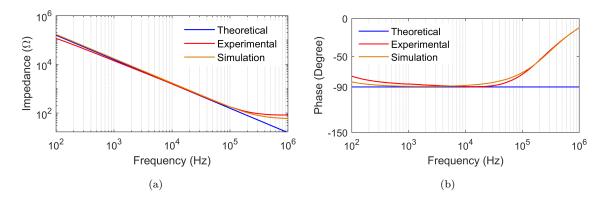

| 3.9 Frequency responses of the proposed lossy capacitance multiplier (magnitude and (b) phase                                        | · / |

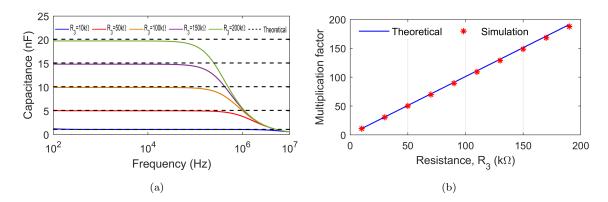

| 3.10 (a) Variation in capacitance by varying resistor R of the circuit                                                               |     |

| Fig. 3.4 and (b) Variation of multiplication factor for different value                                                              |     |

| of R of the circuit of Fig. 3.4                                                                                                      |     |

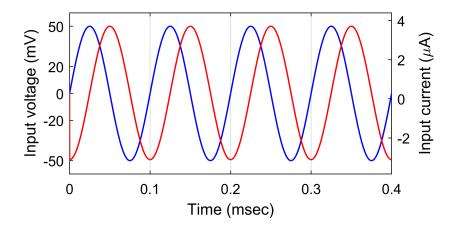

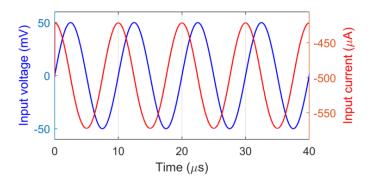

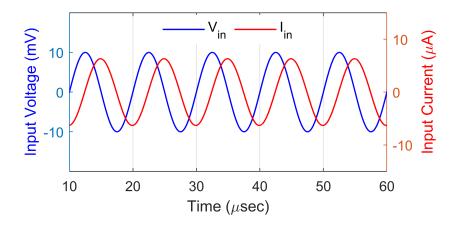

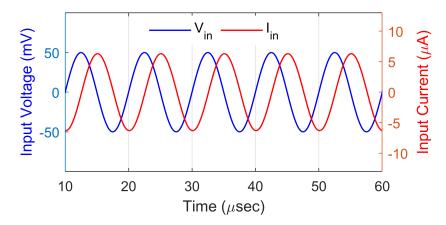

| 3.11 Simulated transient responses of input voltage and input current .                                                              |     |

| 3.12 Frequency responses of proposed circuit for temperature variation (                                                             |     |

| impedance and (b) phase                                                                                                              |     |

| 3.13 Monte Carlo simulations with 5% Gaussian distribution in R devi                                                                 |     |

| tion (a) magnitude responses (b) phase responses                                                                                     |     |

| 3.14 Simulated noise analysis responses                                                                                              |     |

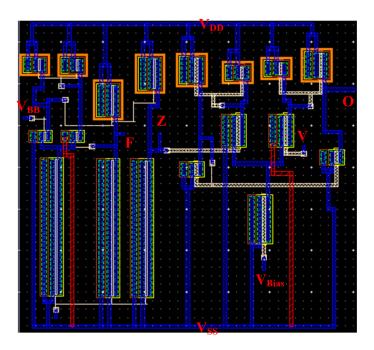

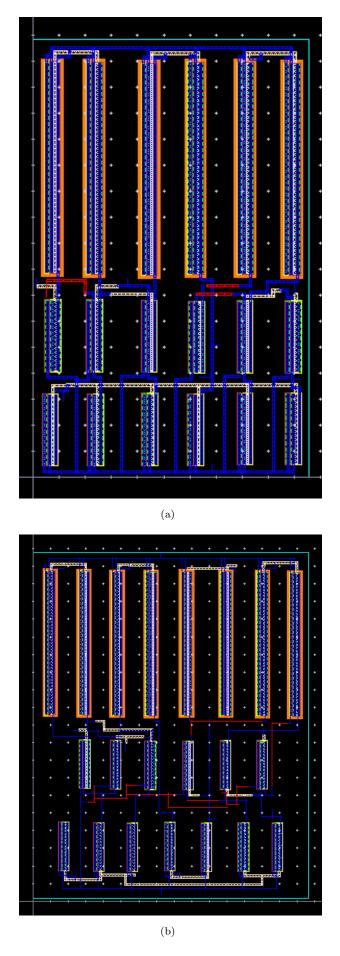

| 3.15 Layout of CFDITA                                                                                                                |     |

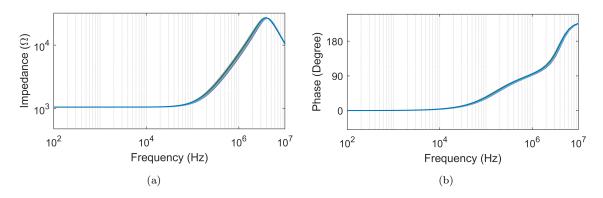

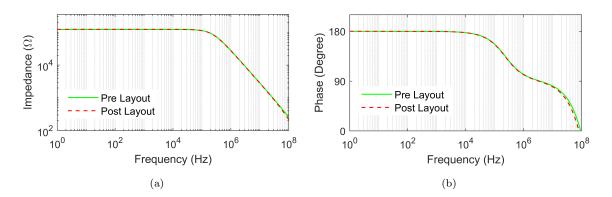

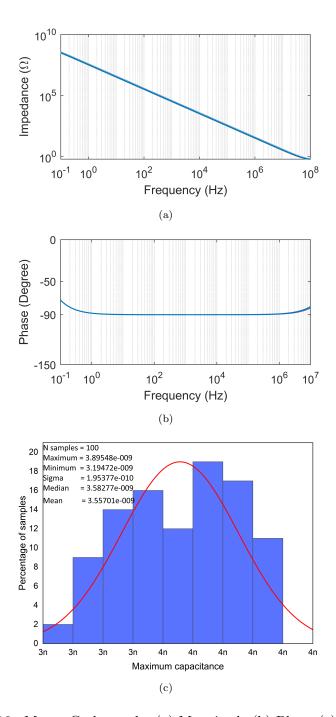

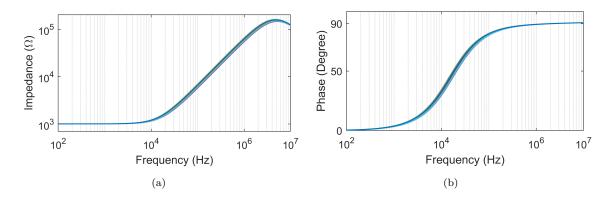

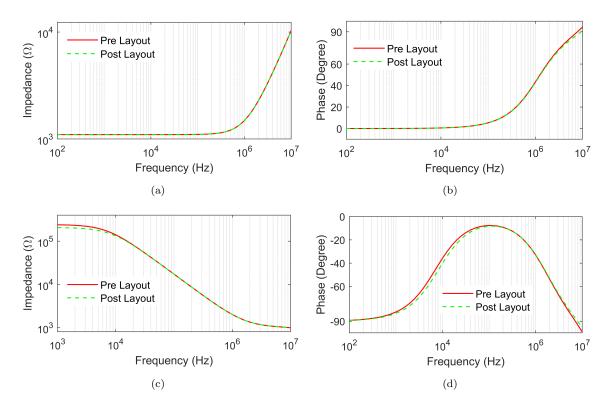

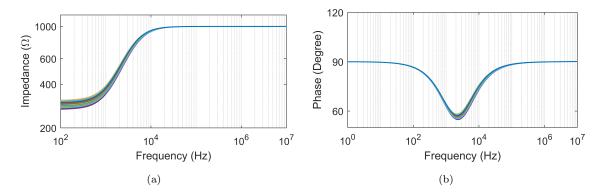

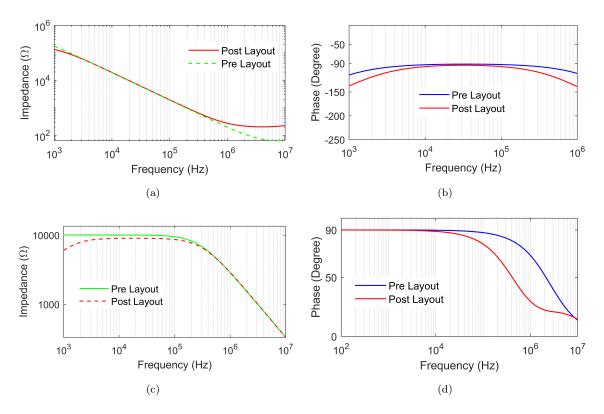

| 3.16 Pre and post layout frequency responses of (a) impedance and (                                                                  |     |

| phase of the proposed CM circuit                                                                                                     | · / |

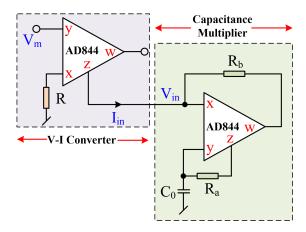

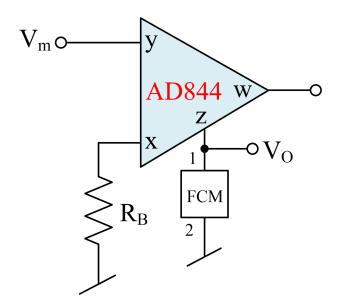

| 3.17 Implementation of CFDITA using commercially available ICs                                                                       |     |

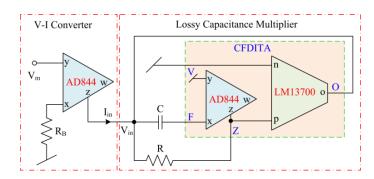

| 3.18 Schematic arrangement of proposed lossy capacitance multiplier using                                                            |     |

| available off-the-shelf ICs                                                                                                          | 105 |

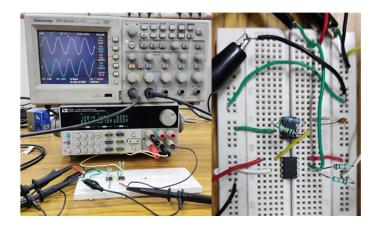

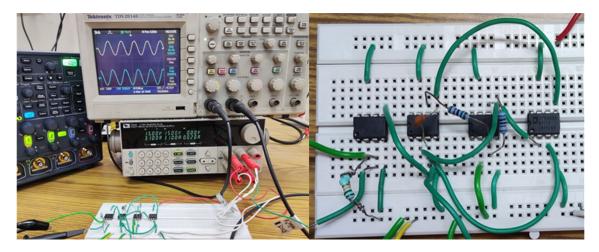

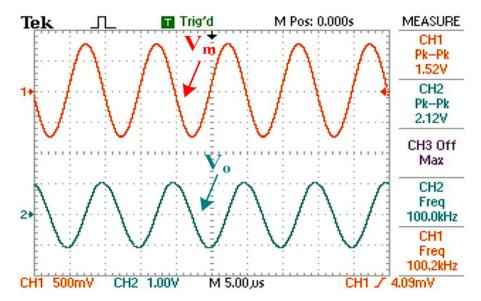

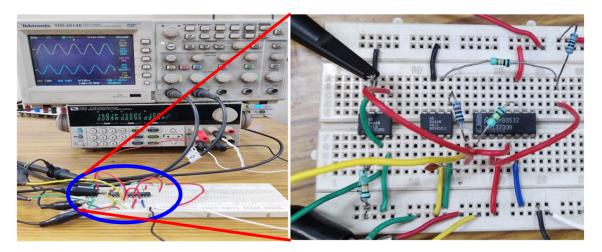

| 3.19 | Snapshot of experimental setup of the lossy capacitance multiplier circuit of Fig. 3.4                                                   | 128  |

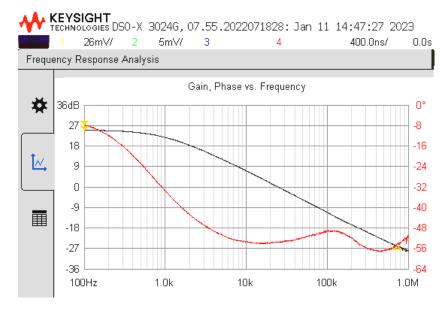

|------|------------------------------------------------------------------------------------------------------------------------------------------|------|

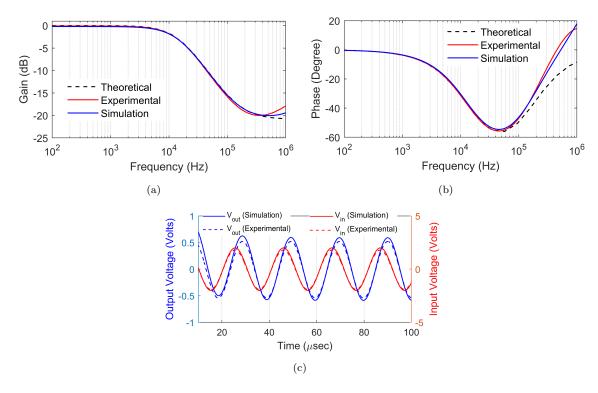

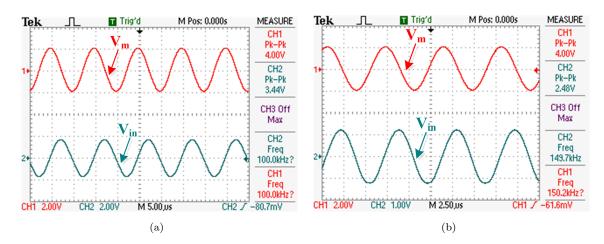

| 3.20 | Frequency responses (a) magnitude (b) phase of the experimental setup shown in Fig. 3.18                                                 | 129  |

| 3.21 | Experimental transient responses of proposed circuit at (a) 100kHz                                                                       |      |

|      | and (b) 150kHz                                                                                                                           |      |

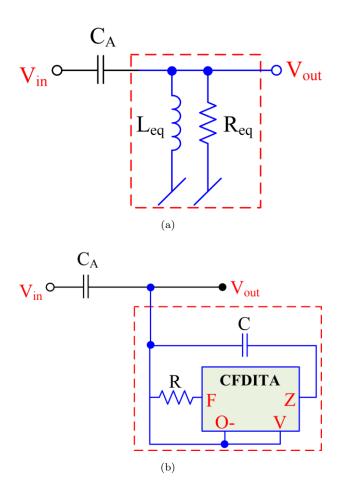

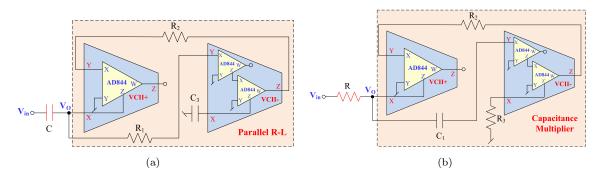

| 3.22 | Approach to implement of CM circuits                                                                                                     | 130  |

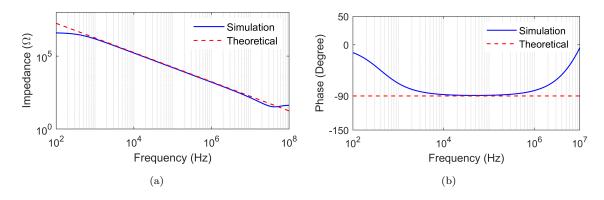

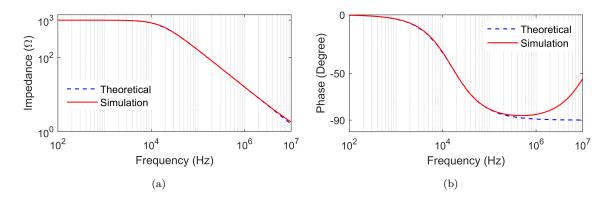

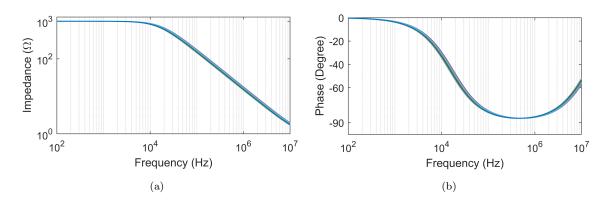

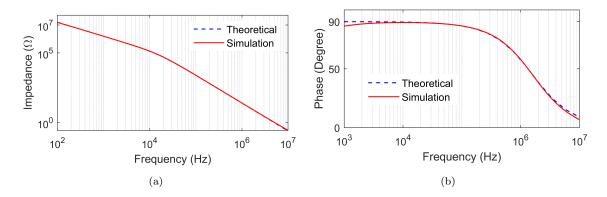

| 3.23 | Proposed lossless grounded capacitance multiplier circuits                                                                               | 131  |

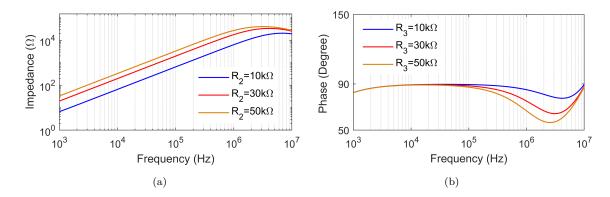

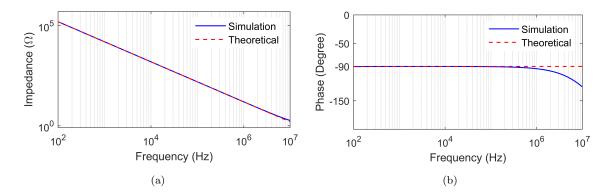

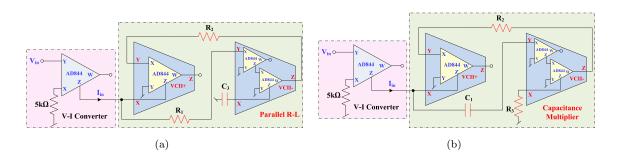

| 3.24 | Proposed lossy parallel-type RL simulator circuits                                                                                       | 132  |

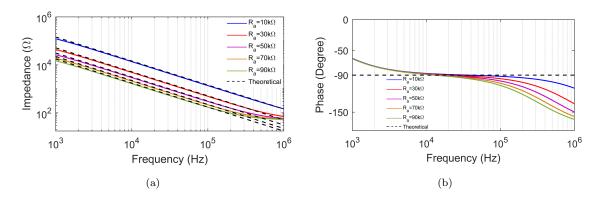

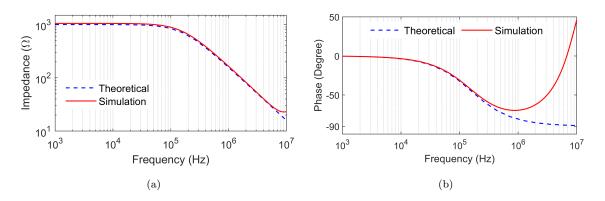

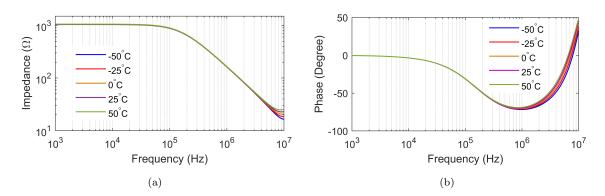

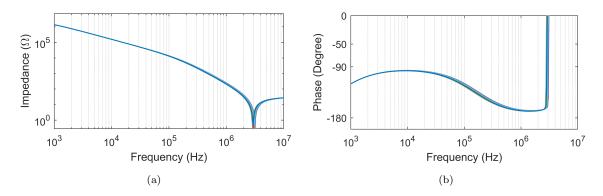

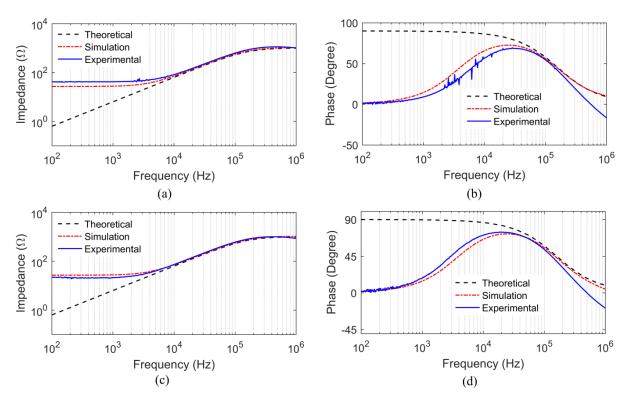

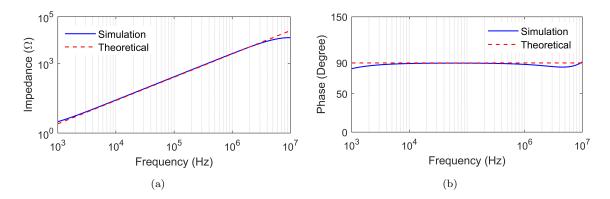

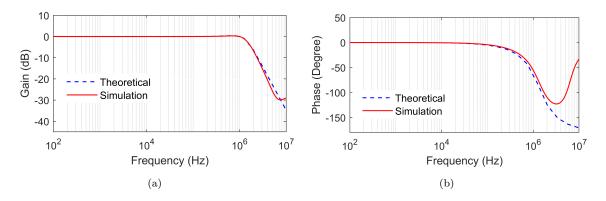

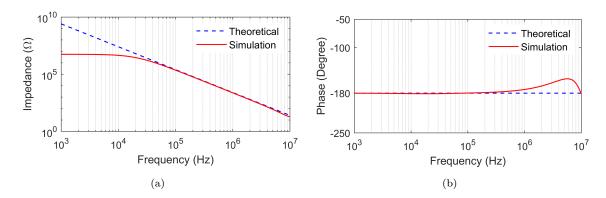

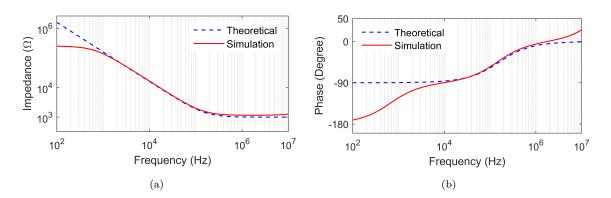

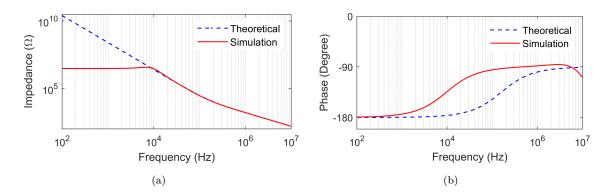

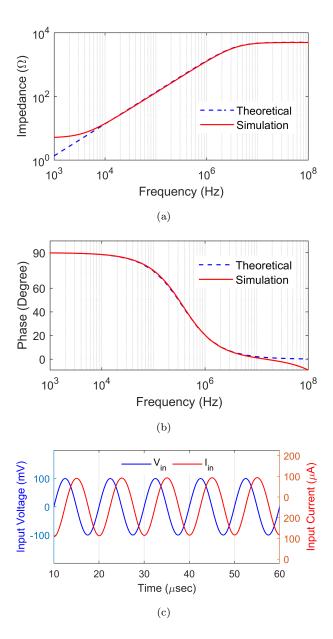

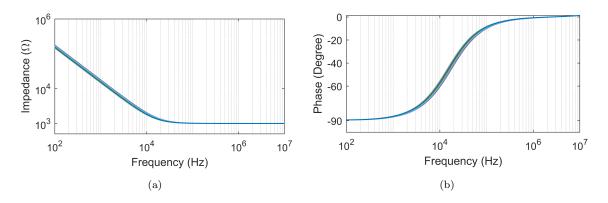

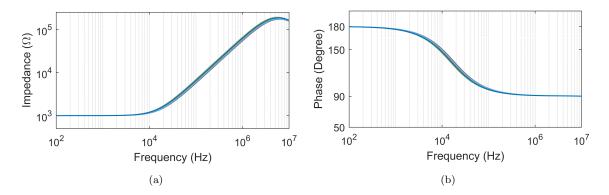

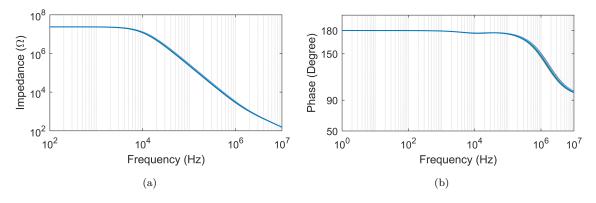

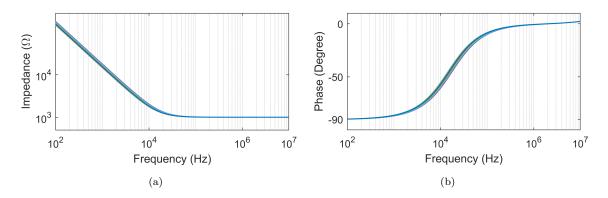

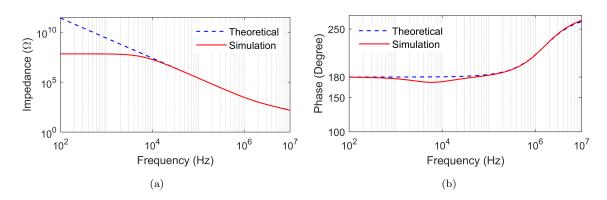

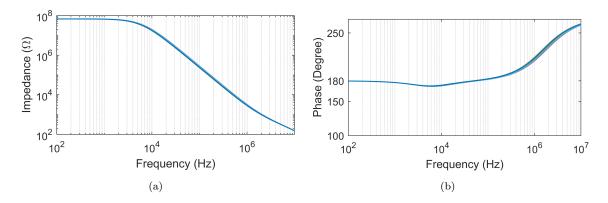

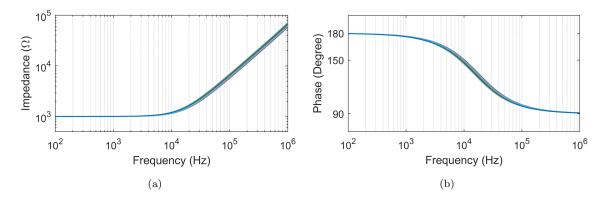

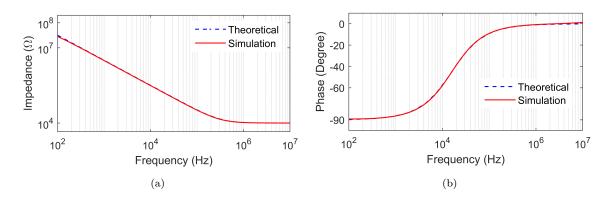

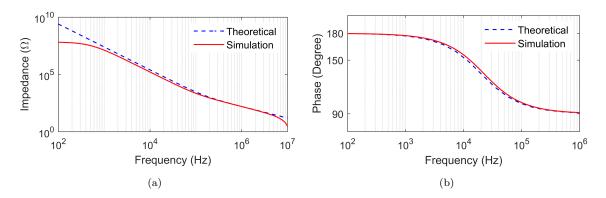

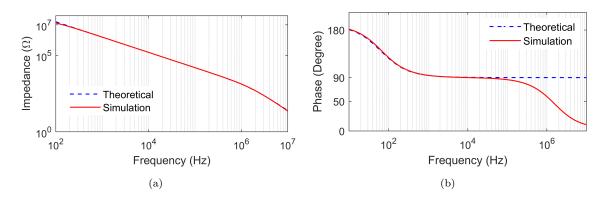

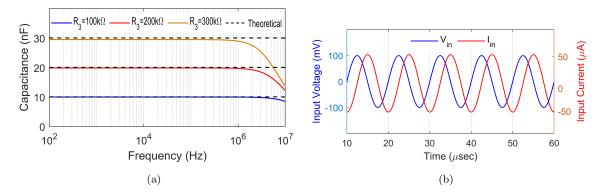

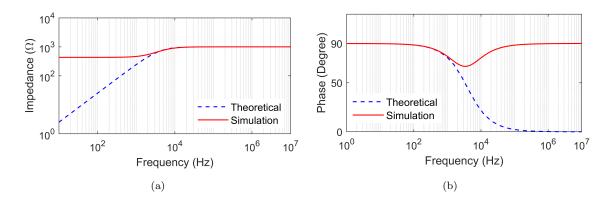

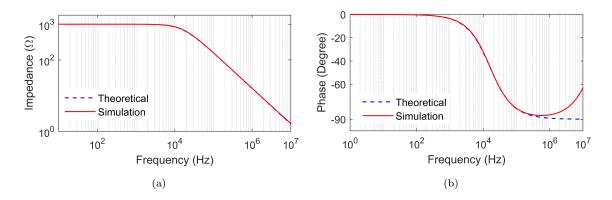

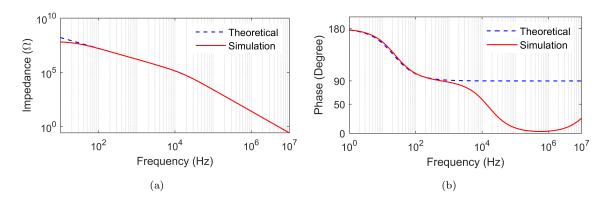

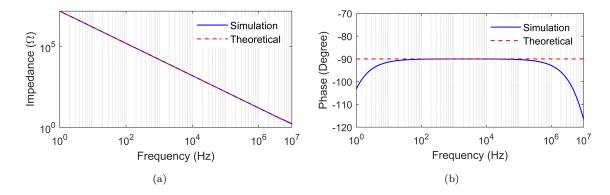

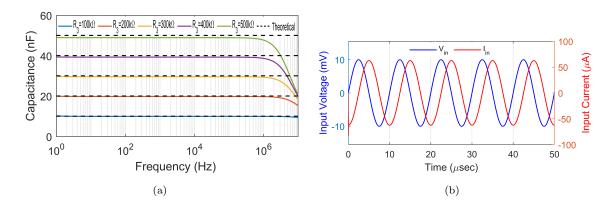

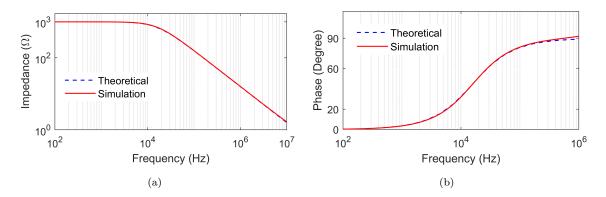

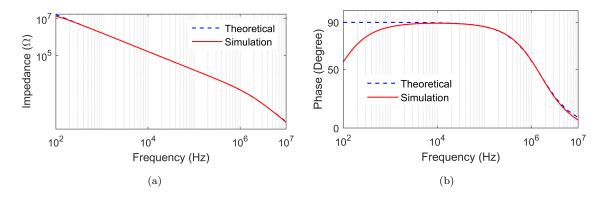

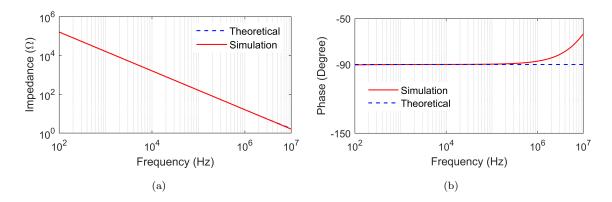

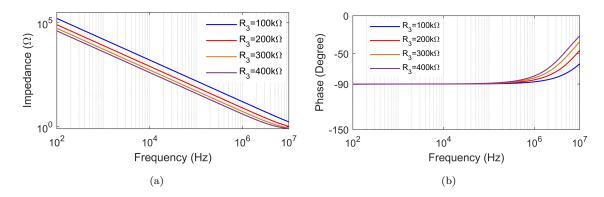

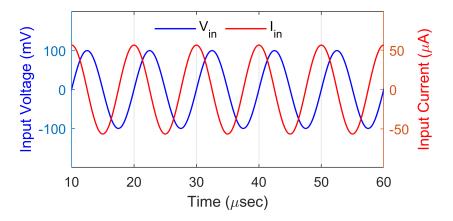

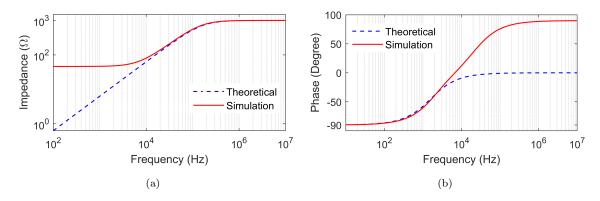

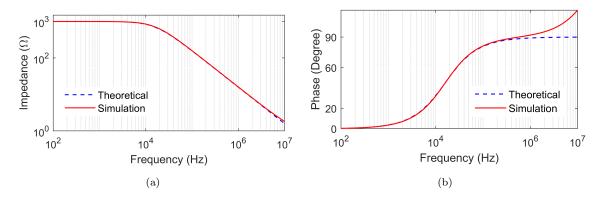

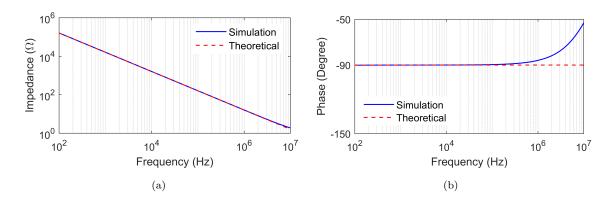

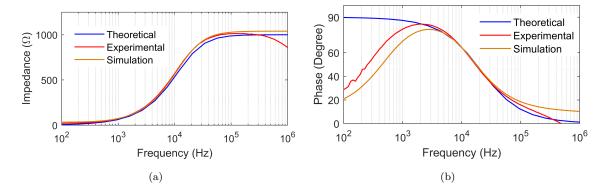

| 3.25 | Simulated magnitude and phase of the impedance of CM circuit along with theoretical evaluations                                          | 135  |

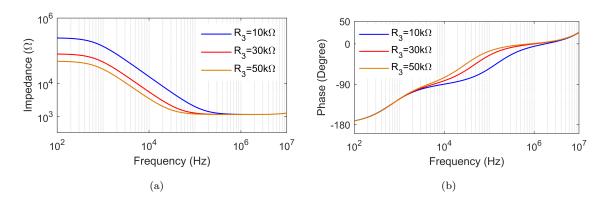

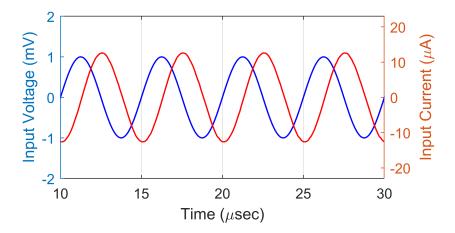

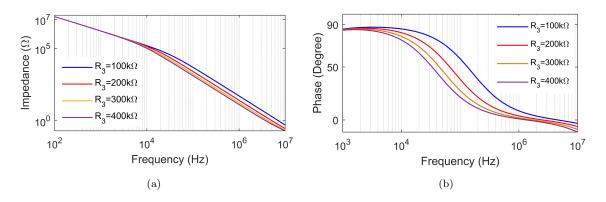

| 3.26 | Transient input voltage and current of CM circuit at 100kHz                                                                              | 135  |

| 3.27 | (a) Variation in capacitance with Resistor R (b) Variation in MF with                                                                    |      |

|      | $I_{Bias}$                                                                                                                               | 136  |

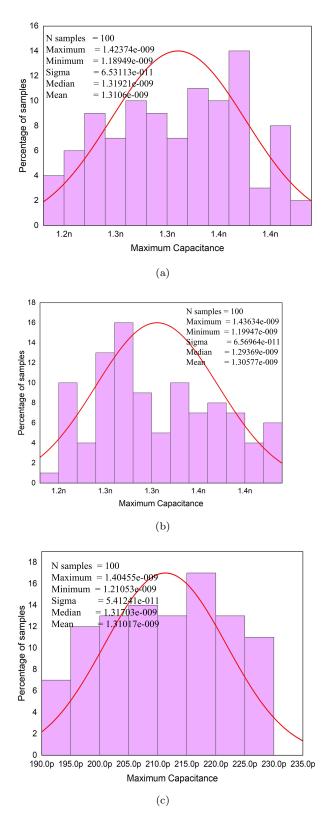

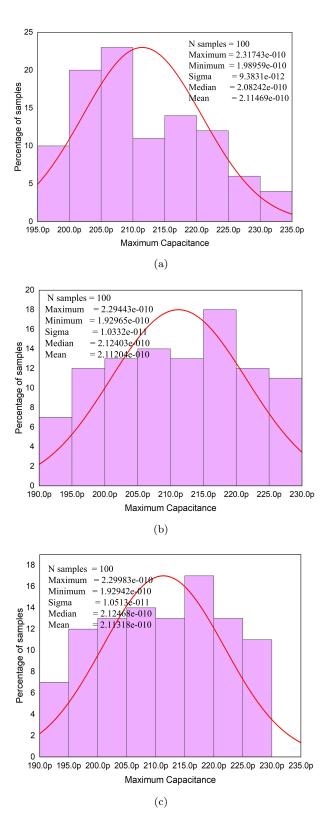

| 3.28 | Monte-Carlo results (a) Magnitude (b) Phase (c) Histogram                                                                                | 137  |

| 3.29 | Simulated (a) magnitude and (b) phase responses of CM circuit under                                                                      |      |

|      | different temperatures                                                                                                                   | 138  |

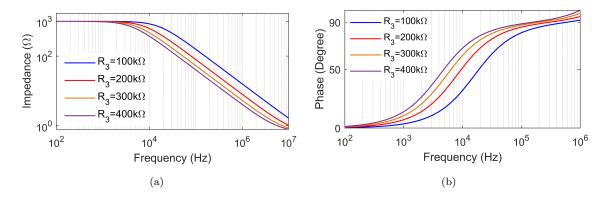

| 3.30 | Simulated frequency and transient responses of the proposed parallel                                                                     |      |

|      | RL circuit (a) Magnitude responses (b) Phase responses (c) Input                                                                         |      |

|      | voltage and current                                                                                                                      |      |

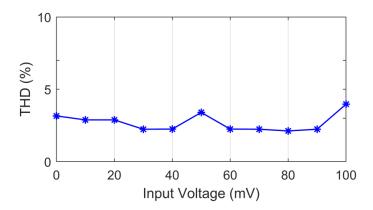

|      | Variation in THD with input voltage                                                                                                      |      |

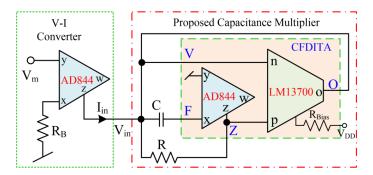

|      | Schematic of proposed CM circuit using off-the-shelf ICs                                                                                 | 141  |

| 3.33 | Experimentally obtained magnitude, phase and time domain results                                                                         |      |

|      | for CM circuit                                                                                                                           | 142  |

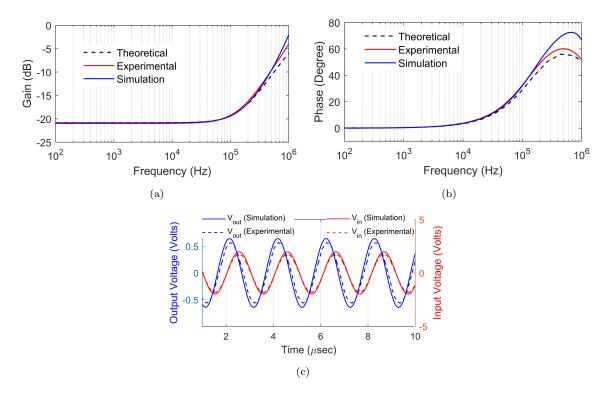

| 3.34 | Experimentally obtained frequency and transient responses of parallel                                                                    | 1.40 |

| 0.05 | RL simulator                                                                                                                             | 143  |

| 3.35 | Application example of proposed capacitance multiplier as first order                                                                    | 1.45 |

| 2 26 | low pass filter (a) circuit model (b) Implementation using CFDITA . Application example of proposed capacitance multiplier as second or- | 140  |

| 5.50 | der high pass filter (a) circuit model (b) Realization using CFDITA.                                                                     | 146  |

| 2 27 | Experimentally obtained frequency response of first order LPF shown                                                                      | 140  |

| 0.01 | in Fig. 3.35                                                                                                                             | 146  |

| 3 38 | Experimentally obtained frequency response of second order HPF                                                                           | 110  |

| 0.00 | shown in Fig. 3.36                                                                                                                       | 147  |

|      |                                                                                                                                          |      |

| 4.1  | Lossless grounded capacitance multiplier circuits proposed in<br>[154] $$ .                                                              | 151  |

| 4.2  | VCII based grounded CM circuit with positive multiplication factor                                                                       |      |

|      | proposed in [155], $C_{\text{eq}} = KC \dots \dots \dots \dots \dots \dots$                                                              | 151  |

| 4.3  | VCII-based grounded capacitive multiplier circuit proposed in [156]                                                                      |      |

|      | with (a) positive multiplication factor (b) negative multiplication factor                                                               | r152 |

| 4.4  | (a) Floating positive capacitive multiplier circuit proposed in [157]                                                                    |      |

|      | (b) Floating negative capacitive multiplier circuit proposed in [157] .                                                                  | 152  |

| 4.5         | (a) Positive impedance simulator circuit proposed in [158] (b) Nega-                                    |      |

|-------------|---------------------------------------------------------------------------------------------------------|------|

|             | tive impedance simulator circuit proposed in [158]                                                      | 153  |

| 4.6         | VCII-based simulated grounded inductor proposed in [68], $L_{eq} = CR_1R_2$ :                           | 153  |

| 4.7         | (a) FDNR (b) FDNC (c) Parallel R-L (d) Series R-L proposed in [67]                                      | 154  |

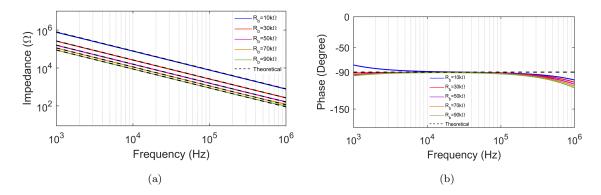

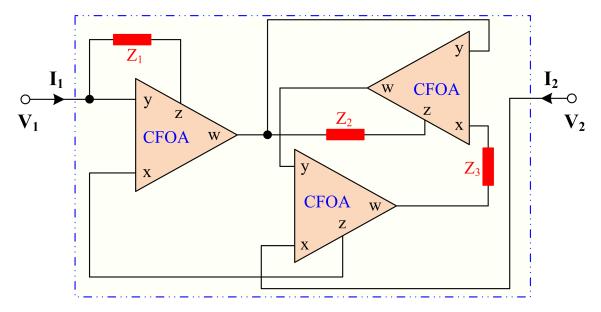

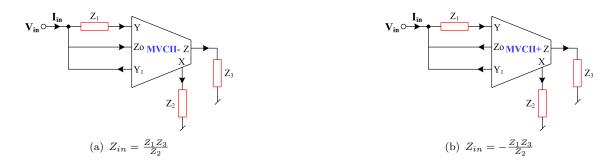

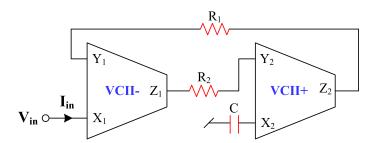

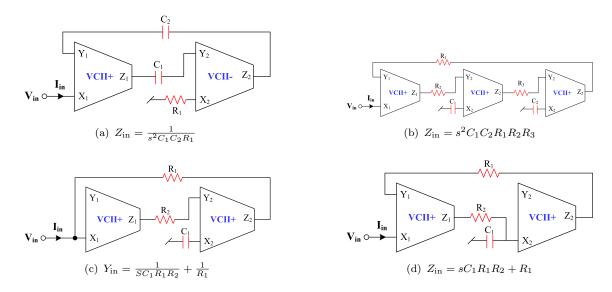

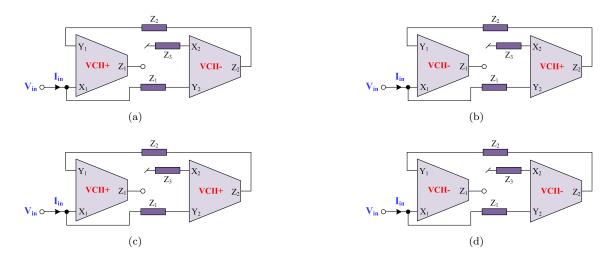

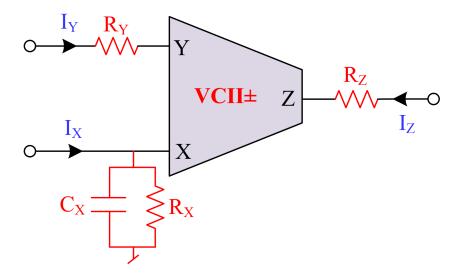

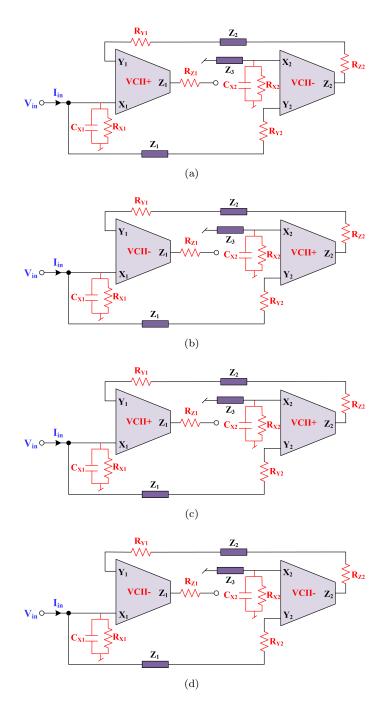

| 4.8         | Proposed generalized grounded series immittance simulators                                              | 155  |

| 4.9         | CMOS structure [68] of (a) VCII+ and (b) VCII                                                           | 159  |

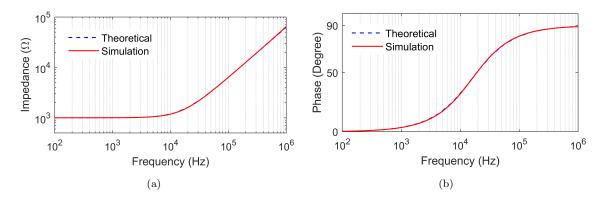

| 4.10        | Frequency responses of series R-L simulator (a) impedance and (b)                                       |      |

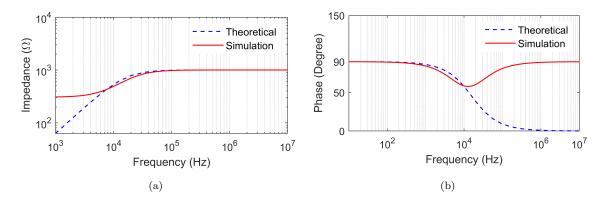

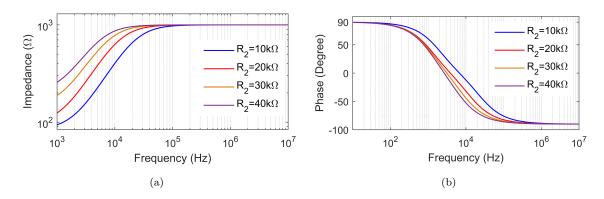

|             | phase                                                                                                   | 160  |

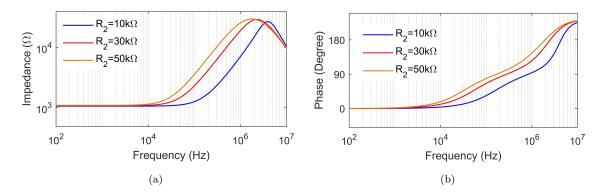

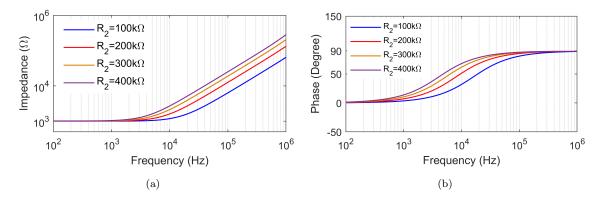

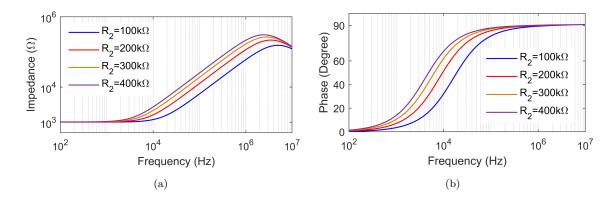

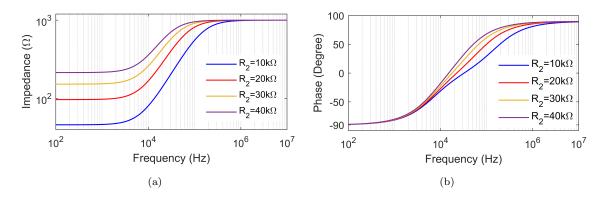

| 4.11        | Frequency responses of series R-L simulator for different values of $R_2$                               |      |

|             | (a) magnitude (b) phase                                                                                 | 160  |

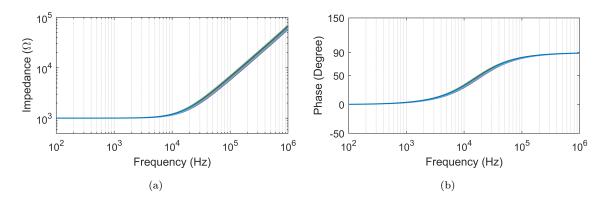

| 4.12        | AC Monte-Carlo results of series R-L simulator (a) magnitude re-                                        | 1.01 |

| 4.10        | sponses (b) Phase responses                                                                             |      |

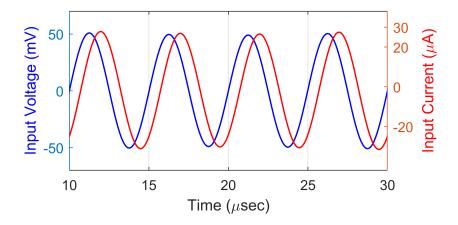

|             | Transient responses of input voltage and current of series R-L simulator.                               | 161  |

| 4.14        | Frequency responses of series R-C simulator (a) impedance and (b)                                       | 160  |

| 4 1 5       | Phase                                                                                                   | 102  |

| 4.13        | Frequency responses of series R-C simulator for different value of resistors (a) magnitude (b) phase    | 169  |

| <i>1</i> 16 | AC Monte-Carlo results of series R-C simulator (a) magnitude re-                                        | 102  |

| 4.10        | sponses (b) Phase responses                                                                             | 162  |

| 4.17        | Transient responses of input voltage and current for series R-C simulator.                              |      |

|             | Frequency responses (a) impedance and (b) phase of the series C-D                                       |      |

|             | simulator of Circuit-1                                                                                  | 163  |

| 4.19        | Frequency responses of (a) magnitude (b) phase of series C-D simu-                                      |      |

|             | lator at different value of resistors                                                                   | 164  |

| 4.20        | AC Monte-Carlo results of series C-D simulator (a) magnitude re-                                        |      |

|             | sponses (b) Phase responses                                                                             | 164  |

| 4.21        | Transient responses of input voltage and current for series C-D sim-                                    |      |

|             | ulator of Circuit-1                                                                                     | 164  |

| 4.22        | Frequency responses of series R-L simulator of Circuit-2 (a) impedance                                  |      |

| 4.00        | and (b) phase                                                                                           | 165  |

| 4.23        | Frequency responses of series R-L simulator of Circuit-2 for different                                  | 165  |

| 4.94        | values of $R_2$ (a) magnitude (b) phase                                                                 | 100  |

| 4.24        | AC Monte-Carlo results of series R-L simulator of Circuit-2 (a) magnitude responses (b) Phase responses | 166  |

| 1 25        | Transient responses of input voltage and current of series R-L simu-                                    | 100  |

| 4.20        | lator of Circuit-2                                                                                      | 166  |

| 4.26        | Frequency responses of series R-C simulator of Circuit-2 (a) impedance                                  | 100  |

| 1.20        | and (b) phase                                                                                           | 167  |

| 4.27        | Frequency responses of series R-C simulator of Circuit-2 for different                                  |      |

| •           | value of resistors (a) magnitude (b) phase                                                              | 167  |

| 4.28        | AC Monte-Carlo results of series R-C simulator of Circuit-2 (a) mag-                                    |      |

|             | nitude responses (b) Phase responses                                                                    | 168  |

| 4.29 | Transient responses of input voltage and current for series R-C simulator of Circuit-2                                                     | 168  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.30 | Frequency responses (a) impedance and (b) phase of the series C-D simulator of Circuit-2                                                   | 169  |

| 4.31 | Frequency responses of (a) magnitude (b) phase of series C-D simulator at different value of resistors                                     |      |

| 4.32 | AC Monte-Carlo results of series C-D simulator (a) magnitude responses (b) Phase responses                                                 |      |

| 4.33 | Transient responses of input voltage and current for series C-D simulator of Circuit-2                                                     |      |

| 4.34 | Frequency responses of series R-L simulator (a) impedance and (b) phase of Circuit-3                                                       |      |

| 4.35 | Frequency responses of series R-L simulator for different values of $R_2$ (a) magnitude (b) phase                                          |      |

| 4.36 | AC Monte-Carlo results of series R-L simulator of Circuit-3 (a) magnitude responses (b) Phase responses                                    |      |

| 4.37 | Transient responses of input voltage and current of series R-L simulator of Circuit-3                                                      |      |

| 4.38 | Frequency responses of series R-C simulator (a) impedance and (b) phase                                                                    |      |

| 4.39 | Frequency responses of series R-C simulator for different value of resistors (a) magnitude (b) phase                                       |      |

| 4.40 | AC Monte-Carlo results of series R-C simulator (a) magnitude responses (b) Phase responses                                                 |      |

|      | Transient responses of input voltage and current for series R-C simulato Frequency responses (a) impedance and (b) phase of the series C-D | r173 |

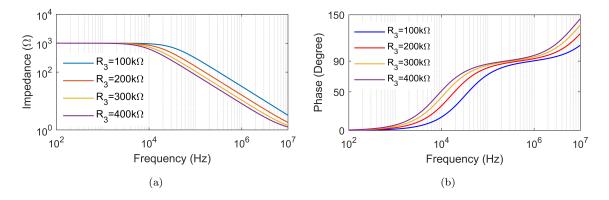

| 4.43 | simulator of Circuit-3                                                                                                                     |      |

| 4.44 | lator at different value of resistors                                                                                                      |      |

| 4.45 | sponses (b) Phase responses                                                                                                                | 175  |

| 4.46 | ulator of Circuit-3                                                                                                                        |      |

| 4.47 | phase of Circuit-4                                                                                                                         |      |

| 4.48 | (a) magnitude (b) phase                                                                                                                    |      |

| 4.49 | nitude responses (b) Phase responses                                                                                                       |      |

| 4.50 | lator of Circuit-4                                                                                                                         |      |

|      | phase                                                                                                                                      | 177  |

| 4.51 | Frequency responses of series R-C simulator for different value of resistors (a) magnitude (b) phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 178 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1 59 | AC Monte-Carlo results of series R-C simulator (a) magnitude re-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 110 |

| 4.02 | sponses (b) Phase responses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 178 |

| 4.53 | Transient responses of input voltage and current for series R-C simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |