# **Designing of Battery Charger with Totem-Pole PFC and Phase-Shift Full Bridge Converter**

A DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE AWARD OF THE DEGREE

OF

**MASTER OF TECHNOLOGY**

IN

**POWER ELECTRONICS AND SYSTEMS**

Submitted by:

**Shubham Sharma**

2K23/PES/05

Under the supervision of

**Dr. Mayank Kumar**

(Assistant Professor, EED, DTU)

**DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**M.Tech (Power Electronics and Systems)**

**Shubham Sharma**

**2025**

**May, 2025**

**DEPARTMENT OF ELECTRICAL ENGINEERING**

**DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CANDIDATE'S DECLARATION**

I, Shubham Sharma, Roll No. 2K23/PES/05 student of MTech (Power Electronics & Systems), hereby declare that the project Dissertation titled **“Designing of Battery Charger with Totem-Pole PFC and Phase-Shift Full Bridge Converter”** which is submitted by me to the Department of Electrical Engineering, Delhi Technological university, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship, or other similar title or recognition.

**Place:** Delhi

**(Shubham Sharma)**

**Date:** 7<sup>th</sup> June 2025

**DEPARTMENT OF ELECTRICAL ENGINEERING**

**DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CERTIFICATE**

I hereby certify that the project Dissertation titled "**Designing of Battery Charger with Totem-Pole PFC and Phase-Shift Full Bridge Converter**" which is Submitted by **Shubham Sharma**, Roll No. **2K23/PES/05**, Department of Electrical Engineering, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the student under my supervision. To the best of my knowledge, this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

**Place:** Delhi

**Dr. Mayank Kumar**

**Date:** 31<sup>st</sup> May 2025

**(SUPERVISOR)**

**DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**ACKNOWLEDGEMENT**

I would like to express my gratitude towards all the people who have contributed their precious time and effort to help me without whom it would not have been possible for me to understand and complete the project. I would like to thank **Dr. Mayank Kumar, DTU Delhi, Department of Electrical Engineering**, my Project Supervisor, for supporting, motivating, and encouraging me throughout this work was carried out. His readiness for consultation always, his educative comments, and his concern and assistance even with practical things have been invaluable.

Finally, I must express my very profound gratitude to my parents, seniors, and my friends for providing me with unfailing support and continuous encouragement throughout the research work.

**Date:** 31<sup>st</sup> May 2025

**Shubham Sharma**

M.tech (Power Electronics & Systems)

Roll No. 2K23/PES/05

## **ABSTRACT**

High reliability and efficiency are critical factors in the development of a battery charger. Therefore, battery charging systems must be designed to comply with grid standards and ensure safe operation. This research discusses the design of a charger that incorporates a Totem-Pole Power Factor Correction (PFC) and a Phase-Shift Full Bridge (PSFB) DC-DC converter. Implementing a power factor correction (PFC) converter will allow one to connect straight to the power grid for AC/DC power conversion and maximize the actual power going to the downstream DC/DC converters. The Phase-Shift full-bridge (PSFB) converter is a high-performance power supply with very fast transient response, given its high-power density and high converter efficiency. The devices are engineered to comply with Power Factor requirements and ensure isolation between the voltage source and the battery. The integration of PSFB provides these areas with galvanic isolation and efficient DC-DC conversion capabilities. A PSFB design built on the Modular Hardware-System-Common Redundant Power Supply (M-CRPS) base specification shows the ability of a PSFB converter. The integration of these topologies results in a charger design that is both compact and highly efficient. The device is capable of operating across a range of voltages while maintaining a stable output power suitable for battery charging.

Simulation and experimental findings support and examine the power and efficiency aspects. This work assumes that battery chargers can be developed utilizing these systems. This research also addresses the challenges associated with charging technology by enhancing efficiency, reliability, and compliance with stringent regulations.

**Keywords-** *Battery charger Topology, Phase-Shift Full Bridge (PSFB), Power Factor Correction, Soft-Switching, Totem-Pole PFC, Zero Voltage Switching (ZVS)*

## **TABLE OF CONTENTS**

|                                                                                |              |

|--------------------------------------------------------------------------------|--------------|

| <b>CANDIDATE DECLARATION</b>                                                   | <b>i</b>     |

| <b>CERTIFICATE</b>                                                             | <b>ii</b>    |

| <b>AKNOWLEDGEMENT</b>                                                          | <b>iii</b>   |

| <b>ABSTRACT</b>                                                                | <b>iv</b>    |

| <b>TABLE OF CONTENTS</b>                                                       | <b>v</b>     |

| <b>LIST OF FIGURES</b>                                                         | <b>vii</b>   |

| <b>LIST OF TABLES</b>                                                          | <b>ix</b>    |

| <b>LIST OF ABBREVIATIONS</b>                                                   | <b>x</b>     |

| <b>CHAPTER 1 Introduction...</b>                                               | <b>11-18</b> |

| 1.1.Background.....                                                            | 11           |

| 1.1.1. Introduction to Various battery charging topologies.....                | 11           |

| 1.1.2 Application of Battery Charger.....                                      | 13           |

| 1.2.Motivation.....                                                            | 16           |

| 1.3.Objective and Scope .....                                                  | 17           |

| <b>CHAPTER 2 Literature Review .....</b>                                       | <b>19-25</b> |

| 2.1. Introduction and Evolution of Battery Charger Topologies.....             | 19           |

| 2.1.1. Power Factor Correction (PFC) Topologies .....                          | 19           |

| 2.1.2. DC-DC Converters for Battery Charging .....                             | 20           |

| 2.2. Proposed Configuration.....                                               | 21           |

| 2.2.1. Totem-Pole PFC Converter .....                                          | 22           |

| 2.2.2. Phase Shift Full Bridge Converter (PSFB).....                           | 23           |

| <b>CHAPTER 3 System Design of the Battery Charger .....</b>                    | <b>26-36</b> |

| 3.1. Introduction.....                                                         | 26           |

| 3.2. Totem-Pole Power Factor Correction.....                                   | 26           |

| 3.3. Phase Shift Full Bridge (PSFB) Converter .....                            | 29           |

| 3.3.1. Benefits of Phase Shift Full Bridge Converter.....                      | 30           |

| 3.3.2. Losses in Phase Shift Full Bridge Converter .....                       | 30           |

| 3.3.3. Relevance of Phase Shift Full Bridge Converter in Battery Charger ..... | 30           |

| 3.4. Mode of Operations of Charger .....                                       | 31           |

| 3.4.1. Positive Half-Cycle Operation .....                                     | 32           |

| 3.4.2. Negative Half-Cycle Operation.....                                      | 35           |

| <b>CHAPTER 4 Designing of Battery Charger .....</b>                            | <b>38-45</b> |

| 4.1. Totem Pole PFC Designing.....                                             | 38           |

| 4.1.1. Input Filter Inductor Design.....                                       | 38           |

| 4.1.2. Maximum Inductor Current .....                                          | 39           |

| 4.1.3. Output DC Link Capacitor Design.....                                    | 40           |

| 4.2. Phase Shift Full Bridge Converter Designing.....                          | 41           |

| 4.2.1. Output Inductor and Capacitor Filter Designing.....                     | 41           |

|                                                                      |              |

|----------------------------------------------------------------------|--------------|

| 4.3. Key Semiconductor and Passive Component Selection.....          | 43           |

| 4.3.1. Power Semiconductor Selection.....                            | 44           |

| 4.3.2. Different Control Strategies of Totem-Pole PFC and PSFB ..... | 45           |

| <b>CHAPTER 5 Mathematical Modelling and Analysis .....</b>           | <b>46-53</b> |

| 5.1. Totem Pole PFC Converter .....                                  | 46           |

| 5.1.1. Large-Signal Modelling .....                                  | 46           |

| 5.1.2. Derivation of 0-Average Index Equations .....                 | 46           |

| 5.1.3. Derivation of 1-Average Index Equations .....                 | 48           |

| 5.1.4. Complete Large-Signal State-Space Model .....                 | 48           |

| 5.1.5. Small-Signal Modelling .....                                  | 49           |

| 5.2. Phase Shift Full Bridge Converter.....                          | 50           |

| <b>CHAPTER 6 Simulation Study and Conclusion.....</b>                | <b>54-60</b> |

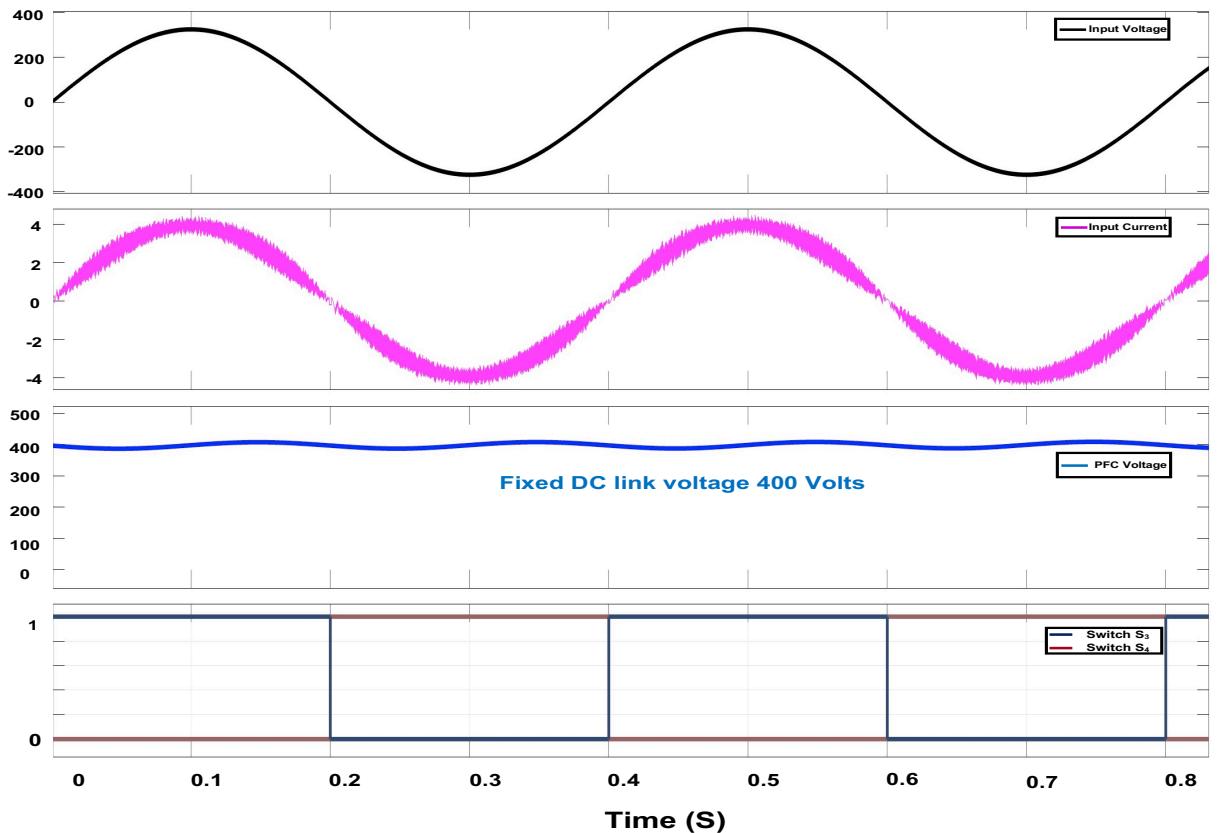

| 6.1. Stage 1: Totem Pole Power Factor Correction.....                | 54           |

| 6.2. Stage 2: Phase Shift Full Bridge (PSFB) Converter .....         | 55           |

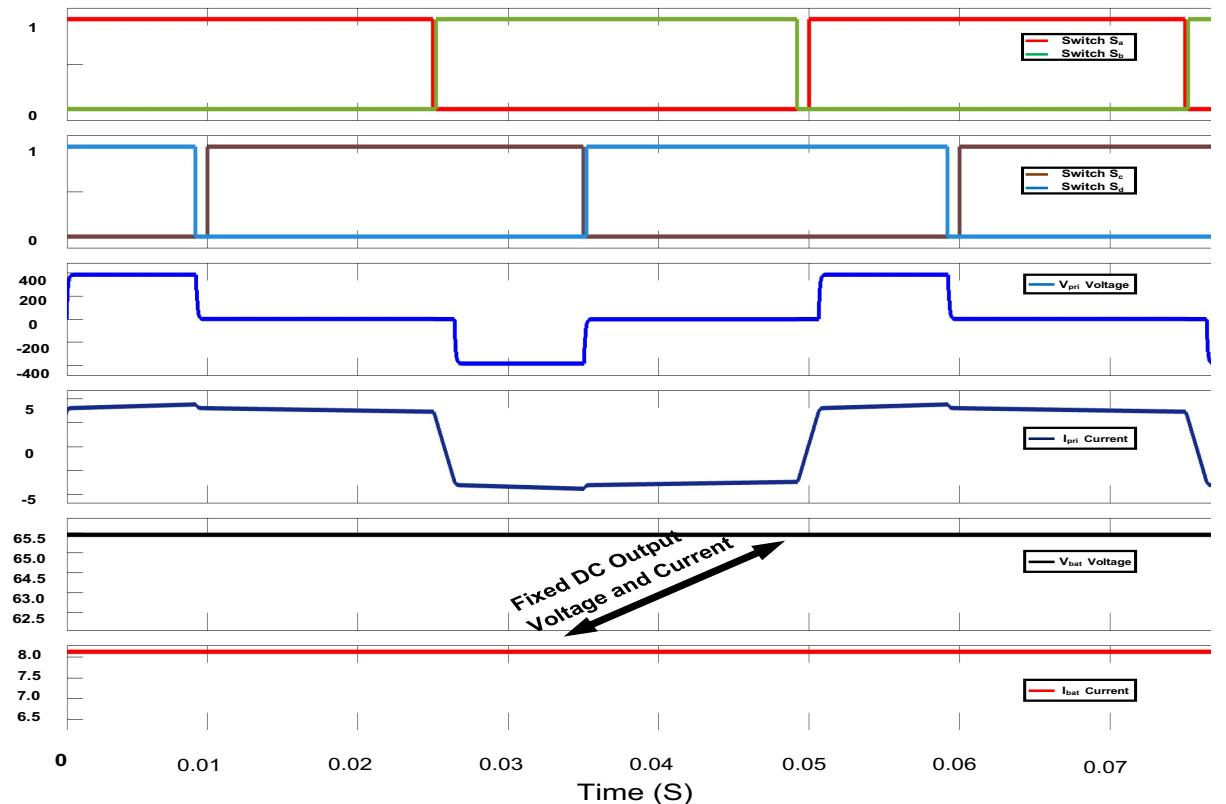

| 6.3. Conclusion .....                                                | 58           |

| 6.4. Future Scope .....                                              | 59           |

| <b>References .....</b>                                              | <b>62-65</b> |

| <b>Appendix A.....</b>                                               | <b>66-69</b> |

## **LIST OF FIGURES**

| <b>Figure No.</b> | <b>Figure Name</b>                                                                      | <b>Page No.</b> |

|-------------------|-----------------------------------------------------------------------------------------|-----------------|

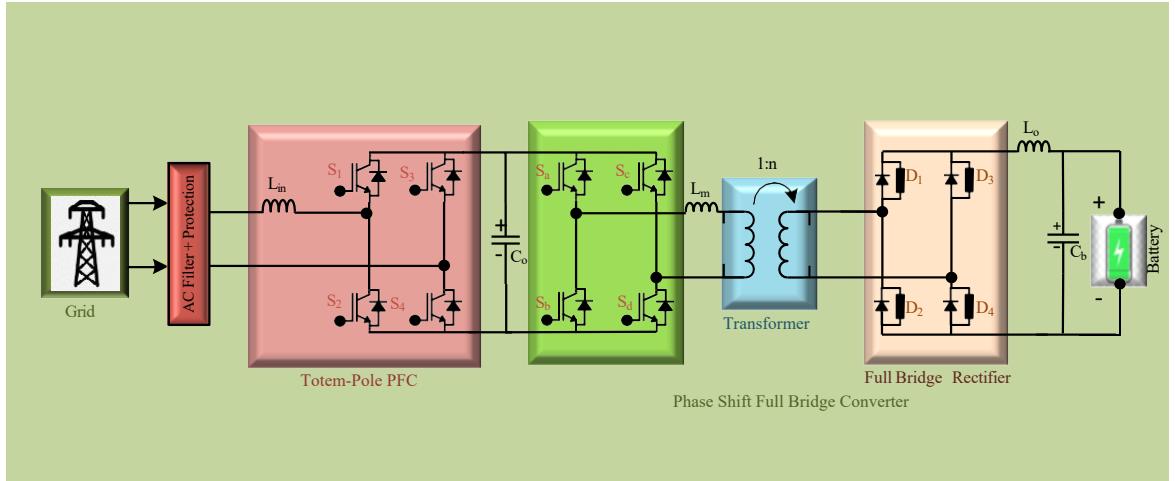

| Figure.1.1        | Typical circuit architecture of a battery charger.                                      | 13              |

| Figure.1.2        | Basic Power flow diagram of Battery Charger                                             | 13              |

| Figure.1.3        | Power flow diagram of E. V. Battery Charger                                             | 14              |

| Figure.2.1        | Block Diagram for Proposed Battery Charger                                              | 21              |

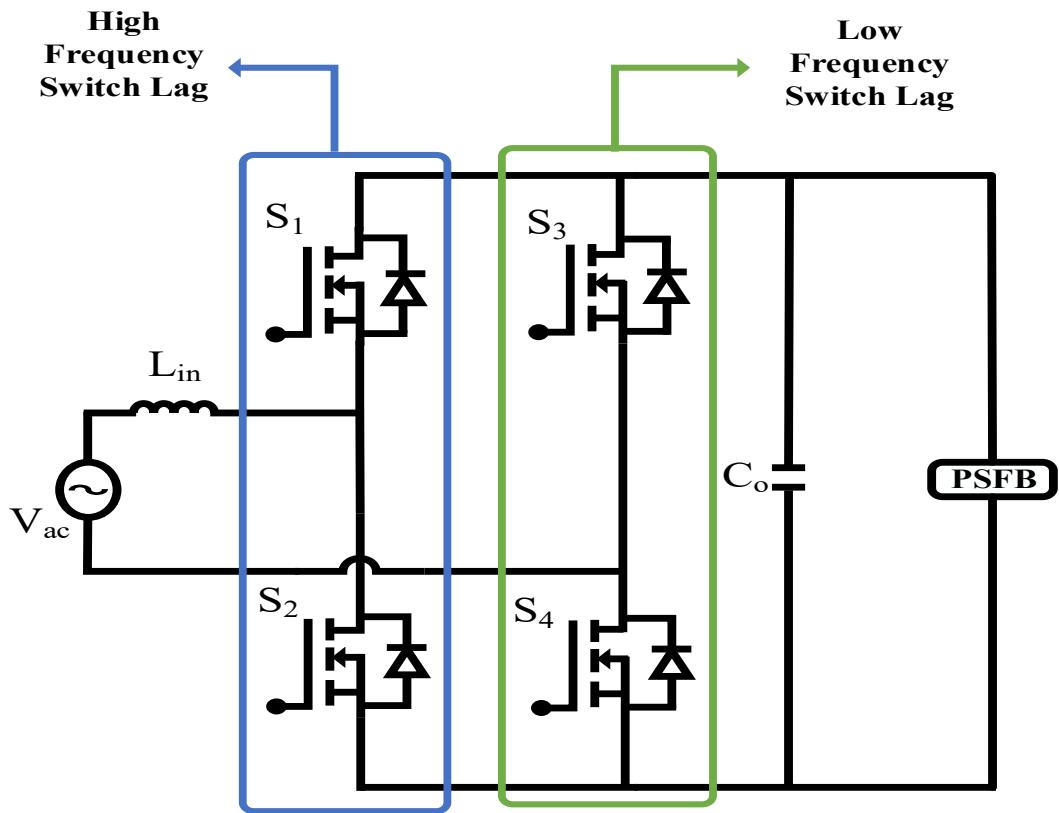

| Figure.2.2        | Proposed Battery Charger Configuration                                                  | 22              |

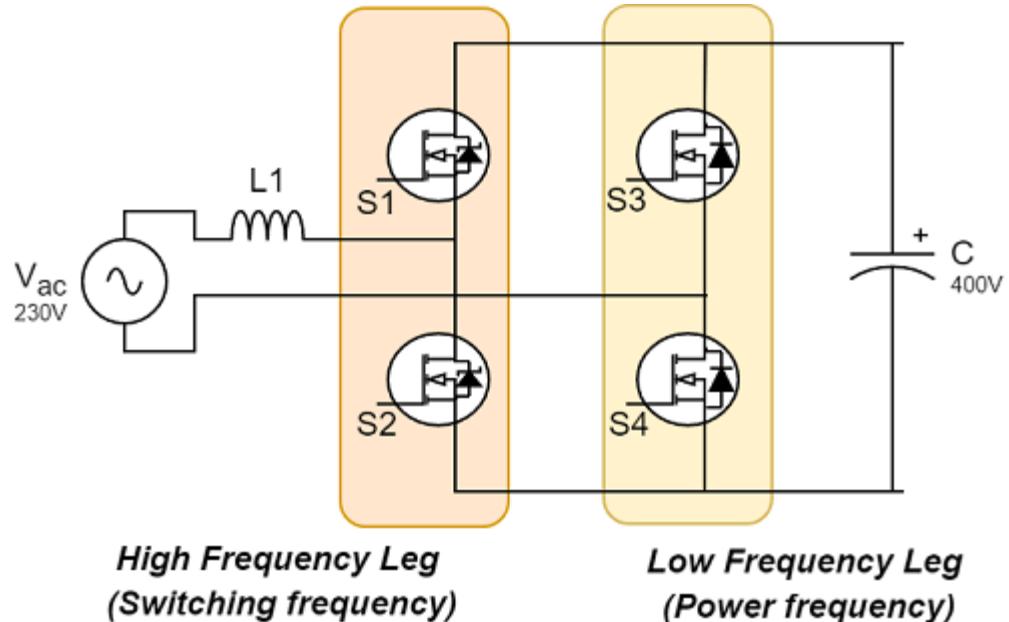

| Figure.2.3        | Totem Pole Power Factor Correction Configuration                                        | 22              |

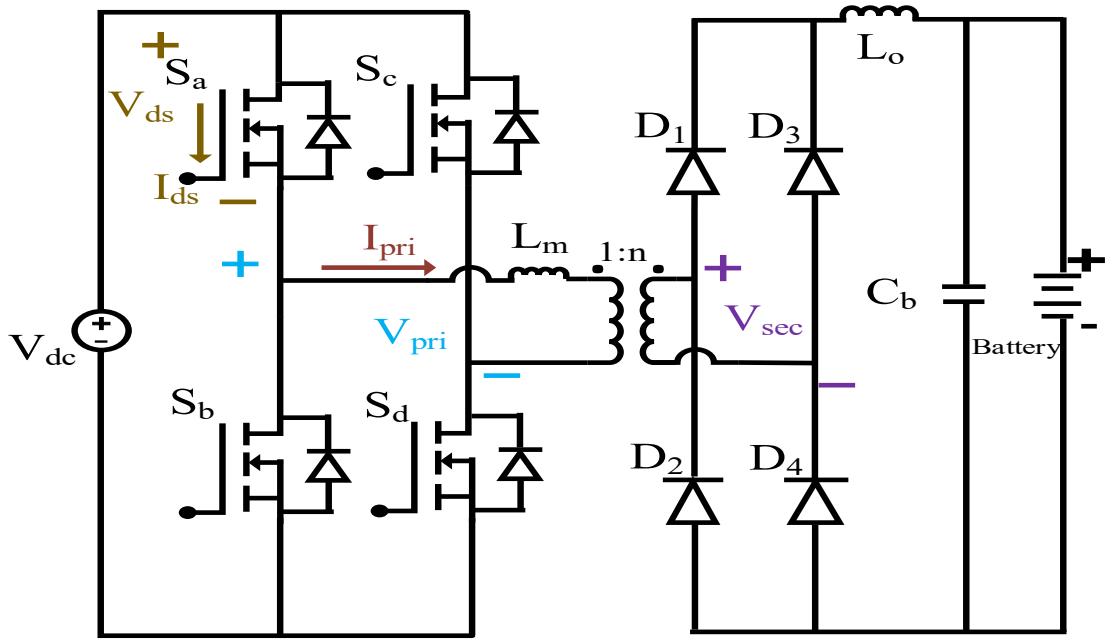

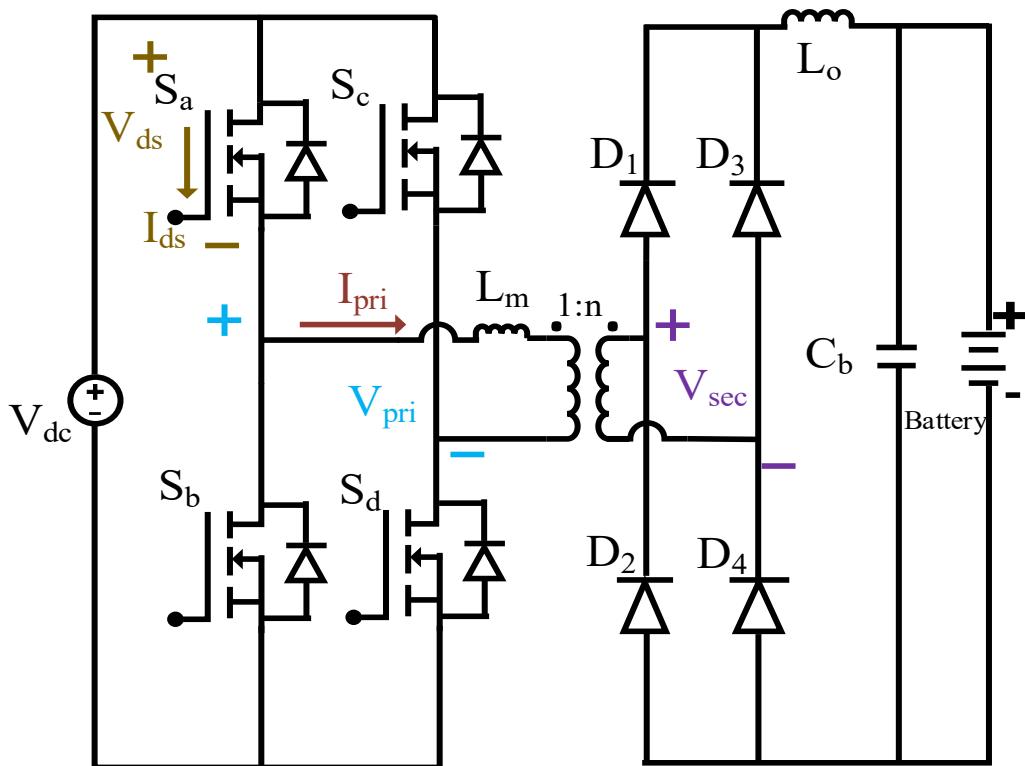

| Figure.2.4        | Phase Shift Full Bridge Converter                                                       | 24              |

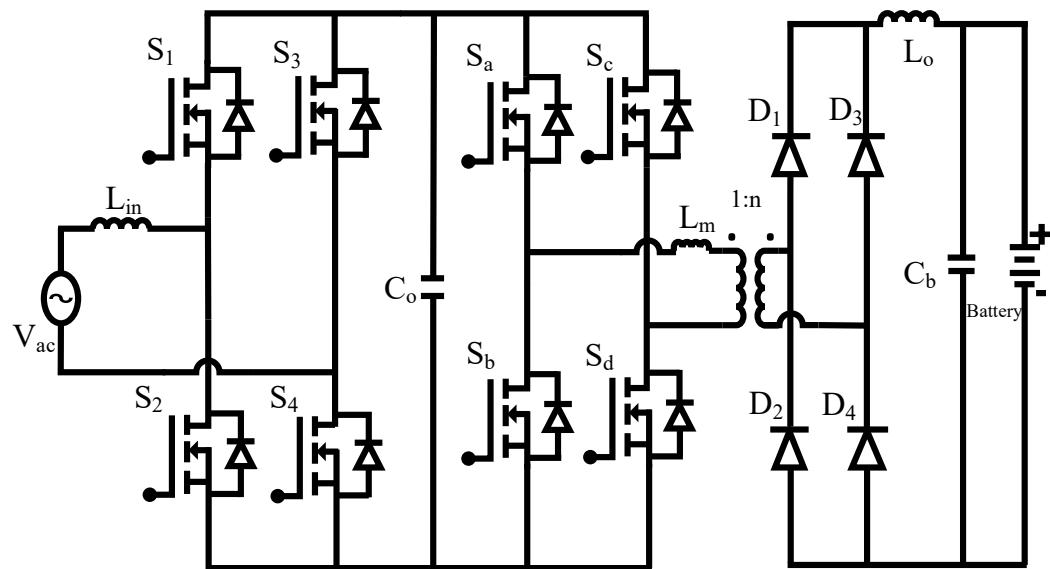

| Figure.3.1        | Battery Charger Configuration                                                           | 26              |

| Figure.3.2        | Totem Pole PFC Configuration                                                            | 27              |

| Figure.3.3        | Phase-Shift Full Bridge (PSFB) Converter                                                | 30              |

| Figure.3.4        | Positive Cycle for Input AC: Mode of Operations                                         | 32              |

| Figure.3.5        | Negative Cycle for Input AC: Mode of Operations                                         | 35              |

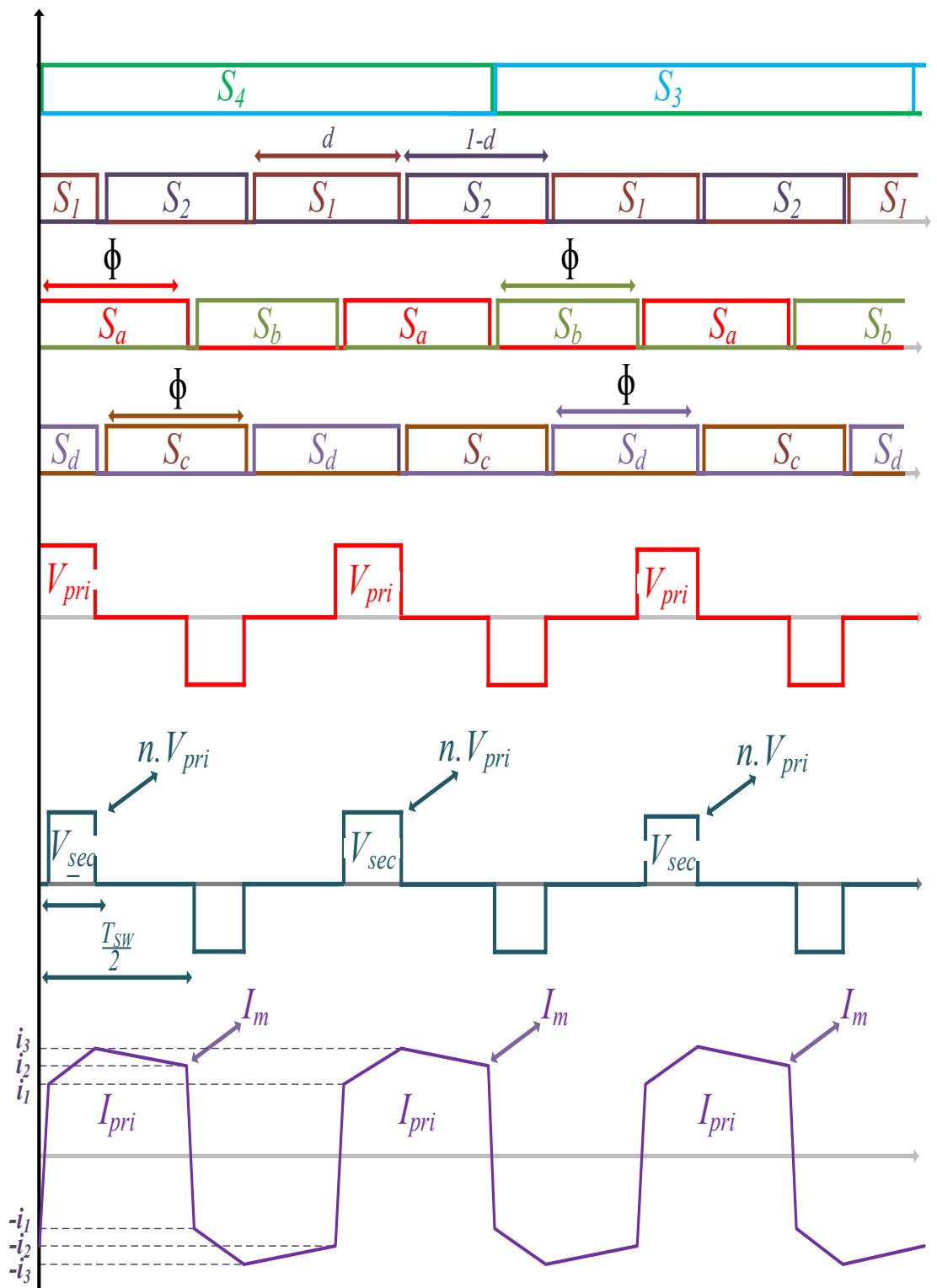

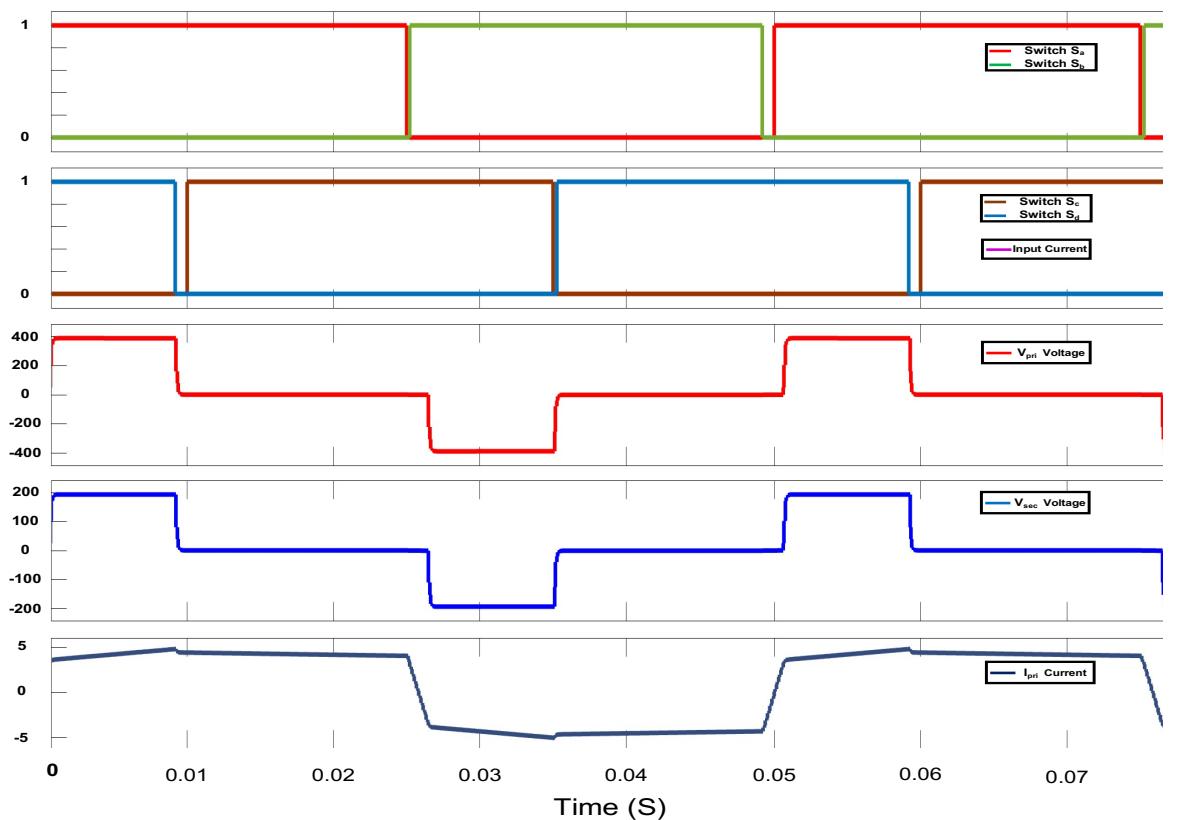

| Figure.3.6        | Switching Cycle, Primary, Secondary Voltage and Primary Current of Transformer          | 37              |

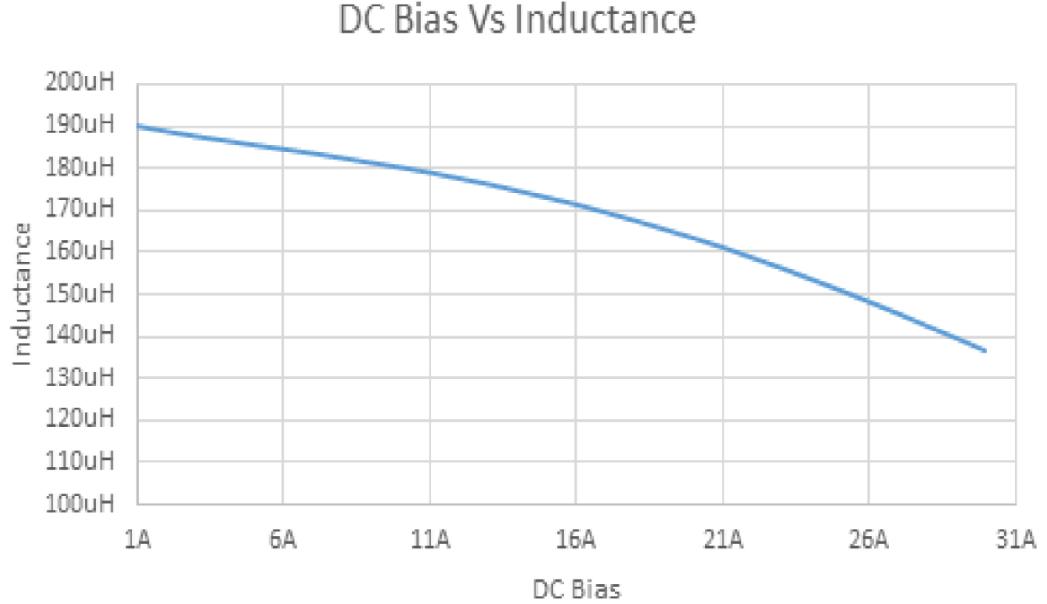

| Figure.4.1        | Totem-Pole PFC Input inductor: L vs DC bias                                             | 40              |

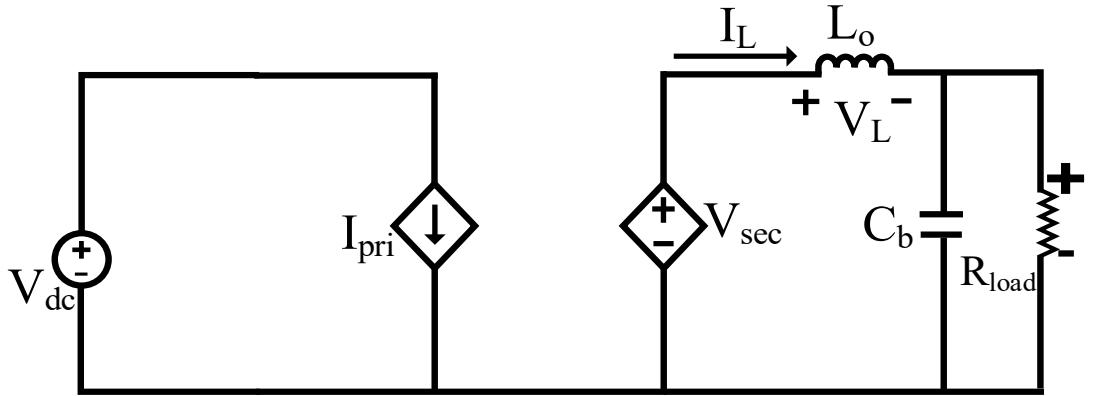

| Figure.5.1        | Averaged model of the PSFB converter with R Load                                        | 52              |

| Figure.6.1        | Input Voltage, Input Current, DC Link Output Voltage, Switching Cycle of Totem-Pole PFC | 55              |

| Figure.6.2        | Switching Cycle, Primary and Secondary Voltage, and Primary Current of Transformer.     | 56              |

|               |                                                                                           |    |

|---------------|-------------------------------------------------------------------------------------------|----|

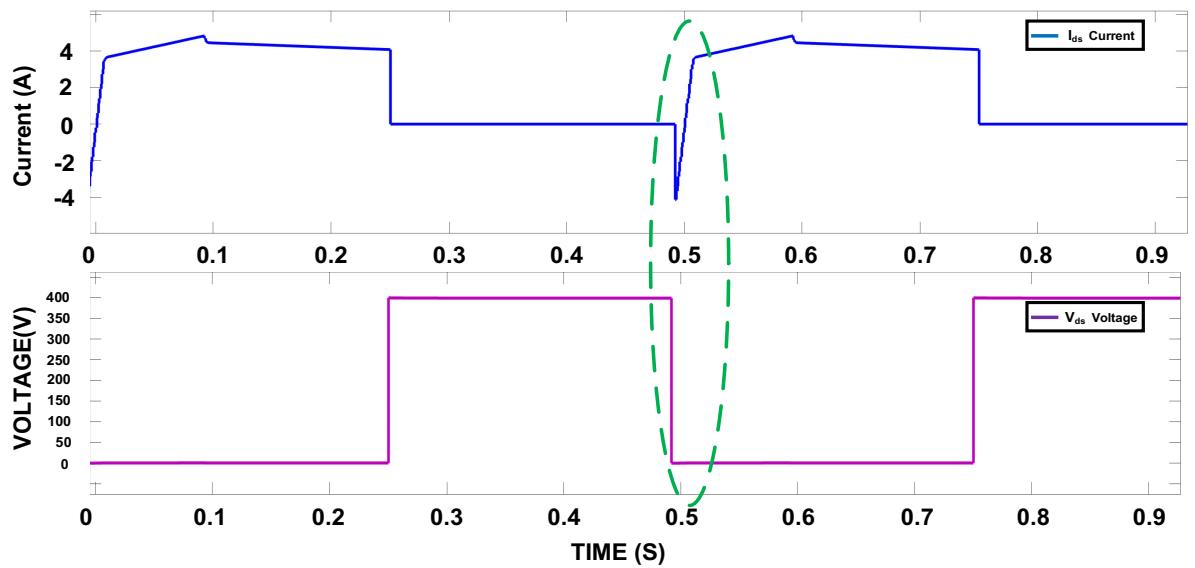

| Figure No.6.3 | PSFB MOSFET Current and Voltage with ZVS.                                                 | 57 |

| Figure No.6.4 | Switching Cycle, Primary Voltage and Current of Transformer, Battery Voltage and Current. | 57 |

## **LIST OF TABLES**

| <b>Table No.</b> | <b>Table Name</b>                                                                                | <b>Page No.</b> |

|------------------|--------------------------------------------------------------------------------------------------|-----------------|

| Table.3.1        | Comparative Table of Different Topology for PFC                                                  | 28              |

| Table 3.2.       | Different Switching Cycle for TotemPole PFC                                                      | 36              |

| Table.4.1        | Comparison of Power Semiconductor Technologies<br>(Si, SiC, GaN)                                 | 44              |

| Table.4.2        | Capacitor Technology Characteristics for Power Electronics                                       | 44              |

| Table.4.3        | Comparison of Different Control Strategies for<br>Totem-Pole PFC and PSFB                        | 45              |

| Table.6.1        | Other measurement results (Power, PF, $\cos \phi$ , and efficiency)<br>for battery-charging mode | 59              |

## **LIST OF ABBREVIATIONS**

|        |                                                          |

|--------|----------------------------------------------------------|

| PFC    | Power Factor Correction                                  |

| TP-PFC | Totem-Pole Power Factor Correction                       |

| PSFB   | Phase-Shift Full Bridge                                  |

| DAB    | Dual Active Bridge                                       |

| M      | Mutual inductance                                        |

| k      | Coupling coefficient                                     |

| EV     | Electric vehicle                                         |

| Pri    | Primary                                                  |

| Sec    | Secondary                                                |

| SRs    | Synchronous Rectifiers                                   |

| P      | Parallel                                                 |

| WBG    | Wide Bang Gap                                            |

| SOC    | State of charge                                          |

| VA     | Volt-ampere                                              |

| LC     | Filter circuit (series inductor and parallel capacitors) |

| EMI    | Electromagnetic Interference                             |

| PTE    | Power transfer efficiency                                |

| TP     | Transferred power                                        |

# Chapter 1

## INTRODUCTION

### 1.1. Background

This chapter presents an outline of Battery charging systems with Power Factor Correction configuration, including galvanic isolation with different topologies used, and their accomplishments. Additionally, this thesis highlights its objectives, scope, and contributions of the proposed topologies that can be used in a battery charger with increased efficiency and several other benefits.

#### 1.1.1. Introduction to Various Battery Charger Topologies

The design of battery chargers with high efficiency, power factor correction, and isolation has been a widely common significant area of research in recent years. Several studies have explored different topologies, combinations and control strategies to improve efficiency, enhance overall performance, and improve the system's Power Factor. Various topologies have emerged, connected with different architectures to provide isolation, correct the Power Factor near unity and improve the overall efficiency of the Battery Charger.

The conventional boost PFC is one of the most widely used topologies in battery chargers due to its very simple design and ease of achieving a high-power factor. A single-phase Boost PFC was implemented in a 3.3 kw battery charger, achieving a power factor of 0.99 and efficiency of 95% [1]. However, a drawback of this topology is the presence of a diode bridge rectifier, which introduces limits to efficiency improvement and significantly high conduction losses in the system.

A high-frequency flyback converter was designed for portable electronics, achieving an efficiency of 85% with a minimum number of components [2]. This study highlighted the advantages of galvanic isolation and ease of implementation. However, flyback converters suffer from high voltage stress on the switch and limited power handling capability, which makes them unsuitable for high-power applications such as Battery Chargers. Also, significantly high-power losses make these topologies inconvenient in modern use cases.

In [3], the author presented a bridgeless Totem-Pole PFC circuit using Gan-based switches, demonstrating an efficiency of over 98% with reduced conduction losses. The study highlighted the advantage of Totem-Pole PFC with minimum switching losses and improved thermal performance. A full-bridge LLC resonant converter is implemented in an 11-kw fast EV Charger, which achieves efficiency of 97% with minimal electromagnetic interference (EMI) [4]. The study highlighted that LLC converters provide excellent voltage regulation and reduced switching losses, making them suitable for high-power applications. However, the design complexity and sensitivity to component variation require careful tuning of the resonant circuit.

The Dual Active Bridge (DAB) converter is a widely used isolation topology for battery charging due to its bidirectional power transfer capability, soft-switching operation, and very high efficiency. A 10-kw bidirectional EV Battery charger that achieves an efficiency of 96% across a wide range of loads. However, the DAB converter also requires precise control strategies to handle variation in battery voltage to ensure stable operation [5].

Several researchers have investigated the Totem-Pole PFC topology due to its abilities, such as higher efficiency, low component count, Low Total Harmonic Distortion and near unity power Factor. The suggested Battery Charger is the integration of a Totem-Pole Power Factor Correction (PFC) stage and a Phase-Shift Full Bridge (PSFB) DC-DC converter. This strategy is focused on designing battery chargers [6] by improving efficiency, reducing the number of components required, and maintaining a small size. One of the most important parameters of the Totem-Pole PFC topology is that it has a power factor as close to unity as possible, has low total harmonic distortion (THD) and conduction losses, and exhibits a low circuit complexity.

Utilizing the best of these two topologies, the proposed system is expected to operate efficiently over a wide range of input voltages and battery chemistries and yet provide high efficiency under all operating conditions. This paper also presents the findings of a rigorous analysis of design models, simulation, and laboratory tests, demonstrating the feasibility of integrating both Totem-Pole PFC and PSFB converter stages into a single battery charger.

Through good layout design, precise component selection, and the implementation of an effective control strategy, this work demonstrates how performance is not compromised at the expense of meeting existing grid standards and environmental protection regulations.

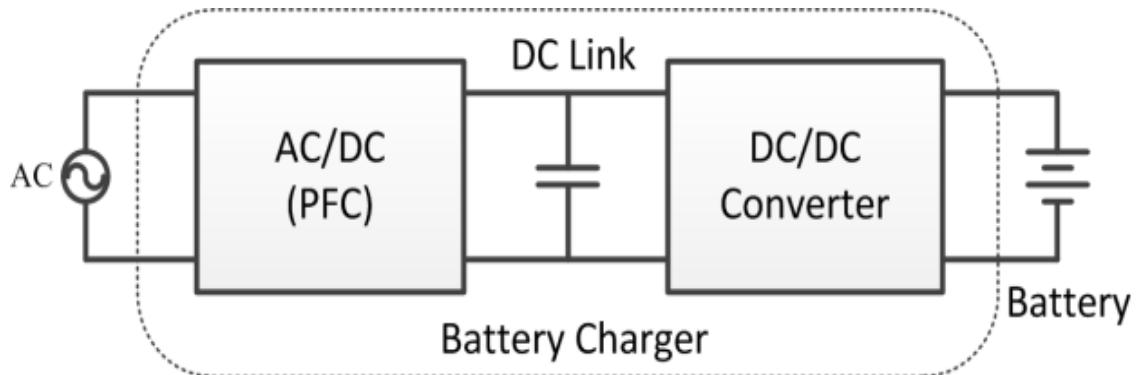

As seen in Fig. 1, A battery charger typically consists of two conversion stages: An isolated DC/DC converter with a wide voltage output for the battery and an AC/DC converter with PFC [7] [8]. Dual Active Bridge (DAB) converters and LLC resonant converters are the two most popular isolated DC/DC converters. For high efficiency and high-power density, high frequency soft-switching technology is frequently used in LLC resonant converters and DAB converters.

Fig.1.1 Typical circuit architecture of a battery charger.

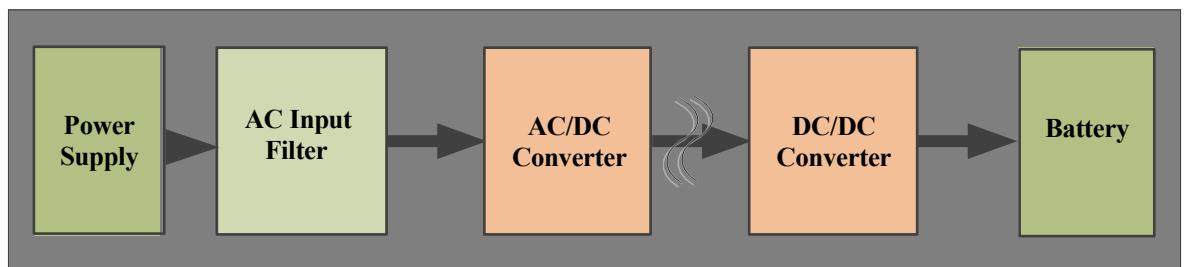

Fig.1.2 Basic Power flow diagram of Battery Charger

### 1.1.1. Applications of Battery Charger

Essential tools that restore the energy in rechargeable batteries are battery chargers, which let many devices in many industries run. The planned use of the batteries these chargers power directly influences their design and execution. With an eye toward electric vehicle (EV) charging infrastructure, below is an examination of the several uses for charged batteries [9]:

## 1. Electrified transportation and electric vehicles (EVs)

This is a well-known and fast-growing area of battery charger technology. The primary power source for: Battery electric cars, or BEVs, run only on electricity kept in large battery packs.

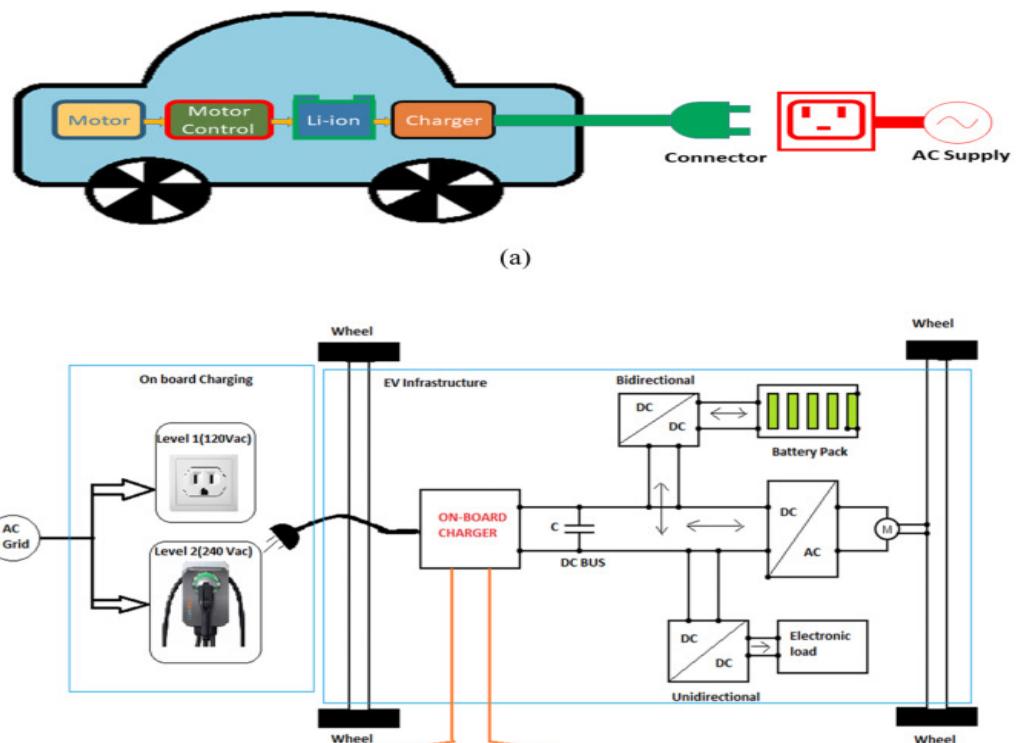

Chargers onboard (OBCs) Built into the BEV, OBCs convert AC power from public or private AC charging stations (Level 2) or household outlets (Level 1) into DC electricity to charge the vehicle's high-voltage traction battery. The electric motor or motors are then powered by the charged battery. OBC design influences charging speed at home or at business, grid interface, and user convenience.

Fig.1.3 Power flow diagram of E. V. Battery Charger

Level 3 high-power charging stations called Off-Board chargers, sometimes referred to as DC fast chargers, send high-voltage DC power straight to the BEV battery, bypassing the OBC. This makes possible far quicker charging times, which are required for quick top-ups and long-distance travel. Charged batteries in these systems allow EVs to travel on routes comparable to those travelled by internal combustion engine cars [10].

## **2. Electronics for consumers**

Communication, information access, and entertainment all depend on charged batteries in mobile devices—smartphones, tablets. Usually small AC-DC converters, chargers follow USB power delivery guidelines. Increasingly popular are wireless (inductive) chargers.

These depend on rechargeable batteries charged by specific AC-DC chargers, therefore allowing portable entertainment and mobility. For health monitoring, communication, and other smart activities, small, low-power chargers—often proprietary (magnetic, pogo-pin) or wireless—keep these devices powered. Users may take pictures and videos free from power source tethering by charging removable battery packs with specialized external chargers on cameras and camcorders [11].

Usually powered by USB, the batteries offer hours of untethered audio pleasure. The portability and wireless freedom provided by these gaming devices depend on charged batteries. Essentially portable batteries, power banks are themselves charged (usually via USB) and then used to power other electronic devices on the go.

## **3. Tools and Equipment Powered**

Cordless power tools provide notable convenience and mobility:

Drills, saws, sanders, grinders, lawn and garden equipment: These tools use strong battery packs (often Li-ion based) charged by dedicated chargers. To reduce downtime for professional and DIY users, fast chargers are common in this category. In places without convenient access to mains power, the charged batteries supply the power required for gardening, maintenance, and construction activities [12].

## **4. Commercial and Industrial Uses**

A wide variety of devices are powered by batteries, therefore improving efficiency and adaptability. Material Handling Equipment (Forklifts, Pallet Jacks, AGVs - Automated Guided Vehicles) Large battery packs—traditionally lead-acid, progressively Li-ion—are charged using industrial-grade battery chargers, including conventional, opportunity, and fast-charging systems. Charged batteries power activities in distribution centers, manufacturing plants, and warehouses. "Opportunity charging" lets batteries be charged during brief pauses without

requiring swap out.

## 5. Backup Power Systems (UPS - Uninterrupting Power Supplies):

Critical Infrastructure (Data Centers, Hospitals, Telecom): Integrated float or standby chargers in UPS systems keep batteries—usually lead-acid or Li-ion—at full charge. Should there be a power outage, these charged batteries immediately supply power to stop data loss, service disruption, or failure of vital life-support systems. UPS for Home and Office Smaller UPS systems protect other electronics and personal computers using the same concept.

### 1.2. Motivation

The fast spread of portable electronics, the growing electric vehicle (EV) market, and the rising integration of renewable energy systems have highlighted the critical need of advanced battery charging technologies. No longer merely supplementary devices, battery chargers are essential for the efficiency, performance, and usability of systems powered by batteries. Conventional charger designs frequently disappoint as these systems call for quicker charging times, more power capabilities, and more energy efficiency, showing constraints in efficiency, power density, and general performance. This calls for a paradigm change toward more advanced power conversion topologies with some major improvements.

Often using a diode bridge rectifier followed by a standard boost Power Factor Correction (PFC) stage and a hard-switched DC-DC converter, traditional battery chargers have several disadvantages. The diode bridge rectifier naturally creates notable conduction losses, so restricting the front-end efficiency. Although traditional boost PFCs increase power factor, their efficiency might be improved more. Furthermore, hard-switching methods in the DC-DC stage cause significant switching losses, particularly at higher frequencies, so limiting the possible power density and usually calling for large thermal management solutions. These inefficiencies raise running costs and energy use. Moreover, the growing harmonic rules all around call for cleaner power extraction from the grid, which presents difficulties for more basic PFC circuits. This study emphasizes the design of a battery charger using a mix of two sophisticated

power converter topologies—the Totem-Pole Power Factor Correction (PFC) converter and the Phase-Shifted Full-Bridge (PSFB) DC-DC converter—to overcome these constraints and satisfy the strict requirements of modern applications—such as high-efficiency power supplies for telecom and data centers, fast chargers for electric vehicles, and grid-interactive power systems.

### 1.3. Objective and Scope

This study mostly intends to design, test, and possibly construct a high-efficiency, high-power-factor battery charger. Combining two complex power electronic topologies—a Phase-Shifted Full-Bridge (PSFB) DC-DC converter and a Totem-Pole Power Factor Correction (PFC) stage—will help to accomplish.

**Objective:** To get low total harmonic distortion (THD) at the AC input and near unity power factor, model and design a bridgeless Totem-Pole PFC rectifier. Design and model a Phase-Shifted Full-Bridge DC-DC converter for efficient power transfer and galvanic isolation, appropriate for battery charging profiles (e.g., constant current, constant voltage). A comprehensive control system for both the PFC stage (e.g., average current mode control) and the PSFB converter (e.g., phase-shift control, including soft-switching techniques such Zero Voltage Switching (ZVS) or Zero Current Switching (ZCS) to minimize switching losses) is to be developed.

Using MATLAB/Simulink, comprehensive simulations will help to confirm the performance of the distinct stages and the integrated charger system under various operating conditions—line voltage fluctuations, load changes. Examination:

To assess the efficiency of the entire battery charger system and identify key loss reduction areas in both converter stages.

Investigate how component selection—e.g., MOSFETs, diodes, magnetics—affects the performance, efficiency, and power density of the charger.

To investigate the stability of the control loop for both PFC.

**Scope:**

1. System Specifications: Defining the input voltage range (e.g., universal AC input 90-265V).

2. Specifying the output voltage and current ratings for the battery (e.g., 64V Li-ion battery, 8A charging current).

3. Stating the charger's desired power level (e.g., 500W, 1kW).

4. Establishing the intended efficiency, for example, >95%.

5. Setting the desired power factor (e.g., >0.99) and THD criteria (e.g., <5% per applicable standards including IEC 61000-3-2).

**Converter Topology:** Thorough design and analysis of the power stages, including choice of semiconductor switches (GaN MOSFETs) are common for totem-pole PFC due to their performance benefits), magnetic components (inductors, transformers), and filter components.

**Control System:** Development and simulation of digital or analog control schemes for both converters. This covers gate drive circuits and controller design (e.g., PI Controller).

Research on control strategies to maximize performance, such as advanced PFC control algorithms or ZVS for the PSFB converter.

# Chapter 2

## Literature Review

### 2.1. Introduction and Evolution of Battery Charging Technologies

As portable electronics, electric vehicles (EVs), and energy storage systems have proliferated, efficient, small, high-performance battery chargers have been in great demand. Early battery charger designs employed basic rectification and large line-frequency transformers, which produced poor power quality, low efficiency, and large form factors. Improved performance requirements pushed the use of switch-mode power supply (SMPS) methods, which permitted more efficiency, smaller component sizes, and higher switching frequencies[13].

Standard has become high power factor, low input current harmonics, and precise output voltage/current control with two-stage charger designs comprising a DC-DC converter back-end and a Power Factor Correction (PFC) front-end. Following international standards such as IEC 61000-3-2, the PFC stage forms the input current to be sinusoidal and in phase with the input voltage. The split DC-DC stage then provides the regulated output voltage and current required for optimal battery charging (e.g., constant current-constant voltage, CC-CV profiles) [14]-[20].

#### 2.1.1. Power Factor Correction (PFC) Topologies:

**2.1. Conventional Boost PFC Converter:** Because of its steady input current and straight forward control, the traditional boost converter has been the workhorse for active PFC. Its efficiency is therefore limited, particularly at greater power levels, since the diode bridge rectifier at the input causes significant conduction losses. Specific applications have also seen investigation of other topologies such as buck, buck-boost, and flyback PFC converters, which usually have their own efficiency, component stress, or power handling capacity restrictions.

**Advantages:**

1. Simple design and control

2. Reliable operation

3. Well-documented and widely understood

**Disadvantages:**

1. Lower efficiency compared to advanced topologies

2. Larger passive components (inductors and capacitors)

3. Higher total harmonic distortion (THD)

**2.2 Interleaved PFC:** Interleaved PFC converters employ multiple boost converters operating out of phase to share the load current. This method reduces current ripple and enhances efficiency.

**Advantages:**

1. Reduced input current ripple

2. Improved efficiency compared to conventional PFC

3. Smaller passive components due to current sharing

**Disadvantages:**

1. More complex control and design

2. Increased component count

3. Potential for imbalance between phases

**2.3. Bridgeless PFC Converter:** Bridgeless topologies have attracted much interest to surpass the constraints of traditional PFC converters. Bridgeless PFC converters can be more efficient by cutting the number of semiconductor devices in the present path. Among the several bridgeless topologies are the bridgeless boost, bridgeless SEPIC, and bridgeless cuk converters. Some bridgeless designs may experience higher electromagnetic interference (EMI) or more complicated control needs even while they enhance efficiency [21].

**2.1.2. DC-DC converters for battery charging:**

A battery charger's DC-DC stage offers isolation and exact voltage/current control for the battery. There are several topologies available, each with its trade-offs.

**2.1 Flyback Converter:** For low power uses (<150W), flyback converters are straightforward and affordable. Its application in higher power uses is constrained, though, by significant transformer leakage inductance and high switch stress [22].

**2.2 Forward Converter:** Appropriate for medium power levels—up to a few hundred watts. Though it needs a reset mechanism for the transformer core and may have more switch voltage stress, it provides better efficiency and power handling than flyback [23].

**2.3 LLC Resonant Converter:** High efficiency is its hallmark since it can run at high switching frequencies and ZVS capability across a broad load range. Its output voltage control range, though, may be constrained and its complexity greater, particularly for broad output voltage changes common in battery charging [24].

## 2.2. Proposed Configuration

Fig.2.1 Proposed Block Diagram for Battery Charger

Fig.2.2 Proposed Battery Charger Configuration

### 2.2.1. Totem-Pole PFC Converter:

With the possibility of very high efficiency (almost 99%) and great power density, the totem-pole PFC converter has become a very promising bridgeless topology. Usually MOSFETs, this topology substitutes actively controlled switches for the input diode bridge [25]-[35].

Fig.2.3. Totem Pole Power Factor Correction Configuration

### **Benefits of Totem-Pole PFC:**

- 1. High Efficiency:** Removes the voltage drop and losses linked to the diode bridge. The use of wide-bandgap (WBG) semiconductors like Gallium Nitride (GaN) and Silicon Carbide (SiC) MOSFETs further reduces conduction and switching losses, enabling operation at higher frequencies.

- 2. Reduce Component Count:** Compared to certain other bridgeless topologies, it may have a straighter forward power loop design.

- 3. High Power Density:** WBG devices' higher switching frequencies allow for smaller passive components (capacitors, inductors).

### **Difficulties of Totem-Pole PFC:**

**Control Complexity:** Especially for attaining continuous conduction mode (CCM) operation and controlling zero-crossing distortions, it calls for advanced control techniques. Many times, digital control is preferred.

**Switching Loss in Slow Lag:** In the traditional totem-pole PFC, one leg switches at line frequency (slow leg) and the other at high frequency (fast leg). If not controlled correctly, the body diodes of the MOSFETs in the slow leg can experience considerable reverse recovery losses, especially with silicon MOSFETs. Highly beneficial in reducing this problem are GaN devices, with their zero reverse recovery charge.

**Dead Time Management:** Dead-time control is essential to avoid shoot-through in the high-frequency leg.

**EMI:** While offering high efficiency, careful design is needed to manage EMI due to high  $dv/dt$  and  $di/dt$ .

Recent research in totem-pole PFC focuses on advanced control techniques (e.g., adaptive dead-time control, zero-voltage switching (ZVS) for the fast leg), the use of GaN and SiC devices to push efficiency and frequency limits, and thermal management solutions for high-power-density designs.

#### **2.2.2. Phase Shift Full Bridge Converter (PSFB):**

The Phase Shift Full Bridge (PSFB) converter is a popular choice for medium to high-power isolated DC-DC applications (hundreds of watts to several kilowatts) since it can provide ZVS for the primary switches, so lowering switching losses and ZVS.

Fig. 2.4. Phase Shift Full Bridge Converter

### 1. Benefits of PSFB Conversion

1. **Zero Voltage Switching (ZVS):** Primary switches' capacity to reach zero voltage switching (ZVS) over a significant load range produces high efficiency.

2. **High Power Capability:** Appropriate for charging high power applications

3. **Galvanic Isolation:** The high-frequency transformer offers galvanic isolation as Protection of Battery

4. **Constant Frequency operation:** Reduces magnetic control and design complexity.

### 2. Challenges of Phase Shift Full Bridge (PSFB) Converter:

1. Especially under light loads, circulating currents could run in the primary side and raise conduction losses during the freewheeling period.

2. Keeping ZVS under light load conditions can be difficult and usually calls for altered control techniques or auxiliary circuits.

3. Reverse recovery losses and notable voltage ringing can affect the secondary side rectifier diodes. Efficiency is usually increased by synchronous rectification using MOSFETs [37].

4. The design must consider the loss of effective duty cycle caused by the leakage inductance of the transformer.

5. Complexity: More complex than simpler topologies, such forward converters or flyback [38].

# Chapter 3

## System Design of the Battery Charger

### 3.1. Introduction

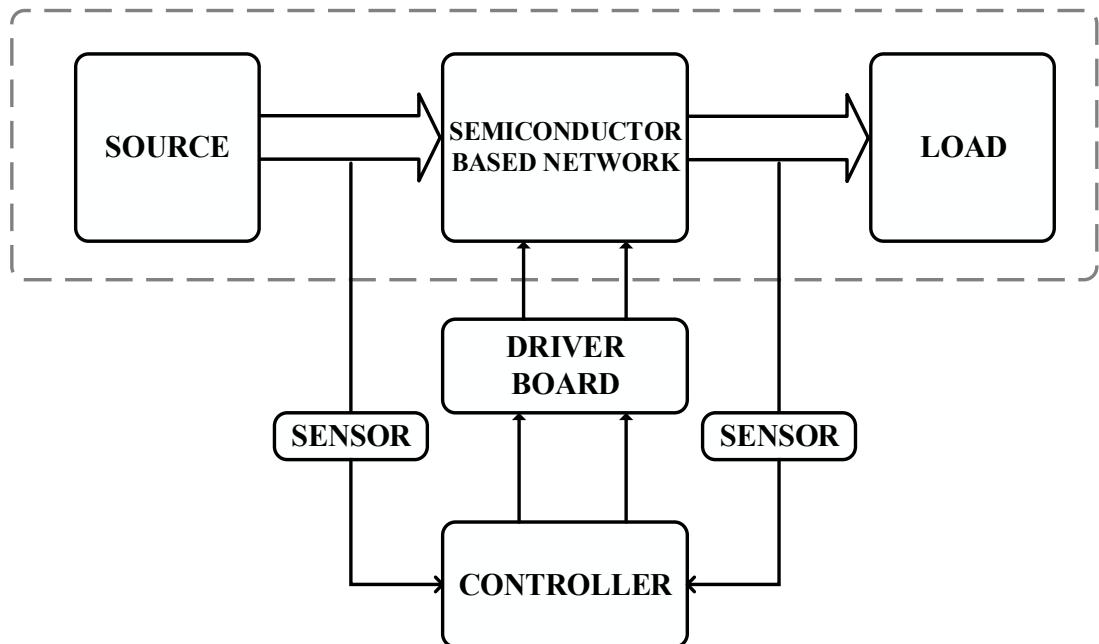

A Totem-Pole Power Factor Correction (PFC) and a Phase Shift Full Bridge (PSFB) converter are the two stages of a power conversion design used in battery charging systems. With a high power factor and low harmonic distortion, this configuration is designed to effectively convert AC power to the DC power required for battery charging. Every stage is optimally designed to improve the power factor, provide high galvanic isolation, and enable efficient direct current (DC) conversion to reduce energy loss and provide uniform system operational efficiency. The initial stage of this configuration is a Totem-Pole Power Factor Correction (PFC) circuit, which offers maximum efficiency by synchronising the input voltage and current. The DC output of the PFC stage is used as an input to the second stage, thus providing efficient and continuous power transmission across the system.

Fig. 3.1 Battery Charger Configuration

### 3.2. Totem Pole Power Factor Correction

Traditional Power Factor Correction (PFC) methods, like the traditional boost PFC, are in common use in a variety of applications.

A totem pole converter is a derived topology of a boost-PFC converter, and it achieves higher efficiency compared to all the other boost-PFC derived topologies.

This figure shows the circuit for the totem pole converter:

Fig. 3.2 Totem Pole PFC Configuration

One of the greatest strengths of Totem-Pole PFC is that it significantly improves power factor performance with high efficiency and smaller component sizes. Additionally, the enhanced power quality favours the overall power system, lowering the grid load by improving equipment reliability. Out of the three types discussed, the Totem-Pole PFC converter is the most compact and efficient. It is a great option for contemporary battery charging systems due to its high efficiency, low total harmonic distortion (THD), and reduced component count.

It is especially appropriate for applications where efficiency and power density are crucial, despite its higher initial cost and more intricate control requirements. A high-frequency leg and a low-frequency leg make up a totem pole converter. The switching frequency is used by the high-frequency leg. Wide band gap (WBG) devices are used in the high-frequency legs because they have low switching energy and faster switching times.

Power frequency is used by the low-frequency leg. MOSFETs or silicon-based diodes are used in low-frequency legs to provide unidirectional or bidirectional power flow.

For the high-frequency and low-frequency legs of the model, silicon carbide (SiC) and silicon (Si) based MOSFETs are used. The controller keeps the intermediate capacitor voltage at a predetermined level while achieving unity power factor (UPF) at the supply terminals.

**Table 3.1.** Comparative Table of Different Topology for PFC

| Features                  | Conventional PFC | Interleaved PFC           | Totem-Pole PFC |

|---------------------------|------------------|---------------------------|----------------|

| <b>Topology</b>           | Boost Converter  | Multiple Boost Converters | Bridgeless     |

| <b>Efficiency</b>         | ~90-95%          | ~95-97%                   | >98%           |

| <b>Power Factor</b>       | ~0.95            | ~0.98                     | ~0.99          |

| <b>THD</b>                | Higher           | Moderate                  | Low            |

| <b>Inductor Size</b>      | Large            | Medium                    | Small          |

| <b>Capacitor Size</b>     | Large            | Medium                    | Small          |

| <b>Component Count</b>    | Low              | High                      | Low            |

| <b>Control Complexity</b> | Simple           | Moderate                  | High           |

| <b>Cost</b>               | Low              | Moderate                  | High           |

The totem-pole PFC structure establishes a new benchmark in performance and efficiency for power factor correction. By achieving high-frequency operation and reduced conduction losses, the design comfortably addresses the expanding requirements of emerging power electronics. Its efficiency-centred design also advances a more power-efficient energy platform to the advantage of the grid infrastructure[20] and end users in terms of improved power quality and lower aggregate energy consumption. This leads to making this topology a trending choice as a PFC circuit, but the complexity in controlling the circuit makes this more complex to implement in the battery charger.

### 3.3. Phase Shift Full Bridge (PSFB) Converter

Following the Power Factor Correction (PFC) phase, the controlled direct current (DC) voltage is converted into a high-frequency alternating current (AC) signal through a Phase-Shift Full Bridge (PSFB) Converter. The AC signal, which has a square wave nature, is filtered through a particular two-winding transformer that doubles as a galvanic isolation and output voltage adaptation to charging battery specifications. The transformer provides an efficient and stable power supply regardless of load changes.

Diodes rectify the AC output to produce a stable DC voltage for battery charging. The optimal design practices are employed to minimise conduction and switching losses to a large degree, contributing to higher efficiency, longer component life, and higher overall system reliability. In Figure 4, a full-bridge converter with a diode rectifier. Phase-Shift Full Bridge (PSFB) is common in high-performance power supplies with faster transient response, high power density and high converter efficiency. Automotive and aerospace uses also need high power density, as lightweight means that transport carriers will have improved energy efficiency. Increasing the converter switching frequency helps to lower the weight by lowering the magnetic volt-seconds and hence its size. Higher switching frequency results in more regular hard-switching transients, which leads to larger switching losses. Increasing the turn-on speed to lower the overlapped area may help to lower switching losses, but a faster voltage-changing slew rate will produce more noise and electromagnetic interference. Conversely, soft-switched turn-on is accomplished by letting the negative drain-to-source current discharge the MOSFET output capacitor voltage prior to the gate voltage rising. One of the best things about the PSFB topology is that it can make the primary-side MOSFETs switch at zero voltage (ZVS). To get ZVS, you usually use the energy stored in the transformer's leakage inductance (or an externally added resonant inductor,  $L_m$ ) to charge and discharge the output capacitances ( $C_b$ ) of the MOSFETs during the dead time between the switching transitions of the devices in each leg. When the voltage across the MOSFETs is already zero (or very near to it), turning them on greatly cuts down on the switching losses that happen when voltage and current overlap at the same time. This lets the device work at greater switching frequencies, which means fewer magnetic parts and capacitors and higher power density, with just a minor drop in efficiency.

But the resonant transitions that ZVS needs cause something called "Duty cycle loss." This is the part of the switching period when the primary current is changing direction through the resonant inductor and the voltage across the transformer primary is almost zero, which means that no power is being sent to the secondary. The design needs to take this loss in effective duty cycle into account, especially when a wide variety of output voltages is needed.

There are different ways to rectify on the secondary side. A current doubler rectifier is often the best choice for applications that need a lot of output current, like charging batteries. This is because it splits the output current across two inductors, which can cut down on conduction losses, improve thermal distribution, and make magnetic components smaller. To cut down on rectification losses, modern high-efficiency PSFB converters nearly often use synchronous rectifiers (SRs) with MOSFETs instead of diodes.

Fig. 3.3. Phase-Shift Full Bridge (PSFB) Converter

The absence of current and voltage overlap at the MOSFET turn-on transient causes no turn-on switching losses, which enables the PSFB to run at a high switching frequency and keep great efficiency at the same time. Because it can be constructed highly effectively, galvanically isolated, and with low switching losses, this PSFB converter is a structure that is commonly employed in high-power applications like battery chargers. Power Supply Units (PSUs) for AI and

edge computing with quick load transients, as well as battery charger applications, including electric vehicle.

- 3.1.1. Benefits of Phase Shift Full Bridge Converter:** The isolation is yet another essential advantage of the PSFB topology, and it occurs through a high-frequency transformer. This isolation provides safety by offering electrical insulation between the battery and voltage grid, thereby protecting user and the battery. Also, the transformer provides the added advantage of voltage transformation such that, the charger can handle a broad spectrum of input and output voltage levels.

- 3.1.2. Losses in PSFB Converter:** Transformer windings and power switches both have conduction losses from current flow, and core losses within the transformer through magnetic hysteresis and eddy currents etc.

- 3.1.3. Relevance in Battery Charging:** In battery charging systems, the Phase-Shift Full Bridge (PSFB) converter is the preferred choice since it can handle high levels of power efficiently while minimizing thermal stress. Its galvanic isolation capability makes it safety-compliant, and its adaptive voltage conversion capability allows it to support a range of battery configurations.

### **3.4. Mode of Operations of Charger**

The Totem-Pole PFC offers a high-power factor in addition to high-efficiency AC-DC conversion, and the Phase Shift Full Bridge (PSFB) converter offers isolated DC-DC conversion.

### 3.4.1. Positive Half-Cycle Operation

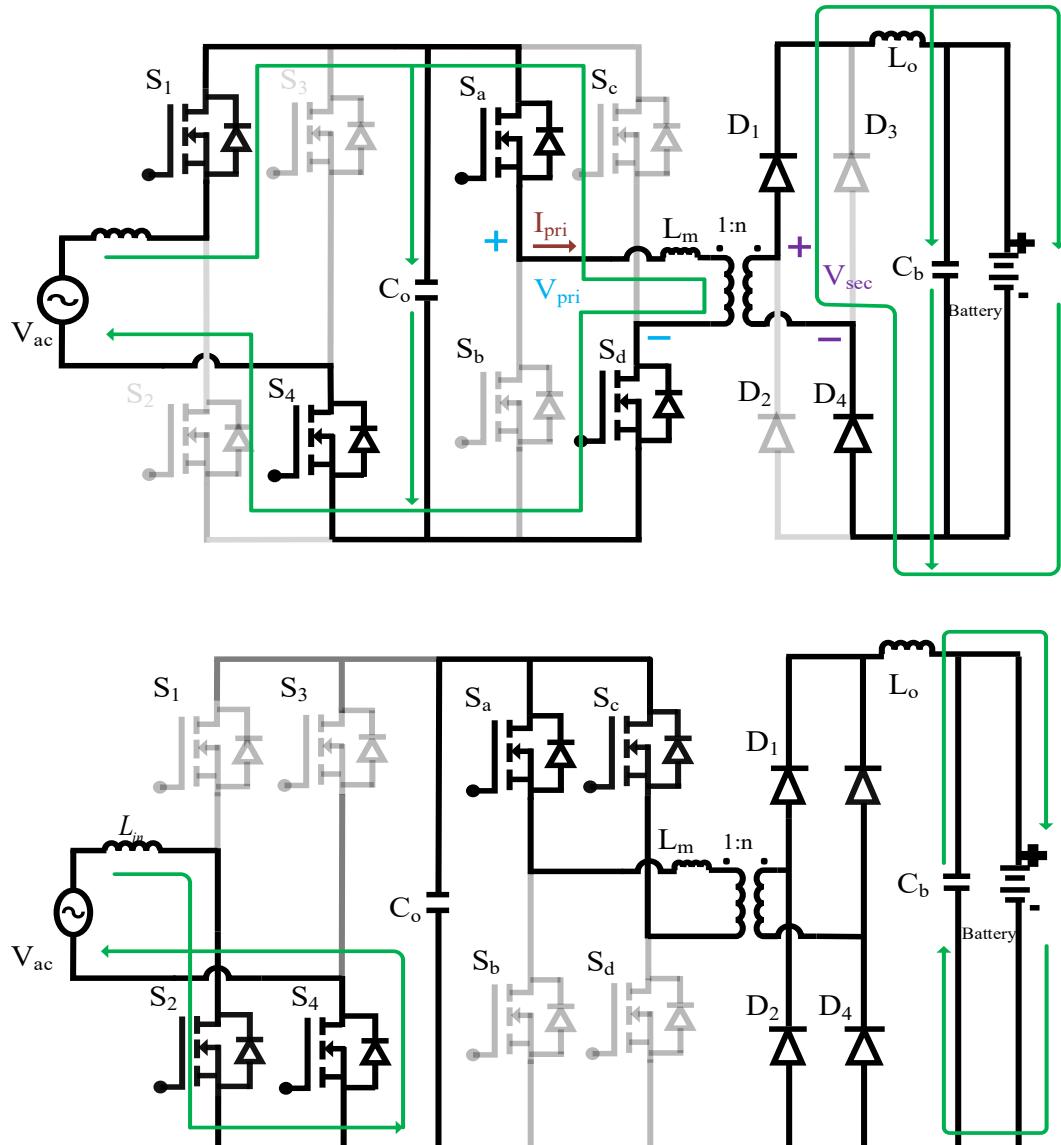

Fig. 3.4. Positive Cycle for Input AC: Mode of Operations

In the positive half cycle of the AC input, the Totem-Pole Power Factor Correction (PFC)  $S_3$  is turned off and  $S_4$  is turned on at the grid frequency, steering the inductor current too closely to follow the rising slope of the line voltage and increasing and charging energy onto the DC link capacitor. The Phase-Shift Full Bridge (PSFB) converter then accurately controls power transmission to the battery by phase relationship modulation of its bridge

switches. A phase difference is created between leg 1 MOSFET driving signals ( $S_a$  and  $S_b$ ) and leg 2 MOSFETs driving signals ( $S_c$  and  $S_d$ ), while all four driving signals keep their duty cycle unchanged. This Phase-Shifting reduces switching losses and enhances overall efficiency, especially during varying load or line conditions.

**Mode 1.** During this phase of the switching sequence for the positive half cycle, the  $S_1$  switch remains on and the  $S_2$  switch stays inactive. Consequently, current from the AC source passes through the input inductor  $L_{in}$ , temporarily storing energy before delivering it to the DC link. Within the PSFB converter, switches  $S_a$  and  $S_d$  are enabled, forming a conduction path to the primary of the transformer, and the secondary winding conducts the current to the battery. With the help of the rectifier circuit at the secondary side of the transformer, which transfers the energy to capacitor  $C_b$ , thereby boosting the DC link voltage to the desired level.

**Mode 2.** After the inductor has supplied its stored energy, switch  $S_1$  is turned off while switch  $S_2$  is activated, putting the circuit into a freewheeling phase. During this interval, the system accumulates additional energy in the output capacitor, bolstering the DC link before the following conduction path. In the PSFB section, switch  $S_d$  is deactivated to facilitate current freewheeling through  $S_a$  and  $S_c$ . This free-wheeling path continues a constant current flow without inducing sudden voltage or current oscillations in the primary winding of the transformer. On the secondary side, the transformer voltage returns to zero and the output inductor starts to release its energy to the load.

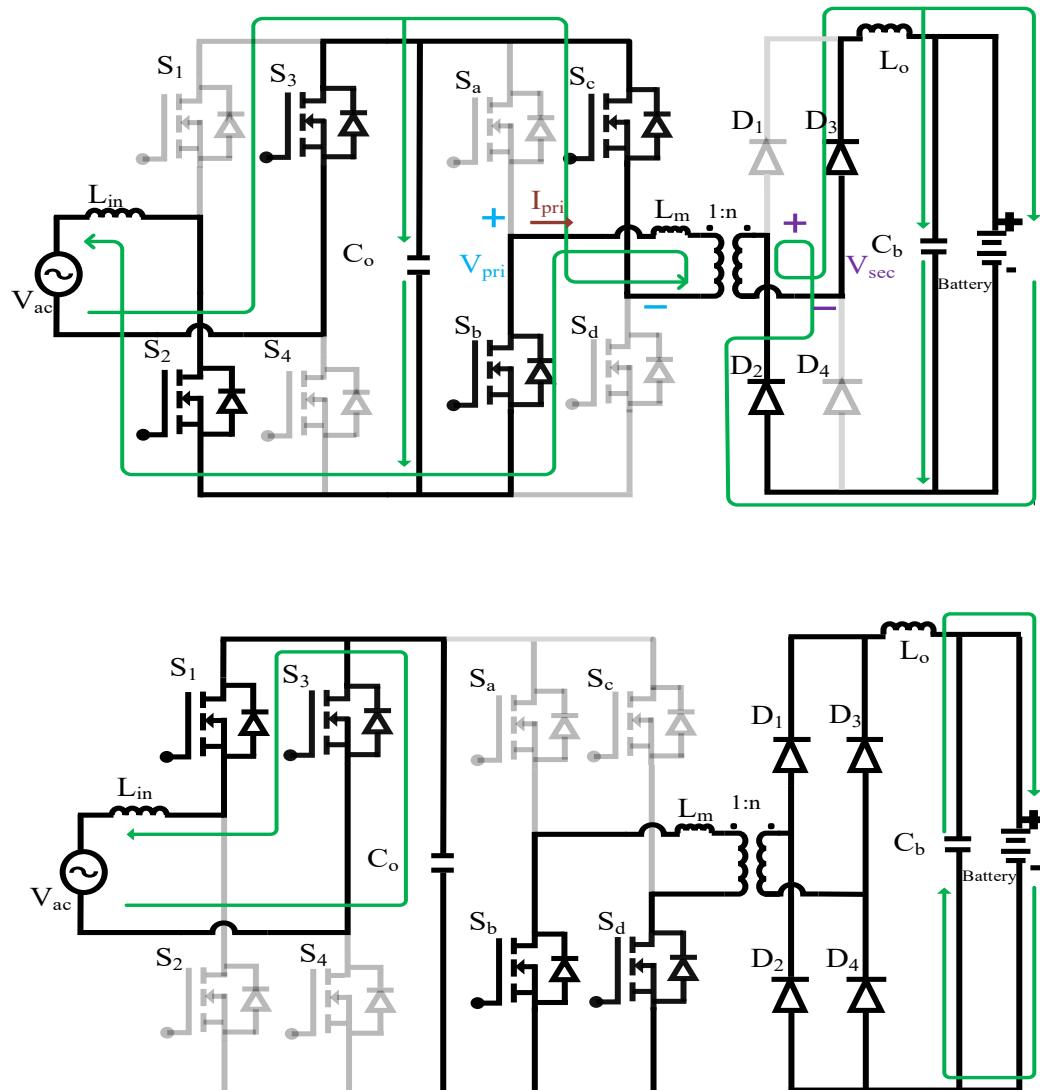

### 3.4.2. Negative Half Cycle:

During the negative half of the AC input supply, the Totem-Pole PFC  $S_3$  is turned on and  $S_4$  is turned off all the time at grid frequency stage, carefully managing conduction paths to ensure inductor current follows while channeling energy onto the DC link capacitor. Through judicious switching control, the circuit retains a high-power factor, minimizes distortion, and provides a robust high-voltage rail for the subsequent converter.

Fig. 3.5. Negative Cycle for Input AC: Mode of Operations

**Mode 3.** During this mode, switch  $S_1$  is switched on while switch  $S_2$  is kept off, creating a path that directs the inductor current through switch. In the corresponding Phase-Shift Full Bridge (PSFB) stage, switches  $S_b$  and  $S_c$  are

reactivated to drive current through the primary winding of the transformer. On the transformer's secondary side,  $D_3$  and  $D_4$  conduct, sending electrical power to the battery and supporting the regulated output voltage. This stage leads to providing a stable output at the battery terminal for continued charging.

**Mode 4.** In the final segment of the switching sequence for the negative half cycle, switch  $S_1$  remains active while  $S_2$  remains off, permitting the output capacitor  $C_0$  to receive charge. Within the PSFB converter, switch  $S_c$  is deactivated, allowing the primary current to freewheel through  $S_c$  and  $S_d$ . On the secondary side, the transformer sees zero volts across its terminals, resulting in the output inductor discharging into the load. This synchronised control maintains a constant output current and voltage and prevents unnecessary stress on the converter components.

Table3.2. Different Switching Cycle for TotemPole PFC

| Switch | Positive AC Voltage Cycle       | Negative AC Voltage Cycle       |

|--------|---------------------------------|---------------------------------|

| S1     | Working as a synchronous switch | Working as a control switch     |

| S2     | Working as a control switch     | Working as a synchronous switch |

| S3     | Permanently off                 | Permanently on                  |

| S4     | Permanently on                  | Permanently off                 |

Fig. 3.6. Switching Cycle, Primary, Secondary Voltage and Primary Current of Transformer

# Chapter 4

## Designing of Proposed Charger

### 4.1. Totem Pole PFC Designing

The totem-pole PFC topology usually has two high-frequency switches, and two low-frequency switches set up in a full-bridge configuration that is directly connected to the AC line and does not have an input diode rectifier. SiC or GaN MOSFETs are often used for the high-frequency switches that do the PWM chopping. This helps reduce switching losses and lets the system work at high frequencies. In some setups, the low-frequency switches can be Si MOSFETs or even diodes. These switches change at the AC line frequency.

#### 4.1.1. Input Filter Inductor ( $L_{in}$ ) Design

The input inductor in a totem-pole PFC stage is an important part that shapes the input current, limits ripple and keeps the system running smoothly [39].

**Purpose:** The main jobs of the input inductor ( $L_{in}$ ) are to keep the CCM running by limiting the input current ripple, filter out the high frequency switching components, and help turn the input current into a sine wave that is in phase with the input voltage. This gives a high-power factor and low THD.

**Minimum Inductance ( $L_{inmin}$ ):** The inductance value is mostly set to keep the peak-to-peak current ripple ( $\Delta IL_{in}$ ) below a specific percentage of the maximum peak input current. This percentage is usually between 20% and 40%. This makes sure that CCM works and keeps the strains on the parts in check.

An equation for the minimum inductance, derived from the [40] guide, is:

$$L_{min} = \frac{D \cdot (1 - D) \cdot V_{out}}{I_{ripple} \% \cdot F_{swpfc}}$$

$$L_{min} = \frac{0.5 \times (1 - 0.5) \times 400}{0.3 \times 16 \times \sqrt{2} \times 100 \times 10^3} = 147 \mu H$$

Or

$$L = \frac{1}{\text{Ripple}} * \frac{V_{ac}^2}{P_o} * \left(1 - \frac{\sqrt{2} * V_{ac}}{V_o}\right) * T$$

To maintain CCM operation, the minimum inductance value can be calculated when the duty cycle  $D=0.5$ , where  $D$  is the duty cycle,  $V_{out}$  is the PFC output DC voltage,  $I_{ripple}\%$  is the desired peak-to-peak ripple current as a percentage of the peak input current, and  $F_{sw}$  is the switching frequency. In PFC applications, the duty cycle  $D(t) = 1 - \frac{V_{in}(t)}{V_{out}}$  varies with the instantaneous AC input voltage  $V_{in}(t)$ . This condition typically occurs when the instantaneous input voltage  $|V_{in}(t)| = \frac{V_{out}}{2}$ . The design should consider the operating point that results in the maximum required inductance or the minimum inductance that satisfies ripple constraints across the entire line cycle.

Since the switching current in a PFC application varies across the AC-line cycle, the average inductor current can be used to calculate the average switching losses across the AC-line cycle. The average input current is given as [41]:

$$I_{L,avg} = \frac{P_o}{V_{ac}} \cdot \frac{2 \cdot \sqrt{2}}{\pi}$$

$$I_{L,avg} = \frac{550}{230} \times \frac{2 \times \sqrt{2}}{3.14}$$

$$= 2.15A$$

**4.1.2. Maximum Inductor Current ( $IL_{max}$ ):** The inductor must be designed to handle the peak current without its core saturating. This peak current typically occurs at the minimum RMS input voltage ( $V_{in,rms,min}$ ) and full load. The equation from is:

$$IL_{max} = \frac{\sqrt{2} \times P_{out}}{V_{in}} \times \left[ 1 + \frac{I_{ripple}\%}{2} \right]$$

$$IL_{max} = \frac{\sqrt{2} \times 550}{230} \times \left[ 1 + \frac{0.3}{2} \right]$$

$$IL_{max} = 3.887A$$

where  $P_{out}$  is the output power. Core saturation must be avoided as it leads to a rapid decrease in inductance and a potentially damaging increase in current [42]. Maintaining low THD and EMI at full load is crucial for PFC applications, but so are light loads where the converter tends to operate in DCM mode and the inductor current is low. A swinging choke is typically utilized for this purpose because it offers both a controlled inductance at high load and a higher

inductance at low DC bias current.

The inductance vs DC bias of the AC choke is presented in figure 7.

Fig 4.1: Totem-Pole PFC Input inductor: L vs DC bias [41]

**4.1.3. Output DC Link Capacitor ( $C_o$ ) Design:** The DC link capacitor is an important part of the totem-pole PFC stage that stores and filters energy. The DC link capacitor ( $C_o$ ) has several important jobs. It stabilizes the DC output voltage ( $V_o$ ) that goes to the downstream DC/DC converter. It also stores energy to keep the output power steady during short AC line sags or dropouts (hold-up time). Finally, it filters out the low-frequency voltage ripple that is a normal part of the PFC rectification process (at twice the AC line frequency for a single-phase PFC system).

**Sizing based on Hold-up Time ( $t_{hold}$ ):** For applications that need to keep working during short AC power outages, the hold-up time requirement usually sets the minimum capacitance value. Using the energy balance concept, capacitance we need.

$$C_o \geq \frac{2 \cdot P_o \cdot t_{hold}}{V_o^2 - V_{o,min}^2}$$

$$C_o = \frac{2 \times 550 \times 10 \times 10^{-3}}{400^2 - 345^2}$$

$$= 2.68\mu F$$

where  $P_o$  is the output power,  $t_{hold}$  is the required hold-up time,  $V_o$  is the nominal DC link voltage, and  $V_{o,min}$  is the minimum allowable DC link voltage during the

hold-up period.

**Sizing based on Output Voltage Ripple ( $\Delta V_o$ ):** The capacitor must also be large enough to limit the peak-to-peak voltage ripple at twice the line frequency to an acceptable level for the downstream converter .

$$C_o \geq \frac{P_o}{2 \cdot \pi \cdot f_{\text{line}} \cdot \Delta V_{o,pp} \cdot V_o}$$

$$C_o = \frac{550}{2 \times 3.14 \times 50 \times 0.2 \times 400}$$

$$= 2.01\mu F$$

Therefore,  $2.68 \mu F$  is the minimum required DC capacitance to fulfil these two criteria.

**Capacitor Selection:** The final capacitance value chosen should be the larger of the values calculated from the hold-up and ripple requirements. Often, multiple capacitors are paralleled to achieve the required total capacitance, improve RMS current handling, and reduce overall ESR and ESL.

## 4.2. Phase Shift Full Bridge Converter Designing:

The PSFB converter is a popular choice for the isolated DC/DC stage in high-power battery chargers due to its ability to achieve high efficiency and power density [43].

**4.2.1. Output Inductor and Capacitor Filter Designing ( $L_o$  and  $C_b$ ):** The LC output filter is important because it changes the high-frequency rectified voltage from the transformer secondary into a smooth DC output that may charge a battery.

The output filter, which has an inductor ( $L_o$ ) and a capacitor ( $C_b$ ), turns the pulsing DC voltage from the secondary-side rectifier into a stable DC output voltage. It reduces the voltage ripple at the switching frequency and its harmonics, and it stores energy to keep the output voltage steady when the load varies quickly.

**Design of the Output Inductor ( $L_o$ ):** The main job of the output inductor is to keep the peak-to-peak output current ripple ( $\Delta I L_o$ ) at a certain level, usually a percentage of the whole load current (for example, 10–30%), while making sure that Continuous Conduction Mode (CCM) works over the whole load range.

The voltage across an inductor can be found using the equation  $V_L = L \frac{di}{dt}$ . During the part of the switching cycle when power comes from the secondary, the voltage across the inductor is about  $V_{L,on} = V_{rect,avg} - V_{out}$  which  $V_{rect,avg}$  is the average rectified voltage that comes before the filter.  $V_{out}$  is the output voltage.  $V_{L,off} = V_{rect,avg} - V_{out}$  throughout the freewheeling phase.

$$\Delta I_{L_o} = \frac{V_{in,ref}(1 - D) \cdot T_{sw}}{2 \cdot L_o}$$

is the ripple current, where  $T_{sw} = \frac{1}{f_{sw}}$  is the time it takes to switch.

A simpler calculation for lowest inductance, based on 1 (originally for an PSFB but usable in principle), takes into account the highest voltage that may be applied to the inductor and aims for a certain maximum ripple current.

$$L_{o,min} = \frac{V_{in,ref,max}}{4 \cdot \Delta I_{out,ripple,max} \cdot 2 \cdot f_{sw}}$$

$$L_{o,min} = \frac{400}{8 \cdot 0.8 \cdot 100 \cdot 10^3}$$

$$L_{o,min} = 0.00625H$$

$V_{in,ref,max}$  is the maximum effective voltage that drives the inductor. It is the rectified secondary voltage minus the output voltage, which happens at a duty cycle that maximizes this difference or ripple.  $\Delta I_{out,ripple,max}$  is the maximum peak-to-peak output inductor current ripple that is allowed. If the highest ripple happens when the effective duty cycle for charging the inductor is 0.5 is what gives birth to the factor of 4 (or 8 in the modified form).

**Output Capacitor ( $C_b$ ) Design:** The output capacitor is sized primarily to limit the peak-to-peak output voltage ripple ( $\Delta V_o$ ) caused by the inductor current ripple flowing through it, and to meet transient response requirements during sudden load changes. The voltage ripple due to the capacitance itself can be approximated by considering the charge accumulated/discharged by the ripple current:

$$\Delta V_{o,cap} = \frac{\Delta Q}{C_o} = \frac{1}{C_o} \int i_c(t) dt$$

For a triangular inductor current ripple, the charge stored/released by the capacitor over a quarter of the ripple period (assuming ripple frequency is  $2 \cdot f_{sw}$ ) is approximately

$$\frac{1}{2} \cdot \frac{\Delta I_{L_o,max}}{2} \cdot \frac{T_{sw}}{2} = \frac{\Delta I_{L_o,max}}{8 \cdot f_{sw}},$$

This leads to,

$$C_{o,min} \approx \frac{\Delta I_{L_o,max}}{8 \cdot f_{sw} \cdot \Delta V_{o,pp,max}}$$

Where,  $V_{o,pp,max}$  is the maximum allowable peak-to-peak output voltage ripple.

Here the difference in the denominator (8 vs. 16) can arise from definitions of ripple frequency or how the charge is calculated. It is crucial to use consistent definitions, So

$$C_{o,min} \approx \frac{\Delta I_{L_o,max}}{16 \cdot f_{sw} \cdot \Delta V_{o,pp,max}}$$

Provides,

$$C_o = \frac{\Delta I_{L_o} \cdot D_{on} \cdot T_{sw}}{\Delta V_{o,ripple}}$$

which is another form based on total charge during  $D_{on}$ .

### 4.3. Key Semiconductor and Passive Component Selection:

The battery charger's performance, efficiency, and reliability all depend on picking the right power semiconductors and passive parts. This part talks about things you should think about for these important pieces.

#### 4.3.1. Power Semiconductor Selection (MOSFETs/IGBTs for PFC and PSFB):

The choice of switching devices is fundamental to achieving the desired performance metrics.

**Totem-Pole PFC Switches:** The high-frequency leg of the totem-pole PFC that does the PWM switching often uses Wide Bandgap (WBG) semiconductors like Silicon Carbide (SiC) MOSFETs or Gallium Nitride (GaN) HEMTs. People like these devices because they switch quickly, don't lose much power when they do, and can work at high temperatures. All these things help them get a lot of power in a small space and be very efficient. The low-frequency leg switches at the AC line frequency and can use regular Si MOSFETs or, in some designs that need to save money, diodes.

**PSFB Switches:** The main-side switches of the PSFB converter are usually high-voltage Si MOSFETs. SiC MOSFETs can also be used for PSFB designs or applications that need the most efficiency at very high frequencies, though. Most of the time, the secondary-side synchronous rectifiers (SRs) are low-voltage Si MOSFETs with very low  $R_{DS(on)}$  to cut down on conduction losses.

Table 4.1. : Comparison of Power Semiconductor Technologies (Si, SiC, GaN)

| Parameter                                   | Silicon (Si) MOSFET | Silicon Carbide (SiC) MOSFET                                    | Gallium Nitride (GaN) HEMT                                                         |

|---------------------------------------------|---------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------|

| Typical $R_{DS(on)}$ per area               | Higher              | Lower                                                           | Lowest                                                                             |

| Gate Charge ( $Q_g$ )                       | Moderate to High    | Lower than Si for similar rating                                | Lowest                                                                             |

| Reverse Recovery ( $Q_{RR}$ ) of Body Diode | Significant         | Very Low / Near Zero                                            | No body diode (typically, but has reverse conduction mechanism)                    |

| Switching Speed                             | Slower              | Faster                                                          | Fastest                                                                            |

| Typical $V_{th}$                            | 2-4 V               | 2-5 V (varies)                                                  | 1-2 V (enhancement mode)                                                           |

| Cost                                        | Lowest              | Higher                                                          | High, decreasing                                                                   |

| Gate Drive Complexity                       | Mature, simpler     | Requires higher $V_{gs}$ (e.g., +20V/-5V), sensitive to ringing | Requires precise VGS (e.g., +6V/0V), very sensitive to overshoot, low $V_{gs,max}$ |

| Operating Temperature                       | Lower Max $T_j$     | Higher Max $T_j$                                                | Moderate to High Max $T_j$                                                         |

Table 4.2. Capacitor Technology Characteristics for Power Electronics

| Capacitor Type                             | Typical Capacitance Range       | Typical Voltage Range                       | Relative ESL     | Ripple Current Capability |

|--------------------------------------------|---------------------------------|---------------------------------------------|------------------|---------------------------|

| Aluminum Electrolytic                      | $\mu\text{F}$ to $\text{F}$     | Up to $\sim 600$ V                          | Moderate to High | Moderate                  |

| Tantalum Electrolytic                      | $\mu\text{F}$ to $\text{mF}$    | Up to $\sim 75$ V                           | Moderate         | Moderate                  |

| Film (Polypropylene, Polyester)            | nF to hundreds of $\mu\text{F}$ | Up to kV range                              | Low              | High                      |

| Ceramic MLCC (Class I: C0G/NP0)            | pF to tens of nF                | Up to kV range                              | Very Low         | Moderate                  |

| Ceramic MLCC (Class II/III: X7R, X5R, Y5V) | nF to hundreds of $\mu\text{F}$ | Up to $\sim 100$ V (higher for specialized) | Very Low         | High                      |

Table 4.3. Comparison of Different Control Strategies for Totem-Pole PFC and PSFB

| Converter Stage      | Control Mode                        | Key Characteristics                                                    | Pros                                                                             | Cons                                                                                   | Typical Implementation |

|----------------------|-------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------|

| <b>TotemPole PFC</b> | Average Current Mode Control (ACMC) | Regulates average inductor current. Requires sinusoidal reference.     | Well-understood, good current shaping.                                           | Requires bidirectional current sensing and processing. May need $d_{FF}$ for best THD. | Analog or Digital      |

| <b>TotemPole PFC</b> | Peak Current Mode Control (PCMC)    | Regulates peak inductor current. Requires slope compensation.          | Fast response, inherent current limit.                                           | Bidirectional sensing complex. Susceptible to noise. Stability needs care.             | Analog or Digital      |

| <b>TotemPole PFC</b> | Duty-Ratio Feedforward ( $d_{FF}$ ) | Pre-calculates duty based on $V_{in} / V_{out}$ . Used with ACMC/PCMC. | Improves THD, reduces current loop burden, faster transient response.            | Requires accurate $V_{in}$ and $V_{out}$ sensing.                                      | Digital                |

| <b>PSFB</b>          | Voltage Mode Control (VMC)          | Error amplifier output directly controls phase shift.                  | Simpler implementation, less sensitive to current noise.                         | Slower transient response. Requires DC blocking capacitor for transformer.             | Analog or Digital      |

| <b>PSFB</b>          | Peak Current Mode Control (PCMC)    | Primary current compared to voltage loop output to set phase shift.    | Faster transient response, inherent current limit, potential for flux balancing. | Complex current sensing, noise sensitivity, requires slope compensation.               | Analog or Digital      |

| <b>PSFB</b>          | Adaptive ZVS/Dead-time Control      | Adjusts dead-times based on operating conditions.                      | Optimizes ZVS over wider range, improves efficiency.                             | Adds complexity, requires sensing/estimation of load/line.                             | Digital                |

# Chapter 5

## Mathematical Modelling and Analysis

### 5.1. Totem Pole PFC Converter:

The low-frequency bridge arm adjusts the current routes in totem-pole PFC during both positive and negative half-cycles of the input AC voltage. But its states stay symmetrical, which makes it easier to set up a single main circuit model [44].

#### Basic State Equations

Let  $d(t)$  be the duty ratio,  $i_{in}(t)$  be the inductor current,  $V_{co}$  the output voltage, and  $R$  be the load resistance

$$\begin{aligned} L_{in} \frac{di_{in}(t)}{dt} &= v_{ac}(t) - (1 - d(t))v_{co}(t) \\ C_o \frac{dv_{co}(t)}{dt} &= (1 - d(t))i_{in}(t) - \frac{v_{co}(t)}{R} \end{aligned} \quad (1)$$

$$d(t) = \begin{cases} 1, & 0 < t < dT_s \\ 0, & dT_s < t < T_s \end{cases}$$

The term  $1-d(t)$  in the equations corresponds to the interval when energy is transferred to the output load.

#### 5.1.1. Large-Signal Modelling using Generalized State-Space Averaging (GSSA)

The model's accuracy depends on the order of the Fourier series expansion. We use first-order Fourier coefficients in our analysis to find a middle ground between accuracy and complexity.

#### 5.1.2. Derivation of 0-Average Index Equations

The 0-average (DC component) equations are derived from the basic state equations,  $D_{avg}$  be the average duty cycle ( $\langle d \rangle_0$ ).

The 0-average equations, adapted from with user-defined variables and considering  $V_{ac_{peak}}$  as the amplitude of the input voltage that contributes to the  $B \cdot V_{ac_{peak}}$  term in the state-space model, are

$$\begin{aligned} L_{in} \frac{d\langle i_{Lin} \rangle_0}{dt} &= Vac_{peak} - \langle v_{Co} \rangle_0 + \langle dv_{Co} \rangle_0 \\ C_o \frac{d\langle v_{Co} \rangle_0}{dt} &= \langle i_{Lin} \rangle_0 - \langle di_{Lin} \rangle_0 + \frac{\langle v_{Co} \rangle_0}{R} \end{aligned} \quad (2)$$

Here,  $\langle x \rangle_k$  is the  $k^{\text{th}}$  Fourier coefficient of variable  $x$ , satisfying

$$\langle x \rangle_k = \frac{1}{T} \int_{t-T}^t x(\tau) \cdot e^{-jk\omega t} dt$$

And in this research, define

$$\begin{aligned} \mathbf{Re}[\langle x \rangle_k] &= \langle x \rangle_k^R, \\ \mathbf{Im}[\langle x \rangle_k] &= \langle x \rangle_k^I \end{aligned}$$

In above equations,

$$\begin{aligned} \langle dv_{Co} \rangle_0 &= \langle d \rangle_0 \langle v_{Co} \rangle_0 + 2 \cdot (\langle d \rangle_1^R \langle v_{Co} \rangle_1^R + \langle d \rangle_1^I \langle v_{Co} \rangle_1^I), \\ \langle di_{Lin} \rangle_0 &= \langle d \rangle_0 \langle i_{Lin} \rangle_0 + 2 \cdot (\langle d \rangle_1^R \langle i_{Lin} \rangle_1^R + \langle d \rangle_1^I \langle i_{Lin} \rangle_1^I) \end{aligned}$$

Here,  $\langle d \rangle_1^R$  and  $\langle d \rangle_1^I$  are the real and imaginary parts of the first Fourier coefficient of the instantaneous duty cycle  $d(t)$  respectively, given by

$$\begin{aligned} \langle d \rangle_0 &= d \\ \langle d \rangle_1^R &= \frac{1}{2\pi} \int_0^{2\pi d} \cos(2\omega\tau) d(\omega\tau) = \frac{\sin(2\pi d)}{2\pi} \\ \langle d \rangle_1^I &= -\frac{1}{2\pi} \int_0^{2\pi d} \sin(2\omega\tau) d(\omega\tau) = \frac{\cos(2\pi d) - 1}{2\pi} \end{aligned}$$

For example, the 0-average (DC) part of the inductor current derivative  $d\langle i_{Lin} \rangle_0 / dt$  is affected by both average values and the products of the first-order harmonic components of the duty cycle and capacitor voltage, such as  $\langle d \rangle_1^R \langle v_{Co} \rangle_1^R$ .

$$\begin{aligned} L_{in} \frac{d\langle i_{Lin} \rangle_1}{dt} &= Vac_{peak} - \langle v_{Co} \rangle_1 + \langle dv_{Co} \rangle_1 - jL_{in}\omega_s \langle i_{Lin} \rangle_1 \\ C_o \frac{d\langle v_{Co} \rangle_1}{dt} &= \langle i_{Lin} \rangle_1 - \langle di_{Lin} \rangle_1 - \frac{\langle v_{Co} \rangle_1}{R} - jC_o\omega_s \langle v \rangle_1 \end{aligned} \quad (3)$$

Where,

$$\begin{aligned} \langle dv_{Co} \rangle_1 &= \langle d \rangle_0 \langle v_{Co} \rangle_1 + \langle d \rangle_1 \langle v_{Co} \rangle_0 \\ &= (\langle d \rangle_0 \langle v_{Co} \rangle_1^R + \langle d \rangle_1^R \langle v_{Co} \rangle_0) + (\langle d \rangle_0 \langle v_{Co} \rangle_1^I + \langle d \rangle_1^I \langle v_{Co} \rangle_0) \mathbf{j} \\ \langle di_{Lin} \rangle_1 &= \langle d \rangle_0 \langle i_{Lin} \rangle_1 + \langle d \rangle_1 \langle i_{Lin} \rangle_0 \\ &= (\langle d \rangle_0 \langle i_{Lin} \rangle_1^R + \langle d \rangle_1^R \langle i_{Lin} \rangle_0) + (\langle d \rangle_0 \langle i_{Lin} \rangle_1^I + \langle d \rangle_1^I \langle i_{Lin} \rangle_0) \mathbf{j} \end{aligned}$$

### 5.1.3. Derivation of 1-Average Index Equations

Similarly, the 1-average (fundamental component at switching frequency  $\omega_s$ ) equations for the state variables are derived. Let  $\omega = 2\pi f_s$  be the angular switching frequency. Adapted from [33]

$$\begin{aligned}

L_{in} \frac{d\langle i_{Lin} \rangle_1^R}{dt} &= Vac_{peak} + \langle d \rangle_1^R \langle v_{Co} \rangle_0 + L_{in} \omega \langle i_{Lin} \rangle_1^I + (\langle d \rangle_0 - 1) \langle v_{Co} \rangle_1^R \\

L_{in} \frac{d\langle i_{Lin} \rangle_1^R}{dt} &= \langle d \rangle_1^I \langle v_{Co} \rangle_0 - L_{in} \omega \langle i_{Lin} \rangle_1^R + (\langle d \rangle_0 - 1) (\langle v_{Co} \rangle_1^I) \\

C_o \frac{d\langle v_{Co} \rangle_1^I}{dt} &= -\langle d \rangle_1^R \langle i_{Lin} \rangle_0 + (1 - \langle d \rangle_0) \langle i_{Lin} \rangle_1^R - \frac{1}{R} \langle v_{Co} \rangle_1^R - C_o \omega \langle v_{Co} \rangle_1^I \\

C_o \frac{d\langle v_{Co} \rangle_1^I}{dt} &= -\langle d \rangle_1^I \langle i_{Lin} \rangle_0 + (1 - \langle d \rangle_0) \langle i_{Lin} \rangle_1^I - C_o \omega \langle v_{Co} \rangle_1^R - \frac{1}{R} \langle v_{Co} \rangle_1^I

\end{aligned} \tag{4}$$

### 5.1.4. Complete Large-Signal State-Space Model

Combining the 0-average and 1-average equations, the GSSA large-signal model of the totem-pole PFC can be expressed in state-space form as:

$$\frac{dX}{dt} = A \cdot X + B \cdot Vac_{peak} \tag{5}$$

Where the state variable X,