# chapters (1) (1).docx

Delhi Technological University

#### **Document Details**

Submission ID

trn:oid:::27535:97220426

Submission Date

May 22, 2025, 7:35 PM GMT+5:30

**Download Date**

May 22, 2025, 7:38 PM GMT+5:30

File Name

chapters (1) (1).docx

File Size

2.5 MB

72 Pages

11,349 Words

68,583 Characters

# 16% Overall Similarity

The combined total of all matches, including overlapping sources, for each database.

#### Filtered from the Report

- Bibliography

- Quoted Text

- Cited Text

- Small Matches (less than 8 words)

#### **Match Groups**

195Not Cited or Quoted 16%

Matches with neither in-text citation nor quotation marks

**99 O** Missing Quotations 0%

Matches that are still very similar to source material

0 Missing Citation 0%

Matches that have quotation marks, but no in-text citation

**0** Cited and Quoted 0%

Matches with in-text citation present, but no quotation marks

#### **Top Sources**

Internet sources

Publications

9%

Submitted works (Student Papers)

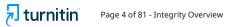

## **Integrity Flags**

1 Integrity Flag for Review

**Replaced Characters**

37 suspect characters on 14 pages

Letters are swapped with similar characters from another alphabet.

Our system's algorithms look deeply at a document for any inconsistencies that  $% \left( 1\right) =\left( 1\right) \left( 1\right) \left($ would set it apart from a normal submission. If we notice something strange, we flag it for you to review.

A Flag is not necessarily an indicator of a problem. However, we'd recommend you focus your attention there for further review.

#### **Match Groups**

195Not Cited or Quoted 16%

Matches with neither in-text citation nor quotation marks

0 Mississ Overtations 00/

Missing Quotations 0%

Matches that are still years

Matches that are still very similar to source material

**0** Missing Citation 0%

Matches that have quotation marks, but no in-text citation

• 0 Cited and Quoted 0%

Matches with in-text citation present, but no quotation marks

#### **Top Sources**

10% Internet sources

8% 📕 Publications

9% Land Submitted works (Student Papers)

#### **Top Sources**

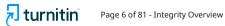

The sources with the highest number of matches within the submission. Overlapping sources will not be displayed.

| 11 Publication                                                                     |      |

|------------------------------------------------------------------------------------|------|

| Anubha Goel, Sonam Rewari, Seema Verma, R. S. Gupta. "Novel Dual-Metal Juncti      | <1%  |

| 12 Submitted works                                                                 |      |

| University of Lancaster on 2017-01-19                                              | <1%  |

| oniversity of Euricuster on 2017 of 15                                             |      |

| 13 Submitted works                                                                 |      |

| Silicon Institute of Technology on 2020-03-13                                      | <1%  |

| 14 Publication                                                                     |      |

| A. Chaudhry, M.J. Kumar. "Investigation of the Novel Attributes of a Fully Deplete | <1%  |

|                                                                                    |      |

| 15 Submitted works                                                                 |      |

| CSU, San Diego State University on 2024-09-18                                      | <1%  |

| 16 Publication                                                                     |      |

| Angsuman Sarkar, Aloke Kumar Das, Swapnadip De, Chandan Kumar Sarkar. "Eff         | <1%  |

|                                                                                    |      |

| 17 Submitted works                                                                 |      |

| Rochester Institute of Technology on 2015-05-13                                    | <1%  |

| 18 Publication                                                                     |      |

| S. Manikandan, N. B. Balamurugan, D. Nirmal. "Analytical Model of Double Gate S    | <1%  |

|                                                                                    |      |

| 19 Submitted works Indian Institute of Science, Bangalore on 2016-12-16            | <1%  |

| Indian Institute of Science, Bangaiore on 2010-12-10                               | ~170 |

| 20 Publication                                                                     |      |

| Karabi Baruah, Radhe Gobinda Debnath, Srimanta Baishya. " Technology comput        | <1%  |

| 21 Internet                                                                        |      |

| ethesis.nitrkl.ac.in                                                               | <1%  |

| etiesisiinti kiide.iii                                                             |      |

| 22 Internet                                                                        |      |

| kupdf.net                                                                          | <1%  |

| 23 Internet                                                                        |      |

| moam.info                                                                          | <1%  |

|                                                                                    |      |

| 24 Internet                                                                        |      |

| www.researchgate.net                                                               | <1%  |

|                                                                                    |      |

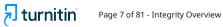

| 25 Submitted works                                                                |     |

|-----------------------------------------------------------------------------------|-----|

| Malaviya National Institute of Technology on 2022-05-18                           | <1% |

| 26 Publication                                                                    |     |

| Marc J. Madou. "Solid-State Physics, Fluidics, and Analytical Techniques in Micro | <1% |

| 27 Submitted works                                                                |     |

| University College London on 2012-04-17                                           | <1% |

| 28 Internet                                                                       |     |

| par.nsf.gov                                                                       | <1% |

| 29 Publication                                                                    |     |

| Jaikissoon, Marc. "Cmos-Compatible Strain Engineering and Device Scaling of Mo    | <1% |

| 30 Submitted works                                                                |     |

| National Institute of Technology, Rourkela on 2014-05-06                          | <1% |

| 31 Submitted works                                                                |     |

| National University of Ireland, Galway on 2024-11-12                              | <1% |

| 32 Internet                                                                       |     |

| www.diva-portal.org                                                               | <1% |

| 33 Submitted works                                                                |     |

| Anna University on 2024-09-18                                                     | <1% |

| 34 Publication                                                                    |     |

| Bouhalouane Amrani. "First-principles investigations of the ground-state and exc  | <1% |

| 35 Submitted works                                                                |     |

| Nanyang Technological University on 2024-03-29                                    | <1% |

| 36 Internet                                                                       |     |

| www.vedantu.com                                                                   | <1% |

| 37 Submitted works                                                                |     |

| Delhi University on 2014-12-12                                                    | <1% |

| 38 Submitted works                                                                |     |

| Silicon Institute of Technology on 2020-04-23                                     | <1% |

| 39 Submitted works National Institute of Technology, Silchar on 2022-05-10        | <1% |

|-----------------------------------------------------------------------------------|-----|

| 40 Submitted works                                                                |     |

| The Scientific & Technological Research Council of Turkey (TUBITAK) on 2025-05-11 | <1% |

| 41 Internet                                                                       |     |

| library.gu.edu.eg                                                                 | <1% |

| 42 Internet                                                                       |     |

| www.tdx.cat                                                                       | <1% |

| 43 Submitted works                                                                |     |

| Jordan University of Science & Technology on 2025-04-28                           | <1% |

| 44 Internet                                                                       |     |

| www.acarindex.com                                                                 | <1% |

| 45 Internet                                                                       |     |

| fastercapital.com                                                                 | <1% |

| 46 Submitted works                                                                |     |

| Higher Education Commission Pakistan on 2017-07-16                                | <1% |

| 47 Submitted works                                                                |     |

| Indian Indian Institute of Science Education and Research Kolkata on 2025-05-07   | <1% |

| 48 Publication                                                                    |     |

| Yun, S.R.N "Quantum-mechanical effects in nanometer scale MuGFETs", Microel       | <1% |

| 49 Submitted works                                                                |     |

| Associatie K.U.Leuven on 2023-08-17                                               | <1% |

| 50 Submitted works                                                                |     |

| Indian Institute of Technology, Bombay on 2016-09-20                              | <1% |

| 51 Publication                                                                    |     |

| Prajvi Udar, Anubha Goel, R.S. Gupta. "Nanoscale temperature dependent quantu     | <1% |

| 52 Internet                                                                       |     |

| doku.pub                                                                          | <1% |

| 53 Internet                                                                                   |      |

|-----------------------------------------------------------------------------------------------|------|

| epdf.pub                                                                                      | <1%  |

| 54 Internet                                                                                   |      |

| www.phy.pku.edu.cn                                                                            | <1%  |

|                                                                                               |      |

| Submitted works                                                                               | -40/ |

| University of Glasgow on 2025-02-13                                                           | <1%  |

| 56 Internet                                                                                   |      |

| patents.justia.com                                                                            | <1%  |

| 57 Internet                                                                                   |      |

| portalrecerca.uab.cat                                                                         | <1%  |

|                                                                                               |      |

| 58 Publication                                                                                |      |

| Angsuman Sarkar, C.K. Sarkar. "RF and analogue performance investigation of D                 | <1%  |

| 59 Internet                                                                                   |      |

| en.unionpedia.org                                                                             | <1%  |

|                                                                                               |      |

| 60 Internet                                                                                   | <1%  |

| pdffox.com                                                                                    |      |

| 61 Submitted works                                                                            |      |

| Anna University on 2025-01-08                                                                 | <1%  |

| 62 Publication                                                                                |      |

| K. Betzler, T. Weller. "Experimental Evidence of Two-Electron Transitions in Solids           | <1%  |

|                                                                                               |      |

| 63 Submitted works                                                                            |      |

| Mizoram University on 2019-03-01                                                              | <1%  |

| 64 Submitted works                                                                            |      |

| Nanyang Technological University on 2025-04-12                                                | <1%  |

|                                                                                               |      |

| 65 Publication Shubham Tayal, Ashutosh Nandi. "Study of Temperature Effect on Junctionless Si | <1%  |

| Shasham Tayar, Ashatosh Nahai. Study of Temperature Effect on Juniculomess St                 | ~170 |

| 66 Submitted works                                                                            |      |

| Silicon Institute of Technology on 2020-04-12                                                 | <1%  |

| 81 Publication                                                                     |     |

|------------------------------------------------------------------------------------|-----|

| Jyi-Tsong Lin. "A unipolar-CMOS with recessed source/drain load", 2011 9th IEEE I  | <1% |

| 82 Publication                                                                     |     |

| K.P. Pradhan, S.K. Mohapatra, P.K. Sahu, D.K. Behera. "Impact of high-k gate diele | <1% |

| 83 Submitted works                                                                 |     |

| National Institute of Technology Jamshedpur on 2021-06-11                          | <1% |

| 84 Publication                                                                     |     |

| P. Vanitha, T.S. Arun Samuel, D. Nirmal. "A New 2 D Mathematical Modeling of Su    | <1% |

| 85 Publication                                                                     |     |

| Ranuarez, J.C "A review of gate tunneling current in MOS devices", Microelectro    | <1% |

| 86 Submitted works                                                                 |     |

| Southern University College on 2021-01-07                                          | <1% |

| 87 Internet                                                                        |     |

| dn790000.ca.archive.org                                                            | <1% |

| 88 Internet                                                                        |     |

| docplayer.net                                                                      | <1% |

| 89 Internet                                                                        |     |

| doczz.net                                                                          | <1% |

| 90 Internet                                                                        |     |

| eitca.org                                                                          | <1% |

| 91 Internet                                                                        |     |

| iusnews.ir                                                                         | <1% |

| 92 Internet                                                                        |     |

| slidehtml5.com                                                                     | <1% |

#### **CHAPTER 1**

## INTRODUCTION

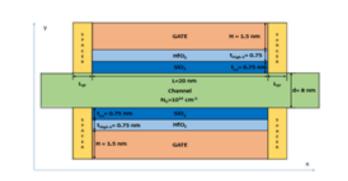

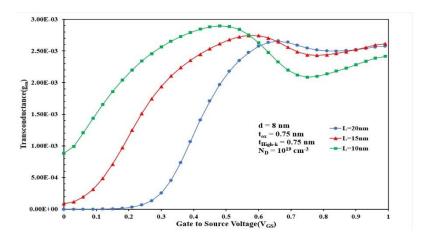

Double gate MOSFETs are emerging as one of the most encouraging ways to lessen SCEs (Short-channel-effects) as CMOS scaling moves closer to its ideal state. Quantum effects [1] are now important in downsized devices in addition to SCEs, particularly when the gate length is less than 20 nm. When the gate length of a device falls below 20 nm, its electrostatic control rapidly declines. Due to the impact of quantum confinement on the carrier's motion, the distribution phenomena and transport characteristics of charge carriers differ from those of classical carriers [1]. Several analytical models for Junctionless Transistors have been published, including Dual Metal Gate engineered Surrounding Gate structure (DMSG) [2], Gate and Drain work function engineered Double Gate structure [3, 4], Gate All Around structure (GAA) [5], and Electrostatic potential distribution, subthreshold current, threshold voltage, and SCEs for Double Gate structure (DG) [6-8]. According to reports, the device's performance will be enhanced by inserting the gate-stack, by developing a high-K layer over the SiO<sub>2</sub> [9–11]. The JL DG FET's preliminary analysis and result are likely to be successful, and they highlight the necessity of a thorough examination of the devices' applicability for contemporary wireless communication systems, including radio frequency integrated circuit (RFIC) design, cellular phones, wireless networks, navigation systems, radio broadcasting, etc.

As semiconductor fabrication technologies push the boundaries of miniaturization, traditional transistor architectures increasingly struggle with performance degradation. Key challenges include threshold voltage roll-off, poor subthreshold swing, and increased leakage currents, all of which can compromise power efficiency and signal fidelity. To address these limitations, researchers have proposed various multigate structures, among which the Double-Gate (DG) configuration stands out due to its superior electrostatic integrity. Meanwhile, the junctionless approach simplifies fabrication by eliminating abrupt junctions, offering process-friendly characteristics and reduced variability in ultra-scaled nodes [12]. By merging the double-gate architecture with junctionless operation, the resulting device benefits from improved control over channel potential and suppression of short-channel effects. This synergy also enables a more uniform electric field distribution along the channel, which can enhance carrier transport and device reliability [13]. For analog and RF circuit designers, these characteristics translate into better linearity,

increased transconductance, and lower noise – all critical in modern high-performance electronics. Furthermore, incorporating a gate stack that uses high-κ dielectric materials improves gate capacitance without compromising gate leakage, ensuring high-frequency compatibility while maintaining power efficiency [14].

The analog/RF performance of conventional double gate devices has been studied by several researchers [15-17], but there are just a few papers on JL DG devices that explore their usefulness for analog/mixed-signal system-on-chip applications [18, 19]. Cho et al. [18] investigated the RF performance of JL nanowire devices in a recent work; however, the impact of downscaling on the RF/analog performance was not thoroughly examined and is still largely unknown. Therefore, better RFIC design for wireless communication systems requires an understanding of how gate-length down scaling affects the DG JL FET's performance figure-of-merits. To ensure low intermodulation and higher-order, the RF system must be linear [19]. Numerous system-level methods that need for intricate circuitry are currently available to reduce these unwanted signals with frequencies distinct from the input signal.

With increasing demands for compact and power-efficient transceivers in 5G, IoT, and wearable technologies, the focus has shifted toward intrinsic linearity at the transistor level. While system-level linearization techniques such as feedback and digital predistortion are widely used, they come with trade-offs in complexity and energy consumption [20]. By achieving better linearity within the device itself, circuit designers can build simplified and more efficient RF systems. Junctionless DG MOSFETs, owing to their symmetric architecture and undoped channel, provide a promising platform for these applications [21].

Thus, it becomes beneficial to make an effort to improve linearity at device-level. Analog & RF (radio-frequency) performance analysis of nanoscale devices is made possible by current research. Linearity, noise figure, cutoff frequency, and inherent gain make up the performance requirements for analog and radio frequency circuits [22–27].

In addition to linearity, parameters like high gain-bandwidth product and low output conductance are essential for RF amplifier stages and analog signal processing. Junctionless DG MOSFETs inherently demonstrate low parasitic resistance due to their uniformly doped channel, which also reduces sensitivity to random dopant fluctuations—a major source of mismatch in scaled CMOS [28]. Their simplified structure and robust control over the conduction path make them suitable

candidates for integration into RF front-end components, including low-noise amplifiers (LNAs), voltage-controlled oscillators (VCOs), and mixers [29].

Moreover, the electrostatic potential across the channel in JL DG devices tends to remain more stable across process variations, allowing more predictable behavior in both analog and digital domains. This is crucial when transistors are used in systems-on-chip (SoCs), where maintaining analog integrity alongside high-speed digital blocks becomes increasingly difficult due to substrate noise coupling and voltage fluctuations [30].

Another vital consideration is the role of quantum effects in ultra-scaled devices. As dimensions shrink below 10 nm, the assumptions of classical charge transport models begin to break down. Instead, phenomena like quantum confinement and tunneling become dominant, altering capacitance, threshold voltage, and mobility [31]. Accurate modeling of such effects is essential not only for understanding device physics but also for correctly predicting performance under real operating conditions. Advanced simulation platforms, including Silvaco ATLAS TCAD, incorporate quantum-corrected drift-diffusion models that help bridge this gap [32].

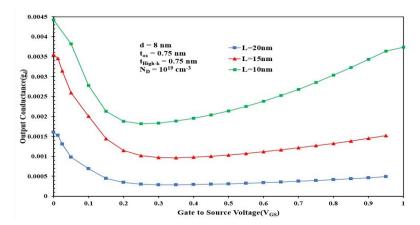

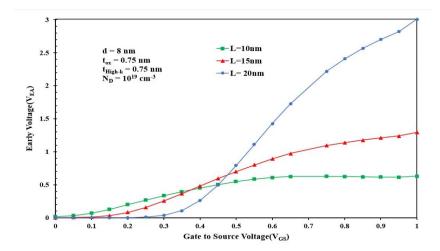

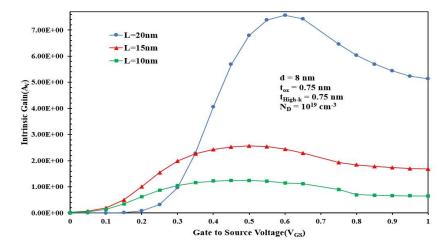

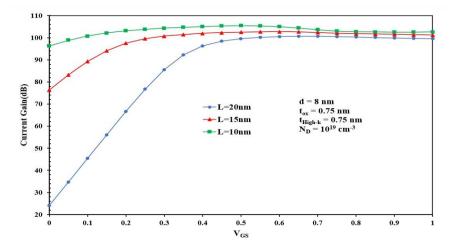

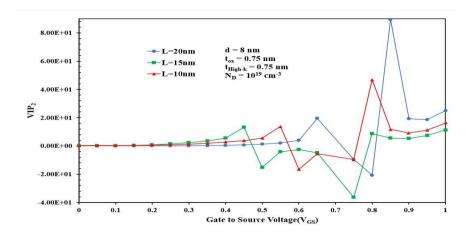

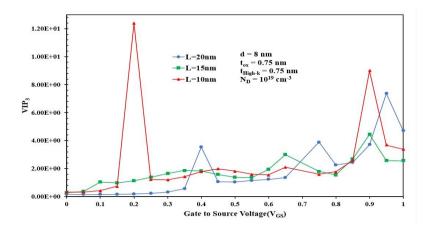

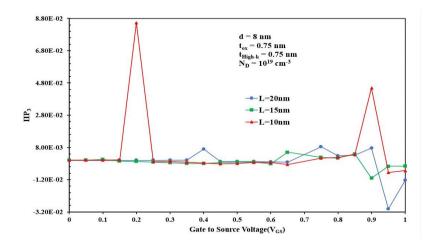

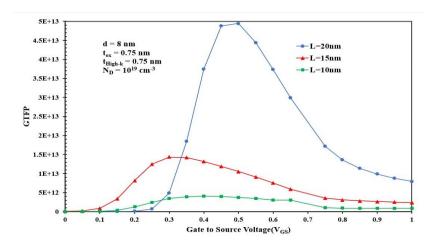

Therefore, in this paper, our main interest is to investigate both, the analog application for the Junctionless Double-Gate Stack MOSFET whilst considering quantum mechanical effects. To investigate analog & RF performance parameters of the device for wireless-communication applications, section IV depicts the results for the same. The section is divided in four parts respectively studying the analog, RF and linearity for the proposed device. Parameters like intrinsic gain (Av), TGF, gd, gm, VEA, f<sub>T</sub>, Gain-Bandwidth Product, S parameters, VIP<sub>2</sub>, VIP<sub>3</sub> & others are extensively discussed here. Simulations are done using the Silvaco ATLAS TCAD software show that the device parameters are suitable for better performance.

Ultimately, the ability of JL DG MOSFETs to meet the rigorous demands of modern analog/RF applications lies in their unique blend of structural simplicity, robust scalability, and superior electrostatics. When accurately modeled with quantum effects and verified through simulation, these devices show great promise for integration into next-generation wireless communication systems and analog signal chains [33, 34].

#### **CHAPTER 2**

#### LITERATURE SURVEY

#### 2.1 EVOLUTION OF MOSFET ARCHITECTURES FOR SCALING

The relentless pursuit of Moore's Law has driven the miniaturization of MOSFETs, leading to significant challenges in maintaining device performance at nanometer scales. Traditional bulk MOSFETs suffer from short-channel effects (SCEs), including threshold voltage roll-off, drain-induced barrier lowering (DIBL), and increased leakage currents, which degrade device reliability and performance [35]. To mitigate these issues, multi-gate structures such as Double-Gate (DG) MOSFETs have been proposed. DG MOSFETs offer superior electrostatic control over the channel, effectively suppressing SCEs and improving subthreshold characteristics [36]. The symmetrical gate configuration in DG MOSFETs enhances gate control, leading to improved scalability and performance in analog and RF applications [37].

## 2.2 JUNCTIONLESS TRANSISTOR CONCEPT AND INTEGRATION WITH **DG ARCHITECTURE**

The Junctionless (JL) transistor concept emerged as a solution to the complexities associated with junction formation in traditional MOSFETs. In JL transistors, the channel is uniformly doped, and current conduction is modulated by gate-induced depletion, eliminating the need for abrupt junctions [38].

Colinge et al. introduced the JL transistor, demonstrating its potential for simplified fabrication and reduced variability [39]. Integrating the JL concept with DG architecture combines the benefits of both approaches, resulting in Junctionless Double-Gate (JL DG) MOSFETs that exhibit excellent electrostatic control and simplified manufacturing processes [40]. Analytical and simulation studies have explored various JL DG structures, including Dual Material Gate (DMG) configurations, which further enhance device performance by modulating the electric field distribution along the channel [41]. These advancements have shown promise in

improving analog and RF characteristics, making JL DG MOSFETs suitable for highfrequency applications.

#### 2.3 GATE STACK ENGINEERING AND HIGH-K INTEGRATION

As device dimensions shrink, gate leakage becomes a significant concern. Incorporating high-κ dielectrics into the gate stack has been a pivotal development in addressing this issue. High-k materials, such as HfO2, allow for increased gate capacitance without the associated leakage currents of traditional SiO<sub>2</sub> dielectrics [42].

In JL DG MOSFETs, gate stack engineering with high-κ materials enhances gate control, reduces leakage currents, and improves overall device performance. Studies have shown that integrating high-κ dielectrics leads to better subthreshold swing, increased transconductance, and improved analog gain, which are critical parameters for analog and RF applications [43].

Furthermore, the combination of high-κ dielectrics with metal gates allows for work function tuning, enabling precise threshold voltage control. This integration is essential for optimizing the performance of JL DG MOSFETs in analog and RF circuits, where device linearity and gain are paramount [44].

## 2.4 ANALOG AND RF PERFORMANCE METRICS IN SCALED DEVICES

The analog and RF performance of MOSFETs is characterized by parameters such as transconductance  $(g_m)$ , output conductance  $(g_d)$ , intrinsic gain  $(A_V)$ , cutoff frequency (f<sub>T</sub>), and maximum oscillation frequency (f<sub>max</sub>). These metrics are crucial for evaluating device suitability in high-frequency applications. In JL DG MOSFETs, the elimination of junctions and the double-gate configuration contribute to enhanced analog and RF performance. Studies have reported improvements in gm and Av, as well as higher f<sub>T</sub> and f<sub>max</sub> values, compared to conventional MOSFETs [45]. However, scaling down the gate length in JL DG MOSFETs presents challenges. Shorter gate lengths can lead to increased SCEs, affecting device linearity and gain. Research has indicated that careful optimization of device dimensions and materials is necessary to maintain high analog and RF performance in scaled JL DG MOSFETs [46].

#### 2.5 LINEARITY AND NOISE IN NANOSCALE MOSFETS

Linearity is a critical parameter in analog and RF circuits, as nonlinearities can lead to signal distortion and intermodulation. JL DG MOSFETs offer advantages in linearity due to their uniform doping and symmetrical structure, which result in a more uniform electric field distribution along the channel [47]. Noise performance, particularly flicker (1/f) noise and thermal noise, is another important consideration. The absence of abrupt junctions in JL DG MOSFETs reduces carrier trapping and scattering, leading to lower noise levels. This characteristic makes JL DG MOSFETs attractive for low-noise amplifier applications in RF circuits [48].

## 2.6 QUANTUM EFFECTS AND THE NEED FOR ACCURATE MODELING

As MOSFET dimensions approach the nanometer scale, quantum mechanical effects become significant. Quantum confinement and tunneling phenomena can alter carrier transport, affecting device characteristics such as threshold voltage and subthreshold swing.

Accurate modeling of these quantum effects is essential for predicting device behavior and performance. Advanced simulation tools, such as TCAD, incorporate quantum mechanical models to analyze the impact of quantum effects on JL DG MOSFETs. Studies have shown that quantum confinement can lead to increased threshold voltage and reduced carrier mobility, necessitating careful design considerations [49].

#### 2.7 IDENTIFIED RESEARCH GAPS

Despite the advancements in JL DG MOSFET research, several areas require further investigation:

- Comprehensive Analysis: While individual aspects of JL DG MOSFET performance have been studied, a holistic analysis encompassing analog, RF, linearity, and noise characteristics is lacking.

- Quantum Effects: The impact of quantum mechanical effects on analog and RF performance metrics in JL DG MOSFETs needs more in-depth exploration.

- **Scaling Challenges:** Understanding the trade-offs and limitations associated with scaling JL DG MOSFETs for high-frequency applications remains an open area of research.

Addressing these gaps is crucial for the development of JL DG MOSFETs optimized for analog and RF applications in advanced integrated circuits.

## **CHAPTER 3**

## **QUANTUM EFFECTS IN MOSFETS**

#### 3.1 SCALING OF MOSFET

#### Challenge 1: Threshold Voltage and Leakage Trade-Offs

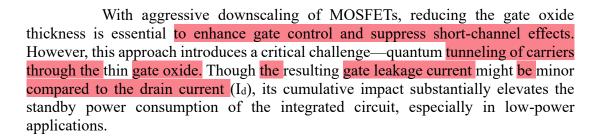

To preserve the switching speed of MOSFETs at lower supply voltages, it is necessary to proportionally reduce the threshold voltage (V<sub>T</sub>). However, this reduction introduces unintended consequences. A lower V<sub>T</sub> leads to an increase in subthreshold leakage current, which significantly impacts the power efficiency and performance reliability of the device. Moreover, achieving a lower threshold voltage often necessitates thinning the gate oxide layer. This, in turn, results in an increase in gate oxide tunneling current—a form of leakage that further deteriorates the device's performance by diminishing the I<sub>on</sub>/I<sub>off</sub> current ratio, thus reducing switching precision and operational control.

#### Challenge 2: Short-Channel Effects and Electrostatic Control

The continual miniaturization of MOSFETs also introduces electrostatic integrity issues. As the channel length shrinks, two-dimensional electrostatic interactions between the gate and the source/drain regions become more prominent. This electrostatic charge sharing leads to a further decline in threshold voltage and an increase in subthreshold swing. Consequently, the gate's control over the channel weakens, leading to a lower I<sub>on</sub>/Ioff ratio and degraded switching behavior. These shortchannel effects limit the scalability and reliability of conventional MOSFET architectures.

turnitin t

#### 3.2 BLOCH'S THEOREM

A Bloch wave (or Bloch function) describes the quantum behavior of particles, such as electrons, in a periodic potential—typically a crystal lattice. It is mathematically represented as a plane wave modulated by a function with the periodicity of the lattice[50]. According to Bloch's theorem, the wave function  $\Psi$  of an electron in a crystalline solid can be written in the form:

$$\Psi_r = e^{ik \cdot r} u(r) \tag{3.1}$$

Here, u(r) is a periodic function with the same periodicity as the crystal lattice. This theorem implies that the energy eigenstates in a crystal can be completely described using Bloch waves, laying the foundation for understanding electronic band structures [50]. In semiconductors, the periodic function  $u_c(r)$  satisfies:

$$u_c = u_r(\vec{r} + \vec{R}) \tag{3.2}$$

where R is a lattice vector. Similarly, in reciprocal space, for a wave vector k, there exists a periodic function  $\phi_k$  such that:

$$\phi(\mathbf{k}) = \phi(\mathbf{k})(\mathbf{r} + \mathbf{R}) \tag{3.3}$$

$$\Phi_c = e^{ik\vec{r}} \Phi_k(\vec{k}, \vec{r})$$

(3.4)

Solving Eqns (3.1) and (3.2) provides the E-k relationship, which describes the dependence of energy on wave vector, ultimately determining the band structure. Carrier motion in semiconductors follows this E-k relationship, and for weak electric fields, electrons and holes can be treated as quasi-classical particles with an effective mass m\* defined by:

$$m^* = \frac{\frac{1}{\hbar^2} \partial^2 E}{\partial \kappa^2} \tag{3.5}$$

In such conditions, the carriers' quantum behavior is masked, and their motion can be modeled using classical mechanics. However, when dimensions become comparable to the de Broglie wavelength or when subjected to strong external fields, this approximation breaks down. The external field can no longer be treated as a small perturbation, and quantum mechanical effects (QMEs) such as tunneling and quantized energy levels become significant. In such nanoscale regimes, one must solve the time-independent Schrödinger equation, incorporating both the periodic crystalline potential  $U_C(r)$  and the external potential  $V_E(r)$ :

$$-\frac{\hbar^2}{2m_0} \nabla^2 \Psi_c + [U_C(\vec{r}) + V_E(\vec{r})] \Psi_c(\vec{r}) = E \Psi_c(\vec{r})$$

(3.6)

where:

- $\hbar = h/2\pi = 1.054 \text{ x} \cdot 10^{-34} \text{ J.S}$  is the reduced Planck constant,

- $m_0=0.911\times10^{-27}$  kg is the electron rest mass,

- $U_C(\vec{r})$  is the periodic potential from the crystal lattice,

- $V_E(\vec{r})$  represents the potential due to an external electric field.

In large crystals,  $V_E(\vec{r})$  is usually negligible compared to  $U_C(\vec{r})$ , and the equation simplifies to:

$$-\frac{\hbar^2}{2m_0}\nabla^2\Psi_c + U_C(\vec{r})\Psi_c(\vec{r}) = E\Psi_c(\vec{r})$$

(3.7)

This simplified model is valid only when quantum interference and boundary effects are negligible [51].

#### 3.3 QUANTUM MECHANICAL EFFECTS

#### 3.3.1 Introduction to Quantum Tunneling

Quantum tunneling is a fundamental phenomenon of quantum mechanics wherein a subatomic particle transitions through a potential energy barrier, despite possessing insufficient kinetic energy to overcome it classically. This effect is explained through the probabilistic nature of wavefunctions, where a particle's presence vanishes from one side of a potential well and reappears on the other side without any conventional current flowing within the barrier itself. This non-intuitive behavior, although negligible in larger devices, becomes increasingly significant in nanoscale semiconductor structures such as modern MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors).

### 3.3.2 Tunneling Concerns in Scaled MOSFETs

The thickness of the gate dielectric directly influences the tunneling probability. A thicker oxide layer limits the extension of electron wavefunctions into the barrier, reducing tunneling effects. Conversely, in sub-2 nm silicon dioxide layers, electron wavefunctions penetrate the barrier easily, resulting in considerable gate leakage current due to tunneling [50][51].

#### 3.3.3 Tunneling Mechanisms in MOSFETs

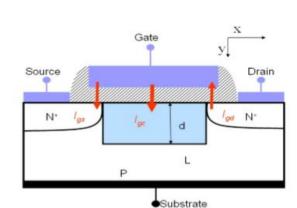

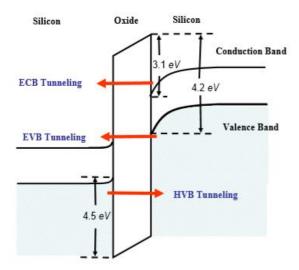

In scaled devices, several tunneling processes are observed:

Electron Conduction Band (ECB) Tunneling: Dominates in n-MOSFETs, where electrons tunnel from the gate into the conduction band of the channel.

- **Hole Valence Band (HVB) Tunneling**: Prominent in p-MOSFETs, with holes tunneling into the valence band.

- Electron Valence Band (EVB) Tunneling: Occurs only under high gate voltages that exceed typical digital CMOS operating levels, rendering it negligible for practical circuit operation [52].

The prevalence of tunneling is strongly influenced by the energy band alignment and the barrier height, which itself is determined by the electron affinity difference between the oxide and the adjacent materials (metal or semiconductor). This creates a potential barrier given by:

$$E = q\chi \tag{3.8}$$

Where  $\chi$  is the electron affinity of the oxide and q is the elementary charge.

Fig 3.2 Energy band diagram for tunneling components in an MOS structure

turnitin 🖯

## 3.3.4 Trapezoidal Potential Barrier and WKB Approximation

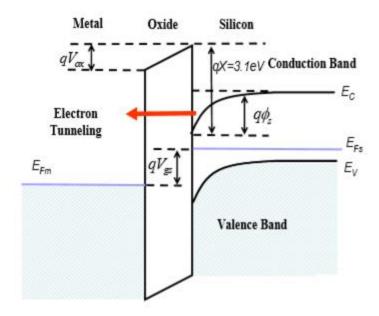

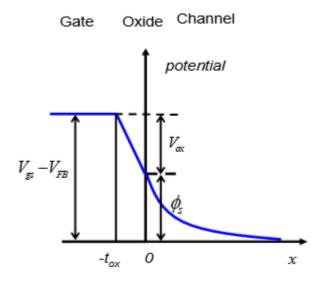

Fig 3.3 Potential at the junction

Fig. 3.4 Potential distribution in the gate-to-channel direction for a metal-gate MOSFET

Due to the applied gate-to-source voltage  $V_{gs}$ , the potential barrier assumes a trapezoidal shape. The voltage drop across the oxide is given as [53]:

$$V_{ox} = V_{gs} - V_{FB} - \phi_S \tag{3.9}$$

Where V<sub>FB</sub> is the flat-band voltage and  $\phi_S$  is the surface potential. Consequently:

$$qV_{gs} = E_{Fs} - E_{Fm} \tag{3.10}$$

the Wentzel-Kramers-Brillouin (WKB) approximation, tunneling probability through a trapezoidal barrier is estimated as:

$$D(E_x) = -\frac{2}{\hbar} \int_{x_1}^{x_2} \sqrt{2m_{OX}(E_b(x) - E_x)} \, dx \tag{3.11}$$

Where:

- E<sub>x</sub> is the electron's kinetic energy in the x-direction.

- tox is the oxide thickness.

- $m_{OX} = 0.35 m_o$ , the effective mass of the electron in the oxide.

- E<sub>b</sub> is the average potential barrier height:

$$E_b(x) = q\chi + qV_{ox} \cdot \frac{x}{t_{ox}}$$

(3.12)

## 3.3.5 Many-Electron Case and Fermi-Dirac Statistics

For systems with many electrons, individual electrons can occupy a continuum of energy states. The probability of occupancy of any energy level E is defined by the Fermi-Dirac distribution:

$$f(E) = \frac{1}{1 + \exp\left(\frac{E - E_f}{kT}\right)}$$

(3.13)

Where E<sub>f</sub> is the Fermi energy, k is Boltzmann's constant, and T is the absolute temperature. Although hole tunneling is theoretically possible, the higher potential barrier for holes compared to electrons renders hole tunneling significantly less probable in typical device conditions.

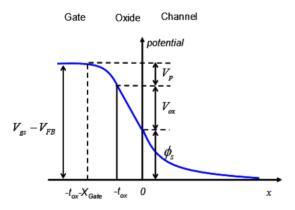

#### 3.3.6 Tunneling Effects in Polysilicon Gate Structures

In MOSFETs using polysilicon gates, the voltage drop across the gate itself must be accounted for. This causes an upward band bending near the polysilicon/oxide interface. The oxide voltage drop becomes:

$$V_{OX} = V_{qs} - \varphi_s - V_p \tag{3.14}$$

Where  $V_p$  is the voltage drop within the polysilicon gate given by:

$$V_p = \frac{1}{2} \left( \frac{q}{\epsilon_{Si}} \right) N_{Gate} X_{Gate}^2$$

(3.15)

Here,  $N_{Gate}$  is the doping concentration and  $X_{Gate}$  is the gate depletion depth. For  $V_{gs}$   $V_{T}$ , the depletion width becomes:

$$X_{Gate} = \frac{\epsilon_{Si}}{\epsilon_{ox}} t_{ox} \sqrt{\left(1 + \frac{2\epsilon_{ox}^2 (V_{gs} - \varphi_s - V_{FB})}{q N_{Gate} \epsilon_{Si} t_{ox}^2}\right)} - 1$$

(3.16)

Fig. 3.5 Potential diagram for the poly-silicon gate MOSFET

As the gate voltage increases, polysilicon depletion leads to reduced electric field at the oxide interface. Therefore, the tunneling density in polysilicon gates is typically lower than that in metal gates at the same gate bias.

#### 3.3.7 High-κ Gate Dielectrics as a Solution

To suppress direct tunneling while preserving gate control, the semiconductor industry has transitioned from conventional SiO<sub>2</sub> to high-dielectric constant (high-κ) materials like hafnium oxide (HfO<sub>2</sub>) and hafnium silicate (HfSiO<sub>2</sub>). These materials enable an increase in physical thickness while maintaining or

improving the gate capacitance, which is crucial for controlling short-channel effects without incurring excessive leakage [54].

The equivalent oxide thickness (EOT) of a high-κ dielectric compared to SiO<sub>2</sub> is defined as:

$$E_{OT} = \frac{\epsilon_{ox}}{\kappa \epsilon_o} t_1 \tag{3.17}$$

Where  $t_1$  is the physical thickness of the high- $\kappa$  dielectric, and  $\kappa$  is its relative dielectric constant. A higher  $\kappa$  value effectively reduces the EOT, enhancing gate control while suppressing quantum tunneling currents[55].

#### **CHAPTER 4**

## **QUANTIZATION MODEL**

The quantization model is instrumental in mitigating short-channel effects (SCEs) in MOSFETs. Advancements in device technology have led to the adoption of highly doped channels and ultra-thin gate oxides. While the increased vertical electric field aids in maintaining gate control over the channel against drain potential influences, it also confines the movement of the narrow potential well [56].

From quantum theory, the energy levels of channel carriers are discrete rather than continuous, as predicted by classical models. This quantization leads to a redistribution of carrier density near the Si/SiO<sub>2</sub> interface compared to classical predictions.

$$|\Psi(x,t)|^2 dx = \left\{ \begin{array}{l} \text{probability of finding the particle} \\ \text{between } x \text{ and } (x+dx), \text{ at time } t. \end{array} \right\}$$

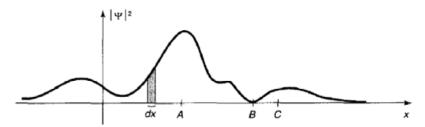

Fig. 4.1 Probability distribution

To analyze quantum mechanical effects (QMEs) in MOSFETs, it's essential to introduce the wave function characterizing inversion charges based on the Schrödinger equation:

$$-\frac{\hbar^2}{2m^*}\nabla^2\Psi(x,y) - q\phi(x,y)\Psi(x,y) = E\Psi(x,y)$$

(4.1)

31

#### Where:

- $\hbar$  is the reduced Planck's constant,

- m\* is the effective mass of electrons in silicon,

- $\Psi(x,y)$  is the electron wavefunction,

- q is the electron charge,

- $\phi(x,y)$  is the electric potential,

- E is the energy of the electrons.

The electric potential  $\phi(x,y)$  is determined by the Poisson equation:

$$\frac{\partial^2 \phi(x,y)}{\partial x^2} + \frac{\partial^2 \phi(x,y)}{\partial y^2} = \frac{q}{\epsilon_{Si}} (N_A + n(x,y))$$

(4.2)

Where:

- $\varepsilon_{Si}$  is the permittivity of silicon,

- N<sub>A</sub> is the doping concentration of the channel,

- n(x,y) is the electron density.

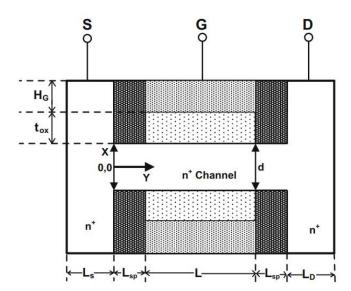

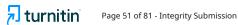

Fig. 4.2 Cross-sectional view of double gate junctionless transistor

Figure 2.1 illustrates a double-gate (DG) junctionless n-MOSFET. Here, H<sub>G</sub>, t<sub>ox</sub>, and d represent the thicknesses of the metal layer, oxide layer, and channel, respectively. L, L<sub>sp</sub>, L<sub>s</sub>, and L<sub>D</sub> denote the lengths of the channel, spacer, source, and drain regions, respectively. The coordinate system is defined with the Y and X directions along and perpendicular to the channel, respectively, and the Z direction

🗾 turnitin

along the channel's width. To solve for the actual DG junctionless MOSFET, we first consider a simplified approach by solving a one-dimensional (1D) Schrödinger equation for an infinite potential well.

#### 4.1 ONE-DIMENSIONAL INFINITE POTENTIAL WELL

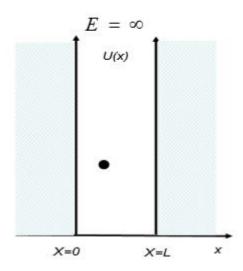

Fig. 4.3 Potential Well

In this model, the potential V(x)V(x)V(x) is defined as:

$$V(x) = \begin{cases} 0, & 0 < x < a \\ \infty, & x \le 0 \end{cases}$$

(4.3)

The wave function  $\Psi(x)$  must vanish where  $V(x) = \infty$ , leading to the boundary conditions:

$$\Psi(x) = 0 \forall x < 0, x > a \tag{4.4}$$

Within the interval 0 < x < a0 < x <becomes:

$$\frac{d^2\Psi}{dx^2} = -\frac{2mE}{\hbar^2}\Psi\tag{4.5}$$

Letting  $k^2 = \frac{2mE}{\hbar^2}$ , we have:

$$\Rightarrow \frac{\partial^2 \Psi}{\partial x^2} = -k^2 \Psi \tag{4.6}$$

The general solution is:

$$\Psi(x) = c_1 \cos(kx) + c_2 \sin(kx) \tag{4.7}$$

- Applying the boundary conditions:

- 1.  $\Psi$  (0) =0 implies  $c_1$ =0,  $\Psi(a)=0$  leads to  $c_2\sin(ka)=0$ , which implies  $ka=n\pi$ , where n=1,2,3...n

Therefore, the normalized wave function is:

$$\Psi_n = \sqrt{\frac{2}{a}} \sin(n\pi x / a) \tag{4.8}$$

The corresponding energy levels are:

$$E = \frac{\hbar^2 k^2}{2m} = \frac{\hbar^2 \pi^2 n^2}{2ma^2} \forall n = 1, 2, 3, 4, \dots$$

(4.9)

This model provides a foundational understanding of quantum confinement in semiconductor devices.

#### 4.2 TWO-DIMENSIONAL **SCHRÖDINGER EQUATION** A RECTANGULAR POTENTIAL WELL

Extending the analysis to two dimensions, consider a rectangular potential well where the potential energy U(x,y) is [57]:

$$U(x,y) = \begin{cases} 0, & x \le \frac{d}{2} \\ \infty, & x \ge \frac{d}{2} \end{cases}$$

(4.10)

Assuming electron motion in the x and y directions, the two-dimensional Schrödinger equation is:

$$-\frac{\hbar^2}{2m^*}\nabla^2\Psi_n(\mathbf{x},\mathbf{y}) - q\phi(\mathbf{x},\mathbf{y})\Psi_n(\mathbf{x},\mathbf{y}) = E_n\Psi_n(\mathbf{x},\mathbf{y})$$

(4.11)

Within the well, where U(x,y)=0, the equation simplifies to [58]:

$$-\frac{\hbar^2}{2m^*} \left[ \frac{\partial^2 \Psi_n(x,y)}{\partial x^2} + \frac{\partial^2 \Psi_n(x,y)}{\partial y^2} \right] = E_n \Psi_n(x,y)$$

(4.12)

Employing separation of variables:

$$\Psi(x, y) = X(x)Y(y) \tag{4.13}$$

Substituting into the equation yields:

For X(x):

$$\Rightarrow -\frac{\hbar^2}{2m^*} \left[ \frac{\partial^2 \Psi_n(x, y)}{\partial x^2} \right] = E_{\chi} X(\chi) \tag{4.14}$$

2. For Y(y):

$$\Rightarrow -\frac{\hbar^2}{2m^*} \left[ \frac{\partial^2 \Psi_n(x, y)}{\partial y^2} \right] = E_x Y(y) \tag{4.15}$$

Where  $E=E_x+E_y$ .

Solving for X(x):

$$X(x) = A_x \sin(k_x x) + B_x \cos(k_x x)$$

(4.16)

Applying boundary conditions:

•

$$X(\frac{d}{2})=0,$$

(4.17)

•

$$X(-\frac{d}{2})=0,$$

(4.18)

We find that:

$$k = \frac{n\pi}{d} \forall n = 1, 2, 3, \dots$$

(4.19)

Similarly, for Y(y), assuming infinite potential walls at y=0 and y=L:

$$Y(y) = A_y \sin(k_y y) + B_y \cos(k_y y)$$

(4.20)

Applying boundary conditions:

•

$$Y(0)=0$$

, (4.21)

•

$$Y(L)=0$$

, (4.22)

We deduce:

$$k = \frac{m\pi}{L} \forall n = 1, 2, 3, \dots$$

(4.23)

The normalized wave function is [59]:

$$\Psi_{n,m}(x,y) = \sqrt{\frac{2}{d}} \sin \frac{n\pi x}{d} \cdot \sqrt{\frac{2}{L}} \sin \frac{m\pi y}{L}$$

(4.24)

The energy levels are:

$$E_{n,m} = \frac{\hbar^2 \pi^2}{2m^*} \left( \frac{n^2}{d^2} + \frac{m^2}{L^2} \right) \tag{4.25}$$

These quantized energy states are pivotal in understanding the behavior of electrons in confined systems, such as quantum wells and nanostructures.

# CHAPTER 5

## BAND STRUCTURE AND PROPERTIES

The band structure of a solid is a fundamental concept in solid-state physics that describes the range of energy levels that electrons within a material can occupy. It is critical in determining whether a material behaves as a conductor, semiconductor, or insulator, based on the distribution and separation of these energy levels. Specifically, a band structure represents the allowed energy states of electrons as a function of their wave vector  $\vec{k}$ , which corresponds to momentum in a periodic crystal lattice [1][2].

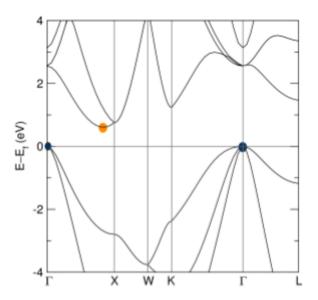

Fig. 5.1 Band Structure of Silicon

A band structure diagram is a graphical representation that maps the relationship between electron energy and momentum within the first Brillouin zone, a uniquely defined region in reciprocal space. These diagrams are often referred to as

"spaghetti plots" due to the tangled appearance of multiple energy bands. Despite their complexity, they allow researchers to extract crucial information about a material's electronic behavior. For instance:

- If the valence band maximum (VBM) and the conduction band minimum (CBM) do not overlap and are separated by an energy gap, the material is an insulator or a semiconductor, depending on the size of the gap [1].

- If these bands overlap or touch, the material exhibits metallic or semi-metallic behavior.

- The nature of the band gap (direct or indirect) is determined by whether the VBM and CBM occur at the same  $\vec{k}$ -point in the Brillouin zone.

- The curvature of the energy bands around the extrema indicates the effective mass of charge carriers, and thus provides insight into carrier mobility [3].

For instance, the band structure of silicon (Si) reveals that its CBM and VBM are located at different  $\vec{k}$ -points. The conduction band minimum lies near the X point, while the valence band maximum is near the  $\Gamma$  point. This results in an indirect band gap of approximately 1.1 eV at room temperature (though some computational models may estimate it around 0.62 eV due to underestimation in Density Functional Theory without advanced corrections) [4]. This indirect gap makes Si less efficient for optoelectronic applications like LEDs, where direct recombination of electrons and holes is desired.

The energy eigenvalues  $E(\vec{k})$  that constitute the band structure are calculated using solutions to the Schrödinger equation with a periodic potential, as described by Bloch's theorem. These calculations are carried out in reciprocal space (k-space), which reflects the momentum characteristics of electrons rather than their positions [1][2]. The use of wave vector  $\vec{k}$ , representing the electron's crystal momentum, simplifies the problem by taking advantage of the periodicity of the lattice.

The crystal momentum (also known as quasi-momentum) is defined by:

$$\vec{p}_{crystal} = \hbar \, \vec{k} \tag{5.1}$$

Where:

- $\vec{p}_{crystal}$  is the crystal momentum,

- $\hbar$  is the reduced Planck's constant,

- $\vec{k}$  is the wave vector.

In crystals, the allowed  $\vec{k}$ -values are constrained to the first Brillouin zone, which is the Wigner-Seitz cell in reciprocal space [2]. This zone contains all the unique momentum states of electrons due to the periodic nature of the lattice.

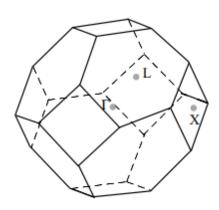

For face-centered cubic (FCC) lattices—common in semiconductors such as GaAs, Si, and Ge—the Brillouin zone exhibits high-symmetry points labeled as  $\Gamma$  (center), X, L, and K, among others. The electronic band extrema often lie at or near these symmetry points. For example:

- In Silicon, the CBM is at the X point, and the VBM is at  $\Gamma \rightarrow$  indirect gap [4].

- In Gallium Arsenide (GaAs), both CBM and VBM are at  $\Gamma \rightarrow$  direct gap, which is optimal for photon emission [3].

Thus, band structure analysis serves as a powerful predictive tool for determining the electronic, optical, and transport properties of materials. Understanding how these bands arise, shift with strain, doping, or size (as in nanostructures), and interact with external fields is crucial for the design of semiconductor devices like transistors, solar cells, photodetectors, and quantum dots [3][4].

IMPORTANT HIGH SYMMETRY POINTS

$$\Gamma$$

point:  $k_{\chi} = 0 = k_{V} = k_{Z}$

X point:

$$k_x = \frac{2\pi}{a}$$

;  $k_y = k_z = 0$

L point:

$$k_x = k_y = k_z = \frac{\pi}{a}$$

a = lattice constant (cube edge)

Fig. 5.2- Brillouin Zone for fcc lattice

To understand the origin of electronic band structures, it is necessary to begin with the quantum mechanical treatment of a free particle, particularly how its energy relates to its wavenumber k. This foundation is essential for progressing to the more complex periodic systems found in crystalline solids.

We start by solving the time-independent Schrödinger equation for a free particle moving in one dimension, where no external potential is acting on the system. The governing equation is:

$$-\frac{\hbar^2}{2m}\partial^2\Psi(x) = E\Psi(x) \tag{5.2}$$

#### where:

- $\hbar$  is the reduced Planck constant,

- m is the mass of the particle,

- $\Psi(x)$  is the spatial part of the wave function,

- and E is the total energy of the particle.

A trial solution to this differential equation, motivated by the wave-like nature of particles, is:

$$\Psi(x) = Ce^{ikx} \tag{5.3}$$

where C is a normalization constant,  $i=\sqrt{-1}$ , and k is the wavenumber, which characterizes the number of wave cycles per unit length. Substituting this into the Schrödinger equation yields:

$$\frac{\partial^2 \Psi(x)}{\partial x^2} = i^2 k^2 C e^{ikx} = -k^2 C e^{ikx} \tag{5.4}$$

$$\Rightarrow \frac{\hbar^2}{2m} \partial^2 \Psi(x) = \frac{\hbar^2}{2m} k^2 C e^{ikx}$$

(5.5)

$$\Rightarrow E\Psi(x) = \frac{\hbar^2}{2m} k^2 \Psi(x) \tag{5.6}$$

Therefore, we obtain the energy–wavevector relation:

$$E = \frac{\hbar^2}{2m}k^2 \tag{5.7}$$

This quadratic dependence of energy on the wavevector k is a defining characteristic of free particle dispersion and forms the basis for understanding electron motion in crystalline solids [1][2].

To develop an intuitive understanding of the wavenumber k, we turn to the de Broglie hypothesis, which postulates the wave-particle duality of matter. The de Broglie relation is given as:

$$\lambda = \frac{h}{mv} = \frac{h}{p} \tag{5.8}$$

where:

- $\lambda$  is the de Broglie wavelength of the particle,

- h is Planck's constant,

- p= mv is the linear momentum of the particle.

Instead of wavelength  $\lambda$ , we often use the wavenumber defined as:

$$k = \frac{2\pi}{\lambda} \tag{5.9}$$

which describes how many wave cycles fit into a unit distance. Combining the two expressions, the momentum p can be expressed as:

$$p = \hbar k \tag{5.10}$$

Substituting this into the classical kinetic energy expression:

$$E = \frac{1}{2}mv^2 = \frac{p^2}{2m} \tag{5.11}$$

$$\Rightarrow E = \frac{\hbar^2}{2m}k^2 \tag{5.12}$$

This re-derives the quantum mechanical result obtained from solving the Schrödinger equation, thereby reinforcing the consistency between classical and quantum interpretations of a free particle's energy [3].

The implications of this relation are profound. Even though kkk is defined in terms of inverse length (1/ length), it connects directly to momentum, wavelength, and energy. This is particularly crucial in the context of solid-state physics, where electrons are not entirely free but instead experience a periodic potential due to the ion cores in a crystal lattice.

By extending this simple model to periodic systems using Bloch's theorem, and considering the electron's behavior in the first Brillouin zone, one derives the electronic band structures fundamental to understanding semiconductors, insulators, and conductors. In such periodic systems, the same energy—wavevector relationship becomes more complex, leading to the formation of allowed energy bands and band gaps [1][4]. This foundational understanding is critical for interpreting more

advanced topics such as effective mass theory, density of states, and carrier dynamics in semiconductors.

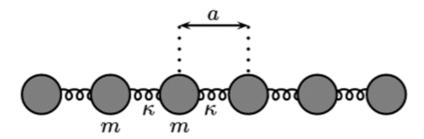

#### 5.1 JUSTIFICATION FOR PARABOLIC ENERGY BANDS

To explore the origin of parabolic energy bands, consider a one-dimensional chain of atoms. Suppose n atoms are arranged linearly, each separated by a uniform distance aa. The position of the n<sup>th</sup> atom is denoted by  $x_n$ , while its equilibrium position is:

$$x_n^{eq} = na (5.13)$$

The displacement from equilibrium is given by:

$$\delta x_n = x_n - x_n^{eq} \tag{5.14}$$

For simplicity, we restrict our analysis to motion along a single spatial dimension.

Fig. 5.3 The one-dimensional monatomic harmonic chain. Each ball has mass m and each spring has spring constant κ. The lattice constant, or spacing between successive masses at rest, is a.

At sufficiently low temperatures, atomic vibrations can be approximated using a harmonic potential, similar to that of a simple harmonic oscillator. Under this assumption, the total potential energy of the system becomes:

$$V_{TOT} = \sum V(x_{i+1} + x_i) = \sum \frac{k}{2} (x_{i+1} - x_i - a)^2$$

(5.15)

$$\Rightarrow V_{TOT} = \sum_{i=1}^{k} (\delta x_{i+1} - \delta x_i)^2$$

(5.16)

The force acting on the n<sup>th</sup> atom is derived from the gradient of the total potential energy:

turnitin t

$$F_n = -\frac{\partial V_{TOT}}{\partial x_n} = k(\delta x_{n+1} - \delta x_n) + k(\delta x_{n-1} - \delta x_n)$$

(5.17)

Which simplifies to:

$$F_n = k(\delta x_{n+1} + \delta x_{n-1} - 2\delta x_n)$$

(5.18)

Assuming a wave-like solution of the form:

$$\delta x_n = Ae^{iwt - ikx_n^{eq}} = Ae^{iwk - ikna} \tag{5.19}$$

Substituting into the equation of motion yields:

$$-m\omega^2 A e^{i\omega t - ikna} = kA e^{i\omega t} e^{-ika(n+1)}$$

(5.20)

$$m\omega^2 = 2k(1 - \cos ka) = 4k\sin^2\frac{ka}{2}$$

(5.21)

Solving this leads to the dispersion relation:

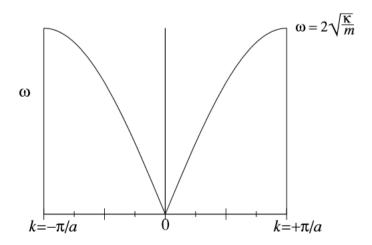

$$\omega = 2\sqrt{\frac{k}{m}} \left| \sin \frac{ka}{2} \right| \tag{5.22}$$

Fig. 5.4 Dispersion relation for vibrations of the one-dimensional monatomic harmonic chain. The dispersion is periodic in  $k \to k + 2\pi/a$

This expression describes the dispersion relation, which is inherently periodic due to the sinusoidal dependence on k. In the long-wavelength limit (small k), the sine function can be approximated linearly, leading to a quadratic dependence of energy on wavevector. This quadratic behavior is characteristic of parabolic energy bands. A similar approach can be extended to tight-binding models and three-

dimensional lattices, where the resulting energy-momentum relations also exhibit parabolic characteristics near the band extrema.

### 5.2 RECIPROCAL LATTICE AND THE BRILLOUIN ZONE

In the previous discussion, we plotted the dispersion relation only within the interval  $-\frac{\pi}{a} \le k \le \frac{\pi}{a}$ . This restriction is not arbitrary—it reflects a fundamental property of periodic systems: the dispersion relation is inherently periodic in wavevector, such that:

$$k \to k + \frac{2\pi}{a} \tag{5.23}$$

This periodicity arises from the underlying periodic structure in real space. More generally, any system with spatial periodicity as will exhibit a corresponding periodicity of  $\frac{2\pi}{a}$  in reciprocal space (also known as k-space).

This concept implies that if a system remains unchanged under a spatial translation  $x \to x + a$ , then in reciprocal space, the dispersion relation remains invariant under  $k \to k + \frac{2\pi}{a}$ . The smallest repeating unit in k-space is referred to as the Brillouin zone, with the first Brillouin zone defined as the region centered around k=0, typically spanning from  $-\pi/a$  to  $\pi/a$ . The points  $k = \pm \frac{\pi}{a}$  are symmetric about the origin and are separated by  $\frac{2\pi}{a}$ .

It is worth reflecting on why the dispersion curve repeats with  $k \to k + \frac{2\pi}{a}$ . This periodicity means that a wavevector shifted by  $\frac{2\pi}{a}$  describes a physically indistinguishable oscillation mode from the original. Mathematically, this is because:

$$e^{-i2\pi np} = 1 \tag{5.24}$$

for any integer pp, which implies that wavefunctions differing by integer multiples of  $2\pi/a$  in wavevector are identical at all lattice points.

This leads to the definition of the reciprocal lattice—a set of wavevectors in k-space that are physically equivalent to k=0. In contrast, the original set of atomic positions xn=na forms the direct lattice (or real-space lattice). These can be expressed as:

$$x_n = \dots - 2a, -a, 0, a, 2a, \dots$$

(5.25)

$$G_n = \dots - 2\left(\frac{2\pi}{a}\right), -\frac{2\pi}{a}, 0, \frac{2\pi}{a}, 2\left(\frac{2\pi}{a}\right), \dots$$

(5.26)

A defining property of the reciprocal lattice is that for any reciprocal lattice vector  $G_m$ , the following condition holds for all real-space lattice points  $x_n$ :

$$e^{iG_m x_n} = 1 (5.27)$$

This condition ensures that Gm is a valid member of the reciprocal lattice.

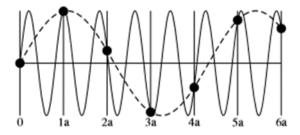

However, this equivalence between k and k+G<sub>m</sub> can be conceptually challenging. For instance, we often associate a wavevector kk with a wavelength  $\lambda=2\pi/k$ . But if k and k+G<sub>m</sub> are physically indistinguishable, which wavelength should we use  $\frac{2\pi}{k}$  or  $\frac{2\pi}{k+Gm}$ ?

Fig. 5.5 Symmetry Points

The resolution lies in recognizing that this equivalence only holds at discrete lattice points  $x_n$ =na. Between these points, the wavefunctions corresponding to k and  $k + \frac{2\pi}{a}$  differ. Therefore, it is meaningless to assign a unique wavelength based solely on the wavevector when sampling is restricted to lattice points. This phenomenon, where different wavevectors yield indistinguishable results at discrete sampling points, is known as aliasing.

#### **CHAPTER 6**

#### EFFECTIVE MASS AND ORIENTATION

### **6.1 EFFECTIVE MASS AND DISPERSION**

Within the framework of the tight-binding model, the energy spectrum of electrons in a periodic potential is given by:

$$E = E_0 - 2t coska \tag{6.1}$$

Unlike the case of free electrons, this dispersion relation exhibits both a maximum and a minimum energy, meaning that electrons can only occupy states within a specific energy range—referred to as an energy band. The term "band" is used to describe both this energy interval and the continuous segment of the dispersion curve associated with it.

The dispersion relation—the functional dependence of energy on wavevector k—plays a central role in determining how electrons respond to external forces. In quantum mechanics, electrons behave as wave packets, and their motion is governed by the group velocity, which is derived from the dispersion relation. When an electric field is applied, it shifts the wavevectors of the components of the wave packet, causing the electron to accelerate. Thus, the electron's response to forces is entirely dictated by the shape of the dispersion curve [1]. For a free electron, the dispersion is:

$$E = \frac{\hbar^2 \mathbf{k}^2}{2m} \tag{6.2}$$

where m is the actual mass of the electron. However, near the bottom of a conduction band in a solid, the dispersion takes the form:

$$E = \frac{\hbar^2 \mathbf{k}^2}{2m^*} \tag{6.3}$$

Here, m\* is the effective mass, which characterizes how the electron behaves under external forces in the crystal. This effective mass is not a physical mass but a parameter derived from the curvature of the band structure.

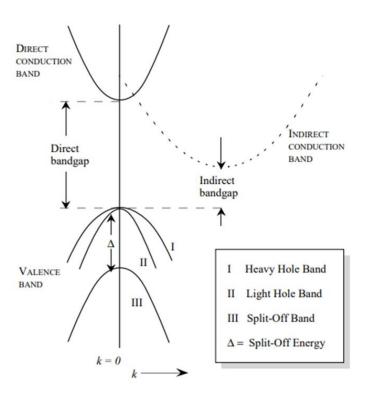

Fig. 6.1 Different type of bandgap

Interestingly, near the top of the valence band, the dispersion still has the same form but with a negative effective mass. This implies that electrons near the valence band maximum move in the opposite direction to the applied force. This counterintuitive behavior arises purely from the curvature of the band and is independent of whether the band is full or empty. If a single electron were placed near the top of the valence band (a hypothetical and unstable scenario), it would move "backward" in response to a force.

The bandwidth—the energy difference between the top and bottom of the band—defines the range of energies for which k-states exist. Outside this range, no such states are available. The formation of this band structure is due to hopping between atomic orbitals, which causes some states to shift below and others above the

original atomic energy level  $\epsilon_0$ . This is analogous to the formation of bonding and antibonding orbitals in molecular systems [2]

When the band is partially filled, the total energy of the electrons decreases as atoms are brought closer together and the bandwidth increases. This energy reduction contributes to the metallic bonding in solids. The mobility of electrons in metals allows them to adjust their positions as the lattice deforms, which explains why metals are typically soft and malleable.

Near the bottom of the band, the dispersion can be approximated as parabolic. Expanding for small kk, we get:

$$E(k) = constant + ta^2k^2 (6.4)$$

For t<0, the energy minimum occurs at the Brillouin zone boundary  $k=\pi/a$ , and the expansion would be centered around that point instead. This parabolic behavior mirrors that of free electrons:

$$E_{free}(k) = \frac{\hbar^2}{2m}k^2 \tag{6.5}$$

To match this form, we define the effective mass m\* such that:

$$\frac{\hbar^2 k^2}{2m^*} = ta^2 k^2 \tag{6.6}$$

$$\Rightarrow m^* = \frac{\hbar^2}{2ta^2} \tag{6.7}$$

Thus, the effective mass encapsulates how the electron behaves dynamically in the crystal, and it depends entirely on the hopping parameter t, not on the actual electron mass. It's also important to note that the wavevector k in this context represents the crystal momentum, a quantum number arising from the periodicity of the lattice.

### 6.2 EFFECTIVE MASS OF THE ELECTRON

Near the bottom of the conduction band, the energy of an electron can be approximated by a quadratic expansion:

$$E = E_{min} + \alpha (k - k_{min})^2 + \dots$$

(6.8)

From this expression, the effective mass m\* is defined through the second derivative of energy with respect to wavevector k:

$$\frac{\hbar^2}{m^*} = \frac{\partial^2 E}{\partial k^2} = 2\alpha \tag{6.9}$$

This effective mass characterizes how an electron responds to external forces within the crystal. Importantly, it is not the actual mass of the electron but a parameter derived from the curvature of the energy band [1]

In modern solid-state physics, it is conventional to define the effective mass of holes—which are the absence of electrons near the top of the valence band as positive, even though the curvature of the band is downward. The energy of a hole near the valence band maximum is given by:

$$E_{hole} = constant + \frac{\hbar^2 (k - k_{max})^2}{2m^*_{hole}}$$

(6.10)

Additionally, the energy associated with the absence of an electron in a given k-state is the negative of the energy of the electron in that state:

$$E(absence of e^{-} in k state) = -E(electron in k state)$$

(6.11)

This inversion is essential in understanding hole dynamics in semiconductors.

### **6.3 VALLEYS IN BAND STRUCTURES**

For simplicity, we neglect the spin of the electron in this discussion. However, in general, spin-orbit coupling can influence the dispersion relation, leading to spin-dependent band structures and modifying properties such as the effective gfactor of electrons.

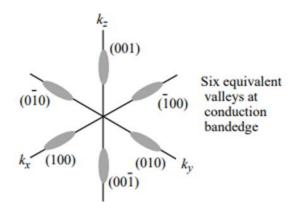

In many semiconductors, the conduction band minimum does not occur at a single point in the Brillouin zone. Instead, there may be multiple equivalent minima, turnitin [

known as valleys, located at different k-points but having the same energy. This phenomenon arises due to the crystal symmetry.

Fig. 6.2 Valleys at conduction bandedge

For instance, in silicon, which has a face-centered cubic (FCC) lattice with a basis, there are six equivalent conduction band minima located approximately at  $(\pm 5.3/a, 0.0)$ ,  $(0,\pm 5.3/a,0)$ , and  $(0,0,\pm 5.3/a)$ . These are referred to as valleys, and the presence of multiple valleys is a key feature in valleytronics and advanced semiconductor physics [2].

Each valley exhibits anisotropic effective mass, characterized by:

- A longitudinal mass m<sub>e,l</sub>\* along the direction of the valley.

- Two transverse masses me, in the perpendicular directions.

In silicon, these values are:

$$m_{e,l}^* = 0.97 m_0$$

,  $m_{e,t}^* = 0.19 m_0$

where  $m_0=9.11\times10-31$  kg is the free electron mass. This anisotropy significantly affects charge transport and mobility in semiconductors.

# 6.4 MILLER INDICES AND (100) ORIENTATION

Miller indices are a standardized notation system used in crystallography to describe the orientation of planes and directions within a crystal lattice. Each set of

planes is identified by a triplet of integers (hkl), known as the Miller indices, which correspond to the intercepts of the plane with the crystallographic axes. These indices are derived from the reciprocal of the intercepts and are typically reduced to their smallest integer values [1]

Fig. 6.3 Miller Indices

### In this notation:

- Negative integers are denoted with a bar (e.g., 3 for -3).

- The indices are written in parentheses (hkl) to denote planes.

- Square brackets [hkl] indicate a specific direction.

- Angle brackets (hkl) represent a family of equivalent directions due to crystal symmetry.

- Curly braces {hkl} denote a family of equivalent planes.

For example, in a cubic crystal system, the directions [100],[010], and [001] are all symmetry-equivalent and collectively represented as  $\langle 100 \rangle$ . Similarly, the planes (100), (010), and (001) are grouped as  $\{100\}$  [2].

Although the primitive lattice vectors in face-centered cubic (FCC) and body-centered cubic (BCC) structures are not orthogonal, Miller indices are typically defined with respect to the cubic supercell, allowing them to align with Cartesian directions for simplicity.

In this research, we focus on the (100) orientation of silicon, a choice driven by its favorable surface properties. The (100) surface of silicon exhibits a lower atomic density compared to other orientations, which results in fewer dangling bonds. This reduction in surface states leads to enhanced carrier mobility, making it a preferred orientation in semiconductor device fabrication.

### **CHAPTER 7**

# **DENSITY OF STATES**

In solid-state and condensed matter physics, the density of states (DOS) describes the number of quantum states available for occupation at each energy level. It is typically expressed as a probability density function and represents an average over space and time for the system's accessible states. The DOS is fundamentally linked to the system's dispersion relation, which defines how energy varies with wavevector k. A high DOS at a particular energy implies a large number of available states at that energy [1].

In semiconductors, the DOS plays a critical role near the band edges. For instance, in the conduction band, as the electron energy increases, more states become available. Conversely, within the band gap, the DOS is zero, indicating no available states. This implies that an electron at the conduction band edge must lose at least the band gap energy to transition to the valence band.

The DOS can be defined for various quantum systems—electrons, phonons, or photons—and can be expressed as a function of either energy or wavevector. To convert between these forms, the dispersion relation E(k) must be known[2]. The mobile charge carrier density n(x) is given by:

$$n(x) = \frac{1}{\Delta V} \sum_{i=1,j=1}^{j=2} \left[ g_{i=1} \int_{-\frac{d}{2}}^{\frac{d}{2}} |\psi(x)|^2 \partial x \right]$$

(7.1)

Where  $g_i=1$  is the degeneracy of the i<sup>th</sup> valley and  $\Delta V=Wd\Delta L$  is the volume element. Alternatively:

$$n(\mathbf{x}) = \int_{E_i}^{\infty} g(E)f(E)\partial E \tag{7.2}$$

$$n(x) = \int_{E_{i,j}}^{\infty} \frac{D(E)f(E)}{D(E)} dE$$

(7.3)

Here, D(E) is the 1D density of states, and f(E) is the Fermi-Dirac distribution function. In 1D systems, the allowed wavevectors are:

$$k_x = \frac{n\pi}{d} \tag{7.4}$$

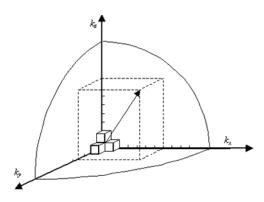

The total number of states is calculated by evaluating the volume of 1/8 of a sphere in k-space and dividing by the volume of a single state:

$$N = 2 \times \frac{1}{8} \times \left(\frac{d}{\pi}\right)^3 \times \frac{4}{3} \times \pi \times k^3 \tag{7.5}$$

Differentiating with respect to energy:

$$\frac{dN}{dE} = \frac{dN}{dk} \times \frac{dk}{dE} = \frac{\left(\frac{d}{\pi}\right)^3 \pi k^3 dk}{dE}$$

(7.6)

Given:

$$E = \frac{\hbar^2 k^2}{2m^*} \Rightarrow \frac{dk}{dE} = \frac{m^*}{\hbar^2 k} \tag{7.7}$$

Fig. 7.1 Solution of different value of k

The 1D density of states becomes:

$$g_{c,1D} = \frac{dN_{1D}}{dE} = \sqrt{\frac{2\pi m^*}{\hbar^2} \frac{1}{\sqrt{E - E_{min}}}} \forall E \ge E_{min}$$

(7.8)

#### 7.1 MAIN CALCULATIONS

Assuming a (100) orientation of silicon, we consider two valleys with effective masses  $0.19 \text{m}_0$  (i = 1) and  $0.97 \text{m}_0$  (i = 2). Since over 90% of electrons occupy the lowest sub-band  $E_{1,1}$  we simplify the Poisson equation as:

$$\frac{\partial^2 \varphi(x)}{\partial x^2} = \frac{q}{\epsilon_{Si}} N_D + \frac{Q_{1,1}}{q \epsilon_{Si}} + \frac{Q_{1,2}}{q \epsilon_{Si}}$$

(7.9)

The 1D mobile charge carrier density is:

$$n_{1D}(x) = \frac{g_{i=1}\sqrt{2m_{d,i}^*}}{W\hbar d\pi} \int_{E_{i,j}}^{\infty} \frac{\left(E - E_{i,j}\right)^{-\frac{1}{2}} dE}{1 + e^{\frac{E - E_{Fn}}{kT}}}$$

(7.10)

Using the substitution  $\varepsilon = \frac{E - E_{i,j}}{k_h T}$ , we get:

$$n_{1D}(x) = \frac{g_{i=1}}{w_d} \sqrt{\frac{2m_{d,i}^*kT}{\pi\hbar^2}} \int \left(\frac{\varepsilon^{-\frac{1}{2}}}{1 + e^{\varepsilon - \eta_F}}\right) d\varepsilon$$

(7.11)

$$\Rightarrow n_{1D}(x) = \frac{g_{i=1}}{w_d} \sqrt{\frac{2m_{d,i}^*kT}{\pi\hbar^2}} F_{-\frac{1}{2}}(\eta_F)$$

(7.12)

Where:

$$\eta_F = \frac{E_F - E_{i,j}}{kT} \tag{7.13}$$

#### 7.2 FERMI DIRAC SOLUTION

The general Fermi-Dirac integral is defined as:

$$F_{j} = \frac{1}{\Gamma(j+1)} \int_{0}^{\infty} \frac{\varepsilon^{j} \partial \varepsilon}{1 + \exp(\varepsilon - \eta_{F})}$$

(7.14)

For degenerate semiconductors:

$$F_m(x) = \left(\frac{E_{Fn} - E_{i.j}}{kT}\right)^{m+1}$$

(7.15)

For non-degenerate semiconductors:

$$F_m(x) = exp\left(\frac{E_{Fn} - E_{i,j}}{kT}\right) \tag{7.16}$$

Thus, the final charge densities are:

$$Q_{1,1} = \frac{g_{i=1}}{Wd} \sqrt{\frac{2m_{d,1}^*kT}{\pi\hbar^2}} e^{\frac{E_{Fn} - E_{1,1}}{kT}}$$

(7.17)

$$Q_{1,2} = \frac{g_{i=1}}{Wd} \sqrt{\frac{2m_{d,1}^*kT}{\pi\hbar^2}} e^{\frac{E_{Fn} - E_{1,2}}{kT}}$$

(7.18)

These expressions are essential for modeling carrier distributions in low-dimensional semiconductor systems [1][2][3].

turnitin

### **CHAPTER 8**

### SURFACE POTENTIAL AND THRESHOLD VOLTAGE MODEL

## 8.1 SURFACE POTENTIAL

The electrostatic potential in the surface region of a silicon semiconductor is governed by Poisson's equation, which relates the electric field to the local charge distribution. The energy expression is given by:

$$E^{2}(x) = \left(\frac{\partial \psi}{\partial x}\right)^{2} = \frac{2kTN_{a}}{\varepsilon_{Si}} \left[ \left(e^{-\frac{q\psi}{kT}} + \frac{q\psi_{S}}{kT} - 1\right) + \frac{n_{i}^{2}}{N_{a}^{2}} \left(e^{\frac{q\psi}{kT}} - \frac{q\psi_{S}}{kT} - 1\right) \right]$$

(8.1)

This equation typically requires numerical methods for a full solution. However, in the depletion region, where  $2\psi_B > \psi > \frac{kT}{a}$ , the dominant term simplifies the expression to:

$$E = \sqrt{\frac{2qN_a\psi}{\epsilon_{Si}}}, \frac{\partial\psi}{\partial x} = -\sqrt{\frac{2qN_a\psi}{\epsilon_{Si}}}$$

(8.2)

Integrating both sides:

$$\int_{\psi_S}^{\psi} \frac{\partial \psi}{\sqrt{\psi}} = \int_0^x \sqrt{\frac{2qN_a}{\epsilon_{Si}}} dx \tag{8.3}$$

$$\Rightarrow \psi = \psi_S \left( 1 - \sqrt{\frac{2qN_a}{2\varepsilon_{Si}\psi_S} x} \right)^2 \tag{8.4}$$

This parabolic potential profile is a standard approximation in MOS capacitor modelling[1].

Assuming a 2D potential of the form:

$$\varphi(x, y) = \varphi_1(y) + x\varphi_2(y) + x^2\varphi_3(y)$$

(8.5)

and applying boundary conditions:

•

$$\varphi\left(\pm \frac{d}{2}, y\right) = \varphi_S(y)$$

(8.6)

$$\bullet \quad \frac{\partial \varphi(x,y)}{\partial x} = 0 \tag{8.7}$$

•

$$\varphi\left(\pm\frac{d}{2},y\right) = \varphi_S(y)$$

(8.6)

•  $\frac{\partial\varphi(x,y)}{\partial x}\Big|_{x=0} = 0$  (8.7)

•  $\frac{\partial\varphi(x,y)}{\partial x}\Big|_{x=\pm\frac{d}{2}} = \frac{c_{ox}}{\epsilon_{Si}}[V_{GS} - \varphi_S(x) - V_{FB}]$  (8.8)

we derive:

$$\varphi(x,y) = \varphi_s(y) \left[ 1 + \frac{dC_{ox}}{4\varepsilon_{Si}} \right] - \frac{dC_{ox}}{4\varepsilon_{Si}} \left[ V_{gs} - V_{fb} \right] - \frac{x^2 C_{ox}}{d\varepsilon_{Si}} \left[ V_{gs} - V_{fb} - \varphi_s(y) \right]$$

(8.9)

This expression captures the electrostatic potential distribution in the channel under gate control [2].

Now the 2D Poisson equation for the electrostatic potential becomes:

$$\frac{\partial^2 \varphi(x,y)}{\partial x^2} + \frac{\partial^2 \varphi(x,y)}{\partial y^2} = \frac{qN_D}{\varepsilon_{Si}} + \frac{1}{\varepsilon_{Si}} \left[ Q_{(1,1)} + Q_{(1,2)} \right]$$

(8.10)

This can be separated into: