## DESIGN AND ANALYSIS OF A BI-POLAR LOW VOLTAGE D.C SYSTEM

A DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE

OF

#### **MASTER OF TECHNOLOGY**

IN

#### POWER ELECTRONICS AND SYSTEMS

Submitted by

#### **VIPUL THAKUR**

2K23/PES/12

Under the Supervision of

#### Saurabh Mishra

(Assistant Prof., EED, DTU)

# DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**MAY, 2025**

DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CERTIFICATE**

I hereby certify that the Project Dissertation titled "DESIGN AND ANALYSIS OF A

BI-POLAR LOW VOLTAGE D.C SYSTEM" which is submitted by VIPUL

THAKUR (2K23/PES/12), Electrical Engineering Department, Delhi Technological

University, Delhi in partial fulfilment of the requirement for the award of the degree

of Master of Technology, is a record project work carried out by the student under my

supervision. To the best of my knowledge this work has not been submitted in part or

full for any Degree or Diploma to this University or elsewhere.

Place: New Delhi

Date: 31<sup>th</sup> May, 2025

Saurabh Mishra

**Assistant Professor**

**Department of Electrical Engineering**

[II]

DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**ACKNOWLEDGMENT**

I would like to express my heartfelt gratitude to my respected teacher and mentor

Saurabh Mishra, Assistant Professor, Department of Electrical Engineering for their

invaluable guidance, unwavering support, and expert insights throughout this journey.

Their dedication and expertise have been instrumental in shaping this work. Grateful

to all the Electrical Engineering faculties, Power Electronics laboratory, PhD scholars,

and laboratory assistants for their valuable inputs.

A special note of thanks goes to my mother and father, their boundless love,

encouragement, and unwavering faith have been my pillar of strength. Her sacrifices

and support have been the cornerstone of my endeavours.

Lastly, my heartfelt thanks to all my friends who have stood by me, offering support,

encouragement, and moments of relief during challenging times. Your camaraderie and

companionship have made this journey memorable.

Thank you to everyone who played a part, directly or indirectly, in the realization of

this endeavour. Your contributions will forever be cherished.

Date: 31th May, 2025

Place: Delhi

(Vipul Thakur)

[111]

#### **ABSTRACT**

This thesis presents a comprehensive study on the design, analysis, and control of bipolar DC-DC converters tailored for low-voltage DC (LVDC) bipolar distribution systems. Bipolar LVDC systems offer a flexible and efficient means of power distribution, particularly in renewable energy-integrated microgrids. A key challenge in such systems is maintaining voltage balance across the positive and negative rails, which is addressed using specialized bipolar DC-DC converters acting as voltage balancers. The thesis begins with the classification of various bipolar converter topologies, configurations, and interconnections. It then introduces and analyses two main converter designs: the Boost derived and the boost-luo interleaved (NBLI) DC-DC converters. The Boost derived converter is designed as a single-input dual-output topology by interleaving boost stages and buck-boost. Time multiplex regulation strategy presented for independently regulate both output capacitors, maintaining balanced voltages in the bipolar bus. The NBLI converter is designed for high-gain, high-efficiency operation with reduced current ripple and lower stress on switching components. Interleaving improves dynamic response and power density, making it suitable for high-current applications. Furthermore, additional converter topologies including a dual-output buck and buck-boost-based converter, and a boost-SEPIC interleaved converter are explored. These designs offer independent voltage control, minimal component stress, and reduced right-half-plane zero issues, improving overall system reliability. Also, the classification of bipolar DC system with its connection configurations and derived topologies for bipolar operations are presented. Control strategies for each topology are formulated using open-loop and voltage-mode feedback methods. Presented converters effectively enhance voltage balancing, current sharing, and load regulation in bipolar LVDC systems. Overall, the thesis delivers technically robust converter designs and control schemes that improve performance, reliability, and scalability in bipolar LVDC system and the performance of the presented DC-DC converter is verified by the MATLAB/Simulink simulation modal.

### TABLE OF CONTENT

| CERTIFICATE                                                     | II        |

|-----------------------------------------------------------------|-----------|

| ACKNOWLEDGMENT                                                  | III       |

| ABSTRACT                                                        | IV        |

| LIST OF FIGURES                                                 | VIII      |

| LIST OF TABLES                                                  | XII       |

| CHAPTER 1                                                       | 1         |

| INTRODUCTION                                                    | 1         |

| 1.1 General Aspects                                             | 1         |

| 1.2 State of The Art on DC Bipolar Grid                         | 2         |

| 1.3 Conclusion                                                  | 4         |

| CHAPTER 2                                                       | 5         |

| LITERATURE SURVEY                                               | 5         |

| 2.1 General Aspects                                             | 5         |

| 2.2 Objectives of Thesis                                        | 8         |

| 2.3 Outline of Thesis                                           | 8         |

| 2.4 Conclusion                                                  | 10        |

| CHAPTER 3                                                       | 11        |

| CLASSIFICATION OF BI-POLAR DC SYSTEM                            | 11        |

| 3.1 General Aspects                                             | 11        |

| 3.2 Connection Configuration in Bi-polar DC System              | 11        |

| 3.3 Boost Derived Bipolar DC-DC Converter Topologies            | 13        |

| 3.3.1 Single-Switch Boost Derived Bipolar DC-DC Converter Topol | ogies 13  |

| 3.3.2 Multi-Switch Boost Derived Bipolar DC-DC Converter Topolo | gies 14   |

| 3.4 Buck-Boost Derived Bipolar DC-DC converter Topologies       | 17        |

| 3.4.1 Single-Switch Buck-Boost Derived Bipolar DC-DC Converter  |           |

| 3.4.2 Multi-Switch Buck-Boost Derived Bipolar DC-DC Converter   |           |

| 3.4.3 Boost and Buck Boost Derived Bipolar DC-DC Converter Ton  | ologies22 |

| 3.4.   | 4 Buck and Buck Boost Derived Bipolar DC-DC Converter Topologies -          | 23 |

|--------|-----------------------------------------------------------------------------|----|

| 3.5 Lc | oad Connection in Bipolar DC System                                         | 24 |

| 3.6 Co | onclusion                                                                   | 25 |

| СНАРТ  | ER 4                                                                        | 26 |

|        | N DEVELOPMENT AND ANALYSIS OF BI-POLAR BOOST ED INTERLEAVED DC-DC CONVERTER | 26 |

|        | eneral Aspect                                                               |    |

|        | hematic of Bi-Polar Boost Derived Interleaved DC-DC Converter               |    |

|        | odes of Operation                                                           |    |

|        | odelling of Bi-Polar Boost Derived Interleaved DC-DC Converter              |    |

|        | esign Specification:                                                        |    |

|        | ontrol Scheme                                                               |    |

|        | esults and Discussion                                                       |    |

|        | 1 Input Current and Inductor Current:                                       |    |

|        | 2 Output Current and Voltage of SIDO BBB converter:                         |    |

|        | onclusion                                                                   |    |

| СНАРТ  | ER 5                                                                        | 39 |

| DESIG  | N DEVELOPMENT AND ANALYSIS OF BOOST-LUO                                     |    |

| INTER  | LEAVED DC-DC CONVERTER                                                      | 39 |

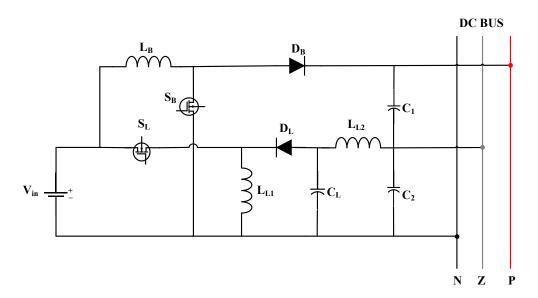

| 5.1 Ge | eneral Aspect                                                               | 39 |

| 5.2 Sc | hematic of Boost-Luo Interleaved Converter                                  | 39 |

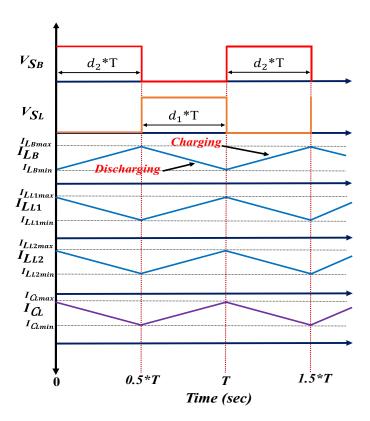

| 5.3 M  | odes of Operation                                                           | 41 |

| 5.4 M  | odelling of Boost-Luo Interleaved DC-DC Converter                           | 45 |

| 5.5 De | esign Specification                                                         | 46 |

| 5.6 Co | ontrol Scheme                                                               | 48 |

| 5.7 Re | esult & Discussion                                                          | 49 |

| 5.8 Co | onclusion                                                                   | 53 |

| CHA    | PTER 6                                                                      | 54 |

|        | GN DEVELOPMENT AND ANALYSIS OF BI-POLAR BUCK BUC                            |    |

|        | ST DC-DC CONVERTER                                                          |    |

| 6.1    | General Aspect                                                              |    |

| 6.2    | Schematic of Bi-Polar Buck Buck-Boost DC-DC Converter                       | 54 |

| 6.3 Modes of Operation                                                                          | 56 |

|-------------------------------------------------------------------------------------------------|----|

| 6.4 Modelling of Bi-Polar Buck Buck-Boost DC-DC Converter                                       | 59 |

| 6.5 Design Specification                                                                        | 61 |

| 6.6 Control scheme                                                                              | 62 |

| 6.7 Result & Discussion                                                                         | 63 |

| 6.8 Conclusion                                                                                  | 65 |

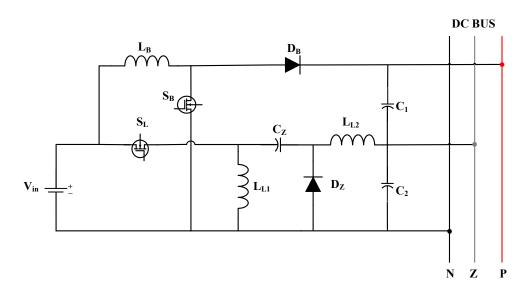

| CHAPTER 7                                                                                       | 66 |

| DESIGN DEVELOPMENT AND ANALYSIS OF BIPOLAR BOOST-S INTERLEAVED DC-DC CONVERTER WITH ACTIVE LOAD |    |

| 7.1 General Aspect                                                                              | 66 |

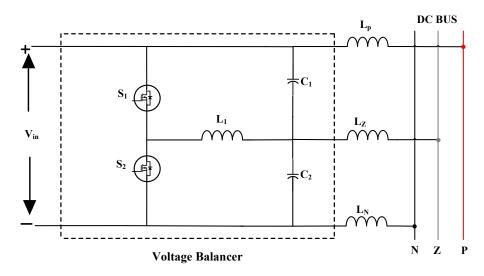

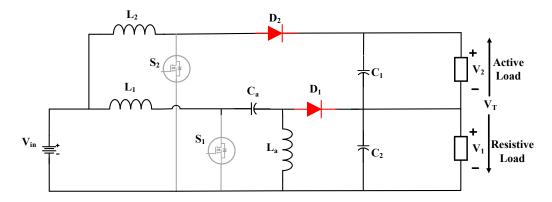

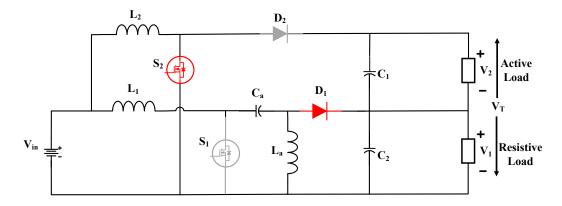

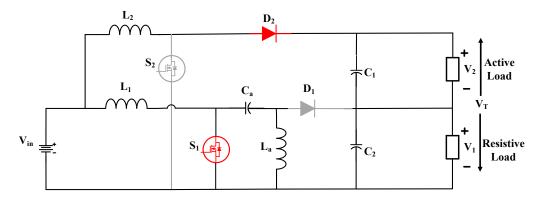

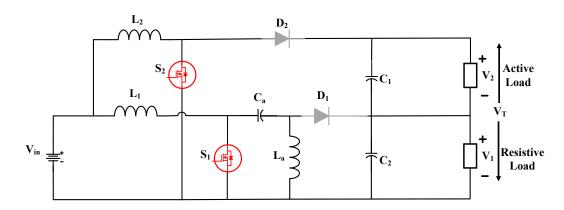

| 7.2 Schematic of Bipolar interleaved DC-DC Converter                                            | 66 |

| 7.3 Modes of Operation                                                                          | 68 |

| 7.4 Modelling of Bipolar Interleaved DC-DC Converter                                            | 72 |

| 7.5 Design Specification                                                                        | 72 |

| 7.6 Control Scheme                                                                              | 74 |

| 7.7 Result & Discussion                                                                         | 76 |

| 7.8 Conclusion                                                                                  | 78 |

| Chapter 8                                                                                       | 79 |

| CONCLUSION                                                                                      | 79 |

| REFREANCES                                                                                      | 80 |

| LIST OF PUBLICATION                                                                             | 87 |

### LIST OF FIGURES

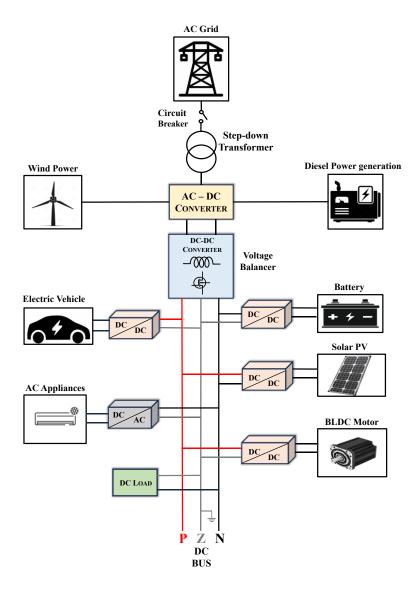

| Fig. 1.1 Bipolar LVDC Connected to Grid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

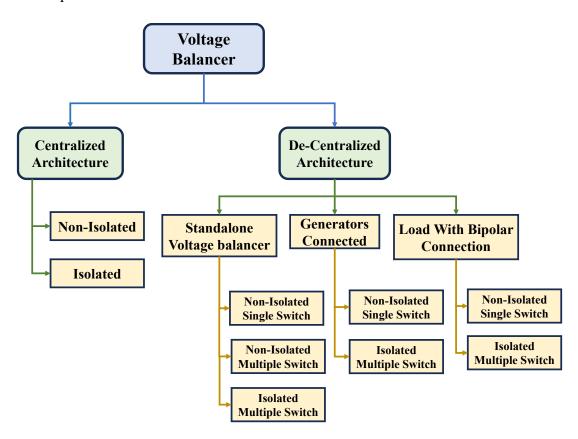

| Fig. 1.2 Classification of Voltage Balancers in Bipolar DC System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3            |

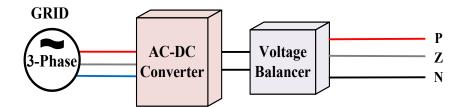

| Fig. 3.1 Centralized Architecture of Bipolar DC System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11           |

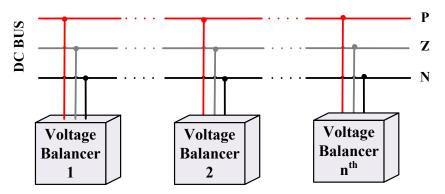

| Fig. 3.2 Decentralized Architecture of Bipolar DC system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12           |

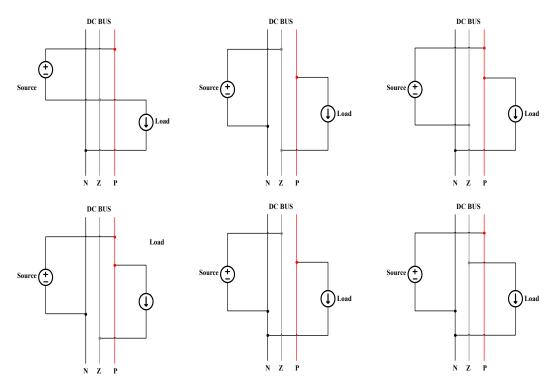

| Fig. 3.3 Six Connections Produce Bipolar DC Microgrid Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12           |

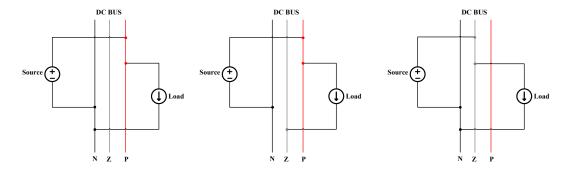

| Fig. 3.4 Connection Configuration to Mitigate Voltage Imbalance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13           |

| Fig. 3.5 Boost Self-Lift Type Type DC-DC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14           |

| Fig. 3.6 Boost self-lift type DC-DC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14           |

| Fig. 3.7 Multi switch input-parallel output-series type DC-DC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15           |

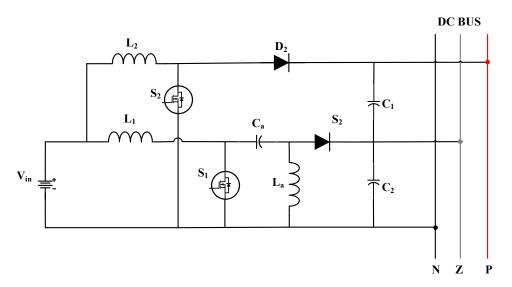

| Fig. 3.8 Interleaved bidirectional boost-SEPIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15           |

| Fig. 3.9 Interleaved bidirectional boost-SEPIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16           |

| Fig. 3.10 Interleaved bidirectional boost and zeta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16           |

| Fig. 3.11 Interleaved boost-SEPIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17           |

| Fig. 3.12 Circuit diagram of Bi-Polar buck boost Zeta converter De                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C <b>-DC</b> |

| converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17           |

| Fig. 3.13 Circuit diagram of Bi-Polar multidirectional buck-boost converte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>r</b> 18  |

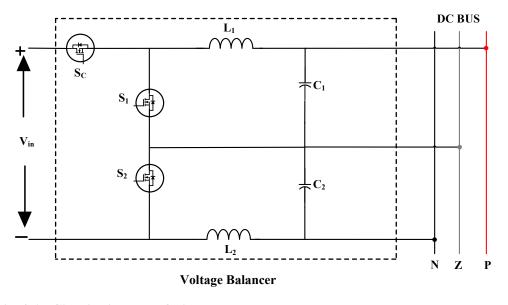

| Fig. 3.14 Circuit Diagram of Bi-Polar Buck-Boost Converter Type Vo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | oltage       |

| Balancer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19           |

| Fig. 3.15 Circuit diagram of Bi-Polar Improved buck-boost converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | type         |

| voltage balancer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19           |

| Fig. 3.16 Circuit diagram of Bi-Polar three-level buck-boost converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20           |

| Fig. 3.17 Circuit diagram of Bi-Polar three-level bidirectional buck-boost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | type         |

| converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20           |

| Fig. 3.18 Circuit diagram of Bi-Polar Buck-Boost Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21           |

| Fig. 3.19 Bidirectional modified SEPIC-cuk DC-DC converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 21           |

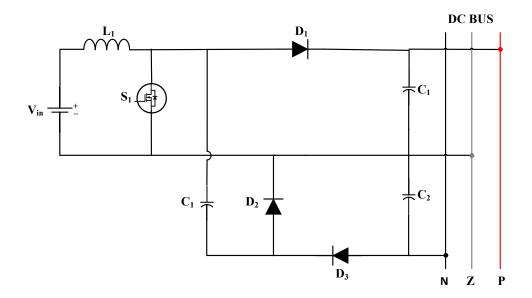

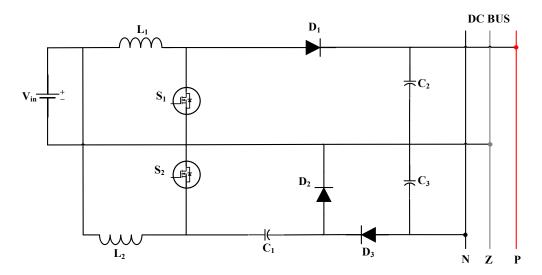

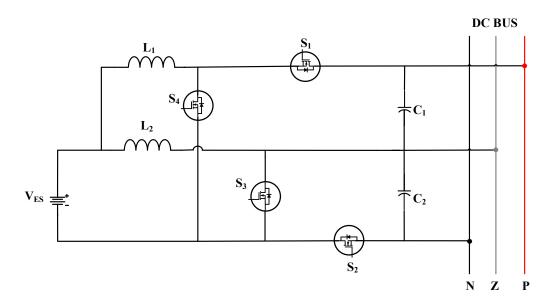

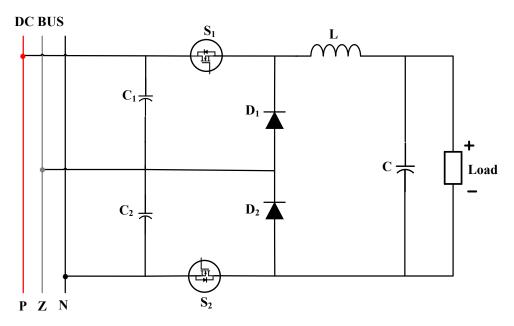

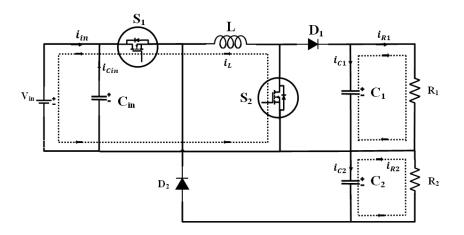

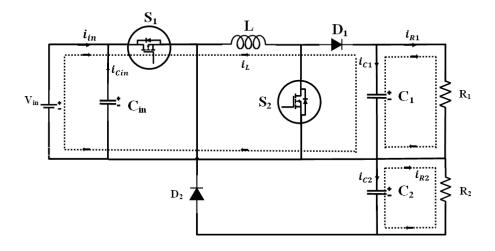

| Fig. 3.20 Circuit diagram of Bi-Polar Boost Derived Interleaved Derived Derived Interleaved Derived Derived Interleaved Derived Derived Interleaved In | C <b>-DC</b> |

| converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22           |

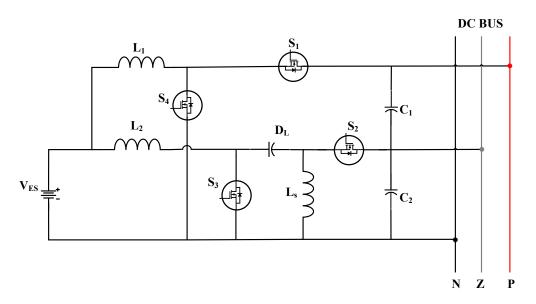

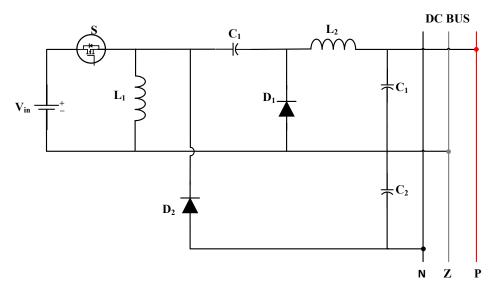

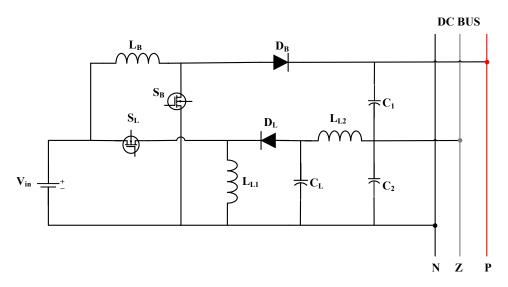

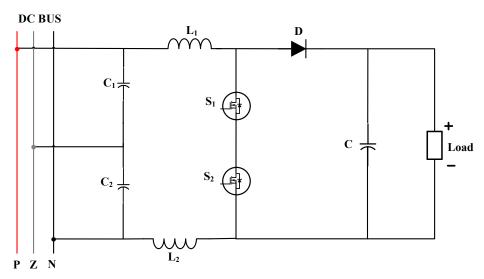

| Fig. 3.21 Circuit diagram of Boost-Luo interleaved DC-DC converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23           |

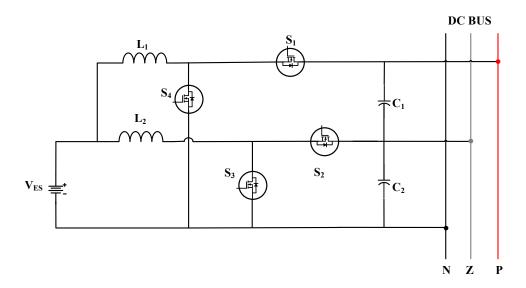

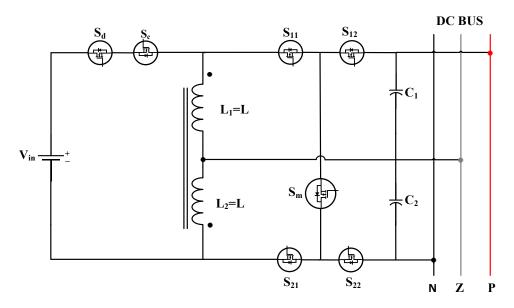

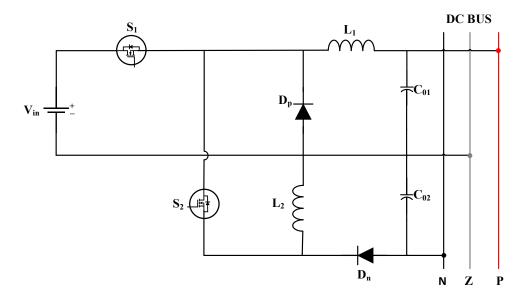

| Fig. 3.22 Circuit diagram of Buck Buck-Boost interleaved DC-DC converte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | r23          |

| Fig. 3.23 Circuit diagram of three-level buck converter's load Connection                                                    | ı in |  |

|------------------------------------------------------------------------------------------------------------------------------|------|--|

| bipolar system                                                                                                               |      |  |

| Fig. 3.24 Circuit diagram of three-level boost converter's load Connection                                                   |      |  |

| bipolar system                                                                                                               | 24   |  |

| Fig. 3.25 Circuit diagram of three-level boost converter's load Connection                                                   | ı in |  |

| bipolar system                                                                                                               | 25   |  |

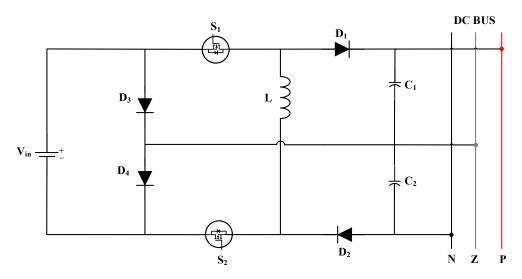

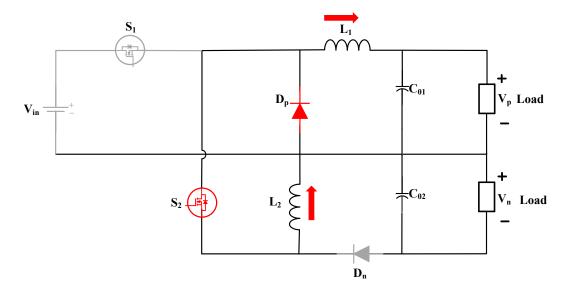

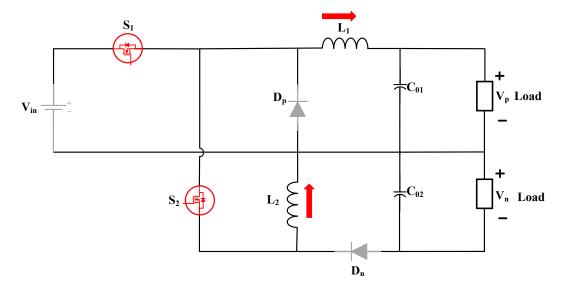

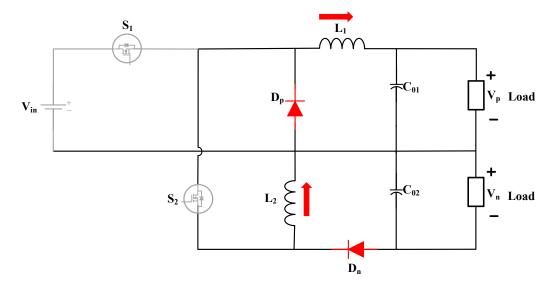

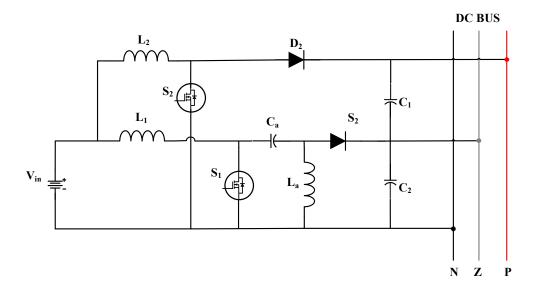

| Fig. 4.1 Circuit diagram of Bi-Polar Boost Derived Interleaved DC-DC Conve                                                   | rter |  |

|                                                                                                                              | 26   |  |

| Fig. 4.2 Mode 1 of Operation                                                                                                 | 27   |  |

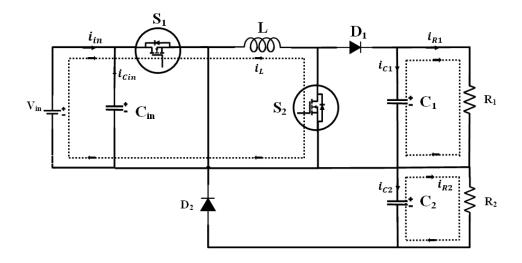

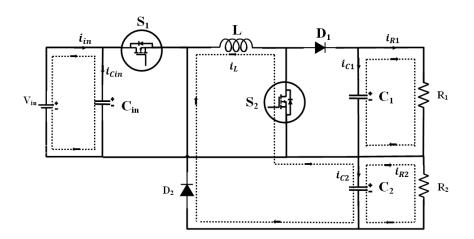

| Fig. 4.3 Mode 2 of Operation                                                                                                 | 27   |  |

| Fig. 4.4 Mode 3 of Operation                                                                                                 | 28   |  |

| Fig. 4.5 Mode 4 of Operation                                                                                                 | 28   |  |

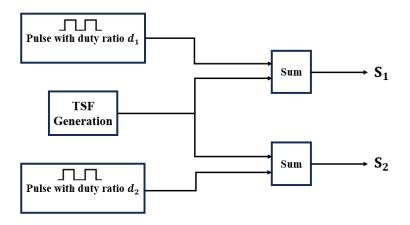

| Fig. 4.6 Block diagram of the presented Time Multiplexing Control Scheme                                                     | . 34 |  |

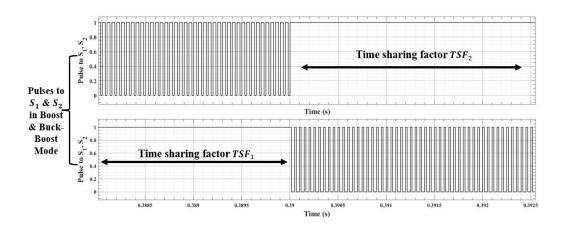

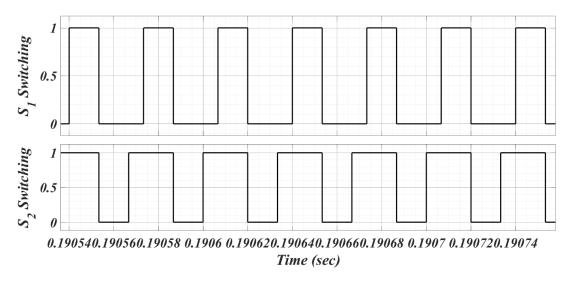

| Fig. 4.7 Time Sharing Factor for S <sub>1</sub> and S <sub>2</sub>                                                           | . 34 |  |

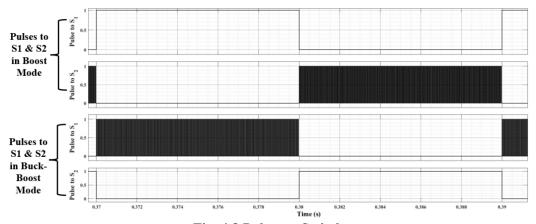

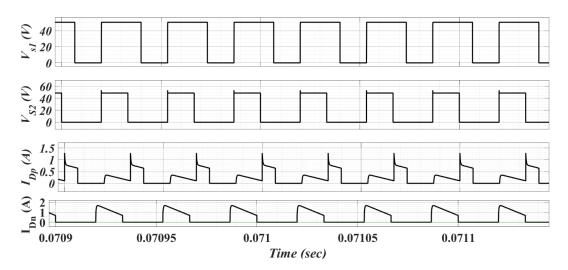

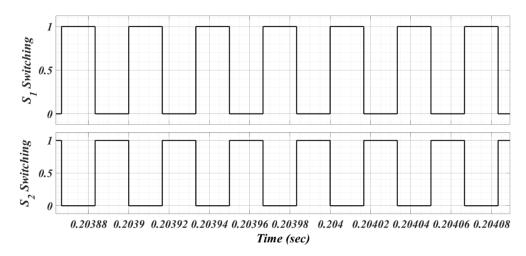

| Fig. 4.8 Pulses to Switches                                                                                                  | 35   |  |

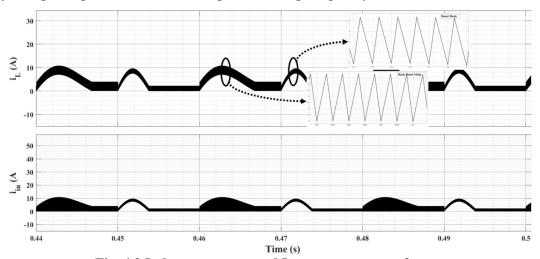

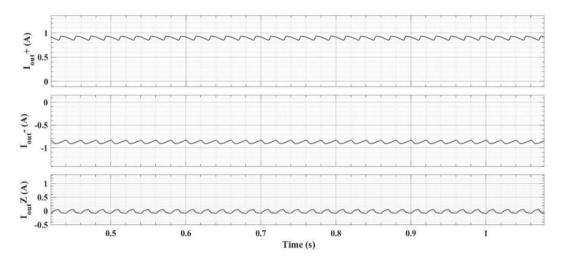

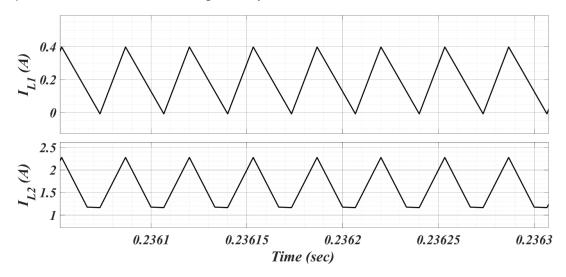

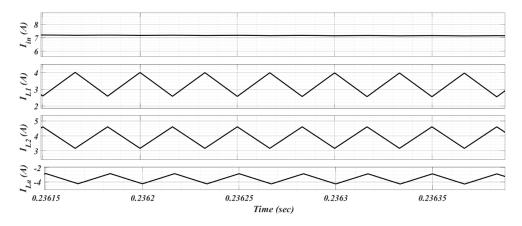

| Fig. 4.9 Inductor current and Input current waveforms                                                                        | 36   |  |

| Fig. 4.10 Output current waveforms                                                                                           | 37   |  |

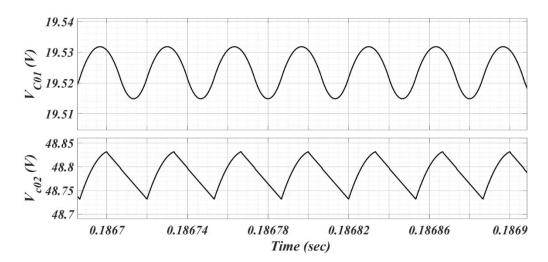

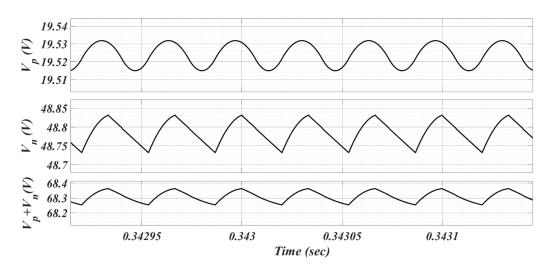

| Fig. 4.11 Output Voltage waveforms                                                                                           | 38   |  |

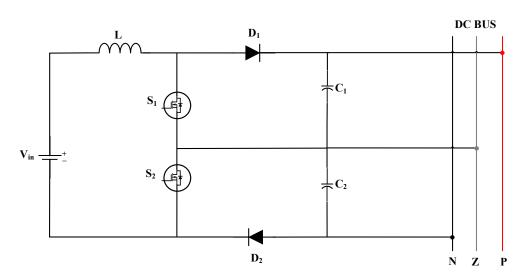

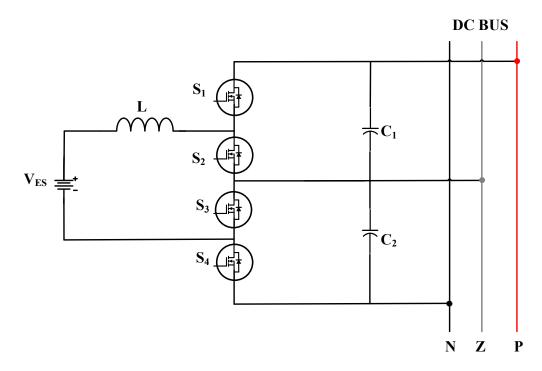

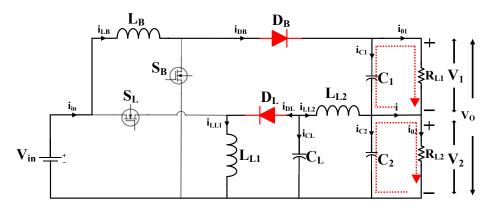

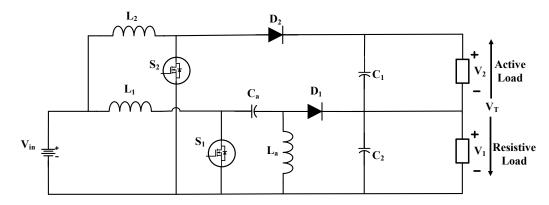

| Fig. 5.1 Circuit diagram of Boost-Luo interleaved DC-DC converter                                                            | 39   |  |

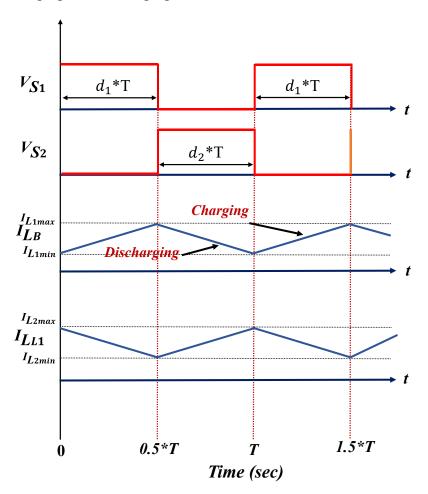

| Fig. 5.2 Steady state waveform of SIDO NBLI converter in CCM                                                                 | 40   |  |

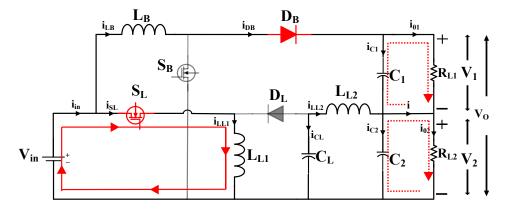

| Fig. 5.3 Passive mode 1                                                                                                      | 42   |  |

| Fig. 5.4 Active mode 1                                                                                                       | 43   |  |

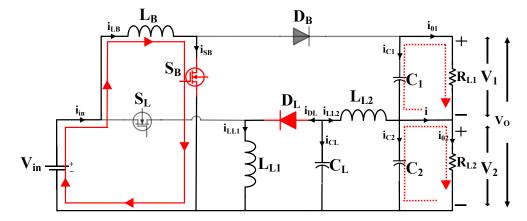

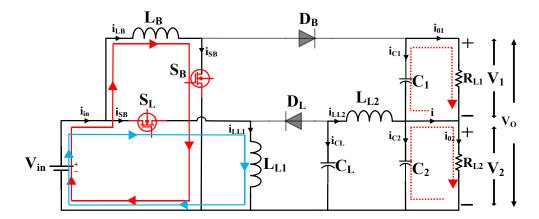

| Fig. 5.5 Active mode 2                                                                                                       | . 44 |  |

| Fig. 5.6 Passive mode 2                                                                                                      | . 44 |  |

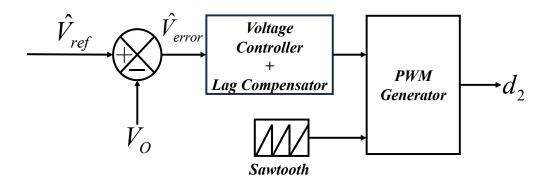

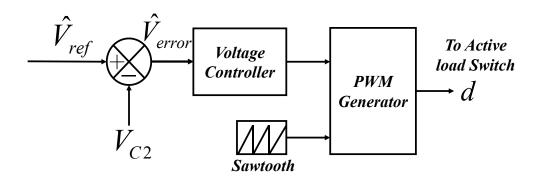

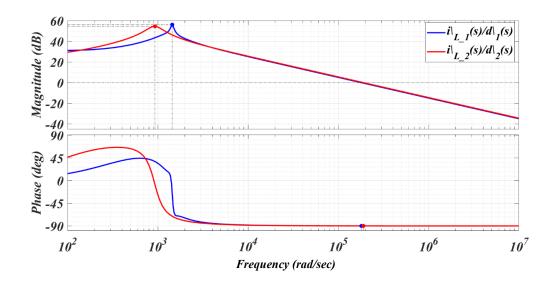

| Fig. 5.7 Output Voltage V <sub>0</sub> Control                                                                               | 48   |  |

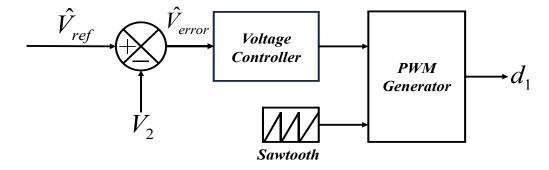

| Fig. 5.8 Output Voltage V2 Control                                                                                           | 48   |  |

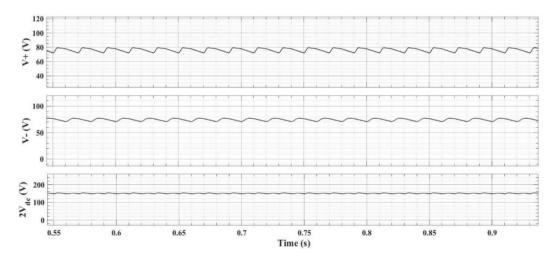

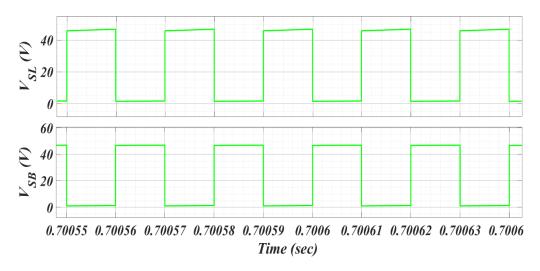

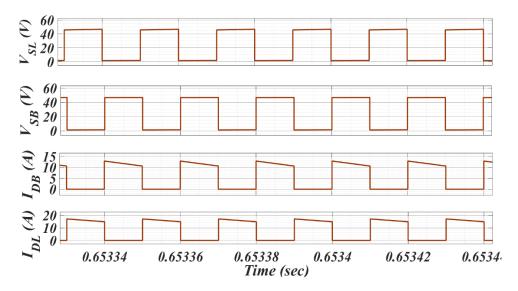

| Fig. 5.9 Voltage Stress across switches V <sub>SL</sub> (V), V <sub>SB</sub> (V)                                             | 49   |  |

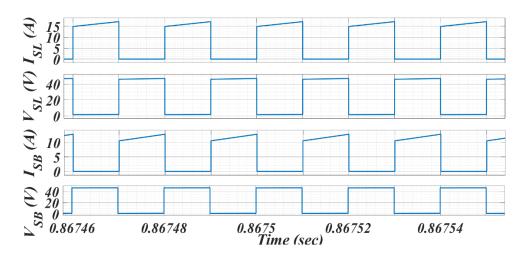

| Fig. 5.10 Switches voltage stress V <sub>SL</sub> (V), V <sub>SB</sub> (V), Current I <sub>SL</sub> (A), I <sub>SB</sub> (A) | 50   |  |

| Fig. 5.11 Switch Voltage Stress (V <sub>SL</sub> ), (V <sub>SB</sub> ), Diode current (I <sub>DB</sub> ), (I <sub>DB</sub> ) | 50   |  |

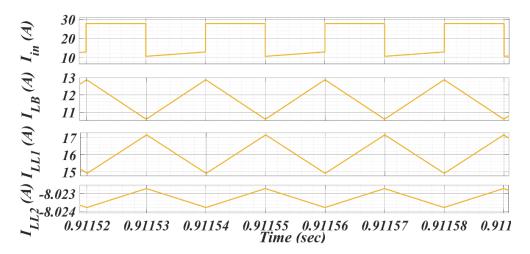

| Fig. 5.12 Input current I <sub>in</sub> (A) and Inductor Currents of Boost and Luo conver                                    | ters |  |

| ILB (A), ILL1 (A), ILL2 (A)                                                                                                  | 51   |  |

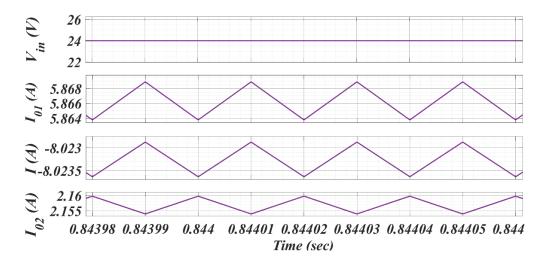

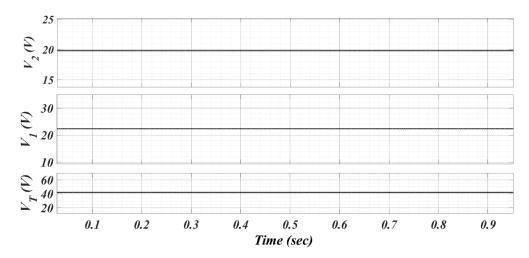

| Fig. 5.13 Input Voltage V <sub>in</sub> (V), and Output Currents I <sub>01</sub> (A), I (A), I <sub>02</sub> (A              | 51   |  |

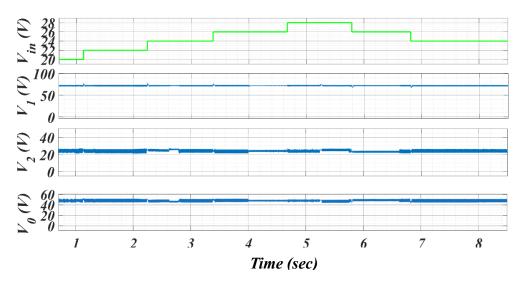

| Fig. 5.14 Voltage Control of output voltages for dynamic source voltage                                                                                  | 52       |

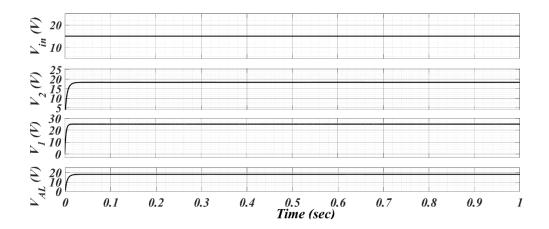

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

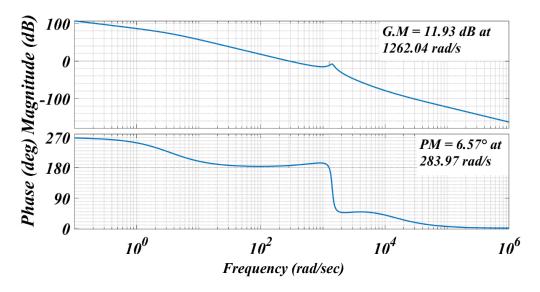

| Fig. 5.15 Bode Plot of Compensated Boost section                                                                                                         | 52       |

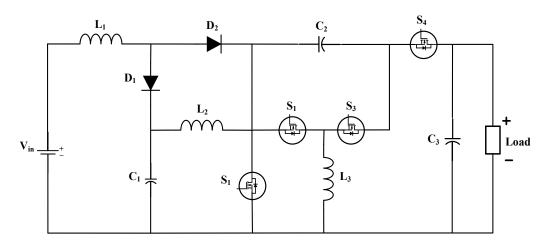

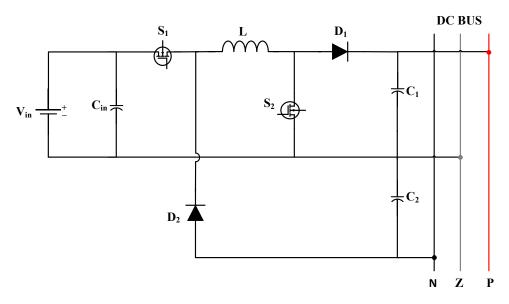

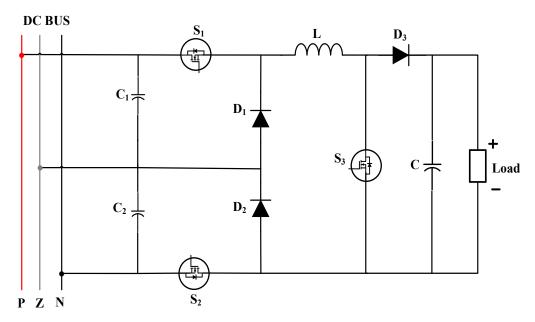

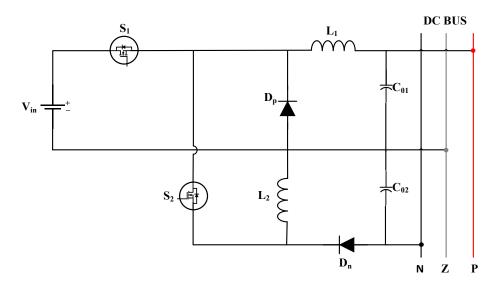

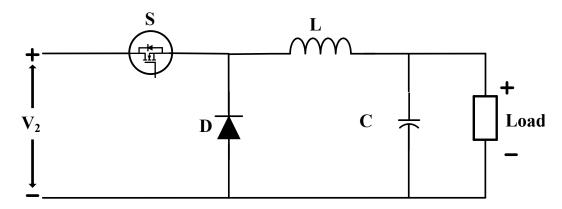

| Fig. 6.1 Circuit Diagram of Boost-Luo Interleaved DC-DC Converter w                                                                                      | ith DC   |

| bus                                                                                                                                                      | 54       |

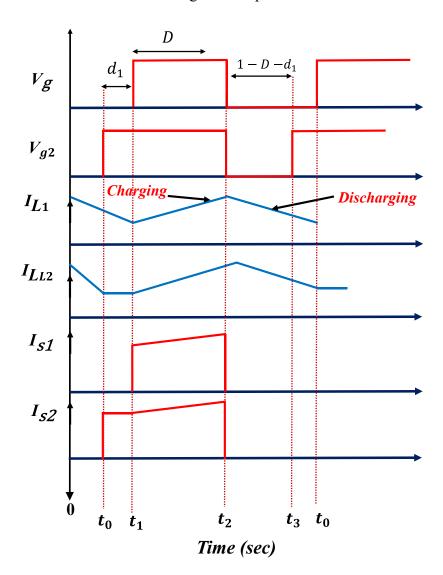

| Fig. 6.2 Steady State Waveform of Buck Buck-Boost Converter                                                                                              | 55       |

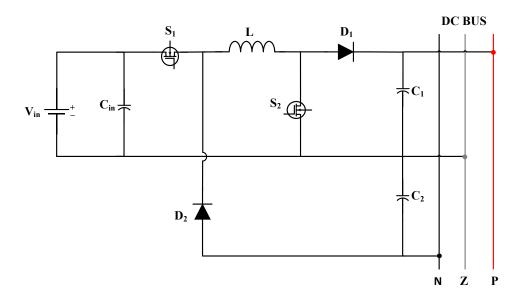

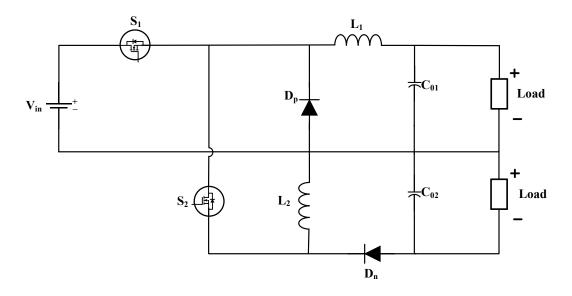

| Fig. 6.3 Circuit diagram of Boost-Luo interleaved DC-DC converte                                                                                         | r with   |

| Resistive load                                                                                                                                           | 56       |

| Fig. 6.4 Circuit diagram of Operating state 1 DC-DC converter                                                                                            | 57       |

| Fig. 6.5 Circuit Diagram of Operating State 2 DC-DC Converter                                                                                            | 57       |