# Realization of various Linear and Non-linear Applications using Current Mode Building Blocks

Thesis Submitted to Delhi Technological University for the Degree of DOCTOR OF PHILOSOPHY

in

Department of Electronics and Communication Engineering

by

Sweta Kumari

(2K18/PHDEC/503)

Under the supervision of

Dr. Deva Nand

(Associate Professor, ECE)

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Delhi-110042, India

2025

# **CANDIDATE DECLARATION**

I hereby certify that the research presented in this thesis, entitled "Realization of various Linear and Non-linear Applications using Current Mode Building Blocks," in fulfilment of the requirements for the award of the degree of Doctor of Philosophy, is an authentic record of my research work carried out under the supervision of Dr. Deva Nand.

The matter presented in this thesis has not been submitted elsewhere in part or fully to any other University or Institute for awarding any degree.

Sweta Kumari 2K18/PHDEC/503 Department of Electronics and Communication Engineering Delhi Technological University Delhi-110042, India

# CERTIFICATE

This is to certify that the thesis entitled "**Realization of various Linear and Nonlinear Applications using Current Mode Building Blocks**" being submitted by Ms. Sweta Kumari (2K18/PHDEC/503) for the award of the degree of Doctor of Philosophy in the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, is the record of students own work carried out by her under my supervision. The contents of this research work have not been submitted in part or fully to any other institute or university for the award of any degree.

Dr. Deva Nand Associate Professor Department of Electronics and Communication Engineering Delhi Technological University Delhi-110042, India

#### ACKNOWLEDGMENT

I would like to express my profound gratitude to the individuals who provided support and guidance throughout my research program. Their assistance made this challenging and rewarding journey possible, contributing significantly to my personal and academic growth. It is a privilege to have the opportunity to extend my heartfelt thanks to all of them.

The support and expert advice of my supervisor **Dr. Deva Nand**, Department of Electronics and Communication Engineering, Delhi Technological University is greatly acknowledged with gratitude. His supervision, continuous motivation, and unwavering support have been invaluable throughout my journey.

Sincere appreciation and thanks extended to **Prof. O. P. Verma** and the Head of Department of Electronics and Communication Engineering, Delhi Technological University, Delhi for providing me with this opportunity and for his immense help during this work.

A special mention goes to **Prof. Neeta Pandey** and **Prof. Rajeshwari Pandey**, Department of Electronics and Communication Engineering, Delhi Technological University, India, whose invaluable support, guidance, and feedback are crucial to completing my doctorate. Their expertise and dedication greatly enriched the quality and depth of my research.

I also sincerely thank all the faculty members of the ECE Department, DTU, for their timely support and assistance.

I would also like to thank my colleagues and seniors in the Electronics Department for their support, especially Dr. K. Gurumurthy, Dr. Parveen, Dr. Garima, Dr. Damyanti, Ms. Kavita, Ms. Bhawna and Dr. Massoud Massoudi. My heartfelt gratitude goes to my parents, Smt. Anita Devi and Shri Binod Kumar Choudhary, for their unfailing support throughout my life. I am also deeply grateful to my husband, Mr. Hemant Choudhary, for his constant encouragement in my doctoral studies. Lastly, I thank my sister and brother, Manisha and Ashutosh, for their support throughout this long and challenging process.

#### Sweta Kumari

### ABSTRACT

The rapid evolution of semiconductor technology has enabled the integration of millions of transistors on a single chip, diminishing the gaps between analog and digital domains. This trend has led to the rise of integrated solutions that incorporate both analog and digital subsystems on a single die. Despite a significant shift towards digital circuit design over the past two decades, analog design remains essential, particularly for functions such as signal processing, amplification, filtering, and conversion between analog and digital signals. The demand for high-performance analog interface circuits continues to grow with the emergence of new applications.

Designing analog circuits faces challenges due to the ongoing scaling of device dimensions and power supply voltages. Reduced power supply voltages can limit input common-mode range, linearity, and output voltage swing. Analog circuits can be classified as voltage mode (VM) or current mode (CM) based on whether they process information via nodal voltages or branch currents. Scaling adversely affects VM circuits' performance parameters, including dynamic range, slew rate, and common-mode range. In contrast, CM circuits offer enhanced slew rate, wider bandwidth, and better dynamic range due to smaller time constants and the ability to utilize transistors up to their unity-gain bandwidth. Additionally, CM circuits can be more compact, as current addition is achieved by simply connecting branches.

To leverage the advantages of CM signal processing, various analog building blocks have been developed. Components like Differential Difference Current Conveyors (DDCC), Differential Difference Current Conveyor Transconductance Amplifiers (DDCCTA), and Extra-X Current Controlled Current Conveyor Transconductance Amplifiers (EXCCCCTA) combine the features of current conveyors and current feedback operational amplifiers, with added current outputs to enhance design flexibility. These blocks are well-suited for processing and delivering both current and voltage at appropriate impedance levels, making them invaluable in modern analog circuit design.

A novel voltage-mode First Order Universal Filter (FOUF) utilizing a single DDCC combined with one resistor and one capacitor is presented. The proposed FOUF, designed as a multiple-input single-output (MISO) configuration, provides low-pass, high-pass, and all-pass responses, achieving a pole frequency of Mega Hz. Additionally, the application of the filter in a trans-admittance mode (TAM) controller is presented. This TAM controller employs Proportional-Derivative (PD), Proportional-Integral (PI), and Proportional-Integral-Derivative (PID) configurations, utilizing a DDCCTA with three resistors and three capacitors. Key features include the use of grounded capacitors and independent electronic tuning of control parameters, enabling simultaneous PD, PI, and PID operations. The study explores the impact of DDCCTA non-idealities on the controller and demonstrates an enhanced gain-frequency response. The controller's effect on the step response of a DDCCTA-based second-order filter system is analyzed to validate its practical application.

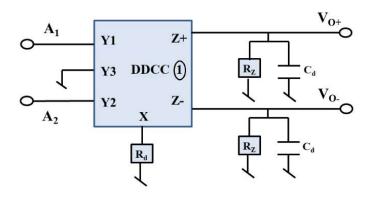

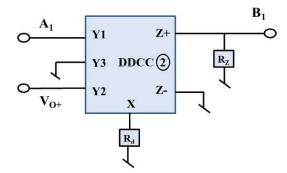

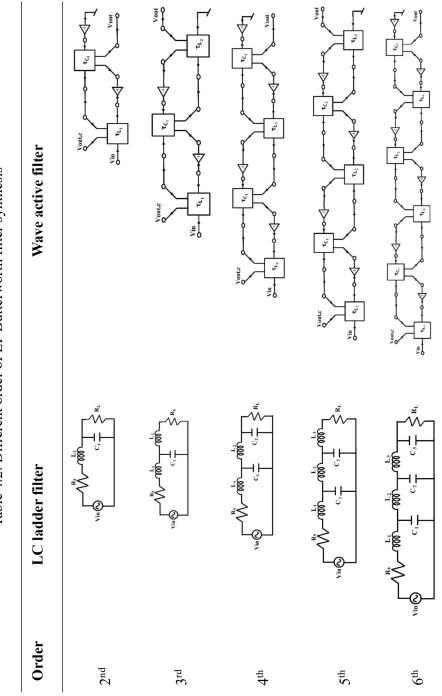

Two novel designs for wave active filters (WAF) based on voltage mode and current mode configurations are presented. The first design utilizes a DDCC to implement a wave-active filter, with wave quantity processing forming the foundation of its operation. The DDCC serves as the analog building block (ABB) for executing mathematical operations such as lossy integration-subtraction, subtraction, summation, and inversion, which are essential for creating wave-active components like series inductors and shunt capacitors. This design is applied to develop low to high-order low-pass Butterworth filter topologies, with theoretical verification is provided for nth-order low-pass Butterworth filters (n = 2, 3, 4, 5, 6). The second design introduces a current-mode wave active filter employing the EX-CCCCTA. This approach features a simplified design using a single EX-CCCCTA, grounded passive components, and electronic tuning capabilities, making it well-suited for highfrequency applications up to approximately Mega Hz. Compared to passive filters, this current-mode WAF offers advantages such as tunable gain, compatibility with monolithic integration, and optimal input-output impedance. Both filters' performance is validated through Monte Carlo analysis, THD assessment, and noise analysis, demonstrating its efficacy in practical applications.

The CM full-wave rectifiers (FWR) use two distinct analog building blocks: DDCC and DDCCTA. The first design employs a DDCC, two MOS-based diodes, and three grounded resistors to implement CM full-wave positive and negative rectifiers in different topologies, achieving an operating frequency of Mega Hertz. The second design introduces an electronically tunable, dual-output CM FWR using a single DDCCTA, two MOS-based active diodes, and four grounded active resistors. A key advantage of this design is its high output impedance with dual outputs (positive and negative) simultaneously, enabling easy cascading with other circuits. The work thoroughly analyzes the effects of non-idealities, including non-unity transfer gains and parasitic elements, on the circuit's performance. Additionally, Monte Carlo simulations are performed to validate the robustness and practical applicability of the proposed designs.

To evaluate functionality and performance, SPICE and Virtuoso simulators are used with 180 nm TSMC CMOS technology and 180 gpdk parameters, respectively. Various simulations are carried out to demonstrate the effectiveness of all proposed designs.

# **TABLE OF CONTENTS**

| CANDIDATE DECLARATION                                                           | .i  |

|---------------------------------------------------------------------------------|-----|

| CERTIFICATE                                                                     | .ii |

| ACKNOWLEDGMENT                                                                  | iii |

| ABSTRACT                                                                        | v   |

| TABLE OF CONTENTv                                                               | iii |

| LIST OF FIGURES                                                                 | xi  |

| LIST OF TABLESx                                                                 | iv  |

| CHAPTER 1: Introduction1-1                                                      | 10  |

| 1.1 Introduction                                                                | .2  |

| 1.2 Available literature and scope of work                                      | 6   |

| 1.3 Thesis organization                                                         | 10  |

| CHAPTER 2: Description of DDCC, DDCCTA & EX-CCCCTA Analo                        | og  |

| Building Blocks11-2                                                             | 28  |

| 2.1 Differential Difference Current Conveyor (DDCC) Block                       | 12  |

| 2.1.1 AC Characteristics                                                        | 13  |

| 2.1.2 DC Characteristics                                                        | 14  |

| 2.1.3 Non-ideal Effects                                                         | 15  |

| 2.1.4 Parasitic Effects                                                         | 15  |

| 2.2 Differential Difference Current Conveyor Trans-Conductance Amplifi          | er  |

| (DDCCTA) Block1                                                                 | .6  |

| 2.2.1 AC Characteristics                                                        | 19  |

| 2.2.2 DC Characteristics                                                        | 20  |

| 2.2.3 Non-ideal Effects                                                         | 22  |

| 2.2.4 Parasitic Effects                                                         | 22  |

| 2.3 Extra-X Current Controlled Current Conveyor Trans-Conductance Amplifier (EX | X-  |

| ССССТА)                                                                         | 3   |

| 2.3.1 AC Characteristics                                                        | 25  |

| 2.3.2 DC Characteristics                                                        | 26  |

| 2.3.3 Non-ideal Effects                                                 | 28   |

|-------------------------------------------------------------------------|------|

| 2.3.4 Parasitic Effects                                                 | 28   |

| CHAPTER 3: Single ABB-based Filter and Controller Designs2              | 9-54 |

| 3.1 Introduction                                                        | 30   |

| 3.2 Literature review                                                   | 31   |

| 3.3 Proposed designs using Single ABB                                   | 32   |

| 3.3.1 Proposed MISO-type VM-based FOUF using DDCC Block                 | 32   |

| 3.3.1.1 Sensitivity Analysis                                            | 33   |

| 3.3.1.2 Non-idealities Analysis                                         | 33   |

| 3.3.1.3 Sensitivity for Non-ideal conditions                            | 34   |

| 3.3.1.4 Parasitic effects                                               | 34   |

| 3.3.1.5 Simulation results                                              | 35   |

| 3.3.2 Proposed TAM-based PD, PI and PID Controllers using DDCCTA Block. | 41   |

| 3.3.2.1 PD controller                                                   | 42   |

| 3.3.2.2 PI Controller                                                   | 42   |

| 3.3.2.3 PID Controller                                                  | 43   |

| 3.3.2.4 Non-ideal effects                                               | 44   |

| 3.2.2.5 Simulation results                                              | 45   |

| 3.3.2.6 Example as application                                          | 52   |

| 3.4 Concluding remarks                                                  | 54   |

| CHAPTER 4: VM and CM-based wave active filter5                          | 5-83 |

| 4.1 Introduction                                                        | 56   |

| 4.2 Literature review                                                   | 57   |

| 4.3 Proposed designs VM and CM WAF                                      | 59   |

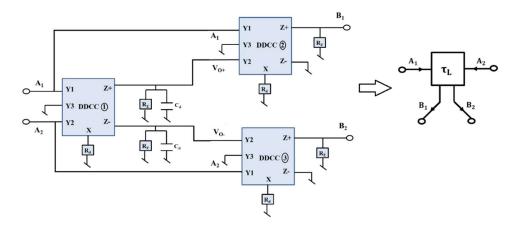

| 4.3.1 Basic Wave Equivalent                                             | 59   |

| 4.3.2 Proposed VM-based Wave Active Filter using DDCC Block             | 62   |

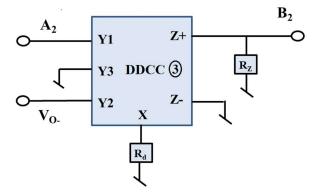

| 4.3.2.1 Lossy Integration-Subtraction operation                         | 62   |

| 4.3.2.2 Subtraction operation                                           | 63   |

| 4.3.2.3 Summation operation                                             | 63   |

| 4.3.2.4 Inverter                                                        | 64   |

| 4.3.2.5 Simulation results                                              | 65   |

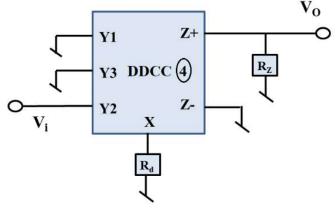

| 4.3.3 Proposed CM-based Wave Active Filter using EXCCCCTA Block  | 72      |

|------------------------------------------------------------------|---------|

| 4.3.3.1 Series inductor                                          | 72      |

| 4.3.3.2 Shunt capacitor                                          | 74      |

| 4.3.3.3 Simulation results                                       | 75      |

| 4.4 Concluding remarks                                           | 82      |

| CHAPTER 5: Design and analysis of rectifiers                     | 84-102  |

| 5.1 Introduction                                                 | 85      |

| 5.2 Literature review                                            | 85      |

| 5.3 Proposed Designs of Rectifiers                               |         |

| 5.3.1 Proposed CM-based rectifier using DDCC Block               | 87      |

| 5.3.1.1 Simulation results                                       | 88      |

| 5.3.2 Proposed CM-based dual output rectifier using DDCCTA Block | 91      |

| 5.3.2.1 Effect of non-unity gains                                | 93      |

| 5.3.2.2 Effects of parasitic                                     | 93      |

| 5.3.2.3 Simulation results                                       | 94      |

| 5.4 Concluding remarks                                           | 101     |

| CHAPTER 6: Conclusion and Future Scope                           | 103-106 |

| 6.1 Conclusion                                                   | 104     |

| 6.2 Future scope                                                 | 106     |

| REFERENCES                                                       | 107-118 |

| LIST OF PUBLICATIONS                                             | 119-120 |

| AUTHOR'S BIOGRAPHY                                               | 121     |

# **LIST OF FIGURES**

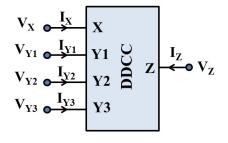

| Fig. 2.1: Symbol of DDCC                                                   | 12 |

|----------------------------------------------------------------------------|----|

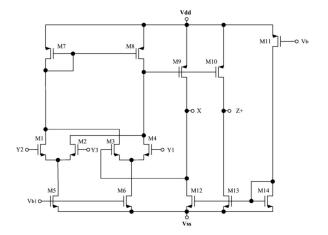

| Fig. 2.2: CMOS schematic of DDCC block                                     | 13 |

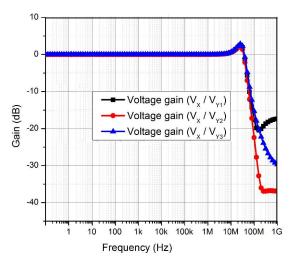

| Fig. 2.3: AC response of Voltage at Y-terminals vs. voltage at X-terminal  | 13 |

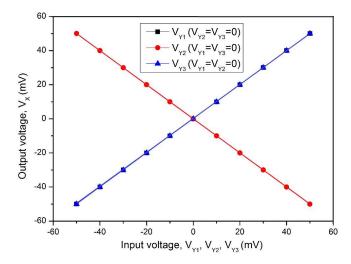

| Fig. 2.4: DC response of Voltage at Y-terminals vs. voltage at X-terminal  | 14 |

| Fig. 2.5: DC response of Current at X-terminal vs. current at Z-terminal   | 14 |

| Fig. 2.6: Equivalent circuit of DDCC with frequency-dependent gains        | 15 |

| Fig. 2.7: Equivalent circuit showing parasitic elements in DDCC            | 16 |

| Fig. 2.8: Symbol of DDCCTA                                                 | 18 |

| Fig. 2.9: CMOS implementation of DDCCTA                                    | 18 |

| Fig. 2.10: AC response of Voltage at Y-terminals vs. voltage at X-terminal | 19 |

| Fig. 2.11: AC response of Voltage at Z-terminal vs. current at O-terminal  | 19 |

| Fig. 2.12: DC response of Voltage at Y-terminals Vs voltage at X-terminal  | 20 |

| Fig. 2.13: DC response of Current at X-terminal Vs current at Z-terminal   | 20 |

| Fig. 2.14: DC response of Current at O-terminal Vs voltage at Z-terminal   | 21 |

| Fig. 2.15: Variation of transconductance with bias current                 | 21 |

| Fig. 2.16: Equivalent circuit of DDCC with frequency-dependent gains       | 22 |

| Fig. 2.17: Equivalent circuit showing parasitic elements in DDCCTA         | 23 |

| Fig. 2.18. Symbol of EX-CCCCTA                                             | 24 |

| Fig. 2.19: CMOS structure of EX-CCCCTA                                     | 25 |

| Fig. 2.20: AC response of current at Z-terminals vs. current at X-terminal | 25 |

| Fig. 2.21: Variation of transconductance with bias current                 | 26 |

| Fig. 2.22: DC response of Voltage at Y-terminals vs. voltage at X-terminal | 26 |

| Fig. 2.23: DC response of Current at X-terminal vs. current at Z-terminal  | 27 |

| Fig. 2.24: DC response of Current at O-terminal Vs voltage at Z-terminal   | 27 |

| Fig. 2.25: Equivalent circuit showing parasitic elements in EX-CCCCTA      | 28 |

| Fig. 3.1: Proposed circuit of the FOUF                                     | 32 |

| Fig. 3.2: (a) Magnitude (b) Phase vs frequency plot of low-pass filter     | 36 |

| Fig. 3.3: (a) Magnitude (b) Phase vs frequency plot of high-pass filter    | 37 |

| Fig. 3.4: (a) Magnitude (b) Phase vs frequency plot of all-pass filter     | 38 |

| Fig. 3.5: Total output voltage noise of filter                                                 |

|------------------------------------------------------------------------------------------------|

| Fig. 3.6: Transient response of LPF, HPF, and APF                                              |

| Fig. 3.7: Lissajous patterns of (a) LPF (b) HPF (c) APF40                                      |

| Fig. 3.8: MC analysis of max output voltage of APF based on 3%40                               |

| Fig. 3.9: THD against Frequency of APF41                                                       |

| Fig. 3.10: Proposed TAM-based PD, PI, PID controller using DDCCTA41                            |

| Fig. 3.11: Tuning of trans-conductance by current bias                                         |

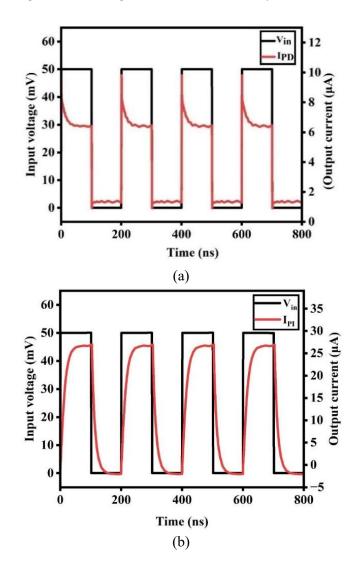

| Fig. 3.12: Transient response of the proposed controllers (a) PD (b) PI (c) PID47              |

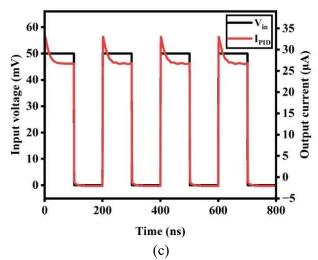

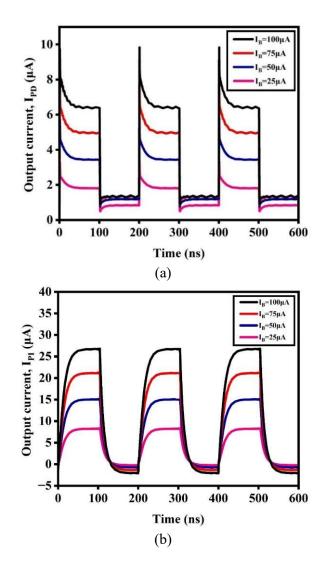

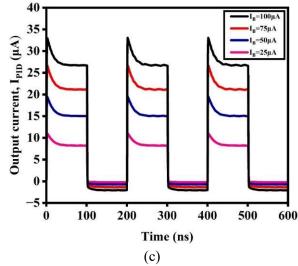

| Fig. 3.13: Transient responses of (a) PD (b) PI (c) PID with the tuning of $I_B$ 48            |

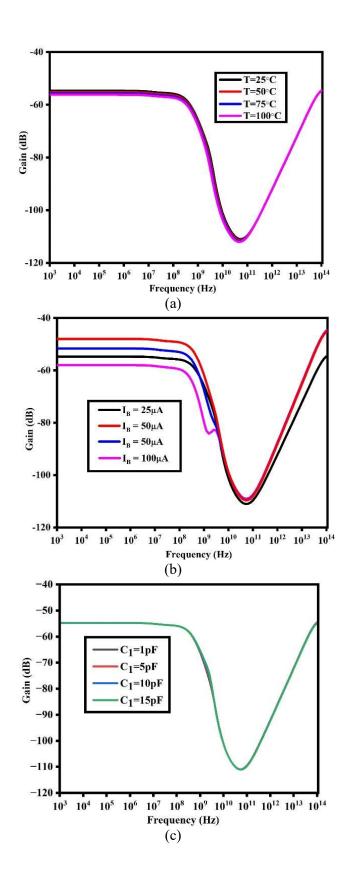

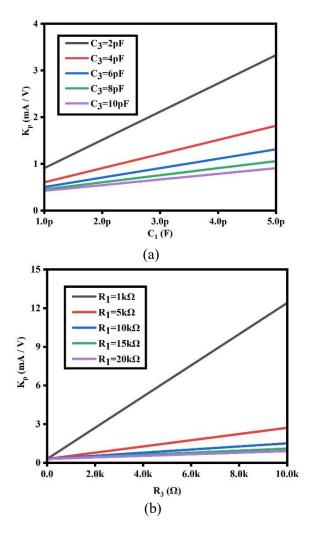

| Fig. 3.14: Gain response of PID controller with (a) different temperatures (b) tuning          |

| of $I_B$ (c) different values of $C_1$ (d) different values of $R_1$                           |

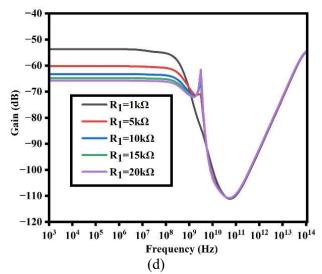

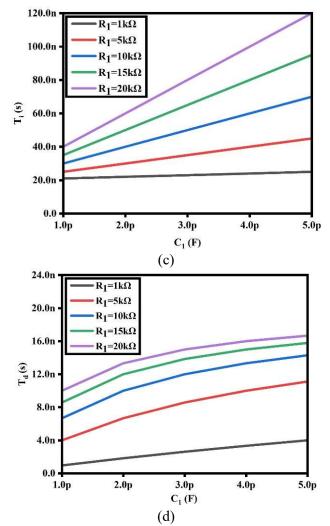

| Fig. 3.15: Gain to passive components control parameter response of PID (a) $K_p$ to $C_1$     |

| (b) $K_p$ to $R_3$ (c) $T_i$ to $C_1$ (d) $T_d$ to $C_1$                                       |

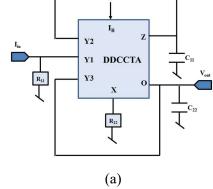

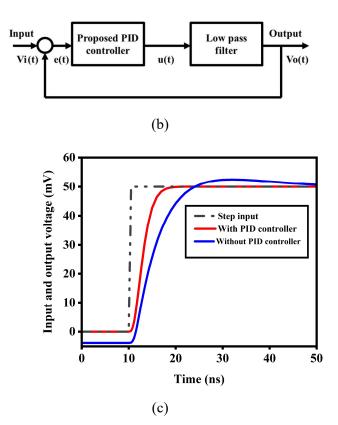

| Fig. 3.16: (a) DDCCTA-based TIM-LPF (b) Closed loop system with proposed TAM-                  |

| PID controller and TIM-LPF filter (c) Step input and output53                                  |

| Fig. 4.1: Two-port network with active wave variables                                          |

| Fig. 4.2: Lossy Integration-Subtraction using DDCC                                             |

| Fig. 4.3: Subtraction operation using DDCC63                                                   |

| Fig. 4.4: Summation operation using DDCC63                                                     |

| Fig. 4.5: Inverter using DDCC                                                                  |

| Fig. 4.6: WAE topology for series inductor                                                     |

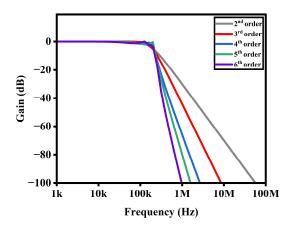

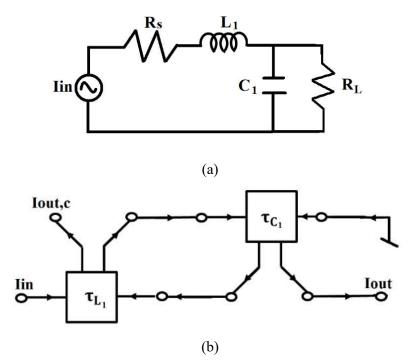

| Fig. 4.7: Frequency response of $n^{th}$ order Butterworth filter (n = 2, 3, 4, 5, 6)67        |

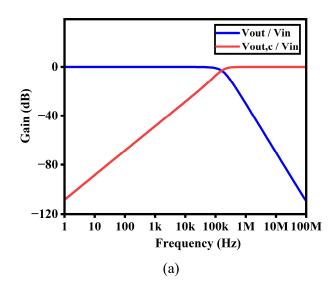

| Fig. 4.8: Frequency response of 2 <sup>nd</sup> order LPF and its complementary HPF at (a) 200 |

| kHz (b) 5 MHz (c) 10 MHz frequencies                                                           |

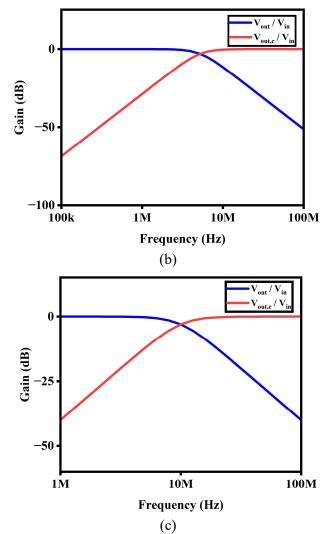

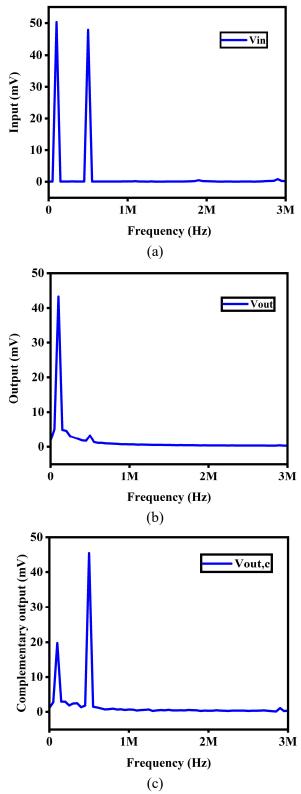

| Fig. 4.9: Spectrum of 2nd order LPF (a) input (b) output and (c) its complementary69           |

| Fig. 4.10: Transient response of 2nd order LPF and its complementary70                         |

| Fig. 4.11: Monte Carlo simulation (a) LPF (b) its complementary as HPF71                       |

| Fig. 4.12: Total output noise voltage72                                                        |

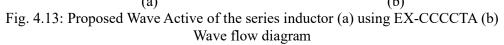

| Fig. 4.13: Proposed Wave Active of the series inductor (a) using EX-CCCCTA (b)                 |

| Wave flow diagram73                                                                            |

| Fig. 4.14: Proposed Wave Active of shunt capacitor (a) using EX-CCCCTA (b) Wave                |

| flow diagram74                                                                                 |

|                                                                                                |

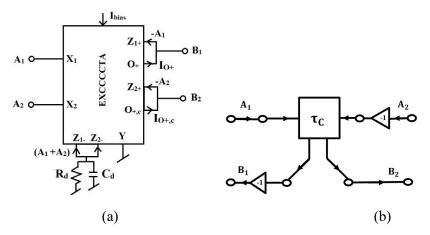

| Fig. 4.15: (a) 2 <sup>nd</sup> order Butterworth low pass filter (b) Wave flow diagram of 2 <sup>nd</sup> order |

|-----------------------------------------------------------------------------------------------------------------|

| Butterworth low pass filter76                                                                                   |

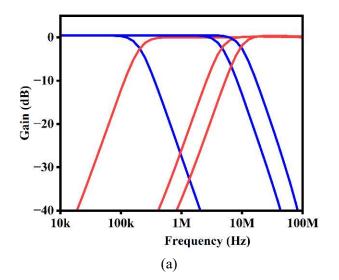

| Fig. 4.16: LPF and HPF (a) Frequency response (b) Transient response77                                          |

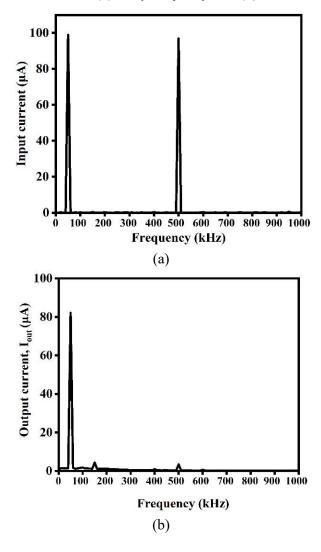

| Fig. 4.17: Spectrum analysis of (a) input current (b) LPF (c) HPF78                                             |

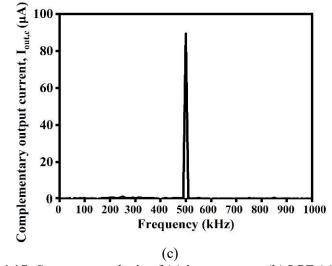

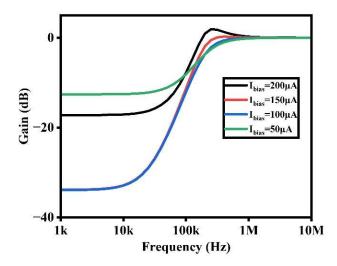

| Fig. 4.18: Frequency response of low pass filter at different current bias78                                    |

| Fig. 4.19: Frequency response of high pass filter at different current bias79                                   |

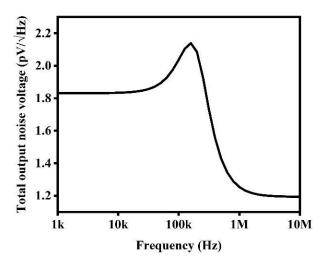

| Fig. 4.20: Total output noise voltage                                                                           |

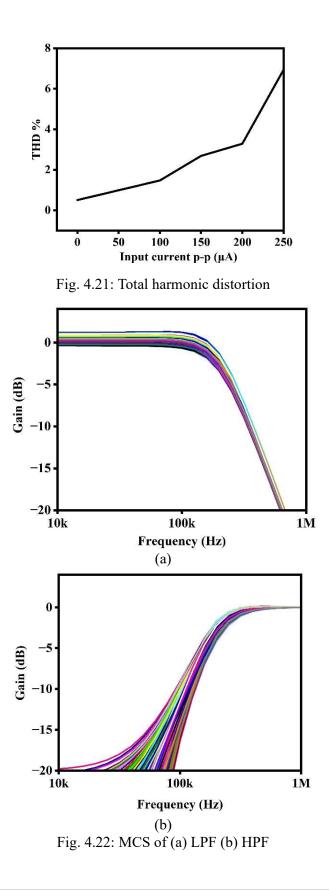

| Fig. 4.21: Total harmonic distortion of EXCCCCTA based WAF80                                                    |

| Fig. 4.22: MCS of (a) LPF (b) HPF80                                                                             |

| Fig. 5.1: Proposed (a) positive rectifier (b) negative rectifier                                                |

| Fig. 5.2: DC response of the proposed FWRs                                                                      |

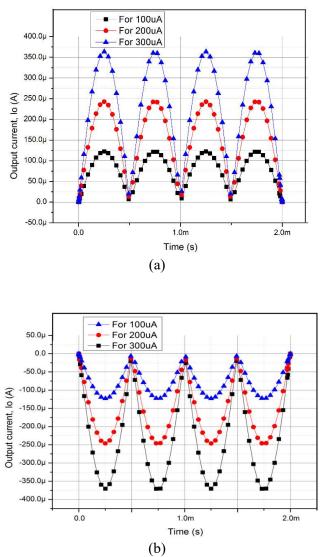

| Fig. 5.3: Transient responses of proposed (a) positive FWR (b) negative FWR89                                   |

| Fig. 5.4: The output current of (a) Positive FWR (b) Negative FWR at 200 MHz90                                  |

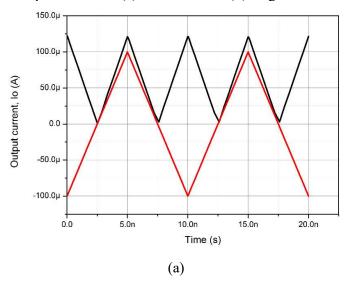

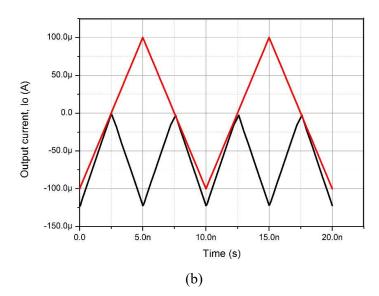

| Fig. 5.5: The output current of (a) Positive FWR (b) Negative FWR for triangular input                          |

| current                                                                                                         |

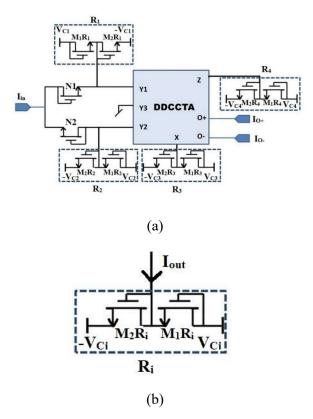

| Fig. 5.6: (a) Proposed dual-output FWR (b) MOS-based active resistor92                                          |

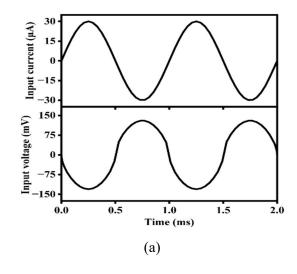

| Fig. 5.7: (a) Input current and its corresponding input voltage (b) Mode of operations                          |

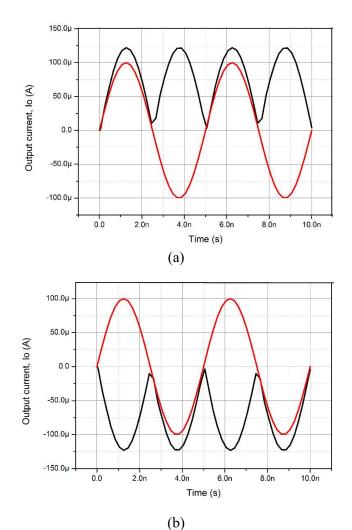

| of NMOS-based diode95                                                                                           |

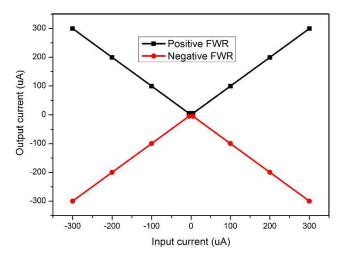

| Fig. 5.8: DC response of proposed dual-outputs FWR95                                                            |

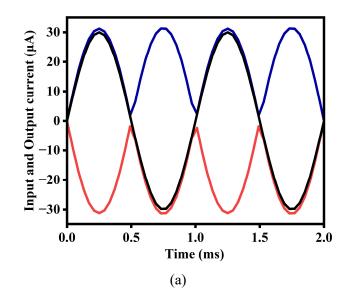

| Fig. 5.9: Transient response of FWR at different frequencies (a) 1 kHz (b) 1MHz (c)                             |

| 10MHz97                                                                                                         |

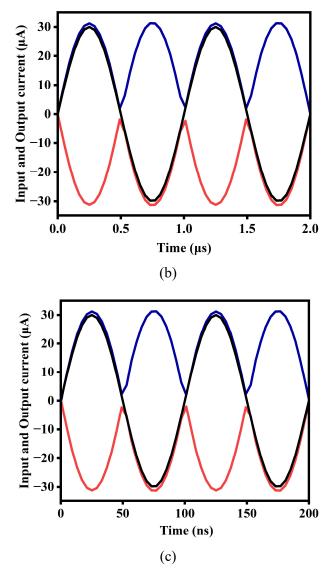

| Fig. 5.10: Transient response (a) with different current amplitudes (b) at the different                        |

| temperatures                                                                                                    |

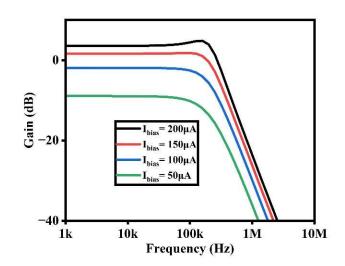

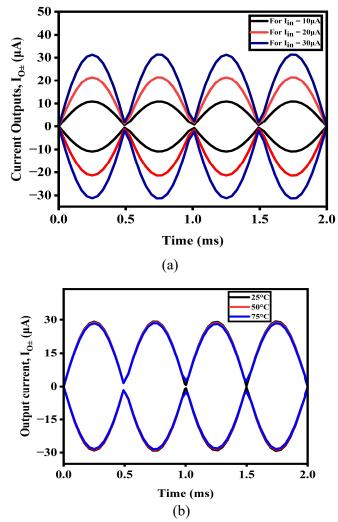

| Fig. 5.11: Electronic tuning of rectifier gain through Ibias                                                    |

| Fig. 5.12: Monte-Carlo simulations (a) DC characteristics (b) Rectified output of                               |

| Positive and Negative FWR100                                                                                    |

| Fig. 5.13: Output voltage noise of proposed rectifiers100                                                       |

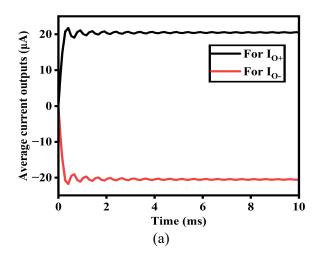

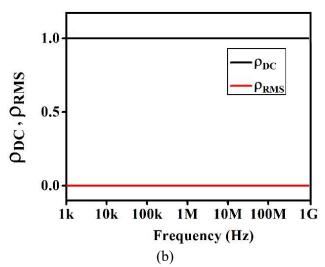

| Fig. 5.14 (a) Dual phase positive ( $I_{O+}$ ) and negative ( $I_{O-}$ ) average DC outputs (b) $\rho dc$       |

| and $\rho$ rms versus frequency                                                                                 |

# LIST OF TABLES

| Table 2.1: Aspect ratio of various transistors of DDCC                               |

|--------------------------------------------------------------------------------------|

| Table 2.2 Aspect ratio of PMOS and NMOS transistors    18                            |

| Table 2.3: Transistor sizes for EX-CCCCTA25                                          |

| Table 3.1: Working principle of MISO type first-order universal filter               |

| Table 3.2: Comparison of performance of the second-order filter                      |

| Table 4.1: Wave topologies of series/shunt inductor and capacitor61                  |

| Table 4.2: Different order of LP Butterworth filter synthesis                        |

| Table 4.3: Normalized values and calculated Wave active values for the design of 200 |

| kHz cut-off frequency67                                                              |

| Table 4.4. The performance values of EX-CCCCTA based $2^{nd}$ order Butterworth      |

| filter                                                                               |

# **Chapter 1**

# Introduction

## **1.1 Introduction**

A system is known as very large scale integration (VLSI) because of involving integration of millions of transistors on a single chip to enable the functioning of highly complex integrated circuits (ICs). Complementary Metal-oxide-semiconductor (CMOS) technology is the heart of modern VLSI systems and a widely used form of Analog circuit design. CMOS technology allows designers to optimize parameters like speed of operation, power dissipation and chip size which leads to more efficient systems-on-chip (SoC) designs [1]. To be familiar with the basics of microelectronic circuits such as how transistors work, and how to build a circuit from those basic components. It allows us to show the extreme difference between properly designed digital logic to analog design [2] which is important for the VLSI design development. Furthermore, the design of analog CMOS integrated circuits is essential for developing interfaces that connect digital components to the analog environment, which improves the capabilities of VLSI systems. This covers a wide range of functionalities, from basic transistor behavior and digital logic design to advanced approaches in analog circuits, demonstrating the scope of VLSI advancements [3].

The operational amplifier (Op-amp) is a useful device, having several applications, nevertheless, it has a limited amplification factor, poor slew rate, and a non-uniform bandwidth product. Furthermore, the op-amp-based designs often require exactly passive components that face challenges such as the need for internal matching and a large number of non-canonical features. To overcome these limitations, researchers and circuit designers have developed various alternatives to analog building blocks (ABBs) over the past decades [4]. Fundamentally, an op-amp operates as a voltage-controlled voltage source (VCVS), producing an output voltage dependent on the differential voltage at its input terminals. Most of the active devices implement one of four types of controlled sources: VCVS, voltage-controlled current source (VCCS), current-controlled voltage source (CCVS), and current-controlled current source (CCCS). These controlled sources enable different modes of circuit operation, namely

voltage mode, current mode, trans-impedance mode, and trans-admittance mode. A comprehensive review provides a unified framework for developing new ABBs with diverse features [5]. In practice, input sources of amplifiers are not ideal; a voltage source has a non-zero output resistance, and a current source has finite output resistance. Similarly, loads driven by an amplifier could vary from very low to very high impedance. Thus, the circuit designers must have the degree of flexibility to select amplifier types appropriate to the needs of the applications.

The open-loop gain for VCVS or Voltage amplifiers, in the case of the input source being of negligible output impedance along with the load impedance being quite high requires the amplifier to have a high (ideally infinite) input impedance and low (ideally zero) output impedance. This class of devices includes traditional op-amp, Differential Difference Amplifiers (DDA), Voltage Differencing Buffered Amplifiers (VDBA), and Voltage Differencing Inverted Buffered Amplifiers (VDIBA), which use voltage for both input and output, leading to high input as well as low output impedance. If the source that is outputting to the amplifier is low, as well as the load that the amplifier drives, the input impedance and output impedance will be high. The VCCS, or transconductance amplifiers use an input voltage and output current. These include high input-output resistance, like operational trans-conductance amplifier (OTA), voltagedifferential transconductance amplifiers (VDTA), and voltage-differential current conveyors (VDCC), etc. If the input source has a high output impedance and the load impedance is low, the amplifier must have low input impedance (ideally zero) and high output impedance (ideally infinity). This is where the CCCS comes in, current amplifiers meet this need and furnish a controlled current as defined by the input current. This includes Current Conveyor (CC), Current Differential Transconductance Amplifier (CDTA), Current Differential Current Conveyor (CDCC), Dual X Current Conveyor Transconductance Amplifier (DXCCTA), Current Controlled Transconductance Amplifier (CCTA). On the other hand, if both input source output impedance is high, and the load impedance is high, the amplifier would need low input, and output, impedance. This is the domain of the trans-resistance amplifier, or CCVS, which accepts a current input and produces a voltage output. Current difference buffered amplifiers (CDBA), current difference differencing input buffer amplifiers

(CDDIBA), current difference differencing output buffer amplifiers (CDDOBA), and operational trans-resistance amplifiers (OTRA), all with ideally zero input and output impedance [4-5].

A signal in both digital and analog circuitry can be understood better with the help of the two basic design techniques: Voltage mode (VM) and current mode (CM). Using this method, the circuits are built around voltages across components, an approach that is extremely common in CMOS technology because of its robustness, ease of integration, and low power consumption. For the aforementioned reasons, CMOS VLSI design in general utilizes VM circuits in its digital logic functions. On the other hand, the CM design revolves around the idea of current flowing through a circuit to signify a signal and this kind of signal representation provides many benefits including high speed, greater linearity, and better performance on low-power configurations.

Various analog VLSI design blocks have been created to leverage CM signal processing advantages. Op-amps are key components in VM circuits, recognized for their high gain and input impedance. Other important blocks include the current differencing buffer amplifier (CDBA) [34, 75] and voltage differencing buffer amplifier (VDBA) [61]. Current conveyors (CCs) which exist in multiple versions (CCI, CCII, CCIII) [14, 24, 32, 87, 89, 95, 108, 112], are essential in CM designs and frequently used in current mirrors. More sophisticated conveyors like Differential Voltage Current Conveyors (DVCC) [13, 18, 19, 41, 111], Extra-X Current Conveyors (EXCCII) [80], and Dual-X Current Conveyors (DXCCII) [109, 116] support complex applications such as chaotic circuits and analog computation. Operational Floating Current Conveyors (OFCC) [72] and Differential Difference Current Conveyors (DDCCs) [96, 106] broaden the capabilities of CM designs. OTAs, critical for converting input voltage into output current, find widespread use in tunable filters, oscillators, and multipliers. Their tunability is ideal for low-power, programmable circuits. Other significant blocks include the Current Differencing Transconductance Amplifier (CDTA) [20, 26, 67, 69, 71, 123], Voltage Differencing Transconductance Amplifier (VDTA) [59, 60, 124], and Differential-Difference Transconductance Amplifier (DDTA) [63, 129]. Cascading blocks like the Differential Difference Current Conveyor Transconductance Amplifier (DDCCTA) [10], Extra-X Current

Controlled Current Conveyor Transconductance Amplifier (EXCCCCTA) [11], and Dual-X Current Conveyor Transconductance Amplifier (DXCCTA) [109, 116] enhance the flexibility, tunability, and functionality of analog VLSI designs. These advanced building blocks are essential for achieving better precision, enhanced performance, and lower power consumption, making them crucial in current lowpower and high-performance analog VLSI circuits.

In VLSI design, analog circuits play a crucial role in facilitating both linear and nonlinear applications that are essential for various contemporary systems such as communications, signal processing, and instrumentation. The integration capabilities of VLSI technologies enable the incorporation of multiple analog components onto a single chip, greatly improving performance in terms of area efficiency, power consumption, and operational speed. This thorough analysis explores the design and implementation of these applications, emphasizing how analog components are utilized within the VLSI framework. Linear applications, which include filters, amplifiers, and oscillators, are examined for their potential to maximize key performance metrics. These metrics include bandwidth improvement, power efficiency, and the reduction of circuit area, all of which are vital for creating compact and efficient systems. Filters are crafted to achieve specific frequency responses, amplifiers seek to deliver stable gain with minimal distortion, and oscillators concentrate on producing consistent and reliable frequencies. The design process entails careful consideration of trade-offs among power, speed, and area, guaranteeing that the integrated circuits fulfill the rigorous demands of current applications. Conversely, non-linear applications like rectifiers, multipliers, and waveform generators leverage the inherent non-linear characteristics of analog components to realize high-speed and effective designs. Rectifiers are vital for converting AC signals to DC, multipliers find their use in modulation and demodulation tasks, and waveform generators are essential for producing various signal shapes needed in testing and communication systems. These non-linear applications are specifically designed to enhance operational speed and efficiency, meeting the increasing demand for highperformance analog parts in sophisticated VLSI systems.

In conclusion, the role of analog circuits in VLSI design encompasses a broad use of linear and non-linear applications. The continuous innovation in analog building blocks and their integration into VLSI systems underscores the ongoing significance of analog design in achieving superior performance in contemporary electronic systems. As technology progresses, the exploration and optimization of these analog circuits will remain a cornerstone of VLSI design, driving the development of more advanced and efficient systems.

### **1.2** Available literature and scope of work

Filters are crucial in signal processing, designed to allow or reduce certain frequency ranges in a signal. They can be categorized as low-pass (LP), high-pass (HP), all-pass (AP), band-pass (BP), or band-stop (BS) [6]. Filters help remove noise, isolate signals, and shape frequency responses. In control systems, they are vital for stable operations, enhancing signal quality, and improving control accuracy by reducing noise and filtering high-frequency interference. This boosts controller performance in applications like robotics, automation, and communication systems. Analog filters (LP, HP, AP) are significant for selecting frequencies and minimizing noise. While early designs using voltage-mode (VM) operational amplifiers (Op-Amps) are effective, they had high-frequency bandwidth limitations. Current-mode (CM) filters, using Current Conveyors (CCs) and Operational Transconductance Amplifiers (OTAs), provide better bandwidth and quicker responses, especially at high frequencies. AP filters are essential for altering phase response while maintaining amplitude, important for phase shifters and oscillators. Studies have introduced various first-order filter topologies utilizing active components like DXMOCCII [12], DVCC [13], CCIII [14], FDCCII [15], MO DXCCTA [16], VDCC [18], CCCDTA [20], and DBTA [21]. Some designs incorporate multiple blocks such as ICCII [23], CCII [24], DO CF [25], CDTA [26], OFCC [27], OTRA [28], and BJT [30]. These are assessed based on operational modes—VM [13, 28], CM [12, 16, 20, 23-26, 29, 30], TAM [27], and mixed-mode [14, 15, 17, 19, 21], and involving grounded or floating passive components [18-20, 23-27, 29]. Many designs aim for high input/output impedances, low total harmonic

distortion (THD), reduced noise, and efficient power usage. Structures that simultaneously provide low-pass, high-pass, and all-pass responses are emphasized [12, 13, 15, 17, 18, 23, 24, 27, 28, 30], especially in VM and CM configurations. Notably, AP filters are commonly used as oscillators [12, 17, 20, 25-27], highlighting the need for single analog building blocks (ABBs) with minimal passive elements.

In control systems, Proportional-Derivative (PD), Proportional-Integral (PI), and Proportional-Integral-Derivative (PID) controllers are widely used for the precise control of dynamic processes [7]. VLSI implementations with CM circuits have shown better dynamic response and low power consumption and are suitable for real-time feedback control applications in robotics and industrial automation. Active block-based controllers are being compared for CCII [31], DO-CCII [32], MO-CCCCTA [33], CCCDBA [34], CFOA [35, 39, 42], FDCCII [37], OTRA [38], DVCCTA [40], VDCC [41], CFTA [43], VCII [46], and CCTA [45]. Their operations in VM, CM, and mixed mode have been demonstrated to possess independent or dependent tunable parameters in terms of PD, PI, and PID configurations [31, 34, 37, 38, 40].

Although first-order and second-order filters are enough for most simple applications, advanced systems often require higher precision and selectivity, which can be achieved with higher-order filters. Higher-order filters have sharper roll-off characteristics and better frequency discrimination, allowing them to handle complex signal environments with closely spaced frequency components [6]. Of the higher-order filters, wave-active filters have the best dynamic range and energy efficiency. Taking advantage of wave propagation principles in the wave, such filters are quite efficient in managing high-frequency signals with variations of operational conditions; hence, it is particularly applicable in high-performance control systems, telecommunications, and power electronics for precision and robustness. Higher-order filters are implemented by cascading multiple first-and second-order stages, which results in an increased complexity of the filter and its improvement in frequency response. A better design for filters involves proper alignments of active circuit components like inductors and capacitors which directly impacts various properties such as the steepness of the cut-off slope, attenuation rate, and selectivity of the filters. Higher-order filters allow better

sharp cutoffs, increase specificity, and maximize attenuations that effectively remove signals without any significance at stopband positions. These features make them indispensable in applications like audio processing, communications, and medical devices, where precise frequency control is crucial. Apart from their noise and interference reduction capabilities, higher-order filters are significant in sensitive applications such as radar, biomedical technology, and RF communication. They also ensure stability and phase control, which are critical in control and communication systems requiring strict phase fidelity. There have been VM-based WAEs reported that incorporate a significant number of analog building blocks in their construction, except [17]. The realization of complex series inductors and shunt capacitors has been elaborated in various works [55, 56, 59, 64]. Second-order [63, 64], third-order [54, 57, 58, 62-64], and fourth-order [55, 56, 59-63] filters have been discussed in many sources. Advanced properties of these filters show their importance in modern electronic systems where high performance and reliability are considered critical.

Rectifiers are basic circuits in signal processing and power conversion. They are very important in the transformation of alternating current (AC) signals into direct current (DC) [8]. The conversion process is essential for the operation of electronic devices, as it guarantees that they obtain a consistent DC supply. Rectifiers are generally categorized into two types: half-wave and full-wave, with full-wave rectifiers providing enhanced efficiency and a more uniform output. This integration is very important in motor drives, power controllers, and audio applications where the absence of ripple on the DC output is considered crucial for achieving the maximum performance output. Full-wave rectifiers have various applications in signal processing, instrumentation, communication systems, radio frequency modulation, and demodulation, measurement of alternating current measurement instruments, detection of signal polarity, peak detection, and frequency doubling. The conventional configurations of the rectifier are primarily based on diodes and operational amplifiers. Such configurations limit the speed and efficiency of their operation. Current designs use CM methodologies and active components such as current conveyors to enhance performance in terms of speed and power consumption. Advanced rectifier topologies involve current-mode components, which include CCII [95], EXCCII [80], DVCC

[74], CDTA [67, 69, 71], OTA [74, 86], OTRA, CFDITA [84], CDBA [75], and OFCC [72]. Most of these utilize active elements and devices like diodes and MOS transistors to offer maximum efficiency for the variable loads due to their sensitivity. Most of these rectification topologies use diodes to rectify while others use MOS transistors [67, 69, 71]; however, most of them are not dual output in one configuration, except [80]. The current configurations of rectifiers portray the changing necessities of today's control and power conversion applications; they are offered greater efficiency and performance within increasingly complex systems.

A comprehensive literature review based on CM-based analog signal processing and generation circuits results in the following shortcomings:

- No designs for MISO-type Universal first-order filters using DDCC have been reported.

- Until now, controller circuits involving DDCCTA have not been reported for independent tunability or equivalent resistance preservation.

- (iii) Further, no such wave active filter designs involving DDCC and EXCCCCTA are reported, which includes a minimum number of passive components without considering component matching limitations.

- (iv) To existing work, no reported work has demonstrated the ability of a DDCC and DDCCTA-based rectifier circuits to simultaneously generate positive and negative rectified outputs.

# 1.3 Thesis organization

The work presented in the thesis has been organized as follows:

**Chapter 1** titled **Introduction**, provides an overview of the fundamental concepts of VLSI technology, focusing on CM blocks and their linear and non-linear applications.

**Chapter 2** titled **Description of DDCC, DDCCTA & EXCCCCTA ABBs**, describes an overview of key analog building blocks used in thesis work and their applications in current circuit design. Understanding the functionalities and advantages of DDCC, DDCCTA, and EX-CCCCTA is crucial for developing efficient analog circuits.

**Chapter 3** titled **Single ABB-based Filter and Controller Designs**, addresses reducing circuit complexity by employing single analog building blocks (ABB). Simplifying circuit designs is essential for reducing power consumption, lowering fabrication costs, and improving integration in VLSI systems. A Multiple Input Single Output (MISO) VM first-order universal filter using DDCC and TAM-based PD, PI, and PID controllers using a single DDCCTA are discussed.

**Chapter 4** titled **VM and CM-based Wave-Active Filters**, focuses on improving the circuit responses in terms of accuracy, stability, and frequency performance. The design of an nth-order wave active low-pass filter using a DDCC and a Simplified Wave Active Filter realized using a single EX-CCCCTA are discussed.

**Chapter 5** titled **Design and Analysis of Rectifiers**, addresses designing circuits, an MOS-based electronically tunable CM dual-output full-wave rectifier, utilizing a single DDCCTA and a CM positive and negative rectifier based on DDCC is presented.

Chapter 6, Conclusion and Future Scope summarizes the work presented in the thesis and identifies the future scope.

# Chapter 2

# Description of DDCC, DDCCTA and EX-CCCCTA Blocks

### 2.1 Differential Difference Current Conveyor (DDCC) Block

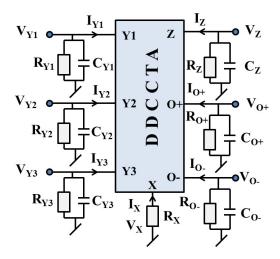

DDCC is a DDA cascaded with CCII, with three differential inputs at Y-terminals, one X-terminal, and one Z-terminal [9]. The current at all Y-terminals is shown to be zero as per equation (2.2). The X-terminal voltage is arithmetically proportional to the Y-terminal voltage of the equation (2.3). The Z-terminal current follows the X-terminal current as per equation (2.4), whether inward or outward direction. The X-terminal offers low impedance input, the Y-terminal a high impedance input, and the Z-terminal a high impedance output. The DDCC symbol is presented in Fig. 2.1(a). The terminal relations are shown as matrix characteristics in equation (2.1):

$$\begin{bmatrix} I_{Y_{1,2,3}} \\ V_X \\ I_Z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 1 & -1 & 1 & 0 \\ 0 & 0 & 0 & \pm 1 \end{bmatrix} \begin{bmatrix} V_{Y_1} \\ V_{Y_2} \\ V_{Y_3} \\ I_X \end{bmatrix}$$

(2.1)

-17 -

$$I_{Y1} = I_{Y2} = I_{Y3} = 0 (2.2)$$

$$V_X = V_{Y1} - V_{Y2} + V_{Y3} (2.3)$$

$$I_Z = \pm I_X \tag{2.4}$$

Fig. 2.1: Symbol of DDCC [9]

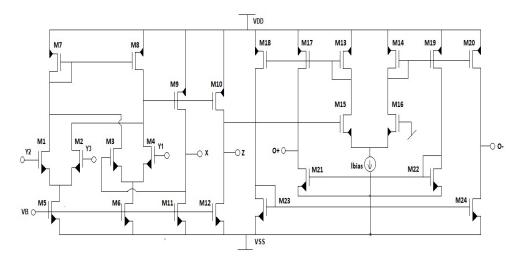

SPICE simulator with 180 nm TSMC CMOS technology parameters is used. The CMOS schematic of the DDCC block is shown in Fig. 2.2 and respective W/L ratios of nMOS and pMOS transistors are shown in Table 2.1. The supply voltages  $V_{DD} = V_{SS}$ =  $\pm 0.9 V$  and a bias voltages  $V_b = -0.31 V$  are used. In Fig. 2.2, the two input differential stages (M1, M2) and (M3, M4), by considering the large gain phase, a current mirror (M7 and M8) transforms the differential current into a single-end output current (M9). The M10 duplicates the M9 current.

| Transistors | Aspect ratio W(μm)/L(μm) |

|-------------|--------------------------|

| All PMOS    | 10/0.4                   |

| All NMOS    | 05/0.4                   |

Table 2.1: Aspect ratio of various transistors of DDCC [9]

Fig. 2.2: CMOS schematic of DDCC block [9]

#### 2.1.1 AC Characteristics

Fig. 2.3 plots the frequency response of voltage gains  $(V_X/V_{YI}, V_X/V_{Y2}, V_X/V_{Y3})$ . The cut-off frequencies of the voltage gains obtained without load are about 25 MHz, and the gains are unity at low frequencies.

Fig. 2.3: AC response of Voltage at Y-terminals vs. voltage X-terminal

#### 2.1.2 DC Characteristics

The DC voltage characteristics between the Y-terminals and X-terminal are presented in Fig. 2.4. The output voltages obtained to X-terminal  $V_X$  according to  $V_{YI}$ ,  $V_{Y2}$  and  $V_{Y3}$  show a common dynamic range extended from -50 mV to 50 mV

Fig. 2.4: DC response of Voltage at Y-terminals vs. voltage X-terminal

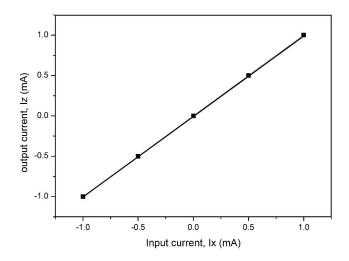

Fig. 2.5 shows the variation of output current  $I_Z$  versus the current  $I_X$ , with grounded Y terminals and a load resistance of about 1 k $\Omega$ , the current follower characteristic with a boundary linear range from -1 mA to 1 mA.

Fig. 2.5: DC response of Current at X-terminal vs. current Z-terminal

#### 2.1.3 Non-ideal Effects

In Fig 2.6, the consideration of the non-ideal values of DDCC, the characteristic matric can be rewritten as:

$$\begin{bmatrix} I_{Y1,2,3} \\ V_X \\ I_Z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ \alpha_1 & -\alpha_2 & \alpha_3 & 0 \\ 0 & 0 & 0 & \pm \beta \end{bmatrix} \begin{bmatrix} V_{Y1} \\ V_{Y2} \\ V_{Y3} \\ I_X \end{bmatrix}$$

(2.5)

$$V_X = \alpha_1 V_{Y1} - \alpha_2 V_{Y2} - \alpha_3 V_{Y3} \tag{2.6}$$

$$I_Z = \pm \beta I_X \tag{2.7}$$

$$I_{Y1} = I_{Y2} = I_{Y3} = 0 (2.8)$$

Where  $\alpha_1$ ,  $\alpha_2$  and  $\alpha_3$  are non-ideal voltage-transfer gains from Y1 to X, Y2 to X and Y3 to X-terminal respectively.  $\pm\beta$  Is non-ideal current transfer gain from X to Z-terminal.

Fig. 2.6: Equivalent circuit of DDCC with frequency-dependent gains

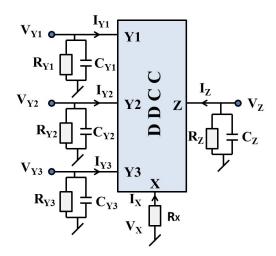

#### **2.1.4 Parasitic Effects**

In Fig. 2.7, the parasitic effects of DDCC are characterized by:

- R<sub>X</sub> is parasitic resistance that occurs at the X-terminal.

- R<sub>Y1</sub> // C<sub>Y1</sub>, R<sub>Y2</sub> // C<sub>Y2</sub> and R<sub>Y3</sub> // C<sub>Y3</sub> are parasitic impedances at Y<sub>1</sub>, Y<sub>2</sub> and Y<sub>3</sub>-terminals respectively.

- $R_Z // C_Z$  is parasitic impedance at Z-terminal.

The passive component values including non-ideal parasitic resistances and impedances can be modified as:

$$Z_{l} = R_{Yl} // (l/sC_{Yl})$$

(2.9)

$$Z_2 = R_{Y2} // (1/sC_{Y2})$$

$$Z_3 = R_{Y3} // (1/sC_{Y3})$$

(2.10)

(2.11)

$$Z_4 = R_Z // (1/sC_Z)$$

(2.12)

$$Z_5 = R_X \tag{2.13}$$

The parasitic at the X-terminal terminal ( $R_X$ ) is very low, the parasitic at Y-terminal terminals ( $R_Y$ ,  $C_Y$ ) is very high, 18 fF, the parasitic at the Z-terminal ( $R_Z$ ,  $C_Z$ ) is 200 k $\Omega$ , 30 fF. The power consumption of the DDCC circuit is about 2.94 mW.

Fig. 2.7: Equivalent circuit showing parasitic elements in DDCC

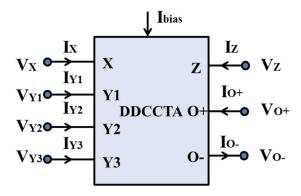

# 2.2 Differential Difference Current Conveyor Trans-Conductance Amplifier (DDCCTA) Block

The DDCCTA analog building block is constructed by cascading of DDCC and OTA and its circuit symbol is shown in Fig. 2.8 [10] and its CMOS implementation is shown in Fig. 2.9. To clarify, the DDCCTA provides a single block, unified active component

for proposed circuit design by integrating the advantages of the OTA's transconductance properties with the DDCC's current conveyor characteristics. This integration is essential because it eliminates the need for extra discrete active components while allowing the DDCCTA to perform multiple functions efficiently, including high input and output impedances and enabling electronic tuning. The DDCCTA block has high impedance input Y (*Y1, Y2, Y3*) whereas the X-terminal is low impedance input, and while Z-terminal and O-terminals are the high impedance output terminals. The terminal characteristics are defined by the matrix given below as per equation (2.14):

$$\begin{bmatrix} I_{Y_{1,2,3}} \\ V_X \\ I_Z \\ I_{O+} \\ I_{O-} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 \\ 1 & -1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & g_m \\ 0 & 0 & 0 & 0 & -g_m \end{bmatrix} \begin{bmatrix} V_{Y_1} \\ V_{Y_2} \\ V_{Y_3} \\ I_X \\ V_Z \end{bmatrix}$$

(2.14)

$$I_{Y1} = I_{Y2} = I_{Y3} = 0 (2.15)$$

$$V_X = V_{Y1} - V_{Y2} + V_{Y3} (2.16)$$

$$I_Z = \pm I_X \tag{2.17}$$

$$I_{0\pm} = \pm g_m V_Z \tag{2.18}$$

The trans-conductance  $(g_m)$  is electronically controllable by an electronic bias current  $(I_{bias})$  and the value can be calculated as given in equation (2.19):

$$g_m = \sqrt{\mu C_{ox} \frac{W}{L} I_{bias}}$$

(2.19)

Where  $\mu$  is the effective channel mobility, *Cox* is the gate-oxide capacitance per unit area, *W* and *L* correspond to the channel width and length of the MOS transistor (*M15 and M16 in Fig. 2.9*).

SPICE simulations are performed by using 180 nm TSMC CMOS technology. The width and length are mentioned in Table 2.2 for all transistors. The supply voltages are taken  $V_{DD} = V_{SS} = \pm 0.9$  V. The bias voltage  $V_{bias}$  and the bias current  $l_{bias}$  are taken as - 0.31 V and 50  $\mu$ A respectively.

Fig. 2.8: Symbol of DDCCTA [10]

Table. 2.2 Aspect ratio of PMOS and NMOS transistors [10]

| Transistors          | Aspect ratio W(µm)/L(µm) |

|----------------------|--------------------------|

| M1-M6, M11, M12      | 4.50/0.36                |

| M7-M10               | 9.00/0.36                |

| M13, M14             | 4.32/0.36                |

| M15, M16             | 11.52/0.36               |

| M17-M20              | 4.80/0.36                |

| M21-M24              | 2.88/0.36                |

| N1, N2, M1Ri*, M2Ri* | 0.36/0.36                |

Fig. 2.9: CMOS implementation of DDCCTA [10]

#### 2.2.1 AC Characteristics

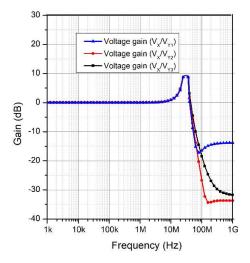

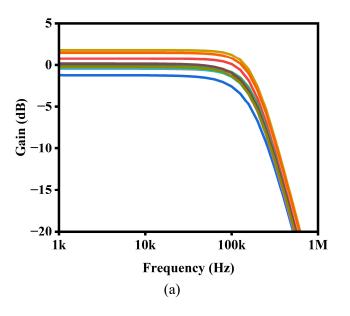

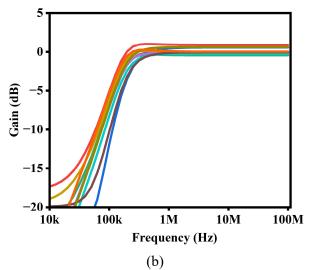

Fig. 2.10 plots the frequency response of voltage gains  $(V_X/V_{YI}, V_X/V_{Y2}, V_X/V_{Y3})$ . The cutoff frequencies of the voltage gains obtained without load are about 45 MHz, and gains are unity at low frequencies. Fig 2.11 shows the OTA gain  $(I_{O\pm}/V_Z)$  is 5 MHz when an input voltage of 1 mV is applied at the Z-terminal.

Fig. 2.10: AC response of Voltage at Y-terminals vs. voltage X-terminal

Fig. 2.11: AC response of Voltage at Z-terminal vs. current at O-terminal

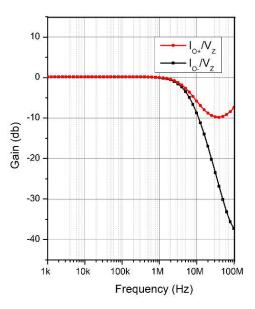

#### 2.2.2 DC Characteristics

The DC voltage characteristics between the Y-terminals and X-terminal are presented in Fig. 2.12. The output voltages obtained to X-terminal  $V_X$  according to  $V_{YI}$ ,  $V_{Y2}$  and  $V_{Y3}$  show a common dynamic range extended from -300 mV to 300 mV.

Fig. 2.12: DC response of Voltage at Y-terminals Vs voltage at X-terminal

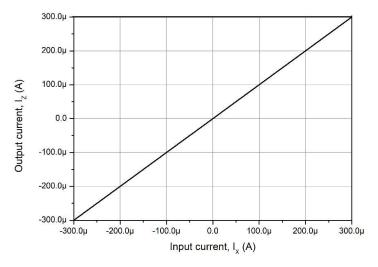

Fig. 2.13 shows the variation of output current  $I_Z$  versus the current  $I_X$ , with grounded Y terminals and a load resistance of about 1 k $\Omega$ , the current follower characteristic with a boundary linear range from -300  $\mu$ A to 300  $\mu$ A.

Fig. 2.13: DC response of Current at X-terminal Vs current at Z-terminal

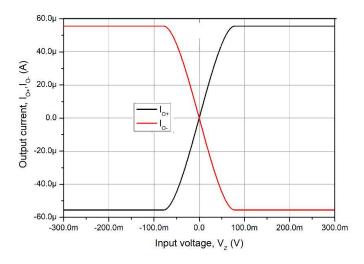

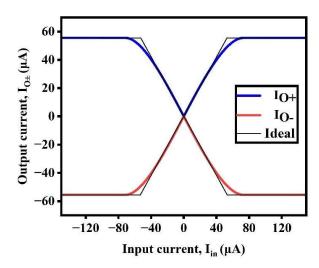

Fig. 2.14 presents the DC voltage characteristics between the Z-terminals and O-terminals. The output current obtained to O-terminal ( $I_{O\pm}$ ) according to voltage at Z-terminal ( $V_Z$ ) shows a dynamic range extended from -55 µA to 55 µA and -75 mV to 75 mV, respectively.

Fig. 2.14: DC response of Current at O-terminal Vs voltage at Z-terminal

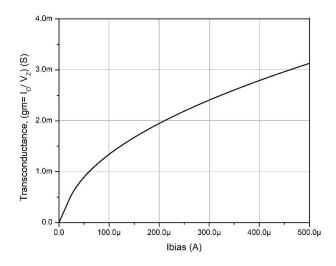

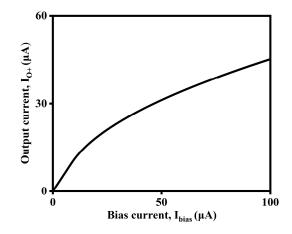

The variation of the trans-conductance value by changing  $I_{bias}$  from 0 to 500  $\mu$ A is depicted in Fig. 2.15. The increase in transconductance for larger bias currents. The maximum transconductance is about 3.1 mS.

Fig. 2.15: Variation of transconductance with bias current

#### 2.2.3 Non-ideal Effects

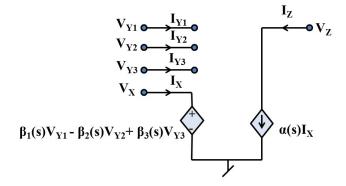

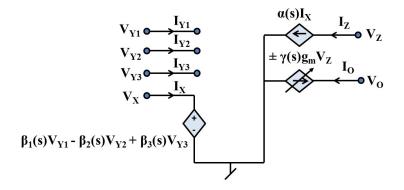

In Fig. 2.16, the impact of the non-ideal effect of DDCCTA may be examined by considering non-unity transfer gains and rewritten below in Eq. (2.20):

$$\begin{bmatrix} I_{Y1,2,3} \\ V_X \\ I_Z \\ I_{O+} \\ I_{O-} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 & 0 \\ \beta_1 & -\beta_2 & \beta_3 & 0 & 0 \\ 0 & 0 & 0 & \alpha & 0 \\ 0 & 0 & 0 & 0 & \gamma g_m \\ 0 & 0 & 0 & 0 & -\gamma g_m \end{bmatrix} \begin{bmatrix} V_{Y1} \\ V_{Y2} \\ V_{Y3} \\ V_Z \end{bmatrix}$$

(2.20)

Where,  $\beta_1$ ,  $\beta_2$ , and  $\beta_3$  are non-ideal voltage-transfer gains from voltage *Y1*, *Y2*, and *Y3* to voltage X-terminal respectively. The  $\alpha$  is the non-ideal current transfer gain from current X to current Z-terminal and the  $\gamma$  is the non-ideal trans-admittance transfer gain from voltage Z to current O-terminals.

Fig. 2.16: Equivalent circuit of DDCC with frequency-dependent gains

#### **2.2.4 Parasitic Effects**

In Fig. 2.17, the parasitic effects of DDCC are characterized by:

- R<sub>X</sub> is parasitic resistance that occurs at the X-terminal.

- R<sub>Y1</sub> // C<sub>Y1</sub>, R<sub>Y2</sub> // C<sub>Y2</sub> and R<sub>Y3</sub> // C<sub>Y3</sub> are parasitic impedances at Y<sub>1</sub>, Y<sub>2</sub> and Y<sub>3</sub>-terminals respectively.

- $R_Z // C_Z$  is parasitic impedance at Z-terminals.

- $R_O // C_O$  is parasitic impedance at O-terminals.

The passive component values including non-ideal parasitic resistances and impedances can be modified as:

$$Z_{I} = R_{YI} / (I/sC_{YI})$$

(2.21)

$$Z_2 = R_{Y2} // (1/sC_{Y2}) \tag{2.22}$$

$$Z_3 = R_{Y3} // (1/sC_{Y3}) \tag{2.23}$$

$$Z_4 = R_Z // (1/sC_Z)$$

(2.24)

$$Z_5 = R_0 / (1/Sc_0) \tag{2.25}$$

$$Z_5 = R_X \tag{2.26}$$

The parasitic at the X-terminal terminal ( $R_X$ ) is very low, the parasitic at Y terminals ( $R_Y$ ,  $C_Y$ ) very high, 20 fF, Parasitic at Z terminals ( $R_Z$ ,  $C_Z$ ) 218 k $\Omega$ , 35 fF, Parasitic at O- terminals ( $R_0$ ,  $C_0$ ) 324 k $\Omega$ , 20 Ff. The power consumption of the DDCC circuit is about 3.21 mW.

Fig. 2.17: Equivalent circuit showing parasitic elements in DDCCTA

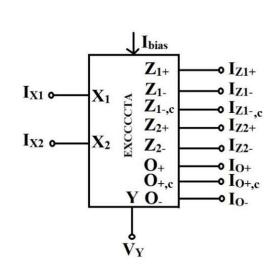

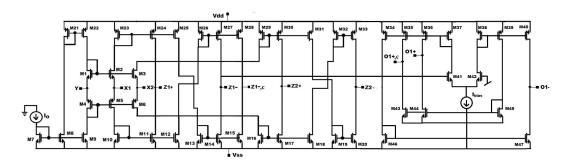

## 2.3 Extra-X Current Controlled Current Conveyor Trans-Conductance Amplifier (EX-CCCCTA)

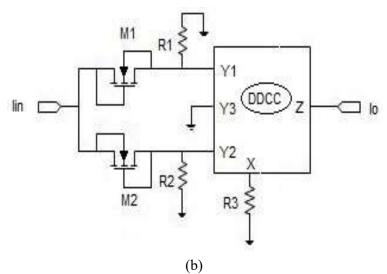

The Fig. 2.18 and Fig. 2.19 show the symbol and CMOS implementation of EX-CCCTA. It has nine terminals. EX-CCCII [11] transistors (M1-M33) comprise the

first stage. At the X<sub>1</sub> and X<sub>2</sub> nodes, the voltage that is applied at the Y node is shown. Nodes  $Z_{1\pm}$  and  $Z_{2\pm}$  receive the current input from node X<sub>1</sub> and node X<sub>2</sub>. The input current from the X<sub>1</sub> node flows to Z<sub>1+</sub> and Z<sub>1-</sub>, similarly, the input current from the X<sub>2</sub> node flows to Z<sub>2+</sub> and Z<sub>2-</sub> terminal current following operate independently of one another. The trans-conductance amplifier (TA) takes up the second stage and transistors (M34-M47) are used to implement. The voltage Z<sub>2-</sub> determines the output current of the TA. The output current I<sub>O+</sub> and I<sub>O-</sub> of the TA is provided by Eq. (2.27) if all transistors operate in the saturation and transistors M41 and M42 have equivalent W/L ratios. Table 2.3 shows transistor sizes for EX-CCCCTA.

$$\begin{bmatrix} I_{Y} \\ V_{X1} \\ V_{X2} \\ I_{Z1} \\ I_{Z2} \\ I_{0\pm} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 1 & R_{X1} & 0 & 0 \\ 1 & 0 & R_{X2} & 0 \\ 0 & \pm 1 & 0 & 0 \\ 0 & 0 & \pm 1 & 0 \\ 0 & 0 & 0 & \pm g_{m} \end{bmatrix} \begin{bmatrix} V_{Y} \\ I_{X1} \\ I_{X2} \\ V_{Z1} \end{bmatrix}$$

(2.27)

$$R_{X1} = R_{X2} = \frac{1}{\sqrt{8\mu C_{ox} \frac{W}{L} I_O}}$$

(2.28)

$$g_m = \sqrt{K_n \frac{W}{L} I_{bias}} \tag{2.29}$$

Where intrinsic resistances  $R_{X1}$  and  $R_{X2}$  are at terminals  $X_1$  and  $X_2$ ,  $I_0$  and  $I_{bias}$  are the bias currents of EX-CCCCTA, and,  $\mu$ ,  $C_{ox}$ , W, and L are the usual MOS transistor parameters.

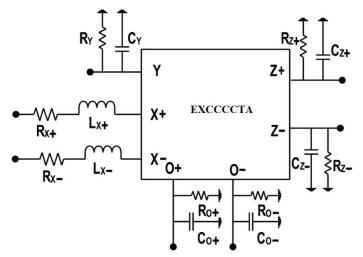

Fig. 2.18. Symbol of EX-CCCCTA [11]

Table 2.3 Transistor sizes for EX-CCCCTA [11]

| Transistors | Aspect ratio W (µm)/L (µm) |

|-------------|----------------------------|

| M1-M3       | 7.2/0.36                   |

| M4-M6       | 11.52/0.36                 |

| All PMOS    | 4.32/0.36                  |

| All NMOS    | 7.2/0.36                   |

Fig. 2.19: CMOS structure of EX-CCCCTA [11]

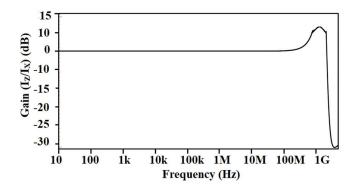

The simulation employs 0.18  $\mu$ m TSMC CMOS technology, with bias currents set at  $I_o = 10 \ \mu$ A,  $I_{bias} = 130 \ \mu$ A, and a supply voltage of ±1 V.

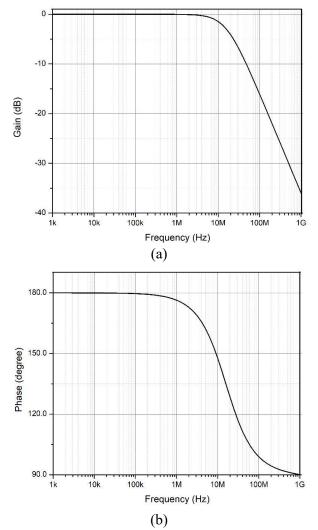

#### **2.3.1 AC Characteristics**

Fig. 2.20 plots the frequency response of current gains  $(I_Z/I_X)$ . The cutoff frequencies of the current gains obtained without load are about 2 GHz, and gains are unity at low frequencies.

Fig. 2.20: AC response of current at Z-terminals vs. current at X-terminal

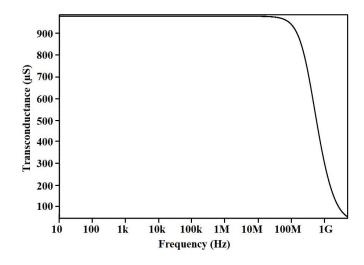

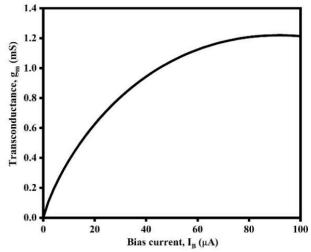

The bandwidth of the OTA which is found to be 330 MHz. The Fig. 2.21 gives the value of transconductance when the bias current is set at  $100\mu$ A which is found to be 984 $\mu$ S.

Fig. 2.21: Variation of transconductance with bias current

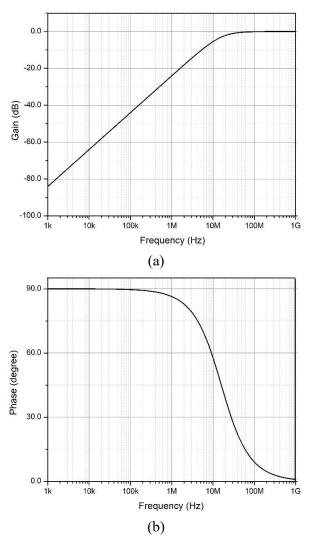

#### 2.3.2 DC Characteristics

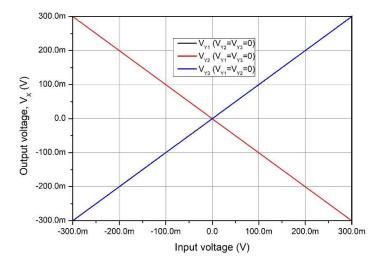

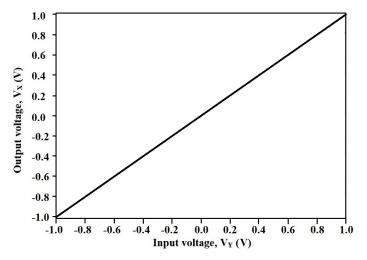

The DC voltage characteristics between the Y-terminals and X-terminal are presented in Fig. 2.22. The output voltages obtained to X-terminal  $V_X$  according to  $V_{Y1}$ ,  $V_{Y2}$  and  $V_{Y3}$  show a common dynamic range extended from -1 V to 1 V

Fig. 2.22: DC response of Voltage at Y-terminals vs. voltage at X-terminal

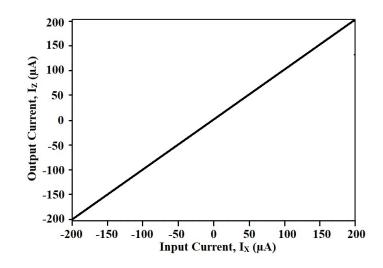

Fig. 2.23 shows the variation of output current  $I_Z$  versus the current  $I_X$ , with grounded Y terminals and a load resistance of about 1 k $\Omega$ . The current follower characteristic has a boundary linear range from -200  $\mu$ A to 200  $\mu$ A.

Fig. 2.23: DC response of Current at X-terminal vs. current at Z-terminal

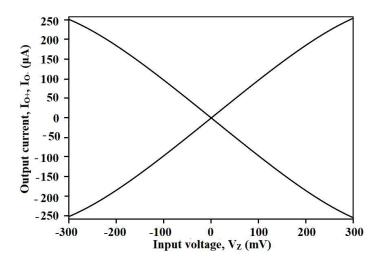

A voltage sweep of  $\pm 300$  mV is applied at the  $V_{Z1}$  node and the output current flowing from the O+ and O- nodes is plotted. The linear range of the OTA is  $\pm 200$  mV after this the output current began to saturate as can be inferred from Fig. 2.24.

Fig. 2.24: DC response of Current at O-terminal Vs voltage at Z-terminal

#### 2.3.3 Non-ideal Effects

A non-ideal model of EXCCCCTA is provided. Non-ideal frequency-dependent current and voltage transfer gains,  $\alpha_i(s)$  and  $\beta_i(s)$ , are the primary factors leading to deviations in frequency performance.  $\alpha_i(s) = \alpha_{0i}/(1 + s/\omega\alpha_i)$ , and  $\beta_i(s) = \beta_{0i}/(1 + s/\omega\beta_i)$ . Ideally,  $\alpha_{0i} = \beta_{0i} = 1$ , and  $\omega_{\alpha i} = \omega_{\beta i} = \infty$ . To account for non-ideal gains, modify the EXCCCCTA's V-I relations to  $I_Y = 0$ , with  $V_X = \beta(s)V_Y$ .  $I_{Z1+} = \alpha(s)I_{X1}$ ,  $I_{Z2+} = \alpha(s)I_{X2}$ ,  $I_{Z2-} = -\alpha(s)I_{X2}$ ,  $I_{O+} = \gamma g_m V_{Z1-}$ , and  $I_{O-} = -\gamma g_m V_{Z1-}$ .

#### **2.3.4 Parasitic Effects**

Fig. 2.25 shows an equivalent circuit showing parasitic elements in EX-CCCCTA. The performance of the X nodes can be defined as  $Z_X = R_X + sL_X$ .  $R_{Z+}$ ,  $R_{Z-}$ , and  $R_Y$  represent the parasitic resistance and capacitance of the Y and Z nodes, respectively. The corresponding capacitances are  $C_{Z+}$ ,  $C_{Z-}$ , and  $C_Y$ . The ideal values are equal to zero. The  $\gamma$  reflects the OTA's transconductance transfer inaccuracy, whereas  $R_0$  and  $C_0$  are parasitic at the output.

Fig. 2.25: Equivalent circuit showing parasitic elements in EX-CCCCTA [11]

# **Chapter 3**

# Single ABB-based Filter and Controller Designs

- S. Kumari and D. Nand, "DDCC-based MISO type voltage mode First-order Universal Filter," 2022 2nd International Conference on Intelligent Technologies (CONIT 2022), Hubli, India, 2022, pp. 1-6. https://doi.org/10.1109/CONIT55038.2022.9847828.

- 2. S. Kumari and D. Nand, "Realization of TAM-based PD, PI, PID Controllers Utilizing a Single DDCCTA for Closed-Loop System Applications", (2024).

### 3.1 Introduction

Audio amplifiers, equalizers, speaker systems, image processing, integrators, AC coupling, various control systems, radio systems, communication subsystems, and signal generators all demand first-order filters [6]. Some literature can find a dependable method for adjusting the phase of an input signal without disrupting the amplitude against frequency in communications. The applications of controllers are in industrial automation and process control, aerospace and automotive systems, power systems, and renewable energy [7]. PID controllers consist of three terms: The proportional term enhances the device's response time, the integral term improves steady-state error, and the derivative term increases the device's stability. A PD controller can improve the device's timing response. It allows the device to respond quickly while maintaining its steady-state error. A PI controller works effectively when process trends are fundamentally first-order. It can only enhance the device's steady-state response.

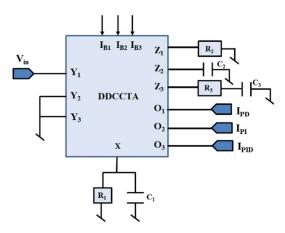

This chapter provides an in-depth study of two new circuit designs that use the Differential Difference Current Conveyor (DDCC) and its advanced variant, the Differential Difference Current Conveyor Transconductance Amplifier (DDCCTA). First, a novel voltage-mode first-order universal filter (FOUF) is shown, which uses a single DDCC, one resistor, and one capacitor to accomplish multiple-input, single-output (MISO) capabilities with low-pass, high-pass, and all-pass responses. Second, a novel Trans-admittance Mode (TAM) controller design is proposed, incorporating Proportional-Derivative (PD), Proportional-Integral (PI), and Proportional-Integral-Derivative (PD) control mechanisms via a DDCCTA with grounded capacitors and electronic tuning for control parameters. TAM functionality, the ability to operate PD, PI, and PID controllers simultaneously, and the analysis of non-idealities in DDCCTA performance are all key aspects. The study also investigates how the controller impacts the step response and gain-frequency characteristics with a closed-loop second-order filter system, demonstrating improved performance and practical application.

### 3.2 Literature review

A literature survey of filters is performed based on a few parameters such as mode of operation, grounded and floated passive components and their count, input/output impedance, total harmonic distortion (THD) [16, 17, 21, 23-26, 28-30], noise [16, 24, 25], power dissipation [16, 17, 23-26, 29, 30], and supply voltages. It is crucial, as it has been reported in [12-30] to use single analog building blocks (ABB) with a minimal number of passive components. Since the input/output impedances are so high [12-16, 20, 21, 27], the industry has recently focused on AABs with cascadable capabilities [15-22, 24-27, 30]. Multiple floating passive components have been employed in the literature [18-20, 23-27, 29]. All first-order filter responses i.e. low pass (LP), high pass (HP) and all-pass (AP) responses have been covered in [12, 13, 15, 17, 18, 23, 24, 27, 28, 30], and APF is frequently utilized as oscillators as reported in [12, 17, 20, 25-27]. A literature review where we have observed the following points: (i) The structures reported in [1,5,9,12-15,18,19] fall under the category of CM, whereas those reported in [2,7,17] belong to VM and TIM/TAM is reported in [14, 15, 12]17, 19, 21, 22, 27]. (ii) few literatures reported first-order filter topologies using single blocks such as DX MOCCII [12], DVCC [13, 17], CCIII [14, 22], FDCCII [15], MO DXCCTA [16], VDCC [18], CCCCDTA [20], DBTA [21], and some reported multiple blocks such as ICCII [23], CCII [24], DO CF [25], CDTA [26], OFCC [27], OTRA [28], and BJT [29, 30]. A first-order voltage-mode universal filter based on DDCC is proposed to cater above-mentioned limitations. The silent features of the proposed FOUF: (i) Employment of only one AAB. (ii) Used a minimal number of passive components. (iii) Low active or passive sensitivities. (iv) Used for low power and low voltage designs. (v) Used for high pole frequency (in MHz).

In the literature on controllers, a comparison of active block-based controllers such as CCII [31], DO-CCII [32], MO-CCCCTA [33], CCCDBA [34], CFOA [35, 39, 42], FDCCII [37], OTRA [38], DVCCTA [40], VDCC [41], CFTA [43], VCII [44, 46] and CCTA [45]. The PD, PI, and PID parameters can be selected dependently or independently in [31, 34, 37, 38, 40]. The CM-based controllers reported in [31, 32,

34, 36, 42, 46] and VM-based controllers reported in [31, 33, 35, 45], while the mixed mode is given in [36] including TIM and TAM topologies. With the above facts and features of the current mode block in literature, a controller using the DDCCTA block is investigated. This is the first proposal to use DDCCTA to develop a TAM-based PD, PI, and PID controller in one topology. The main highlights of the proposed design: (i) Using only one analog building block. (ii) Grounded capacitors are used. (iii) The PD, PI, and PID controller outputs are achieved in a single proposed topology. (iv) It can be electronically tuned and the output impedance is high.

### 3.3 Proposed designs using Single ABB

This section includes two proposed structures: The proposed filter circuit comprises of a single DDCC block, a single resistor, and a capacitor. The proposed controller comprises one DDCCTA active block, three resistors, and three grounded capacitors.

## 3.3.1 Proposed MISO-type VM-based first-order universal filter using DDCC Block

The proposed circuit, shown in Fig. 3.1, consists of a single DDCC block with a single resistor and capacitor. Table 3.1 shows the working principle of MISO-type filter responses. The output voltage obtained from the proposed circuit assuming the ideal DDCC is:

$$V_{0} = \frac{sRCV_{in2} - V_{in1}}{sRC + 1}$$

(3.1)

Fig. 3.1: Proposed circuit of the FOUF

| 0   | LPF |

|-----|-----|

| Vin | HPF |

| Vin | APF |

|     | Vin |

Table 3.1: Working principle of MISO type first-order universal filter

From the proposed circuit, various transfer functions are observed as follows:

$$\frac{V_O}{V_{in1}} = -\frac{\left(\frac{1}{RC}\right)}{s + \left(\frac{1}{RC}\right)} \qquad \text{For LPF}$$

(3.2)

$$\frac{V_O}{V_{in2}} = \frac{s}{s + \left(\frac{1}{RC}\right)}$$

For HPF (3.3)

$$\frac{V_O}{V_{in}} = \frac{s - \left(\frac{1}{RC}\right)}{s + \left(\frac{1}{RC}\right)}$$

For APF (3.4)

$$\omega = \frac{1}{RC}, f = \frac{1}{2\pi RC}$$

(3.5)

Phase for APF =

$$\pi - 2 \tan^{-1}(\omega RC)$$

(3.6)

### 3.3.1.1 Sensitivity Analysis

The first-order filter transfer function may alter as the component's value changes. The sensitivity results show how output responses vary depending on which circuit components are employed. The sensitivities of the proposed filter's output concerning various circuit components have been mathematically computed of APF to R, C.

$$S_R^{\omega} = S_C^{\omega} = -1 \tag{3.7}$$

#### 3.3.1.2 Non-idealities Analysis

In consideration of the non-ideal values of DDCC, the characteristic matrix can be rewritten as:

$$\begin{bmatrix} I_{Y1,2,3} \\ V_X \\ I_Z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ \beta_1 & -\beta_2 & \beta_3 & 0 \\ 0 & 0 & 0 & \pm \alpha \end{bmatrix} \begin{bmatrix} V_{Y1} \\ V_{Y2} \\ V_{Y3} \\ I_X \end{bmatrix}$$

(3.8)

$$V_X = \beta_1 V_{Y1} - \beta_2 V_{Y2} - \beta_3 V_{Y3} \tag{3.9}$$

$$I_Z = \pm \alpha I_X \tag{3.10}$$

Where  $\beta_1$ ,  $\beta_2$  and  $\beta_3$  are non-ideal voltage-transfer gains from Y1, Y2 and Y3 terminals to X terminal. The non-ideal current transfer gain from X to Z-terminal is  $\pm \alpha$ . Considering non-idealities, equations are modified as follows:

$$\frac{V_O}{V_{in1}} = \frac{-\left(\frac{\alpha}{RC}\right)}{s + \left(\frac{\beta_2 \alpha}{RC}\right)}$$

For LPF (3.11)

$$\frac{V_O}{V_{in2}} = \frac{s}{s + \left(\frac{\beta_2 \alpha}{RC}\right)}$$

For HPF (3.12)

$$\frac{V_O}{V_{in}} = \frac{s - \left(\frac{\alpha}{RC}\right)}{s + \left(\frac{\beta_2 \alpha}{RC}\right)}$$

For APF ( $V_{in1} = V_{in2} = V_{in}$ ) (3.13)

$$\omega = \frac{\beta_2 \alpha}{RC}, f = \frac{\beta_2 \alpha}{2\pi RC}$$

(3.14)

Phase for APF =

$$\pi - tan^{-1} \left(\frac{\omega RC}{\beta_2 \alpha}\right) - tan^{-1} \left(\frac{\omega RC}{\alpha}\right)$$

(3.15)

#### 3.3.1.3 Sensitivity for Non-ideal conditions

The sensitivities of the non-ideal condition of proposed filter outputs to circuit components and non-idealities have been mathematically obtained. The sensitivity of APF to R, C,  $\beta_2$ ,  $\alpha$ .

$$S_R^{\omega} = S_C^{\omega} = -\frac{1}{2} \; ; \; S_{\alpha}^{\omega} = S_{\beta_2}^{\omega} = \frac{1}{2}$$

(3.16)

#### **3.3.1.4 Parasitic effects**

The parasitic effects of DDCC are characterized by:

• R<sub>X</sub> is parasitic resistance that occurs at the X-terminal.

- R<sub>Y1</sub> // C<sub>Y1</sub>, R<sub>Y2</sub> // C<sub>Y2</sub> and R<sub>Y3</sub> // C<sub>Y3</sub> are parasitic impedances at Y<sub>1</sub>, Y<sub>2</sub> and Y<sub>3</sub>-terminals respectively.

- $R_Z // C_Z$  is parasitic impedance at Z-terminal.

The passive component values including non-ideal parasitic resistances and impedances can be modified as:

$$\frac{V_O}{V_{in1}} = \frac{-\left(\frac{1+SR_ZC+SR_ZC_Z}{C(1+R_ZC_Z)(R+R_X)}\right)}{s+\left(\frac{1+SR_ZC+SR_ZC_Z}{C(1+R_ZC_Z)(R+R_X)}\right)}$$

For LPF (3.17)

$$\frac{V_O}{V_{in2}} = \frac{s}{s + \left(\frac{1 + sR_Z C + sR_Z C_Z}{C(1 + R_Z C_Z)(R + R_X)}\right)} \qquad \text{For HPF}$$

(3.18)

$$\frac{V_O}{V_{in}} = \frac{s - \left(\frac{1 + sR_Z C + sR_Z C_Z}{C(1 + R_Z C_Z)(R + R_X)}\right)}{s + \left(\frac{1 + sR_Z C + sR_Z C_Z}{C(1 + R_Z C_Z)(R + R_X)}\right)}$$

For APF  $V_{in1} = V_{in2} = V_{in}$  (3.19)

$$Z' = \left(\frac{(1+R_Z C_Z)(R+R_X)}{1+sR_Z C+sR_Z C_Z}\right)$$

(3.20)

$$\frac{V_O}{V_{in}} = \frac{s - \left(\frac{1}{CZ'}\right)}{s + \left(\frac{1}{CZ'}\right)}$$

(3.21)

$$\omega = \frac{1}{CZ'} = \frac{(1 + SR_Z C + SR_Z C_Z)}{C(1 + R_Z C_Z)(R + R_X)}$$

(3.22)

Phase for APF =

$$\pi - 2 \tan^{-1} \left( \frac{\omega C (1 + R_Z C_Z) (R + R_X)}{(1 + s R_Z C + s R_Z C_Z)} \right) = \pi - 2 \tan^{-1} (\omega C Z')$$

(3.23)

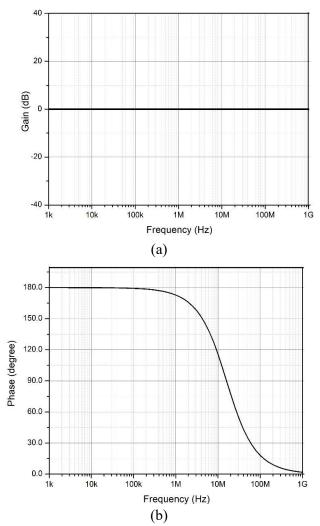

#### **3.3.1.5** Simulation results

The proposed FOUF filter is tested using PSPICE simulations obtained by 180 nm TSMC CMOS technology parameters. The supply voltages  $V_{DD} = V_{SS} = \pm 0.9$  V and a bias voltages  $V_b = -0.31$  V are used. In the proposed universal filter design input voltage is 3 mV applied, R=1 k $\Omega$ , C = 10 pF, angular frequency ( $\Omega$ ) is 100 MHz and the pole frequency (fc) is 15.9 MHz. The simulations of the low-pass gain and phase plot with  $V_{in1} = V_{in}$  and  $V_{in2} = 0$  are shown in Fig. 3.2(a) and Fig. 3.2(b) respectively, where the gain bandwidth of 15.85 MHz at -3dB, the phase of 134.82° are obtained through simulations and the theoretical value of phase is 135°. The high-pass gain and phase plot are simulated in Fig. 3.3(a) and Fig. 3.3(b) respectively, with  $V_{in1} = 0$  and  $V_{in2} = V_{in}$ , where the gain bandwidth of 16 MHz at -3dB, the phase of 44° is obtained

through simulations and theoretical value of phase is 45°. The all-pass gain and phase plot are simulated in Fig. 3.4(a) and Fig. 3.4(b) respectively, with  $V_{in1} = V_{in2} = V_{in}$ , where the gain bandwidth of 15.85 MHz at 0dB, the phase of 89.21° is obtained through simulations and the theoretical value of phase is 90°. The phase shifter for the all-pass filter response was configured for a 90-phase shift in Fig. 3.4(b) is 15.9 MHz observed.

Fig. 3.2: (a) Magnitude (b) Phase vs frequency plot of low-pass filter

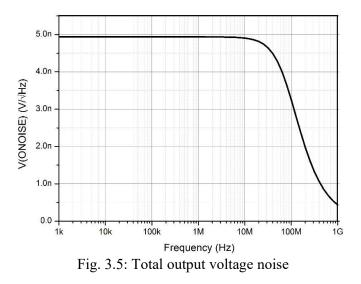

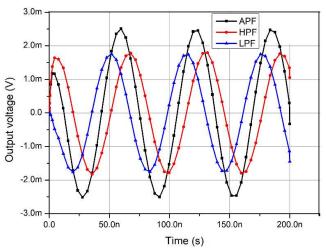

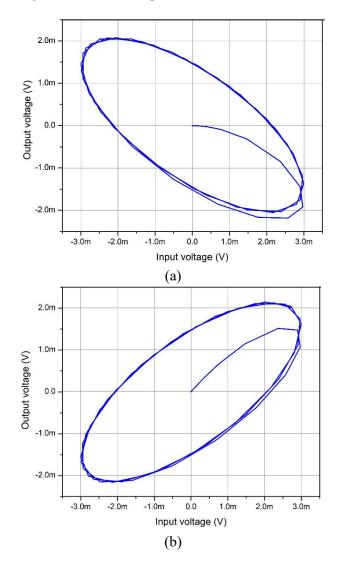

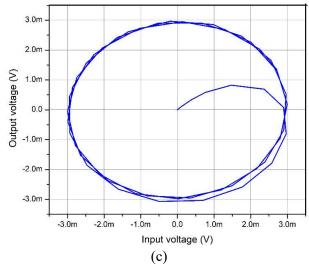

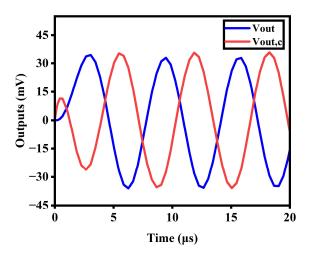

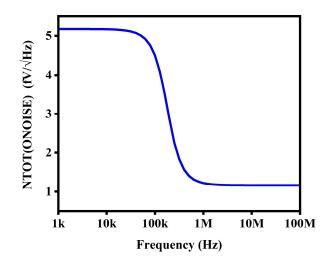

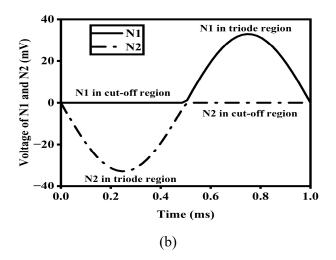

Fig. 3.5 shows the output noise is  $4.937nV/\sqrt{Hz}$ . Fig. 3.6 shows the transient response of LPF, HPF, and APF at 15.9 MHz when V<sub>in</sub> is 3 mV. The generated relationship of waveforms within the LPF, HPF and APF circuit has been verified by the Lissajous

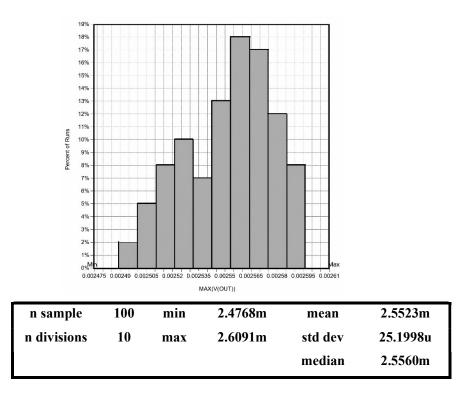

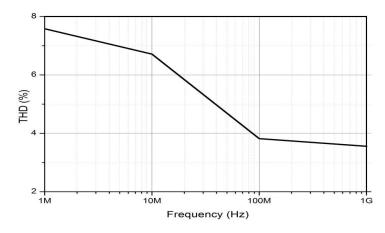

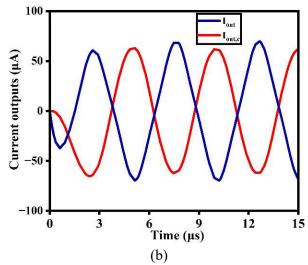

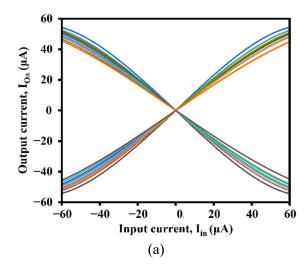

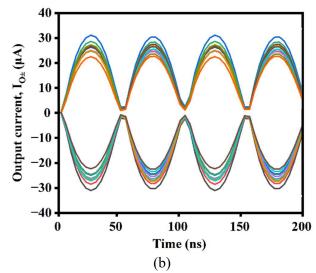

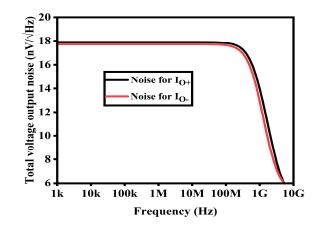

patterns shown in Fig. 3.7(a), Fig. 3.7(b), and Fig. 3.7(c) respectively. Fig. 3.8 shows the deviation in all-pass filter response through Monte Carlo simulations corresponds to  $\pm$  3% variation in R and C passive component values. We can observe that the mean value of maximum output voltage MAX(V(OUT) is 2.55mV, for 100 samples and 10 divisions. Fig. 3.9 shows the total harmonic distortions (THDs) of output voltage V<sub>o</sub> varies about 3-7% when center frequency varies from 1 MHz to 1 GHz.