## SELF-CONSISTENT LCAO-BASED DFT ANALYSIS OF FERROELECTRIC AND GATE MATERIAL ENGINEERED NEGATIVE CAPACITANCE FET FOR IMPROVED DEVICE-CIRCUIT PERFORMANCE

A Thesis Submitted In Partial Fulfillment of the Requirements for the degree of

## **DOCTOR OF PHILOSOPHY**

by

## **RASHI MANN**

(Roll No. 2K19/PHDAP/05)

Under the Supervision of

## **Prof. RISHU CHAUJAR**

Professor, Department of Applied Physics Delhi Technological University

Department of Applied Physics DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Shahbad Daulatpur, Main Bawana Road, Delhi-110042. India OCTOBER 2024 © Delhi Technological University-2024

All rights reserved.

## **Dedicated** to

My Parents

## Mrs. Nirmla Devi

## Å

## Mr. Roshan Mann

"All that I am, and all that I hope to be, I owe to my parent's love, guidance, and support"

## ACKNOWLEDGMENTS

Through my PhD journey, I have learned patience, resilience, and the power of perseverance. I have grown not only as a researcher but as an individual, learning to embrace uncertainty and face challenges head-on. This experience taught me the value of failure—it is in the setbacks that I discovered my strengths and found new ways to approach problems. This journey would have been impossible without the love and support of those around me. My family stood by me, encouraging me when I felt discouraged. My friends offered laughter and perspective when I needed it most. The guidance and mentorship of my supervisor was contributory, not only in my academic development but in navigating the many challenges of the PhD process.

First and foremost, I would like to express my deepest gratitude to my supervisor, **Prof. Rishu Chaujar**. Your unwavering support, encouragement, and belief in my abilities have been the pillars that sustained me throughout this PhD journey. You not only treated me with love and care but also strictly corrected me whenever I got sidetracked from my work, which has shaped me as a researcher and nurtured my personal growth and development. There were moments when I doubted myself, but your patience, wisdom, and constant reassurance gave me the strength to keep pushing forward. You've not only been an academic guide but also a mentor who has shaped my way of thinking and approaching challenges. For your invaluable feedback, for always making time for my questions, and for your kindness during the tough times, I am truly grateful. I couldn't have asked for a better supervisor, and I will always carry the lessons I've learned from you with me.

I am thankful to **Prof. Prateek Sharma** (Vice Chancellor, DTU) and **Prof. Vinod Singh** (HoD, Applied Physics, DTU) for providing the necessary resources to facilitate the research activity. I further thank the experts and SRC and DRC members **Prof. S.C Sharma** (chairman DRC), **Prof. R.S. Gupta** (External Expert), **Prof. Avinashi Kapoor** (External Expert), and **Prof. Poornima Mittal** (expert outside the department) for generously dedicating their valuable time to serve on my committee and providing their invaluable support of my thesis. Also, I thank all the faculty members of the Department for their helpful recommendations and advice during my Ph.D. journey. The journey of pursuing a PhD is a challenging and demanding effort that often requires the support and encouragement of good friends. I consider myself incredibly fortunate to developed meaningful friendships during my PhD. I want to thank **Dr. Vineet Sharma** for his support and encouragement. Receiving rejections from academic journals is an inevitable part of the research process, and it can be disheartening and discouraging. However, Vineet has always been there to uplift my spirits and motivate me. Thank you for walking this journey with me. I thank my dearest friend, **Viren**, a person who has loved me like an elder brother. His ability to listen and to always be there for me is the quality I cherish most in him. He has brought immeasurable joy and positivity into my PhD.

I would like to extend my heartfelt thanks to **Dr. Bhavya Kumar**, who has been more than just a senior, your support throughout this journey felt like that of an elder brother. From guiding me through the intricacies of research to offering words of wisdom when I needed them most, your presence has been a constant source of strength and reassurance. I'm deeply grateful for your kindness, and generosity, and for always being there when I needed guidance. I will definitely miss your storytelling sessions and the laughter we had on this journey. Also, I want to thank **Dr. Samriti Sharma** and **Dr. Megha Sharma, Dr. Mekonnen Getnet Yirak** for all the healthy discussions we had that have helped me get through this endeavor. Next, I want to thank, **Dr. Ankita Banwal** and **Yakshansh** who offered valuable advice for navigating the challenges in my professional and personal life. I deeply appreciate and cherish the friendship we share.

I would like to sincerely thank my juniors, Anshul, Yash, Ayushi, Kajal, Shubhdha, and Shikha for their support and assistance throughout this journey. Your enthusiasm, fresh perspectives, and willingness to help make a significant difference during some of the most challenging moments. Whether it was assisting with work, sharing ideas, or simply offering a friendly chat, your presence made the process more enjoyable and manageable. I'm proud to have worked alongside such talented and dedicated individuals, and I wish you all the best in your future endeavors. Among them, Anshul is a pure-hearted individual, who has been more like a younger sister than just a junior to me. Your positive energy has been such a blessing throughout this journey. Whether it was brainstorming ideas together, sharing late-night chat sessions, or simply being there to lift my spirits, you made this experience so much more bearable and enjoyable. You've always had my back, and your support has meant the world to me. I'm so grateful for your friendship and sisterly care—you're a big part of what got me through this. Thank you for everything.

Ayushi Lamba is a truly down-to-earth person who has no ill will toward anybody. She has a profound and genuine respect for me, and every time I ask for her assistance, she completes the tasks with remarkable ease. Also, I want to extend my heartfelt appreciation to my juniors, Yash Pathak, Kajal Verma, Shubhdha, and Shikha, for always respecting and admiring me. Cheers to the countless fun-filled moments we've shared in our lab, making my journey truly memorable and enjoyable. I'm grateful for everything you all have done and for the genuine friendship we've built along the way. Thank you for being an amazing junior.

I want to express my deepest gratitude to my wonderful husband, **Dr. Aashish Sangwan**. Your unwavering love, support, and understanding have been my anchor throughout this journey. You have been my biggest cheerleader, encouraging me during moments of self-doubt and celebrating every achievement, big and small. Your patience and belief in me made all the difference, allowing me to pursue my dreams with confidence. Thank you for standing by my side, for your motivational line "mujhe pta h, tu kar legi O", and for always knowing how to lift my spirits. I am so grateful to have you in my life, and I couldn't have done this without you.

I am profoundly grateful for the immense impact that my father, **Mr. Roshan Mann**, has had on my life. Words fall short of capturing the depth of my gratitude towards him. He has consistently supported and motivated me in every step of my life, instilling the confidence to pursue my dreams fearlessly. Because of you and Mommy, I am here to be called Dr. Rashi Mann. I also want to express my gratitude to my mother, **Mrs. Nirmla Devi**. She is the pillar of love and understanding in my life. Throughout my PhD journey, she has been my confidante, the one person with whom I can freely share my worries, doubts, and problems. Her unwavering support and comforting presence have provided me with the strength to face challenges head-on. I would like to extend my sincere gratitude to my fatherin-law, **Mr. Jasvir Sangwan** for your incredible support throughout my studies. Your wisdom, guidance, and kind words gave me the confidence to push forward and pursue my dreams. I am deeply grateful for your support, and I feel truly fortunate to have you in my life. I extend my thanks to my mother-in-law, **Dr. Urmila Sangwan**, whose love and care have been a constant source of comfort. Her presence in my life has been a blessing and I am grateful for her affectionate support. You make me believe that a mother-in-law can be a mother, which I was afraid of before marriage. I would also like to express my appreciation to my siblings Nidhi didi, Neeraj, Nitin, Aman, Robin, Vishwas, and Ashutosh. They have played a significant role in my life, providing both companionship and support. I would also like to thank my sister-in-law, Dr. Vineet Sangwan, and Priyanka, their adorable nature and positive energy have brought immense joy and relaxation. I would like to extend my heartfelt thanks to my niblings, Aayan, Milan, Manan, and Advik. Your laughter, joy, and unconditional love have been a constant source of happiness in my life. Thank you for being my biggest cheerleaders and for filling my life with happiness.

Last but not least, I would like to express my deepest gratitude to Lord Shiva for granting me health and strength throughout my journey. Your divine blessings have been a source of inspiration and resilience in my life. In moments of doubt and challenge, I found solace in your presence, which provided me with the courage to overcome obstacles. Thank you for the unwavering support and protection that guided me every step of the way. I am truly grateful for your blessings and grace.

### Rashi Mann

## **DELHI TECHNOLOGICAL UNIVERSITY**

(Established by Govt. of Delhi vide Act 6 of 2009) (Formerly Delhi College of Engineering) Shahbad Daulatpur, Bawana Road, Delhi- 110042

#### **CANDIDATE'S DECLARATION**

I <u>Rashi Mann</u> hereby certify that the work which is being presented in the thesis entitled <u>SELF-CONSISTENT LCAO-BASED DFT ANALYSIS OF FERROELECTRIC</u> <u>AND GATE MATERIAL ENGINEERED NEGATIVE CAPACITANCE FET FOR</u> <u>IMPROVED DEVICE-CIRCUIT PERFORMANCE</u> in partial fulfillment of the requirements for the award of the Degree of Doctor of Philosophy, submitted in the <u>Department of Applied Physics</u>, Delhi Technological University is an authentic record of my own work carried out during the period from <u>2019</u> to <u>2025</u> under the supervision of <u>Prof. Rishu Chaujar</u>.

The matter presented in the thesis has not been submitted by me for the award of any other degree of this or any other Institute.

#### **Candidate's Signature**

This is to certify that the student has incorporated all the corrections suggested by the examiners in the thesis and the statement made by the candidate is correct to the best of our knowledge.

Signature of Supervisor (s)

**Signature of External Examiner**

**Delhi Technological University**

(Govt. of National Capital Territory of Delhi) Bawana Road, Delhi-110042

## **CERTIFICATE BY THE SUPERVISOR(s)**

This is to certify that the thesis titled "Self-Consistent LCAO-based DFT Analysis of Ferroelectric and Gate Material Engineered Negative Capacitance FET for Improved Device-Circuit Performance" is being submitted by Ms. RASHI MANN with registration number 2K19/PHD/AP/05 to the Delhi Technological University for the award of the degree of Doctor of Philosophy in Physics. The work embodied in this thesis is a record of bonafide research work carried out by me in the Microelectronics Research Lab, Department of Applied Physics, Delhi Technological University (Formerly Delhi College of Engineering), New Delhi, under the guidance of PROF. RISHU CHAUJAR. It is further certified that this work is original and has not been submitted in part or fully to any other University or Institute for the award of any degree or diploma.

> Rashi Mann Roll No.2K19/PHD/AP/05

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

**Prof. Rishu Chaujar** Supervisor (Professor) Department of Applied Physics Delhi Technological University Delhi, India

**Prof. Vinod Singh** Head of Department Department of Applied Physics Delhi Technological University Delhi, India

Rashi Mann

## Self-Consistent LCAO-based DFT Analysis of Ferroelectric and Gate Material Engineered Negative Capacitance FET for Improved Device-Circuit Performance

This thesis explores the challenges associated with Negative Capacitance Field-Effect Transistors (NCFETs), an emerging technology that promises to overcome traditional CMOS devices' fundamental power efficiency limitations. NCFETs, by utilizing a negative capacitance effect in ferroelectric materials, offer a solution for lowering subthreshold swing (SS) beyond the thermionic limit, thus reducing power consumption in next-generation transistors. This research systematically investigates these problems through simulation-based approaches. A detailed analysis of ferroelectric materials used in NCFETs, such as Hafnium-based oxides, is presented to identify performance degradation factors. The study also proposes optimized device architectures and material compositions to mitigate these effects. The findings contribute to understanding NCFET limitations and offer pathways for overcoming these barriers, providing insights for further research in low-power semiconductor technologies.

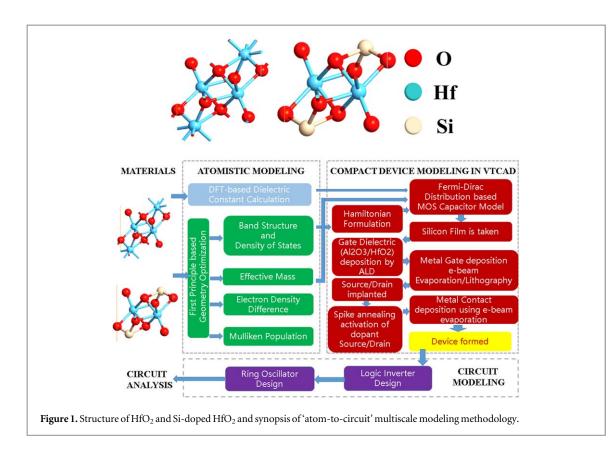

At this beginning, the effect of ferroelectric material on the substrate region is considered. The ferroelectric material is placed between the high-k HfO<sub>2</sub> layers in the conventional MOSFET's substrate, and this modified structure is termed FE-MOSFET. A study of the analog and RF parameters was investigated. The VISUAL TCAD simulator does all the simulation work. Then, the Quantum ATK simulator examines the reliability of silicon-doped HfO<sub>2</sub> as a ferroelectric material with different concentrations of silicon. The DFT analysis comparison of hafnia and 1Si-HfO<sub>2</sub> and 2Si-HfO<sub>2</sub> is done. DFT analysis contains the band structure and PDOS data corresponding to different materials. The effect of this 2Si-HfO<sub>2</sub> as a ferroelectric material is taken into account on the performance parameters of MOSFET, and the modified device with 2Si-HfO<sub>2</sub> as a ferroelectric in gate stack and high-k HfO<sub>2</sub> in substrate region is termed as Modified NCFET. Further, to ensure the device's

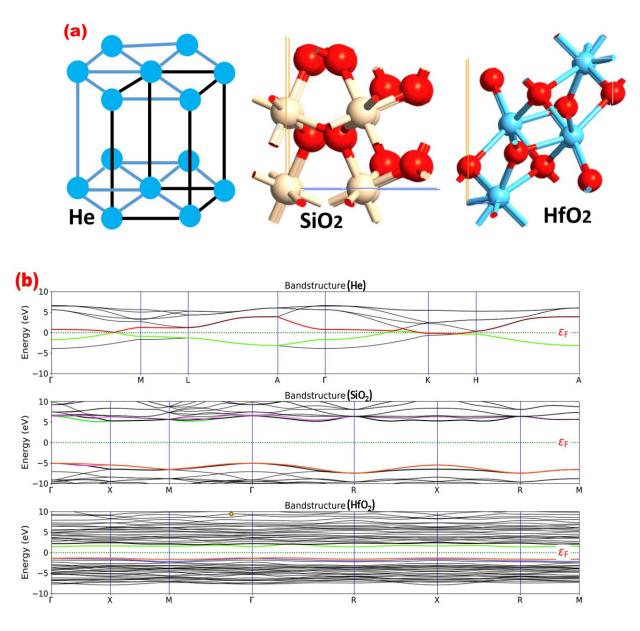

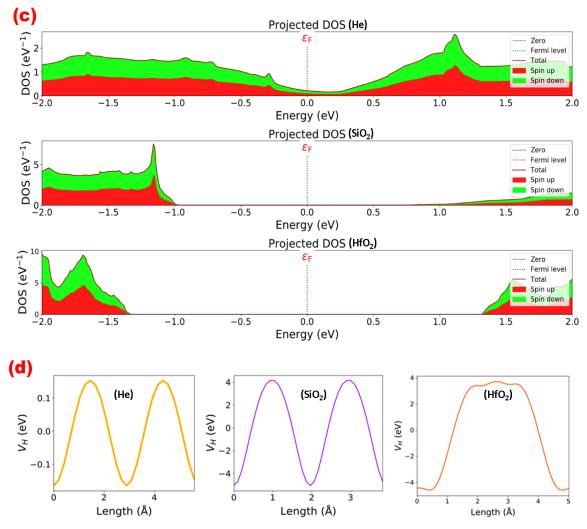

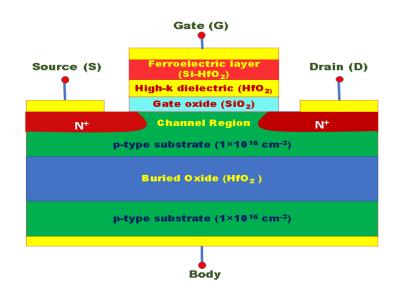

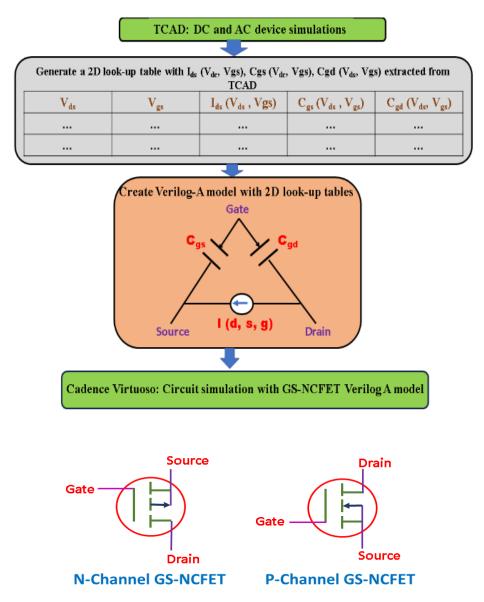

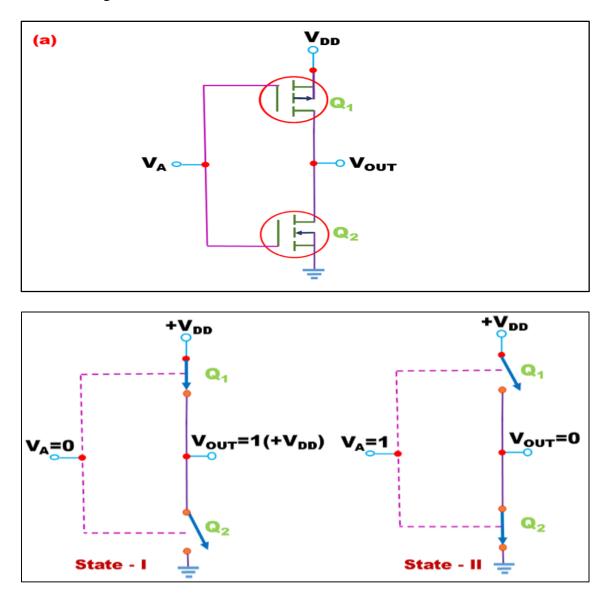

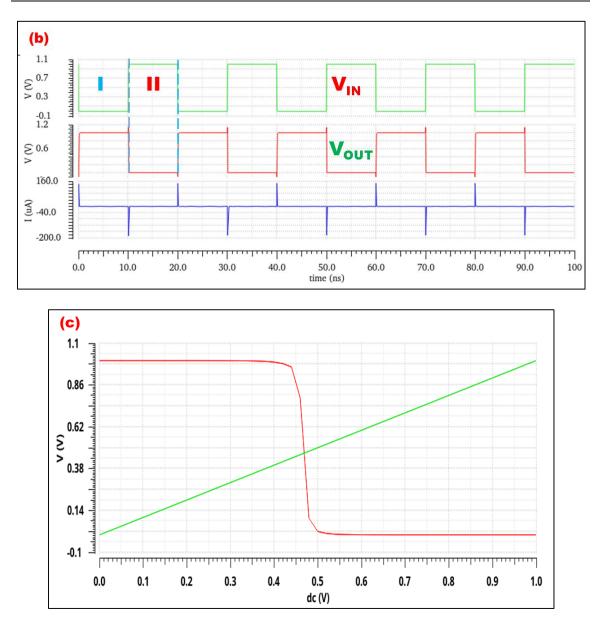

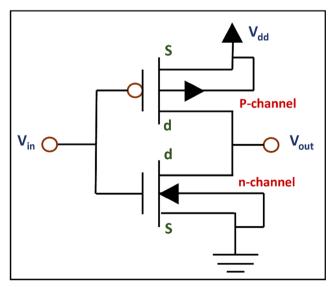

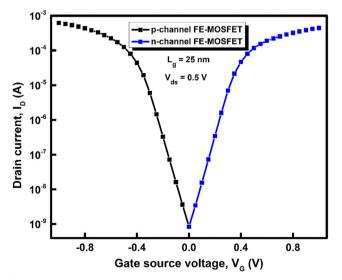

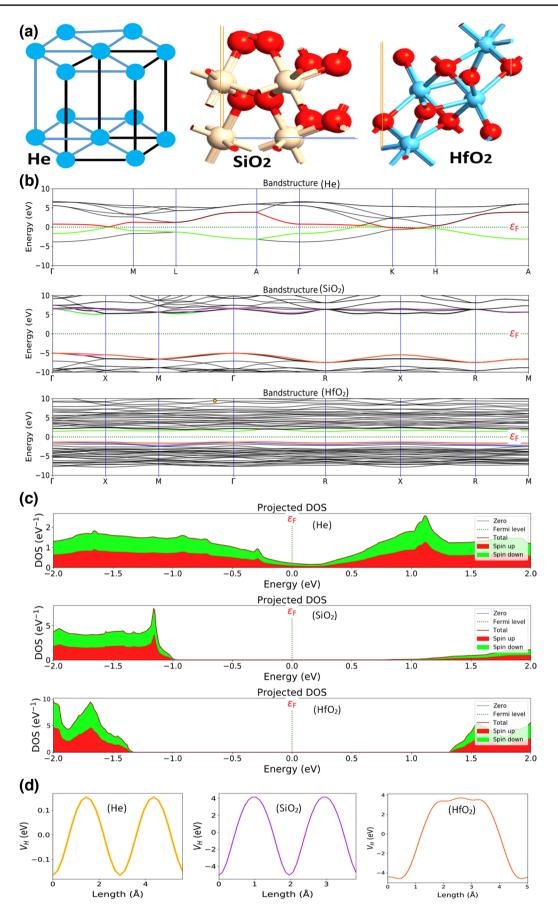

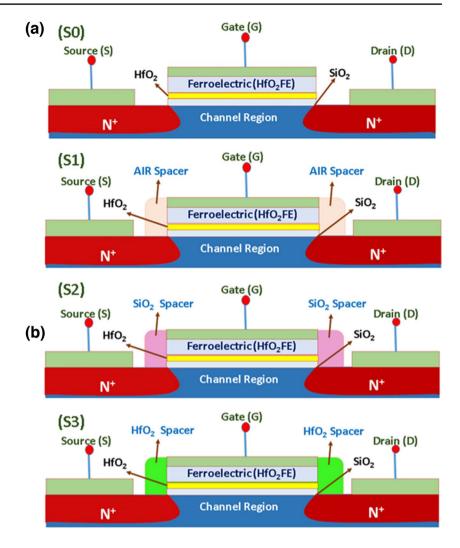

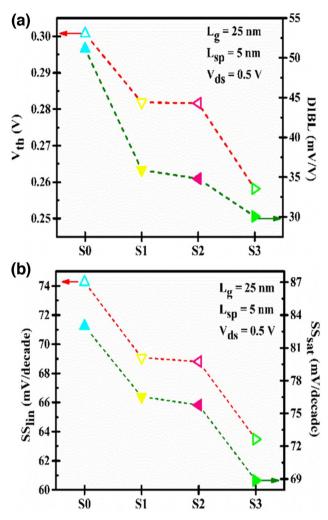

reliability, it is crucial to explore its characteristics, and the temperature variations taken into account. The performance parameter comparison of Modified NCFET is done with the conventional NCFET structure. Moreover, the impact of the high-k spacers on the analog/RF and inverter-based parameter performance of Gate-Stacked NCFET (Modified NCFET) is examined. Spacer materials are HfO<sub>2</sub>, SiO<sub>2</sub>, and helium (due to the unavailability of air molecule structure in the quantum ATK database, we investigate the structural properties of helium (k=1.000074 at  $0^{0}$  C and 1atm), which has nearly the same dielectric constant of air (k=1).) Self-consistent LCAO-based DFT analysis is done for the spacer materials regarding band structure, PDOS, and Hartree potential. Four configurations are simulated for this analysis, defined as GS-NCFET with no spacer (S0), GS-NCFET with AIR spacer (S1), GS-NCFET with SiO<sub>2</sub> spacer (S2), GS-NCFET with HfO<sub>2</sub> spacer (S3). After analyzing the electrical properties of the proposed device (GS-NCFET), the device modelling is done using the VISUALFAB simulator. The Cadence Virtuoso tool creates two symbols corresponding to N-GS-NCFET and P-GS-NCFET. Then, the digital application of GS-NCFET is shown as NAND, NOR, and NOT logic gates. It was found that the digital applications of GS-NCFET in terms of logic gates show the device is working properly with expected input-output curves.

Thus, GS-NCFET can be considered a promising candidate for use in low-power, analog, RF, and high-performance CMOS circuits due to its high switching ratio, lower leakage current, better reliability in terms of temperature, and superior static, analog, and RF performance, suppressed SCEs and parasitic capacitances.

### **PUBLICATIONS RESULTING FROM THIS THESIS WORK**

### ARTICLES IN INTERNATIONAL REFEREED JOURNALS (4):

- 1. **R. Mann** and R. Chaujar, "TCAD investigation of ferroelectric-based substrate MOSFET for digital application," *Silicon*, vol. 14, pp. 5075-5084, 2022. (**IF 2.8**)

- R. Mann and R. Chaujar, "DFT-based Atomic Calculation of Si-doped HfO<sub>2</sub> and Effect of its Negative Capacitance on Analog/RF, and VTC parameters of MOSFET," *Silicon*, vol. 16, pp. 1237-1252, 2024. (IF – 2.8)

- **3. R. Mann** and R. Chaujar, "DFT-based Atomic Modeling and Temperature Analysis on the RF and VTC curve of high-k dielectric layer-assisted NCFET," *Physica Scripta* vol. 99, pp. 015029, 2024. (**IF 2.6**)

- 4. **R. Mann** and R. Chaujar, "Self-Consistent LCAO Based DFT Analysis of Highk Spacers and its Assessment on Gate-Stacked NCFET for Improved Device-Circuit Performance," *Silicon*, 2024. (IF – 2.8)

- 5. **R. Mann** and R. Chaujar, "Device and Circuit-level assessment of Gate Stacked NCFET for digital applications,"IEEE Transaction on circuit and systems-1(communicated).

#### **ARTICLES PRESENTED IN INTERNATIONAL CONFERENCES (7):**

- R. Mann, R. Chaujar, "A Comparative Investigation on Characteristics of Conventional MOSFET and Ferroelectric Thin Film Modified FET"," 2021 Devices for Integrated Circuit (DevIC 2021), Kolkata, India, pp. 53-56, 2021, doi: 10.1109/DevIC50843.2021.9455861.

- R. Mann, R. Chaujar, "Electrostatic Analysis of Ferroelectric and High dielectric layer assisted MOSFET"2021 7th International Conference on Signal Processing and Communication (ICSC), Noida, India, pp. 321-324, 2021, doi: 10.1109/ICSC53193.2021.9673258.

- R. Mann, R. Chaujar, "Temperature Analysis on Short Channel Effects of Modified NCFET: A Simulation Study," *8th International Conference on electronics, computing, and communication technologies, IEEE CONECCT*, Banglore, pp. 1-5, doi: 10.1109/CONECCT55679.2022.9865782, 2022.

- 4. R. Mann, R. Chaujar, "Impact of high-k spacers on the switching and VTC characteristics of Gate-Stacked NCFET," *10th International Conference on 'Microelectronics, Circuits and Systems', MICRO2023, Assam, India, 2023.*

- R. Mann, R. Chaujar, "Impact of LCAO-DFT analysed Si-HfO<sub>2</sub> on GS-NCFET with its Digital Application," *19th IEEE International Conference on*  '*Nano/Micro Engineered and Molecular Systems'*, *NEMS2024*, Kyoto, Japan, pp. 1-4, 2024, doi: 10.1109/NEMS60219.2024.10639839.

- 6. Y. Pathak, R. Mann, B. D. Malhotra and R. Chaujar, "Impact of Temperature on

Negative Capacitance FET: A TCAD Simulation Study," *2023 2nd Edition of IEEE Delhi Section Flagship Conference (DELCON)*, Rajpura, India, pp. 1-4, 2023, doi: 10.1109/DELCON57910.2023.10127565.

7. R. Mann, A. Narwal, R. Chaujar, "DFT based analysis of HfO2 layer assisted NCFET for Linearity Performance" 2024 Asia-Pacific Microwave Conference, APMC 2024, Bali, Indonesia, 2024.

## TABLE OF CONTENTS

| Ackno   | wledgm   | ents                               | i          |

|---------|----------|------------------------------------|------------|

| Candi   | date's D | Declaration                        | <i>v</i>   |

| Certif  | icate by | the supervisor(s)                  | vi         |

| Abstra  | act      |                                    | <i>vii</i> |

| List of | f Public | ations                             | <u>ix</u>  |

| Table   | of Cont  | ents                               | <i>xi</i>  |

|         | U        |                                    |            |

|         |          |                                    |            |

| Lisi Oj | rigure   | <i>S</i>                           |            |

| Снар    | TER 1: ] | INTRODUCTION                       | 1          |

| 1.1     | Backg    | round                              | 2          |

| 1.2     | Thesis   | Objectives                         | 4          |

| 1.3     | Schem    | e of Chapters                      | 5          |

| 1.4     | Refere   | nces                               | 10         |

| Снар    | TER 2: ] | LITERATURE SURVEY                  | 12         |

| 2.1 Sc  | aling of | f MOSFET                           | 13         |

|         | 2.1.1    | Dennard Scaling and the Golden Era | 13         |

| 2.2 Sh  | nort-Cha | nnel Effects                       | 15         |

|         | 2.2.1    | Drain-Induced Barrier Lowering     | 15         |

|         | 2.2.2    | Surface Scattering                 | 15         |

|         | 2.2.3    | Threshold Voltage (Vth) Roll-off   | 16         |

|         | 2.2.4    | Impact Ionization                  | 16         |

|         | 2.2.5    | Hot-Carrier Effects                | 17         |

| 2.3     | Ways     | to Overcome Short-Channel Effects  | 18         |

|         | 2.3.1    | Engineering Schemes                | 19         |

|         |          | 2.3.1.1 Junctionless Engineering   | 19         |

|         |          | 2.3.1.2 Gate Engineering           | 20         |

|         |          | 2.3.1.3 Dual-k Spacer Engineering  | 12         |

|     | 2.3.2  | Device Concepts                                 | 22 |

|-----|--------|-------------------------------------------------|----|

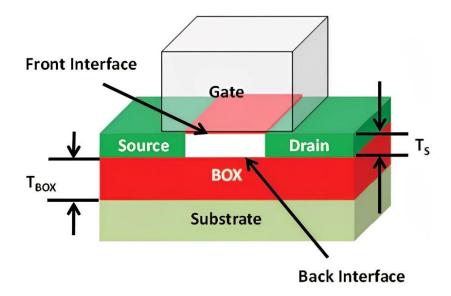

|     |        | 2.3.2.1 Silicon-on-Insulator MOSFET             | 22 |

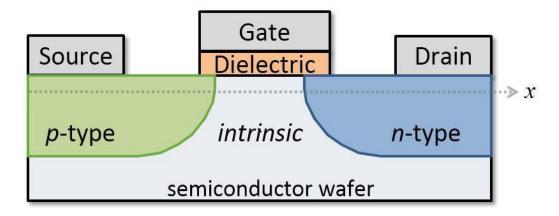

|     |        | 2.3.2.2 Tunneling Field Effect Transistor       | 23 |

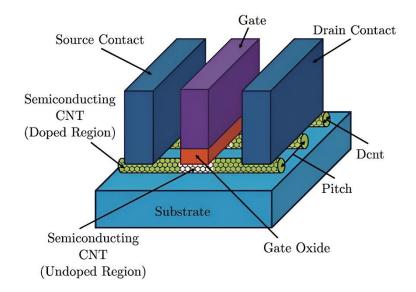

|     |        | 2.3.2.3 Carbon Nanotube Field Effect Transistor | 24 |

| 2.4 | Resear | rch Gaps                                        | 25 |

| 2.5 | Possib | ele Solution - NCFET                            | 26 |

|     | 2.5.1  | Development and Prospects of NCFETs             | 26 |

|     | 2.5.2  | Experimental Evidence of Negative Capacitance   | 28 |

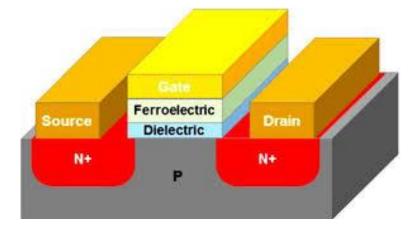

|     | 2.5.3  | NCFET Classification                            | 29 |

|     | 2.5.4  | Advantages of NCFET                             | 32 |

|     | 2.5.5  | Challenges Confronted by NCFET                  | 33 |

| 2.6 | Refere | ences                                           | 34 |

|       |          | TCAD INVESTIGATION OF FERROELECTRIC ASSISTED SUB<br>LICATION |    |

|-------|----------|--------------------------------------------------------------|----|

| 3.1 I | ntroduct | ion                                                          |    |

| 3.2 E | Device D | Design and Physical Models                                   | 42 |

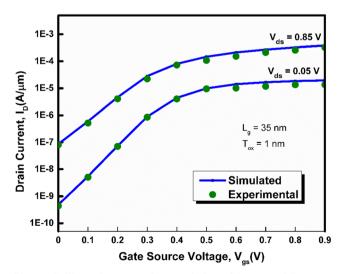

| 3.3   | Calibi   | ration                                                       | 45 |

| 3.4   | Fabric   | cation Feasibility                                           | 46 |

| 3.5   | Resul    | ts and Discussion                                            | 47 |

|       | 3.5.1    | Device Scalability                                           | 47 |

|       | 3.5.2    | Analog metrics                                               | 49 |

|       | 3.5.3    | RF Analysis                                                  |    |

|       | 3.5.4    | Application of FE-MOSFET                                     | 56 |

|       |          | 3.5.4.1 Noise Margin calculation                             | 57 |

| 3.6   | Sumn     | nary                                                         | 58 |

| 3.7   | Refer    | ences                                                        | 60 |

## CHAPTER 4: DFT-BASED ATOMIC CALCULATION OF SI-HFO2 AND IMPACT OF NEGATIVE CAPACITANCE ON ANALOG/RF, AND VTC PARAMETERS OF MOSFET....64

| 4.1 Int | roduction                       | .65 |

|---------|---------------------------------|-----|

| 4.2 De  | vice Design and Physical Models | .69 |

| 4.3     | Results and Discussion          | .74 |

|     | 4.3.1  | DFT-based Atomic Calculation of Hafnium Oxide (HfO <sub>2</sub> )                  | 74 |

|-----|--------|------------------------------------------------------------------------------------|----|

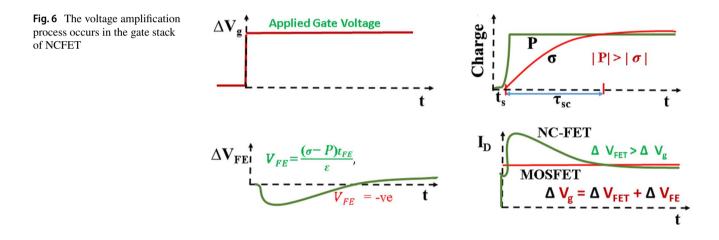

|     | 4.3.2  | Voltage Amplification and SCEs in Modified NCFET over MOSFET                       | 76 |

|     | 4.3.3  | Analog/RF metrics                                                                  | 79 |

|     | 4.3.4  | Comparison of Conventional MOSFET-based inverter and Modified NCFET-based inverter | 85 |

| 4.4 | Summ   | ary                                                                                | 89 |

| 4.5 | Refere | ences                                                                              | 90 |

####

| 5.1 Int | roducti | on                                                                                           | 95 |

|---------|---------|----------------------------------------------------------------------------------------------|----|

| 5.2 De  | evice D | esign and Physical Models                                                                    | 98 |

| 5.3     | Result  | s and Discussion1                                                                            | 02 |

|         | 5.3.1   | DFT-based Atomic Calculation of Hafnium Oxide (HfO <sub>2</sub> ) and Si-HfO <sub>2</sub> .1 | 02 |

|         | 5.3.2   | SCEs analysis between conventional NCFET and Modified NCFET1                                 | 07 |

|         | 5.3.3   | Analog/RF Performance Metrics at different temperatures10                                    | 98 |

|         | 5.3.4   | Temperature impact on the VTC curve of Modified NCFET-based inverted                         |    |

|         |         | 5.3.4.1 Noise Margin Calculation1                                                            | 16 |

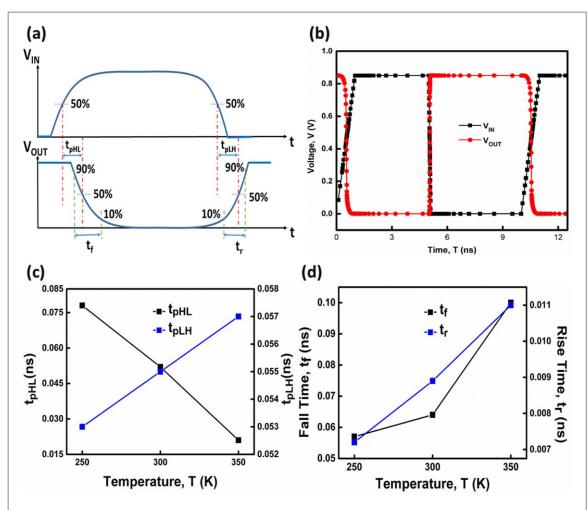

|         |         | 5.3.4.2 Propagation Delay and Transition Time                                                | 16 |

| 5.4     | Summ    | ary1                                                                                         | 19 |

| 5.5     | Refere  | ences12                                                                                      | 20 |

####

| 6.1 Introducti | ion                                                         | .127 |

|----------------|-------------------------------------------------------------|------|

| 6.2 LCAO-ba    | ased DFT calculation for spacers                            | .129 |

| 6.3 Device A   | rchitecture and Physical Models                             | .133 |

| 6.4 Results ar | nd Discussion                                               | .135 |

| 6.4.1          | Comparison of conventional NCFET and GS-NCFET               | .135 |

| 6.4.2          | Effect of spacers on switching profile and SCEs of GS-NCFET | .137 |

| 6.4.3          | RF/analog parameters of spacers-based GS-NCFET              | .139 |

| 6.4.4          | Effect of spacers on linearity parameters of GS-NCFET       | .142 |

| 6.4.5          | Effect of spacers on parameters of GS-NCFET-based inverter  | .144 |

| 6.5 | Summary    | 145 |

|-----|------------|-----|

| 6.6 | References | 147 |

|          |         | Device and Circuit-level Assessment of Gate Stacked NCFET | -   |

|----------|---------|-----------------------------------------------------------|-----|

| 7.1 Inti | oducti  | on                                                        |     |

| 7.2 De   | vice A1 | rchitecture and Physical Models                           | 155 |

| 7.3      | Result  | s and Discussion                                          | 157 |

|          | 7.3.1   | Comparison of Conventional NCFET and GS-NCFET             |     |

|          | 7.3.2   | Device-to-circuit modeling                                | 159 |

|          | 7.3.3   | Digital Application of GS-NCFET                           | 161 |

|          |         | 7.3.3.1 GS-NCFET-based NOT GATE                           | 161 |

|          |         | 7.3.3.2 GS-NCFET-based NAND GATE                          | 164 |

|          |         | 7.3.3.3 GS-NCFET-based NOR GATE                           | 166 |

| 7.4      | Summ    | ary                                                       | 167 |

| 7.5      | Refere  | ences                                                     |     |

| CHAPTER 8: CONCLUSION AND FUTURE SCOPE |     |

|----------------------------------------|-----|

| 8.1 Conclusion                         | 173 |

| 8.2 Future Scope                       | 179 |

## **REPRINTS OF JOURNAL PUBLICATIONS**

## LIST OF TABLES

| Table 3.1: Different device configurations used for simulation                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.2: Summary of electrostatic and analog parameters for different structures    51                                                               |

| Table 3.3: Summary of RF parameters for different Structures    55                                                                                     |

| Table 3.4: Summary of inverter-based parameters for different structures    58                                                                         |

| Table 4.1: Different device configurations used for simulation                                                                                         |

| Table 4.2: Comparison of SCEs in conventional MOSFET and Modified NCFET       78                                                                       |

| Table 4.3: Summary of the analog parameter of conventional MOSFET and Modified NCFET                                                                   |

| Table 4.4: Noise margin comparison between inverters using Modified NCFETs and Conventional         MOSFETs                                            |

| Table 5.1: Default device dimensions and parameters of conventional NCFET and Modified NCFET         structure are taken for the simulation         10 |

| Table 5.2: Variation of SCEs with the impact of temperature                                                                                            |

| Table 5.3: Summary of analog and RF performance parameters of Modified NCFET with different temperatures                                               |

| Table 5.4: Comparison of noise margin and propagation delay for different temperatures of Modified         NCFET-based inverters         118           |

## LIST OF FIGURES

| Figure 1.1: Log plot of transistor counts per microprocessor against calendar years                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Expected steep slope less than 60 mV/dec at room temperature for an NC-FET                                                                                                                                                                         |

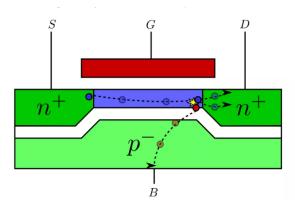

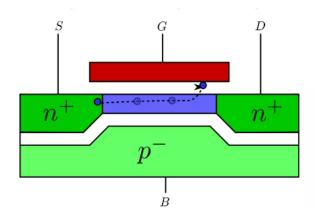

| Figure 2.1: Drain-Induced Barrier Lowering15                                                                                                                                                                                                                   |

| Figure 2.2: Surface Scattering16                                                                                                                                                                                                                               |

| Figure 2.3: Impact Ionization17                                                                                                                                                                                                                                |

| Figure 2.4: Hot Carrier Effects in NMOS17                                                                                                                                                                                                                      |

| Figure 2.5: Different ways to overcome SCEs in nano-scale MOSFET18                                                                                                                                                                                             |

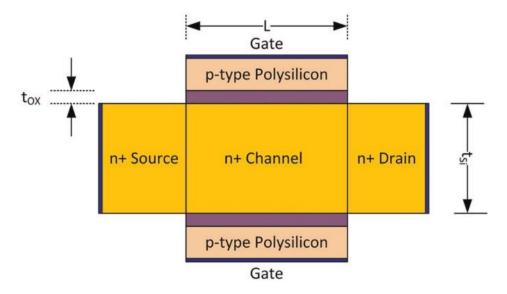

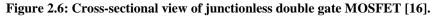

| Figure 2.6: Cross-sectional view of junctionless double gate MOSFET                                                                                                                                                                                            |

| Figure 2.7: Schematic structure of dual material gate MOSFET                                                                                                                                                                                                   |

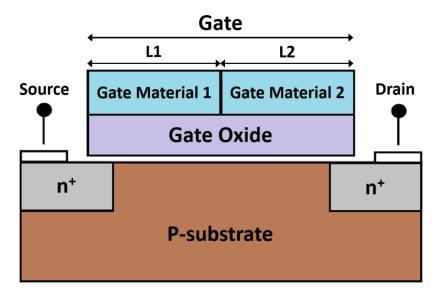

| Figure 2.8: Schematic FinFET structure with dual-k underlap spacers                                                                                                                                                                                            |

| Figure 2.9: Schematic structure of FD-SOI MOSFET                                                                                                                                                                                                               |

| Figure 2.10: Schematic lateral structure of TFET                                                                                                                                                                                                               |

| Figure 2.11: Schematic structure of CNTFET device                                                                                                                                                                                                              |

| Figure 2.12: Schematic image of an NC-FET with ferroelectric and conventional dielectric as the gate stack                                                                                                                                                     |

|                                                                                                                                                                                                                                                                |

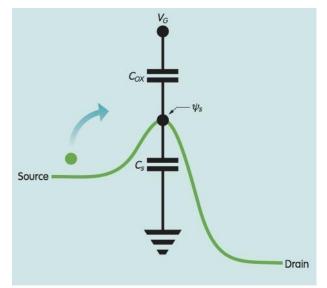

| Figure 2.13: Gate is coupled to channel potential $\psi_s$ by a capacitive network                                                                                                                                                                             |

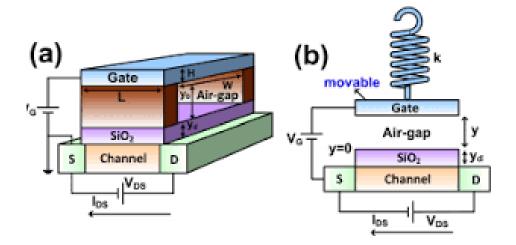

| Figure 2.14: Suspended gate and ideal logic switch (a) suspended gate NCMOS with a nanomechanical spring (b)2D view of the suspended gate                                                                                                                      |

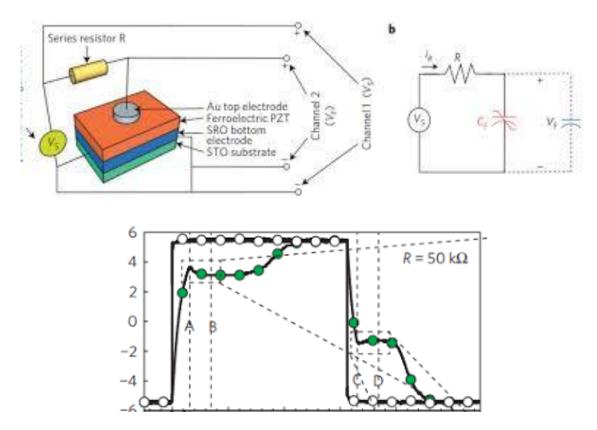

| Figure 2.15: Verification of negative capacitance (a) Ferroelectric capacitor connected in series with a resistor to demonstrate NC effect (b) Resistance hinders the flow of screening charges, which results in a transient NC effect between points A and B |

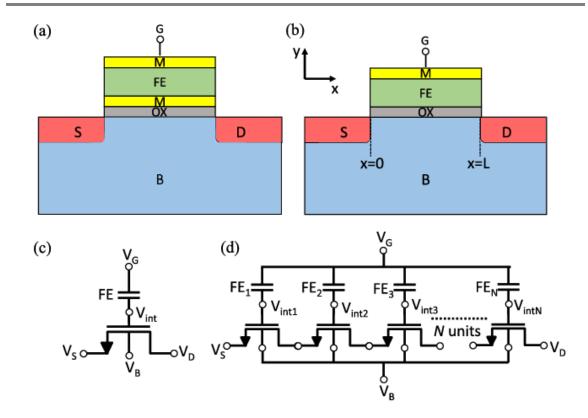

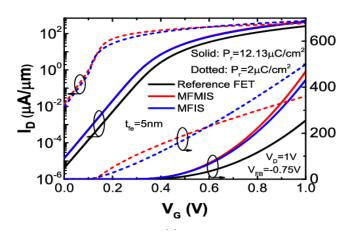

| Figure 2.16: Structural comparison between (a) MFMIS and (b) MFIS (c) MFMIS and (d) MFIS30                                                                                                                                                                     |

| Figure 2.17: Comparison of I <sub>d</sub> –V <sub>g</sub> of MFMIS and MFIS NCFETs for different remnant polarization values                                                                                                                                   |

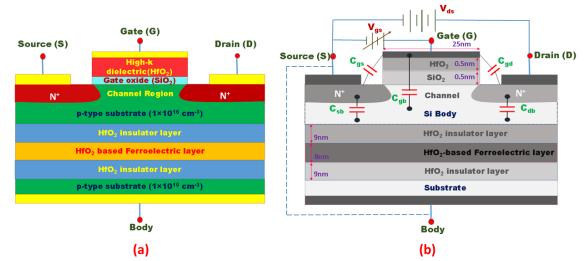

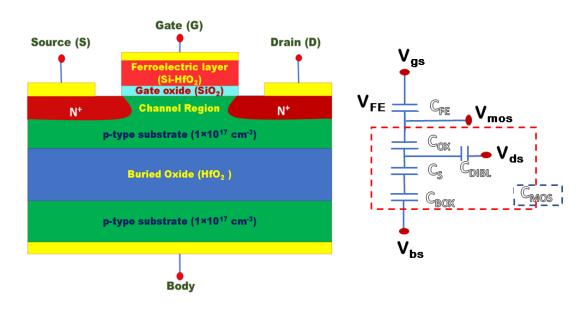

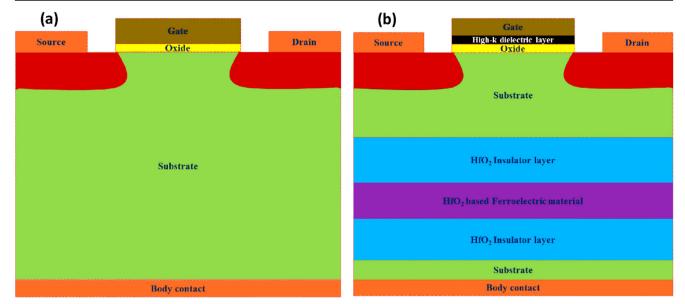

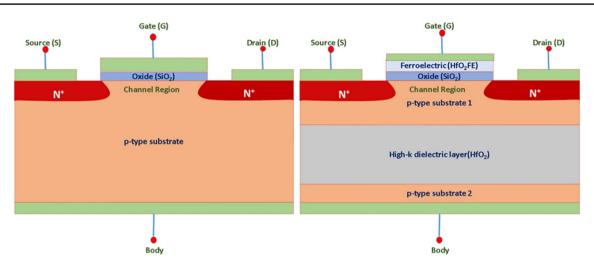

| Figure 3.1: (a) Proposed FE-MOSFET structure, (b) Cross-section view and capacitance representation of the device                                                                                                                                              |

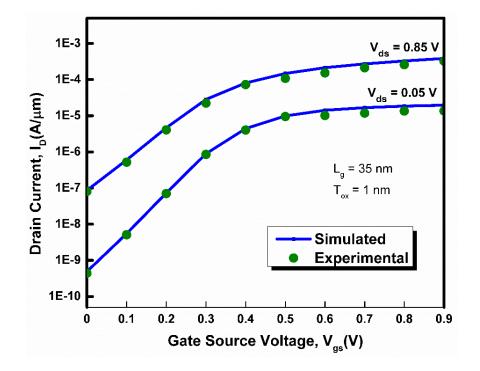

| Figure 3.2: Experimental and simulated transfer characteristics of the MOSFET45                                                                                                                                                                                |

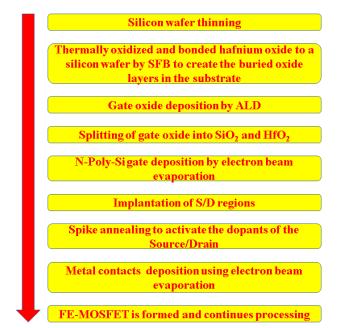

| Figure 3.3: FE-MOSFET step-by-step fabrication outline                                                                                                                                                                                                         |

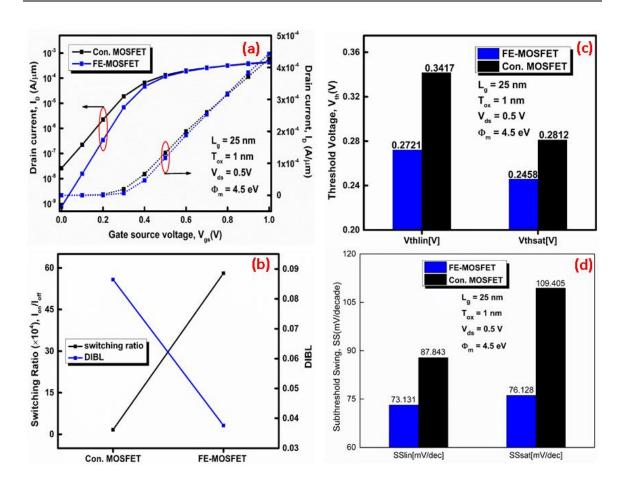

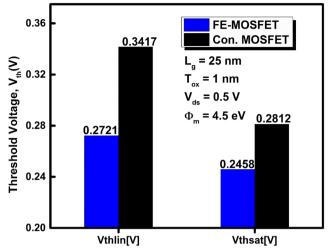

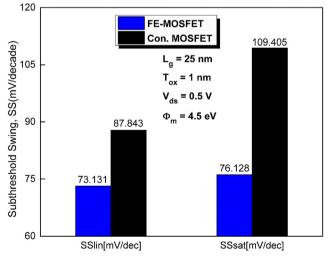

| Figure 3.4: (a) Variation of $I_d$ - $V_{gs}$ in linear and log scales, (b) $I_{on}/I_{off}$ ratio and DIBL, (c) $V_{th}$ , and (d) SS comparisons for different configuration                                                                                 |

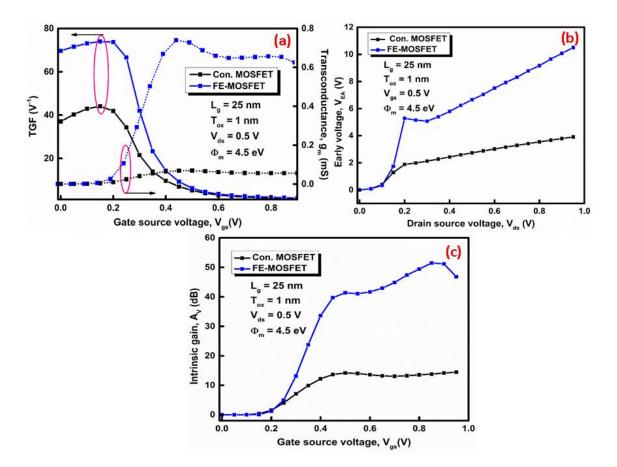

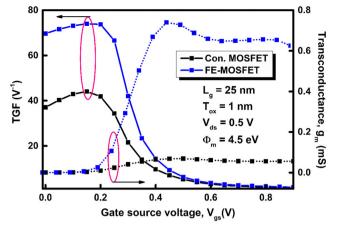

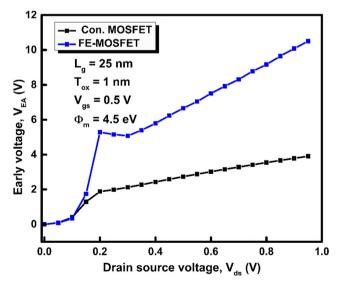

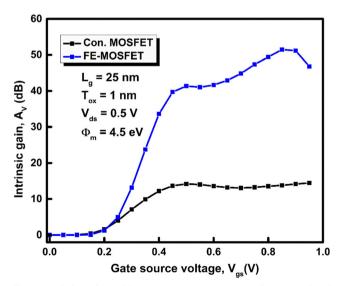

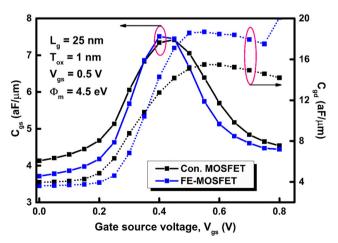

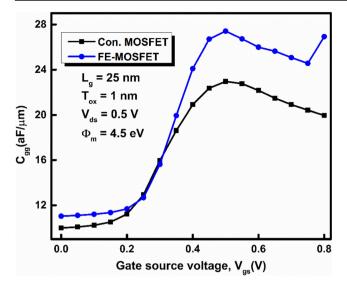

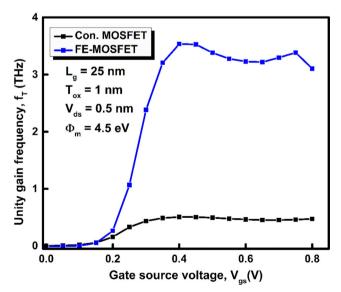

| Figure 3.5: (a) $g_m$ and TGF vs $V_{gs}$ , (b) $V_{EA}$ vs $V_{ds}$ , and (c) $A_v$ vs $V_{gs}$ for different structures48                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

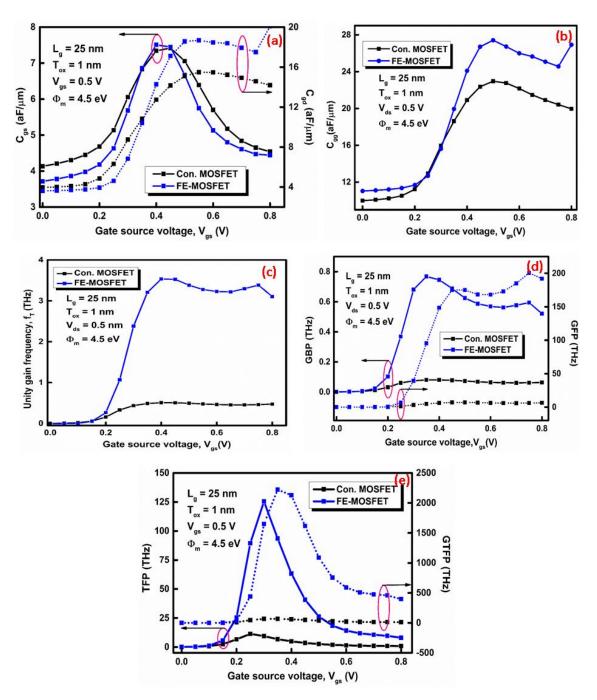

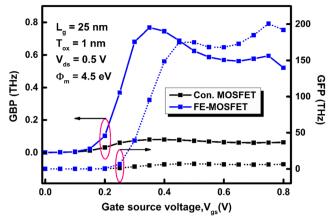

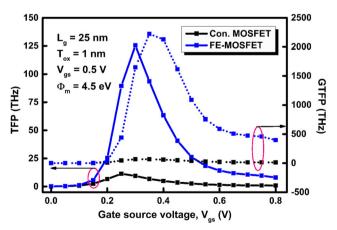

| Figure 3.6: Variation of (a) $C_{gs}$ and $C_{gd}$ to $V_{gs}$ , (b) $C_{gg}$ to $V_{gs}$ , (c) $f_T$ to $V_{gs}$ , (d) GBP and GFP to $V_{gs}$ , (e) TFP and GTFP to $V_{gs}$ for each configuration                                                                                  |

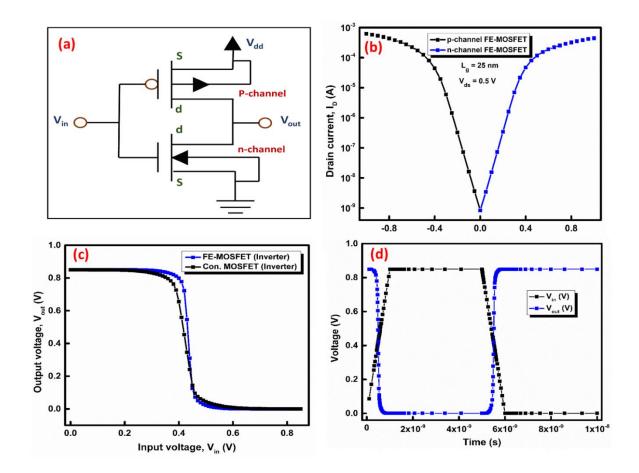

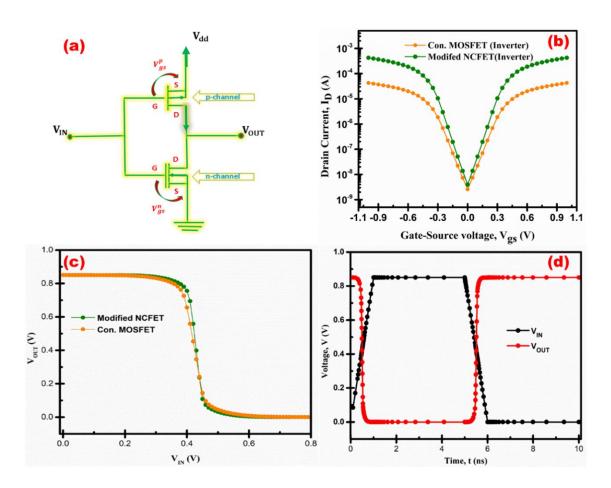

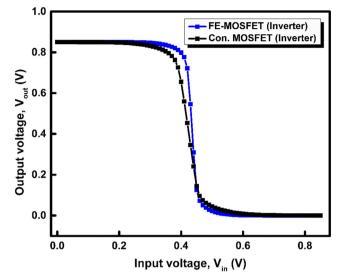

| Figure 3.7: (a) Schematic of FE-MOSFET-based inverter, (b) threshold voltage matching of n and p-channel FE-MOSFET to $V_{gs}$ , (c) Voltage Transfer Curve (VTC) Characteristics of conventional MOSFET and FE-MOSFET based inverter, (d) Transient curve of FE-MOSFET-based inverter |

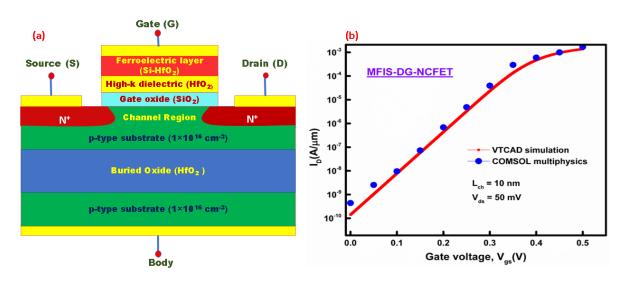

| Figure 4.1 Proposed Modified NCFET structure with Si-HfO <sub>2</sub> ferroelectric material and HfO <sub>2</sub> as BOX69                                                                                                                                                             |

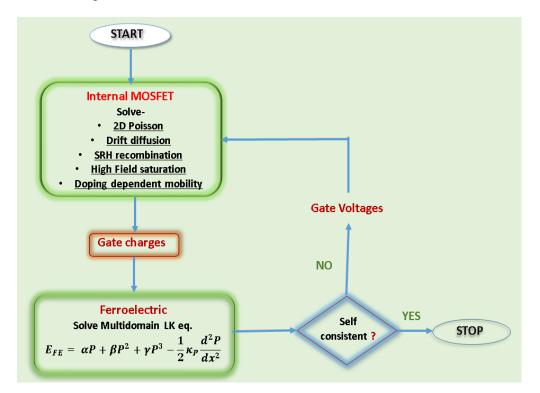

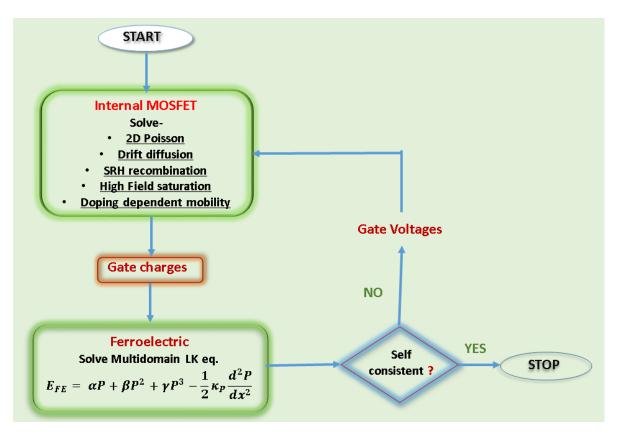

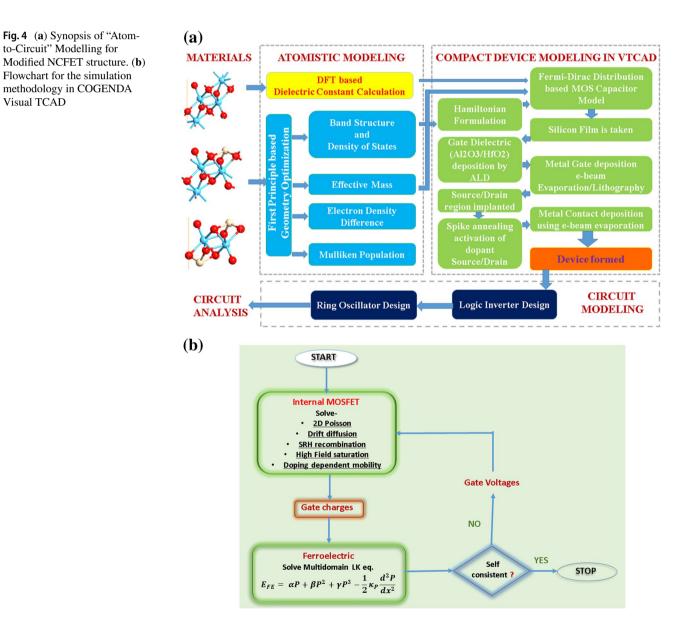

| Figure 4.2: Flowchart for the simulation methodology in COGENDA Visual TCAD                                                                                                                                                                                                            |

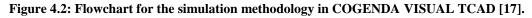

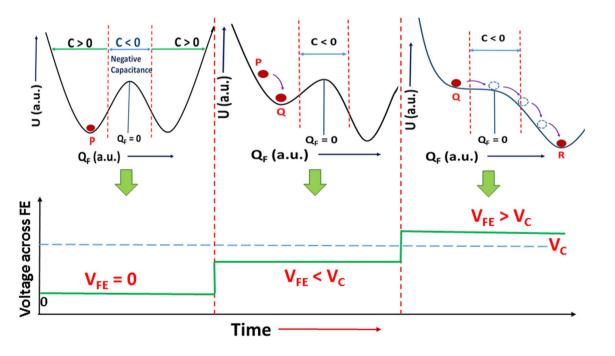

| Figure 4.3 The band structure corresponds to (a) HfO <sub>2</sub> , (b) 1 Si-atom HfO <sub>2</sub> , and (c) 2 Si-atom HfO <sub>2</sub>                                                                                                                                                |

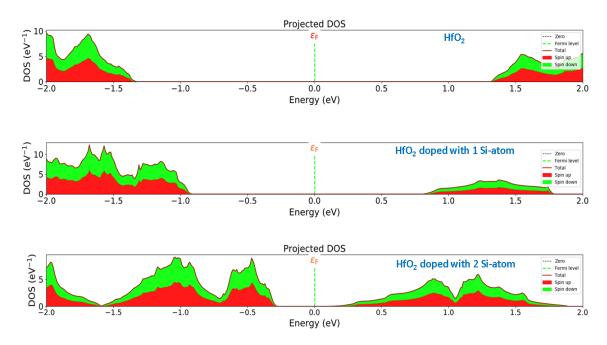

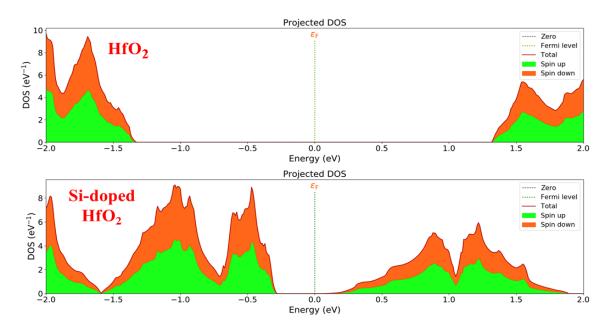

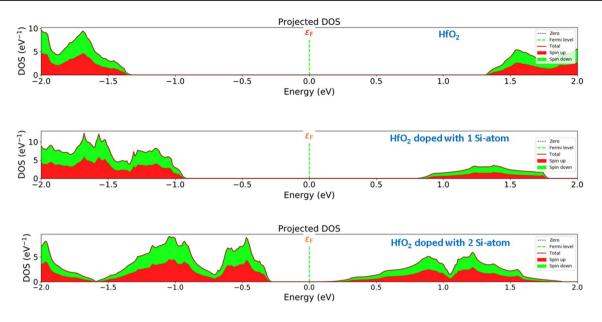

| Figure 4.4: The Projected DOS concerning the energy for different configurations of HfO <sub>2</sub> 75                                                                                                                                                                                |

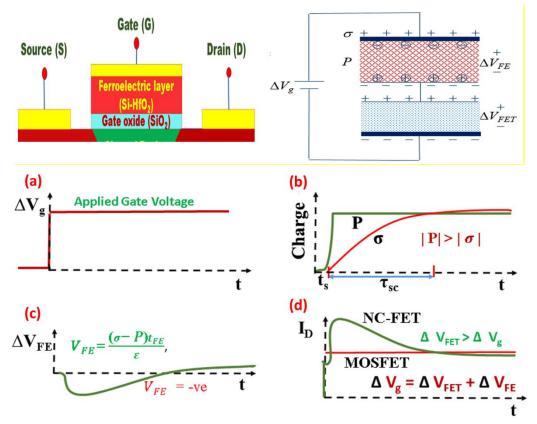

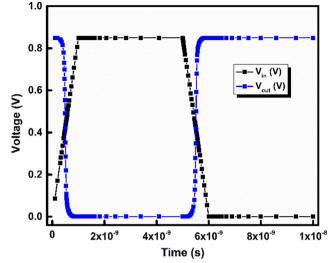

| Figure 4.5: The voltage amplification process occurs in the gate stack of NCFET76                                                                                                                                                                                                      |

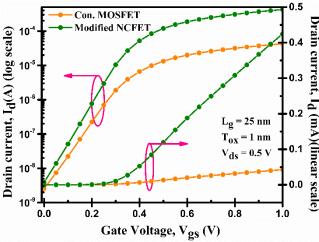

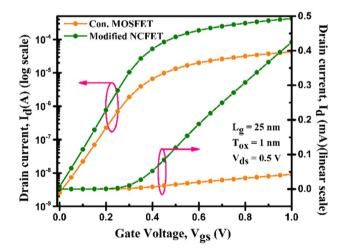

| Figure 4.6: Transfer characteristic comparison of conventional MOSFET and Modified NCFET in linear and logarithmic scale                                                                                                                                                               |

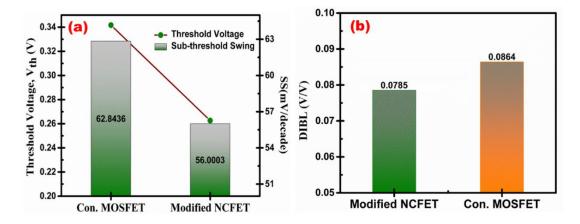

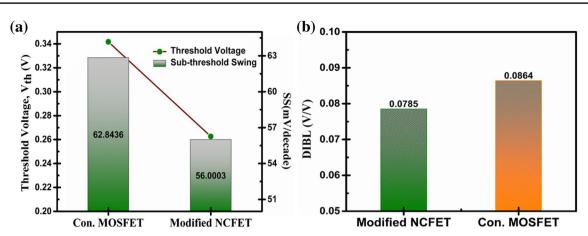

| Figure 4.7: Comparison of (a) V <sub>th</sub> and SS, (b) DIBL comparison of conventional MOSFET and Modified NCFET                                                                                                                                                                    |

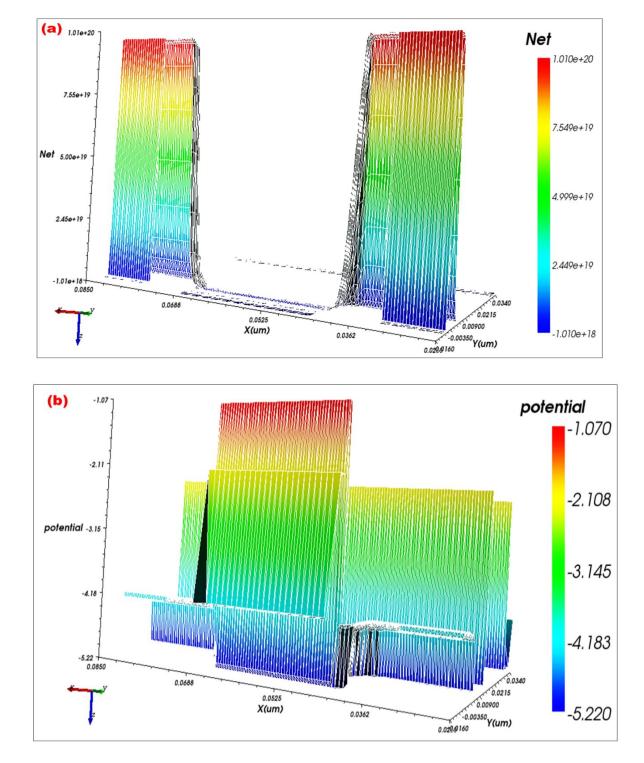

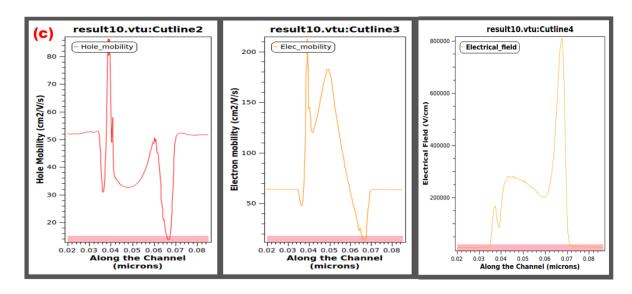

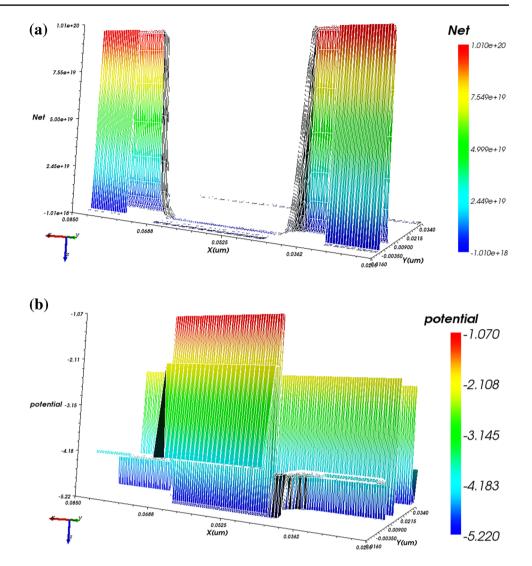

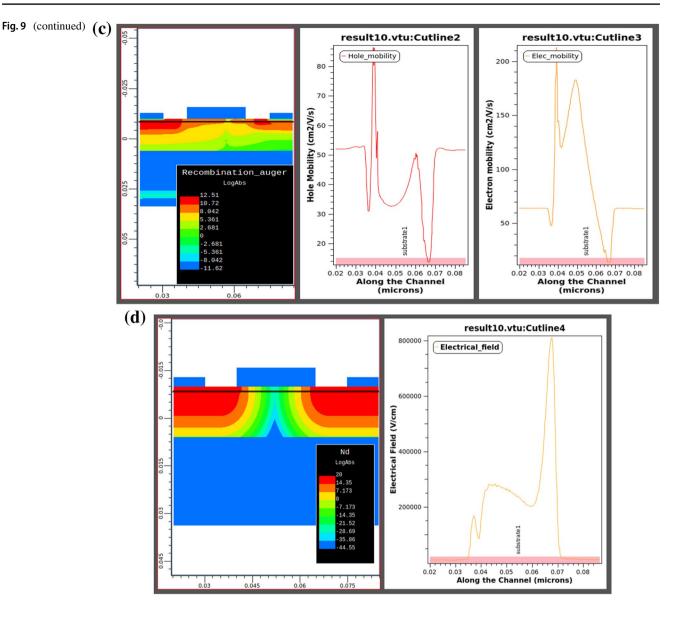

| Figure 4.8(a) Net charge (b) potential, (c) hole, electron mobility, and electric field across the channel region of Modified NCFET structure                                                                                                                                          |

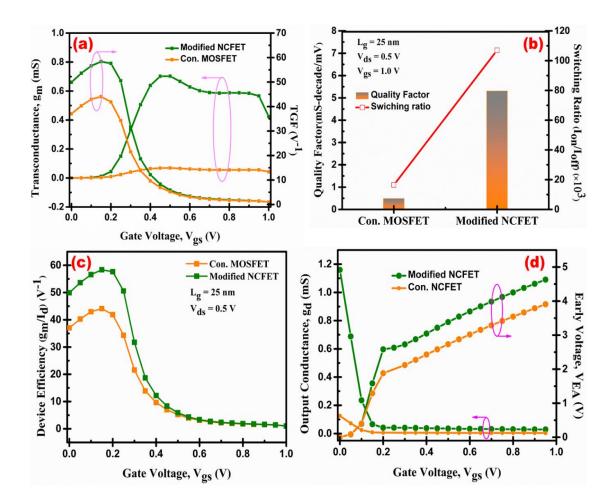

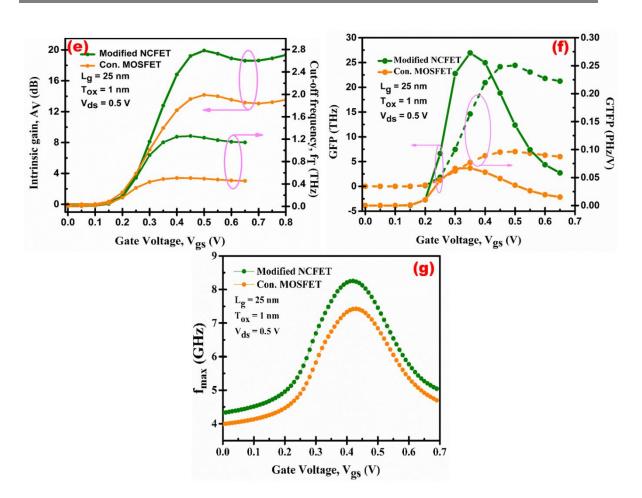

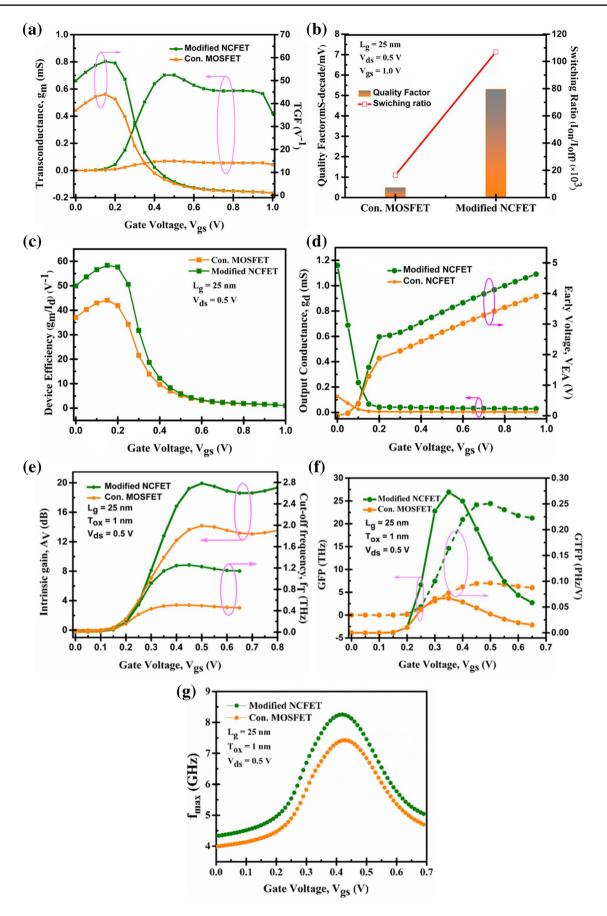

| Figure 4.9: Variation of (a) $g_m$ and TGF, (b) QF and $I_{on}/I_{off}$ ratio, (c) device efficiency, (d) $g_d$ and $V_{EA}$ , (e) $f_T$ and $A_v$ , (f) $f_{max}$ to $V_{gs}$ for both configurations                                                                                 |

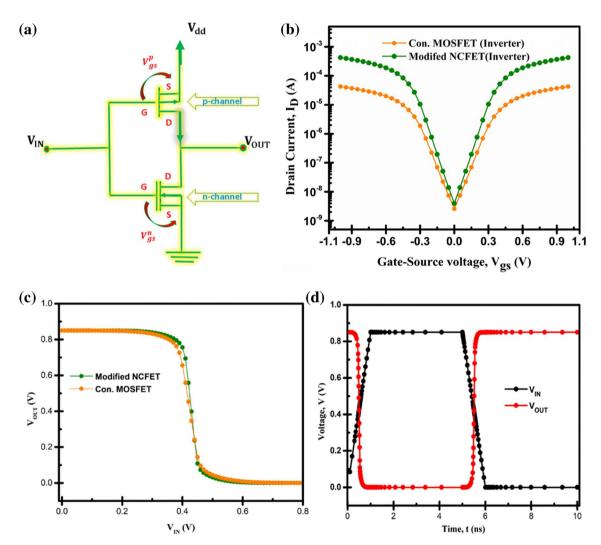

| Figure 4.10: (a) Schematic diagram of MOS-based inverter, (b) Threshold voltage matching, (c) VTC curve for both configurations, (d) The transient curve for a Modified NCFET-based inverter                                                                                           |

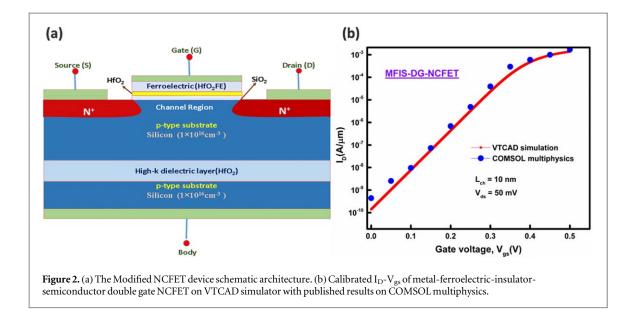

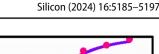

| Figure 5.1: (a) The Modified NCFET device schematic architecture. (b) Calibrated $I_D$ - $V_{gs}$ of metal-<br>ferroelectric-insulator-semiconductor double gate NCFET on VTCAD simulator with published results on<br>COMSOL Multiphysics                                             |

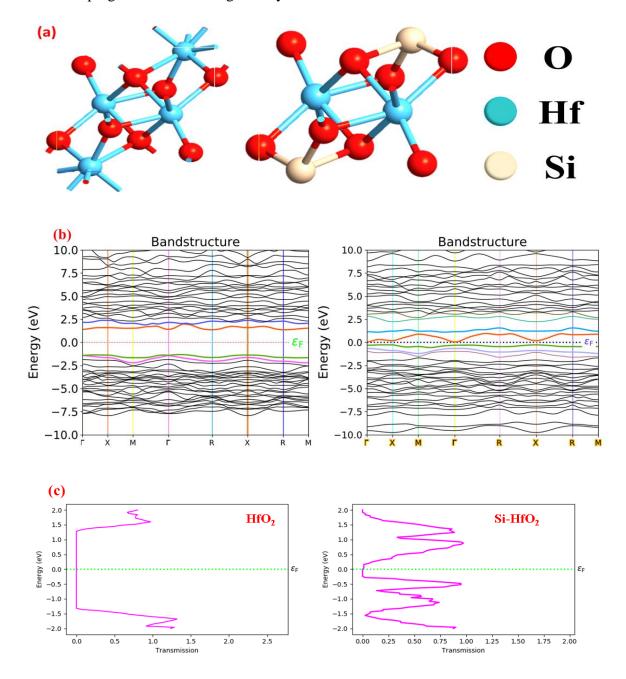

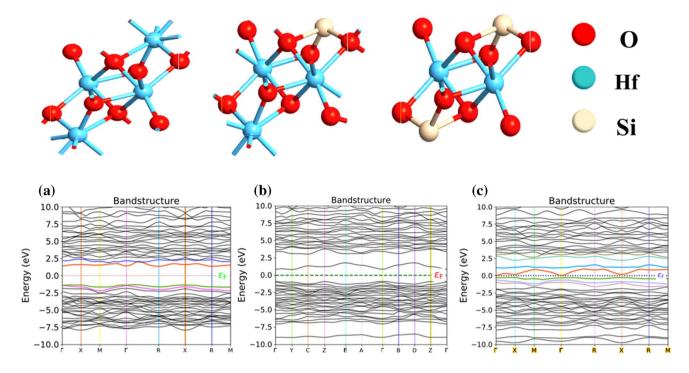

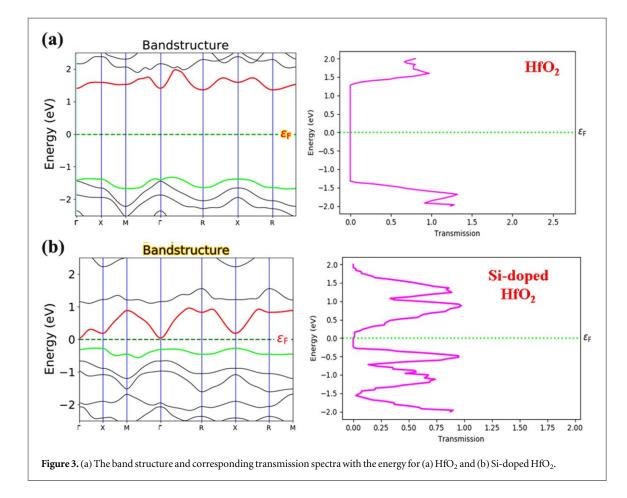

| Figure 5.2: (a) Structure, (b) band structure, and (c) transmission spectra with the energy of $HfO_2$ and Si- $HfO_2$ 103                                                                                                                                                             |

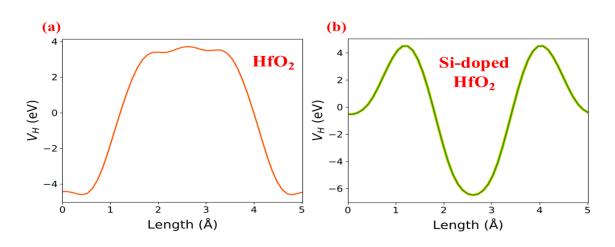

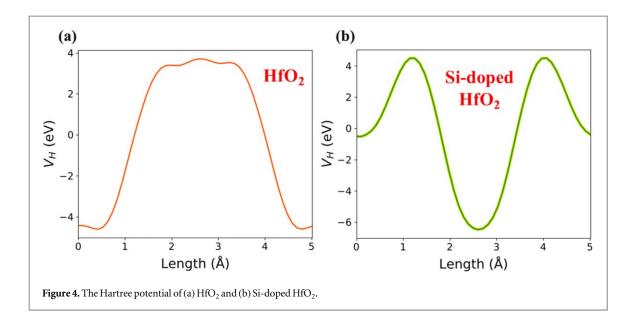

| Figure 5.3: The Hartree potential of (a) HfO <sub>2</sub> and (b) Si-doped HfO <sub>2</sub> 105                                                                                                                                                                                        |

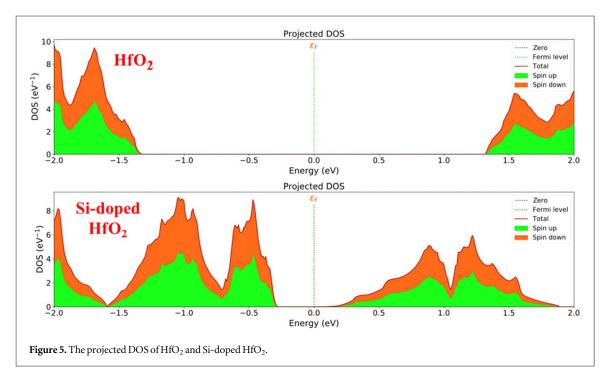

| Figure 5.4: The projected DOS of HfO <sub>2</sub> and Si-HfO <sub>2</sub> 106                                                                                                                                                                                                          |

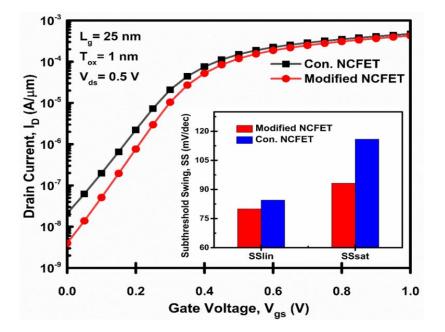

| Figure 5.5: Transfer characteristic and Subthreshold Swing (inset) comparison of conventional NCFET and Modified NCFET at a drain-source voltage of 0.5V                                                                                                                               |

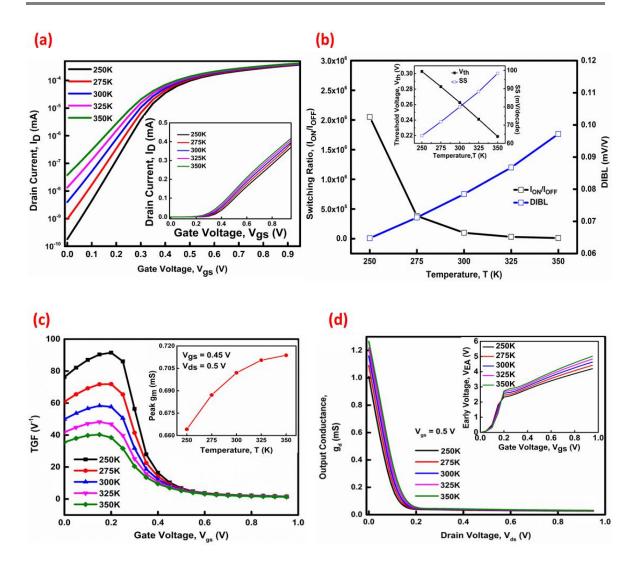

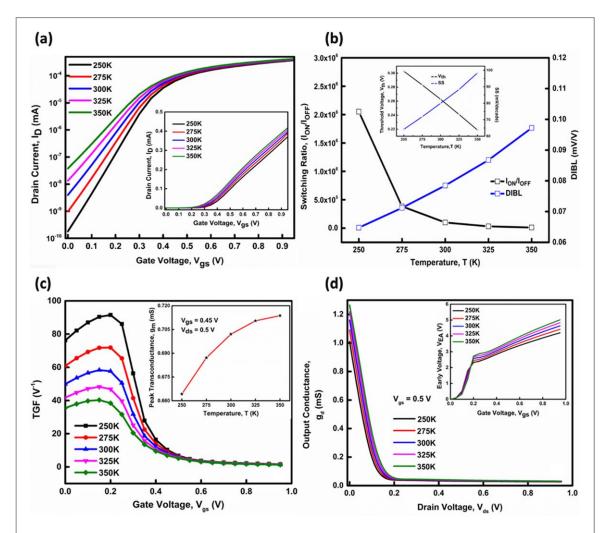

| Figure 5.6: Temperature variation impacts (a) $I_D$ - $V_{gs}$ characteristic in logarithm scale and linear scale (inset), (b) $I_{on}/I_{off}$ , DIBL, and $V_{th}$ , SS (inset), (c) TGF, and peak transconductance value (inset), (d) $g_d$ and $V_{EA}$ (inset) with $V_{gs}$      |

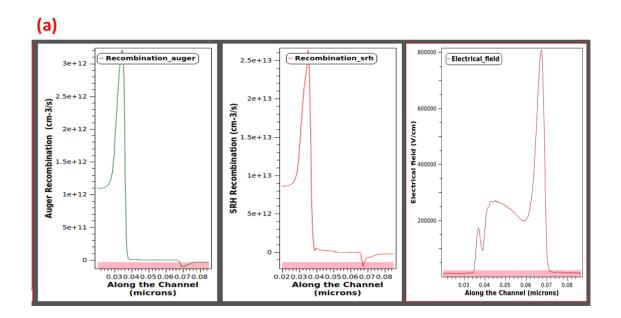

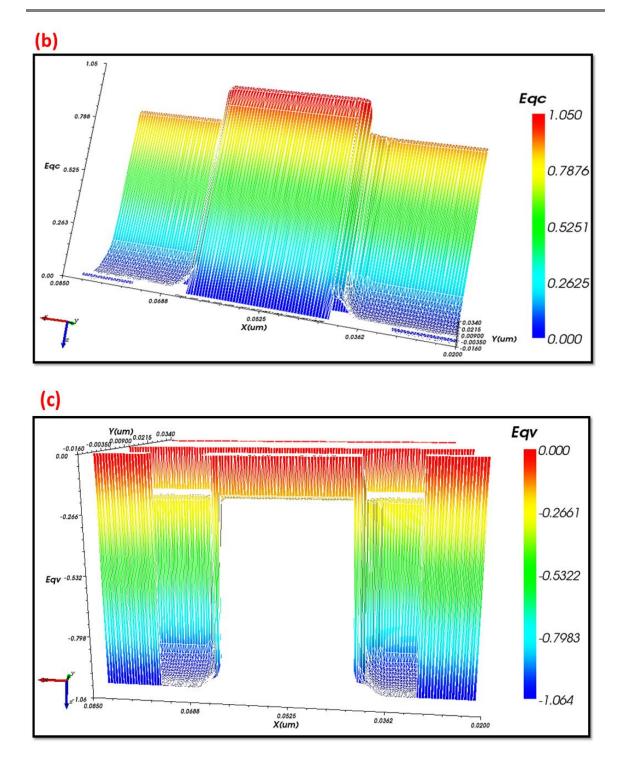

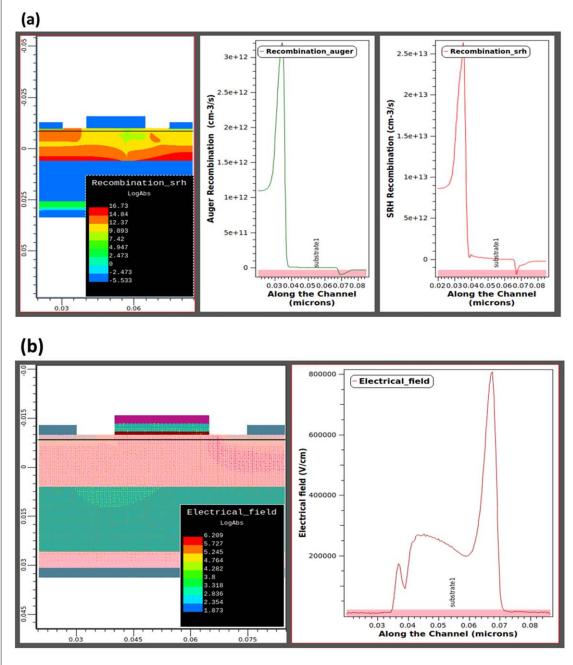

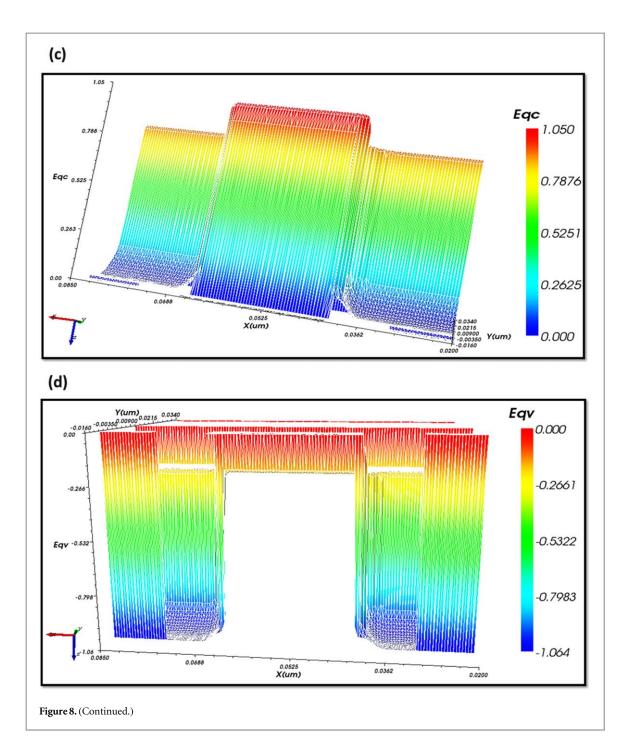

| Figure 5.7: (a) Auger, SRH recombination, and Electric Field along the channel length, (b) conduction Band energy, (c) Valence Band energy across the architecture                                                                                                                     |

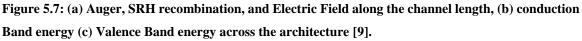

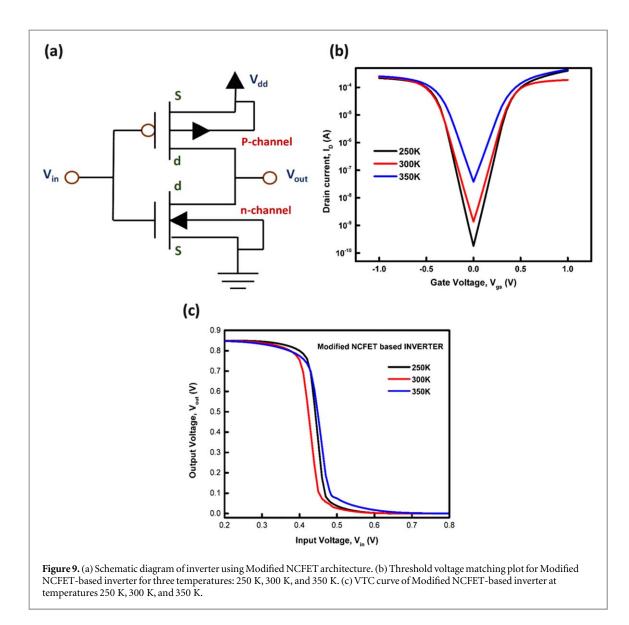

| Figure 5.8: (a) Schematic diagram of inverter using Modified NCFET architecture, (b) Threshold voltage matching plot, (c) VTC curve of Modified NCFET-based inverter at temperatures 250K, 300K, and 350K.                                                                             |

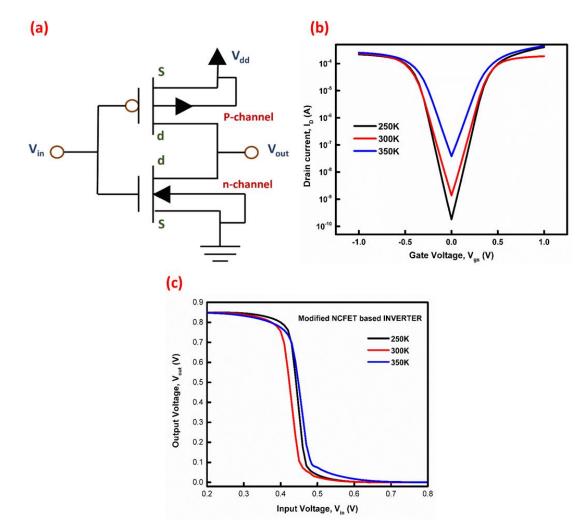

| Figure 5.9: (a) Propagation delay and transition time schematic of NCFET-based inverter, (b) Propagation characteristic of Modified NCFET-based inverter at 300K, (c) Variation of t <sub>p</sub> , (d) trf with rise of temperature |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.1: (a) Atomic structure (b) Band structure (c) PDOS (d) The Hartree potential corresponding to He (assumed Air molecule), SiO <sub>2</sub> , and HfO <sub>2</sub>                                                           |

| Figure 6.2: Gate-Stacked Negative Capacitance Field Effect Transistor (GS-NCFET) Device architecture 133                                                                                                                             |

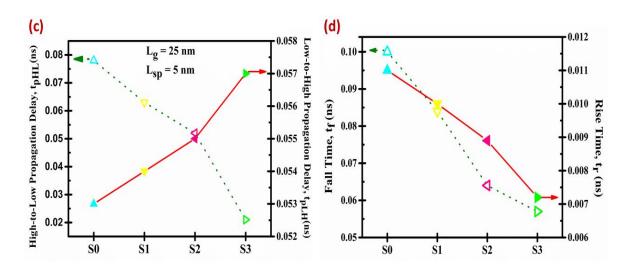

| Figure 6.3: GS-NCFET with no spacer (S0) Air spacer (S1) SiO <sub>2</sub> spacer (S2) HfO <sub>2</sub> spacer (S3)134                                                                                                                |

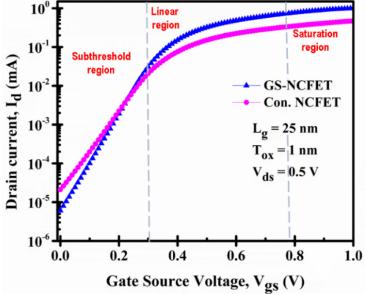

| Figure 6.4: Transfer characteristics comparison of conventional NCFET and GS-NCFET                                                                                                                                                   |

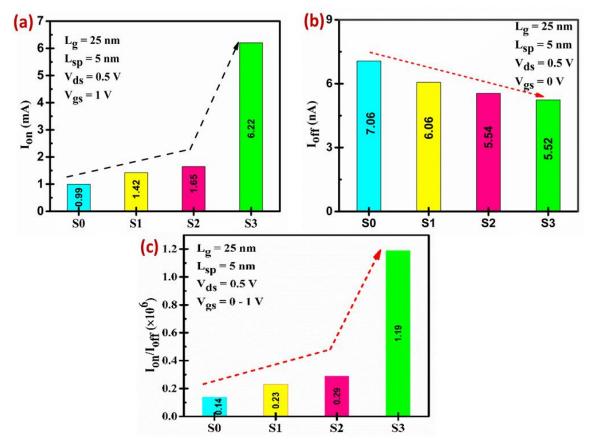

| Figure 6.5: Comparison of (a) $I_{on}$ current. (b) $I_{off}$ current. (c) Switching ratio ( $I_{on}/I_{off}$ ) for S0, S1, S2, and S3 configuration                                                                                 |

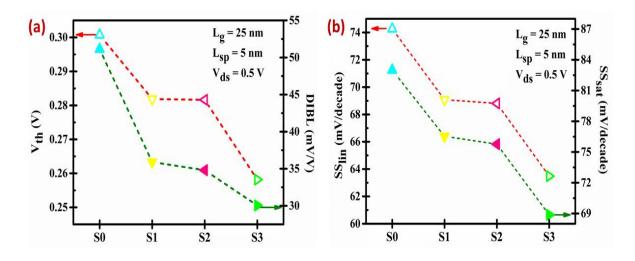

| Figure 6.6: Comparison of (a) V <sub>th</sub> and DIBL. (b) SS in linear and saturation regions for S0, S1, S2, and S3 configurations                                                                                                |

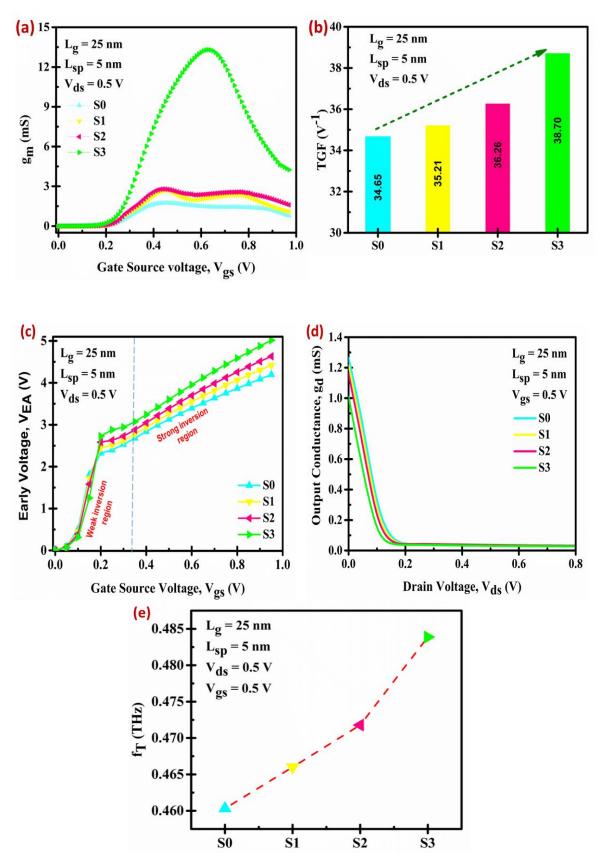

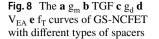

| Figure 6.7: Comparison of (a) $g_m$ . (b) TGF. (c) $V_{EA}$ . (d) $g_d$ . (e) $f_T$ curves of GS-NCFET with different types of spacers                                                                                               |

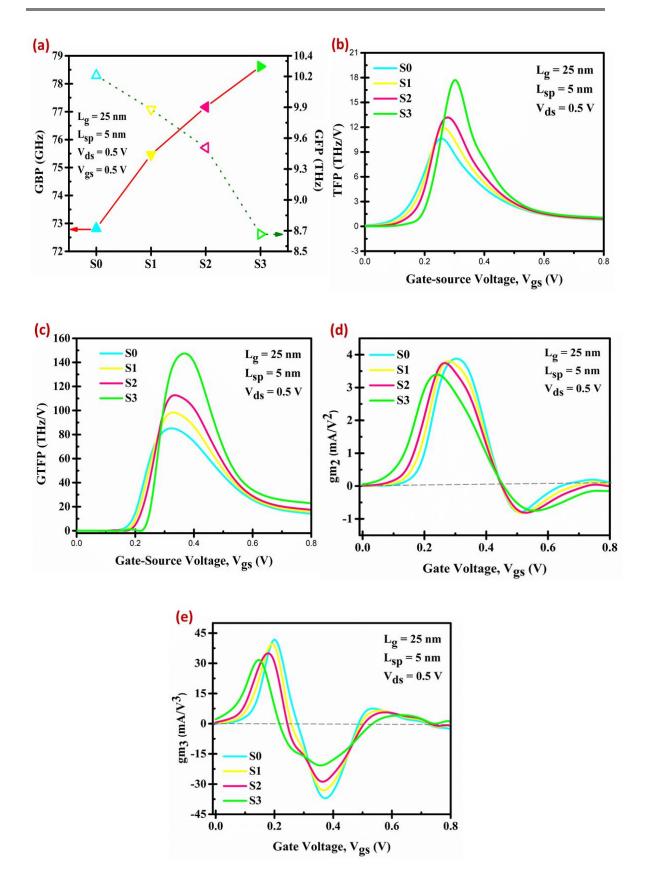

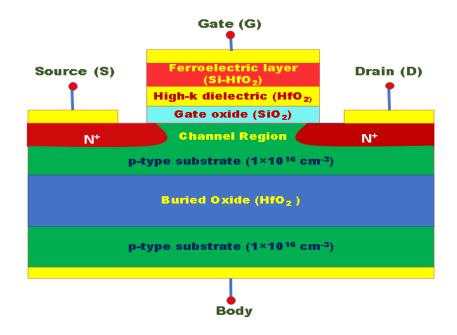

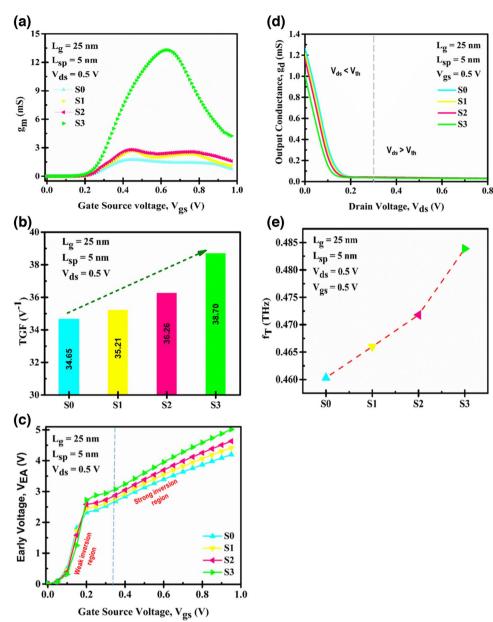

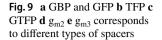

| Figure 6.8: Comparison of (a) GBP and GFP. (b) TFP. (c) GTFP. (d) g <sub>m2</sub> . (e) g <sub>m3</sub> corresponds toGS-NCFET with different types of spacers                                                                       |

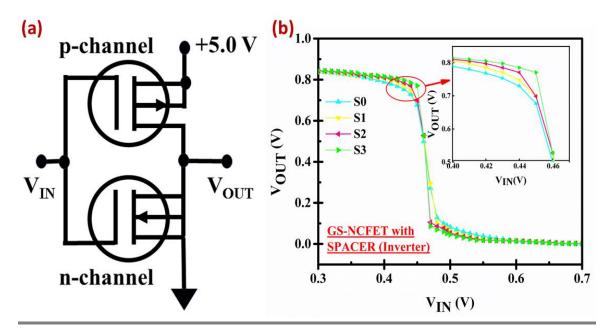

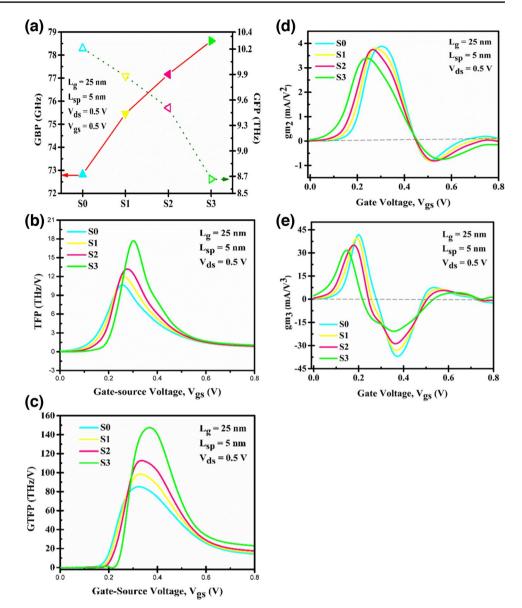

| Figure 6.9: (a) Schematics of GS-NCFET-based inverter. (b) VTC curve. (c) propagation delay. (d) rise time and fall time of GS-NCFET-based S0, S1, S2, and S3 inverters                                                              |

| Figure 7.1: Gate-Stacked Negative Capacitance Field Effect Transistor (GS-NCFET) Device architecture 155                                                                                                                             |

| Figure 7.2 Flowchart for the simulation methodology in COGENDA Visual TCAD                                                                                                                                                           |

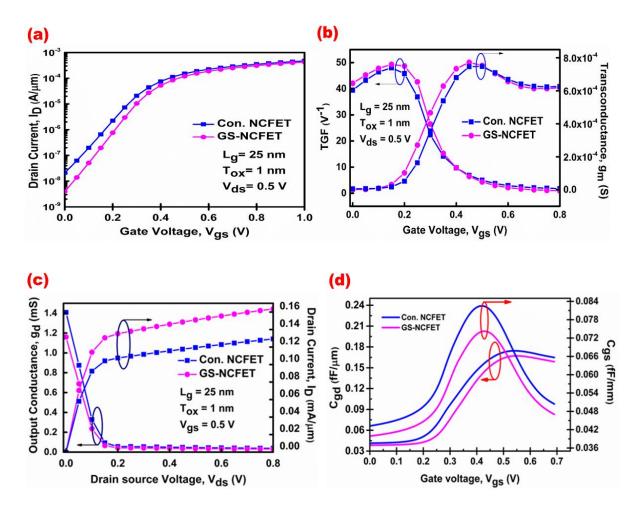

| Figure 7.3: Parameter comparison of conventional NCFET and GS-NCFET (a) $I_D - V_{gs}$ . (b) $g_m$ and TGF. (c) $I_D - V_{ds}$ and $g_d$ . (d) $C_{gd}$ and $C_{gs}$ correspond to $V_{gs}$                                          |

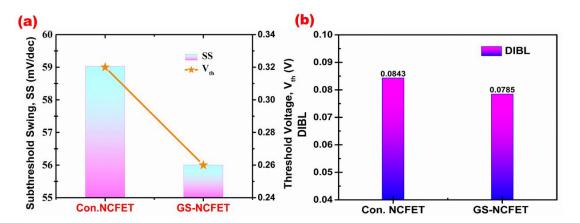

| Figure 7.4: Comparison of (a) SS and Vth (b) DIBL of conventional NCFET and GS-NCFET158                                                                                                                                              |

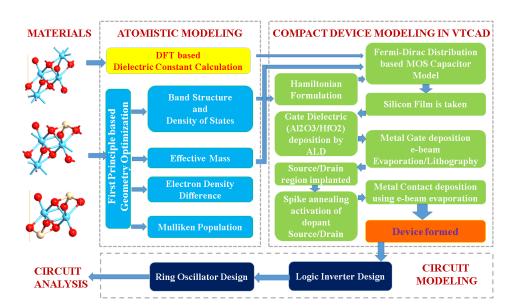

| Figure 7.5: Synopsis of "Atom-to-Circuit" Modeling for GS-NCFET Structure                                                                                                                                                            |

| Figure 7.6: Flowchart for the look-up table-based Verilog-A model creation process from TCAD simulations with generated N- and P-GS-NCFET symbols                                                                                    |

| Figure 7.7: Threshold voltage matching for N and P-type GS-NCFET on Visual TCAD simulator                                                                                                                                            |

| Figure 7.8: (a) schematic diagram of GS-NCFET-based inverter with the possible input-output states. (b) output curve corresponding to GS-NCFET-based inverter. (c) VTC curve of GS-NCFET-based inverter                              |

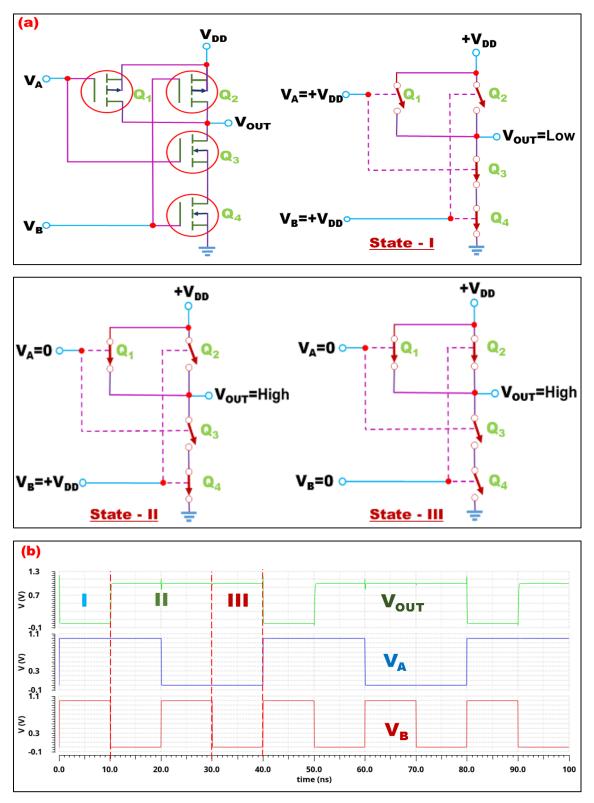

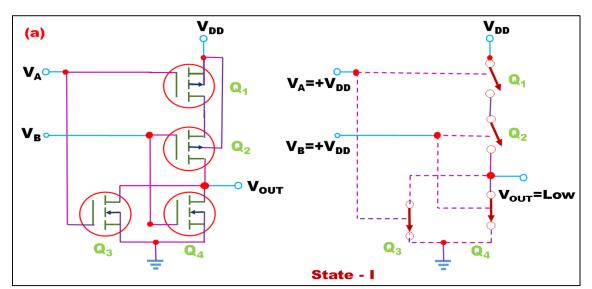

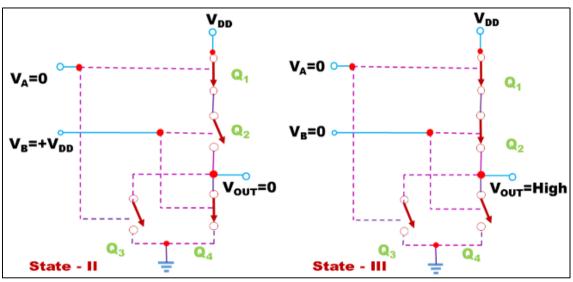

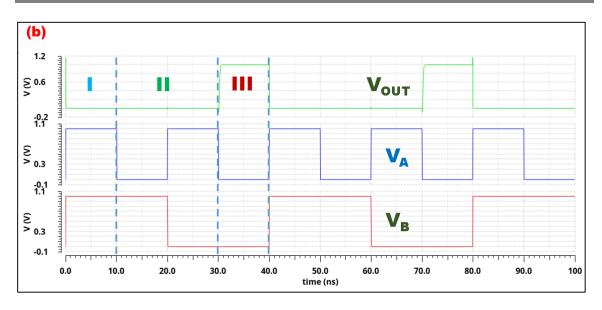

| Figure 7.9: (a)Schematic diagram of GS-NCFET-based NAND gate with possible input-output states.<br>(b) Output curve of GS-NCFET-based NAND gate                                                                                      |

| Figure 7.10: (a)Schematic diagram of GS-NCFET-based NOR gate with possible input-output states. (b) Output curve of GS-NCFET-based NOR gate                                                                                          |

# **1** CHAPTER

## Introduction

- This chapter presents a thorough background of the research work, emphasizing the importance of NCFET in the contemporary integrated circuit industry.

- Further, the chapter discusses the thesis objectives based on the background of MOSFET technology.

- Finally, the chapter provides an overview of the thesis research objectives, followed by a summary of all the chapters.

## **1.1 BACKGROUND**

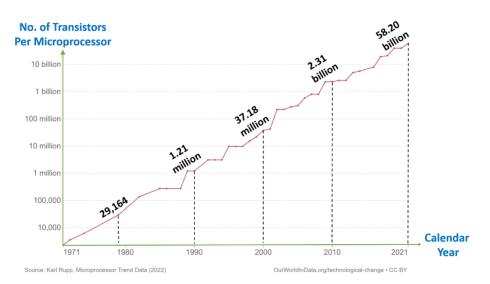

In 1958, Jack Kilby, while employed at Texas Instruments, independently developed the concept of the integrated circuit (IC) [1]. Because of this innovation, it is now possible to fabricate several electronic components on a single semiconductor substrate, revolutionizing the electronics industry. On the other hand, Moore's law caused the CMOS technology to downscale, accelerating the development of ICs. The fact that a chip's transistor count doubles every two years is known as Moore's law, after one of Intel's co-founders, Gordon Moore [2]. This observation has been true for over 50 years, as shown by Figure 1.1, and has developed into a core idea in the semiconductor sector [3]. Transistors become smaller and more tightly packed on a single chip, which increases IC performance while lowering cost and power consumption. This trend has made it easier for a variety of electronic devices to be used widely, from cell phones and personal computers to cutting-edge medical technology and driverless cars. Our everyday lives have been miraculously changed by this amazing breakthrough in integrated circuit technology, and further device scaling is necessary to sustain further advancements in IC technology.

Figure 1.1: Log plot of transistor counts per microprocessor against calendar years [3].

However, maintaining this downscaling in the nanoscale region is challenging because of constraints including higher leakage current, higher power consumption, heat dissipation problems, quantum effects, and short-channel effects (SCEs) [4-6]. In deeply scaled MOSFETs, the drain potential starts to alter the channel's electrostatics, which raises the leakage current between the drain and the source. Furthermore, important SCEs that contribute to power loss in transistors include threshold voltage (V<sub>th</sub>) roll-off, drain-induced barrier lowering (DIBL), and subthreshold slope (SS) [7–10]. To mitigate these challenges, a variety of device topologies have been proposed, including multi-gate MOSFETs [11], TFETs [12], HEMTs [13, 14], FinFETs [15–17], and NCFETs. NCFET has emerged as the most desirable alternative to MOSFETs and is the driving force behind the current IC industry, which optimizes SCEs to achieve exceptional scalability, augment battery longevity, and minimize power consumption [18, 19].

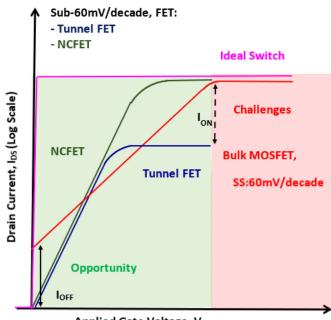

Applied Gate Voltage, V<sub>GS</sub>

Figure 1.2: Expected steep slope less than 60 mV/dec at room temperature for an NC-FET [20]. Figure 1.2 demonstrates the performance of NCFETs over conventional planar MOSFETs. Leakage current and transistor gate delay have been reduced significantly for the NCFET structure over the planar MOSFET architecture [20]. NCFET ensures superior voltage

amplification with negative capacitance properties. Finally, NCFET offers a larger packing density. With a reduction in device dimensions according to Dennard scaling rules, the capacitances of the devices have reduced promising lesser power consumption. However, the supply voltage  $(V_D)$  could not be scaled according to the scaling rules, manifesting itself as a bottleneck in achieving high-speed low-power devices. This is because carriers in the source and drain region of the MOSFET are governed by Boltzmann statistics which limits the rate of increase of drain current for voltage to 60 mV/dec. In this Chapter, we give the thesis objectives, an overview of the thesis chapters, what are the research gaps after doing the literature survey and we explore the idea of negative capacitance in the gate stack of MOSFETs to overcome the Boltzmann limit (SS = 60 mV/dec) to realize high-frequency low-power devices. In this work, we did the step-by-step simulation work on the different architectures of NCFETs and explored the analog/RF parameters to discuss their further assessment of the digital circuits. Firstly, we explored the effect of the ferroelectric material layer as BOX in the substrate of conventional MOSFET and discussed its parameters. After that, the ferroelectric material in the gate stack with the dielectric layer in the substrate region as the BOX layer is explored termed as GS-NCFET, and compared with the conventional NCFET structures. Further, the temperature reliability and spacer's effects of GS-NCFET were discussed. Lastly, the simulated GS-NCFET is converted into the symbol using the VISUALFAB and cadence virtuoso simulator to explore its use in digital circuits like logic gates, amplifiers, etc.

#### **1.2 THESIS OBJECTIVES**

The entire work in the present thesis is divided into seven chapters based on the following objectives listed below:

- **1.** To explore the TCAD investigation of ferroelectric-based substrate MOSFET for digital application.

- To discuss the reliability of Si-doped HfO<sub>2</sub> by its DFT-based atomic calculation and the effect of its Negative Capacitance on SCEs, Analog/RF, and VTC parameters of MOSFET.

- **3.** To explore the impact of temperature on the RF and VTC curve of high-k dielectric layer-assisted NCFET and to discuss DFT-based Atomic Modeling of hafnium oxide.

- **4.** Self-Consistent LCAO-based DFT analysis of high-k spacers and to discuss its assessment on Gate-Stacked NCFET for improved device-circuit performance.

- **5.** To discuss the device and circuit-level assessment of Gate-Stacked NCFET for digital applications.

### **1.3 SCHEME OF CHAPTERS**

This thesis is organized into seven chapters to accommodate all the research objectives. Each chapter is organized to be fundamentally self-contained.

#### **Chapter 1.Introduction**

In this chapter, the general introduction to the theory of negative capacitance is discussed with a follow-up of the research objective and the overall organization of the thesis, as well as the importance of the research work presented in this thesis, are discussed.

#### **Chapter 2.Literature Survey**

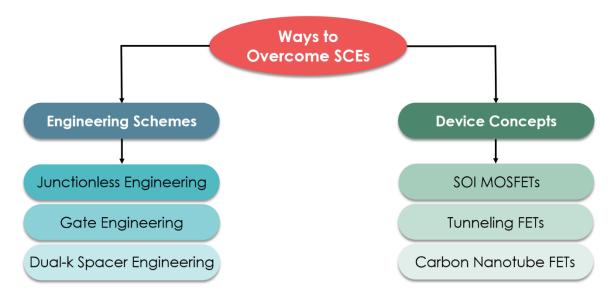

This chapter overviews the basics of nanoscale MOSFET, scaling issues, and short-channel effects. After that, the ways to overcome the short-channel effects are discussed. In this regard, the different engineering schemes and the advanced FET structures, such as SOI MOSFET, FE-MOSFET, and NCFET, reported in different research articles, have been presented. Further, the research gaps found during the literature survey have been explored.

Then, the chapter progresses toward the architecture of NCFET, the basic working principle of NCFET, and its potential advantages and drawbacks.

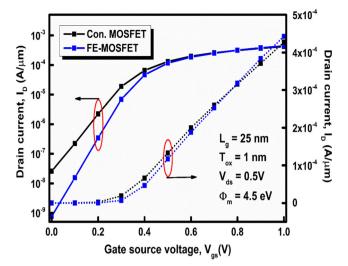

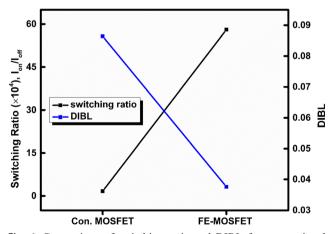

# Chapter 3.TCAD investigation of ferroelectric-based substrate MOSFET for digital application

This chapter presents an investigation on the analog/RF performance of ferroelectric (FE) based substrate metal oxide semiconductor field effect transistor (MOSFET) for digital application as an inverter. Short channel effect (SCEs) reduced significantly with improvement in switching ratio ( $I_{on}/I_{off}$ ). The simulation shows the immunity towards parameters like transconductance ( $g_m$ ), transconductance generation factor (TGF), early voltage ( $V_{EA}$ ), and intrinsic gain ( $A_V$ ) which allows the device to look into digital applications. Also, the RF performance parameters come out to be superior for the proposed device structure, as the gain frequency product (GFP) and gain bandwidth product (GBP) are enhanced by 100 and 10 folds, respectively. Further, RF investigation shows the enhanced results as attributed to peak values for transconductance frequency product (TFP) and gain transconductance frequency product (GTFP). The transient analysis shows an improvement in the noise margin (NM) for the FE-MOSFET structure. Thus, the proposed architecture can be an attractive alternative for the digital application.

# Chapter 4.DFT-based Atomic Calculation of Si-doped HfO<sub>2</sub> and impact of Negative Capacitance on Analog/RF and VTC parameters of MOSFET

Execution grids of developing electronic devices are being examined to find substitutes for MOSFETs in the quest to minimize power dissipation and ease energy efficiency limitations. The innovative architecture of negative capacitance field effect transistors (NCFETs), which offer advantages from the design, performance, and fabrication perspectives, is presented and examined in this chapter. This proposed structure in this chapter is called Modified NCFET. Modification of NCFET includes the DensityFunctional-Theory (DFT) based atomic modelling for Ferroelectric material Hafnium Oxide (FE-HfO<sub>2</sub>) with different doping concentrations of silicon (Si). The performance metrics of Modified NCFET are compared with conventional MOSFET designed on the same technology node to draw the effect of Si-doped HfO<sub>2</sub>. DFT calculations like Projected Density of States (PDOS) and energy band structure are done using the Quantum Atomistix Tool Kit (ATK) simulator, which is atomic-scale modelling software, and device modelling is done by the Visual Technology-Computer-Aided-Design (TCAD) simulator. The device performance comparison of Modified NCFET and conventional MOSFET is made by the VISUAL TCAD in terms of short-channel effects (SCEs), analog/RF matrices, and FET-based inverter parameters (noise margin (NM), voltage transfer characteristics (VTC)). Additionally, the proposed NCFET is contrasted with the various FOMs' IRDS criteria.

# Chapter 5.DFT-based Atomic Modeling and Temperature Analysis on the RF and VTC curve of high-k dielectric layer-assisted NCFET

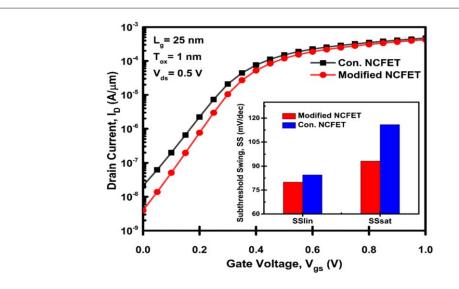

In this chapter, Density Functional Theory (DFT) based calculation using a Quantum Atomistic Tool Kit (ATK) simulator is done for the hafnia-based ferroelectric material. The band structure, projected density of states (PDOS), and Hartree potential (V<sub>H</sub>) are taken into account for hafnium oxide (HfO<sub>2</sub>) and silicon-doped hafnium oxide (Si-doped HfO<sub>2</sub>). Further, we analyze the temperature variation impact on analog parameters and voltage transfer characteristic (VTC) curve of inverter application of Modified Negative Capacitance Field-Effect-Transistor (NCFET) using the VISUAL Technology-Computer-Aided-Design (TCAD) simulator. The Modified NCFET structure enhances the DC parameters like leakage current ( $I_{OFF}$ ) and Subthreshold Swing (SS) compared to the conventional NCFET structure. With the temperature impact, the variation in the parameters of Modified NCFET is discussed at 250 K, 275 K, 300 K, 325 K, and 350 K like transconductance ( $g_m$ ), output conductance ( $g_d$ ), early voltage ( $V_{EA}$ ) shows the

increment as we move from 250 K to 350 K. The short channel effects (SCEs) like Drain Induced Barrier Lowering (DIBL) and Subthreshold Swing (SS) decrease with the temperature fall at 32.98% and 34.74%, respectively. Further, the VTC curve, Noise Margin (NM), and propagation delay between the input and corresponding output curve of the Modified NCFET-based inverter are discussed, along with the impact of temperature. The propagation delay between the input and corresponding output curve of the Modified NCFET-based inverter for the circuit decreased by 67.94% with the rise in the temperature. These factors show that the Modified NCFET-based inverter provides fast switching performance at high temperatures.

## Chapter 6.Self-Consistent LCAO based DFT analysis of high-k spacers on Gate-Stacked NCFET for improved device-circuit performance

This chapter investigates a Gate-Stacked negative capacitance field-effect transistor with a high dielectric material layer in the substrate region (GS-NCFET). Also, the effect of different types of spacers is taken into account. Spacers are differentiated based on their dielectric constant, i.e., GS-NCFET with no spacer is denoted as S<sub>0</sub>, with air spacer is denoted as S<sub>1</sub>, with SiO<sub>2</sub> specified as S<sub>2</sub>, and with HfO<sub>2</sub> noted as S<sub>3</sub> device architecture. Self-consistent LCAO-based DFT analysis is done for the spacer materials in terms of band structure, PDOS, and Hartree potential. Further, the switching ratio (I<sub>on</sub>/I<sub>off</sub>) is discussed for S<sub>0</sub>, S<sub>1</sub>, S<sub>2</sub>, and S<sub>3</sub>. Further, the short channel effects (SCEs) like subthreshold swing (SS) and drain-induced barrier lowering (DIBL) are extracted at drain-source voltage (V<sub>ds</sub>) of 0.5 V. In addition, the voltage transfer characteristic (VTC) curve of GS-NCFET with a spacer-based inverter is considered for digital application purposes, and the transition region is drawn out for all the device architecture-based inverters. Essential parameters like propagation time delay between input and corresponding output curve of FET-based inverter and their rise/fall time are evaluated to study the application purposes. In GS-

NCFET, a dielectric layer, which is a buried oxide (BOX), is inserted in the substrate region to reduce the leakage current.

# Chapter 7.Device and Circuit-level assessment of Gate Stacked NCFET for digital applications

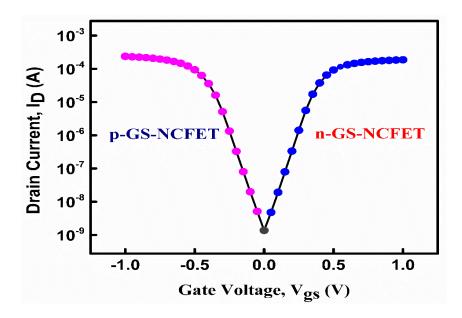

The work demonstrates a Gate-Stacked Negative Capacitance Field Effect Transistor (GS-NCFET) study. NCFETs have become promising devices in the sub-nano-meter regime. The design possibility of NCFET is explored in this work, and the device modelling is done using the Verilog A code. We will start with the basic analog parameters like transfer characteristics, transconductance (g<sub>m</sub>), and transconductance generation factor (TGF), with an improvement of 81.42% (leakage current), 9.97% and 21.54%, respectively, for GS-NCFET. Further, output characteristics and output conductance (g<sub>d</sub>) showed a 17.85% decrease in GS-NCFET for the GS-NCFET. Also, the short channel effects for conventional NCFET and GS-NCFET are discussed. Moreover, the authors explored the device-to-circuit modelling using the Verilog A code, which uses the device parameter's "tbl" files. The symbols of N-GS-NCFET and P-GS-NCFET are generated using the Cadence Virtuoso simulator. Further, the digital application of GS-NCFET is shown as NAND, NOR, and NOT logic gates.

#### **Chapter 8. Conclusion and Future Scope**

This chapter summarizes the overall research work illustrated in this thesis, along with the concrete conclusions drawn from the results presented in this thesis. This chapter also discusses the future scope of the present work and how this work can be extended and used in future research directions.

## **1.4 REFERENCES**

- [1] A.N. Saxena, "Invention of integrated circuits: Untold important facts," *World Scientific*, 2009.

- [2] G.E. Moore, "Cramming more components onto integrated circuits," *Proceedings* of the IEEE, vol. 86, no. 1, pp. 82-85, 1998.

- [3] https://ourworldindata.org/grapher/transistors-per-microprocessor.

- [4] K.J. Kuhn, "CMOS scaling for the 22nm node and beyond: Device physics and technology," *Proceedings of 2011 International Symposium on VLSI Technology, Systems and Applications*, pp. 1-2, 2011.

- [5] K. Roy, S. Mukhopadhyay, and H.M. Meimand, "Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits," *Proceedings* of the IEEE, vol. 2, no. 2, pp. 305-327, 2003.

- [6] T. Skotnicki, J.A. Hutchby, T.-J. King, H.-S.P. Wong, and F. Boeuf, "The end of CMOS scaling: Toward the introduction of new materials and structural changes to improve MOSFET performance," *IEEE Circuits and Devices Magazine*, vol. 21, no. 1, pp. 16-26, 2005.

- [7] Q. Xie, C.-J. Lee, J. Xu, C. Wann, J.Y.-C. Sun, and Y. Taur, "Comprehensive analysis of short-channel effects in ultrathin SOI MOSFETs," *IEEE Transactions on Electron Devices*, vol. 60, no. 6, pp. 1814-1819, 2013.

- [8] A. Chaudhary and M.J. Kumar, "Controlling short-channel effects in deepsubmicron SOI MOSFETs for improved reliability: A review," *IEEE Transactions* on Device and Materials Reliability, vol. 4, no. 1, pp. 99-109, 2004.

- [9] A. Kumar, N. Gupta, and R. Chaujar, "TCAD RF performance investigation of transparent gate recessed channel MOSFET," *Microelectronics Journal*, vol. 49, pp. 36-42, 2016.

- [10] X. Zhang, J. Xu, Z. Chen, Q. Wang, W. Liu, Q. Li, W. Bai, and X. Tang, "Investigation and optimization of electro-thermal performance of double gate-allaround MOSFET," *Microelectronics Journal*, vol. 129, 105540, 2022.

- [11] R.M. Barsan, "Analysis and modeling of dual-gate MOSFET's," *IEEE Transactions on Electron Devices*, vol. 28, no. 5, pp. 523-534, 1981.

- [12] A.K. Singh, M.R. Tripathy, K. Baral, and S. Jit, "Design and performance assessment of HfO<sub>2</sub>/SiO<sub>2</sub> gate stacked Ge/Si heterojunction TFET on SELBOX substrate (GSHJ-STFET)," *Silicon*, vol. 14, pp. 11847-11858, 2022.

- [13] A. Gowrisankar, V.S. Charan, H. Chandrasekar, A. Venugopalarao, R. Muralidharan, S. Raghavan, and D.N. Nath, "Compensation dopant-free GaN-on-Si HEMTs with a polarization engineered buffer for RF applications," *IEEE Transactions on Electron Devices*, vol. 70, no. 4, pp. 1622-1627, 2023.

- [14] M. Sharma and R. Chaujar, "Ultrascaled 10 nm T-gate E-mode InAlN/AlN HEMT with polarized doped buffer for high power microwave applications," *International Journal of RF and Microwave Computer-Aided Engineering*, vol. 32, no. 4, pp. 1-10, 2022.

- [15] C.-Y. Chang, C.-H. Chang, C.-H. Hou, K.-L. Lin, K.-Y. Lee, X.-F. Yu, and C.-O. Chui, "Semiconductor devices, Finfet devices and methods of forming the same," U.S. Patent App 15/876,223, 2019.

- [16] D. Hisamoto, W.C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T.J. King, J. Bokor, and C. Hu, "FinFET-a self-aligned double-gate MOSFET scalable to 20 nm," *IEEE Transactions on Electron Devices*, vol. 47, no. 12, pp. 2320-2325, 2000.

- [17] K. Banerjee and A. Biswas, "Enhanced analog/RF performance of hybrid charge plasma based junctionless C-FinFET amplifiers at 10 nm technology node," *Microelectronics Journal*, vol. 131, 105662, 2023.

- [18] S. Salahuddin, S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," *Nano Letters*, vol. 8, no. 2, pp. 405-410, 2008.

- [19] A. Jain, A. Rusu, A. M. Ionescu, "A compact model for ferroelectric-gate fieldeffect transistors based on the negative capacitance effect," *IEEE Transactions on Electron Devices*, vol. 61, no. 6, pp. 2235-2242, 2014.

- [20] S. Tayal, S. B. Rahi, J. Srivastava, S. Bhattacharya, "Recent Trends in Compact Modeling of Negative Capacitance Field-Effect Transistors," *Semiconductor Devices and Technologies for Future Ultra Low Power Electronics*, 10.1201/9781003200987-9, 2021.

# 2 CHAPTER

## Literature survey

- This chapter presents a thorough literature survey of NCFETs, emphasizing their importance in the contemporary integrated circuit industry.

- The problems related to MOSFET scaling and the different short-channel effects have been comprehensively reviewed in this chapter.

- After that, this chapter encompasses an examination of several engineering methods, such as junctionless engineering, gate engineering, and dual-k spacer engineering, as well as advanced FET architectures, including SOI MOSFET, TFET, and CNTFET, as documented in different research publications, for mitigating short-channel effects.

- Furthermore, the chapter discusses NCFET as a potential approach to address the limitations. The chapter then progresses toward the fundamental architecture of NCFETs, categorization, basic working principles, possible benefits, and challenges confronted by NCFET technology.

- ✤ Finally, the research gaps and challenges faced by the NCFET technology is discussed.

### 2.1 SCALING OF MOSFET

The development of MOSFETs dates back to the 1960s, with the invention of the first practical metal-oxide-semiconductor transistor by Mohamed Atalla and Dawon Kahng at Bell Labs in 1959. Early MOSFETs were relatively large by today's standards, with gate lengths (the distance between the source and drain under the gate electrode) measured in micrometers ( $\mu$ m). The first commercially viable MOSFETs had gate lengths on the order of 10  $\mu$ m or more [1].

These early devices were suitable for use in logic circuits and basic memory applications. Still, their size limited the number of transistors that could be integrated onto a single chip, leading to relatively low computing power. The scaling of MOSFETs began in earnest in the 1970s, driven by the realization that reducing the size of transistors could improve performance and energy efficiency [2-6].

As transistors became smaller, they required less power to switch on and off, and they could operate at higher speeds due to the reduced parasitic capacitance and resistance associated with smaller geometries. This marked the beginning of the era of scaling, where each new generation of transistors was designed to be smaller, faster, and more powerefficient than the previous generation.

#### 2.1.1 Dennard Scaling and the Golden Era

The early period of MOSFET scaling was largely guided by a principle known as Dennard scaling, proposed by IBM engineer Robert Dennard in 1974. Dennard's theory stated that as transistors were scaled down in size, their power density would remain constant as long as both the voltage and the current were scaled down proportionally [7-10]. This meant that as transistors got smaller, they would consume less power and produce less heat while switching faster, allowing for higher clock speeds in processors. For several decades,

MOSFET scaling followed this model, with chip manufacturers reducing the size of transistors while maintaining or improving their performance. Throughout the 1980s and 1990s, the semiconductor industry saw rapid improvements in MOSFET technology. Gate lengths shrank from micrometers to nanometers, with the 1 µm barrier being broken in the late 1980s. The transition from aluminium to copper interconnects in the late 1990s also helped reduce resistance and improve the overall speed of circuits, further enhancing the benefits of scaling.

During this time, MOSFET scaling was relatively straightforward, with each new generation of transistors offering better performance, lower power consumption, and increased transistor density. This period, often referred to as the "golden era" of Moore's Law, saw dramatic improvements in computing power and the proliferation of personal computers, mobile phones, and other electronic devices. By the early 2000s, however, the limits of classical MOSFET scaling began to emerge [11]. As gate lengths approached 100 nm and below, several issues became more pronounced, threatening to derail the continued progress predicted by Moore's Law.

- One of the most significant challenges was power dissipation. While Dennard's scaling suggested that power density would remain constant as transistors shrank, in reality, this assumption began to break down as transistors became extremely small.

- Another issue was short-channel effects, which occur when the channel length (the distance between the source and drain) becomes so short that the electric field from the drain begins to influence the behaviour of the channel. This can lead to threshold voltage roll-off, reduced gate control, and increased susceptibility to leakage currents, all of which degrade the performance of the transistor.

### 2.2 SHORT-CHANNEL EFFECTS

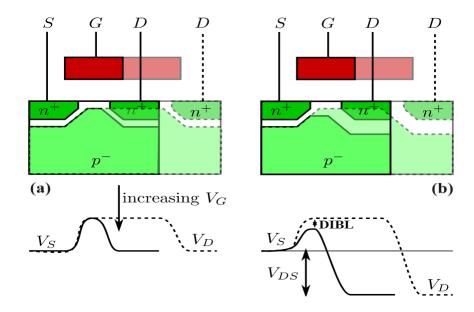

#### 2.2.1 Drain-Induced Barrier Lowering (DIBL)

Drain-induced barrier Lowering (DIBL) is a short-channel effect in MOSFETs where the threshold voltage decreases as the drain voltage increases, as shown in **Figure 2.1**. This occurs because the electric field from the drain penetrates into the channel near the source, lowering the energy barrier for carriers to flow.

As a result, the gate loses some control over the channel, leading to increased leakage currents and degraded device performance [12]. DIBL becomes more pronounced as MOSFETs are scaled to smaller dimensions, negatively affecting power efficiency and off-state behaviour by allowing current to flow even when the device should be off [8,9].

Figure 2.1: Drain-induced barrier lowering [11]. 2.2.2 Surface Scattering

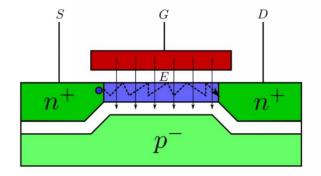

Surface scattering occurs in MOSFETs when charge carriers (electrons or holes) move through the channel and collide with the rough surface of the semiconductor-oxide interface expressed in **Figure 2.2**. As MOSFETs are scaled down and the channel becomes thinner, the influence of this surface becomes more pronounced. These collisions scatter the carriers, reducing their mobility and leading to lower current drive and performance degradation [13]. Surface scattering becomes especially significant in short-channel devices, where the proximity of the channel to the surface is greater, making it a critical factor in limiting device speed and efficiency in advanced semiconductor technologies.

Figure 2.2: Surface Scattering [31].

#### 2.2.3 Threshold Voltage (Vth) Roll-off

Threshold voltage roll-off is a short-channel effect in MOSFETs, where the threshold voltage ( $V_{th}$ ) decreases as the channel length shrinks. In long-channel MOSFETs, the gate has strong control over the channel, keeping the threshold voltage stable. However, in short-channel devices, the electric fields from the drain and source influence the channel potential more significantly, weakening the gate's control. This causes the threshold voltage to decrease with reduced channel length, resulting in an earlier turn-on of the transistor and increased leakage currents. Threshold voltage roll-off negatively impacts performance and power efficiency in highly scaled devices [14].

#### **2.2.4 Impact Ionization**

Impact ionization occurs in MOSFETs when high electric fields, typically near the drain in short-channel devices, accelerate charge carriers (electrons or holes) to high velocities, as shown in **Figure 2.3.** These energetic carriers can collide with atoms in the semiconductor lattice, generating additional electron-hole pairs **[15]**. This process results in an increase in

current beyond what is controlled by the gate voltage and can lead to several adverse effects, such as:

- Increased leakage current: Unwanted current due to the creation of extra charge carriers.

- Hot carrier injection: Damage to the gate oxide as high-energy carriers are injected into it.

- > **Device reliability issues:** Long-term degradation of the MOSFET.

Impact ionization becomes more significant as MOSFETs are scaled down and electric fields intensify.

Figure 2.3: Impact Ionization [11].

## **2.2.5 Hot-Carrier Effects**

Figure 2.4: Hot Carrier Effects in NMOS [11].

The hot carrier effect in MOSFETs occurs when charge carriers (electrons or holes) gain significant kinetic energy from the electric field within the device, as shown in **Figure 2.4**. This energy can lead to carrier scattering, resulting in increased leakage currents and reduced device performance. As carriers are accelerated through the channel, they may gain enough energy to overcome potential barriers at the oxide-semiconductor interface, leading to impact ionization. This effect can cause device degradation, threshold voltage shifts, and eventual failure, particularly in high-frequency and high-power applications. To mitigate this, device design and fabrication techniques are employed to reduce electric fields and enhance reliability **[16]**.

## 2.3 WAYS TO OVERCOME SHORT-CHANNEL EFFECTS

## Figure 2.5: Different ways to overcome SCEs in nano-scale MOSFET.

These SCEs should be minimized or eliminated to preserve the electrical long-channel behavior of a physical short-channel device, given that they impede device operation and performance. Literature from recent years suggests that the use of novel device designs and engineering techniques (as presented in **Figure 2.5**) may diminish these short-channel effects.

## 2.3.1 Engineering Schemes

Researchers have developed various engineering schemes to mitigate the impact of SCEs on transistor performance. Here are some engineering schemes to address SCEs.

#### 2.3.1.1 Junctionless Engineering

A junctionless field effect transistor (JLFET) is a transistor that functions in its channel area without a traditional p-n junction, as depicted in **Figure 2.6** [17]. They use a single-gated silicon nanowire structure instead. This nanowire serves as the current flow channel, and the gate terminal regulates the current flow by controlling the conductivity of the nanowire. When a positive gate voltage is applied, it draws negatively charged carriers (electrons) to the nanowire's surface, forming an accumulation region. This accumulation region improves the nanowire's conductivity, enabling current to pass between the source and drain terminals. When a negative gate voltage is supplied, the negatively charged carriers carriers are repelled, resulting in a depletion zone at the nanowire's surface.