# Design and Implementation of Immittance Circuits Using Active Building Blocks

A Thesis Submitted In Partial Fulfillment of the Requirement for the Degree of

# **DOCTOR OF PHILOSOPHY**

by

Navnit Kumar (Enrollment No. 2K20/PHDEC/07)

Under the Supervision of

Dr. Manjeet Kumar Assistant Professor (ECE) DTU, Delhi Prof. Neeta Pandey Professor (ECE) DTU, Delhi

**Department of Electronics and Communication Engineering**

# **DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering) Shahbad Daulatpur, Main Bawana Road, Delhi – 110042. India

November, 2024

**DELHI TECHNOLOGICAL UNIVERSITY** (Formerly Delhi College of Engineering) Shahbad Daultpur, Main Road, Delhi – 42

#### **CANDIDATE'S DECLARATION**

I Navnit Kumar hereby certify that the research work, which is being presented in the thesis, entitled Design and Implementation of Immittance Circuits Using Active Building Blocks in partial fulfillment of requirements of the award of the degree of Doctor of Philosophy, submitted in the Department of Electronics and Communication, Delhi Technological University is an authentic record of my own work carried out during the period from August 2020 to November 2024 under the supervision of Dr. Manjeet Kumar and Prof. Neeta Pandey.

The matter presented in the thesis work has not been submitted by me for the award of any other degree or any other Institute.

Navnit Kumar (2K20/PHDEC/07) Department of ECE Delhi Technological University Delhi-110042, India

This is to certify that the student has incorporated all the corrections suggested by the examiners in the thesis and the statement made by the candidate is correct to the best of our knowledge.

**Dr. Manjeet Kumar** Supervisor, Department of ECE Delhi Technological University Delhi-110042, India.

Prof. Neeta Pandey Co-Supervisor, Department of ECE Delhi Technological University Delhi-110042, India.

**DELHI TECHNOLOGICAL UNIVERSITY** (Formerly Delhi College of Engineering) Shahbad Daultpur, Main Road, Delhi – 42

#### **CERTIFICATE BY SUPERVISOR(s)**

Certified that Navnit **Kumar** (enrollment no. 2K20/PHDEC/07) has carried out their search work presented in this thesis entitled "Design and Implementation of Immittance Circuits Using Active Building Blocks" for the award of Doctor of Philosophy from Department of Electronics and Communication Delhi Technological University, Delhi, under our supervision. The thesis embodies results of original work, and studies are carried out by the student himself, and the contents of the thesis do not form the basis for the award of any other degree to the candidate or to anybody else from this or any other University/Institution.

Dr. Manjeet Kumar Supervisor, Department of ECE Delhi Technological University Delhi-110042, India. Prof. Neeta Pandey Co-Supervisor, Department of ECE Delhi Technological University Delhi-110042, India.

Date:

#### ABSTRACT

The discipline of analog signal processing has experienced significant growth and development during the past few decades. The literature describes a variety of voltage-mode and current-mode active components for carrying out analog signal processing tasks. Nevertheless, the analog signal processing circuits in the current domain offers advantages such as enhanced bandwidth, less circuit complexity, expanded dynamic, low power consumption, and high speed. Therefore, the current-mode approach is widely recognized as a viable alternative to conventional voltage-mode circuits.

The immittance circuits have numerous applications in microelectronics, communication, analog signal processing, instrumentation, and measurement. There are limitations of realizing traditional components namely inductor and resistor in microelectronics circuits, such as occupying significant chip space, being heavy, expensive, and lacking tunability. It makes the active immittance circuits, a prominent area of study. This thesis deals with design of immittance emulators and their applications.

A variety of integer order immittance emulators have been developed in the literature. However, there is a lean presence of emulators that simultaneously fulfil the following criterions: tunability, no matching constraint, less components, low power consumption, low chip area, and working in positive and negative mode without topological changes. In addition, it is pertinent to mention here that to obtain positive and negative modes the topological change is not possible once the circuit is laid down and fabricated. Also, if two different circuits are realized in IC form for positive and negative immittances, the resulting silicon footprint would require more. Hence, Current Conveyor Transconductance Amplifier (CCTA) based a grounded and floating immittance emulators are developed that provides both positive and negative immittances through appropriate setting of MOS switches. The proposed topology does not require any component matching, thus making it suitable for integration viewpoint. Further, these immittance emulators are tuned electronically via bias current of CCTA. The proposed immittance circuit is used to implement the fifth order low pass filter, and capacitance cancellation circuit.

Nowadays, fractional order circuits gain considerable attention among researchers due to the extra degree of freedom to control the phenomena of the system. The fractional order inductor circuits reported in literature are limited in terms of large number of active and passive components, tunability, slew rate, operating frequency, and high-power dissipation. Hence, Operational Transconductance Amplifier (OTA) based electronically tunable grounded and floating fractional order inductor circuits are also developed. These circuits can flip between positive and negative modes without modifying their architecture. The usefulness of the proposed positive fractional order high pass ladder filter. The usefulness of the proposed negative fractional inductance circuit is demonstrated through a fractional inductance cancellation circuit.

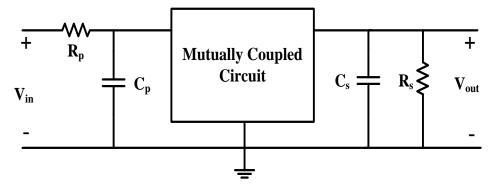

The synthetic transformer (ST) circuit or Mutual Coupled Circuit (MCC) is yet another application of immittance circuit. It is frequently used in circuits for instrumentation, measurement, analog communications, and signal processing. It is observed that MCC circuit featuring mutual inductance in four different pairs like passive transformer is not available in open literature. To fill this gap, a CCTA based tunable floating MCC is designed which can be configured in four different pairs of mutual coupled circuits through appropriate setting of MOS switches. The proposed MCC does not require component matching condition. Self-inductance, mutual inductance, and resonant frequency can be tuned by bias current of CCTA. A double tuned band pass filter is shown as an application.

Furthermore, memristor is the fourth fundamental element in circuit theory after resistor, capacitor, and inductor. It is gaining considerable attention among researchers due to its high-density storage property. It is a non-linear device provides relation between electric charge (q) and magnetic flux ( $\varphi$ ). A solid state memristor is not available in the market due to its high price and difficult manufacturing process. Hence, charge and flux controlled memristor emulators are developed employing Inverting Current Conveyor Transconductance Amplifier (ICCTA). In addition, both proposed circuits do not include intricate components such as analog multiplier circuits, passive inductors, and analog to digital converter circuits in their design, which is beneficial in terms of integrated circuit implementation point of view. Further, the effectiveness of the developed circuits is validated using meminductor circuits, and memristor-based active filters.

The behavior of the proposed circuits is analyzed in the presence of parasites that may appear in practice. The operation has been examined through SPICE simulations and post-layout simulations are also included in the thesis. Corner and Monte-Carlo analysis is performed to assess the robustness of the various proposals.

### ACKNOWLEDGEMENT

I take this opportunity to express my profound gratitude and deep regards to my supervisors Dr. Manjeet Kumar (Assistant Professor) and Prof. Neeta Pandey (Professor), Department of Electronics and Communication Engineering, DTU Delhi for their exemplary guidance, monitoring, and constant encouragement throughout the research work. The blessing, help and guidance given by him from time to time shall carry me a long way in the journey of life on which I am about to embark.

I avail myself of this proud privilege to express my regards to Prof. O. P. Verma (HOD) and all the faculties of department of electronics and communication engineering at DTU Delhi for empathizing and providing all the necessary facilities throughout the work.

I also take this opportunity to express a deep sense of gratitude to VC, Dean academic affairs, Registrar and all others for the good infrastructure which was vitally necessary for the research work. All the facilities I utilized helped me a lot in completing this task through various stages.

I am delighted to thank my family for their constant support and encouragement throughout my life. My mother and father are inspirations to my life, and I hereby strongly acknowledge them for their support in my entire life and for my education.

NAVNIT KUMAR

### **CONTENTS**

#### **CHAPTER DESCRIPTION**

### PAGE NUMBER

| CANDIDATE'S DECLARATION              | i     |

|--------------------------------------|-------|

| <b>CERTIFICATE BY SUPERVISOR(s)</b>  | ii    |

| ABSTRACT                             | iii   |

| ACKONWLEDGEMENT                      | vi    |

| LIST OF TABLES                       | Х     |

| LIST OF FIGURES                      | xii   |

| <b>ABBREVIATIONS &amp; NOTATIONS</b> | xviii |

#### **CHAPTER 1 INTRODUCTION**

| 1.1 Literature survey   | 2  |

|-------------------------|----|

| 1.2 Research gaps       | 9  |

| 1.3 Research Objectives | 10 |

| 1.4 THESIS organization | 10 |

#### **CHAPTER 2 ANALOG BUILDING BLOCKS**

| 2.1 Operational transconductance amplifier                |    |

|-----------------------------------------------------------|----|

| 2.1.1 Non-ideal model of OTA                              | 14 |

| 2.1.2 Verification of OTA                                 | 15 |

| 2.2 Current conveyor transconductance amplifier           | 16 |

| 2.2.1 Non-ideal model of CCTA                             | 17 |

| 2.2.2 Verification of CCTA                                | 17 |

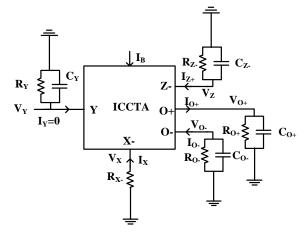

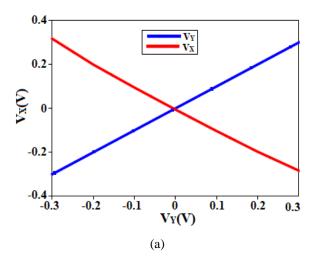

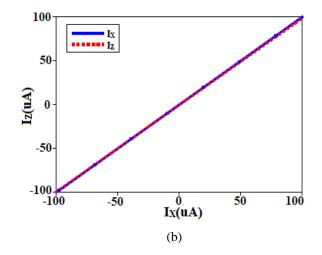

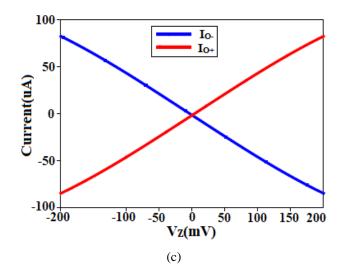

| 2.3 Inverting current conveyor transconductance amplifier | 19 |

| 2.3.1 Non-ideal model of ICCTA                            | 20 |

| 2.3.2 Verification of ICCTA                               | 21 |

# **CHAPTER DESCRIPTION**

| 2.4 Current feedback operational amplifier              | 22 |

|---------------------------------------------------------|----|

| 2.4.1 Non-ideal model of CFOA                           | 23 |

| 2.4.2 Verification of CFOA                              | 24 |

| 2.5 Summary                                             | 25 |

| CHAPTER 3 INTEGER ORDER IMMITTANCE EMULATORS            |    |

| 3.1 Proposed grounded integer order immittance circuit  | 26 |

| 3.1.1 Non-ideal Analysis                                | 28 |

| 3.1.2 Results and discussion                            | 29 |

| 3.1.3 Application                                       | 32 |

| 3.2 Proposed floating integer order immittance circuits | 34 |

| 3.2.1 Proposed floating immittance circuit 1            | 34 |

| 3.2.1.1 Non-ideal analysis                              | 36 |

| 3.2.1.2 Results and discussion                          | 36 |

| 3.2.1.3 Application                                     | 39 |

| 3.2.2 Proposed floating immittance circuit 2            | 40 |

| 3.2.2.1 Non-ideal analysis                              | 42 |

| 3.2.2.2 Results and discussion                          | 43 |

| 3.2.2.3 Applications                                    | 46 |

| CHAPTER 4 FRACTIONAL ORDER INDUCTOR CIRCUIT             |    |

| 4.1 Proposed grounded fractional order inductor circuit | 50 |

| 4.2 Proposed floating fractional order inductor circuit | 51 |

| 4.3 Non-ideal analysis                                  | 52 |

| 4.4 Results and discussion                              | 53 |

| 4.5 Applications                                        | 58 |

| 4.6 Comparison                                          | 63 |

| 4.7 Summary                                             | 64 |

### **CHAPTER DESCRIPTION**

#### CHAPTER 5 CCTA BASED MUTUALLY COUPLED CIRCUIT

| 5.1 Proposed mutually coupled circuit               | 65  |

|-----------------------------------------------------|-----|

| 5.2 Non-ideal analysis                              | 69  |

| 5.3 Application                                     | 73  |

| 5.4 Results and discussion                          | 74  |

| 5.5 Comparison                                      | 80  |

| 5.6 Summary                                         | 81  |

| CHAPTER 6 FLUX & CHARGE CONTROLLED MERMRISTORS      |     |

| 6.1 Flux controlled memristor emulator              | 82  |

| 6.1.1 Proposed flux controlled memristor emulator   | 82  |

| 6.1.1.1 Non-ideal analysis                          | 83  |

| 6.1.1.2 Results and discussion                      | 85  |

| 6.1.1.3 Applications                                | 88  |

| 6.2 Charge controlled memristor emulator            | 89  |

| 6.2.1 Proposed charge controlled memristor emulator | 89  |

| 6.2.1.1 Non-ideal analysis                          | 91  |

| 6.2.1.2 Results and discussion                      | 92  |

| 6.2.1.3 Application                                 | 95  |

| 6.3 Comparison                                      | 97  |

| 6.4 Summary                                         | 98  |

| <b>CHAPTER 7 CONCLUSIONS &amp; FUTURE SCOPES</b>    |     |

| 7.1 Conclusions                                     | 100 |

| 7.2 Future scopes                                   | 102 |

| REFERENCES                                          | 103 |

| LIST OF PUBLICATIONS & THEIR PROOFS                 |     |

#### PLAGIARISM REPORT

# LIST OF TABLES

### TABLE TITLEPAGE NUMBER

| 2.1 | Aspect ratio of transistors of OTA                                        | 15 |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | Aspect ratio of transistors of CCTA                                       | 18 |

| 2.3 | Aspect ratio of transistors of ICCTA                                      | 21 |

| 3.1 | Different configurations of the proposed CCTA based grounded              | 27 |

|     | immittance                                                                |    |

| 3.2 | Active grounded immittances value with respect component value and        | 29 |

|     | bias current ( $I_B = 200 \ \mu A$ )                                      |    |

| 3.3 | Different configurations of the proposed CCTA based floating immittance   | 35 |

|     | circuit                                                                   |    |

| 3.4 | Active floating immittances value with respect component values and bias  | 37 |

|     | current ( $I_B = 200 \mu A$ )                                             |    |

| 3.5 | Different configurations of the proposed CCTA based floating immittance   | 41 |

|     | circuit                                                                   |    |

| 3.6 | Active floating immittances value with respect component value and bias   | 44 |

|     | current ( $I_B = 40 \ \mu A$ )                                            |    |

| 3.7 | Comparison of positive and negative immittances with the proposed circuit | 48 |

|     | using CCTA                                                                |    |

| 4.1 | Comparison of the developed fractional order inductor with previously     | 63 |

|     | published ones                                                            |    |

| 5.1 | MCC is configured in four different pairs of mutually coupled circuits    | 68 |

| 5.2 | Self-inductance and mutual inductance with parasitic components of        | 71 |

|     | CCTA for four different configurations                                    |    |

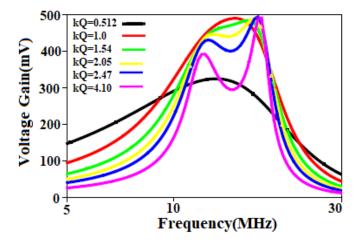

| 5.3 | Variation in bandwidth and voltage gain of DTBPF with respect to          | 79 |

|     | variation in Q while $k$ is fixed                                         |    |

| 5.4 | Comparison of performance of DTBPF of published MCC with DTBPF | 81 |

|-----|----------------------------------------------------------------|----|

|     | of the proposed MCC                                            |    |

6.1 Comparison of the proposed memristor emulator with existing memristor 98 emulator

# **LIST OF FIGURES**

### FIGURE TITLE PAGE NUMBER

| 2.1  | OTA (a) circuit symbol (b) MOS based design                                                  | 14 |

|------|----------------------------------------------------------------------------------------------|----|

| 2.2  | Non-ideal model of OTA                                                                       | 14 |

| 2.3  | DC characteristic of OTA                                                                     | 15 |

| 2.4  | Frequency response of OTA                                                                    | 15 |

| 2.5  | CCTA (a) circuit symbol (b) MOS based implementation of CCTA                                 | 16 |

| 2.6  | Non-ideal model of CCTA                                                                      | 17 |

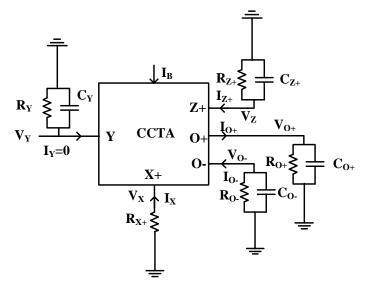

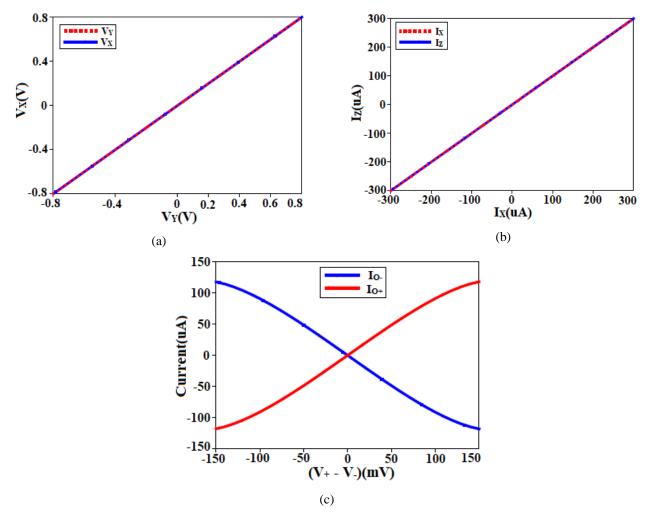

| 2.7  | Port relations of CCTA. (a) $V_X = V_Y$ , (b) $I_Z = I_X$ , and (c) $I_{0\pm} = \pm g_m V_Z$ | 18 |

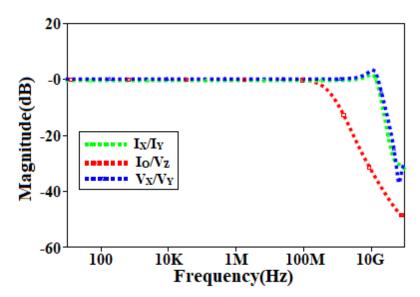

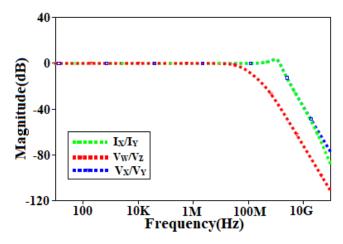

| 2.8  | Frequency response of CCTA                                                                   | 19 |

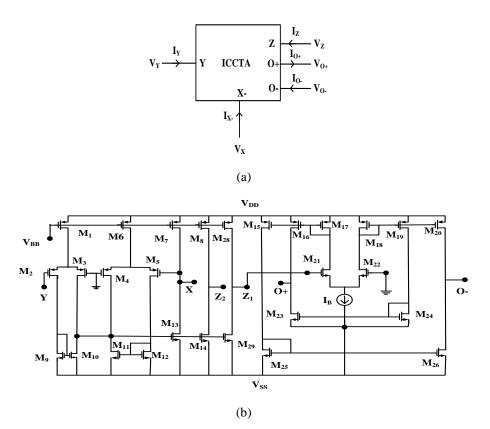

| 2.9  | ICCTA (a) circuit Symbol and (b) CMOS based realization                                      | 20 |

| 2.10 | Non-ideal model of ICCTA                                                                     | 20 |

| 2.11 | Port relations of ICCTA. (a) $V_X = -V_Y$ , (b) $I_Z = I_X$ , and (c) $I_{0\pm} =$           | 22 |

|      | $\pm g_m V_Z$                                                                                |    |

| 2.12 | Frequency response of ICCTA                                                                  | 22 |

| 2.13 | Circuit Symbol of CFOA                                                                       | 23 |

| 2.14 | Non-ideal model of CFOA                                                                      | 23 |

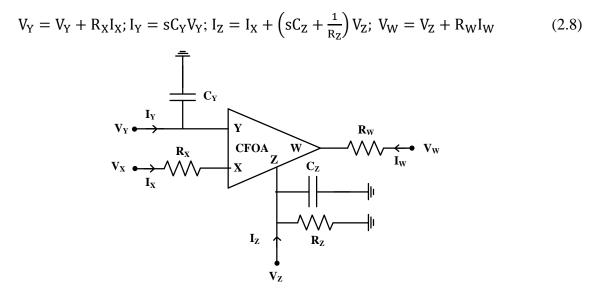

| 2.15 | Port relations of CFOA. (a) $V_X = V_Y$ , (b) $I_Z = I_X$ , and (c) $V_Z = V_W$              | 24 |

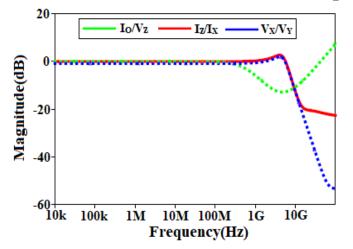

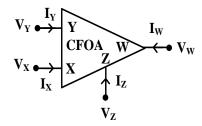

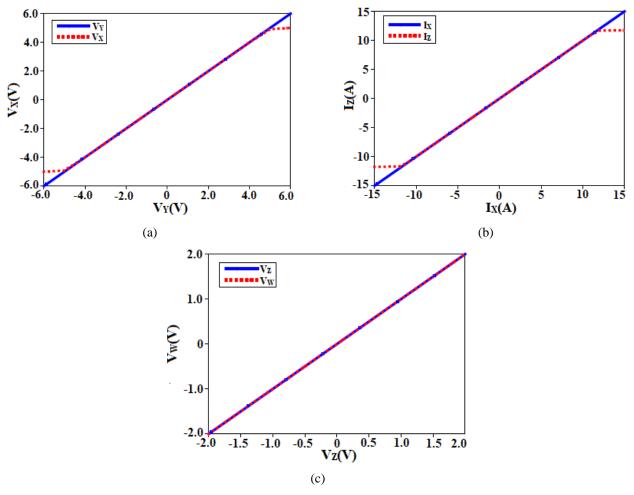

| 2.16 | Frequency response of CFOA                                                                   | 25 |

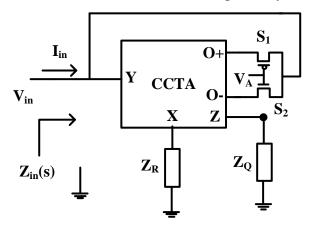

| 3.1  | Proposed CCTA based grounded immittance circuit                                              | 26 |

| 3.2  | Proposed grounded immittance circuit with parasitic components.                              | 28 |

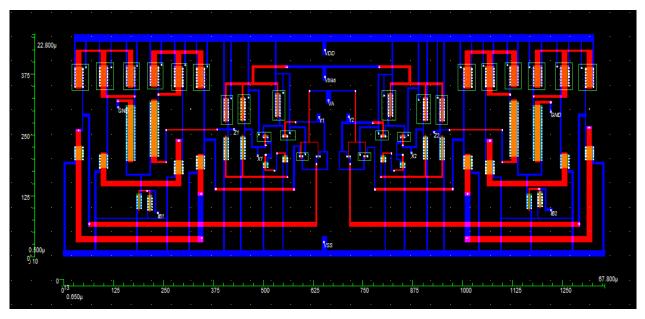

| 3.3  | Layout of grounded immittance                                                                | 30 |

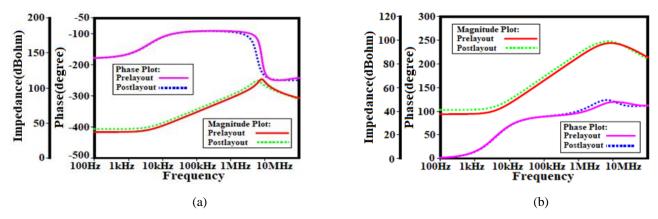

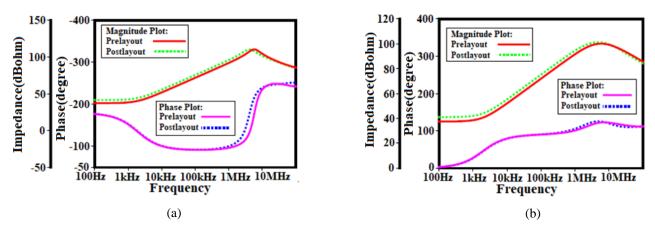

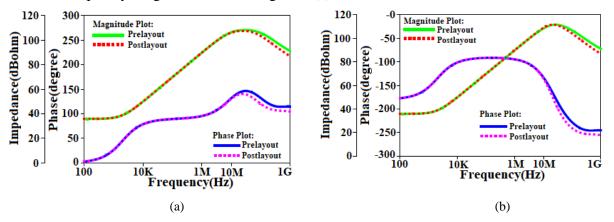

| 3.4  | Frequency response of proposed grounded integer order (a) negative                           | 31 |

|      | inductor, and (b) positive inductor                                                          |    |

| 3.5  | Frequency response of proposed grounded (a) negative resistor, and (b)                       | 31 |

|      | negative capacitor                                                                           |    |

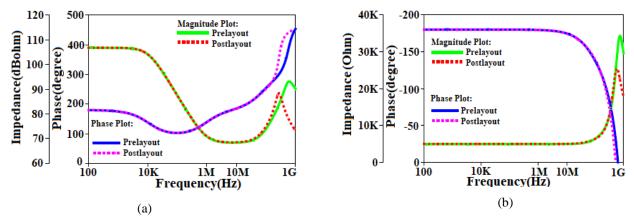

| 3.6  | Magnitude response of proposed grounded inductor for variation in (a)                        | 32 |

|      | passive component, and (b) temparatures                                                      |    |

|      |                                                                                              |    |

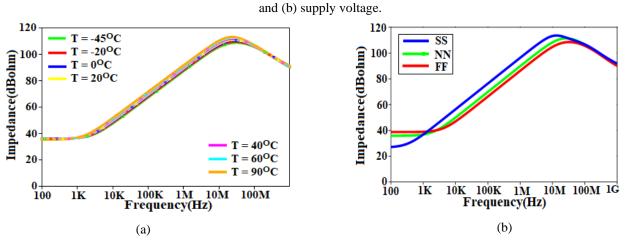

| 3.7  | Magnitude response of proposed grounded inductor for variation in (a)           | 32 |

|------|---------------------------------------------------------------------------------|----|

|      | supply voltages, and (b) corner analysis                                        |    |

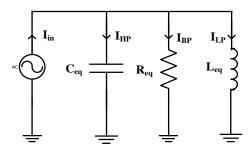

| 3.8  | 2 <sup>nd</sup> order current mode multi-function filter circuit                | 32 |

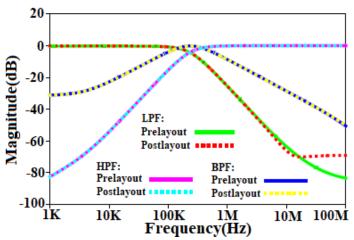

| 3.9  | Frequency response of current mode 2 <sup>nd</sup> order multi-function filter. | 33 |

| 3.10 | Proposed floating immittance circuit 1                                          | 34 |

| 3.11 | Proposed floating immittance circuit 1 with parasitic components                | 36 |

| 3.12 | Frequency response of proposed floating inductor (a) negative, and (b)          | 37 |

|      | positive                                                                        |    |

| 3.13 | Frequency response of proposed floating (a) negative capacitor, and (b)         | 37 |

|      | negative resistor                                                               |    |

| 3.14 | Magnitude response of proposed grounded inductor for variation in (a)           | 38 |

|      | passive components, and (b) temparatures                                        |    |

| 3.15 | Magnitude response of proposed grounded inductor for variation in (a)           | 39 |

|      | supply voltage, and (b) corner analysis                                         |    |

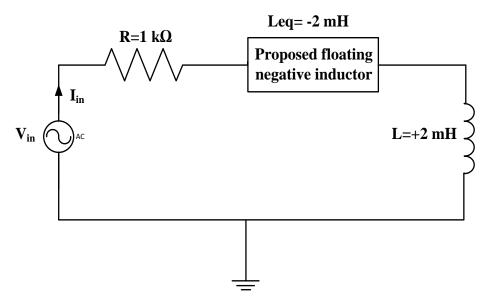

| 3.16 | Inductance cancellation using proposed inductor                                 | 39 |

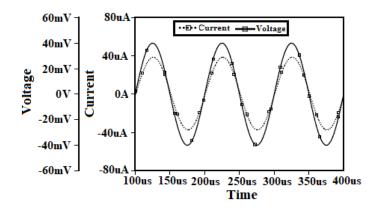

| 3.17 | Transient response of the inductance cancellation                               | 40 |

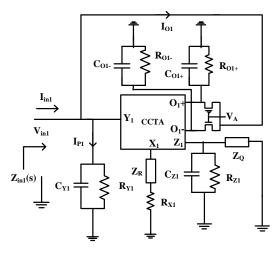

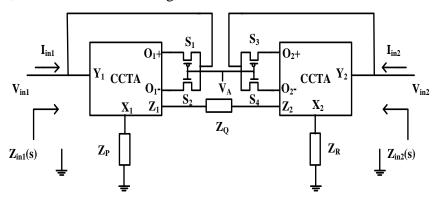

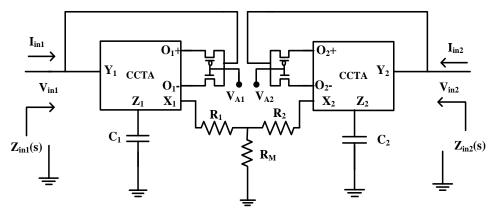

| 3.18 | Proposed CCTA based floating immittance circuit 2                               | 40 |

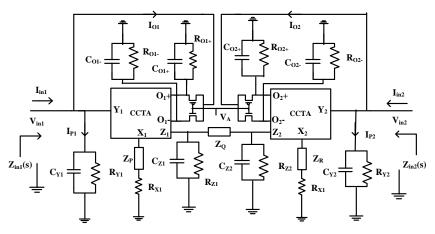

| 3.19 | Proposed CCTA based floating immittance circuit 2 with parasitic                | 42 |

|      | components                                                                      |    |

| 3.20 | Layout of floating immittance circuit                                           | 43 |

| 3.21 | Frequency response of the proposed floating inductor (a) positive, and (b)      | 44 |

|      | negative                                                                        |    |

| 3.22 | Frequency response of the proposed floating negative (a)capacitor, and          | 45 |

|      | (b) resistor                                                                    |    |

| 3.23 | Magnitude response of proposed grounded inductor for variation in (a)           | 45 |

|      | passive components, and (b) supply voltage                                      |    |

| 3.24 | Magnitude response of proposed grounded inductor for variation in (a)         | 45 |

|------|-------------------------------------------------------------------------------|----|

|      | temparatures, and (b) corner analysis                                         |    |

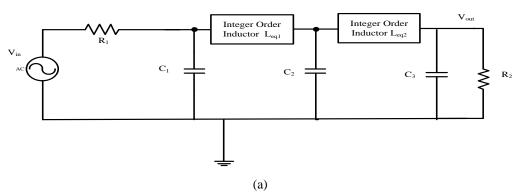

| 3.25 | Fifth order low pass filter. (a) circuit, and (b) response of the fifth order | 47 |

|      | low pass filter                                                               |    |

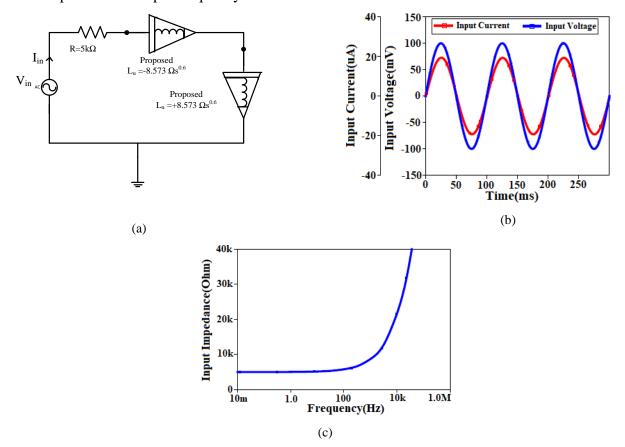

| 3.26 | (a) Capacitance cancellation circuit. (b) Input voltage and input current     | 47 |

|      | waveform. (c) Output voltage and output current waveform                      |    |

| 4.1  | Proposed grounded positive and negative fractional order inductor             | 50 |

| 4.2  | Proposed floating positive and negative fractional order inductor             | 51 |

| 4.3  | Proposed circuit with parasitic components                                    | 52 |

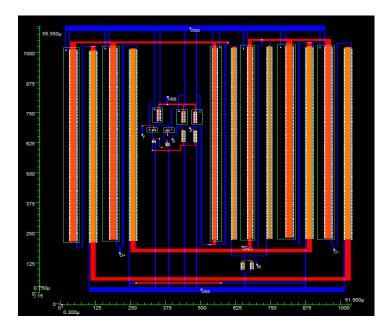

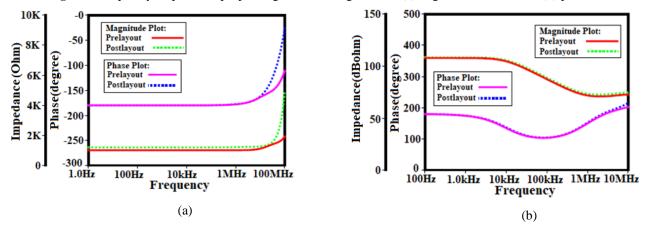

| 4.4  | Layout of proposed circuit                                                    | 54 |

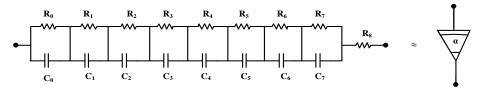

| 4.5  | RC ladder structure for fractional capacitor                                  | 54 |

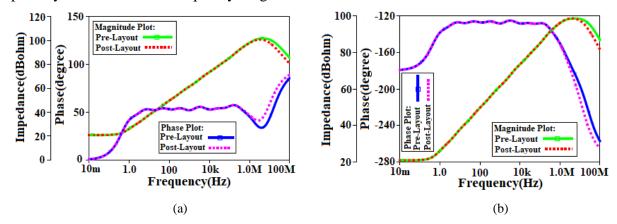

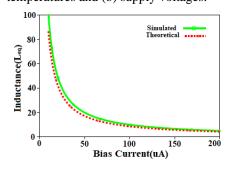

| 4.6  | Frequency response of proposed fractional order inductor (a) positive         | 55 |

|      | grounded, (b) negative grounded, (c) positive floating, and (d) negative      |    |

|      | floating                                                                      |    |

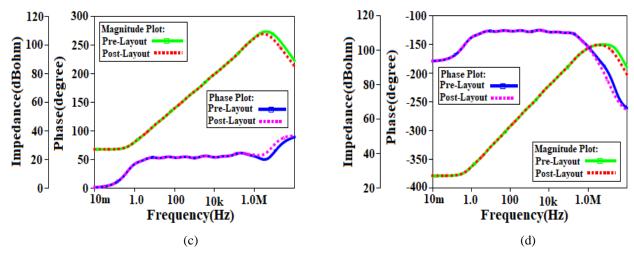

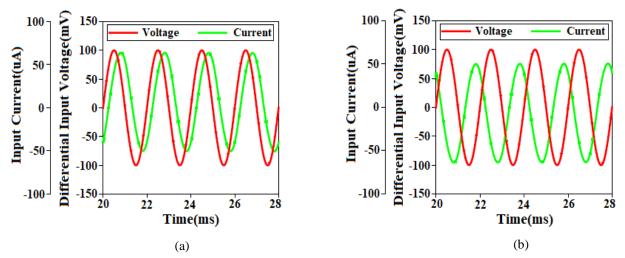

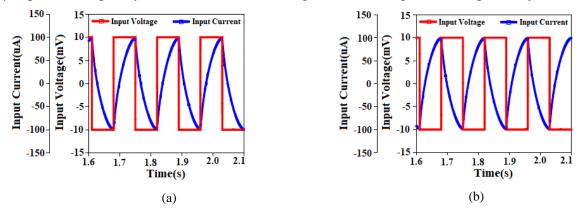

| 4.7  | Transient response of floating fractional order inductor. (a) positive, and   | 55 |

|      | (b) negative                                                                  |    |

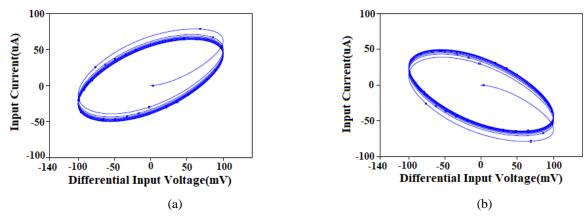

| 4.8  | Lissajous pattern of floating fractional order inductor (a) positive, and (b) | 56 |

|      | negative                                                                      |    |

| 4.9  | The applied square input voltage and corresponding triangular (for $\alpha =$ | 56 |

|      | 0.6) input current response for (a) grounded positive fractional order        |    |

|      | inductor, and (b) grounded negative fractional order inductor                 |    |

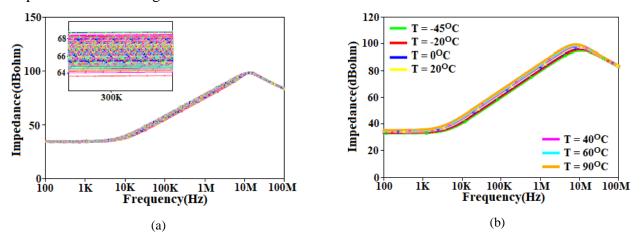

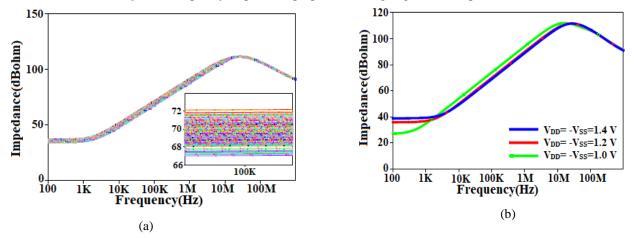

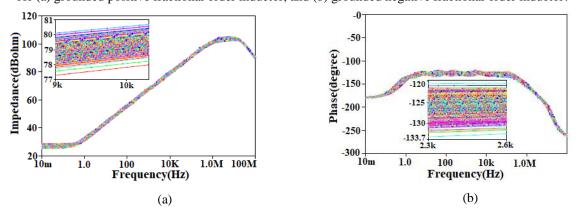

| 4.10 | Monte Carlo analysis for grounded negative fractional inductor (a)            | 56 |

|      | magnitude, and (b) phase                                                      |    |

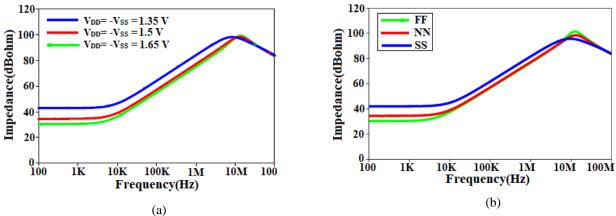

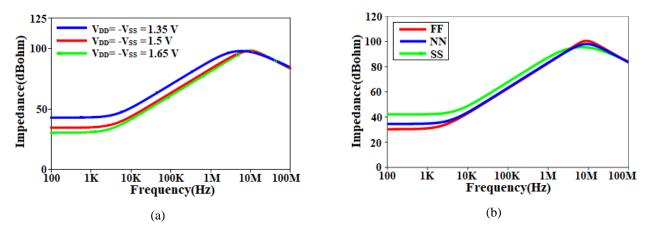

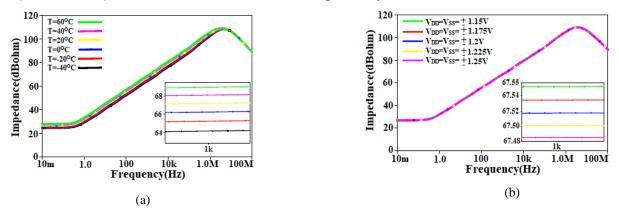

| 4.11 | Magnitude response of proposed grounded positive fractional inductor          | 57 |

|      | for variation in (a) temperatures and (b) supply voltage                      |    |

| 4.12 | Magnitude response of proposed grounded positive fractional inductor          | 57 |

|      | for different bias cirrent of OTA                                             |    |

|      |                                                                               |    |

| 4.13 | Corner analysis of proposed grounded positive fractional inductor             | 58 |

|------|-------------------------------------------------------------------------------|----|

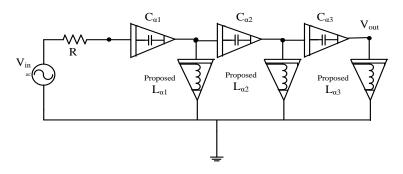

|      | Fractional order high-pass ladder filter                                      |    |

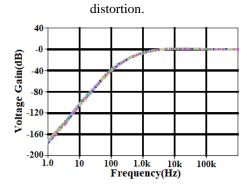

| 4.14 | Fractional order high-pass ladder filter                                      | 58 |

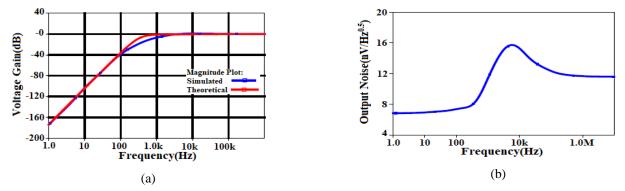

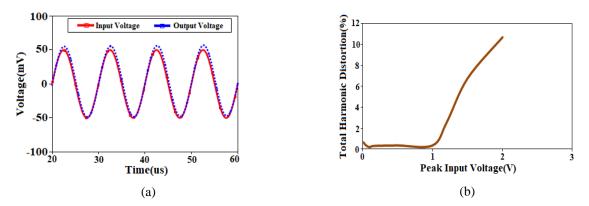

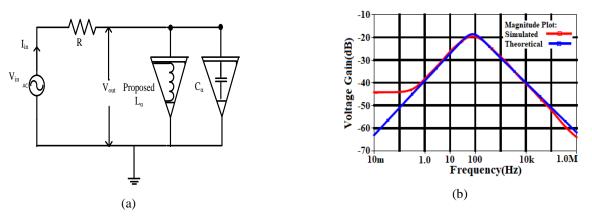

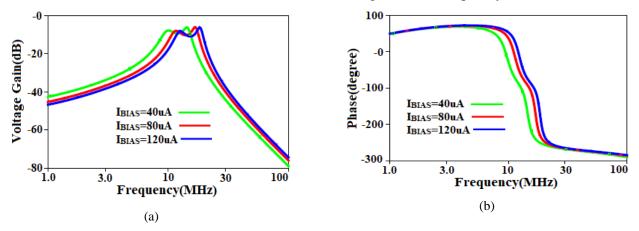

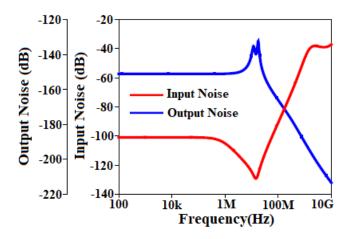

| 4.15 | Response of high pass fractional ladder filter. (a) Voltage gain (b) Output   | 59 |

|      | noise ladder                                                                  |    |

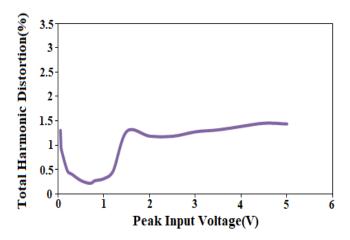

| 4.16 | Response of fractional order high pass ladder filter. (a) Transient analysis, | 60 |

|      | and (b) total harmonic distortion                                             |    |

| 4.17 | Monte Carlo analysis of Voltage gain of fractional order high pass ladder     | 60 |

|      | filter                                                                        |    |

| 4.18 | Fractional order band pass filter. (a) circuit, and (b) voltage gain          | 61 |

| 4.19 | Response of fractional band pass filter. (a) Monte Carlo analysis, and (b)    | 61 |

|      | output noise                                                                  |    |

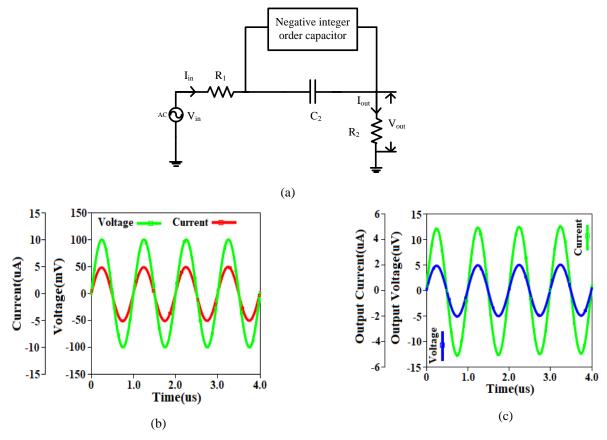

| 4.20 | (a)Fractional inductance cancelation circuit. (b) Transient response of       | 62 |

|      | fractional Inductance cancellation circuit. (c) Frequency response of         |    |

|      | fractional inductance cancelation circuit                                     |    |

| 5.1  | Proposed mutually coupled circuit                                             | 65 |

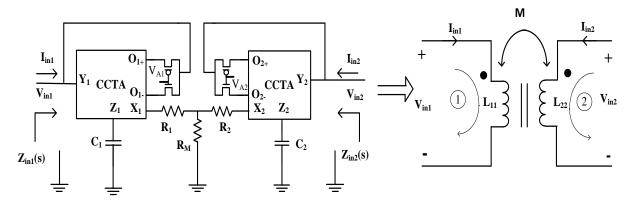

| 5.2  | Proposed MCC and its equivalent transformer circuit for $V_{A1} = V_{A2} =$   | 66 |

|      | High                                                                          |    |

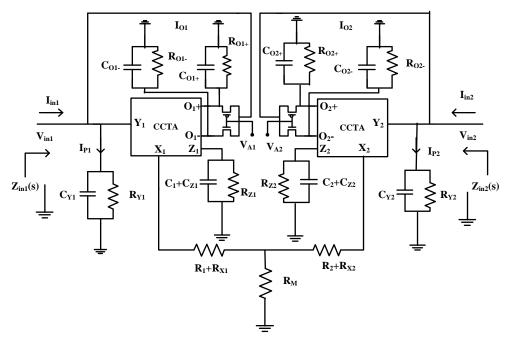

| 5.3  | Proposed MCC with parasitic components                                        | 69 |

| 5.4  | Double tuned band pass filter circuit                                         | 73 |

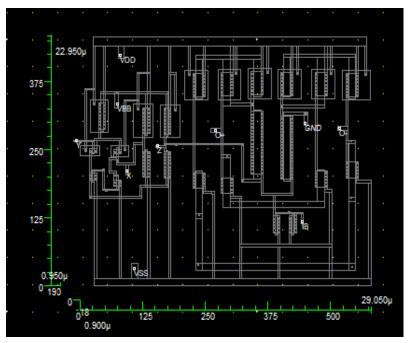

| 5.5  | Layout of CCTA                                                                | 74 |

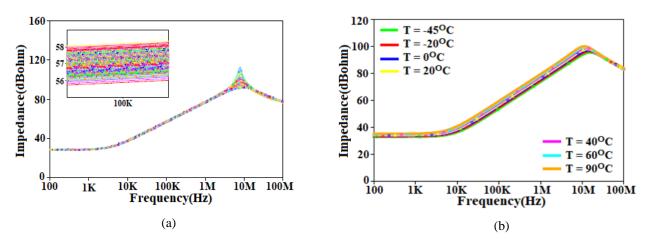

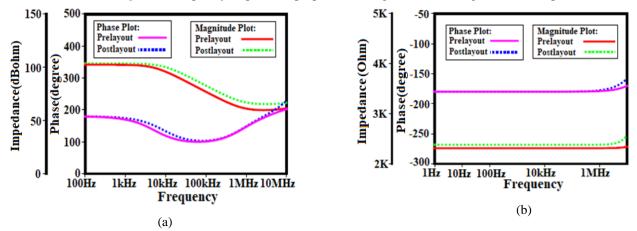

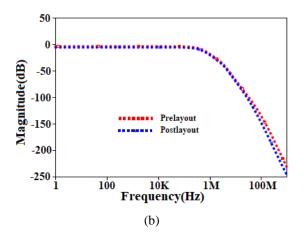

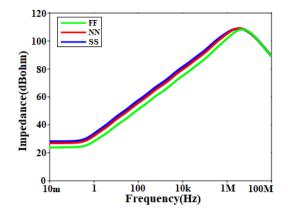

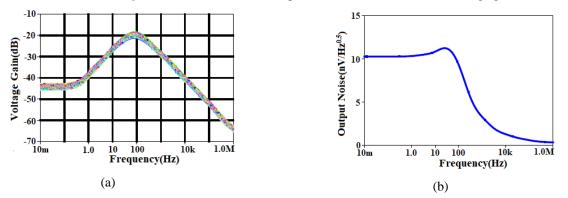

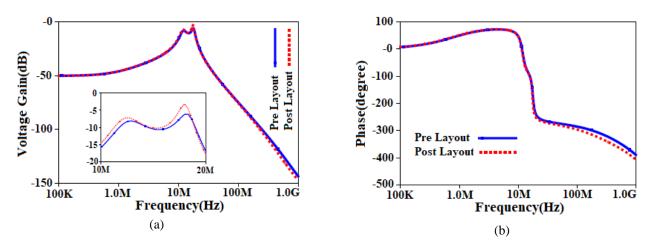

| 5.6  | Pre-layout and post-layout plot of frequency response of DTBPF circuit        | 75 |

|      | (a) magnitude, and (b) phase                                                  |    |

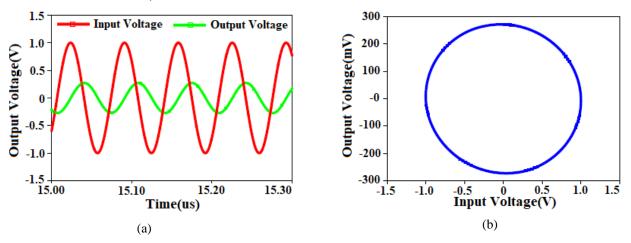

| 5.7  | (a)Time domain response of DTBPF circuit, and (b) corresponding               | 75 |

|      | Lissajous pattern                                                             |    |

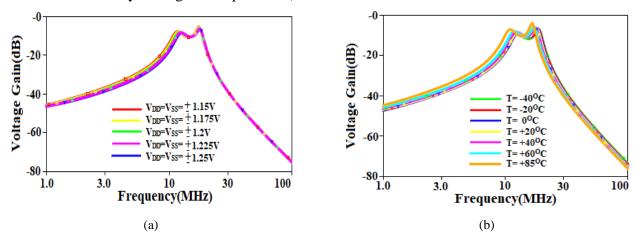

| 5.8  | Frequency response of DTBPF for different (a) supply voltage, and (b)         | 76 |

|      | temperature                                                                   |    |

|      |                                                                               |    |

\_\_\_\_\_

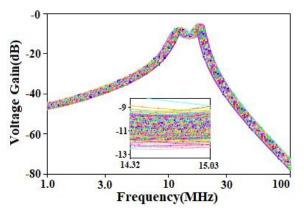

| 5.9  | Monte Carlo analysis of frequency response of DTBPF                     | 76 |

|------|-------------------------------------------------------------------------|----|

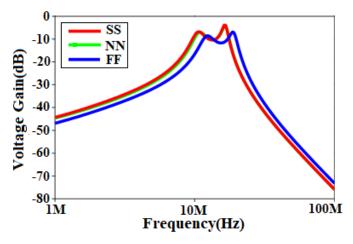

| 5.10 | Corner analysis of frequency response of DTBPF                          | 77 |

| 5.11 | Frequency response of DTBPF for different value of kQ                   | 78 |

| 5.12 | Frequency response of double tuned band pass filter for different bias  | 79 |

|      | current. (a) Magnitude, and (b) phase                                   |    |

| 5.13 | Noise response of proposed synthetic transformer                        | 80 |

| 5.14 | Total harmonic distortion of output voltage of band pass filter circuit | 80 |

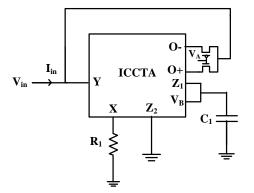

| 6.1  | Proposed flux controlled grounded memristor emulator                    | 82 |

| 6.2  | Proposed memristor emulator with parasitic components                   | 83 |

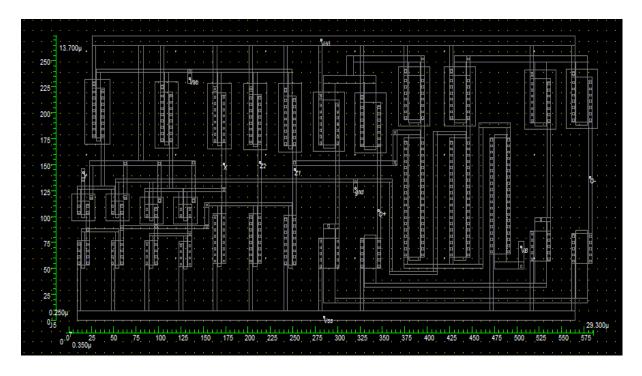

| 6.3  | Layout of ICCTA                                                         | 85 |

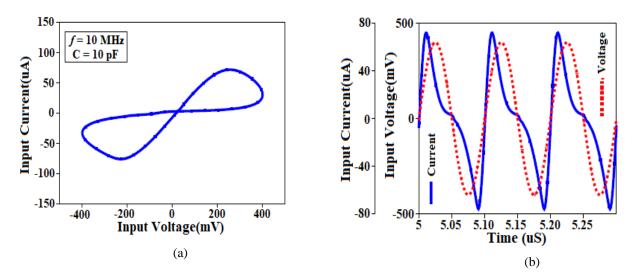

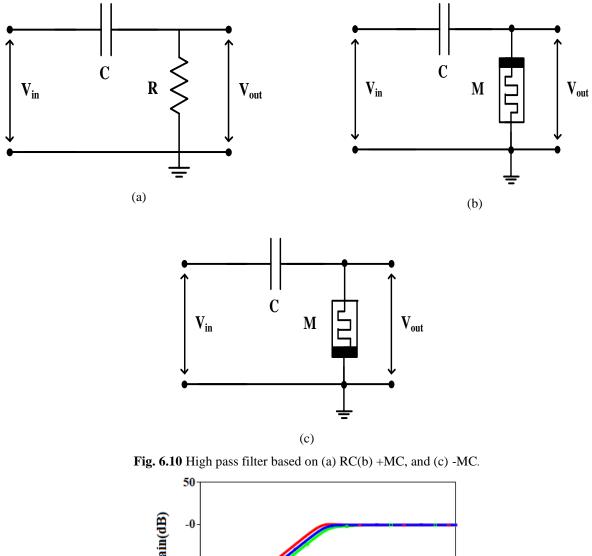

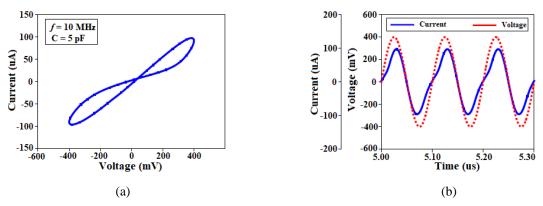

| 6.4  | Responses of grounded memristor at f=10 MHz. (a) PHL, and (b) time      | 86 |

|      | domain response                                                         |    |

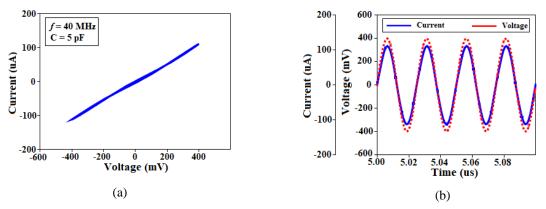

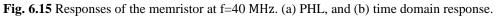

| 6.5  | Responses of the grounded memristor at f=40 MHz. (a) PHL, and (b) time  | 86 |

|      | domain response                                                         |    |

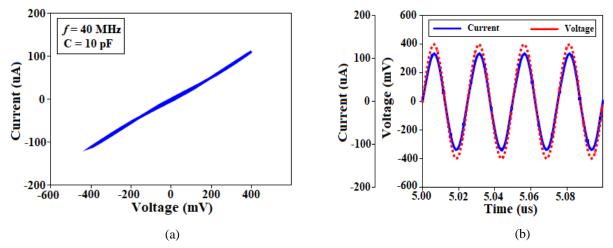

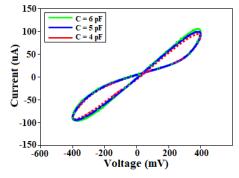

| 6.6  | PHL of grounded memristor for different capacitance values              | 87 |

| 6.7  | PHL of grounded memristor for different bias voltages                   | 87 |

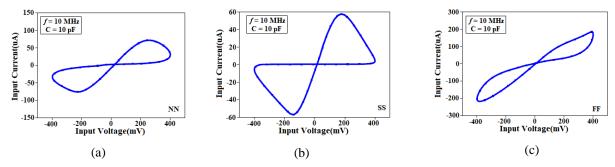

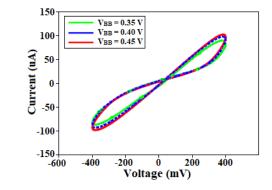

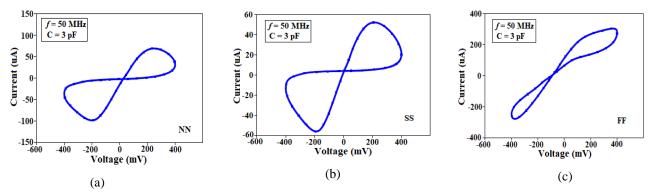

| 6.8  | Corner analysis of the grounded memristor. (a) NN, (b) SS, and (C) FF   | 87 |

| 6.9  | PHL of grounded memristor for 125 MHz frequency                         | 88 |

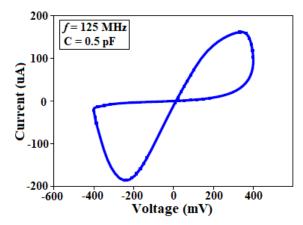

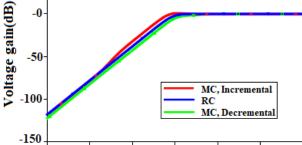

| 6.10 | High pass filter based on (a) RC, (b) +MC, and (c) -MC                  | 89 |

| 6.11 | Frequency response of RC and MC high pass filter circuit                | 89 |

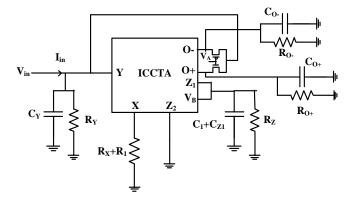

| 6.12 | Proposed charge controlled memristor emulator                           | 90 |

| 6.13 | Proposed charge controlled memristor emulator with parasitic            | 91 |

|      | components                                                              |    |

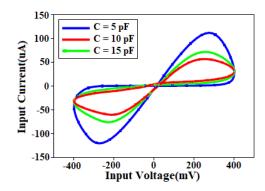

| 6.14 | Responses of the floating memristor at f=10 MHz. (a) PHL, and (b) time  | 93 |

|      | domain response                                                         |    |

| 6.15 | Responses of the floating memristor at f=40 MHz. (a) PHL, and (b) time | 93 |

|------|------------------------------------------------------------------------|----|

|      | domain response                                                        |    |

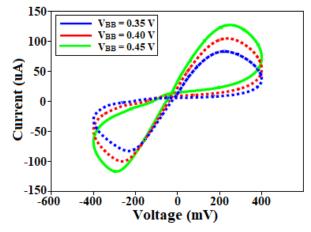

| 6.16 | PHL of the memristor for different capacitance values                  | 94 |

| 6.17 | PHL for different bias voltages of the memristor.                      | 94 |

| 6.18 | Corner analysis of the memristor. (a) NN, (b) SS, and (C) FF           | 94 |

| 6.19 | Nonvolatile nature of the memristor                                    | 95 |

| 6.20 | PHL of the proposed memristor for 100 MHz frequency                    | 95 |

| 6.21 | Proposed meminductor circuit using charge controlled memristor         | 96 |

| 6.22 | Response of meminductor circuit. (a) PHL, and (b) time domain response | 97 |

# **ABBREVIATIONS & NOTATIONS**

| ΟΤΑ        | Operational Transconductance Amplifier                              |            |             |                |         |          |  |

|------------|---------------------------------------------------------------------|------------|-------------|----------------|---------|----------|--|

| CCII       | Second-Generation Current Controlled Conveyor                       |            |             |                |         |          |  |

| CCCII      | Second-Generation Current Controlled Current Conveyor               |            |             |                |         |          |  |

| OTRA       | Operational Trans resistance Amplifier                              |            |             |                |         |          |  |

| CFOA       | Current Feedback Operational Amplifier                              |            |             |                |         |          |  |

| CDBA       | Current Differencing Buffered Amplifier                             |            |             |                |         |          |  |

| DDCC       | Differential Difference Current Conveyor                            |            |             |                |         |          |  |

| VDTA       | Differential Difference Current Conveyor                            |            |             |                |         |          |  |

| VDCC       | Voltage Differencing Current Conveyor                               |            |             |                |         |          |  |

| CBTA       | Current Backward Transconductance Amplifier                         |            |             |                |         |          |  |

| DVCC       | Differential Voltage Current Conveyor                               |            |             |                |         |          |  |

| DXCCTA     | Dual-X Current Conveyor Transconductance Amplifier                  |            |             |                |         |          |  |

| CFTA       | Current Follower Transconductance Amplifier                         |            |             |                |         |          |  |

| CDBA       | Current Differencing Buffered Amplifier                             |            |             |                |         |          |  |

| DVCC       | Differential Voltage Current Conveyor                               |            |             |                |         |          |  |

| CDTA       | Current Differencing Transconductance Amplifier                     |            |             |                |         |          |  |

| MO- CCCCTA | Multiple                                                            | Output     | Current     | Controlled     | Current | Conveyer |  |

|            | Transconduc                                                         | ctance Am  | plifier     |                |         |          |  |

| ZC-VDCCC   | Z-Copy Vol                                                          | tage Diffe | rencing Cur | rent Conveyor  |         |          |  |

| DDCCTA     | Differential Difference Current Conveyor Transconductance Amplifier |            |             |                |         |          |  |

| VD-DIBA    | Voltage Differencing Differential Input Buffered Amplifier          |            |             |                |         |          |  |

| ССТА       | A Current Conveyor Transconductance Amplifier                       |            |             |                |         |          |  |

| CC-CFA     | A Current Controlled Current Feedback Amplifier                     |            |             |                |         |          |  |

| VDBA       | Voltage Differencing Buffered Amplifier                             |            |             |                |         |          |  |

| VDIBA      | Voltage Differencing Inverting Buffered Amplifier                   |            |             |                |         |          |  |

| CFCC       | Current Follower Current Conveyor                                   |            |             |                |         |          |  |

| MDVCC      | Modified Di                                                         | fferential | Voltage Cu  | rrent Conveyor |         |          |  |

|            |                                                                     |            |             |                |         |          |  |

| DXCCDITA  | Dual-X Current Conveyor Differential input Transconductance<br>Amplifier |  |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------|--|--|--|--|--|--|

| VCII      | Second Generation Voltage Conveyor                                       |  |  |  |  |  |  |

| DO-DVCC   | Dual Output Voltage Differential Current Conveyor                        |  |  |  |  |  |  |

| MCFOA     | Modified Current Feedback Operational Amplifier                          |  |  |  |  |  |  |

| MICCI     | Minus-Type Modified Inverting First-Generation Current Conveyor          |  |  |  |  |  |  |

| DXCCII    | Second-Generation Dual-X Current Conveyor                                |  |  |  |  |  |  |

| VCG-CCII  | Voltage and Current Gained Second Generation Current Conveyor            |  |  |  |  |  |  |

| D0-CCII   | Dual Output Second-Generation Current Controlled Current Conveyor        |  |  |  |  |  |  |

| DDCCTA    | Differential Difference Current Conveyor Transconductance Amplifier      |  |  |  |  |  |  |

| MDO-DDCC  | Modified Dual Output Differential Difference Current Conveyor            |  |  |  |  |  |  |

| MVDVTA    | Modified Voltage Differencing Voltage Transconductance Amplifier         |  |  |  |  |  |  |

| CC-CFA    | Current Controlled Current Feedback Amplifier                            |  |  |  |  |  |  |

| VDDDA     | Voltage Differencing Differential Difference Amplifiers                  |  |  |  |  |  |  |

| FTFNTA    | Four Terminal Floating Nuller Transconductance Amplifier                 |  |  |  |  |  |  |

| DVTCC     | Differential Voltage to Current Converters                               |  |  |  |  |  |  |

| MICCII    | Modified Inverting Second-Generation Current Conveyor                    |  |  |  |  |  |  |

| PFTFN     | Positive Four Terminal Floating Nuller                                   |  |  |  |  |  |  |

| ZC-CCCITA | Z-Copy Current Controlled Current Inverting Transconductance             |  |  |  |  |  |  |

|           | Amplifier                                                                |  |  |  |  |  |  |

| OTRA      | Operational Transresistance Amplifier                                    |  |  |  |  |  |  |

| ICFOA     | Inverting Current Feedback Operational Amplifier                         |  |  |  |  |  |  |

| CCDDCC    | Current Controlled Differential Difference Current Conveyor              |  |  |  |  |  |  |

| CCIIITA   | Third Generation Current Conveyor Transconductance Amplifier             |  |  |  |  |  |  |

| ICCII     | Inverting Second Generation Current Conveyor                             |  |  |  |  |  |  |

| DVB       | Differential Voltage Buffer                                              |  |  |  |  |  |  |

| CFDITA    | Current Follower Differential Input Transconductance Amplifier           |  |  |  |  |  |  |

| FDNR      | Frequency Dependent Negative Resistance                                  |  |  |  |  |  |  |

| WDA       | Weighted Differential Amplifier                                          |  |  |  |  |  |  |

| WAA       | Weight Adder Amplifier                                                   |  |  |  |  |  |  |

| IInV            | Inverting Integration Circuit                                    |

|-----------------|------------------------------------------------------------------|

| IWAA            | Inverting Weighted Adder Amplifier                               |

| ICCTA           | Inverting Current Conveyor Transconductance Amplifier            |

| Op-amp          | Operational Amplifier                                            |

| ABB             | Active Building Blocks                                           |

| MCC             | Mutually Coupled Circuit                                         |

| ST              | Synthetic Transformer                                            |

| GIC             | General Impedance Convertor                                      |

| VCR             | Voltage-Controlled Resistor                                      |

| DVCCTA          | Differential Voltage Current Conveyor Transconductance Amplifier |

| VIM             | Voltage Inverting Mutator                                        |

| LDR             | Light Dependent Resistor                                         |

| DTBPF           | Double Tuned Band Pass Filter                                    |

| PHL             | Pinch Hysteresis Loop                                            |

| THD             | Total Harmonic Distortion                                        |

| g <sub>m</sub>  | Transconductance                                                 |

| $\mu_n$         | Electron Mobility                                                |

| C <sub>ox</sub> | Gate Oxide Capacitance Per Unit Area                             |

| C <sub>α</sub>  | Fractional Order Capacitor                                       |

| I <sub>O</sub>  | Inverter                                                         |

| $L_{\alpha}$    | Fractional Order Inductor                                        |

| I <sub>B</sub>  | Bias Current                                                     |

| Q               | Quality Factor                                                   |

| k               | Coupling Coefficient                                             |

| ω <sub>0</sub>  | Resonant Frequency                                               |

# CHAPTER 1 INTRODUCTION

#### **1** Introduction

The signals appearing in real life are analog in nature which makes analog signal processing a niche area. Though the thrust is towards digitization of the signal processing, the circuits specially oscillators, rectifiers, amplifiers, analog to digital converters (A/D), and digital to analog converters (D/A) are going to stay and cannot be realized digitally. To elaborate this further, analog signal generated by microphones and other acoustic transducers are appropriately conditioned throughout this procedure utilizing amplifiers and filters. They are then transformed to digital format to allow for further activities such as mixing, editing, and creating special effects. Additionally, digital signals are used for important operations such as transmission, storage, and retrieval. Finally, digital information is converted into analog signal that are transmitted through loudspeakers. The physical environment is ultimately analog, which means that analog circuitry will always be required to modify physical signals, such as those generated by transducers. As a result, analog designers are expected to create interfaces that have superior performance and are compatible with digital circuits to the greatest extent possible. In modern times, VLSI technology has the capability to incorporate millions of transistors into a compact single chip. Further, with scaling down of geometries, it becomes necessary to operate the circuits at reduced supply voltages. The operation of analog circuits at low power supply presents several challenges e.g. decrease in input common mode range, output swing, and linearity. Moreover, it is preferable to use low voltage circuit techniques that are compatible with normal CMOS processes to avoid this clash rather than expensive CMOS technologies with lower thresholds.

The information processed by electronic circuits may be represented by branch current and node voltages of the circuits. An electronic circuit in which performance of the circuit is identified in terms of referred voltage at different input and output nodes known as Voltage-Mode (VM) circuit. An operational amplifier is one of the most predominant devices to develop VM circuits. The VM circuit has high impedance nodes architecture, so the underlying parasitic components present at different nodes get charged and discharged with high voltage swing. Therefore, the VM circuit is not suitable for low power, wide bandwidth, high speed, and high slew rates operation. Current Mode (CM) signal processing circuits have emerged over the past few decades as an alternative design strategy for low power analog signal processing. The concept of the Current Conveyor (CC) was first introduced by Sedra and Smith in 1968 and subsequently

revised in 1970 [1]. An essential component for the formulation and execution of integrated circuits is the Operational Transconductance Amplifier (OTA), which was introduced by Wheatley and Wittlinger in 1969 [2]. The Third-Generation Current Conveyor [3] emerged in 1995 as an improved iteration of the preexisting conveyor. However, another current conveyor, known as the Second-Generation Current Controlled Current Conveyor (CCCII) [4], was documented in 1996. There are a number of functional CM blocks accessible in the scholarly literature such as, Operational Trans resistance Amplifier (OTRA) [5], Current Feedback Operational Amplifier (CFOA) [6], Current Differencing Buffered Amplifier (CDBA) [7], Differential Difference Current Conveyor (DDCC) [8], Differential Difference Current Conveyor (VDTA) [9], Voltage Differencing Current Conveyor (VDCC) [10], Current Backward Transconductance Amplifier (CBTA) [11], Differential Voltage Current Conveyor (DVCC) [12], Dual-X Current Conveyor Transconductance Amplifier (DXCCTA) [13], Current Follower Transconductance Amplifier (CFTA) [14], and many more.

#### **1.1 Literature survey**

Active immittance circuit is a prominent area of study within the realm of active circuit design due to the drawbacks associated with incorporating traditional components such as inductors and resistors into microelectronic circuits. These drawbacks include the utilization of significant chip space, increased weight, higher costs, and limited adjustability. The immittance circuits find numerous applications in the domains of microelectronics, communication, analog signal processing, instrumentation, and measurement.

Various implementations of the integer order immittance circuit exist, relying on analog active building blocks. Literature survey on available integer order grounded and floating immittance emulators [15-83] shows that – Refs. [15-61] provide floating immittances. while those reported in Refs. [62-83] furnish grounded immittances. The available floating immittance emulators use single [27,29,35,36,41,43,45,47,51,52,53,56,58-60]/ multiple active block(s) [15-26,28,30-34,37-40,44,46,48-50,54,55,57,61]. These emulators use CCII [15-19], Current Differencing Buffered Amplifier (CDBA) [20], CCCII and Dual Output Second-Generation Current Controlled Current Conveyor (Do-CCCII) [21-22], OTA [23], Dual Output Second Generation Current Conveyor (Do-CII) [24], Second-Generation Dual-X Current Conveyor (DXCCII) and MOS transistors [25], Minus-Type Modified Inverting First-Generation Current Conveyor (MICCI) [26], Modified Current Feedback Operational Amplifier (MCFOA) [27], CCCII [28],

CFOA [29,30], Differential Voltage Current Conveyor (DVCC) and CCII [31], DDCC and CCII [31], DVCC and DDCC [31], CFOA and MOS Transistor [32], OTA and DO-CCII [33], DVCCTA [34,35], DVCC and DDCC [36], Voltage and Current Gained Second Generation Current Conveyor (VCG-CCII) [37], Current Differencing Transconductance Amplifier (CDTA) [38], DVCCC [39], DVCCII [40], Multiple Output Current Controlled Current Conveyer Transconductance Amplifier (MO-CCCCTA) [41], Z-Copy Voltage Differencing Current Conveyor (ZC-VDCCC) [42], Differential Difference Current Conveyor Transconductance Amplifier (DDCCTA) [43], Voltage Differencing Differential Input Buffered Amplifier (VD-DIBA) [44], CBTA [45,46], Modified Dual Output Differential Difference Current Conveyor (MDO-DDCC) [47], CFTA [48], VDTA [49], Voltage and Current Follower [50], VDCC [51], Current Conveyor Transconductance Amplifier (CCTA) [52], Modified Voltage Differencing Voltage Transconductance Amplifier (MVDVTA) [53], Current Controlled Current Feedback Amplifier (CC-CFA) [54], Voltage Differencing Buffered Amplifier (VDBA) [55], DXCCTA [56], Voltage Differencing Differential Difference Amplifiers (VDDDA) [57], Four Terminal Floating Nuller Transconductance Amplifier (FTFNTA) [58], DDCC [59-60], and Differential Voltage to Current Converters (DVTCC) [61] Now, grounded immittance emulators available in literature utilize either a single [62,64-77,79,83] or multiple active blocks [63,78,80-82]. These emulators employ Modified Inverting Second-Generation Current Conveyor (MICCII) [62], CCII [63], Positive Four Terminal Floating Nuller (PFTFN) [64], Z-Copy Current Controlled Current Inverting Transconductance Amplifier (ZC-CCCITA) [65], Operational Transresistance Amplifier (OTRA) [66-70], VDCC [71], Inverting Current Feedback Operational Amplifier (ICFOA) [72], DXCCII [73], Voltage Differencing Buffer Amplifier (VDBA) [74], Voltage Differencing Inverting Buffered Amplifier (VDIBA) [75], Current Follower Current Conveyor (CFCC) [76], Modified Differential Voltage Current Conveyor (MDVCC) [77], CFOA [78], Dual-X Current Conveyor Differential input Transconductance Amplifier (DXCCDITA) [79], CCII and Inverting Voltage Buffer (IVB) [80], Second Generation Voltage Conveyor (VCII) [81], Dual Output Voltage Differential Current Conveyor (DO-DVCC) [82], and VDDDA [83]. Moreover, floating and grounded immittance emulator may be further classified as positive and negative immittance emulator. Literature survey on available positive and negative immittance emulators [15-83] shows that - Refs. [15-41,43-65,68,69,71-75,77-83] provide positive

immittances. while those reported in Refs. [22,23,30,32,33,41,45,53,56,59,60,65,66,67,70,71,73] denotes negative immittances.

A detailed study of floating and grounded immittance emulators reveals that - there is limited presence of impedance tunning features in [15-19,24,26,27,29-31,39,40,47,50,59,62,63,66-70,73,77,78,80-82]. Further, component matching is required in [26,30,36,50,60,62,64,66-70,73,77,78,82] for correct functionality which is difficult to achieve in integrated circuits. Also, the circuit in the topological change (interchanging of input terminals, changing components' placement)/different circuit design is required for providing positive and negative immittance in [22,23,30,32,33,41,45,53,59,60,65,71,73,76]. In addition, more than one passive component is [15-19,21,22,24-27,30-37,39,40,45-47,50,51-53,55,58,59,60-64,66-74,76-82]. required in Moreover, Refs. [15,16,24,27,31,47,57,58,72,75,76,78,79] and Refs. [17-19,26,29,30-32,36,37,50,55,59,61,62,64,66-70,73,74,77,80-82] require single floating passive component and multiple floating components respectively. It is clear from above discussion that a limited literature is available immittance emulators that may simultaneously fulfil the following criterions: tunability, no matching constraint and working in positive and negative mode without topological changes. Further, it is pertinent to mention here that the topological change is not possible once the circuit is laid down and fabricated. Also, if two different circuits are realized in IC form for positive and negative immittances, the resulting in larger silicon footprint.

The biomedical signal processing applications require at low frequency operation which require large magnitude of immittance value. An active immittance multiplier is useful in such situations for realizing a substantial magnitude of immittance value from a component of smaller magnitude. In the literature, there have been several reports on the development of active floating [84-97] and grounded immittance multiplier circuits [98-119]. The available floating immittance multiplier use single [91]/ multiple active block(s) [84-90,92-94,96,97]. These floating immittance multiplier employ OTA [84], CCII [85], CCCII [86], CFOA [87,88], CDTA [89], Current Controlled Differential Difference Current Conveyor (CCDDCC) [90], FB-VDBA [91], MODVCC [92], DO-CCII [93,94], FTFN [95], VDCC [96], and VDCCII [97]. Further, floating immittance multiplier available in literature utilize either a single [99,101,105,106,108] or multiple active blocks [98,100,102,103,104,107,109]. These grounded immittance multiplier uses OTA [98], CCII [99], CFOA [100-104], ICFOA [105], DXCCII [106], CFOA and OTA [107], Third Generation Current Conveyor Transconductance Amplifier (CCIIITA) [108],

OTRA [109], VCCII [110,111], Inverting Second Generation Current Conveyor (ICCII) [112], OTA and Differential Voltage Buffer (DVB) [113], CFTA [114,115], Current Follower Differential Input Transconductance Amplifier (CFDITA) [116], VDTA [117,118], and CCCDTA [119].

Nowadays, fractional order circuits gain considerable attention among researcher due to extra degree of freedom to control the phenomena of the system. Fractional calculus is a powerful and widely used tool to demonstrate the characteristics of many systems in the real world such as thermodynamic [120], volcanology [121], human organ [122], biomedicine [123], earthquake [124], modelling of virus [125] and many more. The fractional-order circuits and systems have immense potential in the areas of fractional order controller [126], fractional order signal generating [127,128] and signal processing circuits [129,130,131]. The basic building blocks for the design of a fractional order system are known as fractor having input impedance of  $Z(s) = \frac{k_0}{s^{\alpha}}$  where  $\alpha$  ( $|\alpha| < 1$ ) represents order of fractor and  $k_0$  is constant. Depending upon the value of  $\alpha$  the behavior of the element changes from fractional order inductor to fractional order capacitor. For specific value of  $\alpha$  as -1, 0, 1 the fractance turns into classical element capacitor, resistor, inductor respectively, whereas  $\alpha = -2$  corresponds to Frequency Dependent Negative Resistance (FDNR).

Over the years, a limited no. of active block based fractional capacitor is designed. Pacheco et. al [132] developed FC using combinations of Op-amp based Weighted Differential Amplifier (WDA), Weight Adder Amplifier (WAA), Inverting Integration Circuit (IInv), Inverting amplifier (Inv), and Inverting Weighted Adder Amplifier (IWAA). Active realization of first order Continued Fractional Expansion approximation of the fractional capacitor needs three Opamps, six grounded resistors, seven floating resistors, and one floating capacitor. The order of the Op-amp based fractional capacitor is changed by varying pole frequency of lead/lag phase network. The Op-amp non-idealities such as finite unity gain frequency may reduce the constant phase zone of the fractional order device and deteriorate its constant phase nature [133]. Prommee et al. [134] designed a fractional-order capacitor using OTA-based voltage gain circuit and integrator circuit. The order of OTA based fractional capacitors. An active realization of the fifth order CFE approximation of the fractional capacitor needs 19 OTAs and 5 capacitors. Design of a fractional inductor using large number of OTA-based fractional-order capacitor may result in a low figure of merit. Therefore, the researchers have made effort in the direction of approximating the fractional order capacitor behavior (Carlson approximation [135], Matsuda approximation [136], Oustaloup approximation [137] Charef approximation [138] and Continued Fractional Expansion [139]) and subsequently designing and developing emulators using appropriate RC ladder.

The fractional order inductor may be designed using a General Impedance Converter (GIC) and fractional order capacitor. These inductors can be classified as positive and negative fractional order inductors. The former is used to design fractional order filter, modeling of the human respiratory system, and fractional order oscillator whereas the latter may find application in parasitic inductance cancellation. Over the years, GIC based fractional inductor simulators [56,140-147] have been presented in the literature. These fractional inductor circuits use OTA and CFOA [56], Op-amp [140-143], CFOA [144,145], OTA and Differential Voltage Buffer (DVB) [146], and OTA [147]. Further, fractional order inductor present in literature is operating either in floating mode [56,146] or grounded mode [140-145,147]. The reported positive fractional inductor circuits are limited in terms large number of active and passive components [56,140-143], tunability [140-144], slew rate [140-143], operating frequency [140-144,147], high power dissipation [146], high chip area [146], and low figure of merit [56,140-147]. Moreover, from the perspective of integration, a single topology positive and negative fractional inductor can be helpful. This type of topology may be referred to as reconfigurable circuit as it provides both positive and negative fractional inductors by varying only the gate voltage of MOS switches and thereby making the circuit user-friendly. Such a reconfigurable circuit benefits from reduced chip area, lower power dissipation, and lower cost. Further, the study of available literature reveals that no circuit is present featuring reconfigurable fractional order positive and negative inductor circuits.

Mutually Coupled Circuit (MCC) is yet another domain of immittance circuits. It is frequently used in circuits for instrumentation, measurement, analog communications, and signal processing. The coupling factor, mutual inductance, primary inductance, and secondary inductance are the primary features of the MCC. The MCC simulator provides a relationship between the voltages and currents of their ports even though they lack real magnetic couplings. By altering the bias current of the active block circuit, the values of the inductances and the coupling coefficient may both be adjustable. Due to the lack of inductive components, the MCC

simulators are easily incorporated. The lack of significant inductive components makes MCC suitable for integrated circuits.

Literature survey reveals that MCCs have been reported [148-164] using different active building blocks. The MCC reported in [148,149] is implemented using large no. of Bipolar Junction Transistor (BJT) and large number of resistors and capacitors. In [150], a MCC is developed using eight OTAs. Moreover, in [151] the MCC topologies are designed using BJT, CCII, and OTAs. Furthermore, the MCC is given in [152] employ six CCIIs. However, four CCIIs based MCC topology is illustrated in [153]. The MCC in [154] realized using three CCCIIs and two DO-CCCIIs. In [155], the reported MCC utilizes four CCCIIs. The topology presented in [156] realizing MCC using two DVCCs and two CCIIs. However, [157] used three CC-CBTAs in implementation of MCC. In [158], the MCC produces using two DVCCTAs. Moreover, in [159] MCC is developed using two CCCCTAs. Further, the MCC is proposed using two CBTAs in [160]. The circuit reported in [161] realizes MCC using four CFOAs. In [162], the reported MCC is developed using two VDDCCs. However, two VDTAs based MCC are mentioned in [163]. Moreover, in [164] the realization of MCC is done using two CCTAs. It is also observed from the above literature survey, the number of active blocks and passive components in available MCCs vary from 2 to 8 and 2 to 11 respectively. The MCCs [150-157,162] use more than two active blocks while those presented in [151-161,164] consist of more than two passive components. The MCCs reported in [151-153,161] do not facilitate tuning feature. The overall transistor counts in [153-158,161,164] is more than 46 transistors and therefore these circuits may require a larger chip area for realization. Further, the study of available MCCs reveals that no circuit is present featuring mutual inductance in four different pairs like passive transformers. Furthermore, Memristor is the fourth [165] fundamental element in circuit theory after resistors, capacitors, and inductors. It is gaining considerable attention among researchers due to its highdensity storage property. It is a non-linear device depending upon the previous history of current. Leon O. Chua developed memristor by giving the relation between electric charge (q) and magnetic flux ( $\varphi$ ) in 1971 [166]. The memristor's memristance remains constant even when the input signal is absent, which is referred to as the non-volatile characteristic of the memristor. Since memristor has nonlinear characteristic, non-volatile nature, and high-density storage properties, it is being used in a variety of applications such as programmable gate arrays [167], programmable analog circuits [168], neuromorphic circuits [169], adaptive learning [170,171],

adaptive filters [172], chaotic oscillators [173], and relaxation oscillators [175,176] etc. After 37 years of proposal of the memristor by L O. Chua, Hewlett-Packard (H. P.) lab created the first solid-state memristor in 2008. Due to its high price and difficult manufacturing process, this solid state memristor is not currently accessible. This constraint spurs researchers to create memristor circuits based on Active Building Blocks (ABB). Below is a literature review of an ABB-based memristor emulator.

A variety of memristor emulators have been reported in current literature [177-193]. The programmable analog circuit-based memristor emulator was created by Pershin and Ventra [177]. It is made up of an Analog to Digital Converter (ADC), a microprocessor, and a digital potentiometer. However, the digital potentiometer's finite resolution limits performance. The Voltage-Controlled Resistor (VCR), CCII, and Operational Amplifier (Op-amp) are components of the memristor circuit invented by Hussein and Fouda [178]. Nevertheless, performance is constrained due to the limited linear range of VCR transistors. Arundeepakvel et al. [179] designed Mutator circuit needs one Voltage Inverting Mutator (VIM), two resistors, two diodes and one inductor. The study suggests that passive inductor based memristor circuit requires large chip area. According to the study, passive inductor-based circuits are expensive and large. Three Op-amps, eleven resistors, one Light Dependent Resistor (LDR), one capacitor, and one diode make up the memristor circuit that Fitch et al. [180] showed. The performance of the memristor at higher frequencies was constrained by LDR characteristics. A straightforward and adaptable memristor was created by Abuelama'atti and Khalifa [181] using four CFOA, four resistors, two diodes, and four capacitors. Off-the-shelf floating memristor was introduced by Sozen and Cam [182] and features four CCIIs, three OTAs, six resistors, and one capacitor. A second voltage source is needed to bias the current of one of the OTAs. Some memristor emulators [183-187] call for an extra circuit, such as a multiplier circuit, in addition to active and passive elements. Voltage across a memristor must be multiplied by the flux of the memristor using an analog multiplier circuit. The use of extra circuitry might make the memristor circuit more complicated and lower its operating frequency. One grounded capacitor and two OTAs are present in the floating memristor that is being demonstrated [188] without the need of multiplier circuits. It is nonetheless used up to 400 kHz. However, the floating memristor emulator described in [189] only needs one VDTA, one capacitor, and one resistor, and it can function up to 50 MHz. Additionally, the floating memristor described in [190] has a 10 MHz maximum working

frequency. Three resistors, one grounded capacitor, and one CCTA are used. The literature has a reconfigurable, adjustable grounded memristor emulator [191-193]. The exhibited memristor's maximum operational frequencies in [191], [192], and [193] are 1 MHz, 26.3 MHz, and 9 MHz, respectively. According to the study, grounded memristors are inappropriate for complicated circuits [190]. A floating memristor [194] was developed using OTA and CDTA. The architecture is significantly altered to allow it to work in incremental and decremental mode up to 2 MHz frequency. The memristor emulators shown in [195-197] use different supply voltages, necessitating a high-quality manufacturing architecture [188]. A review of the literature indicates that the reported memristor circuits have limitations in terms of the operating frequency range, mode of operation, supply voltage, number of active and passive components, and additional circuits like multipliers, digital potentiometers, microprocessors, passive inductors, and ADC.

#### **1.2 Research Gaps**

The following research gap can be obtained from above literature survey:

- a. There is limited presence of impedance tunning features in available immittance emulators. Further, component matching is required for correct functionality which is difficult to achieve in integrated circuits. Also, the circuit in the topological change (interchanging of input terminals, changing components' placement)/different circuit design is required for providing positive and negative immittance. Thus, a limited literature is available immittance emulators that may simultaneously fulfil the following criteria: tunability, no matching constraint and working in positive and negative mode without topological change is not possible once the circuit is laid down and fabricated. Also, if two different circuits are realized in IC form for positive and negative immittances, the resulting in larger silicon footprint.

- b. No MCC circuit is present featuring mutual inductance in four different pairs like passive transformers is available in open literature.

- c. The reported memristor emulators have limitations in terms of their operating frequency range, mode of operation, supply voltage, number of active and passive components, and usage of additional circuits like multipliers, digital potentiometers, microprocessors, passive inductors, and ADC.

#### **1.3 Research Objectives**

Research objectives of the thesis are established with consideration of the research gap highlighted in the previous section. The study aims to design different types of immittance circuit such as grounded and floating elements, positive and negative integer order elements using single topology, positive and negative fractional order elements using single topology, mutually coupled circuit, and memristor emulators using suitable ABBs (Active Building Blocks). The primary considerations for these designs include fewer active blocks and passive elements, low power consumption, wide operating frequency, low chip area, and a simple architecture. Thus, there are following objectives are set for the research work:

- a. Design of tunable grounded immittance circuit that can work in both positive and negative modes without topological change.

- b. Design of tunable floating immittance circuit that can work in both positive and negative modes without topological change.

- c. Design of mutually coupled circuit capable of working in all four pairs.

- d. Designing of multiplier less mem immittance circuit.

#### **1.4 THESIS Organization**

The thesis is structured into seven chapters. Each chapter includes a brief introduction, circuit analysis description, nonideal analysis of the proposed circuit, Monte Carlo analysis, supply voltage variation, temperature variation etc. Furthermore, these chapters present a discussion on simulation results, and a comparison with previously published work, followed by a summary.

**Chapter 1** describes evolution and significance of current mode based analog circuit. The constraint of voltage mode ABB is analyzed briefly. A short review of different kinds of current mode ABB is also presented. After words, research gaps in the field of integer and fractional order immittance circuit, synthetic transformer, and memristor circuit are illustrated. Finally, this chapter ends with organization of thesis.

**Chapter 2** describes detail illustration of ideal and non-ideal model of current mode analog building blocks such as Operational Transconductance Amplifier (OTA), Current Conveyor Transconductance Amplifier (CCTA), Inverting Current Conveyor Transconductance Amplifier (ICCTA), and Current Feedback Operational Amplifier (CFOA).

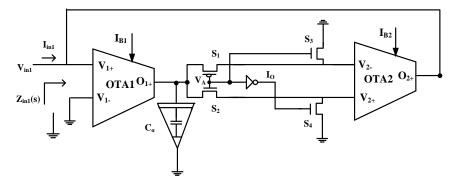

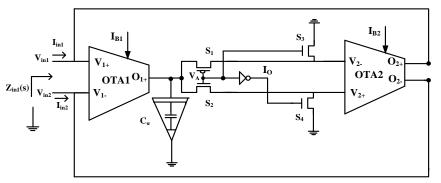

**Chapter 3** illustrates three positive and negative tunable integer order immittance circuit and their applications. The first positive and negative grounded immittance circuit is designed using

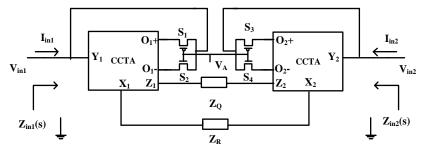

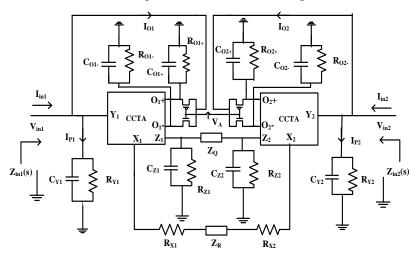

one CCTA, one grounded resistor, one grounded capacitor and two MOS switches. The second positive and negative floating immittance circuit utilizes two CCTAs, two grounded resistors, one floating capacitor, and four MOS switches. Whereas the third positive and negative floating immittance circuit employs two CCTAs, one floating MOS resistor, one floating capacitor and four MOS switches. In addition, Current Feedback Operational Amplifier (CFOA) based lossless grounded negative impedance multiplier circuit is also designed. This circuit is designed by two CFOAs and three passive components. The designed circuit may emulate grounded capacitance multiplier, grounded inductance multiplier, grounded frequency dependent negative resistor and grounded resistance divider circuit. Impact of the parasitic components associated with terminals of CCTA and CFOA on performances of the above designed circuits is mathematically formulated. Transient and frequency response of designed circuits are demonstrated to justify the theoretical prepositions. The applicability of the proposed is demonstrated through active filters.

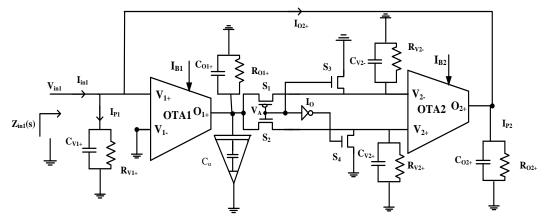

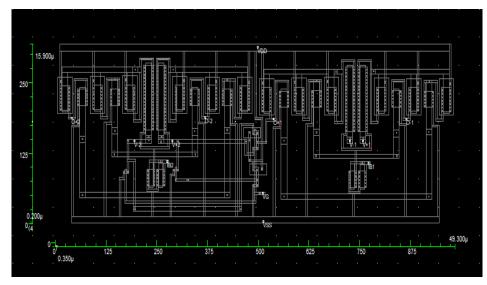

**Chapter 4** describes electronically adjustable floating and grounded fractional order inductor circuits. The developed circuits utilize two OTAs, one fractional order capacitor, one inverter, and four MOS switches. These circuits can operate in both positive and negative modes without any changes to their topology. The behavior of the suggested circuit is further examined in the presence of parasitic elements that may arise in the practical circuit. The efficacy of the suggested positive fractional inductor circuit is showcased by employing it in a fractional order band pass filter and a fractional order high pass ladder filter. The practicality of the suggested negative fractional inductance circuit is showcased with the help of a fractional inductance cancellation circuit.

**Chapter 5** investigates electronically tunable mutual coupled circuit employing CCTA. This circuit includes two CCTAs, two capacitors, three resistors and four MOS switches. The designed circuit follows the dot convention of passive transformer and produces all four pairs of mutually coupled circuit like passive transformer by appropriate setting of MOS switches. The proposed MCC does not require component matching condition. Self-inductance, mutual inductance, and resonant frequency can be tuned by bias current of CCTA. Furthermore, non-ideal effects on the proposed MCC are discussed. A double tuned band pass filter is shown as an application.

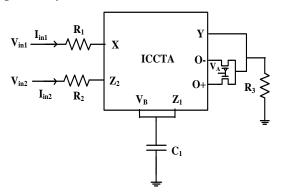

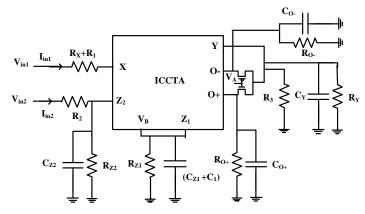

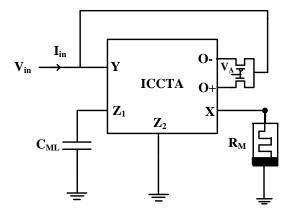

**Chapter 6** presents charge and flux controlled memristor emulators and their application using ICCTA. The flux-controlled floating memristor emulator is implemented using one ICCTA, one

resistor, and one capacitor. Whereas charge controlled floating memristor emulator is composed of one ICCTA, one capacitor, and three resistors. Both emulators are free from additional circuits like ADC, DAC, analog multiplier circuits, passive inductor, light dependent resistor, and diodes. Furthermore, non-ideal analysis of these memristors is mathematically examined. Additionally, the meminductor circuit and memristor-based active filter have been implemented to examine the designed memristor emulators.

Chapter 7 discusses the conclusion and future scope of the work.

CHAPTER 2 ANALOG BUILDING BLOCKS

This chapter describes different analog building blocks used to develop immittance emulator in this work. The port relationships of these blocks and their verification through SPICE is also put forward as background material.

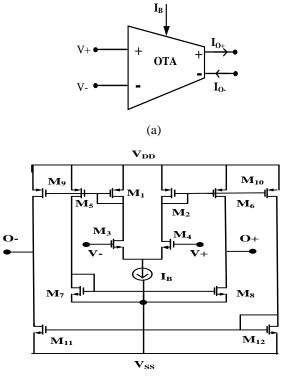

#### 2.1 Operational transconductance amplifier

Operational Transconductance Amplifier (OTA) is a current mode active building block that has various advantages over voltage mode active building blocks for instance high dynamic range, more linearity, wide bandwidth, high slew rate, simple tunning, low chip area, and low power consumption. Due to these benefits, OTA has made a substantial contribution to many analog signal processing and generating circuits including filter [211,212], oscillator [212, 213], and multivibrator [214] etc. The OTA is a differential voltage controlled current source with high input and output impedance. The transconductance of OTA may be controlled by the input bias current (I<sub>B</sub>). Circuit symbol of OTA is given in Fig. 2.1(a). The OTA has four terminals namely V<sub>+</sub>, V<sub>-</sub>, O<sub>+</sub>, and O<sub>-</sub>. V<sub>+</sub> and V<sub>-</sub> are input terminals and O<sub>+</sub> and O<sub>-</sub> are output terminals. MOS based circuit realization of OTA is illustrated in Fig. 2.1(b). It is seen from Fig. 2.1(b) that the differential stage consists of transistors  $M_1$ - $M_4$ , whereas transistors  $M_5$ - $M_{12}$  ensure that the currents at O<sub>+</sub> and O<sub>-</sub> terminals of OTA are equal in magnitude. Thus, the difference of the input voltage  $(V_+ - V_-)$  is converted to be the output current  $(I_{0\pm})$  through transconductance  $(g_m)$ . The characteristic equation of OTA is given by eq. (2.1) which may be used to add electronic tunning feature to the performance parameters of immittance emulator, filter, oscillator, and multivibrator.

$$I_{0\pm} = g_{\rm m} (V_+ - V_-) \tag{2.1}$$

Where  $V_+$  and  $V_-$  are input voltages at inverting and non-inverting terminals. The  $g_m$  represents transconductance of the OTA, while  $I_{0\pm}$  are output currents at  $O_+$  and  $O_-$  terminals. Here, the transconductance gain  $g_m$  of OTA can be written as:

$$g_{\rm m} = \sqrt{\mu_{\rm n} C_{\rm OX} I_{\rm B} \left(\frac{W}{L}\right)_{3/4}}$$

(2.2)

where  $\mu_n$ ,  $C_{ox}$ , and  $\left(\frac{W}{L}\right)_{3/4}$  are the electron mobility of NMOS, gate oxide capacitance per unit area, and aspect ratio of transistor  $M_3$  or  $M_4$  respectively. It is notable from eq. (2.2) that the value of transconductance can be changed by varying the bias current of OTA.

(b)

Fig. 2.1 OTA (a) circuit symbol (b) MOS based design.

#### 2.1.1 Non-ideal model of OTA

The parasitic components appear at different terminals of OTA in the form of the parallel combination of resistances and capacitances are depicted in Fig. 2.2. The parasitic components associated with terminals,  $V_{-}$ ,  $V_{+}$ ,  $O_{+}$ ,  $O_{-}$  are represented as  $R_{V-} \parallel C_{V-}$ ,  $R_{V+} \parallel C_{V+}$ ,  $R_{O+} \parallel C_{O+}$ , and  $R_{O-} \parallel C_{O-}$  respectively. These parasitic components may lead to deviation in the performance of the device.

Fig. 2.2 Non-ideal model of OTA.

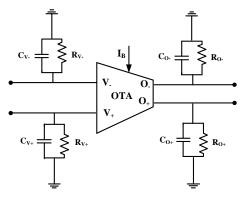

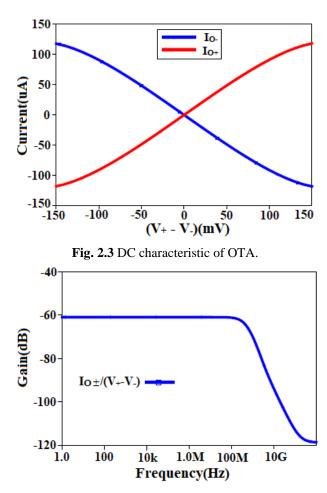

# 2.1.2 Verification of OTA

Verification of OTA is carried out using SPICE simulator. CMOS parameter of 90 nm technology is used for the purpose of simulations. Aspect ratios of the transistors employed in Fig. 2.1 are provided in Table 2.1. Supply voltage is chosen to be  $\pm 1.2$  V, whereas the value of bias current is 120 µA is taken for simulations. The variation of current I<sub>O+</sub> and I<sub>O</sub> against the (V<sub>+</sub> - V<sub>-</sub>) is shown in Fig. 2.3. Fig. 2.3 shows that I<sub>O+</sub> and I<sub>O</sub> exhibit a linear variation within the voltage range of -100 mV to 100 mV. Frequency response of OTA is shown in Fig. 2.4. The operating frequency of the OTA for transconductance gain is found to be 200 MHz.

| Transistor                             | W(μm)/ L(μm) |

|----------------------------------------|--------------|

| $M_{1,}M_{2,}M_{9,}M_{10,}M_{5,}M_{6}$ | 2.15/0.7     |

| M <sub>3</sub> - M <sub>4</sub>        | 5.75/0.7     |

| $M_{7\!,}M_{8\!,}M_{11\!,}M_{12}$      | 1.45/0.7     |

Table 2.1: Aspect ratio of transistors of OTA.

Fig. 2.4 Frequency response of OTA.

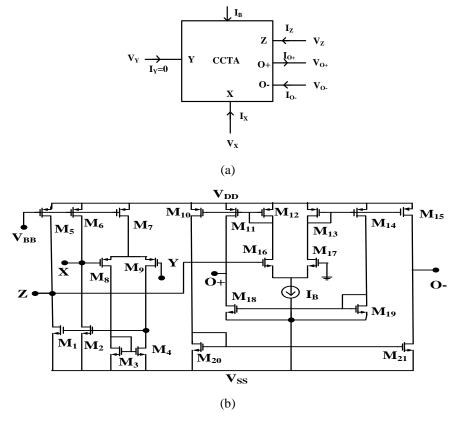

# 2.2 Current conveyor transconductance amplifier

Current Conveyor Transconductance Amplifier (CCTA) comprises of CCII and a dual output Operational Transconductance Amplifier (OTA). Its circuit symbol and MOS based schematic are shown in Fig. 2.5. The current mirror, comprised of transistors  $M_3$  and  $M_4$ , ensures that the drain currents of transistors  $M_8$  and  $M_9$  are identical. Hence, the voltage at Y terminal is conveyed to X terminal. The current conveying operation from terminal X to Z is facilitated by selecting transistors  $M_1$  and  $M_2$  with equal aspect ratios. Hence, current fed into X terminal is conveyed to Z terminal. The current flowing out of  $O_{\pm}$  terminal is product of transconductance of OTA and Z terminal voltage. The characteristics equations of the CCTA are given by eq. (2.3).

$$I_{Y} = 0; V_{X} = V_{Y}; I_{Z} = I_{X}; I_{0\pm} = \pm g_{m}V_{Z}$$

(2.3)

The  $g_m$  corresponds to transconductance parameter that can be mathematically defined as:

$$g_{\rm m} = \sqrt{\mu_{\rm n} C_{\rm OX} I_{\rm B} \left(\frac{\rm W}{\rm L}\right)_{16/17}} \tag{2.4}$$

where  $\mu_n$  is the mobility of charge carrier,  $C_{OX}$  is a gate capacitance per unit area,  $I_B$  is bias current of CCTA and  $(W/L)_{M_{16/M_{17}}}$  is aspect ratio of the MOS transistor  $M_{16}/M_{17}$  respectively.

Fig. 2.5 CCTA (a) circuit symbol (b) MOS based implementation of CCTA.

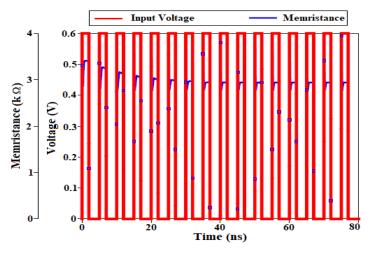

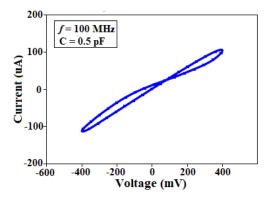

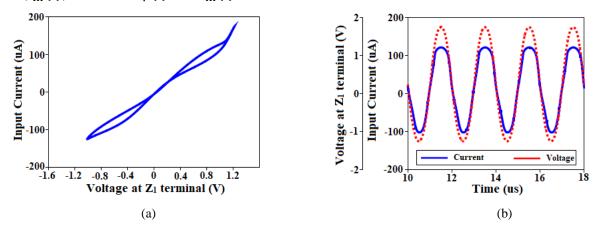

#### 2.2.1 Non-ideal Model of CCTA