## DEVELOPMENT OF CM CIRCUITS FOR ANALOG SIGNAL PROCESSING AND SIGNAL GENERATION

A Thesis Submitted In Partial Fulfillment of the Requirements for the Degree of

### DOCTOR OF PHILOSOPHY by

PARVEEN RANI (2K16/PhD/EC/08)

Under the Supervision of Prof. RAJESHWARI PANDEY Delhi Technological University

**Department of Electronics and Communication Engineering**

**DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering) Shahbad Daulatpur, Main Bawana Road, Delhi-110042. India

December, 2024

### Acknowledgement

Post completion of my research work; I finally, would like to take this opportunity to thank everyone, who have motivated, guided and helped me in undertaking this wonderful journey.

Ever since I was a budding researcher, there were initial hiccups about the change in the domain, but I remain indebted to my supervisor for opening a window of opportunities in the arena of analog VLSI (specifically, fractional order dynamics). I fell short of words to thank my mentor Prof. Rajeshwari Pandey for her kind, benevolent guidance and unwavering support. I really appreciate and could not thank her enough for taking out precious time out of her tight schedule whenever the contours of my research work needed clarity. It need a special mention, she went extra mile beyond academic guidance when despite all our relentless efforts and patience; to look beyond and iterated 'Surrender to that supreme power!'. Thank you, Ma'am, for extracting best out of me.

Prof. Neeta Pandey - a stalwart in this domain and a motherly figure holds a special place in my heart. I also take this opportunity to extend my heartfelt thanks to Prof. Raj Senani, Prof. D. R. Bhaskar, Prof. O. P. Verma, Prof. S. Indu, Prof. J. Panda, Dr. Manjit Kumar. I would also like to thank my fellow researchers of the department for their support and help on various occasions, especially Dr. Priyanka Gupta, Dr. K. Gurumurthy, Dr. Rakesh Verma, Dr. Garima Varshney, Dr. Damyanti Singh, Ms. Sweta Kumari and Mr. Lokesh Soni. Special thanks to Mr. Rajendra Kumar for making excellent arrangements for conducting research simulations because I could spend significant hours / substantial time in the VLSI laboratory.

I express my deep sense of respect and gratitude to my parents, Smt. Nirmala Devi and Sh. Satya Prakash for their continuous support in all stages of my life. My fatherin-law (in heaven) has always been a guiding spirit. After that thanks to my better half; it would not have been possible without you, Sachin! Thanks for believing in my potential despite the odds. I would also like to thank my brother, Yashveer for supporting me through this long journey. With all my heart, I would like to thank the apple of my eye; my lovely son, Harshitu (what I call him out of sheer love), who with patience has endured staying away from her mother.

I also take this opportunity to thank each and everyone all those whom I have inadvertently forgotten to mention – my friends, colleagues, near and dear ones who have given direct or indirect valuable support.

Thank you Almighty and Universe for everything ©

**Parveen Rani**

### DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Shahbad Daulatpur, Main Bawana Road, Delhi-42

### **CANDIDATE'S DECLARATION**

I <u>Parveen Rani</u> hereby certify that the work which is being presented in the thesis entitled <u>Development of CM Circuits for Analog Signal Processing and Signal</u> <u>Generation</u> in partial fulfillment of the requirements for the award of the Degree of Doctor of Philosophy, submitted in the Department of <u>Electronics and</u> <u>Communication Engineering</u>, Delhi Technological University is an authentic record of my own work carried out during the period from <u>August, 2016</u> to <u>December, 2024</u> under the supervision of <u>Prof. Rajeshwari Pandey</u>.

The matter presented in the thesis has not been submitted by me for the award of any other degree of this or any other Institute.

**Candidate's Signature**

This is to certify that the statement made by the candidate is correct to the best of my knowledge.

Signature of Supervisor

**DELHI TECHNOLOGICAL UNIVERSITY** (Formerly Delhi College of Engineering) Shahbad Daulatpur, Main Bawana Road, Delhi-42

### **CERTIFICATE BY THE SUPERVISOR**

Certified that **Parveen Rani** (2K16/PhD/EC/08) has carried out her research work presented in this thesis entitled **"Development of CM Circuits for Analog Signal Processing and Signal Generation"** for the award of **Doctor of Philosophy** from Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, under my supervision. The thesis embodies results of original work, and studies are carried out by the student herself and the contents of the thesis do not form the basis for the award of any other degree to the candidate or to anybody else from this or any other University/Institution.

Signature

(Prof. Rajeshwari Pandey) (Professor) (Electronics and Communication Engineering) (Delhi Technological University)

Date: /12/2024

### Abstract

Over the past couple of decades, analog signal processing (ASP) has seen a paradigm shift from voltage mode (VM) to current mode (CM) design technique due to inherent merits of the CM processing. Though the design techniques are fundamentally limited by device characteristics; however, for specific applications CM design may provide one or more of the following advantages: higher bandwidth and slew rates, lower power consumption and better signal linearity and accuracy. Additionally, current mode circuits may lead to significant chip area saving also owing to their less complex designs than the voltage mode circuits.

The merits of CM design has led researchers to explore variety of CM analog building blocks (ABBs) and existence of numerous such blocks in literature is a testament of the same. These ABBs find applications in various analog signal processing and generating circuits. The voltage differencing transconductance amplifier (VDTA) is one among the other CM ABBs which is conceptually presented by Biolek et al. in 2008. The VDTA is a voltage input current output ABB having two transconductance gain stages which helps in realization of resistor-less compact CMOS applications. Additionally, the transconductances of the VDTA can be tuned through bias current which facilitates electronic tunability of the system parameters. Thus, VDTA is a preferred choice for designing on-chip high frequency applications. Its first CMOS realization was present by Yesil et al. in 2011.

Further, fractional order (FO) circuits and systems are gaining researcher's increased attention as these provide extra degree of freedom and models natural systems more precisely as compared to their integer order counterparts. Fractional order elements (FOEs) namely fractional capacitors and inductors (FCs and FIs) are the basic building blocks for realizing FO circuits. Though the FCs and FIs are not commercially available as circuit components but a variety of rational approximation methods exists in the open literature to emulate the FCs. The FIs can be derived through classical methods which are used in integer domain for emulating inductors using capacitors.

Thus, combining the advantages of CM processing with fractional order designs researchers have proposed a wide range of signal processing and generation application using variety of ABBs. This research trend has been explored in context of VDTA having identified the advantages of VDTA based designs in the presented work. Additionally, this work also presents few integer order applications of the VDTA.

Exploring significant avenue of the active inductance emulation, VDTA based compact, resistor-less generic inductance emulator (IE) have been proposed. This emulator can be configured as (i) integer order positive inductance emulator (ii) integer order negative inductance emulator (iii) fractional order positive inductance emulator and (iv) fractional order negative inductance emulator.

Research contribution in the domain of analog filter design is presented in the form of a classical integer order filter and two  $\alpha$ -order voltage mode fractional order filters (FOFs) based on VDTA. The integer order filter is a multiple input multiple output biquad filter. Moving on to the fractional order counterparts, first FOF represents voltage mode multiple input single output universal configuration whereas, second FOF topology presents voltage mode single input multiple output multifunction structure.

Further, there is considerable scope for exploring improved design of higher order sinusoidal oscillators. In that attempt, a third order sinusoidal oscillator (TOSO) has been proposed using a single VDTA.

In this work proposition of new CMOS structures of the VDTA are also explored and its outcome has led to the proposition of two new transconductance boosted architectures of the VDTA. The former structure is based on the partial positive feedback whereas the later utilizes the concept of gate to source voltage variation for transconductance enhancement.

The proposed designs are verified either through simulations or combination of simulations and experimental validation. The simulations are carried out either with Cadence tool suite or PSPICE using 180 nm CMOS technology parameters. For experimental purpose, the VDTA is implemented using off the shelf IC LM13700 with  $\pm 10V$  supply voltage.

### List of Tables

| Table 1.1(a) | Literature Summary for Fractional Order Inductance Emulators $(0 < \alpha < 1)$ .                              |

|--------------|----------------------------------------------------------------------------------------------------------------|

| Table 1.1(b) | Literature Summary for Integer Order Inductance Emulators.                                                     |

| Table 1.2(a) | Literature Summary for VDTA based Integer Order Biquads.                                                       |

| Table 1.2(b) | Literature Summary for Fractional Order Filters.                                                               |

| Table 1.3    | Literature Summary for VDTA based Sinusoidal Oscillators.                                                      |

| Table 1.4    | Literature Summary for VDTA CMOS Implementations.                                                              |

| Table 2.1    | Component Values for Carlson based RC Ladder Network with Centre Frequency 1 kHz for 1 $\mu \mho/s^{\alpha}$ . |

| Table 2.2    | CFE based Approximated Transfer Functions.                                                                     |

| Table 2.3    | Component Values for CFE based RC Ladder Network with Centre Frequency 1 kHz for 1 $\mu \sigma/s^{\alpha}$ .   |

| Table 2.4    | Frequency Responses for Approximated FC (1 $\mu \mho/s^{\alpha}$ ) based on CFE (a) Magnitude (b) Phase.       |

| Table 2.5    | Post-Scaling Frequency Range of Operation of the CFE based Approximated FC.                                    |

| Table 2.6    | Post-Scaling Frequency Range of Operation of the CFE based<br>Approximated FC and the Corresponding Phase.     |

| Table 3.1    | Switch Settings for Emulator Selection.                                                                        |

| Table 3.2    | Impedance Functions of Integer and Fractional Order<br>Positive/Negative Inductance Emulators.                 |

| Table 3.3    | Performance Parameters for Fractional Order High Pass Filter.                                                  |

| Table 4.1    | Input Selections for Various Filter Responses.                                                                 |

| Table 4.2    | Input Selections for Various FOF Responses and Corresponding Transfer Functions.                               |

| Table 4.3    | Performance Parameters for FOFs for 1 $\mu \sigma/s^{\alpha}$ ( $\alpha = 0.5$ ).                              |

| Table 4.4    | Performance Parameters for Fractional Order High Pass Filter.                                                  |

| Table 4.5    | Critical Frequencies for Various FOF-III Responses.                                                            |

| Table 6.1    | Device Dimensions.                                                                                             |

| Table 6.2    | Summary of Existing CMOS VDTA Implementations.                                                                 |

Table 7.1Summary of the Work Presented in the Thesis.

#### **List of Figures**

- Fig. 1.1 Classification of Fractional Order Elements [60].

- Fig. 1.2 RC Networks for FC Emulation (a) Foster-I (b) Foster-II (c) Cauer-I (d) Cauer-II.

- Fig. 2.1 VDTA (a) Symbol (b) Equivalent Model (c) CMOS Implementation [27].

- Fig. 2.2 DC Transfer Characteristics of VDTA.

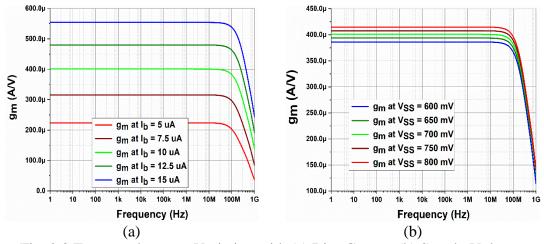

- Fig. 2.3 Transconductance Variation with (a) Bias Current (b) Supply Voltage.

- Fig. 2.4 Truncated n<sup>th</sup> order RC Ladder Circuit.

- Fig. 2.5 Frequency Response for FC of 1  $\mu \overline{O}/s^{\alpha}$  (a) Magnitude (b) Phase.

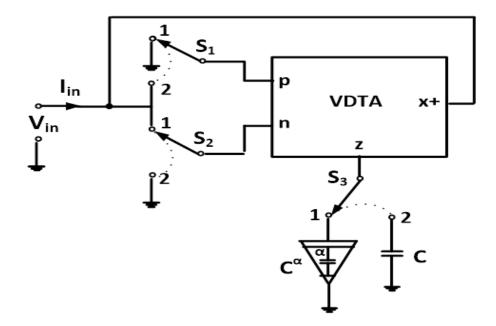

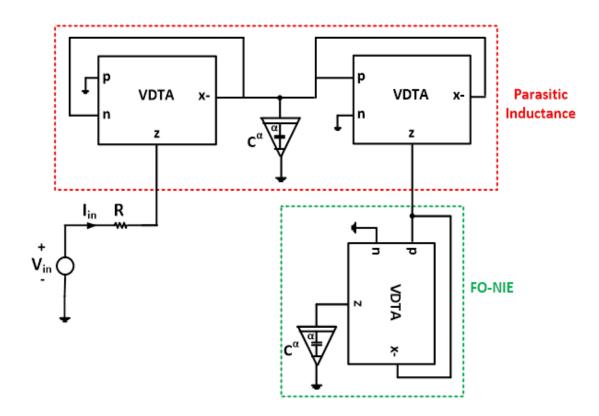

- Fig. 3.1 Proposed Generic Inductance Emulator.

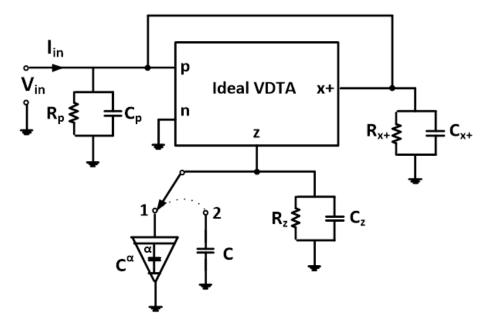

- Fig. 3.2 Non Ideal Behavioural Model of the FO-NIE.

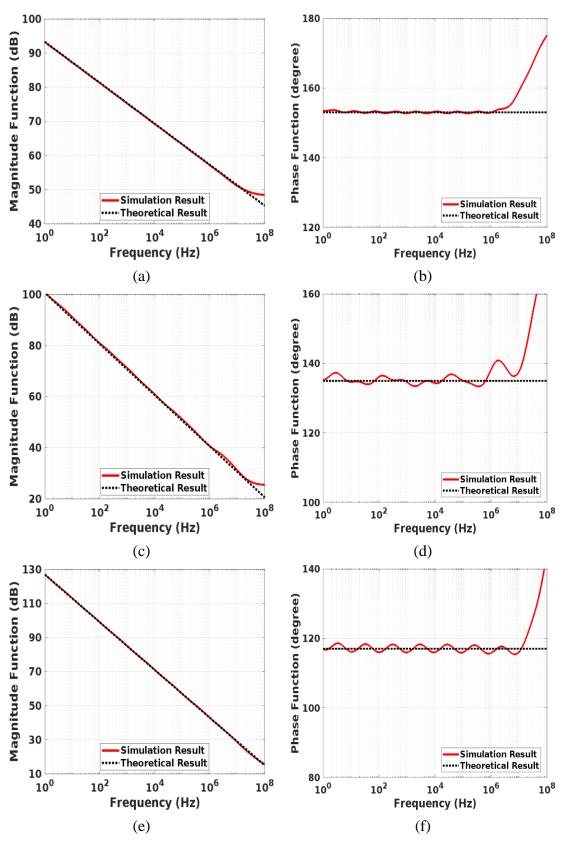

- Fig. 3.3 The FC Impedance: (a),(c),(e) Magnitude (b),(d),(f) Phase Response with  $C^{\alpha} = 12.5 \text{ uV/s}^{0.3}$ , 3.75  $\text{uV/s}^{0.5}$  and 0.13  $\text{uV/s}^{0.7}$  respectively.

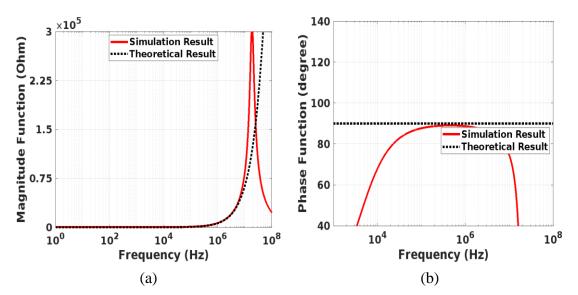

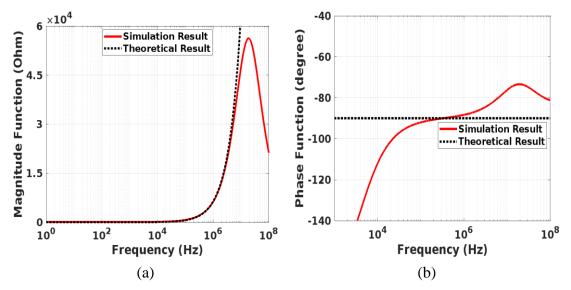

- Fig. 3.4 Positive Impedance: (a) Magnitude (b) Phase Response with L = 1 mH.

- Fig. 3.5 Negative Impedance: (a) Magnitude (b) Phase Response with L = 1 mH.

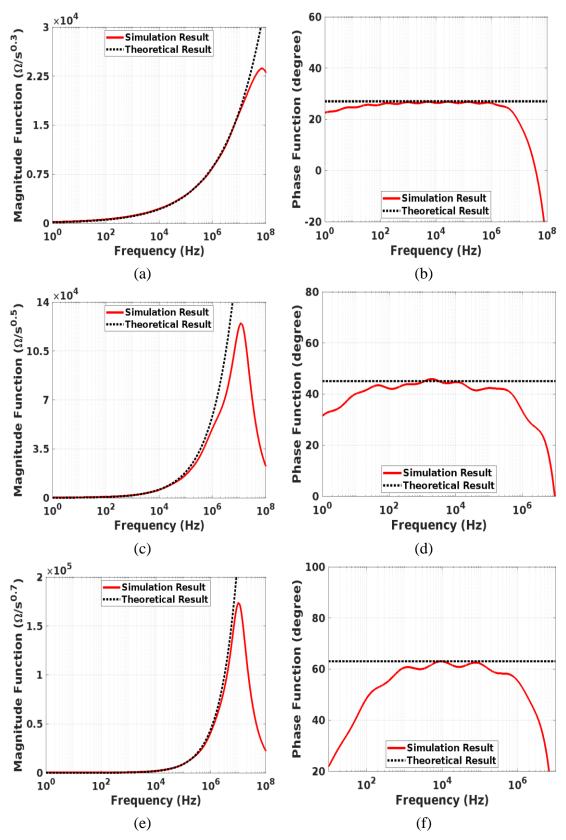

- Fig. 3.6 Fractional Positive Impedance: (a),(c),(e) Magnitude (b),(d),(f) Phase Response with  $L^{\alpha} = 78.13 \ \Omega/s^{0.3}$ , 23.44  $\Omega/s^{0.5}$  and 0.78  $\Omega/s^{0.7}$ respectively.

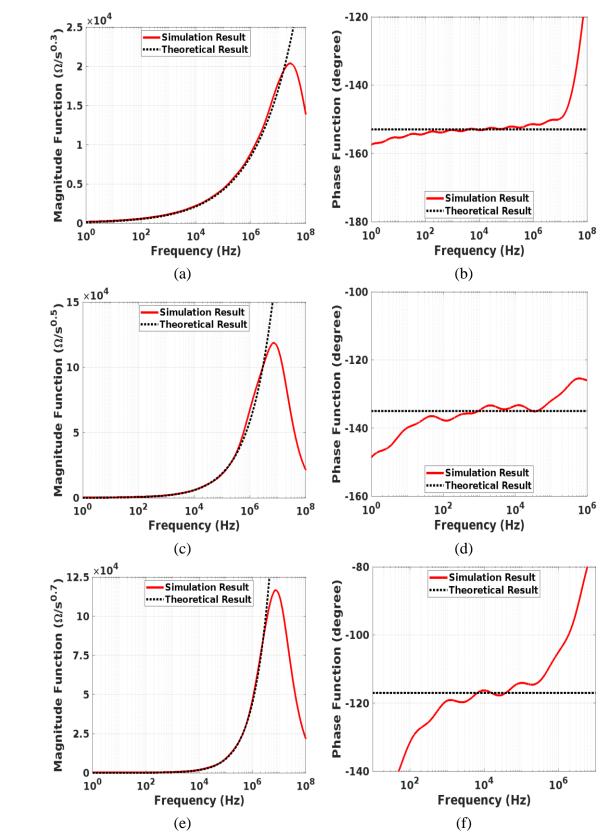

- Fig. 3.7 Fractional Negative Impedance: (a),(c),(e) Magnitude (b),(d),(f) Phase Response for Values 78.13  $\Omega/s^{0.3}$ , 23.44  $\Omega/s^{0.5}$  and 0.78  $\Omega/s^{0.7}$  respectively.

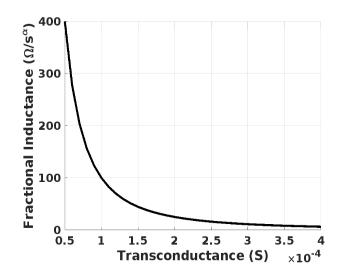

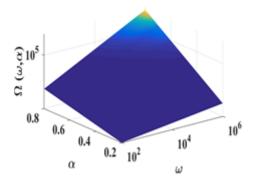

- Fig. 3.8 Fractional Inductance Variation with Transconductance.

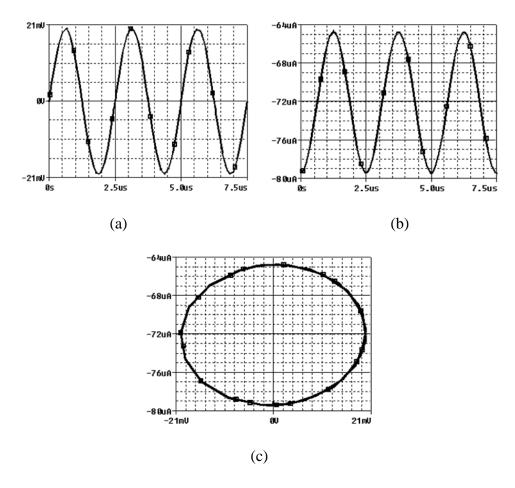

- Fig. 3.9 Positive Impedance: (a),(b) Transient Response: Voltage and Current respectively (c) Lissajous.

- Fig. 3.10 Negative Impedance: (a),(b) Transient Response: Voltage and Current respectively (c) Lissajous.

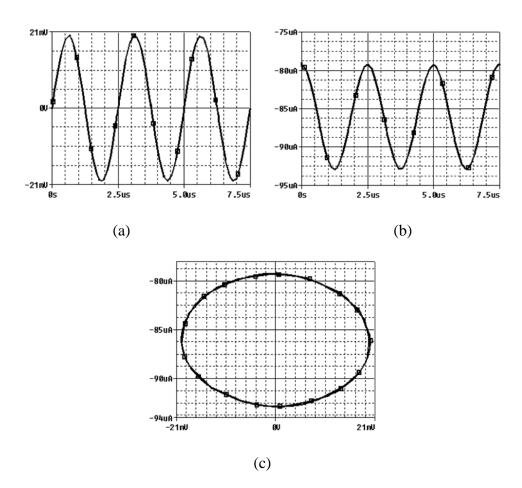

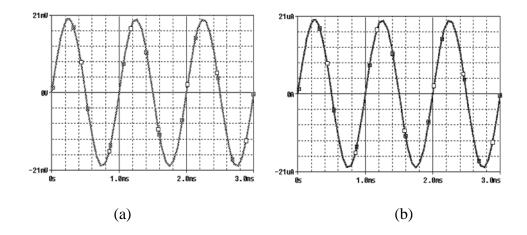

- Fig. 3.11 Fractional Positive Impedance: (a) Transient (b) Lissajous.

- Fig. 3.12 Fractional Negative Impedance: (a) Transient (b) Lissajous.

- Fig. 3.13 Hardware Setup.

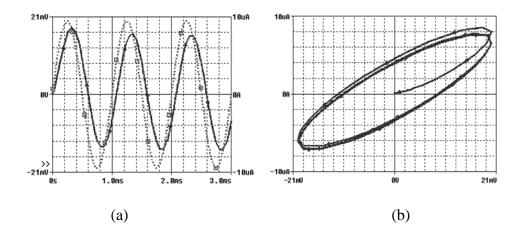

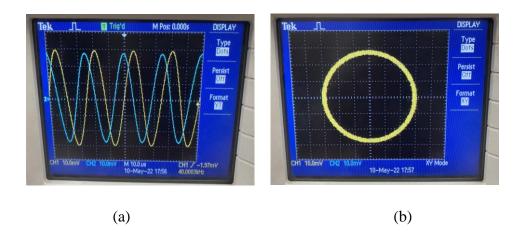

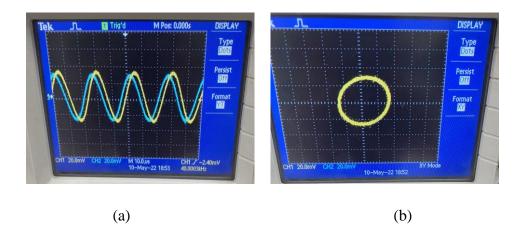

- Fig. 3.14 Positive Impedance: (a) Transient Response (b) Lissajous.

- Fig. 3.15 Negative Impedance: (a) Transient Response (b) Lissajous.

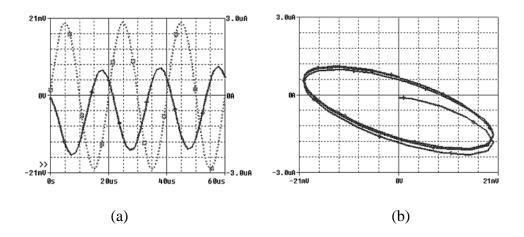

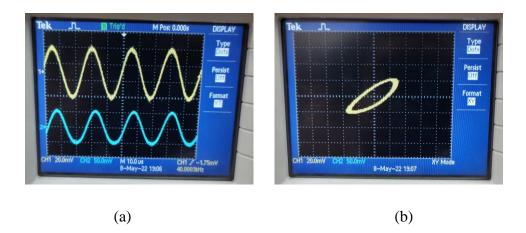

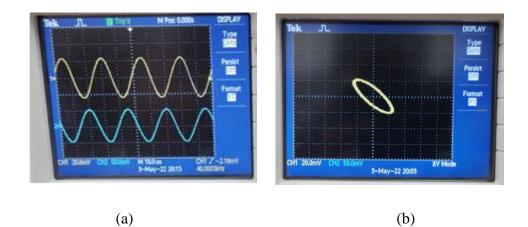

- Fig. 3.16 Fractional Positive Impedance: (a) Transient Response (b) Lissajous.

- Fig. 3.17 Fractional Negative Impedance: (a) Transient Response (b) Lissajous.

- Fig. 3.18 Impedance at different Fractional Orders.

- Fig. 3.19 Circuit depicting Inductance Cancellation using Proposed FO-NIE.

- Fig. 3.20 Transient Response: (a) Voltage (b) Current of the Circuit of Fig. 3.19.

- Fig. 3.21 Circuit depicting FO-HP RL<sup>α</sup>C Filter.

- Fig. 3.22 Frequency Response for FO-HP RL<sup>α</sup>C Filter (a) Magnitude (b) Phase.

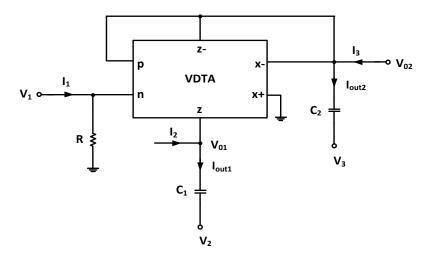

- Fig. 4.1 The Proposed Multi-Mode MIMO Filter.

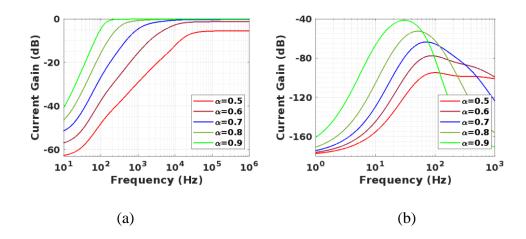

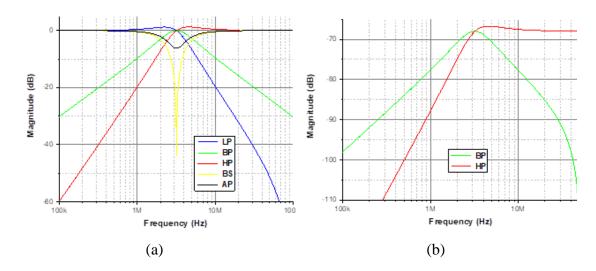

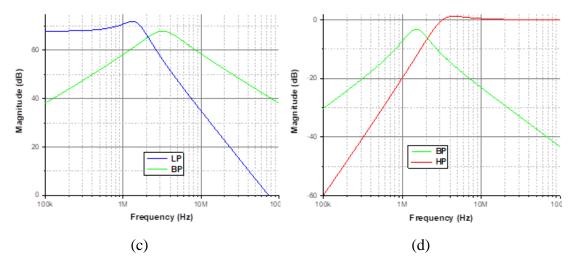

- Fig. 4.2 Magnitude Responses of (a) LP, BP, HP, BS and AP in VM;(b) LP, BP in TAM, (c) LP, BP in TIM (d) HP, BP in CM.

- Fig. 4.3 Electronic Tuning of BP Filter Frequency in VM Mode.

- Fig. 4.4 Proposed FOF-I.

- Fig. 4.5 Frequency Response for FLPF (a) Magnitude (b) Phase.

- Fig. 4.6 Frequency Response for FBPF (a) Magnitude (b) Phase.

- Fig. 4.7 Frequency Response for FHPF (a) Magnitude (b) Phase.

- Fig. 4.8 Frequency Response for FBSF (a) Magnitude (b) Phase.

- Fig. 4.9 Frequency Response for FAPF (a) Magnitude (b) Phase.

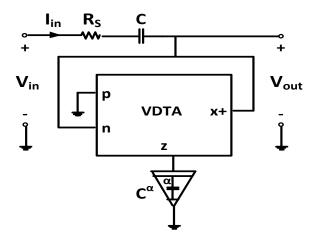

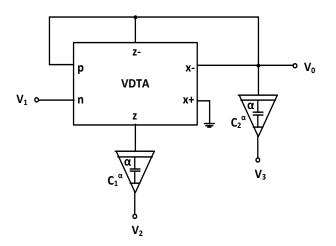

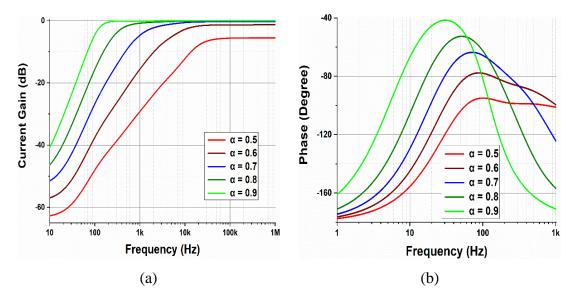

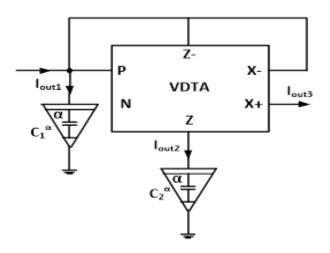

- Fig. 4.10 Proposed FOF-II.

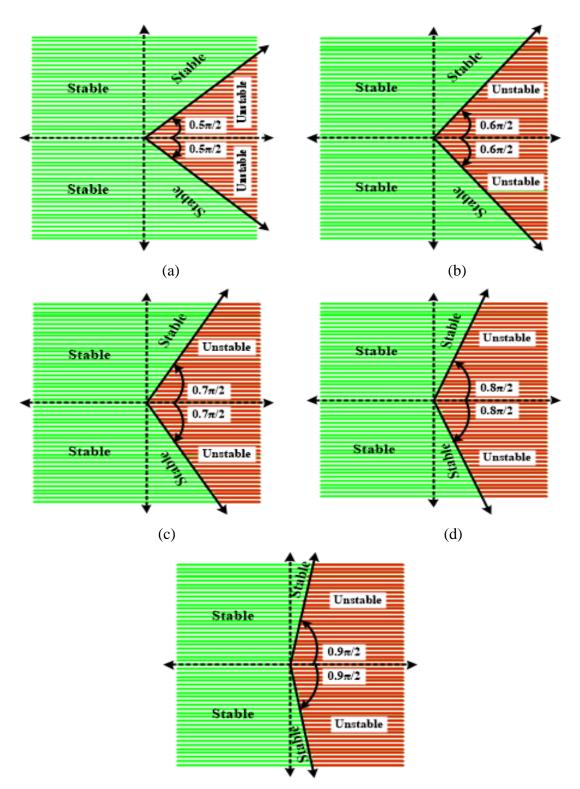

- Fig. 4.11 Stability Region in w Plane for  $\alpha = (a) 0.5$  (b) 0.6 (c) 0.7 (d) 0.8 (e) 0.9.

- Fig. 4.12 Frequency Response for FHPF (a) Magnitude (b) Phase.

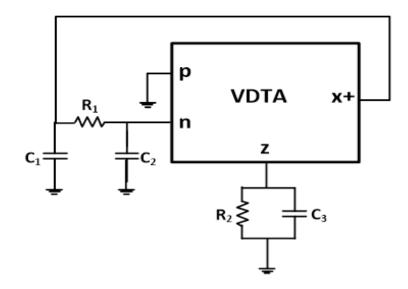

- Fig. 4.13 Proposed FOF-III.

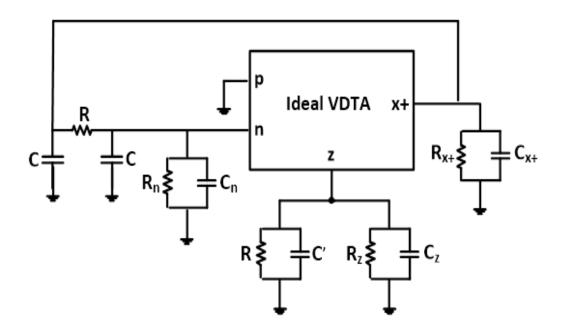

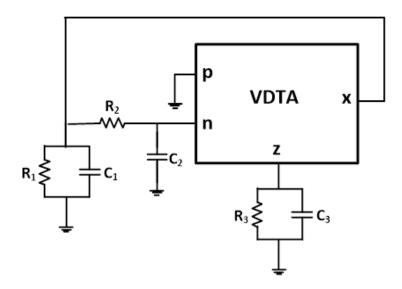

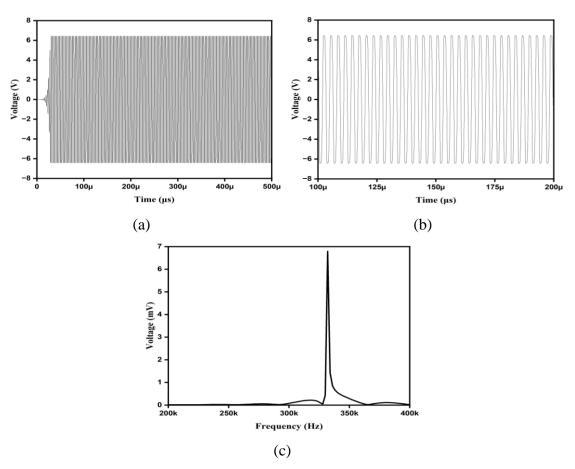

- Fig. 5.1 Proposed Circuit (TOSO-I).

- Fig. 5.2 Non Ideal Behavioural Model of the TOSO-I.

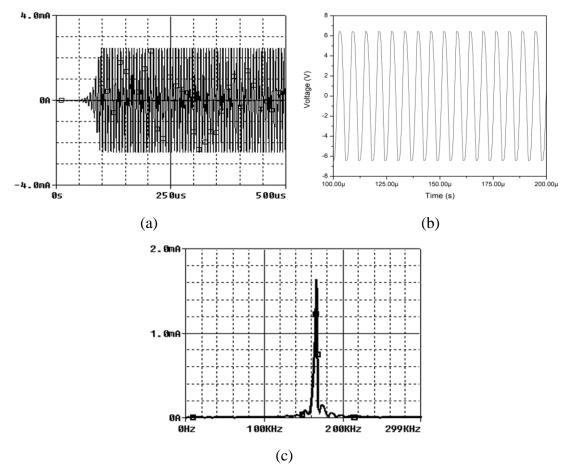

- Fig. 5.3 TOSO-I (a) Transient Output (b) Sustained Oscillations (c) Frequency Spectrum.

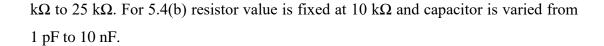

- Fig. 5.4 Frequency Tuning with (a) Resistance (b) Capacitance.

- Fig. 5.5 Proposed Circuit (TOSO-II).

- Fig. 5.6 TOSO-II (a) Transient Output (b) Sustained Oscillations (c) Frequency Spectrum.

- Fig. 6.1 Conventional Scheme for Designing VDTA.

- Fig. 6.2 Proposed VDTA-I (a) Scheme (b) CMOS Implementation.

- Fig. 6.3 Small-Signal High-Frequency Model of TA1 Stage of the Proposed VDTA-I.

- Fig. 6.4 Proposed VDTA-II (a) Scheme (b) CMOS Implementation.

- Fig. 6.5 Small-Signal High-Frequency Model of Proposed VDTA-II.

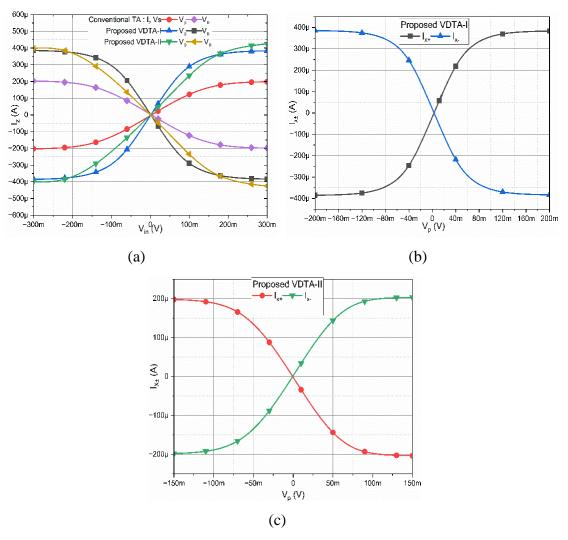

- Fig. 6.6 The DC Transfer Characteristics (a)  $I_z$  versus  $V_{in}$ (b)  $I_{x\pm}$  versus  $V_p$  for VDTA-I (c)  $I_{x\pm}$  versus  $V_p$  for VDTA-II.

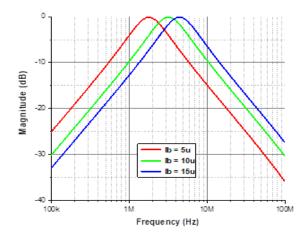

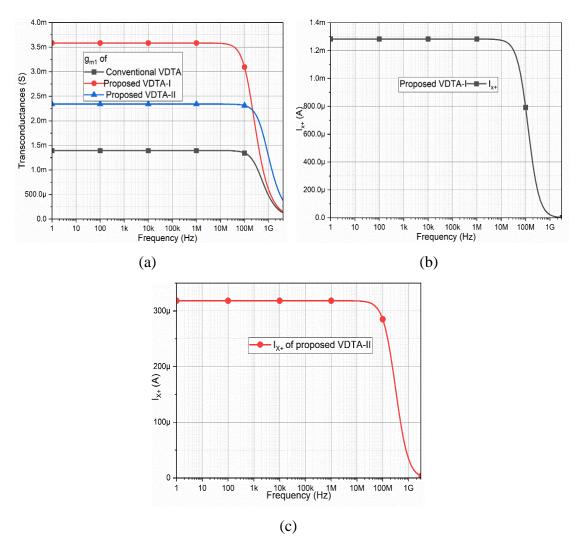

- Fig. 6.7 Frequency Response (a) Transconductance Gain (g<sub>m1</sub>) (b) I<sub>x+</sub> of VDTA-I

I (c) I<sub>x+</sub> of VDTA-II.

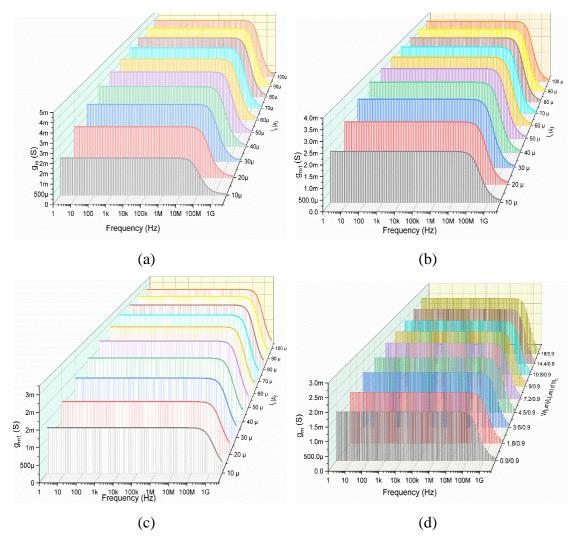

- Fig. 6.8 AC Response of Transconductance  $(g_{m1})$  with variation in (a) I<sub>b</sub> for VDTA-I (b) I<sub>s</sub> for VDTA-I (c) I<sub>b</sub> for VDTA-II (d) Gain of Inverters for VDTA-II.

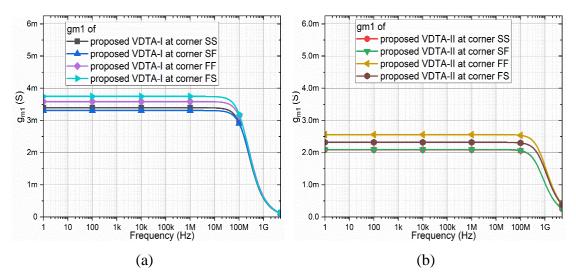

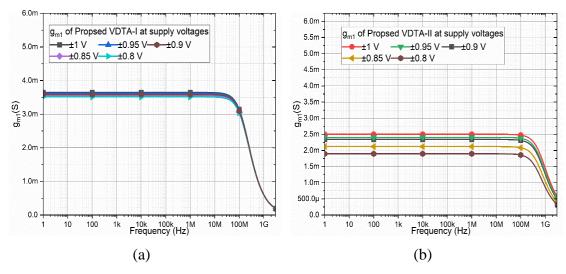

- Fig. 6.9 Transconductance for different Process Corners (SS, SF, FS and FF) (a) VDTA-I (b) VDTA-II.

- Fig. 6.10 Transconductances for different Supply Voltages for proposed (a) VDTA-I (b) VDTA-II.

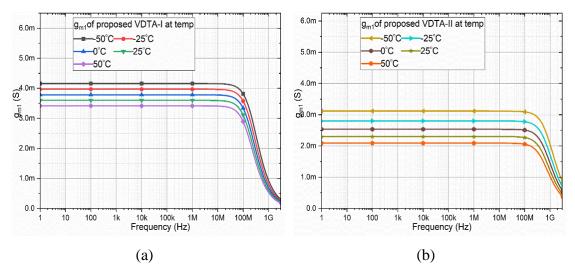

- Fig. 6.11 Variations in Transconductance with respect to Temperature for (a) VDTA-I and (b) VDTA-II.

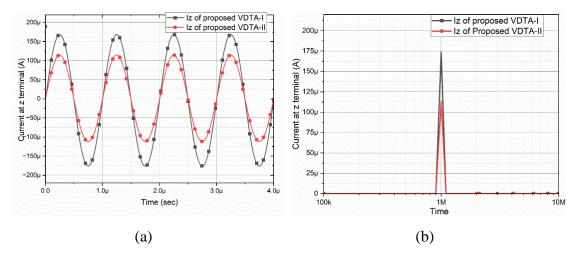

- Fig. 6.12 Current  $I_{x+}$  for VDTA-I and VDTA-II (a) Time domain (b) FFT, for Sinusoidal inputs.

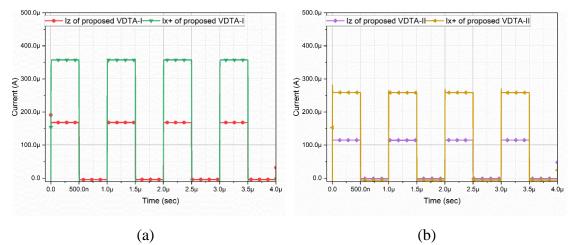

- Fig. 6.13 Current at Z and X+ Terminal for (a) Proposed VDTA-I (b) Proposed VDTA-II.

### List of Abbreviations

| Analog Building Blocks                                          | ABBs      |

|-----------------------------------------------------------------|-----------|

| Analog Signal Processing                                        | ASP       |

| Current Conveyor                                                | CC        |

| Current Differencing Buffered Amplifier                         | CDBA      |

| Current Differencing Transconductance Amplifier                 | CDTA      |

| Current Feedback Operational Amplifier                          | CFOA      |

| Current Mode                                                    | СМ        |

| Fractional order Capacitor                                      | FC        |

| Fractional order Inductor                                       | FI        |

| Fractional order All Pass Filter                                | FAPF      |

| Fractional order Band Pass Filter                               | FBPF      |

| Fractional order Band Stop/Reject Filter                        | FBSF/FBRF |

| Fractional order High Pass Filter                               | FHPF      |

| Fractional order Low Pass Filter                                | FLPF      |

| Fractional Order                                                | FO        |

| Fractional Order Elements                                       | FOEs      |

| Fractional Order Filter                                         | FOF       |

| Multiple Input Multiple Output                                  | MIMO      |

| Multiple Input Single Output                                    | MISO      |

| Multiple-output Voltage Differencing Transconductance Amplifier | MO-VDTA   |

| Second-generation Current Conveyor                              | CCII      |

| Single Input Single Output                                      | SISO      |

| Single Input Multiple Output                                    | SIMO      |

| Sinusoidal Oscillator                                           | SO        |

| Third-generation Current Conveyor                               | CCIII     |

| Third Order Sinusoidal Oscillator                               | TOSO      |

| Transadmittance Mode                                            | TAM       |

|                                                                 |           |

| Transimpedance Mode                                    | TIM     |

|--------------------------------------------------------|---------|

| Voltage Differencing Transconductance Amplifier        | VDTA    |

| Voltage Mode                                           | VM      |

| Z-copy Voltage Differencing Transconductance Amplifier | ZC-VDTA |

### CONTENTS

| Title                         | Page No. |

|-------------------------------|----------|

| Acknowledgement               | ii       |

| Candidate's Declaration       | iii      |

| Certificate by the Supervisor | iv       |

| Abstract                      | v        |

| List of Tables                | vii      |

| List of Figures               | viii     |

| List of Abbreviations         | xi       |

| CHAPTER 1: INTRODUCTION                          |    | 1-26  |

|--------------------------------------------------|----|-------|

| 1.1. INTRODUCTION                                | 2  |       |

| 1.2. LITERATURE REVIEW                           | 5  |       |

| 1.2.1 INDUCTANCE EMULATION                       | 5  |       |

| 1.2.2 ANALOG FILTER AND FRACTIONAL ORDER FILTERS | 9  |       |

| 1.2.3 SINUSOIDAL OSCILLATORS                     | 18 |       |

| 1.2.4 VDTA IMPLEMENTATIONS                       | 20 |       |

| 1.3. RESEARCH GAPS                               | 22 |       |

| 1.4. RESEARCH OBJECTIVES                         | 23 |       |

| 1.5. ORGANIZATION OF THE THESIS                  | 23 |       |

|                                                  |    |       |

| CHAPTER 2: PRELIMINARIES                         |    | 27-46 |

| 2.1. INTRODUCTION                                | 28 |       |

| 2.2. THE VDTA                                    | 29 |       |

| 2.2.1 SIMULATION RESULTS                         | 31 |       |

|                                                  | 22 |       |

| 2.3. FC REALIZATION                           | 32 |

|-----------------------------------------------|----|

| 2.3.1 FC REALIZAITON USING CARLSON METHOD     | 32 |

| 2.3.1.1 SIMULATION RESULTS                    | 35 |

| 2.3.2 THE CONTINUED FRACTION EXPANSION METHOD | 35 |

| 2.3.2 FC REALIZAITON USING CFE METHOD                     | 38  |        |

|-----------------------------------------------------------|-----|--------|

| 2.3.2.1 SIMULATION RESULTS                                | 40  |        |

| 2.4. CONCLUSION                                           | 45  |        |

|                                                           |     |        |

| CHAPTER 3: GENERIC INDUCTANCE EMULATOR                    |     | 47-72  |

| 3.1. INTRODUCTION                                         | 48  |        |

| 3.2. PROPOSED GENERIC INDUCTANCE EMULATOR                 | 48  |        |

| 3.2.1 INTEGER ORDER INDUCTANCE EMULATOR                   | 50  |        |

| 3.2.2 FRACTIONAL ORDER INDUCTANCE EMULATOR                | 50  |        |

| 3.3. NON-IDEAL ANALYSIS                                   | 51  |        |

| 3.4. FUNCTIONAL VALIDATION                                | 52  |        |

| 3.4.1 SIMULATION RESULTS                                  | 53  |        |

| 3.4.1.1 THE FC IMPLEMENTATION                             | 53  |        |

| 3.4.1.2 INTEGER ORDER INDUCTANCE EMULATOR                 | 55  |        |

| 3.4.1.3 FRACTIONAL ORDER INDUCTANCE EMULATOR              | 56  |        |

| 3.4.2 EXPERIMENTAL RESULTS                                | 64  |        |

| 3.5. APPLICATIONS                                         | 67  |        |

| 3.5.1 INDUCTANCE CANCELLATION                             | 67  |        |

| 3.5.2 FRACTIONAL ORDER HIGH PASS RL <sup>α</sup> C FILTER | 69  |        |

| 3.6. CONCLUSION                                           | 71  |        |

| CHAPTER 4: INTEGER AND FRACTIONAL ORDER FITL              | ERS | 73-100 |

| 4.1. INTRODUCTION                                         | 74  |        |

| 4.2. INTEGER ORDER FILTER                                 | 75  |        |

| 4.2.1 SENSITIVITY ANALYSIS                                | 78  |        |

| 4.2.2 SIMULATION RESULTS                                  | 79  |        |

| 4.3. PROPOSED FOF-I                                       | 81  |        |

| 4.3.1 THE FRACTIONAL ORDER LOW PASS FILTER                | 83  |        |

| 4.3.2 THE FRACTIONAL ORDER BAND PASS FILTER               | 84  |        |

| 4.3.3 THE FRACTIONAL ORDER HIGH PASS FILTER               | 85  |        |

| 4.3.4 THE FRACTIONAL ORDER BAND STOP/REJECT FILTER | 86  |

|----------------------------------------------------|-----|

| 4.3.5 THE FRACTIONAL ORDER ALL PASS FILTER         | 87  |

| 4.3.6 SIMULATION RESULTS                           | 88  |

| 4.4. PROPOSED FOF-II                               | 92  |

| 4.4.1 SENSITIVITY ANALYSIS                         | 94  |

| 4.4.2 STABILITY ANALYSIS                           | 94  |

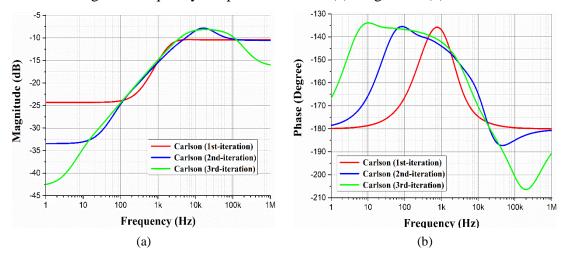

| 4.4.3 SIMULATION RESULTS                           | 96  |

| 4.5. PROPOSED FOF-III                              | 97  |

| 4.6. CONCLUSION                                    | 100 |

| CHAPTER 5: SINUSOIDAL OSCILLATORS | 101-112 |

|-----------------------------------|---------|

| 5.1. INTRODUCTION                 | 102     |

| 5.2. TOSO-I                       | 103     |

| 5.2.1 NON-IDEAL ANALYSIS          | 105     |

| 5.2.2 SENSITIVITY ANALYSIS        | 106     |

| 5.2.3 SIMULATION RESULTS          | 107     |

| 5.3. TOSO-II                      | 109     |

| 5.3.1 SENSITIVITY ANALYSIS        | 111     |

| 5.3.2 SIMULATION RESULTS          | 111     |

| 5.4. CONCLUSION                   | 112     |

| CHAPTER 6: VDTA STRUCTURES | 113-130 |

|----------------------------|---------|

| 6.1. INTRODUCTION          | 114     |

| 6.2. PROPOSED CIRCUITS     | 115     |

| 6.2.1 CONVENTIONAL VDTA    | 115     |

| 6.2.2 PROPOSED VDTA-I      | 116     |

| 6.2.3 PROPOSED VDTA-II     | 119     |

| 6.3. SIMULATION RESULTS    | 122     |

| 6.3.1 DC CHARACTERISTICS   | 123     |

| 6.3.2 AC CHARACTERISTICS | 124 |

|--------------------------|-----|

| 6.3.3 PVT ANALYSIS       | 126 |

| 6.3.4 TRANSIENT RESPONSE | 128 |

| 6.4. CONCLUSION          | 130 |

### CHAPTER 7: CONCLUSION AND FUTURE SCOPE 131-136

| 7.1. | SUMMARY OF WORK DONE | 132 |

|------|----------------------|-----|

| 7.2. | FUTURE SCOPE         | 136 |

# CHAPTER – 1 INTRODUCTION

#### **1.1 Introduction**

Researchers are continuously striving to explore different analog building blocks (ABBs) with attributes like higher bandwidth, higher slew rate, lower power consumption and better linearity. This has led to paradigm shift from voltage mode (VM) to current mode (CM) [1,2] signal processing. Numerous CM ABBs have evolved as presented in [3] and references cited therein. The current conveyor (CC) [4], a hybrid voltage/current circuit, is the most exhaustively explored/utilized block. Since then, three generations of the CC; namely CCI, CCII [5] and CCIII [6], which differ in terms of the terminal characteristics were introduced way back in 1968, 1970 and 1995 respectively. The current feedback operational amplifier (CFOA) [7] has terminal characteristics that resemble those of a CCII followed by a voltage follower. The circuit element operational transresistance amplifier (OTRA) [8] serves/functions as a current controlled voltage source (CCVS). Recently, yet another class of CM blocks having current differencing input stage, has also emerged. Current Differencing Transconductance Amplifier (CDTA) [9] and current differencing buffered amplifier (CDBA) [10] are two notable examples of this class. The voltage differencing transconductance amplifier (VDTA) is yet another versatile CM analog building blocks available in literature. The VDTA is a voltage input current output ABB having two transconductance gain stages which helps in realization of resistor-less compact CMOS applications. Additionally, the transconductances of the VDTA can be tuned through bias current which facilitates electronic tunability of the system parameters. Thus, VDTA is a preferred choice for designing on-chip high frequency applications. This has led to realization of various signal processing [11-43] and generation [44-53] applications based on VDTA. Its CMOS implementation was first proposed by Yesil et al. [11]. Since then, various research efforts are made to propose CMOS implementations [11,15,18,27,110-112] of VDTA with enhanced performance.

On the other hand, fractional order (FO) signal processing which is based on the fundamentals of fractional calculus is an emerging interdisciplinary research area. Fractional calculus is the domain of mathematics concerned with the investigation and application of derivatives and integrals of arbitrary (real or complex) order [54-56]. A fractional derivative of order ' $\alpha$ ' may be represented by the Riemann–Liouville definition

$$D^{\alpha}f(t) \coloneqq \begin{cases} \frac{1}{\Gamma(n-\alpha)} \frac{\partial^{n}}{\partial t^{n}} \int_{0}^{t} \frac{f(\tau)}{(t-\tau)^{\alpha+1-n}} \partial \tau & ; n-1 < \alpha < n \\ \frac{\partial^{n}}{\partial t^{n}} f(t) & ; \alpha = n \end{cases}$$

(1.1)

The Grunwald–Letnikov approximation gives a more physical interpretation of a fractional derivative

$$D^{\alpha}f(t) \triangleq \left(\Delta t\right)^{-\alpha} \sum_{i=0}^{n} \frac{\Gamma(i-\alpha)}{\Gamma(-\alpha)\Gamma(i+1)} f\left((n-i)\Delta t\right)$$

(1.2)

where  $\Delta t$  represents the integration step. In order to describe electronic circuits in the complex frequency s-domain, Laplace transform is widely used. Thus, assuming zero initial conditions and applying the Laplace transform to Eqn. (1.2), yields

$$L\left\{{}_{0}\partial_{t}^{\alpha}f(t)\right\} = s^{\alpha}F(s)$$

(1.3)

where  ${}_{0}\partial_{t}^{\alpha}f(t) = \partial f(t)/\partial t$  with zero initial conditions.

Fractional order circuits and systems are gaining researchers' increased attention as these provide extra degree of freedom and models natural systems more precisely [57-59] as compared to their integer order counterparts. These circuits find potential applications pertaining to biomedical, instrumentation and control and analog signal processing and generation. Fractional order elements (FOEs) are the basic building blocks for realizing FO circuits and may be characterized by the generalized impedance function

$$Z_F^{\alpha}(s) = Ks^{\alpha} = K\omega^{\alpha} \exp(j(\alpha\pi/2))$$

(1.4)

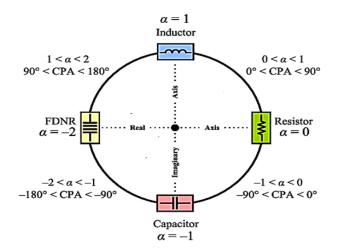

where 'K' is termed as fractance and ' $\alpha$ ' represents the order of the FOE. The phase of the FOE does not depend on the frequency and remains incessant; hence it can also be termed as a constant phase element (CPE) and the corresponding phase can be referred as the constant phase angle (CPA). The ' $\alpha$ ' is a fractional number in the range -n <  $\alpha$  < n, where 'n' is an integer number. The generalized impedance function of Eqn. (1.4) represents impedance of a fractional capacitor (FC) if ' $\alpha$ ' assumes a negative value and a positive ' $\alpha$ ' value corresponds to impedance of fractional inductor (FI) as depicted in Fig. 1.1.

Fig. 1.1 Classification of Fractional Order Elements [60].

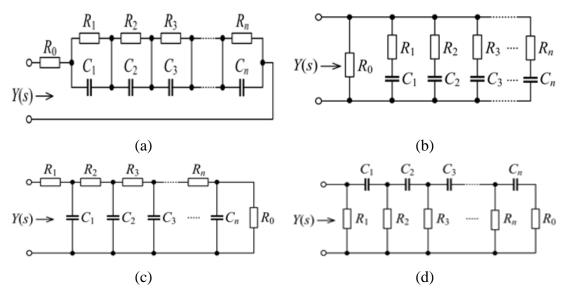

The fractional order elements (FOEs) namely FCs and FIs are not commercially available as circuit components. However, the research efforts are being directed towards designing physical FCs [57-59] though, still at very primitive phase. A variety of rational approximation methods [61-69] exists in the open literature to emulate the behaviour of FCs in the range ( $-1 < \alpha < 0$ ). The FCs so derived can be realized using appropriately configured RC networks depicted in Fig. 1.2.

Fig. 1.2 RC Networks for FC Emulation (a) Foster-I (b) Foster-II (c) Cauer-I (d)

Cauer-II.

In last few decades analog signal processing has seen a paradigm shift from voltage mode (VM) to current mode (CM) due to inherent advantages of CM processing. Combining the advantages of fractional order designs with CM processing, researchers have proposed a variety of signal processing and generation applications using variety of ABBs. In this work this research trend has been explored in context of VDTA having identified the advantages of VDTA based designs.

#### **1.2 Literature Review**

It is observed through comprehensive literature survey that a wide range of electronic circuits using VDTA have been proposed in the literature which broadly include application areas such as grounded inductance simulation [12,13], filter design [11,14-43], signal generation [44-53] and VDTA implementation [11,15,18,27,110-112].

#### **1.2.1 Inductance Emulation**

Inductors are an integral part of the electronic circuit design; however, designing an inductor on a chip has issue/challenge in terms of the usage of space, weight, cost and tunability. Thus, it is desired to simulate an inductor using the active components

available thereby saving in chip area. Further, to reap the advantages of fractional order processing; fractional order inductor (FI) realization is equally important. The fractional inductor in the range ( $0 < \alpha < 1$ ) [70-77] can be emulated using various active RC methods similar to their integer order counter parts. These systematic methods include functional block diagram (FBD) approach and generalized impedance converter (GIC) based realization. These methods use large number of active blocks for FI realization. Alternatively, the FI can also be realized using direct intuitive methods using different active blocks and few passive components. An exhaustive review suggests that though VDTA based integer order grounded inductances realizations are available [12,13] in literature but no fractional order inductors are existing. A further exploration suggested that few realizations of FI [69-76] using ABBs other than VDTA are available as enlisted in Table 1.1(a). Additionally, detailed comparison of a few available conventional integer order reading order inductance simulators [12,13,78-86] has been presented in Table 1.1(b) for ready reference.

|      | ABB                | Passive | Elements    |               | Emulator Type                    | Electronic |

|------|--------------------|---------|-------------|---------------|----------------------------------|------------|

| Ref. | No. Type           | C/FC    | R           | Method Used   | (Positive<br>/Negative<br>/Both) | Tuning     |

| [70] | 1 DXCCTA           | 1C (G)  | 0           | Direct Method | Both                             | Yes        |

| [71] | 1 CCTA             | 1FC (G) | 1R (G)      | Direct Method | Both                             | Yes        |

| [72] | 2 Op-Amps          | 1FC (F) | 4R (1G+3F)  | GIC           | Positive                         | No         |

| [73] | 9 OTAs             | 2C (G)  | 0           | FBD           | Positive                         | Yes        |

| [74] | 1 CFOA             | 1FC (F) | 2R (1G+1F)  | Direct Method | Positive                         | No         |

| [75] | 2 Op-Amps          | 1FC (F) | 4R (1G+3F)  | GIC           | Positive                         | No         |

| [76] | 1 OTA + 10 Op-Amps | 3C (F)  | 17R (F)     | FBD           | Positive                         | No         |

|      | 23 CCIIs           | 3C (G)  | 14R (G)     | FBD           | Positive                         | No         |

|      | 10 CFOAs           | 3C (G)  | 17R (8G+9F) | FBD           | Positive                         | No         |

|      | 14 OTAs            | 3C (G)  | 0           | FBD           | Positive                         | Yes        |

| [77] | 3 CFOAs            | 1FC (G) | 3R (2G+1F)  | Direct Method | Positive                         | No         |

Table 1.1(a) Literature Summary for Fractional Order Inductance Emulators ( $0 \le \alpha \le 1$ ).

|      | ABB         | Passiv | Emulator Type<br>(Positive | Electronic |        |

|------|-------------|--------|----------------------------|------------|--------|

| Ref. | No. Type    | С      | R                          | /Negative  | Tuning |

|      |             |        |                            | /Both)     |        |

| [78] | 1 OTRA      | 1C (F) | 5R (2G+3F)                 | Negative   | No     |

| [70] | 1 DXCCTA    | 1C (G) | 0                          | Both       | Yes    |

| [71] | 1 CCTA      | 1C (G) | 1R (G)                     | Both       | Yes    |

| [79] | 2 CCCDBAs   | 1C (G) | 0                          | Negative   | No     |

| [80] | 1 DXCCII    | 1C (F) | 2R (1G+1F)                 | Both       | No     |

| [81] | 1 CBTA      | 1C (G) | 1R (1G)                    | Both       | No     |

| [82] | 1 ZC-CCCITA | 1C (G) | 0                          | Both       | No     |

| [83] | 1 VDCC      | 1C (G) | 1R (1G)                    | Both       | No     |

| [84] | 1 OTRA      | 1C (F) | 4R (4F)                    | Negative   | No     |

| [85] | 1 OTRA      | 1C (F) | 3R (3F)                    | Negative   | No     |

| [86] | 1 CDBA      | 1C (G) | 3R (1G+2F)                 | Negative   | No     |

| [12] | 1 VDTA      | 1C (G) | 0                          | Positive   | Yes    |

| [13] | 1 VDTA      | 1C (G) | 0                          | Positive   | Yes    |

Table 1.1(b) Literature Summary for Integer Order Inductance Emulators.

It may be observed from Table 1.1(a) that

- only two topologies [70,71] can emulate both negative and positive fractional order inductance. Further, the topology presented in [71] makes use of resistance

- the emulators of [72,73,75-77] use large number of ABBs

- the existing topologies use large number of resistances [71,72,74-77] and capacitances [73,76]

- Refs. [70,71,74,77] use direct method while [72,75] and [73,76] make use of GIC and FBD based approaches respectively

- Refs [72,74-77] use floating components

- inductance emulators [72,74-77] lack electronic tuning.

Further, inspection of Table 1.1(b) suggests that

- existing designs [71,80,81,83-86] use more number of passive components than the proposed one

- the structure of [79] makes use of more number of ABBs

- Refs. [80,84-86] use floating passive components as against the proposed topology which employs grounded capacitor only.

#### **1.2.2 Analog Filter and Fractional order Filters**

Filters are an important class of electronic circuits and widely used for analog signal processing for a wide range of applications. Further, the use of fractional order calculus in analog filter design offers the advantage of better control of the attenuation gradient in stop band as the magnitude response of an  $(n+\alpha)$  order filter exhibits a stop-band attenuation of  $20^*(n+\alpha)$  dB/decade, as against  $20^*n$  dB/decade by integer-order filter where, *n* represents an integer value. In order to achieve FO behaviour, the fractional order filters (FOFs) either make use of an emulated FOE or deploy a suitable integer-order transfer function, to obtain a fractional order

counterpart, which is subsequently realized using functional block diagram (FBD) approach.

The filter structures on the basis of number of inputs processed and outputs provided can be classified as single-input single-output (SISO), single-input multiple-output (SIMO) and multiple-input single-output (MISO) and multiple-input multiple-output (MIMO).

A detailed review of various VDTA based filters suggests a variety of SISO [14], SIMO [15-30], MISO [18,24,27,31-40] and MIMO [11] integer order VDTA based filters available literature. On the other hand, though a variety of fractional order filters (FOFs) [41-43,87-108] implemented around other ABBs are available but only limited VDTA based fractional order filters (FOFs) are reported [41-43]. Only two FOFs based on VDTA have been reported so far. Both the FOFs are designed using the FBD approach for fractional orders ( $\alpha = 1.1$ , 1.5, 1.8). FOFs [41] are designed around three and four VDTAs providing fractional order band pass filter (FBPF) and fractional order band stop/reject filter (FBSF/FBRF) responses respectively. Likewise, [42] provides fractional order low pass filter (FLPF) and fractional order high pass filter (FHPF) responses respectively. A detailed comparison of all available conventional biquads and fractional-order filters has been presented in Tables 1.2(a) and 1.2(b) for ready reference.

| Def           | No. of  | Filter     | Passive E    | Elements   | Filter             |

|---------------|---------|------------|--------------|------------|--------------------|

| Ref.          | VDTA(s) | Mode Type  | R            | С          | Response(s)        |

| SISO Filters: |         |            |              |            |                    |

| [14]          | 1 VDTA  | VM (SISO)  | 0            | 2C (1F+1G) | HP                 |

| SIMO Filters: |         |            |              |            |                    |

| [15]          | 1 VDTA  | CM (SIMO)  | 0            | 2C (2G)    | LP, BP, HP         |

| [16]          | 2 VDTAs | CM (SIMO)  | 0            | 2C (2G)    | LP, BP, HP         |

| [17]          | 2 VDTAs | VM (SIMO)  | 2 MOS-R (2G) | 2C (2G)    | LP, BP, HP, BS, AP |

| [18]          | 2 VDTAs | TAM (SIMO) | 0            | 2C (1F+1G) | LP, BP, HP         |

| [19]          | 1 VDTA  | CM (SIMO)  | 1R (G)       | 2C (2G)    | LP, BP, HP, BS, AP |

| [20]          | 2 VDTAs | TAM (SIMO) | 0            | 2C (2G)    | LP, BP, HP         |

| [21]          | 2 VDTAs | VM (SIMO)  | 0            | 2C (2G)    | LP, BP             |

|               | 2 VDTAs | CM (SIMO)  | 0            | 2C (2G)    | LP, BP, BR         |

| [22]          | 1 VDTA  | CM (SIMO)  | 0            | 2C (2G)    | LP, BP             |

| [23]          | 1 VDTA  | TAM (SIMO) | 1R (F)       | 2C (2G)    | BP, HP             |

| [24]          | 2 VDTAs | TAM (SIMO) | 0            | 2C (1F+1G) | LP, BP, HP         |

Table 1.2(a) Literature Summary for VDTA based Integer Order Biquads.

| Ref.              | No. of    | Filter         | Passive E    | Elements   | Filter             |

|-------------------|-----------|----------------|--------------|------------|--------------------|

| Kel.              | VDTA(s)   | Mode Type      | R            | С          | Response(s)        |

| SIMO Filters (con | ntinued): | 1              |              |            |                    |

| [25]              | 1 VDTA    | TAM (SIMO)     | 1R (G)       | 2C (1F+1G) | LP, BP, HP, BR     |

| [26]              | 1 VDTA    | VM & CM (SIMO) | 1R (G)       | 3C (1F+2G) | LP, BP, HP         |

| [27]              | 2 VDTAs   | TAM (SIMO)     | 0            | 2C (2G)    | LP, BP, HP         |

| [28]              | 3 VDTAs   | VM (SIMO)      | 0            | 2C (2G)    | LP, BP, HP         |

|                   | 3 VDTAs   | TAM (SIMO)     | 0            | 2C (2G)    | LP, BP, HP, BR, AP |

| [29]              | 1 VDTA    | TIM (SIMO)     | 2 MOS-R (2G) | 2C (2G)    | LP, BP, HP, BR     |

| [30]              | 2 VDTAs   | VM (SIMO)      | 1R (G)       | 2C (2G)    | LP, BP             |

| MISO Filters:     |           |                |              |            |                    |

| [31]              | 1 VDTA    | VM (MISO)      | 0            | 2C (2F)    | LP, BP, HP, BS, AP |

| [18]              | 2 VDTAs   | VM (MISO)      | 0            | 2C (1F+1G) | LP, BP, HP, BS, AP |

|                   | 2 VDTAs   | TAM (MISO)     | 0            | 2C (1F+1G) | LP, BP, HP, BS, AP |

| [32]              | 2 VDTAs   | CM (MISO)      | 0            | 2C (2G)    | LP, BP, HP, BS, AP |

| [33]              | 1 VDTA    | VM (MISO)      | 1R (G)       | 2C (2F)    | LP, BP, HP, BS, AP |

Table 1.2(a) (continued)

| Ref.             | No. of     | Filter     | Passive E    | Elements   | Filter             |

|------------------|------------|------------|--------------|------------|--------------------|

| Kel.             | VDTA(s)    | Mode Type  | R            | С          | Response(s)        |

| MISO Filters (co | ontinued): |            |              |            |                    |

| [34]             | 1 VDTA     | VM (MISO)  | 1R (F)       | 2C (1F+1G) | LP, BP, HP, BS, AP |

| [35]             | 1 VDTA     | CM (MISO)  | 0            | 2C (2G)    | LP, BP, HP, BS, AP |

|                  | 2 VDTAs    | CM (MISO)  | 0            | 2C (2G)    | LP, BP, HP, BS, AP |

| [36]             | 2 VDTAs    | CM (MISO)  | 2R (2G)      | 2C (2G)    | LP, BP, HP, BS, AP |

| [37]             | 2 MO-VDTAs | TAM (MISO) | 2 MOS-R (2G) | 2C (1F+1G) | LP, BP, HP, BR, AP |

| [38]             | 1 VDVTA    | VM (MISO)  | 1R (G)       | 2C (2F)    | LP, BP, HP, BR     |

| [24]             | 2 VDTAs    | VM (MISO)  | 0            | 2C (1F+1G) | LP, BP, HP, BR, AP |

| [39]             | 1 VDTA     | CM (MISO)  | 1R (G)       | 2C (2G)    | LP, BP, HP, BR, AP |

| [27]             | 1 VDTA     | VM (MISO)  | 1R (G)       | 2C (2F)    | LP, BP, HP, BS, AP |

| [40]             | 1 VDTA     | CM (MISO)  | 1R (G)       | 2C (2G)    | LP, BP, HP, BR, AP |

| MIMO Filters:    |            |            |              |            |                    |

| [11]             | 1 VDTA     | VM (MIMO)  | 0            | 2C (1F+1G) | LP, BP, HP         |

Table 1.2(a) (continued)

| Ref. | ABB       | ]          | Passive Elemen | nts         | FOF  | FOF                          | Input/Output    | Impedance |

|------|-----------|------------|----------------|-------------|------|------------------------------|-----------------|-----------|

| Kel. | No. Type  | R          | С              | FC          | Туре | Response(s)                  | mput/Output     |           |

| [87] | 1 Op-Amp  | 4R (3F+1G) | -              | 2FC (1F+1G) | SISO | Sallen-Key FLPF              | Voltage/Voltage | Low       |

|      | 1 Op-Amp  | 4R (2F+2G) | -              | 2FC (2F)    | SISO | Sallen-Key FHPF              | Voltage/Voltage | Low       |

|      | 1 Op-Amp  | 5R (3F+2G) | -              | 2FC (1F+1G) | SISO | Sallen-Key FBPF              | Voltage/Voltage | Low       |

|      | 3 Op-Amps | 6R (6F)    | -              | 2FC (2F)    | SIMO | FO-KHN<br>(FLPF, FBPF, FHPF) | Voltage/Voltage | Low       |

| [88] | 3 Op-Amps | 6R (6F)    | 1C (1F)        | 1FC (1F)    | SIMO | FO-TT (FLPF, FBPF)           | Voltage/Voltage | Low       |

| [89] | 3 Op-Amps | 6R (6F)    | -              | 2FC (2F)    | SIMO | FO-KHN<br>(FLPF, FBPF, FHPF) | Voltage/Voltage | Low       |

| [90] | 2 Op-Amps | 4R (2F+2G) | 2C (2F)        | 1FC (1F)    | SISO | FBPF                         | Voltage/Voltage | Low       |

|      | 4 Op-Amps | 7R (7F)    | 2C (2F)        | 1FC (1F)    | SISO | FBPF                         | Voltage/Voltage | Low       |

|      | 2 Op-Amps | 4R (3F+1G) | 2C (1F+1G)     | 1FC (1F)    | SISO | FBPF                         | Voltage/Voltage | Low       |

|      | 4 Op-Amps | 6R (6F)    | 2C (2F)        | 1FC (1F)    | SISO | FBPF                         | Voltage/Voltage | Low       |

|      | 2 CCIIs   | 4R (4F)    | 2C (2F)        | 1FC (1F)    | SISO | FBPF                         | Voltage/Voltage | Low       |

| [91] | 2 Op-Amps | 3R (2F+1G) | 1C (1F)        | 1FC (1F)    | SISO | FLPF, FHPF, FBPF             | Voltage/Voltage | Low       |

Table 1.2(b) Literature Summary for Fractional Order Filters.

| Ref. | ABB                         | Pa         | ssive Elem | ents        | FOF  | FOF                          | Input/Output    | Impedance |

|------|-----------------------------|------------|------------|-------------|------|------------------------------|-----------------|-----------|

| Kel. | No. Type                    | R          | C          | FC          | Туре | Response(s)                  | mput/Output     | Impedance |

| [92] | 3 Op-Amps                   | 6R (6F)    | -          | 2FC (2F)    | SIMO | FO-KHN                       | Voltage/Voltage | Low       |

| [93] | 5 CCII<br>(3CCII+ & 2CCII-) | 6R (3F+3G) | -          | 2FC (2G)    | SIMO | FO-KHN (FLPF)                | Voltage/Voltage | High      |

|      | 3 CCII+                     | 4R (4G)    | -          | 2FC (2G)    | SIMO | FO-TT (FLPF)                 | Voltage/Voltage | High      |

| [94] | 3 Op-Amps                   | 6R (6F)    | -          | 2FC (2F)    | SIMO | FO-KHN<br>(FLPF, FBPF, FHPF) | Voltage/Voltage | Low       |

|      | 1 Op-Amp                    | 4R (3F+1G) | -          | 2FC (1F+1G) | SISO | FO Sallen-Key                | Voltage/Voltage | Low       |

| [95] | 5 CCII<br>(3CCII+ & 2CCII-) | 7R (3F+4G) | -          | 2FC (2G)    | SIMO | FO-KHN<br>(FLPF, FBPF, FHPF) | Voltage/Voltage | High      |

| [96] | 2 Op-Amps                   | 4R (3F+1G) | 1C (1F)    | -           | SISO | FBPF                         | Voltage/Voltage | Low       |

|      | 2 Op-Amps                   | 3R (2F+1G) | 1C (1F)    | 1FC (1F)    | SISO | FBPF                         | Voltage/Voltage | Low       |

| [97] | 3 Op-Amps                   | 6R (6F)    | -          | 2FC (2F)    | SIMO | FO-KHN<br>(FLPF, FBPF, FHPF) | Voltage/Voltage | Low       |

|      | 1 Op-Amp                    | 4R (3F+1G) | -          | 2FC (1F+1G) | SISO | FO Sallen-Key                | Voltage/Voltage | Low       |

| [98] | 3 Op-Amps                   | 6R (6F)    | 1C (1F)    | 1FC (1F)    | SISO | FO-TT (FLPF)                 | Voltage/Voltage | Low       |

Table 1.2(b) (continued)

| Table 1.2(b) (continued) | <u>Table 1.2(b) (cc</u> | ntinued) |

|--------------------------|-------------------------|----------|

|--------------------------|-------------------------|----------|

| Ref.  | ABB                    | Pas         | ssive Eleme | nts            | FOF  | FOF                             | Input/Output    | Impedance |

|-------|------------------------|-------------|-------------|----------------|------|---------------------------------|-----------------|-----------|

| Kei.  | No. Type               | R           | С           | FC             | Туре | Response(s)                     | mput/Output     | Impedance |

| [99]  | 5 DDCC                 | 7R (7G)     | 3C (3G)     | -              | SISO | FLPF                            | Voltage/Voltage | High      |

| [100] | 2 Op-Amps              | 3R (2F+1G)  | 1C (1F)     | 1FC (1F)       | SISO | FBPF, FNF                       | Voltage/Voltage | Low       |

| [101] | 7 OTAs                 | -           | 2C (2G)     | -              | SISO | FLPF, FHPF, FAPF (α)            | Voltage/Voltage | High      |

|       | 11 OTAs                | -           | 4C (4G)     | -              | SISO | FLPF, FHPF, FBPF,<br>FBSF (α+β) | Voltage/Voltage | High      |

| [102] | 3 OTAs + 3 ACAs + 1 CF | -           | 3C (3G)     | -              | SISO | FLPF, FHPF $(1+\alpha)$         | Current/Current | High      |

| [103] | 3 OTAs                 | -           | -           | 2FC (2F)       | SIMO | FLPF, FBPF (0.5, 0.9)           | Current/Current | High      |

| [104] | 2 OTAs                 | -           | -           | 1FC (1F)       | SISO | FAPF                            | Voltage/Voltage | High      |

| [105] | 1 CDBA                 | 5R (4F+1G)  | -           | 5FC<br>(4F+1G) | MISO | FLPF, FHPF, FBPF                | Voltage/Voltage | Low       |

| [106] | 1 CCII+                | 1R (1G)     | -           | 1FC (1G)       | SISO | Current Integrator              | Current/Current | High      |

| [107] | 3 OTAs                 | -           | -           | 2FC* (2G)      | SIMO | FLPF, FBPF, FHPF                | Current/Current | High      |

| [41]  | 3 VDTAs                | 7R (3F+4G)  | 3C (3G)     | -              | SISO | FBPF (1+a)                      | Current/Current | High      |

|       | 4 VDTAs                | 11R (4F+7G) | 3C (3G)     | -              | SISO | FBRF $(1+\alpha)$               | Current/Current | High      |

| Table 1.2(b) (continued) |

|--------------------------|

|--------------------------|

| Ref.  | ABB      | Pas         | ssive Eleme | ents     | FOF  | FOF                                    | Input/Output    | Impedance |

|-------|----------|-------------|-------------|----------|------|----------------------------------------|-----------------|-----------|

| Ker.  | No. Type | R           | C           | FC       | Туре | Response(s)                            | input Output    | Impedance |

| [42]  | 3 VDTAs  | 7R (3F+4G)  | 3C (3G)     | -        | SISO | FLPF (1+a)                             | Current/Current | High      |

|       | 4 VDTAs  | 10R (3F+7G) | 3C (3G)     | -        | SISO | FHPF (1+α)                             | Current/Current | High      |

| [108] | 1 OTRA   | 4R (4F)     | -           | 4FC (4F) | SISO | FHPF ( $\alpha$ + $\beta$ + $\gamma$ ) | Voltage/Voltage | Low       |

It may be observed from Table 1.2(a) that

- limited SISO [14] and MIMO [11] type biquads are available

- Ref. [15-30] exhibit SIMO behaviour and MISO type biquads are presented in [18,24,27,31-40]

- structures of [16-18,20,21,24,27,28,30,32,35-37] are designed around large number of active blocks.

Further, inspection of Table 1.2(b) suggests that

- the FOF of [99,101,102,41,42] are designed using the FBD approach while FOEs are employed for obtaining desired functionality in [87-98,100,103-107,108]

- only FCs are employed in [88,90,91,96,100] whereas both capacitors and FCs are used in [87,94,96,97] to obtain desired FO responses

- all structures use large number of ABB except for [105,106,108] and large number of passive components except for [103,104,106,107]

- Ref. [87-101,104,105,108] provide voltage output and [102,103,106,107] are current output circuits

- voltage output is available at high impedance [93,95,99,101,104] thus require a buffer circuit for cascading.

### **1.2.3 Sinusoidal Oscillators**

Sinusoidal oscillators (SOs) are linear electric/electronic circuits and are widely used in various applications pertaining to telecommunications, control systems, signal processing and measurement systems. Based on the order, VDTA based sinusoidal oscillators may be broadly classified as second- and third- order sinusoidal oscillators (TOSOs).

A comparative study for various voltage differencing transconductance amplifier based oscillators [44-53] has been recorded in Table 1.3 for ready reference.

| Ref. | ABB             | Passiv | e Elements | Output Type | Order  |

|------|-----------------|--------|------------|-------------|--------|

|      | No. Type        | R      | С          |             |        |

| [44] | 1 VDTA          | 1 (G)  | 2 (G)      | Voltage     | Second |

| [45] | 2 VDTAs         | 0      | 2 (G)      | Current     | Second |

| [46] | 1 DDCC + 1 VDTA | 1 (G)  | 3 (G)      | Current     | Third  |

| [47] | 2 VDTAs         | 0      | 2 (G)      | Voltage     | Second |

|      | 2 VDTAs         | 0      | 2 (G)      | Current     | Second |

| [48] | 2 VDTAs         | 0      | 3 (G)      | Current     | Third  |

| [49] | 2 VDTAs         | 0      | 3 (G)      | Voltage     | Third  |

|      | 2 VDTAs         | 0      | 3 (G)      | Current     | Third  |

| [50] | 2 VDTAs         | 1 (G)  | 2 (G)      | Voltage     | Second |

| [51] | 1 VDTA          | 0      | 2 (G)      | Voltage     | Second |

|      | 1 VDTA          | 0      | 2 (G)      | Current     | Second |

| [52] | 1 VDTA          | 2 (G)  | 2 (G)      | Voltage     | Second |

| [53] | 1 VDTA          | 1 (G)  | 2 (G)      | Current     | Second |

Table 1.3 Literature Summary for VDTA based Sinusoidal Oscillators.

Based on the inferences made from Table 1.3, it can be drawn that:

- there is lean presence of TOSOs [46,48,49]

- explored TOSOs are designed around two active blocks; either combination of blocks [46] or both VDTAs [48,49]

- the TOSO proposition makes use of single VDTA only

- the proposed structure employs canonical number of grounded capacitors.

#### **1.2.4 VDTA Implementations**

It is well known that, transconductance amplifier (TA) with high transconductance gain ' $g_m$ ' is essential for designing high performance analog circuits. Most traditionally the  $g_m$  can be enhanced by increasing the bias current of the TA stage. However, increased bias current essentially leads to large power dissipation leading to a trade-off between the transconductance gain and the power dissipation. Extensive review suggests that all available CMOS based VDTA implementations [11,15,18,27,110-112] increase the bias current for enhancing the  $g_m$  of the TA stages. Thus, it may be summarized that the available VDTA structures do not provide characteristics like low power and high transconductance gain simultaneously. A comparative study of various performance parameters of all available CMOS based VDTA implementations [11,15,18,27,110-112] is given in Table 1.4.

| Ref.  | Technology<br>(µm) | Power<br>Supply<br>(V) | No. of<br>Current Sources<br>(Value)    | Input Voltage<br>Range<br>(mV) | Transconductance<br>(µS) | BW<br>(MHz) | Power<br>Consumption |

|-------|--------------------|------------------------|-----------------------------------------|--------------------------------|--------------------------|-------------|----------------------|

| [11]  | 0.18               | ± 0.9                  | 4<br>(150 μA)                           | ± 300                          | 636                      | NA*         | NA                   |

| [15]  | 0.35               | ± 2                    | 2<br>(40 µA)                            | NA*                            | 381                      | NA*         | 1 mW                 |

| [18]  | 0.18               | ± 1.5                  | 4<br>(40 μA)                            | NA*                            | 150                      | NA*         | NA                   |

| [110] | 0.045              | ± 1                    | _                                       | NA*                            | NA*                      | NA*         | 0.184 mW             |

| [27]  | 0.18               | ± 0.7                  | 4<br>(10 μA)                            | -80 to 80                      | 415                      | 225         | 145 µW               |

| [111] | 0.18               | ± 1.8                  | NA*<br>(Voltage sources<br>for biasing) | NA*                            | NA*                      | NA          | NA*                  |

| [112] | 0.25               | ± 2                    | 8<br>(70 μA)                            | ± 125                          | 1300                     | 145         | NA*                  |

Table 1.4 Literature Summary for VDTA CMOS Implementations.

## **1.3 Research Gaps**

Comprehensive literature review suggests that designing and development of FO circuits and systems is still in nascent stage. For designing fractional order circuits FOEs are essential elements. No significant work has been reported in fractional order inductance emulation using VDTA though, other ABBs based designs have been explored. Further, only two topologies are available which can emulate both negative and positive fractional order inductance. Additionally, no structure is existing which provides both integer and fractional order behaviour using a single structure.

Survey on VDTA based integer order filter suggested that only a single structure providing multimode biquad responses is existing. Further, exploring the domain of fractional order filters, it is clearly observed that limited literature is available on VDTA based FOFs. Only three structures are reported [41-43] which make use of large number of active blocks and are the structures are making use of resistive components.

Yet, another research gap that is observed is the lean presence of VDTA based third order sinusoidal oscillators in literature. It is further explored that existing structures are designed around two active blocks. Additionally, only single configuration is reported which provides voltage output.

Exploring further, it is observed that several CMOS VDTA implementations are available in literature; however, scope is always there to enhance its performance parameters namely linearity, transconductance gain, bandwidth etc.

## **1.4 Research Objectives**

Based on the literature survey and research gaps following objectives were formulated:

- 1) To develop VDTA based generic impedance emulation topology to provide both positive and negative fractional and integer order behaviour.

- 2) To develop VDTA based integer and fractional order filter topologies.

- 3) To develop higher order signal generation applications.

- 4) To design a new VDTA structures with improved performance.

## 1.5 Organization of the Thesis

The primary objective of this research is on VDTA based conventional integer order and state of the art fractional order circuits for analog signal processing (ASP) and signal generation. The organization of the research work carried out is presented in a chapter-wise format and is as follows:

## Chapter 1

This chapter briefs about the background and motivation behind the work carried out in the thesis. Literature review and summary of available analog circuits and/or their fractional order counterparts is put up followed by locating the research gaps to formulating the objectives for the work. The layout of the thesis is described shortly.

#### Chapter 2

This chapter presents a brief description of fractional order element implementation using Carlson and continued fraction expansion approximations. It also includes characterization of active block used i.e., Voltage Differencing Transconductance Amplifier to develop different analog circuits in the thesis.

## Chapter 3

This chapter presents generic impedance emulator with lesser component count which can be configured as (i) integer order positive inductance emulator (ii) integer order negative inductance emulator (iii) fractional order positive inductance emulator and (iv) fractional order negative inductance emulator. Functional validation of the proposition is carried out through simulations as well as experimentally. Further, the applicability of the proposed structure is justified through two application examples namely parasitic fractional order inductance cancellation and fractional order high pass filter.

## Chapter 4

This chapter presents an classical analog filter and two  $\alpha$ -order voltage mode fractional order filters based on VDTA. Moving on to the fractional order counterparts, first FOF represents voltage mode multiple input single output universal configuration and is based on Carlson approximation. Whereas, second FOF topology presents voltage mode single input single output structure.

## Chapter 5

This chapter is devoted to signal generating circuits [i.e. sinusoidal oscillators (particularly, third order SOs)]. A generic TOSO is proposed first followed by two configurations extracted from it by suitably selecting the impedances connected.

## Chapter 6

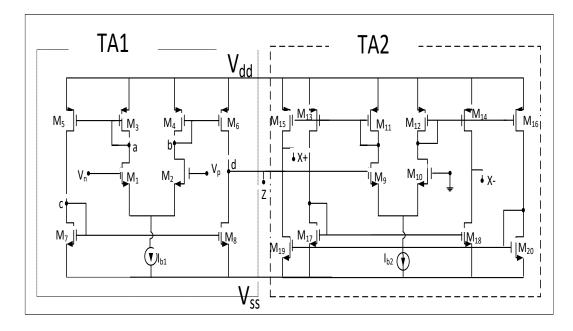

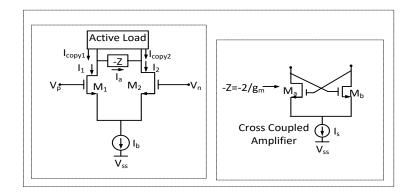

Two transconductance boosted VDTA structures are presented in this chapter. General schemes of the two propositions are discussed, firstly, followed by their CMOS implementations.

## Chapter 7

Based on the roadmap outlined above, the work is concluded in **Chapter 7** with a thought on the prospective future scope.

# CHAPTER – 2 PRELIMINARIES

## **2.1 Introduction**

Researchers are continuously striving to explore different analog building blocks with attributes like higher bandwidth, higher slew rate, lower power consumption and better linearity. This has led to paradigm shift from voltage mode to current mode signal processing. Hence, numerous current mode active blocks as given in [3] has evolved and references cited therein. The voltage differencing transconductance amplifier (VDTA) is one among those and its CMOS implementation was first proposed by Yesil et al. [11]. Since then, various research efforts are made to propose CMOS implementations [11,15,18,27,110-112] of VDTA with enhanced performance. The VDTA is a voltage input current output ABB having two transconductance gain stages which helps in realization of resistor-less compact CMOS applications. Additionally, the transconductances of VDTA can be tuned through bias current which facilitates electronic tunability of the system parameters. It is well known that, transconductance amplifier (TA) with high transconductance gain 'g<sub>m</sub>' is essential for designing high performance analog circuits. Thus, VDTA is a preferred choice for designing on-chip high frequency applications. This has led to realization of various signal processing [12-43] and generation [44-53] applications using VDTA.

The FOE is a fundamental component for designing the fractional order circuits. It is observed from literature that though the efforts are being directed towards physical realization of FC yet these are still in very primitive stage [57-59] and the reported off the shelf FCs are bulky and non-reconfigurable to be used in circuits. On the other hand, various rational approximations [60-68] such as Carlson approximation [60,62,64], Oustaloup recursive approximation [61,62,64], continued fraction expansion (CFE) [62], Matsuda approximation [62,64], Chareff method [62], Modified approximation [63], Halley approximation [65,67], El-Khazali approximation [66] and Laguerre approximation [68] are available to emulate the behaviour of FOE.

This thesis presents realization of integer and fractional order signal processing and generating circuits using VDTA, therefore in this Chapter preliminaries of VDTA and fractional order elements has been presented.

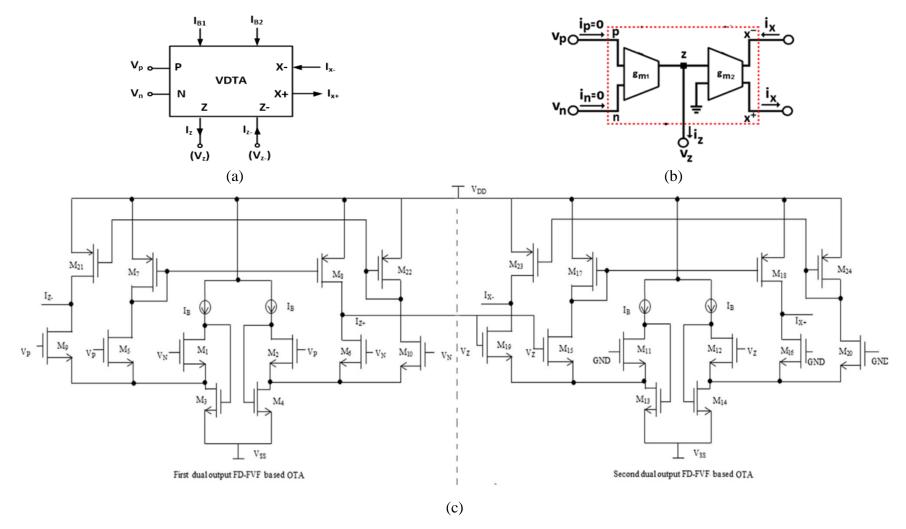

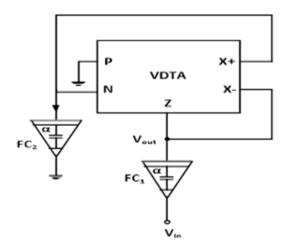

## 2.2 The VDTA

The VDTA can be modelled as a differential voltage driven current output ABB with two transconductance (TC) gain stages where ' $g_{mF}$ ' and ' $g_{mS}$ ' represent the transconductance gains of the first and second stages, respectively. The port relations of VDTA are expressed using matrix Eqn. (2.1); that is, two high impedance voltage input terminals 'p' and 'n' and three high impedance current output terminals 'z', 'x+' and 'x-'. The circuit symbol and equivalent model of the VDTA [3] are shown in Fig. 2.1 (a) and (b) respectively.

$$\begin{bmatrix} I_{z} \\ I_{z-} \\ I_{x+} \\ I_{x-} \end{bmatrix} = \begin{bmatrix} g_{mF} & -g_{mF} & 0 & 0 \\ -g_{mS} & g_{mS} & 0 & 0 \\ 0 & 0 & g_{mS} & 0 \\ 0 & 0 & -g_{mS} & 0 \end{bmatrix} \begin{bmatrix} V_{p} \\ V_{n} \\ V_{z} \\ V_{z-} \end{bmatrix}$$

(2.1)

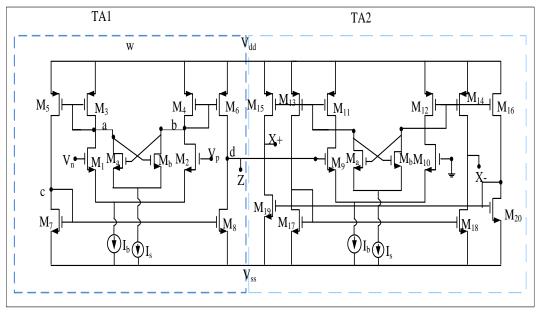

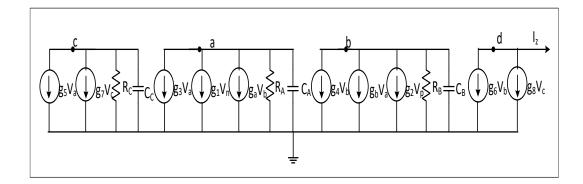

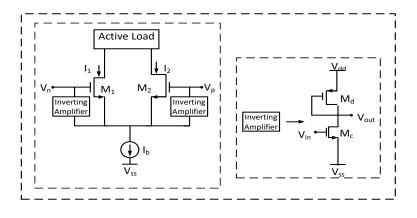

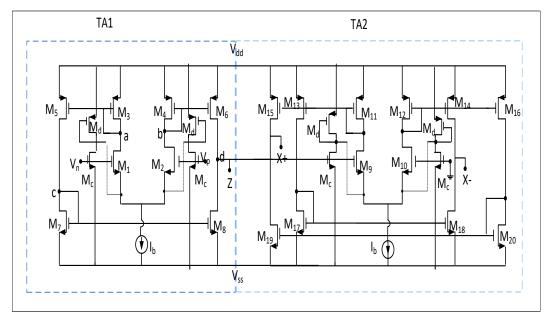

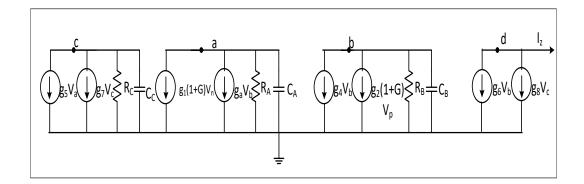

The fully differential - flipped voltage follower (FD-FVF) based CMOS structure of VDTA which is used in this work for verification of all propositions, is shown in Fig. 2.1(c). Two dual output OTAs (DO-OTAs) have been used to realize this structure wherein MOSFETs  $M_1$ - $M_{10}$ ,  $M_{21}$  and  $M_{22}$  constitute first dual output OTA and  $M_{11}$ - $M_{20}$ ,  $M_{23}$  and  $M_{24}$  constitute second dual output OTA.

The transconductance gain of each stage  $(g_{mF}, g_{mS})$  is given by

$$g_{mF,mS} = \sqrt{2\mu_n C_{ox} \frac{W}{L} I_{B_{F,S}}}$$

(2.2)

where  $\mu_n$ ,  $C_{ox}$ , W and L denote the carrier mobility (effective), gate-oxide capacitance (per unit area), effective channel width and length of MOS transistor of differential pair respectively and  $I_{BF,BS}$  represent the bias current of the respective transconductance stages.

Fig. 2.1 VDTA (a) Symbol (b) Equivalent Model (c) CMOS Implementation [27].

### 2.2.1 Simulation Results

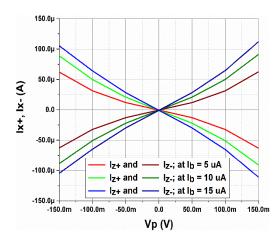

The functionality of the reproduced CMOS VDTA [27] shown in Fig. 2.1(c), which is used in this work for all proposed realizations, is validated through simulations. Simulations are carried out using Virtuoso from Cadence tool suite using 180 nm generic process design kit (gpdk) CMOS technology parameters. Device dimensions (W/L) are taken as 7.2 $\mu$ m/0.36 $\mu$ m for NMOS, 14.4 $\mu$ m/0.36 $\mu$ m for PMOS transistors and supply voltage of ±0.7 V is used for simulations. The DC characteristics of the VDTA for different values of biasing currents are depicted in Fig. 2.2. Dependence of the transconductance on the biasing current and the supply voltage is illustrated in Fig. 2.3 (a) and (b) respectively. The value of transconductance (g<sub>mF</sub> = g<sub>mS</sub>) is found to be 400 uA/V for the biasing current and supply voltage of 10  $\mu$ A and ±0.7 V. Further, from the Fig. 2.2, the linear range is measured to be -150 mV to 150 mV.

Fig. 2.2 DC Transfer Characteristics of VDTA.

Fig. 2.3 Transconductance Variation with (a) Bias Current (b) Supply Voltage.

## 2.3 FC Realization

Comprehensive literature review suggests that various research efforts have been made to perceive a fractional order capacitor. As of now, there are two design techniques to implement:

- Fabrication (i.e. single-component realization) [57-59]

- Emulation (i.e. multi-component realization) [60-68]

The FCs are not commercially available and their physical realization is still in primitive phase [57-59]. However, a number of rational approximations; namely, Carlson approximation [60,62,64], Oustaloup recursive approximation [61,62,64], continued fraction expansion (CFE) [62], Matsuda approximation [62,64], Chareff method [62], Modified approximation [63], Halley approximation [65,67], El-Khazali approximation [66] and Laguerre approximation [68] are available in literature for FOE behaviour emulation.

In this work, Carlson and CFE approximations are used, therefore both these methods have been presented in following subsections.

## 2.3.1 FC Realization using Carlson Method

Based on the Carlson method, rational integer order approximation function obtained after first iteration for  $\alpha = 0.5$  is

$$C^{\alpha}_{1/2\_1st} = \frac{s+3}{3s+1}$$

(2.3)

Similarly, post second iteration rational approximation obtained is

$$C_{1/2_{-2}nd}^{\alpha} = \frac{s^4 + 36s^3 + 126s^2 + 84s + 9}{9s^4 + 84s^3 + 126s^2 + 36s + 1}$$

(2.4)

Likewise, rational approximation obtained after third iteration is

$$s^{13} + 351s^{12} + 17550s^{11} + 296010s^{10} + 2220075s^{9} + 8436285s^{8} + 17383860s^{7} + 20058300s^{6} + 13037895s^{5} + 4686825s^{4} + 888030s^{3} + 80730s^{2} + 2925s + 27 - 27s^{13} + 2925s^{12} + 80730s^{11} + 888030s^{10} + 4686825s^{9} + 13037895s^{8} + 20058300s^{7} + 17383860s^{6} + 8436285s^{5} + 2220075s^{4} + 296010s^{3} + 17550s^{2} + 351s + 1$$

$$(2.5)$$

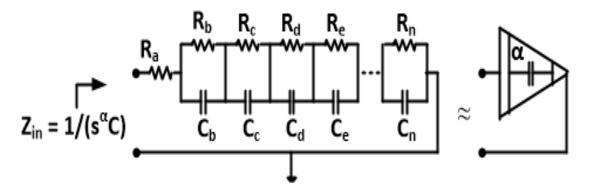

It may be observed from Eqn. (2.3) through Eqn. (2.5) that the Carlson based first, second and third iterations result in first, fourth and thirteenth order rational approximation functions respectively. These integer order approximation functions may be used to implement the FC as the impedance of FC is expressed as  $Z(s) = 1/Ks^{\alpha}$ . The impedance function can be implemented using RC ladder network of Fig. 2.4 thereby emulating the FC. The component values for ladder networks for three iterations are listed in Table 2.1.

Fig. 2.4 Truncated n<sup>th</sup> order RC Ladder Circuit.

|           | р     | R <sub>b</sub>      | R <sub>c</sub> | R <sub>d</sub>      | R <sub>e</sub>      | $R_{\mathrm{f}}$ | R <sub>g</sub>      | $R_h$                  | $R_i$                   | $R_j$                   | R <sub>k</sub> | $R_1$       | R <sub>m</sub>      | R <sub>n</sub>         |

|-----------|-------|---------------------|----------------|---------------------|---------------------|------------------|---------------------|------------------------|-------------------------|-------------------------|----------------|-------------|---------------------|------------------------|

|           | $R_a$ | (kΩ),               | (kΩ),          | (kΩ),               | (kΩ),               | (kΩ),            | (kΩ),               | (kΩ),                  | (kΩ),                   | (kΩ),                   | (kΩ),          | (kΩ),       | (kΩ),               | (kΩ),                  |

|           | (kΩ)  | C <sub>b</sub> (nF) | $C_{c}(nF)$    | C <sub>d</sub> (nF) | C <sub>e</sub> (nF) | $C_{f}(nF)$      | C <sub>g</sub> (nF) | $C_{h}\left( nF ight)$ | $C_{i}\left( nF\right)$ | $C_{j}\left( nF\right)$ | $C_{k}(nF)$    | $C_{l}(nF)$ | C <sub>m</sub> (nF) | $C_{n}\left( nF ight)$ |

| First     | 4.21  | 33.64               |                |                     |                     |                  |                     |                        |                         |                         |                |             |                     |                        |

| Iteration | 4.21  | 14.19               | -              | -                   | -                   | -                | -                   | -                      | -                       | -                       | -              | -           | -                   | -                      |

| Second    | 1.40  | 3.17                | 4.78           | 11.21               | 92.97               |                  |                     |                        |                         |                         |                |             |                     |                        |

| Iteration | 1.40  | 6.64                | 23.46          | 42.58               | 55.06               | -                | -                   | -                      | -                       | -                       | -              | -           | -                   | -                      |

| Third     | 0.47  | 0.95                | 0.99           | 1.06                | 1.17                | 1.34             | 1.59                | 1.98                   | 2.62                    | 3.74                    | 5.96           | 11.36       | 30.99               | 276.41                 |

| Iteration | 0.47  | 2.30                | 9.06           | 19.92               | 34.30               | 51.43            | 70.37               | 90.11                  | 109.58                  | 127.73                  | 143.59         | 156.30      | 165.18              | 169.74                 |

Table 2.1 Component Values for Carlson based RC Ladder Network with Centre Frequency 1 kHz for FC = 1  $\mu O/s^{\alpha}$ .

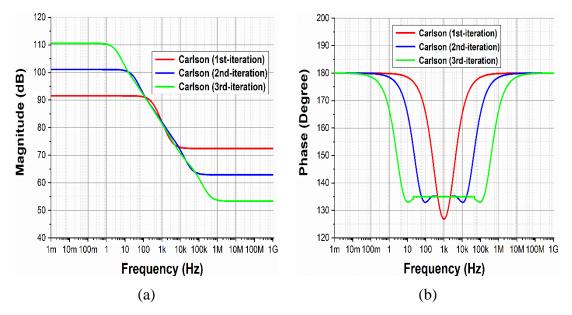

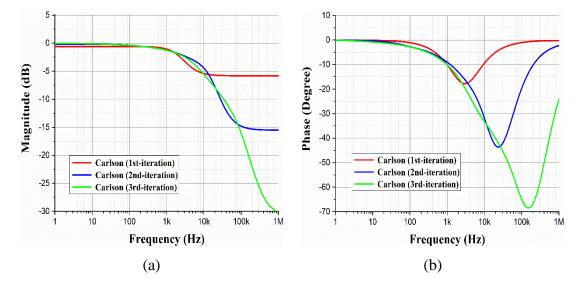

## 2.3.1.1 Simulation Results

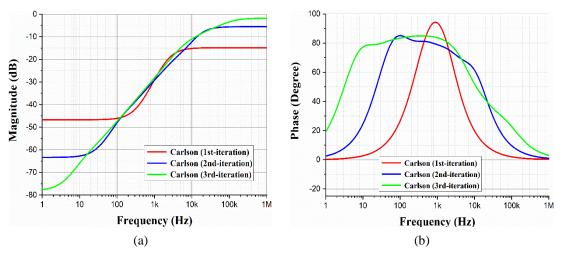

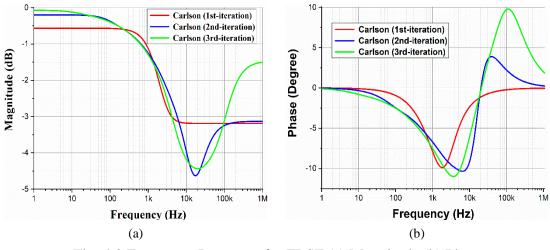

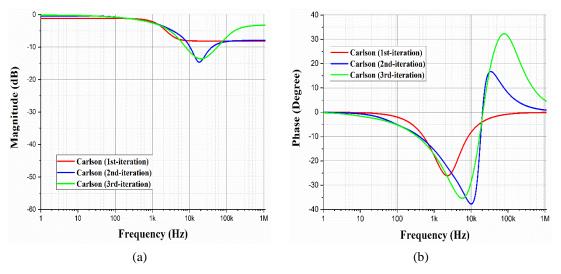

It may be observed from Fig. 2.5 that the simulated magnitude and phase values match with ideal values over a larger frequency range as the order of the approximation function is increased. Hence, it can be concluded that, larger the number of iterations, higher is the order of the approximation function and hence better is the performance of the FC.

Fig. 2.5 Frequency Response for FC of 1  $\mu O/s^{\alpha}$  (a) Magnitude (b) Phase.

## 2.3.2 The Continued Fraction Expansion Method

The Continued fraction expansion [62] of  $(1+x)^{\alpha}$  is given by

$$(1+x)^{\alpha} = \frac{1}{1-\frac{\alpha x}{1+\frac{\alpha x}{2+\frac{\alpha x}{2+$$

which has infinite terms. Substituting x=s-1 and retaining only 'n' finite terms the generalized rational approximation for s<sup> $\alpha$ </sup> can be obtained as

$$s^{\alpha} \cong \frac{a_{n}s^{n} + a_{n-1}s^{n-1} + \dots + a_{1}s + a_{0}}{a_{0}s^{n} + a_{1}s^{n-1} + \dots + a_{n-1}s + a_{n}}$$

(2.7)

where, n is the order of the approximation.

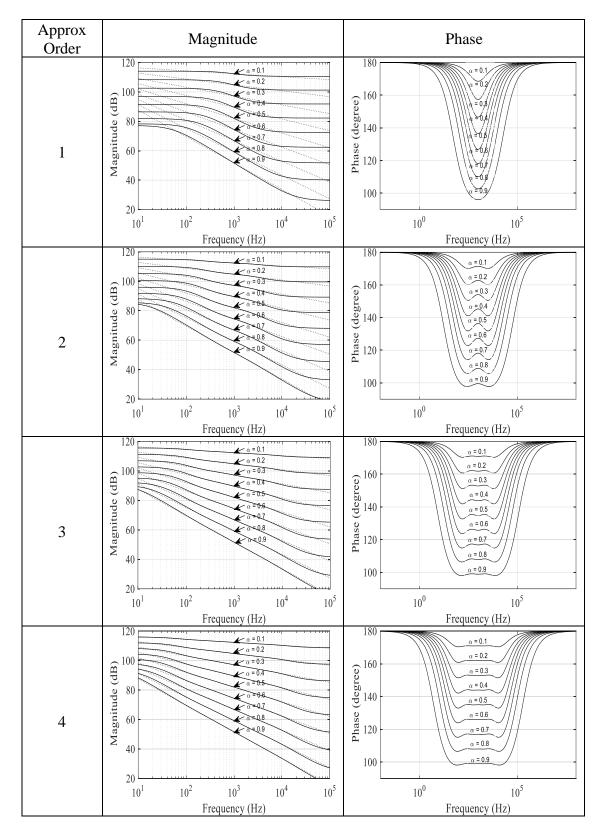

Considering finite number of terms in Eqn. (2.7), the rational approximations of different orders may be obtained for  $s^{\alpha}$ . In this work, different orders for  $s^{\alpha}$  ( $\alpha$  ranging from 0.1 to 0.9 in steps of 0.1) are listed in Table 2.2. It is evident from the Table 2.2 that the order of the approximated transfer function obtained is dependent on the order of the approximation, that is, CFE based n<sup>th</sup>-order approximation leads to an n<sup>th</sup>-order transfer function.

|         | 1 <sup>st</sup> -order | 2 <sup>nd</sup> -order                            | 3 <sup>rd</sup> -order                                                          | 4 <sup>th</sup> -order                                                                                                |

|---------|------------------------|---------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

|         | Approximation          | Approximation                                     | Approximation                                                                   | Approximation                                                                                                         |

| α = 0.1 | $\frac{9s+11}{11s+9}$  | $\frac{57s^2 + 266s + 77}{77s^2 + 266s + 57}$     | $\frac{1653s^3 + 17081s^2 + 18879s + 2387}{2387s^3 + 18879s^2 + 17081s + 1653}$ | $\frac{64467s^4 + 1174732s^3 + 2875002s^2 + 1387932s + 97867}{97867s^4 + 1387932s^3 + 2875002s^2 + 1174732s + 64467}$ |