## Analysis and Design of CMOS Multistage Amplifiers

A Thesis Submitted

In Partial Fulfilment of the Requirements

For the Degree of

## **DOCTOR OF PHILOSOPHY**

in

### **Department of Electronics & Communication Engineering**

by

**Om Krishna Gupta** 2K18/PhD/EC/513

Under the Supervision of

**Prof. Neeta Pandey** Dept. of ECE Delhi Technological University, Delhi –110042

**Prof. Maneesha Gupta** Dept. of ECE

Netaji Subhas University of Technology, Delhi –110078

Department of Electronics & Communication Engineering, Delhi Technological University, Shahbad Daulatpur, Main Bawana Road Delhi-110042 December 2024

## CERTIFICATE

This is to certify that the thesis entitled "Analysis and Design of CMOS Multistage Amplifiers" submitted by Om Krishna Gupta (2K18/PhD/EC/513) to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi, for the award of the degree of Doctor of Philosophy is based on the original research work carried out by him under our guidance and supervision. In our opinion, the thesis has reached the standards fulfilling the requirement of the regulations relating to the degree. It is further certified that the work presented in this thesis is not submitted to any other university or institution for the award of any other degree or diploma.

20/11/2024

**Prof. Neeta Pandey** Supervisor Department of Electronics & Communication Engineering, Delhi Technological University, Delhi –110042 Prof. Maneesha Gupta Co-Supervisor Department of Electronics & Communication Engineering, Netaji Subhas University of Technology, Delhi –110078

## **DECLARATION**

I hereby declare that the work presented in this thesis entitled "ANALYSIS AND DESIGN OF CMOS MULTISTAGE AMPLIFIERS" has been carried out by me under the supervision of Prof. Neeta Pandey, Department of Electronics & Communication Engineering, Delhi Technological University, Delhi and Prof. Maneesha Gupta, Department of Electronics & Communication Engineering, Netaji Subhas University of Technology, Delhi and is hereby submitted for the award of the degree of Doctor of Philosophy in Department of Electronics & Communication, Delhi Technological University, Delhi.

I further undertake that the work embodied in this thesis has not been submitted for the award of any other degree or diploma elsewhere.

## **Om Krishna Gupta**

2K18/PhD/EC/513

## ACKNOWLEDGMENT

It is indeed a great pleasure to thank all those who guided, supported and helped me in completing this research work. The grace of almighty God, blessings of my teachers and elders, strengthen my courage in the course of my research.

First and foremost, I express my deepest gratitude to my supervisors Prof. Neeta Pandey, Professor, Electronics and Communication Engineering Department, Delhi Technological University, New Delhi and Prof. Maneesha Gupta, Professor, Electronics and Communication Engineering Department, Netaji Subhas University of Technology, New Delhi for their valuable suggestions, guidance and encouragement during the research work.

I would like to acknowledge the reviewers of the research publications and conferences for their valuable suggestions.

Finally, I would like to express my sincere appreciation to all my family members and friends who helped me directly or indirectly for the successful completion of this research work.

**Om Krishna Gupta**

## ABSTRACT

A multistage amplifier is an essential component of analog signal processing. Although it provides high gain but the complexity of the amplifier increases with the number of stages. Moreover, a multistage amplifier produces a large number of comparable poles and zeros, which causes the phase margin to deteriorate. As a result, the stability of the amplifier is reduced. Consequently, the frequency compensation techniques become crucial when designing multistage amplifiers in order to improve the stability of the amplifier. However, in addition to addressing the amplifier's stability, the frequency compensation technique should enhance the gain bandwidth product (GBW), phase margin, and slew rate of the amplifier. The key objective of this thesis is to propose improved three stage amplifiers using different frequency compensation techniques.

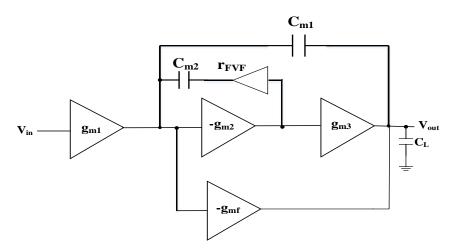

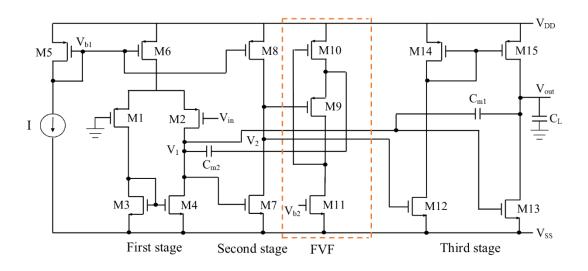

One of the conventional frequency compensation techniques called Reversed Nested Miller Compensation (RNMC) is widely used in three stage amplifiers. However, RNMC suffers with the problem of Right Half Plane (RHP) zero, which reduces the phase margin of the amplifier. In order to address the RHP zero problem of RNMC, the proposed amplifier 1 utilizes Flipped Voltage Follower (FVF) in the inner compensation loop of RNMC. Moreover, it improves the frequency response of the amplifier. Further, a feed forward path is employed to enhance the transient response of the amplifier.

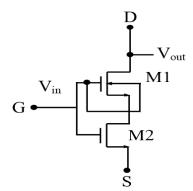

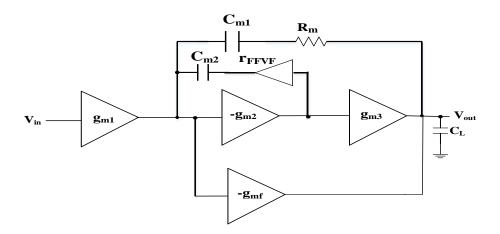

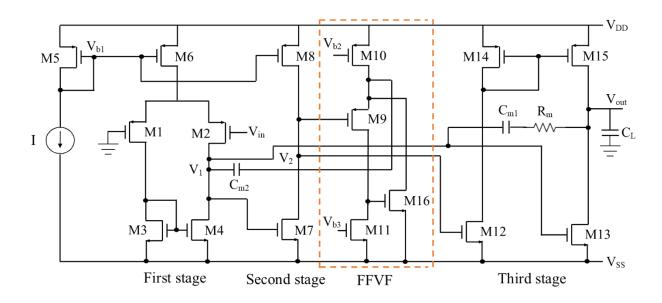

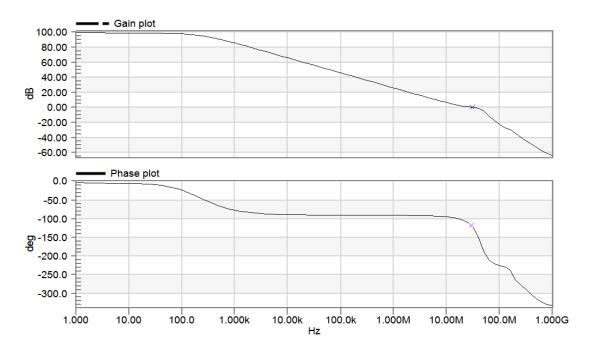

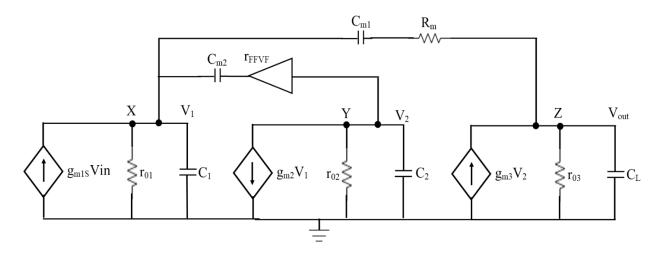

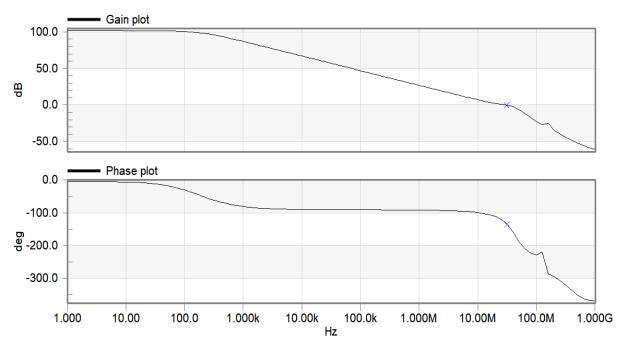

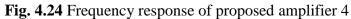

Another variant of voltage follower called Folded Flipped Voltage Follower (FFVF) is exploited in the inner compensation loop of RNMC in the proposed amplifiers 2-5. It resolves the RHP zero issue and improves the Gain Bandwidth Product (GBW) of the amplifiers. Moreover, the proposed amplifiers 3-5 also make use of a resistor in the outer compensation loop. It results in double pole-zero cancellation, which enhances the phase margin. Additionally, the proposed amplifiers 4 and 5 employ the self cascode structure and DTMOS transistors in the input stage, respectively. This results in better GBW of the amplifiers. The proposed amplifiers 2-5 also take advantage of the feed forward path to improve the transient response.

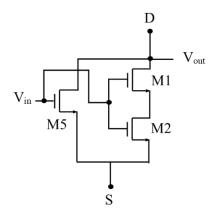

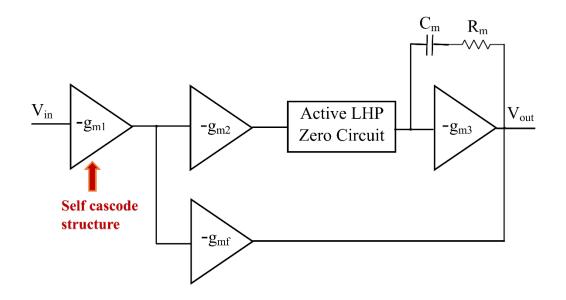

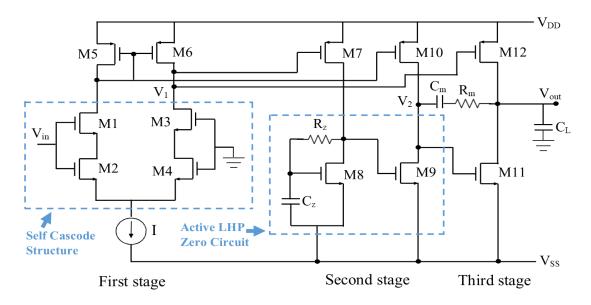

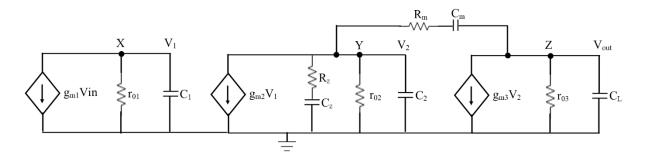

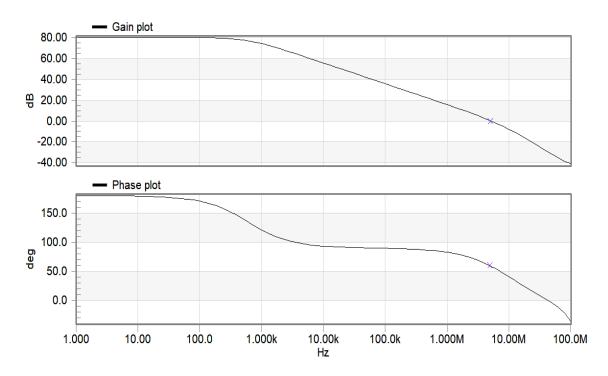

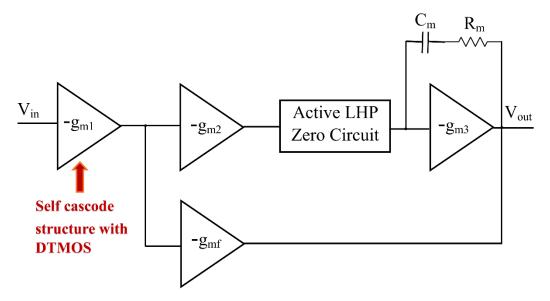

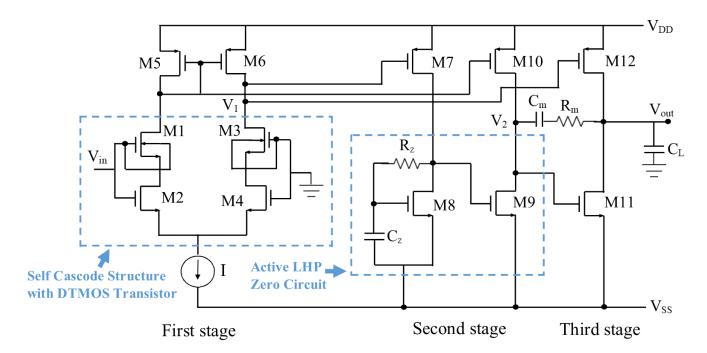

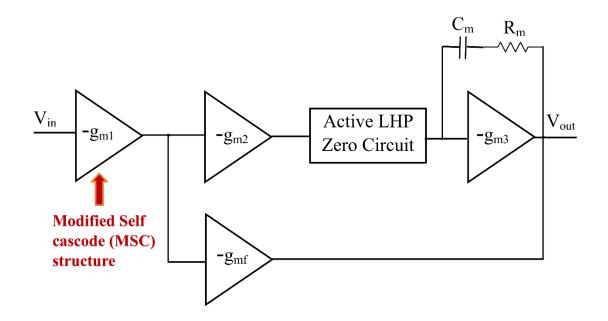

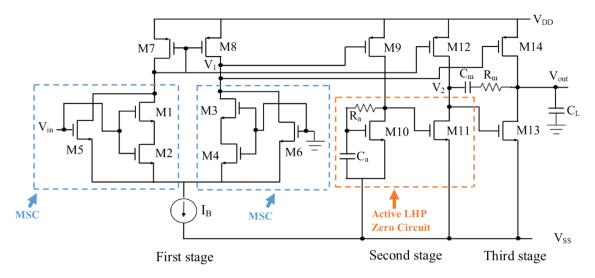

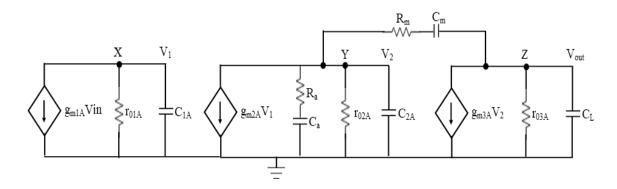

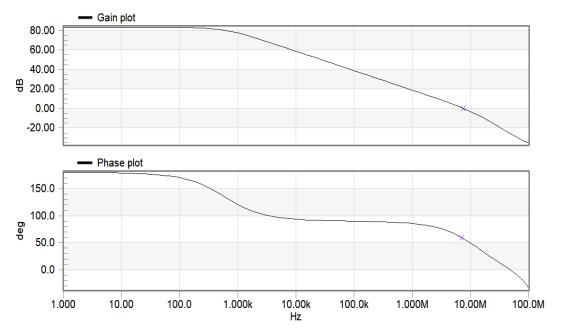

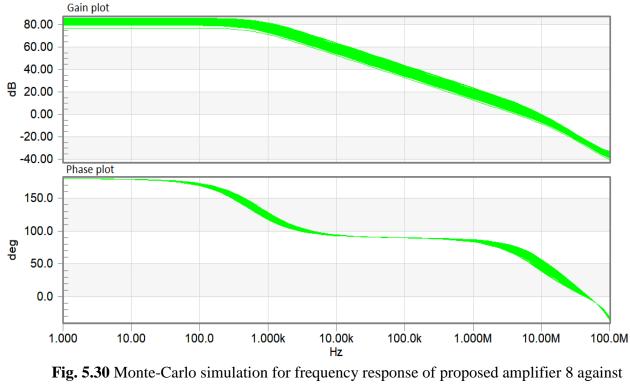

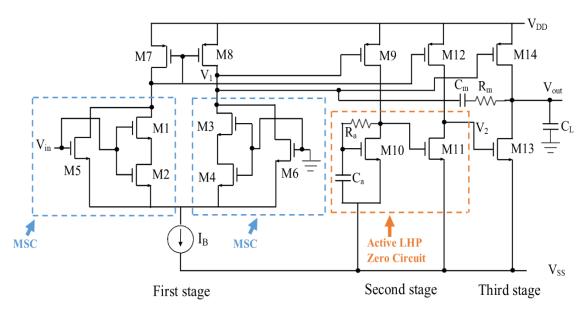

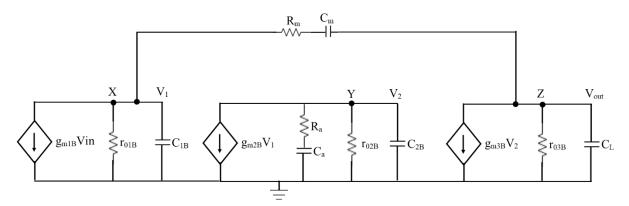

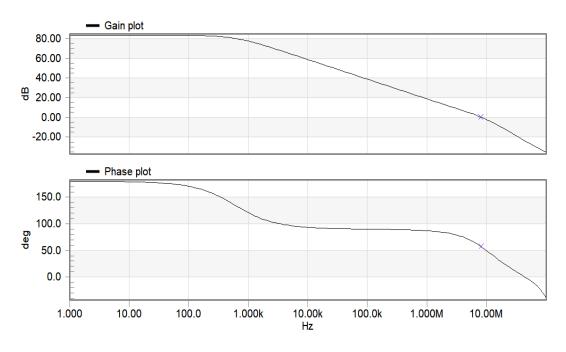

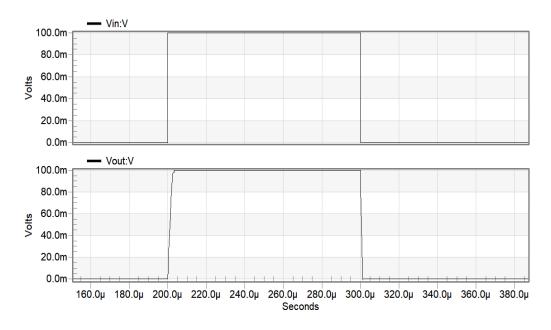

Further, an active LHP zero circuit is employed in the proposed amplifiers 6-9 to cancel the parasitic pole of the second stage. It enhances the GBW of the amplifiers. Additionally, a Miller capacitor with resistor ensures the stability of the amplifiers. Moreover, a self cascode structure and self cascode with DTMOS are used in the input stage of the proposed amplifiers 6 and 7, respectively. It results in better GBW of the amplifiers. The GBW is further enhanced by employing a modified self cascode structure in the first stage of the proposed amplifiers 8 and 9. Moreover, a feed forward path is exploited to improve the transient response of the proposed amplifiers 6-9.

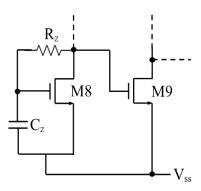

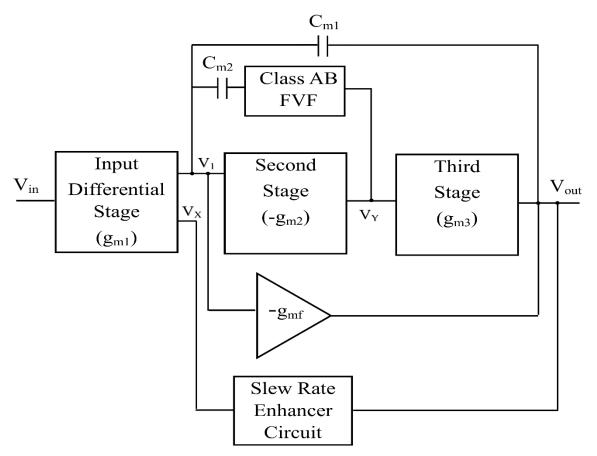

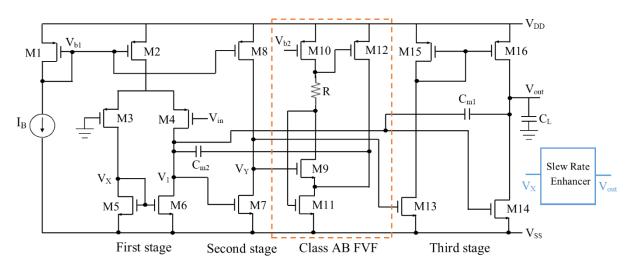

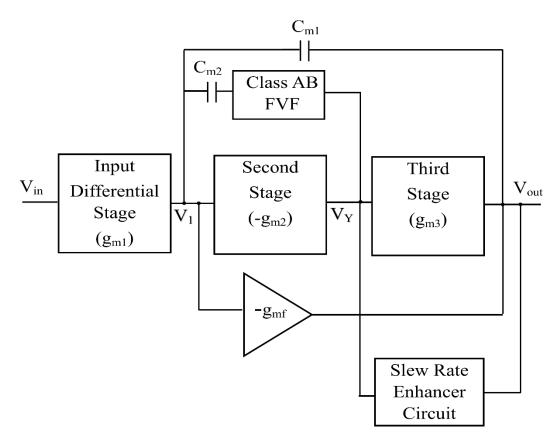

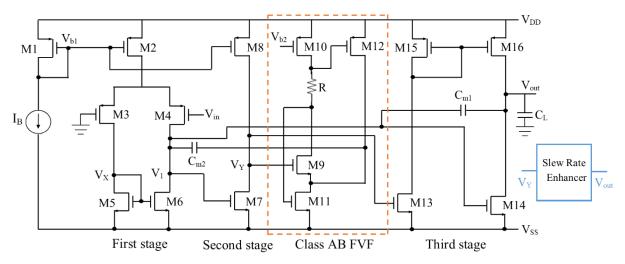

To further enhance the frequency response of three stage amplifiers, a class AB FVF is utilized in the inner compensation loop of RNMC in the proposed amplifiers 10 and 11. Additionally, a slew rate enhancer circuit and a feed forward path are exploited to improve the transient response.

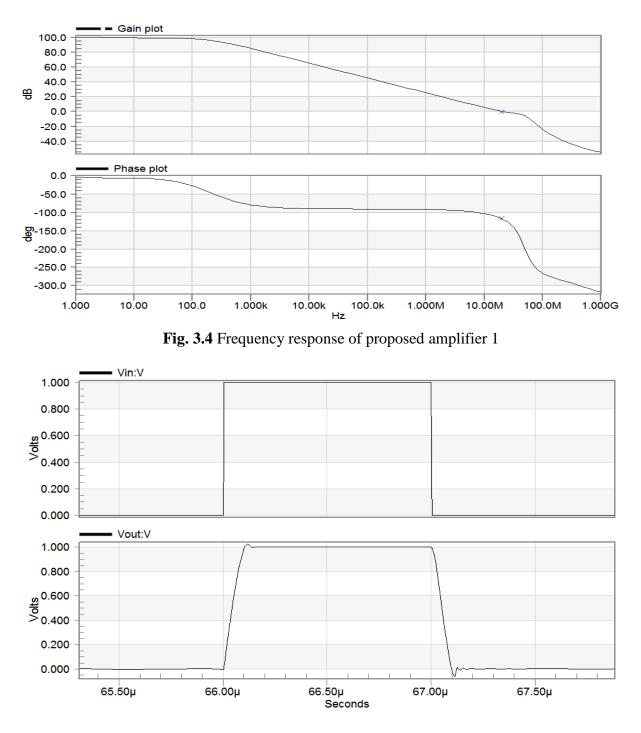

In this thesis, the small signal analysis is performed for all proposed amplifiers to find out the transfer function, which helps in evaluating the GBW and the stability of the amplifiers. Further, the performance of all proposed amplifiers is compared with their counterparts. The functionality of the proposed amplifiers is verified using TSMC 0.18 µm CMOS technology parameters in Tanner tool. Corner analysis, supply voltage variation, and Monte Carlo analysis are carried out to confirm the robustness of the proposed amplifiers.

# TABLE OF CONTENTS

| CERTIFICATE                                                                     | i     |

|---------------------------------------------------------------------------------|-------|

| DECLARATION                                                                     | ii    |

| ACKNOWLEDGMENT                                                                  | iii   |

| ABSTRACT                                                                        | iv    |

| TABLE OF CONTENTS                                                               | vi    |

| LIST OF FIGURES                                                                 | xi    |

| LIST OF TABLES                                                                  | xviii |

| Chapter 1 Introduction                                                          | 1     |

| 1.1 Motivation                                                                  | 2     |

| 1.2 Multistage Amplifiers                                                       | 2     |

| 1.3 Frequency Compensation Technique                                            | 3     |

| 1.4 Literature review of frequency compensation techniques                      | 4     |

| 1.5 Research gaps                                                               | 16    |

| 1.6 Research objectives                                                         | 16    |

| 1.7 Key contributions                                                           | 17    |

| 1.8 Organization of the thesis                                                  | 18    |

| Chapter 2 Various frequency compensation techniques used in proposed amplifiers | 20    |

| 2.1 Introduction                                                                | 21    |

| 2.2 Reversed Nested Miller Compensation (RNMC)                                  | 21    |

| 2.3 Flipped Voltage Follower                                                    | 24    |

| 2.4 Class AB Flipped Voltage Follower                                           | 25    |

| 2.5 Folded Flipped Voltage Follower                                             | 26    |

| 2.6 Push pull class AB output stage                                           | 27     |

|-------------------------------------------------------------------------------|--------|

| 2.7 Slew Rate Enhancer Circuit                                                | 29     |

| 2.8 Dynamic Threshold Voltage MOSFET (DTMOS) technique                        | 29     |

| 2.9 Self Cascode Structure                                                    | 30     |

| 2.10 Self Cascode Structure with Dynamic Threshold Voltage MOSFET technic     | Jue30  |

| 2.11 Modified Self Cascode Structure                                          | 31     |

| 2.12 Active LHP Zero Circuit                                                  | 32     |

| 2.13 Summary                                                                  | 33     |

| Chapter 3 Reversed Nested Miller Compensation with Flipped Voltage Follower   | 34     |

| 3.1 Introduction                                                              | 35     |

| 3.2 Proposed amplifier 1                                                      | 35     |

| 3.2.1. Circuit description of proposed amplifier 1                            | 36     |

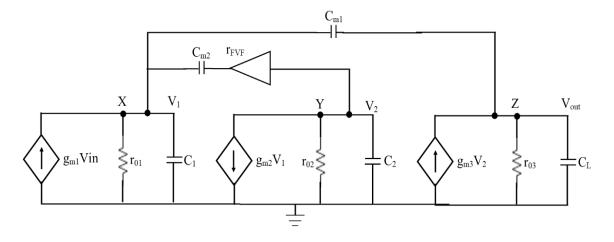

| 3.2.2. Small signal analysis of proposed amplifier 1                          | 37     |

| 3.2.3. Simulation results and discussions                                     |        |

| 3.3 Comparison                                                                | 45     |

| 3.4 Summary                                                                   | 46     |

| Chapter 4 Reversed Nested Miller Compensation with Folded Flipped Voltage Fol | lower, |

| Self Cascode structure and DTMOS                                              | 47     |

| 4.1 Introduction                                                              | 48     |

| 4.2 Proposed amplifier 2                                                      | 48     |

| 4.2.1 Circuit description of proposed amplifier 2                             | 49     |

| 4.2.2 Small signal analysis of proposed amplifier 2                           | 50     |

| 4.2.3 Simulation results and discussions                                      | 52     |

| 4.3. Proposed amplifier 3                                                     | 57     |

| 4.3.1. Circuit description of proposed amplifier 3                                                                                                                                                                                                                                                                                 |                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 4.3.2. Small signal analysis of proposed amplifier 3                                                                                                                                                                                                                                                                               |                                   |

| 4.3.3. Simulation results and discussions                                                                                                                                                                                                                                                                                          | 61                                |

| 4.4. Proposed amplifier 4                                                                                                                                                                                                                                                                                                          | 65                                |

| 4.4.1. Circuit description of proposed amplifier 4                                                                                                                                                                                                                                                                                 | 66                                |

| 4.4.2. Small signal analysis of proposed amplifier 4                                                                                                                                                                                                                                                                               | 67                                |

| 4.4.3. Simulation results and discussions                                                                                                                                                                                                                                                                                          | 69                                |

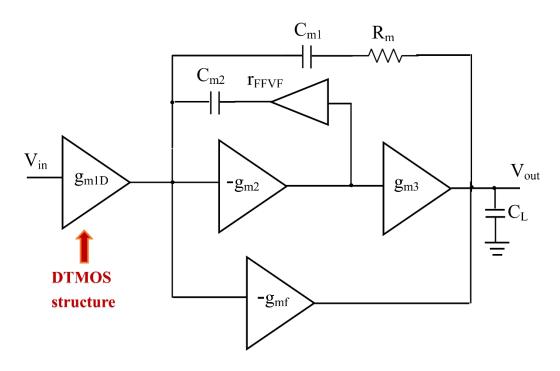

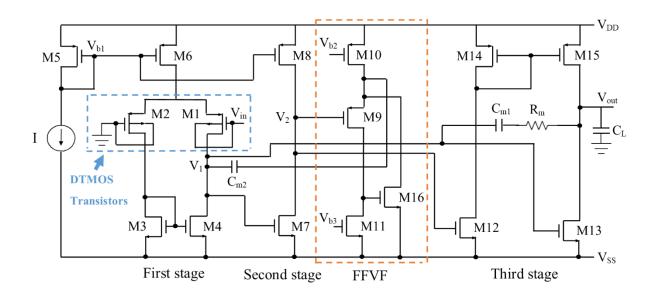

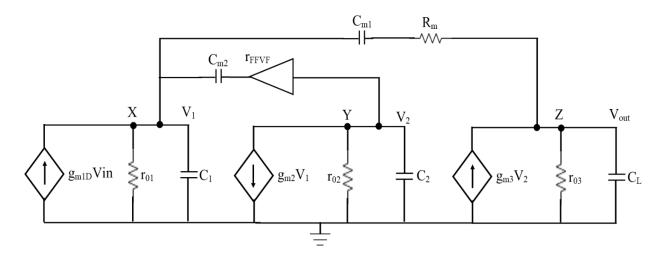

| 4.5.Proposed amplifier 5                                                                                                                                                                                                                                                                                                           | 74                                |

| 4.5.1. Circuit description of proposed amplifier 5                                                                                                                                                                                                                                                                                 | 75                                |

| 4.5.2. Small signal analysis of proposed amplifier 5                                                                                                                                                                                                                                                                               | 76                                |

| 4.5.3. Simulation results and discussions                                                                                                                                                                                                                                                                                          | 78                                |

| 4.6 Comparison                                                                                                                                                                                                                                                                                                                     | 83                                |

| iio companion                                                                                                                                                                                                                                                                                                                      |                                   |

| 4.7 Summary                                                                                                                                                                                                                                                                                                                        |                                   |

|                                                                                                                                                                                                                                                                                                                                    | 84                                |

| 4.7 Summary                                                                                                                                                                                                                                                                                                                        | 84<br>f Cascode                   |

| 4.7 Summary<br>Chapter 5 Frequency compensation using Active LHP Zero Circuit with Sel                                                                                                                                                                                                                                             | 84<br>f Cascode<br>86             |

| 4.7 Summary<br>Chapter 5 Frequency compensation using Active LHP Zero Circuit with Self<br>structure and DTMOS                                                                                                                                                                                                                     | 84<br>f Cascode<br>86<br>87       |

| <ul> <li>4.7 Summary.</li> <li>Chapter 5 Frequency compensation using Active LHP Zero Circuit with Self structure and DTMOS.</li> <li>5.1 Introduction.</li> </ul>                                                                                                                                                                 | 84<br>f Cascode<br>86<br>87<br>87 |

| <ul> <li>4.7 Summary</li> <li>Chapter 5 Frequency compensation using Active LHP Zero Circuit with Self structure and DTMOS</li></ul>                                                                                                                                                                                               |                                   |

| <ul> <li>4.7 Summary.</li> <li>Chapter 5 Frequency compensation using Active LHP Zero Circuit with Self structure and DTMOS.</li> <li>5.1 Introduction.</li> <li>5.2. Proposed amplifier 6.</li> <li>5.2.1. Circuit description of proposed amplifier 6.</li> </ul>                                                                |                                   |

| <ul> <li>4.7 Summary.</li> <li>Chapter 5 Frequency compensation using Active LHP Zero Circuit with Self structure and DTMOS.</li> <li>5.1 Introduction.</li> <li>5.2. Proposed amplifier 6.</li> <li>5.2.1. Circuit description of proposed amplifier 6.</li> <li>5.2.2. Small signal analysis of proposed amplifier 6.</li> </ul> |                                   |

| <ul> <li>4.7 Summary</li> <li>Chapter 5 Frequency compensation using Active LHP Zero Circuit with Self structure and DTMOS</li></ul>                                                                                                                                                                                               |                                   |

| <ul> <li>4.7 Summary</li> <li>Chapter 5 Frequency compensation using Active LHP Zero Circuit with Self structure and DTMOS</li></ul>                                                                                                                                                                                               |                                   |

| 5.4. Proposed amplifier 8                                                 | 103          |

|---------------------------------------------------------------------------|--------------|

| 5.4.1. Circuit description of proposed amplifier 8                        | 104          |

| 5.4.2. Small signal analysis of proposed amplifier 8                      | 105          |

| 5.4.3. Simulation results and discussions                                 | 107          |

| 5.5. Proposed amplifier 9                                                 | 111          |

| 5.5.1. Circuit description of proposed amplifier 9                        | 112          |

| 5.5.2. Small signal analysis of proposed amplifier 9                      | 113          |

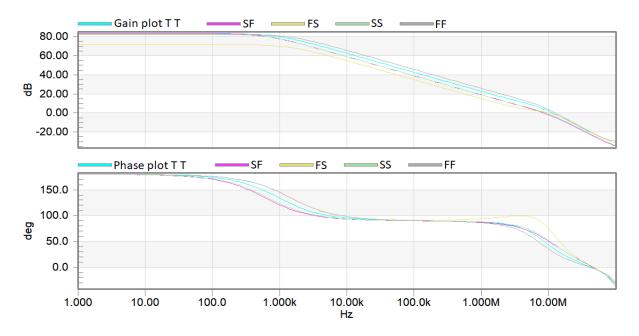

| 5.5.3. Simulation results and discussions                                 | 115          |

| 5.6 Comparison                                                            | 119          |

| 5.7 Summary                                                               | 121          |

| Chapter 6 Reversed Nested Miller Compensation with Class AB Flipped Volta | age Follower |

| and Slew Rate Enhancer Circuit                                            | 122          |

| 6.1. Introduction                                                         | 123          |

| 6.2. Proposed amplifier 10                                                | 123          |

| 6.2.1. Circuit description of proposed amplifier 10                       |              |

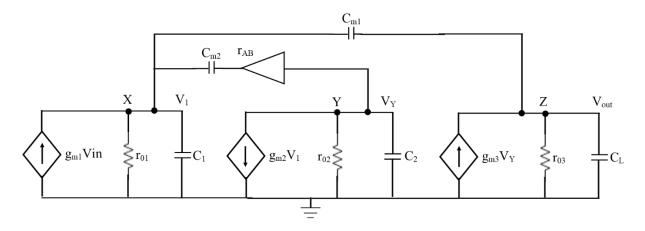

| 6.2.2. Small signal analysis of proposed amplifier 10                     | 125          |

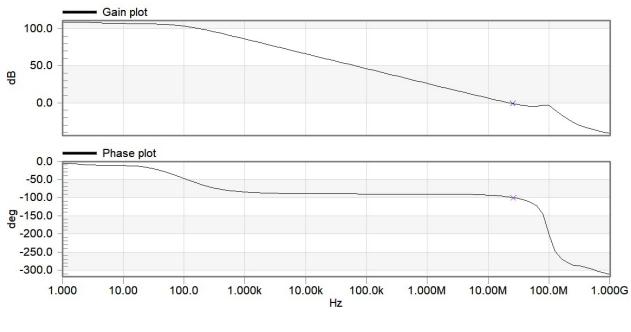

| 6.2.3. Simulation results and discussions                                 | 127          |

| 6.3. Proposed amplifier 11                                                | 136          |

| 6.3.1. Circuit description of proposed amplifier 11                       | 136          |

| 6.3.2. Small signal analysis of proposed amplifier 11                     | 137          |

| 6.3.3. Simulation results and discussions                                 | 139          |

| 6.4 Comparison                                                            | 148          |

| 6.5 Summary                                                               | 148          |

| Chapter 7 Conclusion and Future Scope                                     | 150          |

| 7.1 Summary of work done  | 151 |

|---------------------------|-----|

| 7.2 Scope for future work | 153 |

| References                | 154 |

| Publications              | 162 |

| Appendix A                |     |

# LIST OF FIGURES

| Fig. 1.1 Miller compensation of two-stage op amp4                   |

|---------------------------------------------------------------------|

| Fig. 1.2 Pole Splitting as a result of Miller compensation4         |

| Fig. 1.3 Miller Compensation with Nulling Resistor                  |

| Fig. 1.4 Miller Compensation with Voltage Buffer5                   |

| Fig. 1.5 Miller Compensation with Current Buffer                    |

| Fig. 1.6 Nested Miller Compensation                                 |

| Fig. 1.7 NMC with Nulling Resistor                                  |

| Fig. 1.8 Multipath NMC9                                             |

| Fig. 1.9 Reversed Nested Miller Compensation10                      |

| Fig. 1.10 RNMC with Nulling Resistor10                              |

| Fig. 1.11 RNMC with Voltage Buffer11                                |

| Fig. 1.12 RNMC with Current Buffer11                                |

| Fig. 1.13 RNMC with Voltage Buffer and Resistor12                   |

| Fig. 1.14 Reversed Active Feedback Frequency Compensation12         |

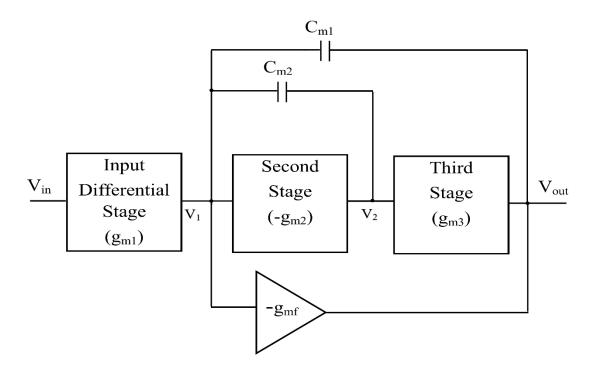

| Fig. 2.1 Reversed nested Miller compensation technique              |

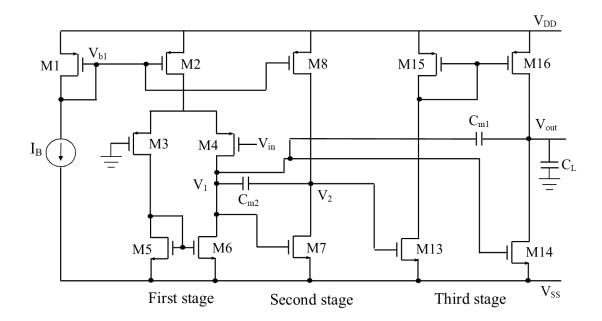

| Fig. 2.2 Circuit Diagram of three stage amplifier with RNMC22       |

| Fig. 2.3 Small signal equivalent circuit of RNMC23                  |

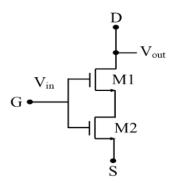

| Fig. 2.4 Flipped Voltage Follower                                   |

| Fig. 2.5 Class AB Flipped Voltage Follower                          |

| Fig. 2.6 Folded Flipped Voltage Follower                            |

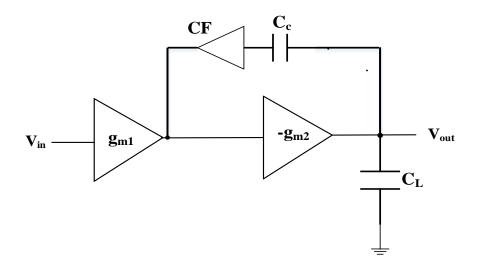

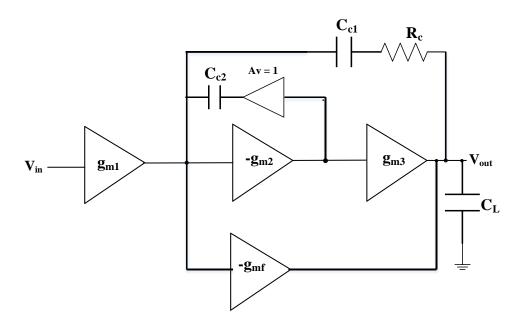

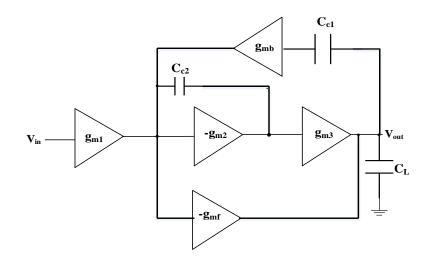

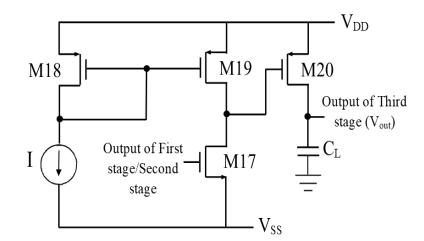

| Fig. 2.7 Reversed Nested Miller Compensation with feed forward path |

| Fig. 2.8 Circuit diagram of Reversed Nested Miller Compensation with feed forward                                   |

|---------------------------------------------------------------------------------------------------------------------|

| path                                                                                                                |

| Fig. 2.9 Slew Rate Enhancer Circuit                                                                                 |

| Fig. 2.10 DTMOS                                                                                                     |

| Fig. 2.11 Self cascode structure                                                                                    |

| Fig. 2.12 Self Cascode Structure with DTMOS                                                                         |

| Fig. 2.13 Modified self cascode structure                                                                           |

| Fig. 2.14 Active LHP Zero Circuit                                                                                   |

| Fig. 3.1 Block diagram of proposed amplifier 136Fig. 3.2 Transistor level implementation of proposed amplifier 137  |

| Fig. 3.3 Small signal model of proposed amplifier 1                                                                 |

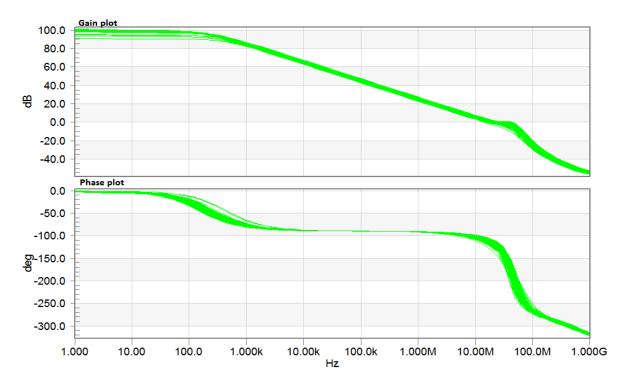

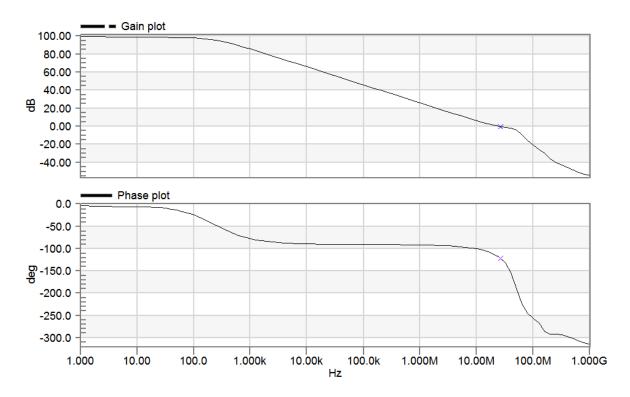

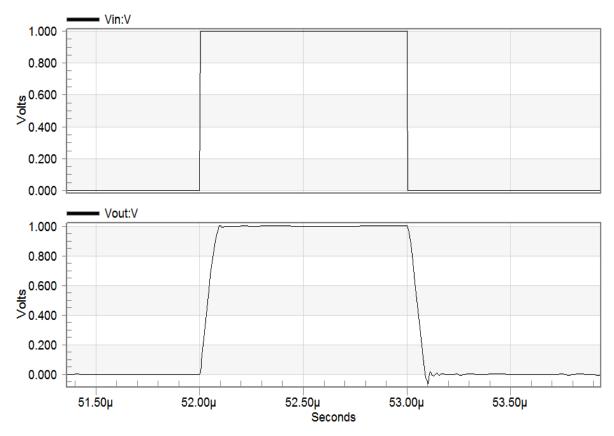

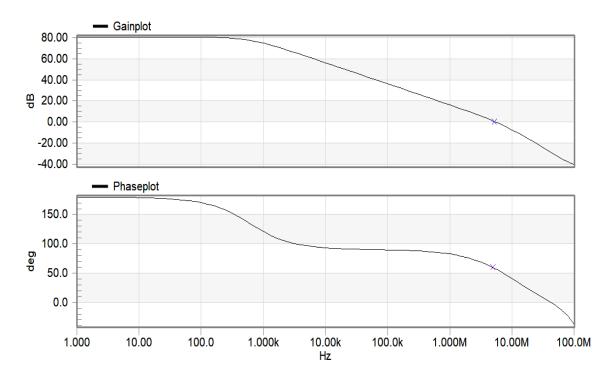

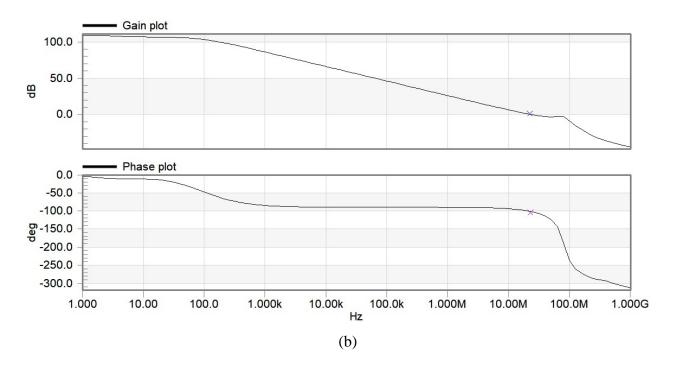

| Fig. 3.4 Frequency response of proposed amplifier 141                                                               |

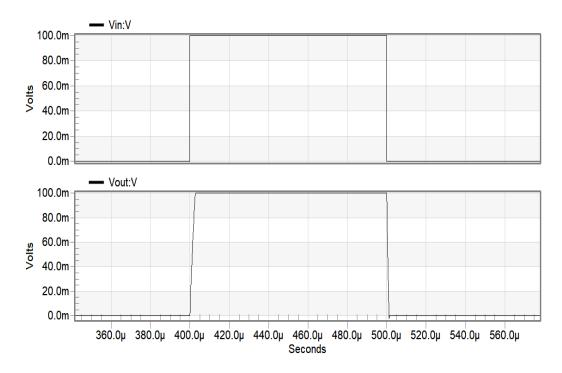

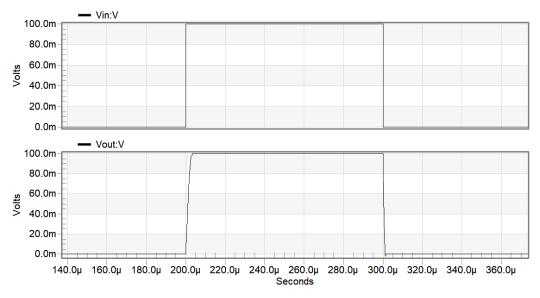

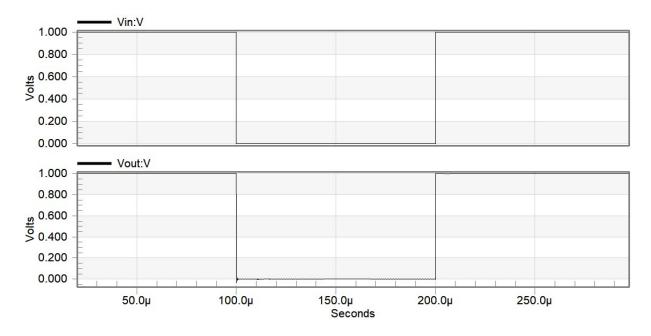

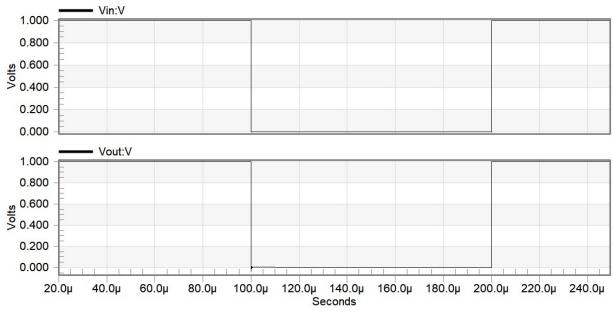

| Fig. 3.5 Transient response of proposed amplifier 141                                                               |

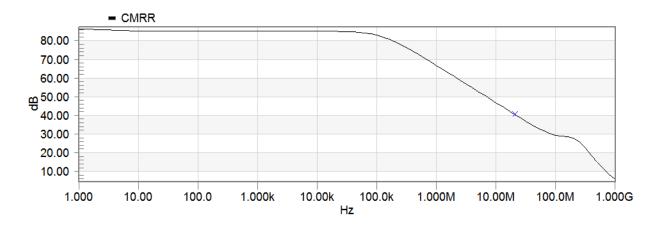

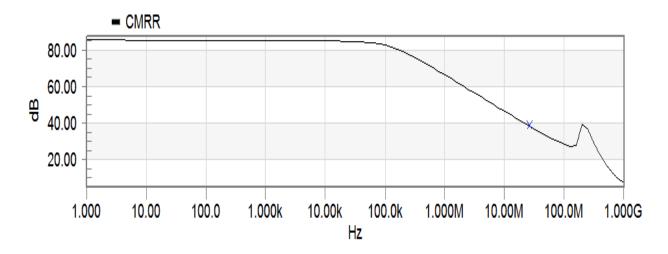

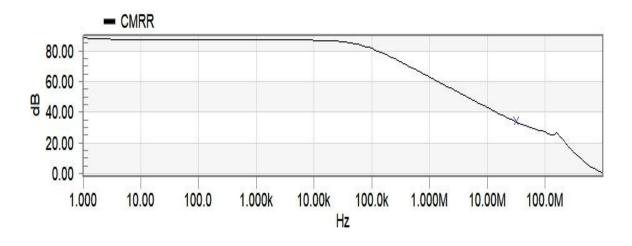

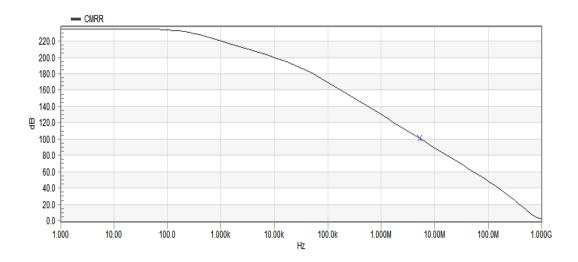

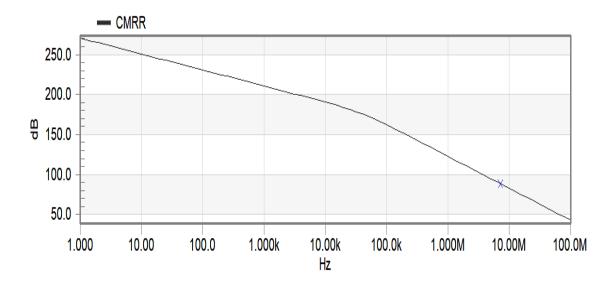

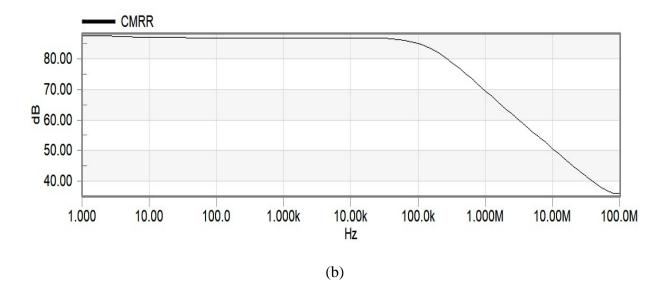

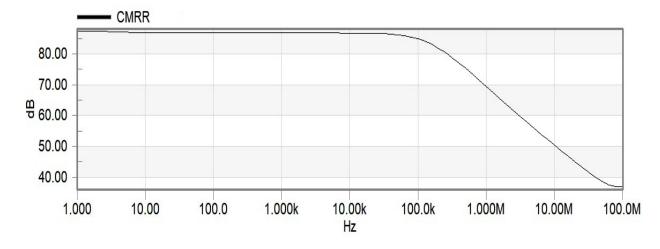

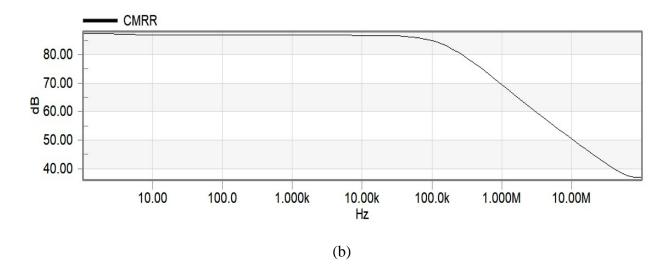

| Fig. 3.6 Frequency response of CMRR of proposed amplifier 142                                                       |

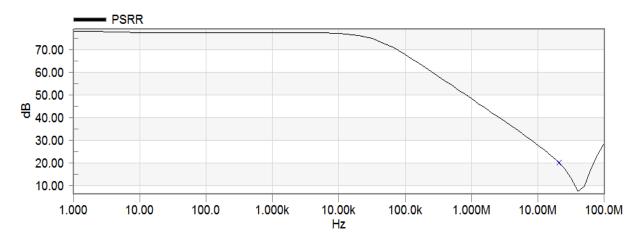

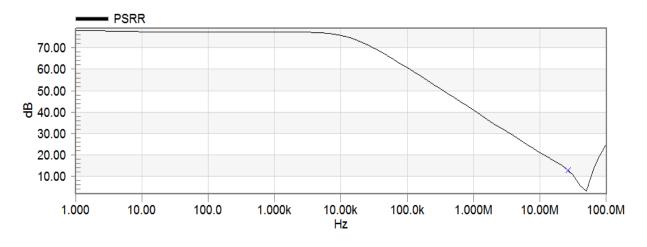

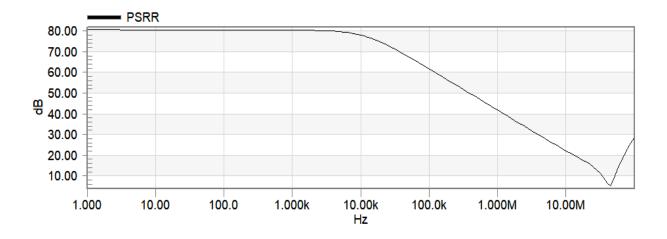

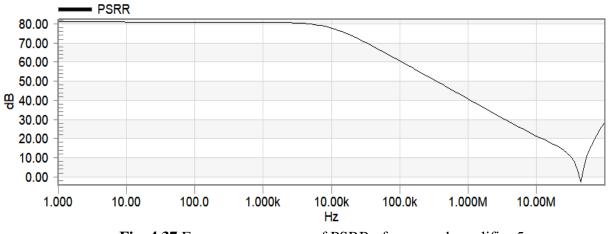

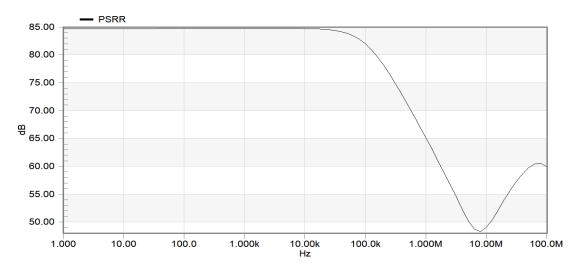

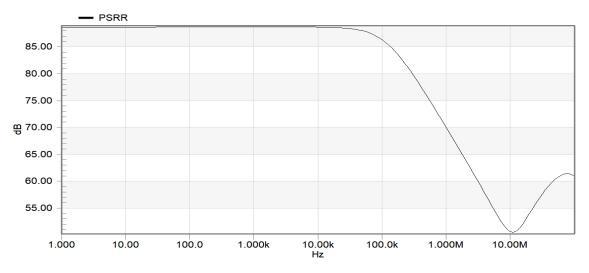

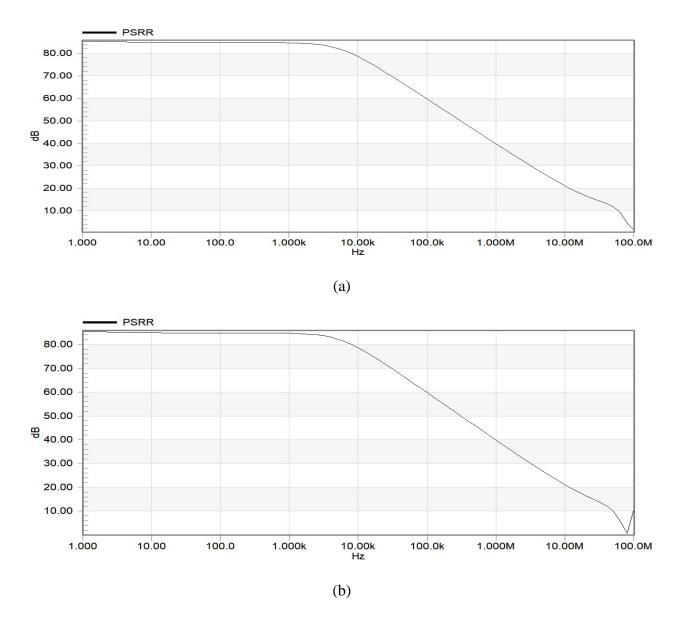

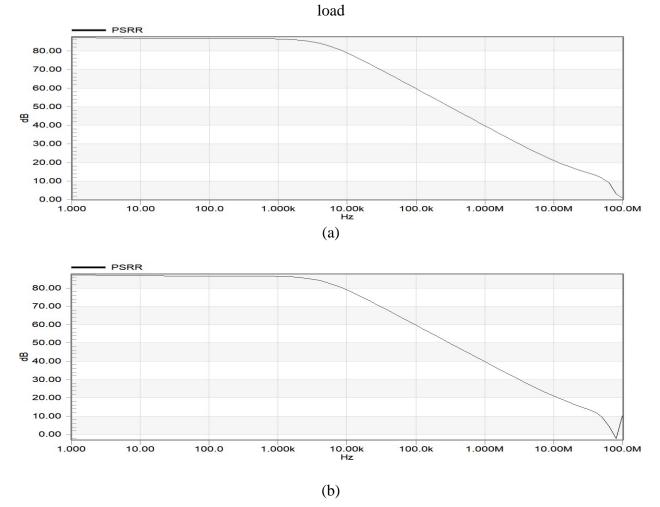

| Fig. 3.7 Frequency response of PSRR of proposed amplifier 142                                                       |

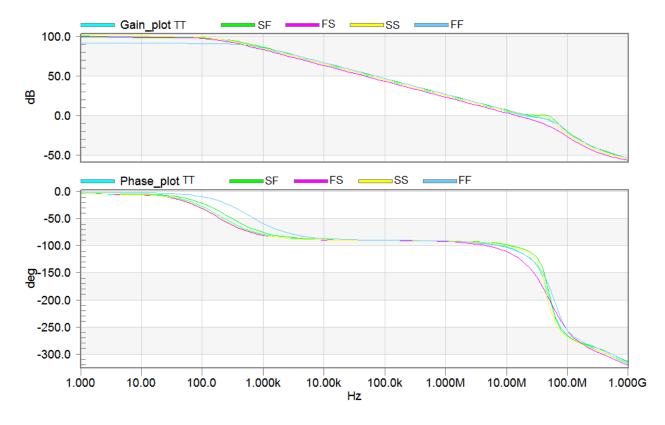

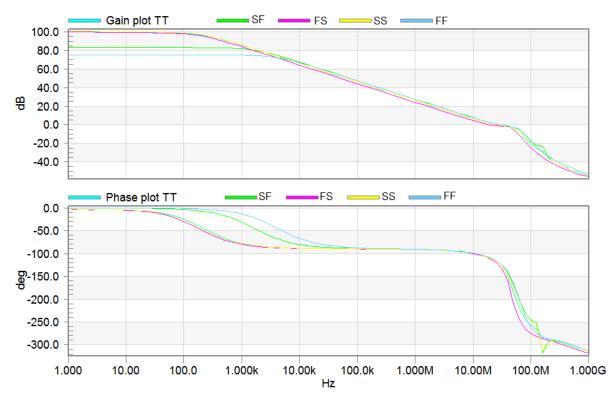

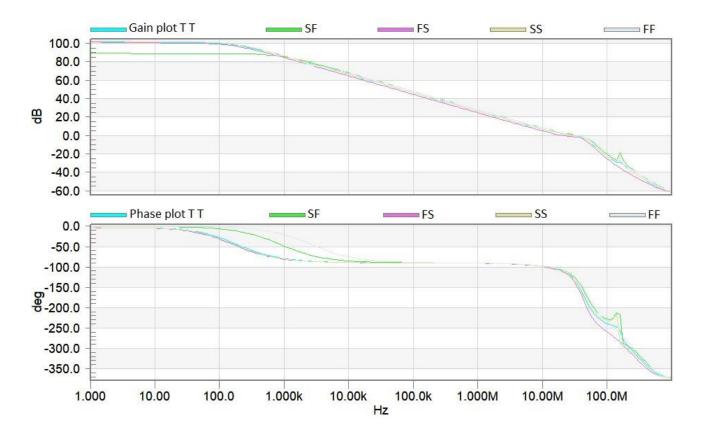

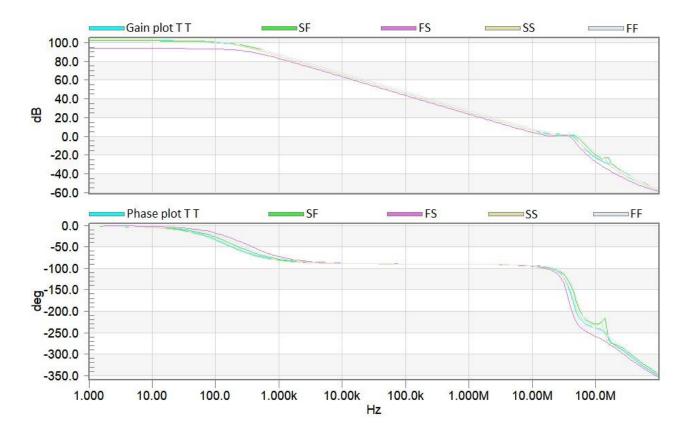

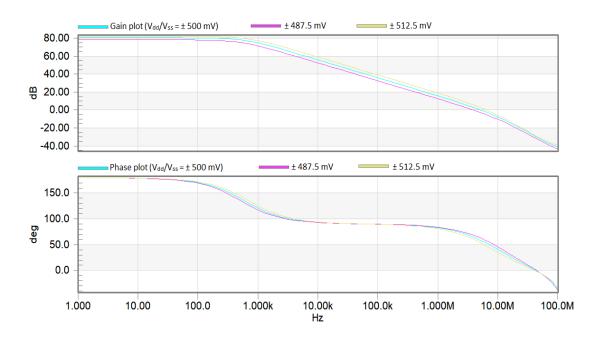

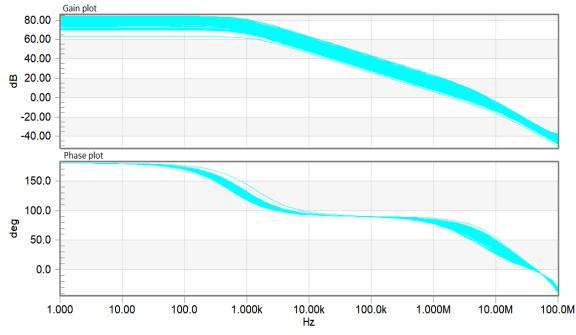

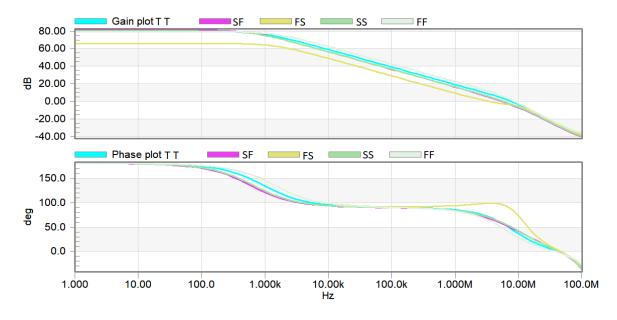

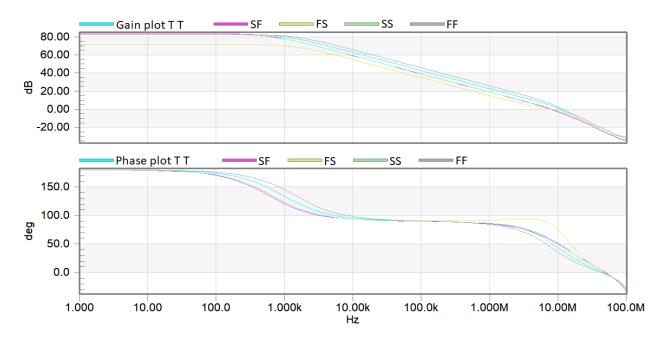

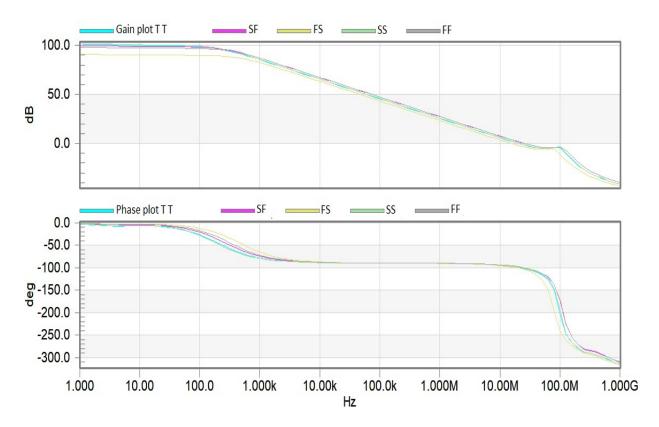

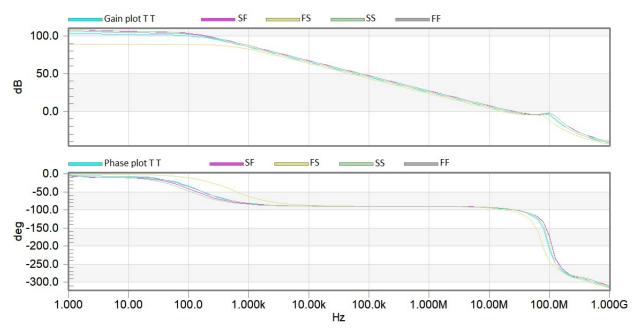

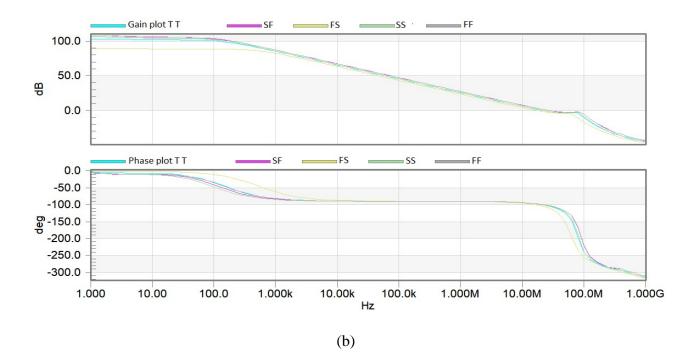

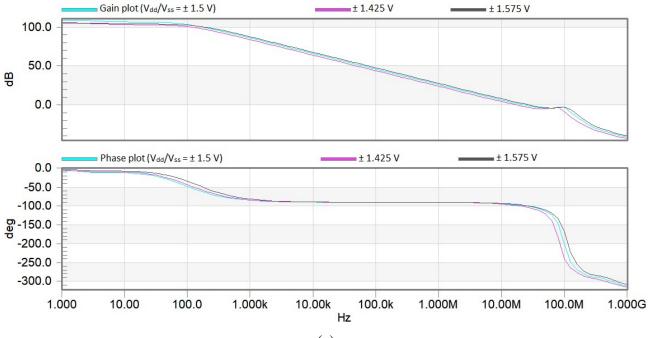

| Fig. 3.8 Frequency response of proposed amplifier 1 at different process corners                                    |

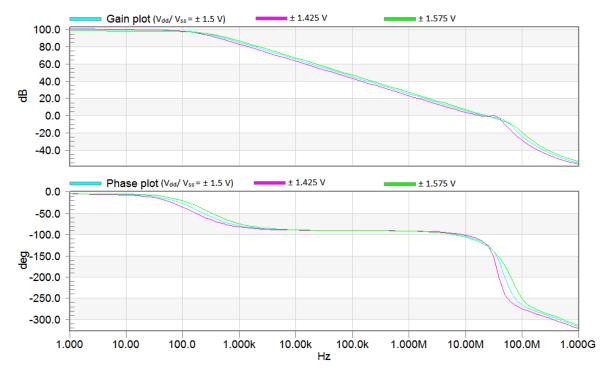

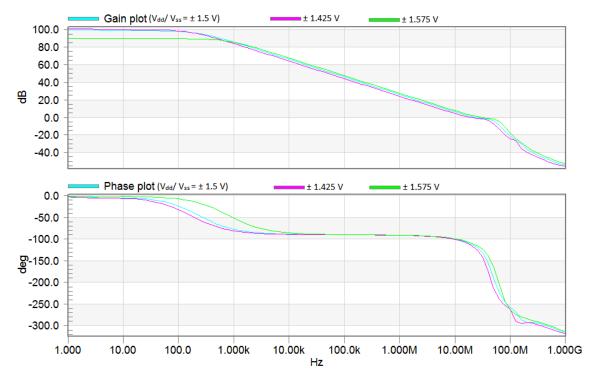

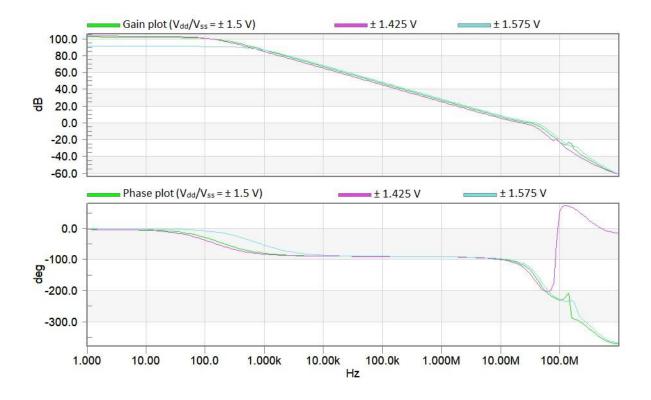

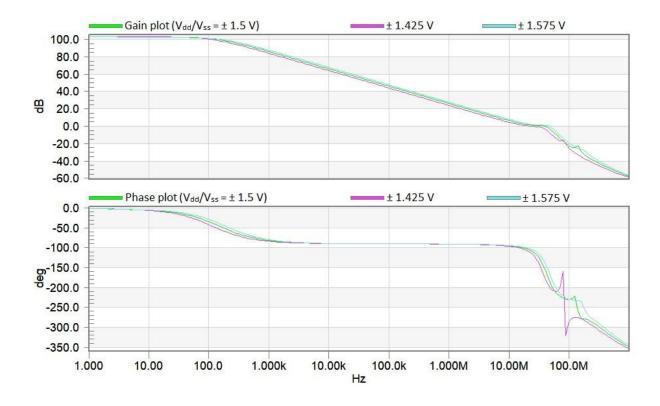

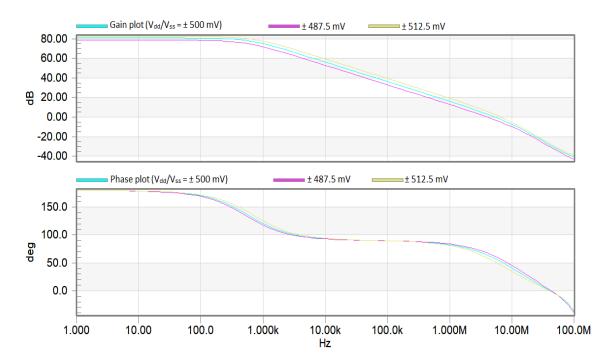

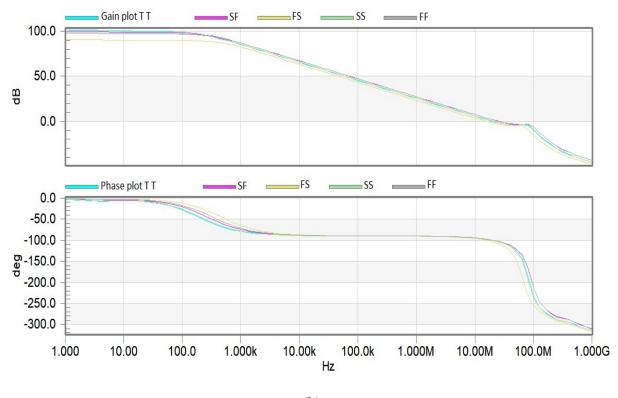

| Fig. 3.9 Frequency response of proposed amplifier 1 with variations in supply voltage44                             |

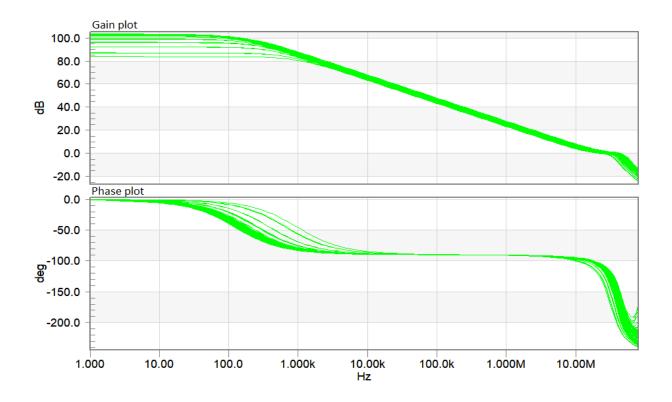

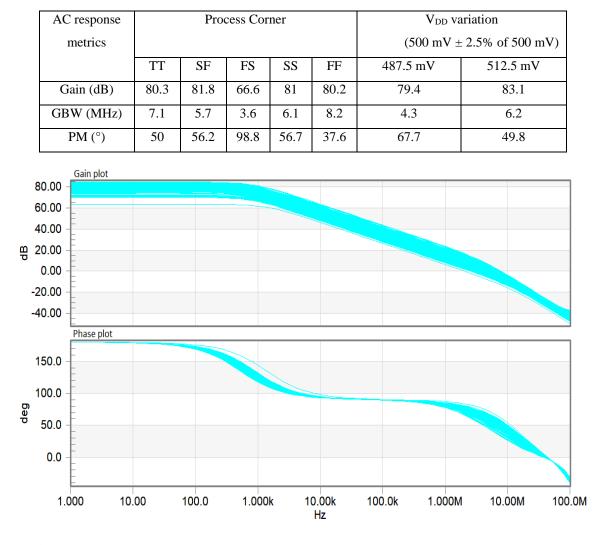

| Fig. 3.10 Monte-Carlo analysis for frequency response of the proposed amplifier 1 against supply voltage variations |

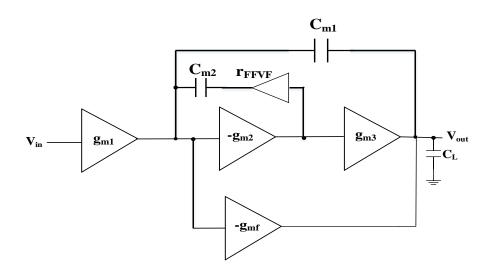

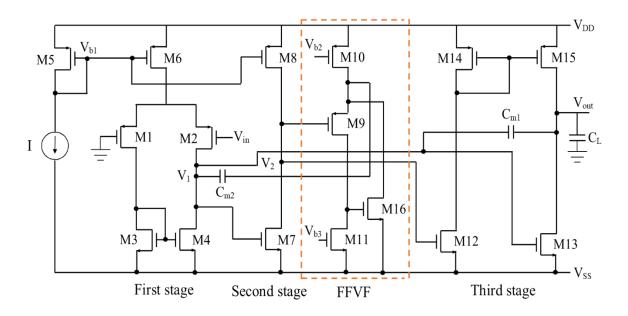

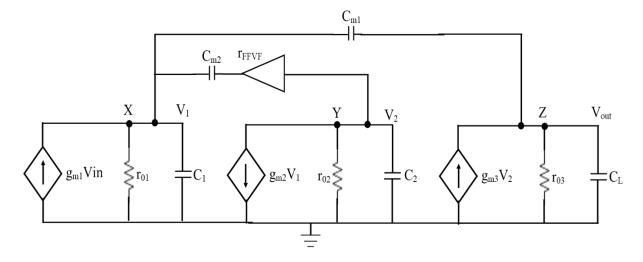

| Fig. 4.1 Block diagram of proposed amplifier 249                                                                    |

| Fig. 4.2 Transistor level implementation of proposed amplifier 250                                                  |

| Fig. 4.3 Small signal model of proposed amplifier 250                                                               |

| Fig. 4.4 Frequency response of proposed amplifier 253                                                               |

| Fig. 4.5 Transient response of proposed amplifier 254                                                               |

| Fig. 4.6 Frequency response of CMRR of proposed amplifier 254                                                       |

|---------------------------------------------------------------------------------------------------------------------|

| Fig. 4.7 Frequency response of PSRR of proposed amplifier 255                                                       |

| Fig. 4.8 Frequency response of proposed amplifier 2 at different process corners55                                  |

| Fig. 4.9 Frequency response of proposed amplifier 2 with variations in supply voltage56                             |

| Fig. 4.10 Monte-Carlo analysis for frequency response of the proposed amplifier 2 against supply voltage variations |

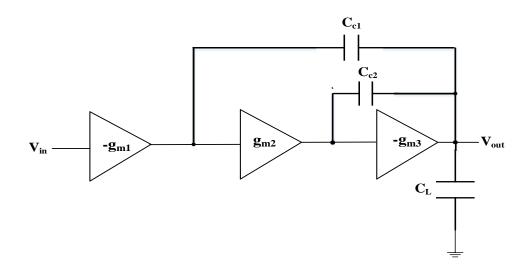

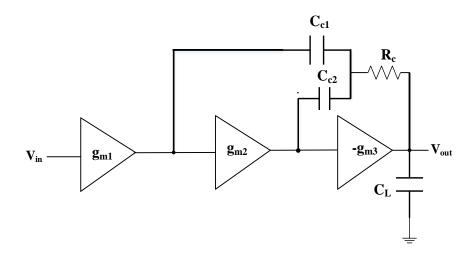

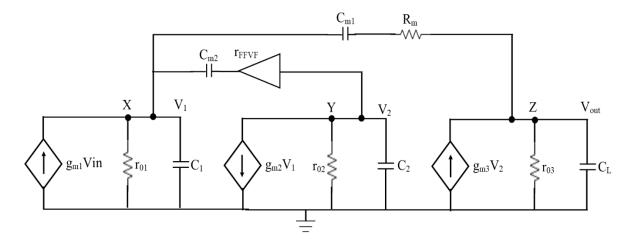

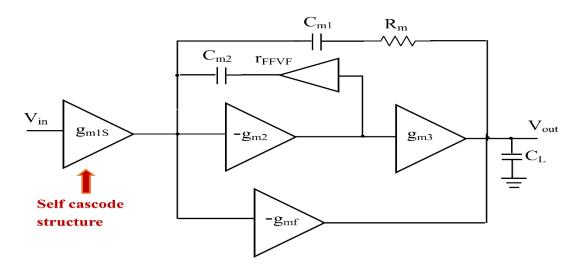

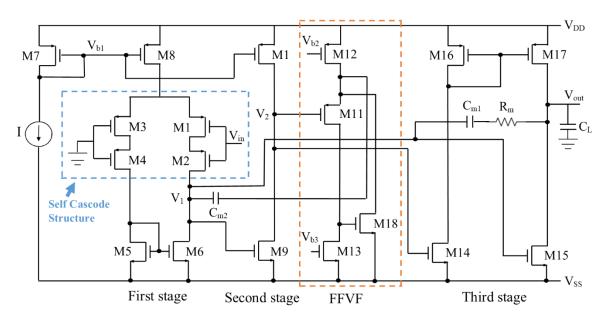

| Fig. 4.11 Block diagram of proposed amplifier 358                                                                   |

| Fig. 4.12 Transistor level implementation of proposed amplifier 359                                                 |

| Fig. 4.13 Small signal model of proposed amplifier 359                                                              |

| Fig. 4.14 Frequency response of proposed amplifier 362                                                              |

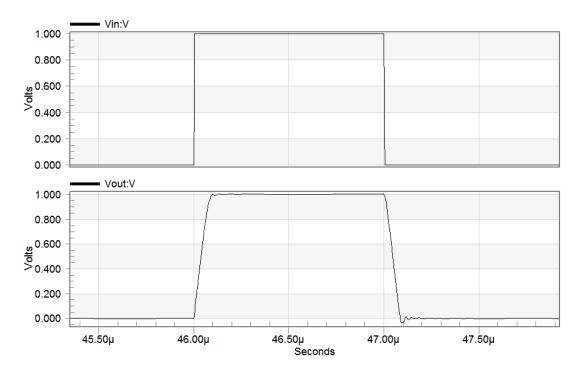

| Fig. 4.15 Transient response of proposed amplifier 3                                                                |

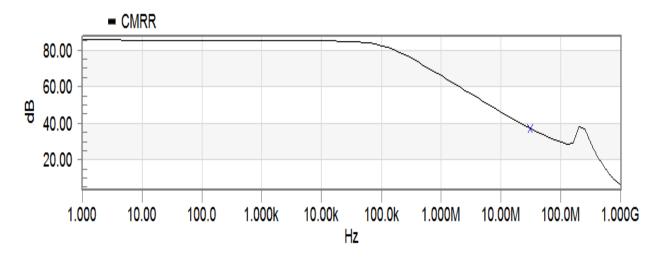

| Fig. 4.16 Frequency response of CMRR of proposed amplifier 363                                                      |

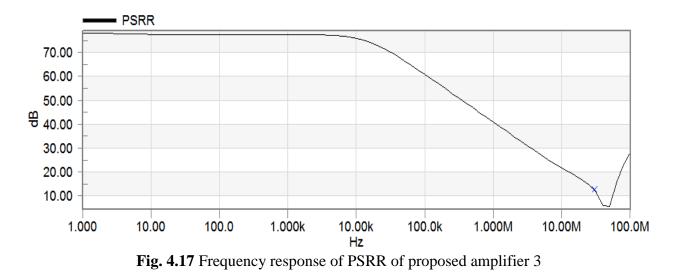

| Fig. 4.17 Frequency response of PSRR of proposed amplifier 363                                                      |

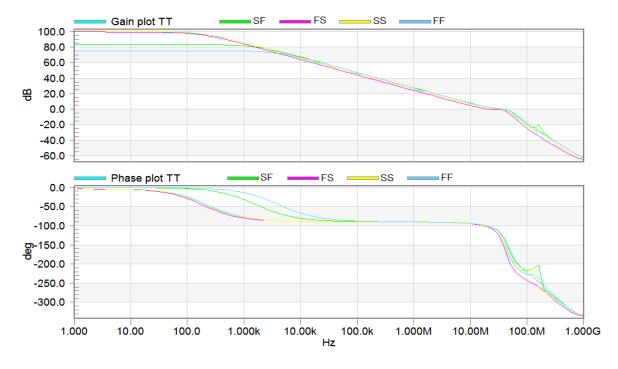

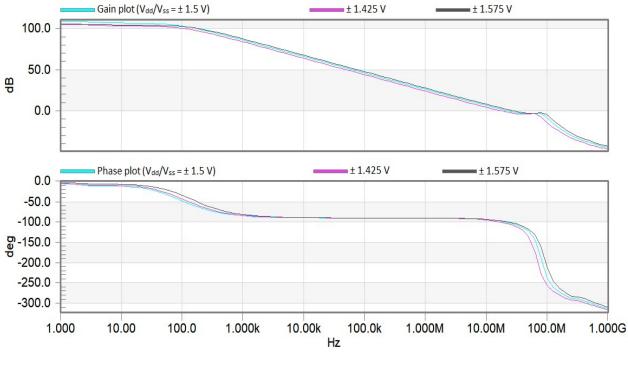

| Fig. 4.18 Frequency response of proposed amplifier 3 at different process corners                                   |

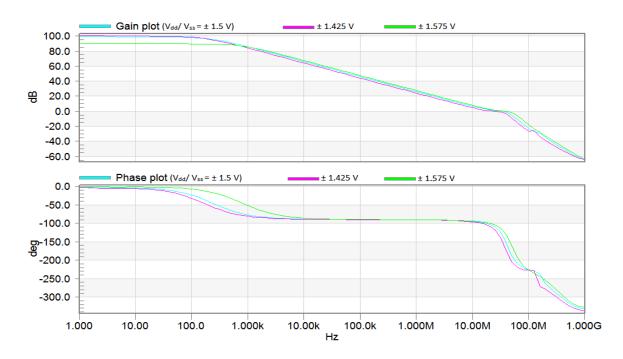

| Fig. 4.19 Frequency response of proposed amplifier 3 with variations in supply voltage64                            |

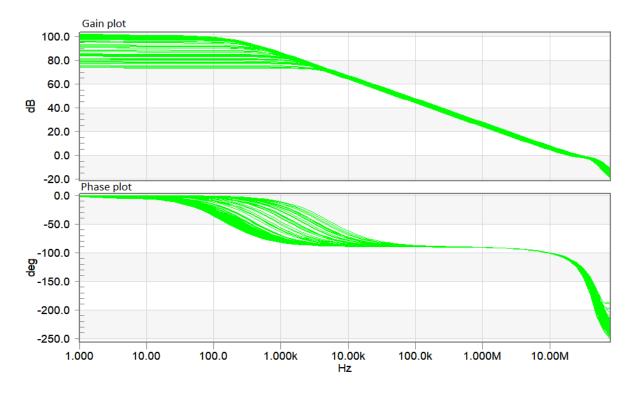

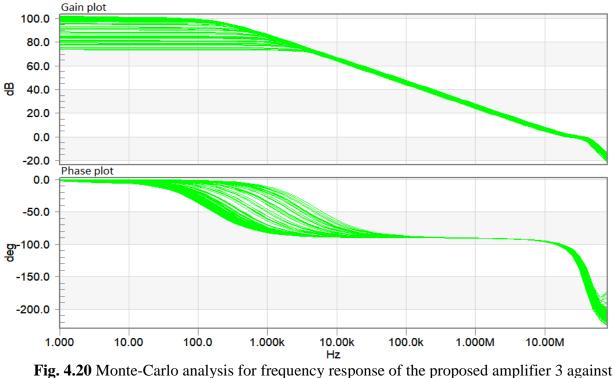

| Fig. 4.20 Monte-Carlo analysis for frequency response of the proposed amplifier 3 against supply voltage variations |

| Fig. 4.21 Block diagram of proposed amplifier 466                                                                   |

| Fig. 4.22 Transistor level implementation of proposed amplifier 467                                                 |

| Fig. 4.23 Small signal model of proposed amplifier 467                                                              |

| Fig. 4.24 Frequency response of proposed amplifier 470                                                              |

| Fig. 4.25 Transient response of proposed amplifier 470                                                              |

| Fig. 4.26 Frequency response of CMRR of proposed amplifier 471                                                      |

| Fig. 4.27 Frequency response of PSRR of proposed amplifier 471                                                      |

|---------------------------------------------------------------------------------------------------------------------|

| Fig. 4.28 Frequency response of proposed amplifier 4 at different process corners72                                 |

| Fig. 4.29 Frequency response of proposed amplifier 4 with variations in supply voltage73                            |

| Fig. 4.30 Monte-Carlo analysis for frequency response of the proposed amplifier 4 against supply voltage variations |

| Fig. 4.31 Block diagram of proposed amplifier 575                                                                   |

| Fig. 4.32 Transistor level implementation of proposed amplifier 576                                                 |

| Fig. 4.33 Small signal model of proposed amplifier 576                                                              |

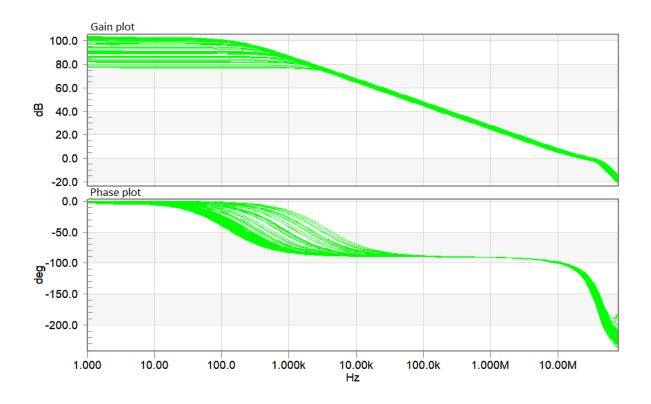

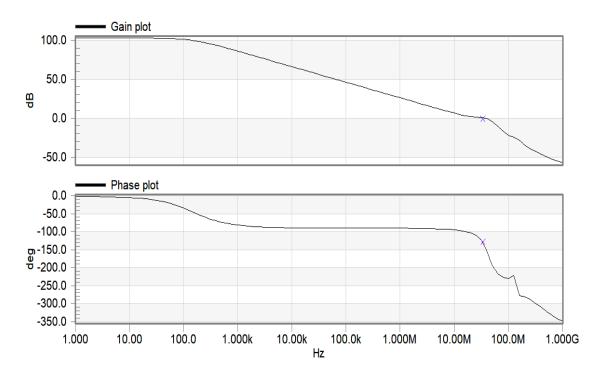

| Fig. 4.34 Frequency response of proposed amplifier 5                                                                |

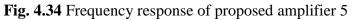

| Fig. 4.35 Transient response of proposed amplifier 5                                                                |

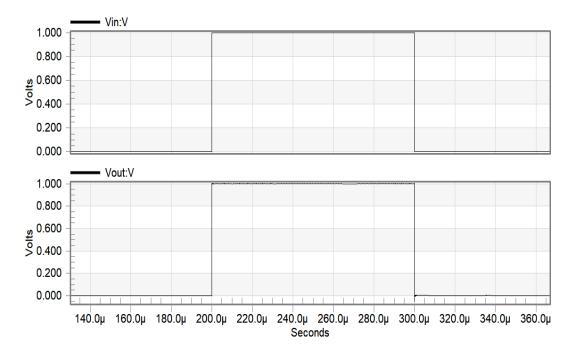

| Fig. 4.36 Frequency response of CMRR of proposed amplifier 580                                                      |

| Fig. 4.37 Frequency response of PSRR of proposed amplifier 580                                                      |

| Fig. 4.38 Frequency response of proposed amplifier 5 at different process corners                                   |

| Fig. 4.39 Frequency response of proposed amplifier 5 with variations in supply voltage82                            |

| Fig. 4.40 Monte-Carlo analysis for frequency response of the proposed amplifier 5 against supply voltage variations |

| Fig. 5.1 Block diagram of proposed amplifier 6                                                                      |

| Fig. 5.2 Transistor level implementation of proposed amplifier 6                                                    |

| Fig. 5.3 Small signal model of proposed amplifier 6                                                                 |

| Fig. 5.4 Frequency response of proposed amplifier 692                                                               |

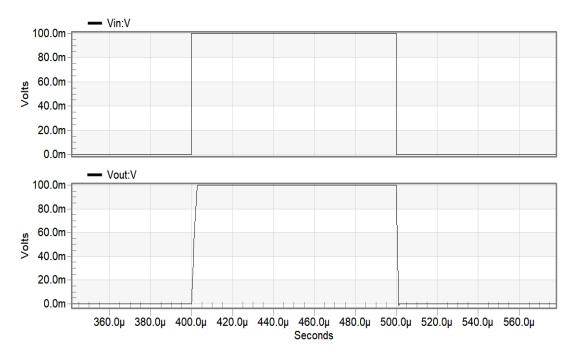

| Fig. 5.5 Transient response of proposed amplifier 692                                                               |

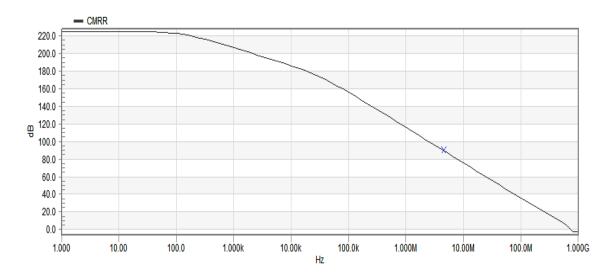

| Fig. 5.6 Frequency response of CMRR for proposed amplifier 6                                                        |

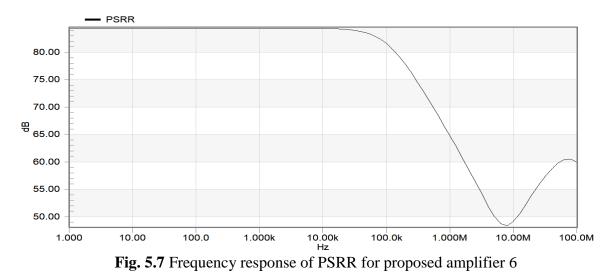

| Fig. 5.7 Frequency response of PSRR for proposed amplifier 6                                                        |

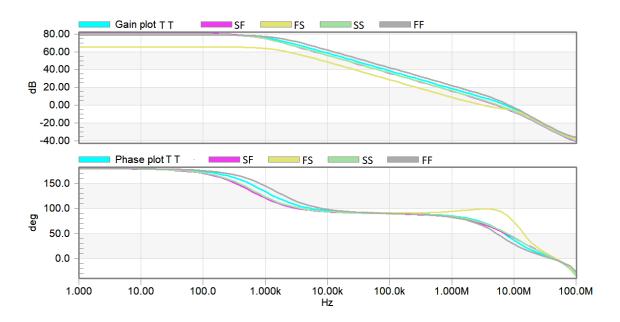

| Fig. 5.8 Frequency response of proposed amplifier 6 at different corners                                            |

| Fig. 5.9 Frequency response of proposed amplifier 6 against variations in supply                                         |

|--------------------------------------------------------------------------------------------------------------------------|

| voltage                                                                                                                  |

| Fig. 5.10 Monte-Carlo simulation for gain and phase response of the proposed amplifier 6 with V <sub>DD</sub> deviations |

|                                                                                                                          |

| Fig. 5.11 Block diagram of proposed amplifier 7                                                                          |

| Fig. 5.13 Small signal model of proposed amplifier 797                                                                   |

| Fig. 5.14 Frequency response of proposed amplifier 7100                                                                  |

| Fig. 5.15 Transient response of proposed amplifier 7100                                                                  |

| Fig. 5.16 Frequency response of CMRR for proposed amplifier 7101                                                         |

| Fig. 5.17 Frequency response of PSRR for proposed amplifier 7101                                                         |

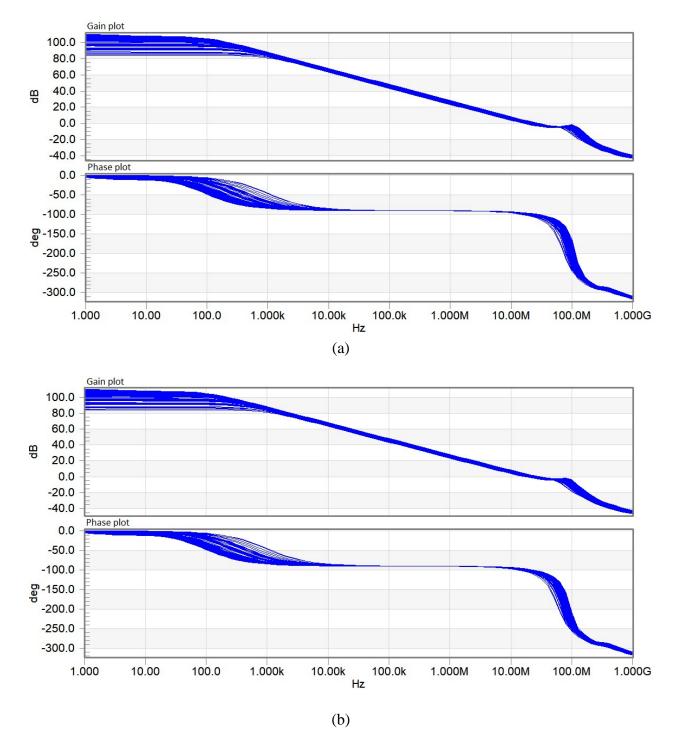

| Fig. 5.18 Frequency response of proposed amplifier 7 at different process                                                |

| corners                                                                                                                  |

| Fig. 5.19 Frequency response of proposed amplifier 7 against variations in supply      voltage                           |

| Fig. 5.20 Monte-Carlo simulation for gain and phase response of the proposed amplifier 7                                 |

| with V <sub>DD</sub> deviations                                                                                          |

| Fig. 5.21 Block diagram of proposed amplifier 8104                                                                       |

| Fig. 5.22 Transistor level implementation of proposed amplifier 8105                                                     |

| Fig. 5.23 Small signal model of proposed amplifier 8105                                                                  |

| Fig. 5.24 Frequency response of proposed amplifier 8108                                                                  |

| Fig. 5.25 Transient response of proposed amplifier 8                                                                     |

| Fig. 5.26 Frequency response of CMRR for proposed amplifier 8109                                                         |

| Fig. 5.27 Frequency response of PSRR for proposed amplifier 8109                                                         |

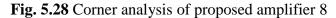

| Fig. 5.28 Corner analysis of proposed amplifier 8110                                                                     |

| Fig. 5.29 Impact of supply voltage variations on proposed amplifier 8110                             |

|------------------------------------------------------------------------------------------------------|

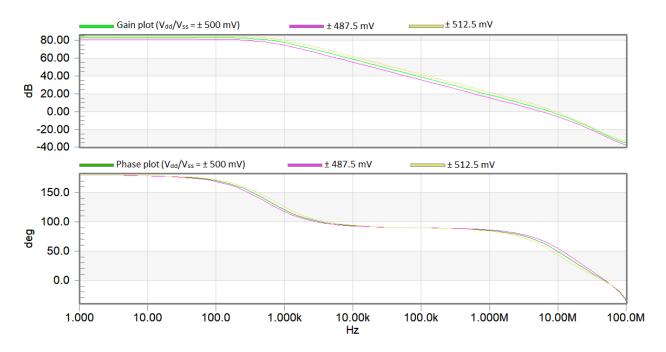

| Fig. 5.30 Monte-Carlo simulation for frequency response of proposed amplifier 8 against              |

| V <sub>DD</sub> deviations                                                                           |

| Fig. 5.31 Block diagram of proposed amplifier 9112                                                   |

| Fig. 5.32 Transistor level implementation of proposed amplifier 9113                                 |

| Fig. 5.33 Small signal model of proposed amplifier 9                                                 |

| Fig. 5.34 Frequency response of proposed amplifier 9                                                 |

| Fig. 5.35 Transient response of proposed amplifier 9                                                 |

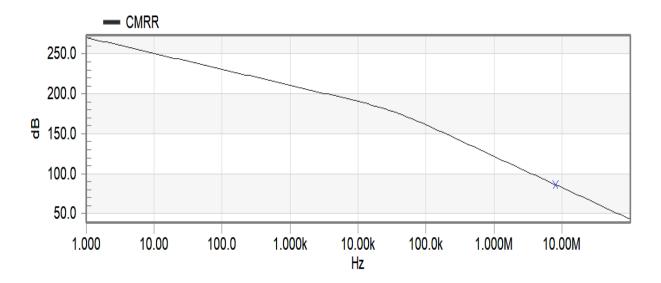

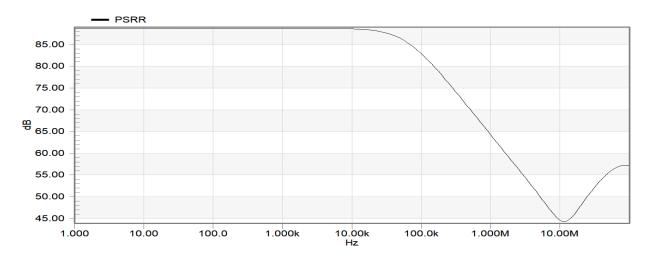

| Fig. 5.36 Frequency response of CMRR for proposed amplifier 9117                                     |

| Fig. 5.37 Frequency response of PSRR for proposed amplifier 9117                                     |

| Fig. 5.38 Corner analysis of proposed amplifier 9118                                                 |

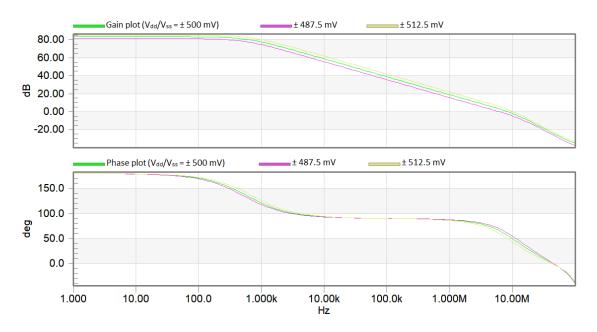

| Fig. 5.39 Impact of supply voltage variations on proposed amplifier 9118                             |

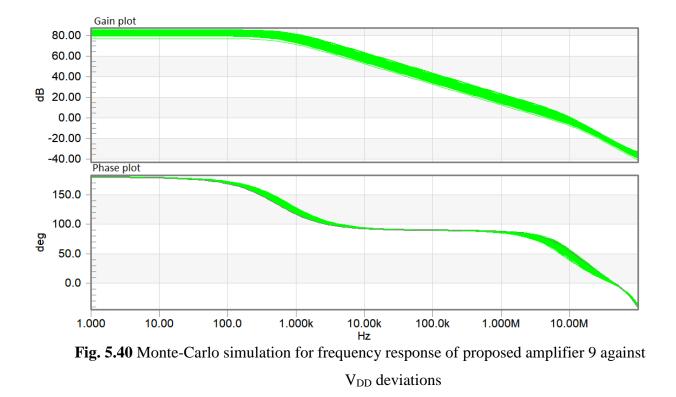

| Fig. 5.40 Monte-Carlo simulation for frequency response of proposed amplifier 9 against              |

| V <sub>DD</sub> deviations119                                                                        |

| Fig. 6.1 Block diagram of proposed amplifier 10124                                                   |

| Fig. 6.2 Transistor level implementation of proposed amplifier 10125                                 |

| Fig. 6.3. Small signal model of proposed amplifier10125                                              |

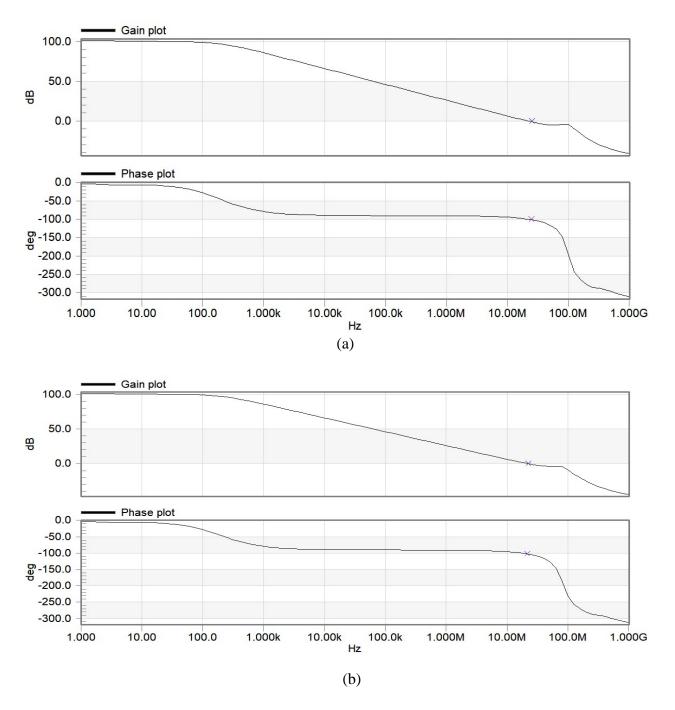

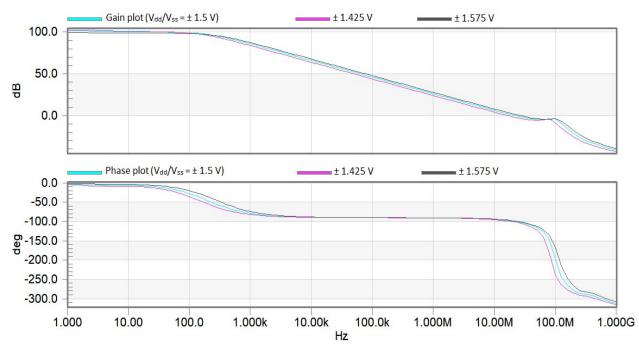

| Fig. 6.4 Frequency response of proposed amplifier 10 (a) at 20 pF load (b) at 30 pF                  |

| load                                                                                                 |

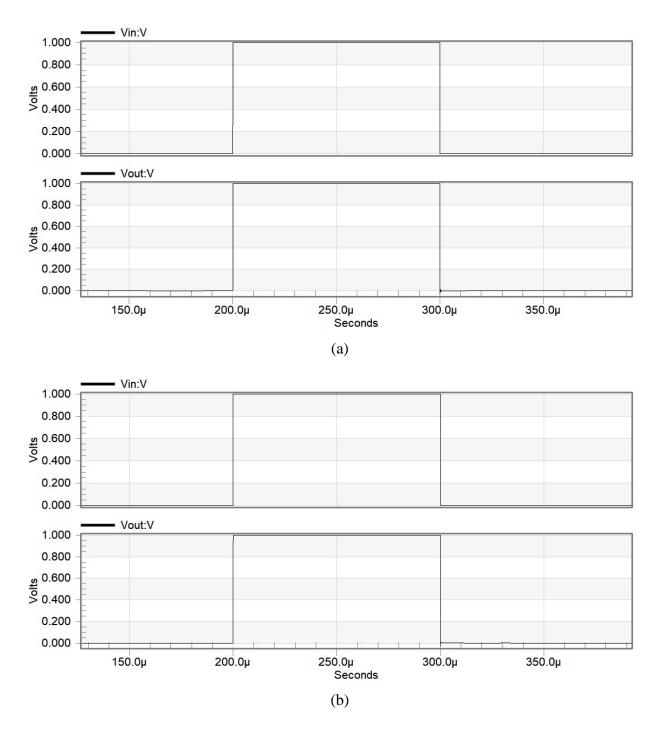

| Fig. 6.5 Transient response of proposed amplifier 10 (a) at 20 pF load (b) at 30 pF load             |

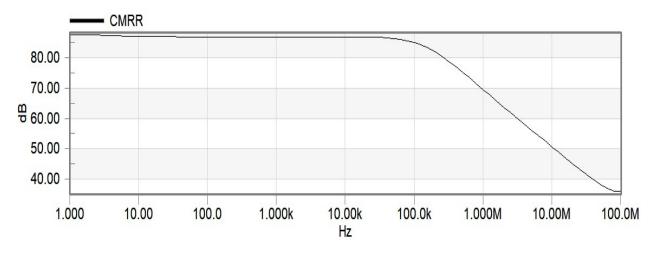

| Fig. 6.6 Frequency response of CMRR for proposed amplifier 10 (a) at 20 pF load (b) at 30 pF load    |

| Fig. 6.7 Frequency response of PSRR for proposed amplifier 10 (a) at 20 pF load (b) at 30 pF load131 |

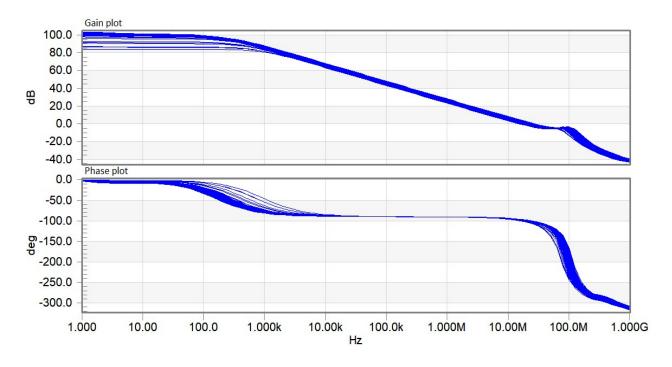

| Fig. 6.8 Corner analysis of proposed amplifier 10 (a) at 20 pF load (b) at 30 pF load133                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 6.9 Impact of supply voltage variations on proposed amplifier 10 (a) at 20 pF load (b) at 30 pF load                                               |

| Fig. 6.10 Monte-Carlo simulation for frequency response of proposed amplifier 10 (a) at 20 pF load (b) at 30 pF load against V <sub>DD</sub> variations |

| Fig. 6.11 Block diagram of proposed amplifier 11136                                                                                                     |

| Fig. 6.12 Transistor level implementation of proposed amplifier 11137                                                                                   |

| Fig. 6.13 Small signal model of proposed amplifier 11138                                                                                                |

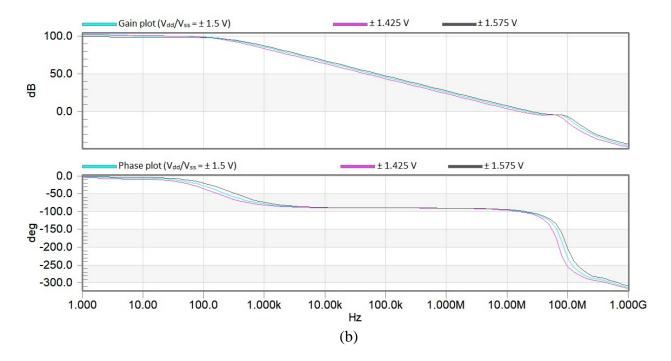

| Fig. 6.14 Frequency response of proposed amplifier 11 (a) at 20 pF load (b) at 30 pF load                                                               |

| Fig. 6.15 Transient response of proposed amplifier 11 (a) at 20 pF load (b) at 30 pF load                                                               |

| Fig. 6.16 Frequency response of CMRR of proposed amplifier 11 (a) at 20 pF load (b) at 30 pF load                                                       |

| Fig. 6.17 Frequency response of PSRR of proposed amplifier 11 (a) at 20 pF load (b) at 30 pF load                                                       |

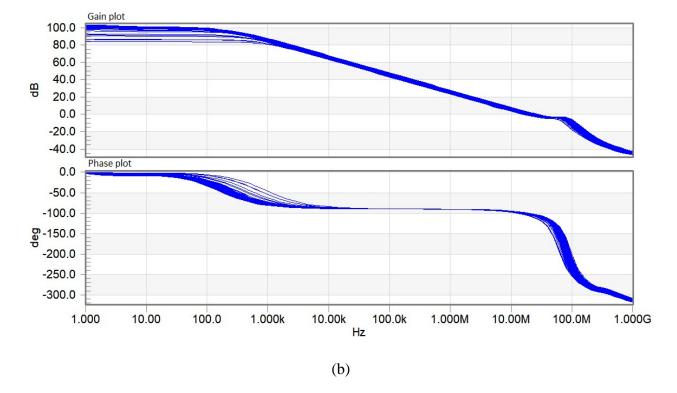

| Fig. 6.18 Corner analysis of proposed amplifier 11 (a) at 20 pF load (b) at 30 pF load145                                                               |

| Fig. 6.19 Impact of supply voltage variations on proposed amplifier 11 (a) at 20 pF load (b) at 30 pF load146                                           |

| Fig. 6.20 Monte-Carlo simulation for frequency response of proposed amplifier 11 (a) at 20 pF load (b) at 30 pF load against V <sub>DD</sub> variations |

# LIST OF TABLES

| Table 3.1 Design parameters of proposed amplifier 140                                   |

|-----------------------------------------------------------------------------------------|

| Table 3.2 Summary of simulation results at different process corners and supply voltage |

| variation for proposed amplifier 144                                                    |

| Table 3.3: Performance comparison of proposed amplifier 1 with its counterparts46       |

| Table 4.1 Design parameters of proposed amplifier 2                                     |

| Table 4.2 Summary of simulation results at different process corners and supply voltage |

| variation for proposed amplifier 2                                                      |

| Table 4.3 Design parameters of proposed amplifier 3                                     |

| Table 4.4 Summary of simulation results at different process corners and supply voltage |

| variation for proposed amplifier 365                                                    |

| Table 4.5 Design parameters of proposed amplifier 4                                     |

| Table 4.6 Summary of simulation results at different process corners and supply voltage |

| variation for proposed amplifier 473                                                    |

| Table 4.7 Design parameters of proposed amplifier 5                                     |

| Table 4.8 Summary of simulation results at different process corners and supply voltage |

| variation for proposed amplifier 5                                                      |

| Table 4.9: Performance comparison of proposed amplifiers 2-5 with their                 |

| counterparts                                                                            |

| Table 5.1 Design parameters of proposed amplifier 6                                     |

| Table 5.2 Summary of simulation results at different process corners and supply voltage |

| variation for proposed amplifier 695                                                    |

| Table 5.3 Design parameters of proposed amplifier 7                                     |

| Table 5.4 Summary of simulation results at different process corners and supply voltage                                   |

|---------------------------------------------------------------------------------------------------------------------------|

| variation for proposed amplifier 7103                                                                                     |

| Table 5.5 Design parameters of proposed amplifier 8107                                                                    |

| Table 5.6 Summary of simulation results at different process corners and supply voltagevariation for proposed amplifier 8 |

| Table 5.7 Design parameters of proposed amplifier 9115                                                                    |

| Table 5.8 Summary of simulation results at different process corners and supply voltagevariation for proposed amplifier 9 |

| Table 5.9: Performance comparison of proposed amplifiers 6-9 with their                                                   |

| counterparts                                                                                                              |

| Table 6.1 Design parameters of proposed amplifier 10                                                                      |

| Table 6.2 Summary of simulation results at different process corners and supply voltage                                   |

| variation for proposed amplifier 10                                                                                       |

| Table 6.3 Design parameters of proposed amplifier 11                                                                      |

| Table 6.4 Summary of simulation results at different process corners and supply voltage                                   |

| variation for proposed amplifier 11146                                                                                    |

| Table 6.5: Performance comparison of proposed amplifiers 10-11 with their                                                 |

| counterparts148                                                                                                           |

# Chapter 1 Introduction

## **1.1 Motivation**

The amplifiers are essential building blocks of cutting-edge integrated systems and are used in reference circuits, data converters, and linear regulators. Further, it is imperative to use amplifiers as front end in the applications where data sensed from the environment is to be processed. The data so sensed is very small in magnitude and need to be amplified before it can be processed. The amplifier design has become increasingly more challenging with the scaling down of the feature size and supply voltages. With a reduction in channel length, the unity gain bandwidth of the amplifier improves, whereas the open loop gain deteriorates. Therefore, it becomes difficult to achieve large gain and wide bandwidth using single stage amplifiers in sub-micron technologies, pushing researchers to switch to an alternative route to multistage designs.

## **1.2 Multistage Amplifiers**

Multistage amplifiers rely on cascading of gain stages for improving the gain. In addition to providing gain, the input stage is usually required to provide a high input resistance in order to avoid loss of signal level when the amplifier is fed from a high resistance source and to combat the effect of noise. To achieve it, a differential amplifier is used in the input stage, which must provide large common mode rejection. The function of the middle stages of a multistage amplifier is to provide the bulk of voltage gain. In addition, the middle stages provide other functions, such as the conversion of the signal from differential mode to single-ended mode and the shifting of the DC level of the signal in order to allow the output signal to swing both positive and negative. Finally, the main function of the last or output stage of an amplifier is to provide a low output resistance in order to avoid loss of gain. Also, the output stage should be able to supply the current required by the load in an efficient manner [1].

Moreover, multistage OTA gives high DC gain, but it also gives high number of comparable poles and zeros, which exhibits low phase margin, leading to stability issues.

The multiple-pole nature of the multistage amplifiers causes closed loop stability issues. It is pertinent to mention that the phase crossover point is moved closer to the origin as a result of further negative phase shift caused by a zero in the right half plane. According to Bode approximations, the zero pushes the gain crossover away from the origin by slowing down the magnitude drop. Consequently, the stability is reduced considerably. Necessary measures are required so that the gain crossover point moves towards the origin. To achieve this, the dominant pole frequency may simply be lowered by increasing the load capacitance, but due to the presence of the non-dominant pole, which is near the dominant pole, the gain cross over point moves away from the origin, which is a big threat to stability [2-3]. To ensure closed loop stability, frequency compensation is mandatory. Various frequency compensation techniques are proposed in the literature for multistage amplifiers.

## **1.3 Frequency Compensation Technique**

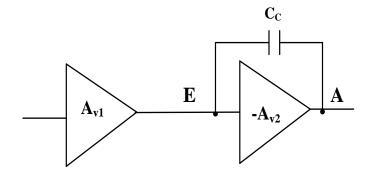

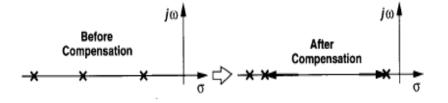

A two-stage amplifier with Miller compensation [2] is depicted in Fig. 1.1, which uses a compensation capacitor  $C_C$ . Here, the voltage gains of the first stage and second stage are denoted by  $A_{v1}$  and  $A_{v2}$ . The idea of Miller compensation is to move the low frequency pole (dominant pole) towards the origin and the other pole away from the origin. It makes the gain cross over frequency less than the phase crossover frequency, which enhances the stability of the amplifier. The compensation capacitor  $C_c$  creates a large capacitance at the input of the second stage (node E), equal to  $(1 + A_{v2}) C_c$ . It effectively moves the dominant pole to

$\frac{1}{R_{out1}\left[C_E + (1 + A_{v2}) C_C\right]}, \text{ where } C_E \text{ denotes the capacitance at node E before } C_c \text{ is added},$

and  $R_{out1}$  is the output resistance of the first stage. As a result, a low frequency pole can be established with a moderate capacitor value, saving considerable chip area. In addition to lowering the required capacitor value, Miller compensation moves the output pole away from the origin. This effect is called pole splitting (Fig. 1.2). Since the Miller loop should exhibit a negative gain for stability, therefore, the second stage is the inverting amplifier in order to create favorable condition for Miller's effect.

Fig. 1.1 Miller compensation of two-stage op amp

Fig. 1.2 Pole Splitting as a result of Miller compensation

## 1.4 Literature review of frequency compensation techniques

Since single stage amplifiers do not provide sufficient gain for many applications, it is imperative to use multistage amplifiers. Due to high number of comparable poles and zeros, multistage amplifiers need to be compensated for stability. In the literature, various frequency compensation techniques are proposed for multistage amplifiers for different capacitive loads. A brief description of frequency compensation techniques for two stage & three stage amplifiers is given below.

#### Frequency Compensation Techniques for Two Stage Amplifier:

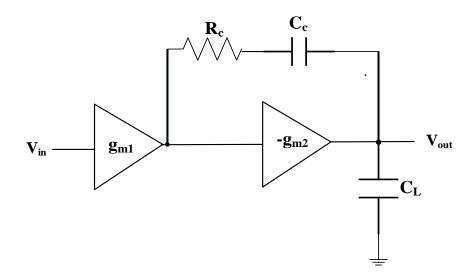

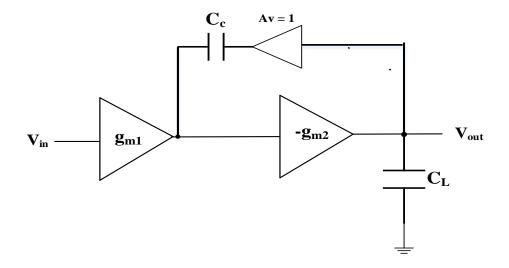

The implementation of a simple Miller compensation scheme is accountable for a RHP zero due to the forward path to the output through the compensation capacitor. This RHP zero degrades the stability. In order to address the RHP zero problem, frequency compensation using nulling resistor, voltage buffer and current buffer are proposed in the literature [4-5]. Ref. [4] uses a simple Miller compensation with a resistor  $R_c$  along with a capacitor  $C_c$  to break

the forward path (Fig. 1.3). Additionally, the block diagram of a two-stage amplifier that improves the GBW and PM by using the voltage buffer and current buffer in the Miller compensation loop is displayed in Figs. 1.4–1.5 [4-5].

Fig. 1.3 Miller Compensation with Nulling Resistor

Fig. 1.4 Miller Compensation with Voltage Buffer

Fig. 1.5 Miller Compensation with Current Buffer

Moreover, voltage buffer compensation using flipped voltage follower (FVF) and folded flipped voltage follower (FFVF) improves the performance of two stage amplifier in terms of GBW [6]. Frequency compensation using negative capacitance and a flipped voltage follower is proposed, which improves GBW and PM [7]. In Ref. [7], negative capacitance reduces the parasitic capacitance of a particular stage, which enhances GBW. Further, the pole-zero cancellation is achieved with the help of FVF, which improves phase margin. Ref. [8] offers feed forward compensation in two stage amplifiers, which creates a LHP zero, resulting in higher GBW and PM.

Frequency compensation using positive feedback, positive capacitive feedback, and positive resistive-capacitive feedback gives an extra LHP zero to cancel a pole, which improves GBW [9-11]. Furthermore, in the positive feedback compensation technique, the amplifier's stability is less sensitive to the capacitive load. Compared to Miller compensation with the same compensation capacitance, pseudo cascode compensation improves GBW and large signal settling response [12]. Moreover, a bulk-biasing technique has been employed in [12] to increase the two stage op-amp's DC gain without changing the output voltage swing and without requiring more power. Gain-boosting and indirect current feedback frequency compensation performed by regulated cascode amplifier is suggested in [13], which enhances the low frequency gain and phase margin with a reduction in settling time. Further, one of the low voltage lower technique (LVLP), Quasi-Floating Gate MOSFET (QFGMOS) is employed

in [13] to reduce the power supply requirement. In Ref. [14], a hybrid class A/AB two stage OTA has been presented, which includes a folded cascode in the first stage and active current mirrors in the second stage in order to increase the speed of the amplifier. In order to achieve class-AB operation, the Class AB-AB Miller op-amp described in [15] uses a transconductance boosting technique based on local common-mode feedback. This leads to improved open-loop gain, GBW, and slew rate without appreciably raising the quiescent power consumption. Further, Miller and phase-lead compensation provide the stability over wide range of capacitive loads in [15].

The compensation capacitor is simply reconnected in [16] to enhance the bandwidth without requiring additional power dissipation. Moreover, improvements in power-supply rejection ratio (PSRR) and slew rate are obtained in [16]. A two-stage fully differential CMOS amplifier includes inverters as input structures with self-biasing technique is put forward in [17], which results in high energy efficiency and low power consumption. Embedded capacitor multiplier frequency compensation technique is suggested in [18] to improve the stability and slew rate with lesser area and power consumption.

Since the gain requirement is high for many applications, such a high gain has not been achieved by two stage amplifiers in the literature. So, the need for three stage amplifiers arises.

#### **Frequency Compensation Techniques for Three Stage Amplifier:**

There are two conventional frequency compensation techniques for three stage amplifiers in the literature. One of the conventional frequency compensation technique is Nested Miller Compensation (NMC) [19]. Figure 1.6 dispalys the block diagram of NMC. It uses simple Miller compensation in both of its inner compensation loop and outer compensation loop with the help of two compensation capacitors. However, both the compensation capacitors load the output node, which results in a reduction in bandwidth. Further, NMC suffers with the problem of RHP zero. To address the RHP zero problem of NMC, a resistor R<sub>c</sub> is connected in series with compensation capacitors, which is used to break the feed forward path [20]. It is shown in Fig. 1.7. It improves the phase margin by cancelling the RHP zero while keeping the LHP zero, thus resulting in higher stability of the circuit. Using an extra feed forward path, Multipath NMC (MNMC) increases the bandwidth of the original NMC structure [21]. Figure 1.8 displays the block diagram of MNMC. In contrast to the NMC structure, it provides an extra LHP zero.

This LHP zero can be used to cancel out the second non-dominant pole of the amplifier, which enhances the gain-bandwidth product of the amplifier.

Fig. 1.6 Nested Miller Compensation

Fig. 1.7 NMC with Nulling Resistor

Fig. 1.8 Multipath NMC

Further, Nested Transconductance-Capacitance Compensation (NGCC) is proposed, which offers better GBW than NMC [22]. Moreover, NMC with feed forward stage (NMCF) and damping-factor-control frequency compensation (DFCFC) are employed to improve the frequency response and transient response [23]. Ref. [24] adds a Nested feed-forward transconductance stage and a nulling Resistor to NMC, which enhances GBW, phase margin and slew rate of three stage amplifier.

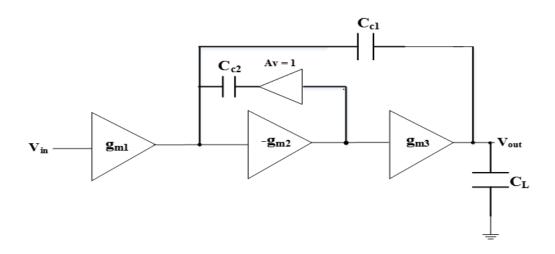

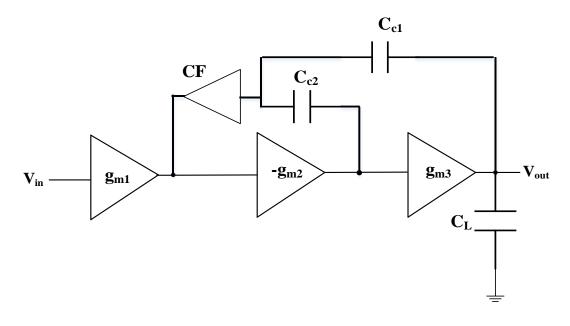

Figure 1.9 shows the block diagram of another conventional technique, Reversed Nested Miller Compensation (RNMC) [25]. OTA based on RNMC shows higher GBW and better performance compared to NMC due to the independence of inner compensation capacitor from output. Further, RNMC has RHP zero in its transfer function. This RHP zero degrades the stability of the amplifier. To cancel this RHP zero, various techniques have been proposed by the authors in the literature, such as RNMC with nulling resistor, voltage follower and current follower [25], and are shown in Figs. 1.10-1.12. These techniques break the feed forward path, while maintaining the LHP zero and shift the RHP zero to a very high frequency, which results in higher phase margin of the circuit. Further, Ref. [26] results in double pole-zero cancellation by using a resistor in the outer compensation loop and a voltage buffer in the inner

compensation loop of RNMC, which further enhances the phase margin (Fig. 1.13). A feed forward path is added to improve the transient response in [26].

Fig. 1.9 Reversed Nested Miller Compensation

Fig. 1.10 RNMC with Nulling Resistor

Fig. 1.11 RNMC with Voltage Buffer

Fig. 1.12 RNMC with Current Buffer

Fig. 1.13 RNMC with Voltage Buffer and Resistor

Reversed Active Feedback Frequency Compensation (RAFFC) employs the current buffer in the outer compensation loop [27]. Figure 1.14 displays the block diagram of RAFFC. In RAFFC, the removal of zero is more reliable because it does not demand matching between resistance and transconductances. Further, the feed forward path has been added to enhance the large signal response.

Fig. 1.14 Reversed Active Feedback Frequency Compensation

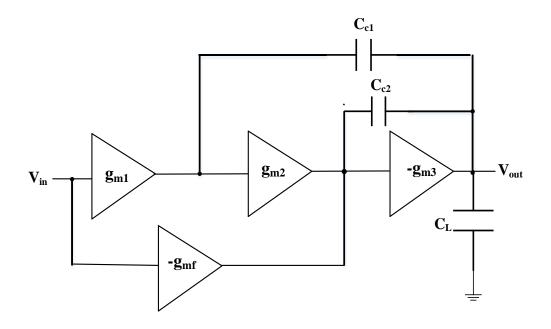

Many other frequency compensation techniques using RNMC have been proposed for high capacitive load in the literature. Ref. [28] utilizes a current subtractor in the common node of Miller capacitors of RNMC to remove the feed forward path and RHP zero. RNMC with a current comparator in the feedback path is presented in [29] to achieve higher GBW and phase margin. A Second generation Differential Current Conveyor (DCCII) in the feedback path from output of the second and third stage to the output of first stage is suggested in [30] to remove the feed forward path and RHP zero, resulting in enhanced GBW and PM. Further, by using a single compensation capacitor and differential amplifier in third stage, adverse effects of feedback and feed forward paths are reduced simultaneously [31]. So, it removes the need of using voltage or current buffer. Further, [28-31] suffers with low figure of merits. In Ref. [32], analytical formulation of various RNMC based topologies has been elucidated. Moreover, [32] compares RNMC based topologies on the basis of figure of merits, which shows that RNMC with feed forward, voltage buffer, and two resistors offers a better FOM than other RNMC topologies. Apart from these, a dual complex pole-zero cancellation frequency compensation scheme employing one pair of complex zeros to cancel one pair of complex poles is suggested in [33] to improve bandwidth and phase margin. Further, a current buffer along with Miller capacitor is connected between output of first and third stage to improve the figure of merits [34]. Moreover, [34] utilizes the feature of an active LHP zero circuit to enhance the frequency response. Embedded capacitor-multiplier compensation and active parallel compensation are put forward in [35] to enhance the area efficiency. Further, GBW is improved due to transconductance boosting technique in [35]. Negative capacitance circuit is utilized in [36] to minimize the parasitics capacitance of the critical node, which moves the non-dominant pole to higher frequency. It results in higher GBW. However, [34-36] endures low FOM. The local feedback enhanced compensation scheme is suggested in [37] for improving GBW. Some other techniques used for this purpose are - dual active capacitive feedback compensation under the variation of the load capacitance [38], cross feed forward cascode compensation [39], and active single Miller capacitor compensation with inner halffeed forward stage [40]. A slew rate enhancer circuit is also used in [40] to improve large signal performance. Damping-Factor-Control frequency compensation presented in [41] enhances the GBW and improves the transient response of amplifier for large capacitive load. Active-Feedback frequency compensation is put forward in [42], which simultaneously

enhances gain and GBW. Further stability and transient response are also improved due to the presence of LHP zero. An AC Boosting compensation scheme presented in [43] adds ac path to the internal stage of three stage amplifier to improve GBW and slew rate. Ref. [44] uses a serial R-C branch and current buffer to enhance the frequency response of three stage amplifier. In Ref. [45], the frequency of non-dominant complex pole is boosted using cascode Miller compensation. Moreover, the step response is enhanced using a feed forward transconductance stage and the stability is improved with the help of LHP zero. Hybrid active Miller enhancement compensation is used in [46] to increase GBW and PM. Additionally, [46] employs a slew rate enhancement method to further improve the transient response. Single Miller capacitor frequency compensation techniques are analytically compared in [47]. Ref. [48] offers multistage amplifiers, which can drive a wide range of capacitive loads using lowfrequency zeros. Further, [49] suggests a three stage amplifier with a Miller capacitor and a small feed forward capacitor to improve the stability of the amplifier for a wide range of load capacitors. The frequency compensation using cascade zero is employed in [50] to enhance the gain of three stage amplifier. Moreover, [51] presents folded cascode OTA at lower supply voltage by using current driven bulk technique, while design techniques to operate OTA at low supply voltage are proposed in [52]. A feed forward transconductance stage and indirect compensation capacitor combined with a resistor are suggested in [53] to improve the stability of the amplifier. In Ref. [54], the complex-pole frequency of the amplifier is extended by eliminating the inner Miller capacitor and utilizing cascode Miller compensation in the outer compensation loop, which results in higher GBW. Further, an optimized trade-off between the frequency and the quality factor of the complex pole is achieved by using a local impedance attenuation block in [54]. In Ref. [55], second-stage bypass compensation scheme for three stage amplifier is presented, in which the second stage is bypassed using a capacitive feed forward path, thus reducing the amplifier to a two-stage. Further, unity closed loop gain stability of [55] is ensured using a conventional two-stage compensation technique.

Ref. [56] employs a nonlinear current mirror in the input stage to realize class AB operation, which enhances the slew rate of the amplifier. Auxiliary feedback is used in [57] to reduce the total compensation capacitance, resulting in higher GBW and slew rate. A three gain stage topology with class AB output stage is put forward in [58] to improve the driving capability of the amplifier. Further, Reversed Nested Indirect Compensated (RNIC) topology is

employed in [59], which reduces the settling time of the amplifier. Ref. [60] increases the slew rate of the amplifier by providing more current to the output node while avoiding an excessively high increase in power consumption. In Ref. [61], the transconductance stage in the internal feedback loop of NMC is utilized to improve GBW and the stability of the amplifier. Further, the feed forward stage in [61] improves the large signal performance of the amplifier. A single Miller capacitor with a resistor and feed forward path is introduced in [62] to improve the frequency response and transient response. Moreover, [63] employs a single Miller capacitor with current buffer and slew rate enhancer circuit, which improves the figure of merits of three stage amplifier. In Ref. [64], GBW is improved by using an attenuator in the path of Miller compensation capacitor. Moreover, a feed forward path is employed to deal with the LHP zero in [64]. It cancels out the first non-dominant pole. Another feed forward path in [64] forms push-pull output stage, which enhances the transient response. Further, sensitivity and robustness analysis of different three stage amplifiers are performed in [65].

Ref. [66] utilizes one of the low voltage low power (LVLP) technique, called Floating Gate MOS (FGMOS), to reduce the power supply requirement of the three stage amplifier. It reduces the power consumed by the circuit. Further in [66], an active LHP zero circuit and a resistor are used to improve GBW.

Further, following Figure of Merits (FOMs) are used to compare the results obtained from different frequency compensation techniques [43]. Eqs. 1.1-1.4 describe the four figures of merits.

$$FOM_{S} = \frac{GBW \times C_{L}}{Power} \left(\frac{Hz \times F}{W}\right)$$

(1.1)

$$FOM_{L} = \frac{SR \times C_{L}}{Power} (\frac{1}{V})$$

(1.2)

$$IFOM_{S} = \frac{GBW \times C_{L}}{I_{B}} \left(\frac{Hz \times F}{A}\right)$$

(1.3)

$$IFOM_{L} = \frac{SR \times C_{L}}{I_{B}}$$

(1.4)

In the above equations, index S and L denote the small-signal mode and large-signal mode, respectively.  $I_B$  is the total bias current. A higher value of the figure of merits is desirable for any amplifier.

## **1.5 Research gaps**

There is a range of performance metrices to be taken into account while designing multistage amplifiers, such as GBW, stability, power consumption, DC gain, noise, CMRR, slew rate, etc. It is desirable to have high gain, large GBW, optimum phase margin, high slew rate, high CMRR and less power consumption for wide range of capacitive loads for any multistage amplifier. Following are the observations from the literature review:

- (i) There are many applications which require the ability to drive large capacitive loads, e.g. low dropout regulators (LDO), peak detectors, MEMS devices, LCD drivers etc. [63]. In the literature, various multistage amplifiers are proposed for high capacitive load, however, GBW is limited for high capacitive load. Also, there is a scope for improvement in GBW for multistage amplifiers for low and moderate value of capacitive load.

- (ii) Slew rate defines how quickly the output changes with time. It should be high for any amplifier. In the literature, slew rate is limited for multistage amplifiers at high capacitive load. There is a scope for further improvement in slew rate for multistage amplifiers to increase the speed of the circuit for different capacitive loads.

- (iii) Figure of merits (FOM) are used to compare the results obtained from different frequency compensation techniques. It should be high for any multistage amplifier. In the literature, figure of merits (FOM) are limited for multistage amplifier. There is a scope of further improvement in figure of merits for multistage amplifier.

- (iv) The use of Low-Voltage Low-Power (LVLP) techniques such as Bulk Driven technique, Dynamic Threshold Voltage MOSFET (DTMOS), Floating Gate MOS (FGMOS), and Quasi Floating gate MOS (QFGMOS) is limited in the literature. These techniques can be further explored for three stage amplifiers.

#### **1.6 Research objectives**

On the basis of the research gaps, the following objectives are formulated:

- (i) Develop compensation technique for better frequency response of multistage amplifiers.

- (ii) Design of multistage amplifiers with improved transient response and/or figure of merits.

(iii) Apply low voltage/low power techniques to improve performance of multistage amplifiers.

### **1.7 Key contributions**

This thesis discusses different frequency compensation techniques applied in a three stage amplifier to enhance the performance of the amplifier. The key contributions are listed below.

- (i) A Flipped Voltage Follower (FVF) is utilized in the inner loop of Reversed Nested Miller Compensation (RNMC) to address the RHP zero problem. This compensation technique enhances the GBW. Moreover, the push pull output stage is used to enhance the slew rate.

- (ii) The frequency response of three stage amplifier is improved with the help of Folded Flipped Voltage Follower (FFVF) in the inner loop of RNMC. Further, the transient response is enhanced using feed forward path.

- (iii) RNMC makes use of FFVF and resistor in the inner and outer compensation loop, which results in double pole-zero cancellation. It improves the frequency response of the amplifier. Additionally, the transient response gets better due to feed forward path.

- (iv) In order to refine the frequency response and transient response of three stage amplifier, Dynamic Threshold Voltage MOSFET (DTMOS) and self cascode structure are employed along with FFVF with resistor and feed forward path.

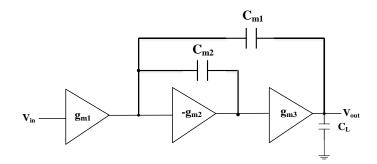

- (v) An active LHP zero circuit is used to cancel the parasitic pole of the second stage to improve GBW of the amplifier. Moreover, a self cascode structure in the input stage and a Miller capacitor with resistor make the frequency response better. Additionally, a self cascode structure with DTMOS in the input stage and a Miller capacitor with resistor further enhance the GBW.

- (vi) Modified self cascode with active LHP zero circuit and a single Miller capacitor with resistor improve the GBW of three stage amplifier.

(vii) Enhanced frequency compensation of a three stage amplifier is achieved by employing class AB FVF, a slew rate enhancer circuit, and push pull output stage in RNMC.

### **1.8 Organization of the thesis**

This research focuses on enhanced frequency compensation of three stage amplifier. This thesis is organized into seven chapters, which are briefly explained below.

**Chapter 1:** This chapter outlines multistage amplifiers and frequency compensation techniques. Moreover, the frequency compensation techniques available in the literature are reviewed and classified on the basis of performance parameters. After the review of available compensation techniques, research gaps are identified, and research objectives are formulated.

**Chapter 2:** This chapter describes the different frequency compensation techniques used in the proposed work, such as Reversed Nested Miller Compensation (RNMC), Flipped Voltage Follower (FVF), class AB FVF, folded FVF, push pull output stage, slew rate enhancer circuit, self-cascode structure, Dynamic Threshold Voltage MOSFET (DTMOS), self-cascode with DTMOS, modified self-cascode, and active LHP zero circuit. The significance of these techniques to enhance the performance of the amplifier is discussed throughout the chapter.

**Chapter 3:** Frequency compensation using FVF along with one of the conventional compensation techniques, RNMC, is elaborated in this chapter. FVF is used to break the forward path of RNMC to resolve the RHP zero issue. This technique also utilizes the feed forward path to improve the transient response. Small signal analysis of the amplifier has been performed in this chapter. Moreover, simulation results are discussed to verify the performance of the amplifier.

**Chapter 4:** This chapter proposes the amplifiers, which utilize folded FVF (FFVF) to break the forward path of RNMC to solve the RHP zero problem. Moreover, a resistor along with FFVF has been exploited in the compensation loops of RNMC, which results in double polezero cancellation. This technique offers better frequency response. Further, DTMOS and self cascode structures are employed in the input stage of the amplifier to improve GBW. Additionally, the feed forward path makes the transient response better. Moreover, this chapter examines the small signal analysis and simulation results of the proposed amplifiers.

**Chapter 5:** This chapter presents the frequency compensation of three stage amplifiers using an active LHP zero circuit to cancel the parasitic pole of second stage, which improves GBW. Additionally, self cascode structure, self cascode with DTMOS, modified self cascode and a Miller capacitor with resistor enhance the frequency response of the proposed amplifiers. Small signal analysis of the circuits is performed, and simulation results are shown to verify the effectiveness of the proposed circuits.

**Chapter 6:** Frequency compensation using class AB FVF, along with RNMC, is presented in this chapter. Class AB FVF is used to break the forward path of RNMC to address the RHP zero issue. This technique also utilizes the feed forward path to enhance the transient response. Further, a slew rate enhancer circuit is employed along with class AB FVF to improve the large signal response. Small signal analysis of the amplifiers has been performed in this chapter. Moreover, simulation results are discussed to verify the performance of the amplifiers.

**Chapter 7:** It concludes all the proposed three stage amplifiers to improve the frequency response and transient response. All simulations are performed using TSMC 0.18  $\mu$ m CMOS process in Tanner tool to examine the functionality and performance of the proposed amplifiers. It is illustrated that the simulation results of the proposed amplifiers match up with the theoretical results. Additionally, this chapter also suggests possible future work.

# **Chapter 2**

# Various frequency compensation techniques used in proposed amplifiers

### **2.1 Introduction**

The improvement in the performance of amplifiers is required continuously due to the rapid advancement in technology and the scaling down of the supply voltage. In this regard, single stage amplifiers suffer from low gain and low bandwidth. Therefore, multistage amplifiers become mandatory. Further, multistage amplifiers come with frequency compensation to address the stability problem. Researchers have proposed various frequency compensation techniques over the last few decades. However, there is still scope for improving the frequency compensation techniques. In this thesis, eleven three stage amplifiers are proposed with enhanced performance. This chapter briefly describes the techniques employed in the proposed amplifiers to improve the performance of the amplifiers The organization of this chapter is as follows: Section 2.2 describes one of the conventional frequency compensation techniques, Reversed Nested Miller Compensation (RNMC), while Sections 2.3 to 2.5 include Flipped Voltage Follower (FVF), class AB FVF, and folded FVF. Moreover, the push pull output stage and slew rate enhancer circuit are elucidated in Sections 2.6 and 2.7, respectively. Dynamic Threshold Voltage MOSFET (DTMOS), self cascode structure, self cascode with DTMOS, modified self cascode, and active LHP zero circuit are detailed in Sections 2.8 to 2.12. Section 2.13 provides the summary of the chapter.

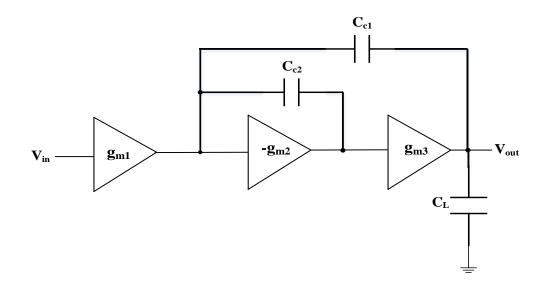

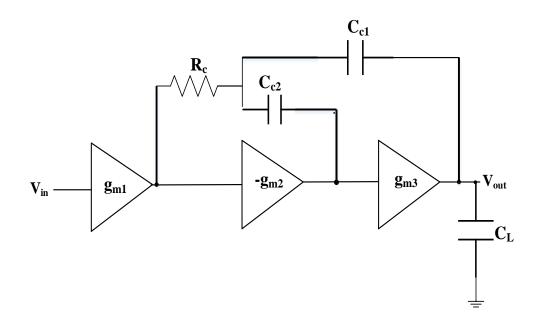

### 2.2 Reversed Nested Miller Compensation (RNMC) [25]

The main difficulty in the design of multistage amplifiers is performing frequency compensation due to increased high impedance nodes. Also, it is required to fulfill the stability criterion for a multistage amplifier with adequate GBW and phase margin of the amplifier. To deal with it, RNMC technique (shown in Fig. 2.1) can be used due to its independency of the inner compensation capacitor from the output. It helps in improving the GBW of the amplifier. This technique is widely used due to its simplicity of design and no extra power consumption. However, it has RHP zero in its transfer function, which degrades the phase margin.

Fig. 2.1 Reversed nested Miller compensation technique

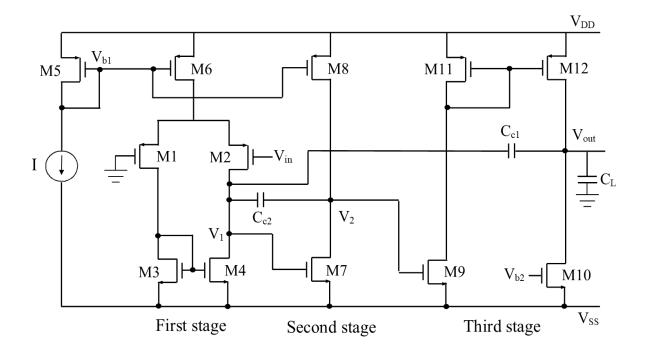

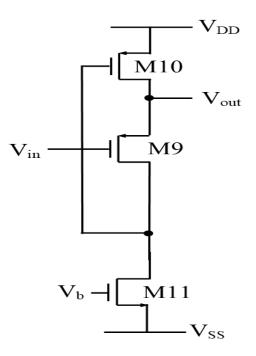

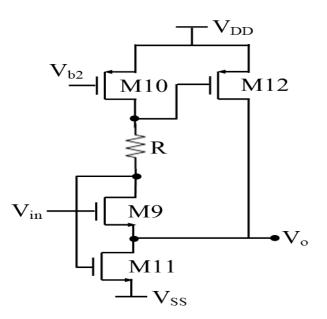

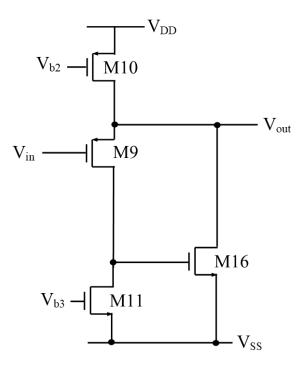

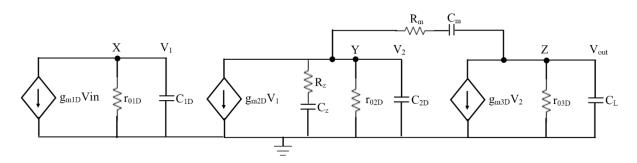

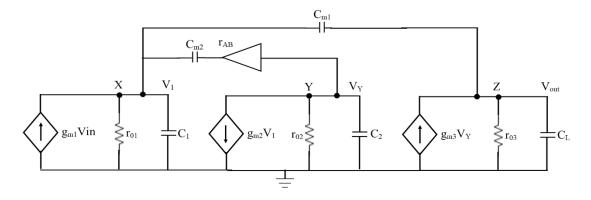

Figure 2.2 shows the circuit diagram of a three stage amplifier with RNMC. In Fig. 2.2, transistors M1-M4 and M6 form the differential amplifier for the first stage. Transistors M7-M8 form the second stage, which is a common source amplifier; followed by a non-inverting stage, which constitutes the third stage (M9-M12). Apart from this, two Miller capacitors,  $C_{c1}$  and  $C_{c2}$ , are connected in the feedback loop.

Fig. 2.2 Circuit Diagram of three stage amplifier with RNMC

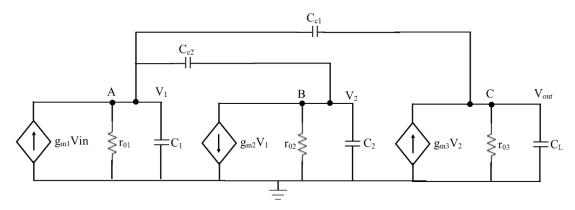

A small signal equivalent circuit of a three stage amplifier using RNMC is described in Fig. 2.3. In this figure, the input stage has output resistance  $r_{o1}$ , output capacitance  $C_{1}$ , transconductance  $g_{m1}$ , and output voltage  $V_1$ . The second stage has output resistance, output

capacitance, and output voltage of  $r_{o2}$ ,  $C_2$ , and  $V_2$  with transconductance  $g_{m2}$ . Final stage possesses output resistance  $r_{o3}$ , transconductance  $g_{m3}$ , total equivalent load capacitance  $C_L$ , and output voltage  $V_{out}$ . Apart from this, two Miller capacitors,  $C_{c1}$  and  $C_{c2}$ , are connected in the feedback loop. The compensation capacitor  $C_{c1}$  is connected between the output of the third stage and the first stage, while  $C_{c2}$  is connected between the output of the second stage and the first stage.

Fig. 2.3 Small signal equivalent circuit of RNMC

The transfer function of RNMC can be obtained by analyzing the small signal equivalent circuit. To simplify the calculations, following assumptions are made,

$$g_{m1}r_{o1}, g_{m2}r_{o2}, g_{m3}r_{o3} \gg 1$$

(2.1)

$$C_L, C_{c1}, C_{c2} \gg C_1, C_2$$

(2.2)

The following equations are obtained by applying nodal analysis at nodes A, B, and C in Fig. 2.3,

$$g_{m1}V_{in} - V_1(\frac{1}{r_{o1}} + sC_1) - (V_1 - V_2)sC_{c2} - (V_1 - V_{out})sC_{c1} = 0$$

(2.3)

$$(V_1 - V_2)sC_{c2} - g_{m2}V_1 - V_2(\frac{1}{r_{o2}} + sC_2) = 0$$

(2.4)

$$g_{m3}V_2 + (V_1 - V_{out}) s C_{c1} - V_{out} (\frac{1}{r_{o3}} + sC_L) = 0$$

(2.5)