# Studies on Technology Computer Aided Design of Double Metal Negative Capacitance FET using DFT and Machine Learning Approach for Analog/Sensing Applications

A THESIS to be Submitted by

Yash Pathak

### 2K19/PHDAP/505

for the award of the degree of

### Doctor of Philosophy

in

Physics

Under the Supervision of

Prof. Rishu Chaujar and Prof. Bansi Dhar Malhotra

Department of Applied Physics DELHI TECHNOLOGICAL UNIVERSITY BAWANA ROAD, NEW DELHI-110042 INDIA September, 2024

© Delhi Technological University–2024 All rights reserved.

Dedicated

to My Loving Family

# DECLARATION

I declare that the research work presented in this thesis titled "Studies on Technology Computer Aided Design of Double Metal Negative Capacitance FET using DFT and Machine Learning Approach for Analog/Sensing Applications" for the attainment of the degree of *Doctor of Philosophy in Physics* has been conducted by me, under the guidance of *Prof. Rishu Chaujar* from the Department of Applied Physics, and co-guidance of *Prof. Bansi Dhar Malhotra* from the Department of Biotechnology, Delhi Technological University, Delhi, India. This work has not been previously submitted, either partially or in its entirety, to any other academic institution for any degree or diploma.

I declare that this thesis reflects my ideas expressed in my own words. Wherever the ideas or words of others have been incorporated, appropriate citation and referencing have been provided to acknowledge the sources. I also confirm that I have upheld the principles of academic honesty and integrity and that I have not misrepresented, fabricated, or falsified any information, data, fact, or source in the content of my submission.

> Mr. Yash Pathak Enrollment No. 2K19/PHDAP/505 Department of Applied Physics Delhi Technological University

# CERTIFICATE

This is to certify that the thesis titled Studies on Technology Computer Aided Design of Double Metal Negative Capacitance FET using DFT and Machine Learning Approach for Analog/Sensing Applications, submitted by Mr. Yash Pathak, to the Delhi Technological University, Delhi, for the award of the degree of Doctor of Philosophy, is a bonafide record of the research work done by him under our supervision and guidance. The contents of this thesis, in full or in parts, have not been submitted to any other Institute or University for the award of any degree or diploma.

**Prof. Rishu Chaujar** Supervisor Department of Applied Physics Delhi Technological University **Prof. B. D. Malhotra** Joint-Supervisor Department of Biotechnology Delhi Technological University

**Prof. A. S. Rao** Head Department of Applied Physics Delhi Technological University

New Delhi September, 2024

### ACKNOWLEDGEMENTS

This five-year journey of my research work has been an incredible and transformative experience, filled with numerous lessons and personal growth. As I reflect upon this momentous milestone, I am overwhelmed with gratitude for the many individuals who have guided, supported, and believed in me throughout this tremendous journey. Without their unwavering assistance, completing this thesis would have been an immensely challenging task. Therefore, I would like to express my deepest appreciation and acknowledge their invaluable contributions.

I would like to express my heartfelt gratitude to my supervisor, **Prof. Rishu Chaujar**. The successful completion of this challenging academic endeavor would not have been possible without her affection, unwavering guidance, and support. Her dedication to academic excellence and enthusiasm for research have been truly inspiring. Under her guidance, I learned to embrace independence, strengthen my mental resilience, and focus on higher aspirations. Her belief in my abilities, even when I doubted myself, has been a tremendous source of motivation. She not only treated me with love and care but also strictly corrected me whenever I got sidetracked from my work, which has shaped me as a researcher and nurtured my personal growth and development. Her suggestions have been instrumental in impacting the quality and depth of my research. I am particularly grateful for her prompt assessment of my manuscripts and thesis chapters. Her punctuality has greatly facilitated the timely completion of my Ph.D. work with a substantial number of publications.

I wish to extend my appreciation to my co-supervisor, **Prof. Bansi Dhar Malhotra** from the Department of Biotechnology at Delhi Technological University (DTU), for their consistent encouragement, supportive guidance, assistance during my research endeavors and for granting me the autonomy to pursue my ideas. Their mentorship has positively influenced my academic pursuits and greatly benefited my personal and professional growth. Undoubtedly, being under their supervision has been a delightful experience for me.

I am thankful to **Prof. A. S. Rao** (DRC Chairman and HoD, Applied Physics, DTU) and **Prof. Prateek Sharma** (Vice Chancellor, DTU) for providing the necessary resources to facilitate the research activity. I further thank the experts and members of the SRC and DRC for generously dedicating their valuable time to serve on my committee and providing their invaluable support of my thesis. Also, I thank all the faculty members of the department for their helpful recommendations and advice during my Ph.D. journey. I appreciate all the care and support shown to me by the staff members of the department (especially **Suresh Ji, Krishna Ji, Babita Ji, Deepak Ji, and Naresh Ji**).

The Ph.D. journey is tough and often needs the assistance of seniors, and I consider myself extremely fortunate to have **Dr. Samriti Sharma**, **Dr. Megha Sharma**, **Dr. Bhavya Kumar** as my senior. During my most challenging days, they emerged as a ray of hope, guiding me through the darkest of times. Their willingness to freely share their expertise, helpful ideas, soft copies of documents, and presentations has been an irreplaceable resource for me. I would also like to thank Microelectronics Research Laboratory's most senior **Dr. Jaya Madan**, **Dr. Ajay Kumar**, **Dr. Rahul Pandey**, **Dr. Neha Gupta**.

I would like to express sincere gratitude towards my labmates, **Rashi Mann, Anshul, Kajal Verma, Ayushi Lamba, Shubhda Kaushik, and Shikha Singh**. Their unconditional support and understanding, have made my time in the lab truly memorable and enjoyable. I am extremely grateful to **Kajal Verma**. She has helped me in refining my research papers through her knowledge and fluent writing skills. She has been my firm supporter through thick and thin, celebrating with me in the moments of happiness and consoling me in times of sorrow. I would also like to thank **Anshul** for being there to lighten the stressful atmosphere of the lab by cracking jokes and fun talks to make the moments memorable.

I extend my heartfelt gratitude to my friends Anurag Bhandari, Dr. Surya Giri, Kunal Madaan, Monu, Dr. Kartikey khatri, Gagan Sharma, Bishan Chauhan, Puneet Pal, Ramesh Bishnoi, Dr. Ankita, Mansha Kanshal, Aneesha, Priyanka Mann, and Dristi Tomar for their consistent support and motivation. I am sincerely thankful to all the research scholars from the department. I am deeply grateful to Nanoelectronics labmates at the Department of Biotechnology, DTU, Dr. Shipra Solanki, Dr. Suveen Kumar, Dr. Niharika Gupta, Dr. Sharda, Dr. Shine. I am also thankful to Scientist Ved Varun Agarwal and Piyush, Sagar in the Department of Biomedical, NPL CSIR, Delhi.

I owe everything I am today to my father (Ashok Kumar Pathak), my mother (Rajni Pathak), my late grandfather Vishamber Dhayal Pathak, Bhudhaa Pathak, Kalichran Pathak and my grandmother Shanta Devi. Throughout my journey, my father never once deterred me from pursuing my studies and consistently served as a source of motivation. He selflessly set aside his dreams, expectations and supported me emotionally and financially, ensuring that I could pursue my ambitions without hindrance. My mother's love has been an inexhaustible wellspring of affection and support. She instilled in me a set of invaluable ethical principles, which have been an integral part of my Ph.D. journey. The impact of her teachings on my life is immeasurable, and I carry her wisdom with me as a treasured gift. The love and care I've received from my elder brother (Laxman Prasad Goswami) and younger brother (Ankit Pathak) are assets that I hold close to my heart. Beyond their love, they have selflessly gone above and beyond to fulfill my wishes, supporting me in ways that words can hardly describe. I am eternally grateful to them for their unwavering presence, their selfless gestures, and the countless ways in which they've enriched my life.

I wish to extend my gratitude to all those individuals who, although not explicitly listed, have supported, motivated, and inspired me throughout my doctoral studies.

Finally, and of greatest significance, I extend my heartfelt thanks to God for steering me on the correct course to complete my doctoral work.

(Mr. Yash Pathak)

New Delhi September, 2024

# ABSTRACT

Studies on Computer Aided Design Technology of Double Metal Negative Capacitance FET using DFT and Machine Learning Approach for Analog/Sensing Applications.

The exponential growth in transistor density has been the driving force behind advancements in computing power, energy efficiency, and cost reduction for decades. As transistor dimensions shrink, the gate loses control over the channel, causing issues such as threshold voltage roll-off, increased leakage currents, drain-induced barrier lowering (DIBL) etc, higher transistor densities increase power consumption per unit area. Shrinking device dimensions exacerbate parasitic capacitance, parasitic resistance, heat dissipation etc. The primary issue with conventional integrated circuits and systems based on CMOS technology is increasing power consumption. Due to the ability to reduce supply voltages using steep-subthreshold swing Field Effect Transistor devices, they have been proposed as a viable option for future circuits and systems that prioritize energy efficiency. The scientific and academic communities have shown significant interest in Negative Capacitance Field Effect Transistors (NCFETs). NCFETs offer numerous notable benefits compared to conventional FETs, primarily due to unique characteristics of the ferroelectric material used in their gate stack. The advantages of NCFETs include low power consumption, increased drive current, reduced subthreshold swing, and higher energy efficiency.

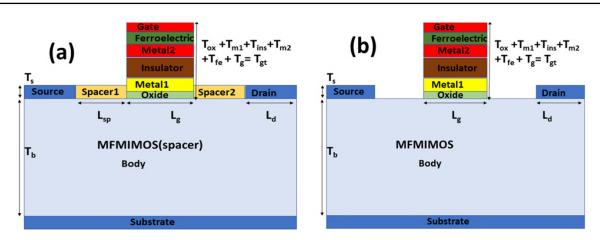

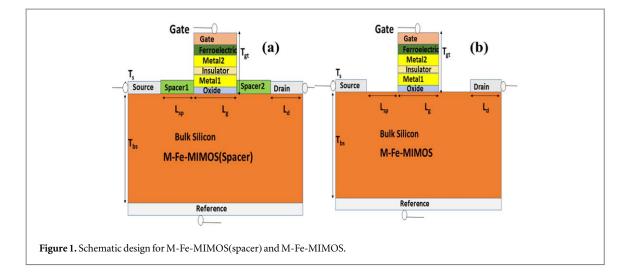

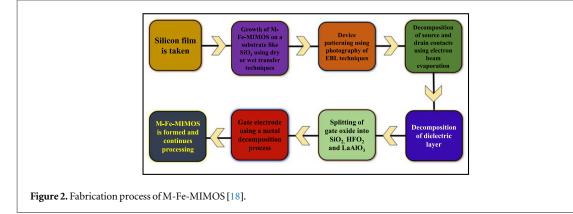

The property of NCFETs that allows them to achieve low off-current  $(I_{off})$  and comparable on-current  $(I_{on})$  at low supply voltages means that they work effectively at low switching voltage and with less power consumption. Different types of NCFETs depending on their structural integration with ferroelectric materials and engineering such as Planar NCFET, NC FinFET, Nanowire NCFET, NC Tunnel FET, etc have been analysed in various literature, each configuration has distinct benefits but also poses various obstacles in their functioning like ferroelectric material stability, control of ferroelectric properties, power-performance trade-offs, temperature sensitivity, and overall device reliability. To counter these challenges, a new device structure, DM NCFET (Double Metal NCFET) is proposed and examined in this thesis. It comprises two metallic layers below the ferroelectric material with stacked insulator in between, resulting in MFMIMIS (Gate Metal-Ferroelectric-Metal-Insulator-Metal-Insulator-Semiconductor) configuration. The idea behind the inclusion of metal layers in the structure is due to its several benefits. The metal layer helps in redistributing the electric field across the ferroelectric and insulator layers. The metal layer also acts as a barrier, preventing direct tunnelling currents between the semiconductor and ferroelectric layers, thus enhances device reliability by minimizing leakage. The metal layer also provides better control over the interface properties, which reduces hysteresis effects in the ferroelectric layer. The metal layer can act as a heat sink, dissipating heat generated during device operation, thus improves the thermal stability and longevity of the device. Further, by isolating the ferroelectric and insulator layers, the metal layer minimizes defects at their interface, thus enhances the overall performance and reliability of the device. Subsequently, spacer technology is also incorporated in the DM NCFET configuration to form DM-NCFET (spacer) to further improve device performance and scalability. Spacers are typically insulating materials, such as silicon nitride  $(Si_3N_4)$  or silicon dioxide (SiO<sub>2</sub>), formed on the sidewalls of the gate stack. They reduce hot-carrier injection (HCI), thereby improves device reliability and reduces electric field peaks at the drain junction. Spacers electrically isolate the gate electrode from the source/drain regions, thus prevent parasitic capacitance and any associated leakage paths. Spacers also help in achieving self-aligned source and drain regions during fabrication. So, by providing precise control over doping, isolation, and stress, spacers in general enhance the reliability and efficiency of the device. Thus, this proposed structure presents a promising direction for overcoming the limitations of conventional NCFETs, especially as technology nodes scale down. It provides a pathway to achieve a more promising device for meeting the demands of modern electronics.

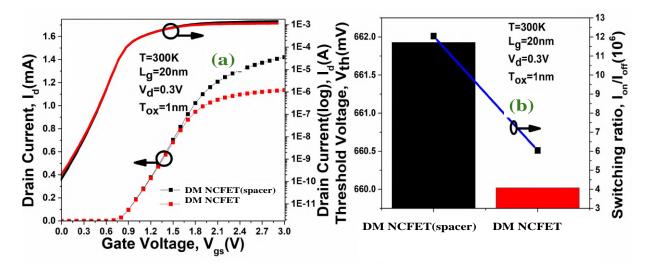

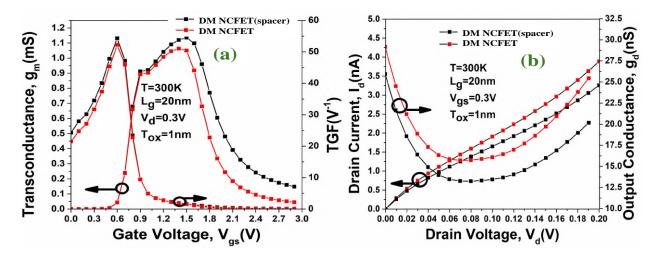

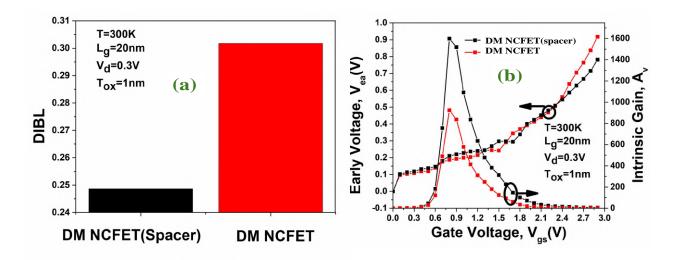

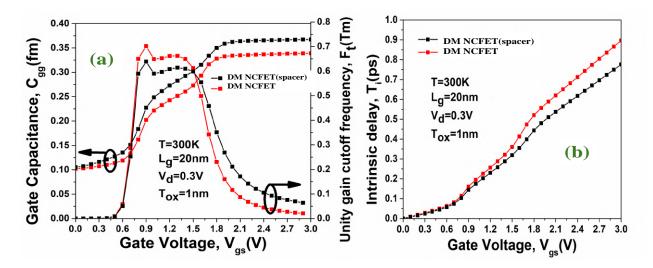

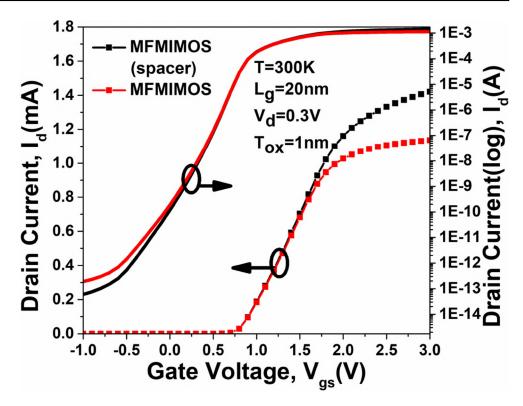

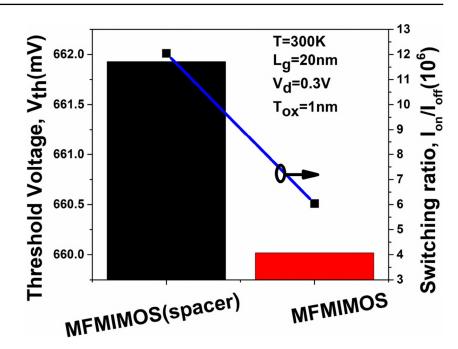

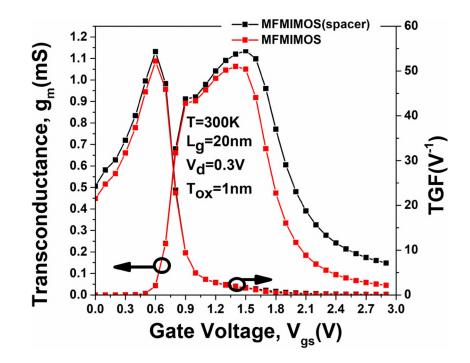

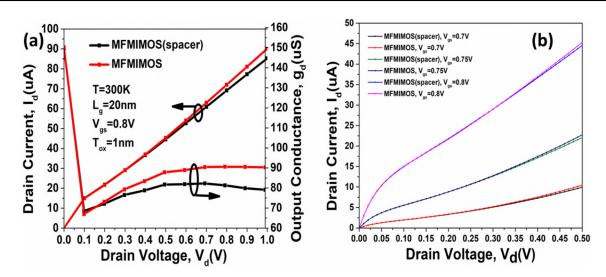

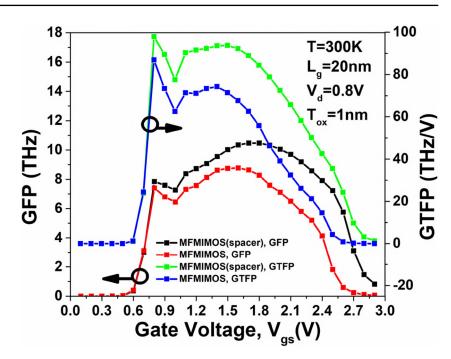

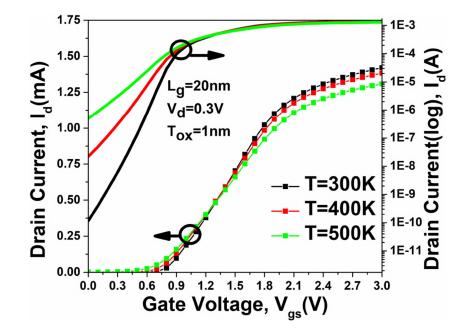

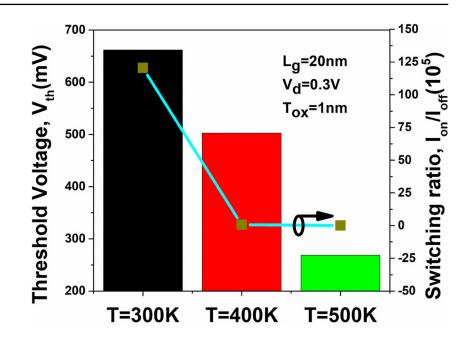

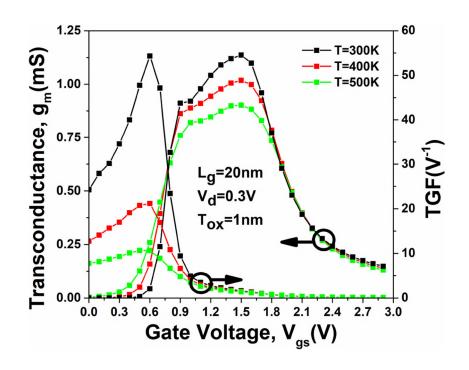

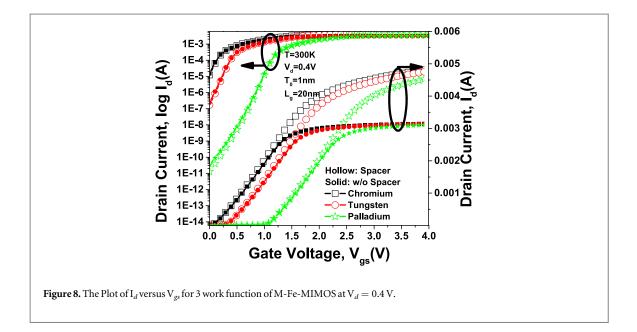

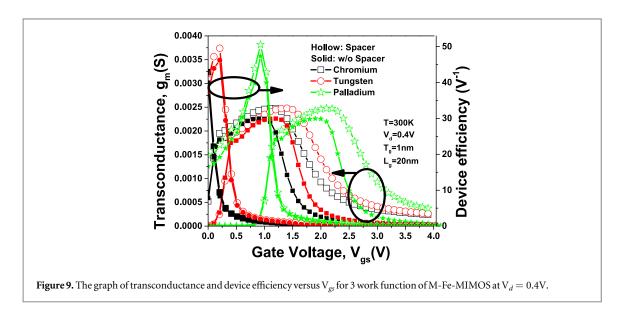

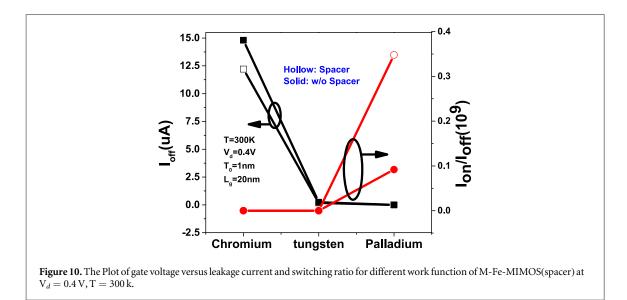

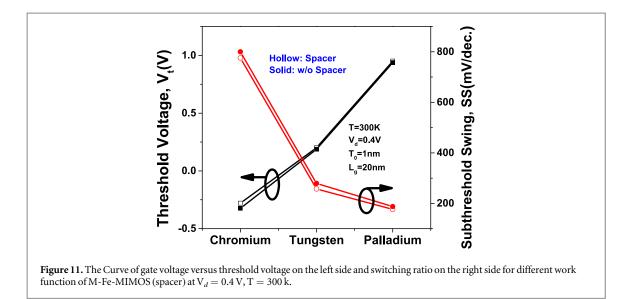

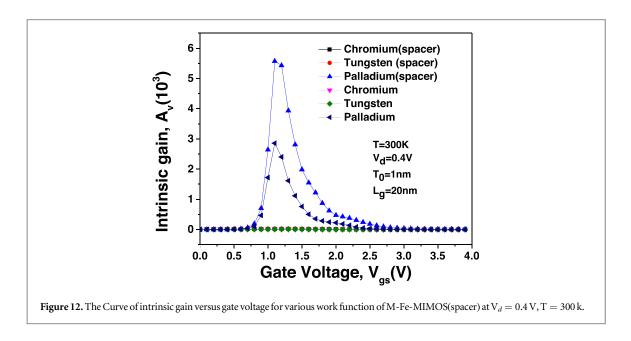

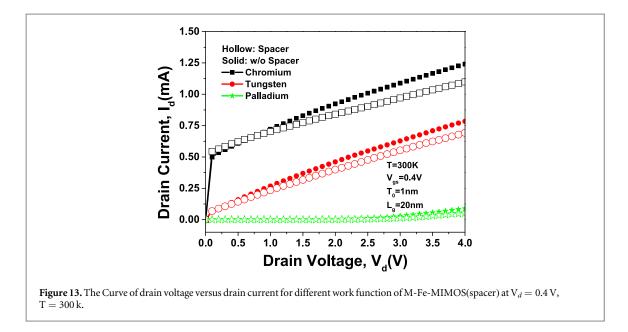

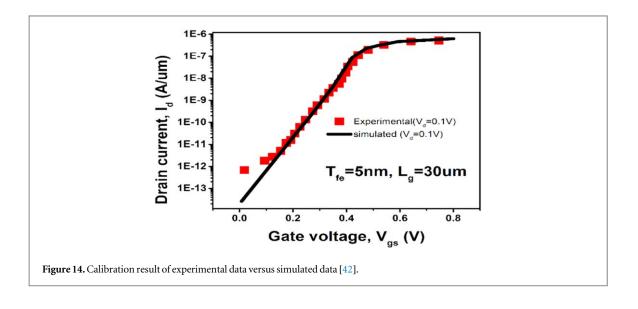

Initially, the analog and RF (Radio Frequency) performance of the ferroelectric Field Effect Transistor device, specifically the DM-NCFET with and without a spacer were studied. The proposed DM-NCFET (spacer) improves the ON-current ( $I_{on}$ ) by 25% as compared to the DM-NCFET without a spacer, reduces leakage current ( $I_{off}$ ) by approximately 37%, enhances the switching ratio  $(I_{on}/I_{off})$  by 99%, increases the threshold voltage  $(V_{th})$  by 0.29%, and lowers drain-induced barrier lowering (DIBL) by 17.6%. We also examined various analog parameters to improve the performance of the DM-NCFET with a spacer at 300K, including transconductance generation factor (TGF), transconductance  $(g_m)$ , intrinsic gain  $(A_v)$ , early voltage  $(V_{ea})$ , intrinsic delay  $(T_i)$ , and some RF parameters like gain transconductance frequency product (GTFP), cut-off frequency  $(F_t)$ , and gain frequency product (GFP). At 300K, the DM-NCFET(spacer) shows improved performance for these parameters compared to higher temperatures (400K and 500K). Simulated results using Visual TCAD confirm the high compatibility and enhanced performance of DM-NCFET(spacer) at room temperature (300K). Additionally, the gate electrode work function was varied using materials like Palladium, Chromium, and Tungsten. Palladium with a work function of 5.3eV, showed the best performance with improvement in leakage current by 106 times and switching ratio by 107 times compared to Chromium.

Furthermore, the DM-NCFET is explored for biosensing applications, analyzing the effects of nano cavity gaps with biomolecules like proteins, cholesterol oxidase  $(ChO_x)$ , streptavidin, and uricase. Electrical characteristics such as threshold voltage and switching ratio  $(I_{on}/I_{off})$  are higher with biomolecules compared to without biomolecules. Protein sensitivity is improved by 1.11 times, and the detection limit is higher by 1.012 times. The biosensor's sensitivity is increased with increase in dielectric parameter of the biomolecules, and modulation of the cavity gap length (from 8nm to 12nm). Visual TCAD software was used for all the simulations, showing that the DM-NCFET biosensors are highly sensitive with low-power consumption, thus suitable in numerous applications like checking infections, food investigation, crime detection, ecological monitoring, and biomedical field.

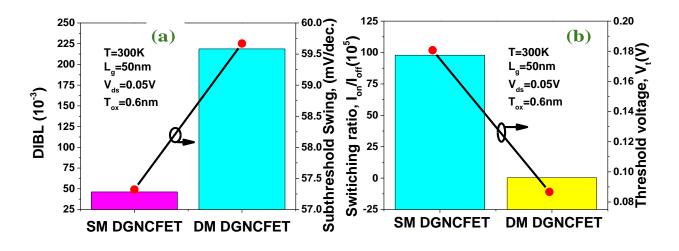

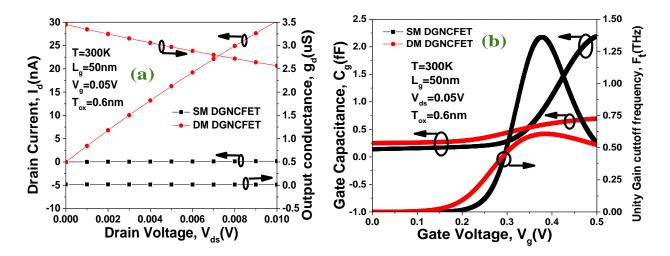

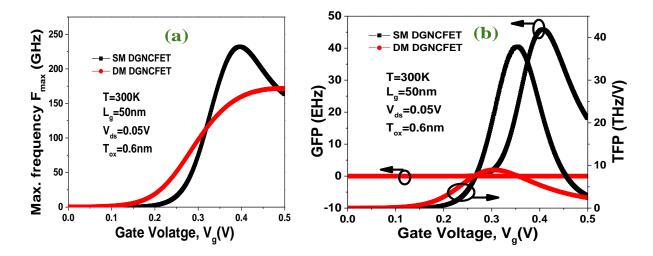

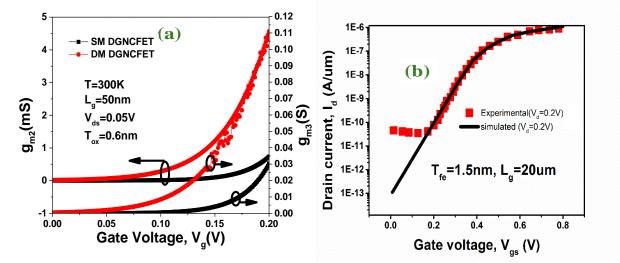

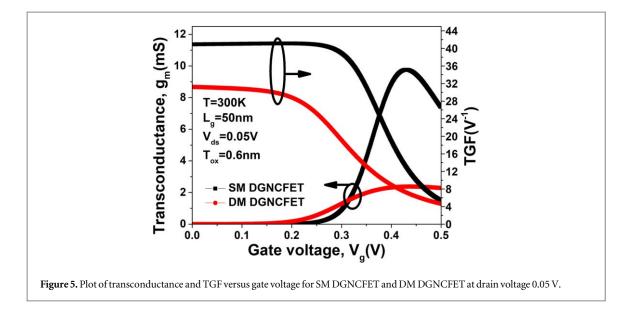

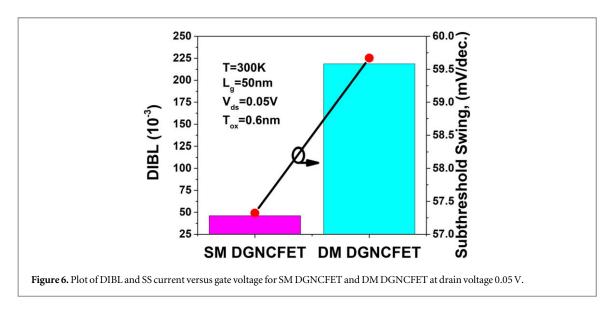

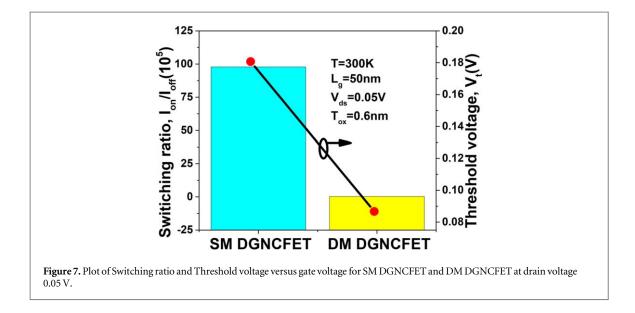

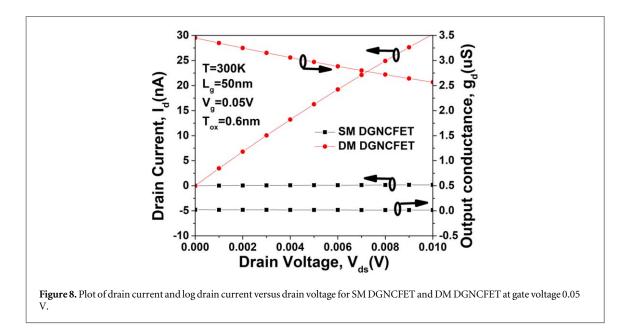

Moreover, the analog/RF and linearity parameters of Single Metal Double Gate NCFET (SM-DGNCFET) and Double Metal Double Gate NCFET (DM-DGNCFET) are observed using Cogenda Visual TCAD and Quantum ATK tool. SM-DGNCFET demonstrated better performance with a 279 times higher switching ratio, 54% lower DIBL, reduced SS, and improved transconductance, TGF, and RF parameters like TFP, confirming the enhanced device's reliability and stability. Linearity parameters such as second and third-order transconductance ( $g_{m2}$ ,  $g_{m3}$ ) and voltage intercept points for 2nd and 3rd order are also improved. The Tran-Blaha modified Becke-Johnson (TB-mBJ) approximation provided accurate band gap calculations, and DFT-based atomic studies with 12.5% Si doping in HfO<sub>2</sub> crystals showed better conductivity for the device.

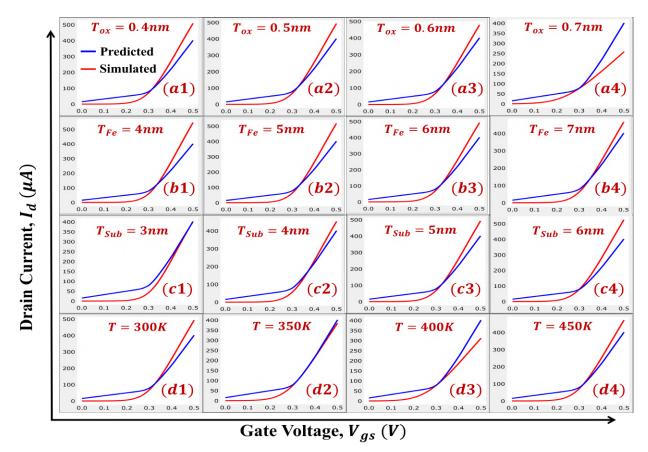

Further, the machine learning approach for predicting key analog and RF parameters of NCFETs is also explored using Visual TCAD and Python. The algorithm of an artificial neural network effectively predicted multi-input to single-output relationships, reducing computational costs. Simulations demonstrated that DM-DGNCFETs performed optimally at T=300K,  $T_{ox}$ =0.8nm, and  $T_{sub}$ =3nm, improving the switching ratio and reducing leakage current. Notably, at T = 300K, the switching ratio is higher and the leakage current is 84 times lower compared to T = 500K. Similarly, at ferroelectric thicknesses  $T_{Fe} = 4nm$ , the switching ratio improves by 5.4 times compared to  $T_{Fe} = 8nm$ . Furthermore, at substrate thicknesses  $T_{sub} = 3nm$ , switching ratio increases by 81% from  $T_{sub} = 7nm$ . For oxide thicknesses at  $T_{ox} = 0.8nm$ , the switching ratio increases by 41% compared to  $T_{ox} = 0.4nm$ . The analysis reveals that  $T_{Fe} = 4nm$ , T = 300K,  $T_{ox} = 0.8nm$ , and  $T_{sub} = 3nm$  represent the optimal settings for DM DGNCFET, resulting in significantly improved performance.

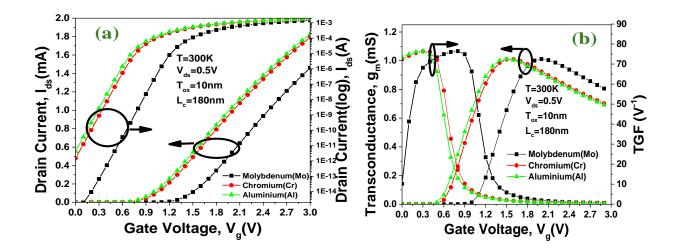

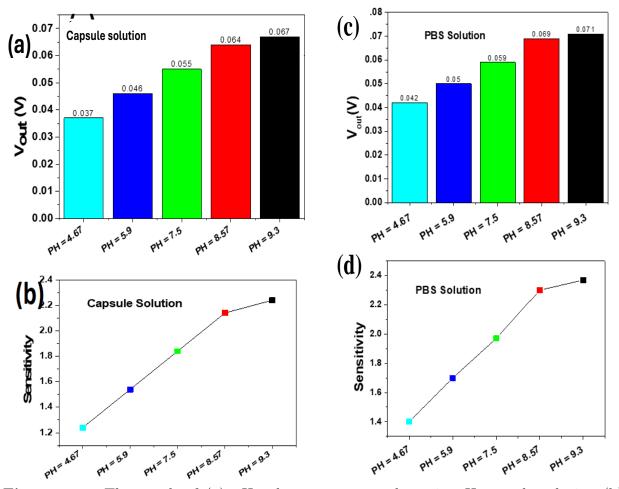

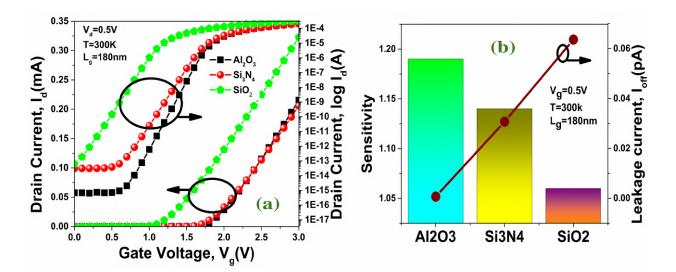

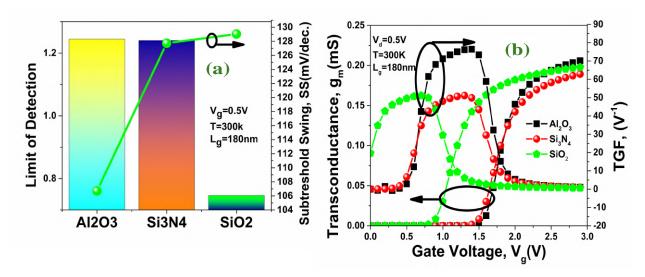

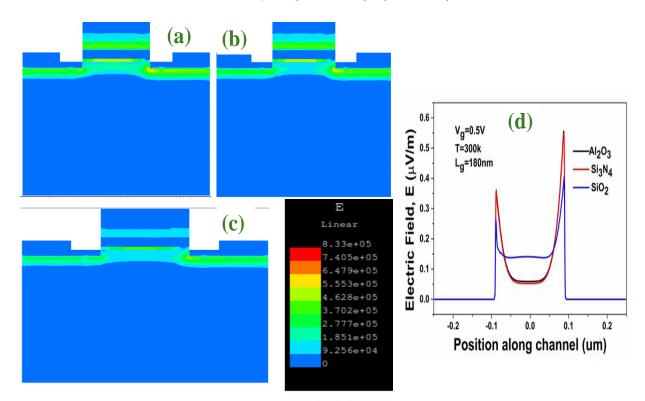

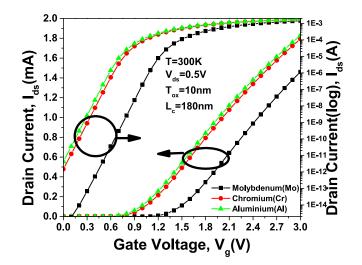

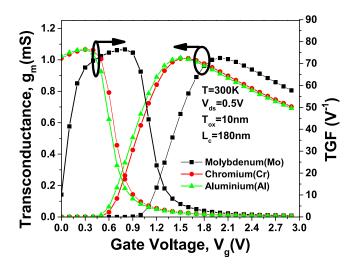

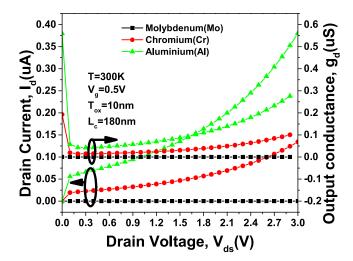

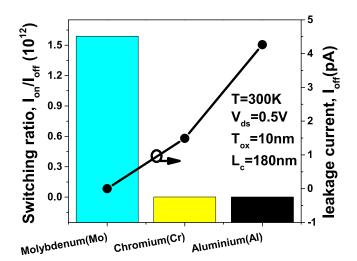

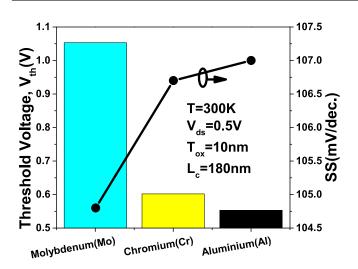

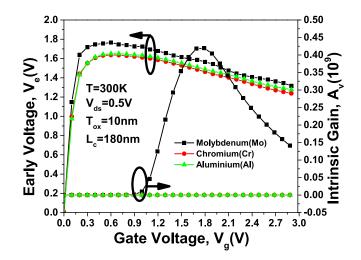

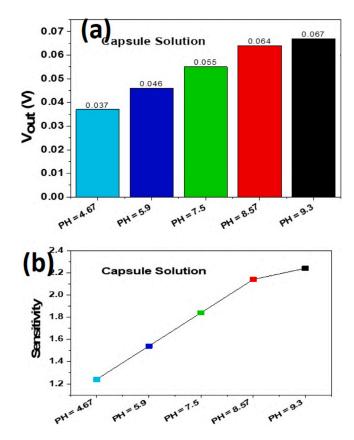

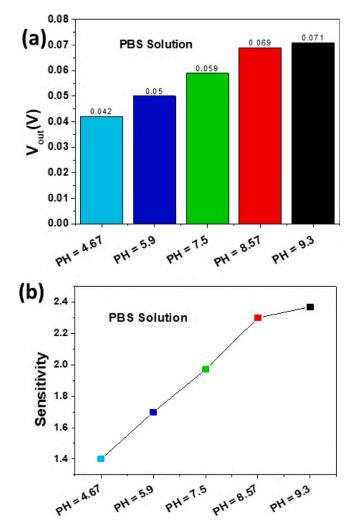

Additionally, experimental circuit designs of Ion-Sensitive FETs (ISFETs) for pH sensing are investigated. The gate electrode work function on ISFETs was rigorously studied using Cogenda Visual TCAD, with molybdenum showing better results than aluminum. Based on its I-V characteristics, it may deduce that molybdenum, with a work function of 4.75eV, has a larger threshold voltage, switching ratio ( $10^4$ ) and lower leakage current ( $10^{-3}$ ) than aluminium at 300K. Comparative studies of ISFET sensing layers ( $Al_2O_3$ ,  $Si_3N_4$ ,  $SiO_2$ ) indicated that  $Al_2O_3$  displayed the best results for switching ratio, leakage current, sensitivity, and transconductance. The enhancement in pH sensing is also demonstrated experimentally with proper circuit designing of ISFET. ISFET display instability, often referred to as drift, in the form of a gradual, monotonic, temporal increase in the device's threshold voltage. The validation of the observations is done by increasing the value of the pH as follows: 4.67, 5.9, 7.5, 8.57, and 9.3, which were checked by pH meter.

In conclusion, DM-NCFET shows great potential for low-power, analog, RF, and sensing applications along with its compatibility with DFT and machine learning approaches as discussed comprehensively in this research work.

# Contents

| D             | ECL   | ARATION                                                                                      | i     |

|---------------|-------|----------------------------------------------------------------------------------------------|-------|

| Cl            | ERT   | IFICATE                                                                                      | iii   |

| A             | CKN   | OWLEDGEMENTS                                                                                 | v     |

| A]            | BST   | RACT                                                                                         | viii  |

| $\mathbf{Li}$ | st of | figures                                                                                      | xviii |

| Li            | st of | tables                                                                                       | xix   |

| $\mathbf{Li}$ | st of | publications                                                                                 | xx    |

| 1             | Intr  | roduction                                                                                    | 1     |

|               | 1.1   | Background                                                                                   | 2     |

|               | 1.2   | Theory of NCFET                                                                              | 4     |

|               |       | 1.2.1 Basic Structure of NCFET                                                               | 4     |

|               |       | 1.2.2 Ferroelectric Material                                                                 | 5     |

|               |       | 1.2.3 Operation of NCFET                                                                     | 7     |

|               |       | 1.2.4 NCFET Device Engineering                                                               | 9     |

|               | 1.3   | Advantages of NCFET                                                                          | 12    |

|               | 1.4   | Challenges Confronted by NCFET                                                               | 14    |

|               | 1.5   | Proposed Device                                                                              | 16    |

|               | 1.6   | Research Objectives                                                                          | 17    |

|               | 1.7   | Thesis Organisation                                                                          | 18    |

| <b>2</b>      |       | ect of Temperature and Work Function Variation on Double Metal NCFET<br>h Spacer Engineering | 22    |

|               | 2.1   | Introduction                                                                                 | 23    |

|   | 2.2 | Device                                                                 | e Architecture                                                                        | 24 |

|---|-----|------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----|

|   | 2.3 | Meth                                                                   | od of Simulation                                                                      | 25 |

|   | 2.4 | Result                                                                 | & Discussion                                                                          | 26 |

|   |     | 2.4.1                                                                  | Device Scalability                                                                    | 26 |

|   |     | 2.4.2                                                                  | Analog Analysis                                                                       | 27 |

|   |     | 2.4.3                                                                  | RF (Radio Frequency) Analysis                                                         | 30 |

|   |     | 2.4.4                                                                  | Effect of Variation of Temperature on the performance of DM-NCFET                     | 33 |

|   |     | 2.4.5                                                                  | Effect of Variation of Work Function on the performance of DM-NCFET .                 | 35 |

|   | 2.5 | Summ                                                                   | ary                                                                                   | 40 |

| 3 |     |                                                                        | of Biomolecules in Dielectric Modulated Double Metal NCFET with<br>Sensitivity        | 42 |

|   | 3.1 | Introd                                                                 | uction                                                                                | 43 |

|   | 3.2 | Device                                                                 | e Structure                                                                           | 44 |

|   | 3.3 | Simula                                                                 | ation Methodology                                                                     | 45 |

|   | 3.4 | Result                                                                 | and Discussion                                                                        | 46 |

|   |     | 3.4.1                                                                  | Impact of Various Biomolecules on DM-NCFET                                            | 46 |

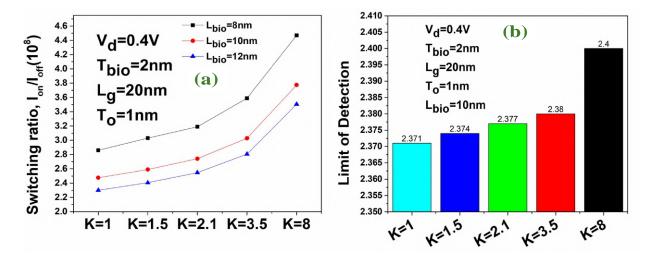

|   |     | 3.4.2                                                                  | Effect of Length Modulation in Cavity Gap                                             | 51 |

|   | 3.5 | Summ                                                                   | ary                                                                                   | 53 |

| 4 |     | OFT Based Atomic Modeling and Optimization of Double Metal Double Gate |                                                                                       |    |

|   | 4.1 | Introd                                                                 | uction                                                                                | 55 |

|   | 4.2 | Device                                                                 | e Design and Atomic Study                                                             | 56 |

|   |     | 4.2.1                                                                  | Device Structure                                                                      | 56 |

|   |     | 4.2.2                                                                  | Structure of Ferroelectric HfO <sub>2</sub> -Based Crystal                            | 58 |

|   | 4.3 | Metho                                                                  | dology and Theoretical Details                                                        | 59 |

|   |     | 4.3.1                                                                  | Device Methods                                                                        | 59 |

|   |     | 4.3.2                                                                  | Method for $HfO_2$ Crystal                                                            | 59 |

|   |     | 4.3.3                                                                  | Flowchart for Fabrication Feasibility from Atomic Modeling to Device Fabri-<br>cation | 60 |

|   | 4.4 | Result                                                                 | and Discussion                                                                        | 61 |

|   |     | 4.4.1                                                                  | Comparative Study of NCFET Device                                                     | 61 |

|   |     | 4.4.2                                                                  | DFT Analysis of Ferroelectric HfO <sub>2</sub> based Crystal                          | 67 |

|   | 4.5                                                                                                              | Summ     | ary                                                                                                   | 70  |  |

|---|------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------|-----|--|

| 5 |                                                                                                                  |          | Neural Network based Modelling for Variational Effect on Double<br>uble Gate Negative Capacitance FET | 71  |  |

|   | 5.1                                                                                                              | Introd   | uction                                                                                                | 72  |  |

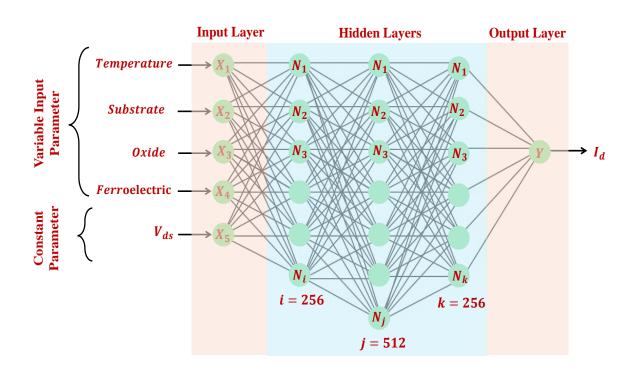

|   | 5.2                                                                                                              | Device   | e Architecture and Simulation Methodology                                                             | 73  |  |

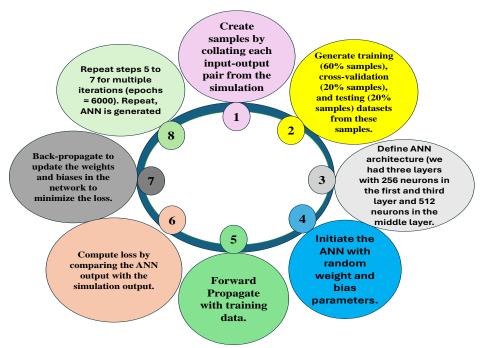

|   | 5.3                                                                                                              | Artific  | ial Neural Network (ANN) Implementation                                                               | 74  |  |

|   | 5.4                                                                                                              | Result   | and Discussion                                                                                        | 76  |  |

|   | 5.5                                                                                                              | Summ     | ary                                                                                                   | 82  |  |

| 6 | Experimental Circuit Design and TCAD Analysis of Ion Sensitive Field Effect<br>Transistor (ISFET) for pH Sensing |          |                                                                                                       |     |  |

|   | 6.1                                                                                                              | Introd   | uction                                                                                                | 85  |  |

|   | 6.2                                                                                                              | Device   | e Structure and Circuit Designing                                                                     | 86  |  |

|   |                                                                                                                  | 6.2.1    | Device Structure of ISFET                                                                             | 86  |  |

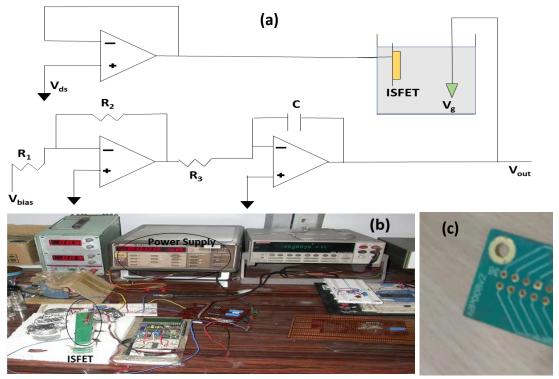

|   |                                                                                                                  | 6.2.2    | Experimental Circuit Designing of ISFET based pH Sensor                                               | 88  |  |

|   | 6.3                                                                                                              | Simula   | ation Study of ISFET and Circuit based pH Sensor                                                      | 89  |  |

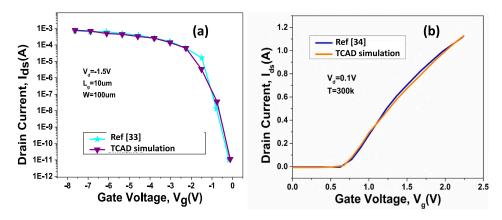

|   |                                                                                                                  | 6.3.1    | Simulation Study of ISFET Device                                                                      | 89  |  |

|   |                                                                                                                  | 6.3.2    | Techniques for Experimental Circuit Designing                                                         | 89  |  |

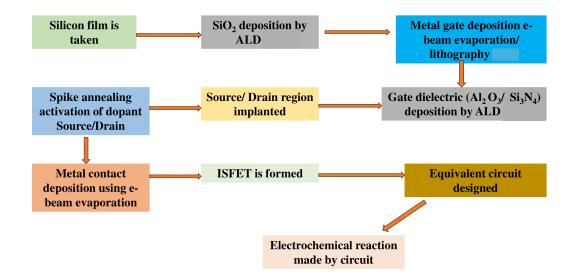

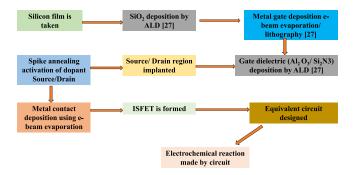

|   |                                                                                                                  | 6.3.3    | Fabrication Feasibility of ISFET based pH Sensor                                                      | 90  |  |

|   | 6.4                                                                                                              | Result   | and Discussion                                                                                        | 91  |  |

|   |                                                                                                                  | 6.4.1    | Comparative Study of ISFET for Different Gate Electrode Material                                      | 91  |  |

|   |                                                                                                                  | 6.4.2    | Experimental Circuit Design Result of ISFET                                                           | 95  |  |

|   |                                                                                                                  | 6.4.3    | Effect of Variation of Sensing Layer on ISFET performance                                             | 97  |  |

|   | 6.5                                                                                                              | Summ     | ary                                                                                                   | 100 |  |

| 7 | Summary and Future Scope                                                                                         |          |                                                                                                       |     |  |

|   | 7.1                                                                                                              | Summ     | ary                                                                                                   | 101 |  |

|   | 7.2                                                                                                              | Future   | e Work                                                                                                | 104 |  |

| R | efere                                                                                                            | nces     |                                                                                                       | 116 |  |

| R | eprin                                                                                                            | nts of J | ournal Publication                                                                                    | 117 |  |

# List of Figures

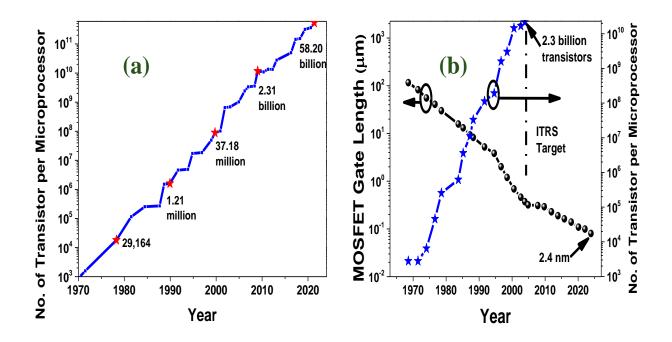

| 1.1 | The plot of (a) No. of Transistor per Microprocessor vs Year (hpm) (b) MOSFET Gate Length vs Year (Rad13).                                                                                                                                                 | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

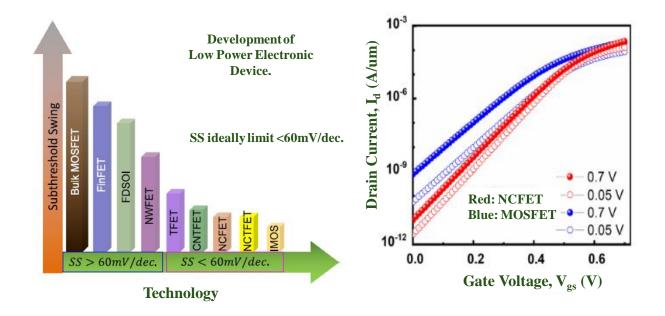

| 1.2 | (a) The advancement of semiconductor FET vs SS (RTU21) (b)The graph of drain current vs gate voltage for MOSFET and NCFET (LSH <sup>+</sup> 23)                                                                                                            | 3  |

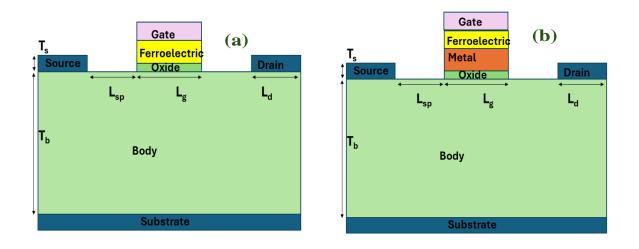

| 1.3 | Schematic diagram for (a) NCFET with MFIS configuration (Pah20) (b) NCFET with MFMIS configuration (PDAC18)                                                                                                                                                | 5  |

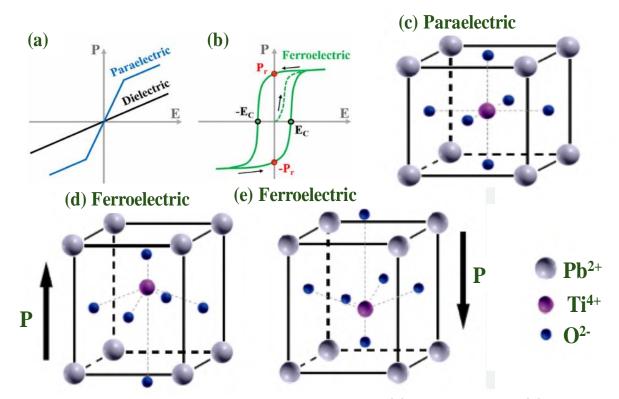

| 1.4 | The plot of polarisation vs electric field for (a) paraelectric and (b) ferroelectric (DDVK22). Atomic structure of $Pb^{2+}Ti^{4+}O_3^{6-}$ for (c) paraelectric (d) ferroelectric with up polarisation (e) ferroelectric with down polarisation (WYSK15) | 6  |

| 1.5 | (a) Schematic diagram for equivalent capacitance model of NCFET and (b) Device structure of NCFET (Pah20).                                                                                                                                                 | 9  |

| 1.6 | <ul> <li>(a) The plot of polarisation vs electric field for NC (Kha15) (b) Drain current vs gate voltage graph for MFIS vs MFMIS (CB20) (c) Energy vs charge graph (MCM22)</li> <li>(d) Hystresis curve for NC.</li> </ul>                                 | 10 |

| 1.7 | The schematic diagram of device engineering for (a) Planar NCFET (TWW <sup>+</sup> 18) (b)<br>NC FinFET (TWW <sup>+</sup> 18)(c) Fe-Ins-FET (LKSH16) (d) Nanowire NCFET (SHH20)<br>(e) GAA NCFET (SHH20) (f) NC-TFET (TWW <sup>+</sup> 18).                | 11 |

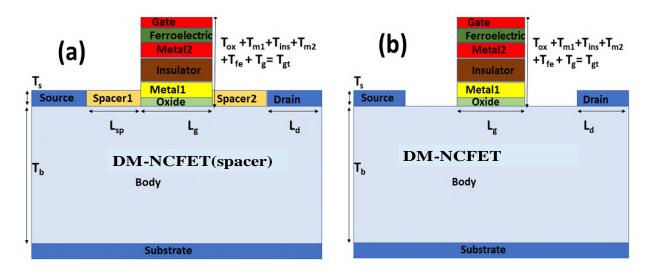

| 2.1 | The two different DM-NCFET schematics structure (a) DM-NCFET with spacer (b) DM-NCFET (PMC22b).                                                                                                                                                            | 25 |

| 2.2 | (a) The curve of drain current vs gate voltage in linear and log scale (b) comparison of $V_{th}$ (V) and switching ratio at $V_d=0.3V$ for DM-NCFET(spacer) and DM-NCFET (PMC22b).                                                                        | 27 |

| 2.3 | The curve of different structures at $V_d=0.3V$ (a) transconductance and transconduc-<br>tance generation factor vs gate voltage (b) drain current and output conductance vs<br>drain voltage (PMC22b).                                                    | 28 |

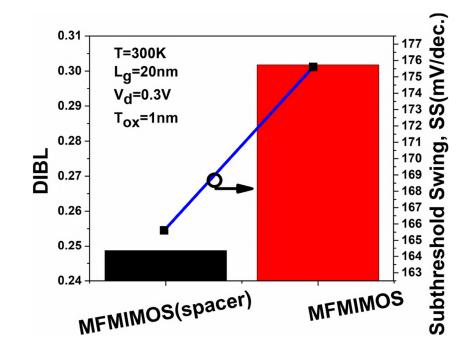

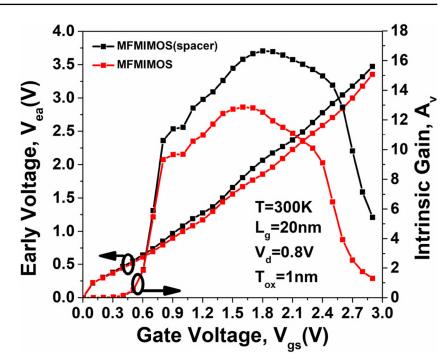

| 2.4 | Graph of different structures at $V_d=0.3V$ showing (a) drain induced barrier low-<br>ering (b) Variation of early voltage and intrinsic gain vs gate voltage at T=300K<br>(PMC22b)                                                                        | 29 |

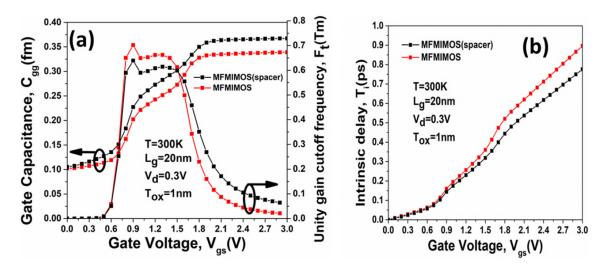

| 2.5 | Variation of (a) gate capacitance vs gate voltage and cutoff frequency vs gate voltage (b) intrinsic delay vs gate voltage for different structures with $V_d=0.3V$ and $L_g = 20$ nm at T=300K (PMC22b).                                                  | 31 |

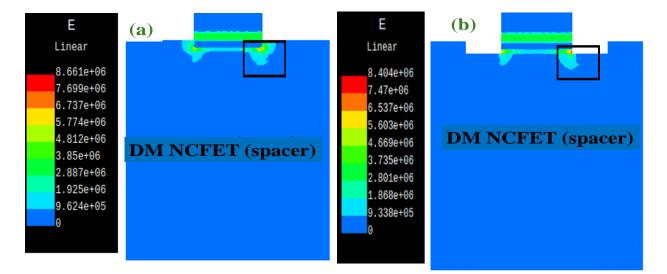

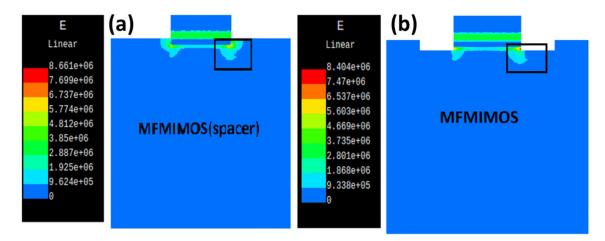

| 2.6  | Electric field contour with (a) DM-NCFET (spacer) from 0 to 8.661E+06 and (b) DM-NCFET from 0 to 8.404E+06 at $V_d$ =0.3V and T=300K.(PMC22b)                                                                                                                                                                                    | 32 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

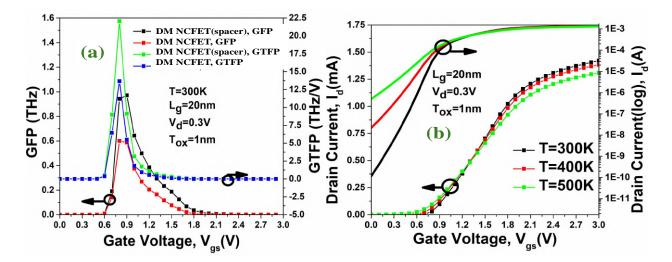

| 2.7  | Graph for different structures at $V_d=0.3$ showing (a) Variation of gain frequency<br>product and gain transconductance frequency gain product vs gate voltage at T=300K,<br>(b) Variation of drain current in linear and log scale vs gate voltage for different tem-<br>perature of DM-NCFET (spacer) at $V_d=0.3$ (PMC22b)   | 33 |

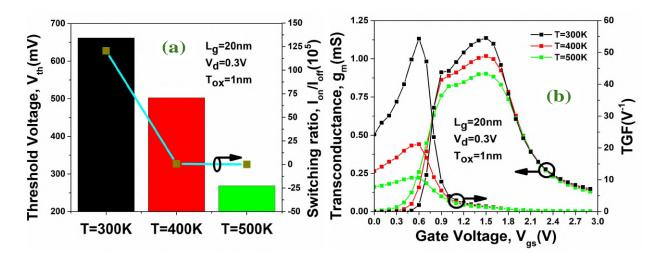

| 2.8  | The graph showing variation of (a) threshold voltage and switching ratio vs gate voltage (b) transconductance and transconductance generation factor vs gate voltage for DM-NCFET (spacer) at different temperature, T=300K, 400K and 500K at $V_d=0.3$ (PMC22b).                                                                | 34 |

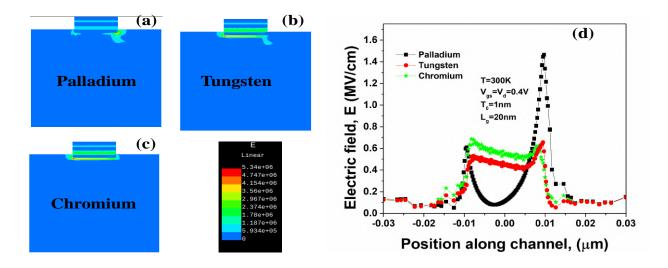

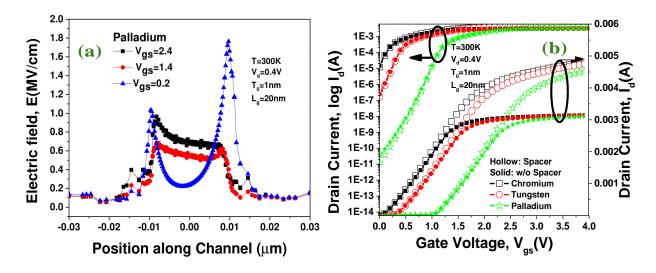

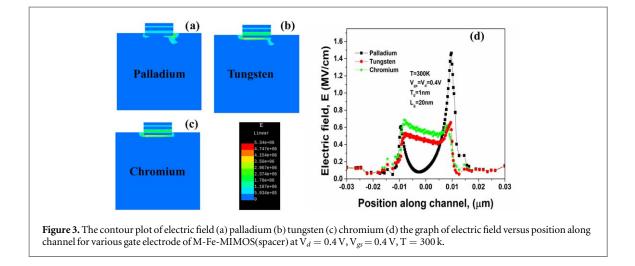

| 2.9  | The contour plot of electric field for (a) palladium (b) tungsten (c) chromium (d) Variation of electric field vs position along the channel for various gate electrode of DM-NCFET(spacer) at $V_d=0.4V$ , $V_{gs}=0.4V$ , and T=300k (PMC22b)                                                                                  | 36 |

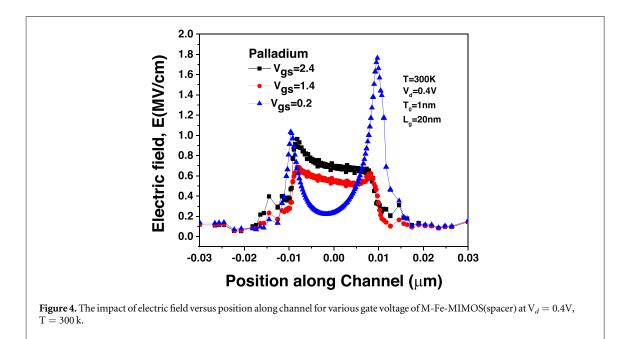

| 2.10 | (a) The impact on electric field vs position along channel for palladium gate electrode at different gate voltage (b) Variation of drain current vs gate voltage of DMNCFET(spacer) for various gate electrode at $V_d$ =0.4V and T=300k (PMC22b).                                                                               | 36 |

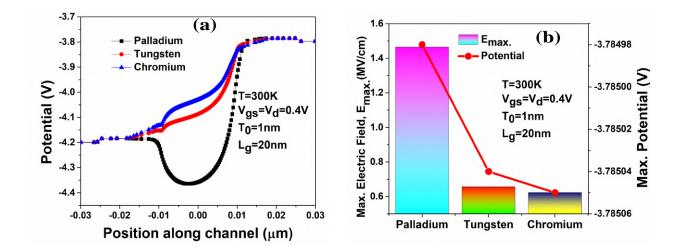

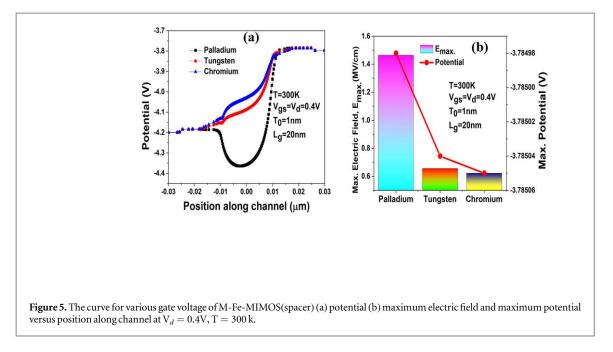

| 2.11 | Variation of (a) potential vs position along channel (b) maximum electric field and maximum potential of DM-NCFET(spacer) with various gate electrode materials at $V_d=0.4V$ and T=300K (PMC22b)                                                                                                                                | 38 |

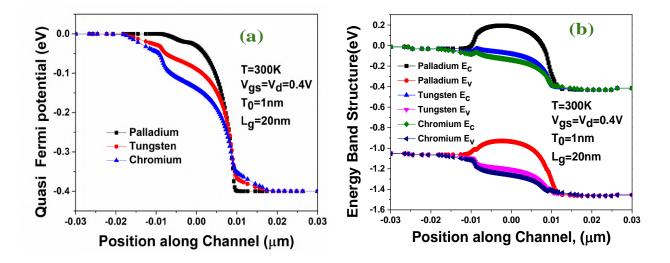

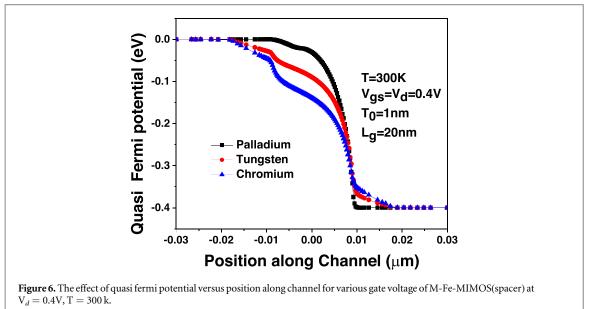

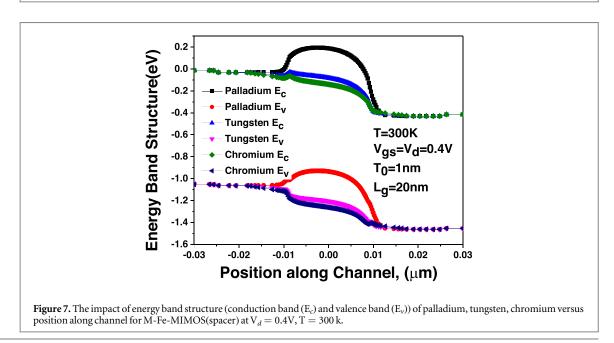

| 2.12 | (a) The effect on quasi fermi potential vs position along channel and (b) The impact<br>on energy band structure (conduction band $(E_c)$ and valence band $(E_v)$ ) vs position<br>along channel for DM-NCFET(spacer) with palladium, tungsten, and chromium as<br>gate electrode materials at $V_d=0.4V$ and $T=300K$ (PMC22b) | 39 |

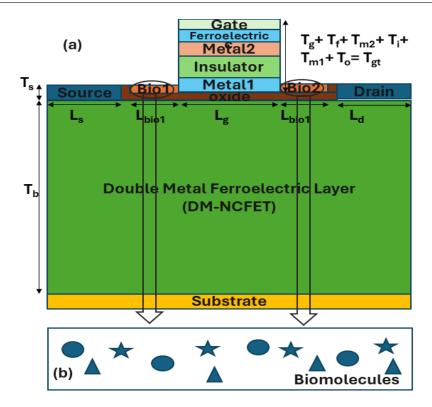

| 3.1  | (a) The Schematic diagram of DM-NCFET for detection of biomolecule (b) Magnified view of cavity with biomolecules(PMC22c).                                                                                                                                                                                                       | 45 |

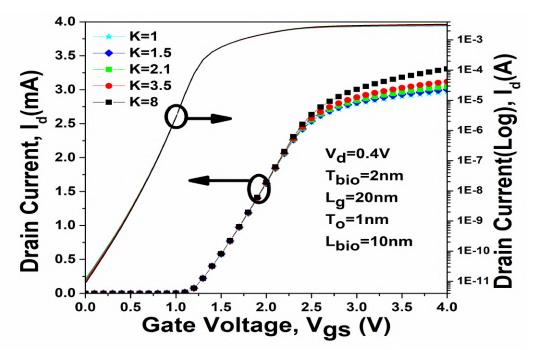

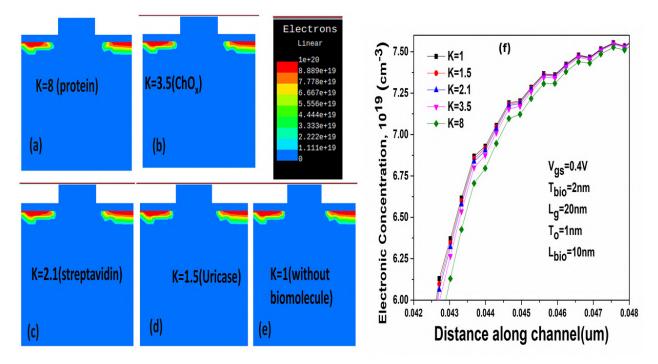

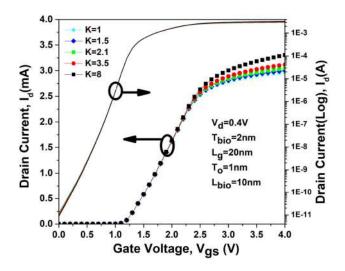

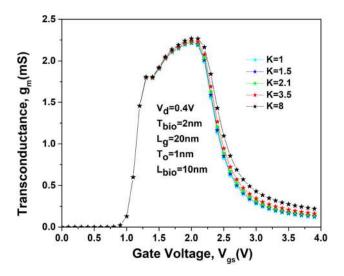

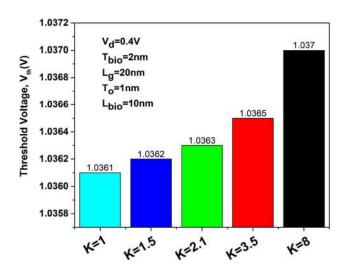

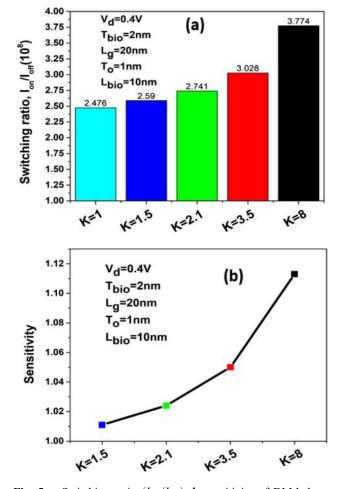

| 3.2  | Transfer characteristic of different biomolecules for DM-NCFET at drain voltage $=0.4V.$ (PMC22c).                                                                                                                                                                                                                               | 46 |

| 3.3  | Variation of (a) Transconductance, $(g_m)$ (b) Threshold voltage $(V_{th})$ versus gate voltage of different biomolecules for DM-NCFET at $V_d = 0.4V$ . (PMC22c)                                                                                                                                                                | 47 |

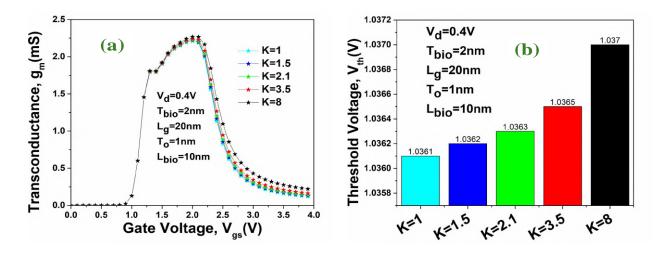

| 3.4  | (a) Switching ratio $(I_{on}/I_{off})$ (b) Sensitivity of DM-NCFET for different biomolecules at drain voltage =0.4V. (PMC22c).                                                                                                                                                                                                  | 47 |

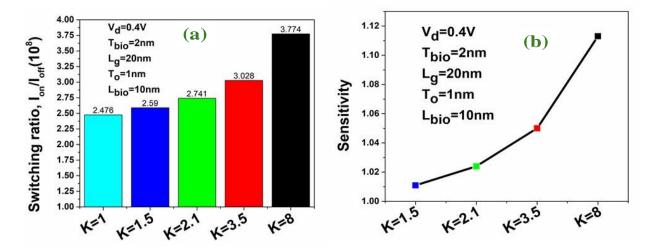

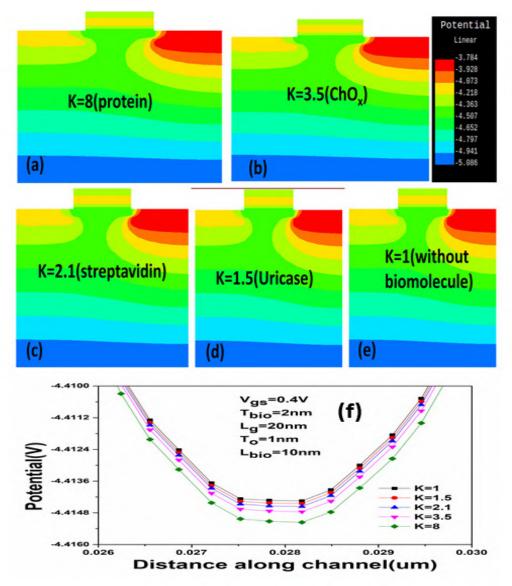

| 3.5  | Contour plot for Electronic concentration of DM-NCFET for different biomolecules with dielectric constant (a) $K=8$ (b) $K=3.5$ (c) $K=2.1$ (d) $K=1.5$ (e) $K=1$ and (f) Variation of electronic concentration vs distance along channel for various biomolecules (PMC22c).                                                     | 48 |

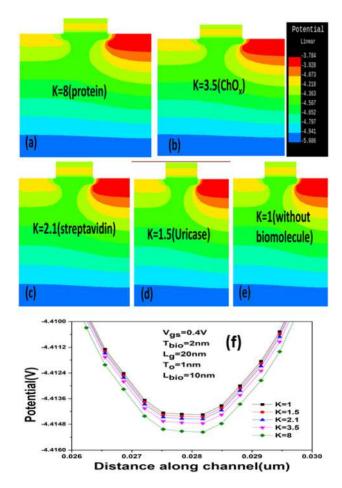

| 3.6  | Contour plot for Potential of DM-NCFET for different biomolecules with dielectric constant (a) $K=8$ (b) $K=3.5$ (c) $K=2.1$ (d) $K=1.5$ (e) $K=1$ . (f) Variation of potential vs distance along channel at drain voltage = 0.4V for different biomolecules (PMC22c).                                                           | 49 |

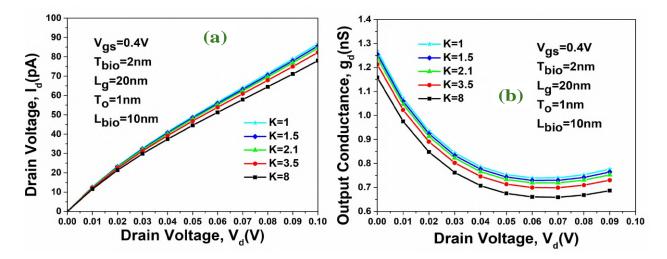

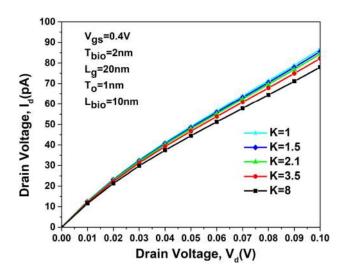

| 3.7  | Variation of (a) drain current vs drain voltage (b) output conductance vs drain voltage of DM-NCFET at gate voltage = $0.4V$ for different biomolecules (PMC22c).                                                                                                                                                                | 50 |

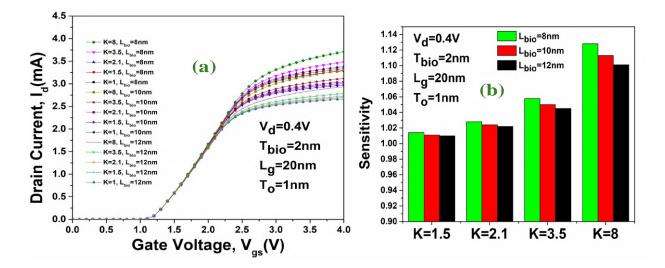

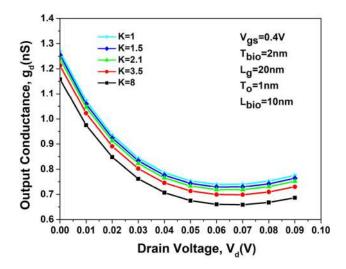

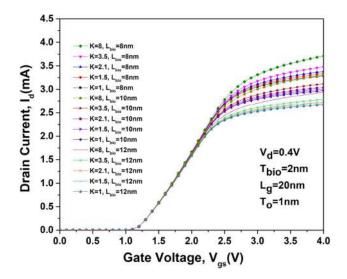

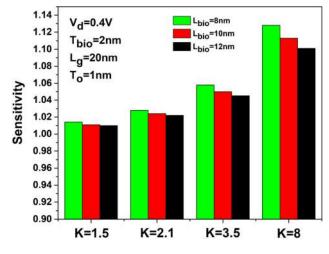

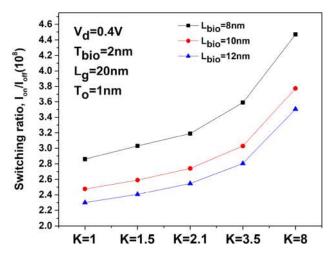

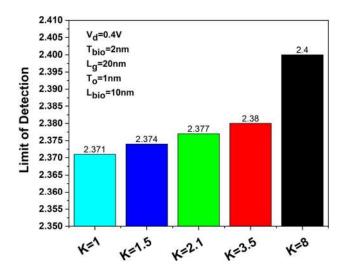

| 3.8  | Variation of (a) drain current vs gate voltage (b) Sensitivity of DM-NCFET for various biomolecules with different cavity length, $L_{bio} = 8$ nm, 10nm, and 12nm at drain voltage = 0.4V (PMC22c).                                                                  | 51 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | Variation of (a) switching ratio of DM-NCFET (b) limit of detection (LOD) for various biomolecules with different cavity length, $L_{bio} = 8$ nm, 10nm, and 12nm at drain voltage = 0.4V (PMC22c).                                                                   | 52 |

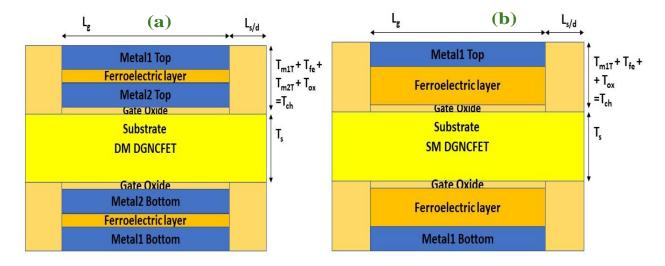

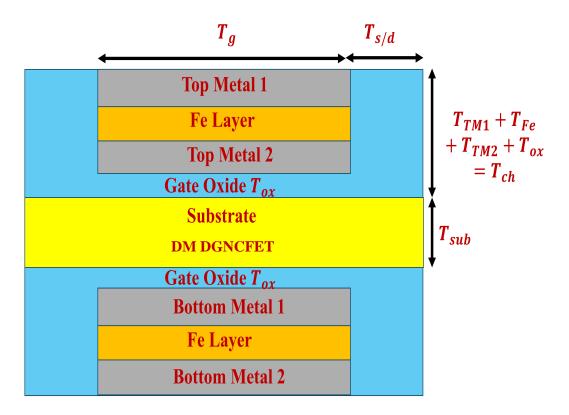

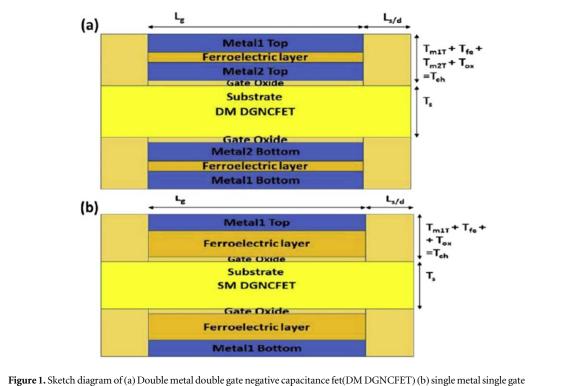

| 4.1  | Structural diagram of (a) Double Metal Double Gate NCFET(DM DGNCFET) and (b) Single Metal Double Gate NCFET device (SM DGNCFET) (PMC23)                                                                                                                               | 57 |

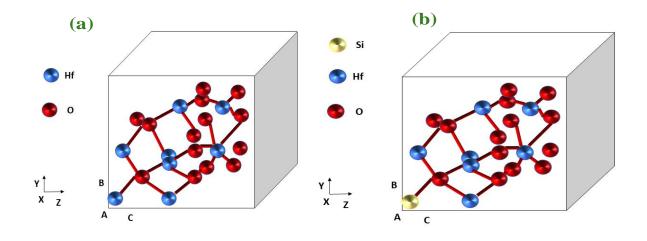

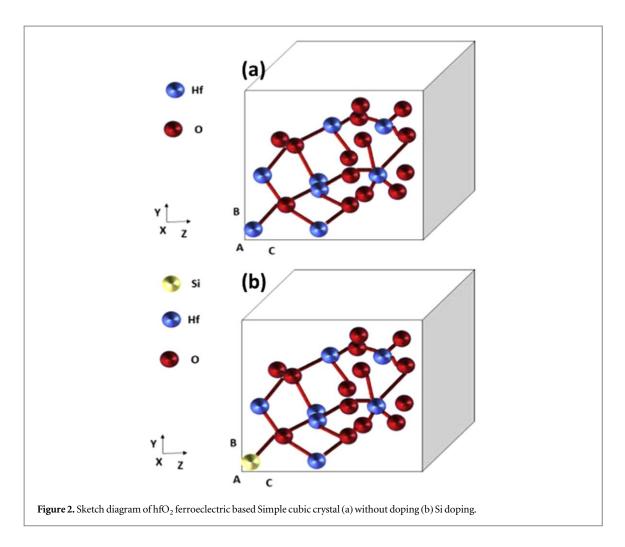

| 4.2  | Structural diagram of $HfO_2$ ferroelectric based simple cubic crystal (a) without doping (b) with Si doping (PMC23).                                                                                                                                                 | 58 |

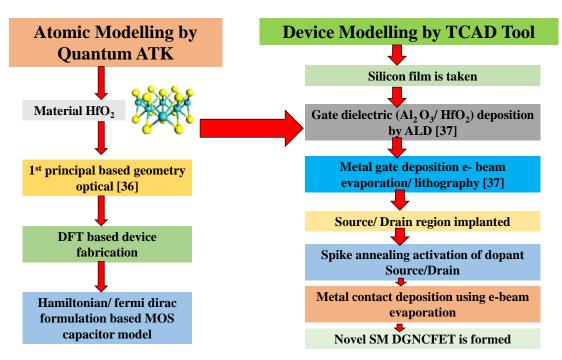

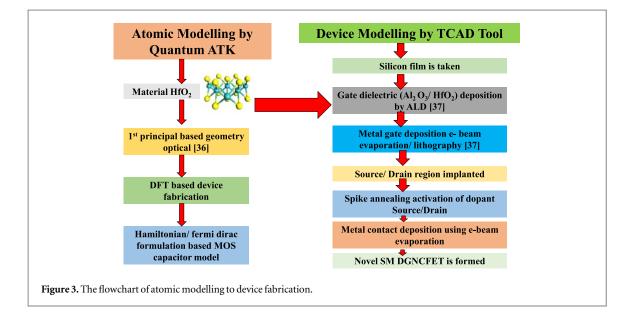

| 4.3  | Fabrication process flowchart from atomic modelling to device modelling (PMC23).                                                                                                                                                                                      | 60 |

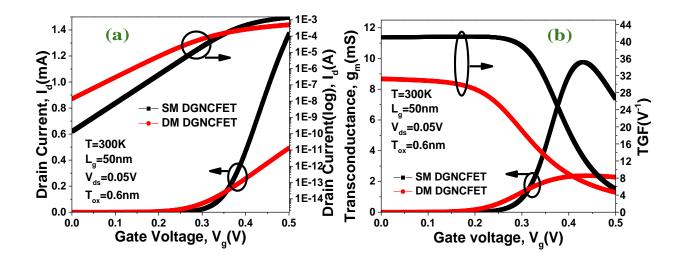

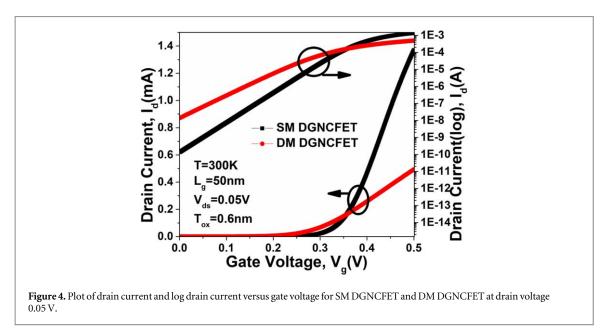

| 4.4  | Plot of (a) drain current and log drain current vs gate voltage (b) transconductance<br>and TGF vs gate voltage for SM DGNCFET and DM DGNCFET at drain voltage<br>0.05V (PMC23).                                                                                      | 61 |

| 4.5  | Plot of (a) DIBL and subthreshold swing vs gate voltage (b) switching ratio and threshold voltage vs gate voltage for SM DGNCFET and DM DGNCFET at drain voltage= 0.05V (PMC23).                                                                                      | 63 |

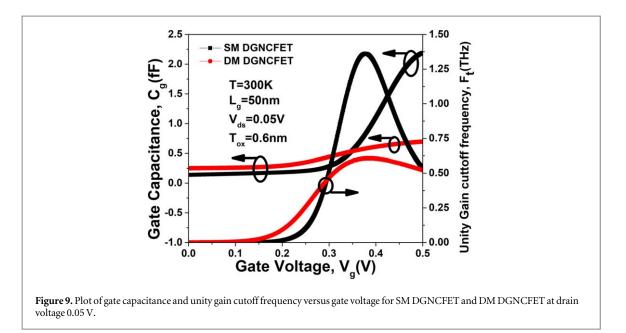

| 4.6  | Plot of (a) drain current and output conductance vs drain voltage (b) gate capaci-<br>tance and unity gain cutoff frequency vs gate voltage for SM DGNCFET and DM<br>DGNCFET at drain voltage $=0.05V$ (PMC23)                                                        | 63 |

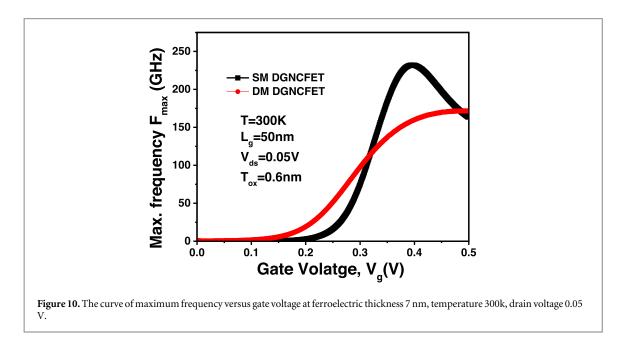

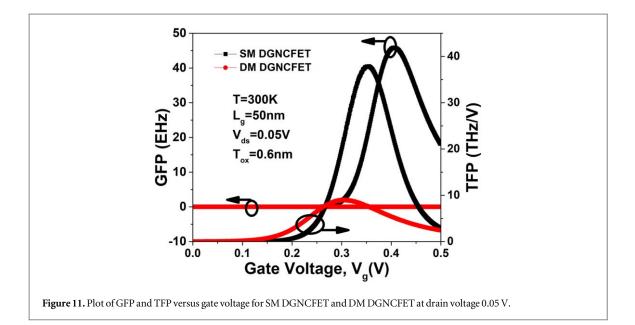

| 4.7  | (a) The curve of maximum frequency vs gate voltage (b) GFP and TFP vs gate voltage at ferroelectric thickness =7nm, temperature =300K, drain voltage = 0.05V (PMC23).                                                                                                 | 65 |

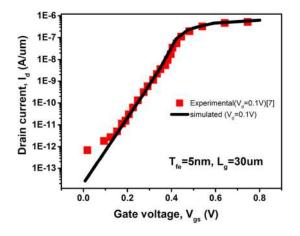

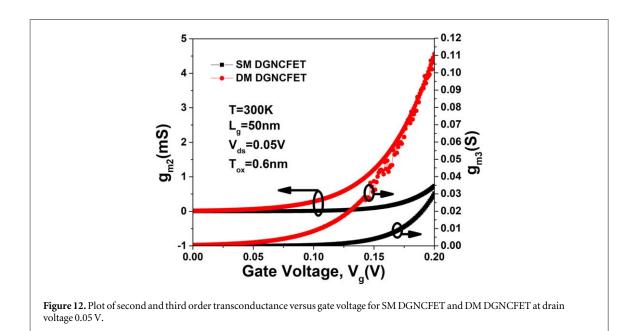

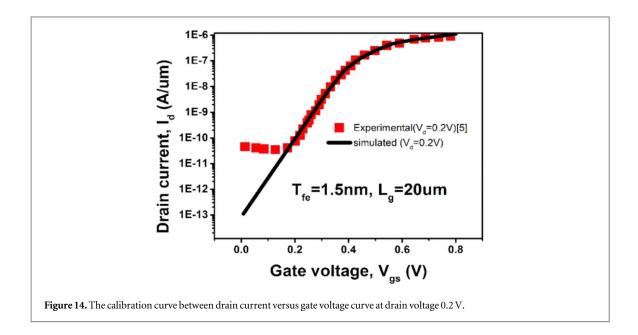

| 4.8  | (a) Plot of second and third order transconductance vs gate voltage for SM DGNCFET and DM DGNCFET at drain voltage =0.05V, (b) The calibration curve between drain current vs gate voltage curve at drain voltage =0.2V from reference (LFT <sup>+</sup> 16) (PMC23). | 66 |

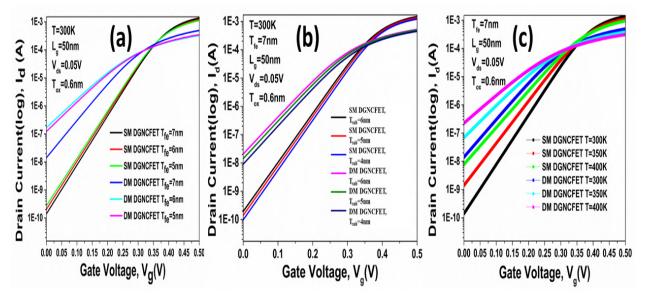

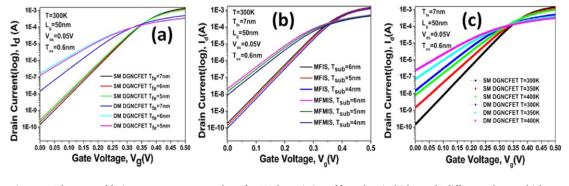

| 4.9  | The curve of drain current vs gate voltage for (a) variation of ferroelectric thickness (b) different substrate thickness (c) variation of temperature (PMC23)                                                                                                        | 67 |

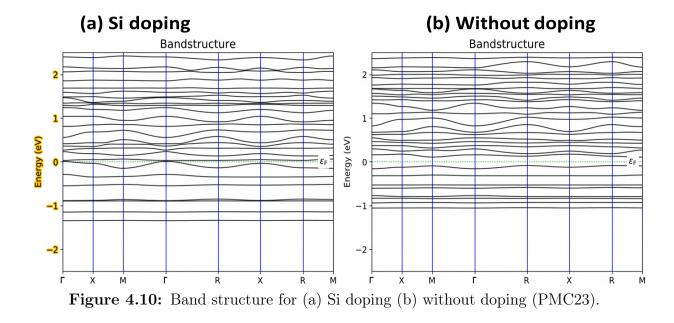

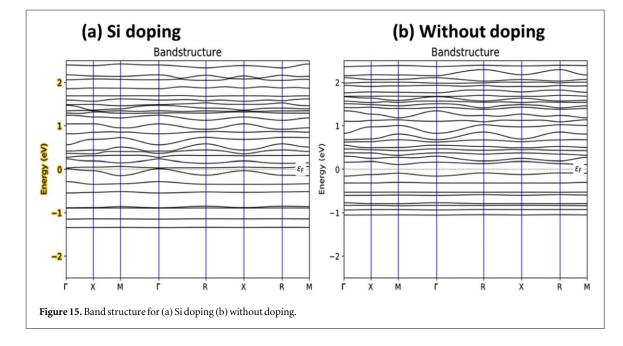

| 4.10 | Band structure for (a) Si doping (b) without doping (PMC23).                                                                                                                                                                                                          | 68 |

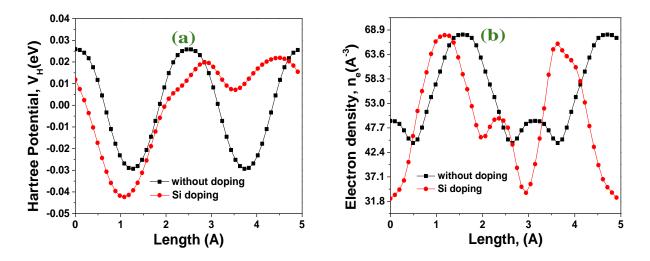

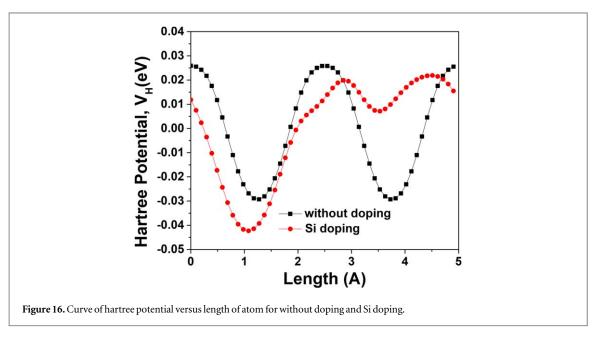

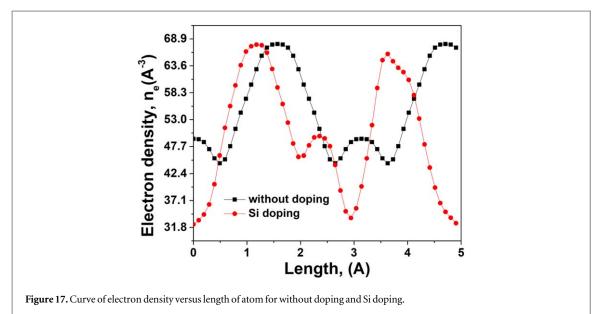

| 4.11 | (a) Curve of Hartree potential vs length of atom, (b) Curve of electron density vs length of atom for without doping and Si doping (PMC23).                                                                                                                           | 69 |

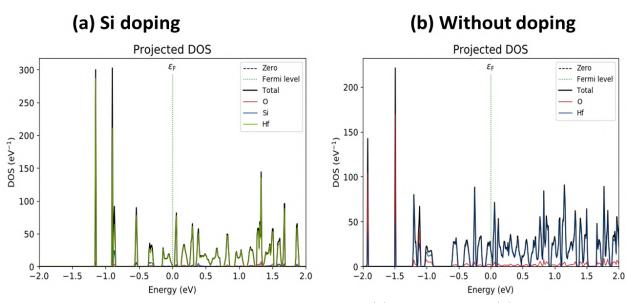

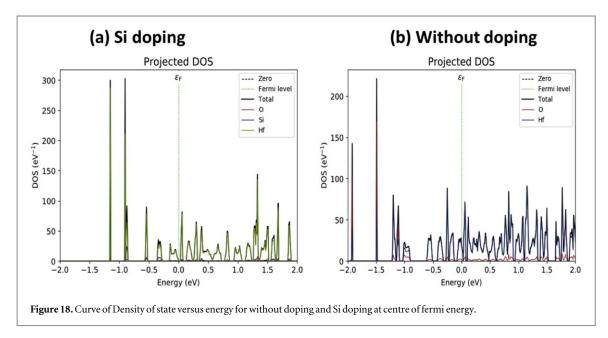

| 4.12 | Curve of density of state vs energy for (a) Si doping and (b) without doping at centre of fermi energy (PMC23).                                                                                                                                                       | 69 |

| 5.1  | The 2D schematic diagram of Double Metal Double Gate NCFET (PMC23). $\ . \ .$                                                                                                                                                                                         | 73 |

| 5.2  | The figure shows the DM DGNCFET Artificial Neural Network (ANN) with one input, one output, and three hidden layers. There are 256 neurons in the first and third hidden layers, and 512 neurons in the middle layer $V_{ds}$ (KLK <sup>+</sup> 19a)                  | 74 |

| 5.3  | Algorithm for DM DGNCFET Artificial Neural Network (ANN) (KLK <sup>+</sup> 19a)                                                                                                                                                                                       | 75 |

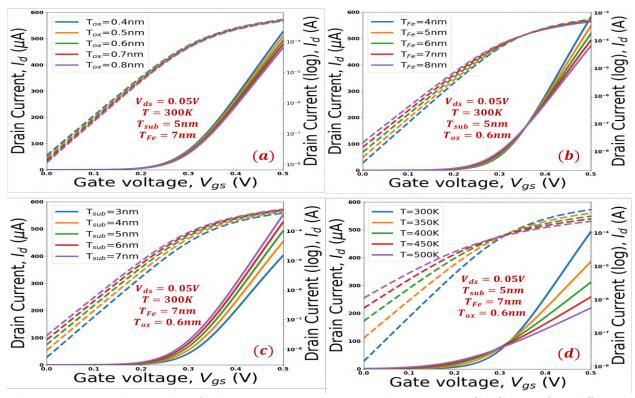

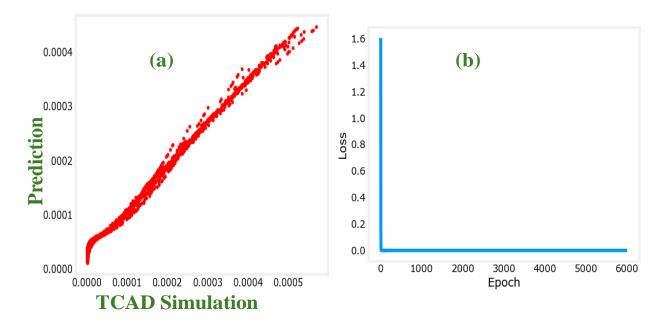

| 5.4  | The graph of drain current vs gate voltage for predicted and simulated data of DM DGNCFET for different variations of temperature, oxide thickness, ferroelectric thickness, and substrate thickness at $V_{ds}$ =0.05V (KLK <sup>+</sup> 19a; PMC23)                                     | 76  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.5  | The graph of drain current vs gate voltage DM DGNCFET for different variations of temperature, oxide thickness, ferroelectric thickness, and substrate thickness at $V_{ds}$ =0.05V (PMC23).                                                                                              | 77  |

| 5.6  | Artificial Neural Network Model for DGNCFET                                                                                                                                                                                                                                               | 79  |

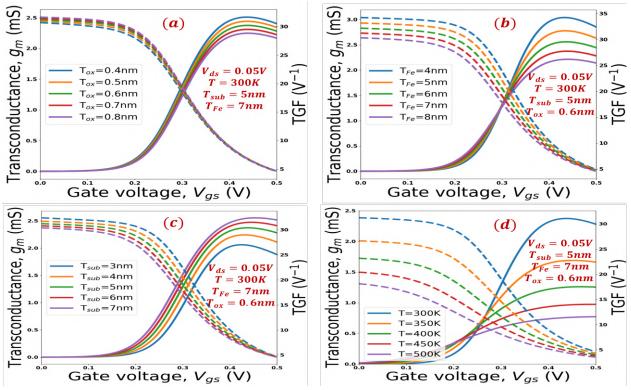

| 5.7  | The plot of transconductance and TGF vs $V_{gs}$ for various temperature and thicknesses at $V_{ds}$ =0.05V (PMC23).                                                                                                                                                                      | 81  |

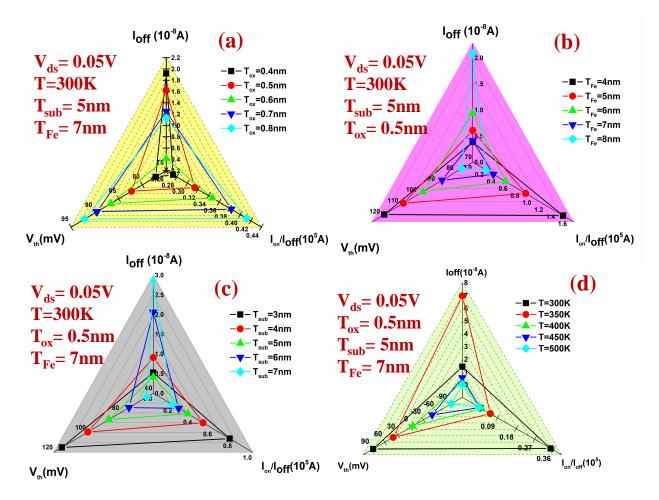

| 5.8  | The spider chart of leakage current, switching ratio, threshold voltage for different temperature and thicknesses at $V_{ds}$ =0.05V (PMC23).                                                                                                                                             | 82  |

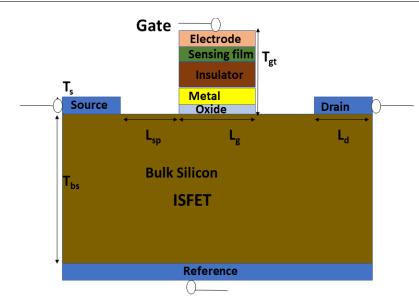

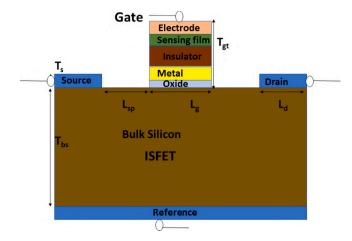

| 6.1  | Sketch diagram for ISFET structure by TCAD tool (PMS <sup>+</sup> 24).                                                                                                                                                                                                                    | 87  |

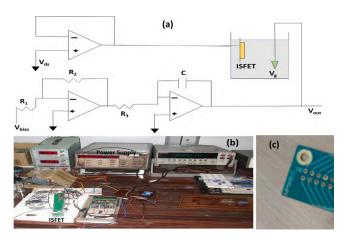

| 6.2  | (a) Circuit diagram of ISFET based pH sensor (b) Experimental setup (c) MP008v2<br>ISFET (PMS <sup>+</sup> 24).                                                                                                                                                                           | 88  |

| 6.3  | The flowchart of fabrication feasibility of ISFET based pH Sensor from ISFET to circuit designing (PMS <sup>+</sup> 24).                                                                                                                                                                  | 91  |

| 6.4  | (a) $I_{ds} - V_g$ characteristics on the left side and log drain current on the right side (b) $g_m - V_g$ characteristics on left side and TGF on the right side for different materials of electrode used in ISFET designing at $V_{ds}$ =0.5V and T=300K (PMS <sup>+</sup> 24).       | 92  |

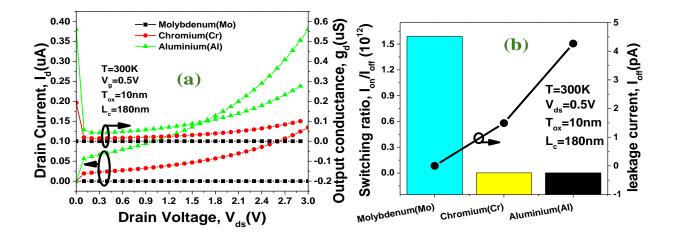

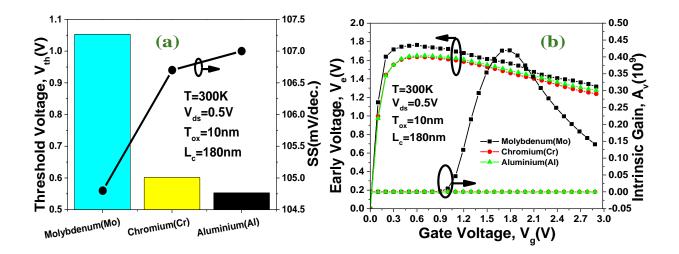

| 6.5  | (a) $I_{ds}$ - $V_{ds}$ characteristics in the left side and output conductance on the right side<br>(b) The plot of switching ratio on the left side and leakage current on the right side<br>for different materials of electrode used in ISFET designing T=300K (PMS <sup>+</sup> 24). | 93  |

| 6.6  | (a) The plot of threshold voltage on the left side and subthreshold swing on the right side (b) $V_e - V_g$ characteristics on the left side and intrinsic gain on the right side for different materials of electrode used in ISFET designing at $V_{ds}=0.5V$ , T=300K (DMG+24)         | 0.4 |

| 0 7  | $(PMS^+24). \qquad (VZD^+15)$                                                                                                                                                                                                                                                             | 94  |

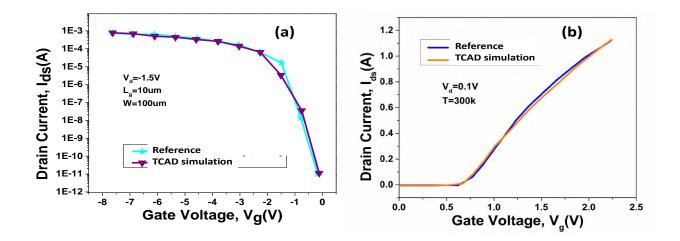

| 6.7  | The calibration of ISFET from (a) reference (KZH07) (b) reference (KZP <sup>+</sup> 15).                                                                                                                                                                                                  | 95  |

| 6.8  | The graph of (a) pH value vs output voltage in pH capsule solution (b) Sensitivity vs pH value in pH capsule solution (c) pH value vs output voltage in PBS solution (d) Sensitivity vs pH value in PBS solution for pH based ISFET device (PMS <sup>+</sup> 24).                         | 96  |

| 6.9  | The curve of (a) drain current vs gate voltage for different sensing layer (b) sensitivity and leakage current for various sensing layer ( $PMS^+24$ )                                                                                                                                    | 97  |

| 6.10 | The variation of (a) limit of detection and SS for varous sensing layer (b) transconductance and device efficiency vs gate voltage ( $PMS^+24$ )                                                                                                                                          | 98  |

| 6.11 | Contour plot of electric field for various sensing layer (a) $Al_2O_3$ (b) $Si_3N_4$ (c) $SiO_2$ (d) variation of electric field along the channel for various sensing layer (PMS <sup>+</sup> 24).                                                                                       | 98  |

# List of Tables

| 2.1 | Parameters used for the simulation of DM-NCFET (spacer) and DM-NCFET $\ . \ .$                                                             | 24       |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2 | Comparison of different performance parameters for different configurations at $T_{ox}=1$ nr T=300K and $L_g=20$ nm                        | n,<br>31 |

| 2.3 | Comparison of different performance parameters for DM-NCFET (spacer) at various temperature with $T_{ox}=1nm$ , and $L_g=20nm$ .           | 34       |

| 2.4 | Performance comparison of DM-NCFET (spacer) and DM-NCFET for different gate electrode materials such as palladium, chromium, and tungsten. | 37       |

| 3.1 | Comparison of different performance parameters for various biomolecules in DM-<br>NCFET at $T_{ox} = 1nm$ and cavity length of $10nm$      | 50       |

| 4.1 | The Device parameters for SM DGNCFET and DM DGNCFET used for the simulation                                                                | 57       |

| 4.2 | The parameters of leakage current, subthreshold swing, DIBL, and others for SM DGNCFET and DM DGNCFET                                      | 62       |

| 4.3 | Brillouin Zone (BZ) of the specific position of ferroelectric HfO <sub>2</sub> based crystal for band stucture                             | 68       |

| 5.1 | The Device parameters for DM DGNCFET are used for the simulation                                                                           | 74       |

| 5.2 | DM DGNCFET comparison for different temperature, substrate thickness, ferroelectric, oxide thickness.                                      | 80       |

| 6.1 | ISFET device parameter by TCAD simulation.                                                                                                 | 87       |

| 6.2 | Performance comparison of ISFET for different gate electrode materials such as molybdenum, chromium, and aluminium                         | 92       |

| 6.3 | Comparison of output voltage and sensitivity of this ISFET device with previously reported results                                         | 95       |

### List of publications

#### Publication Result from this thesis work

#### Article in International Refereed Journal (5):

- Yash Pathak, Bansi Dhar Malhotra, and Rishu Chaujar "Analog/RF Performance and Effect of Temperature on Ferroelectric Layer Improved FET device with Spacer", *Silicon*. vol. 14, pp. 12269–12280, 2022 (SCIE index, Impact Factor: 2.8).

- Yash Pathak, Bansi Dhar Malhotra, and Rishu Chaujar "Detection of biomolecules in dielectric modulated double metal below ferroelectric layer FET with improved sensitivity", *Journal of Materials Science: Materials in Electronics*. vol. 33, no. 17, pp. 13558– 13567, 2022 (SCIE index, Impact Factor: 2.4).

- Yash Pathak, Bansi Dhar Malhotra, and Rishu Chaujar "DFT based atomic modeling andAnalog/RF analysis of ferroelectric HfO2based improved FET device", *Physica Scripta*. vol. 98, no. 8, pp. 1-15, 2023 (SCIE index, Impact Factor: 2.8).

- Yash Pathak, Piyush Mishra, Megha Sharma, Shipra Solanki, Ved Varun Agarwal, Bansi Dhar Malhotra, and Rishu Chaujar "Experimental circuit design and TCAD analysis of ion sensitive field effect transistor (ISFET) for pH sensing", *Materials Science and Engineering: B.* vol. 299, no. , pp. 116951, 2024 (SCIE index, Impact Factor: 3.9).

- Yash Pathak, Kajal Verma, Bansi Dhar Malhotra, and Rishu Chaujar "Impact of Work function and Effect of Electric Field across the Channel on Gate Staked NCFET for Analog/Switching Performance", *Physica Scripta*. 2024 (SCIE index, Impact Factor: 2.8).

#### Chapter Contributed in Books (3):

1. Yash Pathak, Kajal Verma, Bansi Dhar Malhotra, and Rishu Chaujar "TCAD Analysis of Linearity Performance on Modified Ferroelectric Layer in FET Device with Spacer", Advanced Nanoscale MOSFET architectures: Current Trends and Future Perspectives (pp. 113-123), Wiley, 2023.

- Yash Pathak, Anshul, Bansi Dhar Malhotra, and Rishu Chaujar "Dielectric-modulated Gate Engineered NCFET as a label-free biosensor", *LNEE Proceedings, Scopus indexed*, Springer, 2024. (Accepted).

- Yash Pathak, Rashi Mann, Bansi Dhar Malhotra, and Rishu Chaujar "Numerical Study on Impact of Sensing Film on modified ISFET for improved analog performance", *LNEE Proceedings, Scopus indexed*, Springer, 2024. (Accepted).

#### Article in International Conferences (4):

- Yash Pathak, Bansi Dhar Malhotra, and Rishu Chaujar "Tcad analysis and simulation of double metal negative capacitance fet (dm ncfet)", 2021 Devices for Integrated Circuit (DevIC). Kalyani, India, pp. 224–228, 2021.

- Yash Pathak, Bansi Dhar Malhotra, and Rishu Chaujar "A numerical study of analog parameter of negative capacitance field effect transistor with spacer", 2021 7th International Conference on Signal Processing and Communication (ICSC). Noida, India, pp. 277–281, 2021.

- Yash Pathak, Bansi Dhar Malhotra, and Rishu Chaujar "Linearity Performance of Double Metal Negative Capacitance Field-Effect Transistors: A Numerical Study", 2022 IEEE VLSI Device Circuit and System (VLSI DCS). Kolkata, India, pp. 19–23, 2022.

- Yash Pathak, Bansi Dhar Malhotra, and Rishu Chaujar "Impact of Temperature on Negative Capacitance FET: A TCAD Simulation Study", 2023 2nd Edition of IEEE Delhi Section Flagship Conference (DELCON). Rajpura, India, pp. 1–4, 2023.

#### Communicated Journal Paper (2):

- Yash Pathak, Laxman Prasad Goswami, Bansi Dhar Malhotra, and Rishu Chaujar "Artificial Neural Network based Modelling for Variational Effect on Double Metal Double Gate Negative Capacitance FET using Machine Learning Approach", *IEEE Transactions on Electron device*. 2024.

- 2. Yash Pathak, Bansi Dhar Malhotra, and Rishu Chaujar "Synthesis of SnO2 based study using DFT and Experimental result", *IEEE Transaction Nanotechnology*, *IEEE*. 2024.

# Chapter 1

# Introduction

- \* This chapter provides a comprehensive overview of the research work, focusing primarily on the significance of NCFET in the low power memory device and the modern integrated circuit industry.

- \* Following that, this chapter includes a review of several engineering techniques for reducing short channel effects(SCEs), such as planar NCFET, junctionless engineering, NC FinFET, NC TFET, and Fe-Ins-FET as reported in various research articles.

- \* Moreover, NCFET is covered in the chapter as a possible solution to the issues. The chapter then goes on to discuss the basic design of NCFETs, their classification, their basic operation, potential advantages, and the technological difficulties incurred in NCFETs.

- \* The chapter concludes with a summary of all the chapters and an outline of the research objectives for the thesis.

#### 1.1 Background

Jack Kilby independently developed the concept of the integrated circuits (ICs) while employed at Texas Instruments in 1958, which transformed the electronic world (Sax09). Moore's law served to reduce Complementary Metal-Oxide-Semiconductor (CMOS) technology, which in turn fueled the development of ICs. Moore's Law, named after Gordon Moore, an Intel co-founder, is credited with coining the Moore's Law, which states that a chip's transistor count doubles every two years (Moo98). Figure 1.1 reveals (a) the curve showing increase in number of transistors per microprocessor with the increasing time (hpm), and (b) trend of decreasing length of gate for mosfet with time along with exponential scaling trend of transistors according to International Technology Roadmap for Semiconductors (ITRS) target (Rad13). The performance of ICs has greatly enhanced as transistor's size has been reduced and more densely integrated on a chip, resulting in reduced cost and power consumption. This tendency has enabled the extensive use of diverse range of electronic devices, including personal computers, cellphones, and modern medical equipment, as well as autonomous vehicles (Kum24).

**Figure 1.1:** The plot of (a) No. of Transistor per Microprocessor vs Year (hpm) (b) MOSFET Gate Length vs Year (Rad13).

Nevertheless, achieving this reduction in size to the nanoscale is very challenging owing to constraints such as higher leakage current, elevated power consumption, SCEs, quantum phenomena, and heat dissipation problems, etc (Kuh11; RMMM03). The drain potential starts to impact the electrostatics of the channel in highly scaled MOSFETs, leading to an increased leakage current between the drain and the source. Furthermore, transistors are prone to significant SCEs, including threshold voltage ( $V_{th}$ ) roll-off, which contribute to power dissipation, drain induced barrier lowering, and subthreshold slope (XLX<sup>+</sup>13; CK04). The primary issue with conventional integrated circuits and systems based on CMOS technology is increasing power consumption. Due to the ability to reduce supply voltages using steep-subthreshold swing Field Effect Transistor devices, they have been proposed as a viable option for future circuits and systems that prioritize energy efficiency (RTU21).

**Figure 1.2:** (a) The advancement of semiconductor FET vs SS (RTU21) (b)The graph of drain current vs gate voltage for MOSFET and NCFET (LSH<sup>+</sup>23).

The scientific and academic communities have shown significant interest in NCFETs. The notion of negative capacitance in a FET involves increasing the internal potential without changing the transport phenomenon of conventional MOSFETs. NCFETs have successfully achieved comparable switching at a lower supply voltage,  $V_{DD}$ , than conventional MOSFETs. The SS of NCFET is ideally less than 60mV/dec. as illustrated in Figure 1.2(a) (RTU21). The property of NCFETs that allows them to achieve low off-current ( $I_{off}$ ) and comparable on-current ( $I_{on}$ ) at low supply

Delhi Technological University, Delhi-42

voltages means that they work effectively at low switching voltage and with less power consumption as exhibited in Figure 1.2(b) (LSH<sup>+</sup>23). This can be accomplished by making minor adjustments to ordinary CMOS devices, i.e. by incorporating a small layer of ferroelectric material into the gate stack. This small change to a conventional MOSFET is aimed at NC, which is a distinctive feature of FE materials. Materials with non-linear dielectric behaviour are called FE materials. These materials exhibit a phenomenon called pre-existing polarization, which undergoes a reversal in direction when an external electric field is applied.

#### 1.2 Theory of NCFET

#### **1.2.1** Basic Structure of NCFET

The negative capacitance FET is a sophisticated variation of the FET that incorporates a ferroelectric material into the gate stack in order to attain a negative capacitance phenomenon. The presence of negative capacitance may address the drawbacks of traditional FETs by effectively decreasing the subthreshold swing to a level below the 60 mV/decade threshold. This, in turn, improves the performance and energy efficiency of the device.

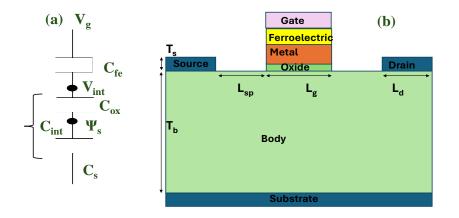

Figure 1.3 reflects the schematic diagram for (a) NCFET with Metal Ferroelectric Insulator Semiconductor (MFIS) configuration (Pah20), and (b) NCFET with Metal Ferroelectric Metal Insulator Semiconductor (MFMIS) configuration (PDAC18). The NCFET is characterized by its specific structure:

- 1. Substrate refers to the underlying substance, often silicon or another semiconductor, that serves as the basis for a transistor.

- 2. The source and drain of the FET are heavily doped areas in the substrate that facilitate the injection and extraction of charge carriers, which may be either electrons or holes.

- 3. The channel is the area located between the source and drain, where the charge carriers flow. The gate voltage regulates the conductivity of the channel.

- 4. The gate oxide, also known as the dielectric layer, is a thin insulating layer that separates the gate from the channel. Typically, in an NCFET, this layer consists of a high-k dielectric material, which enhances gate control and minimizes leakage currents.

- 5. The ferroelectric layer is the crucial element that distinguishes NCFETs from regular FETs. The ferroelectric layer, typically composed of hafnium oxide (HfO<sub>2</sub>) doped with dopants such as zirconium, silicon and aluminium, which has been proved to possess ferroelectricity, is positioned above the gate oxide. The ferroelectric material demonstrates a negative capacitance phenomenon, which augments the total gate capacitance and decreases the subthreshold swing.

- 6. The gate electrode refers to the uppermost layer of a device, often composed of metal or polycrystalline silicon. The gate electrode is used to administer a voltage that regulates the conductivity of the channel.

**Figure 1.3:** Schematic diagram for (a) NCFET with MFIS configuration (Pah20) (b) NCFET with MFMIS configuration (PDAC18)

#### 1.2.2 Ferroelectric Material

While discussing the materials exhibiting nonlinear polarization under the influence of electric field, there are two categories: one is paraelectric materials, which give enhanced nonlinear polarization and no polarisation occurs even in absence of electric field as shown in Figure 1.4(a), while the other is ferroelectric materials, which give non zero spontaneous polarization that exhibit two possible states of polarization even in the absence of electric field as illustrated in Figure 1.4(b). The polarization is directly proportional to an electric field applied in the ferroelectric material. Even when the electric field is no longer present in the ferroelectric material, the remnant polarisation remains as depicted in the hysteresis loop owing to the material's inherent spontaneous polarization.

**Figure 1.4:** The plot of polarisation vs electric field for (a) paraelectric and (b) ferroelectric (DDVK22). Atomic structure of  $Pb^{2+}Ti^{4+}O_3^{6-}$  for (c) paraelectric (d) ferroelectric with up polarisation (e) ferroelectric with down polarisation (WYSK15).

Figure 1.4 reveals the atomic structure of lead titanate (PbTiO<sub>3</sub>) for (c) paraelectric and (d) ferroelectric with up polarisation (e) ferroelectric with down polarisation (WYSK15). The centrosymmetric property and linear dielectric are in paraelectic material. The non-centrosymmetric property and non-linear dielectric are in ferroelectric material (RAT07; Kha15).

The L-K and Miller models are often used to elucidate the polarisation (P) and voltage across ferroelectric (FE) materials (SDG18; LK54; Son05). However, L-K has received greater recognition. This section has focused on the L-K model. The Landau–Khalatnikov (L–K) equation is a dynamic formulation of the Landau–Devonshire theory as shown in Eq. 1.1. The L–K equation is a very useful tool for comprehending the ferroelectric switching features in the development of NCFET technology (SDG18; SD08). The Landau theory of nonlinear dielectric is given below:

$$G = \alpha P^{2} + \beta P^{4} + \gamma P^{6} - EP, \alpha = \alpha_{0}[T - T^{0}]$$

(1.1)

Here, G is free energy density,  $\alpha$ ,  $\beta$ ,  $\gamma$  are landau coefficients, P is polarization, and E is an electric

field.

The concept of negative capacitance is explained using the L–K equation, which describes the relationship between polarisation (P) and voltage (V) in a steady-state condition. In this equation, there is a region where the derivative of polarisation with respect to voltage is negative. The L-K model describes the temporal changes in the polarisation of a ferroelectric material. The L–K model also describes the charge–voltage characteristic of the ferroelectric material as depicted in Eq. 1.2. The landau Khalanikov (L-K) theory is given below:

$$\delta \frac{\partial P}{\partial t} = -\frac{\partial G}{\partial P} \tag{1.2}$$

here,  $\delta$  is polarisation damping factor, P is polarization. On differentiating the Eq. 1.1 w.r.t. P, we get the electric field (E) by Eq. 1.3,

$$E = 2\alpha P + 4\beta P^3 + 6\gamma P^5 \tag{1.3}$$

If E=0 means polarisation for paraelectric is zero (P=0) as shown in Figure 1.4(a) and (c), but polarisation for ferroelectric (P) =0, + P<sub>r</sub>, - P<sub>r</sub>. The two state of polaristion is formation for ferroelectric material by Eq. 1.4.

$$P_{\rm r} = + -\sqrt{(\sqrt{\beta^2 - 3\alpha\gamma} - \beta)/3\gamma} \tag{1.4}$$

#### 1.2.3 Operation of NCFET

The NCFET's ferroelectric layer demonstrates a phenomenon known as negative capacitance, which can be comprehended using the Landau-Khalatnikov theory of ferroelectrics. The voltage is applied to the gate causes the ferroelectric layer to polarise, resulting in an amplification of the gate voltage. This amplification reduces the voltage needed to turn on and off of the transistor. Consequently, this leads to a more pronounced subthreshold slope and enhanced switching properties in comparison to conventional FETs. The subthreshold swing (SS) is becoming the primary characteristic for low-power devices, as it determines their behavior in the subthreshold region using the equivalent capacitance model and device structure of NCFET as reveals in Figure 1.5(a) and (b) respectively. In conventional MOSFETs, the subthreshold slope is mathematically defined as the ratio of the logarithm of the change in drain current to the change in gate-source voltage. The logarithm of the drain current ratio represents the rate of change of the drain current. The SS of a FET device is the inverse of the subthreshold slope. Classical MOS devices experience a voltage sag of about 60 mV per decade at a temperature of 300 K, often referred as the "Boltzmann tyranny" (BCBD19; ZLH<sup>+</sup>19). To address these restrictions, researchers have created and improved a number of field-effect transistor devices that have a sharp subthreshold swing characteristic. The steady-state behavior of classical MOS devices is represented by the following model to show the SS by Eq. 1.5, Eq. 1.6, and Eq. 1.7:

$$SS = \frac{\partial V_{\rm g}}{\partial \log_{10}(I_{\rm d})} \tag{1.5}$$

$$SS = \frac{\partial V_{\rm g}}{\partial V_{\rm int}} \times \frac{\partial V_{\rm int}}{\partial \psi_{\rm s}} \times \frac{\partial \psi_{\rm s}}{\partial \log_{10}(I_{\rm d})}$$

(1.6)

$$SS = \frac{1}{A_{\rm v}} \times \frac{1}{m} \times \frac{\partial \psi_{\rm s}}{\partial \log_{10}(I_{\rm d})}$$

(1.7)

$$A_{\rm v} = \frac{\partial V_{\rm int}}{\partial V_{\rm g}} = \frac{C_{\rm fe}}{C_{\rm fe} + C_{\rm int}} \tag{1.8}$$

here, m is body factor,  $A_v$  is amplification factor, and  $A_v$  is greater than 1 in Eq. 1.8,  $C_s$  is negative, then body factor is always less than 1 as shown in Eq. 1.9.

$$m = \frac{\partial \psi_{\rm s}}{\partial V_{\rm int}} = (1 + \frac{C_{\rm s}}{C_{\rm ox}})^{-1}$$

(1.9)

The negative capacitance might be used to get high on the current and steep subthreshold swing. Recently, the phenomena of negative capacitance have been demonstrated in different systems experimentally: (i) superlattice, (ii) ferroelectric dielectric bilayer, and (iii) isolated ferroelectric

**Figure 1.5:** (a) Schematic diagram for equivalent capacitance model of NCFET and (b) Device structure of NCFET (Pah20).

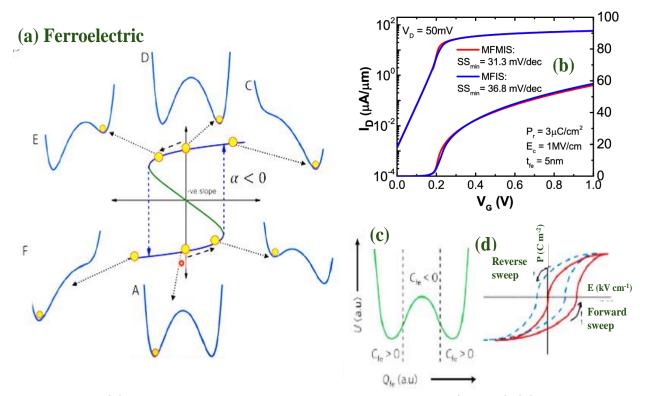

film. The ferroelectric material is exploited to obtain the phenomenon of negative capacitance with negative slope of the curve as depicted in Figure 1.6(a). The steeper slope of negative capacitance is shown in Figure 1.6(b), which illustrates the curve of drain current and gate voltage for conventional MFIS vs MFMIS. MFMIS structure shows lower subthreshold swing as compared to MFIS. When we work on ferroelectric materials to exploit the property of negative capacitance, The unstable point on ferroelectric material gives negative capacitance phenomenon thus NCFET. It is difficult to reach the atom from left stable state to right stable state, also shown in Figure 1.6(c). So, the applied voltage should be higher than the coercive voltage, which can be defined as the voltage at which the net polarization of ferroelectric is zero, resulting in the creation of the metastable state that facilitates the negative capacitance phenomenon. Figure 1.6(d) illustrates the curve of polarisation vs electric field to represent the hysteresis loop for forward and backward sweeps. It also shows remnant polarisation and coercive field.

#### **1.2.4** NCFET Device Engineering

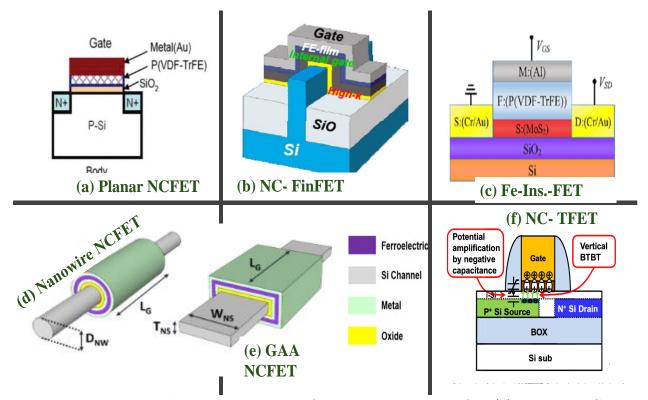

NCFETs exist in several forms, distinguished by the precise manner in which the ferroelectric material is incorporated into the device structure. The following are the main categories of NCFETs as shown in Figure 1.7(a)-(f):

Figure 1.6: (a) The plot of polarisation vs electric field for NC (Kha15) (b) Drain current vs gate voltage graph for MFIS vs MFMIS (CB20) (c) Energy vs charge graph (MCM22) (d) Hystresis curve for NC.

1. Planar NCFET (Two-dimensional Nanoscale Channel NCFET): In planar NCFETs, the ferroelectric material is included into the gate stack of a conventional planar FET device. This variant is similar to traditional planar MOSFETs, except it has an extra ferroelectric layer as reveals in Figure 1.7(a).

Composition: The gate stack comprises a metallic gate, a ferroelectric layer, and a high-k dielectric layer, usually positioned above a silicon channel. It is well-suited for planar technology nodes and provides a more straightforward integration route with current planar CMOS processes.

2. NC FinFET: NC FinFET refers to a kind of transistor known as a Fin FET (FinFET) that integrate the ferroelectric layer into the gate stack of FinFETs, which are three-dimensional devices with channel as fins as shown in Figure 1.7(b).

Configuration: The ferroelectric layer is encased around the vertical fins that create the channel, together with a high-k dielectric and metal gate. It enhances electrostatic control in the channel, making it ideal for advanced technology nodes that use FinFETs to mitigate short-channel effects. 3. Fe-Ins-FET: The Ferroelectric-Insulator-FET (Fe-Ins-FET) is a kind of field-effect transistor that utilizes a ferroelectric insulator material. In Fe-Ins-FETs, the ferroelectric layer is integrated with an insulating layer instead of being directly connected to the semiconductor channel as shown in Figure 1.7(c).

Composition: The gate stack consists of a ferroelectric layer positioned above a conventional high-k dielectric, which is then followed by the metal gate. This engineering combines the advantageous characteristics of ferroelectric materials with the insulating capabilities of high-k dielectrics. It is well-suited for a range of applications that need both high performance and low power consumption.

**Figure 1.7:** The schematic diagram of device engineering for (a) Planar NCFET (TWW<sup>+</sup>18) (b) NC FinFET (TWW<sup>+</sup>18)(c) Fe-Ins-FET (LKSH16) (d) Nanowire NCFET (SHH20) (e) GAA NCFET (SHH20) (f) NC-TFET (TWW<sup>+</sup>18).

4. Nanowire NCFET (Junctionless Nanowire Channel NCFET): Junctionless NCFETs distinguish themselves from conventional FETs by lacking a clearly defined source and drain junction as shown in Figure 1.7(d).

Structure: The channel area has a uniform distribution of dopants, and the flow of current is regulated by the voltage applied to the gate. Negative capacitance is achieved by integrating

Delhi Technological University, Delhi-42

a ferroelectric layer into the gate stack of nanowired channel FET. Its advantage is streamlined manufacturing by removing the need for accurate connection creation, which might be beneficial for reducing device size.

5. GAA NCFET (Gate-All-Around (GAA) NCFET): GAA NCFETs use a gate-all-around architecture, whereby the gate completely encloses the channel from all directions, therefore including the ferroelectric material in this arrangement as shown in Figure 1.7(e).

Composition: The channel is often constituted by nanowires or nanosheets, encased by a ferroelectric layer, high-k dielectric, and metal gate. Its advantage is providing superior electrostatic control, making it ideal for cutting-edge technological nodes and future iterations of highly miniaturized transistors.

6. NC-TFET (Negative Capacitance Tunnel FET): It is a type of field-effect transistor that combines the principles of negative capacitance and tunneling to achieve enhanced performance characteristics. This device leverages the unique properties of a ferroelectric material to provide negative capacitance, which help in further reducing the steep subthreshold characteristics of TFET thus give the super steep subthreshold swing as shown in Figure 1.7(f).

As different types of NCFETs depending on their structural integration with ferroelectric materials and engineering have been discussed above, each configuration has distinct benefits but also poses various obstacles on the incorporation of materials. Thus thorough and detailed engineering and optimisation are necessary to properly exploit the capabilities of NCFETs in different applications and technology nodes.

# 1.3 Advantages of NCFET

NCFETs provide numerous notable benefits compared to ordinary FETs, principally attributable to the distinctive characteristics of the ferroelectric material used in their gate stack. The following are the primary benefits:

- 1. Steep Subthreshold Swing: