# INTEGERATED CONTROL STRATEGIES FOR CUK CONVERTER

A DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE AWARD OF THE DEGREE

OF

MASTER OF TECHNOLOGY

IN

### POWER ELECTRONICS AND SYSTEMS

Submitted by:

### PRAANSHU SRIJAN SHANDILYA

2K22/PES/10

Under the supervision of

### **PROF.DHEERAJ JOSHI**

(Professor, EED, DTU)

### PROF.NARENDRA KUMAR

(Professor, EED, DTU)

# DEPARTMENT OF ELECTRICAL ENGINEERING DELID TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

JUNE, 2024

**Q**.a.

### DEPARTMENT OF ELECTRICAL ENGINEERING

#### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

# **DECLARATION**

I, Praanshu Srijan Shandilya, Roll No. 2K22/PES/10 student of M.Tech (Power Electronics and Systems), hereby declare that the project Dissertation titled **"Integrated Control Strategies for Cuk Converter"** which is submitted by me to the Department of Electrical Engineering Department, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is original work and not previously used for the award of any Degree.

Place: Delhi Date: T11 June 2024 PRAANSHU SRIJAN SHANDILYA

### DEPARTMENT OF ELECTRICAL ENGINEERING

#### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

# **CERTIFICATE**

This is to certify that the dissertation entitled "Integrated Control Strategies for Cuk Converter" being submitted by PRAANSHU SRIJAN SHAND IL YA (2K22/PES/10) in partial fulfillment of the requirements for the award of Master of Technology degree in "ELECTRICAL ENGINEERING" with specialization of "POWER ELECTRONICS & SYSTEMS" at the Delhi Technological University is an authentic work carried out by him under my supervision and guidance. To the best of my knowledge, the matter embodied in the thesis has not been submitted to any other University/Institute for the award of any degree or diploma.

# Prof DHEERAJ JOSHI

### SUPERVISOR

Electrical Engineering Department Delhi Technological University

#### Prof. NARENDRA KUMAR- II

#### **CO-SUPERVISOR**

Electrical Engineering Department Delhi Technological University

# ACKNOWLEDGEMENT

I would like to express my deepest gratitude to my supervisors, **Prof. Dheeraj Joshi** and **Prof. Narendra Kumar**, for their invaluable guidance, continuous support, and encouragement throughout the course of this research. Their expertise and insights have been instrumental in the completion of this thesis.

I extend my heartfelt thanks to **Mr. Ashutosh Gupta** for his guidance and help. His valuable feedback and suggestions have significantly contributed to the refinement of my work.

I am profoundly grateful to **my mother**, Premlata Kumari, for her unwavering support and encouragement. Her sacrifices and constant belief in me have been a source of strength throughout my academic journey. I would also like to thank my uncles, Pankaj Kumar and Manoj Sharma, for their support and encouragement.

Special thanks to my beloved grandparents, Sohan Sharma and Veena Devi, for their love, wisdom, and blessings. Their unwavering faith in my abilities has always motivated me to strive for excellence.

Finally, I would like to acknowledge the support and camaraderie of my peers and batchmates. Their companionship and collaborative spirit have made this journey enjoyable and enriching.

Thank you all for your encouragement, support, and contributions to this thesis.

PRAANSHU SRIJAN SHANDILYA

# ABSTRACT

This thesis explores the design, analysis, modeling, and control of DC-DC converters, which are essential components in contemporary electronic systems valued for their efficiency, compactness, and reliability. With their wide range of uses in various industries like computer power supplies, aerospace, medical, and telecommunications, it is crucial for these converters to deliver a stable DC output voltage even in the face of fluctuating input voltage and varying load currents.

Within the parameters of this study, particular focus is made to the Cuk converter in both ideal and non-ideal forms. Starting with important design issues, the paper improves the duty cycle, inductor, and capacitor calculations by including actual non-ideal factors. Especially in the performance of capacitors, a thorough study of output voltage ripple emphasizes even more the importance of the equivalent series resistances (ESRs). The thesis discusses the development of a comprehensive mathematical model that encompasses all aspects of the converter, including both ideal and non-ideal elements. Through the utilization of advanced techniques like state-space averaging and averaged switch modeling, a highly accurate model is created that closely resembles the dynamic and steady-state characteristics of real converters.

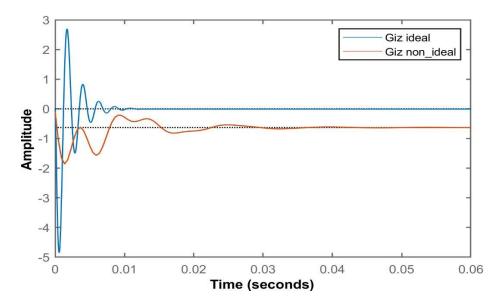

Comparative study of the ideal model and the one with non-ideal components confirms the better accuracy of the latter, more precisely reflecting what practitioners could expect from real-world operations of DC-DC converters.

This work investigates improving the performance of both ideal and non-ideal Cuk converters by means of several control techniques including sliding mode controllers, PI-lead controllers, and PI controllers in the final part. Furthermore, it evaluates the sliding mode controller's performance against the conventional two-loop PI controller configuration, therefore providing insightful analysis on how to maximize converter efficiency using sophisticated control techniques.

All things considered, this study holistically covers the essential characteristics of DC-DC converters and provides important new perspectives on their optimization achieved with creative control strategies. The result opens the path for improved performance in electronic systems where such converters are essentially supporting.

# **TABLE OF CONTENTS**

| Title                | Page No. |

|----------------------|----------|

| DECLARATION          | i        |

| CERTIFICATE          | ii       |

| ACKNOWLEDGEMENT      | iii      |

| ABSTRACT             | iv       |

| TABLE OF CONTENTS    | v        |

| LIST OF ABBREVIATION | vi       |

| LIST OF FIGURES      | vii      |

| LIST OF TABLES       | viii     |

#

| 1.2 | Introduction to DC - DC Converters:                 | 3                                                  |

|-----|-----------------------------------------------------|----------------------------------------------------|

| 1.3 | Motivation for the research                         | 5                                                  |

| 1.4 | Contribution of the Author                          | 7                                                  |

| CH  | HAPTER 2 DESIGN OF DC-DC CONVERTERS                 | 9                                                  |

| 2.1 | Introduction                                        | ,                                                  |

| 2.2 | Analysis of Ideal Cuk DC- DC Converter 1            | l                                                  |

| 2.2 | 2.1 Mode 1 of operation $0 < t < DTS$               | 2                                                  |

| 2.2 | Mode 2 of operation $DTs < t < (1 - DTs)$           | 3                                                  |

| 2.2 | 2.3 Steady state analysis                           | 5                                                  |

| 2.2 | 1.4 Inductor current ripple and Inductor design 1   | 7                                                  |

|     | 1.3<br>1.4<br>CH<br>2.1<br>2.2<br>2.2<br>2.2<br>2.2 | <ul> <li>1.3 Motivation for the research</li></ul> |

| 2.  | .2.5 | Output Voltage ripple and capacitor design:           |

|-----|------|-------------------------------------------------------|

| 2.  | .2.6 | Results and discussion                                |

| 2.3 | Ana  | alysis of Non ideal Cuk converter                     |

| 2.  | 3.1  | Mode 1 of operation $0 < t < DTS$                     |

| 2.  | .3.2 | Mode 2 of operation $DTs < t < (1 - DTs)$             |

| 2.  | .3.3 | Steady state analysis                                 |

| 2.  | .3.4 | Inductor current ripple and inductor design:          |

| 2.  | .3.5 | Capacitor design                                      |

| 2.  | .3.6 | Results and discussion:                               |

| 2.4 | Cor  | nelusion                                              |

| C   | HAP  | FER 3 MODELLING OF DC-DC CONVERTERS 40                |

| 3.1 | Intr | oduction                                              |

| 3.2 | Stat | e Space Averaging Modelling Technique                 |

| 3.  | .2.1 | Small signal Ac model:                                |

| 3.  | .2.2 | Modelling of Ideal Cuk converter45                    |

| 3.  | 2.3  | Modelling of Non-Ideal Cuk converter                  |

| 3.3 | Cor  | nparison of ideal and Non-ideal Cuk Converter Models: |

| 3.  | .3.1 | Steady state model:                                   |

| 3.  | .3.2 | Small Signal Model                                    |

| 3.4 | Cor  | nelusion                                              |

| С   | HAP  | FER 4 CONTROL OF DC-DC CONVERTERS                     |

| 4.1 | Intr | oduction                                              |

| 4.2 | Cor  | ntrol of DC-DC Cuk Converter                          |

| 4.  | .2.1 | PI CONTROLLER DESIGN FOR IDEAL CUK CONVERTER73        |

| 4.  | .2.2 | PID CONTROLLER DESIGN OF IDEAL CUK CONVERTER 84       |

| 4.2.3 | PI CONTROLLER DESIGN FOR AN NON-IDEAL CUK   |

|-------|---------------------------------------------|

| 4.2.3 | FI CON I KOLLEK DESIGN FOK AN NON-IDEAL CUK |

|     | CC  | )NVE  | ERTER                                                            |

|-----|-----|-------|------------------------------------------------------------------|

|     | 4.2 | .4    | PID controller design for a Non-Ideal Cuk converter 101          |

| 4.3 | 3   | Con   | clusion 109                                                      |

|     | CE  | IAPT  | TER 5 SLIDING MODE CONTROL OF CUK CONVERTER .111                 |

| 5.  | 1.  | Intro | oduction 111                                                     |

| 5.  | 2.  | Cuk   | Converter:                                                       |

|     | 4.3 | .1    | Dynamic Equations of CUK Converter: 113                          |

| 5.  | 3.  | Des   | ign of sliding mode control for Cuk converter 115                |

|     | 5.4 |       | Defining of Control equivalent model: 116                        |

|     | 5.4 | .1.   | Derivation of equivalent control law: 118                        |

|     | 5.4 | .2.   | Existence and stability conditions: 119                          |

| 5.: | 5.  | Con   | nparison Between A PI Controller And Sliding Mode Controller 123 |

|     | 5.5 | .1.   | Output voltage comparison 123                                    |

|     | 5.5 | .2.   | Reference voltage tracking 124                                   |

|     | 5.5 | .3.   | Load Variation Transients 125                                    |

|     | 5.5 | .4.   | Input Voltage Variation Transients                               |

| 5.  | 6.  | Con   | clusion 127                                                      |

|     | CE  | IAPT  | TER 6 CONCLUSION AND FUTURE SCOPE 129                            |

| 6.  | 1.  | Con   | clusion                                                          |

| 6.  | 2.  | Futi  | Ire Scope                                                        |

|     | LI  | ST O  | F PUBLICATIONS 132                                               |

|     | RE  | FER   | ENCES 133                                                        |

# **LIST OF FIGURES**

| Fig 1.1 Applications of Power Electronics systems                                      |

|----------------------------------------------------------------------------------------|

| Fig 1.2 Classification of DC-DC Converters                                             |

| Fig 2.1 Schematic Diagram of Cuk Converter 12                                          |

| Fig 2.2 Mode of operation (a) Mode 1 (b) Mode 2 14                                     |

| Fig 2.3 Switching Waveforms of Cuk DC-DC Converter 15                                  |

| Fig 2.4 Output Voltage Variation with Duty Cycle 17                                    |

| Fig 2.5 Variation of inductance with Duty Cycle (a) $L_1$ (b) $L_2$ 19                 |

| Fig 2.6 Charging and Discharging behaviour of Capacitor ClandC221                      |

| Fig 2.7 Duty Cycle Vs Output Voltage                                                   |

| Fig 2.8 Output Voltage response at rated conditions                                    |

| Fig 2.9 Ripple Voltage variation with switching frequency for (a) $C_1$ (b) $C_2$ 24   |

| Fig 2.10 Relation of frequency with inductance (a) $L_1$ (b) $L_2$                     |

| Fig 2.11 Schematic diagram of Non- Ideal Cuk Converter                                 |

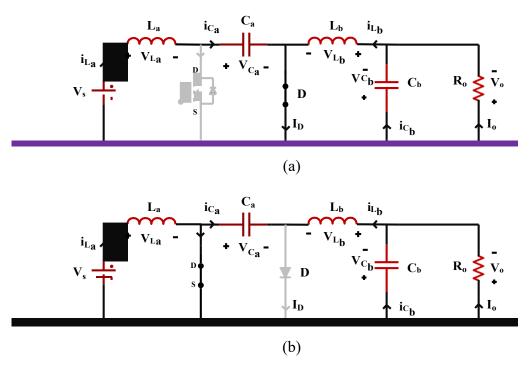

| Fig 2.12 Modes of operation (a) Mode 1 (b) Mode 2                                      |

| Fig 2.13 Output voltage of Non-ideal Cuk converter as a function of duty cycle 32      |

| Fig 2.14 Current and ripple voltage waveforms associated with capacitor $C_1$ 36       |

| Fig 2.15 Current profiles of energy storing elements                                   |

| Fig 2.16 Output voltage response of ideal cuk converter at $D = 0.66$                  |

| Fig 2.17 Output voltage response of Non-ideal Cuk converter at $D = 0.725$             |

| Fig 3.1 Circuit diagram of ideal Cuk converter (a) equivalent circuit during switch-   |

| on (b) equivalent circuit during switch-off                                            |

| Fig 3.2 Circuit diagram of non-ideal DC-DC Cuk converter (b) equivalent circuit        |

| during switch-on (c) equivalent circuit during switch of                               |

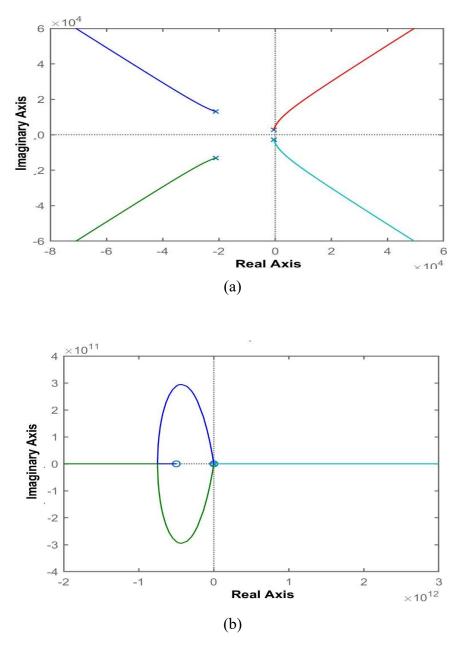

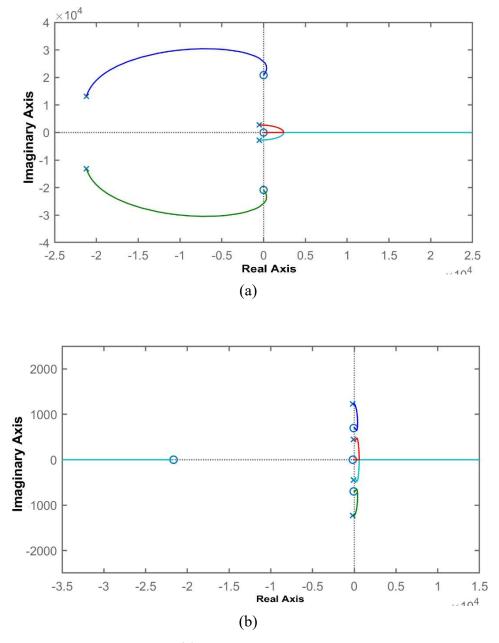

| Fig 3.3 Root locus plot of Line to output transfer function (a) Ideal (b) Non-Ideal 61 |

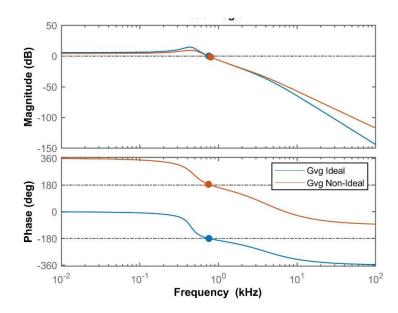

| Fig 3.4 Frequency response of Ideal and Non ideal line to output transfer function     |

|                                                                                        |

| Fig 3.5 Step response comparison of Ideal and Non ideal line to output transfer        |

| function                                                                               |

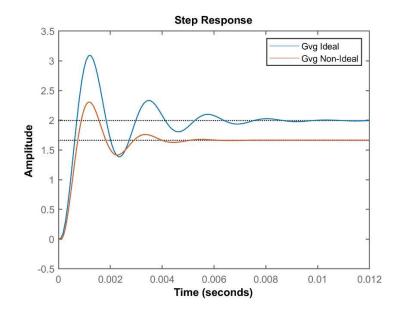

| Fig 3.6 Root locus plot of Line to output transfer function (a) Ideal (b) Non-Ideal 64 |

|                                                                                        |

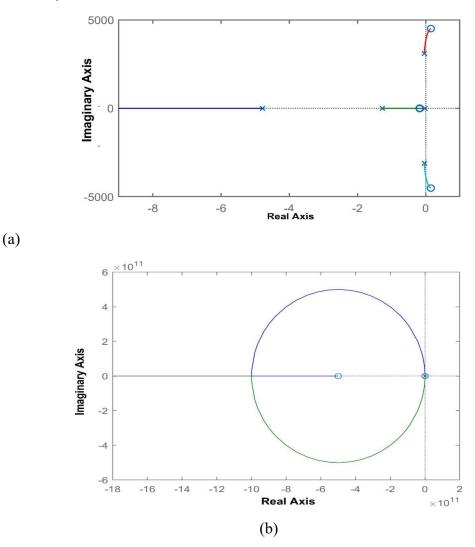

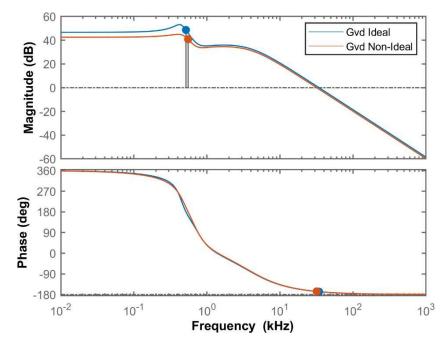

| Fig 3.7 Frequency response comparison of $Gvd(s)$ for ideal and non ideal case 65               |

|-------------------------------------------------------------------------------------------------|

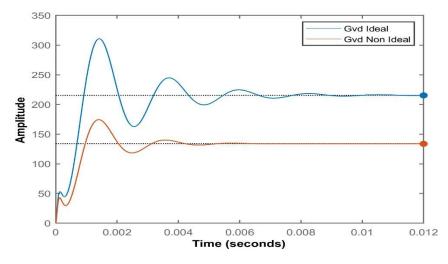

| Fig 3.8 Comparison of step responses of $Gvd(s)$ for ideal and non-ideal case 65                |

| Fig 3.9 Root locus plot for <i>Gvzs</i> for ideal and non-ideal case                            |

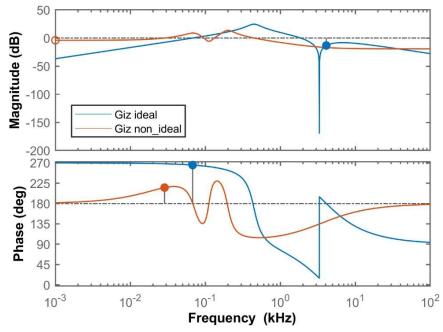

| Fig 3.10 Comparison of Bode plots of $Gvz(s)$ for ideal and non-ideal case                      |

| Fig 3.11 Comparison of step responses of Gvzs for ideal and non-ideal case                      |

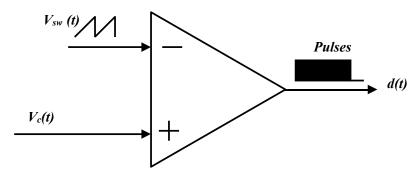

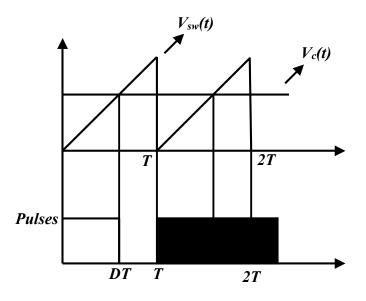

| Fig 4.1 Pulse width modulator circuit                                                           |

| Fig 4.2 Waveforms of Pulse Width Modulator                                                      |

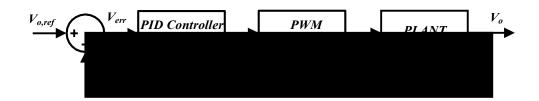

| Fig 4.3 Voltage mode control algo using PI controller                                           |

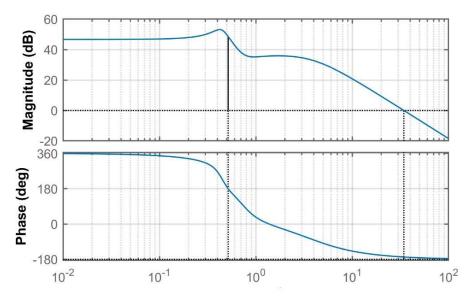

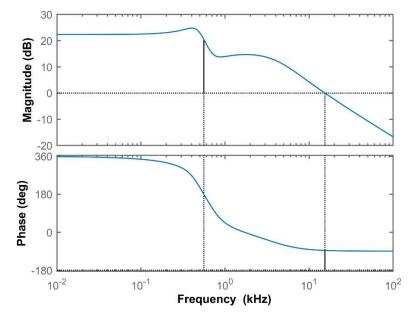

| Fig 4.4 Bode plot of Uncompensated Transfer function76                                          |

| Fig 4.5 Frequency response of PI controlled DC-DC Cuk Converter                                 |

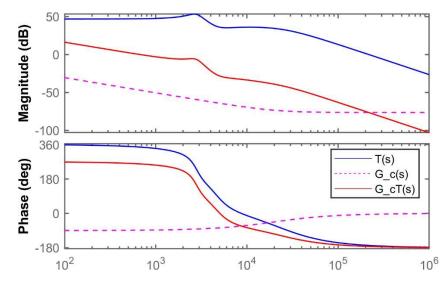

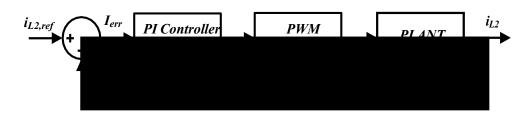

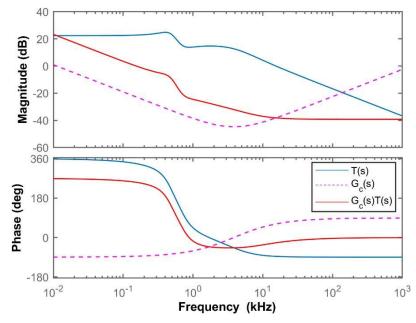

| Fig 4.6 Current mode control algo using PI control                                              |

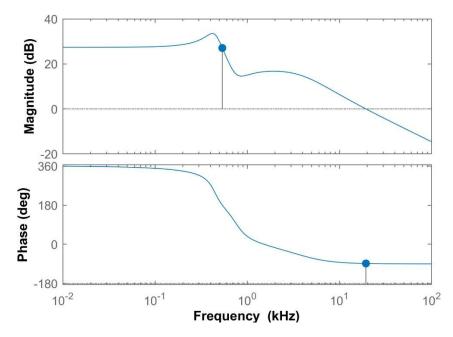

| Fig 4.7 Frequency response of uncompensated Cuk Converter                                       |

| Fig 4.8 Frequency response of PI controlled DC-Dc Cuk converter                                 |

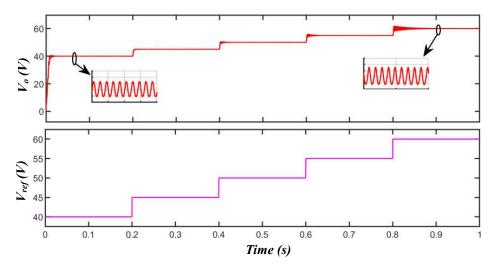

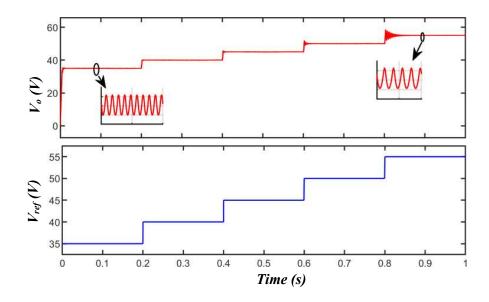

| Fig 4.9 Simulation results for reference variation from 40V to 60V                              |

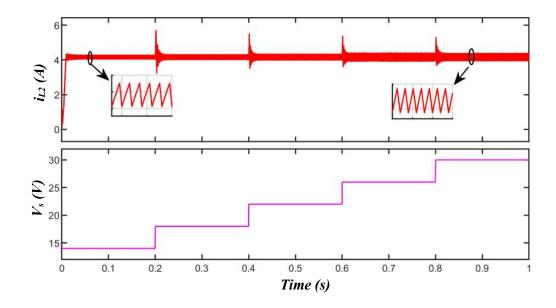

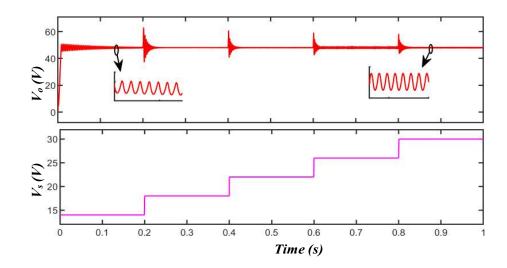

| Fig 4.10 Line voltage variation from 14V to 30V                                                 |

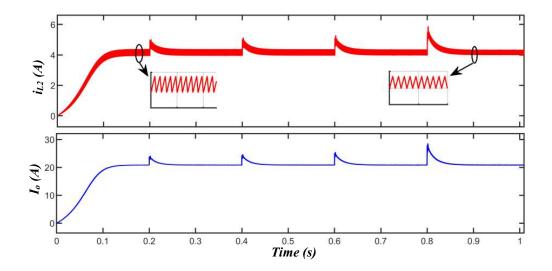

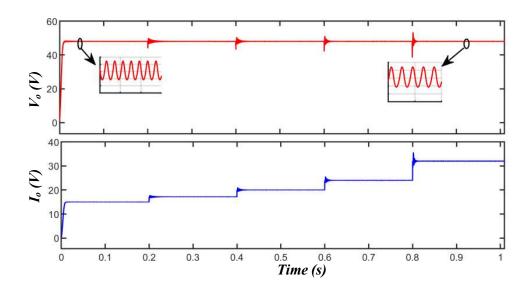

| Fig 4.11 Load variation from 16 $\Omega$ to 7.5 $\Omega$                                        |

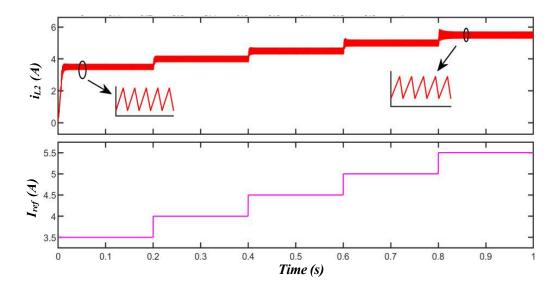

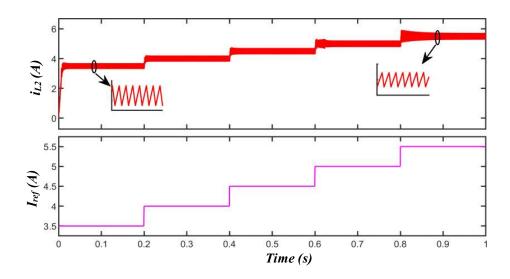

| Fig 4.12 Simulation result for reverence current variation from 3.5A to 5.5A 82                 |

| Fig 4.13Simulation results for line voltage variation from 14V to 30V                           |

| Fig 4.14Simulation of results for load resistance variation from 16 $\Omega$ to 7.5 $\Omega$ 83 |

| Fig 4.15Voltage mode control using PID Controller                                               |

| Fig 4.16Frequency response of PID Controlled Cuk Converter                                      |

| Fig 4.17Current mode control using PID Controller                                               |

| Fig 4.18Frequency response of Uncompensated Cuk Converter                                       |

| Fig 4.19 Frequency response of PID controlled Cuk Converter                                     |

| Fig 4.20 Simulation results for reference voltage tracking from 40V to 60V                      |

| Fig 4.21 Simulation results for line voltage variation from 14V to 30V                          |

| Fig 4.22 Simulation results for load variation from 16 $\Omega$ to 7.5 $\Omega$                 |

| Fig 4.23 Simulation results for reference current variation from 3.5A to 5.5A 91                |

| Fig 4.24 Simulation results for line voltage variation from 14V to 30V                          |

| Fig 4.25 Simulation results for load resistance variation from 16 $\Omega$ to 7.5 $\Omega$      |

| Fig 4.26 Frequency response of Uncompensated Cuk Converter                                      |

| Fig 4.27 Frequency response of PI controlled Non-Ideal Cuk converter                            |

| Fig 4.28 Frequency response of PI controlled Non-Ideal Cuk converter                           |

|------------------------------------------------------------------------------------------------|

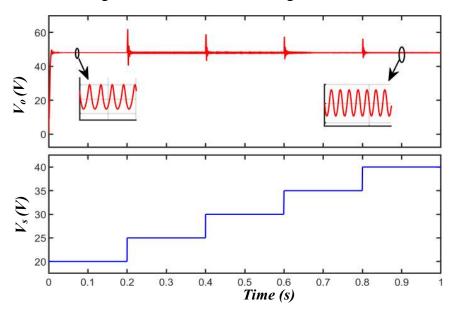

| Fig 4.29 Simulation results for reference voltage tracking from 40V to 60V                     |

| Fig 4.30 Simulation results for line voltage variation from 20V to 40V                         |

| Fig 4.31 Simulation results for load resistance variation from 16 $\Omega$ to 7.5 $\Omega$     |

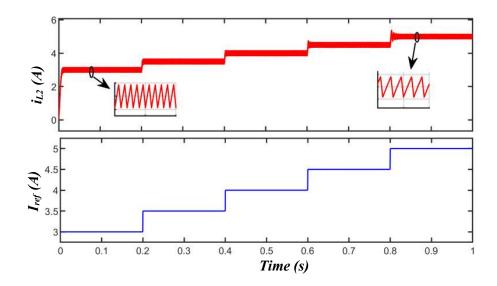

| Fig 4.32 Simulation results for reference current variation from 3A to 5A 100                  |

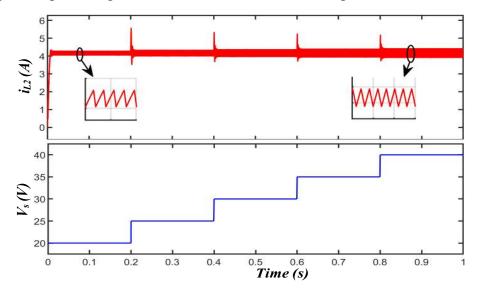

| Fig 4.33 Simulation results for line voltage variation from 20V to 40V 100                     |

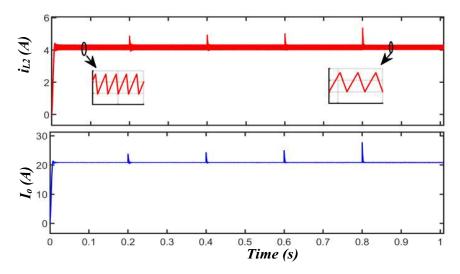

| Fig 4.34 Simulation results for load resistance variation from 16 $\Omega$ to 7.5 $\Omega$ 101 |

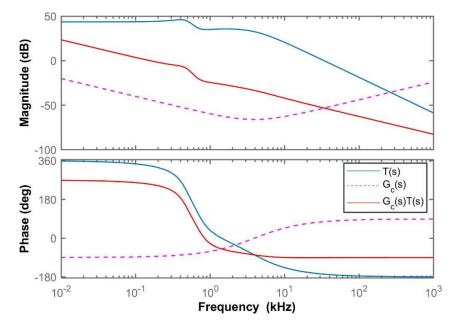

| Fig 4.35 Frequency response of PID controlled Non-Ideal Cuk converter                          |

| Fig 4.36 Frequency response of Uncompensated Cuk Converter 104                                 |

| Fig 4.37 Frequency response of PID controlled Non-Ideal Cuk converter                          |

| Fig 4.38 Simulation results for reference voltage tracking from 35V to 55V 106                 |

| Fig 4.39 Simulation results for line voltage variation from 20V to 40V 106                     |

| Fig 4.40 Simulation results for load resistance variation from 16 $\Omega$ to 7.5 $\Omega$ 107 |

| Fig 4.41 Simulation results for reference current variation from 3A to 5A 108                  |

| Fig 4.42 Simulation results for line voltage variation from 20V to 40V 108                     |

| Fig 4.43 Simulation results for load resistance variation from 16 $\Omega$ to 7.5 $\Omega$ 109 |

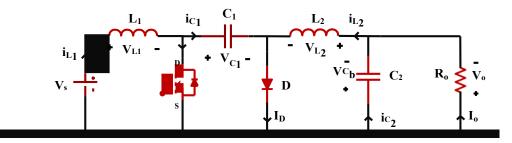

| Fig 5.1 Schematic Diagram of Ideal Cuk Converter 113                                           |

| Fig 5.2 Mode of Operation (a) Interval I (b) Interval II 114                                   |

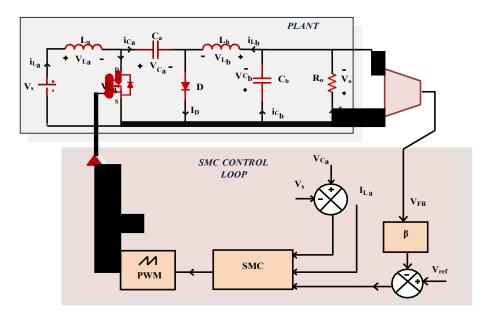

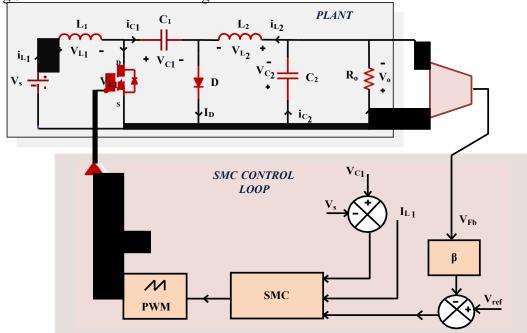

| Fig 5.3 Block diagram for sliding mode control of Cuk Converter 115                            |

| Fig 5.4 Control Scheme of Sliding Mode Control                                                 |

| Fig 5.5 Output Voltage Comparison between Sliding Mode Control and PI Control                  |

|                                                                                                |

| Fig 5.6 Reference Voltage tracking for : (a) SMC control (b) PI Control 125                    |

| Fig 5.7 Response of the Cuk converter under step variation of the load Resistance              |

| (a)SMC Control (b) PI Control 126                                                              |

| Fig 5.8 Response of the Cuk converter under step variation of the Line Voltage (a)             |

| SMC control (b) PI Control                                                                     |

# LIST OF TABLES

| Table 2.1 Ideal Cuk Converter Specifications                                 | 16 |

|------------------------------------------------------------------------------|----|

| Table 2.2 Non-Ideal Cuk Converter Specifications                             | 30 |

| Table 3.1 Steady state parameters for Ideal Cuk converter                    | 59 |

| Table 3.2 Steady state parameters for Non-Ideal Cuk converter                | 59 |

| Table 3.3 Comparison between steady state values of Ideal and Non- Ideal Cuk |    |

| Converter                                                                    | 60 |

| Table 4.1 Controller Design parameters for an Ideal Cuk Converter            | 74 |

| Table 4.2 Controller design parameters for Non-Ideal Cuk Converter           | 93 |

# CHAPTER 1 INTRODUCTION

### 1.1. Overview

In modern times, the availability of electrical power has become an essential requirement for both household appliances and industrial operations. There are diverse uses that necessitate electric power in distinct forms such as AC (Alternative current) or DC (direct current), constant or variable voltage, set or variable frequency, and so on. Typically, electrical power is provided to consumers in the form of AC with a consistent voltage magnitude and frequency (either 50 or 60 Hz). To be able to cater to the needs of diverse consumers, a wide range of power electronic converters have been developed. They have the ability to transform electrical power from one form to another as needed. It is crucial to acknowledge the extensive uses of power electronic converters across diverse industries, in addition to comprehending their complex workings. These converters play a crucial role in many advanced technologies, allowing for the efficient and dependable transformation of electrical power to fulfil a wide range of requirements. Power electronic converters are essential components in renewable energy systems as they transform energy from sources such as solar panels and wind turbines into electricity that can be used by households and businesses.

Similarly, converters in electric vehicles enable the transformation of battery electricity into the necessary energy to drive motors, ensuring a seamless and effective functioning. Furthermore, in portable electronic devices such as smartphones and laptops, DC-DC converters are used to control voltage levels to supply power to delicate electronic parts, hence enhancing battery life and overall performance. Researchers can improve the efficiency and reliability of existing systems and enable new applications in upcoming technologies by comprehending the principles and control mechanisms of power electronic converters.[1]-[5] There are four main categories of power to meet various demands: [6]-[9]:

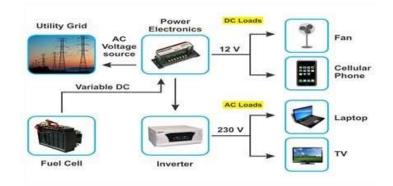

Fig 1.1Application of Power Electronics Converter Systems

- AC-DC Converters: These converters transform AC voltage into either fixed or variable DC voltage in a precise and efficient manner. For example, diode rectifiers are highly efficient at converting AC into fixed DC. On the other hand, phase-controlled rectifiers are more advanced and allow for the regulation of variable DC voltage by modulating the conduction angle.

- 2. **DC-AC Converters (Inverters)**: Responsible for converting DC input into AC output, inverters ensure the provision of the desired voltage and frequency by precisely adjusting the switch-on time of the components. This allows them to efficiently operate a wide range of loads, including motors and appliances.

- 3. AC-AC converter: A class of converters known as an AC-AC converter skilfully modifies fixed AC voltage to produce variable AC voltage, frequently with the option to change the frequency. While cyclo-converters have the special capacity to modify both voltage and frequency, making them appropriate for applications, AC voltage regulators, for example, maintain voltage levels without changing frequency.

- 4. **DC-DC Converters:** With specialization in modifying fixed DC voltage to variable DC voltage, these converters employ precise control over switch-on time to achieve the desired output. There are various types of converters available that are designed to efficiently adjust voltage levels for a wide range of applications. These converters are commonly used in portable electronics and renewable energy systems.

### **1.2. Introduction to DC - DC Converters**

The search for effective and flexible power conversion in the always changing field of electronics has never ended. DC-DC converters are now a mainstay of technology that have revolutionized the way power is controlled and used in a wide range of applications. Innovations sparked by these converters have allowed devices to be made smaller while maintaining great efficiency and flexibility that linear regulators could not match on their own[6]-[8]. Before DC-DC converters became widely used, linear regulators were commonly used for voltage regulation tasks. Although linear regulators are known for their simplicity in design and ability to deliver clean, stable output with minimal noise, their operational inefficiency in certain situations prompted the exploration of alternative solutions. Because linear regulators dissipate extra power as heat to regulate voltage, they have a poor energy conversion efficiency by design, particularly in applications where the input and output voltages range significantly. This constraint led to the creation and acceptance of DC-DC converters[9]-[15].

Unlike linear regulators, DC-DC converters employ a distinct method for power conversion. They utilize switch-mode technology, where power switches efficiently convert input voltage to a desired output voltage through high-frequency switching. The energy is stored temporarily in inductors or capacitors and then released at the desired output voltage, greatly reducing energy waste. Making the switch to DC-DC converters instead of traditional linear regulators offers clear advantages, mainly because of their higher efficiency. These converters are well-known for their impressive efficiency rates, often exceeding 90%. This efficiency proves crucial, especially when modern power supplies systems are taken into consideration. Since DC-DC converters are flexible and efficient, they have established essential positions in many different industries. In portable electronics, they effectively control battery life in anything from computers to cell phones. They improve device uptime by guaranteeing constant voltages across various circuit components, which is essential in our world going more and mobile.

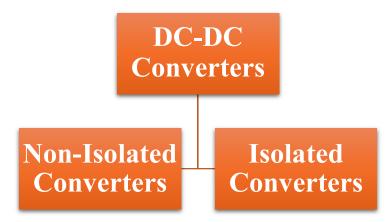

For maximum efficiency, the renewable energy industry—which is typified by fuel cells and solar panels—uses DC-DC converters. They skilfully change output voltage to suit the requirements of the grid or storage system, so promoting more seamless energy integration [20]-[23]. The topologies of DC-DC converters are classified in the literature according to several criteria. Still, two basic groups can be distinguished among the important DC-DC converters which is shown in Fig.1.2.:

Fig 1.2 Classification of DC-DC Converters

- Non-Isolated Converters: These converters enable seamless energy transfer without any isolative barrier, resulting in cost-effective construction and compact design while ensuring dependable performance in different environments. Among the many topologies covered are the Buck, Boost, Buck-boost, Cuk, Zeta, and SEPIC converters.

- 2. **Isolated Converters:** Isolated converters use high-frequency transformers to overcome situations that need electrical isolation between the input and output. They play a crucial role in reducing noise and protecting delicate components. Some examples of these types are the forward converter, flyback converter, push-pull converter, half-bridge converter, and full-bridge converter, among other types, are commonly used in power electronics.

In addition, DC-DC converters can be classified according to their output characteristics, such as having single or multiple outputs. They can also be categorized based on the nature of inductor current flow, which can be either Continuous Conduction Mode (CCM) or Discontinuous Conduction Mode (DCM). Furthermore, the output voltage magnitude is another factor that determines the classification, typically seen in buck, boost, and buck-boost configurations. CCM maintains a stable inductor current above zero throughout the switching cycle, ensuring reliable operation. On the other hand, DCM experiences a drop in the inductor current to zero during a portion of this cycle, which can lead to size reduction benefits for the inductor. To meet a wide range of power management needs, converters like the buck, which steps down input voltage, the boost, which raises it, and the buck-boost, which can do both, use different operational strategies. Adaptive and efficient power supply designs, which serve a wide variety of electronic devices and systems, rely on these converters. Additionally, there are fourth-order converters such as cuk, sepic, and zeta that are based on buck boost topology.

### **1.3.** Motivation for the research

Modern electronics infrastructure would not be complete without DC-DC converters, which have recently come under increased scrutiny in the race for more efficient and effective electronic gadgets. The exact regulation of direct current (DC) power supplied to different circuits from a single source relies heavily on such converters. The many DC-DC converter topologies, which are designed to meet the needs of individual applications by carefully selecting and rating their components, have been previously covered. Several variables impact this complex selection process. These include, but are not limited to, input and output voltages, input current ripple, output voltage ripple, output power, and switching frequency. In particular, the design details cover passive components like inductors and capacitors and active components like semiconductor devices, which are crucial to the efficiency of the converter. To achieve performance goals including improving the converter's efficiency and dependability and reducing voltage and current ripples, their ratings are crucial. Inductors play a crucial role in converter design [24]. Their value has a direct impact on ripple current, where higher inductance results in decreased ripple but at the trade-off of larger size and

potentially higher cost. The shift towards higher switching frequencies indicates a way to reduce the size of the inductor, although it does pose difficulties in terms of managing heat and electromagnetic interference (EMI). In high-frequency applications, the efficiency of inductors can be affected by their inherent resistance. To minimize these losses, it is important to use high-quality inductors with low resistance, often achieved through the use of ferrite cores. However, a careful analysis of scholarly discussions uncovers a lack of consideration for non-idealities in the design equations of inductors and capacitors. This research is driven by the observation that there are gaps in the current understanding of DC-DC converter design processes and aims to fill them by incorporating the effects of non-idealities. Improved converter designs are expected as a result of thorough analysis and consideration of less-than-ideal factors, such as capacitor equivalent series resistance (ESR), inductor core losses, and semiconductor switching and conduction losses. The ultimate goal of this study is to help designers create smaller, more dependable, and more efficient converters by creating a complete model that takes these imperfections into account. Another important part of this study is the modelling of DC-DC converters, which requires a delicate balancing act between being accurate and making models as simple as possible. By filling a critical void in current modelling approaches, this study intends to tackle the problem of modelling converter non-idealities in a way that produces more accurate and useful models[25]-[30].

With the aim of keeping output steady under a range of changing conditions, such as input voltage fluctuations and load variability, the development of improved and adaptive control techniques for DC-DC converters is recognized as an important research avenue. The purpose of this study is to investigate the feasibility of using pulse width modulation (PWM) and other advanced control techniques to reliably stabilize the output voltage.

Because Cuk converters and other higher-order systems are inherently complex, this study is also keen to investigate how non ideal study techniques can simplify control strategy design. While maintaining the control system's efficacy, this strategy seeks to reduce the computing cost. By combining theoretical analysis with practical innovation, this project seeks to address the stated issues and make a meaningful contribution to the field. This work aims to improve DC-DC converter design and control mechanisms by bridging the gap between theoretical models and real-world application demands, setting new standards for efficiency and effectiveness [31]-[39].

In short, any DC-DC converter must be built through a series of crucial stages, starting with the first one of identifying design parameters to accomplish user-defined goals. After that, one has to work on creating an exact mathematical model of the system [40]-[50]. The final step in this approach is to design a skilful control plan that will guarantee output voltage regulation over a range of operating circumstances. As such, the following three essential aspects of DC-DC converters are the focus of this dissertation:

- 1. Developing and personalizing DC-DC converter settings.

- 2. Creating thorough mathematical models of these converters.

- 3. The integration of control strategies for DC-DC voltage regulation

This thesis focuses on these topics for both non-ideal and ideal models of the Cuk converter in recognition of the variety of DC-DC converter topologies. Through this narrowly focused perspective, the study seeks to provide light on a route toward improved converter dependability and efficiency.

### **1.4.** Contribution of the author

Even if DC-DC converter design, modelling, and control have been studied extensively, this thesis attempts to go deeper into these fields. Both the voltage drops in diodes and the resistances in inductors, capacitors, diodes, and MOSFETs were frequently ignored by earlier studies. These errors are included into this paper, which offers a more precise analysis. With the introduction, there are six chapters in all to the thesis. Chapters that follow describe the contributions to this work. With its concise synopsis of the work done, each chapter advances our knowledge of DC-DC converters. Incorporating the consequences of imperfections, Chapter 2 presents improved duty cycle calculations for both ideal and non-ideal Cuk converters. These revised design formulae for inductor and capacitor values show how input voltage, defects, and load resistances affect the duty cycle. These converters also have a comprehensive capacitor voltage ripple study done. The maximum ESR value to sustain specified output voltage ripple and inductor current ripple at a given frequency is determined by this analysis. The validation of these theoretical conclusions by means of simulation data closes this chapter.

The emphasis in Chapter 3 moves to using state-space averaging and averaged switch modelling approaches to develop a mathematical model for both the ideal and non-ideal DC-DC Cuk converter. This improved model includes diode voltage dips and parasitic resistances. An evaluation of the mathematical models of the ideal and non-ideal converters is given. This comparison shows that assuming the converter functions perfectly misses important insights into the physical behaviour of the converter that are provided by modelling the converter with its non-ideal features.

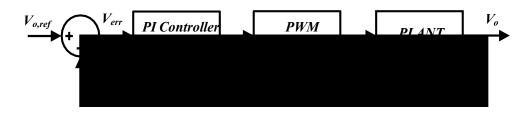

Drawing on their transfer function models; Chapter 4 investigates several conventional control techniques for the ideal and non-ideal DC-DC Cuk converters. This section of the work describes the stability boundary locus technique and a predefined phase margin-based PID controller architecture for each kind of Cuk converter. A PI controller reduces steady-state voltage errors well, but it is not very good at maximizing transient responsiveness, the chapter notes.

The chapter presents a dual loop control technique to improve DC-DC converter voltage response. An external voltage and an internal current PI controller are integrated in this novel method. A new approach to modify the parameters of both PI controllers is presented with the intention of achieving particular gain crossover frequency and phase margin targets. This algorithm's power is in its simultaneous fulfilment of the crossover frequency and best phase margin requirements. A real-world fourth order Cuk converter is then subjected to this recently

developed control approach. The performance of this real application is shown to be rather good, almost matching the performance obtained with the PI controller that was first modelled.

For the DC-DC Cuk converter, Chapter 5 explores the sliding mode control method. It describes how to derive several transfer functions that look at the converter's closed-loop behaviour under sliding mode control. Within the chapter is suggested a simple approach for calibrating the controller's parameters. We present simulation results to show how well the developed controller works.

Chapter 6, which summarises the whole thesis and addresses future study directions, closes the thesis. At the end of the thesis comes supporting material, which includes appendices and a thorough list of references that support the study carried out throughout.

# CHAPTER 2 DESIGN OF DC-DC CONVERTERS

# 2.1 Introduction

Important parts of the electronics industry, DC-DC converters are essential for managing and modifying voltage levels in a wide range of devices. Through the provision of the necessary voltage for electronic circuits, these converters guarantee the effective operation of a wide range of applications, from portable devices like laptops and cell phones to renewable energy systems and automobile electronics. There exist three basic topologies of DC-DC converters, each with unique properties and uses. These are the converters for buck, boost, and buck-boost.

The buck converter reduces the input voltage to a lower output value. It is distinguished by its capacity to deliver a consistent output current with few voltage fluctuations, making it very efficient for applications that necessitate a reliable power supply. However, there is a problem to consider: the input current is not continuous, which means that an input filter must be included in order to guarantee smooth functioning.

Conversely, the boost converter amplifies the input voltage to a greater output voltage. The most notable characteristic of this is its uninterrupted input current flow, which eliminates the requirement for an input filter. Nevertheless, similar to the buck converter, it also has drawbacks. In the boost topology, the output current is not continuous, which means that it is not constant over time. To reduce the amount of fluctuation in the output voltage, a significant amount of capacitance is needed.

The flexible buck-boost converter offers output voltage levels that can be greater, lower, or equal to the input voltage by combining the features of both buck and boost converters. Because it flips the polarity of the output voltage with respect to the input and has discontinuous input and output currents, like a boost converter, its implementation presents special problems.

With clever integration of their benefits, the Cuk converter appears as a smart development of these three fundamental topologies. It can be set to provide continuous

current at the input and output sides and to vary the output voltage to be either equal to, less than, or higher than the input voltage. In comparison to the input voltage, its output voltage is inverted, though.

A fourth-order system, the Cuk converter gains stability and efficiency by adding two inductors and capacitors.

Beyond the Cuk converter, the Zeta and SEPIC converters are also part of the DC-DC converter arena; they both keep the output voltage polarity equal to the input voltage. Though the Zeta converter has discontinuous input current, like the buck topology, the SEPIC converter has discontinuous output current, which is a drawback of the boost architecture. In keeping with their intricacy and degree of control over voltage conversion procedures, both are likewise categorised as fourth-order systems.

When it comes to applications that depend on DC-DC converters, finding the perfect combination of inductance and capacitance is crucial. Achieving the optimal inductance and capacitance configuration is critical for applications depending on DC-DC converters, as several research and scholarly sources [references] demonstrate. Although real-world situations show otherwise, theoretical analysis and design approaches usually presume the components of these converters to be faultless [references]. DC-DC converters' real components are faulty and not at all like the ideal model {List of references}. These imperfections manifest as equivalent series resistances (ESRs) in inductors and capacitors, additional resistances encountered in MOSFETs and diodes during their operational phase, and the diodes' inherent forward voltage drop. Such non-ideal factors can significantly influence the performance and design specifics of DC-DC converters, posing challenges for crafting precise and highquality power supplies. For instance, when theoretically modelling the duty cycle formulas for a Cuk converter in continuous conduction mode (CCM) as shown in Eqn. (2.1), these real-world discrepancies must be accounted for to ensure accuracy and efficiency in design.

$$\frac{V_o}{V_s} = D_{iideal} \tag{2.1}$$

Where  $V_o$  is the output voltage and  $V_s$  is the input voltage of the Cuk converter.

The conventional assumptions for the Cuk converter's operation are based on the ideal performance of every component in the system. Nevertheless, practical implementations of the Cuk converter may not achieve the desired output voltage  $V_O$  when compared to the idealised expressions, due to encountered losses. This phenomenon occurs when there are voltage reductions or energy dissipation across components that deviate from the ideal model.

One must use a duty cycle that is higher than the one anticipated by the ideal formulations Eqn. (2.1) in order to counteract these energy losses. Accurate design and parameter adjustment of the converter also become essential to achieve the performance targets. This demands that the converter's circuitry and operation be thoroughly examined. Here we go into great detail on the non-ideal behaviour of the Cuk converter, which results in the development of improved design equations for the relevant inductors and capacitors. This chapter also provides a thorough analysis and performance review of the Cuk converter, comparing the theoretical ideal models with their real-world, less ideal equivalents.

## 2.2 Analysis of Ideal Cuk DC- DC Converter

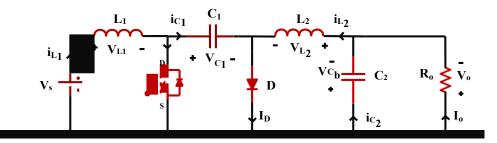

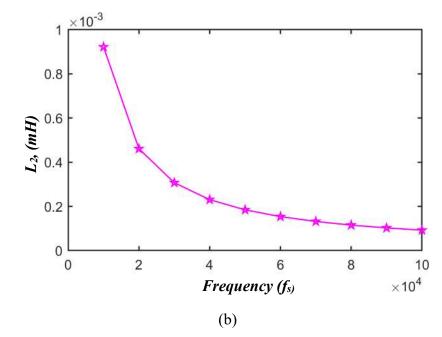

The schematic diagram of a Cuk DC-DC converter as shown in Fig.2.1 reveals a unique arrangement designed to regulate voltage levels efficiently. It consists of two inductors, two capacitors, a semiconductor diode, and a switch, usually a transistor. Using this configuration, energy is transferred effectively between its input and output sides while the polarity of the output voltage is reversed w.r.t the input voltage. Inductors and capacitors, two energy storage components, play a crucial role in smoothing out voltage and current transitions, making sure a stable output happens. What sets the Cuk converter apart is its versatility, demonstrated by its capability to work in two modes: Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM). For the purpose of this study, the focus is narrowed to its operation in CCM. This mode is critical for understanding how the converter performs under steady conditions, with particular emphasis on the duty cycle (D) and the switching frequency ( $f_s$ ). The duty cycle, which is the ratio of the switch's active time to the total cycle time, plays a pivotal role in controlling the converter's output, making it a key factor in our analysis.

Fig 2.1 Schematic Diagram of Cuk Converter

Mathematically,

$$D = \frac{\tau_{on}}{t_{on} + t_{ooooo}} = \frac{\tau_{on}}{T_S} = t_{on} f_S$$

(2.2)

Where  $t_{on}$  is the interval of time when the MOSFET is turned ON, and  $t_{ooooo}$  is the time interval when the MOSFET is turned OFF.

From Eqn. (2.2), we get,

$t_{on} = DT_s$  (When the MOSFET is turned ON) (2.3)

$$t_{ooooo} = (1 - D)T_s = D'T_s$$

(When the MOSFET si turned OFF) (2.4)

Where D' = (1 - D)

Cuk converter is controlled by MOSFET switching mechanisms. In CCM mode it has two switching mode (a) When the MOSFET is ON and the Diode is turned OFF, or (b) When the MOSFET is turned OFF and the Diode Conducts.

## **2.2.1** Mode 1 of operation ( $00 < t < DT_S$ )

In a Cuk DC-DC converter, Mode 1 refers to the phase where the MOSFET, is turned on and the diode, D is non-conducting. As the MOSFET is turned on in Mode 1, the current flows through an inductor,  $L_I$ , the MOSFET, and then to the ground. Because of the applied voltage  $V_s$ , across inductor  $L_I$ , the current through it increases linearly with time. Due to the input voltage source's energy, inductor  $L_I$  stores more energy. During this time, the capacitor  $C_I$  starts to discharge through the closed MOSFET since it's storing energy from the previous cycle. Thus, the voltage across  $C_I$  drops. In this mode, the current flowing through capacitor  $C_I$  contributes to the current flowing through inductor  $L_2$ , which also provides power to the load, so energy is transferred. Using Kirchoff's Voltage and current law, the voltage across the inductor  $L_1$  and  $L_2$ , current across the capacitor  $C_1$  and  $C_2$ , and the output voltage is given by:

$$V_{L_{1,on}} = L_1 \frac{d \ddot{u}_{L_1}}{dt} = V_s$$

(2.5)

$$V_{L_{2},on} = L_2 \frac{du_{L_2}}{dt} = Vc_1 - Vc_2$$

(2.6)

$$iic_{1,on} = C_1 \frac{dVc_1}{dt} = -iiL_2$$

(2.7)

$$ii_{C_{2,on}} = C_2 \frac{dV_{C_2}}{dt} = ii_{L_2} - \frac{V_{C_2}}{R_o}$$

(2.8)

$$V_o = Vc_2 \tag{2.9}$$

# **2.2.2** Mode 2 of operation $(DT_s < t < (11 - D)T_s)$

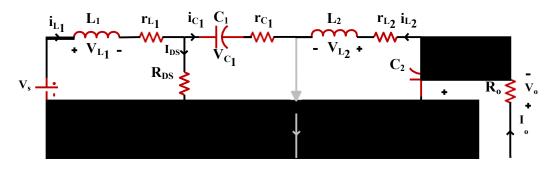

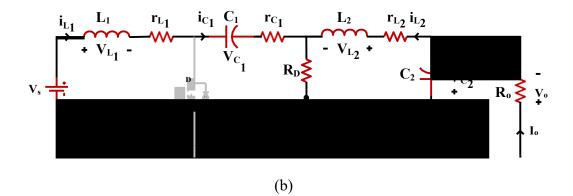

In the Cuk converter's second stage, when the MOSFET turns off, the dynamics of the system change. The inductor  $L_1$ , which had been building up current, now pushes that current through a diode that starts to conduct because of the MOSFET's inactivity. This current goes on to charge capacitor  $C_1$ . and the energy stored in  $L_2$  is transferred to the output capacitor  $C_2$  and the load. Both modes of operation are shown in Fig.2. Using Kirchoff's Voltage and current law, the voltage across the inductor  $L_1$  and  $L_2$ , current across the capacitor  $C_1$  and  $C_2$ , and the output voltage is given by:

$$V_{L_{1,00000}} = L \frac{d \ddot{u}_{L_{1}}}{dt} = V_{s} - V_{C_{1}}$$

(2.10)

$$V_{L2,00000} = L_2 \frac{di_{L_2}}{dt} = -V_{C_2}$$

(2.11)

$$ii_{C_{1},0000} = C_{1} \frac{dV_{C_{1}}}{dt} = -ii_{L_{1}}$$

(2.12)

$$ii_{C_{2},00000} = C_{2} \frac{dVc_{2}}{dt} = ii_{L_{2}} - \frac{Vc_{2}}{R_{o}}$$

(2.13)

$$V_{00} = V_{C_2} \tag{2.14}$$

Fig 2.2 Mode of operation (a) Mode 1 (b) Mode 2

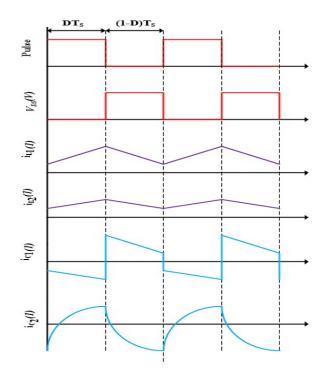

Fig 2.3 Switching Waveforms of Cuk DC-DC Converter

### 2.2.3 Steady state analysis

In the context of steady-state analysis, the mean value of a current and voltage variable, denoted as X can be described as follows:

$$XX = \frac{1}{T} \bigotimes_{0}^{T} x(t)dt = \frac{1}{T} \bigotimes_{0}^{DT} x_{on}(t)dt + \frac{1}{T} \bigotimes_{DT}^{T} x_{ooooo}(t)dt$$

(2.15)

Where  $x_{on}$  and  $x_{off}$  denotes the variable x(t) when switch is on and off respectively.

According to the principle of volt-second balance for an inductor, over a full cycle of a switched-mode power supply, the cumulative voltage applied to an inductor equals zero i.e,

$$V_{L} = \frac{1}{T} \bigotimes_{0}^{T} v_{L}(t) dt = \frac{1}{T} \bigotimes_{0}^{DT} v_{L,on}(t) dt + \frac{1}{T} \bigotimes_{DT}^{T} v_{L,ooooo}(t) dt = 0$$

(2.16)

Similarly, as per the Ampere-Second balance for a capacitor, over a complete switching cycle, the net charge transferred to and from a capacitor equals zero, signifying a state of dynamic equilibrium. This is given by:

$$I_{C} = \frac{1}{T} \bigotimes_{0}^{T} i_{c}(t) dt = \frac{1}{T} \bigotimes_{0}^{DT} i_{c,on}(t) dt + \frac{1}{T} \bigotimes_{DT}^{T} i_{c,om}(t) dt$$

(2.17)

Also, the average output voltage of the ideal Cuk converter is given by:

$$V_{o} = \frac{1}{T} \bigotimes_{0}^{T} v_{o}(t) dt = \frac{1}{T} \bigotimes_{0}^{DT} v_{o,on}(t) dt + \frac{1}{T} \bigotimes_{DT}^{T} v_{o,ooooo}(t) dt$$

(2.18)

### 2.2.3.1 Expression for output voltage

The expression of the output voltage of the ideal Cuk Converter can be derived from applying volt sec balance to the inductor  $L_1$ . Substituting Eqn. (2.5) and Eqn. (2.10) into Eqn. (2.16) we get:

$$\frac{1}{\overline{T}} \bigotimes_{0}^{DT} Vsdt + \frac{1}{\overline{T}} \bigotimes_{DT}^{T} (Vs - Vc_1)dt = 0$$

(2.19)

On simplifying the Eqn. (2.19) we get,

$$V_{SD} + (1-D) \langle V_{S} - V_{c_1} \rangle = 0$$

(2.20)

$$V_S - (1 - D)V_{C_1} = 0 (2.21)$$

The average Voltage of capacitor  $C_l$  can be calculated by applying KVL from voltage source to the output voltage, i.e.,

$$V_{C_1} = V_s + V_o - V_{L_1} + V_{L_2} \tag{2.22}$$

Since the average voltage of inductors is zero as per volt sec balance, therefore,

$$V_{C_1,avaa} = V_s + V_o \tag{2.23}$$

Substituting the value from Eqn. (2.23) to Eqn. (2.21), we get

$$V_o = \frac{DV_s}{1 - D} \tag{2.24}$$

As shown by this equation, the converter is capable of producing an inverted output voltage relative to its input voltage. When the duty cycle is less than 0.5, the converter generates a reduced magnitude of inverted output voltage. Conversely, when the duty cycle is greater than 0.5, the inverted output voltage increases in magnitude, enabling the converter to respond to situations involving higher voltage levels from lower voltage sources in particular.

| <b>Table 2.1 Ideal Cuk Converter Specifications</b>                 |                               |  |

|---------------------------------------------------------------------|-------------------------------|--|

| Parameters                                                          | Values                        |  |

| Input Voltage, Vs                                                   | 24V                           |  |

| Output Voltage, Vo                                                  | 48V                           |  |

| Load Resistance, Ro                                                 | 11.52Ω                        |  |

| Inductance $L_1$                                                    | 0.384µH                       |  |

| Inductance $L_2$                                                    | 0.768µH                       |  |

| Decoupling Capacitor, $C_1$                                         | 38.58µF                       |  |

| Filter Capacitor, $C_2$                                             | 2µF                           |  |

| Switching Frequency, fsss                                           | 50kHz                         |  |

| Desired Inductor current ripple $\Delta ii_{L_1} / \Delta ii_{L_2}$ | $10\% I_{L_1} / 10\% I_{L_2}$ |  |

| Desired Output voltage ripple, $\Delta V_{c_1} / \Delta V_{c_2}$    | $1\% V_{c_1} / 1\% V_{c_2}$   |  |

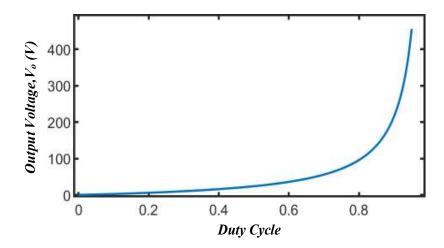

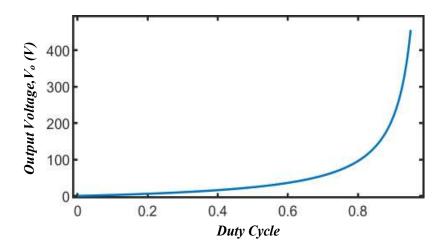

For constant input voltage  $V_s$ , the variation of output voltage with respect to duty cycle is shown in figure. At a load resistance  $R_o = 12$ , the input voltage is kept constant at 24V, and the duty cycle varies from D = 0.1 to D = 0.85. As shown in Figure, for duty cycles less than 0.5, output voltages are less than input voltages. However, for duty cycles greater than 0.5, output voltages rise sharply and exceed input voltages.

Fig 2.4 Output Voltage Variation with Duty Cycle

### 2.2.4 Inductor current ripple and Inductor design

The design of inductors plays a key role in the effectiveness of DC-DC converters. It influences their efficiency, size, and the control over voltage fluctuations. Inductors are central to how energy is stored and transferred, shaping the converter's overall performance. Thus, focusing on innovating inductor design is essential for achieving more efficient, smaller, and robust DC-DC converters.

Let  $\Delta ii_{L_1}$  and  $\Delta ii_{L_2}$  be the desired ripple in inductor current (ICR) and  $x_{L_1}$  and  $x_{L_2}$  be the desired inductor current ripple factor (ICRF) for both the inductors. The relationship between the ICR and ICRF is given by:

$$x_{L_1} = \frac{\Delta i i_{L_1}}{I_{L_1}}$$

$$x_{L_2} = \frac{\Delta i i_{L_2}}{I_{L_2}}$$

(2.25)

Similarly,

Where,  $I_{L_1}$  and  $I_{L_2}$  are the average currents flowing through inductor  $L_1$  and  $L_2$ . Now, under steady state, using Eqn. (2.5), it can be written as,

$$L_1 \frac{d \ddot{u}_{L_1}}{dt} = V_s \tag{2.26}$$

By substituting the switch on duration, dt = DTs, we get,

$$L_1 = \frac{V_S * DT_s}{\Delta \Delta \underline{i} \underline{i}_1} \tag{2.27}$$

Since  $T_s = 1/f_s$ , therefore Eqn. (2.27) can be rewritten as,

$$L_1 = \frac{V_S * D}{\Delta \Delta \underset{L_1}{\overset{\text{dil}}{\underset{L_1}{\overset{\text{s}}{ff}_s}}}$$

(2.28)

For inductor  $L_2$ , using the Eqn. (2.11) i.e. when the switch is off, it can be written as

$$L_2 \frac{d \ddot{u}_{L_2}}{dt} = -V_o \tag{2.29}$$

By substituting the switch off duration,  $dt = (1-D)T_s$  and  $T_s = 1/f_s$ , we get

$$L_{2} = \frac{V_{o} * (1 - D)}{\frac{\Delta \Delta ll}{L_{2}} * ff_{s}}$$

(2.30)

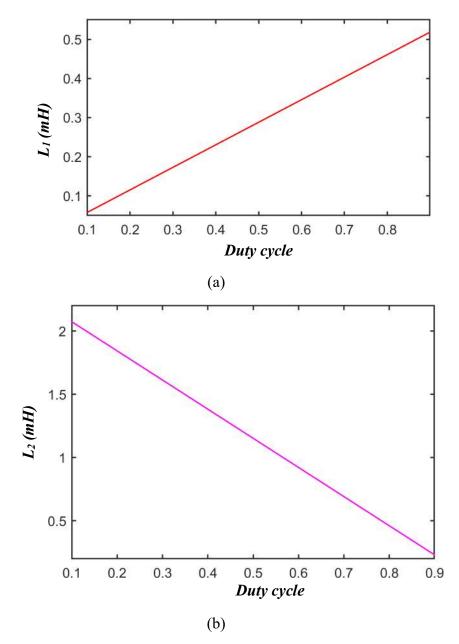

Fig.2.4 masterfully showcases the contrasting dynamics between two inductors,  $L_1$  and  $L_2$ , within the framework of varying duty cycles in a Cuk converter setup. It intriguingly reveals that as we dial up the duty cycle, the inductance of inductor  $L_1$  experiences an upward trajectory, necessitating higher inductance to efficiently manage the system's energy storage and minimize current ripple. As opposed to the narrative when observing inductor  $L_2$  within the same graph, an increase in duty cycle intriguingly leads to a reduction in inductance. Based on this inverse relationship,  $L_2$  demands less inductance as the duty cycle intensifies, suggesting a unique, adaptive behaviour as opposed to  $L_1$ . Moreover, this nuanced interplay emphasizes the delicate balance and precise tuning required for the smooth and efficient operation of Cuk converters, taking into account  $L_1$  and  $L_2$ 's distinct functions and requirements.

Fig 2.5 Variation of inductance with Duty Cycle (a)  $L_1$  (b)  $L_2$

# 2.2.5 Output voltage ripple and capacitor design

The capacitor plays a pivotal role in determining the system's overall efficiency and performance. An optimally designed capacitor ensures the seamless transfer of energy between circuits, minimizing voltage ripples and enhancing power stability. This critical component acts as a buffer, storing and releasing electrical energy, thereby smoothing the output voltage, and reducing electromagnetic interference. The design parameters of the capacitor, including its capacity, voltage rating, and physical size, must be meticulously tailored to meet the specific requirements of the converter. It allows for the achievement of high-efficiency levels, operational reliability, and longevity of the converter, underscoring the necessity for precise capacitor design in crafting an ideal Cuk DC converter.

In steady state, let  $\Delta V c_1$  and  $\Delta V c_2$  be the desired voltage ripple across the capacitor  $C_1$  and  $C_2$ .

Considering the Eqn. (2.7), and also considering the average value of inductor current  $\ddot{u}_{L_2}$  we get,

$$iic_{1,avaa} = I_{00} \tag{2.31}$$

$$C_1 \frac{dVc_1}{dt} = \frac{V_o}{R_o} \tag{2.32}$$

$$C_1 = \frac{V_o * D}{R_o * \Delta V_{C_1} * f_s}$$

(2.33)

The output capacitor is like a buck converter, so using the definition of capacitor,

$$\Delta \Delta \Delta \Delta = C \Delta \Delta V \tag{2.34}$$

So for the output capacitor the relationship shown in Eqn. (2.34) can be written as,

$$\frac{1}{2} \underbrace{\overset{\mathcal{I}}{2}}_{2} \underbrace{$$

$$C_2 = \frac{T_S * \Delta \Xi_2}{8Vc_2} \tag{2.36}$$

Using Eqn. (2.29) and substituting the value of  $\Delta ii_{L_2}$  into Eqn. (2.36) we get,

$$C_{2} = \frac{V_{o} * (1 - D)}{8 * \iint_{s}^{2} * \Delta V * \frac{1}{2}}$$

(2.37)

Fig 2.6 Charging and Discharging behaviour of Capacitor C1andC2

### 2.2.6 Results and discussions

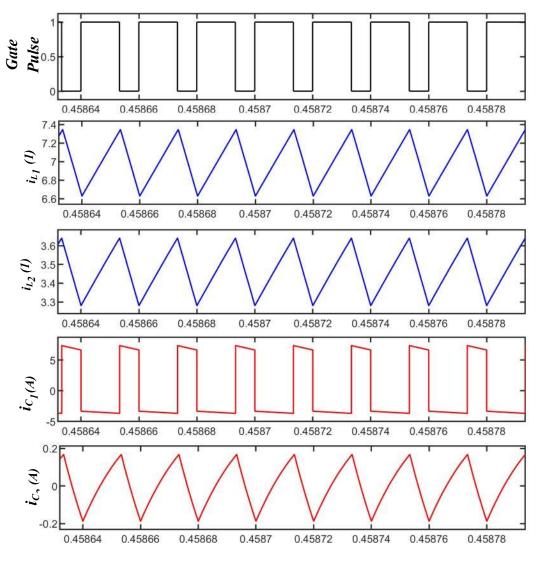

The theoretical study of the ideal Cuk converter was simulated using MATLAB Simulink, with parameters specified in Table 2.1. The simulation aimed to analyse the output voltage response under varying conditions. Results indicated that the output voltage closely followed the expected behaviour predicted by theoretical models. Specifically, as the duty cycle increased, the output voltage also rose, exhibiting a linear relationship. Conversely, decreasing the duty cycle led to a reduction in output voltage.

Fig 2.7 Duty Cycle Vs Output Voltage

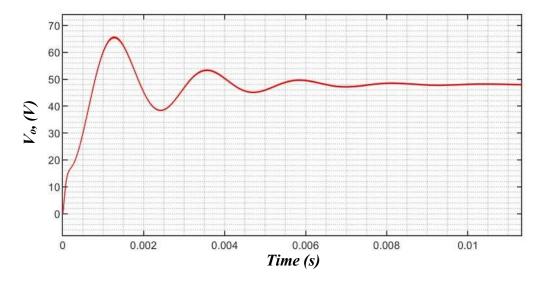

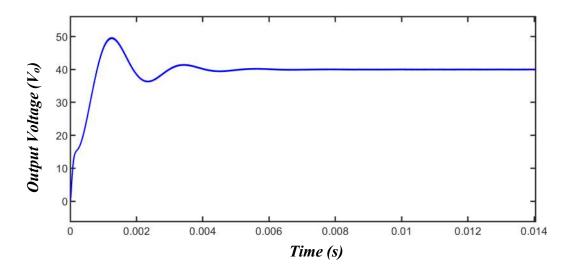

With a carefully calculated duty cycle of 0.66, based on Eqn.(2.1), and inductance values set at 0.384mH for  $L_1$  and 0.768mH for  $L_2$ , the converter was tasked with transforming a 24V input to a 48V output, as dictated by Eqn (2.2). Throughout the simulation, the performance of the Cuk converter was exemplary, achieving a steady and stable 48V output under open loop conditions.

This capability to maintain a precise output voltage, especially notable in an openloop system, emphasizes the converter's efficiency and the accuracy of its design and component selection.

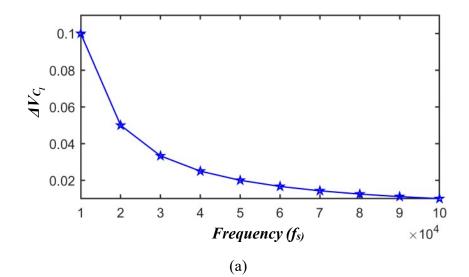

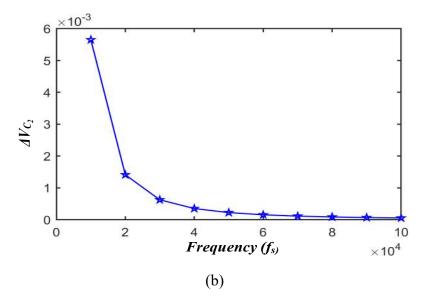

A fascinating aspect captured in Fig 2.9 is the relationship between the output voltage ripple and the switching frequency. The trend is clear and consistent: as the switching frequency climbs, the ripple within the output voltage shows a marked decline. This inverse relationship is critical for applications demanding a smooth DC output, as it suggests that increasing the switching frequency can enhance the output quality.

Fig 2.8 Output Voltage response at rated conditions

Fig 2.9 Ripple Voltage variation with switching frequency for (a)  $C_1$  (b)  $C_2$

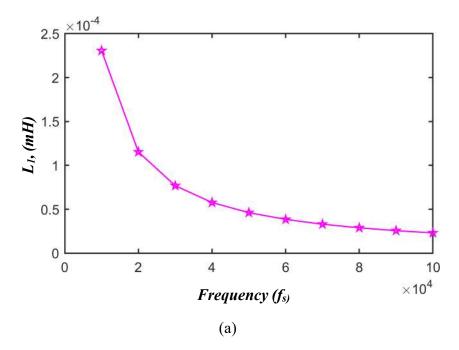

Simultaneously, Fig 2.10 illustrates another interesting correlation between the inductance values and switching frequency. The captured data demonstrates a decrease in the required inductance value as the switching frequency rises. This finding has practical implications for the design of compact Cuk converters; higher switching frequencies allow the use of smaller inductors, which can lead to size and cost reductions without sacrificing performance.

Fig 2.10 Relation of frequency with inductance (a)  $L_1$  (b)  $L_2$

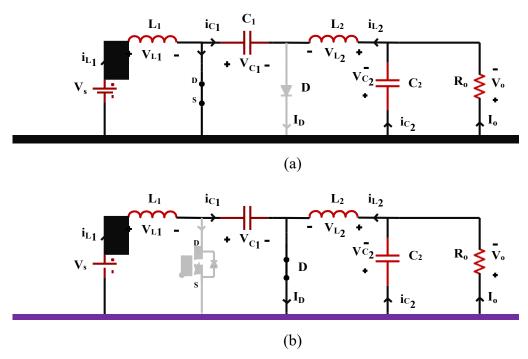

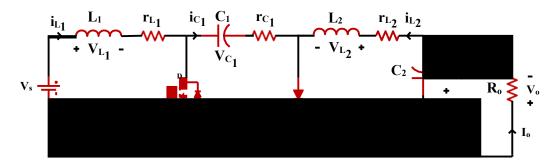

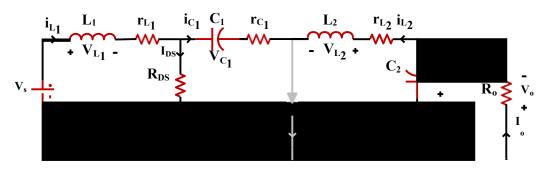

# 2.3 Analysis of Non ideal Cuk converter

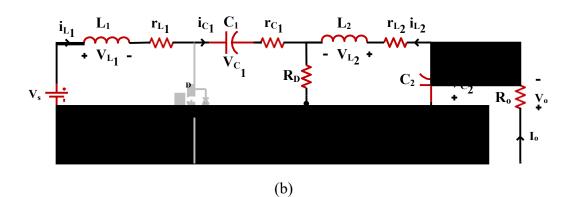

In the schematic of a non-ideal Cuk DC-DC converter, several components critical to its operation must be accounted for beyond the ideal theoretical model. The converter characteristically includes two inductors,  $L_1$  and  $L_2$ , essential for energy storage and smoothing input and output current fluctuations respectively. Between these inductors, a capacitor ( $C_1$ ) is pivotal in transferring energy via a switching mechanism controlled by a pulse-width modulated (PWM) signal. This switching element, typically a MOSFET, orchestrates the charge and discharge cycles of ( $C_1$ ) by alternating its state. Complementing this switch, a diode is strategically placed to provide a pathway for current during the non-conductive states of the transistor, maintaining continuity of operation. Additionally, the output capacitor ( $C_2$ ) plays a vital role in mitigating voltage ripple, thereby stabilizing the output. The schematic is shown in Fig.2.9.

In the realm of non-ideal components, the Equivalent Series Resistance (ESR) of both capacitors and inductors introduces inefficiencies such as heat generation and voltage drop, factors that significantly affect converter performance and efficiency. This intricate configuration of the non-ideal Cuk converter, complexified by real-world component imperfections, provides a robust framework for understanding the challenges in optimizing converter design to balance efficiency, cost, and performance

in practical power supply applications. This detailed examination not only advances the comprehension of the operational principles but also aids in the empirical evaluation and enhancement of DC-DC converter systems. In the comprehensive study of the non-ideal Cuk DC-DC converter, a critical aspect similar to its ideal counterpart is the operation across two distinct modes of conduction: Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM).

The Cuk converter employs MOSFET switching mechanisms for control. In Continuous Conduction Mode (CCM), it operates in two switching modes: (a) when the MOSFET is in the ON state and the diode is turned OFF, or (b) when the MOSFET is turned OFF and the diode conducts.

Fig 2.11 Schematic diagram of Non- Ideal Cuk Converter

## **2.3.1** Mode 1 of operation ( $00 < t < DT_S$ )

The operational dynamics of the non-ideal Cuk converter, as delineated in Fig.2, can be dissected into two principal stages that are critical to understanding its steady-state behaviour. During the initial stage, the MOSFET, denoted as S, is in a closed state, catalysing a notable increment in the current through the inductor  $(L_I)$ . This increment is indicative of the inductor  $(L_I)$  charging, storing energy derived from the input source. Concurrently, the coupling capacitor  $(C_I)$  commences its discharge process, whereby it serves a dual role: it provides the necessary energy to power the load, and at the same time, facilitates the transferal of energy to inductor  $(L_2)$ . Throughout this phase, the diode remains in an OFF state due to the reverse bias induced by the potential difference across it, sustained by the energy transfer dynamics governed by the closed MOSFET. Using Kirchoff's voltage and current equation, the system dynamics under steady state can be written as:

$$V_{L_{1,on}} = L_{1} \frac{dii_{L_{1}}}{dt} = V_{s} - \phi r_{L_{1}} + R_{ds} \phi ii_{L_{1}} - R_{ds} ii_{L_{2}}$$

$$V_{L_{2,on}} = L_{2} \frac{dii_{L_{2}}}{dt}$$

(2.38)

$$= -R_{ds} i L_1 - \mathbf{Q} R_{ds} + r_{c_1} + r_{L_2} + \frac{R_o r_{c_2}}{R_o + r_{c_2}} \mathbf{Q} i L_2 + V_{c_1}$$

(2.39)

$$- \mathbf{Q} \frac{R_o}{R_o + rc_2} \mathbf{Q} V_{c_2}$$

$$\mathbf{u}_{c_{1,on}} = C_1 \frac{dVc_1}{dt} = -\mathbf{u}_{L_2}$$

(2.40)

$$\ddot{u}_{C_{2},on} = C_{2} \frac{dV_{C_{2}}}{dt} = \frac{R_{o}}{R_{o} + r_{C_{2}}} \ddot{u}_{L_{2}} - \frac{V_{C_{2}}}{R_{o} + r_{C_{2}}}$$

(2.41)

$$V_o = \frac{R_o r_{C_2}}{R_o + r_{C_2}} \ddot{u}_{L_2} + \frac{R_o}{R_o + r_{C_2}}$$

(2.42)

# **2.3.2** Mode 2 of operation $(DT_s < t < (11 - D)T_s)$

In the operational process of the non-ideal Cuk DC converter during stage 2, there's a detailed explanation of its inner workings. As the MOSFET S switches to an open state and the diode takes over conduction, a significant transformation occurs within the converter's setup. Essentially, the energy previously stored in the inductor  $L_1$  is discharged, initiating a transfer of power to the capacitor  $C_1$ . This phase is marked by the simultaneous charging of  $C_1$ , which acts as a repository for accumulated energy. At the same time, the discharge of the previously charged inductor  $L_2$  begins, facilitating the delivery of power to the load.

The system dynamics under steady state can be written as Using Kirchoff's voltage and current equation:

$$V_{L_{1},00000} = L_{1} \frac{d \ddot{u}_{L_{1}}}{dt} = V_{s} - \langle r_{L_{1}} + r_{C_{1}} + R_{D} \langle \ddot{u}_{L_{1}} - R_{D} \ddot{u}_{L_{2}} - V_{C_{1}}$$

(2.43)

$$V_{L_{2},00000} = L_{2} \frac{d \ddot{u}_{L_{2}}}{dt}$$

=  $-R_{D} \ddot{u}_{L_{1}} - \mathbf{Q} R_{D} + r_{L_{2}} + \frac{R_{0} r_{C_{2}}}{R_{0} + r_{C_{2}}} \mathbf{Q} \ddot{u}_{L_{2}}$  (2.44)

$$u_{C_{1,0000}} = C_{1} \frac{dt}{dt} = u_{L_{1}}$$

$$u_{L_{1}} = C_{2} \frac{dV_{C_{2}}}{dt} = \frac{R_{o}}{dt} = U_{L_{1}}$$

$$V_{C_{2}} = C_{2} \frac{dV_{C_{2}}}{dt} = \frac{R_{o}}{dt} = U_{L_{1}}$$

$$V_{C_{2}} = C_{2} \frac{dV_{C_{2}}}{dt} = C_{2}$$

$$ii_{C_2,0000} = C_2 \frac{dV_{C_2}}{dt} = \frac{R_o}{R_o + r_{C_2}} ii_{L_2} - \frac{V_{C_2}}{R_o + r_{C_2}}$$

(2.46)

$$V_o = \frac{R_o r_{C_2}}{R_o + r_{C_2}} \ddot{u}_{L_2} + \frac{R_o}{R_o + r_{C_2}}$$

(2.47)

(a)

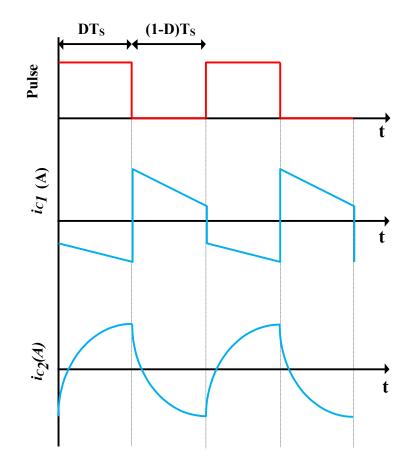

Fig 2.12 Modes of operation (a) Mode 1 (b) Mode 2

## 2.3.3 Steady state analysis

In the context of steady-state analysis, the mean value of a current and voltage variable, denoted as X can be described as follows:

$$XX = \frac{1}{T} \bigotimes_{0}^{T} x(t)dt = \frac{1}{T} \bigotimes_{0}^{DT} x_{on}(t)dt + \frac{1}{T} \bigotimes_{DT}^{T} x_{ooooo}(t)dt$$

(2.48)

Where  $x_{on}$  and  $x_{off}$  denotes the variable x(t) when switch is on and off respectively. According to the principle of volt-second balance for an inductor, over a full cycle of a switched-mode power supply, the cumulative voltage applied to an inductor equals zero i.e.,

$$V_{L} = \frac{1}{T} \bigotimes_{0}^{T} v_{L}(t) dt = \frac{1}{T} \bigotimes_{0}^{DT} v_{L,on}(t) dt + \frac{1}{T} \bigotimes_{DT}^{T} v_{L,ooooo}(t) dt = 0$$

(2.49)

Similarly, as per the Ampere-Second balance for a capacitor, over a complete switching cycle, the net charge transferred to and from a capacitor equals zero, signifying a state of dynamic equilibrium. This is given by:

$$I_{C} = \frac{1}{T} \bigotimes_{0}^{T} i_{c}(t) dt = \frac{1}{T} \bigotimes_{0}^{DT} i_{c,on}(t) dt + \frac{1}{T} \bigotimes_{DT}^{T} i_{c,omm}(t) dt$$

(2.50)

Now using eq. (2.50) for capacitor C1 and C2 we get

$$I_{c_1} = \frac{1}{T} \bigotimes_{0}^{T} \ddot{u}_{c_1}(t) dt = \frac{1}{T} \bigotimes_{0}^{DT} \ddot{u}_{c_{1,on}}(t) dt + \frac{1}{T} \bigotimes_{DT}^{T} \ddot{u}_{c_{1,on00}}(t) dt$$

(2.51)

$$I_{C_{1,avaa}} = D \langle - ii_{L_2} \rangle + (1 - D) \langle ii_{L_1} \rangle = 0$$

$$(2.52)$$

$$\ddot{u}_{L_1} = \frac{D}{D'} \ddot{u}_{L_2} \tag{2.53}$$

Now for capacitor C2,

$$Ic_{2} = \frac{1}{T} \bigotimes_{0}^{T} iic_{2}(t)dt = \frac{1}{T} \bigotimes_{0}^{DT} iic_{2,on}(t)dt + \frac{1}{T} \bigotimes_{DT}^{T} iic_{2,on00}(t)dt$$

(2.54)

$$I_{C_{2,avaa}} = D \, \phi_{iiL_{2}} - \frac{V_{a}}{R_{o}} \phi + (1 - D) \, \phi_{iiL_{2}} - \frac{V_{a}}{R_{o}} \phi = 0 \qquad (2.55)$$

$$\ddot{u}_{L_2} = \frac{Vo}{R_o} \tag{2.56}$$

Also, the average output voltage of the ideal Cuk converter is given by:

$$V_{o} = \frac{1}{T} \bigotimes_{0}^{T} v_{o}(t) dt = \frac{1}{T} \bigotimes_{0}^{DT} v_{o,on}(t) dt + \frac{1}{T} \bigotimes_{DT}^{T} v_{o,ooooo}(t) dt$$

(2.58)

$$V_o = D \langle V c_2 + r c_2 \ddot{u} c_2 \rangle + (1 - D) \langle V c_2 + r c_2 \ddot{u} c_2 \rangle$$

$$(2.59)$$

$$V_o = V_{C_2} \tag{2.60}$$

# 2.3.3.1 Expression for output Voltage

Applying KVL in the outer loop from the input voltage source to the output voltage gives us:

$$Vc_1 = V_s - ii_{L_1} r_{L_1} + ii_{L_2} r_{L_2} + V_o$$

(2.57)

Applying volt-sec balance in inductor  $L_1$  using Eqn. (2.49) we get,

$$V_{S} - \ddot{u}_{L_{1}} \phi r_{L_{1}} + DR_{ds} + D'r_{C_{1}} + D'R_{D} \phi - \ddot{u}_{L_{2}} \phi Dr_{L_{2}} + D'R_{D} \phi - D'V_{C_{1}} = 0$$

(2.58)

Substituting the value of  $V_{c_1}$ ,  $ii_{L_1}$  and  $ii_{L_2}$  from Eqn. (2.60), Eqn. (2.54) and Eqn. (2.57) we get the expression for output voltage as:

$$V_{o} = \frac{\frac{D}{D'}V_{s}}{1 + R_{o} v_{D'} v_{r_{1}} + r_{L_{2}} + \frac{Dr_{C_{1}}}{D'} + \frac{r_{eq}}{D'^{2}}}$$

(2.59)

Where  $r_{eq} = DR_{ds} + D'R_D$

| Table 2.2 Non-Ideal Cuk C | onverter Specifications |

|---------------------------|-------------------------|

|---------------------------|-------------------------|

| Table 2.2 Non-Ideal Cuk Converter Specifications                    |                               |

|---------------------------------------------------------------------|-------------------------------|

| Parameters                                                          | Values                        |

| Input Voltage, V <sub>S</sub>                                       | 24V                           |

| Output Voltage, Vo                                                  | 48V                           |

| Load Resistance, Ro                                                 | 11.52Ω                        |

| Inductance $L_1/r_{L_1}$                                            | 0.384μH /0.1 Ω                |

| Inductance $L_2/r_{L_2}$                                            | 0.768μH/0.1 Ω                 |

| Decoupling Capacitor, $C_1/r_{c_1}$                                 | 38.58μF/1 μ <b>Ω</b>          |

| Filter Capacitor, $C_2/r_{c_2}$                                     | 2μF/1 μ <b>Ω</b>              |

| Switching Frequency, fss                                            | 50kHz                         |

| Diode Resistance, $R_D$                                             | $0.1\Omega$                   |

| MOSFET Resistance, <i>R</i> <sub>ds</sub>                           | $0.25\Omega$                  |

| Desired Inductor current ripple $\Delta ii_{L_1} / \Delta ii_{L_2}$ | $10\% I_{L_1} / 10\% I_{L_2}$ |

| Desired Output voltage ripple, $\Delta V_{c_1} / \Delta V_{c_2}$    | $1\% V_{c_1}/1\% V_{c_2}$     |

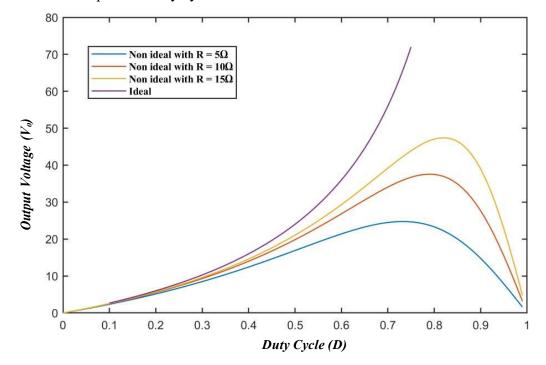

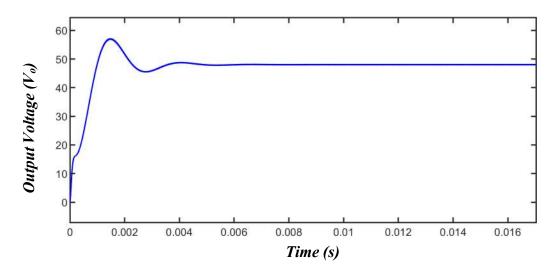

It's clear that the output voltage from a non-ideal Cuk DC-DC converter is influenced by more than just the duty cycle (D) and the input voltage ( $V_s$ ). It also varies with the load resistance ( $R_o$ ), as well as other parasitic resistances that are not ideal. These additional factors are crucial in understanding and predicting the behaviour of the converter in real-world applications. Figure 2.9 illustrates how the output voltage of a non-ideal Cuk DC-DC converter varies with the duty cycle under different load resistances. The input voltage is set at 24V, and the load resistance is adjusted to  $16\Omega$ ,  $10\Omega$ , and  $5\Omega$ . The additional effects of parasitic resistances, which can be referenced in Table 2.2, also play a significant role in this relationship.

In contrast to an ideal converter, where the output voltage linearly depends on the duty cycle, the non-ideal converter exhibits a more complex behaviour. Initially, as the duty cycle increases, the output voltage rises. This increase continues up to a certain point, after which the output voltage reaches a peak. Upon surpassing this peak, further increases in the duty cycle lead to a decrease in the output voltage. This characteristic curve is due to several non-ideal factors inherent in real components. Parasitic resistances, as indicated, along with other losses like those from non-ideal switch behaviour and diode forward voltage, introduce inefficiencies. These factors cause the energy transfer to be less effective at higher duty cycles beyond the optimal point, thus reducing the output voltage.

Understanding this behaviour is crucial for effectively utilizing Cuk converters in practical applications, where achieving maximum efficiency often requires operating at or near this optimum duty cycle.

Fig 2.13 Output voltage of Non-ideal Cuk converter as a function of duty cycle

# 2.3.4 Inductor current ripple and inductor design

In a non-ideal Cuk converter, the design of inductors is a pivotal element that significantly impacts the converter's performance. These components are integral to energy storage and transfer within the system, directly affecting its efficiency, physical dimensions, and voltage regulation capabilities.

Let  $\Delta ii_{L_1}$  and  $\Delta ii_{L_2}$  be the desired ripple in inductor current (ICR) and  $x_{L_1}$  and  $x_{L_2}$  be the desired inductor current ripple factor (ICRF) for both the inductors. The relationship between the ICR and ICRF is given by:

$$x_{L_1} = \frac{\Delta I i L_1}{I_{L_1}}$$

Similarly,

$$x_{L_2} = \frac{\Delta i i_{L_2}}{I_{L_2}}$$

Where,  $I_{L_1}$  and  $I_{L_2}$  are the average currents flowing through inductor  $L_1$  and  $L_2$ .

## 2.3.4.1 Designing of inductor L<sub>1</sub>

Under steady state using Eqn. (2.38), it can be written as:

$$\frac{\Delta \Delta i L_1}{\Delta \Delta t} = \frac{V_s - \langle r L_1 + R_{ds} \langle i L_1 - R_{ds} i L_2}{L_1}$$

(2.61)

When the MOSFET is on,  $\Delta t = DT_s$ , therefore the above equation becomes:

$$\Delta 4ii_{L_1} = \frac{V_s - \langle r_{L_1} + R_{ds} \langle ii_{L_1} - R_{ds} ii_{L_2}}{L_1} DT_s$$

(2.62)

Substituting the value of  $ii_{L_1}$  and  $ii_{L_2}$  from Eqn. (2.54) and Eqn. (2.57) we get,

$$\Delta \Delta i i_{L_1} = \frac{1}{L_1} \langle V_s - \langle r_{L_1} + R_{ds} \rangle \frac{DV_o}{D'R} - \frac{R_{ds}V_o}{R} \langle DT_s \rangle$$

(2.63)

Simplifying the above equation yields,

$$\Delta \Delta i L_1 = \frac{DV_o}{L_1 f_s} \bigvee_{V_o} - \frac{1}{RD'} \bigvee_{Dr_{L_1}} + R_{ds} \bigvee_{Q}$$

(2.64)

Now substituting the value of  $V_s/V_o$  from Eqn. (2.62) into Eqn. (2.67) we get,

(2.60)

$$\Delta Ui_{L_{1}} = \frac{D'V_{o}}{L_{1}f_{s}} \oint 1 + \frac{1}{R} \oint r_{L_{2}} + \frac{Dr_{c}}{D'} + \frac{R_{d}}{D'} \oint i$$

(2.65)

Now from Eqn.  $= x I = \frac{x_{L_1} D^{\nu_0}}{D^F R}, \text{ we get,}$

## 2.3.4.2 Designing of inductor L<sub>2</sub>

For inductor  $L_2$ , using the Eqn. 2.44 i.e. when the switch is off, it can be written as

$$\frac{\Delta \Delta i_{L_2}}{\Delta \Delta t} = \frac{-R_D i_{L_1} - \langle r_{L_2} + R_D \langle i_{L_2} - V_o \rangle}{L_2}$$

(2.67)

For the period when the MOSFET is turned of  $\Delta t = (1 - D)T_s = D'T_s$ . Therefore,

$$\frac{\Delta \Delta i L_2}{\Delta \Delta t} = \frac{R_D i L_1 + \langle r_{L_2} + R_D \langle i L_2 + V_o \rangle}{L_2} D' T_s$$

(2.68)

Substituting the value of  $ii_{L_1}$  and  $ii_{L_2}$  from Eqn. (2.54) and Eqn. (2.57) we get,

$$\Delta ii_{L_{2}} = \frac{D'V_{o}}{ff_{s}L_{2}} \oint 1 + \frac{1}{R} \oint r_{L_{2}} + \frac{R_{D}}{D'} \oint (2.69)$$

$$= x I_{L_{2}} = \frac{x_{L_{2}}V_{o}}{L_{2}L_{2}}, \text{ we get,}$$

$$L_{2} = \frac{D'R}{x_{L_{2}}ff_{s}} \oint 1 + \frac{1}{R} \oint r_{L_{2}} + \frac{R_{D}}{D'} \oint (2.70)$$

Eqn. (2.69) and Eqn. (2.73) provides improved calculation of inductor when there are parasitic components are involved.

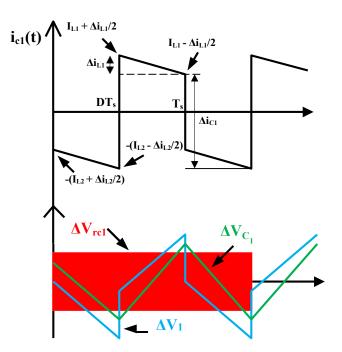

#### 2.3.5 Capacitor design

Now from Eqn.  $(2.63)\Delta ii$

In a non-ideal Cuk DC-DC converter, the additional resistances found in capacitors necessitate a careful approach to their design. These resistances can lead to energy losses, decreasing the overall efficiency of the system. Therefore, selecting the right capacity, voltage tolerance, and size for the capacitors is crucial to combat these energy losses. When designing capacitors for non-ideal Cuk DC-DC converters, one critical factor that must be considered is the Equivalent Series Resistance (ESR) of the capacitor. The ESR represents the internal resistance within the capacitor that can affect the converter's performance. High ESR can lead to significant energy losses,

heat generation, and reduced efficiency of the power conversion process. Therefore, choosing capacitors with low ESR is essential to enhance the system's overall performance. Low ESR capacitors improve energy transfer efficiency, minimize heating, and ensure a stable power output. By carefully selecting capacitors with appropriate ESR values, designers can effectively mitigate potential performance issues, leading to more reliable and efficient converter operations. This nuanced approach to capacitor selection underscores the importance of considering ESR in the design process for optimized circuit performance.

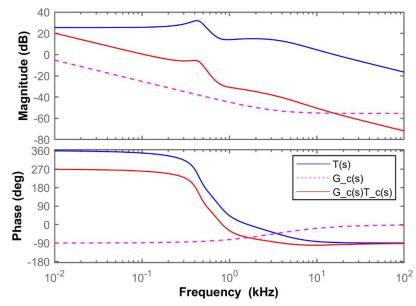

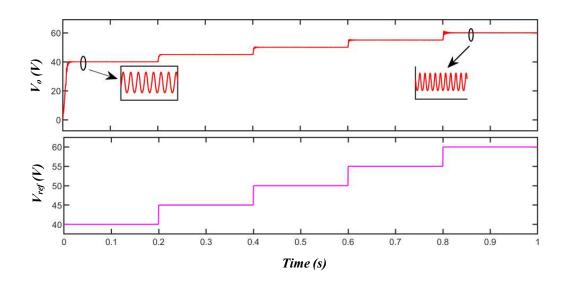

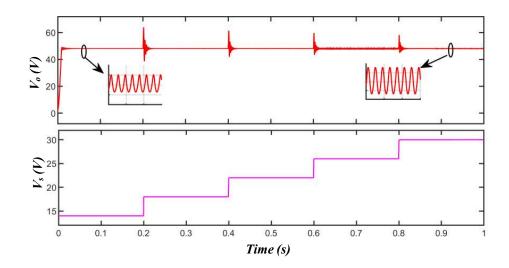

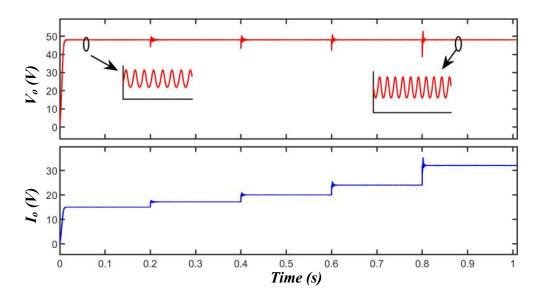

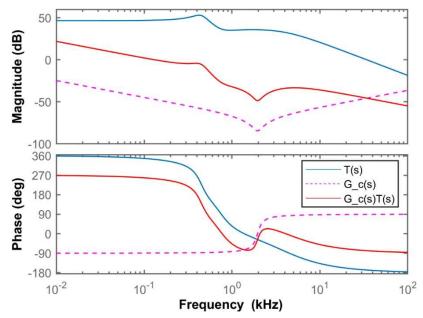

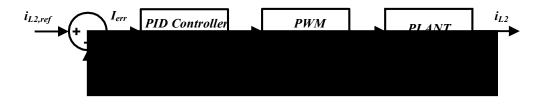

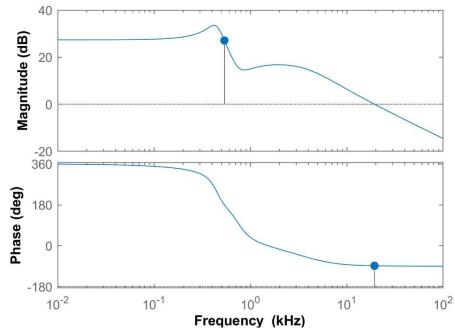

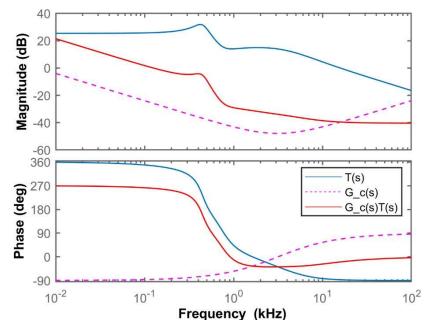

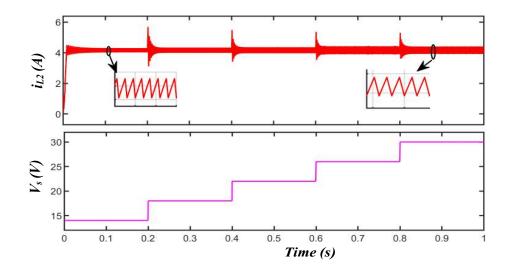

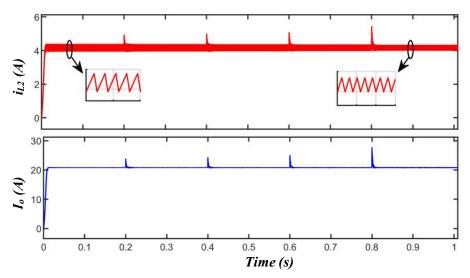

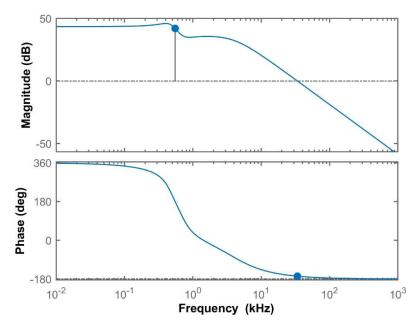

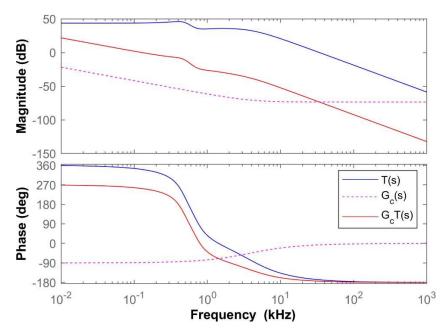

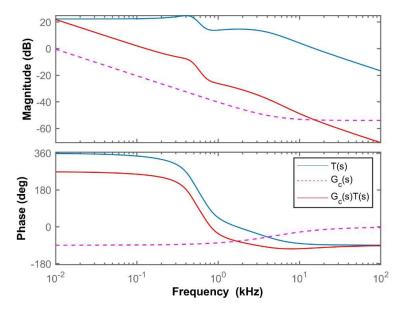

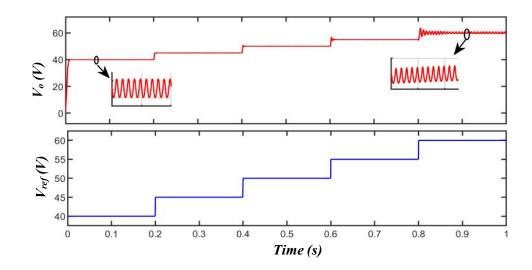

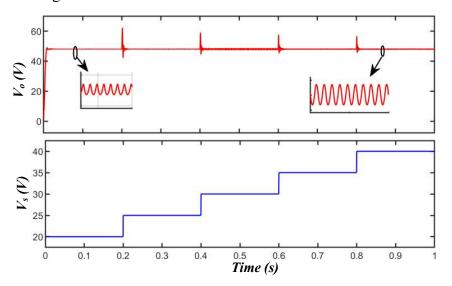

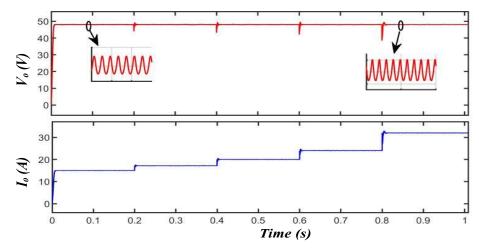

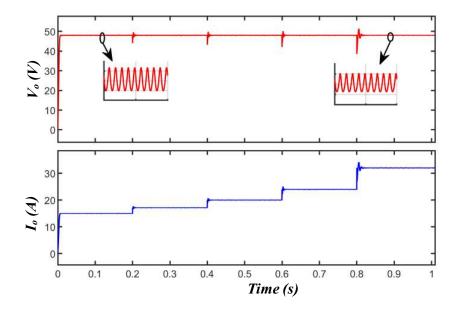

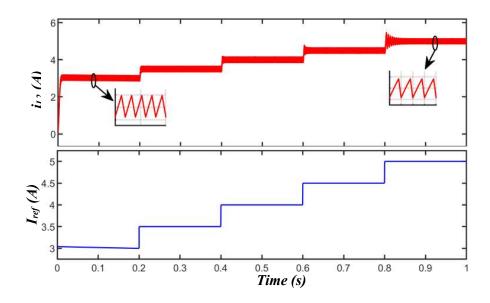

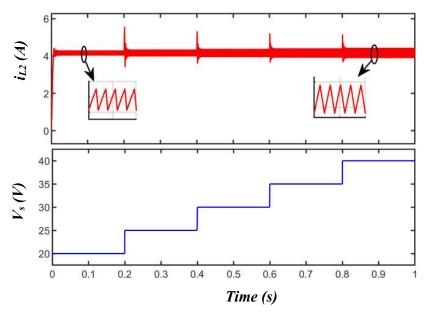

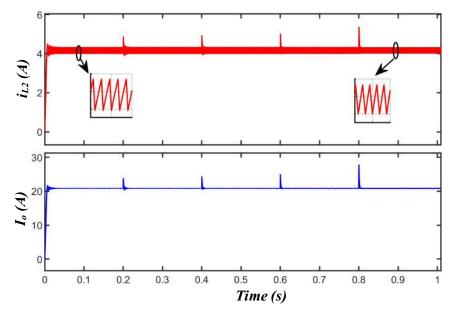

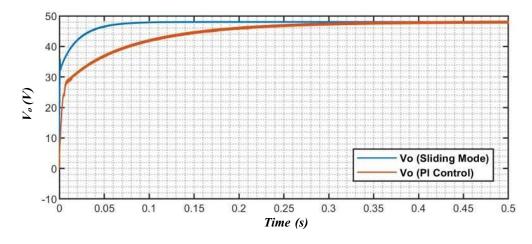

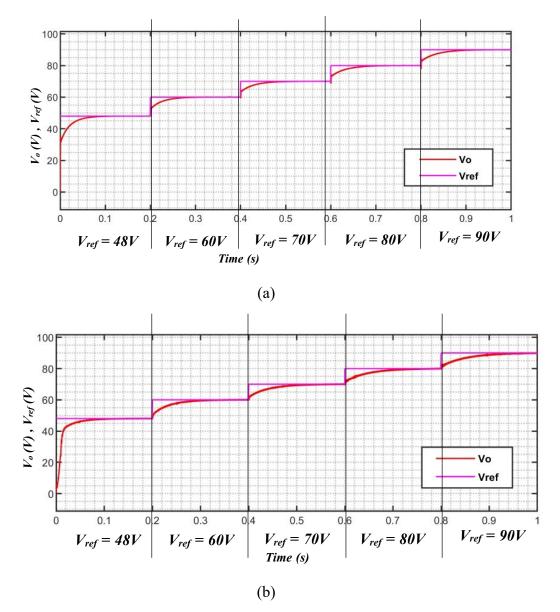

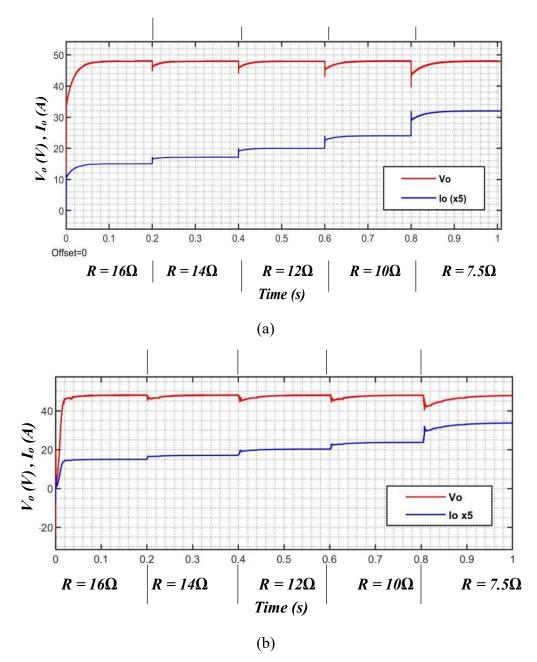

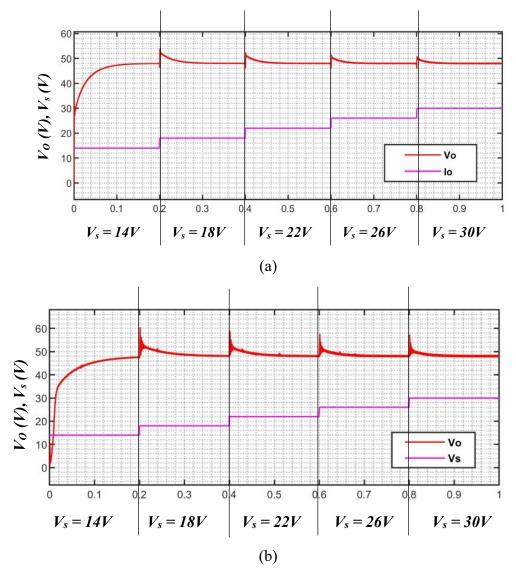

## **2.3.5.1** Capacitor C<sub>1</sub> & C<sub>2</sub>