# Analytical Modeling, Simulation and Characterization of Junctionless Accumulation Mode MOSFET for Analog and RF Circuit Applications

A Thesis Submitted In Partial Fulfilment of the Requirements for the Degree of

## **DOCTOR OF PHILOSOPHY**

by

Sumedha Gupta (Enrollment No.: 2K19/PHDEC/19)

Under the Supervision of

Prof. Neeta Pandey Professor, ECE Department (Delhi Technological University, Delhi) Prof. R.S. Gupta Professor, ECE Department (Maharaja Agrasen Institute of Technology, Delhi)

**Department of Electronics and Communication Engineering**

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Shahbad Daulatpur, Main Bawana Road, Delhi- 110042, India

May, 2024

Dedicated to,

My beloved family and my loved ones, without whose endless love and support, I wouldn't have achieve this.

#### ACKNOWLEDGEMENTS

I am delighted that the day has come that I have completed my research work for my Ph.D. journey and today I am writing my thesis. This Ph.D. journey was very admirable, memorable and knowledgeable for me. Before proceeding towards the work, I would like to express my gratitude and appreciation towards everyone who has been my pillar of strength and support throughout this journey. I feel so blessed and fortunate to have all these people in my life who help me to make this journey a remarkable one.

First of all, I am thankful to the **God** for showering his blessings on me with good health, life, positive energy, great family and friends. Everything happens with his grace.

I am sincerely grateful to my supervisor, **Prof. Neeta Pandey**, from the Department of Electronics and Communication Engineering, Delhi Technological University, for being an inspirational and motivational supervisor throughout. From the day I talked to her for seeking admission under her, she consistently guided me and encouraged me which made me more focussed and helped build enthusiasm towards my research work. At every point of time, she was always there to guide me and provide her priceless learning to get high quality of work. It was a great pleasure to work with her. I want to thank her for believing in my abilities and providing her unparalleled support. She is, and will always be an inspiration for me.

I am immensely thankful to **Prof. R. S. Gupta**, from the Department of Electronics and Communication Engineering, Maharaja Agrasen Institute of Technology, who is exceptionally a great and dedicated mentor. He is very hard working, enthusiastic and always committed towards his work. He owns a wealth of knowledge and experience through which he continuously helps, to improve the technical concepts as well as the concept of life. I have learnt a lot from him and a quote is mentioned on his table that "Nobody can do your work better than you" which always pushes me towards my goal with more dedication. Also I have learnt time management skills from him and to be passionate towards your work. His learnings are lessons which will be remembered for lifetime. He is always there to guide whether he is in India or abroad. Sir this would not have been possible without your blessings. I found myself fortunate enough that I am his student and will cherish to always remain his student for lifetime. Words are not enough to thank him. I am having tears in my eyes while writing this. He is truly an inspiration to me and all. I want to thank him from the bottom of my heart. I owe this to you sir.

I extend my heartfelt appreciation to **Dr. Nand Kishore Garg**, Founder and Chief Advisor, Maharaja Agrasen Technical Education Society, who is an inspirational torch to all of us. He always motivates to keep learning new things, encourages for research work and awards the work as well. I would also like to extend my gratitude towards **Prof. Neelam Sharma**, Director, Maharaja Agrasen Institute of Technology, for always encouraging and providing her continous support and guidance. I would also like to express my thanks to **Prof. S.S. Deswal**, Dean Academics, Maharaja Agrasen Institute of Technology for always providing his invaluable assistance, motivation and enthusiasm. I would also like to thank **Prof. Sunil Mathur**, HOD, ECE Department, for his continous advise, support and encouragement.

I am grateful to all of them for providing the necessary research environment, labs and the facilities to carry out this research work.

I would like to thank all my friends and colleagues for providing me a friendly and learning environment and for their moral support and constant motivation.

I don't have words to express my immense gratitude towards my family. First and foremost my parents, **Mr. Raj Kumar Gupta** and **Mrs. Neeraj Gupta** for their unconditional and continous motivation, support and guidance throughout in my each and every journey of life. They are my great pillars of strength always. I would also like to exceptionally appreciate my husband, **Dr. Nitin Garg**, for always believing in me and pushing me to pursue my dreams. He is a constant source of positivity and a great strength. Thanks to my Father in Law **Mr. Bhushan Garg**, for his support and encouragement. Also, for giving his time to look after our home and kids in a great way. I also wish to acknowledge my brother **Mr. Nishant Gupta** and my sister-in-law **Ms. Sugandha Gupta** to be always there for their help in any manner and always motivating me to achieve something big. Exceptional thanks to my very dear and loving

sons **Master Aarav Garg** and **Master Ridhav Garg** for giving me unconditional love and happiness each and every day. They made my days just by giving their cute little smiles. I feel guilty at times to not able to give them much time because of my work.

You all are the reasons for me to achieve laurels in my life.

I am sincerely whole hearted thankful to all those, whose names remain unquoted, for their direct and indirect unconditional support during this research work.

Sumedha Gupta

١

**DELHI TECHNOLOGICAL UNIVERSITY** (Formerly Delhi College of Engineering) Shahbad Daulatpur, Main Bawana Road, Delhi- 42

## **CANDIDATE'S DECLARATION**

I Sumedha Gupta hereby certify that the work which is being presented in the thesis entitled Analytical Modeling, Simulation and Characterization of Junctionless Accumulation Mode MOSFET for Analog and RF Circuit Applications in partial fulfilment of the requirements for the award of the Degree of Doctor of Philosophy, submitted in the Department of Electronics and Communication Engineering, Delhi Technological University is an authentic record of my own work carried out during the period from July'2019 to May'2024 under the supervision of Prof. Neeta Pandey and Prof. R S Gupta.

The matter presented in the thesis has not been submitted by me for the award of any other degree of this or any other Institute.

Candidate's Signature

This is to certify that the student has incorporated all the corrections suggested by the examiners in the thesis and the statement made by the candidate is correct to the best of our knowledge.

Signature of Supervisor (s) Examiner Signature of External

**DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering) Shahbad Daulatpur, Main Bawana Road, Delhi- 42

#### **CERTIFICATE BY THE SUPERVISOR(s)**

Certified that **Sumedha Gupta** (Enrollment No.: 2K19/PHDEC/19) has carried out her research work presented in this thesis entitled "Analytical Modeling, Simulation and Characterization of Junctionless Accumulation Mode MOSFET for Analog and RF Circuit Applications" for the award of Doctor of Philosophy from the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, under our supervision. The thesis embodies results of original work and studies are carried out by the student herself and the contents of the thesis do not form the basis for the award of any other degree to the candidate or to anybody else from this or any other University/Institution.

All 15/2026

Prof. Neeta PandeyProfessor, ECE DepartmentDelhi Technological UniversityShahbad Daulatpur, Main Bawana Road,Delhi- 110042

Prof. R.S. Gupta Professor, ECE Department Maharaja Agrasen Institute of Technology Sector- 22, Rohini, Delhi- 110086

Date:

#### Abstract

The persistent demand of the market for area- efficient and low power dissipating devices leads to continuous reduction in device size. It persuades the device engineers to develop such Integrated Circuits (ICs) with less fabrication complexity. Integrated circuit industry has revolutionized over the past few decades. Scaling has lead towards the compactness of these physical devices. The density of the transistors present over the chip doubles itself after every 18 months. This factor of scaling has given rise to many novel structures and devices. But as this dimension enters into nanometer regime, it brings about many difficulties known as Short- Channel Effects (SCEs) and Hot-Carrier Effects (HCEs). SCEs include Drain Induced Barrier Lowering (DIBL) effect, threshold voltage roll- off, velocity saturation effect, etc. These effects can alter the device characteristics severely and needs to be minimized. Therefore, to overcome these complications, several novel device architectures involving device engineering techniques have been proposed to maintain the functioning and capabilities of the device inspite of scaling.

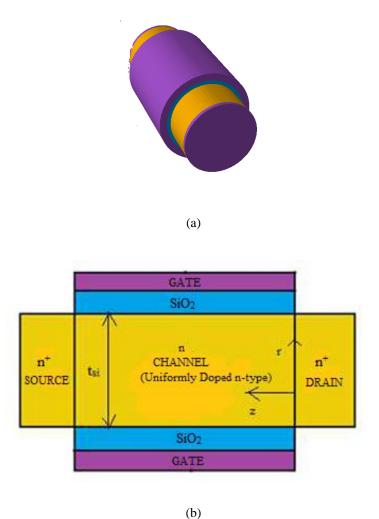

Multiple gate transistors are becoming prevalent these days because of their scaling capabilities, complete depletion of the channel and more control of the gate over the channel region. These structures also help in reduction of the leakage currents and the SCEs to a greater extent. Nowadays, a new structure called Cylindrical Surrounding Gate (CSG) MOSFET has emerged, in which the gate wraps all around the silicon pillar. Thus, provides superior gate controllability, finer scalability, excellent compatibility with Complementary Metal-Oxide-Semiconductor (CMOS) technology, much reduced SCEs, low leakage current and steep Subthreshold Slope (SS). These characteristics make CSG MOSFET as the ultimate short channel device for the future device technology. However, when the device dimensions are extremely scaled (below 22nm technology), higher source/drain resistance is formed due to the formation of abrupt source/drain p-n junctions. This in turn increases the fabrication complexity of the device and therefore, from the fabrication point of view, it is difficult to have control over these metallurgical p-n junctions. Hence, to endure with the future Ultra Large Scale Integration (ULSI) design, progressive changes in the elementary device design needs to be incorporated. A novel device structure called as Junctionless Transistor (JLT) was then proposed to overcome this problem of the increased source/drain resistance. JLT is uniformly heavily doped throughout the source, channel and drain regions either with  $n^+$ -  $n^+$  or  $p^+$ -  $p^+$ -  $p^+$ . Hence, there is no formation of p-n junctions between the source/drain and the channel regions. Due to elimination of junctions, JLT is easy to fabricate and also offers improved electrical properties. But because of the high doped channel, the mobility of the carriers gets degraded in the JLT. This problem of Carrier Mobility Degradation (CMD) leads to lower drain current and lower transconductance. So, another structure, junctionless accumulation-mode (JAM) MOSFET was introduced. In JAM MOSFET, the channel region's doping is done slightly less than that of source and drain. The carriers get accumulated at the source-channel-drain boundaries similar to an ohmic contact. On account of the higher doping present in the source and drain region, it also overcomes the problem of CMD. Thus, provides more conductivity and better characteristics than JLT.

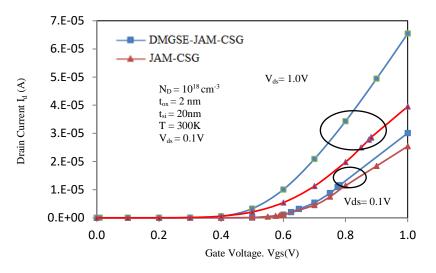

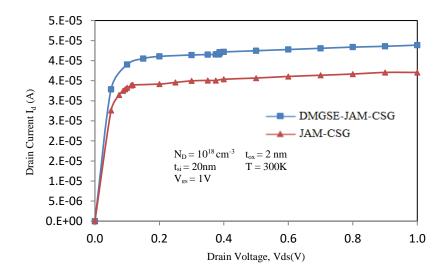

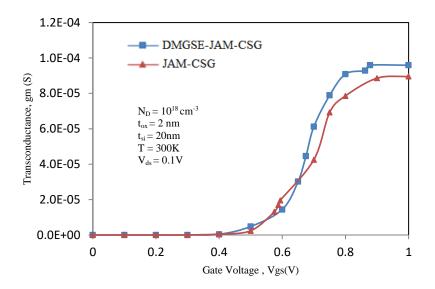

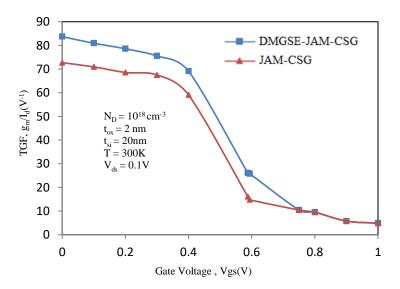

JAM has reduced SCEs but they are still not negligible, so in this research work, techniques of gate metal engineering and gate stack engineering are therefore incorporated in JAM MOSFET and a new structure was proposed named Dual-Metal Gate Stack Engineered JAM-CSG (DMGSE-JAM-CSG) MOSFET. In a MOS device, a high electric field at the drain side causes impact ionization and tunnelling of the carriers, which are responsible for hot- carrier effect. In order to address this problem, high-k gate stack have been implemented in our proposed device architecture. Thus, use of gate stack helps eliminate the problem of leakage currents. Also, the implementation of dual metal gates of different work- functions enhances the gate transport efficiency resulting in excellent gate control, which further leads to high drain current and high transconductance. Hence, our proposed device, DMGSE-JAM-CSG MOSFET possesses better electrical characteristics as compared to the JAM-CSG MOSFET. This has been verified by both using both the analytical and simulation method. 2-D analytical modeling of DMGSE-JAM-CSG MOSFET has also been proposed to address center potential, electric field, subthreshold current, transconductance and various SCEs. Furthermore, the analysis is also done using different high- k gate stack materials. The exactness of this developed model is then established by comparing with the simulated outcomes.

The change in temperature varies the performance of the MOSFET, therefore, it becomes important to examine the impact of temperature upon the various characteristic aspects of the MOSFET. Therefore, to study the influence of temperature on our structure i.e., DMDG-JAM-CSG MOSFET, we have developed this structure's temperature- dependent physics- based analytical model using the applicable boundary conditions. The characterization of the device is also studied at cryogenic temperatures. In addition to this, we have also performed the linearity assessment of our device by determining various figure of merits. Our research also proposes analytical modeling for Junctionless Accumulation-Mode Cylindrical Surrounding Gate (JAM- CSG) MOSFET-based biosensor used for label free electrical detection of the biomolecules (enzymes, cells, DNA, etc.). In this work, non-uniform doping in the channel of DMGAA-JAM-NWFET is also considered and improved characteristics over the uniformly doped channel were observed. Also, the influence of the straggle length parameter and peak doping concentration upon the device behaviour was also examined.

All the device designs discussed above are elaborated in the dissertation. Also, the contribution of the research to the field of Nano Electronics is also discussed herewith.

## **LIST OF PUBLICATIONS**

#### **INTERNATIONAL JOURNALS**

- Sumedha Gupta, Neeta Pandey, and R. S. Gupta. "Analytical modeling of dualmetal gate stack engineered junctionless accumulation-mode cylindrical surrounding gate (DMGSE-JAM-CSG) MOSFET." *Applied Physics A* 127, no. 7 (2021): 1-10. DOI: <u>10.1007/s00339-021-04652-0</u> (SCIE indexed, Impact Factor: 2.584)

- Sumedha Gupta, Neeta Pandey, and R. S. Gupta. "Temperature dependency and linearity assessment of dual-metal gate stack junctionless accumulation-mode cylindrical surrounding gate (DMGS-JAM-CSG) MOSFET." *Physica Scripta* 96, no. 12 (2021): 124055. DOI: <u>10.1088/1402-4896/ac33fd</u> (SCIE indexed, Impact Factor: 2.487)

- Sumedha Gupta, Neeta Pandey, and R. S. Gupta. "Analytical model for junctionless accumulation-mode cylindrical surrounding gate (JAM-CSG) MOSFET as a biosensor." *International Journal of Numerical Modelling: Electronic Networks, Devices and Fields* (2023): e3095. DOI: <u>10.1002/jnm.3095</u> (SCIE Indexed, Impact Factor: 1.436).

- Sumedha Gupta, Neeta Pandey, and R. S. Gupta. "Modeling of Dual- Metal Junctionless Accumulation-Mode Cylindrical Surrounding Gate (DM-JAM-CSG) MOSFET for Cryogenic temperature Applications." *Microelectronics Journal vol.* 139, (2023). DOI: <u>10.1016/j.mejo.2023.105880</u> (SCIE Indexed, Impact Factor: 1.992).

- <u>Sumedha Gupta</u>, Neeta Pandey, and R. S. Gupta. (2024). "Non-uniform doping dependent electrical parameters of dual-metal gate all around junctionless accumulation-mode nanowire FET (DMGAA-JAM-NWFET)." *International Journal of Numerical Modelling: Electronic Networks, Devices and Fields*, 37(2), e3203, (2024). DOI: <u>10.1002/jnm.3203</u> (SCIE indexed, Impact Factor: 1.436)

#### **INTERNATIONAL CONFERENCES**

1. <u>Sumedha Gupta</u>, Neeta Pandey, and R. S. Gupta. "Investigation of dualmaterial double gate junctionless accumulation-mode cylindrical gate all around (DMDG-JLAM-CGAA) MOSFET with High-k gate stack for low power digital applications." In 2020 IEEE 17th India Council International Conference *(INDICON)*, pp. 1-4. IEEE, 2020. **DOI:** <u>10.1109/INDICON49873.2020.9342380</u>

- Sumedha Gupta, Neeta Pandey, and R. S. Gupta. "Analog Performance of Dual-Metal Gate Stack Architecture of Junctionless Accumulation-Mode Cylindrical Surrounding Gate (DMGSA-JAM-CSG) MOSFET." In 2021 Devices for Integrated Circuit (DevIC), pp. 1-5. IEEE, 2021. DOI: <u>10.1109/DevIC50843.2021.9455896</u>

- Sumedha Gupta, Neeta Pandey, and R. S. Gupta. "Comparative study of Compound Semiconductors/Silicon-based Cylindrical Surrounding Dual-Metal Gate Junctionless Accumulation-Mode (CS-DMG-JAM) MOSFET for High Frequency and Switching Applications." In 2022 IEEE International Conference of Electron Devices Society Kolkata Chapter (EDKCON), pp. 486-490. IEEE, 2022. DOI: 10.1109/EDKCON56221.2022.10032896

## **TABLE OF CONTENTS**

|                                                 | Page No. |

|-------------------------------------------------|----------|

| Title                                           | i        |

| Dedication                                      | ii       |

| Acknowledgements                                | iii      |

| Candidate's Declaration                         | vi       |

| Certificate by the Supervisor(s)                | vii      |

| Abstract                                        | viii     |

| List of Publications                            | xi       |

| Table of Contents                               | xiii     |

| List of Tables                                  | xviii    |

| List of Figures                                 | XX       |

| List of Symbols, Abbreviations and Nomenclature | xxvii    |

|                                                 |          |

### **CHAPTER 1: Introduction**

#### 1-31

| 1.1 Backgroun  | nd1                                         |

|----------------|---------------------------------------------|

| 1.2 MOSFET     | Scaling                                     |

| 1.3 Short Cha  | nnel Effects4                               |

| 1.3.1          | Drain Induced Barrier Lowering (DIBL)4      |

| 1.3.2          | Threshold Voltage Roll-off                  |

| 1.3.3          | Channel Length Modulation                   |

| 1.3.4          | Punchthrough7                               |

| 1.3.5          | Impact Ionization and Hot Carriers Effects7 |

| 1.3.6          | Band to Band Tunneling (BTBT) Leakage       |

| 1.3.7          | Velocity Saturation                         |

| 1.3.8 0        | Gate Oxide Leakage10                        |

| 1.4 Literature | Survey10                                    |

| 1.4.1 I        | Double Gate (DG) MOSFET10                   |

| 1.4.2 I        | Fin-FET11                                   |

| 1.4.3 Gate All-Around (GAA) MOSFET                | 12 |

|---------------------------------------------------|----|

| 1.4.3.1 Rectangular GAA MOSFET                    | 12 |

| 1.4.3.2 Triangular GAA MOSFET                     | 12 |

| 1.4.3.3 Cylindrical GAA MOSFET                    | 13 |

| 1.4.4 Gate Electrode Engineering                  | 14 |

| 1.4.5 Gate Dielectric Engineering                 | 14 |

| 1.4.6 Junctionless Nanowire Transistor (JLT)      | 15 |

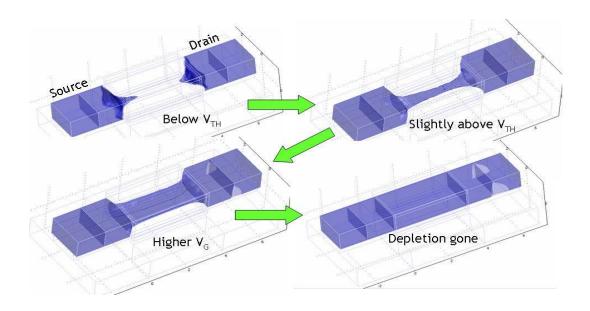

| 1.4.7 Junctionless Accumulation Mode (JAM) MOSFET | 17 |

| 1.4.7.1 Conduction Mechanism in JAM Transistor    | 18 |

| 1.5 Device Simulation                             | 19 |

| 1.6 Thesis Organization                           | 22 |

| 1.7 References                                    | 25 |

#### CHAPTER 2: Analytical Modeling Of Dual- Metal Gate Stack Engineered Junctionless Accumulation- Mode Cylindrical Surrounding Gate (DMGSE-JAM-CSG) MOSFET

|                                                                  | 32-60 |

|------------------------------------------------------------------|-------|

| 2.1 Introduction                                                 | 32    |

| 2.1.1 Gate Metal Engineering                                     | 32    |

| 2.1.2 Gate Oxide Engineering                                     | 33    |

| 2.1.3 Dual- Metal Gate Stack Engineered JAM-CSG (DMGSE-J. MOSFET | ,     |

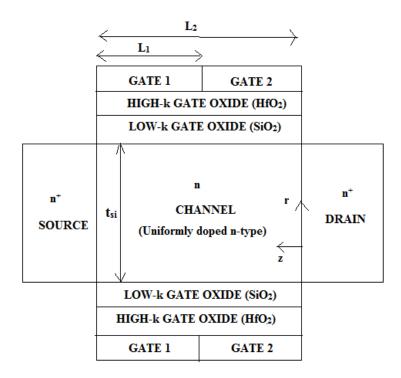

| 2.2 Device Structure                                             | 34    |

| 2.2.1 Device Calibration                                         | 35    |

| 2.2.2 Simulation Setup                                           |       |

| 2.3 Model Derivation                                             |       |

| 2.3.1 Electrostatic Potential                                    |       |

| 2.3.2 Electric Field                                             | 42    |

| 2.3.3 Subthreshold Drain Current                                 |       |

| 2.3.4 Subthreshold Slope (SS)                                    | 42    |

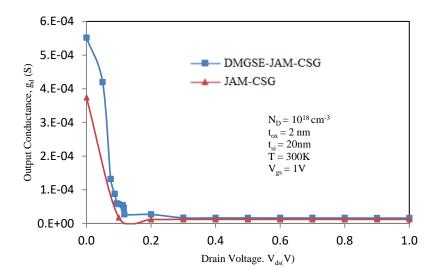

| 2.3.5 Transconductance $(g_m)$ and Output Conductance $(g_d)$    | 42    |

| 2.3.6 Switching Speed (7)                                    | 43 |

|--------------------------------------------------------------|----|

| 2.4 Results and Discussion                                   | 43 |

| 2.4.1 Analysis of the device for different high- k materials | 43 |

| 2.4.2 Comparison with Analogous Devices                      | 51 |

| 2.5 Summary                                                  | 56 |

| 2.6 References                                               | 57 |

## CHAPTER 3: Temperature Dependency and Linearity Assessment of Dual- Metal Gate Stack Junctionless Accumulation- Mode Cylindrical Surrounding Gate (DMGS-JAM-CSG) MOSFET 61-87

| 3.1 Introduction61                                                         |

|----------------------------------------------------------------------------|

| 3.1.1 Temperature Dependency Phenomenon                                    |

| 3.1.2 Linearity Assessment Phenomenon                                      |

| 3.2 Device Description, Simulation Methodology and Calibration             |

| 3.2.1 Device Description                                                   |

| 3.2.2 Models Utilized                                                      |

| 3.2.3 Device Calibration                                                   |

| 3.3 Analytical model                                                       |

| 3.4 Results and discussion                                                 |

| 3.4.1 DMGS-JAM-CSG MOSFET model70                                          |

| 3.4.2 Comparison with analogous device                                     |

| 3.4.3 Linearity assessment                                                 |

| 3.5 Summary                                                                |

| 3.6 References                                                             |

| CHAPTER 4: Analytical Model For Junctionless Accumulation- Mode Cylindrica |

## CHAPTER 4: Analytical Model For Junctionless Accumulation- Mode Cylindrical Surrounding Gate (JAM-CSG) MOSFET as a Biosensor

|                             | 00-100 |

|-----------------------------|--------|

| 4.1 Introduction            | 88     |

| 4.1.1 MOSFET as a biosensor | 89     |

| 4.2 Device Description      | 89     |

| 4.3 Analytical Model        | 92     |

| 4.3.1. Center Potential                 |     |

|-----------------------------------------|-----|

| 4.3.2. Threshold Voltage                | 97  |

| 4.3.3. Subthreshold Current             | 97  |

| 4.3.4. Sensitivity                      | 97  |

| 4.4 Results and Discussion              | 98  |

| 4.4.1 Center Potential                  | 98  |

| 4.4.2 Threshold Voltage                 |     |

| 4.4.3 Drain Current                     |     |

| 4.4.4 Sensitivity                       | 102 |

| 4.4.5 Comparison with analogous devices | 103 |

| 4.5 Summary                             | 104 |

| 4.6 References                          | 105 |

#### CHAPTER 5: Non-Uniform Doping Dependent Electrical Parameters Of Dual-Metal Gate All Around Junctionless Accumulation-Mode Nanowire FET (DMGAA-JAM-NWFET)

| 5.1 Introduction                                                  |

|-------------------------------------------------------------------|

| 5.1.1 Non- Uniform Doping110                                      |

| 5.2 Schematic Description and Simulation Approach110              |

| 5.2.1 Schematic Description112                                    |

| 5.2.2 Simulation Approach113                                      |

| 5.3 Analytical Analysis                                           |

| 5.3.1 Electrostatic Potential113                                  |

| 5.3.2 Electric Field116                                           |

| 5.3.3 Drain Current117                                            |

| 5.3.4 Subthreshold Slope (SS)118                                  |

| 5.3.5 Transconductance $(g_m)$ and Output Conductance $(g_d)$ 118 |

| 5.4 Results and Discussion                                        |

| 5.4.1 DMGAA-JAM-NWFET Device Model118                             |

| 5.4.2 Comparison with other devices                        | 127 |

|------------------------------------------------------------|-----|

| 5.4.2.1 Comparison with analogous devices with and without |     |

| junctions                                                  | 127 |

| 5.4.2.2 Comparison with Uniformly doped device             | 128 |

| 5.5 Summary                                                | 129 |

| 5.6 References                                             | 130 |

#### CHAPTER 6: Modeling of Dual- Metal Junctionless Accumulation-Mode Cylindrical Surrounding Gate (DM-JAM-CSG) MOSFET for Cryogenic **Temperature Applications**

135-158

| 6.1 Introduction                                       | 135     |

|--------------------------------------------------------|---------|

| 6.1.1 Cryogenic Analysis                               | 136     |

| 6.1.2 Cryogenic Analysis of MOSFETs                    | 137     |

| 6.2 Device Design, Simulation Approach and Calibration | 138     |

| 6.2.1 Device Design                                    | 138     |

| 6.2.2 Simulation Methodology                           | 140     |

| 6.2.3 Device Calibration                               | 140     |

| 6.3 Analytical Model                                   | 141     |

| 6.4 Results and Discussion                             | 146     |

| 6.5 Summary                                            | 152     |

| 6.6 References                                         | 154     |

| CHAPTER 7: Conclusion and Future Scope of the work     | 159-162 |

| 7.1 Conclusion               | 159 |

|------------------------------|-----|

| 7.2 Future Scope of the Work | 161 |

## LIST OF TABLES

| Table No. | Title of the Table                                                   | Page No. |

|-----------|----------------------------------------------------------------------|----------|

| Table 1.1 | Various Models available in ATLAS                                    | 21       |

| Table2.1  | Various High- k Materials with their respective dielectric constants | 33       |

| Table 2.2 | Parameters Employed for the DMGSE-JAM-CSG         MOSFET structure   | 35       |

| Table 2.3 | Physical Models used for Simulation                                  | 37       |

| Table 2.4 | Comparison of DMGSE-JAM-CSG MOSFET with<br>Analogous Devices         | 55       |

| Table 3.1 | Structural Parameters Used for JAM-CSG and DMGS-<br>JAM-CSG MOSFET   | 64       |

| Table 3.2 | Physical Models Used                                                 | 65       |

| Table 4.1 | Biomolecules and their dielectric constants                          | 91       |

| Table 4.2 | Structural Parameters of JAM-CSG MOSFET based<br>biosensor           | 91       |

| Table 4.3 | Physical Models used in simulation                                   | 92       |

| Table 4.4 | Comparison Based Upon Sensitivity Parameter                          | 104      |

| Table 5.1 | Structural Specifications for DMGAA-JAM-NWFET                        | 112      |

| Table 5.2 | Description of Models                                                | 112      |

| Table 5.3 | GAA vs. GAA-JAM vs. DMGAA-JAM-NWFET                          | 128 |

|-----------|--------------------------------------------------------------|-----|

| Table 5.4 | Non- Uniformly doped vs. Uniformly doped DMGAA-<br>JAM-NWFET | 128 |

| Table 6.1 | Parametric Values Employed for DM-JAM-CSG<br>MOSFET          | 140 |

| Table 6.2 | Physical Models Used                                         | 141 |

| Table 6.3 | Comparison of DM-JAM-CSG MOSFET with analogous device        | 152 |

| Table 6.4 | Comparison of DM-JAM-CSG MOSFET with another device          | 152 |

## **LIST OF FIGURES**

| Figure No.  | Figure Name                                                                                  | Page |

|-------------|----------------------------------------------------------------------------------------------|------|

|             |                                                                                              | No.  |

| Figure 1.1  | Original and Scaled MOSFET device structure.                                                 | 3    |

| Figure 1.2  | MOSFET scaling.                                                                              | 4    |

| Figure. 1.3 | Elucidation of (a). long channel and short channel device and (b). DIBL.                     | 5    |

| Figure 1.4  | Threshold- Voltage Roll- off illustration using Conduction<br>Band and Valance Band diagram. | 6    |

| Figure 1.5  | Schematic illustration of Channel Length Modulation.                                         | 6    |

| Figure 1.6  | Schematic diagram for punchthrough effect.                                                   | 7    |

| Figure 1.7  | Diagrammatic representation for hot carrier injection mechanism.                             | 8    |

| Figure 1.8  | Schematic diagram of various leakage mechanisms.                                             | 9    |

| Figure 1.9  | Velocity of the electron versus electric field for silicon.                                  | 9    |

| Figure 1.10 | Structure of Double Gate MOSFET.                                                             | 11   |

| Figure 1.11 | Schematic view of Fin-FET structure.                                                         | 11   |

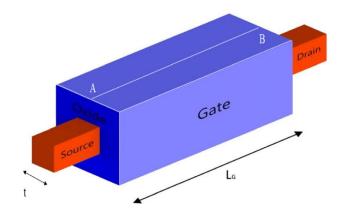

| Figure 1.12 | Rectangular GAA MOSFET.                                                                      | 12   |

| Figure 1.13 | Triangular GAA MOSFET (a) 3D view (b) cross sectional view.                                  | 13   |

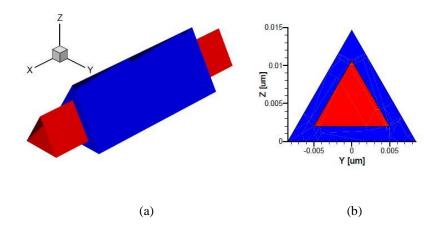

| Figure 1.14 | (a) 2-D and (b) 3-D structure of Cylindrical GAA MOSFET.                                     | 13   |

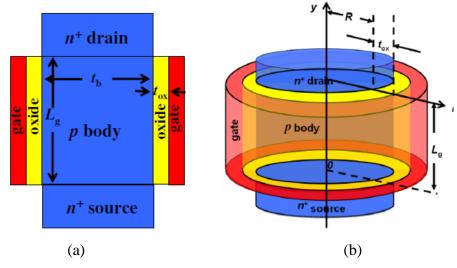

| Figure 1.15 | The Dual Material Gate FET (DMGFET) structure.                                               | 14   |

| Figure 1.16 | Schematic diagram for Gate stack engineering.                                                | 15   |

| Figure 1.17 | Junctionless Transistor.                                                                     | 16   |

| Figure 1.18 | Operation mechanism of junctionless transistor                                               | 17   |

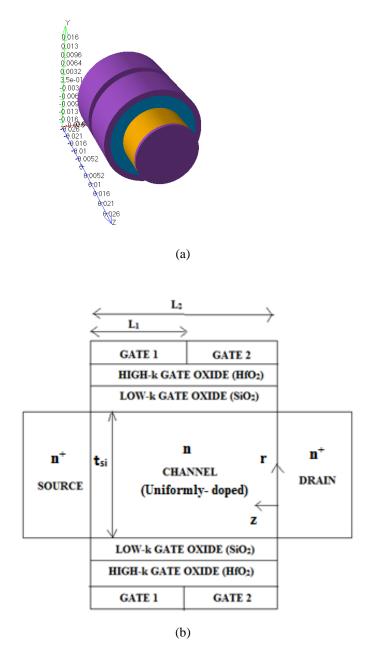

| Figure 1.19 | (a) 3-D and (b) 2-D cross-section view of JAM-CSG MOSFET.                                    | 18   |

| Figure 1.20 | Current in (a). Inversion Mode Transistor, (b). Accumulation                                 | 19   |

|             | Mode and (c) Junctionless transistor.                                |    |

|-------------|----------------------------------------------------------------------|----|

| Figure 2.1  | 3-Dimensional structural view of DMGSE-JAM-CSG                       | 34 |

|             | MOSFET.                                                              |    |

| Figure 2.2  | 2-Dimensional Cross-Section view of DMGSE-JAM-CSG                    | 35 |

|             | MOSFET.                                                              |    |

| Figure 2.3  | (a) Calibration with M. Najmzadeh et al. [18] experimental           | 36 |

|             | work. (b) Calibration with J. Xiao-shi et al. [19] analytical        |    |

|             | data.                                                                |    |

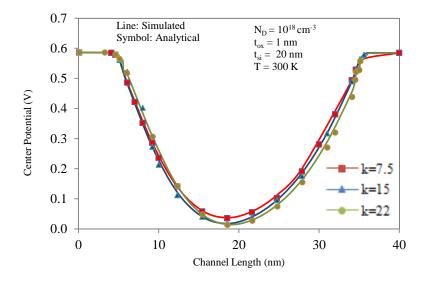

| Figure 2.4  | Center potential over the channel length of DMGSE-JAM-               | 44 |

|             | CSG MOSFET for various gate stack materials ( $k$ = 7.5, 15,         |    |

|             | 22).                                                                 |    |

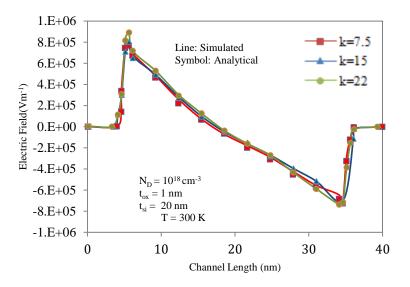

| Figure 2.5  | Electric field over the channel length of DMGSE-JAM-CSG              | 44 |

|             | MOSFET for various gate stack materials ( $k$ = 7.5, 15, 22).        |    |

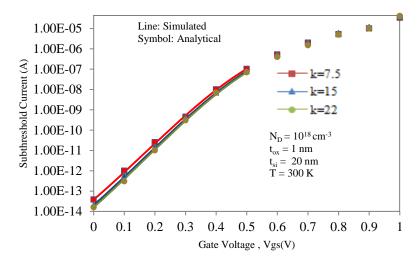

| Figure 2.6  | Subthreshold current vs. gate voltage of DMGSE-JAM-CSG               | 45 |

|             | MOSFET for various gate stack materials ( $k$ = 7.5, 15, 22).        |    |

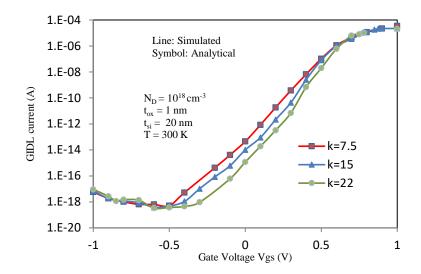

| Figure 2.7  | GIDL current vs. gate voltage of DMGSE-JAM-CSG                       | 46 |

|             | MOSFET for various gate stack materials ( $k$ = 7.5, 15, 22).        |    |

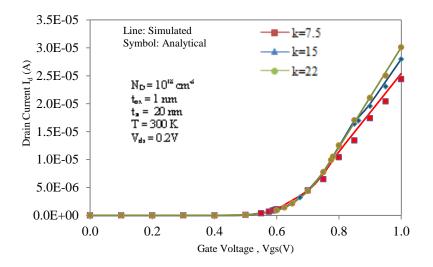

| Figure 2.8  | Drain current vs. gate voltage of DMGSE-JAM-CSG                      | 46 |

|             | MOSFET at $V_{ds}$ = 0.2V for various gate stack materials (k=       |    |

|             | 7.5, 15, 22).                                                        |    |

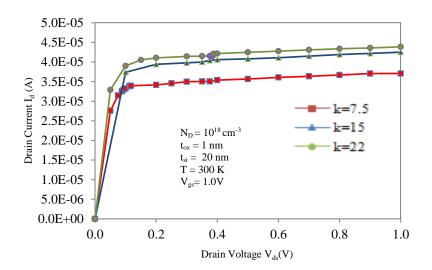

| Figure 2.9  | Output Characteristics of DMGSE-JAM-CSG MOSFET at                    | 47 |

|             | $V_{gs}$ = 1V for various gate stack materials ( $k$ = 7.5, 15, 22). |    |

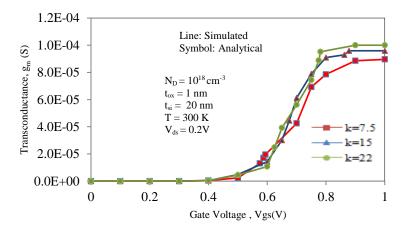

| Figure 2.10 | Transconductance $(g_m)$ w.r.t. gate voltage of DMGSE-JAM-           | 47 |

|             | CSG MOSFET at $V_{ds}$ = 0.2V for numerous gate stack                |    |

|             | materials ( $k$ = 7.5, 15, 22).                                      |    |

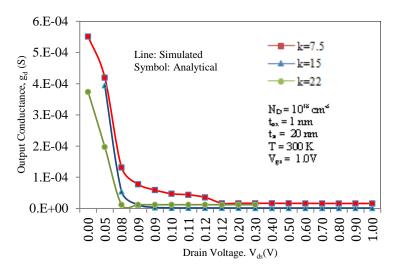

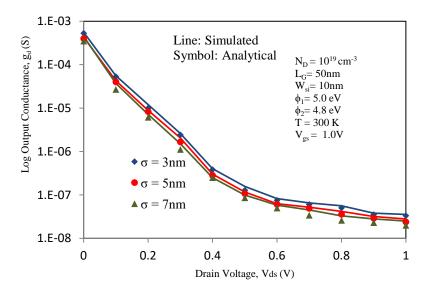

| Figure 2.11 | Output Conductance $(g_d)$ with drain voltage, $V_{ds}$ of DMGSE-    | 48 |

|             | JAM-CSG MOSFET at $V_{gs}$ = 1.0V for different gate stack           |    |

|             | materials ( <i>k</i> = 7.5, 15, 22).                                 |    |

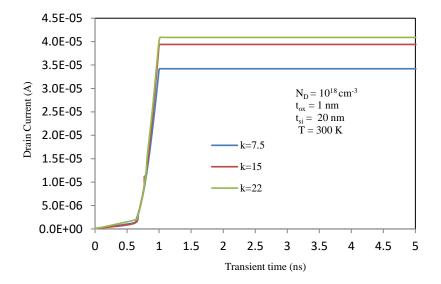

| Figure 2.12 | Transient time response of DMGSE-JAM-CSG MOSFET for                  | 49 |

|             | <i>k</i> = 7.5, 15 and 22.                                           |    |

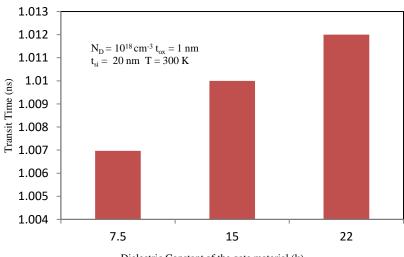

| Figure 2.13 | Switching time of DMGSE-JAM-CSG MOSFET for the                       | 49 |

|             | various gate stack materials used.                                   |    |

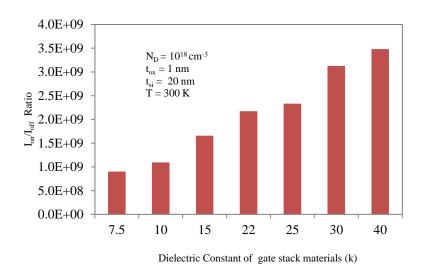

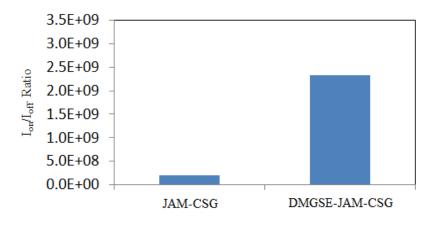

| Figure 2.14 | Ion/Ioff ratio of DMGSE-JAM-CSG MOSFET considering                         | 50 |

|-------------|----------------------------------------------------------------------------|----|

| 0           | various gate stack materials possessing distinct dielectric                |    |

|             | constants.                                                                 |    |

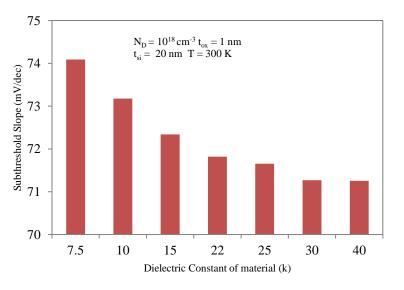

| Figure 2.15 | Subthreshold slope of DMGSE-JAM-CSG MOSFET for the                         | 50 |

|             | various gate stack materials used.                                         |    |

| Figure 2.16 | Subthreshold slope of DMGSE-JAM-CSG MOSFET for the                         | 51 |

| _           | various gate stack materials used.                                         |    |

| Figure 2.17 | Output Characteristics of DMGSE-JAM-CSG MOSFET and                         | 51 |

|             | JAM-CSG MOSFET.                                                            |    |

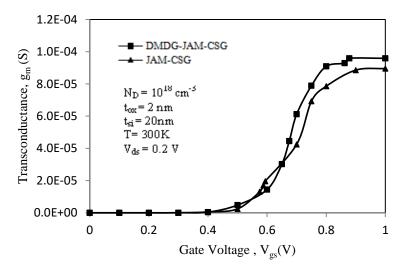

| Figure 2.18 | Transconductance $(g_m)$ with gate voltage, $V_{gs}$ of DMGSE-             | 52 |

|             | JAM-CSG MOSFET and JAM-CSG MOSFET.                                         |    |

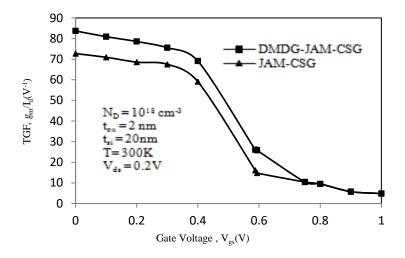

| Figure 2.19 | Variation of TGF with gate voltage, $V_{gs}$ of DMGSE-JAM-                 | 52 |

|             | CSG MOSFET and JAM-CSG MOSFET.                                             |    |

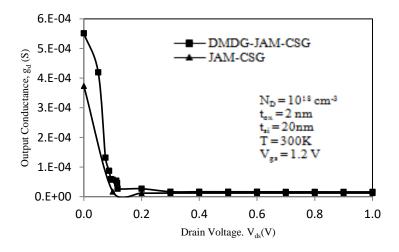

| Figure 2.20 | Variation of Output Conductance, $g_d$ with drain voltage, $V_{ds}$ of     | 53 |

|             | DMGSE-JAM-CSG MOSFET and JAM-CSG MOSFET.                                   |    |

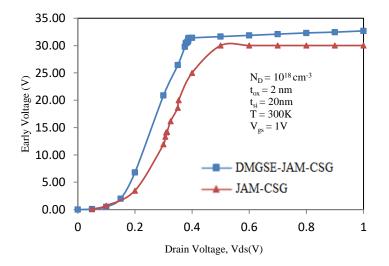

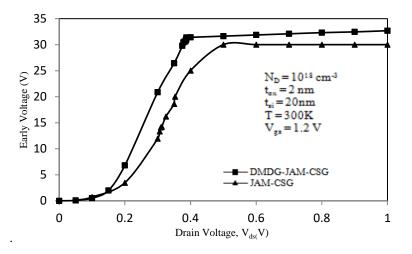

| Figure 2.21 | Early voltage with drain voltage, V <sub>ds</sub> of DMGSE-JAM-CSG         | 53 |

|             | MOSFET and JAM-CSG MOSFET                                                  |    |

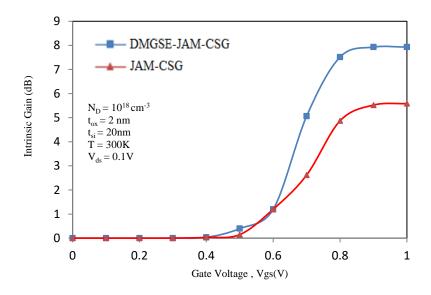

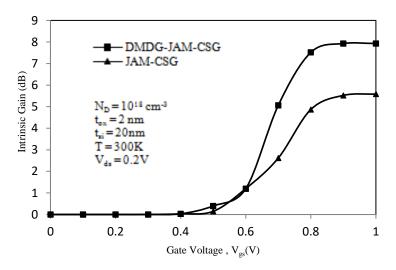

| Figure 2.22 | Intrinsic Gain with gate voltage, $V_{gs}$ of DMGSE-JAM-CSG                | 54 |

|             | MOSFET and JAM-CSG MOSFET.                                                 |    |

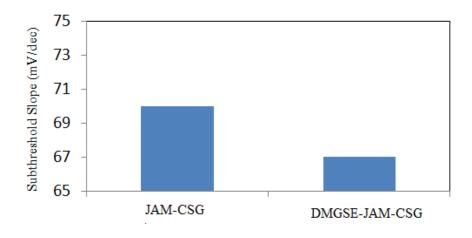

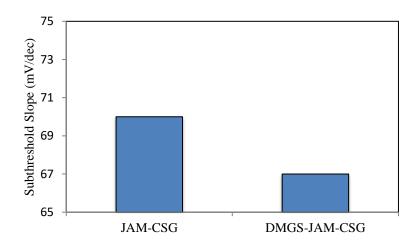

| Figure 2.23 | Subthreshold Slope for JAM-CSG and DMGSA-JAM-CSG                           | 54 |

|             | MOSFET.                                                                    |    |

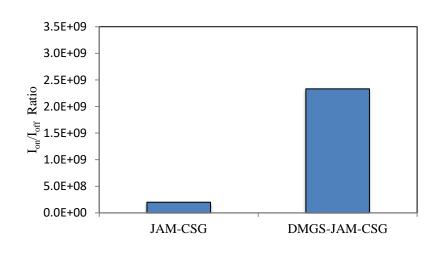

| Figure 2.24 | $I_{\text{on}}/I_{\text{off}}$ ratio for JAM-CSG and DMGSE-JAM-CSG MOSFET. | 55 |

| Figure 3.1  | 2-D view of DMGS-JAM-CSG MOSFET.                                           | 63 |

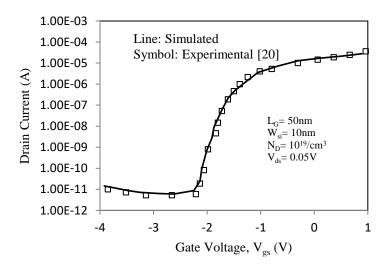

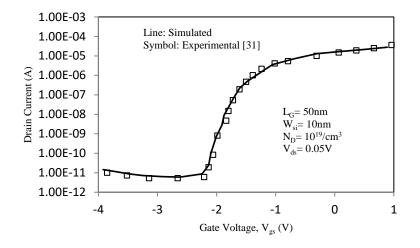

| Figure 3.2  | Calibration of simulated data of our model with the                        | 65 |

|             | experimental data [20].                                                    |    |

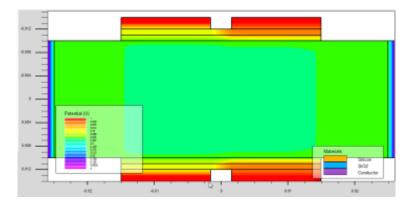

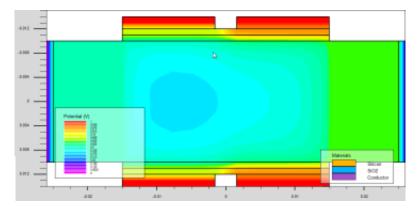

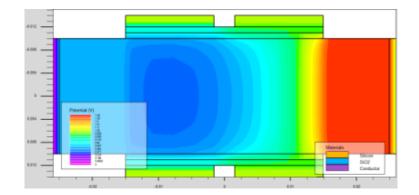

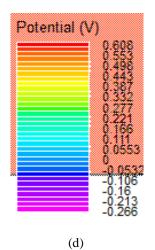

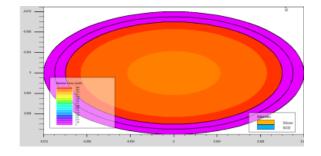

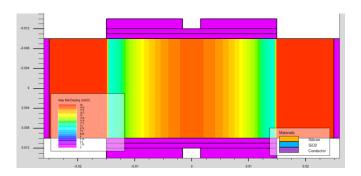

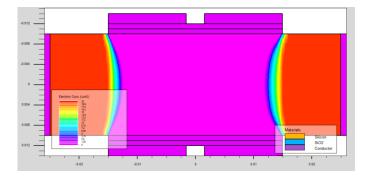

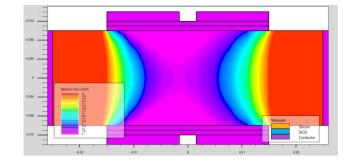

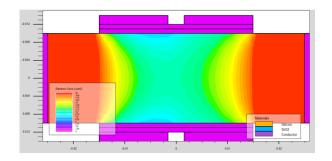

| Figure 3.3  | Potential contour plot for DMGS-JAM-CSG MOSFET at $V_{gs}$ =               | 71 |

|             | 1.0V and $V_{ds}$ = 0.1V for various temperatures (a) 100K (b)             |    |

|             | 300K (c) 500K and (d) color coding scale.                                  |    |

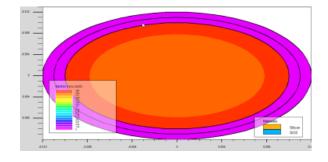

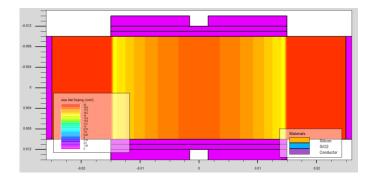

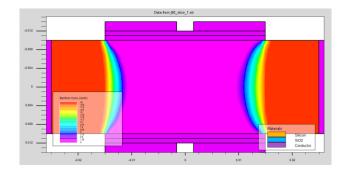

| Figure 3.4  | Contour plot for electron concentration of DMGS-JAM-CSG                    | 72 |

|             | MOSFET at the channel's surface at $V_{gs}$ = 1.0V and $V_{ds}$ = 0.1V     |    |

|             | for various temperatures (a) 100K (b) 300K (c) 500K and (d)                |    |

|             | 101  various temperatures (a) 100K (b) 500K (c) 500K and (d)               |    |

|             | color coding scale.                                                                  |    |

|-------------|--------------------------------------------------------------------------------------|----|

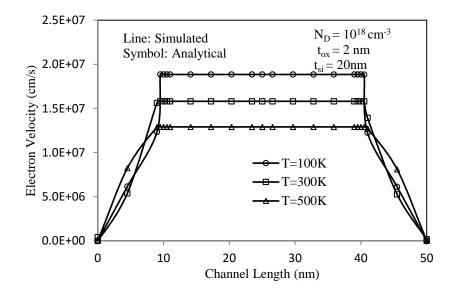

| Figure 3.5  | Electron velocity variation in DMGS-JAM-CSG MOSFET                                   | 73 |

| Figure 5.5  | with channel length at $T$ = 100K, 300K and 500K.                                    | 15 |

| <b>F</b> '  |                                                                                      | 74 |

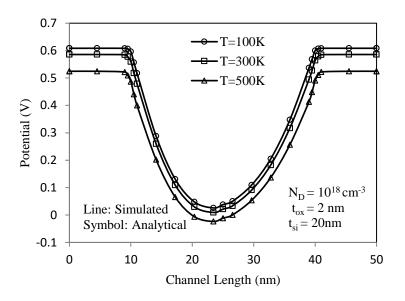

| Figure 3.6  | Potential variation in DMGS-JAM-CSG MOSFET with                                      | 74 |

|             | channel length at different temperatures ( $T$ = 100K, 300K and                      |    |

|             | 500K).                                                                               |    |

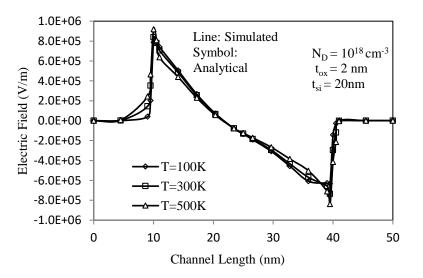

| Figure 3.7  | Electric field variation in DMGS-JAM-CSG MOSFET with                                 | 74 |

|             | channel length at different temperatures ( $T$ = 100K, 300K and                      |    |

|             | 500K).                                                                               |    |

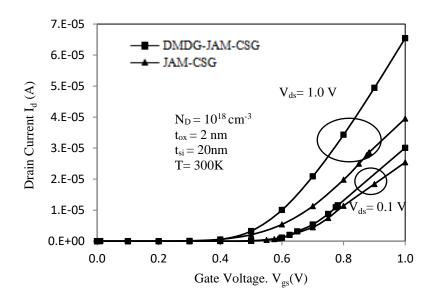

| Figure 3.8  | Transfer characteristics ( $I_d$ vs $V_{gs}$ ) curve for DMDG-JAM-                   | 75 |

|             | CSG and JAM-CSG MOSFET.                                                              |    |

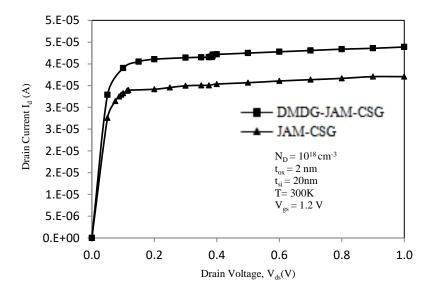

| Figure 3.9  | Output characteristics ( $I_d$ vs $V_{ds}$ ) curve for DMDG-JAM-CSG                  | 75 |

|             | and JAM-CSG MOSFET.                                                                  |    |

| Figure 3.10 | Variation of Transconductance, $g_m$ with gate voltage, $V_{gs}$ for                 | 76 |

|             | DMDG-JAM-CSG and JAM-CSG MOSFET.                                                     |    |

| Figure 3.11 | Variation of TGF with gate voltage, Vgs for DMDG-JAM-                                | 77 |

|             | CSG and JAM-CSG MOSFET.                                                              |    |

| Figure 3.12 | Variation of Output Conductance with Drain Voltage for                               | 77 |

|             | DMDG-JAM-CSG and JAM-CSG MOSFET.                                                     |    |

| Figure 3.13 | Variation of Early voltage with Drain Voltage, $V_{ds}$ for                          | 78 |

|             | DMDG-JAM-CSG and JAM-CSG MOSFET.                                                     |    |

| Figure 3.14 | Variation of Intrinsic Gain with Gate Voltage for DMDG-                              | 78 |

|             | JAM-CSG and JAM-CSG MOSFET.                                                          |    |

| Figure 3.15 | (a) Subthreshold Slope and (b) I <sub>on</sub> /I <sub>off</sub> ratio for DMDG-JAM- | 79 |

|             | CSG and JAM-CSG MOSFET.                                                              |    |

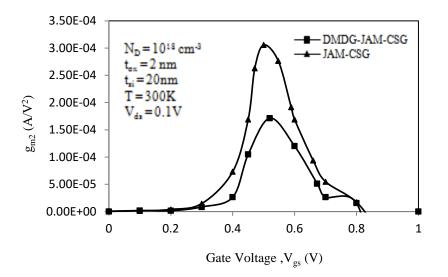

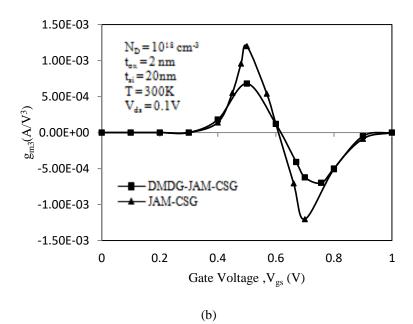

| Figure 3.16 | Variation of Higher-order transconductances for DMDG-                                | 81 |

|             | JAM-CSG and JAM-CSG MOSFET (a) $g_{m2}$ w.r.t. gate                                  |    |

|             | voltage ( <b>b</b> ) $g_{m3}$ w.r.t. gate voltage.                                   |    |

|             |                                                                                      |    |

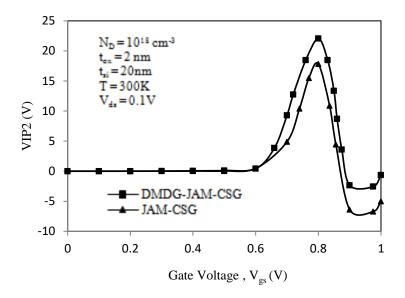

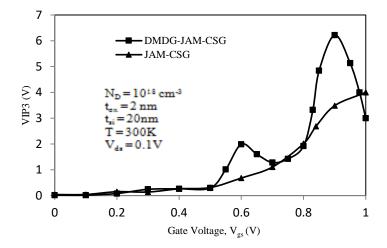

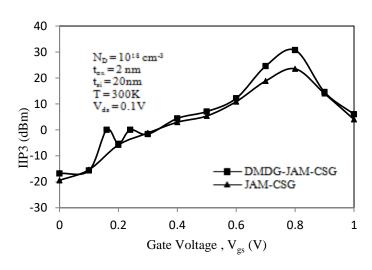

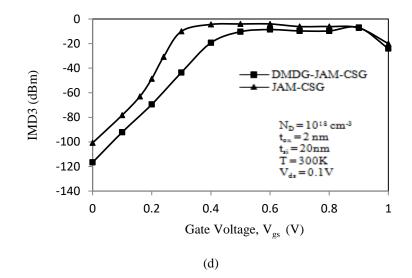

| Figure 3.17 | Variation of various FOMs (a) VIP2 (b) VIP3 (c) IIP3 (d)                             | 84 |

|             | IMD3 with respect to the Gate Voltage, $V_{gs}$ for DMDG-JAM-                        |    |

|             | CSG and JAM-CSG MOSFET.                                                              |    |

|             |                                                                                      |    |

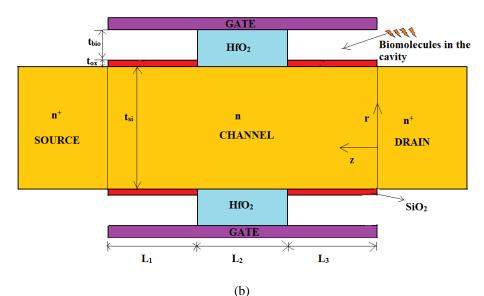

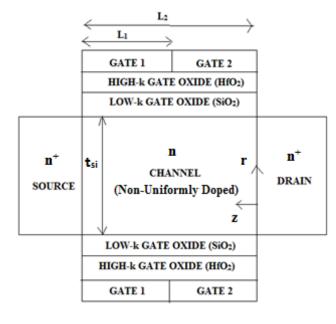

| Figure 4.1   | (a) 3-D and (b) 2-D architectures of JAM-CSG MOSFET                                          | 90  |

|--------------|----------------------------------------------------------------------------------------------|-----|

| i igui e ini | based biosensor.                                                                             | 20  |

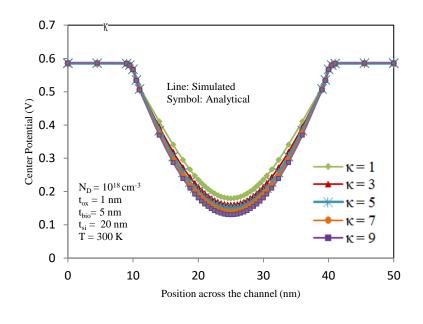

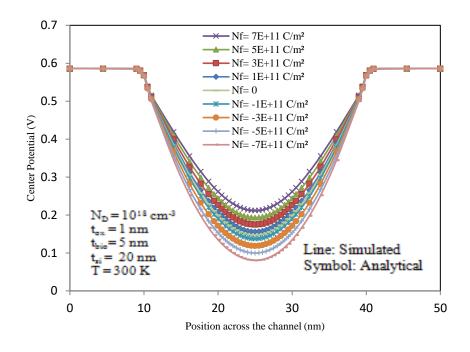

| Figure 4.2   | Center Potential variation of JAM-CSG MOSFET based                                           | 99  |

| rigure 4.2   |                                                                                              | 99  |

|              | biosensor (a) when neutral biomolecules ( $\kappa = 1, 3, 5, 7, 9$ ) are                     |     |

|              | present in the nanogap cavity and (b) when charged                                           |     |

|              | biomolecules ( $N_f = 7E+11 \text{ Cm}^{-2}$ to $-7E+11 \text{ Cm}^{-2}$ when $\kappa = 5$ ) |     |

|              | are filled in the nanogap cavity.                                                            |     |

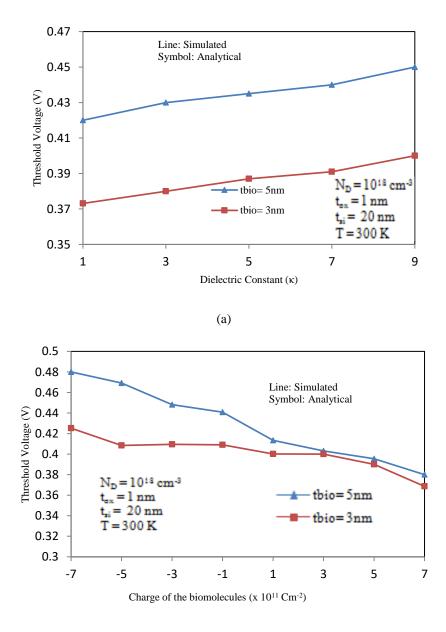

| Figure 4.3   | Threshold voltage variation for distinct cavity heights in                                   | 100 |

|              | JAM-CSG MOSFET based biosensor $(t_{bio})$ (a) when neutral                                  |     |

|              | biomolecules (for $\kappa = 1, 3, 5, 7, 9$ ) are present in the nanogap                      |     |

|              | cavity and (b) when charged biomolecules ( $N_f = 7E+11 \text{ Cm}^{-2}$                     |     |

|              | to -7E+11 Cm <sup>-2</sup> when $\kappa = 5$ ) are filled in the nanogap cavity.             |     |

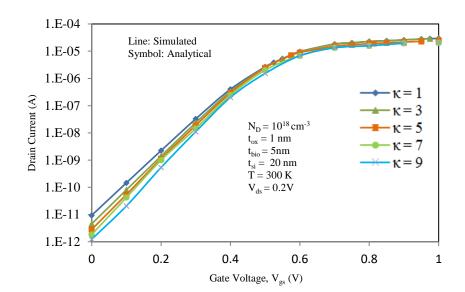

| Figure 4.4   | Transfer characteristics of JAM-CSG MOSFET based                                             | 101 |

|              | biosensor (a) when neutral biomolecules (for $\kappa = 1, 3, 5, 7, 9$ )                      |     |

|              | are present in the nanogap cavity and (b) when charged                                       |     |

|              | biomolecules ( $N_f = 7E+11 \text{ Cm}^{-2}$ to $-7E+11 \text{ Cm}^{-2}$ when $\kappa = 5$ ) |     |

|              | are present.                                                                                 |     |

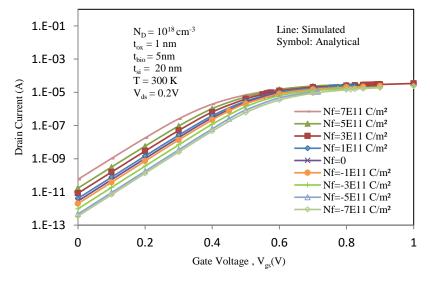

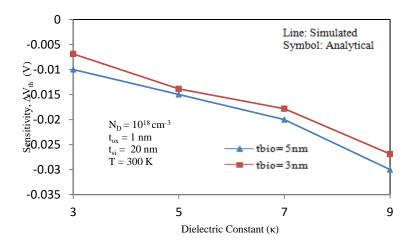

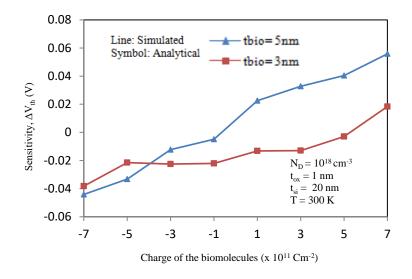

| Figure 4.5   | Variation of Sensitivity factor $\Delta V_{th}$ in JAM-CSG MOSFET                            | 103 |

|              | based biosensor (a) when neutral biomolecules (for $\kappa = 1, 3,$                          |     |

|              | 5, 7, 9) are present in the nanogap cavity and (b) when                                      |     |

|              | charged biomolecules ( $N_f = 7E+11$ Cm <sup>-2</sup> to -7E+11 Cm <sup>-2</sup>             |     |

|              | when $\kappa = 5$ ) are present.                                                             |     |

| Figure 5.1   | (a) 3-D and (b) 2-D schematic of DMGAA-JAM-NWFET.                                            | 111 |

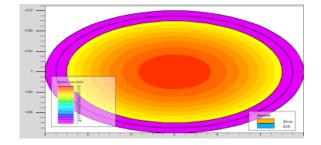

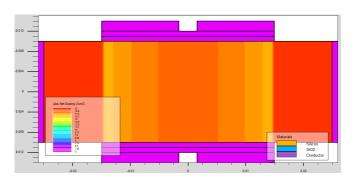

| Figure 5.2   |                                                                                              | 120 |

|              | Contour Plots for Doping Concentration for DMGAA-JAM-                                        |     |

|              | NWFET at $V_{gs} = 1.0$ V and $V_{ds} = 0.2$ V for different straggle                        |     |

|              | lengths, $\sigma$ = (a) 3nm (b) 5nm (c) 7nm and (d) color coding                             |     |

|              | scale used.                                                                                  |     |

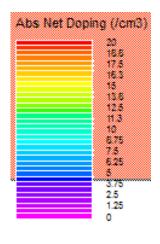

| Figure 5.3   | Doping profile curve for DMGAA-JAM-NWFET with                                                | 120 |

|              | straggle lengths, $\sigma = 3$ nm, 5nm and 7nm.                                              |     |

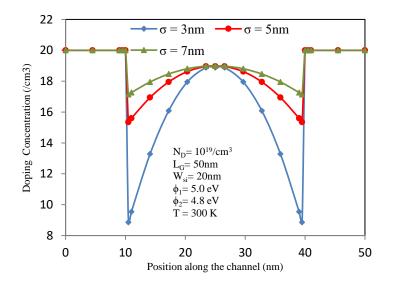

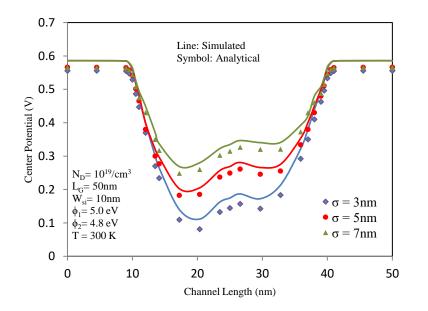

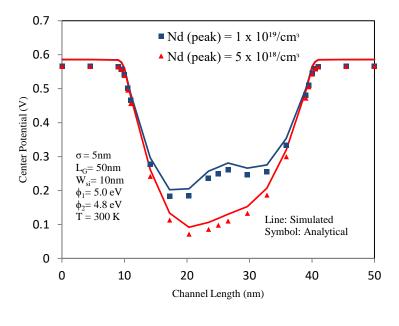

| Figure 5.4   | Center potential variation of DMGAA-JAM-NWFET for                                            | 121 |

|              | different (a) straggle lengths ( $\sigma$ = 3nm, 5nm, 7nm) and (b)                           |     |

|              | peak doping concentration (N <sub>d</sub> (peak) =1 x $10^{19}$ /cm <sup>3</sup> and         |     |

|              |                                                                                              |     |

|             | $5 \times 10^{18} / \text{cm}^3$ ).                                              |     |

|-------------|----------------------------------------------------------------------------------|-----|

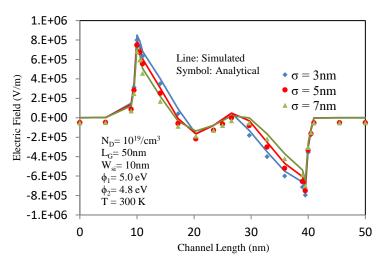

| Figure 5.5  | Electric field variation of DMGAA-JAM-NWFET for                                  | 122 |

| Figure 5.5  | different straggle lengths, $\sigma$ = 3nm, 5nm and 7nm.                         | 122 |

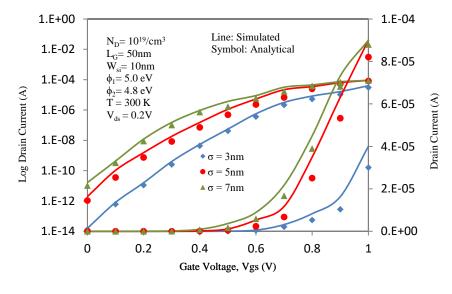

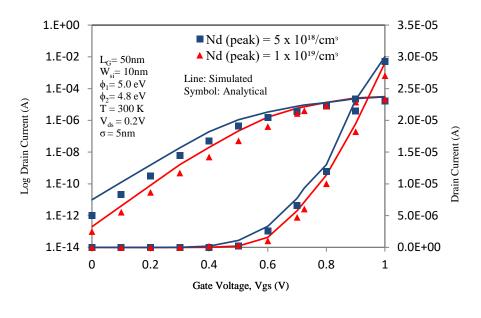

| Figure 5.6  |                                                                                  | 123 |

| Figure 5.6  | Drain current vs. gate voltage of DMGAA-JAM-NWFET for                            | 123 |

|             | various (a) straggle lengths ( $\sigma$ = 3nm, 5nm, 7nm) and (b) peak            |     |

|             | doping concentration (N <sub>d</sub> (peak) = 1 x $10^{19}$ /cm <sup>3</sup> and |     |

|             | $5 \times 10^{18} / \text{cm}^3$ ).                                              |     |

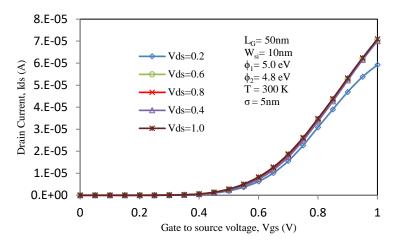

| Figure 5.7  | Transfer characteristics of DMGAA-JAM-NWFET for                                  | 124 |

|             | different drain to source voltages ( $V_{ds} = 0.2, 0.4, 0.6, 0.8$ and           |     |

|             | 1.0V).                                                                           |     |

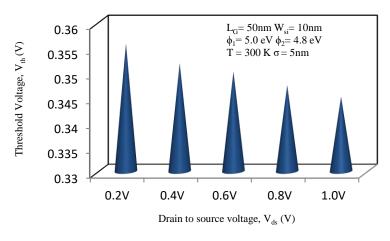

| Figure 5.8  | Threshold voltage of DMGAA-JAM-NWFET at various drain                            | 124 |

|             | to source voltages, $V_{ds}$ .                                                   |     |

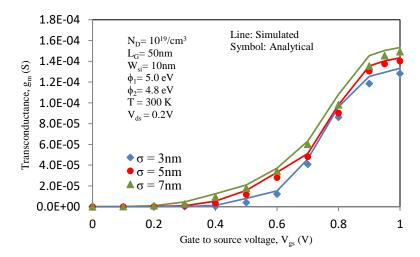

| Figure 5.9  | Transconductance of DMGAA-JAM-NWFET for different                                | 124 |

|             | straggle lengths, $\sigma$ = 3nm, 5nm and 7nm.                                   |     |

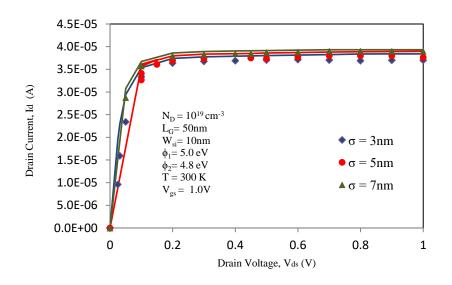

| Figure 5.10 | Output characteristics of DMGAA-JAM-NWFET for different                          | 125 |

|             | straggle lengths, $\sigma = 3$ nm, 5nm and 7nm.                                  |     |

| Figure 5.11 | Output Conductance of DMGAA-JAM-NWFET for different                              | 126 |

|             | straggle lengths, $\sigma$ = 3nm, 5nm and 7nm.                                   |     |

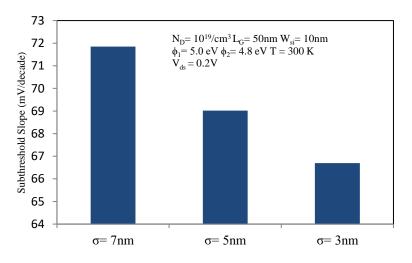

| Figure 5.12 | Subthreshold slope of DMGAA-JAM-NWFET for different                              | 126 |

|             | straggle lengths, $\sigma = 3$ nm, 5nm and 7nm.                                  |     |

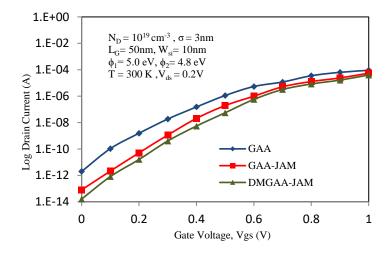

| Figure 5.13 | Input characteristics for GAA, GAA-JAM and DMGAA-                                | 127 |

|             | JAM-NWFET.                                                                       |     |

|             | JAM-NWFEI.                                                                       |     |

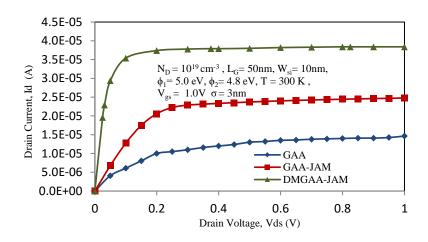

| Figure 5.14 | Output characteristics for GAA, GAA-JAM and DMGAA-                               | 127 |

|             | JAM-NWFET.                                                                       |     |

| Figure 6.1  | (a) 3-D and (b) 2-D view of DM-JAM-CSG MOSFET.                                   | 139 |

| Figure 6.2  | Calibration result.                                                              | 141 |

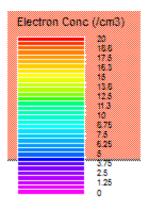

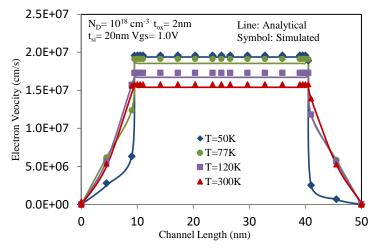

| Figure 6.3  | Electron concentration contour plot for DM-JAM-CSG                               | 147 |

|             | MOSFET at T= (a) 50K (b) 77K (c) 120K (d) 300K and (e)                           |     |

|             | scale for the color coding.                                                      |     |

| Figure 6.4  | Electron velocity at T= 50K, 77K, 120K and 300K for DM-                          | 148 |

|             | JAM-CSG MOSFET.                                                                  |     |

|             |                                                                                  |     |

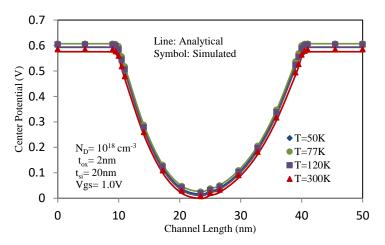

| Figure 6.5 | Center Potential variation at T= 50K, 77K, 120K and 300K         | 149 |

|------------|------------------------------------------------------------------|-----|

|            | for DM-JAM-CSG MOSFET.                                           |     |

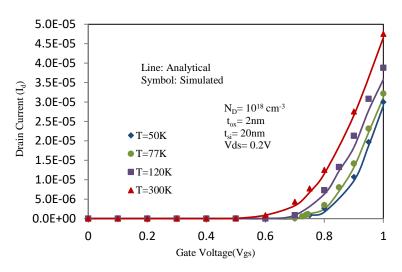

| Figure 6.6 | Transfer characteristics at T= 50K, 77K, 120K and 300K for       | 149 |

|            | DM-JAM-CSG MOSFET.                                               |     |

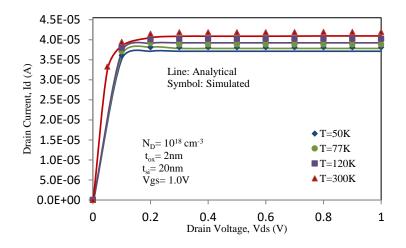

| Figure 6.7 | Output characteristics at T= 50K, 77K, 120K and 300K for         | 150 |

|            | DM-JAM-CSG MOSFET.                                               |     |

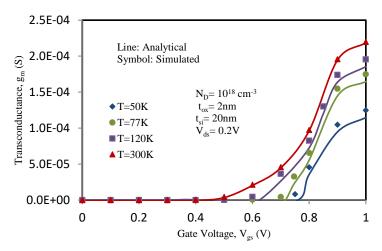

| Figure 6.8 | Transconductance $(g_m)$ variation with $V_{gs}$ at T= 50K, 77K, | 150 |

|            | 120K and 300K for DM-JAM-CSG MOSFET.                             |     |

| Figure 6.9 | Subthreshold Slope for DM-JAM-CSG MOSFET at various              | 151 |

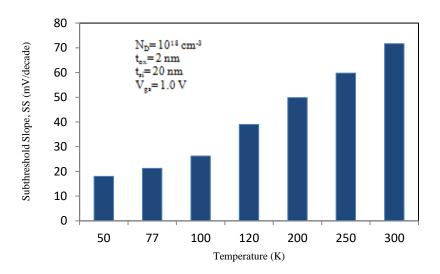

|            | Cryogenic temperatures.                                          |     |

## LIST OF SYMBOLS, ABBRIEVIATIONS AND NOMENCLATURE

| A <sub>v</sub>              | Voltage gain                                   |

|-----------------------------|------------------------------------------------|

| Cox                         | Capacitance per unit area                      |

| I <sub>ds</sub>             | Drain Current                                  |

| I <sub>lin</sub>            | Linear Current                                 |

| I <sub>sat</sub>            | Saturation Current                             |

| I <sub>sub</sub>            | Subthreshold Current                           |

| N <sub>D</sub> <sup>+</sup> | Partial Ionization                             |

| S <sub>Ids</sub>            | Drain Current Sensitivity                      |

| V <sub>EA</sub>             | Early Voltage                                  |

| V <sub>T</sub>              | Thermal Voltage                                |

| k <sub>B</sub>              | Boltzmann's constant                           |

| t <sub>si</sub>             | Substrate's Thickness                          |

| ε <sub>hk</sub>             | Dielectric Constants of HfO <sub>2</sub> layer |

| ε <sub>ox</sub>             | Dielectric Constants of SiO <sub>2</sub> layer |

| ε <sub>si</sub>             | Dielectric Constant of Si                      |

| $\theta_{short}$            | Subthreshold Slope Factor                      |

| $\phi_{bi}$                 | Built- in Voltage                              |

| AM                          | Accumulation-Mode                              |

| BJT                         | Bipolar Junction Transistor                    |

| BTBT                        | Band-to-Band Tunneling                         |

| $C_G$                       | gate capacitance                               |

| CGAA                        | Cylindrical Gate All Around                    |

| CLM                         | Channel Length Modulation                      |

| CMD                         | Carrier Mobility Degradation                   |

| CMOS                        | Complementary Metal Oxide Semiconductor        |

| CONMOB                      | Concentration Dependent Mobility model         |

| CSG                         | Cylindrical Surrounding Gate                   |

| DG                          | Double Gate                                    |

| DIBL                        | Drain-Induced Barrier Lowering                 |

| DM-FET                | Dielectric Modulated-FET                          |

|-----------------------|---------------------------------------------------|

| DMGAA                 | Dual-Metal Gate All Around                        |

| DMGSE                 | Dual- Material Gate Stack Engineered              |

| DSG                   | Double Surrounding Gate                           |

| <i>E<sub>c</sub></i>  | Critical Electric Field                           |

| ED                    | Ionization Energy of the Donor Dopant             |

| ЕОТ                   | Effective Oxide Thickness                         |

| FET                   | Field- Effect Transistor                          |

| FLDMOB                | Field Dependent Mobility Model                    |

| FOMs                  | Figure of Merits                                  |

| GAA                   | Gate All Around                                   |

| gd                    | Output Conductance                                |

| GIDL                  | Gate-Induced Drain Leakage                        |

| gm                    | Transconductance                                  |

| GME                   | Gate Material Engineering                         |

| HCEs                  | Hot Carrier Effects                               |

| ICs                   | Integrated Circuits                               |

| IDSS                  | Maximum Drain Current                             |

| I <sub>gidl</sub>     | GIDL current                                      |

| IIP3                  | Third-order Intercept Input Power                 |

| IM                    | Inversion-Mode                                    |

| IMD3                  | Third-order Intermodulation Distortion            |

| ΙοΝ                   | ON current                                        |

| JAM                   | Junctionless Accumulation Mode                    |

| JLT                   | Junctionless Transistor                           |

| k                     | Dielectric Constant                               |

| L                     | Channel Length                                    |

| LGAA                  | Lateral Gate All Around                           |

| LSP                   | Low Standby Power                                 |

| MOSFET                | Metal Oxide Semiconductor Field Effect Transistor |

| ND                    | Channel Doping                                    |

| N <sub>D</sub> (peak) | Peak Doping Concentration                         |

| $N_D^+$          | Source/Drain Doping                  |

|------------------|--------------------------------------|

| Nf               | Charge of the Biomolecules           |

| NWFET            | Nanowire FET                         |

| PPA              | Parabolic Potential Approximation    |

| q                | Electronic Charge                    |

| RF               | Radio Frequency                      |

| SCEs             | Short- Channel Effects               |

| SELBOX           | Selective Buried Oxide               |

| SS               | Subthreshold Slope                   |

| Т                | Temperature                          |

| t <sub>bio</sub> | Thickness of the Nanogap Cavity      |

| TG               | Tri-Gate                             |

| TGF              | Transconductance Generation Factor   |

| t <sub>ox</sub>  | Thickness of oxide layer             |

| ULSI             | Ultra Large Scale Integration        |

| V <sub>DD</sub>  | drain voltage                        |

| V <sub>ds</sub>  | Voltage across Drain and Source      |

| V <sub>fb</sub>  | Flatband Voltage                     |

| VGAA             | Vertical Gate All Around             |

| VGS              | Gate Voltage                         |

| VIP2             | Second-order Voltage Intercept Point |

| VIP3             | Third-order Voltage Intercept Point  |

| $V_p$            | Pinch-off Voltage                    |

| v <sub>s</sub>   | Saturation Velocity                  |

| Vth              | Threshold Voltage                    |

| Z                | Co-ordinates for Horizontal Axis     |

| $\Delta V_{th}$  | Sensitivity of the device            |

| μ                | Mobility of the carrier              |

| μη               | Low- Field Mobility                  |

| σ                | Straggle Length Parameter            |

| τ                | Switching Speed                      |

| E                | Electric Field                       |

| r               | Co-ordinates for Vertical Axis  |

|-----------------|---------------------------------|

| v               | Electron Velocity               |

| $\Delta V_{fb}$ | Change of the Flat Band Voltage |

| λ               | Characteristic Length           |

| ψ               | Potential                       |

| $\psi(r,z)$     | Potential Distribution          |

| φ               | Work-function                   |

# **CHAPTER 1**

# Introduction

## 1.1 Background

The development of Integrated Circuits (ICs) and Complementary Metal- Oxide-Semiconductor (CMOS) has revolutionized our daily life needs including, televisions, laptops, mobile phones, etc. as well as transformed the industrial applications comprising, robotics, sensors, amplifiers, etc. The fundamental element of the ICs and CMOS technology is the Metal Oxide Semiconductor Field Effect Transistors (MOSFET). Gorden Moore predicted that with the growth in these technologies, after every 18 months, the number of transistors assembled on a chip would nearly get doubled. This compactness of the transistors lead towards the scaling of the MOSFET's size at nanometer scale along with minimum Short- Channel Effects (SCEs). Fabrication complication also arises in the devices with shorter channel. Therefore, in order to suppress these issues and keep up with the proper functioning, advanced materials and innovative device structures are required.

Various device designs with shorter channel lengths have been proposed which possesses lesser SCEs. Multi- gate MOSFETs are augmenting the scaling dimensions of the device because of their upraised control of the gate over the channel. Double Gate (DG) MOSFETs introduced by Sekigama [1] in 1984 and Balestra [2] in 1987, possesses dual gates, one above and one below the channel. The presence of dual gates leads to better gate control and reduced surface leakage path between the source and drain. Hence, offers higher scalability and more exemption from the SCEs as contrasted with the conventional MOSFETs. To reduce these SCEs further, Huang [3] proposed FinFET in the year 1999. FinFET consists of a thin silicon fin which is surrounded by a metal gate. This structure exercises a higher gate command over the channel and minimizes the SCEs.

To extend the scalability and electrostatic control, another structure named, Cylindrical Surrounding Gate (CSG) MOSFET was proposed [4-9]. In CSG MOSFET, the channel

is entirely wrapped by the metal gate which provides much more escalated gate control over the channel. Therefore, augments the charge carrier density and the overall performance of the MOSFET. CSG MOSFET progressed by implementing double gate MOSFET on CSG structure, thus, evolving a Double Surrounding Gate (DSG) MOSFET. DSG MOSFET exhibits a considerable escalation of the gate control over the channel due to the presence of two cylindrical double gates implemented on a surrounding gate structure. Chen [10] demonstrated experimentally and analytically, research on the DSG MOSFET. DSG MOSFET shows much lower ON resistance, higher drain currents and energy storage capacity (~1.4 times of conventional MOSFETs). All the above- stated devices exhibits the problem of source/drain resistance. In order to eliminate this problem, Colinge [11] introduced a Junctionless Transistor (JLT), which has uniformly doped source  $(N^+)$ , channel  $(N^+)$  and drain  $(N^+)$ . As the transistors have scaled upto deca nanometres range, it is becoming difficult to reproduce ultra sharp doping concentration gradients along with the thermal budget requirement and costly annealing techniques. Therefore, elimination of junctions due to uniform doping in JLT MOSFET poses a favourable situation. As, there is no change in the doping gradient, hence the fabrication process also becomes simpler. However, the presence of higher doping in the channel region causes the problem of Carrier Mobility Degradation (CMD), which lowers down the ON-state current. To overcome this problem another transistor Junctionless Accumulation Mode (JAM) MOSFET was introduced. In this MOSFET, the doping of the channel is slightly lesser than the source/drain, which reduces the CMD problem and also avoids high- parasitic resistance. Thus, increases the drain current and transconductance with lowered SCEs.

To further mitigate these issues, Device Engineering has been introduced. Dual Metal Gate Engineering [12-15] is considered as one of the solution. This technique employs two metal gates of different work functions, keeping the lower work function metal gate at the drain end [14-19]. This reduces the impact of the high speed electrons at the drain end and thus, elevating the carrier efficiency. Moreover, subthreshold leakage current is a predominant phenomenon in multigate devices and it is prevalent as the gate oxide leakage current. It can be subsided by employing Gate Dielectric Engineering [20-21], which exhibits a high- k dielectric layer in addition to the SiO<sub>2</sub> layer. This helps to

easily subsides the gate leakage current. In this work, two engineering approaches are proposed to make device more efficient.

## **1.2 MOSFET Scaling**

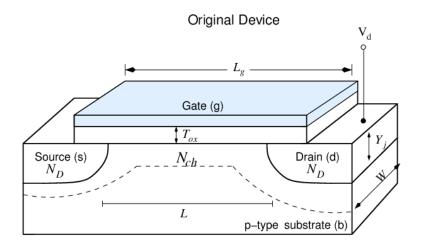

There is spectacular increase in the device density due to continous decrease in minimum feature size. Figure 1.1 depicts the traditional MOSFET device and the scaled MOSFET device, where the MOSFET is scaled by a factor of 'S' (S>1).

Figure 1.1 Traditional and Scaled MOSFET device structure [22].

As the device size is reduced, more functionality may be added in same size. Apart from this, MOSFET scaling also offers reduction in power consumption and cost of Integrated Circuit (IC). Scaling also leads to increased switching speed because of the decrement in the transit time of the carriers. The MOSFET scaling has been a fundamental driving force behind the continuous improvement in integrated circuit (IC) performance and integration density for several decades.

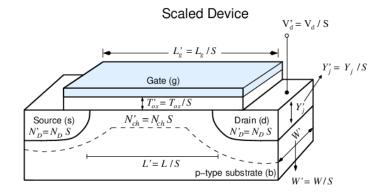

The concept of MOSFET scaling is rooted in Moore's Law. In 1969, Gordon Moore anticipated that the number of transistors on an IC would get twice approximately after every 18 months as shown in Figure 1.2. Over the years, his law has proved to be true because of the continuous efforts from the semiconductor device design engineers to push the limits of technology. Scaling of MOS devices improves the power density and speed performance of IC but also results in several SCEs. The SCEs dominate in reduced size devices and degrade the performance of the device significantly.

Figure 1.2 MOSFET scaling [23].

## **1.3 Short Channel Effects (SCEs)**

These are the phenomena that occur in MOSFET when the length of the channel is down- sized to the nanometer range. As the channel length reduces, traditional MOSFET face several challenges that can degrade transistor performance and reliability. Scaling the dimensions of the MOSFET device has made the depletion region comparable with the channel length. This makes the gate lose all its control over the channel, thus, instigating various kinds of SCEs which hamper the effective working of the MOSFET by altering its input and output characteristics. The main SCEs are described as follows:

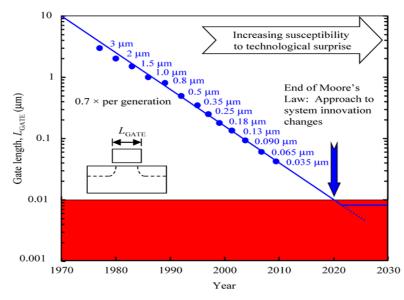

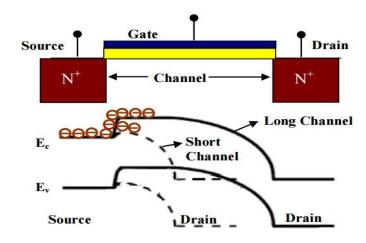

#### 1.3.1 Drain Induced Barrier Lowering (DIBL)

DIBL [24, 25] can be described as the lowering of the threshold voltage of a MOSFET when the drain is connected at higher voltages. The threshold voltage is the gate voltage

required to invert the surface of the channel and to make a conductive path between the source to drain. Figure 1.3(a) illustrates the depletion region in the channel for long and short channel devices and Figure 1.3(b) represents the conduction band profile versus position across the channel length at  $V_{ds}=0$  V and 1.0 V. In the long channel devices, the potential barrier is dependent only on the gate voltage. However, in short channel devices, the potential barrier is also dependent upon the drain bias as well. This is because the source and drain sections lie in close proximity in the case of short channel devices, the potential barrier decreases. This also changes and reduces the threshold voltage. This deduction in the threshold voltage in short channel devices owing to the applied drain bias is termed as DIBL.

Figure. 1.3 Elucidation of (a). long channel and short channel device and (b). DIBL [26].

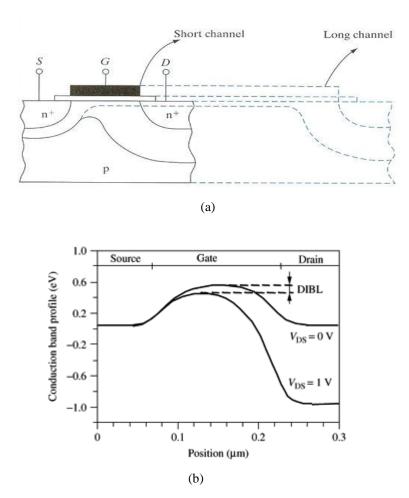

#### 1.3.2 Threshold Voltage Roll-off

In short channel devices, charge sharing takes place between source and drain regions and it further instigates field penetration from drain to source region [26] as depicted in Figure 1.4. Field penetration lowers the potential barrier at the source end, consequently, increasing the charge carriers flow and causing decrement in threshold voltage and higher sub-threshold drain current.

Figure 1.4 Threshold- Voltage Roll- off illustration using Conduction Band and Valance Band diagram.

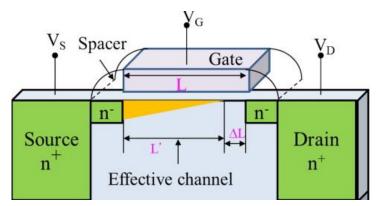

#### 1.3.3 Channel Length Modulation

With the increase in the drain bias, the channel region is pinched off at the drain end, reducing the channel length (*L*) by  $\Delta L$  as shown in Figure 1.5. This decrease in the effectual channel length of the MOSFET is termed as Channel Length Modulation. Tise pinch off at the drain side alters the drain current and threshold voltage for the device. However, in long channel devices the threshold voltage does not depends upon  $\Delta L$ . Hence, the effective channel length will be L- $\Delta L$ .

Figure 1.5 Schematic illustration of Channel Length Modulation [27].

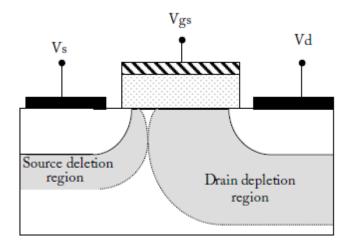

### 1.3.4 Punchthrough

Punchthrough effect in MOSFET takes place when the depletion region encompassing the drain-body junction stretches in the direction of the source-body junction, with the result that the both the depletion regions meet with each other and form a single depletion region. This effect is well depicted in Figure 1.6. At this point, gate loses its control over the channel. Consequently, the current cannot be regulated with the gate voltage and increases rapidly with drain bias [28]. The prime cause behind this punchthrough effect is that the current transport occurs deeper in the bulk and distant from the gate. Thus, increasing the subthreshold leakage current, which further results into an increment in the power consumption. Punchthrough effect can be lowered down by increasing the substrate doping [29]. This technique reduces the depletion regions surrounding the source and drain. Thus, no parasitic current path formation takes place. But this also leads to the increment in the subthreshold swing, which makes this approach not to be suggested to minimize punchthrough effect. Other techniques to diminish punchthrough can be using narrower oxides, shallower junctions and of course, by employing longer channel lengths.

Figure 1.6 Schematic diagram for punchthrough effect [30].

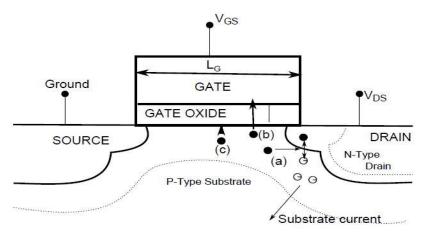

### 1.3.5 Impact Ionization and Hot Carriers Effects

When electric field is enhanced in the short channel length devices, the carriers acquire excessive kinetic energy greater than their thermal energy, and then they are referred to as "hot carriers". These carriers can follow three possible phenomenons: (i). these hot carriers can multiply themselves owing to impact ionization, leading to high substrate current. (ii). Carriers possessing energy more than the dielectric conduction band energy

may cause conduction current towards the gate. (iii). Carriers with very high energy can get introduced towards the inside of the gate oxide layer and may destroy the dielectric interface. This can also alter the threshold voltage and drain current of the device. These three phenomenons portraying hot carrier injection mechanism are displayed in Figure 1.7.

Figure 1.7 Diagrammatic representation for hot carrier injection mechanism [31].

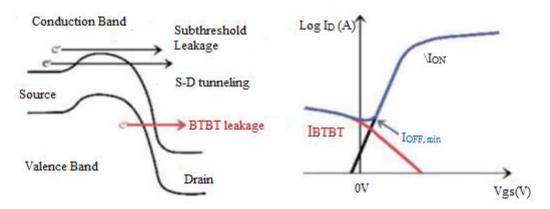

### 1.3.6 Band- to- Band- Tunneling (BTBT) Leakage

Another challenge that arises in heavily doped transistors is the BTBT Leakage mechanism. MOSFETs working in the volume depletion mode in the OFF- state behaviour possesses an overlapping between the valence and the conduction bands in the channel and drain regions respectively [32, 33]. Because of the higher doping present inside the channel, band overlap results in the tunnelling of electrons arising out of valence band of the channel towards the conduction band of the drain region [32] (for n- channel junctionless transistor). This tunnelling leakage mechanism is depicted in Figure 1.8, which further brings about the escalation of the drain leakage current during the OFF- state. This augmentation in the drain current is unenviable and brings about large amount of static power dissipation. Therefore, BTBT is a prime difficulty encountered in the case of low standby power (LSP) applications.

Figure 1.8 Schematic diagram of various leakage mechanisms [34].

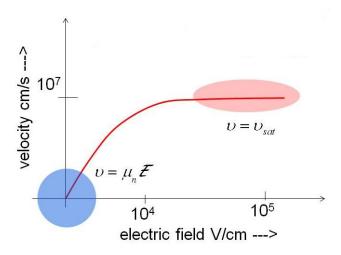

### 1.3.7 Velocity Saturation

This effect also influences the functioning of the short-channel MOSFET devices. The velocity of the electrons is directly proportional to the electric field. With the increase in the electric field, the velocity of the carriers also rises. At elevated electric field, this velocity attains a maximum critical value and at this value, the electron velocity starts to saturate. Beyond the saturation velocity, further increase in the electric field will bring about the decrease in the mobility of the electrons, thus, causing minimization of the drain current and transconductance. With the aim of avoiding such situation, employment of constant field scaling is done; this would retain the identical electric field. The variation of electron velocity with electric field is well represented in Figure 1.9.

Figure 1.9 Velocity of the electron versus electric field for silicon.

### 1.3.8 Gate Oxide Leakage

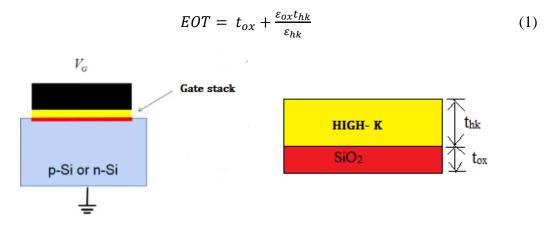

When the width of the gate oxide is reduced to 3nm or 2nm or less than this in the MOSFET devices, tunnelling of the carriers occurs. This in turn increases the gate oxide leakage current, which deteriorates the functioning of the device. This may be eliminated by implementing a gate stack within the device. The gate stack is a combination of a low- k oxide accompanied by a high- k oxide layer, this administers towards the decrement in the leakage current to some extent.

### **1.4 Literature Survey**

In order to compensate for the SCEs upon the device significantly, several device topologies [21, 36-40, 53-55] have been introduced. Such device topologies are enumerated as:

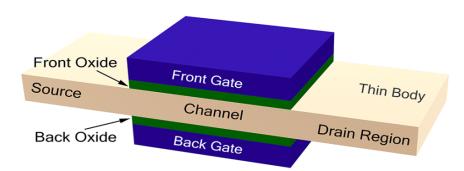

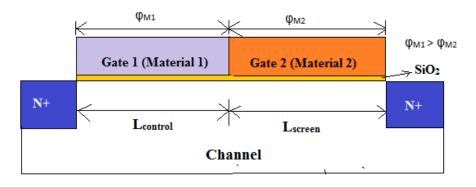

### 1.4.1 Double Gate (DG) MOSFET

It consists of two gates existing on both sides of the channel called as a front gate and a back gate [33] and is shown in Figure 1.10. Thus, controls the channel very effectively by employing dual gate contacts and shorter channel width. This assists in subduing the short channel effects and further directing towards higher drain current [35]. T. Sekigawa and Y. Hayashi introduced DG MOSFET in 1984 [36] stating the robustness of this device over single- gate MOSFET. This happens since the gate guards the channel from both the sides, thus quelling the electric field penetration through the gate and helps in lowering down the SCEs. There can be two alignments for the case of DG MOSFETs: Asymmetric or Symmetric DG MOSFET. Asymmetrical DG MOSFET has distinct biasing applied on both the gates, whereas in symmetrical DG MOSFET, the two gates are connected to a common bias. Also, the thickness of the two oxides is different for the instance of asymmetrical DG MOSFET and similar thickness for the symmetrical DG MOSFET instance.

Figure 1.10 Structure of Double Gate MOSFET [37].

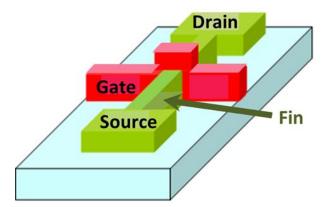

### 1.4.2 Fin-FET

As the number of interconnected gate leads to increment in the control of the gate over the channel, electrostatic potential increases. So the further improvement in DG MOSFET resulted in Tri- Gate or Fin- FET MOSFET structure. In Fin- FET, gate surrounds the narrow silicon pillar from three sides, called as "fin" which builds up the gate control over the channel. Consequently, lowering down the SCEs encountered by deep submicron transistors, such as DIBL and threshold voltage roll- off. It also minimises the leakage current. This device topology was proposed by Huang et al in 1999 [38] and is depicted in Figure 1.11. As, it is gated on three sides of the channel, hence is named "Tri- Gate".

Figure 1.11Schematic view of Fin-FET structure [39].

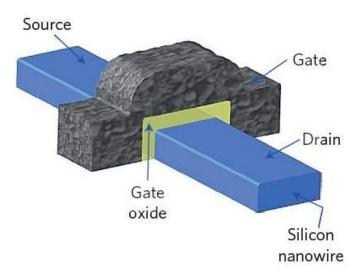

### 1.4.3 Gate All-Around (GAA) MOSFET

In GAA MOSFET [40-42], the gate wraps all over the beam of silicon pillar. The gate may have any type of orientation like broad or thin, rectangular, triangular, or

circular. GAA MOFET is also known as Surrounding Gate MOSFET [43, 44] or Wrap Around Gate MOSFET [45]. As a consequence of the existence of gate all around the channel, better electrostatic control is provided by GAA MOSFET. It offers 50% more scalability than DG FET [43, 45]. The major benefit of the GAA perspective is immensely inflated packing density in the event of vertical structures; on the other hand, the major drawback is the extremely confined current-carrying potential per device which acts as an utmost constraint for rapid logic applications [46].

### 1.4.3.1 Rectangular GAA MOSFET

Figure 1.12 depicts the 3D and cross-sectional structure of Rectangular GAA MOSFET. In this, a gate of rectangular shape completely wraps around the rectangular substrate. Rectangular GAA MOSFET provides magnificent electrostatic control of the channel, elevated current drivability, favourable subthreshold swing, strengthening of mobility and also possesses reduced SCEs as compared with the DG and Fin-FET structures.

Figure 1.12 Rectangular GAA MOSFET [47].

### 1.4.3.2 Triangular GAA MOSFET

Figure 1.13 shows the 3D and cross-sectional structure of triangular GAA MOSFET. Here the gate is of triangular shape, completely surrounding the triangular substrate material. The local volume inversion in corners, called as corner effect increments the low field mobility in these type of MOSFET. It also helps to enhance the conduction across the sharp corners of the triangular GAA MOSFET.

In addition, a substantial strengthening of the carrier mobility (around  $\sim 1000 \text{cm}^2/\text{Vs}$ ) is noticed for the triangular cross-sectional MOSFETs.

Figure 1.13 Triangular GAA MOSFET (a) 3D view (b) cross sectional view [48].

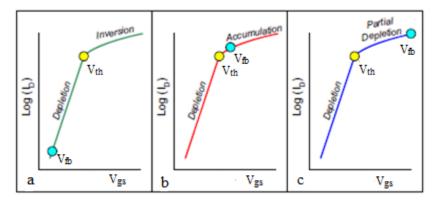

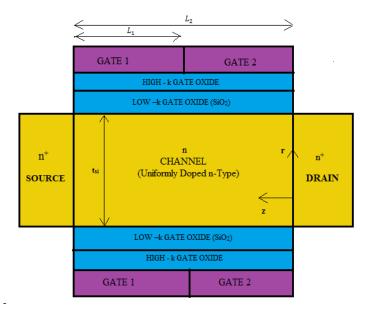

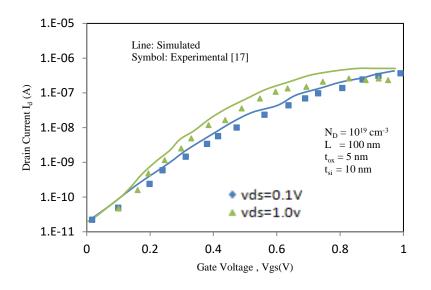

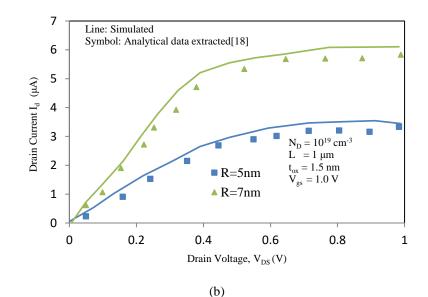

### 1.4.3.3 Cylindrical GAA MOSFET