# LOW POWER, DUAL MODE OPERATIONAL 7T SRAM BIT CELL AND SENSE AMPLIFIER FOR PERFORMANCE ENHANCEMENT

A Thesis Submitted

In Partial Fulfillment of the Requirements

for the Degree of

# **DOCTOR OF PHILOSOPHY**

by

BHAWNA RAWAT (2K19/PHDEC/501)

Under the Supervision of

Prof. POORNIMA MITTAL

Department of Electronics and Communication Engineering

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Shahbad Daulatpur, Main Bawana Road

Delhi-110042. India

June, 2023

# **CERTIFICATE**

Certified that <u>Bhawna Rawat</u> (2K19/PHDEC/501) has carried out their search work presented in this thesis entitled <u>"Low Power, Dual Mode Operational 7T SRAM Bit Cell and Sense Amplifier for Performance Enhancement"</u> for the award of <u>Doctor of Philosophy</u> from Delhi Technological University, Delhi, under my supervision. The thesis embodies results of original work, and studies are carried out by the student herself and the contents of the thesis do not form the basis for the award of any other degree to the candidate or to anybody else from this or any other University/Institution.

Date: 25-June-2023 **Prof. POORNIMA MITTAL**

Supervisor

Department of ECE

Delhi Technological University

Delhi, India

ii

CANDIDATE'S DECLARATION

I, Bhawna Rawat (Roll No. 2K19/PHDEC/501) student of Ph.D., hereby declare that the

Dissertation titled "Low Power, Dual Mode Operational 7T SRAM Bit Cell and Sense

Amplifier for Performance Enhancement" which is submitted by me to the Department

of Electronics and Communication Engineering, Delhi Technological University, Delhi in

partial fulfillment of the requirement for the award of the degree of **Doctor of Philosophy**,

is original and not copied from any source without proper citation. This work has not

previously formed the basis for the award of any Degree, Diploma Associateship,

Fellowship or other similar title or recognition.

Place: DTU, Delhi BHAWNA RAWAT

Date: 25-June-2023

iii

## **ABSTRACT**

Cache memory is a key component for most microprocessors in embedded system. The increasing processing load has resulted in an upsurge in the demand for low power, high performance SRAM bit cells. The memory is formed by an array of bit cells for data storage, and its peripheral circuits. The peripheral circuit comprises of SA, row-column decoders, write drivers, and pre-charge circuitry. The 6T bit cell was the industry standard, but with decreasing technology node and  $V_{DD}$  scaling the performance for the 6T cell is deteriorating. This has motivated researchers to design other bit cells. Altering the bit cell design mandates re-designing the sense amplifier topology as well to make it compatible with the modified cell design.

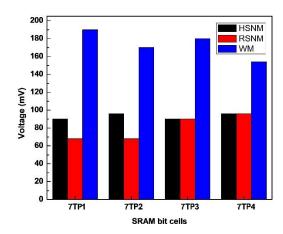

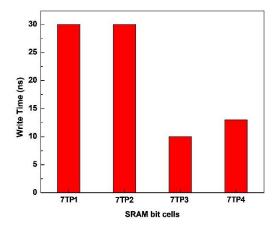

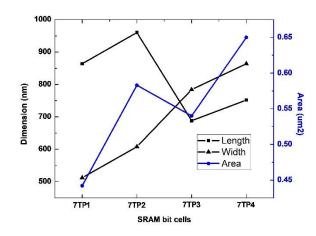

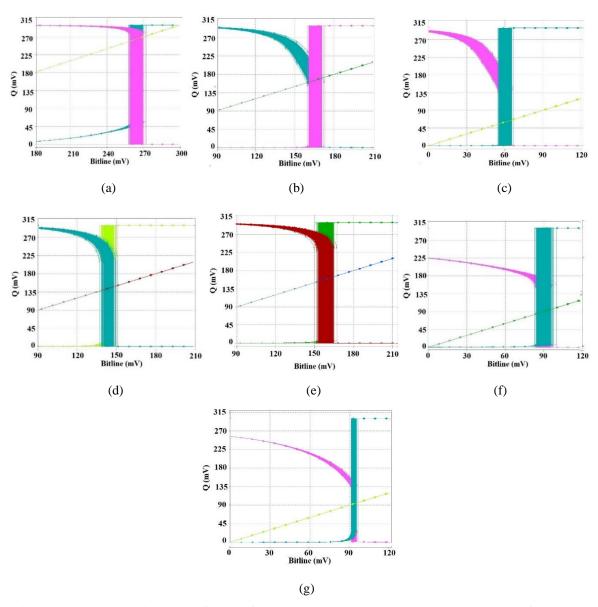

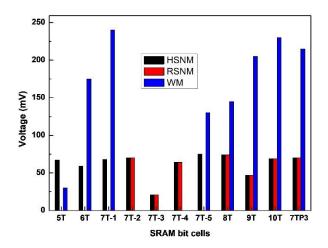

In keeping with the same, four designs (7TP1, 7TP2, 7TP3, and 7TP4) of single ended, single port 7T bit cells are proposed. The cells differ from each other in terms of the number of multi-threshold devices and the read port topology adopted by the cell. The performance of the proposed of the four proposed cells is compared to identify the best design topology. Based on the comparison the 7TP3 cell is identified as the best topology amongst the four designs. Its HSNM and RSNM are high at 90 mV; the WM value is slightly high. While, the write time is considerably low at 10 ns. Additionally, its area is also towards the lower end in comparison to others and the design is also nearly square. Thus, 7TP3 cell design is accepted as the best design topology amongst the four proposed 7T bit cells. All the cells are designed at 32 nm technology node and simulated for 300 mV supply voltage.

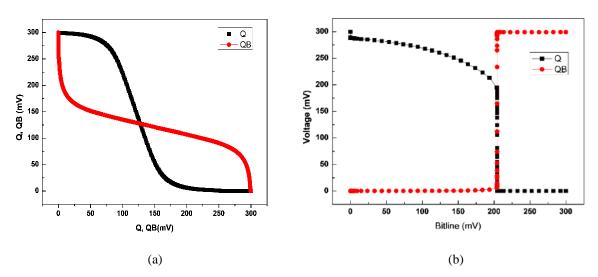

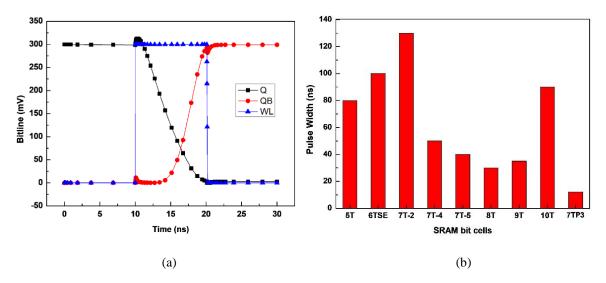

Thereafter, the performance of the proposed 7TP3 bit cell is compared against pre-exiting bit cells to validate its performance. The major highlights for the 7TP3 cell are - its read port which is designed to exclude the data node from read discharge current path and it use of a high performance transistor to improve write ability for the cell. Collectively, they help improve the read and write stability for the cell. The hold, read, and write noise margin for the cell are 90, 90, and 180 mV respectively for supply voltage of 300 mV. It requires a 10 ns pulse-width to perform a successful write operation.

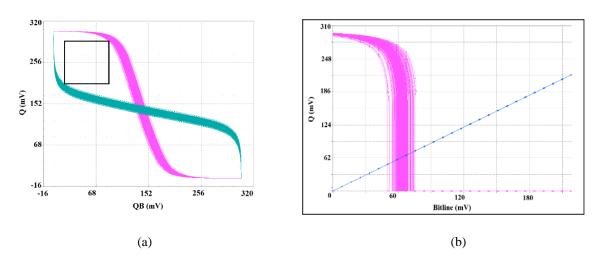

The robustness of 7TP3 cell is analyzed using its resilience to global variation analysis and temperature variation analysis. For the Monte Carlo analysis  $6\sigma$  variation around the mean threshold value are taken for performance analysis, whereas for temperature variation

analysis the environment temperature for the simulation is varied from -10 °C to 80 °C. When subjected to global variations, the cell maintains read as well as hold SNM of 75 mV, while the WM is 215 mV. While for temperature variation analysis, the HSNM and RSNM are reduced by 0.1 mV/°C and the WM changes 0.2 mV/°C. This validates the performance of the proposed 7TP3 cell against both global and temperature variation analysis. This helps validate the reliability of the cell.

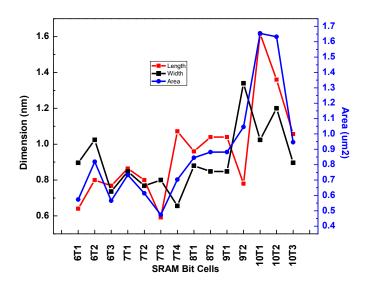

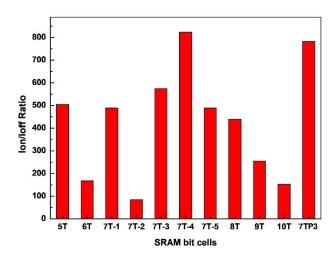

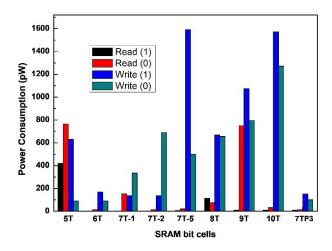

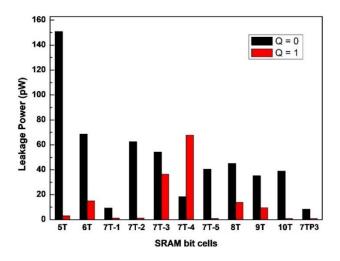

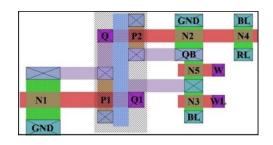

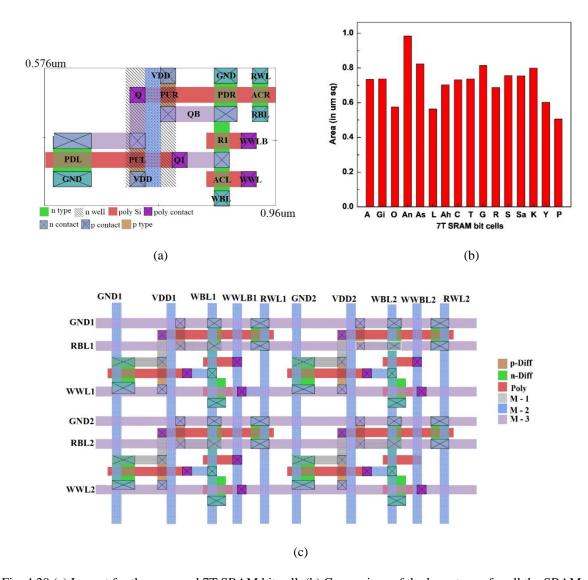

The performance for the 7TP3 cell is compared against other 5T, 6T, 7T, 8T, 9T, 10T cells and is found to be superior. Its leakage current is low, while the ON current is high. Thereby, resulting in high current ratio value of 783 for the cell in comparison to its other pre-existing bit cells in comparison. The power consumption of the proposed bit cell is also found to minimal for all modes of operation. The standby power of the cell is calculated to be 8.4 and 1.05 pW for Q = '0' and '1', respectively. Moreover, the improvement in the performance is obtained for area as low as 0.539  $\mu$ m<sup>2</sup>. The area of 5T, 6T, 7T-1, 7T-2, 7T-4, 7T-5, 8T, 9T and 10T cell is greater than 7TP3 bit cell area by 22.17 %, 51.8 %, 35.8 %, 13.9 %, 30.4 %, 6.78%, 56.6 %, 63.3 % and 75.5 %.

The design for the proposed single ended, single port 7T cells can operate only in this configuration. But, the growing popularity of hyper-personalized devices and round the clock connectivity has generated the need for a bit cell that can switch between low power and high speed operation. Thus, concept for a dual mode operational bit cell is proposed. The concept for the proposed dual mode operation cell describes a bit cell that has the capability to operate in two different design configurations. The selection of mode of configuration for the cell is dependent on the control signals for the cells. The control signals of the cell can steer into from one configuration into the other. To design the dual mode operational bit cell, one mode of operation is the single ended, single port mode of the 7TP3. To determine the second mode of operation for the cell, another 7T cell with single ended, dual port configuration is proposed.

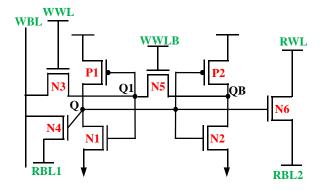

Thus, a single ended, dual port 7T cell is also proposed. The memory core and write port for the proposed dual port cell is similar the memory core and write port for the single ended, single port 7TP3 cell proposed in. The difference between the two topologies lie in their respective read port design. The read port and write port for 7TP3 are connected to a common bitline. Whereas, the read and write port for the dual port 7T cell are isolated and

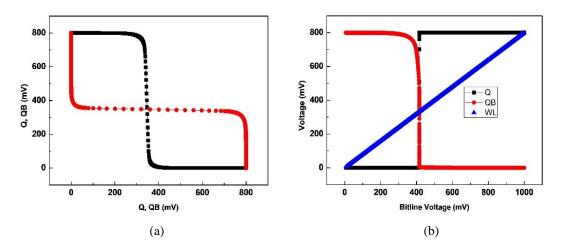

do not share a common bitline for operation. The cell is designed at 32 nm and its performance is compared against other pre-existing 7T bit cells. The cell is simulated for 800 mV as, various pre-existing bit cells performed reliability at this voltage.

The stability analysis for the hold, read, and write operation for the proposed dual port 7T cell yields the noise margin for the three operations as 324, 324, and 488 mV, respectively. For a successful read and write operation pulse-width of 5 ps and 0.14 ns respectively are required. Temperature variation analysis yields 0.15, 0.15, and 0.24 mV/ $^{\circ}$ C variation in hold, read, and write noise margin values, respectively. The leakage power consumption for the cell is 256 pW, while the read, and write power consumption for the cell are 6  $\mu$ W and 1.9  $\mu$ W, respectively. All the aforementioned merits for the proposed dual port 7T cell are achieved with a minimal layout area of 0.553  $\mu$ m $^{2}$ .

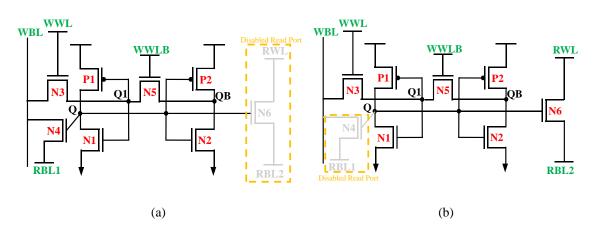

Once the design for the single ended, single port 7T cell and the single ended, dual port 7T cell is finalized, the dual mode operational cell is designed. The dual mode operational cell is a versatile amalgamation of the aforementioned two cells with the capability to function in two different single ended configurations – single port and dual port. The bit cell is composed of eight transistors and is grouped into three sub-parts – single bit memory core, reading port and writing port. The single bit memory core of the reconfigurable memory is the part that stores the desired information. The read and the write port are the access circuitry that enable the device to read and write into the cell, respectively. The single port cell is more suitable for low power applications and the dual port cell is better for high speed operation. Therefore, as per the requirement of the circuit at a given instant, the different configurations for the cell may be used.

All the proposed cells are of single ended nature owing to their better performance at lower supply voltage and high area density. This growing demand for single ended cells has also generated the need for a single ended sense amplifier topology that is compatible with the array of single ended cell. Conventionally, sense amplifiers were designed with differential ended topology. This SA topology is usually voltage based in nature owing to their low area footprint and low operational  $V_{DD}$ . But delay and current for current mode topology are higher. Thus, generating need for a single ended SA that has low power consumption, smaller area footprint, and faster operation. The convenient sensing topology deemed reliable for single ended SRAM is inverter based.

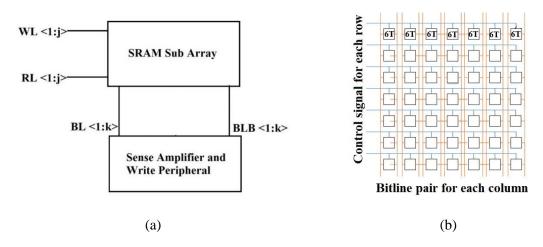

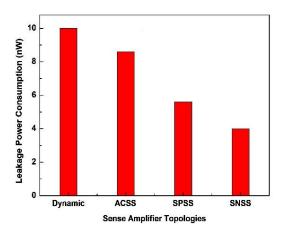

Thus, a single ended switching NMOS based sense amplifier is proposed for 32 nm technology node. It operates in two phases – the pre-charge phase and the evaluation phase. This two-phase functioning for the proposed sense amplifier ensures there is minimal power consumption for the topology when the memory is not executing the read operation. Its pulse-width requirement of 0.32 ns is significantly lower in comparison to its counterparts. While its leakage power is least amongst the different SA topologies at 4 nW. The additional advantage the proposed SA has its lower area footprint of 7.65  $\mu$ m<sup>2</sup>.

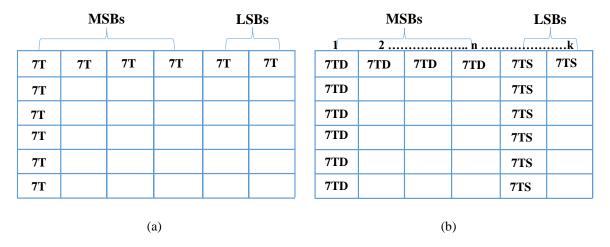

A bit cell is a small peg in a wide m×n matrix that forms the memory core for data storage. Conventionally, a bit cell is replicated to create the entire array. But, in a typical multimedia application the lower order bits may be more vulnerable to noise than higher order bits. Hence, appreciable performance and minimal image quality degradation can be achieved by using two different bit cells for array formation.

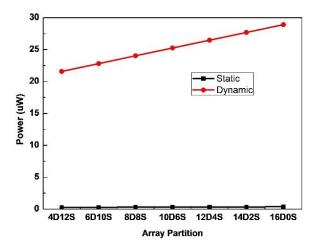

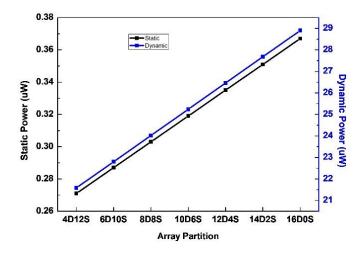

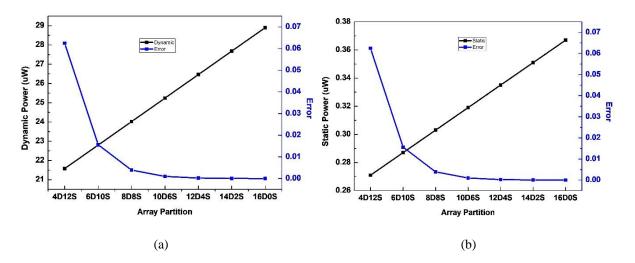

A hybrid array configuration using two different 7T bit cells topologies is proposed. The best results are obtained when six dual port and ten single port cells are used to design the array. The static and dynamic power values obtained for the design are  $0.29\,\mu\text{W}$  and  $23\,\mu\text{W}$ , respectively. These values are 3.5% and 20.7% lower than the static and dynamic power values obtained for memory array designed using only dual port cells. Also, the error tolerance for this partition is approximately 0.015, which is fairly low, making this hybrid array design low power and error resistant.

# **ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude and sincere appreciation to all those who have contributed in the completion of my doctoral thesis. Their guidance, support, and encouragement have been invaluable throughout this journey.

First and foremost, I am immensely grateful to my supervisor, Prof. Poornima Mittal, Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, India. I am greatly thankful for her unwavering commitment, patience, and expertise. Ma'am's guidance and insightful feedback have been instrumental in shaping the direction of my research and enhancing the quality of my work. I am truly fortunate to have had such a dedicated mentor who consistently challenged and inspired me to reach new heights.

I express my gratitude towards the distinguished faculty members who have time and again helped us at different avenues. I extend my sincere regards to HoD sir, for his constant support. I wish to express my gratitude towards the DRC chairperson, the distinguished DRC members. Their expertise, constructive criticism, and valuable suggestions have significantly contributed to the refinement of my thesis. I am deeply grateful for the time and effort they invested in reviewing and evaluating my work.

I am indebted to the esteemed faculty members of Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, who provided me with a rich academic environment and facilitated my intellectual growth. Their lectures, seminars, and discussions have expanded my horizons and shaped my research interests.

I express my deepest regards for Prof. Brijesh Kumar, Department of Information Technology, Indira Gandhi Delhi Technical University, Delhi, India, for investing his valuable time and efforts for providing deep and insightful remarks.

I am also grateful to all my colleagues and seniors of the Electronics and Communication department, especially Mr. Sachin Tyagi, Mr. Mohit Tyagi, Mr. Paritosh Chamola, Mr. Ashish Raturi, Ms. Sugandha, Ms. Yogita Chopra, Mr. Ayush, and Ms. Bharti. I am thankful

to them as they have generously contributed their time and shared their insights, without whom my study would not have been possible. Their willingness to participate and engage in meaningful discussions enriched my research and provided me with valuable data. I also express my thanks all the staff members of the department for their continuous support in

our academic activities.

Lastly, I would like to thank my family for their kindness, support, and patience thought my journey. Their belief in me has kept my spirits and motivation high during this process. Their understanding, love, and encouragement have been a constant source of motivation, and I am truly grateful for their presence in my life.

an truly grateral for their presence in my me.

Finally, I would like to acknowledge the financial support provided by Delhi Technological University, Delhi. Their assistance enabled me to carry out my research effectively and ensured that I had the necessary resources to complete my thesis.

To all those who have directly or indirectly contributed to my doctoral thesis, I extend my deepest gratitude. Your support, whether big or small, has played a significant role in shaping my academic and personal growth. I am profoundly grateful for your presence in my life and for the impact you have had on my journey as a researcher.

**BHAWNA RAWAT**

ix

# **Table of Contents**

|       |           |                                                                         | Page No |

|-------|-----------|-------------------------------------------------------------------------|---------|

| Certi | ficate    |                                                                         | ii      |

| Cand  | idate's D | Declaration                                                             | iii     |

| Abst  | ract      |                                                                         | iv      |

| Ackn  | owledge   | ment                                                                    | viii    |

| List  | of Figure | S                                                                       | xv      |

| List  | of Tables |                                                                         | xxi     |

| List  | of Symbo  | ols, and Abbreviations                                                  | xxiii   |

| СНА   | PTER 1    | : INTRODUCTION                                                          | 1 - 11  |

| 1.1   | INTR      | ODUCTION                                                                | 1       |

| 1.2   | SRAN      | A AND ITS COMPONENTS                                                    | 3       |

|       | 1.2.1     | SRAM Bit Cell                                                           | 4       |

|       | 1.2.2     | Sense Amplifier                                                         | 5       |

|       | 1.2.3     | Array Design                                                            | 6       |

| 1.3   | PROE      | BLEM STATEMENT                                                          | 7       |

| 1.4   | OBJE      | CTIVES                                                                  | 7       |

| 1.5   | OBJE      | CTIVE-WISE METHODOLOGY                                                  | 8       |

| 1.6   | THES      | IS ORGANIZATION                                                         | 10      |

| СНА   | PTER 2    | : LITERATURE REVIEW                                                     | 12 - 57 |

| 2.1   | INTR      | ODUCTION                                                                | 12      |

| 2.2   |           | PARATIVE ANALYSIS OF DIFFERENT SRAM CELLS ED ON TRANSISTOR COUNT        | 13      |

|       | 2.2.1     | Schematic Designs of Different SRAM Bit Cells Based on Transistor Count | 13      |

|       | 2.2.2     | Performance Comparison for SRAM Bit Cells Based on Transistor Count     | 21      |

| 23    | COMI      | DADATIVE ANALVSIS OF DIFFEDENT 7T SDAM CELLS                            | 26      |

|     | 2.3.1       | Differential Ended, Single Port 7T SRAM Bit Cells                       | 27                |

|-----|-------------|-------------------------------------------------------------------------|-------------------|

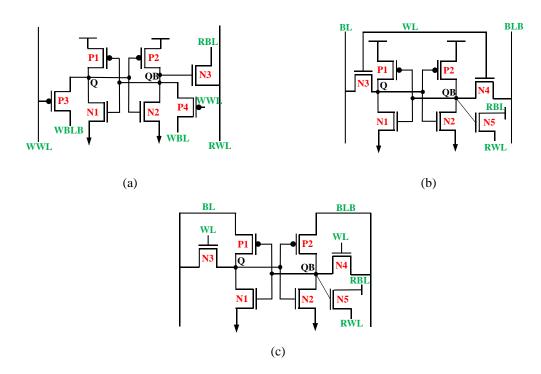

|     | 2.3.2       | Differential Ended with Isolated Read Port 7T SRAM Bit Cells            | 31                |

|     | 2.3.3       | Single Ended, Dual Port 7T SRAM Bit Cells                               | 34                |

|     | 2.3.4       | Single Ended, Single Port 7T SRAM Bit Cells                             | 38                |

| 2.4 |             | PARATIVE ANALYSIS OF DIFFERENT SENSE<br>LIFIER TOPOLOGIES               | 40                |

|     | 2.4.1       | Differential Ended Sense Amplifier Topologies                           | 41                |

|     | 2.4.2       | Single Ended Sense Amplifier Topologies                                 | 48                |

| 2.5 | COM         | PARISON OF DIFFERENT SRAM ARRAY DESIGNS                                 | 53                |

| 2.6 | TECH        | INICAL GAPS                                                             | 56                |

|     |             | : A PROCESS VARIATION RESILIENT SINGLE ENDED,<br>RAM CELL               | SINGLE<br>58 - 85 |

| 3.1 | INTR        | ODUCTION                                                                | 59                |

| 3.2 | PROF        | POSED SINGLE ENDED, SINGLE PORT CELL DESIGNS                            | 60                |

|     | 3.2.1       | Schematic Design for Proposed 7TP1, 7TP2, 7TP3, and 7TP4 SRAM Bit Cells | 60                |

|     | 3.2.2       | Hold, Read, and Write Mechanism for Proposed Bit Cells                  | 62                |

| 3.3 | COM<br>DESI | PARISON OF PERFORMANCE OF ALL PROPOSED CELL<br>GNS                      | 64                |

| 3.4 |             | PARISON OF PERFORMANCE OF 7TP3 WITH PRE-<br>TING CELLS                  | 66                |

|     | 3.4.1       | Static Noise Margin Analysis for 7TP3 Against Pre-existing Bit Cells    | 67                |

|     | 3.4.2       | Tolerance Variation Analysis for 7TP3 Against Pre-existing Bit Cells    | 69                |

|     | 3.4.3       | Failure Probability Analysis for 7TP3 Against Pre-existing Bit Cells    | 78                |

|     | 3.4.4       | Ion/Ioff Analysis for 7TP3 Against Pre-existing Bit Cells               | 79                |

|     | 3.4.5       | Dynamic Write Analysis for 7TP3 Against Pre-existing Bit Cells          | 80                |

|     | 3.4.6       | Power Consumption Analysis for 7TP3 Against Pre-existing Bit Cells      | 81                |

|     | 3.4.7        | Layout and Area Analysis for 7TP3 Against Pre-existing Bit Cells        | 83                |

|-----|--------------|-------------------------------------------------------------------------|-------------------|

| 3.5 | SUMI         | MARY OF IMPORTANT RESULTS                                               | 84                |

|     |              | : DUAL MODE OPERATIONAL SRAM CELL FOR LOW<br>SPEED OPERATION            | POWER<br>86 - 125 |

| 4.1 | INTR         | ODUCTION                                                                | 87                |

| 4.2 | CONC         | CEPT FOR DUAL MODE OPERATIONAL SRAM CELL                                | 88                |

| 4.3 | PROP         | POSED SINGLE ENDED, DUAL PORT SRAM BIT CELL                             | 89                |

|     | 4.3.1        | Hold Mechanism for Proposed 7T Cell                                     | 91                |

|     | 4.3.2        | Read Mechanism for Proposed 7T Cell                                     | 91                |

|     | 4.3.3        | Write Mechanism for Proposed 7T Cell                                    | 91                |

| 4.4 | PERF<br>CELL | ORMANCE ANALYSIS FOR PROPOSED DUAL PORT 7T                              | 92                |

|     | 4.4.1        | Voltage Scaling for Optimal Supply Voltage Determination                | 92                |

|     | 4.4.2        | Stability Analysis for Proposed Dual Port 7T Cell                       | 94                |

|     | 4.4.3        | Read and Write Timing Analysis for Proposed Dual Port 7T<br>Cell        | 97                |

|     | 4.4.4        | Current Ratio Analysis for Proposed Dual Port 7T Cell                   | 98                |

|     | 4.4.5        | Voltage Variation Analysis for Proposed Dual Port 7T Cell               | 99                |

|     | 4.4.6        | Temperature Variation Analysis for Proposed Dual Port 7T<br>Cell        | 100               |

|     | 4.4.7        | Global Variation Analysis for Proposed Dual Port 7T Cell                | 103               |

|     | 4.4.8        | Local Variation Analysis for Proposed Dual Port 7T Cell                 | 106               |

|     | 4.4.9        | Half Select and Soft Error Resilience for Proposed Dual Port<br>7T Cell | 108               |

|     | 4.4.10       | Power Consumption Analysis for Proposed Dual Port 7T Cell               | 112               |

|     | 4.4.11       | Layout and Area Analysis for Proposed Dual Port 7T Cell                 | 113               |

| 4.5 | PROP         | POSED DUAL MODE OPERATIONAL BIT CELL                                    | 115               |

|     | 4.5.1        | Single Port Configuration                                               | 116               |

|     | 4.5.2        | Dual Port Configuration                                                 | 117               |

| 4.6 | PERF<br>CELL | ORMANCE ANALYSIS OF DUAL MODE OPERATIONAL                               | 117               |

|              | 4.6.1 | Static Noise Margin Analysis for Dual Mode Operational Cell            | 117                 |

|--------------|-------|------------------------------------------------------------------------|---------------------|

|              | 4.6.2 | Local Variation Analysis for Dual Mode Operational Cell                | 118                 |

|              | 4.6.3 | Global Variation Analysis for Dual Mode Operational Cell               | 119                 |

|              | 4.6.4 | Temperature Variation Analysis for Dual Mode Operational Cell          | 120                 |

|              | 4.6.5 | Voltage Variation Analysis for Dual Mode Operational Cell              | 121                 |

|              | 4.6.6 | Write and Read Timing Analysis for Dual Mode Operational Cell          | 122                 |

| 4.7          | SUM   | MARY OF IMPORTANT RESULTS                                              | 124                 |

| CHAP<br>PERF |       | 5: SINGLE ENDED, SENSE AMPLIFIER DESIGNACE ENHANCEMENT                 | GN FOR<br>126 - 141 |

| 5.1          | INTR  | ODUCTION                                                               | 127                 |

| 5.2          | PROF  | POSED SENSE AMPLIFIER                                                  | 128                 |

|              | 5.2.1 | Structure and Functioning of Proposed SA                               | 128                 |

|              | 5.2.2 | Delay Analysis for Proposed SA                                         | 131                 |

|              | 5.2.3 | Process, Voltage, and Temperature Tolerance Analysis of Proposed SA    | 132                 |

| 5.3          |       | FORMANCE COMPARISON FOR PROPOSED SA WITH EXISTING SA TOPOLOGIES        | 134                 |

|              | 5.3.1 | Sensing Delay Analysis for Proposed and Pre-existing SA Topologies     | 134                 |

|              | 5.3.2 | Power Consumption Analysis for Proposed and Pre-existing SA Topologies | 137                 |

|              | 5.3.3 | Area Analysis for Proposed and Pre-existing SA Topologies              | 139                 |

| 5.4          | SUM   | MARY OF IMPORTANT RESULTS                                              | 140                 |

| СНАР         | TER 6 | 6: HYBRID ARRAY DESIGN FOR LOW BIT ERROR                               | 142 - 158           |

| 6.1          | INTR  | ODUCTION                                                               | 143                 |

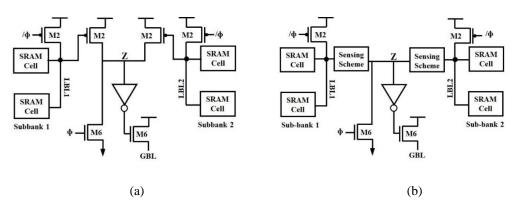

| 6.2          | CON   | VENTIONAL ARRAY CONFIGURATION                                          | 144                 |

| 6.3          | PROF  | POSED HYBRID ARRAY CONFIGURATION                                       | 146                 |

| 6.4          |       | RAM BIT CELLS USED IN PROPOSED HYBRID ARRAY FIGURATION                 | 147                 |

|        | 6.4.1 Evaluation of Static Performance of 7TS and 7TD SRAM Bit Cells  | 148       |

|--------|-----------------------------------------------------------------------|-----------|

|        | 6.4.2 Robustness of 7TS and 7TD Cells Against Half Select Disturbance | 150       |

| 6.5    | BIT ERROR ANALYSIS OF PROPOSED ARRAY CONFIGURATION                    | 151       |

| 6.6    | POWER MODEL FOR PROPOSED HYBRID ARRAY CONFIGURATION                   | 152       |

| 6.7    | POWER PERFORMANCE ANALYSIS OF PROPOSED ARRAY CONFIGURATION            | 155       |

| 6.8    | SUMMARY OF IMPORTANT RESULTS                                          | 157       |

| СНАР   | PTER 7: CONCLUSIONS AND FUTURE SCOPE                                  | 159 - 163 |

| 7.1    | CONCLUSIONS                                                           | 159       |

| 7.2    | FUTURE SCOPE                                                          | 162       |

| REFE   | RENCES                                                                | 164       |

| LIST ( | OF PUBLICATIONS                                                       | 183       |

# **List of Figures**

| S. No.    | Figure Caption                                                                                                                                                                                   | Page No |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Fig. 1.1  | Block diagram for SRAM based memory                                                                                                                                                              | 3       |

| Fig. 2.1  | Schematic design for (a) 6T1, (b) 6T2, and (c) 6T3 bit cell.                                                                                                                                     | 14      |

| Fig. 2.2  | Schematic design for (a) 7T1, (b) 7T2, (c) 7T3, and (d) 7T4 SRAM bit cell.                                                                                                                       | 15      |

| Fig. 2.3  | Schematic design for (a) 8T1, and (b) 8T2 SRAM bit cell.                                                                                                                                         | 16      |

| Fig. 2.4  | Schematic design for (a) 9T1, and 9T2 SRAM bit cell.                                                                                                                                             | 16      |

| Fig. 2.5  | Schematic design for (a) 10T1, (b) 10T2, and (c) 10T3 SRAM bit cell.                                                                                                                             | 17      |

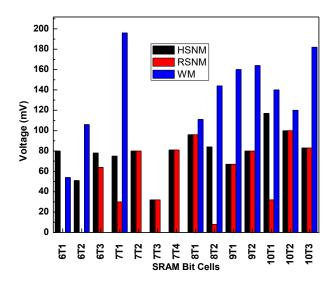

| Fig. 2.6  | Graphical comparison for HSNM, RSNM, and WM values obtained for the different SRAM bit cells.                                                                                                    | 22      |

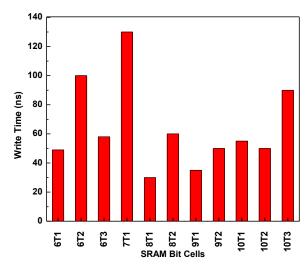

| Fig. 2.7  | Graphical comparison of dynamic write time required for the different SRAM bit cells.                                                                                                            | 23      |

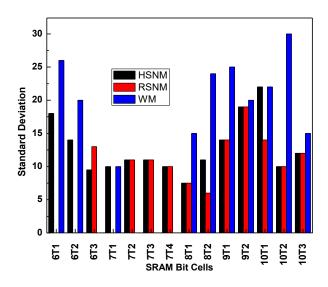

| Fig. 2.8  | Graphical comparison of standard deviation in SNM values of each cell due to process variations.                                                                                                 | 24      |

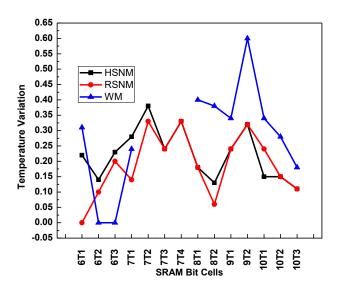

| Fig. 2.9  | Graphical comparison of variation in SNM values for all the pre-<br>existing cells.                                                                                                              | 25      |

| Fig. 2.10 | Graphical comparison for the length, width, and area for the pre-<br>existing cells.                                                                                                             | 26      |

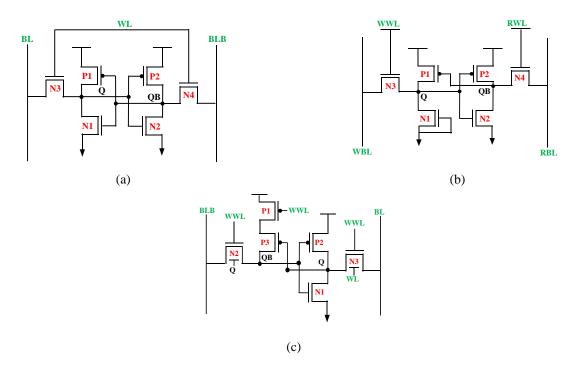

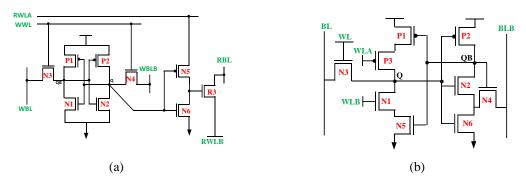

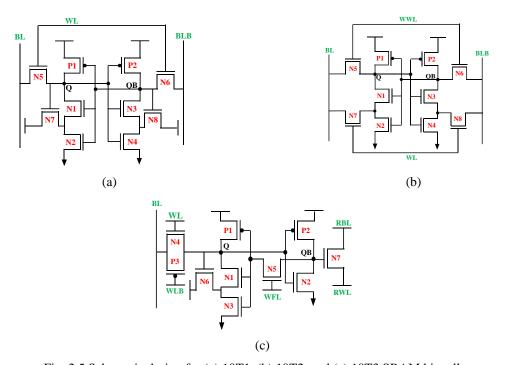

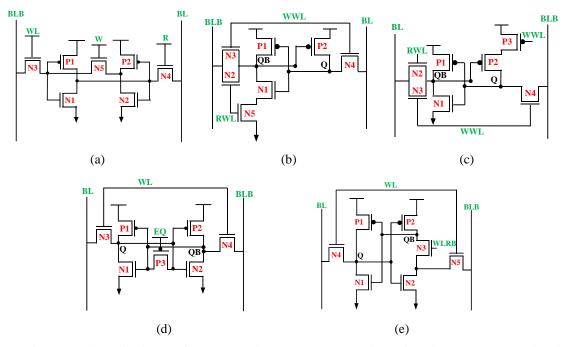

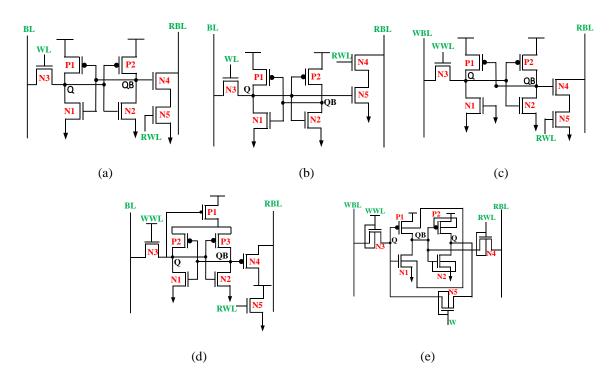

| Fig. 2.11 | Schematic diagram for (a) 7TA, (b) 7TAn, (c) 7TAs, (d) 7TGi, and (e) 7TO, SRAM bit cell topologies.                                                                                              | 28      |

| Fig. 2.12 | Schematic diagram for (a) 7TC, (b) 7TL, and (c) 7TAh SRAM bit cell topologies.                                                                                                                   | 32      |

| Fig. 2.13 | Schematic diagram for (a) 7TT, (b) 7TS, (c) 7TG, (d) 7TR, and (e) 7TSa, SRAM bit cell topologies                                                                                                 | 35      |

| Fig. 2.14 | Schematic diagram for (a) 7TK, and (b) 7TY, SRAM bit cell topologies                                                                                                                             | 38      |

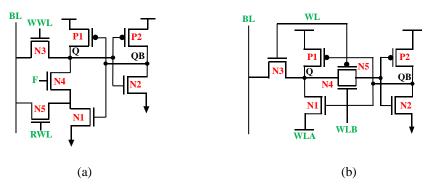

| Fig. 2.15 | Schematic diagram for (a) SA-1, (b) SA-2, (c) SA-3, (d) SA-4, (e) SA-5, and (f) SA-6.                                                                                                            | 42      |

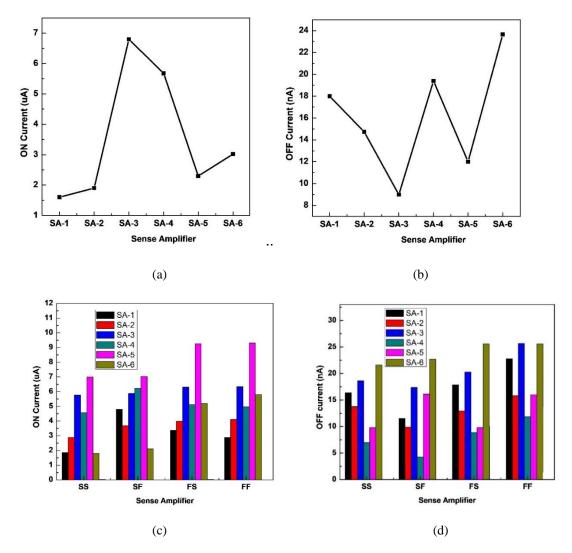

| Fig. 2.16 | Graphical comparison for (a) ON current, (b) OFF current, (c) ON current at different process corners and (d) OFF current at different process corners for all SAs at different process corners. | 45      |

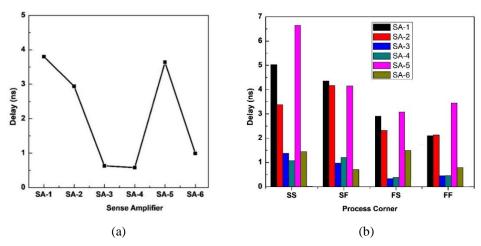

| Fig. 2.17 | Graphical comparison for sensing delay (a) at TT corner, and (b) all process corners for the different SA topologies                                                                             | 46      |

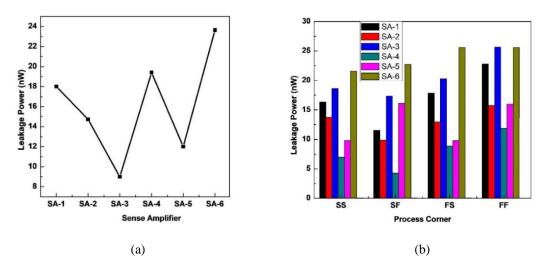

| Fig. 2.18 | Graphical comparison for leakage power at (a) TT corner and (b) all process corners for the different sense amplifier topologies.                                                                                                       | 47 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.19 | Block diagram representation for (a) domino logic based sensing, and (b) modified sensing scheme.                                                                                                                                       | 48 |

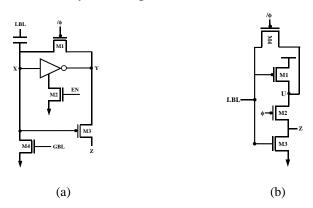

| Fig. 2.20 | Schematic diagram for (a) ACSS, and (b) SPSS topologies.                                                                                                                                                                                | 49 |

| Fig. 2.21 | Output waveform corresponding to (a) ACSS and (b) SPSS topologies [119].                                                                                                                                                                | 50 |

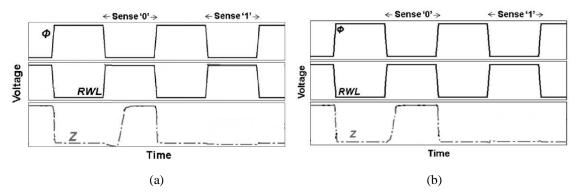

| Fig. 2.22 | Comparison of (a) delay timings at different process corners, (b) average power consumption, and (c) leakage power consumption for all the SA topologies.                                                                               | 52 |

| Fig. 2.23 | Block diagram representation of (a) array for an SRAM memory, and (b) arrangement of cell in an array.                                                                                                                                  | 54 |

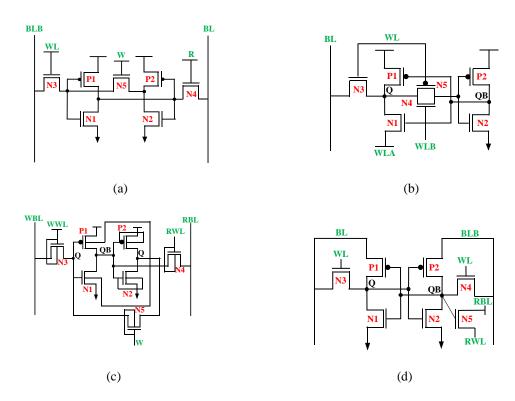

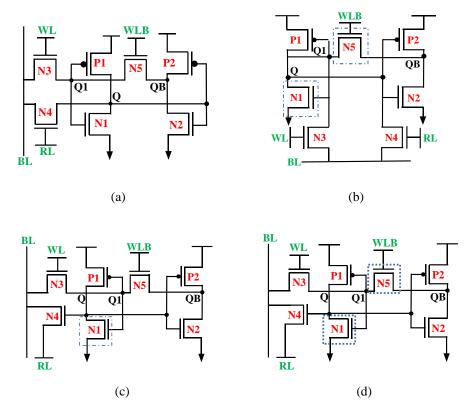

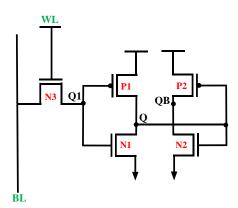

| Fig. 3.1  | The schematic design for (a) 7TP1, (b) 7TP2, (c) 7TP3, and (d) 7TP4 SRAM bit cells.                                                                                                                                                     | 61 |

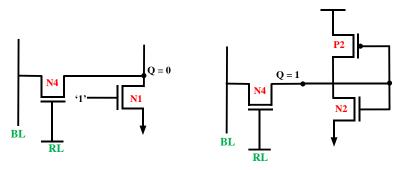

| Fig. 3.2  | Read path for 7TP1 and 7TP2 bit cell for (a) $Q = '0'$ and (b) $Q = '1'$ .                                                                                                                                                              | 62 |

| Fig. 3.3  | Effective circuit during write operation for the proposed SRAM bit cells.                                                                                                                                                               | 63 |

| Fig. 3.4  | Graphical comparison for SNM values obtained for the proposed 7T SRAM bit cells for hold, read, and write operation.                                                                                                                    | 65 |

| Fig. 3.5  | Graphical comparison for the write time values for the different 7T proposed bit cells.                                                                                                                                                 | 65 |

| Fig. 3.6  | Comparison of dimensions and area footprint for the four proposed 7T SRAM bit cells.                                                                                                                                                    | 66 |

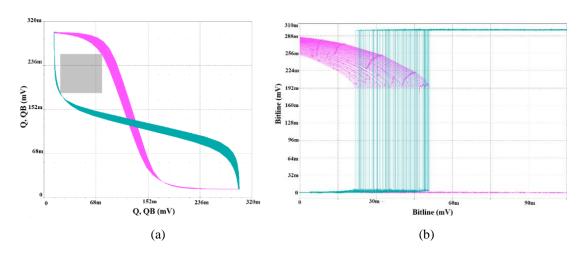

| Fig. 3.7  | The butterfly curve for (a) HSNM and RSNM, (b) WM for 7TP3 SRAM bit cell.                                                                                                                                                               | 67 |

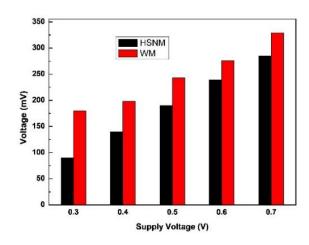

| Fig. 3.8  | Graphical representation for HSNM and RSNM for all SRAM bit cells.                                                                                                                                                                      | 69 |

| Fig. 3.9  | Monte Carlo Simulations for (a) HSNM and RSNM, (b) WM for the proposed 7TP3 SRAM bit cell.                                                                                                                                              | 70 |

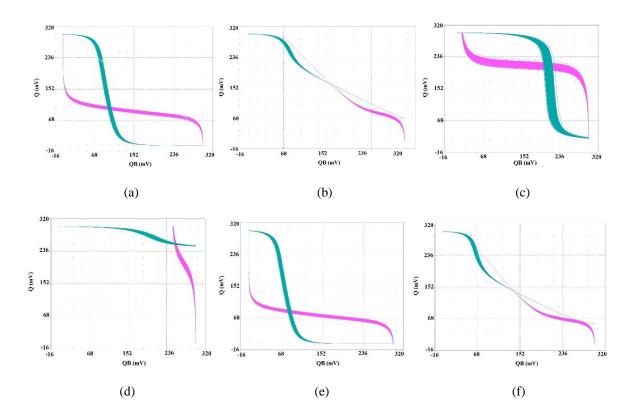

| Fig. 3.10 | Monte Carlo Simulations for (a) 5T HSNM (b) 5T RSNM, (c) 6T HSNM, (d) 6T RSNM, (e) 7T-1 HSNM, (f) 7T-1 RSNM, (g) 7T-2 SNM, (h) 7T-3 SNM, (i) 7T-4 SNM, (j) 7T-5 HSNM, (k) 7T-5 RSNM, (l) 8T SNM, (m) 9T SNM and (n) 10T SRAM bit cells. | 72 |

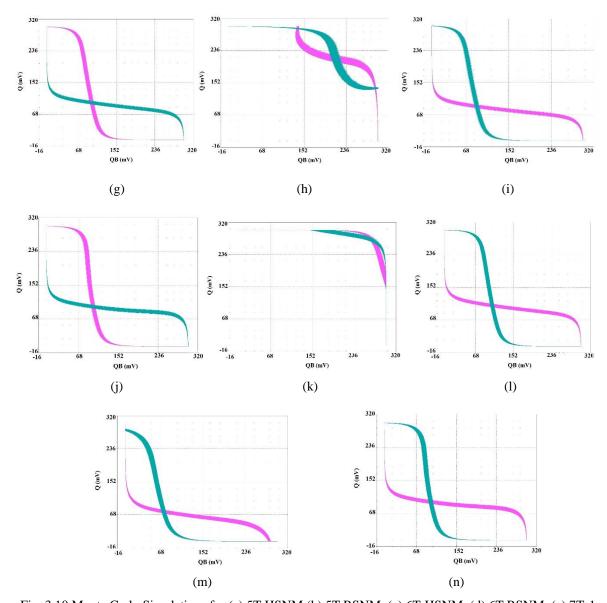

| Fig. 3.11 | Monte Carlo Simulations for WM for (a) 5T, (b) 6T, (c) 7T-1, (d) 7T-5, (e) 8T SNM, (f) 9T SNM and (g) 10T SRAM bit cells.                                                                                                               | 73 |

| Fig. 3.12 | Graphical comparison for the static margins obtained for all the SRAM bit cells under process variation analysis.                                                                                                                       | 75 |

| Fig. 3.13        | Performance of the proposed 7TP3 SRAM bit cell for temperature range from -10 °C to 80 °C (a) HSNM and RSNM and (b) WM.                                                                                                        | 76  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 3.14        | Performance of the proposed 7TP3 SRAM bit cell with varying voltage.                                                                                                                                                           | 77  |

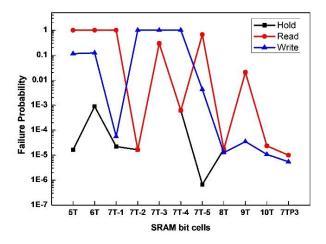

| Fig. 3.15        | Failure Probability Comparison for all SRAM bit cells for read, hold, and write operation.                                                                                                                                     | 79  |

| Fig. 3.16        | Comparison of the $I_{ON}/I_{OFF}$ ratio for all the SRAM bit cells.                                                                                                                                                           | 80  |

| Fig. 3.17        | (a) Dynamic write operation for finite pulse width of 10 ns for the proposed 7TP3 SRAM bit cell and (b) Graphical comparison for the T <sub>crit</sub> needed for successful write operation for the different SRAM bit cells. | 81  |

| Fig. 3.18        | Comparison of read and write power consumption for the proposed 7TP3 SRAM bit cells with pre-existing cells.                                                                                                                   | 82  |

| Fig. 3.19        | Comparison of leakage power consumption for the proposed 7TP3 SRAM bit cells with pre-existing cells.                                                                                                                          | 83  |

| <b>Fig. 3.20</b> | Layout design for the proposed 7TP3 cell.                                                                                                                                                                                      | 84  |

| Fig. 4.1         | Flow diagram representation of the proposed concept for a dual mode operational SRAM cell.                                                                                                                                     | 88  |

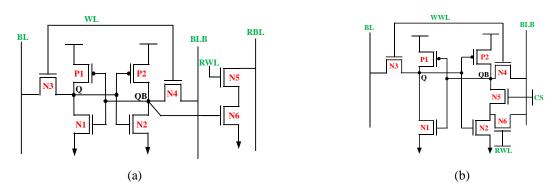

| Fig. 4.2         | (a) Schematic and (b) control signal for 7TP SRAM bit cell.                                                                                                                                                                    | 90  |

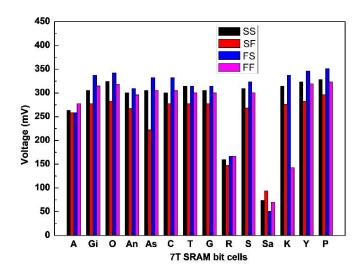

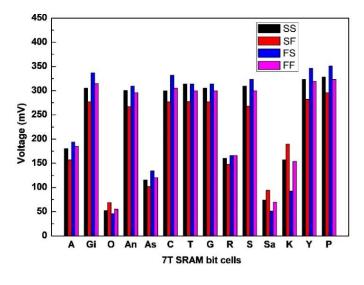

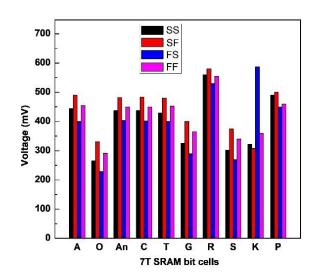

| Fig. 4.3         | Graphical comparison for (a) HSNM, (b) RSNM, and (c) WM for all different 7T SRAM bit cells for supply voltage varying from 0.2 V to 1 V.                                                                                      | 93  |

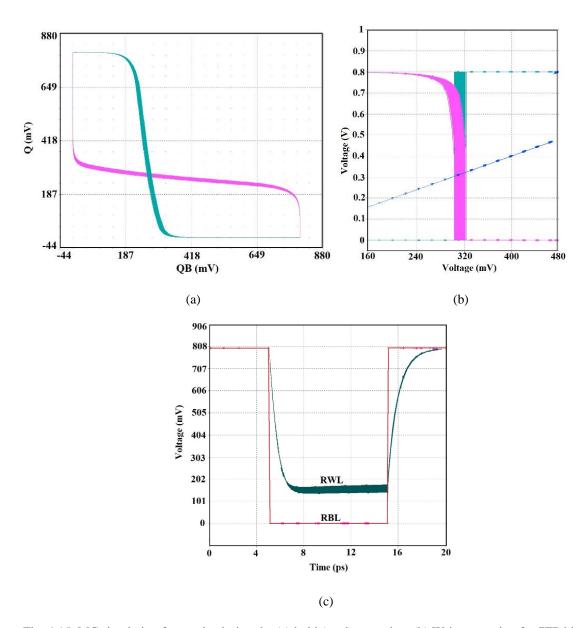

| Fig. 4.4         | (a) Butterfly curve for HSNM (RSNM) for 7TP cell, and (b) Graphical comparison between the HSNM/RSNM values for all 7T SRAM bit cells.                                                                                         | 95  |

| Fig. 4.5         | (a) WM curve for 7TP, and (b) Graphical comparison of WM for the bit cells.                                                                                                                                                    | 96  |

| Fig. 4.6         | Graphical comparison of write and read delay for the 7TP SRAM bit cell.                                                                                                                                                        | 97  |

| Fig. 4.7         | Graphical comparison of current ratio for the different 7T SRAM bit cells.                                                                                                                                                     | 98  |

| Fig. 4.8         | Variation in the static margin for the 7TP SRAM bit cell with variation in supply voltage, (b) HSNM (RSNM) butterfly curve, and (c) WM measurement for $V_{DD}$ variation of 0.04 mV for the proposed 7TP SRAM bit cell.       | 100 |

| Fig. 4.9         | The temperature analysis for HSNM/RSNM for the proposed 7T SRAM cell                                                                                                                                                           | 101 |

| Fig. 4.10        | The temperature analysis for WM of proposed 7T SRAM bit cell.                                                                                                                                                                  | 102 |

| Fig. 4.11 | Comparison of variation in static performance with temperature for all the SRAM bit cells.                                                                                                                                    | 103 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 4.12 | Comparison for HSNM at SS, SF, FS, and FF corner for all 7T SRAM bit cells.                                                                                                                                                   | 104 |

| Fig. 4.13 | Comparison for RSNM at SS, SF, FS, and FF process corner for the 7T SRAM bit cells.                                                                                                                                           | 104 |

| Fig. 4.14 | Comparison for WM at SS, SF, FS, and FF process corner for all the 7T SRAM bit cells                                                                                                                                          | 106 |

| Fig. 4.15 | MC simulation for results during the (a) hold (read) operation, (b) Write operation for 7TP bit cell, and (c) Read discharge current for $Q = '1'$ at the worst corner using 10,000 MC simulations.                           | 107 |

| Fig. 4.16 | A 2×2 array for the proposed 7TSE SRAM bit cell to depict the half-selected cells in an array when an SRAM bit cell is selected.                                                                                              | 109 |

| Fig. 4.17 | (a) Butterfly curve for 7TP <sub>2</sub> half selected cell, (b) butterfly curve for 7TP <sub>3</sub> selected cell, and (c) 10,000 Monte Carlo simulation for butterfly curve for 7TP <sub>2</sub> cell at the worst corner. | 110 |

| Fig. 4.18 | Graphical comparison for static power consumption for the different 7T SRAM bit cell topologies.                                                                                                                              | 112 |

| Fig. 4.19 | Graphical comparison for dynamic power consumption for the different 7T SRAM bit cell topologies.                                                                                                                             | 113 |

| Fig. 4.20 | (a) Layout for the proposed 7T SRAM bit cell, (b) Comparison of the layout area for all the SRAM bit cells, and (c) layout for 2×2 array for the 7TP SRAM bit cell.                                                           | 114 |

| Fig. 4.21 | Schematic design for the proposed reconfigurable SRAM cell.                                                                                                                                                                   | 115 |

| Fig. 4.22 | The effective circuit for the proposed cell when the circuit is operational in (a) single port, and (b) dual port configuration.                                                                                              | 116 |

| Fig. 4.23 | (a) Butterfly curve for hold (read) operation, and (b) Write margin curve for the proposed reconfigurable cell.                                                                                                               | 118 |

| Fig. 4.24 | Results of local variation for (a) HSNM (RSNM), and (b) WSNM values for the proposed reconfigurable cell.                                                                                                                     | 119 |

| Fig. 4.25 | Graphical comparison of the SNM values obtained at the different process corner for the proposed reconfigurable cell.                                                                                                         | 120 |

| Fig. 4.26 | Variation in SNM for (a) hold (read), and (b) write operation for<br>the proposed cell due temperature variation.                                                                                                             | 121 |

| Fig. 4.27 | Variation in SNM values for (a) hold (read) and (b) write operation for the proposed cell due to variation in voltage from 0.75 V to 0.85 V.                                                                                  | 122 |

| Fig. 4.28 | Read current through the different read ports for the dual mode operational SRAM cell.                                                             | 123 |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 5.1  | Schematic diagram for (a) proposed sense amplifier design, equivalent-circuit configuration during (b) pre-charge phase, and (c) evaluation phase. | 128 |

| Fig. 5.2  | Output waveform corresponding to the proposed SNSS topology.                                                                                       | 130 |

| Fig. 5.3  | Delay timing for the proposed sense amplifier topology at different process corner for $V_{DD} = 1 \text{ V}$                                      | 131 |

| Fig. 5.4  | Variation in the output waveform for the proposed SA for sensing 0 for process variation                                                           | 132 |

| Fig. 5.5  | Variation in the output waveform for the proposed SA for sensing 0 for voltage variation between 0.9 to 1.1 V                                      | 132 |

| Fig. 5.6  | Variation in the output waveform for the proposed SA for sensing 0 for temperature variation from -10°C to 110 °C                                  | 133 |

| Fig. 5.7  | Variation in the output waveform for the proposed SA for sensing 0 for temperature variation from 0°C to 70 °C                                     | 134 |

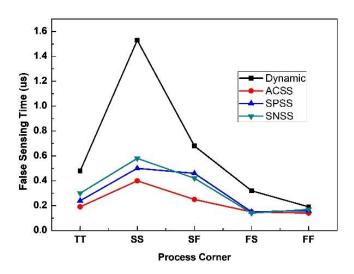

| Fig. 5.8  | Comparison of delay timings at different process corners for all the SA topologies                                                                 | 135 |

| Fig. 5.9  | Comparison of false read time at all process corners for all the SA topologies.                                                                    | 135 |

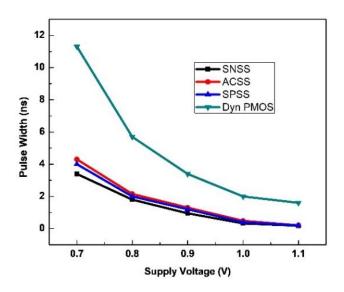

| Fig. 5.10 | Comparison of delay for varying $V_{DD}$ for all the SA topologies.                                                                                | 136 |

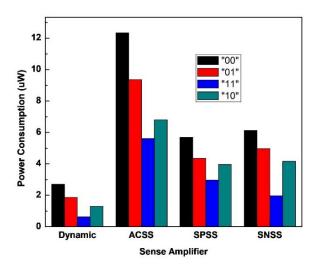

| Fig. 5.11 | Comparison of power consumption corresponding to four data cases – 00, 01, 10, and 11 for all the SA topologies.                                   | 138 |

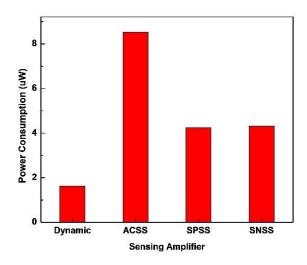

| Fig. 5.12 | Comparison of average power consumption for all the SA topologies.                                                                                 | 138 |

| Fig. 5.13 | Comparison of leakage power consumption for all the SA topologies.                                                                                 | 139 |

| Fig. 6.1  | A block diagram representation for an SRAM memory.                                                                                                 | 144 |

| Fig. 6.2  | Block level representation for cell arrangement in (a) conventional array design, and (b) in proposed hybrid array design.                         | 145 |

| Fig. 6.3  | A 4×4 array representation of SRAM memory based on single port 7T SRAM bit cell.                                                                   | 145 |

| Fig. 6.4  | A 4×4 array representation of SRAM memory based on dual port 7T SRAM bit cell.                                                                     | 146 |

| Fig. 6.5  | A 4×4 array representation of proposed hybrid array configuration designed using single port and dual port 7T cells                                | 147 |

| Fig. 6.6  | Schematic diagram of pre-existing (a) dual and (b) single port 7T SRAM cell.                                                                              | 148 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 6.7  | (a) Hold (read) operation butterfly curve, and (b) write margin curve for the 7T SRAM bit cells.                                                          | 149 |

| Fig. 6.8  | Impact of process variation on (a) hold (read) operation butterfly curve, and (b) write margin curve for the single port and dual port 7T SRAM bit cells. | 149 |

| Fig. 6.9  | A 2×2 array representation or the (a) 7TD and (b) 7TS cell.                                                                                               | 150 |

| Fig. 6.10 | Butterfly curve for (a) 7TD cell and (b) 7TS cells during the half-select condition.                                                                      | 151 |

| Fig. 6.11 | Maximum bit error corresponding information stored in the LSB bits.                                                                                       | 152 |

| Fig. 6.12 | Power consumption curve for the proposed hybrid array configuration for different array partition in absolute terms.                                      | 155 |

| Fig. 6.13 | Power consumption curve for the proposed hybrid array configuration for different array partition in relative double y curve.                             | 156 |

| Fig. 6.14 | Overlap curve for maximum error in keeping with array partition and (a) dynamic power consumption and (b) static power consumption.                       | 157 |

# **List of Tables**

| S. No.            | Table Caption                                                                                                                                                                   | Page No. |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

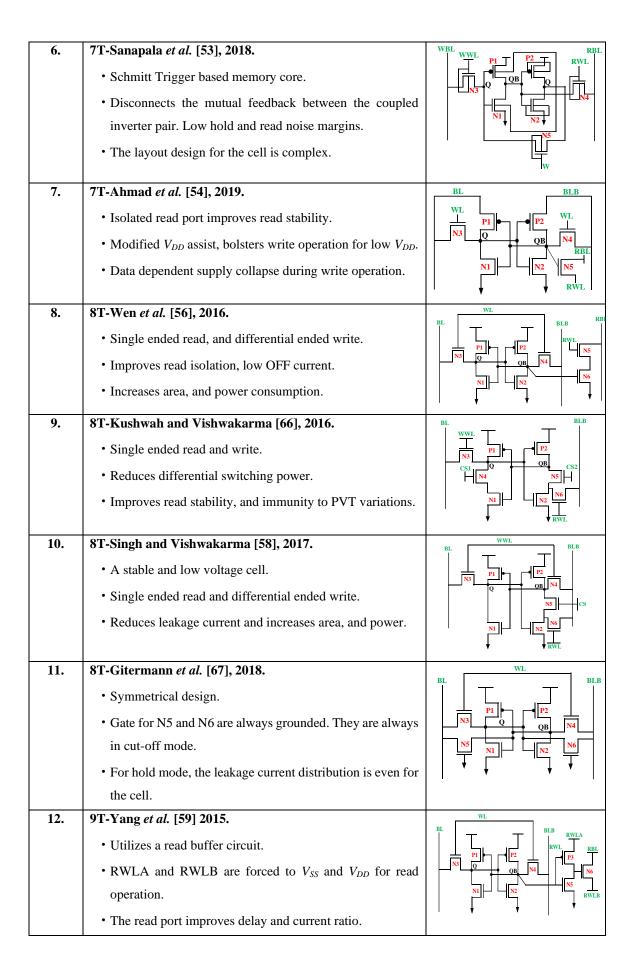

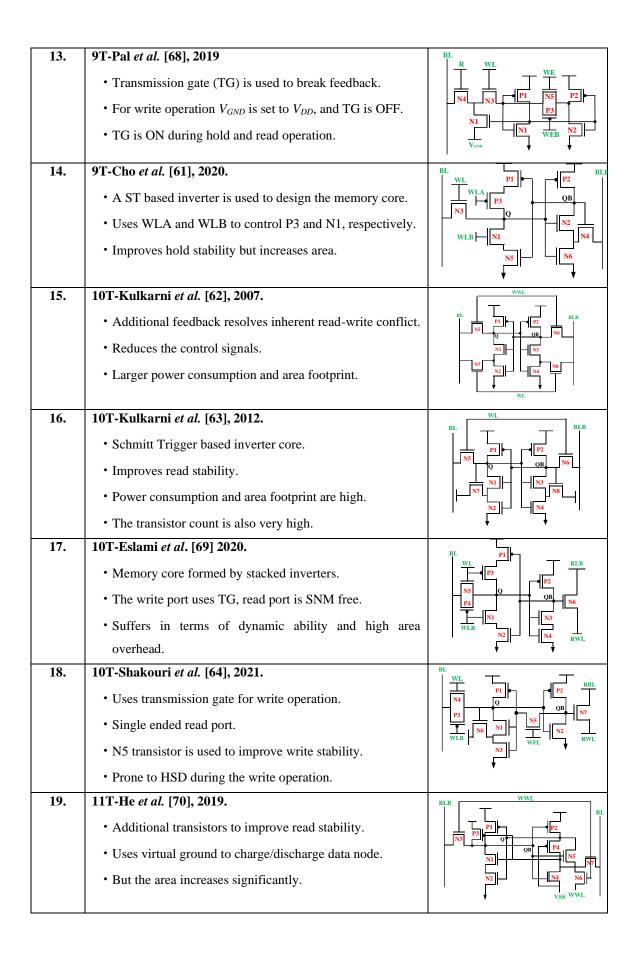

| Table 2.1         | Summarized key features of different pre-existing SRAM bit cells based on transistor count                                                                                      | 18       |

| Table 2.2         | MOS characteristic for SRAM cells given in Fig. 2.11 (b), (c) and 2.13 (a).                                                                                                     | 28       |

| Table 2.3         | Summarized key features of 7T SRAM bit cells with differential ended, single port configuration.                                                                                | 29       |

| Table 2.4         | Results obtained for SNM, temperature variation analysis, global variation analysis and power consumption for the differential ended, single port 7T SRAM bit cells.            | 30       |

| Table 2.5         | Results obtained for timing, current ratio, and area footprint for the differential ended, single port 7T SRAM bit cells.                                                       | 30       |

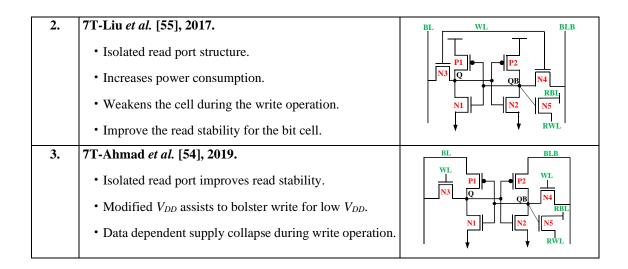

| Table 2.6         | Summarized key features of 7T SRAM bit cells with differential ended with isolated read port configuration.                                                                     | 32       |

| Table 2.7         | Results obtained for SNM, temperature variation analysis, global variation analysis and power consumption for the differential ended with isolated read port 7T SRAM bit cells. | 33       |

| Table 2.8         | Results obtained for timing, current ratio, and area footprint for the differential ended with isolated read port 7T SRAM bit cells.                                            | 34       |

| Table 2.9         | Summarized key features of 7T SRAM bit cells with single ended, dual port configuration.                                                                                        | 36       |

| <b>Table 2.10</b> | Results obtained for SNM, temperature variation analysis, global variation analysis and power consumption for the differential ended, isolated read port 7T SRAM bit cells.     | 37       |

| <b>Table 2.11</b> | Results obtained for timing, current ratio, and area footprint for the single ended, dual port 7T SRAM bit cells.                                                               | 37       |

| <b>Table 2.12</b> | Summarized key features of 7T SRAM bit cells with single ended, single port configuration.                                                                                      | 39       |

| <b>Table 2.13</b> | Results obtained for SNM, temperature variation analysis, global variation analysis and power consumption for the single ended, single port 7T SRAM bit cells.                  | 40       |

| <b>Table 2.14</b> | Results obtained for timing, current ratio, and area footprint for the single ended, single port 7T SRAM bit cells.                                                             | 40       |

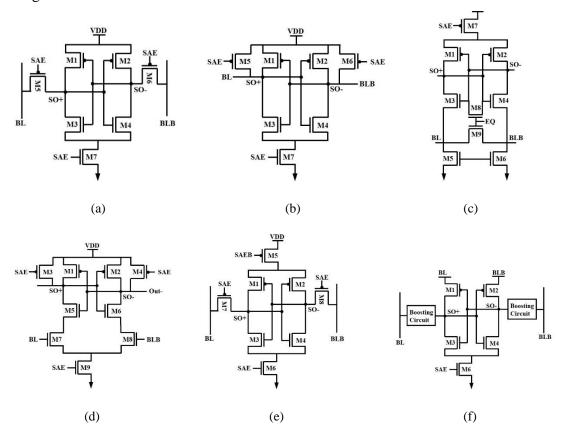

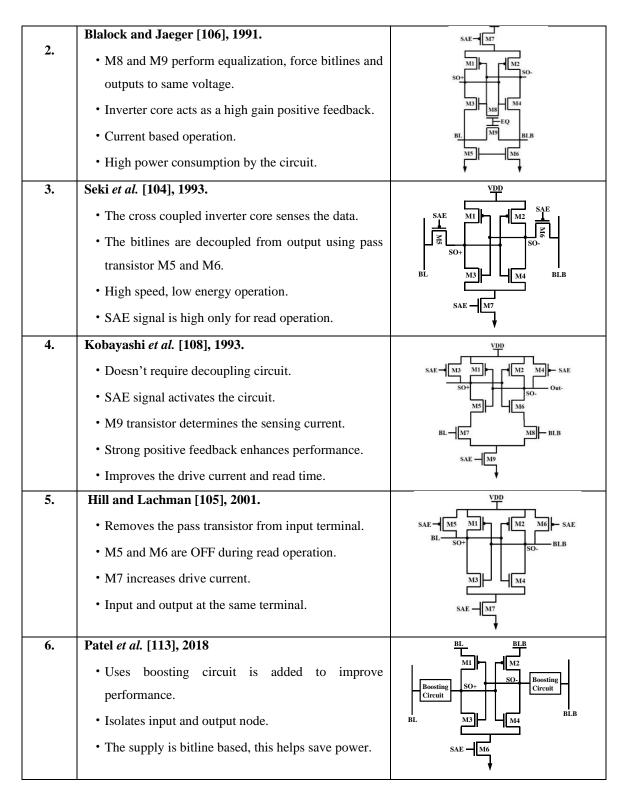

| <b>Table 2.15</b> | Summarized key features of differential ended sense amplifier topologies.                                                                        | 43  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Table 2.16</b> | Summarized key features of single ended sense amplifier topologies.                                                                              | 51  |

| <b>Table 2.17</b> | Summarized key point based on array analysis.                                                                                                    | 55  |

| Table 3.1         | Comparison of noise margin values for different bit cells based on transistor count.                                                             | 68  |

| Table 3.2         | The values obtained for minimum, maximum, mean, and standard deviation for all the bit cell at 32 nm technology node using Monte Carlo Analysis. | 74  |

| Table 3.3         | Layout dimensions for the 7TP3 and other pre-existing SRAM bit cells                                                                             | 84  |

| Table 4.1         | Signal Status during hold, read, and write operation for the proposed 7T SRAM bit cell.                                                          | 90  |

| Table 4.2         | Comparison of results for all the 7T SRAM bit cells for various evaluation parameters.                                                           | 105 |

| Table 4.3         | The control signal conditions during the different operation of the proposed cell.                                                               | 116 |

| Table 4.4         | SNM values for the proposed reconfigurable cell at all process corners.                                                                          | 120 |

# **List of Symbols and Abbreviations**

| Symbol/Abbreviation | Full Form                               |

|---------------------|-----------------------------------------|

| ACSS                | AC Coupled Sensing Scheme               |

| BCC                 | Butterfly Curve Collapse                |

| BER                 | Bit Error Rate                          |

| BI                  | Bit Interleaving                        |

| BL                  | Bitline                                 |

| BLB                 | Bitline Bar                             |

| BTI                 | Bias Temperature Instability            |

| $C_{BL}$            | Bitline Capacitance                     |

| $C_L$               | Load Capacitance                        |

| $C_{OX}$            | Oxide Capacitance                       |

| $C_{RBL}$           | Read Bitline Capacitance                |

| $C_{RL}$            | Readline Capacitance                    |

| $C_{WBL}$           | Write Bitline Capacitance               |

| $C_{WL}$            | Wordline Capacitance                    |

| $C_{WLB}$           | Wordline Bar Capacitance                |

| DP                  | Dual Pulse                              |

| $f_{clk}$           | Clock Frequency                         |

| FF                  | Fast, Fast                              |

| FS                  | Fast, Slow                              |

| GBL                 | Global Bitline                          |

| HS                  | Half Select                             |

| HSD                 | Half Select Disturbance                 |

| HSNM                | Hold Static Noise Margin                |

| $HV_{TH}$           | High Threshold Voltage                  |

| $I_{D\_l}$          | Leakage Current for Dual Port 7T Cell   |

| IoT                 | Internet of Things                      |

| $I_{S\_l}$          | Leakage Current for Single Port 7T Cell |

| j                   | Number of Rows                          |

| k                   | Number of Columns                       |

kT Thermal Noise = 26 mV

L Length

LBL Local Bitline

LSB Least Significant Bit

LV<sub>TH</sub> Low Threshold Voltage

MC Monte Carlo

MSB Most Significant Bit

n Partition for the Array

NBTI Negative Bias Temperature Instability

PBTI Positive Bias Temperature Instability

$P_{D\_Hold}$  Hold Power for Proposed Dual Port 7T Cell  $P_{D\_Read}$  Read Power for Proposed Dual Port 7T Cell  $P_{D\_Write}$  Write Power for Proposed Dual Port 7T Cell

*P*<sub>Read</sub> Read Probability

$P_{S\_Hold}$ Hold Power for Proposed Single Port 7T Cell $P_{S\_Read}$ Read Power for Proposed Single Port 7T Cell $P_{S\_Write}$ Write Power for Proposed Single Port 7T Cell

$P_{TD}$  Total Power for Array formed by Dual Port Cells  $P_{Ts}$  Total Power for Array formed by Single Port Cells

Total Power Consumption for Hybrid Array

$P_{Write}$  Write Probability

PVT Process, Voltage, and Temperature

Q Data Node

$P_T$

QB Data Node Bar

RBL Read Bitline

RBL1 Read Bitline 1

RBL2 Read Bitline 2

RL Readline

RP1 Read Port 1

RP2 Read Port 2

RSNM Read Static Noise Margin

SA Sense Amplifier

SD Standard Deviation

SNM Static Noise Margin

SNSS Switching NMOS Sensing Scheme

SoC System on Chip

SPSS Switching PMOS Sensing Scheme

SRAM Static Random Access Memory

SF Slow, Fast Slow, Slow

ST Schmitt Trigger

T Clock Pulsewidth

T<sub>crit</sub> Write Pulse Width

TG Transmission Gate

T<sub>S</sub> Read Time

V<sub>DD</sub> Supply Voltage

$V_{OH}$  High Level of Output Voltage  $V_{OL}$  Low Level of Output Voltage

V<sub>TH</sub> Threshold Voltage

W Width

WBL Write Bitline

WL Wordline

WLB Wordline Bar

WM Write Margin

WWL Write Wordline

WWLB Write Wordline Bar

$\alpha$  Activity Factor  $\phi$  Enable signal

$\mu_m$  Mean

μ<sub>n</sub> Mobility of Electrons

6σ Six Sigma Standard Deviation

# CHAPTER – 1

# INTRODUCTION

The growing depends of the civilization on digital devices has opened up a new world of processing and data. This plethora of data and its processing is dependent on various types of powerful digital devices. These devices comprise of a microprocessor or a group of microprocessors. An essential component of these microprocessors is the cache memory circuit that enables its fast operation. In this chapter, a detailed introduction to the cache memory and its building blocks are presented. It is essential to understand the different components of cache so as identify the different aspects that can be worked upon to improve its performance.

This chapter is divided into six different sections, including introduction, section 1.1. It is followed by section 1.2, which is dedicated to the essential components that together comprise the SRAM. Based on the brief introduction of the different components of SRAM, the identified problem statement is described in section 1.3. Thereafter in section 1.4, objectives are formulated to rectify the identified problems. The methodology used to achieve each desired objective is explained in section 1.5. Finally in section 1.6, the thesis organization is summarized.

#### 1.1 INTRODUCTION

The electronics industry is progressing towards artificial intelligence and internet of things due to the increased popularity of hyper-personalized system on chip (SoC) devices. Also, the increase in demand for round the clock digital connectivity, and the explosion of everyday personal data has increased the processing demand for embedded systems. A mandatory element for most SoC devices is an on-die embedded cache memory, also referred to as the static random access memory (SRAM). These memories occupy more than 90% of the die surface [1] and thereby dominate power consumption and area footprint of SoC [2]. With the increasing demand for light weight portable devices with longer battery life it has become essential to identify techniques that will help in improving performance for the SoC. As highlighted previously, that area, and power consumption for SRAM makes

up for most of the total proportion. It is mandatory to uplift the performance of the memory while simultaneously lowering its area footprint.

Conventionally the data core for SRAM is formed by bit cells organized in an array. These bit cells store data in forms of single bit value, whereas the task of reading and writing into the cell is facilitated by peripheral circuitry formed by row-column decoders, bit-lines, precharge circuitry and sense amplifier (SA). In its most crude form, memory core along with the peripheral circuit consumes about 30% of the total power for the system and 50% chip area [3-4]. The total power consumption for an SRAM circuit can be divided into two distinct components – static power consumption and dynamic power consumption. Static power has a linear dependence on supply voltage ( $V_{DD}$ ), whereas the latter has a quadratic dependence on  $V_{DD}$  [5].

The most trivial method for lower power consumption is to lower its operational  $V_{DD}$  [6]. But this is limited by process, voltage, and temperature (PVT) variations in the nanometer vicinity [7]. In keeping with the Moore's Law, the technology node for circuit design has scaled drastically. This when coupled with  $V_{DD}$  lowering for power consumption reduction makes the circuit highly susceptible to variations, errors, and other vulnerabilities. Another pitfall of the declining trends for  $V_{DD}$  is that, the static power for the circuit starts dominating the dynamic power component [8]. This is further augment by increased leakage current values for lower technology node that further adds to the static power consumption factor.

Another major limitation that restricts reduction of  $V_{DD}$  for a digital circuit is that it also limits its operational speed [9]. Thereby diminishing the operational frequency for memory [10]. Thus, if the operational frequency for the circuit is lowered, its clock pulse width is widened. This increase in operational time for the circuit increases the power consumption for each operation, even though the total power consumed by the cell decreases [11]. Consequently, resulting in high power consumption for the SRAM, which in turn lowers the battery life for the portable SoC. Thus, it may be inferred that designing a bit cell operational at low levels of  $V_{DD}$  is a mammoth task for designers [12].

Another aspect that limits the performance of SRAM is the slow-fast corner. In general, if NMOS and PMOS transistor are equally sized, the performance for the CMOS circuit is skewed. This is caused by the vast gap between the mobility of charge carries for the NMOS and PMOS transistors. This gap between the charge carriers mobility gets extenuated

because of the skewed corner. At this corner, even if the  $V_{DD}$  for the circuit is maintained in the super-threshold region the performance of the circuit suffers drastically. Then, for low levels of  $V_{DD}$  the impact on cell performance at the skewed corner are highly unreliable.

Besides, apart from  $V_{DD}$ , another factor that highly influence error propensity of SRAM is its total area footprint. Memories with larger area footprint are more prone to reliability issues and failure events [13]. The collective influence of these aforementioned factors increases vulnerability [14] of memory towards read, write, and access time failures. Thus, if the performance of the memory is to be improved, it is essential to modify cell design, along with SA and their array configuration. In keeping with the same, cell and its peripheral circuit are the main focus of this thesis. In this chapter, the SRAM design and its essential circuit components are briefly introduced to highlight the key theme pursued in this thesis.

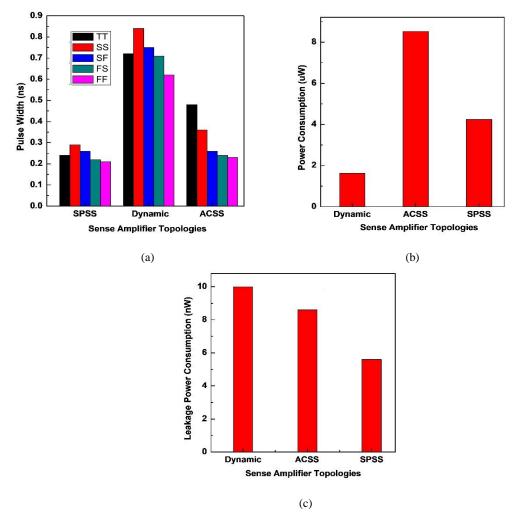

## 1.2 SRAM AND ITS COMPONENTS

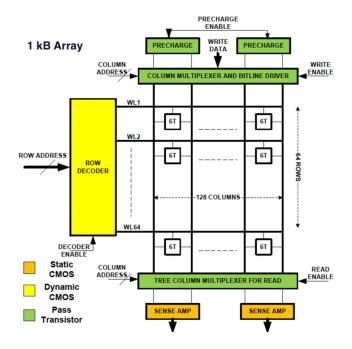

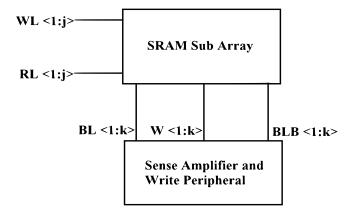

The increase in demand for round the clock digital connectivity, and the explosion of personal data has increased the processing loas for embedded systems. A major component of efficient embedded system is SRAM; formed by bit cells organized in an array and its peripheral circuitry. Bit cell stores data, whereas read and write operation for the cell are facilitated by its peripheral circuitry; composed of decoders, bitlines, pre-charge circuit, and SAs [15]. A block diagram to represent the SRAM memory is depicted in Fig. 1.1.

Fig. 1.1 Block diagram for SRAM based memory

The pre-charge circuit charges the bitlines to high or low potential as per the need of the cell, during the read and hold operation. The read operation in general requires both the bitline to have the same potential. Whereas the write operation deems it necessary to have alternating data on the bitlines. Therefore, during the write operation the bitlines are controlled by the write driver circuit and not the pre-charge circuit.

The row and column based decoders are utilized to identify the exact cell in which read or write operation is to be performed. They are highly useful circuits when creating large memories. Another peripheral circuit that is highly important is the SA. This circuit enables a fast read operation for the memory. The SA is a circuit that senses a small differential voltage that develops on the bitlines to amplify it, to yield correct output for the read operation. It also helps reduce the read access time for the memory.

#### 1.2.1 SRAM Bit Cell

The bit cell is the heart for SRAM circuit. It is the singular unit in which information is stored in the form of a bit. A bit cell can store a single bit of data, and the same bit cell is replicated to create the array for the SRAM. Conventionally, the bit cell design comprised of six transistors (6T), with two complementary bitlines that were common for the read as well as the write operation. But, the performance for bit cell has suffered drastically due to technology node scaling and  $V_{DD}$  reduction. The 6T cell is unable to perform for lower technology node due to the inherent read-write conflict. Other 6T cells designed to eliminate the inherent read-write conflict resulted in high power requirement, thereby making it unfit for low power application. The most trivial method to eliminate the inherent read-write conflict for a cell is to isolate its read and write port. Thus, based on the port configuration a bit cell can be categorized as single port or dual port cell.

## A. Single Port Cells

A bit cell relies on either a pair of bitlines or a single bitline for its operation. If the cell utilizes the same bitline pair or bitline for both read as well as the write operation, the cell is referred to as a single port cell. Conventionally cells are single port in nature, but this results in the inherent read-write conflict. This results in a trade-off between the read and write performance for the bit cell. The improvement in one come at the cost of the other. A major advantage for having a single port cell is that it reduces the power consumption, and

capacitance for the cell, as common signals are used for controlling the different operations.

At higher technology node, the vulnerabilities due to the read-write conflict were not that significant and did not possess any threat to the circuit. But with the decrease in technology node, lowering of  $V_{DD}$  and minimal sizing of transistor for high area density, the impact of this conflict is becoming apparent. It limits the designing of the bit cell and also dramatically impacts the performance of the bit cell. Thus, isolating the read and write port is the only alternative at the disposal of memory designers.

#### **B.** Dual Port Cells

When a bit cell is designed to have separate ports for read and write operation it is referred to as a dual port cell. The scaling technology node and lowering trends of  $V_{DD}$  have resulted in this being a preferred configuration for a bit cell. This configuration is very efficient in eliminating the contradictory sizing requirements for the read and write operation. It makes the cell more stable, increases the speed of operation, and lately is a preferred choice for cell designing for low transistor count cells.

But, the isolation of ports for the cell mandates the use of different control signals to steer the cell into different operations (hold, read and write). Increase in signals implies increase in capacitance for the cell. This also mandates designing additional circuitry to control these signals. Thereby poorly impacting the power consumption and area footprint for the cell.

#### 1.2.2 Sense Amplifier

Additional to the bit cell, a cache memory also comprises of peripheral circuitry. Amongst the different peripheral units, the SA is the most crucial component as the read operation for the cache depends on it. In the array arrangement of the cache, each column culminates in an SA (as illustrated in Fig. 1.1). Conventionally, SA detects a small differential voltage on the bitline, to produce a full swing data output [16-17]. Therefore, it is highly critical for performance of cache memory. It helps in determining the operational frequency, power consumption, and minimum operating point, for cache memory [18-19].

Various SA designs have been reported in literature by researchers. These different SA topologies reported in literature can be categorized into either voltage mode or current mode. The latter is quickly able to amplify a small differential signal at the bitlines to a full swing

voltage output [20-21]. But its higher transistor count and larger area occupancy makes it economically unfeasible. An area efficient SA topology is the latch based voltage mode SA. They are also popular owing to their high speed sensing mechanism and low power consumption [22-23]. Conventionally, both the topologies were differential in nature, but presently single ended bit cells are gaining popularity, therefore single ended SA designs are also in demand.

The efficiency of the SA determines the read operation efficiency for the memory. The operation for the SA is to detect a small differential potential difference that develops on the bitline to sense the data present in the bit cell. The less time it takes, the faster the read operation for the memory. But the decreasing technology node has taken its toll on the performance of SA, making them vulnerable to variability and for credible function occupying high area footprint. Therefore, designing an SA at scaled technology with area efficiency and reduced  $V_{DD}$  is turning out to be a real bottleneck for memory designers.

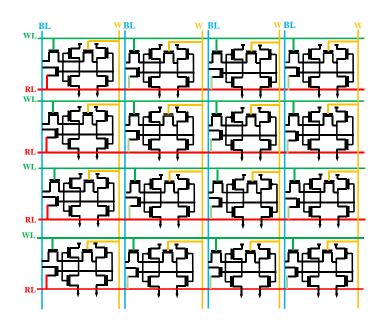

### 1.2.3 Array Design

Different bit cells and their implementation techniques have been described in literature to improve their performance and achieve various design objectives [24-29]. But, in an attempt to improve and optimize cache memory performance, most designers usually restrict themselves to bit cell design. All the different bit cells described in literature improve performance in terms of one parameter or the other. But a bit cell is only a foundational stone in the design of SRAM. It is a small peg that gets replicated multiple times to form the array that actually acts as the memory core. Thus, designing and optimizing the array configuration for memory is equally essential. Improving the performance for the memory implies collectively improving the performance of the cell when it is placed in an array. In an array arrangement, the cells in the same row and column share control signals. Therefore, performance of the cell gets impacted by its neighboring cell. Thus, deeming it necessary to analyze the performance of a cell in array. Also, for lowering power consumption for memory most researchers focus on lowering the operational  $V_{DD}$  for a cell. But SA in general is a circuit that is not operationally at  $V_{DD}$  as low as the cell. Thus, an alternative for power saving for memory may be optimizing the array power consumption, but very few research works have explored this arena.

#### 1.3 PROBLEM STATEMENT

Cache memory is an integral part for most microprocessors and SoC circuits. Additionally, with the increasing dependence of hyper-personalized portable devices, and internet of things, the demand for low power, high density, and faster memories is increasing. A method to increase density of cells per unit area is lowering the technology node, while for power reduction the orthodox method is to reduce the  $V_{DD}$ . But, with the decreasing technology node, the performance of the conventional bit cells is deteriorating. This is further augmented by lowering the  $V_{DD}$ . Therefore, there is need to design a cell that is operational for low voltage and is designed with low transistor count to keep its area under check.

The conventional mechanism to design a cell is to identify the specifications that it has to cater to, and then design its topology. But, in doing so designers have accepted certain trade-offs. But with the growing technological needs, new mechanisms need to be designed to tackling these trade-offs. One such accepted notion is that a cell can operate in a single mode configuration only. But most dynamic devices that are round the clock connected require cells that can cater to low power as well as high speed operations. Thus, generating need for a cell that can operate in low power mode, and when needed switch to high speed mode.

Another circuit essential for proper functioning of a cache memory is the SA. As the bit cells for the memory are being redesigned, there is a need for a SA that is compatible with these modified cell topologies. Thus, once the bit cell topology is finalized, it is essential to design an SA compatible with its design. Also, the shift of cell design from differential ended to single ended configurations, has generated the need for a single ended SA as well.

Also, a bit cell is a small peg in a large array used to form the cache memory. Therefore, it is essential to analyze performance of a cell in array configuration to check the influence of bit cells on each other. When cells are replicated multiple times to form an array configuration, the half select disturbance (HSD) starts hampering cell performance. Also, it is essential to check for impact of bit error on the overall performance of the array.

#### 1.4 OBJECTIVES

The growing demand for faster memory with higher integration density has generated the need for re-designing memory and its peripheral components for performance enhancement.

Also, the cumulative aftermath of reduction in technology node, scaling  $V_{DD}$ , and increased process variation may result in augmented memory failure. Thus, the following four objectives were formulated to improve the performance for SRAM.

#### **Objective 1:**

Design and analysis of an area efficient, low power 7T SRAM bit cell at 32 nm technology node, resilient to process variation.

# **Objective 2:**

Design a dual mode operational SRAM bit cell with the capability to switch between different configurations.

#### **Objective 3:**

Design and performance analysis of a sense amplifier to club the merits of voltage based and current based topologies for performance enhancement.

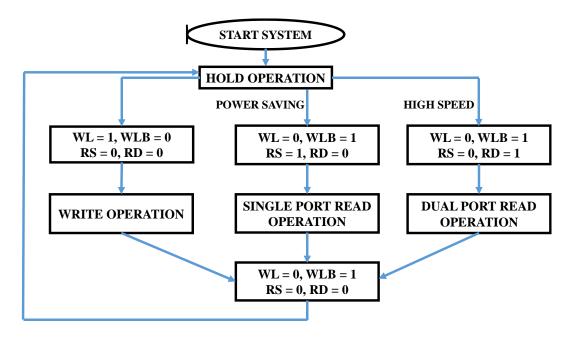

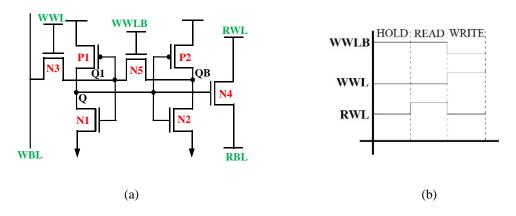

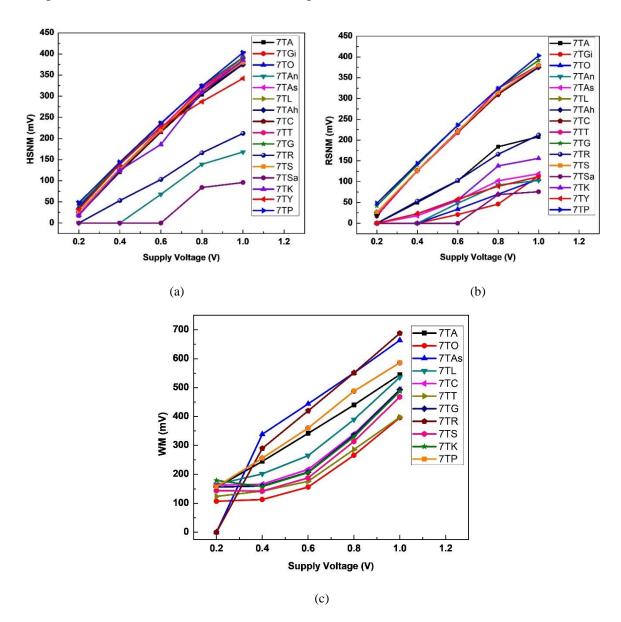

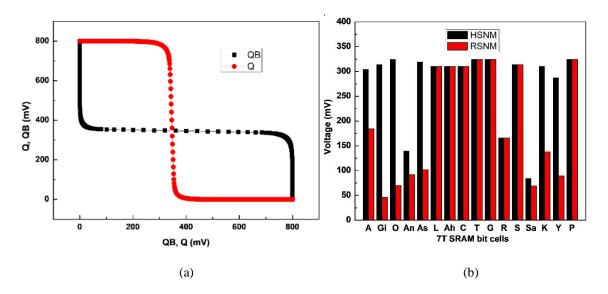

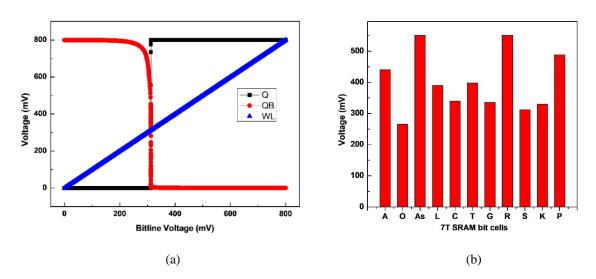

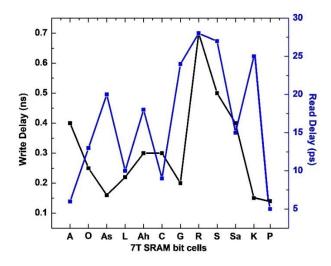

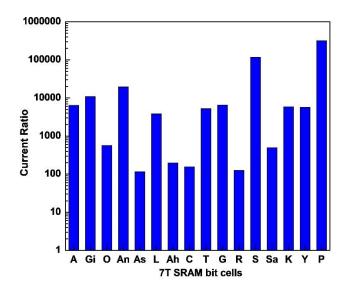

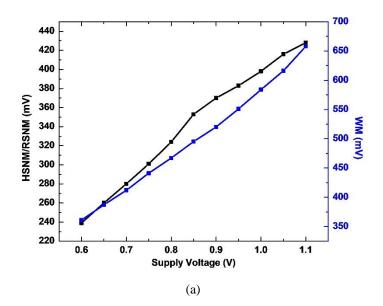

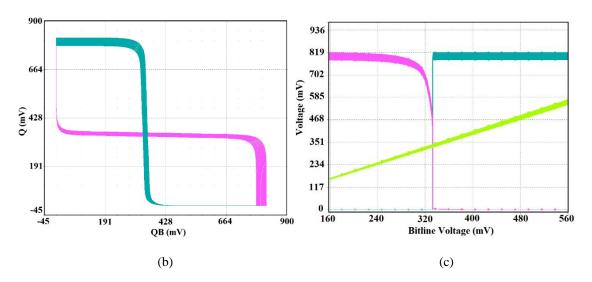

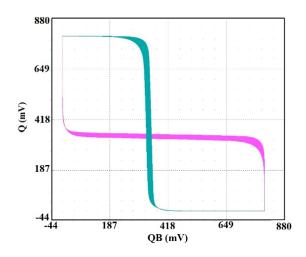

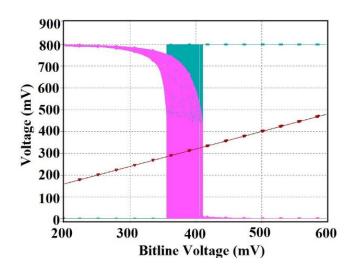

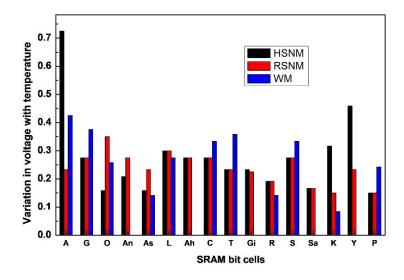

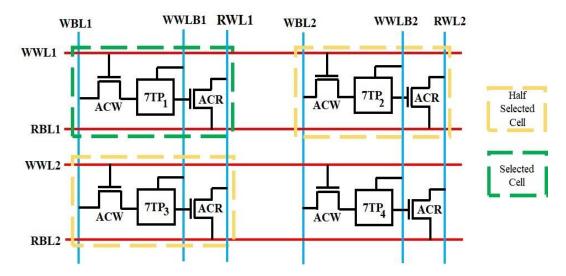

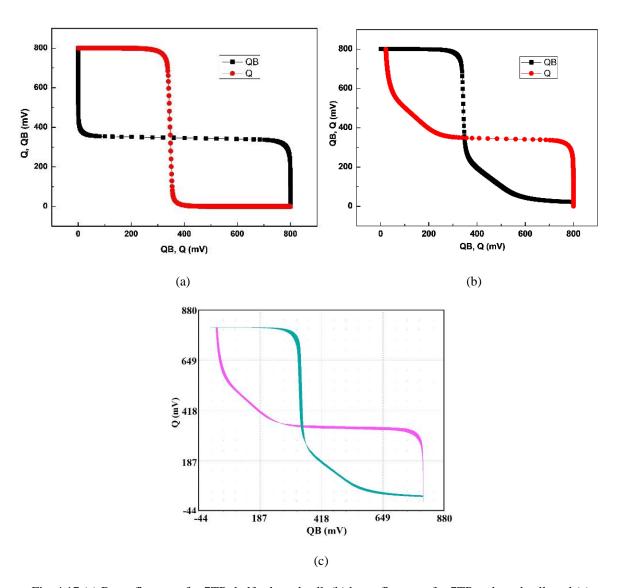

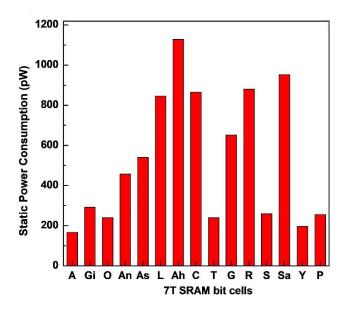

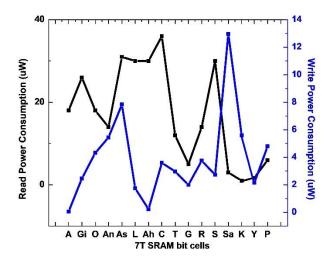

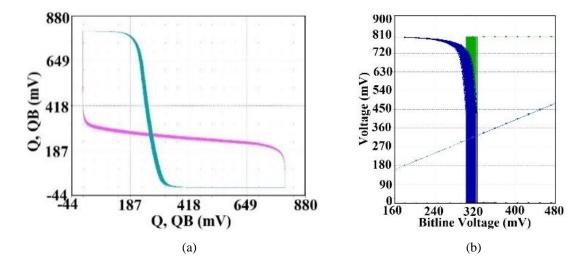

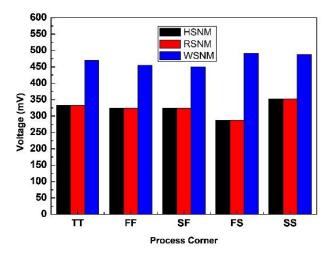

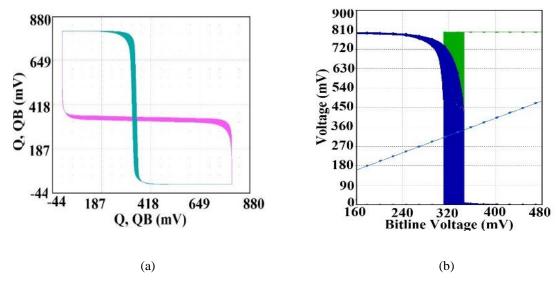

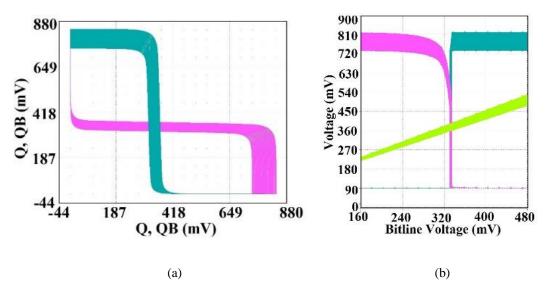

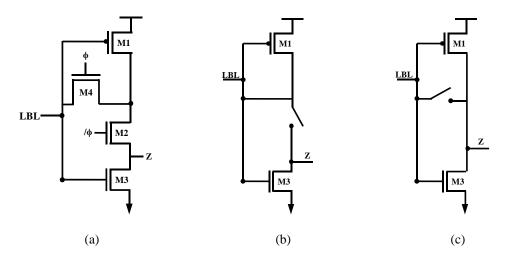

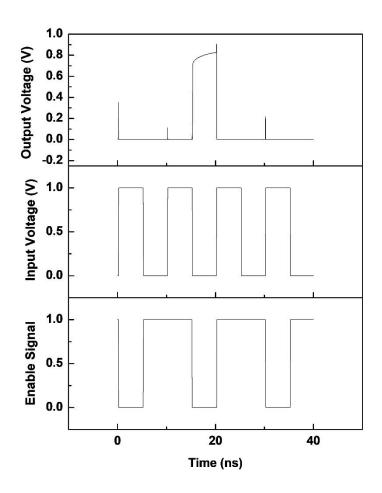

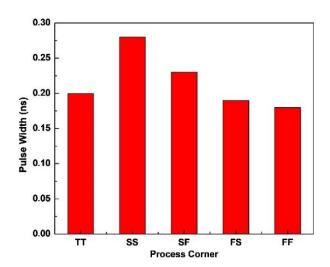

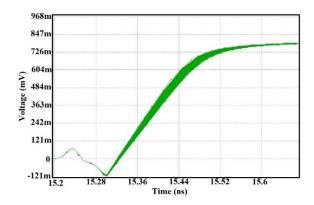

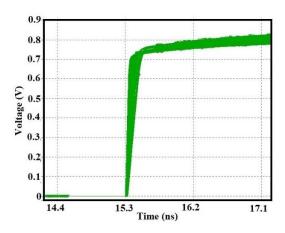

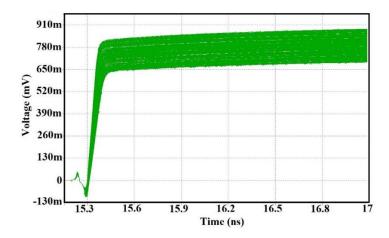

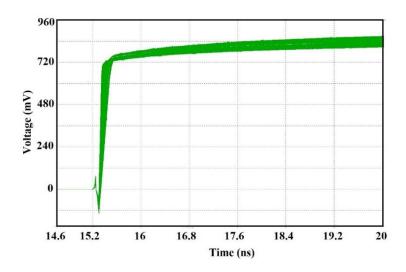

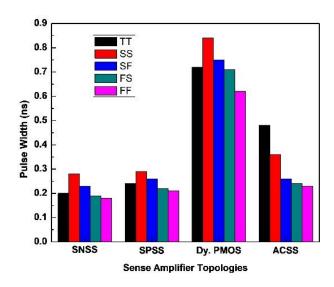

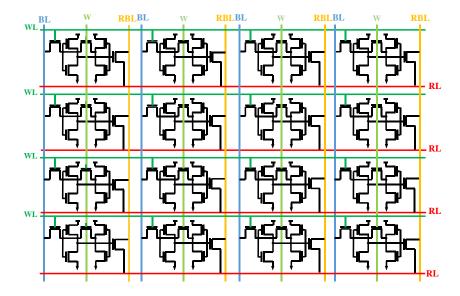

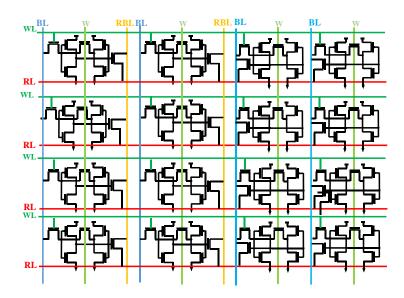

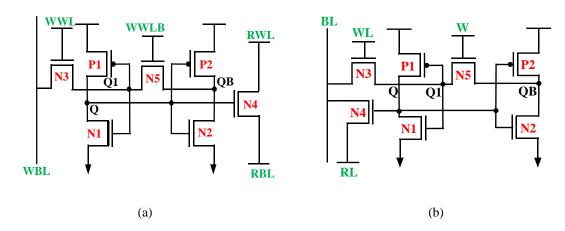

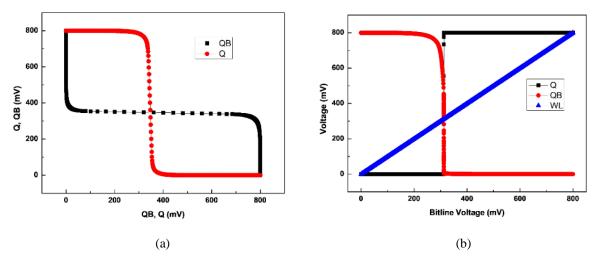

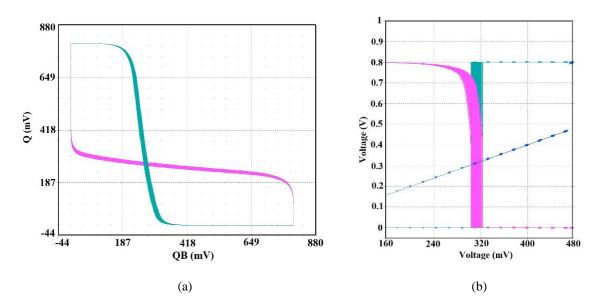

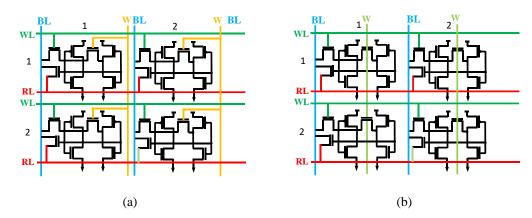

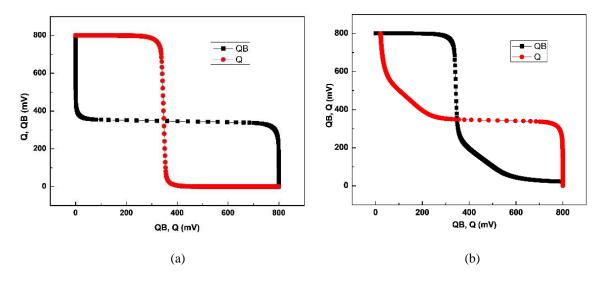

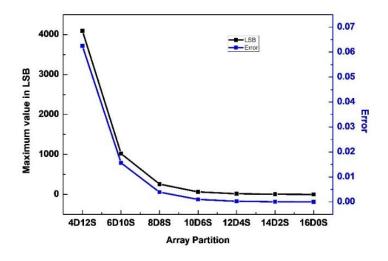

#### **Objective 4:**