# **CNTFET BASED DESIGN OF TERNARY ADDERS BASED ON GDI TECHNIQUE**

A DISSERTATION REPORT SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE

OF

# MASTER OF TECHNOLOGY

IN

**VLSI DESIGN & EMBEDDED SYSTEMS**

SUBMITTED BY:

# **RICHA DUBEY**

(2K22/VLS/11) UNDER THE SUPERVISION OF

MR. ANURAG CHAUHAN ASSISTANT PROFESSOR

ELECTRONICS & COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042 MAY 2024

## DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## ACKNOWLEDGEMENT

I would like to express my sincerest appreciation to my Project Guide, **Mr. Anurag Chauhan**, for his guidance and tremendous support throughout the course of this project. His knowledge and expertise have been helpful in this research work. The regular discussions with him and his ideas for approaching each problem statement in a different manner have been extremely useful. He guided me in every step and in future also he will guide me in completing this research project. I would also like to thank all the other faculty members and non-teaching staff of the Department of ECE for helping me directly or indirectly in this project. Finally, I owe my heartiest gratitude to the most important people in my life, i.e. my parents and my brothers for their unconditional support, love, inspiration, and sacrifices. They have always been a source of inspiration throughout my life.

Name: Richa Dubey Roll no. 2K22/VLS/11

Place: Delhi Date: 31<sup>st</sup> may 2024

## DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **CANDIDATE'S DECLARATION**

I, Richa Dubey, Roll No. 2K22/VLS/11, student of M. Tech (VLSI Design & Embedded System), hereby declare that the Project Dissertation titled "CNTFETbased design of Ternary Adders based on GDI Technique" which is submitted by me to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is original and not derived from any source without appropriate citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship or other similar title or recognition.

Name: Richa Dubey Roll no. 2K22/VLS/11

Place: Delhi Date:31<sup>st</sup> may 2024

## DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

# CERTIFICATE

I hereby certify that the Project Dissertation titled "CNTFET-based design of Ternary Adders based on GDI technique" which is submitted by Richa Dubey, Roll No. 2K22/VLS/11 Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date: 31<sup>st</sup> may 2024

Mr. Anurag Chauhan Assistant Professor, ECE Supervisor

#### ABSTRACT

This study illustrates the design of ternary logic gates, half adders (HA) using CNTFETs, and the Gate Diffusion Input Technique (GDI). The scaling down of devices is increasing which leads to various issues in the device. We know, the dimension of devices has been decreased by two in every two years (According to Moore's) and this scaling down of devices facing several drawbacks. Nonetheless, as the ITRS 2009 edition points out, as device dimensions have decreased to the approximately 22-nm region, scaling down is encountering constraints pertaining to device performances and manufacturing technologies. This scaling down is causing problems for the devices, like passive power dissipation, changes in device structure and doping, including electron tunneling via thin insulator layers and narrow channels, as well as associated leakage currents. By changing the channel materials in most structures and substituting carbon nanotubes or arrays of carbon nanotubes, we can get around these restrictions. So, in the designing of the gates we will use CNTFET model instead of MOSFET. We all have learnt about binary logic but in our designing, we will use ternary logic as it is three valued and has more advantages over binary logic in the design of digital system. Now we can transmit more data with minimal interconnections results in less memory requirements. Because of the less estimation interconnection cost it receives more attention than others. To implement the design, we can use HSPICE or Cadence by taking model file compatible with these tools. On the Stanford University CNFET Model, the CNTFET model file is accessible. Semiconducting single-walled carbon nanotubes function as the channels in this tiny, SPICE-compatible model that represents unipolar MOSFETs working in enhancement mode... Thus, we employed this model in our project. When compared to traditional binary logic design gate techniques, this ternary logic with CNTFET design technique offers superior speed and power consumption. As a result, the power delay product is reduced. It has been noted that, in comparison to the current design, the suggested HA design's delay has been significantly reduced. In this study, the design has been covered in further detail. The device used for this simulation is cadence virtuoso.

## CONTENTS

Page No.

Title

| Acknowledgment                     | i     |

|------------------------------------|-------|

| Candidate's Declaration            | ii    |

| Certificate                        | iii   |

| Abstract                           | iv    |

| Content                            | v     |

| List of Figures                    | vii   |

| List of Tables                     | ix    |

| List of Abbreviations              | x     |

| CHAPTER 1                          |       |

| INTRODUCTION                       | 1-17  |

| 1.1 Motivation                     | 1-2   |

| 1.2 CNTEFT                         | 2-5   |

| 1.3 Ternary Logic                  | 5-10  |

| 1.3.1 Types of Ternary Logic Gates | 6     |

| 1.3.1.1 STI                        | 7     |

| 1.3.1.2 PTI                        | 8     |

| 1.3.1.3 NTI                        | 9     |

| 1.4 Symbols                        | 10    |

| 1.5 GDI                            | 10    |

| 1.6 GDI based gate design.         | 13    |

| 1.6.1 Two input OR gate            | 13    |

| 1.6.2 Two input AND gate           | 13    |

| 1.7 Objective                      | 14-15 |

| 1.8 Methodology                    | 16    |

| 1.9 Thesis Organization            | 16-17 |

| CHAPTER 2                          |       |

| LITERATURE REVIEW                  | 18-22 |

| 2.1 Literature Review              | 18-20 |

| 2.2 Technical Gap                  | 20-22 |

| CHAPTER 3                        |         |

|----------------------------------|---------|

| COMPARISONS WITH EXISTING        |         |

| ART OF TECHNIQUES                | 23-28   |

| 3.1 Binary Vs Ternary Logic      | 23 - 24 |

| 3.1.1 Conclusion                 | 25      |

| 3.2 MOSFET Vs CNTFET             | 26-27   |

| 3.2.1 Conclusion                 | 27      |

| 3.3 Symbol for MOSFET and CNTFET | 28      |

| CHAPTER 4                        |         |

| SETUP AND SIMULATION             | 29-35   |

| 4.1 Existing HA design           | 29-30   |

| 4.2 Proposed HA design           | 30-31   |

| 4.3 Ternary Decoder              | 31-33   |

| 4.3.1 Symbol for Ternary decoder | 33      |

| 4.4 Ternary Buffer               | 34-35   |

| 4.4.1 Symbol for Ternary buffer  | 35      |

| CHAPTER 5                        |         |

| <b>RESULTS AND DISCUSSION</b>    | 36-38   |

| 5.1 Simulations                  | 36-37   |

| 5.2 Results                      | 37-38   |

| CHAPTER 6                        |         |

| CONCLUSION AND FUTURE SCOPE      | 39      |

| PUBLICATIONS                     | 40-41   |

| REFERENCES                       | 42-45   |

# LIST OF FIGURES

| Figure No. | Figure Description            | Page No. |

|------------|-------------------------------|----------|

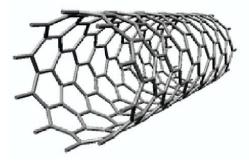

| Fig 1.1    | Single Walled CNT diagram     | 4        |

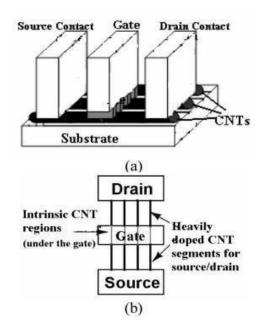

| Fig.1.2    | Schematic of CNTFET           | 5        |

| Fig.1.2    | Circuit Schematic of STI      | 7        |

| Fig.1.3    | Transient response of STI     | 7        |

| Fig.1.4    | Circuit Schematic of PTI      | 8        |

| Fig.1.5    | Transient response of PTI     | 8        |

| Fig.1.6    | Circuit Schematic of NTI      | 9        |

| Fig.1.7    | Transient response of NTI     | 9        |

| Fig.1.8    | STI Symbol                    | 10       |

| Fig.1.9    | PTI Symbol                    | 10       |

| Fig.1.10   | NTI Symbol                    | 10       |

| Fig.1.11   | GDI Basic cell                | 11       |

| Fig.1.12   | GDI based 2 i/p OR Gate       | 13       |

| Fig.1.13   | GDI based 2 i/p AND Gate      | 13       |

| Fig.1.14   | Existing schematic of HA      | 15       |

| Fig.3.1    | MOSFET Symbol                 | 29       |

| Fig.3.2    | CNTFET Symbol                 | 29       |

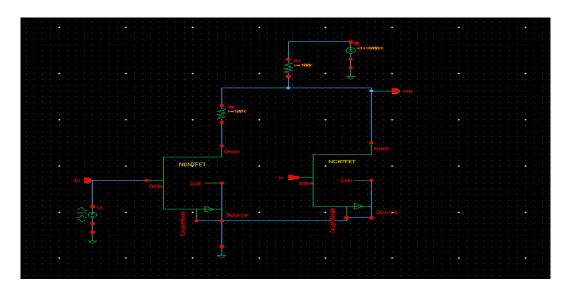

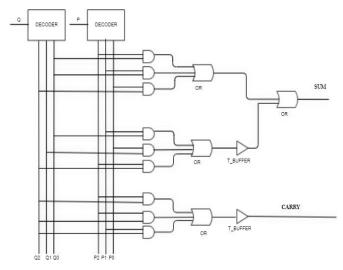

| Fig.4.1    | Schematic of HA               | 30       |

| Fig.4.2    | Ternary Decoder               | 32       |

| Fig.4.3    | Schematic of T-decoder        | 33       |

| Fig.4.4    | Op Waveform of T-decoder      | 33       |

| Fig.4.5    | Ternary decoder symbol        | 33       |

| Fig.4.6    | Circuit Schematic of T-buffer | 34       |

| Fig.4.7 | Output waveform of T-buffer      | 35 |

|---------|----------------------------------|----|

| Fig.4.8 | T-buffer Symbol                  | 35 |

| Fig.5.1 | Circuit Schematic of Proposed HA | 36 |

| Fig.5.2 | Output waveform of HA            | 37 |

| Fig.5.3 | Delay Calculation Waveform       | 37 |

| Fig.5.4 | Transient delay of HAs           | 38 |

# LIST OF TABLES

| Table no. | Table Name                              | Page no. |

|-----------|-----------------------------------------|----------|

| Table 1.1 | Logic Symbols                           | 6        |

| Table 1.2 | TT for STI, PTI and NTI                 | 6        |

| Table 1.3 | TT for Ternary input Logic Gates        | 10       |

| Table 1.4 | Boolean function based on GDI Technique | 11       |

| Table 1.5 | TT of HA                                | 32       |

| Table 5.1 | PDP of HAs                              | 39       |

# LIST OF ABBRIVIATIONS

| S.NO. | Abbreviations | Full Name                                |

|-------|---------------|------------------------------------------|

| 1.    | CMOS          | Complementary Metal Oxide Semiconductor  |

| 2.    | CNTFET        | Carbon Nano Tube Field Effect Transistor |

| 3.    | MVL           | Multi Valued Logic                       |

| 4.    | GDI           | Gate Diffusion Input                     |

| 5.    | STI           | Standard Ternary Inverter                |

| 6.    | PTI           | Positive Ternary Inverter                |

| 7.    | NTI           | Negative Ternary Inverter                |

| 8.    | HA            | Half Adder                               |

|       |               |                                          |

## **CHAPTER 1**

## INTRODUCTION

#### **1.1 MOTIVATION**

The scaling down of devices is increasing which leads to various issues in the device. We know, the dimension of devices has been decreased by two in every two years (According to Moore's) and this scaling down of devices facing several drawbacks. However, as device dimensions shrank down to the sun 22-nm region, scaling down is encountering limitations associated to device performances and fabrication technologies, as stated by ITRS 2009 edition. As a result of this scaling down, the devices are encountering issues such as doping and device structural changes, power consumption, electron tunneling through thin insulator layers and short channels, effects like short channel and related leakage currents [1]. We can overcome these limits by modifying channel materials in MOSFET structure and replacing it with Carbon Nano- tubes or array of carbon nanotubes. So, in the designing of the gates we will use CNTFET model instead of MOSFET. Because of its low OFF-current and ballistic transport characteristics, CNTFET has become a viable option for providing special qualities like low power and high-performance design. [2] - [5]. Another advantage of using CNTEFT over CMOS is that its threshold voltage is dependent on the diameter of the CNT. As a result, by changing the diameter and, in turn, the chirality of CNTs, we can reach a variety of thresholds.

The number of transistors on a device rises as technology scales down, creating issues with interconnect routing throughout the chip [6]. Chip area is decreased when Multi-Valued Logic (MVL) is used through lowering the quantity of interconnects [7]. The comparison is made between binary and ternary from which we can conclude that circuit complexity and cost has been improved results is high performance [8]. The implementation of ternary systems can be done in two ways: unbalanced  $(0, V_{dd}/2, V_{dd})$  comparable to (0, 1, 2) and balanced  $(-V_{dd}, 0, V_{dd})$  corresponding to (-1, 0, 1) [9].

In our design, we have used unbalanced ternary system. A supply voltage of 0.9V is used in our design i.e.  $V_{dd}=0.9V$ .

Logic gates like AND, OR, and NOR have been created with less transistors in the circuit thanks to the use of the Gate Diffusion Input (GDI) technology, resulting in a lower power consumption and reduced room required. When designing low-power circuits, this approach can be used with less transistors than PTL and CMOS approaches used today [10]. the GDI method, which is based on basic cells. It has three inputs (G, P, and N), where the PMOS drain or source is the P node, the NMOS drain or source is the N node, and the NMOS and PMOS common gate input is the G node [11]. The substrate of NMOS and PMOS is connected to the N and P, respectively. Using these ternary gates, based on GDI we have designed a Half adder. This design is then compared with the existing design [12]. Integrating all these advantages results in highly efficient computational logics like ternary half adder.

### **1.2 CNTFET**

CNTFET stands for Carbon Nano Tube Field Effect Transistor. A carbon nanotube is used as the channel in a field effect transistor, or CNTFET. Their great current carrying capacity and excellent metallic and semiconductor qualities make them extensively utilized in several applications. The demand for integrated circuits with fast speed, low power consumption, and tiny size is growing as technology progresses. As per Moore's law the size of transistor will reduced to two after every two years, but this is giving rise to effects like: shorter channel effect which leads to direct tunnelling, increase in gate leakage current [1]. The mentioned drawbacks can be overcome using CNTFET.

CNTFET emerged as a promising candidate for offering unique properties because of its low OFF-current characteristics and ballistic transport, allowing for highperformance design at cheap power. [2] through [5]. The dependence of the CNTEFT threshold voltage on the CNT diameter is another benefit of utilizing it instead of CMOS. Thus, we can achieve numerous thresholds by varying the diameter and, consequently, the chirality of CNTs.

Page 2 of **45**

The carbon atoms in the nanotubes utilized in CNTFETs are connected in a hexagonal pattern and have diameters measured in nanometers. All three carbon atoms in the structure are covalently bound to one another. The carbon nanotubes have a width of one nanometer and a potential length of many centimeters, when discussing their dimensions. These nano tubes are extremely tiny but powerful. They are flexible enough to assume a bent shape before returning to its original form; they are neither brittle not fragile. CNTFETs possess several advantages over other types of transistors. First, they have high carrier velocity. Second, CNT enhances electrostatic control and consumes less power.

Semiconducting single-wall CNTs are used in CNTFETs to construct electrical devices [2]. Single-wall CNTs, also known as SWCNTs, are made up of just one cylinder shown in figure 1.1, and because of their straightforward manufacturing method, they hold great promise as a MOSFET substitute. A SWCNT has the ability to act as a conductor or a semiconductor, depending on the arrangement of atoms along the tube. This is represented by the pair of integers (n, m) and which is also called as chirality vector. Examining a carbon nanotube's (CNT) indices (n, m) can be a simple method of determining if it is metallic or semiconducting. A CNT is metallic if, for any integer i, n = m or n - m = 3i. The tube is semiconducting under all other conditions. Use the formula below to find the CNT's diameter [30] :

$$D_{CNT} = \frac{\sqrt{3}a_0}{\pi}\sqrt{n^2 + m^2 + nm}$$

(1.1)

where  $a_0 = 0.142$  nm is the distance between neighboring carbon atoms on an interatomic scale. The CNTFET schematic diagram is displayed in Fig. 1.1 [30]. The CNTFET features four terminals, just like the conventional silicon device. While the undoped semiconducting nanotubes are positioned as the channel area beneath the gate in Fig. 1, in order to provide a low series resistance in the ON-state, highly doped CNT segments are placed between the gate and the source/drain [2]. Gate is used to electrostatically turn on or off the device when the gate potential increases. MOSFETs and CNTFETs have similar I-V characteristics. It is known as the

threshold voltage, or the voltage needed to switch on a transistor. The half bandgap, which is inversely related to diameter, can be used to estimate the intrinsic CNT channel's threshold voltage to the first order [30].

$$V_{th} \approx \frac{E_g}{2e} = \frac{\sqrt{3}}{3} \frac{aV_{\pi}}{eD_{CNT}}$$

(1.2)

Where distance between carbon-carbon atom is given by a = 2.49 A°, the electric charge unit is denoted by e, the carbon  $\pi$ - $\pi$  bond energy in the tight bonding model is given by  $V_{\pi} = 3.033$  eV, and the CNT diameter is given by D<sub>CNT</sub>. A CNTFET with (19, 0) CNTs as channels has a threshold voltage of 0.293 V from (6) since a (19, 0) CNT's D<sub>CNT</sub> is 1.487 nm in length. There is empirical evidence to support the accuracy of this threshold voltage. The CNTFET's threshold voltage will fluctuate concurrently with the chirality vector. The ratio between the threshold voltages of two CNTFETs with different chirality vectors can be computed as follows, assuming that the m value of the chirality vector is always zero:

$$\frac{V_{th1}}{V_{th2}} = \frac{D_{CNT2}}{D_{CNT1}} = \frac{n_2}{n_1}$$

(1.3)

Equation (1.3) shows that the threshold voltage of a CNTFET is inversely proportional to the chirality vector of a carbon nanotube. The threshold voltage of a CNTFET containing (13, 0) CNTs is 0.428 V, whereas a CNTFET with (19, 0) CNTs has a threshold voltage of 0.293 V. By mimicking the drain current of a CNTFET with chirality (19, 0) at the voltage threshold determined by (1.2), the ON-current of the reference transistor is achieved.

Fig.1.1 Single Walled CNT Page 4 of 45

Fig. 1.2 Schematic of CNTFET a) Cross sectional view (b) Top view [30]

#### **1.3 TERNARY LOGIC**

Ternary Logic provides energy efficiency, simplicity in logic design, and a reduction in chip size and design complexity. Both serial and parallel arithmetic processes are made simpler with the aid of ternary logic. Serial and serial-parallel arithmetic processes can be completed more quickly because to ternary logic. A signed 32-bit multiplier can achieve a more than 50% reduction in chip size and power dissipation by employing an effective MVL implementation.

Based on MOS technology, there are two types of MVL (multiple valued logic) circuits: Current mode Circuits for MVLs and voltage mode Circuits for MVLs [7]. Different voltage levels are used in voltage-mode logic (VML) to represent logic values. Like this, in current-mode logic (CML), current levels are indicative of various logic values. CML circuits can be constructed with fewer transistors and are often fast. However, they have a major drawback in that they lose a lot of power. Three states 0, 1, and 2 represent the low, middle, and high ternary values in ternary logic. Voltage levels are another way to express these values. These logic states 0,1, and 2 are represented by the voltage values 0,  $V_{dd}$ ,  $V_{dd}/2$ , and  $V_{dd}$ , [8], where  $V_{dd}=0.9V$ .

Page 5 of 45

| Table.1. | 1 Logic | Symbols |

|----------|---------|---------|

|----------|---------|---------|

| Voltage level | Logic Values |

|---------------|--------------|

| 0             | 0            |

| $0.5 V_{dd}$  | 1            |

| Vdd           | 2            |

### **1.3.1** Types of Ternary logic inverters [25]:

- 1.3.1.1 Standard Ternary Inverter (STI)

- 1.3.1.2 Positive Ternary Inverter (PTI)

- 1.3.1.3 Negative Ternary Inverter (NTI)

The Truth Table for these three inverters is shown on Table III.

Table.1.2 Truth Table for STI, PTI and NTI [12]

| Input I | NTI | PTI | STI |

|---------|-----|-----|-----|

| 0       | 2   | 2   | 2   |

| 1       | 0   | 2   | 1   |

| 2       | 0   | 0   | 0   |

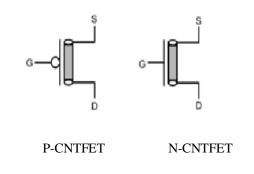

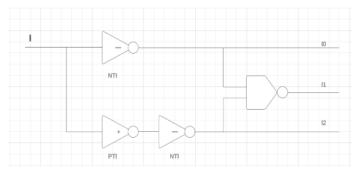

The above inverters are implemented using the CNTFET. A ternary decoder generates three unary outputs for input I. The decoder is made up of a NOR gate based on the GDI approach, two NTI gates, and a PTI gate. The GDI approach is utilized to reduce the 10 transistors in the current NOR gate design to 8 transistors. Figure 3 shows the circuit diagram for a decoder [12].

**STI** (Standard Ternary Inverter): It is made up of two resistors and two MOS transistors (NMOS and PMOS). When  $V_{in}$ , the input voltage, is zero volts (logic zero), PMOS activates and NMOS switches off. Consequently, the output will become logic 2 (V<sub>dd</sub>=0.9 V) and the resistor current will cease.

However, if the input voltage is 0.9V (logic 2), NMOS turns on and PMOS turns off. This prevents current from flowing through the resistors and changes the output to logic 0 (i.e., 0 volts). Furthermore, at 0.45 volts (logic 1), or the voltage level of V<sub>dd</sub>/2, both PMOS and NMOS activate. Current may therefore pass via both resistors. The resistors, which are used to dissipate less power and have a R value of 1 mega ohm, are selected so that their resistance is substantially higher than the resistance of the transistors that are turned on [25].

Fig.1.2 Circuit Schematic of Standard Ternary Inverter (STI)

Fig.1.3 Transient response of STI

Page 7 of 45

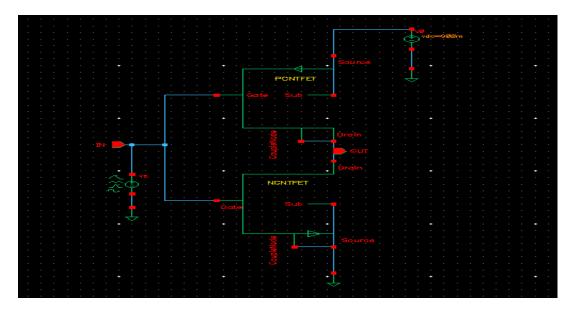

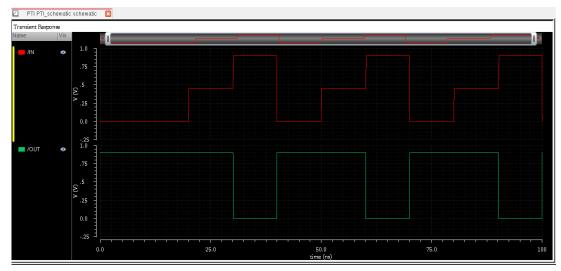

**PTI** (**Positive Ternary Inverter**): With PTI, the output is 0.9 volts (logic2) when input  $V_{in}$  hits 0 volts (logic0), as PMOS is currently turned on. This is because the circuit functions as a closed path, resulting in a total voltage drop of 1.8 volts at the output terminal.  $V_{in}$ =0.45 volts, or a logic 1, is the input; when this occurs, the output is 0.9 volts, or a logic 2. The output seems to be 0 volts (logic 0) when the input is displayed as 0.9 volts or as a logic 2 [25], this is because the PMOS gate to source terminal is open.

Fig.1.4 Circuit Schematic of Positive Ternary Inverter (PTI)

Fig 1.5 Transient response of PTI

Page 8 of 45

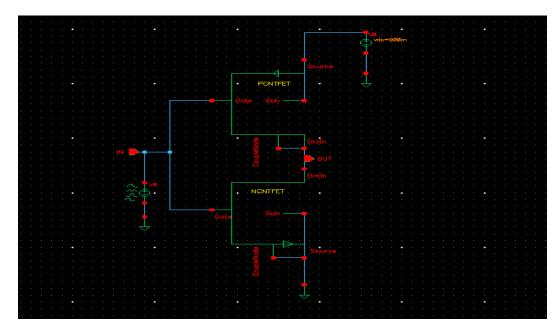

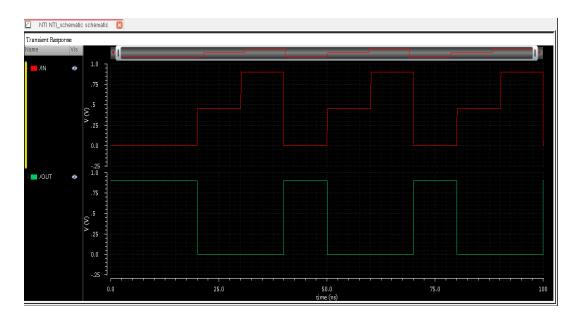

**NTI** (Negative Ternary Inverter): NMOS is on when  $V_{in} = 0.9V$ . When a channel exists, that is, when  $V_{gs} > V_t$  (the threshold voltage), current will always flow, indicating that the circuit's voltage is present. Thus, output from 0 volts (logic 0) to 0.9 volts.

Fig 1.6 Circuit Schematic Negative Ternary Inverter (NTI)

Fig 1.7 Transient response of NTI

Page 9 of 45

Ternary inverters are used in the construction of ternary logic gates. Implementing ternary NAND and NOR gates is comparable to doing so with binary NAND and NOR gates. Here are several instances of fundamental resistor-based ternary NAND, T-NOR, T-AND, and T-OR gates.

#### **1.4 SYMBOLS**

Fig. 1.8 PTI Symbol

Fig.1.9 NTI Symbol

Fig.1.10 STI Symbol

| Α | В | T-NAND | T-NOR | T-AND | T-OR | T-EXOR |

|---|---|--------|-------|-------|------|--------|

| 0 | 0 | 2      | 2     | 0     | 0    | 0      |

| 0 | 1 | 2      | 1     | 0     | 1    | 1      |

| 0 | 2 | 2      | 0     | 0     | 2    | 2      |

| 1 | 0 | 2      | 1     | 0     | 1    | 1      |

| 1 | 1 | 1      | 1     | 1     | 1    | 1      |

| 1 | 2 | 1      | 0     | 1     | 2    | 1      |

| 2 | 0 | 2      | 2     | 0     | 2    | 2      |

| 2 | 1 | 1      | 1     | 1     | 2    | 1      |

| 2 | 2 | 0      | 0     | 2     | 2    | 0      |

Table.1.3 Truth Table for Ternary input logic gates [25]

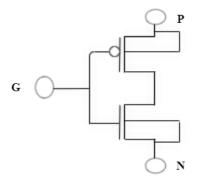

## 1.4 GATE DIFFUSION INPUT TECHNIQUE (GDI)

Figure 1 illustrates the GDI approach, which is predicated on the use of simple cells. There are three inputs (G, P, and N), where the G node is the NMOS and PMOS common gate input, the P node is the PMOS drain or source input, and the N node is the NMOS drain or source input [11]. The N and P, respectively, are connected to the Page **10** of **45**  substrates of NMOS and PMOS.

CMOS implementation of same function required large number of transistors which require larger chip area and increases complexity. GDI based gates require less chip area, as we must only change the input to get the required functionality.

Fig.1.11 GDI basic cell [11]

Table V represents implementation of various Boolean function based on GDI technique. We can see from the Table that, by changing the input configuration results in various Boolean functions. In this paper, we have implemented functions like OR, AND, NOT, NOR (by simply using one OR and one NOT).

Table.1.4 Implementation of various Boolean function based on GDI technique.

| N | Р | G | Out   | Function |

|---|---|---|-------|----------|

| 1 | Q | Р | P+Q   | OR       |

| Q | 0 | Р | PQ    | AND      |

| R | Q | Р | PQ+PR | MUX      |

| 0 | 1 | Р | P     | NOT      |

The main idea behind the GDI technique is that an n-type diffusion region can be diffused inside a p-type diffusion area to create a virtual gate. The gate regulates the transistor action in the circuit and serves as an input terminal. To make a GDI circuit we need a PMOS transistor, NMOS transistor and a resistive load. The GDI logic is comparatively simple that other logic gates because it has only one input terminal. Additionally, it reduces the overall resistance of the circuit by doing away with the need for an external pull-up or pull-down resistor. When the GDI technique is implemented, it gradually decreases the number of transistors required is one of the main benefits of the GDI technique, as it greatly lowers area and power consumption. The number of transistors needed for the circuit is decreased because this method just requires one transistor for shift registers and logic conversions. In this way, the overall circuit power is also reduced.

One benefit of GDI technique is that it may create complicated digital circuits using minimal number of gates. These building pieces can be combined in several ways to produce an infinite variety of circuit designs. Moreover, the GDI technique reduces complexity of digital circuit design by simplifying circuit architectures. Many digital circuits such as adders, multipliers, low-power Boolean logic gates, RAM, analog circuits, have made extensive use of the GDI approach. Digital circuit approaches such as CMOS and SRAM can be substituted with the GDI technique.

For digital circuits found in portable electronics, GDI technology provides a dependable solution. The GDI approach is a desirable and practical substitute for conventional circuit techniques because of its advantages, which include better performance, lower power consumption, and smaller circuit sizes.

In conclusion, GDI technique is a simple and effective CMOS technology for designing low power digital circuit with high performance. The GDI technique's simplicity and low power make it one of the most viable solutions for digital circuits.

## 1.4 GDI (Gate Diffusion Input) BASED GATE DESIGN

# 1.6.1 Two input OR Gate

Fig.1.12 GDI based 2 input OR gate.

1.6.2 Two input AND Gate

Fig.1.13 GDI based 2 input AND gate.

Page 13 of 45

### **1.7 OBJECTIVE**

Ternary Half Adder is based on ternary logic. It is designed using CNTFET and the compared with the existing design [12]. The gates used in the design of HA is based on GDI technique to reduce the quantity of transistors utilized. In the existing design of HA, the logic gates are designed using the conventional method, while in our design we are using GDI technique. One of the significant advantages of GDI technique is the reduced transistor count, which contributes significantly to low power consumption and decreased area. There is a decrease in the number of transistors needed for the circuit because this technique uses only one transistor for shift registers and logic inversion thus, lowers the circuit's overall power usage.

In the designing, we have integrated all the advantages like used CNTFET instead of MOSFET, used ternary logic instead of binary logic and used GDI technique instead of Conventional technique for logic gates design. So, integrating all this advantages, we can design highly efficient computational logics like Half adder, Full adder, Multiplier etc.

This report contains the ternary half adder's GDI-based design technique using CNTFET. The design of Half adder involves the use of ternary buffer, ternary logic gates like AND, OR and ternary decoder. In all this logic designs, we have used supply voltage i.e. V<sub>dd</sub> =0.9V except ternary buffer, where supply voltage of 0.45V is used for PCNTFET. Upon comparison, our suggested Half Adder (HA) design has a significantly lower power and delay product (PDP) than the current design. Table I provides the ternary half adder's truth table.

| A | В | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 0 | 2 | 2   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 2   | 0     |

| 1 | 2 | 0   | 1     |

| 2 | 0 | 2   | 0     |

| 2 | 1 | 0   | 1     |

| 2 | 2 | 1   | 1     |

Table.1.5 Truth Table of HA

Using K-map and the truth table above, we can formulate the expression for Sum and Carry as follows:

$$Sum = A_2B_0 + A_1B_1 + A_0B_2 + 1. (A_1B_0 + A_0B_1 + A_2B_2)$$

(1.4)

Carry=1.

$$(A_1B_2 + A_2B_1 + A_2B_2)$$

(1.5)

The Circuit Schematic of Half Adder (HA) is shown in fig.1.14:

Fig.1.14 Existing Circuit Schematic of HA [13]

The above is the circuit schematic of existing design of HA. In this schematic, we have replaced the conventional logic gates with the GDI based logic gates to reduce the area and increase the overall performance.

#### **1.8 METHODOLOGY**

For the design purpose we have used Stanford CNTEFT model- Verilog A with 32nm technology. Cadence Virtuoso is the design tool utilized in the simulation.

#### **1.9 THESIS ORGANIZATION**

This Thesis is divided into six chapters. Ternary adder based on GDI technique, CNTEFT, Ternary Logic, GDI are covered in chapter 1. Chapter 1 also covers the strategy, motivation, goal, and organization of the thesis. Literature survey and all the previous work related to Ternary Adders is done in chapter 2. The comparison between ternary logic and binary logic, MOSFET and CNTFET with conclusion, is done in chapter 3. In chapter 4, there is discussion about the existing HA design, proposed HA design, ternary decoder, and ternary buffer. In chapter 5 Simulations and result is Page 16 of 45

discussed and in chapter 6, conclusion and future scope is discussed.

CHAPTER 1: Provides the information about the need of the CNTFET, Ternary logic and GDI technique. It also provides information about the existing Ternary HA circuit. The objective, tools used, Motivation is also included in this chapter.

CHAPTER 2: Literature survey is done in this unit. The previous work related to the Ternary Adders is done in this unit. A comparison has been made, based on parameters like PDP of HA with the existing HA design. The results have been shown in this report and from that we can conclude that the PDP is comparatively less than the existing HA design.

CHAPTER 3: The comparison between binary and ternary inverter, CNTFET and MOSFET, is done in this unit conclusion is also drawn, why we use Ternary logic and CNTFET in our design.

CHAPTER 4: It deals with the workflow, from where we got the idea i.e. existing HA design, proposed HA design, ternary decoder, and ternary buffer. Symbols for both Ternary buffer and Decoder is included in this chapter.

CHAPTER 5: In this chapter, conclusion and future scope is discussed. The achieved result of low PDP can be used further in other digital integrated circuits. The simulation result of proposed design is achieved using Stanford CNTEFT model-Verilog A with 32nm technology using cadence virtuoso with the supply voltage of 0.9V.

CHAPTER 6: It deals with conclusion and future scope of the proposed HA design. Later in the report, publications and references are added.

## **CHAPTER 2**

#### LITERATURE REVIEW

#### **2.1 LITERATURE REVIEW**

Binary Logic is a two valued function i.e. '0' and '1' or 'True' and 'False'. But, in some cases it is not possible to decide whether it is 'True' or 'False'. For instance, every signal value in a logic circuit, which can be either 0 or 1 in a steady state, can alternate between 0 and 1 or 1 and 0 in a transient state, making it difficult to determine the value's true value. Another example where it might be challenging to determine whether a value is 0 or 1 in many situations is the starting states of sequential circuits. Moreover, it can be argued that some data are irrelevant to the algorithm or that the process does not stop for a particular set of data. Instead of using binary logic, which uses two values to represent states that are clearly true or false, we can use ternary logic, which uses three values to represent the ambiguous states described above [14].

In [15], a T-gate solution utilizing bipolar transistors is suggested. A different T-gate implementation utilizing MOS technology has been suggested by Muftah and Smith [16], [17]. The major disadvantages of Ternary Logic are its complexity. As the number of variables increases, the complexity of logic gates increases rapidly.

A different ternary logic family is presented in this contribution in [18], which can be applied to the design of sequential and combinational ternary logic circuits. The new family can be implemented in VLSI because it is based on MOS technology. It consists of a set of NANDS, NOR, and inverter gates. Charge-coupled devices (CCDs) have been used in the creation of MVL circuits [19]. Molecular devices are emerging as a possible replacement for current silicon technology as we enter the age of nanotechnology. A lot of research is being done on carbon-nanotube field-effect

Page 18 of 45

transistors (CNFETs) as potential replacements for silicon MOSFETs. In-depth research has begun to investigate potential circuit applications and comprehend the device mechanics of CNFETs [20]. The bandgaps of carbon nanotubes are diameter dependent. The bandgap measures the threshold voltage of the CNTFET. Carbon nanotubes are appropriate for voltage-mode MVL implementation because their diameter may be adjusted to have specific threshold voltages [21].

It is challenging to maintain supply and threshold voltage scaling to provide the necessary reliability, controlled energy consumption, power dissipation management, and performance growth due to the rapid advancement of technology. Several design strategies have been explored to reduce power consumption [22]. Pass transistor logic is one type of logic that is frequently used in low-power digital electronics. PTL provides several advantages, including lower power consumption, faster speeds, and fewer connection effects. The GDI approach helps to lessen a few of PTL's shortcomings. This makes it possible to use just two transistors to implement a large range of complicated logic functions. Furthermore, it can be used to improve power characteristics and build low-power, fast circuits with fewer transistors than CMOS and existing PTL techniques. The GDI approach offers a straightforward top-down design methodology and is helpful for quickly building low-power circuits with just two transistors, as opposed to CMOS and existing PTL approaches [23]. Concurrently, it enhances static power characteristics and logic level swing. The comparison and analysis of various logic gates based on various technique is already done in [24]. It has been observed that the Gate Diffusion Input (GDI) design style exhibits better qualities than other design styles. In terms of factors like power and transistor count, the optimal logic design style may be the gate diffusion input design style. Therefore, high-performance, and low-power applications can both benefit from the employment of the gate diffusion input design approach. CMOS implementation of same function required large number of transistors which require larger chip area and increases complexity. GDI based gates require less chip area, as we must only change the input to get the required functionality.

Page 19 of 45

An existing design of HA involves the use of CNTFET and Ternary Logic is already given in [12]. In this design, the logic gates are designed using the conventional method so, we have replaced the logic gate design with GDI technique which results in reduced area, less complexity, better speed, and low power consumption.

#### 2.2 TECHNICAL GAP

Following observation and review of all the reported work, there is a technical gap. The main objective of the design is to reduce the power consumption and increase the speed of operation. Ternary logic provides fewer interconnections, compact circuitry, and faster computations in advanced computing systems. The proposed design when compared with existing designs, provides less power consumption, better speed, and less chip area. Today, low power consumption is the basic requirement for the VLSI system which can be achieved by reducing number of transistors on chip. So, we have used GDI (Gate Diffusion Input) technique for the designing of Gates. Instead of using MOS, we have used CNTFET as they have less power consumption and provides higher speed. Integrating all these advantages results in highly efficient computational logics like half adder and full adder. A comparison has been made, based on parameters like PDP of HA with the existing HA design. The results have been shown in this report and from that we can conclude that the PDP is comparatively less than the existing HA design.

Ternary half adders are digital circuits that can add ternary numbers. Its two inputs, A and B, and its two outputs, S and C, represent the carry that comes from the addition and the total of A and B, respectively. Carbon nanotube field-effect transistors (CNTFETs) are a promising technology for implementing high-performance and low-power digital circuits, and the GDI (Gate Diffusion Input) technique has been widely used to create effective digital circuits. Consequently, a high-performing and low-power solution can be achieved by combining the GDI technique with CNTFET technology to create a ternary half adder.

Using the GDI technique, a circuit's performance can be improved, and its transistor count can be decreased. GDI can be used to create several digital logic gates, such as the AND, OR, NOT, XOR, and XNOR gates. The Ternary logic functions required for the addition of ternary numbers can be implemented for a ternary half adder using GDI logic circuits. Furthermore, by diffusing an n-type diffusion region within a p-type diffusion area, the GDI approach may be utilized to construct a virtual gate, which lowers the number of transistors needed in the circuit.

CNTFETs are another promising technology for implementing high-performance digital circuits. They are smaller in size and have lower power consumption compared to traditional MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors). The unique properties of CNTFETs make them an ideal technology for designing digital circuits that require high performance and low power consumption.

By combining the GDI technique with CNTFETs, a high-performance ternary half adder circuit can be designed. The GDI technique can be used to implement the ternary logic functions needed for addition, while CNTFETs can be used in place of traditional MOSFETs to increase performance and reduce power consumption. The GDI technique also allows for the creation of virtual gates, further reducing the number of CNTFETs required in the circuit.

The design process for a ternary half adder based on GDI technique using CNTFET technology involves several steps. The logic diagram for the ternary half adder should be created based on the GDI technique and the ternary logic functions needed for addition. Using this logic diagram, each gate in the circuit can be designed using CNTFETs with the GDI technique. The circuit can then be verified using simulation software that considers the unique properties of CNTFETs. The design can be optimized to reduce power consumption and improve performance by fine-tuning the design parameters.

In conclusion, designing a ternary half adder based on GDI technique using CNTFET technology can lead to a high-performance and low-power solution for addition of ternary numbers. The GDI method can be applied to lower the number of transistors in a circuit and enhance its functionality, whereas power consumption can be decreased, and performance can be increased with CNTFETs. Future research in this area may lead to further advancements in high-performance digital circuits using CNTFETs and the GDI technique.

#### **CHAPTER 3**

## **COMPARISONS WITH EXISTING ART OF TECHNIQUES**

#### **3.1 BINARY VS TERNARY LOGIC**

Binary logic is two valued or Boolean logic which deal with either true or false. An approach known as multi-valued logic (MVL) has more than two truth values or potential states. By adjusting the base or radix of a two-valued logic, we can convert it into an n-valued logic. For instance, ternary logic is used in three valued logics, where base or radix is three. Quaternary logic, on the other hand, is used in four valued logics, where radix is four, and so forth. These four valued logics have the logic states 0,1,2, and 3, and such three valued logics have the logic symbols 0,1, and 2. Radix is the number of distinct digits that can be stated in terms of a single digit. The binary system uses the symbols "0" and "1" to represent values, whereas the ternary system uses the three logic symbols (0, 1, and 2) [25]. Also, we can write (-1,0,1) to represent ternary logic. In the architecture of digital systems, "three valued" ternaries offer more benefits than binary logic. The primary benefit of utilizing ternary logic is that it allows us to send a greater amount of multivalued logic information, which reduces the space of the chip. It gets more attention than others because of the estimated connectivity cost being lower.

Mathematically, we can observe that ternary coding is much efficient than the binary coding. But it is less used in computation as binary logic is already established and implementation of ternary logic is more complex. Ternary logic is used in algorithms that use decision trees and in digital communications where error correction coding is employed. As the technology was absent for mass production of MVL so circuit implementation has been delayed. Recently, there has been a lot of activity in the study of compact MVL devices that incorporate multiple-switching characteristics in a single device, such as quantum dot/super lattices-based constant intermediate

current and 2D heterojunction-based negative-differential resistance (NDR)/trans conductance (NDT) devices [26]. Thus, the issue of implementation has also been resolved. When designing logic gates, the use of binary logic may result in more complex circuits and higher power consumption. While binary logic is used for quick computing, ternary logic gates are employed for decoding since they require fewer gates. As integration density rises, CMOS technology is up against a power scaling limit. MVL can be used to tackle this power scaling issue. To overcome the power scaling problem and raise integration density to peta-scale levels by lowering system complexity, multi-valued logic (MVL) is a desirable substitute.

So, at the end we can conclude that ternary logic is a good replacement to binary logic in terms of decreasing circuit complexity and resolving power scaling challenge in CMOS.

#### **3.1.1 CONCLUSION:**

Ternary logic has advantages in terms of binary arithmetic, especially for complex calculations involving many digits. Ternary arithmetic can be up to three times faster than binary arithmetic because it can process three digits at once, making it more efficient. This approach can be especially useful in computing hardware such as GPUs, where larger calculations are needed to produce high-quality graphics.

Another advantage of ternary logic is its ability to reduce circuit complexity, size, and power consumption. Compared to binary circuits, ternary circuits can perform the same operations using fewer transistors, reducing the circuits' size and power consumption. This reduction in power consumption makes ternary circuits particularly useful for battery powered devices where power efficiency is critical.

Ternary logic can also improve the computational power of digital circuits by allowing the use of multiple levels of voltage. In some cases, the third logic state can be used to store information or as an "error flag" to indicate errors during operation. This approach can increase circuit efficiency by reducing the need for additional logic gates and circuits, further reducing power consumption.

In addition, ternary logic can be useful in quantum computing, where qubits (quantum bits) are used to store data. Using qubits, more complex calculations are possible due to multiple states in Qubit. Ternary logic can be used to represent complex quantum states, leading to better performance and more efficient quantum computers. In summary, ternary logic offers several advantages over binary logic, including increased information density, improved computational power, reduced circuit complexity, and lower power consumption. The use of ternary logic can lead to faster, more powerful digital circuits with lower power consumption, making it a potentially significant technology for the future. However, the use of ternary logic is not yet widespread, and binary logic remains the dominant standard in digital electronics today.

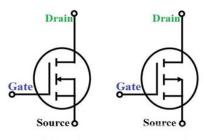

#### **3.2 MOSFET VS CNTFET**

The MOSFET, is made by carefully oxidizing silicon. MOSFETs have an insulated gate, and the device's conductivity is determined by its voltage. In contrast to bipolar transistors like BJTs, it requires no input current to control the load current.

The term "CNTFET" refers to a type of transistor that has good performance at minimal power which uses carbon nano tube as channel, and it has low OFF- current properties.

Multiple thresholds are needed to construct ternary logic circuits using standard MOSFETs, and these can be obtained when we body bias the MOS transistor. Due to this reason we move to CNTFET as it is easy to change the threshold voltage in CNTFET by just changing the chirality. According to research, ternary logic circuits perform better with CNTFETs because they allow the physical dimensions of carbon nanotubes (CNTs) to be channeled to produce different threshold voltages. When we change the diameter of CNTFET, its chirality also changes. By changing its diameter, one can create a changeable threshold voltage. Therefore, by using CNTFETs with distinct chirality, it is possible to obtain the numerous thresholds needed to build ternary logic circuits. Because CNTFET technology offers improved energy efficiency by up to ten times than CMOS technology, it could eventually take the place of CMOS technology in circuit design.

The scaling down of devices is increasing which leads to various issues in the device. We know, the dimension of devices has been decreased by two in every two years (According to Moore's) and this scaling down of devices facing several drawbacks. But as the ITRS 2009 version points out, there are limits to scaling down related to the device performances and fabrication technology as device dimensions shrunk down to sun 22-nm range. The devices are experiencing issues such as electron tunneling through thin insulator coatings and small channels, the corresponding leakage currents, passive power dissipation, short channel effects, and changes in doping and device structure because of this scaling down [1]. We can overcome these limits by modifying channel materials in MOSFET structure and replacing it

with Carbon Nano- tubes or array of carbon nanotubes. So, in the designing of the gates we will use CNTFET model instead of MOSFET model.

We can conclude that using CNTFET instead of MOSFET increases the device performance.

### 3.2.1 CONCLUSION:

Digital electronics commonly uses two types of field-effect transistors: MOSFET and CNTFET. Even though they both function according to the field effect theory, they differ in several ways regarding their design, functionality, and usefulness.

For many years and up to present day, MOSFETs have dominated the field of digital electronics as they are easier and less expensive to create than CNTFETs, they have better design guidelines because of their well characterized nature.

However, CNTFETs have a few advantages over MOSFETs, such as increased size, power consumption, and performance. Because CNTFETs are composed of nanotubes that are merely a few atoms wide, more transistors may be adjusted into given amount of area.

Additionally, CNTFETs perform better than MOSFETs. They can run at lower voltages, consume less power, and have faster switching speeds. Because of these benefits, they are especially well- suited for uses like portable devices, which call for great performance and low battery consumption.

In summary, every semiconductor like MOSFETs and CNTFETs has both advantages as well as disadvantages and the decision between two relies on the objectives of the application. In digital electronics, MOSFETs continue to be the most widely used technology; nevertheless, CNTFETs have some unique benefits that set them apart for specific uses. Future advancements in both technologies are probable in store, and they likely result in even more potent and efficient digital electronics, given the ongoing progress in nanotechnology.

#### **3.3 Symbol for MOSFET and CNTFET:**

Fig 3.1 MOSFET Symbol (N-channel and P-channel) [28]

Fig 3.2 CNTFET Symbol (P-CNTFET and N-CNTFET) [29]

The comparison between the techniques is done above. From the above discussion we can conclude the real reason behind the use of ternary logic instead of binary and CNTFET instead of MOSFET.

## **CHAPTER-4**

## **SETUP AND SIMULATIONS**

The fundamental criterion for a VLSI system nowadays is low power consumption, which can be addressed by lowering the number of transistors on the device. As a result, we designed gates using the GDI (Gate Diffusion Input) technique. Instead of using MOS, we have used CNTFET as they have less power consumption and provide higher speed. To design HA or full adder we can integrate all the advantages of highly efficient computational logic.

In the previous chapters, we have already discussed about CNTFET, GDI and Ternary logic. The gates which are used in the design of half adder has already been simulated and symbols has been created, so that we can directly use this in the HA design. The existing half adder design based on ternary logic has already been discussed. In the design of the proposed HA, we have used ternary decoder and ternary buffer also.

#### 4.1 Existing HA Design

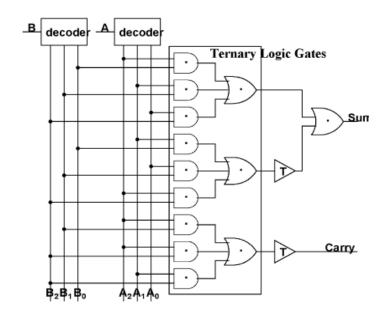

We learned how to create ternary logic gates using the GDI technique in previous section. These gates can now be used to build other arithmetic circuits, including full and half adders. The schematic diagram of HA described in [13] is shown in figure 4.1 below.

Fig.4.1 Schematic diagram of HA

We can use binary logic gates for ternary logic gates in the HA architecture given in [13] since the decoder's output only has two logic levels, 2 or 0, which are equivalent to logic 1 and logic 0 in binary. The computing speed is accelerated by these binary logic gates. However, because these logic gates need a lot of transistors, additional chip space is needed when creating them. So, to overcome this we develop a logic gate design using the GDI technique, which results in a reduced number of transistors, low power, and less area requirement.

#### 4.2 Proposed HA Design

To lower the total area, we replaced the logic gates with GDI-based gates in the HA architecture we suggested in this work. Table IV, which is below, displays the truth table for HA.

| А | В | Sum | Carry |

|---|---|-----|-------|

| 0 | 0 | 0   | 0     |

| 0 | 1 | 1   | 0     |

| 0 | 2 | 2   | 0     |

| 1 | 0 | 1   | 0     |

| 1 | 1 | 2   | 0     |

| 1 | 2 | 0   | 1     |

| 2 | 0 | 2   | 0     |

| 2 | 1 | 0   | 1     |

| 2 | 2 | 1   | 1     |

Table.3.1 Truth Table of HA

The expression for sum and carry can be written as follows using the truth table above:

$Sum=P_2Q_0 + P_1Q_1 + P_0Q_2 + 1. (P_1Q_0 + P_0Q_1 + P_2Q_2)$ (4.1) Carry=1. (P\_1Q\_2 + P\_2Q\_1 + P\_2Q\_2) (4.2)

Where  $P_k$  and  $Q_k$  stand for the decoder's output for inputs P and Q in Figure 4.1. The logic function of the level shifter or ternary buffer employed in the current architecture is discussed further in this chapter.

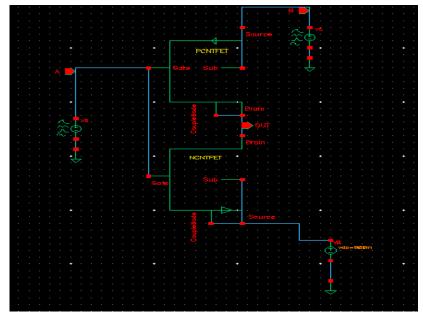

#### 4.3 Ternary Decoder

An electrical circuit with three input lines and many output lines that represent the various ways in which the input lines can be combined is called a ternary decoder. It converts input signals with three possible states—typically represented by the numbers 0, 1, and 2 into output signals that are used to control a variety of devices, including memory chips, motors, and LEDs. The decoder consists of two NTI gates, a PTI gate, and a NOR gate based on the GDI approach. The same idea is depicted in the following figure:

Fig 4.2 Ternary Decoder

One input and three outputs make up a combinational circuit which is called as ternary decoder. It converts an input of x into a unary function. The response of the ternary decoder for input x is given by [12]:

$$X_k = \begin{cases} 2, & \text{if } x = k \\ 0, & \text{if } x \neq k \end{cases}$$

(4.3)

where k in the above equation can have logic value of 0,1 &2. A NOR Gate, two NTIs, and one PTI make up the decoder circuit. This ternary decoder will be used in our half-adder circuit design.

Fig.4.3 Circuit Schematic of Ternary Decoder

Fig.4.4 Output Waveform of Ternary Decoder

# 4.3.1 Symbol for Ternary Decoder:

Fig.4.5 Ternary Decoder symbol Page **33** of **45**

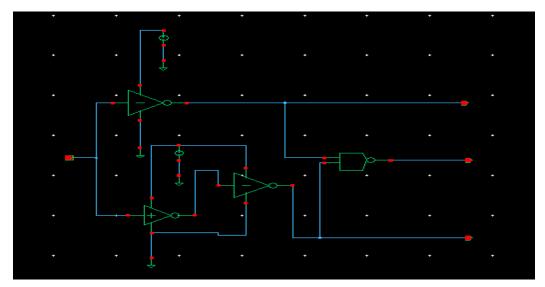

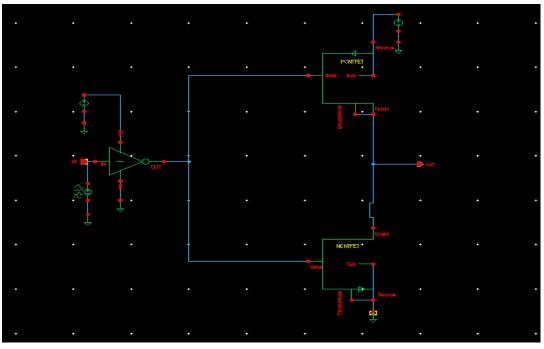

#### 4.4 TERNARY BUFFER:

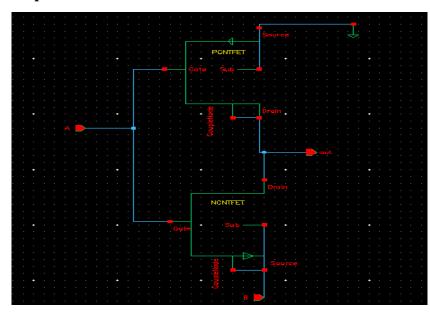

Ternary buffer (T- buffer) which is also called as level shifter. For the design of ternary buffer, we have used NCNTFET, PCNTFET and NTI. Input is given to NTI first and then the output of NTI is connected to the input of PCNTFET and NCNTFET [12]. The PCNTFET is provided with a supply voltage of 0.45V. The logic expression of Ternary Buffer is given by:

$$Out = \begin{cases} 1, & if in = 1,2 \\ 0, & if in = 0 \end{cases}$$

(4.4)

Fig.4.6 Circuit Schematic of Ternary Buffer

| Transient Response |      |                   |      |              |

|--------------------|------|-------------------|------|--------------|

| Name Vis           |      |                   |      | ۰ <b>۱</b> ۲ |

| - /N - 1.0         |      |                   |      |              |

| .75                |      |                   |      |              |

| S.5<br>.25         |      |                   |      |              |

| × .25              |      |                   |      |              |

| 0.0                |      |                   |      |              |

| 25<br>500.0        |      |                   |      |              |

| 400.0              |      |                   |      |              |

| 300.0              |      |                   |      |              |

| 200.0<br>>         |      |                   |      |              |

| 0.0                |      |                   |      |              |

| -100.0             |      |                   |      |              |

| 0.0                | 25.0 | 50.0<br>time (ns) | 75.0 | 100          |

Fig 4.7 Transient response of Ternary Buffer

In this design of ternary buffer, the input is given to an NTI, source of PCNTFET is connected to the supply of 0.45V. Both NCNTFET and PCNTFET have a chirality value of (19,0).

## 4.4.1 Symbol for Ternary Buffer

Fig.4.8 T-Buffer Symbol

## CHAPTER 5

## **RESULTS AND DISCUSSIONS**

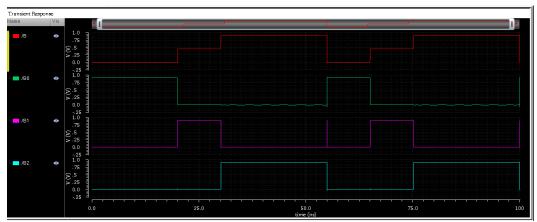

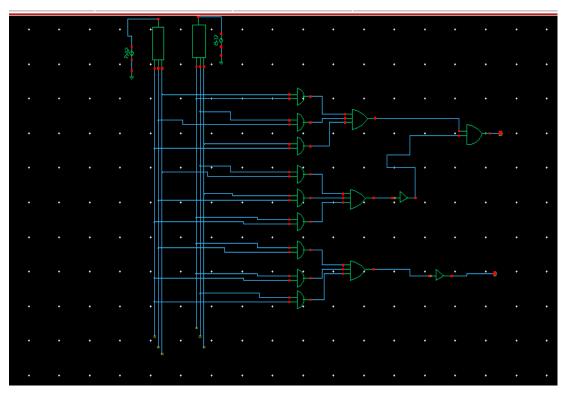

Now, we will integrate all the components together to design a half-adder. The proposed design of the HA and its output waveform is shown in the below figure6.1 and figure6.2. Ternary buffer, Ternary Decoder, and Ternary Logic Gates (AND, OR) are used in the HA design.

#### 5.1 SIMULATIONS

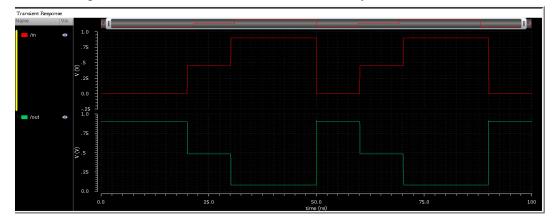

Fig. 5.1 Circuit Schematic of proposed Half Adder (HA)

Fig 5.2 Output Waveform of HA

This output waveform can be verified form the above truth table of HA. We have converted this half adder in the form of symbol, so that we can use it in other circuit design like Full adder etc.

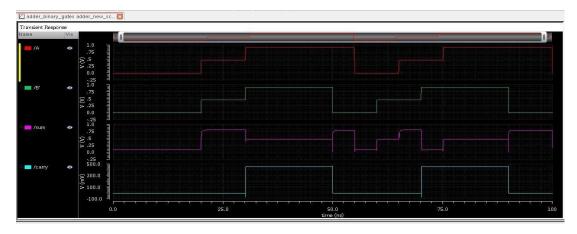

#### **5.2 RESULTS**

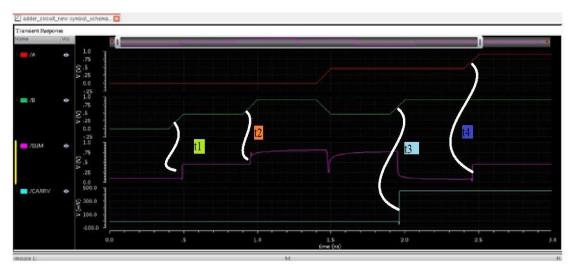

Fig.5.3 Waveform for delay calculation of proposed Half adder

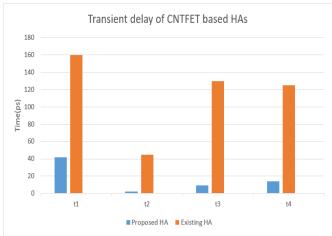

Measurements have been made of the transition delays of t1, t2, t3, and t4. For instance, t1 represents the time lag between input B's rising edge "0->1" and the output Sum's rising edge "0->1". When we compare these transition delays with the

existing transition delays of HA design, we find out that the delay of our design has been decreased. The circuit performs and speeds up because of this delay reduction. Below is a comparison of the current half adder design and the suggested HA design's delays:

Fig 5.4 Transient delay of CNTFET based HAs.

The average delay of the proposed design is calculated and multiplied by the average power dissipation to get PDP.

## Table.5.1 PDP of HAs

| Proposed design(J) | Existing design(J) [13] |

|--------------------|-------------------------|

| 0.045e-20          | 0.411e-15               |

Based on the analysis above, it can be said that the suggested HA design has a lower Power Delay Product (PDP). The GDI approach, which lowers the sub-threshold leakage current, is used in the suggested design to optimize PDP [32]. As a result, the GDI approach speeds up computational logic while reducing power, circuit complexity, and transistor count [10].

## CHAPTER 6

## **CONCLUSION AND FUTURE SCOPE**

A CNTFET-based design of a ternary adder based on the GDI technique has been implemented. The existing design is based on a ternary HA design when compared with the proposed design of HA it can be concluded that, this design reduces the chip area, and the circuit becomes faster as the number of transistor requirements is less in GDI-based logic gates.

The achieved result of low PDP can be used further in other digital integrated circuits. The simulation result of proposed design is achieved using Stanford CNTEFT model- Verilog A with 32nm technology using cadence virtuoso with the supply voltage of 0.9V.

Later, this Ternary based adder can be compared with the Quaternary based adder. Quaternary Logic uses four possible values compared to three is Ternary logic. This means that quaternary logic provides more possible combination of values and can therefore represent more complex data and operations. Some of the advantages of quaternary based adder are: Increased data density, Error Correction etc. Due to the increased number of states, quaternary logic can represent more data in smaller space, making it useful in some applications where storage is limited.

Also, quaternary logic offers better error correction capabilities that ternary logic. With four possible states, it can more easily detect and correct errors in data transmissions.

There are some drawbacks also in quaternary logic. A quaternary-based HA requires more logic gates than a ternary HA due to increased number of input states. This results in more complex and larger circuits. Due to increased number of logic gates required, a quaternary based HA may be slower in operation and require more power that ternary based HA.

## **PUBLICATIONS**

Anurag Chauhan and Richa Dubey, 2023. "CNTFET based design of Ternary Adders based on GDI technique". Proceedings of the 3<sup>rd</sup> International Conference on Innovative Mechanisms for Industry Applications (ICIMIA 2023), Bangaluru, December 21-23,

## **Certificate:**

| VPLORE COMPLIANT ISBN<br>979-8-3503-4363-2 | ŽIC                                             |                                         | ۲                                  |                             |

|--------------------------------------------|-------------------------------------------------|-----------------------------------------|------------------------------------|-----------------------------|

| <b>Certificate of Presentation</b>         |                                                 |                                         |                                    |                             |

|                                            | This certifice                                  | ite is awarded to                       |                                    |                             |

| Richa Dubey                                |                                                 |                                         |                                    |                             |

|                                            | for his/her paper p                             | resentation on the topic                |                                    |                             |

| CNTFET-bas                                 | ed Design of Terna                              | ry Adders based on                      | GDI Techniqi                       | ie                          |

| in the 3rd International                   | Conference on Innovation                        | ve Mechanisms for Indu                  | stry Applications                  | ICIMIA                      |

| Organized by Dayanando                     | ı Sagar College of Engi                         | neering, Bengaluru, Ind                 | ia on 21-23 Dece                   | mber-2023.                  |

| 2 Gatt.                                    | N.L.                                            | Ane                                     | Lung. v                            | E F                         |

| Session Chair                              | <b>Dr. Kiran A Gupta</b><br>Conference Co-Chair | Dr. Anju V Kulkarni<br>Conference Chair | <b>Dr. Suma V</b><br>General Chair | Dr. B G Prasad<br>Principal |

## Fee Receipt:

П

|               | Third International Conference on<br>Innovative Mechanisms for Industry Applications<br>ICIMIA 2023<br>21-23, December 2023<br>Bengaluru, India |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|               | Payment Receipt                                                                                                                                 |

| Receipt No    | ICIMIA-2023-008                                                                                                                                 |

| Article Title | CNTFET-based Design of Ternary Adders based on GDI Technique                                                                                    |

| Paid By       | Richa Dubey, Anurag Chauhan                                                                                                                     |

| Amount Paid   | ₹ 7,250/-<br>Rupees Seven Thousand Two Hundred and Fifty only                                                                                   |

#### **REFERENCES**

[1]. Pop, Eric; Dutta, Sumit; Estrada, David; Liao, Albert (2009). "Avalanche, joule breakdown and hysteresis in carbon nanotube transistors" (PDF). 2009 IEEE International Reliability Physics Symposium (IRPS 2009). p. 405.

[2]. J. Appenzeller, "Carbon nanotubes for high-performance electronics— Progress and prospect," Proc. IEEE, vol. 96, no. 2, pp. 201–211, Feb. 2008.

[3]. A. Rahman, J. Guo, S. Datta, and M. S. Lundstrom, "Theory of ballistic nano transistors," IEEE Trans. Electron Device, vol. 50, no. 10, pp. 1853–1864, Sep. 2003.

[4]. A. Akturk, G. Pennington, N. Goldsman, and A. Wickenden, "Electron transport and velocity oscillations in a carbon nanotube," IEEE Trans. Nanotechnology., vol. 6, no. 4, pp. 469–474, Jul. 2007.

[5]. H. Hashempour and F. Lombardi, "Device model for ballistic CNFETs using the first conducting band," IEEE Des. Test. Comput., vol. 25, no. 2, pp. 178–186, Mar./Apr. 2008.

[6]. E. Roosta and S. A. Hosseini, "A Novel Multiplexer-Based Quaternary Full Adder in Nanoelectronics," Circuits, Syst. Signal Process., vol. 38, no. 9, pp. 4056– 4078, 2019.

[7]. M. Kameyama, "TOWARD THE AGE OF' BEYOND BINARY ELECTRNICS Multiple- Valued Integrated Circuits in Hardware Algorithm Based Representation," no. 1, pp.1–5.

[8]. S.L. Hurst, Multiple-valued logic its status and its future, IEEE Transactions on computers 133 (1984) 1160-1179.

[9]. Ramzi A. Jaber, Ali M. Haidar and Abdullah Kassem, "CNTEFT based design of Ternary Multiplier using Only Multiplexers," 2020 32nd International Conference on Microelectronics (ICM).

[10]. A. Morgenshtein, A.Fish, and I. A. Wagner, "Gate-Diffusion Input (GDI): A Power- Efficient Method for Digital Combinatorial Circuits," IEEE Trans. VLSI Systems, Vol. 10, pp. 566- 581, Oct. 2002.

Page 42 of 45

[11]. Ebrahim Abiri, Mohammad Reza Salehi and Abdolreza Darabi, "Design and Evaluation of Low Power and High-speed Logic Circuits based on the Modified Gate Diffusion Input (m-GDI) Technique in 32nm CNTFET Technology," Iranian Conference on Electrical Engineering, May 2014.

[12]. Sheng Lin, Yong-Bin Kim and Fabrizio Lombardi, "CNTEFT- Based Design of Ternary logic Gates and Arithmetic Circuits," IEEE Transaction on Nanotechnology, vol. 10, no. 2, March 2011.

[13]. A. P. Dhande and V. T. Ingole, "Design & Implementation of 2-Bit Ternary ALU slice," in Proc. Int. Conf. IEEE-Sci. Electron., Technol. Inf. Telecommun., Mar. 2005, pp. 17–21.

[14]. M. Mukaidono, "Regular ternary logic functions—Ternary logic functions suitable for treating ambiguity," IEEE Trans. Comput., vol. C-35, no. 2, pp. 179–183, Feb. 1986.

[15]. "Ternary logic system based on T-gate," in Proc. 5th Int. Symp. Multiple-Valued Logic, Bloomington, IN, May 1975, pp. 290-304.

[16]. Multiple- Valued Logic, Charlotte, May 1977, pp. 120-124. H. T. Mouftah and K.C. Smith, "Design and implementation of three-valued logic systems with MOS integrated circuits," Proc. IEE, VO1. 127, pt. G, pp. 165-167, Aug. 1980.

[17]. "Injected voltage low-power CMOS for 3-valued logic," Proc. IEE, vol. 129, pt.G, pp. 270-272, Dec. 1982.

[18]. P. C. Balla and A. Antoniou, "Low power dissipation MOS ternary logic family," IEEE J. Solid-State Circuits, vol. 19, no. 5, pp. 739–749, Oct. 1984.

[19]. J. T. Butler and H. G. Kerkhoff, "Multiple-valued CCD circuits," IEEE Comput., vol. 21,no. 4, pp. 28–42, Apr. 1988.

[20]. P. Avouris, J. Appenzeller, V. Derycke, R. Martel, and S. Wind, "Carbon nanotube electronics," in Int. Electron Devices Meeting Tech. Dig., 2002, pp. 281–284.

[21]. A. Raychowdhury and K. Roy, "Carbon-nanotube-based voltage-mode multiple-valued logic design," IEEE Trans. Nanotechnol., vol. 4, no. 2, pp. 168–179, Mar. 2005.

#### Page 43 of 45

[22]. Shekhar Borkar," Design challenges of technology scaling,"0272-1732/99/\$10.00,1990IEEE.

[23]. Arkadiy Morgenshtein, Alexander Fish and Israel A Wagner, "Gate diffusion input (GDI)- a technique for low power design of digital circuits: analysis and characterization,"0-7803-7448-7/02/\$17.00,2002 IEEE.

[24]. Shofia Ram, Rooha Razmid Ahamed, —Comparison and analysisof combinational Circuits using Different logic styles IEEE – 31661, 4th ICCCNT – 2013, July 4 – 6- 2013, Tiruchengode, India.

[25]. G. Thrishala, K.Ragini" Design and Implementation of Ternary Logic Circuits for VLSI Applications" International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075 (Online), Volume-9 Issue-4, February 2020.

[26]. Kwan-Ho Kim,Hyung-Youl Park, Jaewoo Shim, Gicheol Shin,"A multiple negative differential resistance heterojunction device and its circuit application to ternary static random access memory."

[27]. "Ternary Logic circuits with CMOS integrated circuits" Hussein T. Moufah,3480 Havenwood Dr., Apt. 203, Mississauga, Ontario, Canada.

[28]. Article "Mosfet-symbol-working-operation-types-and-applications".

[29]. Sandeep Garg and Tarun K Gupta, "A Low leakage domino logic circuit for Wide Fan- in gates using CNTFET" IET Circuits, Devices & Systems, 0.1049/iet-cds.2018.5135.

[30]. J. Deng and H.-S. P. Wong, "A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—Part I: Model of the intrinsic channel region," IEEE Trans. Electron Device, vol. 54, no. 12, pp. 3186–3194, Dec. 2007.

[31]. Rafael Vargas-Berna and Gabriel Herrera-Prez, "Carbon Nanotube- and Graphene BasedDevices, Circuits and Sensors for VLSI Design."

[32]. CNTFET, Types, I-V Characteristics, Comparison of CNTFET with MOSFET,

https://www.learnelectronicswithme.com/

[33]. A. Morgenshtein, I. Shwartz, and A. Fish, "Gate Diffusion Input (GDI) Logic in Standard CMOS Nanoscale Process," IEEE 26th Convention of Electrical and Electronics Engineers in Israel (IEEEI), pp. 776-780, Nov. 2010.

[34]. D. A. Rich, "A survey of multivalued memories," IEEE Trans. Comput., vol. 35, no. 2, pp. 99–106, Feb. 1986.

PAPER NAME

# RICHA\_2K22\_VLS\_11\_Mtech\_thesis\_new 2\_removed.pdf

| WORD COUNT                     | CHARACTER COUNT                |

|--------------------------------|--------------------------------|

| 8797 Words                     | 44259 Characters               |

| PAGE COUNT                     | FILE SIZE                      |

| 45 Pages                       | 1.3MB                          |

| SUBMISSION DATE                | REPORT DATE                    |

| May 31, 2024 11:14 AM GMT+5:30 | May 31, 2024 11:15 AM GMT+5:30 |

## 17% Overall Similarity

The combined total of all matches, including overlapping sources, for each database.

- 11% Internet database

- Crossref database

- 11% Submitted Works database

# Excluded from Similarity Report

• Bibliographic material

- 14% Publications database

- Crossref Posted Content database