## TCAD SIMULATION BASED ANALYSIS OF TFET BASED ON DIFFERENT STRUCTURAL SHAPE: F-SHAPED AND Z-SHAPED

A PROJECT REPORT SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

## MASTERS OF SCIENCE IN PHYSICS

Submitted by: Muskaan (2K22/MSCPHY/26) Jyoti (2K22/MSCPHY/18)

Under the supervision of **Dr. Rishu Chaujar**

## DEPARTMENT OF APPLIED PHYSICS DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042 JUNE, 2024 DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **CANDIDATE'S DECLARATION**

We, Muskaan (2K22/MSCPHY/26) and Jyoti (2K22/MSCPHY/18) of MSc. (Physics), hereby declare that the project Dissertation titled "TCAD SIMULATION-BASED ANALYSIS OF TFET BASED ON DIFFERENT STRUCTURAL SHAPE: F-SHAPED AND Z-SHAPED" which is submitted by us to the Department of Applied Physics, Delhi Technological University, Delhi in partial fulfillment of requirement for the award of the degree of Master of Science, is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any degree, Diploma Associateship, Fellowship or other similar title or recognition.

Place: New Delhi Date: 7th June, 2024 Muskaan Jyoti

#### DECLARATION

We/I hereby certify that the work which is presented in the Major Project-II/Research Work entitled TCAD SIMULATION-BASED ANALYSIS OF TFET in fulfilment of the requirement for the award of the Degree of Bachelor/Mastercof Technology in <u>PH4SIL</u> and submitted to the Department of <u>APPLIED PH4SILS</u>, Delhi Technological University, Delhi is an authentic record of my/our own, carried out during a period from <u>2022-24</u>, under the supervision of <u>DT</u>. RISHU CHAUTAR.

The matter presented in this report/thesis has not been submitted by us/me for the award of any other degree of this or any other Institute/University. The work has been published/accepted/communicated in SCI/SCI expanded/SSCI/Scopus indexed journal OR peer reviewed Scopus indexed conference with the following details:

Title of the Paper: Author names (in sequence as per research paper): Name of Conference/Journal: Conference Dates with venue (if applicable): Have you registered for the conference (Yes/No)?: No. Status of paper (Accepted/Published/Communicated): Date of paper communication: Date of paper acceptance: Date of paper publication:

JHOTI 2K22/MSCPHY/18 2K22/MSCPHY/26 Student(s) Roll No., Name and Signature Jyoti MWS COMMS

#### SUPERVISOR CERTIFICATE

To the best of my knowledge, the above work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere. I, further certify that the publication and indexing information given by the students is correct.

Rchaufar

Supervisor Name and Signature

Place: New Delhi Date: 7th June, 24

NOTE: PLEASE ENCLOSE RESEARCH PAPER ACCEPTANCE/ PUBLICATION/COMMUNICATION PROOF ALONG WITH SCOPUS INDEXING PROOF (Conference Website OR Science Direct in case of Journal Publication).

## **DEPARTMENT OF APPLIED PHYSICS** DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **Abstract**

This work provides a thorough investigation of Z-shaped and F-shaped tunnel fieldeffect transistors (TFETs), emphasizing the unique structural characteristics and improved performance of these devices. With a architecture shaped like the letter "F," the F-shaped TFET provides better electrostatic control over the channel, improving tunnelling efficiency and raising on-current while preserving a competitive subthreshold swing. On the other hand, the Z-shaped TFET exhibits better control over the tunnelling junction due to its Z-like gate design, which lowers the subthreshold slope and lessens the impact of short channels. These sophisticated geometries are intended to overcome the drawbacks of traditional TFETs, including significant off-state leakage and inadequate on-current, thus positioning them as viable options for low-power and high-performance applications. It is anticipated that forthcoming developments will centre on enhancing material attributes, perfecting manufacturing methods, and investigating new device structures in order to augment the efficiency and expandability of these inventive TFET configurations. The findings of this study highlight the potential of Z-shaped and F-shaped TFETs in developing semiconductor technology and satisfying the needs of electronic gadgets of the future. Additionally, integrate these designs with newly developed materials and nanoscale manufacturing techniques.

## **ACKNOWLEDGEMENT**

We are extremely grateful to our project guide, **Dr. Rishu Chaujar**, Professor, Department of Applied Physics, Delhi Technological University, Delhi for providing invaluable guidance and being a constant source of inspiration throughout our research. We will always be grateful to her for the extensive support and encouragement.

We are extremely grateful to all the panel members who evaluated our progress, guided us throughout our project, and gave us constant support and motivation, innovative ideas and all the information that we needed to pursue this project.

MUSKAAN 2K22/MSCPHY/26 JYOTI 2K22/MSCPHY/18

## LIST OF CONTENTS

| Candidate's Declaration                                   | ii   |

|-----------------------------------------------------------|------|

| Certificate                                               | iii  |

| Abstract                                                  | iv   |

| Acknowledgement                                           | v    |

| List Of Contents                                          | vi   |

| List Of Tables                                            | ix   |

| List Of Abbreviations                                     | x    |

| List Of Figures                                           | xi   |

| CHAPTER 1: INTRODUCTION                                   | xii  |

| 1.1 Field- Effect Transistor (FET)                        | xii  |

| 1.2 CMOS Technology                                       | xiii |

| 1.3 TFET                                                  | xiii |

| CHAPTER 2: Overview of SILVACO Atlas Simulation Framework | xv   |

| 2.1 Introduction                                          | xv   |

| 2.2 Overview of SILVACON Atlas                            | xvi  |

| 2.3 Structure simulation                                  | xvii |

| 2.4 2D-TFET proposed Design                               | xvii |

| CHAPTER 3: Tunnel Field-Effect Transistors        | xix    |

|---------------------------------------------------|--------|

| 3.1 An Overview                                   | xix    |

| 3.2 Fundamentals of Functions                     | XX     |

| 3.3 Historical Developments of TFETs              | XX     |

| 3.3.1 Early concepts and theoretical foundations  |        |

| 3.3.2 Initial ideas and early technology          |        |

| 3.3.3 Advancements in materials and device design |        |

| 3.3.4 Modern developments and applications        |        |

| 3.4. Key Points about TFETs                       | xxi    |

| 3.5 On the basis of shape                         | xxii   |

| 3.6. Applications                                 | xxii   |

| 3.7. Challenges                                   | xxii   |

| 3.8. Advantages                                   | xxiii  |

| 3.9. Vision for the Future                        | xxiii  |

| CHAPTER 4: F-Shaped TFET                          | xxiv   |

| 4.1. Introduction                                 | xxiv   |

| 4.2. Structure                                    | XXV    |

| 4.3. Advantages                                   | xxvi   |

| 4.4. F-shaped over conventional ones              | xxvii  |

| 4.5. Applications                                 | xxviii |

| 4.6 Challenges                                    | xxviii |

## CHAPTER 5: Z-Shaped TFET

xxix

| 5.1. Introduction                                 | xxix  |

|---------------------------------------------------|-------|

| 5.2. Structure                                    | XXX   |

| 5.3. Advantages                                   | xxxi  |

| 5.4. Source stacking over regular source building | xxxi  |

| 5.5. Z-shaped over conventional TFETs             | xxxii |

| 5.6. Z-shaped over F-shaped TFETs                 | xxxiv |

| 5.7. Applications                                 | xxxiv |

| 5.8. Challenges                                   | xxxiv |

|                                                   |       |

| CHAPTER 6: RESULTS AND CONCLUSIONS                | xxxvi |

| 6.1. Analysis of 2D F-shaped TFET                 | xxxvi |

| 6.2. Analysis of 2D Z-shaped TFET                 | xl    |

| 6.3. Conclusions                                  | xlv   |

| 6.4. Future directions                            | xlvi  |

## REFERENCES

## **PLAGIARISM REPORT**

## **LIST OF TABLES**

<u>Table 1:</u> A description of the fundamental design parameters used in the TCAD simulation.

<u>Table 2:</u> List of parameters considered in the device simulation process

## **List of Abbrevations**

#### **Abbreviations**

IC- Integrated Circuit

FET- Field Effect Transistor

MOSFET- Metal Oxide Semiconductor Field Effect Transistor

CMOS- Complementary Metal-Oxide Semiconductor

FINFET- Fin Field Effect Transistor

VLSI- Very Large-Scale Integration

IGFET- Insulated-Gate Field-Effect Transistor

E-device – Enhancement mode device

D-device – Depletion mode device

SCE- Short Channel Effect

DIBL- Drain-Induced Barrier Lowering

SS- Subthreshold swing

**RF-** Radio frequency

TFET- Tunnel field effect transistor

BTBT- Band to band tunneling

TCAD- Technology computer aided device

GUI- Graphical user interface

G<sub>m</sub>- Transconductance

T<sub>GF</sub>- Transconductance generating Factor

### **Symbols**

- V<sub>ds</sub> Drain voltage

- V<sub>gs</sub> Gate voltage

V<sub>th</sub> - Threshold voltage

Ids - Drain Current

V<sub>p</sub> – Punchthrough voltag

## **LIST OF FIGURES**

| Figure 2.1: The simulation flow of Atlas                                            | 16 |

|-------------------------------------------------------------------------------------|----|

| Figure 2.2: Showing the groups and statements for the SILVACO ATLAS TCAD simulation | 17 |

| Figure 4.1: The structure of the F-shaped TFET includes multiple sources.           | 24 |

| Figure 4.2 Structure and parameter definitions of the F-shaped TFET                 | 25 |

| Figure 4.3: Single-gate F-shaped TFET (SG-F-TFET) with TOX = 1 nm                   | 28 |

| Figure 5.1: 2-D front view of Z-shaped gate TFET                                    | 30 |

|                                                                                     |    |

Figure 5.2: Tunneling width and footprint of proposed ZG-TFET. 34

# Chapter-1

## Introduction

### 1.1 Field-Effect Transistor (FET):

FET has three terminals, namely the source, gate, and drain. There are two main types of FETs: MOSFET (Metal-Oxide-Semiconductor FET) and JFET (Junction Field-Effect Transistor). An electric field applied across the semiconductor material drives a FET's ability to control current flow. The MOSFET's gate terminal voltage controls the current flow between its source and drain terminals. Without input current, JFETs function by enabling current flow between the source and drain terminals when a voltage is applied to the gate terminal. Because of its high input impedance and voltage control, FETs are a good choice for applications where the input signal level is critical. Generally, FETs have slower switching speeds compared to BJTs, especially in the case of JFETs. However, MOSFETs can have very fast switching speeds, rivaling or surpassing BJTs. FETs, particularly MOSFETs, are known for their low power consumption, especially in static (non-switching) states. BJTs are commonly used in applications requiring moderate to high current amplification, such as audio amplifiers. FETs, especially MOSFETs, are widely used in integrated circuits, digital applications, and situations where high input impedance and low power consumption are essential.

#### <u>1.2 CMOS Technology:</u>

CMOS (Complementary Metal-Oxide-Semiconductor) technology is often used semiconductor manufacturing process that plays a key role in the production of ICs such as microprocessors, memory chips, and other digital logic devices. The term "complementary" refers to the use of both n-type (negatively-doped) and p-type (positively-doped) MOSFETs within the identical integrated circuit. CMOS technology relies on the basic structure of MOSFETs. A small layer of insulating oxide separates the semiconductor from the metal gate of a MOSFET. The semiconductor material is typically silicon. CMOS circuits use both N-channel MOSFETs (NMOS) and P-channel MOSFETs (PMOS) [1]. When a positive voltage is provided to the gate of an NMOS transistor, electrons can go from the source to the drain.

When a negative voltage is given to the gate of a PMOS transistor, holes can move from the source to the drain. The use of both types of MOSFETs allows for complementary operation, where one type of transistor is off while the other is on, minimizing power consumption and heat generation. The low power consumption of CMOS technology is one of its main benefits. This is because CMOS circuits draw negligible current when they are in a static state (not switching), making them highly energy-efficient. CMOS circuits have high noise immunity due to the complementary operation.

When one transistor is off, the other is on, reducing the risk of signal corruption by noise. CMOS technology is highly scalable, allowing for the incorporation of several transistors on a single chip. This scalability has been a driving force in the miniaturization and increasing complexity of electronic devices. CMOS is versatile and is used in both digital and analog applications. It is commonly found in microprocessors, memory chips, image sensors, and other digital circuits.

The fabrication process involves creating patterns on a silicon wafer through photolithography, deposition, and etching. The process includes creating NMOS and PMOS transistors, interconnecting them with metal layers, and adding insulating layers. CMOS technology is prevalent in a variety of electronic devices, such as digital cameras, smartphones, laptops, and numerous other digital systems.

#### <u>1.3 TFET</u>

A transistor type that functions according to the principles of quantum tunneling is called a TFET. TFETs take advantage of quantum tunneling across a thin barrier [2], in contrast to conventional transistors, which depend on thermionic emission of carriers over a potential barrier. Compared to conventional MOSFETs, TFETs can achieve reduced power consumption and possibly higher switching speeds thanks to their unique operating principle.

The TFET makes use of a phenomenon known as quantum tunneling, which allows particles to cross potential energy barriers that would be impossible in classical physics. When it comes to TFETs, electrons travel between the source and drain terminals by tunneling across a tiny barrier. TFETs have the ability to drastically lower an electrical device's power usage. Because tunneling is used for carrier transport rather than thermal emission, TFETs can function at lower voltages, which lower energy dissipation. Theoretically, TFETs' distinct tunneling mechanism can lead to quicker switching speeds than MOSFETs'. For situations where high-speed operation is essential, this feature is beneficial.

Increases in SCEs, off-leakage current, and subthreshold swing have been observed in MOSFETs that have been downscaled. MOSFETs have a minimal subthreshold swing of 60 mV/dec at normal temperature. For the deep submicron domain, MOSFET is hence unsuitable. The drawbacks of MOSFETs are being examined by means of a new device construction. The newest and most advanced device is the TFET. Because of their superior performance—low power dissipation, low leakage current, and SS of less than 60 mV/dec, TFETs are the best option for low power applications [3]. High Ioff current is mostly caused by the ambipolar effect, which can be mitigated by structural asymmetry and different levels of doping in the source and drain. This could lead to a decrease in the TFET's Ioff current and an increase in the Ion/Ioff current ratio. Basic p-i-n structures, TFETs operate on the principle of BTBT and have reversed bias at the gate terminal. Low Ion current also affects TFET's fundamental structure. Nonetheless, the Ion current can be further enhanced by changing the structural physical characteristics.

## Chapter-2

## Overview of the SILVACO Atlas Simulation Framework

#### 2.1 Introduction

A significant part of today's semiconductor device and process development is conducted through computer modeling. This method is known as TCAD. Technology computer aided design is a category of electronic design automation that simulates the manufacturing of semiconductors and the functioning of semiconductor devices. Process TCAD refers to the modeling of the fabrication process, whereas Device TCAD refers to the modeling of the device's functionality. A strong and adaptable tool that is frequently used in the modeling and simulation of semiconductor devices is the SILVACO Atlas simulation framework. Strong meshing capabilities are provided by SILVACO Atlas, giving users control over the mesh's density and quality. Accurate simulation results require proper meshing, particularly when working with complicated device geometries. The software offers an input deck (scripting language) for configuring simulations, and Tony Plot and other GUI (Graphical User Interface) features make it easier to visualize the results. SILVACO uses sophisticated physics models to simulate semiconductor behavior precisely. This ensures that simulations correspond with the behavior of real-world devices. It includes models for carrier transport, tunneling, and several other physical phenomena. This chapter delves into the salient characteristics and functionalities of SILVACO Atlas, with a particular emphasis on its utilization in our research on MOSFETs, DGMOSFETs and TFETs.

#### 2.2 Overview of SILVACO Atlas

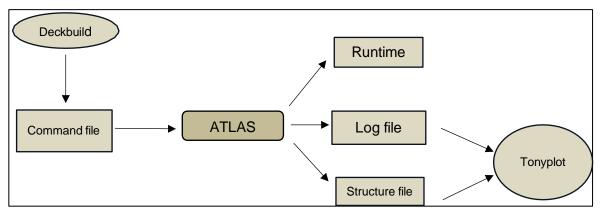

We may simulate and examine the behavior of semiconductor devices at the nanoscale with the help of SILVACO Atlas, a complete device simulation program. It has the capability of simulating the two-dimensional (2D) [4] and three-dimensional (3D) semiconductor devices and helps to predict the energy band gaps, electrical properties, some factors like DIBL, SS etc. It provides a variety of simulation functionalities, such as circuit, device, and process simulation. The program is compatible with a number of semiconductor technologies, including CMOS technology, which makes it appropriate for a broad variety of applications. The physical structures and bias conditions of semiconductor devices are given by ATLAS, which offers physics-based simulation of these devices. Deck build is an interactive visual runtime environment that we have used to construct input decks for the device simulation process. Two different file kinds that we employed are included in the output. structure files and log files. An image of the device at a specific bias voltage is provided by the structure file (.str). Additionally, the terminal features determined by ATLAS are stored in the log file (.log). Tony plot can be used to plot either of these. SILVACO Atlas receives input files through Deck Build. The code in the input file initiates Atlas to run using the commands detailed in section 2.3. After that command, the input file must follow a specific pattern. The command groups are listed in the next section.

Fig 2.1: The simulation flow of Atlas

## 2.3 Structure simulation

The Atlas has a specified way of writing commands as any other software do have. By following the set of commands with primary statements, we have simulated the two-dimensional MOSFET and two dimensional DGMOSFET and TFET.

| Group                            |            | Statements                                 |

|----------------------------------|------------|--------------------------------------------|

| 1. Structure Specification       |            | MESH<br>REGION<br>ELECTRODE<br>DOPING      |

| 2. Material Models Specification |            | MATERIAL<br>MODELS<br>CONTACT<br>INTERFACE |

| 3. Numerical Method Selection    | <u> </u>   | METHOD                                     |

| 4. Solution Specification        | , <u> </u> | LOG<br>SOLVE<br>LOAD<br>SAVE               |

| 5. Results Analysis              | °3         | EXTRACT<br>TONYPLOT                        |

Fig2.2: Showing the groups and statements for the SILVACO ATLAS TCAD simulation

### 2.4. 2D TFET proposed design

On the same tracks we have simulated the basic 2D TFET with length of the structure 0.11 micrometers. The quantum tunnelling meshing is defined. The source and drain are taken to be of silicon with doping  $1e^{+20}$  each. The gate is taken of SiO<sub>2</sub>. The n body of  $1e^{+18}$  doping of silicon is use as channel body [6]. The ferroelectric material region is defined the silver metal with work function 4.07 eV have been used for gate and source and drain are taken as neutrals. mh.tunnel and me.tunnel are 0.24 and 0.20 respectively. For DC analysis, drain voltage is provided as 0V to 1V with the step of

0.1. And for the AC analysis, the ac frequency of  $1e^{6}$  HZ is given with the input voltage of 0 Volts to -1 Volts with the step size of -0.1. Then, some of the parameters has been extracted using extract command like DIBL, Subthreshold voltage,  $I_{on}$  and  $I_{off}$  and their ratio.

## **Chapter 3**

## **Tunnel Field-Effect Transistors**

### 3.1 Tunnel Field-Effect Transistors (TFETs): An Overview

Unlike conventional FETs, which rely on thermionic emission, tunnel field-effect transistors (TFETs) use quantum tunneling to achieve current conduction. Electrons can tunnel through a barrier in a TFET from the source to the drain when a voltage is applied to the gate, which modifies the barrier width at the source-channel junction. Because of their tunneling process, TFETs can function at lower voltages than traditional MOSFETs, which could result in a reduction in power usage. TFETs are viewed as promising prospects for low-power and high-efficiency electronic applications, such as next-generation integrated circuits and low-power logic devices, because to their sharp subthreshold swing and potential for reduced off-state current. Nevertheless, difficulties including enhancing material qualities, enhancing on-current, and manufacturing.In contrast to traditional MOSFETs, which depend on thermionic emission, tunneling is utilized by TFETs, enabling them to attain subthreshold slopes that are steeper than the 60 mV/decade limit. TFETs are therefore excellent options for low-power electrical applications.

Unlike conventional Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs), tunnel field-effect transistors (TFETs) are a sophisticated family of transistors that use quantum mechanical tunneling to achieve charge carrier transport.

#### 3.2 Fundamentals of Function

Band-to-band tunneling is the basis of operation for TFETs (BTBT). One type of carrier, such as p-type, is extensively doped in the source of a TFET, while the drain is heavily doped with the opposite type, such as n-type. The potential barrier width between the source and the channel is modulated when a voltage is applied to the gate. Current can flow when this barrier narrows to the extent that electrons can tunnel from the valence band of the source to the conduction band of the channel.

#### 3.3 Historical Development of TFETs:

3.3.1 Early Concepts and Theoretical Foundations:

The 1950s and 1960s were when the fundamental ideas of tunneling in semiconductors were developed. The Esaki diode, a crucial development for comprehending quantum tunneling in semiconductors, was created as a result of Leo Esaki's discovery of tunneling processes. Researchers started to suggest employing tunneling for switching devices by the 1970s, claiming that it may allow for high subthreshold slopes and lower power consumption than conventional FETs.

#### 3.3.2 Initial Ideas and Early Technology:

The first theoretical suggestions for TFETs were made in the 1980s. Band-to-band tunneling for transistors was first studied, but there were few real-world applications and it was mostly theoretical. The viability of TFETs was demonstrated experimentally in the 1990s, overcoming obstacles including low on-current and fabrication issues.

3.3.3 Advancements in Materials and Device Design:

The twenty-first century saw significant advancements in nanofabrication techniques and materials science. To improve TFET performance, researchers experimented with a variety of semiconductor materials, such as silicon, germanium, and III-V compounds. The low-power potential of silicon-based TFETs was highlighted in 2004 when the first ones showed subthreshold slopes < 60 mV/decade. By 2006, tunneling junction performance had been improved by novel

device topologies such as heterojunction TFETs. All these advancements in design and material design leads to certain advantages despite of giving some cons has been effectively using in day to day market. 3.3.4 Modern Developments and Applications:

During the 2010s, the emphasis switched to circuit integration and TFET optimization for particular uses. Nanotechnology developments produced TFET designs that were more scalable and efficient. The demonstration of record-low subthreshold swings in 2012 and the proposal of hybrid TFET-CMOS circuits in 2015, which combine the lowpower advantages of TFETs with the excellent performance of CMOS technology, are noteworthy turning points in the field. Research to address issues such as low oncurrent and variability has been going on in the 2020s, and TFETs are being explored for use in wearable electronics, energy-efficient computing, and the Internet of Things (IoT).

## 3.4 Key Points about TFETs:

- Principle of Operation: To modify current flow, TFETs use tunneling through a barrier that is controlled by gate voltage.

- Low Power Consumption: By operating at a lower voltage than MOSFETs, TFETs can drastically cut down on the amount of power used in digital circuits.

- Subthreshold Swing (SS): TFETs can attain subthreshold swing (SS) values that are lower than the 60 mV/decade limit, which improves their low-power efficiency.

- Materials and Design: TFETs can be made from a variety of materials, such as III-V compounds, silicon, and germanium, which can affect the device's overall efficiency, off-state leakage, and on-state current.

### 3.5 On the basis of different channel shapes:

In Tunnel Field-Effect Transistors (TFETs), the channel shape can significantly impact the device's performance. Different alphabetical channel shapes are designed to optimize various aspects of the TFET's operation, such as threshold voltage, subthreshold slope, and drive current. Some of these are:-

1. U-shaped

- 2. V-shaped

- 3. H-shaped

- 4. L-shaped

- 5. F-shaped

- 6. Z-shaped

## 3.6 Applications:

Energy-efficient integrated circuits, analog and radio frequency circuits, and lowpower digital circuits are all excellent uses for TFETs.

TFETs are promising in several areas, especially when low power consumption is essential.

- Portable Electronics: The energy efficiency of TFETs can be advantageous for wearables, tablets, and smartphones.

- IoT, or the Internet of Things: TFET technology can help low-power sensors and gadgets in Internet of Things networks last longer on batteries and use less energy.

- Biomedical Devices: TFET integration can be advantageous for wearable and implantable medical devices that have low power requirements.

## 3.7 Challenges:

Although TFETs have great potential, they encounter obstacles including low oncurrent, unpredictability, and fabrication complexity. To solve these problems, research is still being done.

• On-Current (<u>IoN</u>): TFETs' performance in high-speed applications may be constrained by their generally lower I<sub>ON</sub> than MOSFETs.

- Issues with Materials and Fabrication: It is difficult to find the ideal material composition and device architecture for effective tunneling. This involves the requirement for accurate doping profiles and superior heterojunctions.

- Thermal Stability: As device dimensions decrease, it becomes increasingly important to ensure thermal stability and control heat dissipation in TFETs.

### 3.8 Advantages:

- Low Subthreshold Swing (SS): Unlike conventional MOSFETs, TFETs can achieve a subthreshold swing below the thermal limit of 60 mV/decade at ambient temperature. As a result, lower threshold voltages and hence lower power consumption are possible.

- Low Power Consumption: TFETs are ideally suited for low-power applications because of their effective switching properties, which make them perfect for energy-efficient and portable devices.

- High Scalability: It may be possible to scale down TFETs more efficiently than MOSFETs, enabling Moore's Law-compliant device downsizing.

## <u>3.9 Visions for the Future</u>:

To improve TFET performance; current research is concentrated on investigating novel materials such as 2D materials (such as graphene and transition metal dichalcogenides) and creative device topologies. Although TFETs are not currently commonly used in commercial goods, recent developments indicate that they may be important in low-power electronics in the future as power efficiency becomes more and more important and technology continues to scale down. Both theoretical and practical developments have fueled the constant quest for more efficient electronic devices, which is reflected in the history and current development of TFETs. TFETs have the potential to completely transform the semiconductor industry by allowing extremely energy-efficient electronic products

## **Chapter 4**

## **F-Shaped TFET**

#### 4.1 Introduction

An F-shaped Tunnel Field-Effect Transistor is a type of TFET where the channel geometry is shaped like the letter "F." With its unique F-shaped gate architecture, the F-shaped Tunnel Field-Effect Transistor (F-TFET) is a revolutionary design in the field of TFETs. By increasing electrostatic control over the channel, this design seeks to improve subthreshold swing and on-current (Ion), two important performance criteria for the device. The F-shaped gate provides improved control over the carrier injection from the source to the channel by enabling a more effective modification of the tunneling barrier. The F-TFET is a desirable choice for low-power applications because of its enhanced control, which can result in lower off-state currents and lower power consumption. Furthermore, the F-TFET's distinct geometry may be able to lessen some of the fabrication difficulties that come with conventional TFETs, providing a more scalable and producible alternative for upcoming semiconductor technologies.

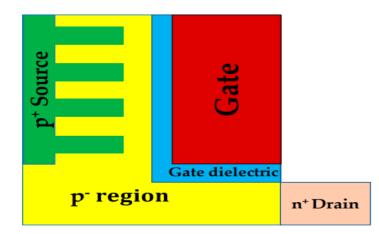

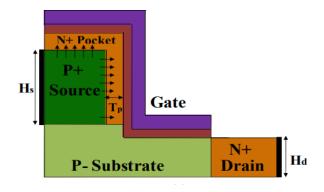

Fig. 4.1: The structure of the F-shaped TFET includes multiple sources.

By utilizing its distinct shape, this design seeks to improve a few of the TFET's performance attributes. An extensive examination of the F-shaped TFET's structure, benefits, possible uses, and difficulties is provided below.

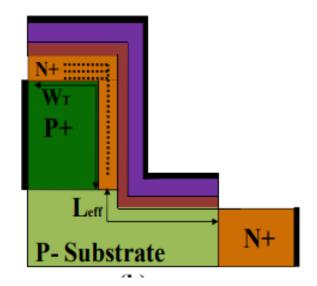

#### 4.2 Structure

The channel of the F-shaped TFET is made up of several horizontal and vertical segments that form the letter "F." The device's overall performance may be enhanced by the many tunneling junctions that this complicated design may produce. Usually, the structure consists of:

Vertical Segments: Band-to-band tunneling mostly takes place along these segments, which act as conduction pathways.

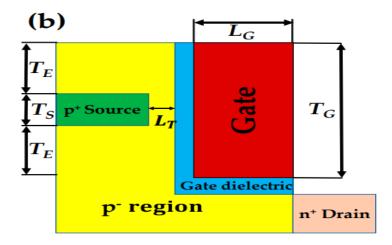

Fig. 4.2: Structure and parameter definitions of the F-shaped TFET

Horizontal Segments: Connecting vertical channels horizontally can aid in dispersing current, lowering resistance and enhancing drive current overall.

| Parameters                     | Abbreviations        | SG-F-TFET                |

|--------------------------------|----------------------|--------------------------|

| Gate oxide thickness           | T <sub>OX</sub>      | 1nm                      |

| Gate oxide material (k-value)  | -                    | SiO <sub>2</sub> (k=3.9) |

| Total device length            | L <sub>tt</sub>      | 160 nm                   |

| Thickness above and below      | T <sub>2</sub>       | Variable (12.5 nm)       |

| source                         |                      |                          |

| Channel thickness at bottom of | $T_1 = T_D + T_{OX}$ | 7 nm                     |

| device                         |                      |                          |

| Total device thickness         | T <sub>tt</sub>      | 42 nm                    |

| Lateral tunneling length       | LT                   | Variable (4 nm)          |

| Source thickness               | Ts                   | Variable (10 nm)         |

| Source length                  | Ls                   | Variable (67 nm)         |

| Gate length                    | L <sub>G</sub>       | 20 nm                    |

| Gate thickness                 | $T_G = 2T_2 + T_S$   | 35 nm                    |

| Channel thickness              | $2T_2 + T_1 + T_S$   | 42nm                     |

| Channel length (upper)         | L <sub>C1</sub>      | 71 nm                    |

| Channel length (bottom)        | Lc                   | 92 nm                    |

| Drain length                   | LD                   | 68 nm                    |

| Drain thickness                | T <sub>D</sub>       | 6nm                      |

| Gate work-function             | WF <sub>G</sub>      | 4.5 eV                   |

| N-type drain doping            | N <sub>D</sub>       | 1018 cm <sup>-3</sup>    |

| concentration                  |                      |                          |

| P-type channel doping          | N <sub>C</sub>       | 1015 cm <sup>-3</sup>    |

| concentration                  |                      |                          |

| P-type source doping           | Ns                   | $1020 \text{ cm}^{-3}$   |

| concentration                  |                      |                          |

<u>Table 1:</u> A description of the fundamental design parameters utilized in TCAD simulations.

### 4.3 Advantages

<u>Multiple Tunneling Junctions</u>: By offering various parallel pathways for current conduction, multiple tunneling junctions, which the F-shaped design can include, can improve the on-current.

<u>Better Electrostatic Control</u>: By exerting more electrostatic control over the vertical segments, the extra horizontal segments can enhance the subthreshold swing and switching properties.

<u>Enhanced Current Drive</u>: By making better use of the available device area, the design may be able to enhance the drive current without appreciably expanding the footprint.

<u>Flexibility in Design</u>: The F-shaped structure is adaptable and versatile for a range of applications since it can be tuned for multiple performance criteria.

### 4.4 Why F-Shaped TFETs better than Conventional TFETs?

Fig. 4.3: Single-gate F-shaped TFET (SG-F-TFET) with TOX = 1 nm

The F-shaped enhances the gate's control over the channel by incorporating numerous bends and segments. This improves device performance and reduces shortchannel effects. Increased scalability due to better electrostatic control enables smaller devices with the same functionality.

The geometry of the F-shaped channel allows for the incorporation of multiple tunneling junctions.

Compared to conventional TFETs, which usually feature a single tunneling area, this increases the total current flow across the device, potentially lowering the threshold voltage and improving the on-state current.

An F-shaped TFET's complex pathway can produce areas with different electric field strengths, which aids in achieving a steeper subthreshold swing which enhances the device's switching capabilities. This allows for quicker transitions between the off and on states, making it essential for low-power applications. Enhanced channel control and various tunneling areas contribute to more effective leakage current suppression, which improves off-state performance, lowers power consumption, and increases the device's energy efficiency.

### 4.5 Applications

- <u>High-Performance Digital Circuits:</u> F-shaped TFETs are suited for high-speed, low-power digital circuits due to their superior switching properties and increased current drive.

- <u>Analog and RF Circuits</u>: Whereas linearity and noise performance are critical, the enhanced electrostatic control and numerous conduction routes can help these circuits.

- <u>Low-Power Devices</u>: F-shaped TFETs are perfect for low-power applications like wearable electronics and Internet of Things devices because they can function effectively at low voltages.

### 4.6 Challenges

<u>Complex Fabrication</u>: It may be difficult to create complex F-shaped geometry using conventional lithography and etching procedures, which could raise manufacturing costs.

<u>Device Variability</u>: Because of the intricacy of the design, it can be difficult to guarantee consistent performance across several F-shaped TFETs. This could lead to manufacturing variability.

<u>Integration with Existing Technologies:</u> Integrating F-shaped TFETs with existing CMOS processes requires careful consideration of process compatibility and device architecture.

## **Chapter 5**

## **Z-Shaped TFET**

### 5.1 Introduction

A Z-shaped Tunnel Field-Effect Transistor is a type of TFET where the channel geometry is shaped like the letter "Z." The purpose of this innovative design is to improve the TFET's performance characteristics for particular applications. With a Z-shaped channel structure that improves its electrical properties, the Z-shaped Tunnel Field-Effect Transistor (Z-TFET) is a cutting-edge TFET design. Superior electrostatic control over the channel region is made possible by this unique Z-shaped design, which also enhances the efficiency of the carrier injection process by adjusting the tunnelling barrier. In order to achieve low-power and high-performance operation, the Z-TFET design offers greater on-current (ION) and a steeper subthreshold swing, which solves some of the intrinsic constraints of conventional TFETs. Additionally, the Z-shaped gate topology helps to increase switching rates and reduce leakage currents. Due to these advancements, Z-TFETs are especially well suited for low-power electronics and next-generation integrated circuit applications, where downsizing and energy efficiency are critical requirements.

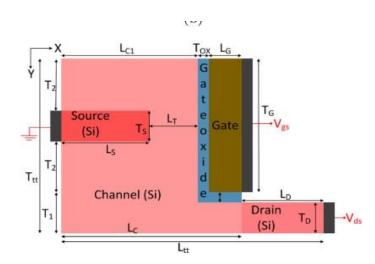

Fig. 5.1: 2-D front view of Z-shaped gate TFET

## 5.2 Structure

The Z-shaped TFET has a channel made up of alternating vertical and horizontal segments that zigzag like the letter "Z." The device's performance may be enhanced by the numerous tunneling junctions that this design produces along the channel.

Band-to-band tunneling mostly takes place along vertical segments, which act as conduction pathways.

Segments that connect vertical channels horizontally can aid in dispersing current, lowering resistance, and enhancing drive current overall.

| Parameters                 | Abbreviations                  | Z- shaped TFET                 |

|----------------------------|--------------------------------|--------------------------------|

| Channel length             | L <sub>ch</sub>                | 25 nm                          |

| Source and drain lengths   | L <sub>s</sub> /L <sub>d</sub> | 30nm                           |

| Gate work-function         | φ                              | 4.20 eV                        |

| Source doping (p+)         | Ns                             | 1e20 cm <sup>-3</sup>          |

| Drain doping (n+)          | Nd                             | 5e18 cm <sup>-3</sup>          |

| Channel doping (intrinsic) | Nch                            | 1e16 cm <sup>-3</sup>          |

| Gate oxide thickness       | t <sub>ox</sub>                | 1 nm                           |

| Silicon body thickness     | t <sub>si</sub>                | 10 nm                          |

| Front gate length          | L <sub>fg</sub>                | 30 nm                          |

| Back gate length           | L <sub>bg</sub>                | 25 nm                          |

| Drain voltage              | V <sub>ds</sub>                | 1.0 V                          |

| Gate voltage               | V <sub>gs</sub>                | (- 1.0 to 1.5) (- 1.0 to 1.5)V |

<u>Table 2:</u> List of parameters considered in the device simulation process

5.3 Advantages

<u>Multiple Tunneling Junctions:</u> By offering several parallel routes for current conduction, the Z-shaped design permits multiple tunneling junctions, which may

improve the on-current.

<u>Enhanced Electrostatic Control:</u> The extra horizontal segments can enhance gate control over the vertical segments, resulting in improved subthreshold swing and switching characteristics.

<u>Enhanced Current Drive</u>: By making the best use of available space, the zigzag construction may be able to raise the drive current without appreciably expanding the device's footprint.

<u>Reduced Short-Channel Effects:</u> To preserve performance in ultra-scaled devices, the zigzag structure can aid in reducing short-channel effects.

# 5.4 The advantages of source stacking compared to regular source building.

When several source regions are stacked vertically in a TFET design, it is called source stacking. Compared to conventional single-source TFETs, this design provides the following advantages:

<u>Enhanced Tunneling Area</u>: By increasing the tunneling area, source stacking makes it possible for multiple tunneling events to take place at once. This may lead to increase on-currents, which would enhance the TFET's overall performance.

<u>Reduced Series Resistance:</u> By stacking sources, the device's effective series resistance is decreased. Improved energy economy and quicker switching rates are the results of lower series resistance.

<u>Improved Subthreshold Slope:</u> In low-power applications where reducing leakage current is essential, a steeper subthreshold slope may result from the expanded tunneling area.

<u>Increased Current Density</u>: By increasing the TFET's current density, source stacking makes it possible for the device to carry more current in less space.

<u>Enhanced Control Over Threshold Voltage</u>: Designers can modify TFETs for particular applications by manipulating the threshold voltage by changing the number of stacked sources or the doping levels.

<u>Compatibility with Existing Processes:</u> Source stacking is compatible with current manufacturing processes since it can be done using common semiconductor fabrication.

### 5.5 Why are Z-shaped preferable to conventional TFETs?

<u>Improved Tunneling Efficiency</u>: There are several sudden direction changes and severe bends in the Z-shaped channel. Carriers have a higher chance of tunneling via these steep bends because they can produce regions with strong electric field gradients. When compared to the linear channels found in conventional TFETs, this may lead to a more effective tunneling process.

<u>Improved Subthreshold Swing (SS)</u>: Because of the Z-shaped channel's unique geometry, it is possible to obtain steeper subthreshold swings, which improves the device's ability to convert from an off to an on state. This results in faster switching rates and lower power consumption in low-power applications.

<u>Reduced Leakage Current:</u> Better electrostatic control over the channel can be achieved by the Z-shaped design, which can assist in suppressing leakage currents

during the off state. This improves power efficiency and lowers standby power consumption, which is important for battery-powered devices.

<u>Improved Electrostatic Control:</u> The Z-shaped channel design makes it possible for the gate to exert more effective control over the whole length of the channel. Short-channel effects, which are frequent in traditional TFETs that have been shrunk down, are minimized by improved electrostatic control. Better performance and scalability for upcoming technological nodes are the outcome of this.

Lower Threshold Voltage: The Z-shaped channel's high electric field regions can lower the threshold voltage needed to start tunneling, allowing the device to run at lower supply voltages and so lowering power consumption, and enhancing energy efficiency.

<u>Fig. 5.2:</u> Tunneling width and footprint of proposed ZG-TFET.

## 5.6 Z-Shaped preferred over F-Shaped TFET.

<u>Subthreshold Swing (SS)</u>: The more prominent high electric field regions at the bends may give Z-shaped TFETs an advantage and result in a potentially steeper SS.

<u>DIBL</u>: Both designs provide adequate control; but, because Z-shaped TFETs have sharper control over the channel at the bends, they may perform slightly more effectively than F-shaped TFETs.

<u>On-State Current (Ion)</u>: F-shaped TFETs also offer high Ion through various tunneling areas, but not more than z-shaped ones. However, Z-shaped TFETs may produce a greater Ion due to the enhanced tunneling efficiency from the sharp bends.

### 5.7 Applications

<u>High-Performance Digital Circuits:</u> Z-shaped TFETs are suited for high-speed, lowpower digital circuits due to their superior switching properties and increased current drive.

<u>Analog and RF Circuits</u>: Where linearity and noise performance are crucial, analog and RF circuits can benefit from enhanced electrostatic control and numerous conduction channels.

<u>Low-Power Devices:</u> Z-shaped TFETs are perfect for low-power applications like wearable electronics and Internet of Things devices because they can function effectively at low voltages.

### 5.8 Challenges

<u>Complex Fabrication</u>: Production costs may rise if sophisticated lithography and etching procedures are needed to fabricate the complex Z-shaped geometry.

<u>Device Variability:</u> The complexity of the design can make it difficult to achieve consistent performance across several Z-shaped TFETs, which could lead to manufacturing variability.

## **Chapter 6**

## **Results and Conclusions**

## 6.1 Analysis of 2D F-shaped TFET

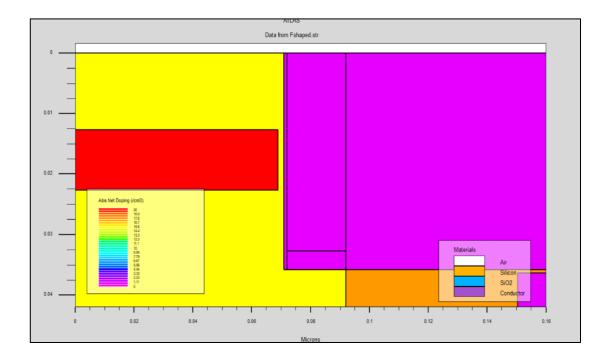

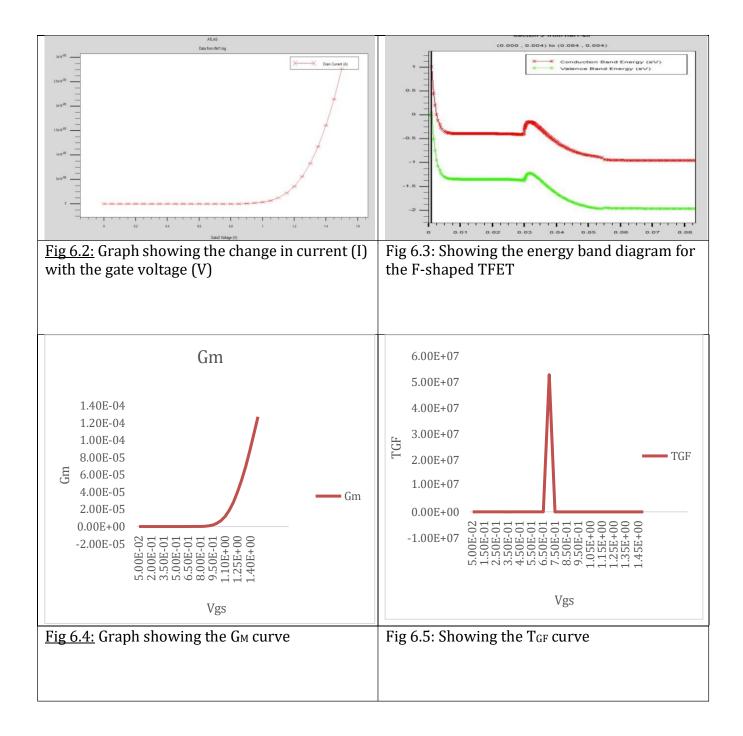

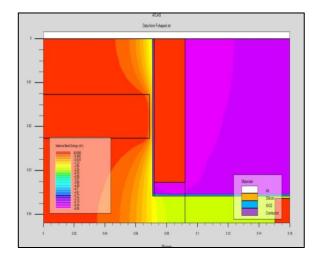

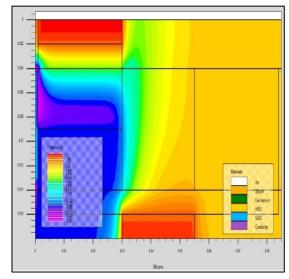

As per the section 2.3, the basic simulation of F shaped TFET has been done. From the output files we get str file and log file. The str file gives the structure of simulated TFET with the parameters considered in above section 2.3.1, as shown in figure 6.1. And the log file gives the drain current vs gate voltage curve, as shown in fig 6.2.

## <u>Fig 6.1</u>: showing the structure of proposed 2D F shaped design

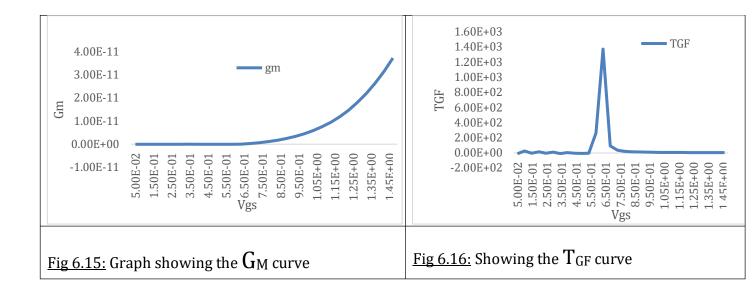

#### The Details on GM curve and TFG curve:

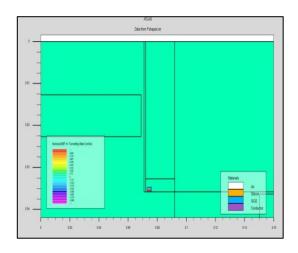

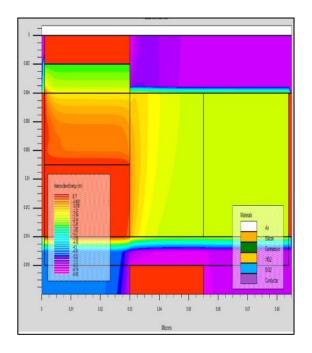

<u>Fig6.6:</u> figure showing the valence band contours.

<u>Fig 6.7:</u> Figure showing the conduction Band contours.

<u>Fig6.8:</u> figure showing the Non local BBT h+ tunneling rate contours.

Fig<u>6.9:</u> Figure showing the Non local BBT e+ tunneling rate contours.

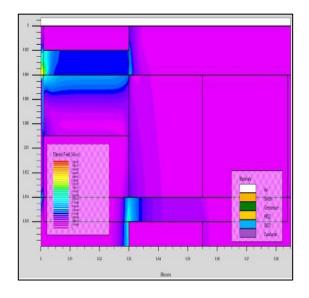

<u>Fig6.10:</u> Figure showing the potential contours.

Fig<u>6.11:</u> Figure showing the Electric. field contours

From this we have extracted potential contours and electric field contours which are shown in below figures 6.6 to 6.11. The electrostatic potential inside the device is represented by the Potential Barrier Contours. It displays the potential variation throughout the semiconductor structure, suggesting the existence of possible wells or barriers. For a TFET to regulate the flow of charge carriers across the channel, the potential barrier at the semiconductor-oxide interface is essential. The vector plots or streamlines that show the device's internal current flow's direction and magnitude are represented by current flow lines. It offers information on the routes that charge carriers—holes or electrons—take as they go from the source to the drain terminals. Comprehending the flow lines of current is crucial for maximizing the efficiency of devices and reducing undesired consequences like leakage currents. <u>Output showing below</u> is the extracted values of Subthreshold voltage. The main thing we are focussing here is the subthreshold voltage which should be less than 60mV/dec for ideal TFets. And we are getting of the almost same order.

```

ATLAS>

EXTRACT> init inf="ffet.log"

EXTRACT> extract name="vt" (xintercept (maxslope (curve (abs (v."gate") ,abs (i."drain")))) - abs(ave(v."drain"))/2.0)

-vt=0.733797 V

EXTRACT> extract name="subvt" 1.0/slope(maxslope(curve(abs(v."gate") ,log10(abs(i."drain")))))

subvt=0.0271382 V/decade

EXTRACT> quit

log off

ATLAS>

ATLAS version 5.26.1.R finished at Sat Jun 01 23:59:27 2024

```

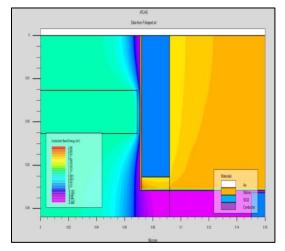

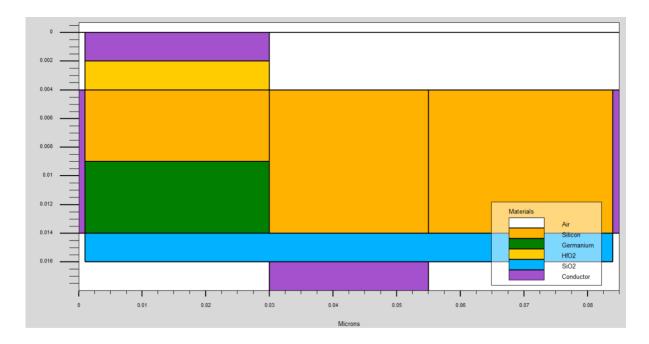

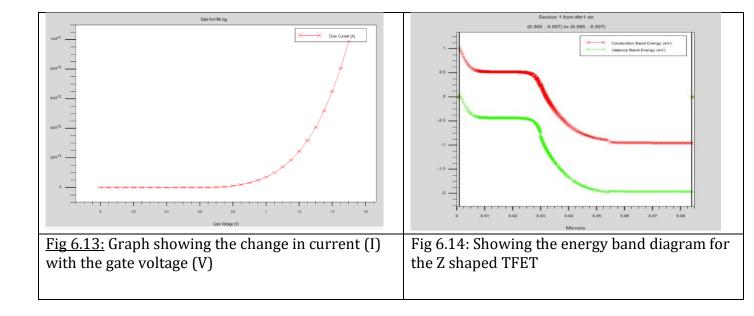

#### 6.2 Analysis of 2D Z shaped TFET

As per the section 2.3, the basic simulation of F shaped TFET has been done. From the output files we get str file and log file. The str file gives the structure of simulated TFET with the parameters considered in above section 2.3.1, as shown in figure 6.1. And the log file gives the drain current vs gate voltage curve, as shown in fig 6.2.

Fig 6.12: showing the structure of proposed 2D Z shaped design

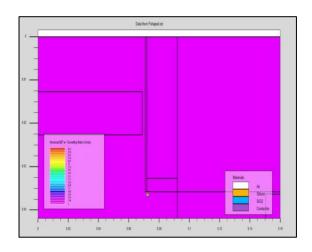

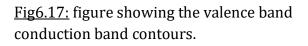

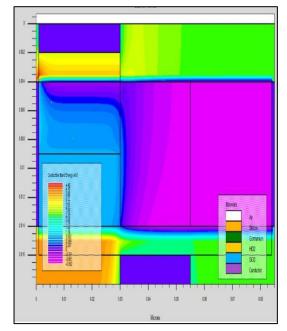

Fig 6.19: figure showing the Non local BBT h+ tunneling rate contours.

Fig<u>6.20:</u> Figure showing the Non local BBT e+ tunneling rate contours.

<u>Fig6.21</u>: figure showing the potential contours.

Fig<u>6.22:</u> Figure showing the Electric. field contours

From this we have extracted potential contours and electric field contours which are shown in below figures 6.17 to 6.22. The electrostatic potential inside the device is represented by the Potential Barrier Contours. It displays the potential variation throughout the semiconductor structure, suggesting the existence of possible wells or barriers. For a TFET to regulate the flow of charge carriers across the channel, the potential barrier at the semiconductor-oxide interface is essential. The vector plots or streamlines that show the device's internal current flow's direction and magnitude are represented by current flow lines. It offers information on the routes that charge carriers—holes or electrons—take as they go from the source to the drain terminals. Comprehending the flow lines of current is crucial for maximizing the efficiency of devices and reducing undesired consequences like leakage currents.

ATLAS>

EXTRACT> init inf="tfet1.log"

EXTRACT> extract name="vt" (xintercept (maxslope (curve (abs (v."gate") ,abs (i."drain")))) - abs(ave(v."drain"))/2.0)

vt=0.780995 V

EXTRACT> extract name="subvt" 1.0/slope(maxslope(curve(abs(v."gate") ,log10(abs(i."drain")))))

subvt=0.00778502 V/decade

EXTRACT> quit

log off

ATLAS>

ATLAS>

ATLAS version 5.26.1.R finished at Sun Jun 02 00:01:44 2024

<u>Output showing above</u> is the extracted values of Subthreshold voltage. The main thing we are focussing here is the subthreshold voltage which should be less than 60mV/dec for ideal TFets. And we are getting of the almost same order.

# 6.3 Conclusion

We have made computed the subthreshold voltage for F shaped TFET and Z shaped TFET and it is noted that for TFET it is less than MOSFETs. For the F shaped TFET it came upto 27.12 mV/decade and for the Z shaped it be barely 7.7 mV/decade.

One important characteristic that shows how well a Tunnel Field-Effect Transistor (TFET) can flip from the off-state to the on-state is its subthreshold slope (SS). For low-power applications, a steeper (lower) subthreshold slope is preferable since it enables the transistor to come on faster and at lower gate voltages. Because of its special gate design that offers better electrostatic control over the channel region, the Z-shaped TFET often exhibits a lower subthreshold slope than the F-shaped TFET. Here are several explanations for why this could be the case: Improved Gate Control: When compared to an F-shaped gate structure, a Z-shaped gate structure can offer the channel region a better electrostatic coupling. This enhanced control facilitates more efficient modulation.

Diminished Short-Channel Effects: The Z-shaped gate's geometry can aid in more effective electric field confinement, minimizing short-channel effects, which frequently deteriorate the subthreshold slope. This indicates that even when the device dimensions are reduced, the Z-TFET can continue to have a higher subthreshold slope.

Optimized Tunneling Junction: Compared to the F-shaped design, the Z-shaped gate might provide a more abrupt and regulated tunneling junction. A decreased subthreshold swing is directly related to an efficient tunneling process, which can be facilitated by a sharper junction.

Symmetric Electric Field Distribution: A more symmetric and consistent electric field distribution across the channel may be the outcome of the Z-shaped structure, which

aids in the achievement of more effective switching behavior. This consistency can improve the leakage currents.

### 6.4 Future Directions

Progress in the development of F-shaped and Z-shaped Tunnel Field-Effect Transistors (TFETs) is expected to yield notable improvements in their functionality and suitability for use in energy-efficient, low-power electronic devices. In order to achieve better electrical characteristics and lower leakage currents for F-shaped TFETs, research is likely to concentrate on optimizing the gate architecture to further improve electrostatic control and tunneling efficiency. Novel materials, such as highk dielectrics or two-dimensional materials, like graphene and transition metal dichalcogenides (TMDs), may also be incorporated. Furthermore, the development of fabrication techniques like atomic layer deposition and accurate doping will be essential to reducing the device's dimensions without compromising its functionality. Future research on Z-shaped TFETs might focus on optimizing the Z-shaped gate design to further lower the subthreshold slope and improve the homogeneity of the electric field distribution. Furthermore, improvements in simulation and modeling tools will help in comprehending and reducing the impacts of small channels as well as improving the architecture of the device to maximize on-current and minimize offstate leakage. Further investigation into strain engineering and heat management techniques is necessary to guarantee the stability and dependability of both F-shaped and Z-shaped TFETs at nanoscale dimensions. Together, these developments will push TFET technology's limits and establish it as a pillar in the creation of nextgeneration semiconductor devices that put energy efficiency and miniaturization first.

# **References**

[1] Avci, U.E.; Morris, D.H.; Young, I.A. Tunnel field-effect transistors: Prospects and challenges. IEEE J. Electron. Devices Soc. 2015, 3, 88–95

[2] C. Auth and A. Shankar, "Evolution of Transistors: Humble Beginnings to the Ubiquitous Present," in IEEE Solid-State Circuits Magazine, vol. 15, no. 3, pp. 20-28, Summer 2023.

[3] Li, M. Review of advanced CMOS technology for post-Moore era. Sci. China Phys. Mech. Astron. 55, 2316–2325 (2012)

[4]C. H. Wann, K. Noda, T. Tanaka, M. Yoshida and Chenming Hu, "A comparative study of advanced MOSFET concepts," in IEEE Transactions on Electron Devices, vol. 43, no. 10, pp. 1742-1753, Oct. 1996

[5] Narain Arora,"MOSFET MODELING FOR VLSI SIMULATION",69,70

[6] Khanna, V.K. (2016). Short-Channel Effects in MOSFETs. In: Integrated Nanoelectronics. NanoScience and Technology. Springer, New Delhi

[7] Narain Arora, "MOSFET MODELINGFOR VLSI SIMULATION", 73-77, 81

[8] P.Razavi and A. A. Orouji, "Dual material gate oxide stack symmetric double gate MOSFET: Improving short channel effects of nanoscale double gate MOSFET," 2008

11th International Biennial Baltic Electronics Conference, Tallinn, Estonia, 2008, pp. 83-86

[9] P.M. Solomon et al., "Two gates are better than one [double-gate MOSFET process]," in IEEE Circuits and Devices Magazine, vol. 19, no. 1, pp. 48-62, Jan. 2003

[10] Viranjay M. Srivastava, K.S. Yadav, G. Singh,"Design and performance analysis of double-gate MOSFET over single-gate MOSFET for RF switch". Microelectronics Journal, Volume 42, Issue 3, 2011, Pages 527-534

[11] Satish M Turkane, A. K. Kureshi, "Review of Tunnel Field Effect Transistor (TFET)", International Journal of Applied Engineering Research ISSN 0973-4562 Volume 11, Number 7 (2016) pp 4922-4929

[12] Prabhat Tamak1, Rajesh Mehra2,"Review on Tunnel Field Effect Transistors (TFET)",International Research Journal of Engineering and Technology (IRJET),Volume: 04 Issue: 07 | July -2017

[13] silvaco Atlas manual,pp 2-7

[14] <u>M. Reiser</u>" A two-dimensional numerical FET model for DC, AC, and large-signal analysis

[15] <u>Ramana Murthy Gajula</u>, <u>Srikanth Itapu</u>, <u>S Mohan Krishna</u>" Analysis of Short Channel Effects in Symmetric Junction-Less Double-Gate Doped MOSFET Using Atlas 2-D Simulator"

[16] <u>Tariqul Islam</u>" <u>Study of an n-MOSFET by Designing at 100 nm and</u> <u>Simulating using SILVACO ATLAS Simulator</u>"

[17] Bhaskar Awadhiya a, Sameer Yadav," Comparative study of Negative Capacitance Field Effect Transistors with different doped hafnium oxides". Microelectronics Journal, Volume 138, August 2023, 105838 [18] Madadi, D., Mohammadi, S. Junction-less SOI FET with an Embedded p<sup>+</sup> Layer: Investigation of DC, RF, and Negative Capacitance Characteristics. Silicon 15, 3959– 3968 (2023).

[19] Choi, W.Y.; Park, B.G.; Lee, J.D.; Liu, T.J.K. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 2007, 28, 743–745.

[20] Avci, U.E.; Morris, D.H.; Young, I.A. Tunnel field-effect transistors: Prospects and challenges. IEEE J. Electron. Devices Soc. 2015, 3, 88–95.

[21] Seunghyun Yun, Jeongmin Oh, Seokjung Kang, Yoon Kim, Jang Hyun Kim, Garam Kim and Sangwan Kim "F-Shaped Tunnel Field-Effect Transistor (TFET) for the Low-Power Application". *Micromachines* 2019, *10*(11), 760;

[22] Li, M. Review of advanced CMOS technology for post-Moore era. Sci. China Phys.Mech. Astron. 55, 2316–2325 (2012)

[23] Satish M Turkane, A. K. Kureshi, "Review of Tunnel Field Effect Transistor (TFET)", International Journal of Applied Engineering Research ISSN 0973-4562Volume 11, Number 7 (2016) pp 4922-4929

[24] Prabhat Tamak1, Rajesh Mehra2,"Review on Tunnel Field Effect Transistors (TFET)", International Research Journal of Engineering and Technology (IRJET),sVolume: 04 Issue: 07 | July -2017

[25]A two-dimensional numerical FET model for DC, AC, and large-signal analysis

DEPARTMENT OF APPLIED PHYSICS DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **Plagiarism Verification**

Title of the Thesis: TCAD SIMULATION-BASED ANALYSIS OF TFET BASED ON DIFFERENT STRUCTURAL SHAPE: F-SHAPED AND Z-SHAPED

Total Pages: 50

Name of the Supervisor: Dr. Rishu Chaujar

Department: Department of Applied Physics

This is to report that the above thesis was scanned for similarity detection. Process and outcome is given below:

Software used: SILVACO Atlas and TONYPLOT

Similarity Index: 8%

Total Word Count: 6787

Date: 7/06/2024

Candidate's Signature

Rchaufar

Signature of Supervisor

PAPER NAME

plag report.pdf

| WORD COUNT                   | CHARACTER COUNT              |

|------------------------------|------------------------------|

| 6787 Words                   | 38092 Characters             |

| PAGE<br>COUNT<br>50 Pages    | FILE SIZE<br>1.4MB           |

| SUBMISSION DATE              | <b>REPORT DATE</b>           |

| Jun 6, 2024 9:26 AM GMT+5:30 | Jun 6, 2024 9:27 AM GMT+5:30 |

#### • 8% Overall Similarity

The combined total of all matches, including overlapping sources, for each database. •

- 5% Internet database

- Crossref database

- 5% Submitted Works database

- Excluded from Similarity Report

- Bibliographic material

- Manually excluded text blocks

- 6% Publications database

- Crossref Posted Content database •

- Small Matches (Less then 10 words)