# DESIGN AND OPTIMIZATION OF JUNCTIONLESS-ACCUMULATION-MODE GATE-STACK GATE-ALL-AROUND FINFET FOR RF AND BIOSENSOR APPLICATIONS

Thesis Submitted by

# **Bhavya Kumar**

In Fulfillment of the Requirements for the Degree of

#### **DOCTOR OF PHILOSOPHY**

Under the Supervision of

#### **PROF. RISHU CHAUJAR**

# DEPARTMENT OF APPLIED PHYSICS DELHI TECHNOLOGICAL UNIVERSITY, DELHI, INDIA OCTOBER 2023

©Delhi Technological University (DTU), Delhi, 2023

### **Delhi Technological University**

(Govt. of National Capital Territory of Delhi) Bawana Road, Delhi-110042

# **CERTIFICATE**

This is to certify that the thesis titled "Design and Optimization of Junctionless-Accumulation-Mode Gate-Stack Gate-All-Around FinFET for RF and Biosensor Applications" is being submitted by MR. BHAVYA KUMAR with registration number 2K18/PHD/AP/17 to the Delhi Technological University for the award of the degree of Doctor of Philosophy in Physics. The work embodied in this thesis is a record of bonafide research work carried out by me in the Microelectronics Research Lab, Department of Applied Physics, Delhi Technological University (Formerly Delhi College of Engineering), New Delhi, under the guidance of PROF. RISHU CHAUJAR. It is further certified that this work is original and has not been submitted in part or fully to any other University or Institute for the award of any degree or diploma.

> Bhavya Kumar Roll No.2K18/PHD/AP/17

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

**Prof. Rishu Chaujar** Supervisor (Professor) Department of Applied Physics Delhi Technological University Delhi, India **Prof. A. S. Rao** Head & DRC Chairman Department of Applied Physics Delhi Technological University Delhi, India

Bhavya Kumar

#### ACKNOWLEDGMENTS

Throughout my Ph.D. journey, I had the opportunity to interact with a variety of individuals. Each encounter has left an indelible mark on my personal and professional development with unique lessons and experiences. Therefore, I sincerely appreciate each person who has contributed to my life.

# īsívaraḥ paramaḥ kṛṣṇaḥ sac-cid-ānanda-vigrahaḥ<br/>anādir ādir govindaḥ sarva-kāraṇa-kāraṇam(Brahma-Samhita 5.1)

First and foremost, I humbly offer my obeisance to the **Supreme Personality of Godhead**, **Kṛṣṇa**, who is the supreme cause of all causes, as concluded in the Brahma-Samhita by Lord Brahma himself. It is by His (**Kṛṣṇa**) grace that I have been blessed with the privilege of expressing my devotion. I acknowledge with utmost humility that whatever I am today, every blessing and accomplishment is a manifestation of His divine will. So, as we traverse the path of life, it is our sacred duty to chant His holy name to accomplish the purpose of this human life.

I would like to express my heartfelt gratitude to my supervisor, **Prof. Rishu Chaujar**. The successful completion of this challenging academic endeavor would not have been possible without her affection, unwavering guidance, and support. Her dedication to academic excellence and enthusiasm for research have been truly inspiring. Under her guidance, I learned to embrace independence, strengthen my mental resilience, and focus on higher aspirations. Her belief in my abilities, even when I doubted myself, has been a tremendous source of motivation. She not only treated me with love and care but also strictly corrected me whenever I got sidetracked from my work, which has shaped me as a researcher and nurtured my personal growth and development. Her suggestions have been instrumental in impacting the quality and depth of my research. I am particularly grateful for her prompt assessment of my manuscripts and thesis chapters. Her punctuality has greatly facilitated the timely completion of my Ph.D. work with a substantial number of publications.

I am thankful to **Prof. A. S. Rao** (DRC Chairman and HoD, Applied Physics, DTU) and **Prof. S. Indu** (Vice Chancellor, DTU) for providing the necessary resources to facilitate the research activity. I further thank the experts and members of the SRC and DRC for generously dedicating their valuable time to serve on my committee and providing their invaluable support of my thesis. Also, I thank all the faculty members of the Department for their helpful recommendations and advice during my Ph.D. journey. I appreciate all the care and support shown to me by the Staff Members of the Department (especially **Babita Ji**, **Deepak Ji**, **Suresh Ji**, **Krishna Ji**, and **Naresh Ji**).

The Ph.D. journey is tough and often needs the assistance of seniors, and I consider myself extremely fortunate to have **Dr. Ajay Kumar** as my senior. During my most challenging days, he emerged as a ray of hope, guiding me through the darkest of times. His willingness to freely share his expertise, helpful ideas, soft copies of documents, and presentations has been an irreplaceable resource for me. Beyond being a senior, he has been a guiding force in my life as an elder brother. I am profoundly grateful for everything he has done for me, and I am aware that I can never truly repay him for his generosity and kindness. Also, I wish to thank **Dr. Neha Gupta** for her invaluable assistance throughout this endeavor.

I owe gratitude to someone extremely special, *Ankita Banwal*. With her by my side, I have experienced a thoughtful transformation, both mentally and spiritually. Her presence in my life has brought me a sense of inner peace and positivity that I never thought possible. She gently cared for my smallest needs without expecting anything in return. She has added color to the graphs of my papers and the canvas of my life. She has been my firm support through thick and thin, standing with me in moments of happiness and consoling me in times of sorrow. I love her with all my heart, and I'm eternally grateful for the incredible impact she had on my life. Furthermore, I thank my dearest friend, *Rohit Vashisht*, a person who has loved me like an elder brother. His ability to listen and to always be there for me is the quality I cherish most in him. It's worth mentioning that he's my one and only male friend, and our bond has stood the test of time, turning into a brotherly connection that means the world to me.

I consider myself incredibly fortunate to have a gem of a labmate in **Dr. Megha Sharma**. She stands out because, instead of harboring jealousy over my successes, she's always motivated me to reach even greater heights. She has always been there for me when I needed help with my papers, guided me to a better knowledge of difficult topics, and offered valuable advice for navigating the challenges in my professional life. I deeply appreciate and cherish the friendship we share. Also, I want to thank **Dr. Samriti Sharma** for all the healthy discussions we had that have really helped me get through this endeavor.

Bhavya Kumar

When it comes to my juniors (Rashi Mann, Yash Pathak, Anshul, Ayushi Lamba, Kajal Verma, and Shubhda), I can't help but be overwhelmed by the immense love and respect they shower upon me. It's become such a regular part of my daily life that I often find myself losing track of time, forgetting about heading home when I'm with them. Among them, **Rashi** Mann is a kind and pure-hearted individual. She not only listens to whatever I say but also treats me with the utmost respect. It's a genuine pleasure to have her as a part of our lab family, as she maintains a positive and harmonious environment. Yash Pathak is a truly down-to-earth person who has no ill will toward anybody. He has a profound and genuine respect for me, and every time I ask for his assistance, he completes the tasks with remarkable ease. It's like having a trustworthy younger brother who is always there for you. Anshul is an absolute lifesaver! Whenever I request her help, she effortlessly takes care of all the tasks, leaving me worry-free. She never uttered a single unkind word against me, which has solidified the deep trust I have in her. She has the ability to infuse laughter into our daily interactions, especially with her Haryanvi expressions, which I truly appreciate. Also, I want to extend my heartfelt appreciation to my super juniors, Ayushi Lamba, Kajal Verma, and Shubhda, for always respecting and admiring me. Cheers to the countless funfilled moments we've shared in our lab, making my journey truly memorable and enjoyable.

I want to thank my friend Yakshansh Kumar, who always appreciated my work and encouraged me to stay motivated. His ability to acknowledge the quality of my work has been a source of positivity in my professional life. I would like to extend my warmest thanks to Sanchit Banwal and Nitika Kalia, two incredible individuals who have shown me an abundance of love and treated me with respect and care. Their presence in my life has been a blessing, and the friendly bond we share is deeply cherished. Also, I would like to thank Bhumika Mehta, Surbhi Garg, Pravesh Sangwan, Latika Aggarwal, Richa Mohley, Dilip Kumar, Agam Jain, Atul Kaushik, Vinod Kumar, Neeraj Chamoli, Sachin, Dr. Parveen Jakhar, Dr. Rajkumar Yadav, Dr. Mekonnen Getnet Yirak, and Megha Narwan for being the incredible friends and colleagues. I'm grateful for your presence in my life.

I owe everything I am today to my father (**Suraj Pal Singh**) and my mother (**Manju Lata**). Throughout my journey, my father never once deterred me from pursuing my studies and consistently served as a source of motivation. He selflessly set aside his dreams and expectations and supported me emotionally and financially, ensuring that I could pursue my ambitions without hindrance. My mother's love has been an inexhaustible wellspring of affection and support. She instilled in me a set of invaluable ethical principles, which have been an integral part of my Ph.D. journey. The impact of her teachings on my life is immeasurable, and I carry her wisdom with me as a treasured gift. The love and care I've received from my elder brother (Sanjeev Kumar) and elder sister (Rajesh Kumari) are assets that I hold close to my heart. Beyond their love, they have selflessly gone above and beyond to fulfill my wishes, supporting me in ways that words can hardly describe. I am eternally grateful to them for their unwavering presence, their selfless gestures, and the countless ways in which they've enriched my life. I am deeply grateful to my sister-in-law (Richi Singh) and brother-in-law (Dr. Vinod Thakur). What they have done for me is nothing short of remarkable, and their efforts are etched in my memory as acts of genuine kindness and love. I am absolutely thankful to my adorable nephews (Viraj and Karan), who have this incredible superpower of whisking away all my mental stress. Their boundless energy, laughter, and infectious spirit are like a magical spell, and every time I'm around them, it's as if all my worries disappear.

Last but not least, I heartily thank my spiritual mentors (HG Paresh Das) and (HG Jahanva Devi Dasi), who helped me discover the Absolute Truth (Lord Kṛṣṇa) and understand the purpose of life. I pray to the Divine to bestow upon me the strength and ability to serve them. Also, I want to thank HG Radharaman Das, HG Ras Parayan Das, HG Antaryami Krishna Das, HG Sarv Sakshi Das, HG Kajal Devi Dasi, and HG Komal Devi Dasi for their kindness and the genuine way in which they made me feel comfortable was truly remarkable. All the glories to HDG AC Bhaktivedanta Swami Srila Prabhupada and Guru Maharaj.

> (Bhavya Kumar) New Delhi, October 2023

# Design and Optimization of Junctionless-Accumulation-Mode Gate-Stack Gate-All-Around FinFET for RF and Biosensor Applications

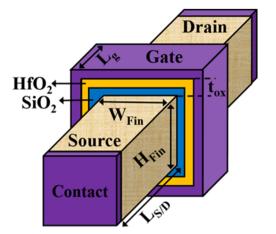

FinFET has emerged as the most desirable alternative to MOSFETs and is the driving force behind the current integrated circuit (IC) industry, which optimizes short-channel effects (SCEs) to achieve exceptional scalability, augment battery longevity, and minimize power consumption. FinFET ensures superior electrostatic control with three gates surrounding the fin and offers a larger packing density due to its three-dimensional construction. In this thesis, Junctionless-Accumulation-Mode Gate-Stack Gate-All-Around (JAM-GS-GAA) FinFET architecture has been rigorously examined and compared with different structures using the SILVACO ATLAS 3D simulator. The analysis exemplified that JAM-GS-GAA FinFET overcomes the challenges faced by conventional FinFET, such as manufacturing complexity, reliability concerns, variability issues, etc. In addition, approaches such as dualk spacer engineering have been used to further improve the device's performance.

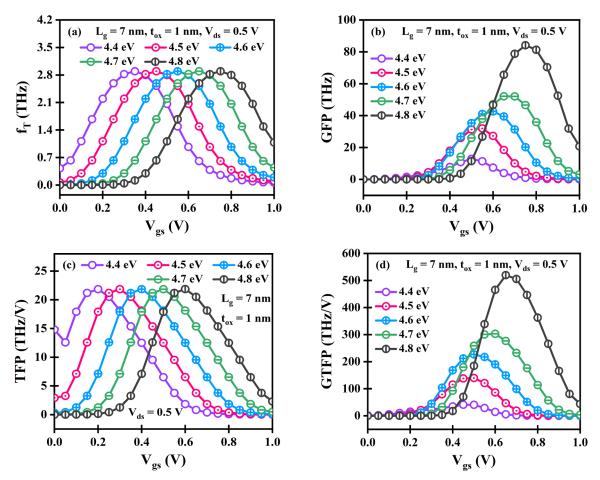

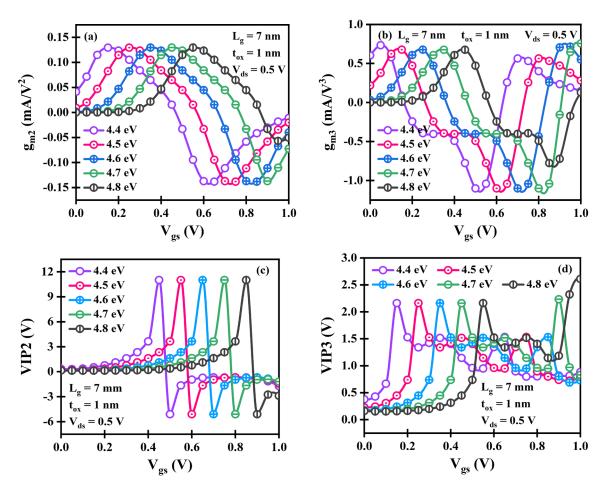

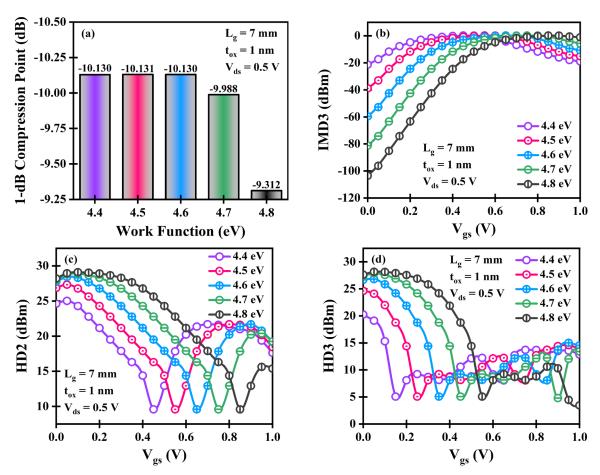

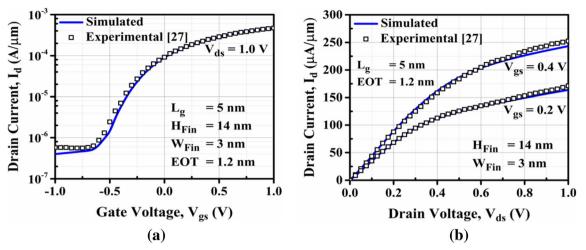

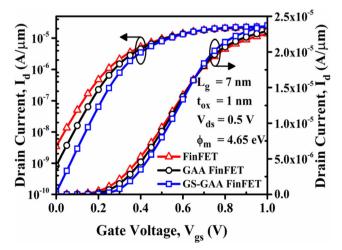

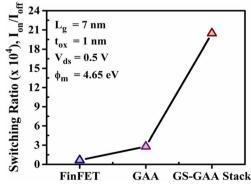

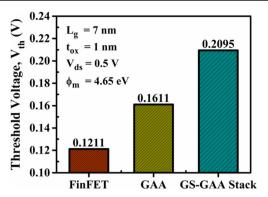

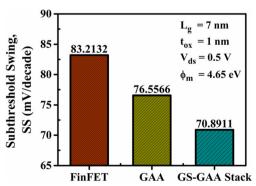

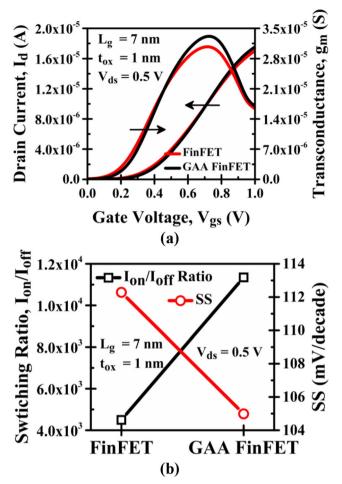

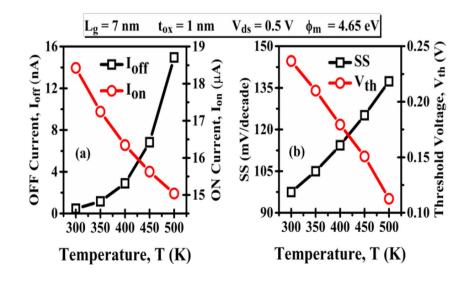

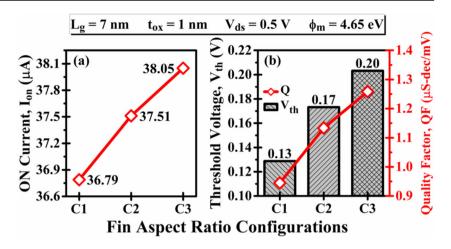

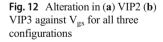

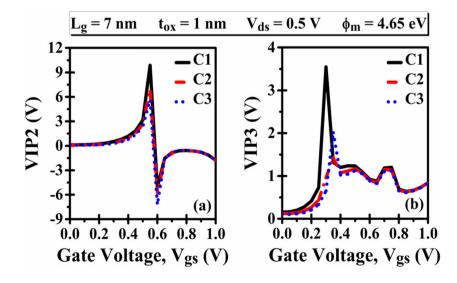

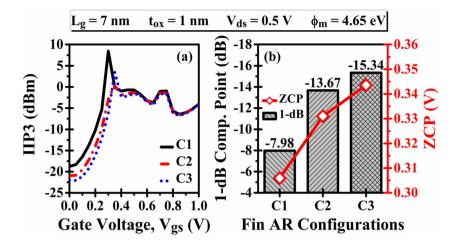

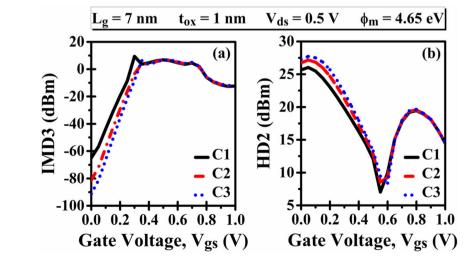

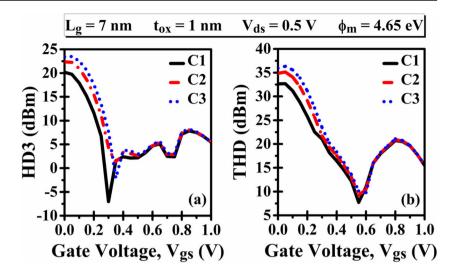

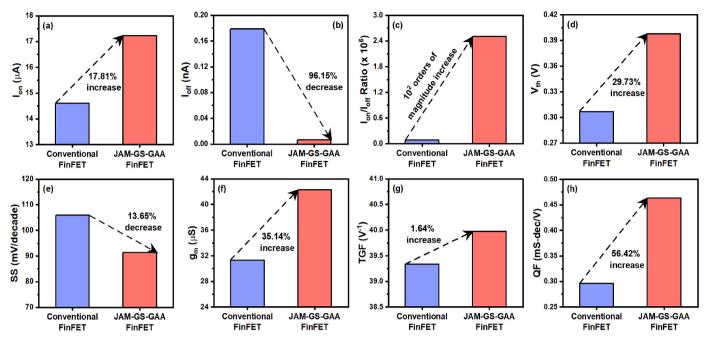

In the beginning, a comprehensive study of the analog and RF characteristics of JAM-GS-GAA FinFET has been analyzed with the optimization of the fin aspect ratio at the subnano level to achieve a high-performance transistor. It has been found that the analog and RF performance of the JAM-GS-GAA FinFET device improved significantly compared to conventional FinFET because of the enhanced gate control on the channel and reduced SCEs. When compared to conventional FinFET, parameters like switching (I<sub>on</sub>/I<sub>off</sub>) ratio, gain transconductance frequency product (GTFP), and gain frequency product (GFP) increased by 31, 3.37, and 2.73 times, respectively, for the JAM-GS-GAA FinFET device. It has also been analyzed that the proposed device with the highest fin aspect ratio configuration exhibits the most improved analog and RF performance compared to the other lower fin aspect ratio configurations. The device with a high fin aspect ratio exhibits a considerable reduction of 94.72% in leakage current (I<sub>off</sub>) and 14.90% in subthreshold swing (SS), along with notable improvements in other metrics. Further, the performance of the proposed JAM-GS-GAA FinFET device has been compared with other existing devices on different technologies at a fixed gate length of 10 nm to evaluate its significance. Then, the reliability issues of the proposed device have been explored by considering the impact of temperature and gate electrode work function in terms of static, analog, RF, linearity, and harmonic distortion characteristics. The study's findings indicate that the JAM-GS-GAA FinFET demonstrates satisfactory reliability in the face of temperature fluctuations and changes in the gate electrode work function. The static, linearity, and harmonic distortion metrics do not change much as the temperature increases from 300 K to 500 K, while the peak values of parameters like gm, f<sub>T</sub>, TFP, gm<sub>2</sub>, gm<sub>3</sub>, VIP2, VIP3, HD2, and HD3 are approximately the same for all gate electrode work functions.

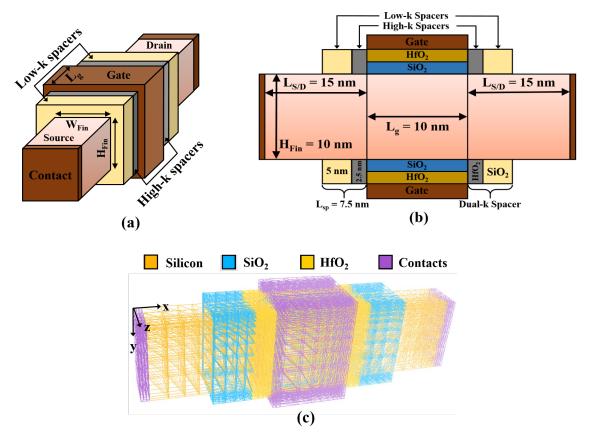

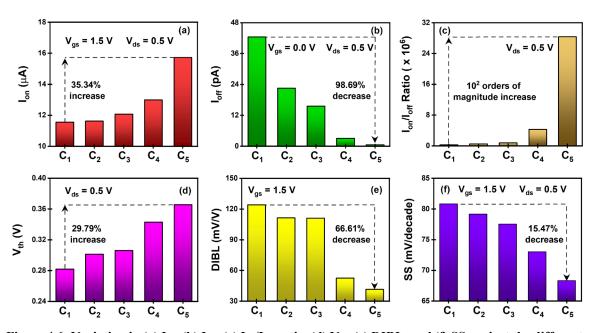

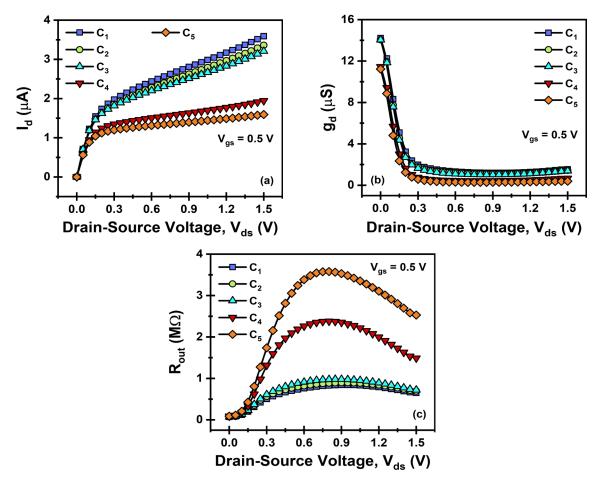

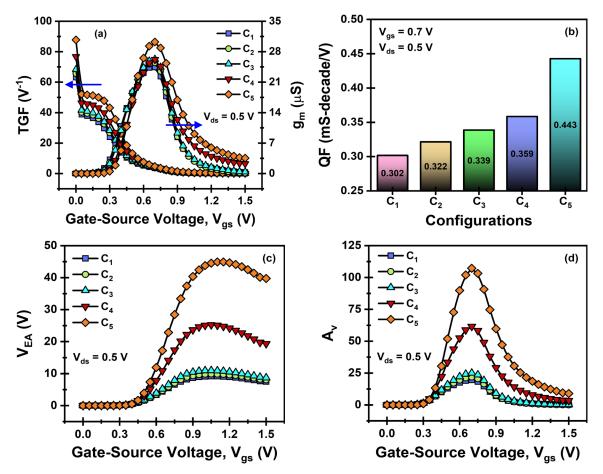

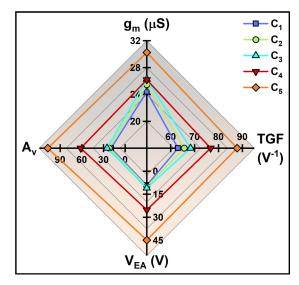

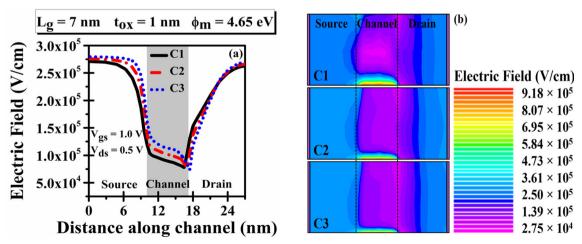

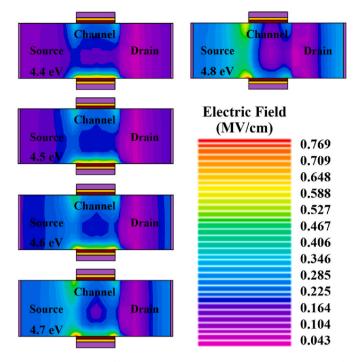

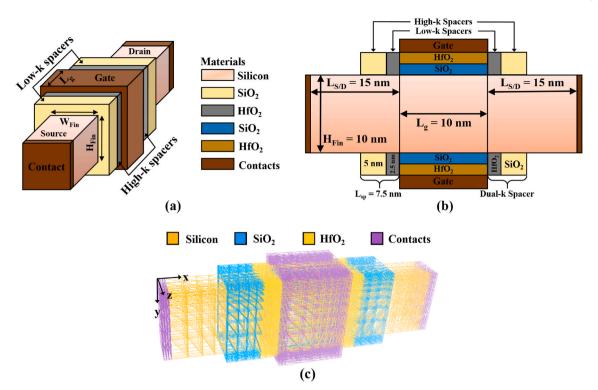

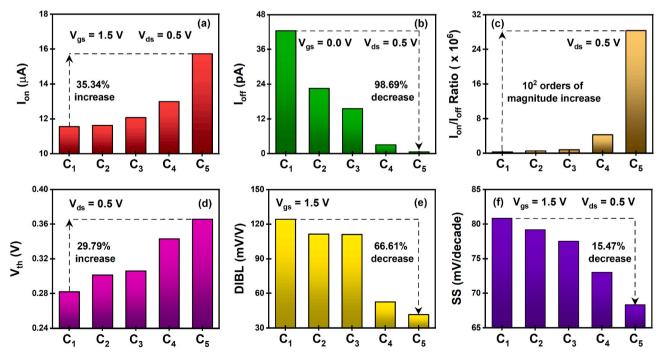

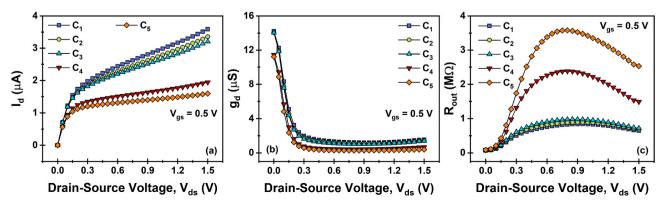

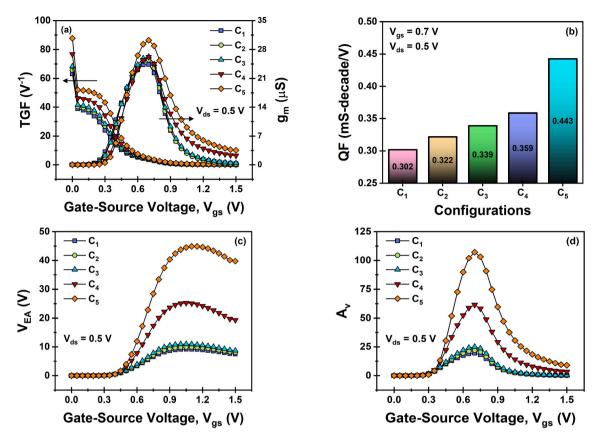

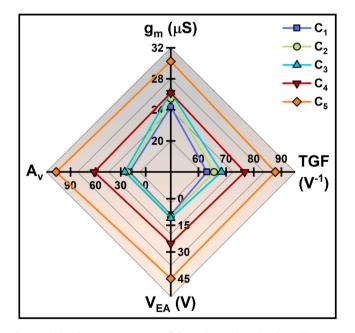

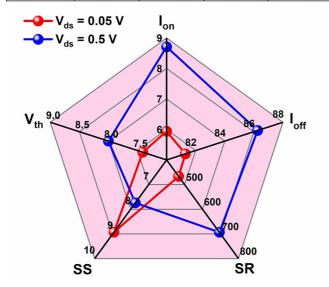

Moreover, the impact of dual-k spacer  $(SiO_2 + HfO_2)$  engineering on the JAM-GS-GAA FinFET has been investigated to further enhance the performance of the proposed device and make it suitable for sub-10 nm RFIC circuits. Different configurations such as conventional tri-gate JAM-GS-FinFET, JAM-GS-GAA-FinFET without a spacer, JAM-GS-GAA-FinFET with single-k spacers, and the proposed JAM-GS-GAA-FinFET with dual-k spacer have been examined. The dual-k spacer configuration uses HfO<sub>2</sub> as a high-k spacer for the inner layer and SiO<sub>2</sub> as a low-k spacer for the outer layer. Due to the fringing field effects, the dual-k spacer configuration improves the electron velocity, electric field, surface potential, and energy band profiles. Thereby increasing the ON-state (I<sub>on</sub>) current of the dual-k spacer configuration by 35.34%, I<sub>on</sub>/I<sub>off</sub> ratio by approximately 10<sup>2</sup> times, transconductance (g<sub>m</sub>) by 24.03%, transconductance generation factor (TGF) by 39.12%, quality factor (QF) by 46.75%, while decreasing the I<sub>off</sub> by over 76 times and SS by 15.47% compared to the conventional FinFET configuration.

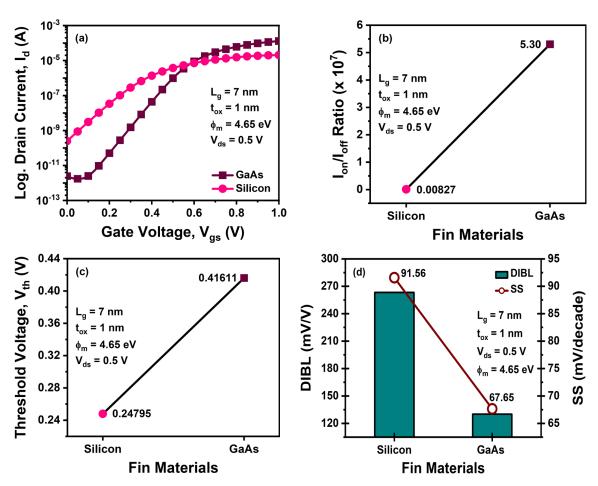

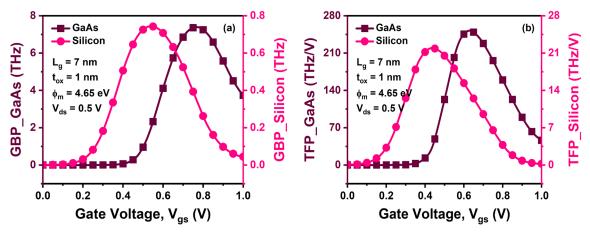

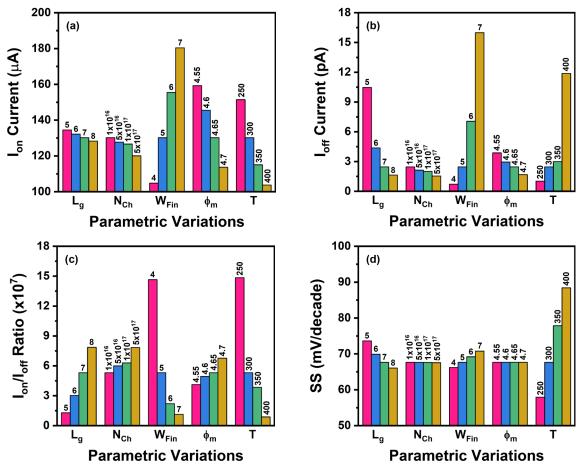

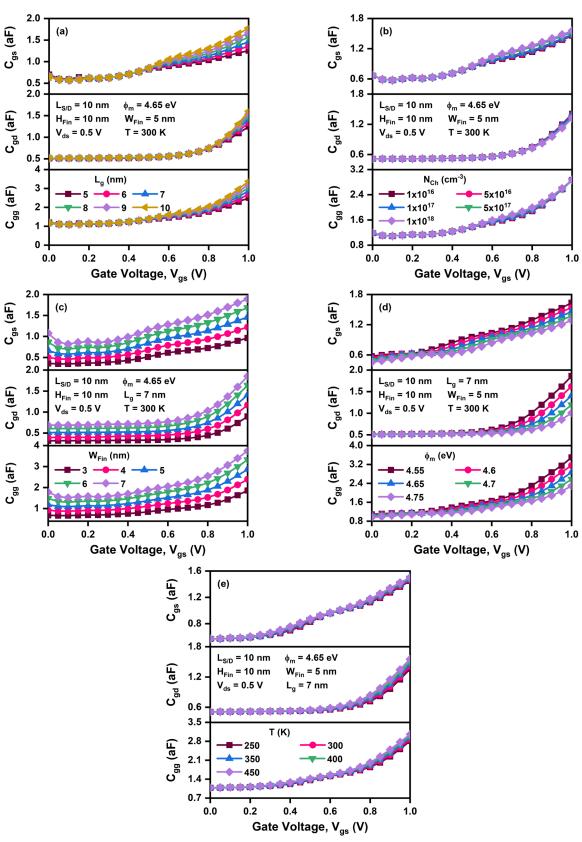

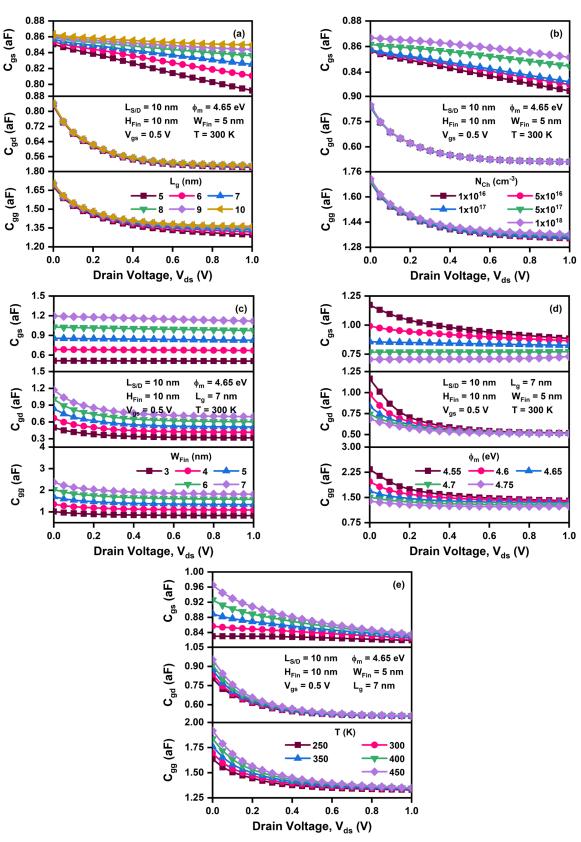

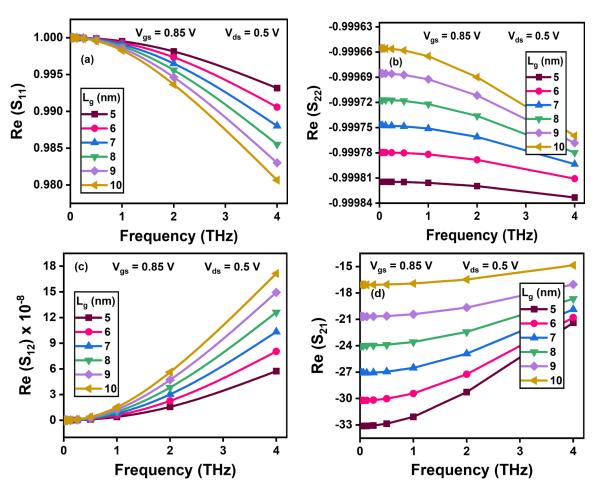

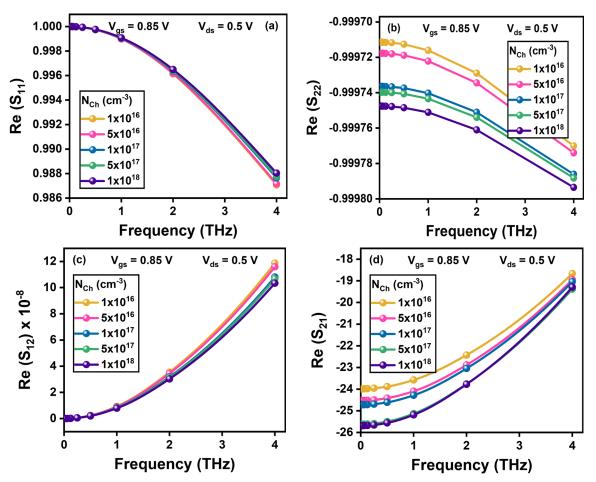

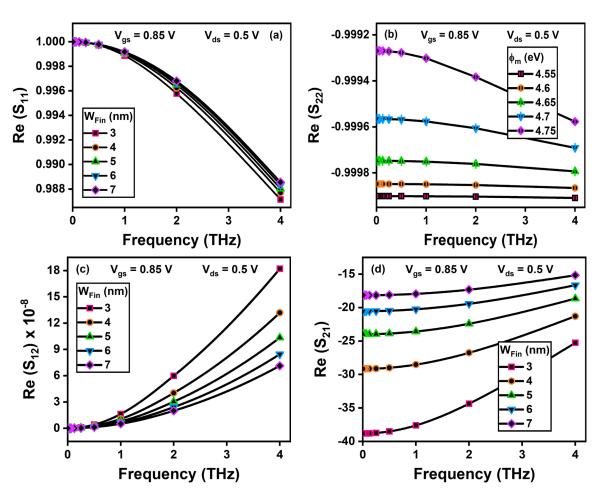

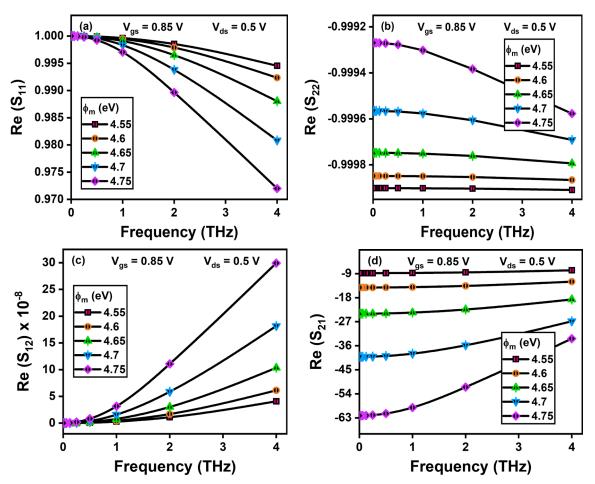

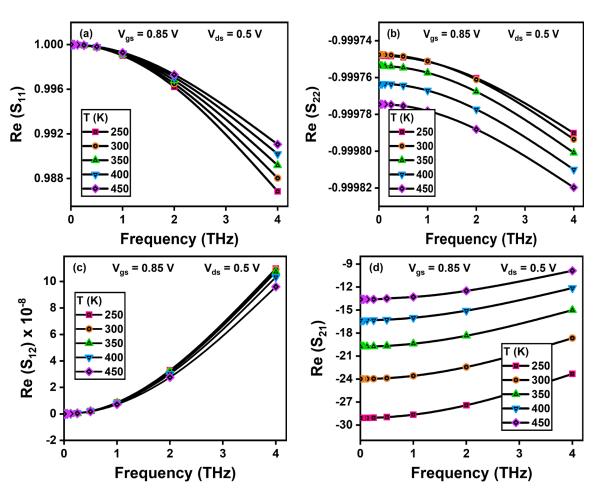

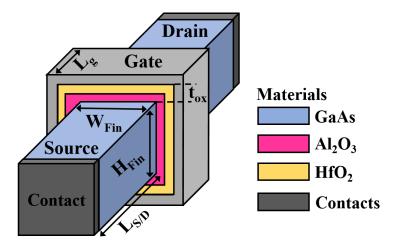

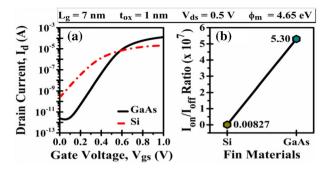

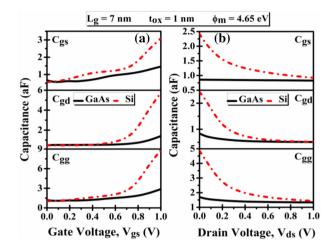

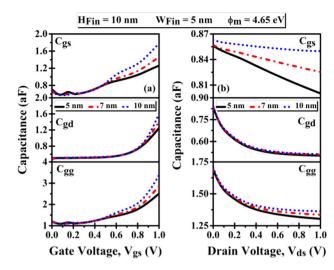

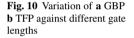

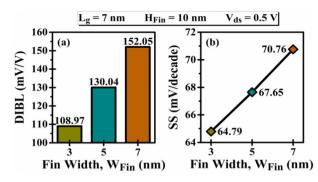

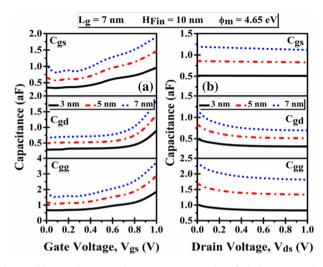

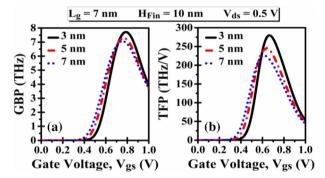

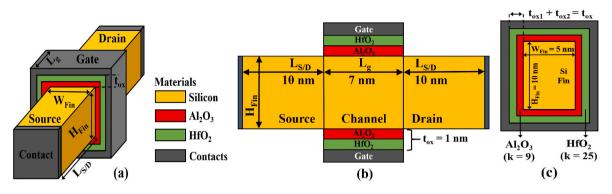

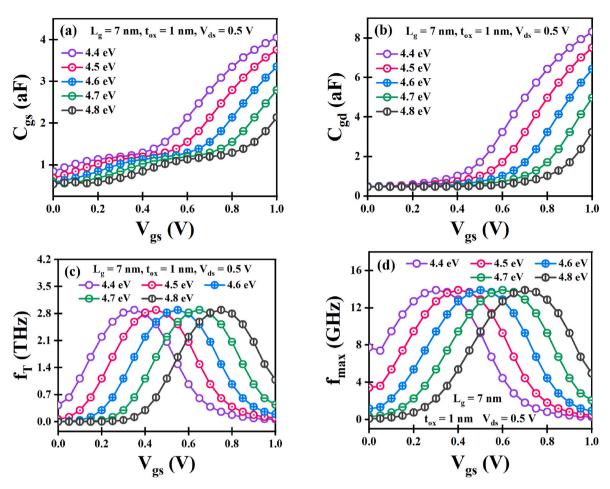

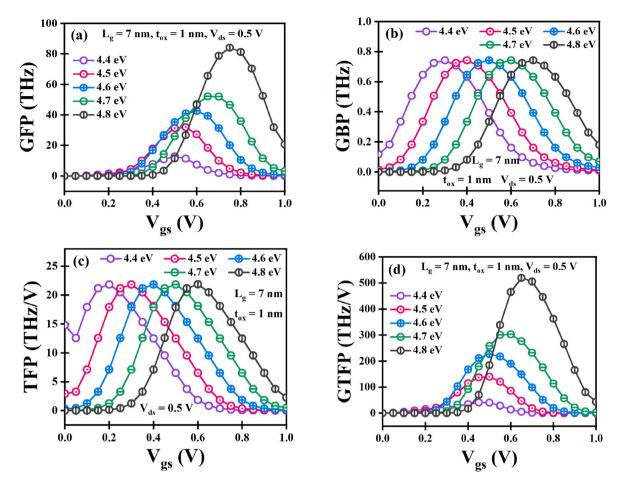

Further, the parasitic capacitances and small-signal behavior of JAM-GS-GAA FinFET have been inspected to assess the efficacy of GaAs as a fin material. Capacitance-related FOMs like gain bandwidth product (GBP) and transconductance frequency product (TFP) have also been analyzed for switching applications. It has been noticed that SCEs and parasitic capacitances reduced considerably, and the peak value of both GBP and TFP increased by 10 times with the incorporation of GaAs. Further, the effect that parameters like gate length ( $L_g$ ), channel doping ( $N_{Ch}$ ), fin width ( $W_{Fin}$ ), gate electrode work function ( $\phi_m$ ), and temperature (T) have on the parasitic capacitances and scattering (S) parameters

of GaAs JAM-GS-GAA FinFET across the terahertz (THz) frequency range have been examined. The results confirm that the parasitic capacitances decreased appreciably for a device with a shorter  $L_g$ , smaller  $N_{Ch}$ , lower  $W_{Fin}$  and T, and higher  $\phi_m$ , whereas, at extremely high frequencies, the S-parameters improved considerably for a device with a larger  $L_g$ , smaller  $N_{Ch}$ , lower  $W_{Fin}$  and T, and higher  $\phi_m$ .

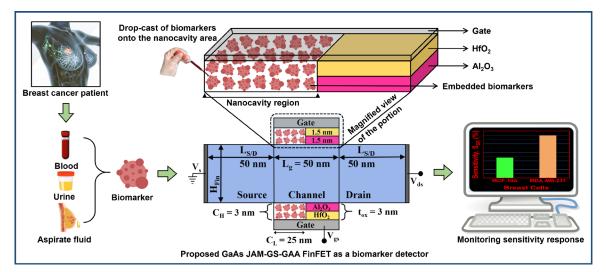

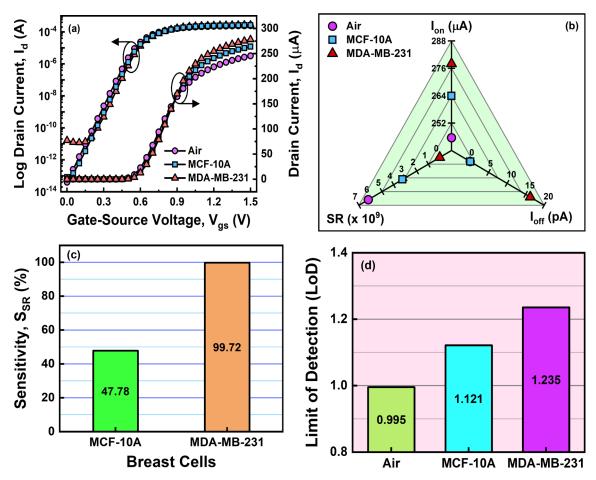

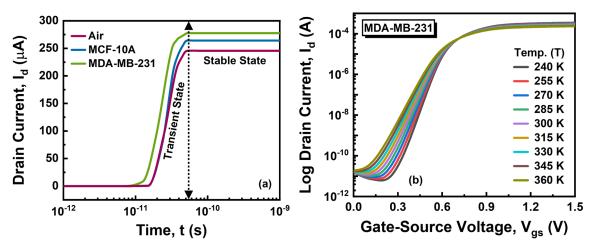

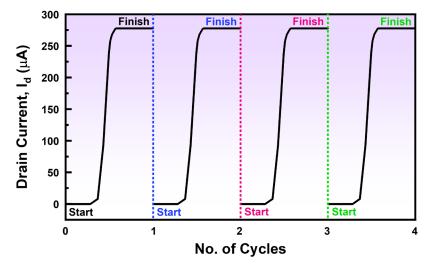

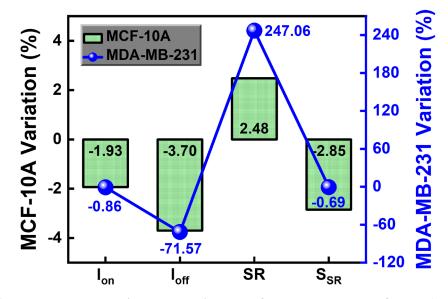

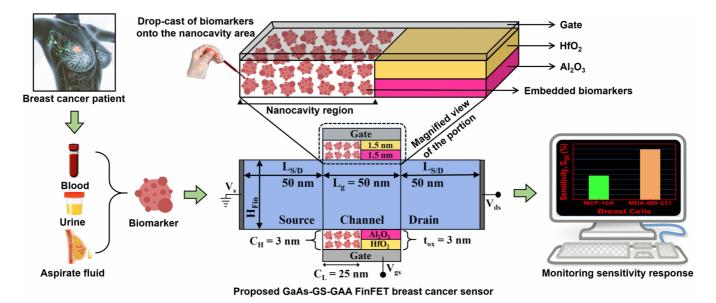

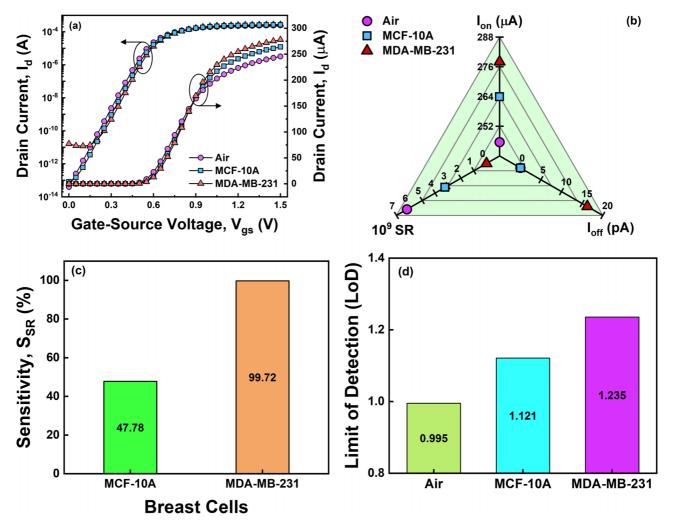

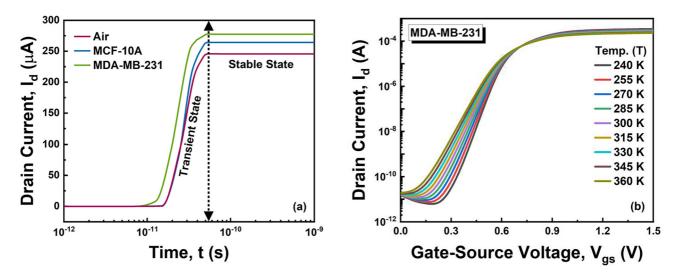

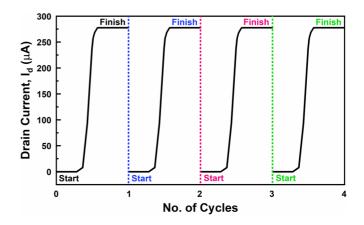

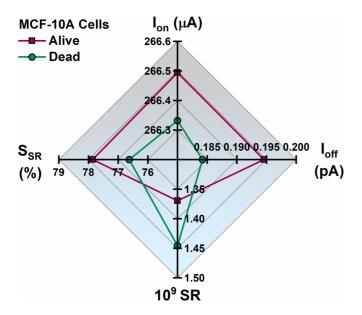

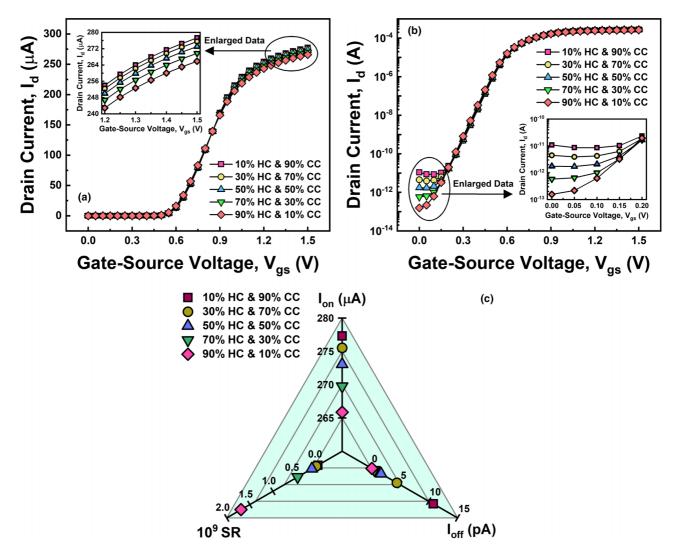

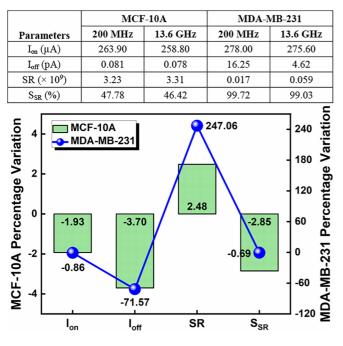

After analyzing the electrical properties of the proposed device, the GaAs JAM-GS-GAA FinFET has been utilized to accomplish the electrical identification of the MDA-MB-231 breast cancer cell by monitoring the device switching ratio. The switching ratio-based device sensitivity has been evaluated by analyzing the drain current characteristics for air (cellfree), MCF-10A (healthy), and MDA-MB-231 (cancerous cells), and it comes out to be 47.78% and 99.72% for healthy and cancerous breast cells, respectively. The sensor has also been assessed for its reproducibility, stability, and capability to distinguish between viable and non-viable cells and was found to be repeatable and adequately stable, with settling times of 55.51 ps for the MDA-MB-231 cell, 60.80 ps for the MCF-10A cell, and 71.58 ps for air. Further, the possibility of early detection of cancerous breast cells using Bruggeman's model and the effect of biomolecule occupancy and frequency fluctuations on the device's sensitivity has been investigated. The impact of the physical parameters, like fin height, fin width, gate electrode work function, channel doping, temperature, and drain voltage, on the device's sensitivity has been explored. Finally, the GaAs JAM-GS-GAA FinFET sensor was compared to already existing breast cancer sensors, and it was found that the proposed sensor performed much better.

Thus, JAM-GS-GAA FinFET can be considered a promising candidate for use in lowpower, analog, RF, and biosensor applications due to its high switching ratio, lower leakage current, better reliability in terms of temperature and gate electrode work function, superior static, analog, and RF performance, suppressed SCEs and parasitic capacitances, and high sensitivity electrical detection of MDA-MB-231 breast cancer cells.

## LIST OF FIGURES

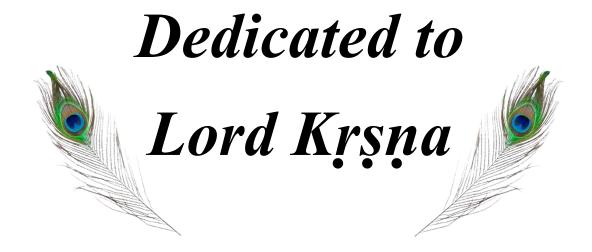

| Figure 1.1: Log plot of transistor counts per microprocessor against calendar years2                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

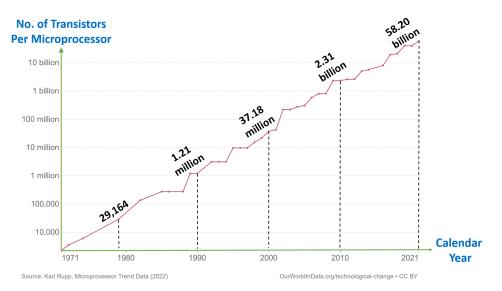

| Figure 1.2: Tri-gate FinFET performance comparison with planar transistors                                                                                             |

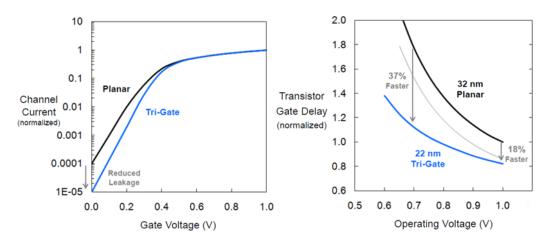

| Figure 1.3: Constant field scaling principles for MOSFETs and ICs4                                                                                                     |

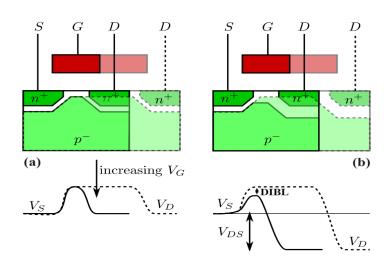

| Figure 1.4: Drain-induced barrier lowering7                                                                                                                            |

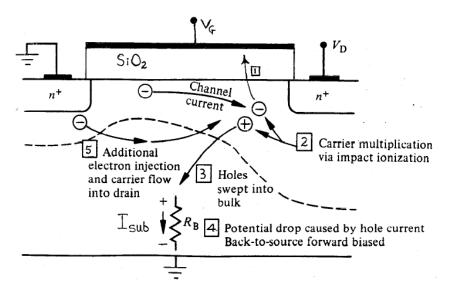

| Figure 1.5: Cross-sectional view of n-channel MOSFET illustrating hot-carrier injection                                                                                |

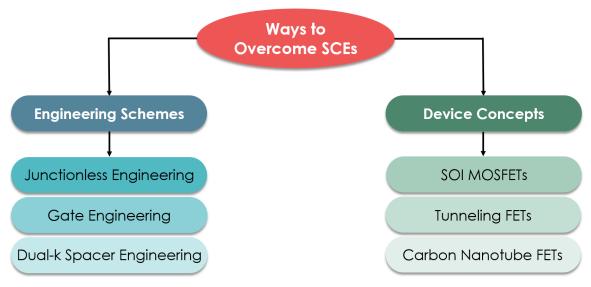

| Figure 1.6: Different ways to overcome SCEs in nano-scale MOSFET8                                                                                                      |

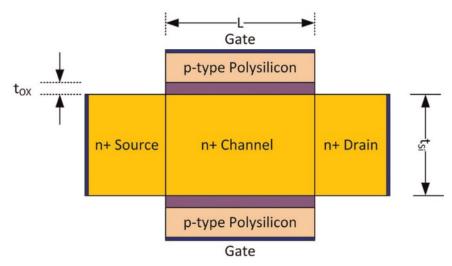

| Figure 1.7: Cross-sectional view of junctionless double gate MOSFET                                                                                                    |

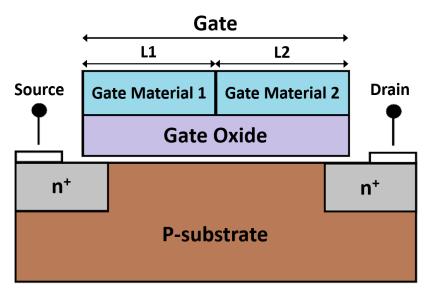

| Figure 1.8: Schematic structure of dual material gate MOSFET10                                                                                                         |

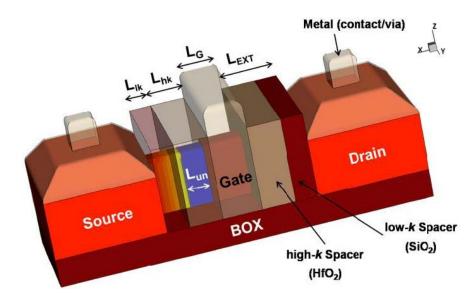

| Figure 1.9: Schematic FinFET structure with dual-k underlap spacers11                                                                                                  |

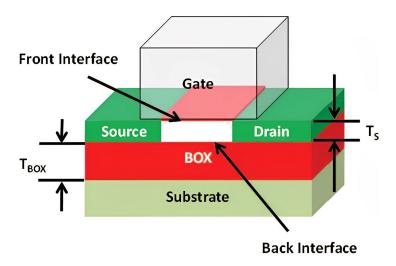

| Figure 1.10: Schematic structure of FD-SOI MOSFET 12                                                                                                                   |

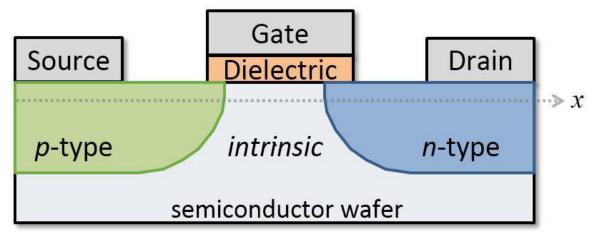

| Figure 1.11: Schematic lateral structure of TFET13                                                                                                                     |

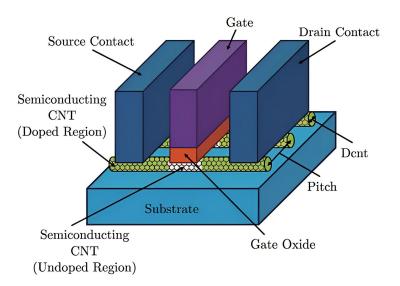

| Figure 1.12: Schematic structure of CNTFET device14                                                                                                                    |

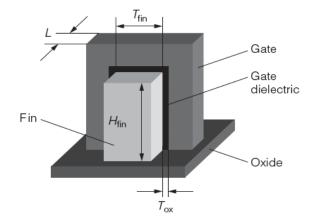

| Figure 1.13: Schematic structure of conventional FinFET16                                                                                                              |

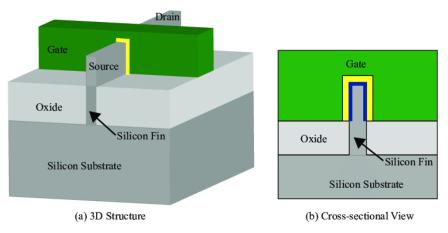

| Figure 1.14: (a) 3D structure and (b) cross-sectional view of Intel's tri-gate FinFET16                                                                                |

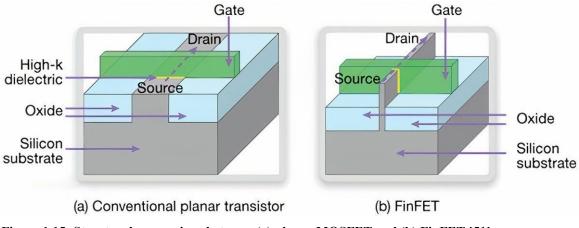

| Figure 1.15: Structural comparison between (a) planar MOSFET and (b) FinFET17                                                                                          |

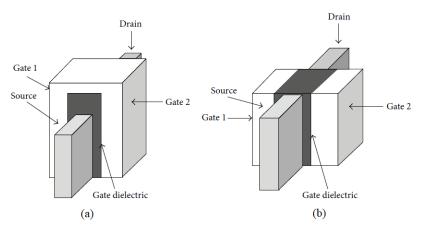

| Figure 1.16: Structural comparison between (a) SG and (b) IG FinFET18                                                                                                  |

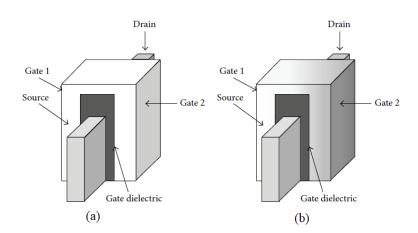

| Figure 1.17: Structural comparison between (a) SG and (b) ASG FinFET                                                                                                   |

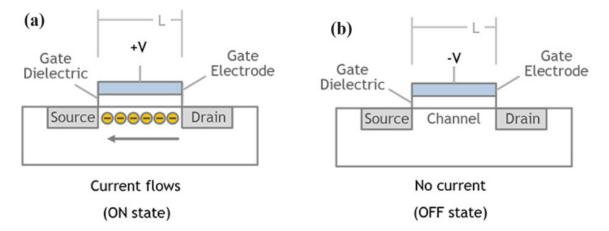

| Figure 1.18: Operating principles of conventional FinFET20                                                                                                             |

| Figure 1.19: Advantages of FinFET device                                                                                                                               |

| Figure 1.20: Challenges associated with FinFET technology                                                                                                              |

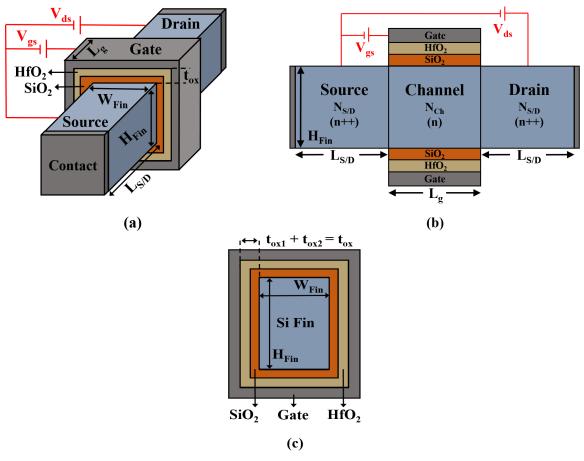

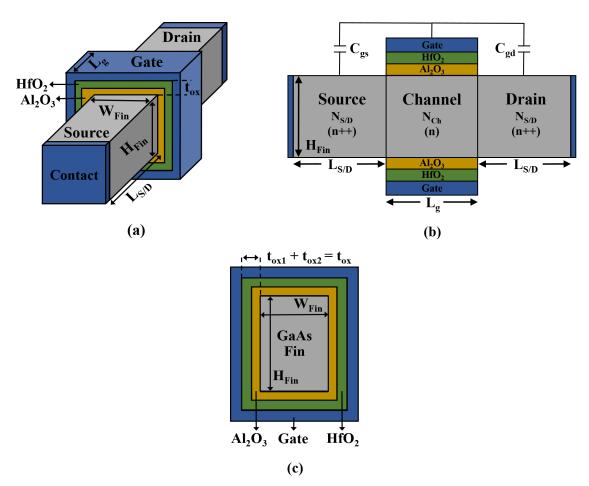

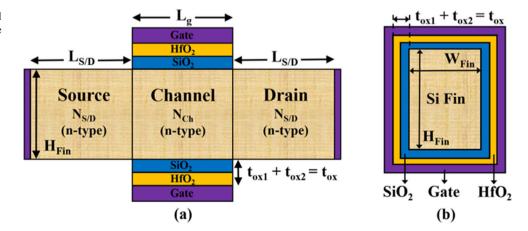

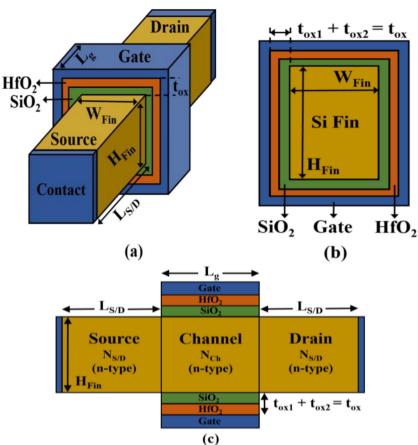

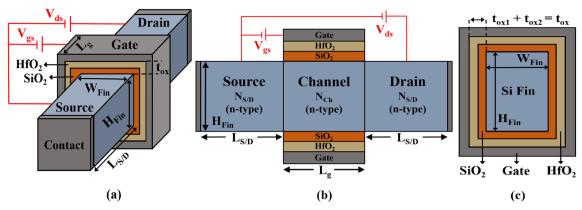

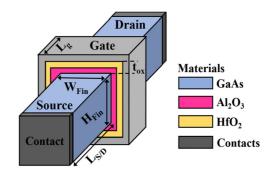

| Figure 2.1: (a) Proposed JAM-GS-GAA FinFET 3-D structure, (b) horizontal, and (c) vertical 2-D view slit through the device's silicon fin                              |

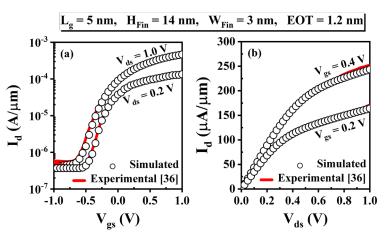

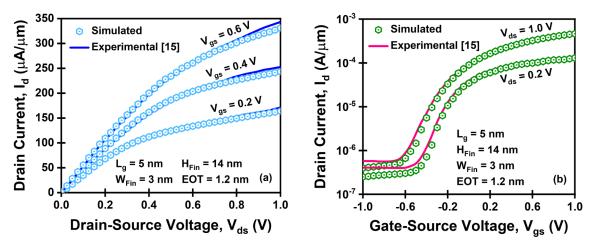

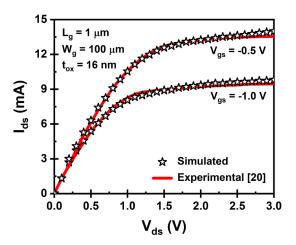

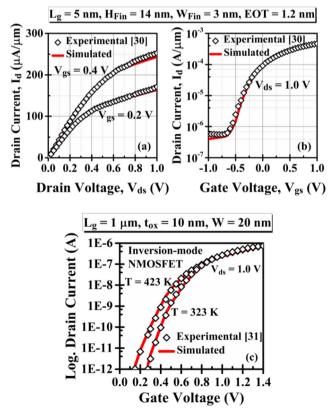

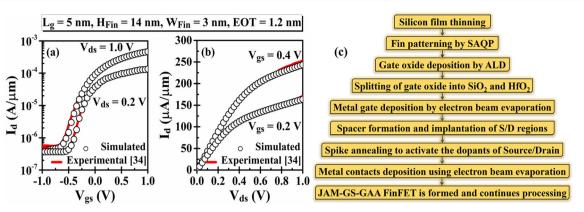

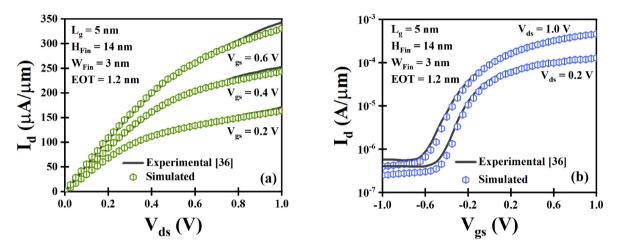

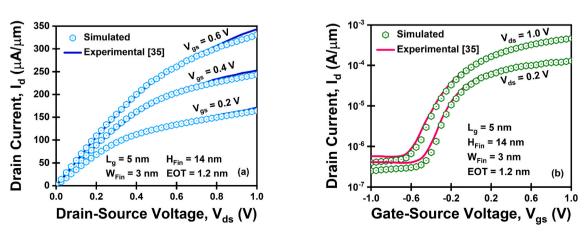

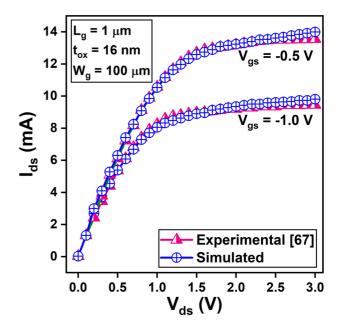

| Figure 2.2: Experimental and simulated (a) transfer and (b) output characteristics of the GAA Si FinFET38                                                              |

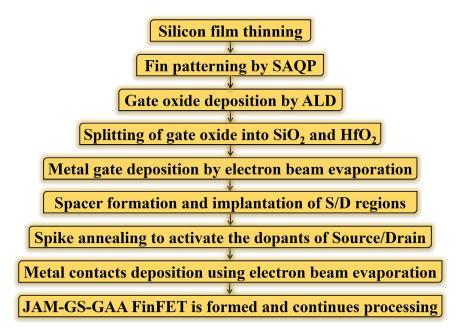

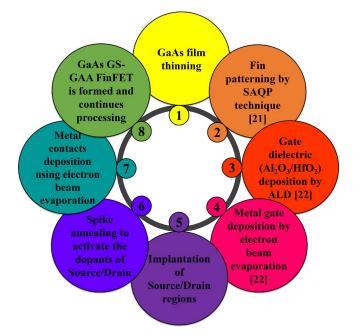

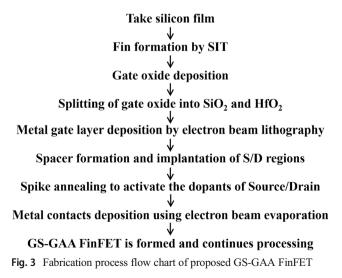

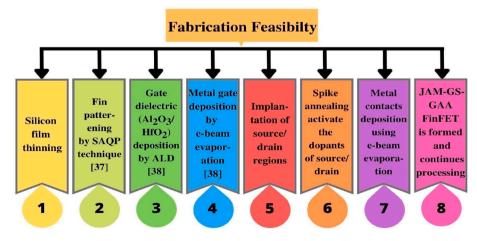

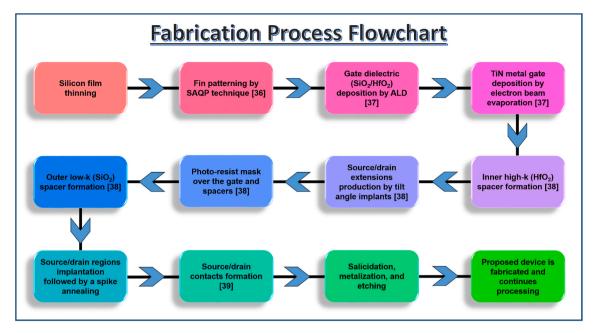

| Figure 2.3: JAM-GS-GAA FinFET step-by-step fabrication outline                                                                                                         |

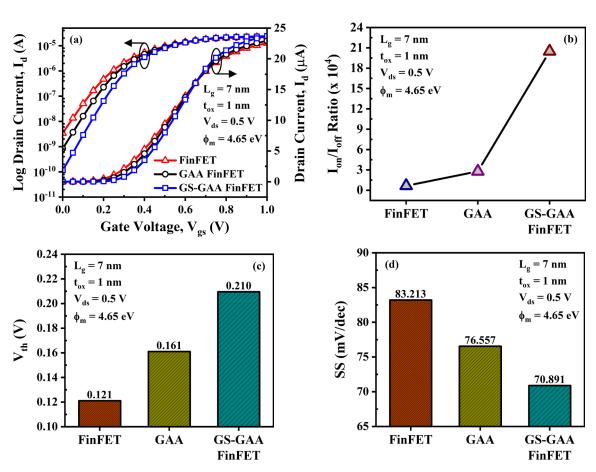

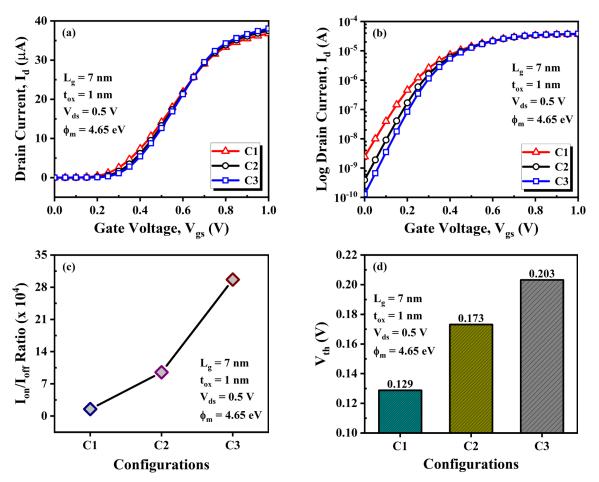

| Figure 2.4: (a) Variation of $I_d$ - $V_{gs}$ in linear and log scales, (b) $I_{on}/I_{off}$ ratio, (c) $V_{th}$ , and (d) SS comparisons for different configurations |

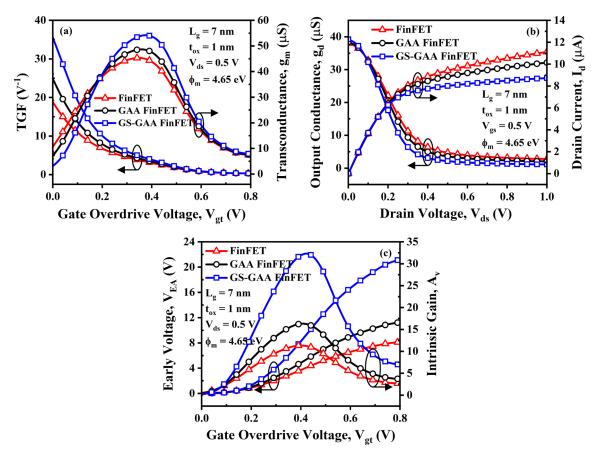

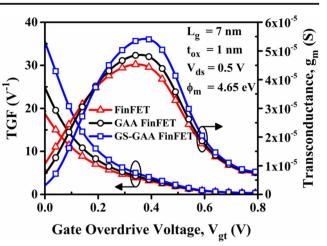

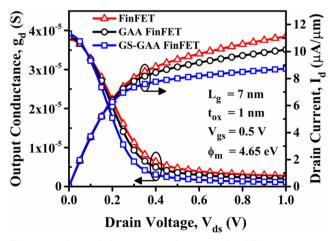

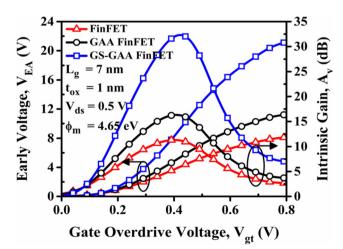

| Figure 2.5: (a) $g_m$ and TGF vs. $V_{gt}$ , (b) $g_d$ and $I_d$ vs. $V_{ds}$ , and (c) $V_{EA}$ and $A_v$ vs. $V_{gt}$ for different structures                       |

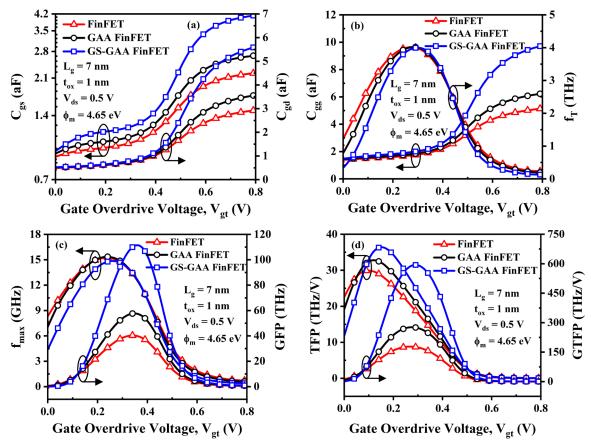

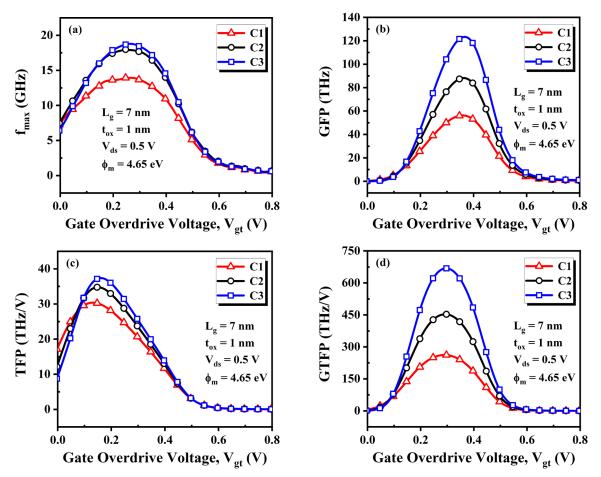

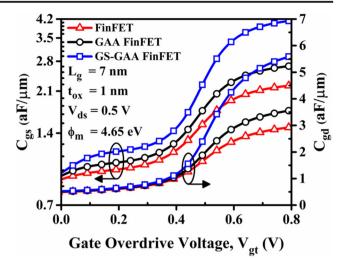

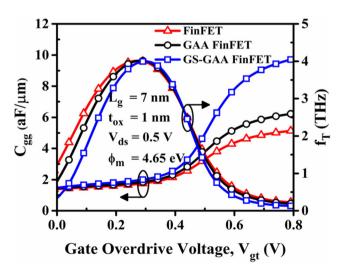

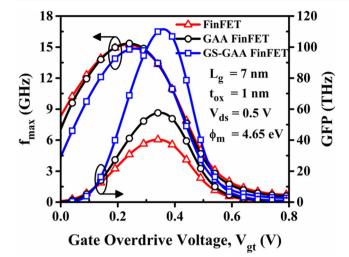

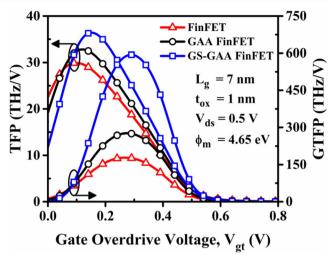

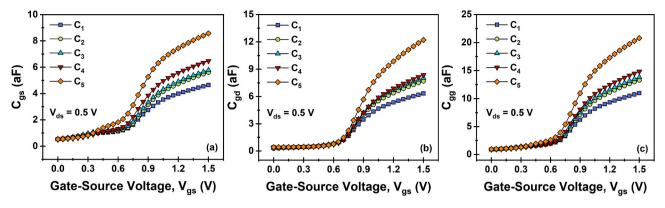

| Figure 2.6: Variation of (a) $C_{gs}$ and $C_{gd}$ to $V_{gt}$ , (b) $C_{gg}$ and $f_T$ to $V_{gt}$ , (c) $f_{max}$ and GFP to $V_{gt}$ , and (d) TFP and GTFP to $V_{gt}$ for each configuration       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

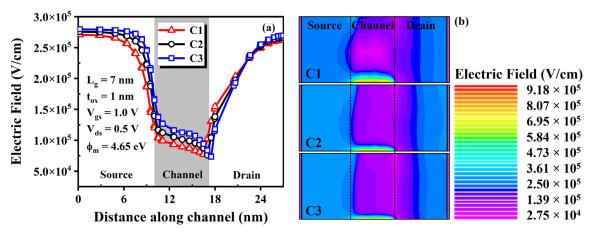

| Figure 2.7: (a) Change in the electric field with the channel distance and (b) electric field contour plot for considered fin aspect ratio configurations                                               |

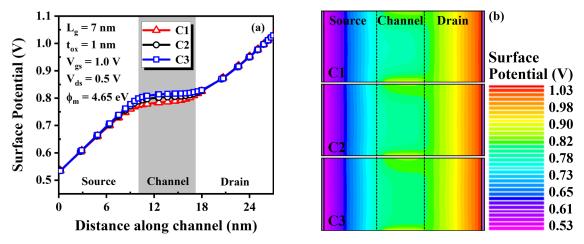

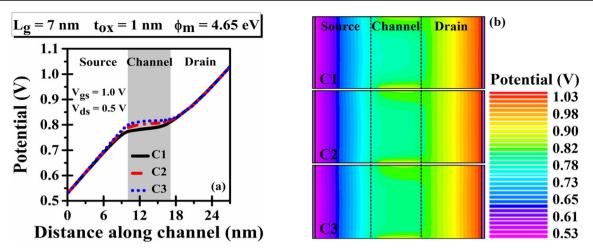

| Figure 2.8: (a) Surface potential profile variation along the channel distance and (b) surface potential contour of all three fin aspect ratio configurations                                           |

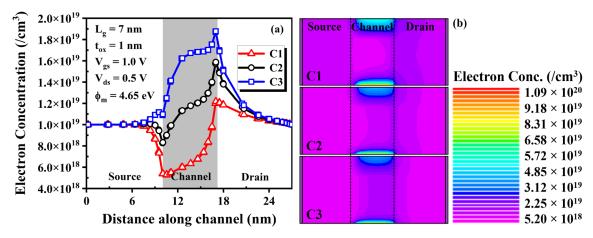

| Figure 2.9: (a) Electron concentration plot against the distance along the channel and (b) electron concentration contour profile of each fin aspect ratio configuration                                |

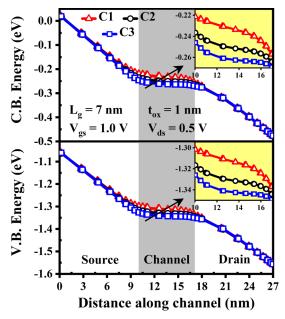

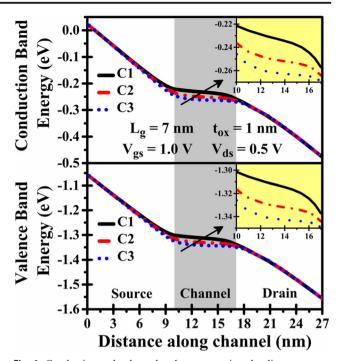

| Figure 2.10: Conduction and valence band energy against the distance across the channel for all considered fin aspect ratio configurations                                                              |

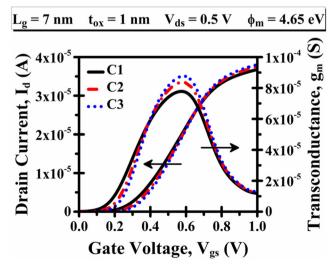

| Figure 2.11: Variation of $I_d$ - $V_{gs}$ in (a) linear and (b) log scales, (c) $I_{on}/I_{off}$ ratio, and (d) $V_{th}$ for different fin aspect ratio configurations                                 |

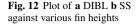

| Figure 2.12: Comparison of (a) SS, (b) g <sub>m</sub> , (c) QF, and (d) TGF for different fin aspect ratio configurations                                                                               |

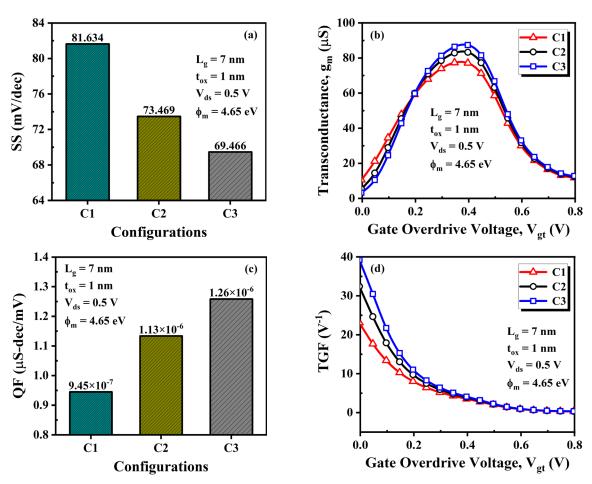

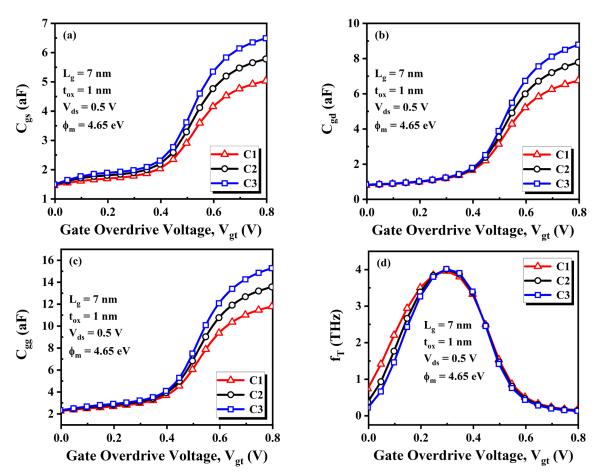

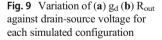

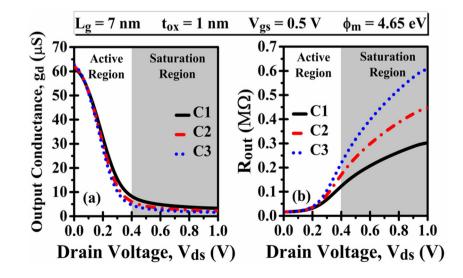

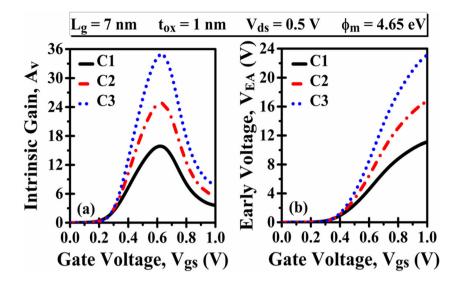

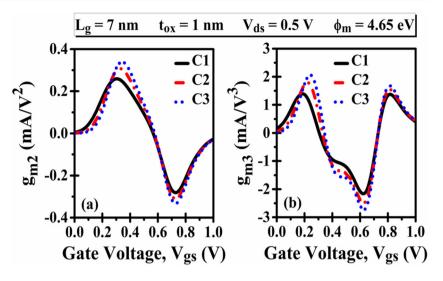

| Figure 2.13: Variation of (a) $g_d$ , (b) $R_{out}$ against $V_{ds}$ , (c) $A_v$ , and (d) $V_{EA}$ against $V_{gt}$ for different fin aspect ratio configurations                                      |

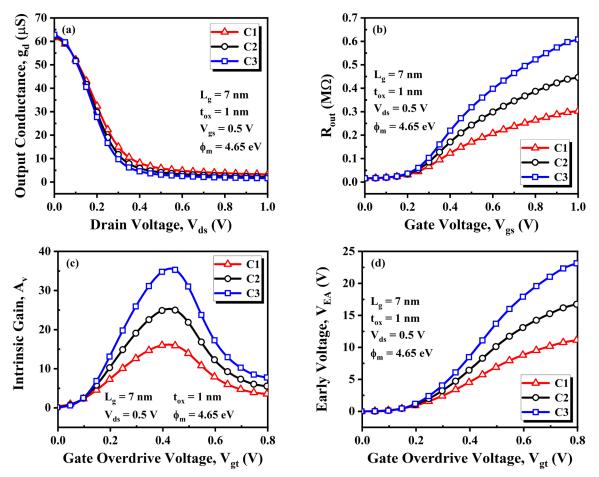

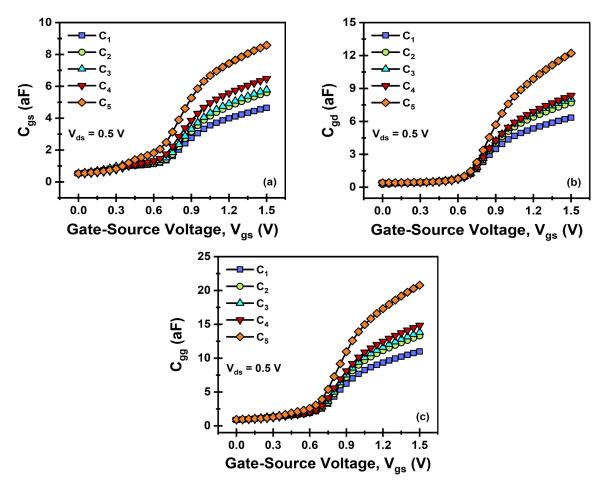

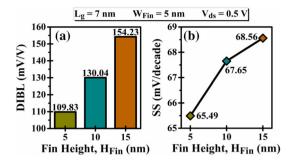

| Figure 2.14: (a) $C_{gs}$ , (b) $C_{gd}$ , (c) $C_{gg}$ , and (d) $f_T$ as a function of $V_{gt}$ for different fin aspect ratio configurations                                                         |

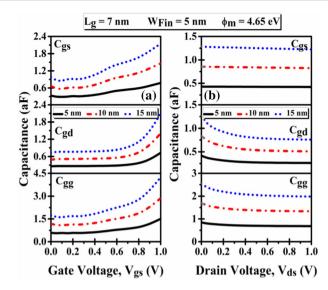

| Figure 2.15: (a) $f_{max}$ , (b) GFP, (c) TFP, and (d) GTFP as a function of $V_{gt}$ for different fin aspect ratio configurations                                                                     |

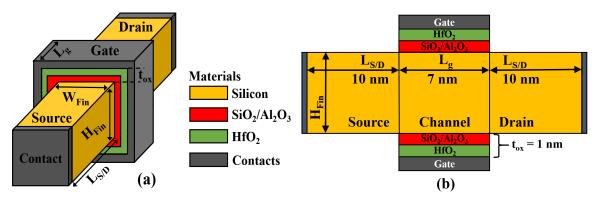

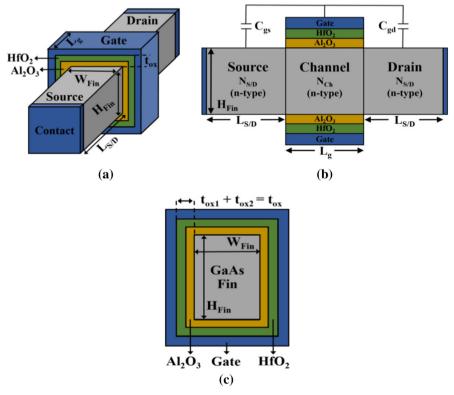

| Figure 3.1: Proposed (a) 3D and (b) 2D horizontally cut structures of JAM-GS-GAA FinFET                                                                                                                 |

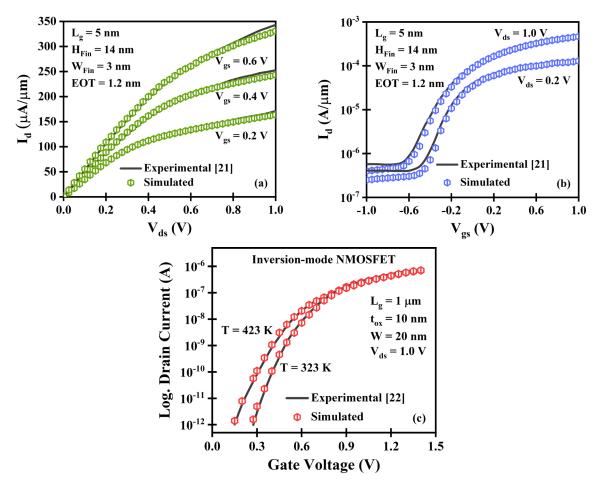

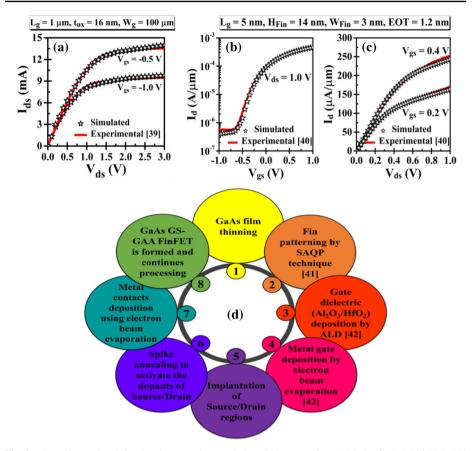

| Figure 3.2: Calibrated (a) $I_d$ - $V_{ds}$ , (b) $I_d$ - $V_{gs}$ characteristics of 5 nm GAA FinFET, and (c) $I_d$ - $V_{gs}$ characteristics at two different temperatures of inversion-mode NMOSFET |

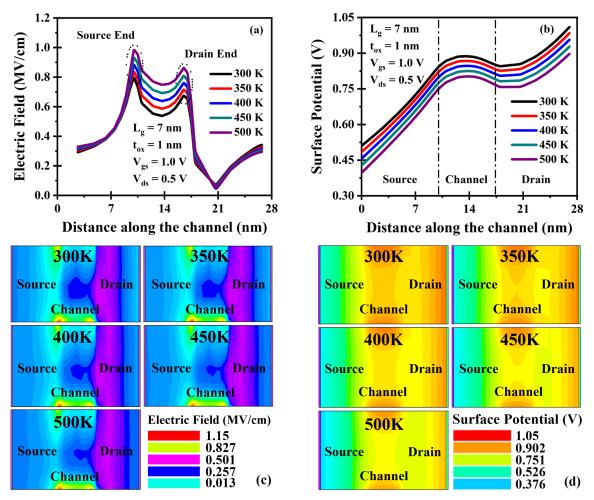

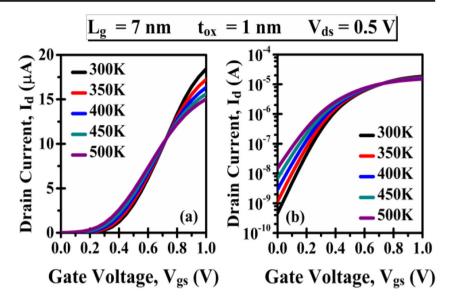

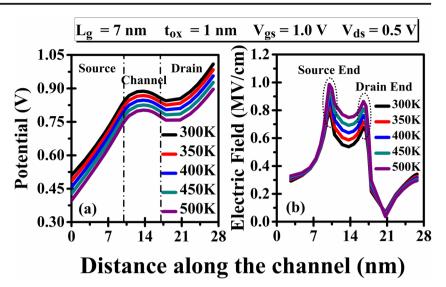

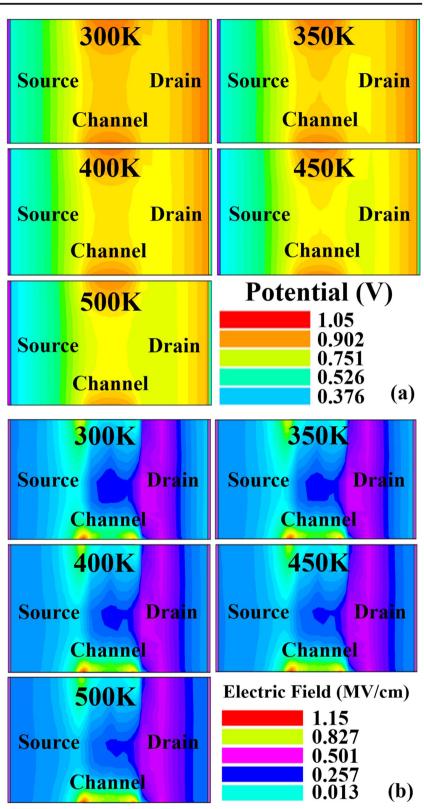

| Figure 3.3: Impact of temperature variation on (a) electric field and (b) surface potential. Contour profile of (c) electric field and (d) surface potential at different temperatures                  |

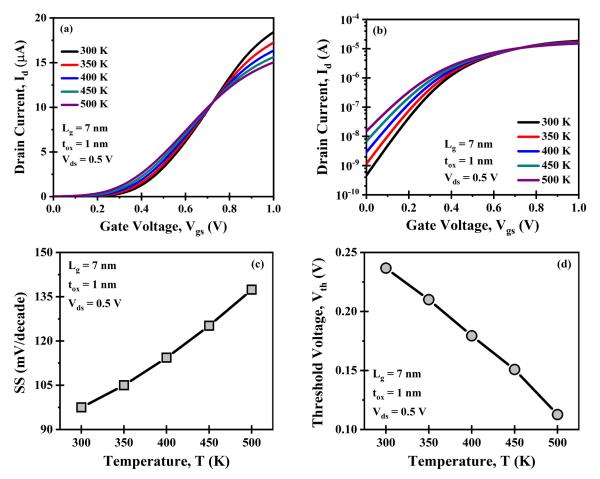

| Figure 3.4: Influence of considered temperatures on (a) $I_{on}$ current, (b) $I_{off}$ current, (c) SS, and (d) $V_{th}$ 72                                                                            |

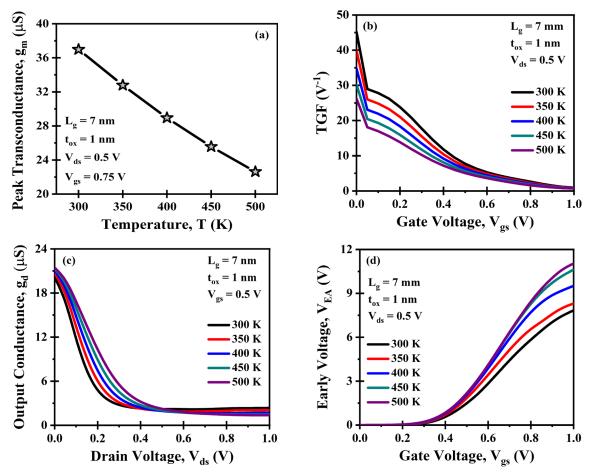

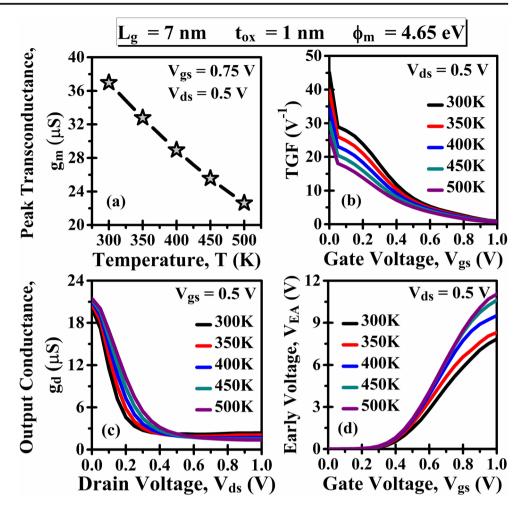

| Figure 3.5: Consequences of the temperature on (a) $g_m$ , (b) TGF, (c) $g_d$ , and (d) $V_{EA}$                                                                                                        |

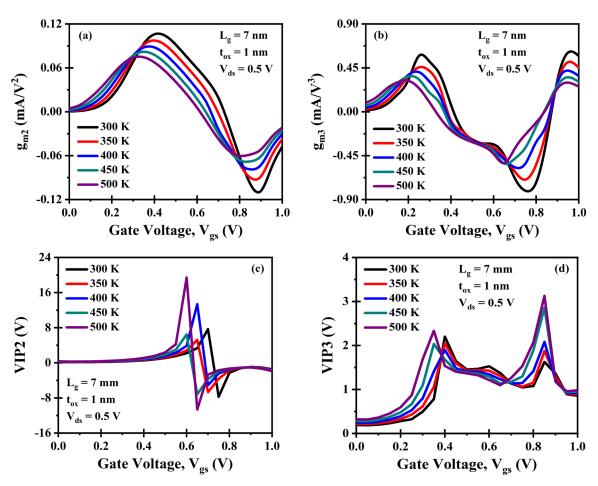

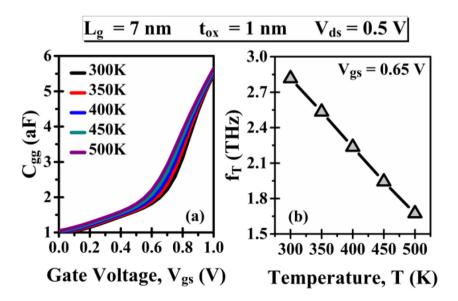

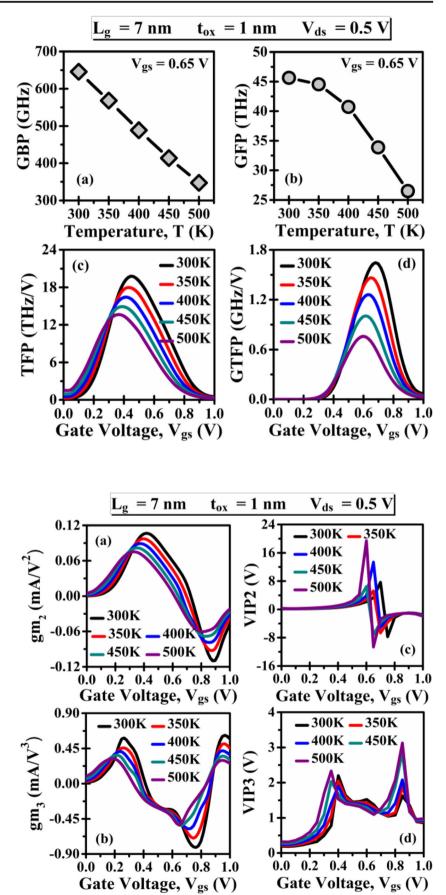

| Figure 3.6: Alteration of (a) $f_T$ , (b) GFP, (c) TFP, and (d) GTFP for the different temperatures75                                                                                                   |

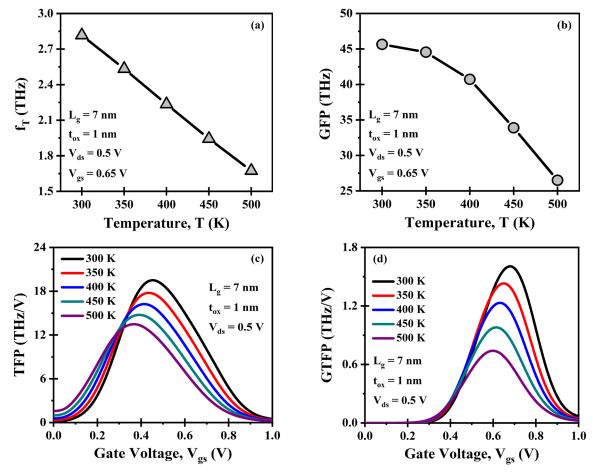

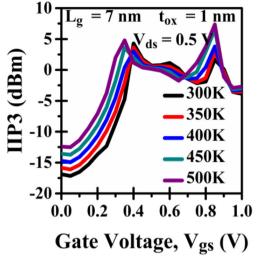

| Figure 3.7: Plot of (a) $g_{m2}$ , (b) $g_{m3}$ , (c) VIP2, and (d) VIP3 concerning the different temperatures                                                                                          |

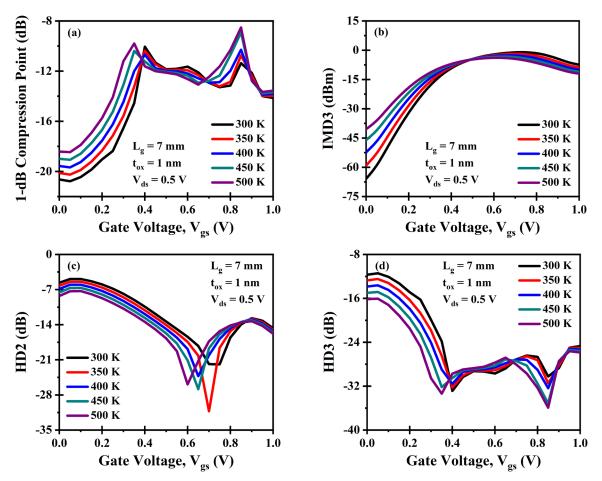

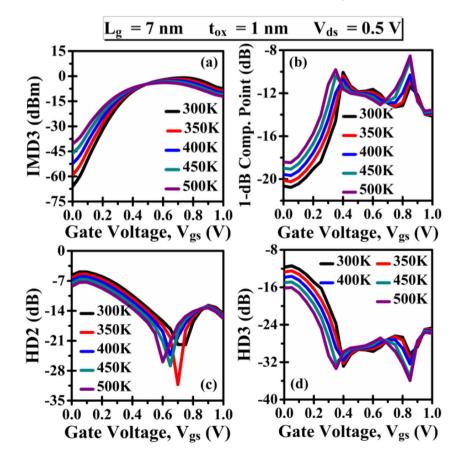

| Figure 3.8: Impact of considered temperatures on (a) 1-dB compression point, (b) IMD3, (c) HD2, and (d) HD3                                                                                             |

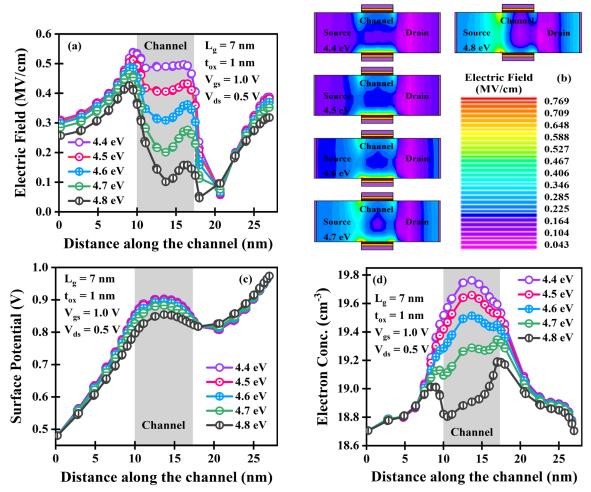

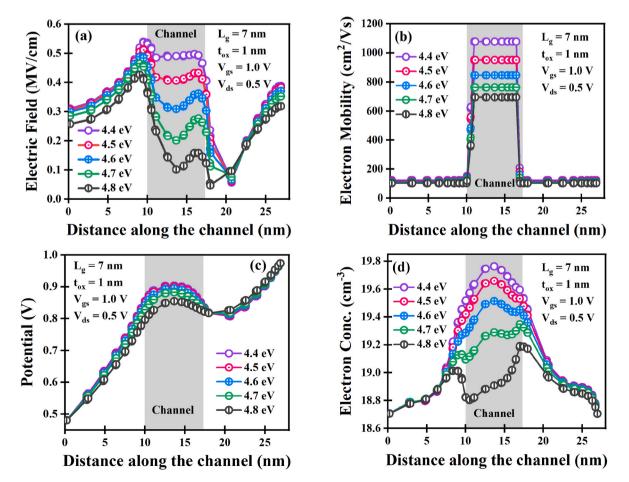

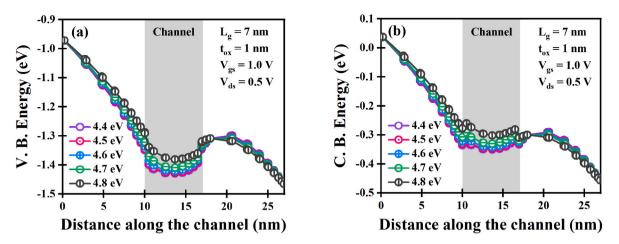

| Figure 3.9: (a) Electric field plot, (b) electric field contour profile, (c) surface potential, and (d) electron concentration for altered gate electrode work functions                                |

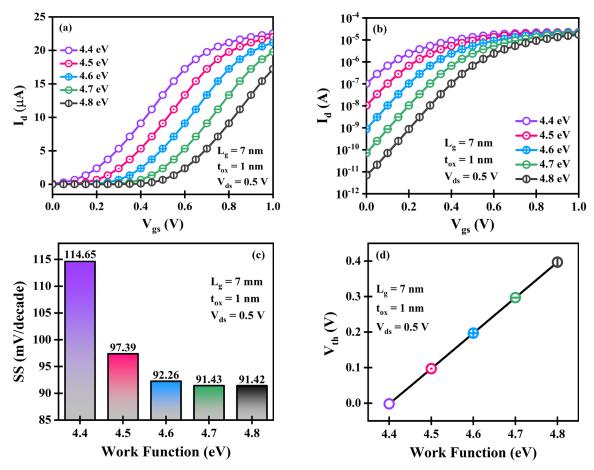

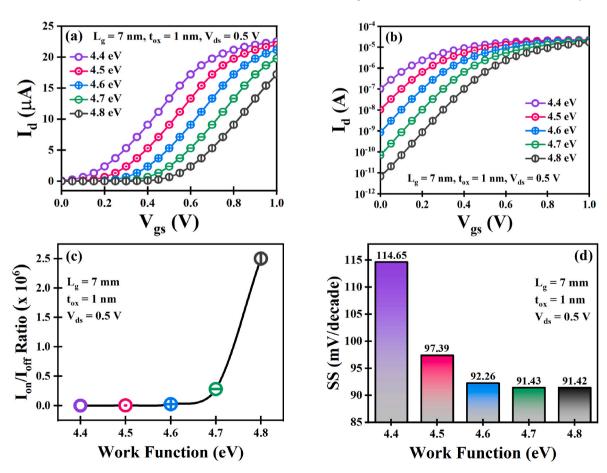

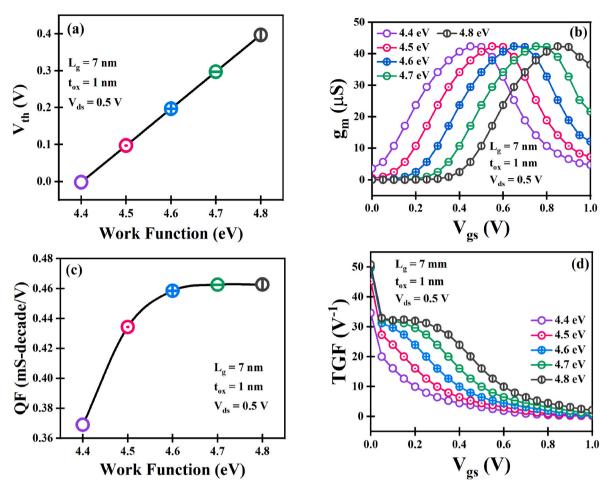

| Figure 3.10: Influence of considered gate electrode work functions on (a) I <sub>on</sub> current, (b) I <sub>off</sub> current, (c) SS, and (d) V <sub>th</sub>                                        |

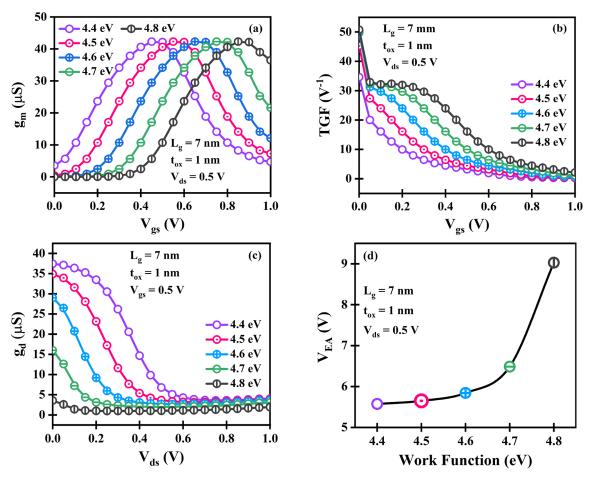

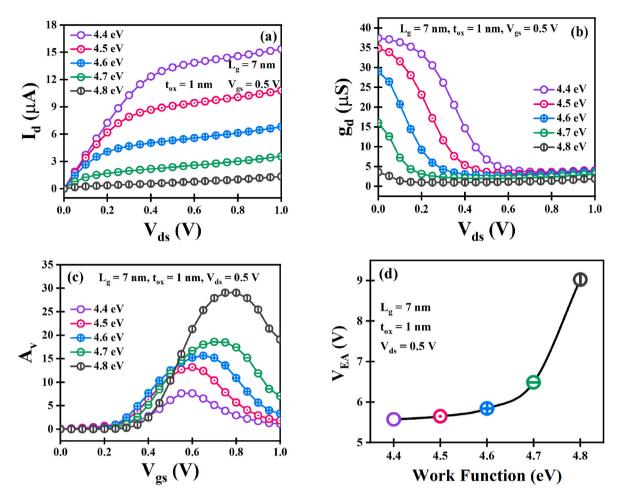

| Figure 3.11: Consequences of the considered gate electrode work function on (a) $g_m$ , (b) TGF, (c) $g_d$ , and (d) $V_{EA}$                                                                           |

|                                                                                                                                                                                                         |

| Figure 3.12: Alteration of (a) $f_T$ , (b) GFP, (c) TFP, and (d) GTFP for the different gate electrode work functions                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.13: Plot of (a) g <sub>m2</sub> , (b) g <sub>m3</sub> , (c) VIP2, and (d) VIP3 concerning the different gate electrode work functions                                                     |

| Figure 3.14: Impact of considered gate electrode work functions on (a) 1-dB compression point, (b) IMD3, (c) HD2, and (d) HD3                                                                      |

| Figure 4.1: (a) Methodical 3D, (b) horizontally sliced 2D, and (c) 3D meshed designs of the proposed JAM-<br>GS-GAA FinFET device with dual-k spacers                                              |

| Figure 4.2: Experimental calibration of the (a) output and (b) transfer characteristics of the GAA FinFET device                                                                                   |

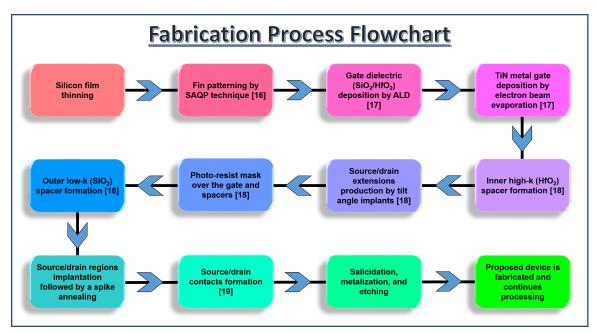

| Figure 4.3: JAM-GS-GAA FinFET with dual-k spacers fabrication process flowchart97                                                                                                                  |

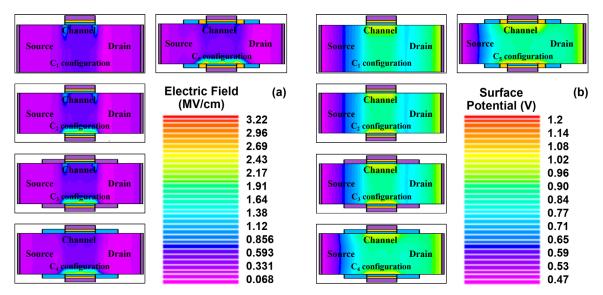

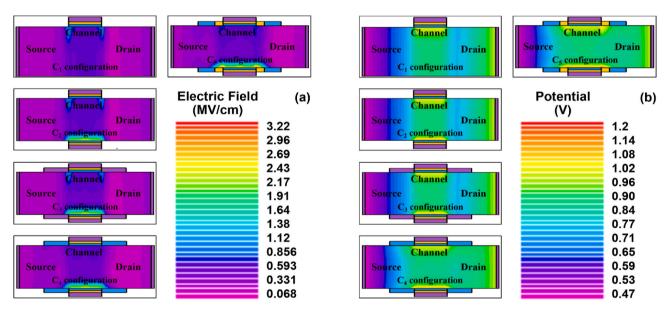

| Figure 4.4: (a) Electric field and (b) surface potential contour plots along the channel across the range of configurations                                                                        |

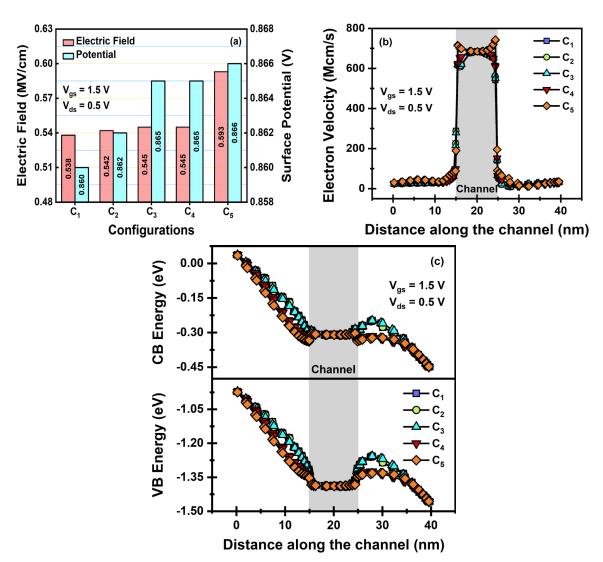

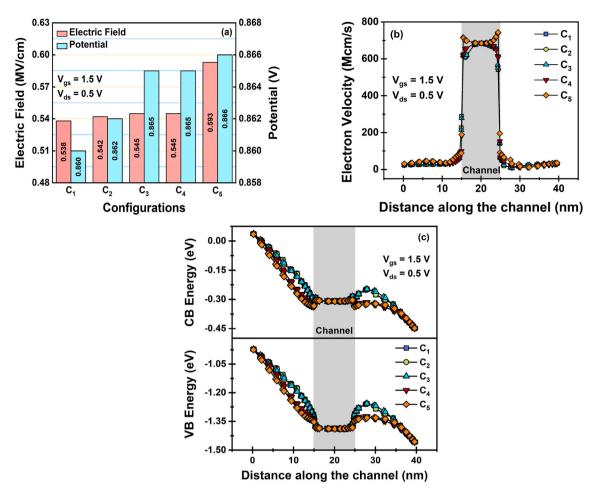

| Figure 4.5: Plot of (a) electric field and potential peak values, (b) electron velocity, and (c) valence and conduction band energy profiles across various configurations                         |

| Figure 4.6: Variation in (a) I <sub>on</sub> , (b) I <sub>off</sub> , (c) I <sub>on</sub> /I <sub>off</sub> ratio, (d) V <sub>th</sub> , (e) DIBL, and (f) SS against the different configurations |

| Figure 4.7: Plot of (a) $I_d$ , (b) $g_d$ , and (c) $R_{out}$ against $V_{ds}$ for all five considered configurations103                                                                           |

| Figure 4.8: Variance of (a) $g_m$ and TGF, (b) QF, (c) $V_{EA}$ , and (d) $A_v$ against $V_{gs}$ for all five considered configurations                                                            |

| Figure 4.9: Spider-chart representation of the variance in peak values of $g_m$ , TGF, $V_{EA}$ , and $A_v$ over the five different combinations                                                   |

| Figure 4.10: Plot of (a) $C_{gs}$ , (b) $C_{gd}$ , and (c) $C_{gg}$ against $V_{gs}$ for the different configurations                                                                              |

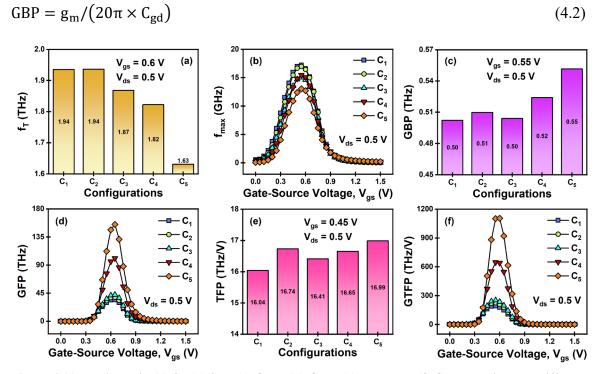

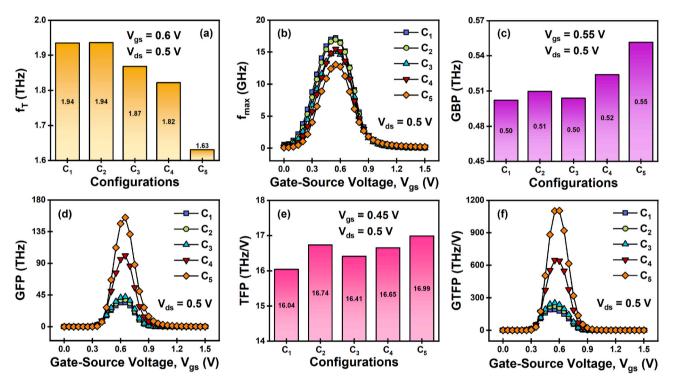

| Figure 4.11: Variance in (a) $f_T$ , (b) $f_{max}$ , (c) GBP, (d) GFP, (e) TFP, and (f) GTFP against the different configurations                                                                  |

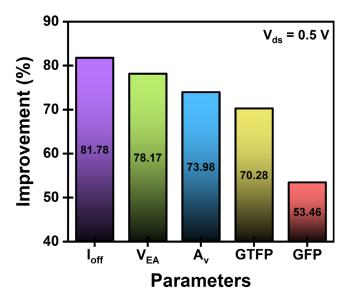

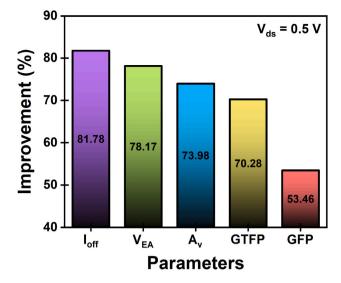

| Figure 4.12: Representation of the improvement in $I_{off}$ , $V_{EA}$ , $A_v$ , GTFP, and GFP parameters following the transition from the C <sub>4</sub> to the C <sub>5</sub> configuration     |

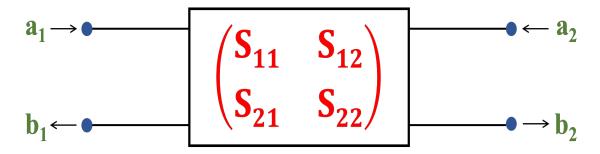

| Figure 5.1: Generalized two-port network for S-parameter measurement                                                                                                                               |

| Figure 5.2: (a) Systematic simulated 3-D structure, (b) horizontal, and (c) vertical 2-D view of GaAs JAM-GS-GAA FinFET with parasitic capacitances                                                |

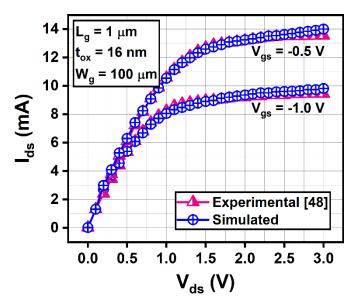

| Figure 5.3: Experimental and simulated output characteristics of Al <sub>2</sub> O <sub>3</sub> /GaAs MOSFET121                                                                                    |

| Figure 5.4: Fabrication process flowchart of proposed GaAs JAM-GS-GAA FinFET122                                                                                                                    |

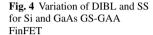

| Figure 5.5: Variation in (a) transfer characteristics, (b) switching ratio, (c) threshold voltage, and (d) DIBL and SS for silicon and GaAs JAM-GS-GAA FinFET                                      |

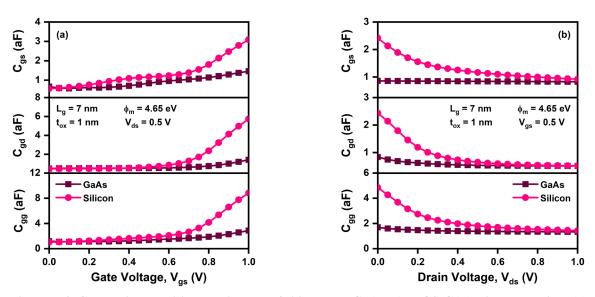

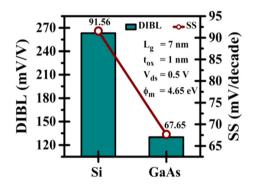

| Figure 5.6: Change in parasitic capacitances of silicon and GaAs JAM-GS-GAA FinFET against (a) gate voltage and (b) drain voltage                                                                  |

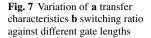

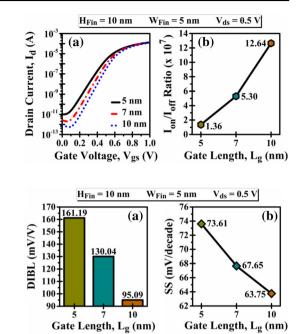

| $      Figure 5.8: Impact of L_{g}, N_{Ch}, W_{Fins}, \phi_{m}, and T on (a) L_{on}, (b) L_{off}, (c) L_{of}/L_{off} ratio, and (d) SS of GaAs JAM-GS-GAA FinFET$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure 5.7: Plot of (a) GBP and (b) TFP against $V_{gs}$ for silicon and GaAs JAM-GS-GAA FinFET125                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{gs} = 129$ Figure 5.10: Change in parasitic capacitances for different (a) L <sub>gs</sub> , (b) N <sub>Ch</sub> , (c) W <sub>Fin</sub> , (d) $\phi_{ms}$ and (e) T against<br>Va. 131 Figure 5.11: Variations of (a) S <sub>11</sub> , (b) S <sub>22</sub> , (c) S <sub>12</sub> , and (d) S <sub>21</sub> of the GaAs JAM-GS-GAA FinFET at THz<br>frequencies for different gate lengths 133 Figure 5.12: Variations of (a) S <sub>11</sub> , (b) S <sub>22</sub> , (c) S <sub>12</sub> , and (d) S <sub>21</sub> of the GaAs JAM-GS-GAA FinFET at THz<br>frequencies for different channel dopings 134 Figure 5.13: Variations of (a) S <sub>11</sub> , (b) S <sub>22</sub> , (c) S <sub>12</sub> , and (d) S <sub>21</sub> of the GaAs JAM-GS-GAA FinFET at THz<br>frequencies for different fin widths 135 Figure 5.14: Variations of (a) S <sub>11</sub> , (b) S <sub>22</sub> , (c) S <sub>12</sub> , and (d) S <sub>21</sub> of the GaAs JAM-GS-GAA FinFET at THz<br>frequencies for different fin widths 135 Figure 5.14: Variations of (a) S <sub>11</sub> , (b) S <sub>22</sub> , (c) S <sub>12</sub> , and (d) S <sub>21</sub> of the GaAs JAM-GS-GAA FinFET at THz<br>frequencies for different gate electrode work functions 136 Figure 5.15: Variations of (a) S <sub>11</sub> , (b) S <sub>22</sub> , (c) S <sub>12</sub> , and (d) S <sub>21</sub> of the GaAs JAM-GS-GAA FinFET at THz<br>frequencies for different temperatures 137 Figure 6.1: Symmetric 3D view of the GaAs JAM-GS-GAA FinFET 148 Figure 6.2: Calibration curve of an Al <sub>2</sub> O <sub>3</sub> /GaAs MOSFET. 150 Figure 6.4: (a) Transfer characteristics in linear and log form for air, MCF-10A, and MDA-MB-231, (b) fluctuation in I <sub>m</sub> , I <sub>m</sub> , and SR for air, MCF-10A, and MDA-MB-231. (c) S <sub>30</sub> comparison of MDA-MB-231 and MCF-10A cells, and (d) LoD plot for air, MCF-10A, and MDA-MB-231 cancer cell |                                                                                                                                                                                                  |

| Va.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                  |

| frequencies for different gate lengths       133         Figure 5.12: Variations of (a) S11, (b) S22, (c) S12, and (d) S21 of the GaAs JAM-GS-GAA FinFET at THz         frequencies for different channel dopings       134         Figure 5.13: Variations of (a) S11, (b) S22, (c) S12, and (d) S21 of the GaAs JAM-GS-GAA FinFET at THz         frequencies for different fin widths       135         Figure 5.14: Variations of (a) S11, (b) S22, (c) S12, and (d) S21 of the GaAs JAM-GS-GAA FinFET at THz         frequencies for different gate electrode work functions       136         Figure 5.15: Variations of (a) S11, (b) S22, (c) S12, and (d) S21 of the GaAs JAM-GS-GAA FinFET at THz       frequencies for different temperatures.         137       Figure 6.1: Symmetric 3D view of the GaAs JAM-GS-GAA FinFET       148         Figure 6.2: Calibration curve of an Al <sub>2</sub> O <sub>3</sub> /GaAs MOSFET.       150         Figure 6.3: Diagrammatic representation of the operation of a GaAs JAM-GS-GAA FinFET sensor for breast cancer cell recognition       151         Figure 6.4: (a) Transfer characteristics in linear and log form for air, MCF-10A, and MDA-MB-231, (b) fluctuation in I <sub>on</sub> , I <sub>off</sub> , and SR for air, MCF-10A, and MDA-MB-231, (c) S <sub>38</sub> comparison of MDA-MB-231 and MCF-10A cells, and (d) LoD plot for air, MCF-10A, and MDA-MB-231 cancer cell       152         Figure 6.5: Transient response of the drain current for air, MCF-10A, and MDA-MB-231 cells and (b) temperature dependence of the I <sub>4</sub> - V <sub>gs</sub> characteristics of the MDA-MB-231 cancer cell       153         Figure 6.7: Variat                                                                                                                                                                                                                           |                                                                                                                                                                                                  |

| frequencies for different channel dopings       134         Figure 5.13: Variations of (a) S <sub>11</sub> , (b) S <sub>22</sub> , (c) S <sub>12</sub> , and (d) S <sub>21</sub> of the GaAs JAM-GS-GAA FinFET at THz         frequencies for different fin widths       135         Figure 5.14: Variations of (a) S <sub>11</sub> , (b) S <sub>22</sub> , (c) S <sub>12</sub> , and (d) S <sub>21</sub> of the GaAs JAM-GS-GAA FinFET at THz         frequencies for different gate electrode work functions       136         Figure 5.15: Variations of (a) S <sub>11</sub> , (b) S <sub>22</sub> , (c) S <sub>12</sub> , and (d) S <sub>21</sub> of the GaAs JAM-GS-GAA FinFET at THz         frequencies for different temperatures       137         Figure 6.1: Symmetric 3D view of the GaAs JAM-GS-GAA FinFET       148         Figure 6.2: Calibration curve of an Al <sub>2</sub> O <sub>3</sub> /GaAs MOSFET       150         Figure 6.4: (a) Transfer characteristics in linear and log form for air, MCF-10A, and MDA-MB-231, (b)       fluctuation in I <sub>an</sub> , I <sub>an</sub> , and SR for air, MCF-10A, and MDA-MB-231, (c) S <sub>SR</sub> comparison of MDA-MB-231, and MCF-10A cells, and (d) LoD plot for air, MCF-10A, and MDA-MB-231 cells and (b)         figure 6.5: Transient response of the drain current for air, MCF-10A, and MDA-MB-231 cells and (b)       153         Figure 6.6: Transient response of the proposed sensor for MDA-MB-231 cancerous cells over four cycles       153         Figure 6.7: Variation in I <sub>an</sub> , I <sub>aff</sub> , SR, and S <sub>SR</sub> of living and dead MCF-10A breast cells       155         Figure 6.8: Transfer characteristics for five different combinations in (a) linear and (b) log form, and (c)       157         Figure 6.9: B                                                                                                        |                                                                                                                                                                                                  |

| frequencies for different fin widths       135         Figure 5.14: Variations of (a) S11, (b) S22, (c) S12, and (d) S21 of the GaAs JAM-GS-GAA FinFET at THz       frequencies for different gate electrode work functions         136       Figure 5.15: Variations of (a) S11, (b) S22, (c) S12, and (d) S21 of the GaAs JAM-GS-GAA FinFET at THz         frequencies for different temperatures       137         Figure 6.1: Symmetric 3D view of the GaAs JAM-GS-GAA FinFET       148         Figure 6.2: Calibration curve of an Al <sub>2</sub> O <sub>3</sub> /GaAs MOSFET       150         Figure 6.3: Diagrammatic representation of the operation of a GaAs JAM-GS-GAA FinFET sensor for breast cancer cell recognition       151         Figure 6.4: (a) Transfer characteristics in linear and log form for air, MCF-10A, and MDA-MB-231, (b) fluctuation in I <sub>an</sub> , I <sub>aff</sub> , and SR for air, MCF-10A, and MDA-MB-231, (c) SsR comparison of MDA-MB-231 and MCF-10A cells, and (d) LoD plot for air, MCF-10A, and MDA-MB-231 cancer cell       152         Figure 6.5: Transient response of the drain current for air, MCF-10A, and MDA-MB-231 cancer cell       153         Figure 6.6: Transient response of the proposed sensor for MDA-MB-231 cancer ous cells over four cycles       153         Figure 6.7: Variation in I <sub>an</sub> , I <sub>aff</sub> , SR, and SsR of living and dead MCF-10A breast cells       155         Figure 6.7: Variation in I <sub>an</sub> , I <sub>aff</sub> , SR, and SsR of living and dead MCF-10A and (b) MDA-MB-231, and (c) sensitivity performance for healthy and malignant cells against different γ <sub>Blo</sub> 158         Figure 6.9: Biomolecule occupanc                                                                                                                                                                                        |                                                                                                                                                                                                  |

| frequencies for different gate electrode work functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                  |

| frequencies for different temperatures       137         Figure 6.1: Symmetric 3D view of the GaAs JAM-GS-GAA FinFET       148         Figure 6.2: Calibration curve of an Al <sub>2</sub> O <sub>3</sub> /GaAs MOSFET       150         Figure 6.3: Diagrammatic representation of the operation of a GaAs JAM-GS-GAA FinFET sensor for breast cancer cell recognition       151         Figure 6.4: (a) Transfer characteristics in linear and log form for air, MCF-10A, and MDA-MB-231, (b) fluctuation in I <sub>on</sub> , I <sub>off</sub> , and SR for air, MCF-10A, and MDA-MB-231, (c) S <sub>SR</sub> comparison of MDA-MB-231 and MCF-10A cells, and (d) LoD plot for air, MCF-10A, and MDA-MB-231       152         Figure 6.5: Transient response of the drain current for air, MCF-10A, and MDA-MB-231 cells and (b) temperature dependence of the I <sub>d</sub> - V <sub>gs</sub> characteristics of the MDA-MB-231 cancer cell       153         Figure 6.6: Transient response of the proposed sensor for MDA-MB-231 cancerous cells over four cycles       153         Figure 6.7: Variation in I <sub>on</sub> , I <sub>off</sub> , SR, and S <sub>SR</sub> of living and dead MCF-10A breast cells       155         Figure 6.8: Transfer characteristics for five different combinations in (a) linear and (b) log form, and (c) variation in I <sub>on</sub> , I <sub>off</sub> , SR, and S <sub>SR</sub> of living and dead MCF-10A and (b) MDA-MB-231, and (c) sensitivity performance for healthy and malignant cells against different γ <sub>Bio</sub> Figure 6.10: S <sub>SR</sub> of the proposed sensor against the deviation of mentioned parameters for the MDA-MB-231       158         Figure 6.10: S <sub>SR</sub> of the proposed sensor against the deviation of an Ion (a) linear and (b) MDA-MB-231, and (c) sensitivity performance for healthy and malignant c                                     |                                                                                                                                                                                                  |

| Figure 6.2: Calibration curve of an Al <sub>2</sub> O <sub>3</sub> /GaAs MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 5.15: Variations of (a) S <sub>11</sub> , (b) S <sub>22</sub> , (c) S <sub>12</sub> , and (d) S <sub>21</sub> of the GaAs JAM-GS-GAA FinFET at THz frequencies for different temperatures |

| Figure 6.3: Diagrammatic representation of the operation of a GaAs JAM-GS-GAA FinFET sensor for breast cancer cell recognition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 6.1: Symmetric 3D view of the GaAs JAM-GS-GAA FinFET                                                                                                                                      |

| cancer cell recognition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Figure 6.2: Calibration curve of an Al <sub>2</sub> O <sub>3</sub> /GaAs MOSFET150                                                                                                               |

| fluctuation in $I_{on}$ , $I_{off}$ , and SR for air, MCF-10A, and MDA-MB-231, (c) S <sub>SR</sub> comparison of MDA-MB-231<br>and MCF-10A cells, and (d) LoD plot for air, MCF-10A, and MDA-MB-231                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                  |

| temperature dependence of the I <sub>d</sub> - V <sub>gs</sub> characteristics of the MDA-MB-231 cancer cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | fluctuation in Ion, Ioff, and SR for air, MCF-10A, and MDA-MB-231, (c) SSR comparison of MDA-MB-231                                                                                              |

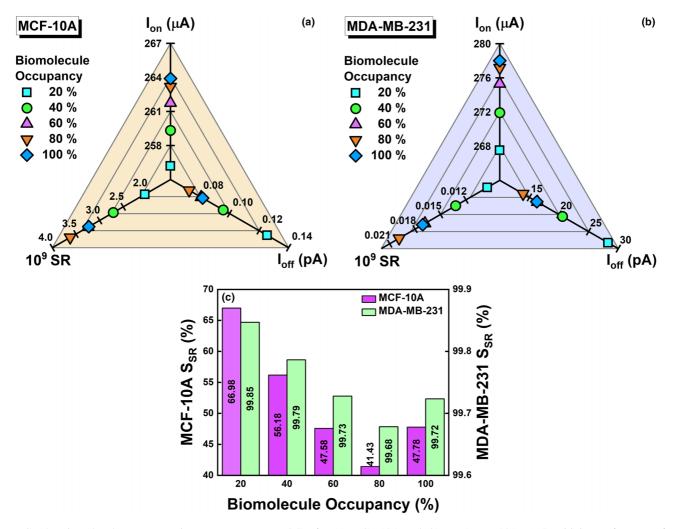

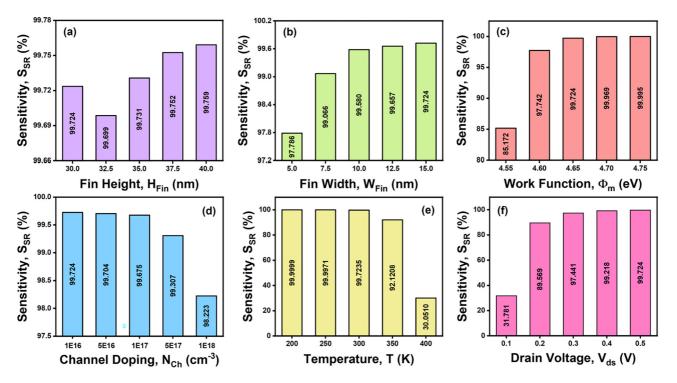

| 153Figure 6.7: Variation in Ion, Ioff, SR, and SSR of living and dead MCF-10A breast cells155Figure 6.8: Transfer characteristics for five different combinations in (a) linear and (b) log form, and (c)variation in Ion, Ioff, and SR for the combinations considered157Figure 6.9: Biomolecule occupancy impact on Ion, Ioff, and SR for (a) MCF-10A and (b) MDA-MB-231, and(c) sensitivity performance for healthy and malignant cells against different $\gamma_{Bio}$ 158Figure 6.10: SSR of the proposed sensor against the deviation of mentioned parameters for the MDA-MB-231159Figure 6.11: Percentage change in each mentioned performance parameter for MDA-MB-231 and MCF-10A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                  |

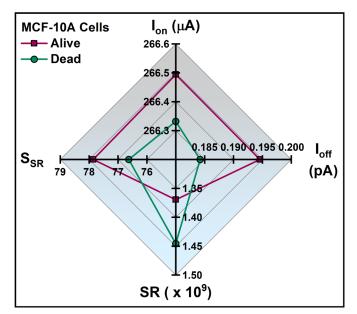

| Figure 6.7: Variation in $I_{on}$ , $I_{off}$ , SR, and $S_{SR}$ of living and dead MCF-10A breast cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                  |

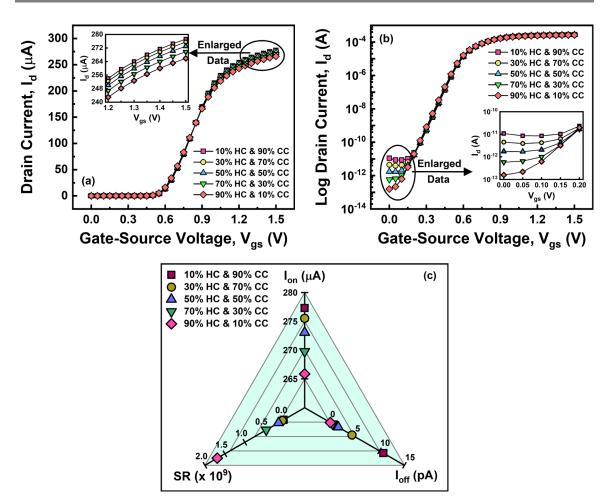

| variation in I <sub>on</sub> , I <sub>off</sub> , and SR for the combinations considered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                  |

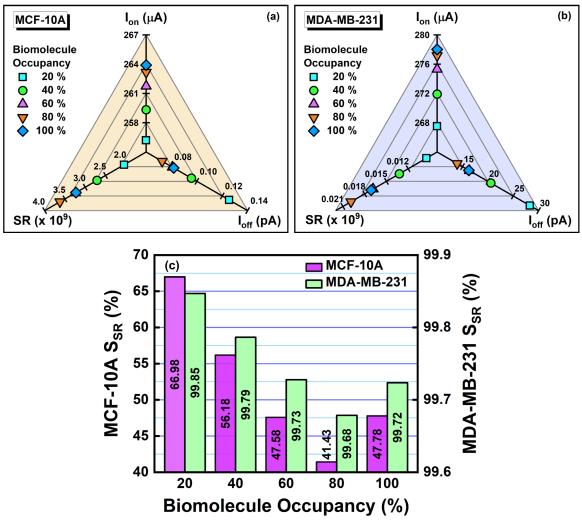

| (c) sensitivity performance for healthy and malignant cells against different $\gamma_{Bio}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                  |

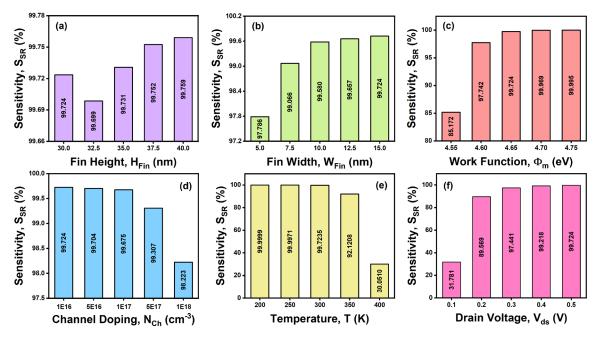

| cancerous cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                  |

# LIST OF TABLES

| Table 2.1: Different device configurations used for simulation                                    |

|---------------------------------------------------------------------------------------------------|

| Table 2.2: Summary of electrostatic and analog parameters for different structures                |

| Table 2.3: Summary of RF parameters for different structures                                      |

| Table 2.4: Summary of different static, analog, and RF parameters of each simulated configuration |

| Table 3.1: Comparison of JAM-GS-GAA FinFET with existing devices at fixed $L_g = 10$ nm70         |

| Table 3.2: Comparison of two oxide layers used for simulation                                     |

| Table 4.1: Details of different configurations used for comparison                                |

| Table 4.2: Values of different parameters used for simulation                                     |

| Table 4.3: Overview of the prominent static, analog, and RF $\Delta$ FoMs110                      |

| Table 5.1: Summary of different analog metrics and parasitic capacitances for silicon and GaAs    |

| Table 6.1: Different simulation parameters and their values                                       |

| Table 6.2: Overview of proposed FinFET-based cancer detector vs. existing cancer detectors        |

#### **PUBLICATIONS RESULTING FROM THIS THESIS WORK (14)**

#### ARTICLES IN INTERNATIONAL REFEREED JOURNALS (7):

- B. Kumar and R. Chaujar, "Analog and RF performance evaluation of junctionless accumulation mode (JAM) gate stack gate all around (GS-GAA) FinFET," *Silicon*, vol. 13, pp. 919-927, 2021. (IF – 3.4)

- B. Kumar and R. Chaujar, "TCAD temperature analysis of gate stack gate all around (GS-GAA) FinFET for improved RF and wireless performance," *Silicon*, vol. 13, pp. 3741-3753, 2021. (IF 3.4)

- B. Kumar and R. Chaujar, "Numerical study of JAM-GS-GAA FinFET: A fin aspect ratio optimization for upgraded analog and intermodulation distortion performance," *Silicon*, vol. 14, pp. 309-321, 2022. (IF 3.4)

- B. Kumar and R. Chaujar, "Numerical simulation of analog metrics and parasitic capacitances of GaAs GS-GAA FinFET for ULSI switching applications," *The European Physical Journal Plus*, vol. 137, 110, 2022. (IF 3.4)

- 5. **B. Kumar**, M. Sharma, and R. Chaujar, "Gate electrode work function engineered JAM-GS-GAA FinFET for analog/RF applications: Performance estimation and optimization," *Microelectronics Journal*, vol. 135, 105766, 2023. (IF 2.2)

- 6. B. Kumar, M. Sharma, and R. Chaujar, "Junctionless-accumulation-mode stacked gate GAA FinFET with dual-k spacer for reliable RFIC design," *Microelectronics Journal*, vol. 139, 105910, 2023. (IF 2.2)

- B. Kumar and R. Chaujar, "Fin field-effect-transistor engineered sensor for detection of MDA-MB-231 breast cancer cells: A switching-ratio-based sensitivity analysis," *Physical Review E*, vol. 108, 034408, 2023. (IF – 2.4)

#### **CHAPTERS CONTRIBUTED IN BOOKS (2):**

- 1. **B. Kumar** and R. Chaujar, "Fin aspect ratio optimization of novel junctionless gate stack gate all around (GS-GAA) FinFET for analog/RF applications," *Microelectronics, Circuits and Systems, Lecture Notes in Electrical Engineering*, vol. 755, pp. 59-67, 2021.