# TCAD Analysis and Simulation of T-Gate E-Mode GaN HEMT

Thesis Submitted by

# **MEGHA SHARMA**

In Partial Fulfillment of the Requirements for the Degree of **DOCTOR OF PHILOSOPHY**

Under the Supervision of

# Prof. Rishu Chaujar

Department of Applied Physics Delhi Technological UniversityDelhi, India.

July-2023

In the memory of my late father in law.....

**Delhi Technological University** (Govt. of National Capital Territory of Delhi) Bawana Road, Delhi-110042

## **CERTIFICATE**

This is to certify that the thesis titled "*TCAD Analysis and Simulation of T-Gate E-Mode GaN HEMT*" is being submittedby *Ms. MEGHA SHARMA* with registration number *2K18/PHDAP/18* to the Delhi Technological University for the award of the degree of Doctor of Philosophy in Applied Physics. The work embodied in this thesis is a record of bonafide research work carried out by me in the Microelectronics Research Lab, Applied Physics Department, Delhi Technological University, New Delhi under the guidance of *Prof. RISHU CHAUJAR*. It is further certified that this work is original and has not been submitted in part or fully to any other university or institute for the award of any degree or diploma.

Megha Sharma Candidate Roll No. 2K18/PHDAP/18

This is to certify that the above statement made by the candidate is correct to the best of our knowledge.

**Prof. Rishu Chaujar** Supervisor (Professor) Department of Applied Physics Delhi Technological University Delhi, India **Prof. A. S. Rao** Head Department of Applied Physics Delhi Technological University Delhi, India

# **ACKNOWLEDGEMENTS**

This five-year journey of my research work has been an incredible and transformative experience, filled with numerous lessons and personal growth. As I reflect upon this momentous milestone, I am overwhelmed with gratitude for the many individuals who have guided, supported, and believed in me throughout this tremendous journey. Without their unwavering assistance, completing this thesis would have been an immensely challenging task. Therefore, I would like to express my deepest appreciation and acknowledge their invaluable contributions.

First and foremost, I extend my heartfelt thanks to my mentor **Prof. Rishu Chaujar**, whose expertise and guidance have been instrumental in shaping my research direction. **Prof. Chaujar** has not only been an exceptional mentor but also an extraordinary individual whom I consider to be the most remarkable person I have ever had the privilege to meet. During the course of my research, I have encountered numerous challenges and obstacles, both academic and personal. However, with **Prof. Chaujar** by my side, I have felt an immense sense of reassurance and encouragement. Her steadfast belief in my abilities has been a constant source of motivation, empowering me to persist in the face of difficulties.

I am thankful to **Prof. A. S. Rao**, Head of Department, Applied Physics DTU, and **Prof. R.K Saini**, Vice Chancellor, DTU for their munificent support and providing the abundant core for executing the research work efficiently. I further thank SRC and DRC members **Prof. S.C Sharma** (chairman DRC), **Prof. R.S. Gupta** (External Expert), **Prof. Annapurni** (External Expert) for taking their momentous time serving in my committee and giving their priceless endorsement on my thesis.

The journey of pursuing a PhD is a challenging and demanding effort that often requires the support and encouragement of good friends. I consider myself incredibly fortunate to developed meaningful friendships during my PhD. I want to thank **Bhavya Kumar** for his support and encouragement. Receiving rejections from academic journals is an inevitable part of the research process, and it can be disheartening and discouraging. However, Bhavya has always been there to uplift my spirits and motivates me. I am immensely grateful for the presence of **Ankita Banwal** in my life, as she has brought immeasurable joy and positivity into my PhD

*journey. Her ability to make me laugh and put me at ease during challenging times has been a true blessing.*

I would like to express sincere gratitude towards my labmates, **Yash Pathak, Rashi Mann,** *Anshul, Ayushi Lamba and Kajal Verma*. Their unconditional support and understanding, have made my time in the lab truly memorable and enjoyable. I would also like to thank *Vishal Singh* for being there to lighten the stressful atmosphere of the lab by cracking jokes and fun talks to make the moments memorable.

I would like to express my deepest gratitude to a very special person, my husband, **Mr. Nikhil Sharma**. His love, care, and unconditional support have been the driving force behind my successful completion of my Ph.D. degree. Thank you so much for being always around at times when it seemed impossible to continue, you helped me to keep things in perspective. I greatly value your contribution and deeply appreciate your belief in me. It is a blessing to have a life partner like you, who has given the liberty and charge of my life in my hands.

I am profoundly grateful for the immense impact that my father, **Mr. Bhim Chand Sharma**, has had on my life. Words fall short in capturing the depth of my gratitude towards him. He has consistently supported and motivated me in every step of my life, instilling in me the confidence to pursue my dreams fearlessly. I would also like to express my gratitude to my mother, **Mrs. Upma Sharma**. She is the pillar of love and understanding in my life. Throughout my PhD journey, she has been my confidante, the one person with whom I can freely share my worries, doubts, and problems. Her unwavering support and comforting presence have provided me with the strength to face challenges head-on. I extend my thanks to my mother-inlaw, **Mrs. Anju Sharma**, whose love and care have been a constant source of comfort. Her presence in my life has been a blessing and I am grateful for her affectionate support. I would also like to express my appreciation to my siblings, **Dr. Dinesh Chand Sharma, Gunjan Sharma, Tanya Sharma**, Utkarsh Sharma and Raveesh Sharma. They have played a significant role in my life, providing both companionship and support. I would also like to thank my niece, **Sarahna Sharma**, her adorable nature and positive energy have brought immense joy and relaxation.

I would like to extend my heartfelt gratitude to my roommate, **Shanu Bhardwaj**, who has been an integral part of my journey throughout my Ph.D. studies. Her presence has brought immense joy, laughter, and a sense of comfort to our shared living space. Lastly, I want to dedicate my thesis to my late father-in-law, **Mr. Satish Sharma**, whose presence in my life has left an indelible mark. In the short span of time, I formed a deep and meaningful connection with him. Even on my most difficult days, his extraordinary sense of humour could instantly make me feel better. All my troubles seemed to vanish when I was with him. It is impossible to express in mere words the depth of love and admiration I felt for him. He touched my life in ways that are beyond measure, and his impact will continue to resonate within me for the rest of my life.

Megha Sharma

# ABSTRACT

# TCAD Analysis and Simulation of T-Gate E-Mode GaN HEMT.

GaN-HEMT semiconductor technology has already solidified its position as the dominant contender in the realm of high-power and RF applications. In this thesis, performance of GaN HEMT device has been studied and various techniques have been proposed to overcome the major roadblock of GaN HEMT such as spilling of 2DEG, leakage current, threshold voltage  $(V_{th})$ , and parasitic capacitances.

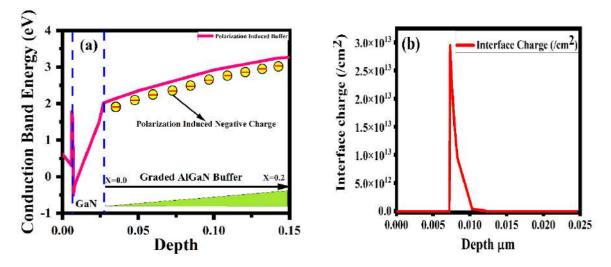

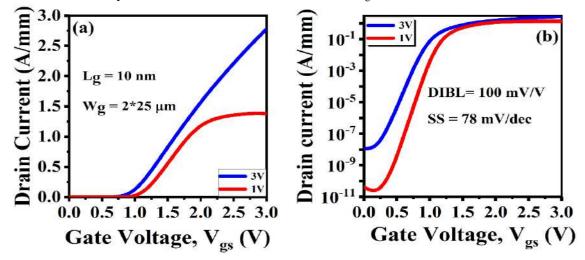

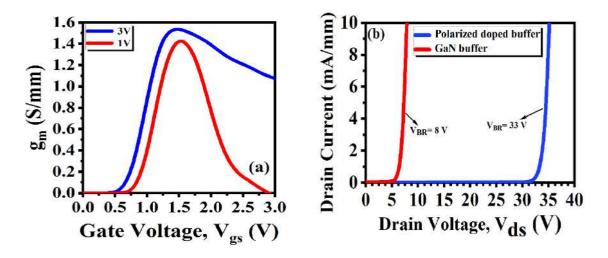

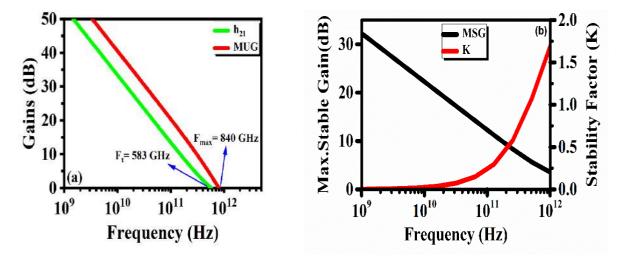

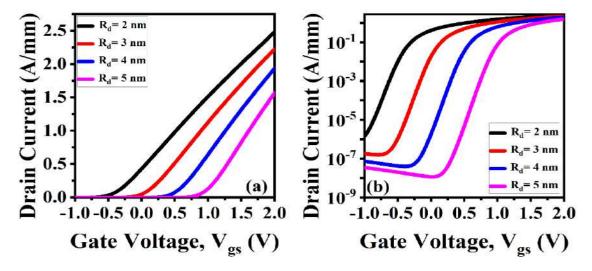

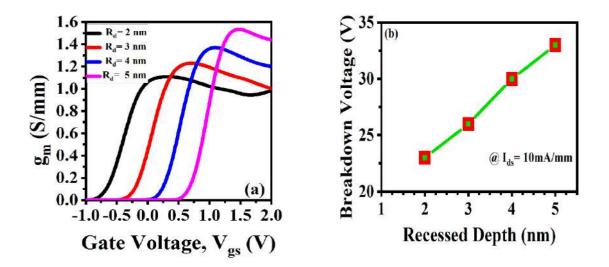

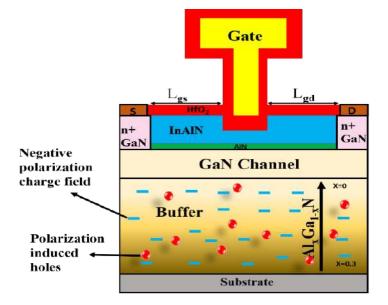

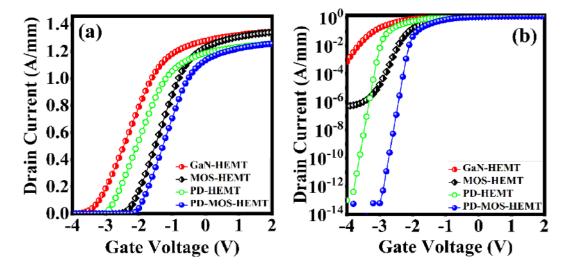

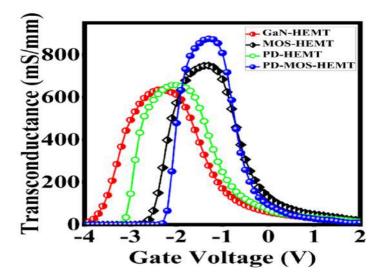

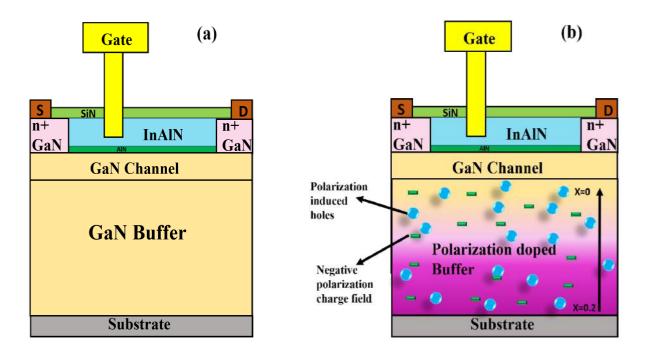

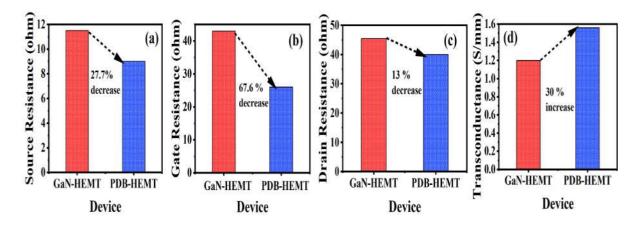

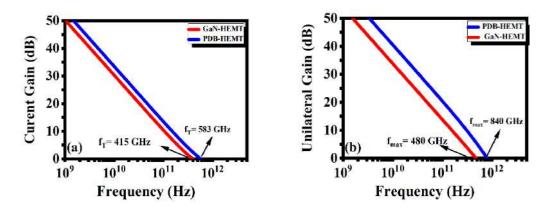

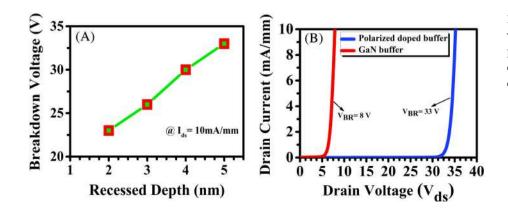

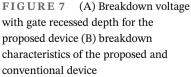

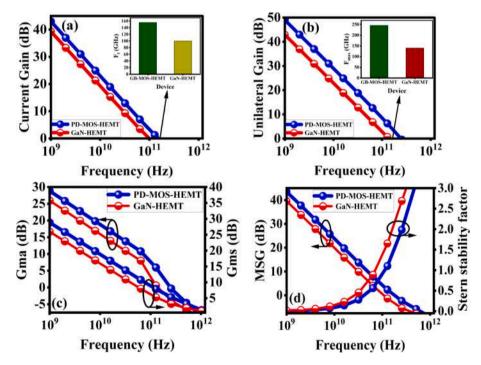

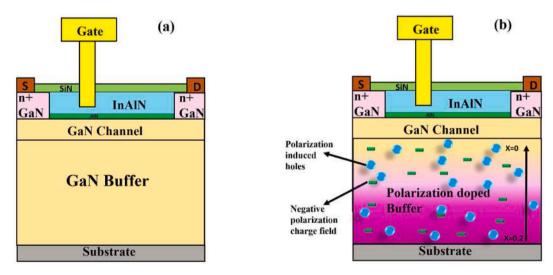

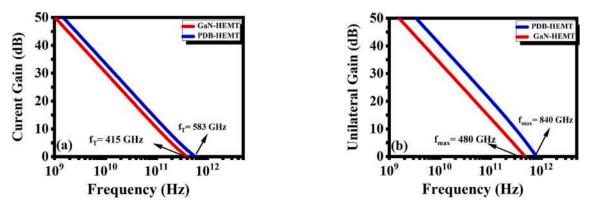

In this regard, firstly polarization induce doping in the buffer layer (buffer Engineering), heavily doped source/drain region, and recessed T-gate (Gate Metal Engineering) are integrated simultaneously on a GaN HEMT i.e. T-gate E mode polarization induced doped buffer HEMT has been proposed. The polarization-induced doping in the buffer layer bent the conduction band upwardly convex, which enhanced the 2DEG confinement, reduced the buffer leakage current, and significantly uplifted the breakdown voltage (33 V), which is 5 times higher than the conventional InAIN/AIN GaN buffer HEMT (8 V). The recessed gate engineering further enhances various performance parameters. It achieves an impressive on/off ratio of 10<sup>9</sup>, reduces the subthreshold swing (SS) to 78 mV/dec, and minimizes the drain-induced barrier lowering (DIBL) to 100 mV/V. The proposed device exhibits a high current density of 2.8 A/mm, transconductance 1.55 S/mm, cutoff frequency fr (583 GHz), and maximum oscillation frequency f<sub>max</sub> (840 GHz). At room temperature, the carrier density and mobility measured are  $2.8 \times 10^{13}$  cm<sup>-2</sup> and 1250 cm<sup>2</sup>/Vs. The large Johnson figure of merit (f<sub>T</sub>. V<sub>BR</sub>) 19.23 THz and (f<sub>T</sub>. f<sub>max</sub>)<sup>1/2</sup> 699 GHz shows the potential of the proposed device for high-power millimeter-wave applications.

Additionally, high-k gate oxide engineering has also been conducted, where a specific region of the recessed gate is substituted with a high-k dielectric material. This integration of the high-k dielectric brings about notable improvements in both interfacial and transport characteristics,

while concurrently reducing the gate leakage current. However, the insertion of gate oxide alone does not enable E-mode operation. As a result, the superior option for achieving E-mode operation is through the utilization of gate-recessed engineering technique.

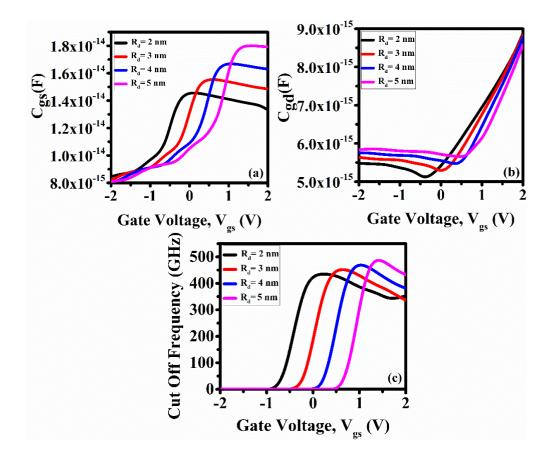

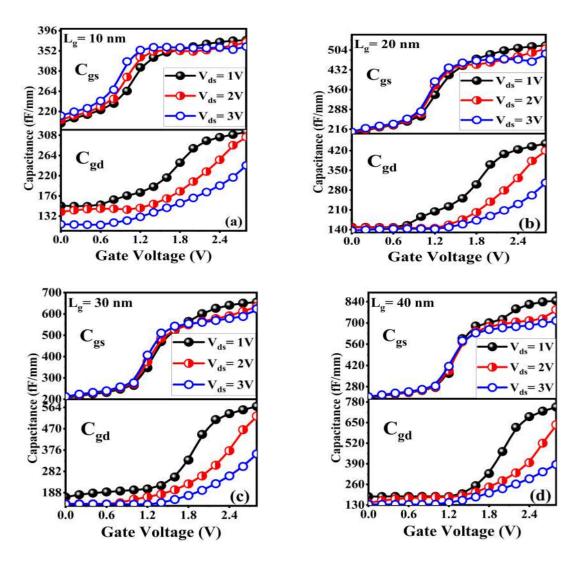

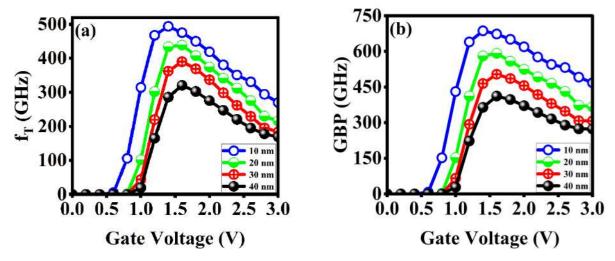

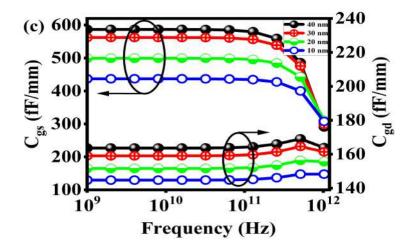

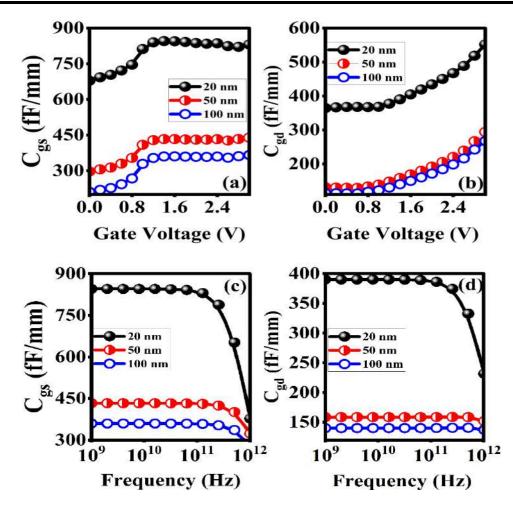

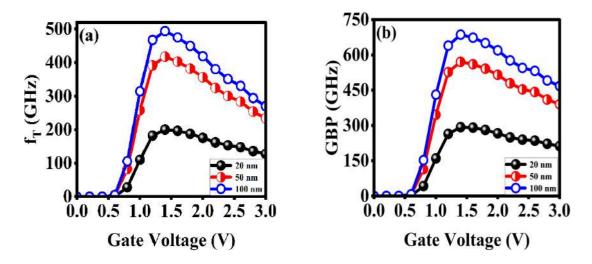

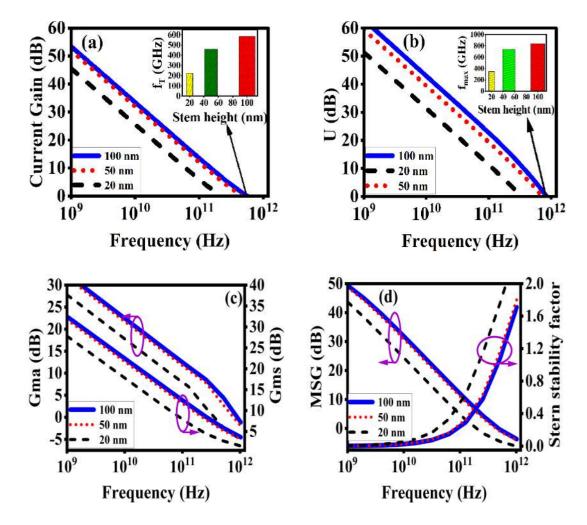

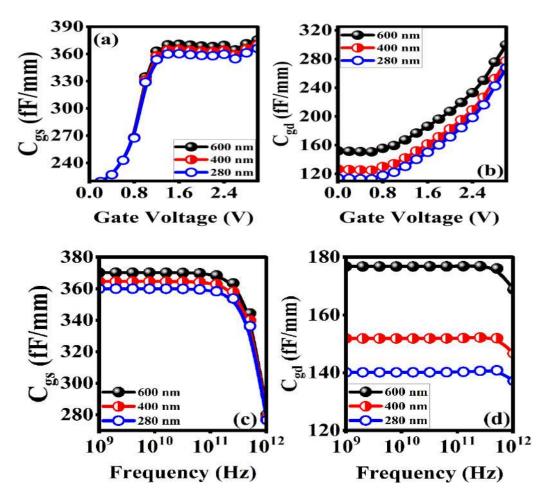

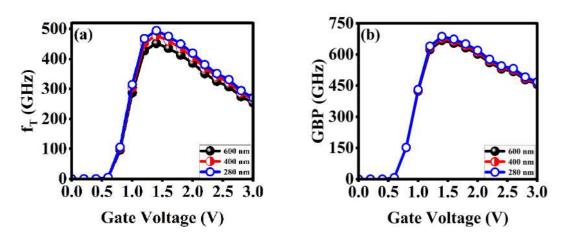

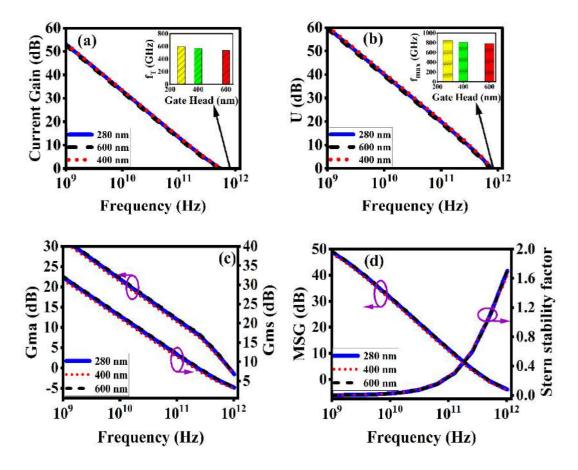

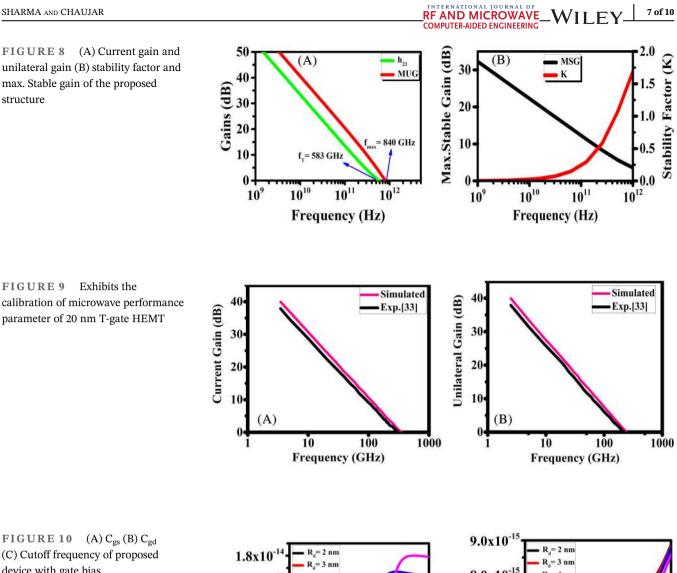

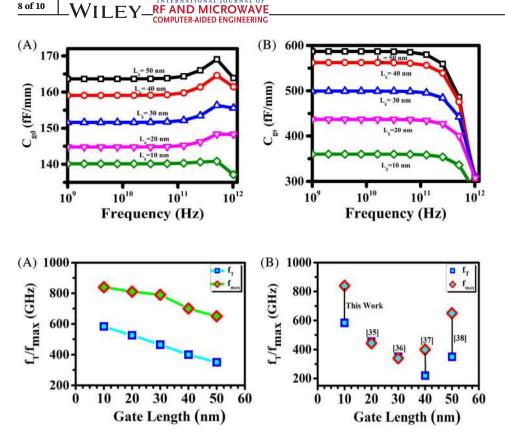

After analyzing the performance of T-gate E mode polarization induced doped buffer HEMT, the in-depth investigation of the influence exerted by the T-gate shape on both the DC and RF performance of the device have been analyzed. The impact of T-shaped gate geometry on parasitic capacitance and RF Figure of Merits (FOMs) such as maximum oscillation frequency ( $f_{max}$ ), gain-bandwidth product (GBP), cut-off frequency ( $f_T$ ), maximum stable and available power gain (Gms and Gma), maximum transducer power gain (MSG) and stability factor (k) has also been investigated for different gate head length ( $H_{length}$ ), gate stem height ( $S_{height}$ ), and gate foot length ( $F_{length}$ ). The simulated results confirm that the proper choice of  $H_{length}$  (280 nm),  $S_{height}$  (100 nm), and  $F_{length}$  (10 nm) significantly reduced the parasitic capacitance ( $C_{gs} = 350$  fF/mm and  $C_{gd} = 140$  fF/mm) and enhanced the  $f_{max}$  (840 GHz), GBP (636 GHz),  $f_T$  (583 GHz) and also improve the power gains. The simulated results of the proposed device provided the detailed knowledge about the impact of T-gate geometry on RF FOMs at such aggressively scaled dimensions.

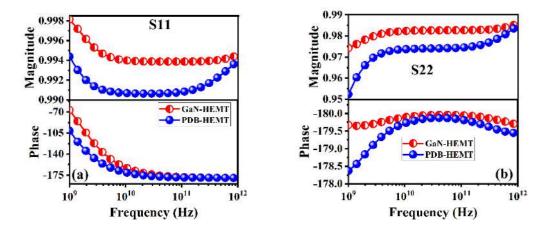

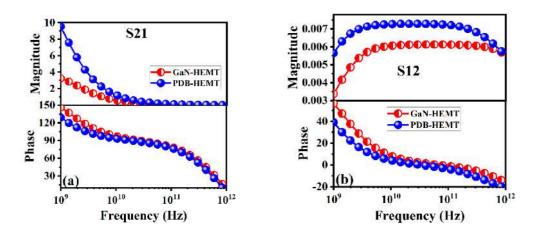

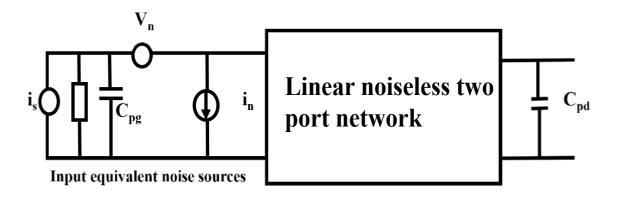

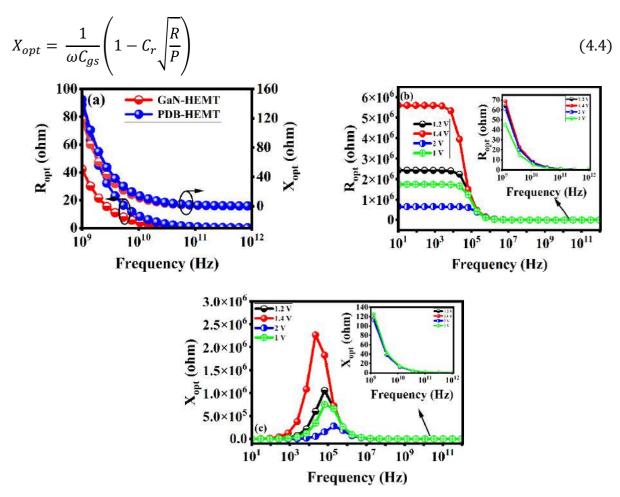

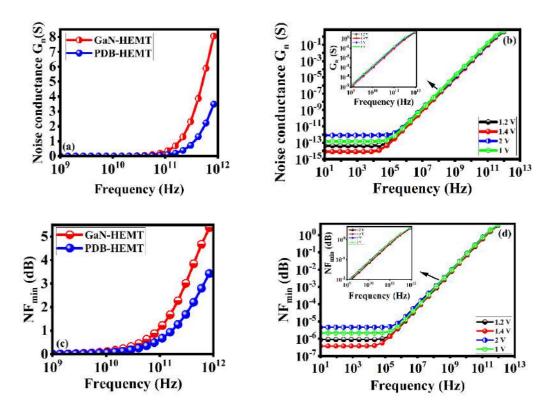

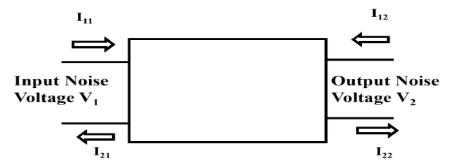

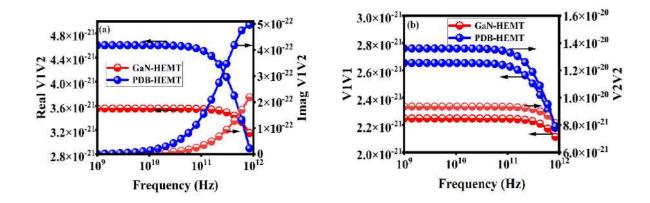

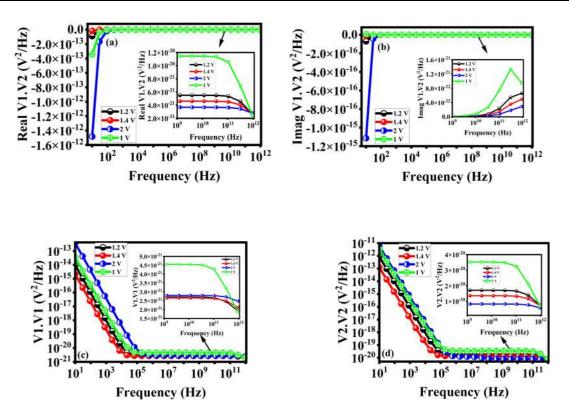

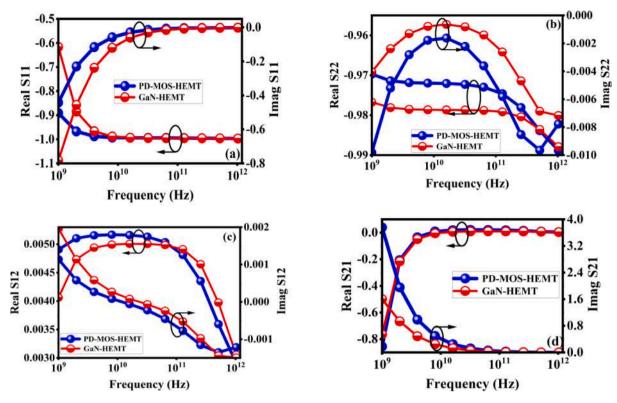

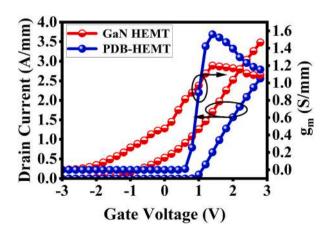

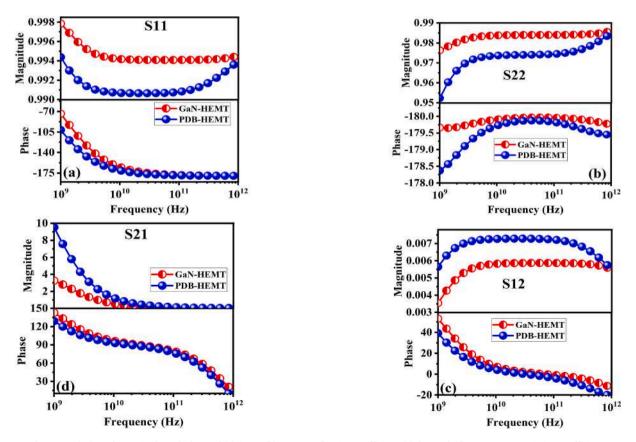

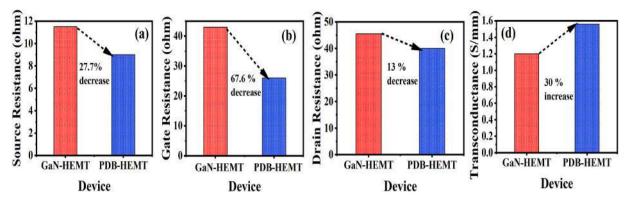

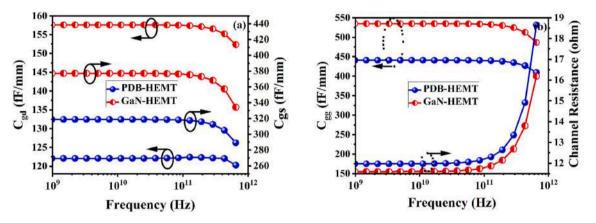

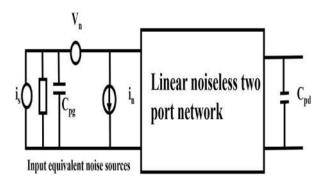

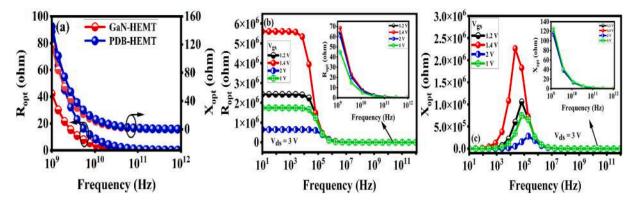

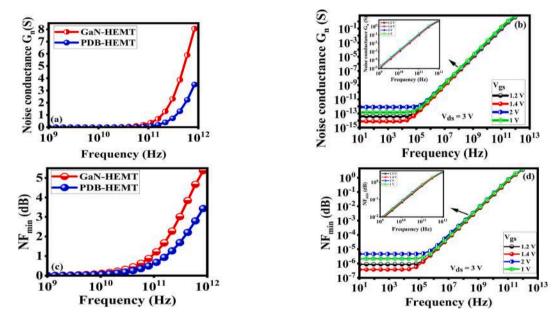

The noise and scattering parameters are critical in determining the overall performance of a device. The noise parameters are important because they determine the amount of noise that is present in the signal as it passes through the device. On the contrary, the scattering parameters determine the magnitude of power dissipated during the transmission of the signal across the device. Thus to account the noise performance T-gate E mode polarization induced doped buffer HEMT, the in depth investigation of the small signal and noise behavior of proposed device has been studied. The results show that the polarization-induced doping in the buffer layer bent the conduction band upwardly convex, which enhanced the 2DEG confinement, reduced the buffer leakage current, and significantly enhance the transconductance (1.55 S/mm). The increment in transconductance leads to a reduction in the reflection coefficient (S11, S22) and an improvement in the transmission coefficient (S21) as compared to GaN buffer HEMT. Furthermore, noise parameters such as auto/cross-correlation factor, minimum noise figure, noise conductance, and optimal noise resistance and reactance were also evaluated for the proposed device. Simulated results reveal that the proposed device has a lower noise figure and noise conductance than the GaN buffer HEMT by 57% and 20%, respectively. This research demonstrates that the T-gate polarization doped buffer (PDB-HEMT) structure is an excellent choice for Low Noise Amplifiers (LNA) operating at higher frequencies.

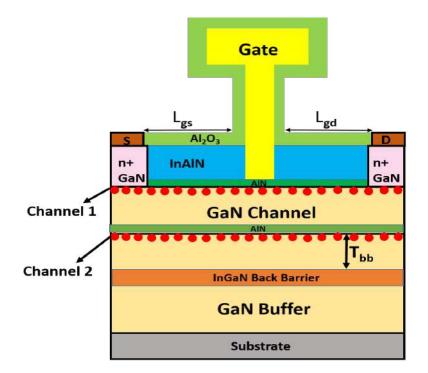

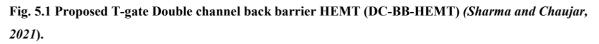

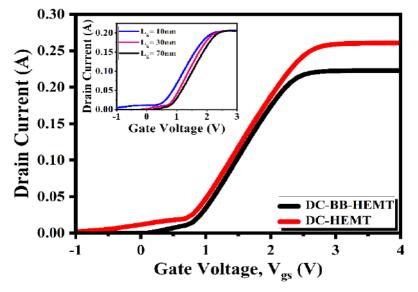

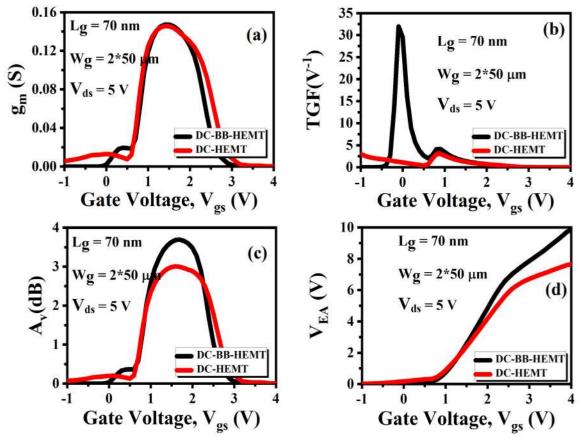

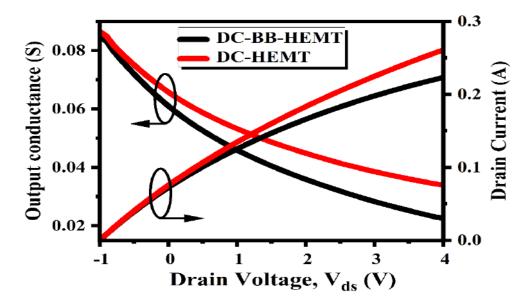

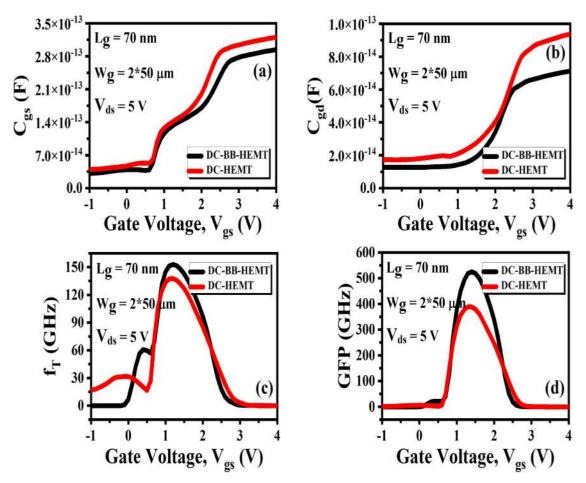

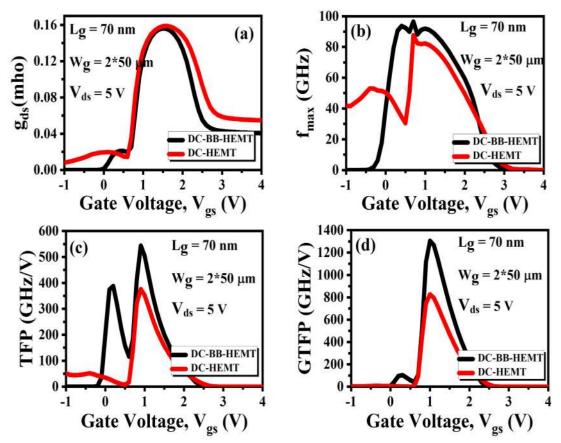

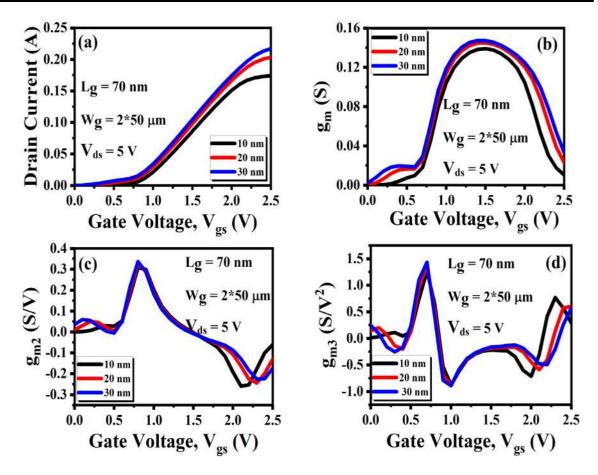

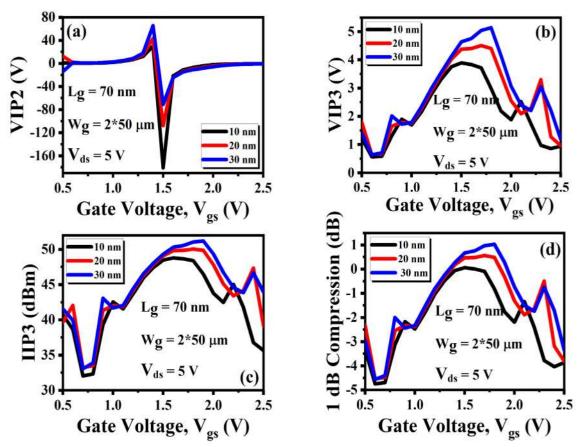

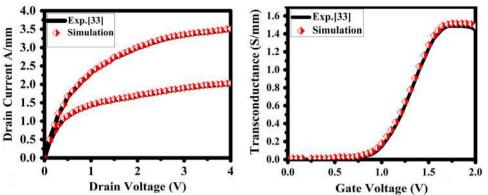

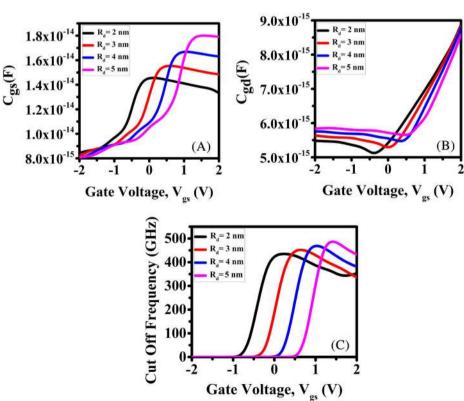

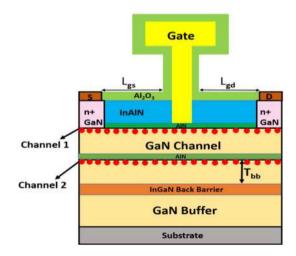

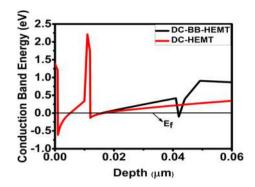

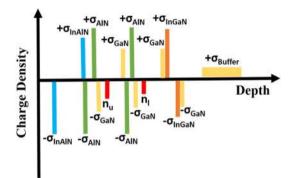

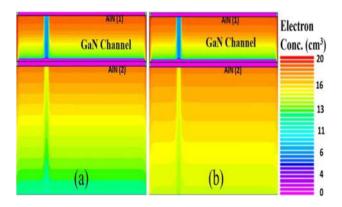

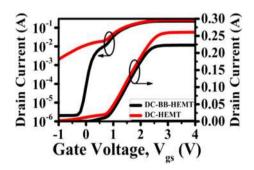

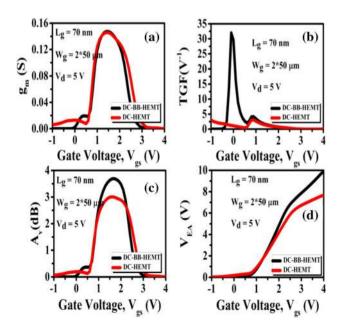

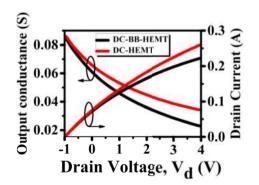

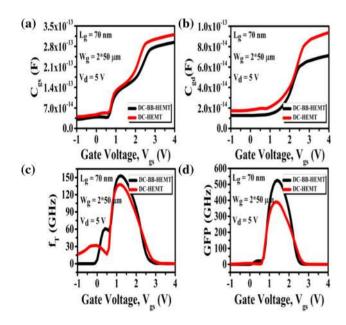

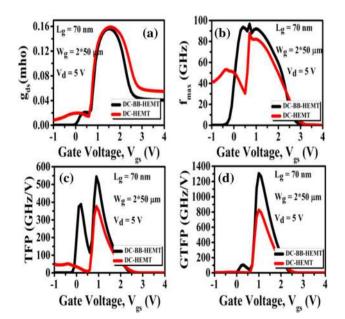

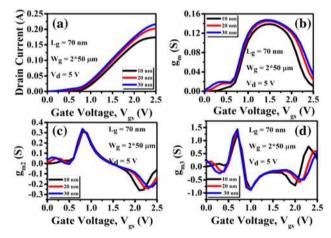

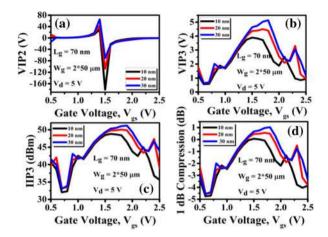

Although using the back barrier engineering enhances the RF and noise performance of device. However, it also reduces the drain current density. Therefore, it is important to find a balance between RF performance and drain current density in device. In this regard, a double channel engineering is executed on T-gate HEMT by inserting the AlN layer below the InAlN/GaN interface developing a double channel HEMT. Simulation results showed that formation of double channel significantly enhance the drain current density of 2.5 A/mm. However, due to a lack of gate controllability over a lower channel, the high leakage current is observed in double channel HEMT. This issue has been addressed by using the InGaN as a back barrier, which improves the carrier confinement of 2DEG by raising the conduction band for the GaN buffer and considerably improves the gate controllability over a lower channel. The performance of the proposed device is compared with that of conventional double-channel HEMTs. The simulation results showed, the proposed double channel back barrier HEMT (DC-BB-HEMT) exhibited substantial improvements in analog performance. The intrinsic gain, which indicates a higher signal amplification capability, improved by 50%. Similarly, the transconductance gain frequency (TGF) increased by an impressive 477%, while the early voltage was enhanced by 23%. These numbers suggest that the InGaN back barrier significantly contributes to the device's analog performance. Moreover, RF performance of (DC-BB-HEMT) also compared with conventional DC-HEMTs. Simulation results showed that both the cut-off frequency and maximum oscillation frequency increased by around 11.7% and 10%, respectively. Moreover, the study also investigated the device's linearity performance with varying back barrier distances. It has been observed that the linearity performance of proposed device improved at a back barrier distance of 30 nm. This result implies that careful optimization of the back- barrier distance can further enhance the device's linearity performance.

### ARTICLES IN INTERNATIONAL REFEREED JOURNALS (7):

- 1. SHARMA, M., and CHAUJAR, R. 2022. Ultrascaled 10 nm T-gate E-mode InAlN/AlN HEMT with polarized doped buffer for high power microwave applications," Int. J. RF Microw. Comput. Aided Eng., 32, 23057 (IF-1.98).

- 2. SHARMA, M., and CHAUJAR, R. 2021. Design and investigation of recessed-Tgate double channel HEMT with InGaN back barrier for enhanced performance. Arabian Journal for Science and Engineering, 1-8. (IF-2.9).

- **3. SHARMA, M.,** and CHAUJAR, R. Device Optimization of T-shaped gate and polarized doped buffer engineered InAlN/GaN HEMT for improved RF/ microwave performance. **Arabian Journal for Science and Engineering (IF-2.9)**.

- SHARMA, M., KUMAR, B. and CHAUJAR, R. 2023. Polarization induced doping and high-k passivation engineering on T-gate MOS-HEMT for improved RF/microwave performance. Materials Science and Engineering,290,116298. (IF-3.4).

- 5. SHARMA, M., KUMAR, B., and CHAUJAR, R. 2023. Small signal and noise analysis of T-gate HEMT with polarization doped buffer for LNAs. Micro and Nanostructures, 180, 207593. (IF-3.22).

- 6. KUMAR, B., SHARMA, M., and CHAUJAR, R. 2023. Gate electrode work function engineered JAM-GS-GAA FinFET for analog/RF applications: Performance estimation and optimization. Microelectronics Journal, 135, 105766. (IF-2.2).

- 7. KUMAR, B., SHARMA, M., and CHAUJAR, R. 2023. Junctionlessaccumulation-mode stacked gate GAA FinFET with dual-k spacer for reliable RFIC design. Microelectronics Journal, 139, 105910. (IF-2.2).

### ARTICLES IN INTERNATIONAL CONFERENCES (9):

- 1. SHARMA, M., and CHAUJAR, R. 2022. BGaN back barrier engineering on Emode T-gate double heterostructure HEMT for high RF applications. In 2022 IEEE International RF and Microwave Conference (RFM) (pp. 1-4). IEEE.

- 2. SHARMA, M., and CHAUJAR, R. 2020. Impact of graded back-barrier on linearity of recessed gate InAlN/GaN HEMT. In 2020 IEEE VLSI Device Circuit and System (VLSI DCS) (pp. 154-158). IEEE.

- **3. SHARMA, M.,** and CHAUJAR, R. 2021. The Performance Analysis of 70nm Tgate InAlN/AlN MOS-HEMT using Graded Buffer. In 2021 Devices for Integrated Circuit (DevIC) (pp. 466-470). IEEE.

- 4. SHARMA, M., KUMAR, B., and CHAUJAR, R. 2022. Linearity analysis of Tgate HEMT with graded back-barrier for wireless applications. In 2022 IEEE International Conference on Electronics, Computing and Communication Technologies (CONECCT) (pp. 1-5). IEEE.

- **5. SHARMA, M.**, KUMAR, B., and CHAUJAR, R. 2021. Effect of Gate Oxide Material Variability on The Analog Performance of T-Gate GaN-MOS-HEMT with Graded Buffer. In 2021 7th International Conference on Signal Processing and Communication (ICSC) (pp. 316-320). IEEE.

- 6. SHARMA, M., KUMAR, B., and CHAUJAR, R. 2022. Simulation investigation of double-heterostructure T-gate HEMT with graded back-barrier engineering for improved RF performance. Materials Today: Proceedings, 71, 155-159.

- 7. KUMAR, B., SHARMA, M., and CHAUJAR, R. 2022. Scattering Parameter Analysis of Gate Stack Gate All Around (GS-GAA) FinFET at THz for RF Applications. In 2022 8th International Conference on Signal Processing and Communication (ICSC) (pp. 653-658). IEEE.

- 8. KUMAR, B., SHARMA, M., and CHAUJAR, R. 2022. Dual-k Spacer JAM-GS-GAA FinFET: A Device for Low Power Analog Applications. In 2022 IEEE Silchar Subsection Conference (SILCON) (pp. 1-5). IEEE.

- **9.** KUMAR, B., **SHARMA, M.**, and CHAUJAR, R. 2021. Static Performance Assessment of Junctionless Accumulation Mode Gate Stack Gate All Around (JAM-GS-GAA) FinFET Under Severe Temperature. In 2021 7th International Conference on Signal Processing and Communication (ICSC) (pp. 386-390). IEEE

# TABLE OF CONTENTS

### Page No.

| CERTIFICATE          | <i>i</i>     |

|----------------------|--------------|

| Acknowledgements     | <i>ii-iv</i> |

| ABSTRACT             | v-vii        |

| LIST OF PUBLICATIONS |              |

| CHAPTER -1                                                   | 1  |

|--------------------------------------------------------------|----|

| INTRODUCTION                                                 | 1  |

| 1.1 BACKGROUND                                               | 2  |

| 1.2 THEORY OF GaN HEMT                                       | 4  |

| 1.2.1 BASIC STRUCTURE                                        | 4  |

| 1.2.2 PIEZOELECTRIC AND SPONTANEOUS POLARIZATION EFFECT      | 6  |

| 1.2.3 Gan-Hemt-Operation                                     | 9  |

| 1.2.4 DEVICE ENGINEERING TECHNIQUES                          |    |

| 1.2.4.1 DOUBLE HETEROSTRUCTURE HEMT WITH GRADED BACK BARRIER |    |

| 1.2.4.2 GATE FIELD PLATE HEMT                                |    |

| 1.2.4.3 HIGH GATE MULTI-RECESSED BUFFER HEMT                 |    |

| 1.2.4.4 DOUBLE CHANNEL MOS- HEMT                             |    |

| 1.2.4.5 P-GATE GaN HEMT                                      |    |

| 1.2.4.6 FERROELECTRIC GATE GaN HEMT                          |    |

| 1.3 ADVANTAGES OF GaN HEMT                                   | 17 |

| 1.4 CHALLENGES CONFRONTED BY THE GaN HEMT                    | 18 |

| 1.5 RESEARCH OBJECTIVES                                      | 19 |

| 1.6 THESIS ORGANIZATION                                      | 20 |

| 1.7 REFERENCES                                               |    |

| CHAPTER-2                                                                                         |    |

|---------------------------------------------------------------------------------------------------|----|

| SIMULATION OF T-GATE E-MODE HEMT WITH POLARIZATION DOPED BUFFER FOR ELECTRICAL AND RF PERFORMANCE |    |

| 2.1 INTRODUCTION                                                                                  | 29 |

| 2.2 DEVICE STRUCTURE                                                                              |    |

| 2.3 SIMULATION MODEL AND CALIBRATION                                                              |    |

| 2.4 FABRICATION PROCESS FLOW                                                                      |    |

| 2.5 RESULTS AND DISCUSSION                                                                        |    |

| 2.5.1 BAND DIAGRAM                                                                                |    |

| 2.5.2 DC CHARACTERISTICS            | 39 |

|-------------------------------------|----|

| 2.5.3 MICROWAVE CHARACTERISTICS     |    |

| 2.5.4 IMPACT OF RECESSED GATE DEPTH |    |

| 2.5.5 IMPACT OF GATE OXIDE          |    |

| 2.6 SUMMARY                         | 48 |

| 2.7 REFERENCES                      | 49 |

| 54               |

|------------------|

| PED BUFFER<br>54 |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

|                  |

| 71               |

|                  |

|                  |

| CHAPTER-4                                                                                  | 76 |

|--------------------------------------------------------------------------------------------|----|

| SMALL SIGNAL AND NOISE BEHAVIOR OF T-GATE E-MODE HEMT<br>POLARIZATION INDUCED DOPED BUFFER |    |

| 4.1 INTRODUCTION                                                                           | 77 |

| 4.2 DEVICE STRUCTURE                                                                       | 80 |

| 4.3 RESULTS AND DISCUSSION                                                                 | 81 |

| 4.3.1 SMALL SIGNAL ANALYSIS                                                                |    |

| 4.3.2 NOISE ANALYSIS                                                                       | 86 |

| 4.4 SUMMARY                                                                                | 92 |

| 4.5 REFERENCES                                                                             | 92 |

| CHAPTER-5                                                                                                  |     |

|------------------------------------------------------------------------------------------------------------|-----|

| DESIGN AND INVESTIGATION OF E-MODE-T-GATE DOUBLE CHANN<br>WITH INGAN BACK BARRIER FOR ENHANCED PERFORMANCE |     |

| 5.1 INTRODUCTION                                                                                           | 97  |

| 5.2 DEVICE STRUCTURE                                                                                       | 99  |

| 5.3 RESULTS AND DISCUSSION                                                                                 | 100 |

| 5.3.1 BAND DIAGRAM AND ELECTRON CONCENTRATION                                                              |     |

| 5.3.2 DC AND ANALOG PERFORMANCE                                                                            |     |

| 5.3.3 RF PERFORMANCE                                                                                       |     |

| 5.3.4 LINEARITY ANALYSIS OF DC-BB-HEMT WITH VARIABLE T <sub>BB</sub> | . 108 |

|----------------------------------------------------------------------|-------|

| 5.4 SUMMARY                                                          | 111   |

| 5.5 REFERENCES                                                       | 111   |

| CHAPTER-6                |  |

|--------------------------|--|

| SUMMARY AND FUTURE SCOPE |  |

| 6.1 SUMMARY              |  |

| 6.2 FUTURE SCOPE         |  |

### **REPRINTS OF JOURNAL PUBLICATION**

# CHAPTER 1

# **INTRODUCTION**

Firstly, this chapter provides a comprehensive background of the research work, with a primary focus on the significance of gallium nitride (GaN) in the power electronics industry. After then, the chapter moves on to the fundamental theory of GaN HEMT, covering topics like its polarization effect and its operating principle. In addition to this, the chapter investigates a number of device engineering techniques that have been reported to overcome the problems faced by HEMT. The chapter continues with a description of the challenges confronted by the GaN HEMT that are found while literature survey. After that, a description of the main objective of this thesis is provided, which is then followed by an overview of all the chapters.

## 1.1. Background

The advancement of semiconductor technology paved the way for the creation of an enormous industry and many applications that profoundly altered our way of life. Silicon technology, which has been the main workhorse of modern electronics, has dominated the semiconductor sector over a decade. Transistors made from silicon have been implemented in many different fields. However, silicon-based devices are quickly reaching their theoretical limit of operation, and future RF and microwave applications will require even higher levels of performance that cannot be achieved with the current technology. As a result, researchers are exploring alternative materials and device architectures to overcome these limitations and enable the next generation of RF and microwave devices. Group III-V semiconductors such as SiC, GaAs, and GaN have all been investigated as possible silicon substitutes. GaAs's high electron mobility in the bulk makes it a promising candidate for use in MESFETs operating at high frequencies. Nevertheless, its inadequate thermal conductivity renders the material unsuitable for highpower applications. Because of this, GaAs MESFETs can only be used in low-power devices like mobile phones and other portable electronics (Kameche and Rozdovski, 2005). SiC, on the other hand, is highly suitable for both high-temperature and high-voltage applications due to its distinctive material properties. Due to their excellent resistance to heat and voltage, SiC MESFETs find widespread use in demanding industries like aerospace and defence. However, SiC devices are unsuitable for high-frequency activities because of their limited electron mobility and inability to create a heterojunction.

Gallium Nitride High Electron Mobility Transistor (GaN-HEMT) semiconductor technology has solidified its position as the dominant contender in the realm of high-power and RF applications. Optoelectronics (*Cai et al., 2018*), MEMS (*Rais et al., 2017*), and electronics (*Karmalkar and Mishra, 2001*) are just a few of the fields that have benefited from the unique features of GaN-based materials. Aluminium gallium nitride (AlGaN)/GaN devices have become highly regarded as top contenders among solid-state microwave power devices for various applications. In comparison to devices based on Si and GaAs, they are better because of their capacity to produce enhanced power densities at higher frequencies. GaN contains a number of beneficial properties, which together lead to the material's outstanding performance. A wide bandgap (3.4 eV), substantial electric breakdown field strengths ( $3 \times 10^6$  V/cm), and a

### TABLE 1.1

|                    | 1.4                 | 1.34                                         | 3.4                                                                  | 1.1                                                                                                                |

|--------------------|---------------------|----------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 5                  |                     |                                              |                                                                      | 1                                                                                                                  |

|                    | 0.5                 | 0.68                                         | 1.3                                                                  | 1.5                                                                                                                |

| 2×10 <sup>-9</sup> | 2.1×10 <sup>6</sup> | 1.3×10 <sup>7</sup>                          | 1.9×10 <sup>-10</sup>                                                | $1.5 \times 10^{10}$                                                                                               |

| 0                  | 2.0                 | 0.9                                          | 2.5                                                                  | 1.0                                                                                                                |

| 20                 | 8500                | 5400                                         | 900                                                                  | 1350                                                                                                               |

| )                  | 12.8                | 10                                           | 9.0                                                                  | 11.8                                                                                                               |

| 0                  | 0.4                 | 0.5                                          | 3.3                                                                  | 0.3                                                                                                                |

|                    | 0 :<br>20 :<br>)    | 0     2.0       20     8500       0     12.8 | 0     2.0     0.9       20     8500     5400       0     12.8     10 | 0       2.0       0.9       2.5         20       8500       5400       900         0       12.8       10       9.0 |

Characteristics of GaN and rival semiconductor materials. (*Trew, 2002, Kemerley et al., 2002*)

high saturation electron drift velocity (>2×10<sup>7</sup> cm/s) are some of these characteristics. The HEMTs made from AlGaN/GaN are particularly appealing because of their superior performance at high power (*Wu et al., 2001*), high-frequency (*Kumar et al., 2002, Chung et al., 2010*), and high temperature (*Gaska et al., 1997*).

**Table 1.1** shows how GaN stacks up against other prominent semiconductors in terms of its key intrinsic electronic properties (*Trew, 2002, Kemerley et al., 2002*). Compared to Si, GaAs, and InP, it's clear that GaN offers numerous benefits. Due to its larger band gap ( $E_g$ ), larger critical electrical field ( $E_c$ ) than Si, GaAs, and InP by as much as a factor of ten. As a result of its high electronegativity, GaN HEMTs have a substantially greater breakdown voltage than other semiconductor devices, making them ideal for high-voltage and high-power applications. GaN transistor-based circuits exhibit remarkable reliability, attributed to their high breakdown voltage. These devices can function at very high frequencies with high drain current thanks to their exceptional electron mobility, saturation drift velocity and high two-dimensional electron gas (2DEG) concentration, which are crucial for high-power RF applications. GaN is a broad band-gap semiconductor with a significantly lower intrinsic carrier generation rate than Si, GaAs, or InP. This allows GaN-based transistors to function at high voltage while maintaining

a low leakage current. As an added bonus, GaN-based devices can operate in high-temperature and high-pressure conditions because of their high thermal conductivity. GaN is the dominating technology for high-power applications at high frequency due to its great mobility and strong critical field, which permits aggressive scaling of the transistor size.

Due to their potential for high frequency and high-power electronic devices, the AlN/GaN (*Smorchkova et al., 2001*), AlInN/GaN (*Kuzmik, 2001*), and AlInN/GaN/GaN (*Lim et al., 2010*, *Wang et al., 2013*) material systems are the topic of active study. Device performance may be enhanced by using these material solutions, which provide both increased carrier densities and aggressive downscaling of gate lengths. AlGaN/GaN HEMTs have already found niche applications and are anticipated to play an increasingly important role in future electronic systems.

# 1.2. Theory of GaN HEMT

## **1.2.1 Basic Structure**

HEMT is a type of semiconductor device used in high-frequency electronic circuits. It consists of two layers of semiconductor materials with different bandgaps, in which the wide bandgap

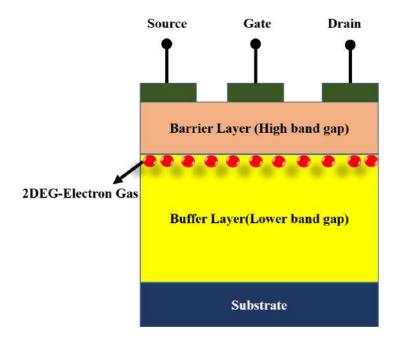

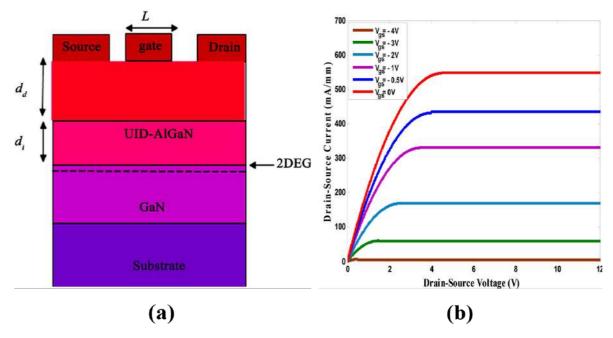

Figure. 1.1 Basic structural cross section of a HEMT (Nirmal and Ajayan, 2019)

material is grown over the narrow bandgap material. The structure of a HEMT is illustrated in **Figure 1.1**, showing the cross-section of the device. To create a HEMT, a substrate of semiconductor material is first prepared. On the substrate, the buffer layer is then grown, followed by the barrier layer. Both layers are usually doped with impurities to create n-type conductivity. The doping concentration in the barrier layer is higher than that in the buffer layer,

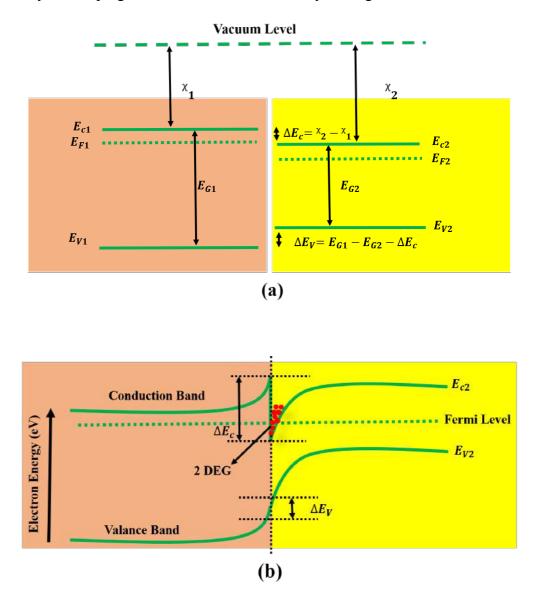

Figure. 1.2 Energy band diagram of heterostructure material (a) before forming the heterojunction (b) bend bending after forming the heterojunction *(Nirmal and Ajayan, 2019)*.

which creates a heterojunction. When the barrier layer is brought into contact with the buffer layer, electrons from the barrier layer diffuse into the buffer layer to achieve a minimum energy configuration. The electron transfer occurs because the two materials have different electron affinities, band gaps, and work functions. The electrons accumulate at the interface between the

two layers, forming a 2DEG with high mobility and conductivity.

The energy band diagram of the HEMT device in its state prior to the formation of the heterojunction is shown in **Figure 1.2 (a)**. **Figure 1.2 (b)** shows the heterojunction interface formation when a material with a large band gap is brought into contact with a material with a small band gap. Due to band bending, a two-dimensional quantum well with a finite energy barrier is formed in the channel area. The electrons that are present in the channel are prevented from leaving the quantum well and are forced to remain at their respective energy levels, which results in the formation of a 2DEG. The electrons that are contained in the quantum well have very high mobility and are often referred to as two-dimensional electron gas. This is the distinguishing quality of HEMTs. Whereas the drain and source make ohmic contacts with the barrier layer, and the gate makes a schottky contact.

# **1.2.2 Piezoelectric and Spontaneous Polarization Effect**

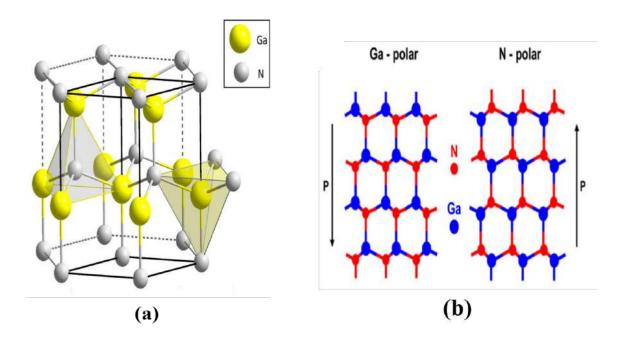

In AlGaN/GaN HEMT, 2DEG is not formed in the same way as it is in the more common AlGaAs/GaAs semiconductor at the heterojunction. Figure 1.3 (a) depicts the hexagonal or wurtzite crystal structure of GaN, in which the bilayers are composed of two closely spaced hexagonal layers created by Ga atoms and N atoms, respectively (*Qin et al., 2017*). A strong net polarization field is induced at the AlGaN/GaN heterojunction interface because the wurtzite structure in GaN is not symmetrical, unlike other semiconductors like GaAs and InP with zincblende crystal structure (*Khan et al., 1994*). Since this polarization field is formed naturally by the GaN material's elemental makeup and crystalline structure, which refer as spontaneous polarization. Ga-face and N-face are the two primary classifications of GaN material, and they are determined by the direction in which the material grows. As can be seen in Figure 1.3 (b) the polarization field directions in the two distinct forms of GaN are directly opposed to one another. All of the devices that were examined in this study were constructed out of Ga-face GaN material.

The difference in polarization that exists between GaN and AlN may be attributed to the fact that structural factors have a substantial impact on the determination of spontaneous polarization (*Ambacher et al., 1999*). While going from GaN to AlN, the crystal structure

Figure. 1.3 (a) Wurtzite crystal structure of GaN *(Kente et al., 2016)* (b) Ga-face and N-face GaN crystal atomic arrangement *(Keller et al., 2014)*

becomes increasingly less perfect, which increases spontaneous polarization. The typical AlGaN/GaN epitaxial film developed along the [0001] axis has the only spontaneous polarization that is taken into consideration along that axis.  $P_{SP} = P_{SP}.z$  is the relation that describes the spontaneous polarization along the c-axis.

Lattice mismatched GaN-based heterostructures, including AlGaN and AlN, exhibit an intriguing phenomenon known as piezoelectric polarization. This type of polarization is engendered by the strain that arises when dissimilar materials with varying lattice constants are combined in a heterostructure.

Notably, the critical thickness of the barrier layer plays a crucial role in determining the presence and magnitude of piezoelectric polarization *(Ambacher et al., 1999)*. The critical thickness is the maximum thickness at which the barrier layer can be formed without introducing any dislocations. The piezoelectric polarization is induced when the thickness of the AlGaN or AlN barrier is reduced below its critical value.

The piezoelectric polarization can be calculated using the values of e33 and e31, which are the coefficients of piezoelectricity (*Ambacher et al., 1999*).

$$P_{PE} = e_{33}\varepsilon_z + e_{33}(\varepsilon_x + \varepsilon_y) \tag{1.1}$$

$$\varepsilon_z = \frac{C - C_o}{C_o} \tag{1.2}$$

$$\varepsilon_x = \varepsilon_y = \frac{a - a_o}{a_o} \tag{1.3}$$

The strain along the c-axis is denoted by the  $\varepsilon_z$ , where  $\alpha_o$  and  $C_o$  are the equilibrium values of the lattice parameters. Wurtzite GaN lattice constants are related using the following equation.

$$\frac{C - C_o}{C_o} = 2 \frac{C_{13}}{C_{33}} \left( \frac{a - a_o}{a_o} \right)$$

(1.4)

The net polarization along the c-axis can be determined by combining equations (1.1) and (1.4)

$$P_{PE} = 2 \frac{a - a_o}{a_o} (e_{31} - e_{33}) \frac{C_{13}}{C_{33}}$$

(1.5)

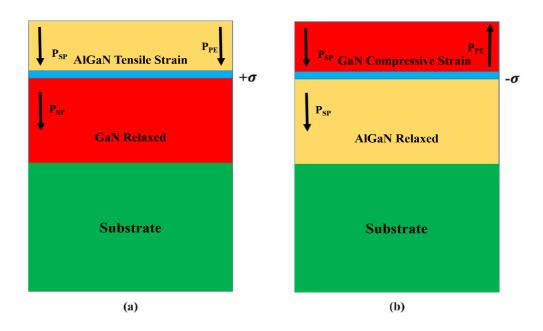

As can be seen in **Figure 1.4(a, b)**, the spontaneous polarization of Ga-face GaN and AlGaN is negative. This is due to the fact that the direction vector points in the direction of the substrate. **Figure 1.4(a)** demonstrates that, when the strain is tensile, the piezoelectric and spontaneous polarizations align parallel to each other. On the other hand, in the case of compressive strain, these polarizations adopt an anti-parallel orientation. This behavior is demonstrated and visually depicted in **Figure 1.4(b)**.

The polarization induced space charge density is given by:

$$\rho_P = \nabla . P \tag{1.6}$$

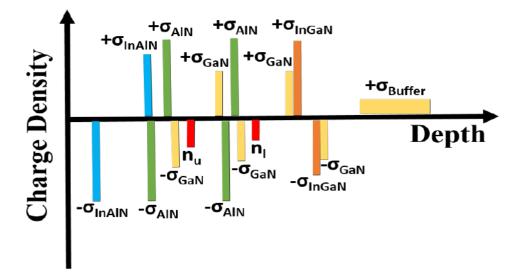

At the abrupt interface polarization sheet charge density ( $\sigma$ ) of an AlGaN/GaN or GaN/AlGaN heterostructure is (*Ambacher et al., 1999*):

$$\sigma = P(bottom) - P(top) \tag{1.7}$$

Free electrons will try to neutralise the charges caused by polarization if the polarizationgenerated sheet charge density is positive (+), and vice versa. At the heterojunction between the barrier and the buffer layer, these charges will begin to accumulate which will result in the formation of a 2DEG. These two polarization effects increase the device structure's electric field, which boosts 2DEG carrier concentration and channel confinement.

Figure. 1.4 Directions of spontaneous and piezoelectric polarization in AlGaN/GaN heterostructure (a) Tensile strain (b) Compressive strain (*Ambacher et al., 1999*).

### **1.2.3 GaN-HEMT-Operation**

Device operation requires a gate electrode to modulate drain-to-source current by controlling the density of 2DEG. Since the heterostructure causes the 2DEG to exist, a negative gate voltage is necessary to deplete it beneath the gate and stop the flow of current through the device. Therefore, GaN HEMTs that do not have specially engineered gate stacks are normally-on (also known as depletion-mode or D-mode) devices. **Figure 1.5(a)** shows the schematic structure of AlGaN/GaN HEMT. The output characteristics of a depletion mode AlGaN/GaN HEMT are shown in **Figure 1.5(b)**. Using a common source configuration is by far the most typical method of applying the bias to a HEMT. The input is at the gate electrode, the output at the drain electrode, and the common terminal at the source. The gate's input signal controls the device's state and may turn it on and off. To turn off a depletion mode device, a negative voltage is applied to the device, depleting the channel of electrons and creating a very resistive channel through which no current may flow, which is called pinch-off.

The equation that describes the relationship between the amount of applied bias voltage and the total number of carriers in the channel is as follows *(Ambacher et al., 2000)*:

$$n_s = \frac{\varepsilon_{AlGaN}}{q(d_{AlGaN} + \Delta d)} (V_{gs} - V_{TH})$$

(1.8)

where,  $n_s$ ,  $d_{AlGaN}$ ,  $\Delta d$ ,  $V_{gs}$ , and  $V_{TH}$  are the charge density per unit area of the 2DEG, AlGaN barrier layer thickness, distance of the 2DEG from the heterointerfaces, gate bias voltage, and threshold voltage.

Due to the term ( $V_{gs} - V_{TH}$ ) in Equation 1.8,  $n_s = 0$  for  $V_{gs} = V_{TH}$ , and the device is to be turned off. The channel of a HEMT is inherently densely packed with electrons at  $V_{gs} = 0$  V, and applying a drain-to-source voltage will result in current flow between the source and drain.

Figure. 1.5 (a) AlGaN/GaN HEMT structure (b) Drain characteristics of AlGaN/GaN HEMT for different gate bias *(Manel et al., 2012)*

The device is said to be operating in the linear regime when the drain voltage is low i.e.  $V_{ds} < V_{gs} - V_{TH}$ . Since the current is proportional to the electric field strength, the velocity of the electrons in the channel will rise as the field strength increases. At this instant, the current flowing between the source and the drain may be expressed as:

$$I_{ds} = qn_s V_{eff} W_G \tag{1.9}$$

where  $V_{eff}$  and  $W_G$  are the effective velocity and the gate width.

The electrons' velocity in the channel is a function of the electrons' mobility and the electric field strength as expressed by Equation 1.10.

**Megha Sharma**

$$V = \mu_n E$$

where  $\mu_n$  and E are the electron mobility and applied electric field.

Carrier scattering through defects and dislocations in the semiconductor crystal impact electron mobility in the 2DEG of an AlGaN/GaN HEMT *(Germain et al., 2003).* When  $V_{ds} < V_{gs} - V_{TH}$ , the current is demonstrated to grow linearly for low fields by using the result of Equation (1.10), which states that electron velocity grows with the applied electric field. Nevertheless, when the drain bias is high enough ( $V_{ds} > V_{gs} - V_{TH}$ ), the effective electron velocity saturates and stops being affected by the bias or the electric field. In the saturated regime, the drain current is given by

$$I_{ds} = \frac{\varepsilon_{AlGaN} V_{sat} W_G}{(d_{AlGaN} + \Delta d)} (V_{gs} - V_{TH})$$

(1.11)

The above equation shows that the at high drain bias,  $I_{ds}$  is independent of  $V_{ds}$ . In reality,  $I_{ds}$  is not absolutely free from  $V_{ds}$  influence. Under conditions of high drain bias, high electric fields emerge between the drain and gate contacts, potentially leading to the injection of electrons into the GaN buffer or captured by electron traps.

### **1.2.4 Device Engineering Techniques**

# **1.2.4.1** Double Heterostructure HEMT with

### **Graded Back Barrier**

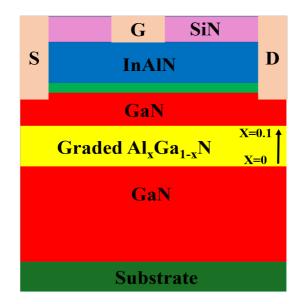

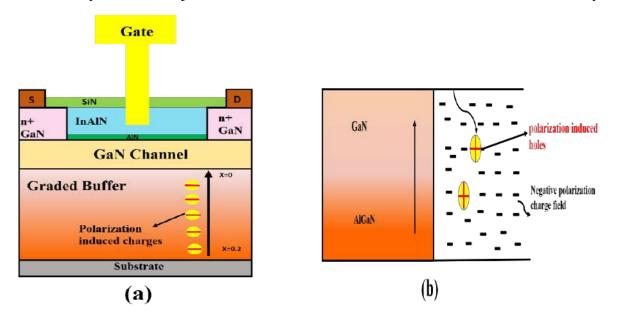

Double heterostructure HEMT with the graded back barrier is designed to enhance the performance of HEMT (*Gu et al., 2019*). As shown in **Figure 1.6**, the barrier layer in this design is made of InAlN rather than AlGaN because the device's performance is enhanced by the lattice matching between the two materials (where the Al content of InAlN is 0.83) (*Neuburger et al., 2004*). Between the InAlN barrier layer and the GaN channel layer lies an additional AlN interlayer. As AlN has a wider forbidden bandwidth, it may cause more discontinuity in the conduction band at the heterojunction interface, which is a major contributor to the dramatic rise in 2DEG concentration (*Shrestha et al., 2014*). Increased device mobility is another benefit of the AlN in the In<sub>0.17</sub>Al<sub>0.83</sub>N/GaN heterojunction interface (*Teke et al., 2009*). The leakage of 2DEG from the channel to the buffer is a problem for single heterostructure HEMTs. The

Figure. 1.6 Schematic representation of InAlN/GaN HEMT with graded back barrier (Gu et al., 2019)

utilization of a back-barrier, creating a double heterojunction structure, is a direct and effective approach for enhancing the confinement of the heterojunction 2DEG and minimizing the carrier overflow into the buffer layer. Many researchers have looked at the effects of AlGaN back-barrier layers on HEMTs structures. Carrier confinement is improved to some extent, but an undesirable parasitic channel is created at the interface of the AlGaN back-barrier and the GaN buffer. Parasitic channel effects may be reduced with the use of a graded AlGaN back-barrier in which the Al concentration varies linearly from 0 to 0.1. The findings show that the graded AlGaN back-barrier HEMT benefits greatly from the conduction band discontinuity at the GaN/AlGaN heterojunction interface, which greatly enhances carrier confinement. In contrast to the standard Al<sub>0.1</sub>Ga<sub>0.9</sub>N back-barrier HEMT, a gradient Al composition results in full lattice relaxation without piezoelectric polarisation, which decreases the concentration of the parasitic electron channel's two-dimensional electron gas. Furthermore, a graded AlGaN back barrier may provide superior radio-frequency performance, greater transconductance, and higher current compared to the standard back-barrier HEMT with a fixed Al content.

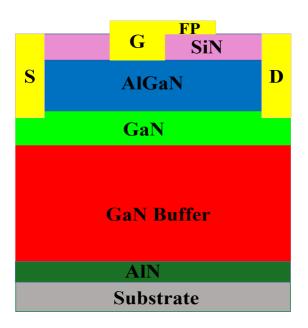

### 1.2.4.2 Gate Field Plate HEMT

The use of field plate technology has gained significant attention in the field of electronic devices, specifically in high-electron-mobility transistors. Researchers have found that this

Figure. 1.7 Schematic representation of Gate field plate HEMT (Kumar et al., 2022)

innovative method offers a practical and efficient approach to enhancing the breakdown voltage of HEMTs by reducing the peak value of the electric field along the channel (*Karmalkar et al., 2001*). **Figure 1.7** illustrates a schematic view of a gate field plate HEMT, demonstrating the implementation of this technology (*Kumar et al., 2021*).

In a gate field plate HEMT, the gate is deposited onto the passivation layer and extended towards the drain side of the device. This extension of gate electrode toward drain side significantly minimizes the electric field at the surface of the AlGaN layer and enhances the breakdown voltage (*Karmalkar et al., 2005*). This improvement in breakdown voltage is of utmost importance in electronic devices as it not only enhances their power capabilities but also elevates their operational speed.

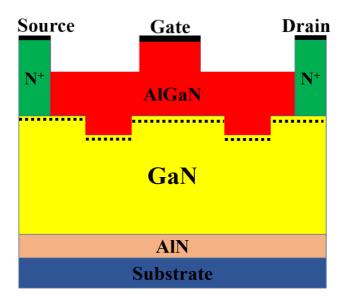

### 1.2.4.3 High Gate Multi-Recessed Buffer HEMT

The high gate multi-recessed buffer HEMT (HGMRB-HEMT) is an innovative design introduced (*Zhu et al., 2019*) to address two crucial aspects of device performance: breakdown voltage and RF characteristics. The structure of the HGMRB-HEMT incorporates specific features aimed at simultaneously enhancing these key parameters. In the HGMRB-HEMT, the barrier region is intentionally positioned lower than the source, drain, and gate electrodes, creating a higher gate section. This distinctive arrangement can be observed in **Figure 1.8**.

Figure. 1.8 Schematic representation of high gate multi recessed buffer HEMT (Zhu et al., 2019).

Additionally, the buffer layer of the HGMRB-HEMT includes recessed regions on both the left and right sides. These recessed regions contribute to the optimization of device performance.

When a high drain voltage is applied in traditional GaN HEMTs, a significant electric field builds up at the edge of the gate. This concentrated electric field can lead to a breakdown near the gate position on the drain side. The implementation of the HGMRB-HEMT introduces a modified electric field distribution that reduces the peak electric field at the edge of the gate electrode. This modification raises the HGMRB-HEMT's breakdown voltage by making it more resistant to greater drain voltages. The decrease in gate-to-source capacitance is yet another great feature of the HGMRB-HEMT. This reduction is primarily attributed to the presence of the high gate in the structure, which facilitates the diffusion of the depletion region mainly in a vertical downward direction. This reduces the capacitance between the gate and the source, which boosts the functionality of the device.

The enhancement in breakdown voltage and reduction in gate-to-source capacitance lead to enhanced output power density and power-added efficiency (PAE) of HGMRB-HEMT. Devices with higher breakdown voltages are capable of withstanding increased power levels without experiencing a breakdown, rendering them appropriate for high-power applications. The decrease in capacitance between the gate and source enables enhanced signal integrity and increased efficacy of power transmission, leading to greater output power density and poweradded efficiency (PAE). Hence HGMRB-HEMT is an attractive choice for applications that require both high power and high efficiency.

### **1.2.4.4 Double Channel MOS- HEMT**

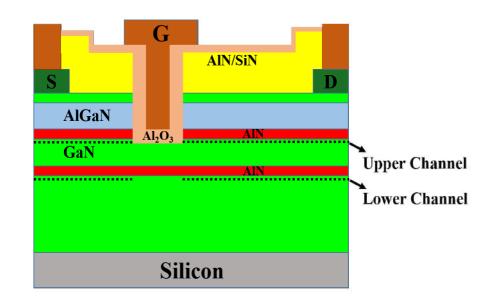

**Figure 1.9** depicts a recessed gate in a DC-MOS-HEMT device from a two-dimensional perspective. When one examines the figure, it is immediately apparent that the DC-MOS-HEMT is composed of not one but two distinct channel layers. The amount of space that is available between the upper and lower channel layers is the primary factor that governs the distribution of electrons in each of these channel levels. As a result of the reverse electric field that is present in the GaN upper layer compared to the AlN layer, the 2DEG density in the lower channel is reduced when there is a big distance between these two channels. In contrast, the 2DEG density in the upper channel is increased when there is a high distance between these two channels. Additionally, the recessed gate design that is used in DC-MOS-HEMT devices assists to terminate the top channel and shift the threshold voltage to the positive side of the voltage scale. The DC-MOS-HEMT offers a strong subthreshold swing, which refers to the efficiency of the device in switching between on and off states. A lower subthreshold swing indicates better control over the device's conductive and non-conductive states, enhancing overall device performance and power efficiency.

### 1.2.4.5 P-Gate GaN HEMT

Figure. 1.10 Schematic representation of P-Gate GaN HEMT (Greco et al., 2018)

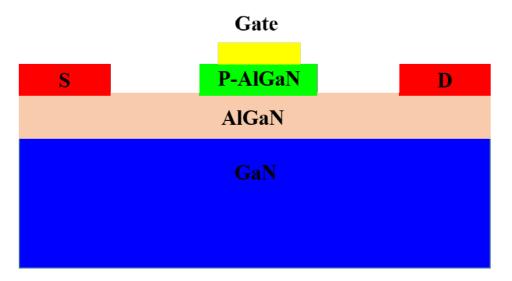

Adding a p-GaN (or p-AlGaN) layer to the AlGaN/GaN heterostructure at the gate contact area is the most promising strategy so far. Even in the absence of a bias ( $V_{gs} = 0$ ) that is imposed from the outside, depletion of the 2DEG channel may still take place due to the p-GaN layer lifting the band diagram. **Figure 1.10** shows a simplified diagram of the basic operating principle of a E-mode HEMT with a p-GaN gate. In an AlGaN/GaN heterostructure, normallyon operation is achieved by using a conventional schottky contact as the gate electrode. However, when a p-GaN cap layer is added to the AlGaN, the AlGaN's conduction band is raised, and the 2DEG is depleted. This allows for the possibility of normally-off functioning of the device.

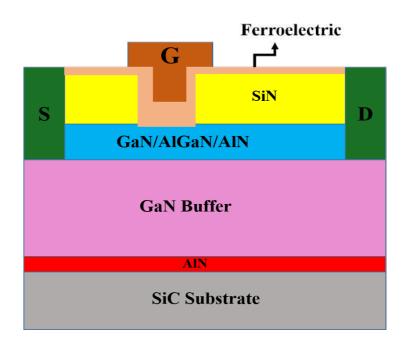

### 1.2.4.6 Ferroelectric Gate GaN HEMT

Ferroelectric gate AlGaN/GaN HEMT construction is shown in **Figure 1.11.** Ferroelectric materials have a strong polarization effect, which can control the polarization in 2-D electron gases (2DEG) and threshold voltage. E-mode GaN-based HEMTs are possible because ferroelectric polarization is opposite to nitride polarization, which is dependent on the growth process and applied voltage. The E-mode ferroelectric gate HEMTs with  $V_{th} = 1$  V had a very high field-effect mobility of 1819 cm<sup>2</sup>/Vs, a low SS of 90 mV/dec, and a significant I<sub>ON</sub>/I<sub>OFF</sub> of  $1.5 \times 10^{10}$  (*Zhu et al., 2017*). As the 2DEG channel is preserved in ferroelectric gate E-mode

HEMTs, they are excellent candidates for use in high-speed logic circuits.

Figure. 1.11 Schematic representation of ferroelectric gate GaN-HEMT (Zhu et al., 2017)

## **1.3 Advantages of GaN HEMT**

- 1. High Power Density: GaN HEMTs offer higher power density compared to traditional silicon-based transistors, enabling smaller and more compact power electronic systems.

- 2. High Switching Speed: GaN HEMTs have fast switching speeds in the nanosecond range, which makes them well-suited for high-speed switching applications such as wireless communication systems, radar, and power converters.

- **3.** High Breakdown Voltage: GaN HEMTs have a wide bandgap, which allows them to handle high voltage levels without experiencing a premature breakdown, making them suitable for high-voltage applications.

- 4. Wide Temperature Range: GaN HEMTs can operate at high temperatures, which makes them useful in high-temperature applications such as aerospace, automotive, and industrial environments.

# **1.4 Challenges Confronted by the GaN HEMT**

Although GaN HEMT devices showcasing outstanding performance in RF and microwave power applications, they predominantly operate in depletion mode (d-mode). However, the market demand leans towards enhancement mode (E-mode) devices. Consequently, extensive research and development have been dedicated to E-mode HEMTs and metal-oxide-semiconductor field-effect transistors (MIS-HEMTs) in recent years, driven by the increasing demand from various applications. The utilization of E-mode devices in RF/microwave circuits enables the elimination of negative-polarity power supply, simplifying the circuit and system architecture. Additionally, power switches based on E-mode devices offer intrinsic fail-safe operation, making them highly desirable for power electronics. Various methods have been proposed for realizing E-mode devices, such as thin barrier structures (*Endoh et al., 2004*), fluorine plasma treatment (*Su et al., 2014*), and p-GaN cap structures (*Hu et al., 2000*). Each approach has its own advantages and disadvantages, leaving room for further improvement.

One significant challenge encountered with HEMT technology is the undesired spilling of 2DEG from the GaN channel to the buffer layer, leading to reduced mobility and device reliability (*Khan et al., 1992*). Numerous techniques have been reported to address this issue and prevent the overflow of 2DEG into the buffer layer. For instance, the double heterostructure HEMT method introduces a back-barrier layer between the channel and the buffer layer (*Gu et al., 2019*). This approach, considered the simplest and most effective way to enhances the confinement of the heterojunction 2DEG and prevents excessive carrier flow into the buffer layer. Various studies (*Chen et al., 2003, Lee et al., 2011, Meng et al., 2012*) have explored the impact of AlGaN back-barrier layers on HEMTs. To some extent, the carrier confinement is improved using this approach, but it also creates a parasitic channel at the junction between the AlGaN back barrier and the GaN buffer. Researchers have also adopted another technique involving doping the buffer layer with iron (Fe) or carbon (C) acceptors to increase its resistivity (*Pampili and Parbrook, 2017*). However, these dopants generate deep-level acceptors in the layer, leading to current collapse (*Uren et al., 2012*).

Another significant challenge that GaN HEMT encounters is related to its strain problem, which arises due to the lattice mismatch at the interface of GaN/AlGaN. At the interface between the barrier-layer and buffer of the AlGaN/GaN HEMT, a polarization discontinuity is formed,

resulting from piezo and spontaneous polarization. This polarization discontinuity generates a highly mobile sheet charge that serves as the channel charge. The polarization discontinuity of standard AlGaN/GaN-HEMTs, which incorporates piezo and random components, is proportional to the aluminium concentration in the barrier layer. Either using modulation doping or increasing the amount of aluminium in the barrier layer is required in order to achieve the desired increase in sheet charge density and subsequent increase in maximum DC-output current. However, excessive Al concentration increases strain and degrades the material quality. Thus, it is crucial to explore new barrier engineering approaches that can overcome the strain issue and enhance the device's performance.

## **1.5 Research Objectives**

- 1. To create a GaN HEMT that can surmount the major challenges of GaN HEMT such as spilling of 2DEG and high leakage current. For this, various engineering schemes such as polarization-doped buffer engineering, T-shaped gate metal engineering, and InAlN/AlN barrier engineering have been amalgamated over GaN HEMT.

- 2. To investigate the influence of a high-k dielectric material, specifically HfO<sub>2</sub>, on the performance of an E-mode T-gate InAlN/AlN HEMT with a polarization-doped buffer. The primary goal here is to get a knowledge of how the presence of HfO<sub>2</sub> changes the electrical properties of the device as well as its overall performance. By examining parameters such as threshold voltage, transconductance, and subthreshold slope, the impact of the high-k dielectric on the device's performance can be evaluated.

- **3.** To investigate the impact of T-shaped gate geometry on parasitic capacitance and RF Figure of Merits (FOMs) such as maximum oscillation frequency, gain-bandwidth product, cut-off frequency, maximum stable and available power gain, maximum transducer power gain and stability factor of E-mode T-gate InAlN/AlN HEMT with polarization doped buffer.

- 4. To examine the small signal and noise behavior of T-gate E mode HEMT with a polarization-doped buffer. By studying the small signal and noise behaviour, valuable insights can be gained regarding the device's overall performance, signal amplification capabilities, and noise figure.

- 5. To design the double channel E-mode T-gate HEMT with back barrier which significantly affects the current driving capability and the switching performance. The various performance parameters, such as drain current, transconductance, intrinsic gain, output conductance, early voltage, parasitic capacitances, cut-off frequency, maximum oscillation frequency, gain frequency product, transconductance frequency product, and gain transconductance frequency product, can be evaluated in order to reflect its effectiveness in RF applications.

- 6. To examine the influence of the back barrier distance from the lower channel in an Emode T-gate double channel HEMT. In order to assess the linearity and intermodulation distortion parameters, which are critical for evaluating the performance of modern highfrequency wireless communication systems.

## **1.6 Thesis Organization**

This thesis is divided into six chapters, each of which is aimed to address specific research objectives. At the end of the respective chapter the references to each chapter are listed.

**Chapter 1** introduces wide-bandgap materials, focusing on gallium nitride (GaN)'s importance in power electronics. The chapter covers GaN HEMT basics including the polarization effect and operating principle. The chapter also examines literature-reported device engineering schemes. These schemes include the double heterostructure HEMT with a graded back barrier, gate field plate, high gate multi-recessed buffer, double-channel MOS-HEMT, P-gate GaN HEMT and Ferroelectric gate GaN HEMT. These engineering methods are described to demonstrate their potential performance improvements in GaN HEMT technology. The chapter also discusses GaN HEMT challenges. Lastly, the Chapter concludes by outlining the overall organization of the thesis. It emphasizes the significance of the research presented in this thesis.

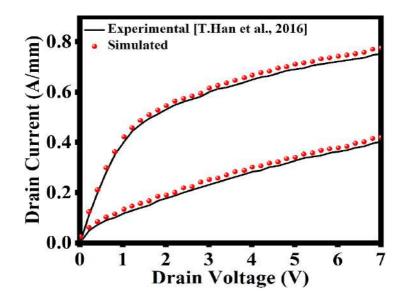

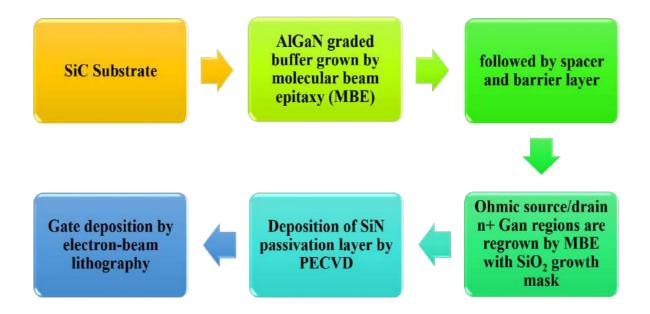

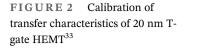

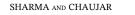

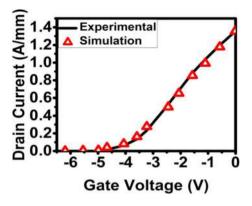

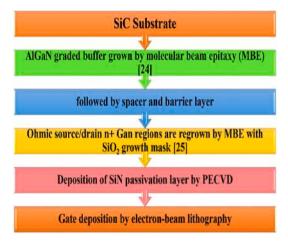

**Chapter 2** describes the proposed device along with simulation parameters. The chapter also describes the simulation models used in this investigation, including their calibration using experimental data from relevant literature. A step-by-step fabrication process flow is shown to determine device fabrication feasibility. The chapter examines how gate and drain bias, gate recessed depth, and high k gate dielectric affect the electrical and RF performance of E-mode T-gate InAlN/AlN HEMTs with polarization doped buffer *(Sharma and Chaujar, 2022, 2022)*.

#### *Sharma et al., 2023a).*

**Chapter 3** investigates the impact of T-shaped gate geometry on parasitic capacitance and RF Figure of Merits (FOMs) such as maximum oscillation frequency  $(f_{max})$ , gain-bandwidth product (GBP), cut-off frequency  $(f_T)$ , maximum stable and available power gain (Gms and Gma), maximum transducer power gain (MSG) and stability factor (k) of E-mode T-gate InAlN/AlN HEMT with polarization doped buffer. Furthermore, the chapter investigates the impact of gate head length (H<sub>length</sub>), gate stem height (S<sub>height</sub>), and gate foot length (F<sub>length</sub>) on the RF FOMs. The simulation results for the proposed device structure showcase its suitability for high-performance RF/microwave applications.

**Chapter 4** discusses the characteristics of a T-gate E mode HEMT with a polarization-doped buffer, focusing on its small signal and noise behaviour. The polarization-induced doping in the buffer layer creates an upwardly convex conduction band, resulting in improved confinement of the 2DEG, reduced buffer leakage current, and significantly enhanced transconductance. This increase in transconductance leads to a decrease in the reflection coefficient (S11, S22) and an improvement in the transmission coefficient (S21) compared to GaN buffer HEMTs. The various noise parameters, including the minimum noise figure, noise conductance, and auto/cross-correlation factor for the proposed device are evaluated. The simulated results indicate that the T-gate polarization-doped buffer (PDB-HEMT) structure is an excellent choice for Low Noise Amplifiers (LNA) operating at higher frequencies (*Sharma et al., 2023b*).

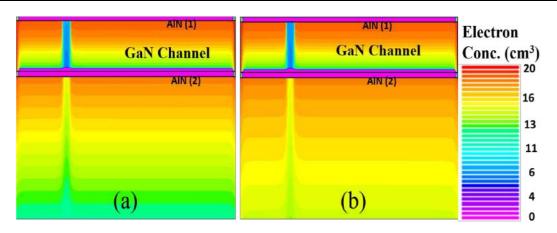

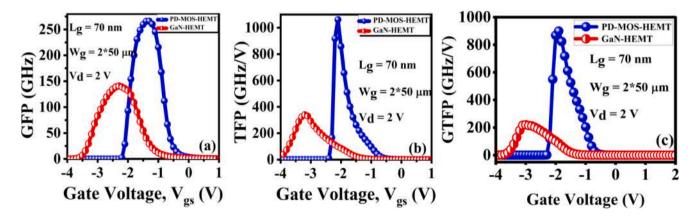

**Chapter 5** discusses the design and analysis of E-mode T-gate double-channel High Electron Mobility Transistor (HEMT) with an InGaN back barrier. The formation of the double channel is due to the addition of the AlN layer underneath the InAlN/GaN interface, which in turn results in an increase in the drain current density of 2.5 A/mm. However, due to a lack of gate controllability over a lower channel, a high leakage current is observed in double channel HEMT. The use of InGaN as a back barrier allowed for the successful resolution of this issue. This increases the conduction band for the GaN buffer, which results in better carrier confinement in 2DEG. The proposed device's performance is measured against that of standard double-channel HEMT. Various performance parameters, such as drain current ( $I_{ds}$ ), transconductance ( $g_m$ ), intrinsic gain ( $A_v$ ), output conductance ( $g_d$ ), early voltage ( $V_{EA}$ ), TGF, parasitic capacitances ( $C_{gs}$ ,  $C_{gd}$ ), cut-off frequency ( $f_T$ ), maximum oscillation frequency (fmax), gain frequency product (GFP), transconductance frequency product (TFP), and gain transconductance frequency product (GTFP), are investigated. Furthermore, the linearity parameters such as VIP2, VIP3, IIP3, 1-dB compression point has been investigated by varying the back barrier distance from the lower channel. *(Sharma and Chaujar, 2021)*.

**Chapter 6** provides a summary of the overall research work illustrated in this thesis. Additionally, this chapter explores the potential for future advancements and discusses how this work can be expanded and used in future for further research directions.

## **1.7 References**

- AMBACHER, O., FOUTZ, B., SMART, J., SHEALY, J. R., WEIMANN, N. G., CHU, K., MURPHY, M., SIERAKOWSKI, A. J., SCHAFF, W. J., EASTMAN, L. F., DIMITROV, R., MITCHELL, A. and STUTZMANN, M. 2000. Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures. Journal of applied physics, 87, 334-344.

- AMBACHER, O., SMART, J., SHEALY, J. R., WEIMANN, N. G., CHU, K., MURPHY, M., SCHAFF, W. J., EASTMAN, L. F., DIMITROV, R., WITTMER, L., STUTZMANN, M., RIEGER, W. and HILSENBECK, J. 1999. Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N-and Ga-face AlGaN/GaN heterostructures. Journal of applied physics, 85, 3222-3233.

- ASIF KHAN, M., KUZNIA, J. N., OLSON, D. T., SCHAFF, W. J., BURM, J. W., and SHUR, M. S. 1994. Microwave performance of a 0.25 μm gate AlGaN/GaN heterostructure field effect transistor. Applied Physics Letters, 65, 1121-1123.

- CAI, Y., GONG, Y., BAI, J., YU, X., ZHU, C., ESENDAG, V., LEE, K. B. and WANG, T.2018. Controllable uniform green light emitters enabled by circular HEMT-LED devices.IEEE Photonics Journal, 10, 1-7.

- CHEN, C. Q., ZHANG, J. P., ADIVARAHAN, V., KOUDYMOV, A., FATIMA, H., SIMIN, G., YANG, J. and ASIF KHAN, M.2003. AlGaN/GaN/AlGaN double heterostructure for high-power III-N field-effect transistors. Appl. Phys. Lett., 82, 4593-4595.

CHUNG, J. W., HOKE, W. E., CHUMBES, E. M., and PALACIOS, T. 2010. AlGaN/GaN

HEMT With 300-GHz fmax. IEEE Electron Device Letters, 31, 195-197.

- ENDOH, A., YAMASHITA, Y., IKEDA, K., HIGASHIWAKI, M., HIKOSAKA, K., MATSUI, T., HIYAMIZU, S. and MIMURA, T.2004.Non-Recessed-Gate Enhancement-Mode AlGaN/GaN High Electron Mobility Transistors with High RF Performance.*Jpn. J. Appl. Phys.*,43, 2255.

- GASKA, R., CHEN, Q., YANG, J., OSINSKY, A., KHAN, M. A., and SHUR, M. S. 1997. High-temperature performance of AlGaN/GaN HFETs on SiC substrates. IEEE Electron Device Letters, 18, 492-494.

- GERMAIN, M., LEYS, M., BOEYKENS, S., DEGROOTE, S., WANG, W., SCHREURS, D., RUYTHOOREN, W., CHOI, K. H., VAN DAELE, B., VAN TENDELOO, G. and BORGHS, G. 2003. High electron mobility in AlGaN/GaN HEMT grown on sapphire: strain modification by means of AlN interlayers. MRS Online Proceedings Library (OPL), 798, Y10-22.

- GRECO, G., IUCOLANO, F., and ROCCAFORTE, F. 2018. Review of technology for normally-off HEMTs with p-GaN gate. Materials Science in Semiconductor Processing, 78, 96-106.

- GU, Y., CHANG, D., SUN, H., ZHAO, J., YANG, G., DAI, Z., and DING, Y. 2019. Theoretical study of InAlN/GaN high electron mobility transistor (HEMT) with a polarization-graded AlGaN back-barrier layer. Electronics, 8, 885.

- HU, X., SIMIN, G., YANG, J., ASIF KHAN, M., GASKA, R. and SHUR, M.S.2000. Enhancement mode AlGaN/GaN HFET with selectively grown pn junction gate.*Electronics Letters*, 36, 753-754.

- KAMECHE, M., and DROZDOVSKI, N. V. 2005. GaAs-, InP-and GaN HEMT-based microwave control devices: what is best and why. Microwave Journal, 48, 164-173.

- KARMALKAR, S., and MISHRA, U. K. 2001. Enhancement of breakdown voltage in AlGaN/GaN high electron mobility transistors using a field plate. IEEE transactions on electron devices, 48, 1515-1521.

- KARMALKAR, S., SHUR, M. S., SIMIN, G., and KHAN, M. A. 2005. Field-plate engineering for HFETs. IEEE Transactions on electron devices, 52, 2534-2540.

- KELLER, S., LI, H., LAURENT, M., HU, Y., PFAFF, N., LU, J., and BROWN, D. F. (2014).

N. A. FICHTENBAUM, JS SPECK, SP DENBAARS, UK MISHRA, Recent progress in metal-organic chemical vapor deposition of (000-1) N-polar group-III nitrides. Semiconductor Science and Technology, 29, 113001.

- KEMERLEY, R. T., WALLACE, H. B., and YODER, M. N. 2002. Impact of wide bandgap microwave devices on DoD systems. Proceedings of the IEEE, 90, 1059-1064.

- KENTE, T., and MHLANGA, S. D. 2016. Gallium nitride nanostructures: Synthesis, characterization and applications. Journal of Crystal Growth, 444, 55-72.

- KHAN, M. A., KUZNIA, J. N., OLSON, D. T., SCHAFF, W. J., BURM, J. W., and SHUR, M.

S. 1994. Microwave performance of a 0.25 µm gate AlGaN/GaN heterostructure field effect transistor. *Applied Physics Letters*, 65, 1121-1123.

- KHAN, M.A., KUZNIA, J.N., HOVE, J.M., PAN, N., and CARTER, J. 1992. Observation of a two-dimensional electron gas in low pressure metalorganic chemical vapor deposited GaN-AlxGa1-xN heterojunctions. *Appl. Phys. Lett.*,60,3027–3029.

- KUMAR, J. R., NIRMAL, D., HOODA, M. K., SINGH, S., AJAYAN, J., and ARIVAZHAGAN, L. 2021. Intensive study of field-plated AlGaN/GaN HEMT on silicon substrate for high power RF applications. Silicon, 1-6.

- KUMAR, V., LU, W., SCHWINDT, R., KULIEV, A., SIMIN, G., YANG, J., KHAN, M. A. and ADESIDA, I. 2002. AlGaN/GaN HEMTs on SiC with f T of over 120 GHz. IEEE Electron Device Letters, 23, 455-457.

- KUZMÍK, J. 2001. Power electronics on InAlN/(In) GaN: Prospect for a record performance. IEEE Electron Device Letters, 22, 510-512.

- LEE, D.S., GAO, X., GUO, S., and PALACIOS, T.2011. InAlN/GaN HEMTs with AlGaN back barriers. IEEE Electron Devcies Lett., 32, 617–619.

- LIM, T., AIDAM, R., WALTEREIT, P., HENKEL, T., QUAY, R., LOZAR, R., MAIER, T., KIRSTE, L. and AMBACHER, O. 2010. GaN-based submicrometer HEMTs with latticematched InAlGaN barrier grown by MBE. IEEE Electron Device Letters, 31, 671-673.

MANEL, C., HAFEDH, B., MOHAMED ALI, Z., and HASSEN, M. 2012. 2-D Theoretical

Model for Current–Voltage Characteristics in AlGaN/GaN HEMT's. Journal of Modern Physics, 2012.

- MENG, F., ZHANG, J., ZHOU, H., MA, J., XUE, J., DANG, L., ZHANG, L., LU, M., AI, S., LI, X., and HAO, Y.2012. Transport characteristics of AlGaN/GaN/AlGaN double heterostructures with high electron mobility. J. Appl. Phys.,112, 023707.

- NEUBURGER, M., ZIMMERMANN, T., KOHN, E., DADGAR, A., SCHULZE, F., KRTSCHIL, A., GUNTHER, M., WITTE, H., BLASING, J., KROST, A., DAUMILLER, I. and KUNZE, M. 2004. Unstrained InAlN/GaN HEMT structure. In Proceedings. IEEE Lester Eastman Conference on High Performance Devices. 161-166.

- NIRMAL, D., and AJAYAN, J. (Eds.). 2019. Handbook for III-V high electron mobility transistor technologies. CRC Press.

- PAMPILI, P. and PARBROOK, P.J.2017. Doping of III-nitride materials.Mater. Sci. Semicond. Process.,62,180–191.

- QIN, H., LUAN, X., FENG, C., YANG, D., and ZHANG, G. 2017. Mechanical, thermodynamic and electronic properties of wurtzite and zinc-blende GaN crystals. Materials, 10, 1419.

- RAIS-ZADEH, M., ZHU, H., and ANSARI, A. 2017. Applications of gallium nitride in MEMS and acoustic microsystems. In 2017 IEEE 17th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF) (pp. 9-11). IEEE.

- SHARMA, M., and CHAUJAR, R. 2021. Design and investigation of recessed-T-gate double channel HEMT with InGaN back barrier for enhanced performance. Arabian Journal for Science and Engineering, 1-8.

- SHARMA, M., and CHAUJAR, R. 2022. Ultrascaled 10 nm T-gate E-mode InAlN/AlN HEMT with polarized doped buffer for high power microwave applications," Int. J. RF Microw. Comput. Aided Eng., 32, 23057.

- SHARMA, M., KUMAR, B. and CHAUJAR, R. 2023a. Polarization induced doping and highk passivation engineering on T-gate MOS-HEMT for improved RF/microwave performance. Materials Science and Engineering,290,116298.

- SHARMA, M., KUMAR, B., and CHAUJAR, R. 2023b. Small signal and noise analysis of Tgate HEMT with polarization doped buffer for LNAs. Micro and Nanostructures, 180, 207593.

- SHRESTHA, N. M., LI, Y., and CHANG, E. Y. 2014. Simulation study on electrical characteristic of AlGaN/GaN high electron mobility transistors with AlN spacer layer. Japanese Journal of Applied Physics, 53, 04EF08.

- SMORCHKOVA, I. P., CHEN, L., MATES, T., SHEN, L., HEIKMAN, S., MORAN, B., ... KELLER, S., DENBAARS, S.P., SPECK, J. S. and MISHRA, U. K. 2001. AlN/GaN and (Al, Ga) N/AlN/GaN two-dimensional electron gas structures grown by plasma-assisted molecular-beam epitaxy. Journal of Applied Physics, 90, 5196-5201.

- SU, L.Y., LEE, F. and HUANG, J.J.2014. Enhancement-Mode GaN-Based High-Electron Mobility Transistors on the Si Substrate With a P-Type GaN Cap Layer.*IEEE Transactions on Electron Devices*,61,460-465.

- TEKE, A., GÖKDEN, S., TÜLEK, R., LEACH, J. H., FAN, Q., XIE, J., OZGUR, U., MORKOC, H., LISESIVDIN, S. B., ÖZBAY, E. 2009. The effect of AlN interlayer thicknesses on scattering processes in lattice-matched AlInN/GaN two-dimensional electron gas heterostructures. New Journal of Physics, 11, 063031.

- TREW, R. J. 2002. SiC and GaN transistors-is there one winner for microwave power applications?. Proceedings of the IEEE, 90, 1032-1047.

- UREN, M. J., MOREKE, J. and KUBALL, M.2012. Buffer design to minimize current collapse in GaN/AlGaN HFETs.IEEE Trans. Electron Devices,59,3327–3333.

- WANG, R., LI, G., KARBASIAN, G., GUO, J., SONG, B., YUE, Y., HU, Z., LABOUTIN,

O., CAO, Y., JOHNSON, W., SNIDER, G., FAY, P., JENA, D. and XING, H. G. 2013.

Quaternary Barrier InAlGaN HEMTs With fT/ fmax of 230/300 GHz. IEEE Electron

Device Letters, 34, 378-380.

- WU, T. L., TANG, S. W., and JIANG, H. J. 2020. Investigation of recessed gate AlGaN/GaN MIS-HEMTs with double AlGaN barrier designs toward an enhancement-mode characteristic. Micromachines, 11, 163.

#### WU, Y. F., KAPOLNEK, D., IBBETSON, J. P., PARIKH, P., KELLER, B. P., and MISHRA, Megha Sharma 26

U. K. 2001. Very-high power density AlGaN/GaN HEMTs. IEEE Transactions on Electron Devices, 48, 586-590.

- ZHU, S., JIA, H., LI, T., TONG, Y., LIANG, Y., WANG, X., ZENG, T. and YANG, Y. 2019. Novel high-energy-efficiency AlGaN/GaN HEMT with high gate and multi-recessed buffer. Micromachines, 10, 444.

- ZHU, J., CHEN, L., JIANG, J., LU, X., YANG, L., HOU, B., LIAO, M., ZHOU, Y., MA, X. and HAO, Y. 2017. Ferroelectric gate AlGaN/GaN E-mode HEMTs with high transport and sub-threshold performance. IEEE Electron Device Letters, 39, 79-82.

## CHAPTER 2

# Simulation of T-Gate E-Mode HEMT with Polarization Induced Doped Buffer for Electrical and RF Performance

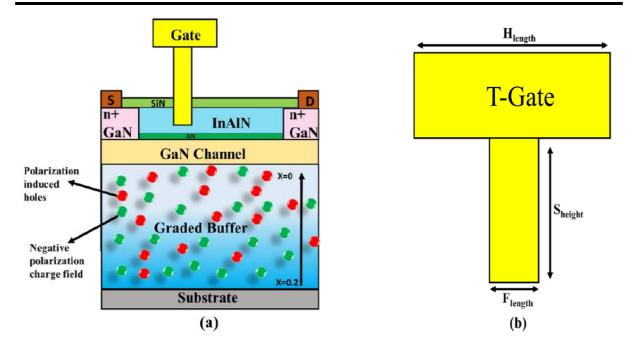

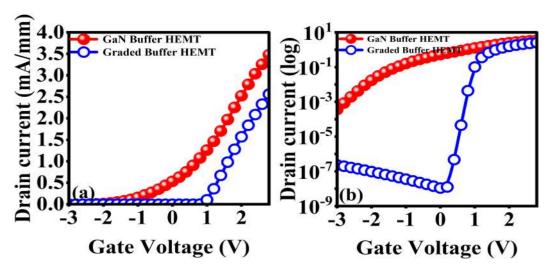

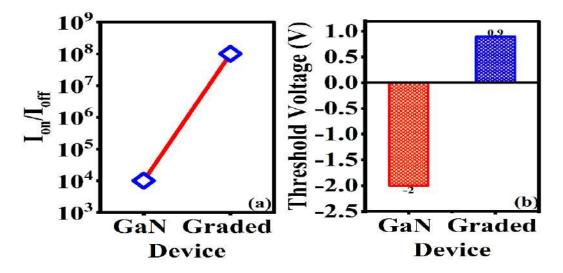

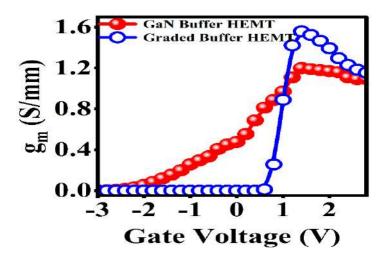

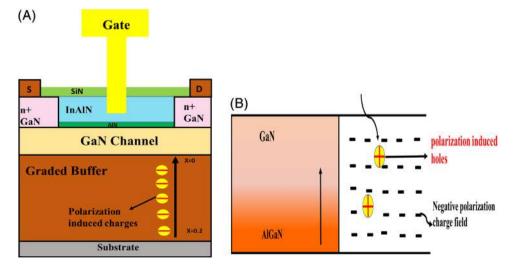

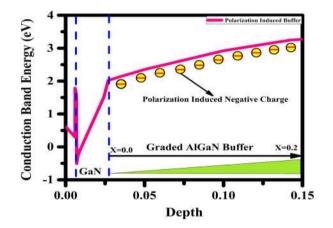

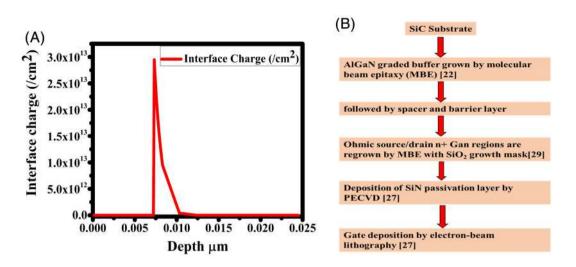

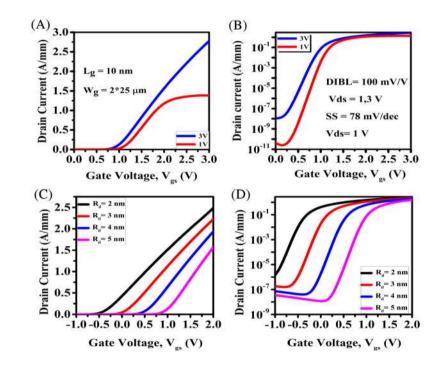

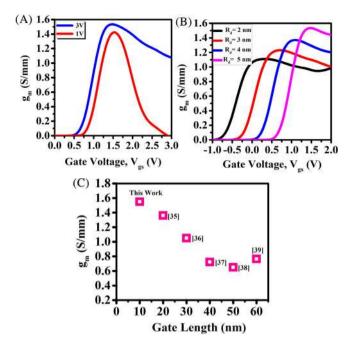

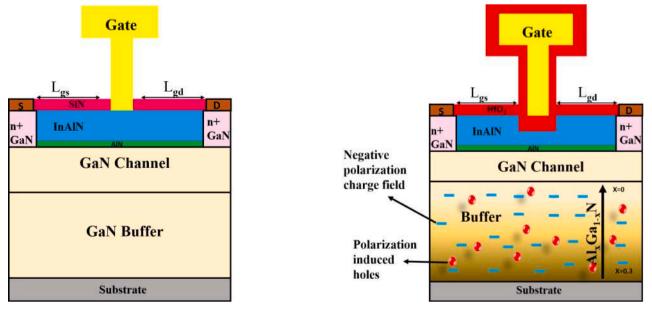

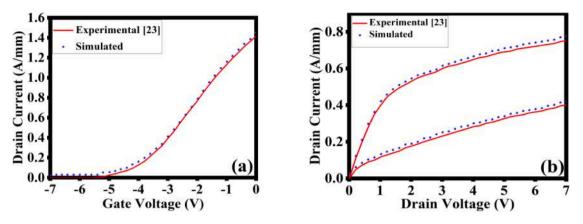

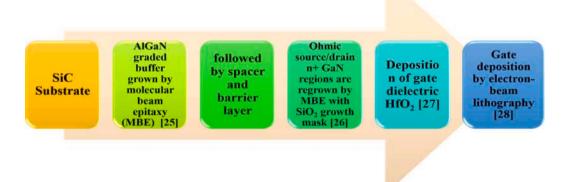

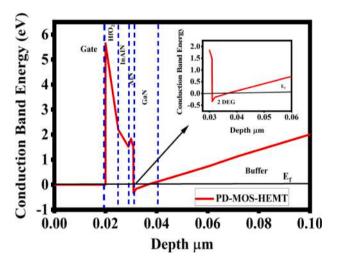

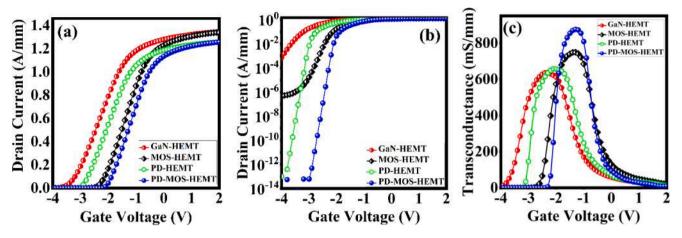

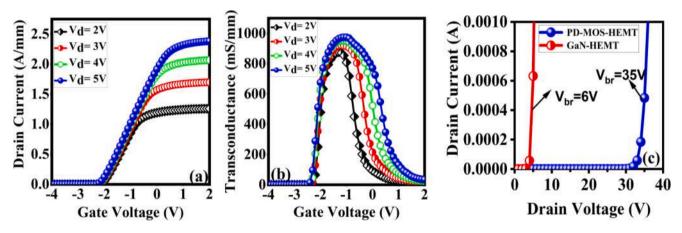

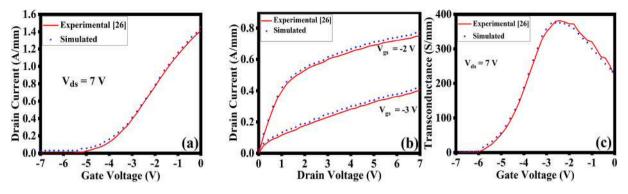

This chapter focuses on the DC and RF performance of T-gate E mode HEMT with polarization induced doped buffer. The proposed device has the feature of polarization induce doping in the buffer layer (buffer Engineered), heavily doped source/drain region, and recessed T-gate (Gate Metal Engineered) structure. The polarization-induced doping in the buffer layer bent the conduction band upwardly convex, which enhanced the 2DEG confinement, reduced the buffer leakage current, and significantly uplifted the breakdown voltage (33 V), which is 5 times higher than the conventional InAlN/AIN GaN buffer HEMT (8 V). The recessed gate engineering further enhances various performance parameters. It achieves an impressive  $I_{on}/I_{off}$  ratio of  $10^9$ , reduces the subthreshold swing (SS) to 78 mV/dec, and minimizes the drain-induced barrier lowering (DIBL) to 100 mV/V. The proposed device exhibits a high current density of 2.8 A/mm, transconductance 1.55 S/mm, cutoff frequency  $f_T$  (583 GHz), and maximum oscillation frequency  $f_{max}$  (840 GHz). At room temperature, the carrier density and mobility measured are 2.8 × 10<sup>13</sup> cm<sup>-2</sup> and 1250 cm<sup>2</sup>/Vs. The large Johnson figure of merit ( $f_T$ .  $V_{BR}$ ) 19.23 THz and ( $f_T$ .  $f_{max}$ )<sup>1/2</sup> 699 GHz shows the potential of the proposed device for high-power millimeter-wave applications.

Additionally, high-k gate oxide engineering has also been conducted in this chapter, where a specific region of the recessed gate is substituted with a high-k dielectric material. This integration of the high-k dielectric brings about notable improvements in both interfacial and transport characteristics, while concurrently reducing the gate leakage current. Nevertheless, it is important to note that implanting the gate oxide alone does not enable E-mode operation. As a result, the superior option for achieving E-mode operation is through the utilization of gate-recessed engineering techniques.

### **2.1 Introduction**

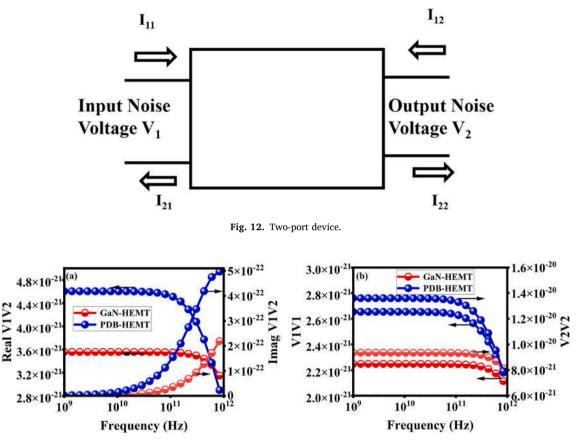

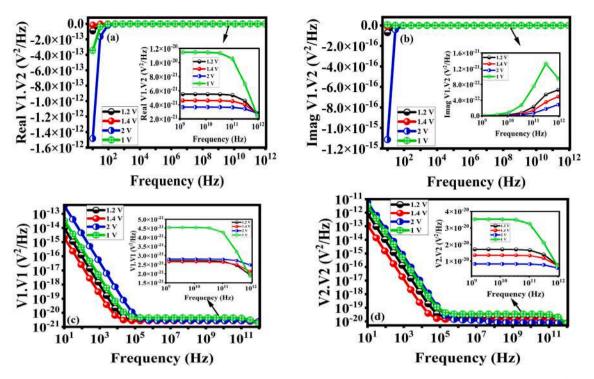

The HEMT is a special type of field effect transistor designed to operate at microwave frequencies. The HEMT is able to function at extremely high microwave frequencies and has a low noise figure. This is a very desirable combination. As a consequence of this, the device is utilized in regions of RF design in which it is necessary to achieve good performance at extremely high RF frequencies. Over the past few years, researchers have significantly enhanced the capabilities of GaN-based transistors used in high-frequency RF power amplifiers. Significant progress has been made in bridging the performance difference between low bandgap semiconductor technologies through advancements in raising the maximum cut-off frequency from several tens of GHz to around 450 GHz. Likewise, innovative methods for maintaining high speeds within broad bias ranges and cutting-edge technologies for enhancing peak frequency performance have emerged. Notably, HEMT devices find application across various RF design domains including radio astronomy, radio telecommunications, direct broadcast receivers (DBS), and RADAR (Radio Detection and Ranging System).