#### **Memristor Based Memory Design**

A thesis submitted to the

#### Delhi Technological University

For the award of the degree of

#### **DOCTOR OF PHILOSOPHY**

#### in

#### **Department of Electronics & Communication Engineering**

by

#### **Damyanti Singh**

#### 2K18/PhD/EC/02

Under the supervision of

#### **Prof. Neeta Pandey**

Department of Electronics & Communication Engineering, Delhi Technological University, Delhi –110 042

#### **Prof. Kirti Gupta**

Department of Electronics and Communication Engineering, Bharati Vidyapeeth's College of Engineering Delhi –110 063

Delhi Technological University, Shahbad Daulatpur, Main Bawana Road Delhi-110042 October 2023

## CERTIFICATE

This is to certify that the thesis entitled "**Memristor Based Memory Design**" submitted by Damyanti Singh (2K18/PhD/EC/02) to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi, for the award of the degree of Doctor of Philosophy is based on the original research work carried out by her under our guidance and supervision. In our opinion, the thesis has reached the standards fulfilling the requirement of the regulations relating to the degree. It is further certified that the work presented in this thesis is not submitted to any other university or institution for the award of any other degree or diploma.

**Prof. Neeta Pandey** Supervisor Department of Electronics & Communication Engineering, Delhi Technological University, Delhi –110 042 Prof. Kirti Gupta Supervisor Department of Electronics and Communication Engineering, Bharati Vidyapeeth's College of Engineering, Delhi –110 063

## DECLARATION

I hereby declare that the work presented in this thesis entitled "**Memristor Based Memory Design**" has been carried out by me under the supervision of **Prof. Neeta Pandey**, Department of Electronics & Communication Engineering, Delhi Technological University, Delhi and **Prof. Kirti Gupta**, Department of Electronics and Communication Engineering, Bharati Vidyapeeth's College of Engineering, Delhi and is hereby submitted for the award of the degree of Doctor of Philosophy in Department of Electronics & Communication, Delhi Technological University, Delhi.

I further undertake that the work embodied in this thesis has not been submitted for the award of any other degree or diploma elsewhere.

> **Damyanti Singh** 2K18/PhD/EC/02

## ACKNOWLEDGEMENT

The support and expert advice of my supervisors Prof. Neeta Pandey, Department of Electronics & Communication Engineering, Delhi Technological University, Delhi and Prof. Kirti Gupta, Department of Electronics and Communication Engineering, Bharati Vidyapeeth's College of Engineering, Delhi are greatly acknowledged with gratitude. I am also deeply grateful for their supervision, continuous motivation and support.

I am extremely thankful to the Head of the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi & other faculty members of Dept. of Electronics & Communication Engineering, Delhi Technological University, Delhi, for the motivation and inspiration. I am also thankful to all non-teaching staff at Delhi Technological University, and who have helped me directly or indirectly in completion of the Ph.D. work.

I express my deep sense of respect and gratitude to my parents for their continuous support in all stage of my life. I would like to thank my siblings for supporting me through this long journey. After that thanks to my husband for motivating me to go on with my research work from time to time. I would also like to thank my colleagues and seniors of the department for their support, especially Dr. Gurumurthy, Dr. Garima Varshney, Ms. Parveen Rani, Ms. Sweta and Mr. Lokesh.

> Damyanti Singh 2K18/PhD/EC/02

### ABSTRACT

Since the past few decades, SRAM is preferred in portable devices and it makes up a large portion of a system-on-chip area. Despite the fact that it is fast, the volatile nature limits its applications. Moreover, the continuous downscaling in technology and supply voltage encounters serious issues in device performance such as higher leakage power consumption. To overcome such issues, the researchers and academia have come up with a solution which is introduction of non-volatile memory (NVM) device with SRAM known as nvSRAM. The NVM device is generally used to back up the information in SRAM when supply voltage is turned off. Further, NVM devices can suppress leakage power consumption by turning off supply voltage of infrequently used SRAMs without loss of information. Among the different types of NVM, memristor have certain benefits such as small size, high-speed of operation, low programming voltage and compatibility with CMOS manufacturing process.

The 6T2R cell is the most common nvSRAM cell. However, it suffers with leakage issue due to the direct connection of memristor with internal nodes. To overcome this, various methods are suggested in literature. The commonly used approach is isolating memristor with internal nodes through a control transistor. Other than this, different techniques to improve nvSRAM performances like margin, power consumption, store/restore functionality are introduced in the existing work.

In most of the existing nvSRAM cells, differential write operation is performed. It needs charging/discharging of bitline pair that contributes significant percentage in total power consumption. To reduce this, a nvSRAM design is introduced in this work that performs single ended write operation and reduces write power consumption in an extent. The

proposed design uses a feedback transistor to improve write operation. It also improves store/restore performance through 1T1M structure. The presence of feedback transistor causes increment in leakage power consumption; three different approaches are suggested to overcome this.

To overcome write/read conflict, two nvSRAM designs with read decoupled (RD) port are introduced in this work. The isolation of read operation from internal nodes enhances read margin of the proposed designs. In one of the designs, the grounded gate low threshold voltage transistor is used to maintain the performance near threshold voltage. It also uses a charge pump circuit to overdrive read port to improve read performance. Another, proposed design uses column shared technique to improve write and restore performances. The 1T1M structure is used in both the designs to perform non-volatile operation.

Other than margins and power consumption, delay is also an important parameter and less attention is paid in this direction. The longer store/restore delay values may lead to loss of data. For this, three different techniques to reduce store and restore delays are presented in this work. These techniques are generic and are applicable to nvSRAM cells which uses 1T1M configuration to perform non-volatile operation. The control signals values are altered in these approaches. For verification purpose, these techniques are applied on one of the proposed designs. Other than this, a transmission gate (TG) based nvSRAM design is also introduced in this work. In existing nvSRAM cell performing single ended write operation, the an NMOS transistor is used to access the data. As it passes strong '0' and weak '1', the write '1' operation speed is degraded. To overcome this, the NMOS access transistor is replaced by TG that gives both strong '0' and '1' and leads to improved write performance.

In this design, memristor is connected between internal node and read bitline through read pass transistor to perform non-volatile operation.

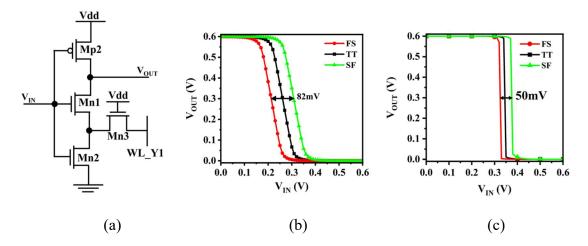

The scaling in technology and supply voltage lead to degradation in nvSRAM cell performance due to increase in sensitivity to process variations. Hence, it is required to introduce process invariant nvSRAM cells. In this work, two process invariant nvSRAM designs are introduced. Both the designs use Schmitt Trigger (ST) inverters in the core instead of CMOS inverters. The ST inverter provides tolerance against process variations specially at lower voltages. Also, the RD port is used to perform read operation. In one of the designs, memristor is connected between internal node and read bitline line to perform non-volatile operation. Another design uses 1T1M structure to perform non-volatile operation. Further, the failure probability analysis is carried out to examine the performance of both the analysis.

In the thesis, the performances of proposed designs are analyzed through SPICE simulations and  $TiO_2$  based memristor model is used to perform non-volatile operation. The results of proposed designs are compared with the considered nvSRAM cells. The supply voltage variation study is also performed for completeness.

vi

# TABLE OF CONTENTS

| C  | ertificatei                                              |  |  |  |

|----|----------------------------------------------------------|--|--|--|

| D  | eclarationii                                             |  |  |  |

| A  | cknowledgementiii                                        |  |  |  |

| A  | Abstractiv                                               |  |  |  |

| Та | able of contentsvii                                      |  |  |  |

| Li | st of Figuresx                                           |  |  |  |

| Li | st of Tablesxvi                                          |  |  |  |

| 1. | Chapter 1: Introduction1                                 |  |  |  |

|    | 1.1. Motivation                                          |  |  |  |

|    | 1.2. Literature review                                   |  |  |  |

|    | 1.3. Research gaps13                                     |  |  |  |

|    | 1.4. Research objectives14                               |  |  |  |

|    | 1.5. Organization of the thesis                          |  |  |  |

| 2. | Chapter 2: nvSRAM Cell with Improved Write Performance17 |  |  |  |

|    | 2.1. Introduction                                        |  |  |  |

|    | 2.2. Existing 8T nvSRAM cells                            |  |  |  |

|    | 2.3. Proposed design 1                                   |  |  |  |

|    | 2.3.1. Operation of Proposed design 121                  |  |  |  |

|    | 2.3.2. Simulation results and discussion                 |  |  |  |

|    | 2.4. Conclusion                                          |  |  |  |

| 3. | Chapter 3: nvSRAM cell with Improved Read Margin        | 41  |

|----|---------------------------------------------------------|-----|

|    | 3.1. Introduction                                       | 42  |

|    | 3.2. Existing RD nvSRAM cells                           | 43  |

|    | 3.3. Proposed design 2                                  | 44  |

|    | 3.3.1. Operation of Proposed design 2                   | 45  |

|    | 3.3.2. Simulation results and discussion                | 49  |

|    | 3.4. Proposed design 3                                  | 61  |

|    | 3.4.1. Operation of Proposed design 3                   | 62  |

|    | 3.4.2. Simulation results and discussion                | 66  |

|    | 3.5. Conclusion                                         | 77  |

| 4. | Chapter 4: nvSRAM cell with Delay Reduction Techniques. | 79  |

|    | 4.1. Introduction                                       | 80  |

|    | 4.2. Techniques for store and restore delay reduction   | 81  |

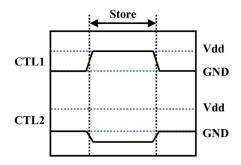

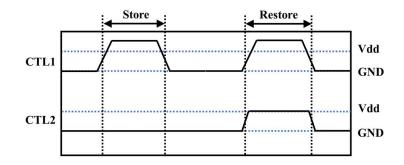

|    | 4.2.1. Negative CTL2 Technique                          | 83  |

|    | 4.2.2. Boosted CTL1 Technique                           | 83  |

|    | 4.2.3. Floating Vss Technique                           | 84  |

|    | 4.2.4. Application of Proposed techniques               | 84  |

|    | 4.3. Proposed design 4                                  |     |

|    | 4.3.1. Operation of Proposed design 4                   | 90  |

|    | 4.3.2. Simulation results and discussion                | 94  |

|    | 4.4. Conclusion                                         | 101 |

| 5. | Chapter 5: Process invariant nvSRAM cell                | 103 |

|    | 5.1. Introduction                                       | 104 |

| 5.2. Propo  | osed design 5                     |     |

|-------------|-----------------------------------|-----|

| 5.2.1.      | Operation of Proposed design 5    | 107 |

| 5.2.2.      | Simulation results and discussion | 111 |

| 5.3. Propo  | osed design 6                     |     |

| 5.3.1.      | Operation of Proposed design 6    | 125 |

| 5.3.2.      | Simulation results and discussion | 129 |

| 5.4. Failur | re Probability Analysis           | 141 |

| 5.5. Concl  | lusion                            | 147 |

| 6. Chapter  | 6: Conclusion and Future Scope    | 149 |

| 6.1. Sumn   | nary of work done                 | 150 |

| 6.2. Scope  | e for future work                 | 153 |

| References  |                                   | 154 |

# LIST OF FIGURES

| Fig. 1.1. Schematic of 6T2R cell [23]4                                                           |

|--------------------------------------------------------------------------------------------------|

| Fig. 2.1. Schematic of Proposed design 121                                                       |

| Fig. 2.2. Proposed design 1 during write operation                                               |

| Fig. 2.3. Proposed design 1 during (a) read '0' and (b) read '1' operation23                     |

| Fig. 2.4. Proposed design 1 during hold operation23                                              |

| Fig. 2.5. Proposed design 1 during (a) store and (b) restore operation                           |

| Fig. 2.6. State of memristor during non-volatile operation (a) initial (b) store (c) power down  |

| and (d) restore for logic '1'25                                                                  |

| Fig. 2.7. State of memristor during non-volatile operation (a) initial (b) store (c) power down  |

| and (d) restore for logic '0'25                                                                  |

| Fig. 2.8. Timing waveform for non-volatile operation of Proposed design 1 for (a) Logic '1'      |

| and (b) Logic '0'                                                                                |

| Fig. 2.9. Write margin and write delay of considered 8T nvSRAM cells and Proposed design         |

| 1 at different supply voltage                                                                    |

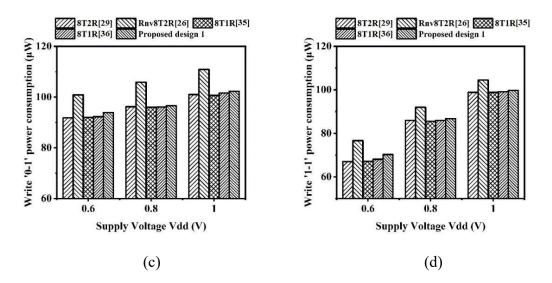

| Fig. 2.10. Write power consumption of considered 8T nvSRAM cells and Proposed design 1           |

| with different write patterns (a) 0-0 (b) 1-0 (c) 0-1 and (d) 1-1 at different supply voltage 32 |

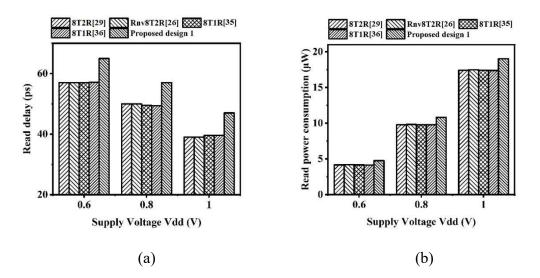

| Fig. 2.11. Read delay and read power consumption of considered 8T nvSRAM cells and               |

| Proposed design 1 at different supply voltage                                                    |

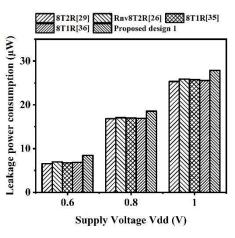

| Fig. 2.12. Leakage power consumption of different 8T nvSRAM cells at different supply            |

| voltage                                                                                          |

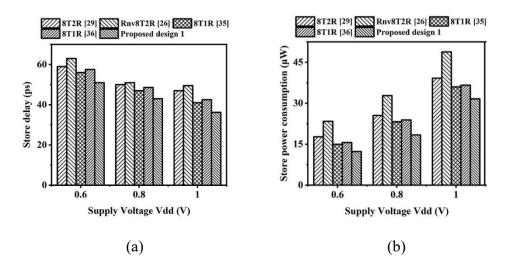

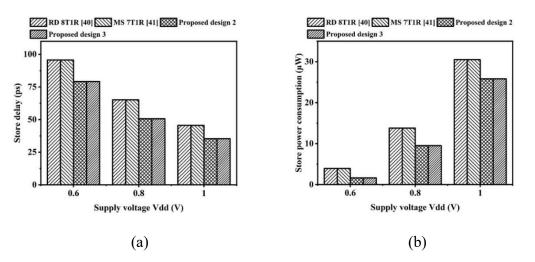

| Fig. 2.13. (a) Store delay and (b) store power consumption of considered 8T nvSRAM cells         |

|                                                                                                  |

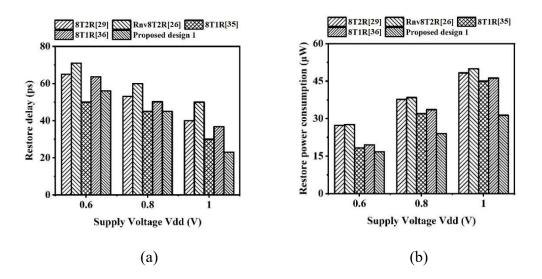

| Fig. 2.14. (a) Restore delay and (b) restore power consumption of considered 8T nvSRAM         |

|------------------------------------------------------------------------------------------------|

| cells and Proposed design 1 at different supply voltage                                        |

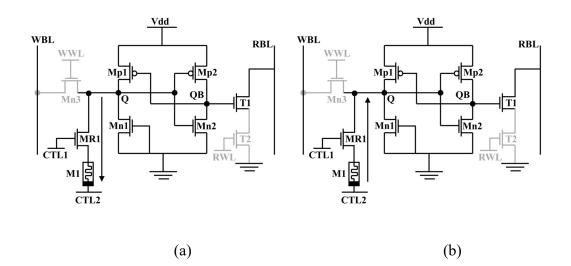

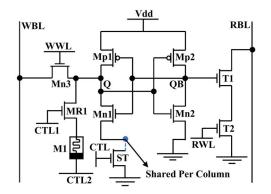

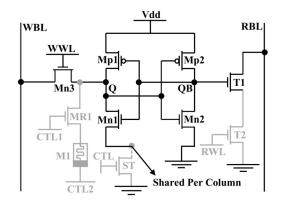

| Fig. 3.1. Schematic of Proposed design 244                                                     |

| Fig. 3.2. Proposed design 2 during write operation                                             |

| Fig. 3.3. Proposed design 2 during read operation                                              |

| Fig. 3.4. Proposed design 2 during hold operation                                              |

| Fig. 3.5. Proposed design 2 during (a) store and (b) restore operation                         |

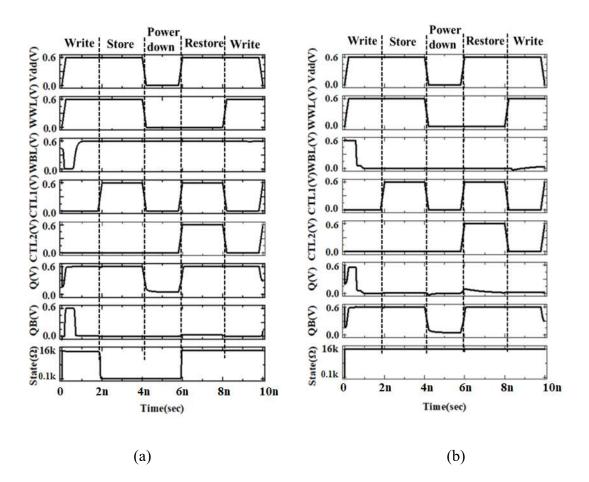

| Fig. 3.6. Timing waveform for non-volatile operation of Proposed design 2 for (a) Logic '1'    |

| and (b) Logic '0 operation                                                                     |

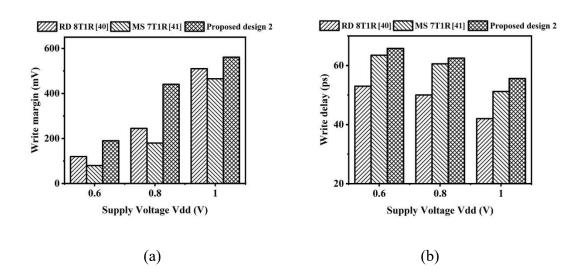

| Fig. 3.7. (a) WM and (b) Write delay of different RD nvSRAM cells at different supply          |

| voltage                                                                                        |

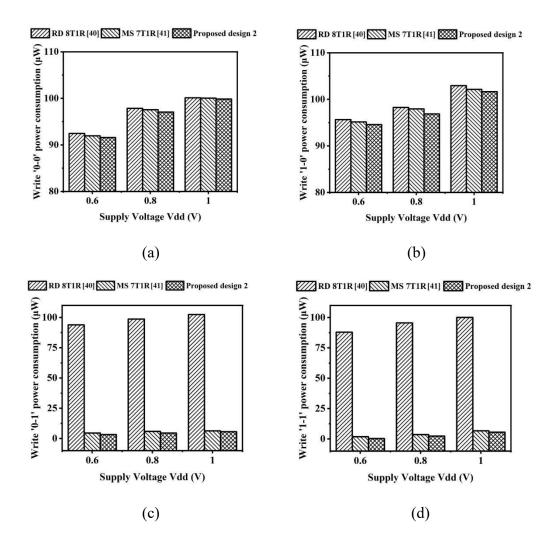

| Fig. 3.8. Write power consumption for Proposed design 2 and considered RD nvSRAM cells         |

| at different supply voltage for (a) 0-0 (b) 1-0 (c) 0-1 and (d) 1-1 write pattern55            |

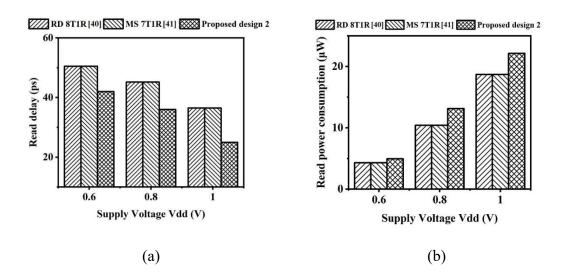

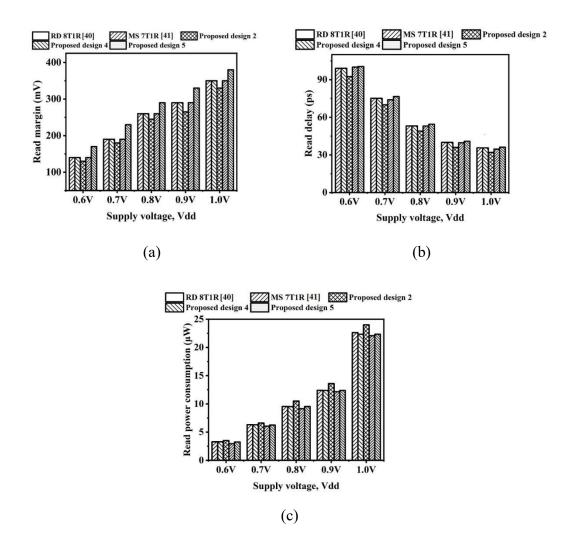

| Fig. 3.9. (a) Read delay and (b) read power consumption of considered RD nvSRAM cells          |

| and Proposed design 2 at different supply voltage                                              |

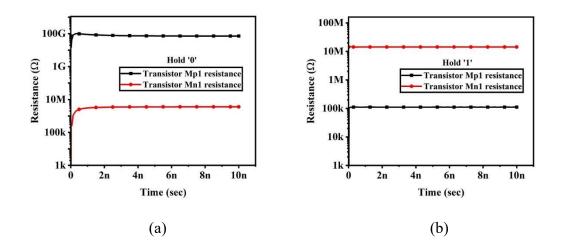

| Fig. 3.10. Resistance of transistor Mn1 and Mp1 during (a) hold '0' and (b) hold '1' operation |

|                                                                                                |

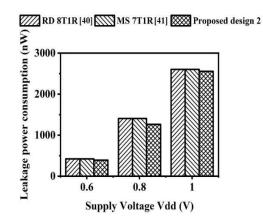

| Fig. 3.11. Leakage power consumption of different RD nvSRAM cells at different supply          |

| voltage                                                                                        |

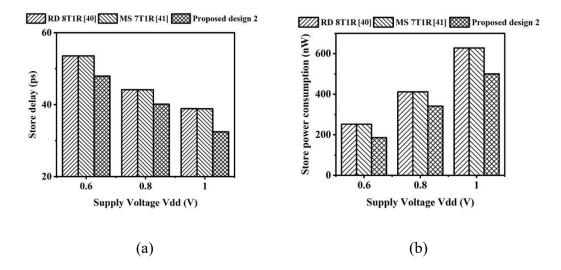

| Fig. 3.12. (a) Store delay and (b) store power consumption of different RD nvSRAM cells at     |

| different supply voltage60                                                                     |

| Fig. 3.13. (a) Restore delay and (b) restore power consumption of different RD nvSRAM          |

| cells at different supply voltage61                                                            |

| Fig. 3.14. Schematic of Proposed design 3                                                      |

| Fig. 3.15. Proposed design 3 during write operation                                          |

|----------------------------------------------------------------------------------------------|

| Fig. 3.16. Proposed design 3 during read operation                                           |

| Fig. 3.17. Proposed design 3 during hold operation                                           |

| Fig. 3.18. Proposed design 3 during (a) store and (b) restore operation                      |

| Fig. 3.19. Timing waveform for non-volatile operation of Proposed design 3 for (a) Logic '1' |

| and (b) Logic '0 operation                                                                   |

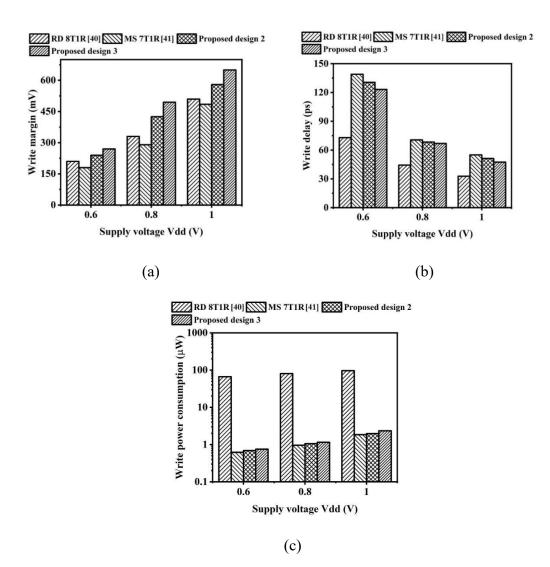

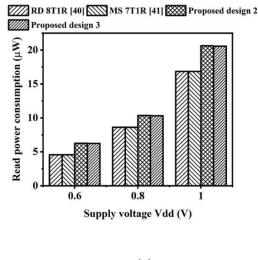

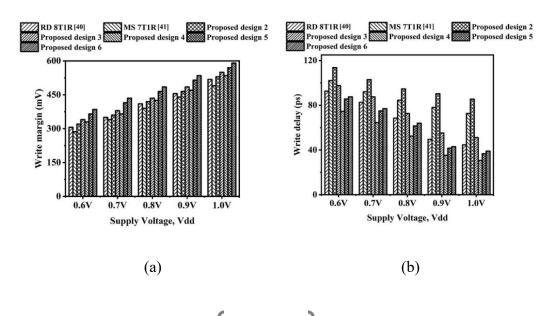

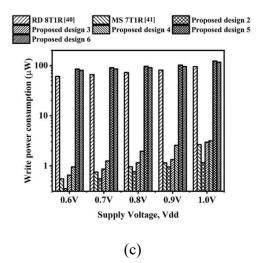

| Fig. 3.20. (a) Write margin (b) write delay and (c) write power consumption of considered    |

| RD nvSRAM cells and Proposed design 3 at different supply voltage70                          |

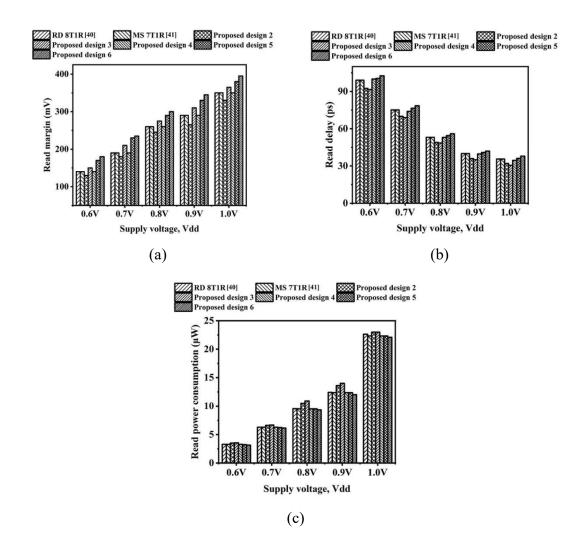

| Fig. 3.21. (a) Read margin (b) read delay and (c) read power consumption of considered RD    |

| nvSRAM cells and Proposed design 3 at different supply voltage72                             |

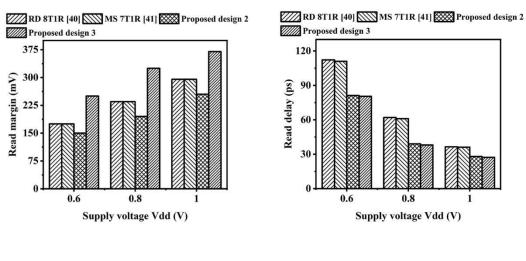

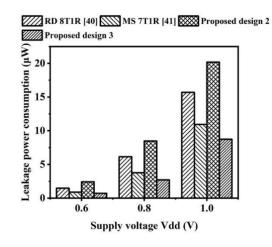

| Fig. 3.22. Leakage power consumption of different RD nvSRAM cells at different supply        |

| voltage73                                                                                    |

| Fig. 3.23. (a) Store delay and (b) store power consumption of different RD nvSRAM cells      |

| and Proposed design 3 at different supply voltage75                                          |

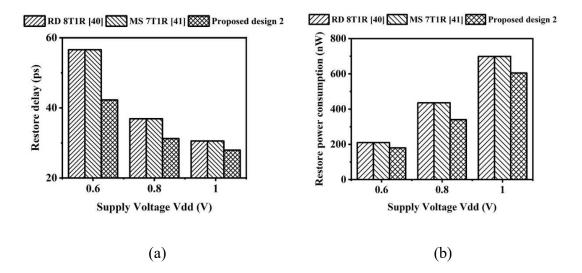

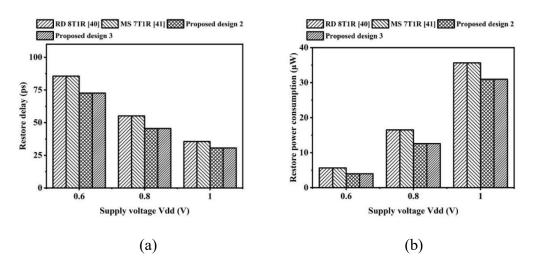

| Fig. 3.24. (a) Restore delay and (b) restore power consumption of different RD nvSRAM        |

| cells and Proposed design 3 at different supply voltage76                                    |

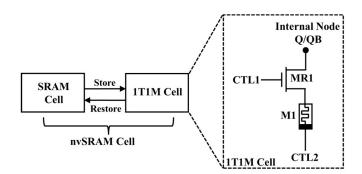

| Fig. 4.1. Generic structure of nvSRAM cell with 1T1M structure                               |

| Fig. 4.2. Negative CTL2 technique                                                            |

| Fig. 4.3. Boosted CTL1 technique                                                             |

| Fig. 4.4. Floating Vss technique                                                             |

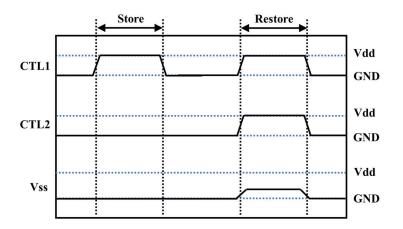

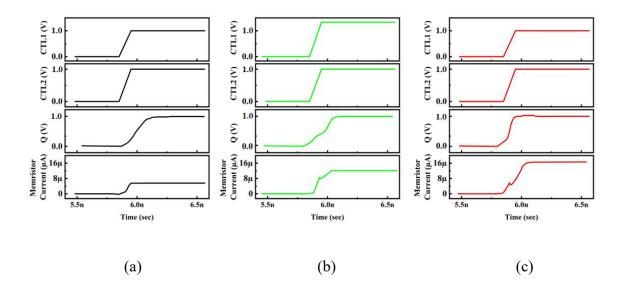

| Fig. 4.5. Timing waveform for store operation using (a) normal values (b) boosted CTL1       |

| technique and (c) negative CTL2 technique of Proposed design 1                               |

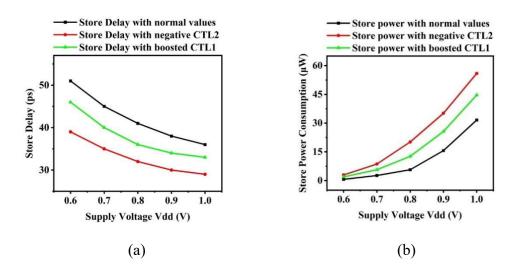

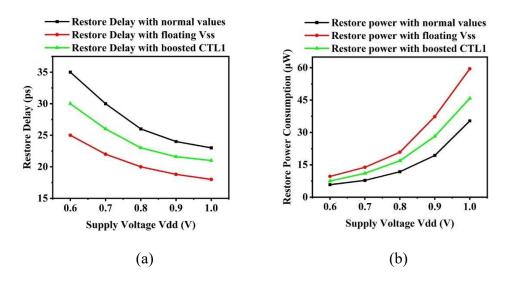

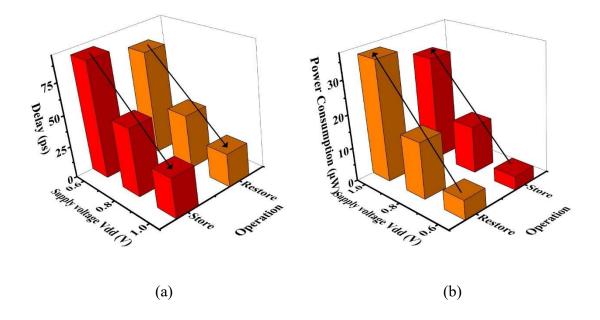

| Fig. 4.6. (a) Store delay and (b) store power consumption of Proposed design 1               |

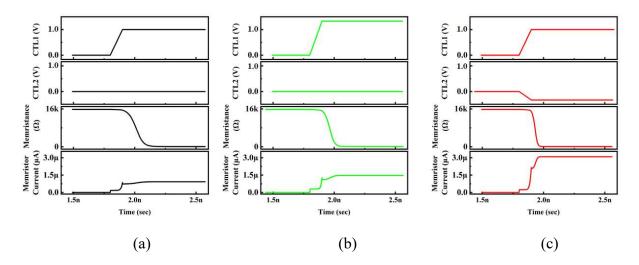

| Fig. 4.7. Timing waveform for restore operation using (a) normal values (b) floating Vss                         |

|------------------------------------------------------------------------------------------------------------------|

| technique and (c) boosted CTL1 technique of Proposed design 1                                                    |

| Fig. 4.8. (a) Restore delay and (b) restore power consumption of Proposed design 1                               |

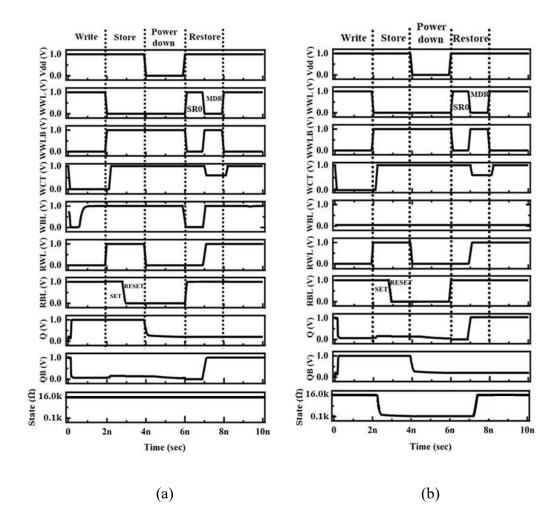

| Fig. 4.9. Schematic of Proposed design 4                                                                         |

| Fig. 4.10. Proposed design 4 during write operation91                                                            |

| Fig. 4.11. Proposed design 4 during read operation92                                                             |

| Fig. 4.12. Proposed design 4 during hold operation92                                                             |

| Fig. 4.13. Timing waveform for non-volatile operation of Proposed design 4 for (a) Logic '1'                     |

| and (b) Logic '096                                                                                               |

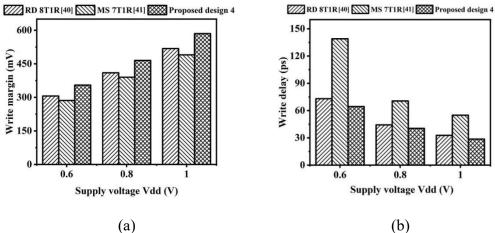

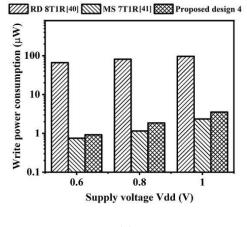

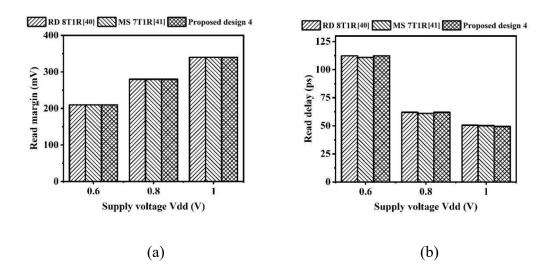

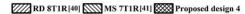

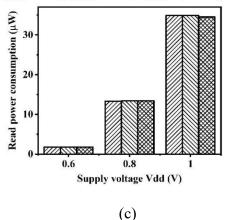

| Fig. 4.14.(a) Write margin (b) write delay and (c) write power consumption of Proposed                           |

| design 4 and considered RD nvSRAM cells at different supply voltage98                                            |

| Fig. 4.15. (a) Read margin (b) read delay and (c) read power consumption of Proposed design                      |

| 4 and considered RD nvSRAM cells                                                                                 |

| Fig. 4.16. Store and restore (a) delay and (b) power consumption of Proposed design 4100                         |

| Fig. 5.1. Schematic of Proposed design 5106                                                                      |

| Fig. 5.2. Proposed design 5 during write '1' operation when memristor M1 is in (a) LRS state                     |

| and (b) HRS state                                                                                                |

|                                                                                                                  |

| Fig. 5.3. Proposed design 5 during read '0' operation when memristor M1 is in (a) LRS state                      |

| Fig. 5.3. Proposed design 5 during read '0' operation when memristor M1 is in (a) LRS state<br>and (b) HRS state |

|                                                                                                                  |

| and (b) HRS state109                                                                                             |

| and (b) HRS state                                                                                                |

| and (b) HRS state                                                                                                |

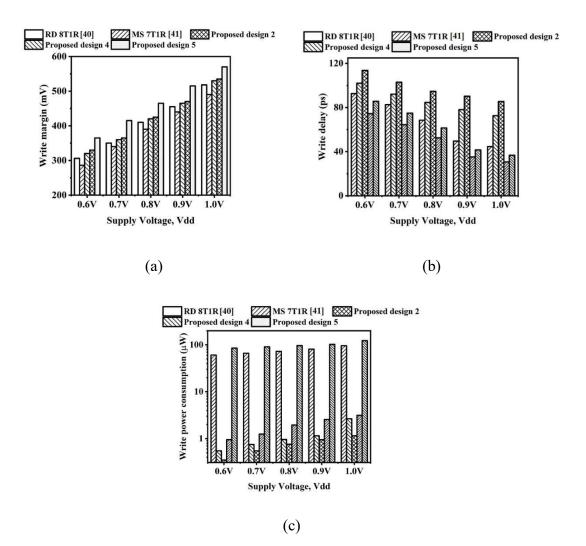

| Fig. 5.7. (a) Write margin (b) write delay and (c) write power consumption of Proposed     |  |

|--------------------------------------------------------------------------------------------|--|

| design 5 and considered RD nvSRAM cells at different supply voltages117                    |  |

| Fig. 5.8. (a) Read margin (b) read delay and (c) read power consumption of Proposed design |  |

| 5 and considered RD nvSRAM cells at different supply voltages                              |  |

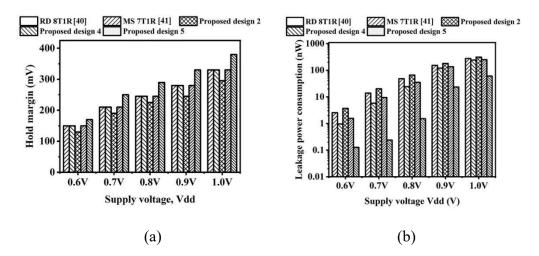

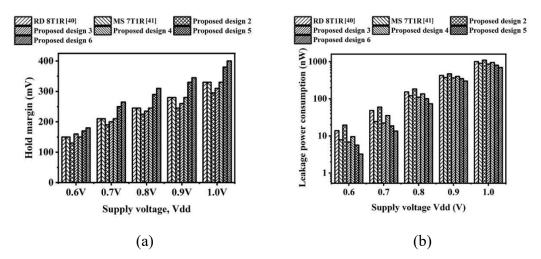

| Fig. 5.9. (a) Hold margin and (b) leakage power consumption of Proposed design 5 and       |  |

| considered RD nvSRAM cells at different supply voltages                                    |  |

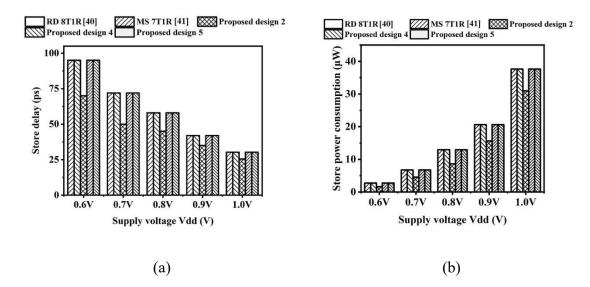

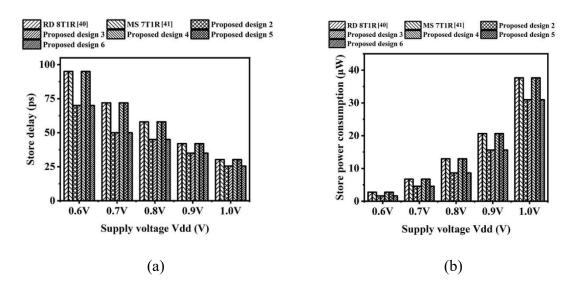

| Fig. 5.10. (a) Store delay and (b) store power consumption of Proposed design 5 and        |  |

| considered RD nvSRAM cells at different supply voltages                                    |  |

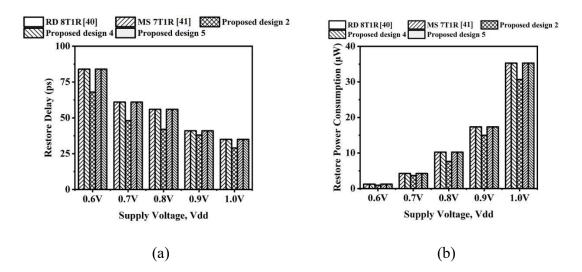

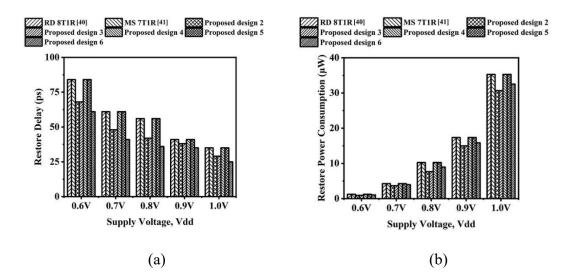

| Fig. 5.11. (a) Restore delay and (b) restore power consumption of Proposed design 5 and    |  |

| considered RD nvSRAM cells at different supply voltages                                    |  |

| Fig. 5.12. Schematic of Proposed design 6124                                               |  |

| Fig. 5.13. Proposed design 6 during write operation                                        |  |

| Fig. 5.14. Proposed design 6 during read operation126                                      |  |

|                                                                                            |  |

| Fig. 5.15. Proposed design 6 during hold operation                                         |  |

| Fig. 5.15. Proposed design 6 during hold operation                                         |  |

|                                                                                            |  |

| Fig. 5.16. Proposed design 6 during (a) store and (b) restore operation129                 |  |

| Fig. 5.16. Proposed design 6 during (a) store and (b) restore operation                    |  |

| Fig. 5.16. Proposed design 6 during (a) store and (b) restore operation                    |  |

| <ul> <li>Fig. 5.16. Proposed design 6 during (a) store and (b) restore operation</li></ul> |  |

| Fig. 5.16. Proposed design 6 during (a) store and (b) restore operation                    |  |

| Fig. 5.16. Proposed design 6 during (a) store and (b) restore operation                    |  |

| Fig. 5.21. (a) Store delay and (b) store power consumption of Proposed design 6 and         |

|---------------------------------------------------------------------------------------------|

| considered RD nvSRAM cells at different supply voltages                                     |

| Fig. 5.22. (a) Restore delay and (b) restore power consumption of Proposed design 6 and     |

| considered RD nvSRAM cells at different supply voltages141                                  |

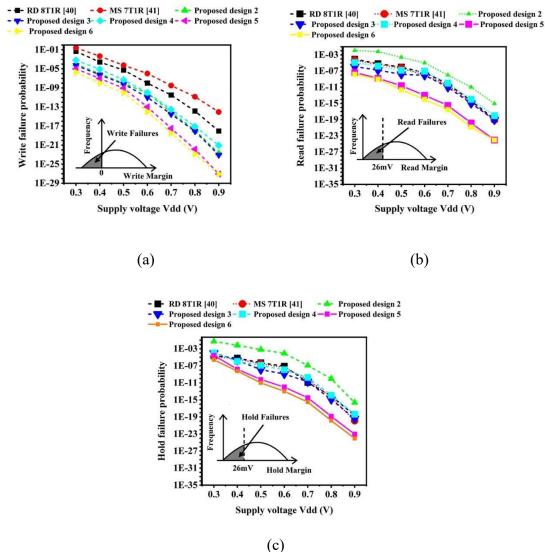

| Fig. 5.23. (a) Write (b) read and (c) hold failure probabilities of Proposed design 6 and   |

| considered RD nvSRAM cells143                                                               |

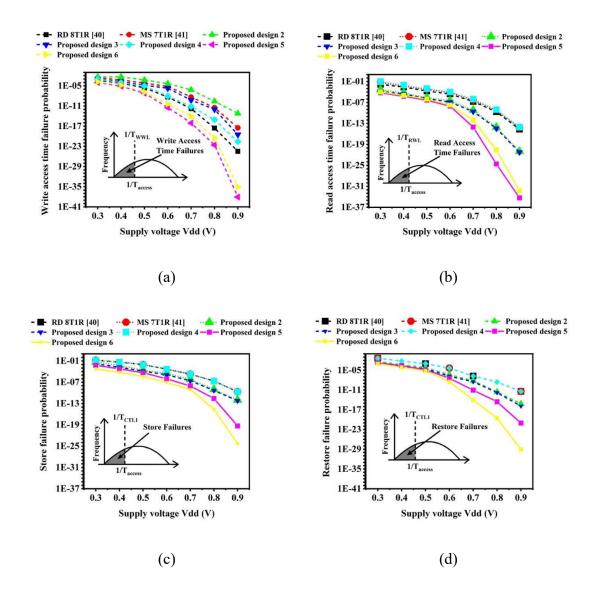

| Fig. 5.24. (a) Write access (b) read access (c) store access and (d) restore access failure |

| probability of Proposed design 6 and considered RD nvSRAM cells146                          |

# LIST OF TABLES

| Table 2.1. Operating Condition of Proposed design 1                                        |

|--------------------------------------------------------------------------------------------|

| Table 2.2. Aspect ratio of various transistors of considered 8T nvSRAM cells and Proposed  |

| design 126                                                                                 |

| Table 2.3. Write power consumption ( $\mu w$ ) of considered 8T nvSRAM cells and Proposed  |

| design 1 at Vdd=1.0V                                                                       |

| Table 2.4. Performance parameters of Proposed design 1 for different design cases at Vdd = |

| 1.0V                                                                                       |

| Table 3.1. Operating Condition of Proposed design 245                                      |

| Table 3.2. Aspect ratio of various transistors of considered RD nvSRAM cells and Proposed  |

| design 2                                                                                   |

| Table 3.3. Write power consumption ( $\mu$ W) of different RD nvSRAM cells and Proposed    |

| design 2 at Vdd = 0.6V                                                                     |

| Table 3.4. Operating Condition of Proposed design 362                                      |

| Table 4.1. Status of control signals during different operations    82                     |

| Table 4.2. Operating Condition of Proposed design 490                                      |

| Table 5.1. Operating condition of Proposed design 5106                                     |

| Table 5.2. Operation condition of Proposed design 6124                                     |

| Table 5.3. Vmin of Proposed design 6 and considered RD nvSRAM cells       147              |

# Chapter 1

# Introduction

Motivation |

#### **1.1. Motivation**

In electronic portable devices, most of the chip area is occupied by static random access memory (SRAM). Thus, it is necessary to design low power SRAM cells to enhance the battery life of portable devices. Tremendous efforts have been devoted in SRAM cell design to address issues related to device [1]–[3], technology [4], [5], and applications [6], [7]. The methods such as power gating [8], [9], clock gating [10], [11] and voltage scaling [12], [13] are widely used to design low power SRAM cells. Among these, voltage scaling is the most popular approach to reduce the power consumption due to its quadratic dependency. Although, this method reduces the power consumption; it degrades device performance at the lower voltages [12], [13].

In SRAM array, the required cell is selected using address decoder, while rest of the unselected SRAM cells remain in idle state. The unselected SRAM cells consume static power in addition to the selected cell [14]. The SRAM cell being volatile in nature retains data as long as it is powered up. Thus, the unselected cells cannot be turned off to save power. This issue can be resolved if non-volatile feature is added in SRAM cells. There are some non-volatile devices available in the literature which have been added in SRAM cell to add non-volatile feature. Due to the intense demand for a high-density, high-speed, and low-power non-volatile memory (NVM) in semiconductor industry, the market of NVM device has grown much faster than the entire semiconductor market in recent years [15]–[17]. There are mainly five types of non-volatile memory technology: Flash memory, ferroelectric random-access memory (FeRAM), magnetic random access memory (MRAM), phase-change memory (PCM), resistive random access memory (RRAM) and memristor [18], [19].

its state before being switched OFF [18], [19]. In FeRAM, the polarization properties of a ferroelectric substance are used as a memory device [18], [19]. MRAM stores the data in magnetic storage element while in PCM, data storage is based on reversible phase conversion between the amorphous and the crystalline state of a glass [18], [19]. In RRAM, the data is stored in the form of resistive state of dielectric material which is sandwiched between conducting plates through a filament or conduction path formed [19]. Memristor follows the same working principle as RRAM. It is formed by sandwiching undoped titanium di-oxide (TiO<sub>2</sub>) and doped oxygen deficient titanium dioxide (TiO<sub>2-X</sub>) layers between platinum (Pt) electrodes [20]–[22]. It is considered as a strong candidate among existing NVM devices due to its compatibility with CMOS technology, high speed and low power consumption [19]. Hence, in this work, memristor based memory cells are worked upon and are commonly reflected as non-volatile SRAM (nvSRAM) cells.

#### **1.2.** Literature review

In literature, several memristor based memory (nvSRAM) cells are available which use either one, two or three memristors to add non-volatile feature in SRAM cell [23]–[45]. In most of the nvSRAM cells, the conventional 6T SRAM cell is used as the core [23]–[41]. A brief discussion on existing nvSRAM cells is given here.

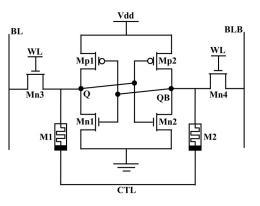

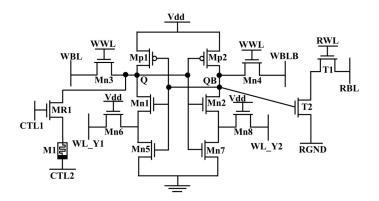

The first nvSRAM cell is 6T2R cell having six transistors and two memristors as shown in Fig. 1.1 [23]. The back-to-back connected inverter pair formed by transistors Mn1-Mp1 and Mn2-Mp2 stores a single bit of data at internal nodes Q and QB. The access transistors Mn3 and Mn4 are controlled by wordline WL. The complimentary bitline pair BL and BLB represents the data during both write and read operation. Memristors controlled by a signal CTL are connected at both the internal nodes to add non-volatile feature. The detailed

operation of 6T2R nvSRAM cell [23] along with the performance metrics are discussed below.

Fig. 1.1. Schematic of 6T2R cell [23]

#### Write operation

A write operation refers to the manner of updating the cell contents with new data. In this operation, the bitline pair is pre-charged to Vdd prior to write operation and the signal CTL is asserted HIGH. For a write '1' operation, BL remains at Vdd, while, BLB is discharged to ground potential (GND). After this, write wordline (WL) is asserted HIGH such that the internal node Q gets charged to Vdd through transistor Mn3. On the other side, the internal node QB is discharged to GND through transistor Mn4. The following design metrics are used to characterize the write performance of the cell.

- Write margin (WM): It is characterized by the write trip point which defines the maximum amount of voltage needed to flip the data of internal node of the cell. The WM is measured as the difference between Vdd and write trip point [46]. In this work, the word line sweep method is used to determine write trip point and WM of the cell [47], [48].

- Write delay: It is defined as the time interval between 50% activation of WL signal and the time when internal node Q reaches 50% of its full swing value [46].

Write power consumption: It is defined as the dynamic power consumed during writing of new contents in the nvSRAM cell.

#### **Read operation**

The read operation refers to manner in which the stored contents are read from the nvSRAM cell. The bitline pair is pre-charged prior to read operation. For a read '1' operation, the signals WL and CTL are asserted HIGH. The bitline BL remains at Vdd while the BLB gets discharged via transistors Mn4 and Mn2. The potential difference in bitline pair is sensed by a sense amplifier. The read '0' operation is also performed in the similar manner. In read operation, the following design metrics of the cell are taken into account.

- *Read margin (RM):* It is determined as the maximum amount of DC noise voltage that can be tolerated by cross coupled inverter pair without state flip or a destructive read. It is measured by fitting the largest square inside the butterfly curve wherein the side length of the square is considered as RM [46].

- Read delay: It is given as the time delay between 50% of WL activation to 10% of precharged voltage difference between the bitline pair [46].

- Read power consumption: It is determined as the power consumed by the nvSRAM cell during read operation.

#### Hold operation

In hold operation, WL is asserted LOW, while, signal CTL is asserted HIGH. The back-toback connected inverter pair maintains the cell data. The hold operation is characterized by the following design metrics.

Hold margin (HM): It is defined as the maximum amount of DC noise voltage that can be tolerated by back-to-back connected inverter pair such that the cell retains its data. The butterfly curve method is used to measure the HM of the cell [46]. The side length of the largest square that can be fitted inside the butterfly curve gives HM value.

Leakage Power Consumption: It is defined as the amount of power consumed when nvSRAM cell is in hold state [46].

#### Non-volatile operation

The non-volatile operation consists of store, power down and restore operations. In store operation, the content at internal nodes Q and QB are stored in memristors M1 and M2, while, in restore operation, the contents are rewritten on the internal nodes after power down. When, a positive potential is applied across memristor, the oxygen deficiencies occupy most of the device thickness. In this position, memristor is said to be in low resistance state (LRS) and it is denoted by R<sub>ON</sub>. If negative voltage is applied across memristor, the amount of oxygen deficiencies is reduced and thickness of undoped region is increased. In this position, memristor is said to be in high resistance state (HRS) and is represented by R<sub>OFF</sub>.

It is assumed that the internal node Q is at logic '1', while internal node QB is at logic '0'. During store operation, the signal CTL is asserted LOW such that a positive potential difference is developed across memristor M1. It helps in changing the state of memristor M1 to LRS, while, memristor M2 continues to remain in HRS state due to zero potential difference across it. The store operation is followed by power down mode. In this mode, the power supply is turned off and the data stored on internal nodes is lost. However, both the memristors maintain their respective states. When the power supply is turned on again, the data is restored at the internal nodes through the restore operation.

In restore mode, CTL is asserted HIGH. As memristors M1 and M2 are in LRS and HRS states, respectively, therefore, the internal node Q gets charged faster than QB. Thus, logic

'1' is restored on internal node Q, whereas internal node QB attains logic '0' due to back-toback connected inverter pair. After completion of restore operation, the memristors are reset to their initial HRS state by raising CTL signal above Vdd. The following design metrics are analysed during non-volatile operation.

- Store delay: It is given as the time required to change the state of memristor from HRS to LRS during store operation.

- Store power consumption: It is represented as the power consumed by the nvSRAM cell while performing store operation.

- Restore delay: The restore delay is given as the time required to recover the data from memristor to internal node of the cell after power down operation.

- Restore power consumption: It is represented at the power consumed by the nvSRAM cell during restore operation.

Further, a close look at Fig. 1.1 shows that a current, however, small may flow through memristors as internal nodes store complimentary data leading to degraded cell stability. Thus, few additional transistors are included in the cell along with memristors to achieve non-volatile feature with improved performance. The nvSRAM cells [24]–[41] work on this methodology.

The 7T2M cell [24] is modified version of 6T2R cell [23] wherein a control transistor is placed between common node of memristor and GND. The write and read performances of 7T2M cell [24] are similar to 6T2R cell [23]. The control transistor is activated during store and restore operations only. During store operation, both the memristors are set to different states due to difference in data available at both the internal nodes. In restore operation, the data is recovered at internal nodes according to respective memristor state. The 7T2M cell

Literature review |

[24] cell aims to increase the stability during write/read operations; however, it has memristor connection same as 6T2R cell [23] and hence, the leakage issue is still there.

The 7T2R cell [25] retains the structure of 6T2R cell [23]. An additional switch transistor (RSW), controlled by signal CTL, is connected between bitline BL and common node of memristors. The RSW transistor provides a parallel path during write operation that improves the WM and write delay in comparison to 6T2R cell [23]. The read operation remains similar to 6T2R cell [23]. During store and restore operations, the RSW transistor remains ON. In store operation, the internal node data is transferred to memristor and its state is changed accordingly, while, in restore operation, the data is rewritten to internal nodes of the cell. The direct connection of memristor with internal nodes of the cell still exists in 7T2R cell [25] and hence, the leakage issue remains unresolved. The Rnv8T2R cell [26] also uses conventional 6T SRAM cell in the core. This cell has two additional transistors each connected between the internal node and corresponding bitline. During write operation, two write paths exist that enhances WM and reduces write delay of the cell. In read operation, the switch transistors are turned off and the cell behaves as 6T2R cell [23]. The absence of direct path between internal nodes and memristors that exists in 7T2R cell [25], reduces the leakage in the cell. In store operation, two subphases namely set and reset are performed to change the memristor state. In restore operation, the original data is recovered in the cell depending on memristor state. Although, the leakage and stability issues are resolved in this cell, the presence of two memristor paths increase the store/restore power consumption. Also, due to two parallel write paths, the write power of the cell is also increased.

The initialization and overwrite (IOW) 7T1R cell [27] introduced an alternate approach to improve cell performance. In this cell, the inverters of latch are operated at different power supply during write operation. The driving capability of the inverter powered by higher

supply voltage than other inverter leads to improvement in WM. The read operation is similar to 6T2R cell [23]. Moreover, the IOW 7T1R cell [27] has a single memristor connected between internal node Q and switch transistor (RSW) which is further connected to switch line (RSL) instead of BL. The store operation takes place in set and reset phases while restore operation need two phases: differential supply initialization (DSI) and pulse overwrite (POW). The IOW 7T1R cell [27] needs to change the state of one memristor only that reduces store/restore power consumption of the cell in comparison to Rnv8T2R cell which requires changing the state of two memristors [26].

The average 7T1R cell [28] further improves WM and reduce restore power consumption in comparison to IOW 7T1R cell [27]. Here, a column shared switch transistor (SN) is used to improve WM of the cell. The SN transistor is turned off during write operation. It reduces pull-down strength and improves WM of the cell. The read operation is similar to 6T2R cell [23]. However, SN transistor is turned on during read operation which reduces RM slightly therefore the cell uses read favoured sizing of transistors. The store operation is similar to IOW 7T1R cell [27]. The restore operation is carried out in two phases namely, circuit self-recovery (CSR) phase and resistance dependent recovery (RDR) phase. As the restore operation is similar to write operation, the presence of SN transistor helps in restore power reduction in comparison to IOW 7T1R cell [27]. Although, the average 7T1R cell [28] improves WM and reduces restore power consumption of the cell, the subphases in store and restore operations increase the cell complexity and, hence, reduces the store/restore operation speed.

In 8T2R cell [29], [30], the combination of memristor and transistor (1T1M structure) is connected to both the internal nodes, while in 8T2R cell [31], the NMOS transistor of 1T1M structure are replaced by PMOS transistors. The write and read operations are similar to 6T2R

Literature review |

cell [23]. In these cells, the memristor needs to reset to their initial state prior to store operation by providing voltage more than Vdd. Although, the complexity during store operation is reduced, the presence of two memristors and voltage needed to reset memristor to their initial state, cause increase in store/restore power consumption. In 7T1R cell [32], the 1T1M structure in connected to internal node Q only. It also needs to reset the memristor to its initial state prior to store operation, however, it does not need voltage more than Vdd. It results in reduction of store/restore power consumption in comparison to 8T2R cell [29]–[31]. Also, it performs write and store operation at the same time, this leads to increment in write/store delay and decrement in WM.

The 7T2M cell [33] uses two memristors wherein one of them improves volatile performance of the cell while the other perform non-volatile operation. The first memristors is placed between pull-down transistors and GND terminal. It is set to HRS state during write operation which reduces the pull-down strength of inverter pair and enhances WM of the cell. The memristor is set to LRS state during read operation and works similar to 6T2R cell [23]. The second memristor is connected to internal node Q through a transistor. Two signals are used to control operation of transistor and memristor, respectively, during store/restore operation. The 7T2M cell [33] also overcomes the issue of complex store/restore operation, however, the cell shows increased store/restore delay. The 8T3R cell [34] is modified form of 7T2M cell [33]. Here, the 1T1M structure is connected at both internal nodes. The store and restore operations are performed through two paths leading to improvement in store/restore delay, however, it increases store/restore power consumption.

The 8T1R cell introduced in [35], maintains the cell stability by performing differential write/read operations similar to 6T2R cell [23]. The control transistors are connected at both the internal nodes of the cell and a memristor is connected in between. During store operation

the control transistors are activated by applying voltage more than Vdd whereas an additional circuit is required for restoring data. The restore circuit provides delay to power supply of both the inverters. Due to this, there is increase in restore delay and power consumption of the cell.

An alternate structure of 8T1R cell is introduced in [36]. It uses 1T1M structure, connected between both the internal nodes Q and QB, to perform non-volatile operation. An additional transistor (gate and drain terminal connected to bitline BL and source terminal connected to internal node Q) is used to store and restore data. The store operation takes place right after write operation. The set and reset phases are required to store data into memristor which necessitates charging/discharging of bitline BL. After store operation, the read operation take place and it is followed by power down mode and restore operation. The data is recovered into cell according to memristor state. The main advantage of this structure is the use of a minimal number of signals (BL, WL and Vdd). The drawback of this structure is related to the store and restore operations complexity, which is executed in two steps.

A modified version of 7T2R [25] is presented in [37] as TG 7T1R which uses transmission gate (TG) in place of access transistors. It improves write performance of the cell as TG provides two parallel write paths. This structure [37] uses a single memristor to support non-volatile operation, therefore, it has better store/restore power consumption than the cells employing two memristors.

Another structure 7T1R cell [38] is introduced in literature that uses single bitline BL to perform write operation. However, in the single ended write operation, the WM of the cell degraded due to asymmetrical structure [46]. It also gives reduced write power consumption. The read operation is performed through a reference resistor and sensing the voltage across it. The store and restore operations are performed in similar manner to 7T2M cell [33].

#### Literature review |

In nvSRAM cells mentioned above, the read/write conflict issue exists as the same port is used to perform read/write operation. In 6T2R cell [23], shown in Fig. 1.1, the pull-down transistor Mn1/Mn2 has to be stronger than access transistor Mn3/Mn4 for successful read operation. For write operation, the access transistor Mn3/Mn4 need to be stronger than pull-up transistor Mp1/Mp2. As the requirement for read and write operations are conflicting in nature, there is a need to analyse the sizing issues separately for read and write assist transistors [46]. Another way is to decouple the read operation by using a separate read port. The nvSRAM cells [39]–[41] has a read decoupled (RD) port to perform read operation. The 9T2R cell [39] is a modified form of Rnv8T2R cell [26]. A RD port having read pass transistor (RPT) controlled by internal node Q with separate read bitline (RBL) is used to read data on internal node. The read decoupled 9T2R cell [39] has high RM. The 9T2R cell [39] reads opposite data and, hence, an additional inverter is required to retrieve original data. The write, store and restore operations remain similar to Rnv8T2R cell [26].

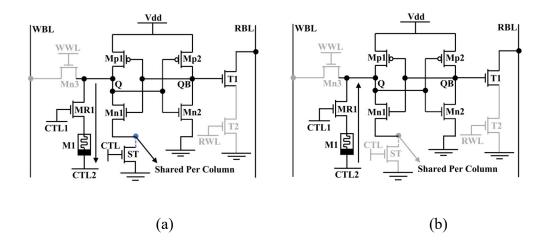

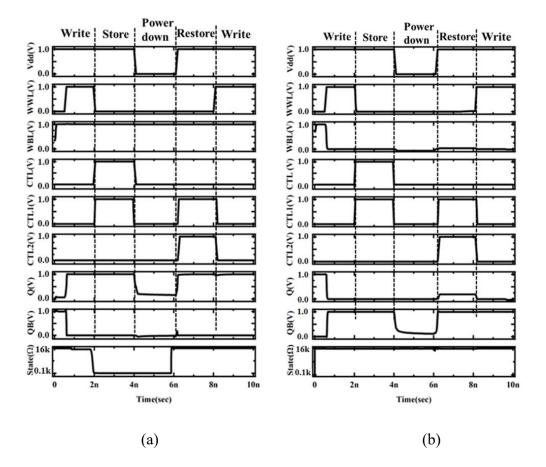

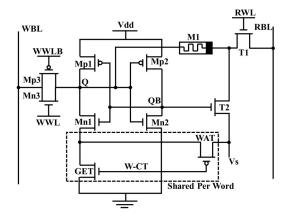

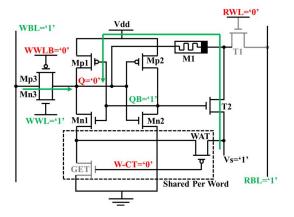

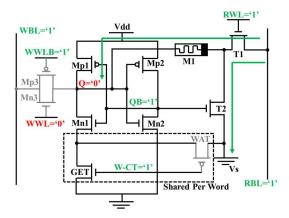

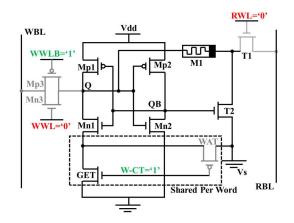

The RD 8T1R cell [40] has a read decoupled port comprised of a read pass transistor (RPT) and a read decision transistor (RDT). The read wordline (RWL) and internal node QB controls operation of RPT and RDT, respectively. The non-volatile operation is achieved by connecting a memristor between internal node Q and RPT. Additionally, this cell uses two function and word sharing transistors: gate enabled transistor (GET) and write assist transistor (WAT) which are controlled by WCT signal. These transistors are used in write and restore operations, assisting write and data recovery process, respectively. The store operation takes place in two subphases: set and reset. The restore operation also requires two subphases, namely: self-recovery '0' (SR) and memristor data recovery (MDR). After restore operation, the opposite data is recovered in the cell, hence, an additional inverter is required

at output stage to get original data. The multiple sharing (MS) 7T1R cell [41] is similar to RD 8T1R cell [40] except write operation. It performs single ended write operation in contrast to differential write operation in [40]. The read, store and restore operations are similar to RD 8T1R cell [40]. In these cells, the read decoupled port enhances the RM, while, the shared per word scheme improves write and restore performances.

The above study reveals that the write delay and WM are improved by using additional transistors, differential power supply rails, column shared transistor, memristor between pulldown transistors and GND terminal of inverter pair and using TG in place of access transistors. It is also observed that the read decoupled port and shared per word scheme can be used to improve read and WM of the nvSRAM cell, respectively. Limited investigations are done on improving write delay of the cells. Further, there is no specific technique for reducing store/restore delay. In small geometry devices, the inter die and intra die process variations limit the memory cell operations especially near threshold region. It may result in threshold mismatch between adjacent transistors in memory cell which may lead to memory failure. This aspect in context of nvSRAM cell design is not looked into.

#### **1.3.** Research gaps

Based on study of literature on memristor based memories, following research gaps are identified:

- The researchers have concentrated toward improving the WM and write delay of nvSRAM cell. The efforts to reduce write power are limited. Therefore, there is a need to design a novel nvSRAM cell with reduced write power consumption.

- 2. Most of the existing nvSRAM cells perform write and read operation through a common port wherein read/write conflict exist that degrade the overall performance.

So, novel read decoupled nvSRAM cells wherein different techniques to enhance read and write performances are required.

- 3. The main thrust in nvSRAM cells is to enhance read stability and write ability, however, the delay performance of the cell remains bottleneck.

- 4. There is an impact of technology scaling and process variations on the performance of nvSRAM cell. Hence, it is necessary to introduce process invariant nvSRAM cells.

#### **1.4. Research objectives**

Based on the gaps the following objectives are formulated:

- 1. To design memristor based memory with improved write performance.

- 2. To design memristor based memory with improved read margin.

- 3. To improve delay performance of memristor based memory.

- 4. To design process invariant memristor based memory cell.

#### **1.5.** Organization of the thesis

The focus of this research is on nvSRAM cells and improvement in its performance. The organisation of this research work is presented in chapter-wise format as follows:

#### **Chapter 1**

This chapter outlines the issues of SRAM cell in portable devices. The introduction of nonvolatile memory (NVM) devices with SRAM cell has emerged as one of the possible solutions to these issues. The working of a nvSRAM cell and its performance parameters are briefly described. The available nvSRAM cells are reviewed followed by identification of research gaps and laying down of research objectives.

#### Chapter 2

In this chapter, a novel low power 8T1M nvSRAM cell (Proposed design 1) is introduced. The detailed explanation on working of the Proposed design 1 is put forward and its operation is verified through timing waveforms. The write performance, read performance, store and restore performances of the Proposed design 1 are compared with its 8T nvSRAM counterparts. The leakage power analysis for Proposed design 1 is also studied and three different cases are introduced to reduce it. The supply voltage variation study is also carried out for the sake of completeness.

#### Chapter 3

This chapter presents two nvSRAM cells with read decoupled port (Proposed design 2 and 3) to improve read performance. The techniques to improve WM are also applied to the Proposed designs. The Proposed design 2 aims to improve its performance near threshold voltage. In Proposed design 3, the column shared technique is used to improve the cell performance. The performances such as write, read, store and restore are verified through simulations and the results are compared with considered read decoupled nvSRAM cells. The supply voltage variation study is also carried out for each performance parameters.

#### Chapter 4

This chapter uses transmission gate as access transistor in read decoupled nvSRAM cell (Proposed design 4) to improve write delay. The write, read, store and restore performances are studied for the Proposed design and the results are compared with considered nvSRAM cells. Further, three techniques namely boosted CTL1, negative CTL2 and floating Vss are introduced to reduce store and restore delays. These techniques are applied on the Proposed design 1 and a comparison is made to evaluate the effect of each introduced technique on

store and restore delays. The supply voltage variation study is also carried out for each performance parameter.

#### Chapter 5

This chapter put forward two process invariant nvSRAM cells (Proposed design 5 and 6) which use read decoupled port. Both Proposed designs use Schmitt trigger inverter as core which helps in maintaining performance against process variation. The performance of the Proposed designs is verified and is compared against available RD nvSRAM cells, Proposed design 2, Proposed design 3 and Proposed design 4. The impact of process variation on cell performance is examined. The failure probability analysis is carried out to check the stability of the cells under process variations. Further, the leakage power analysis is also carried out for the sake of completeness.

#### Chapter 6

This chapter summarizes the work presented in the thesis. It also gives the idea for the future work which can be carried out to improve nvSRAM cell functionality.

# Chapter 2

# nvSRAM Cell with Improved Write Performance

The contents of this chapter are published in:

[1] D. Singh, K. Gupta, and N. Pandey, "A Novel Low-Power Nonvolatile 8T1M SRAM Cell," Arabian Journal for Science and Engineering, vol. 47, no. 3, pp. 3163–3179, 2022, doi: 10.1007/s13369-021-06035-2. (SCIE indexing, IF 2.807)

Introduction |

#### 2.1. Introduction

In battery operated portable devices, most of the power is consumed during memory access that have significant impact on battery life [49]. In these portable devices, SRAM cell occupies major chip area and consumes significant amount of active power and leakage power. The reduction in leakage power can be achieved by addition of memristor with SRAM cell that leads to introduction of nvSRAM cell [39]. It enables a portable device to switch off its power supply to suppress leakage power without a loss of data. The active power can be effectively reduced in two manners: (1) by lowering the supply voltage as it is quadratically dependent on total power consumption and (2) by lowering charging/discharging of capacitance of word and bitline [49] as upto 60% of total active power is consumed in charging/discharging of bitlines during write operation [50], [51].

In this chapter, eight transistors based nvSRAM cell (Proposed design 1) is introduced which performs single ended write operation and differential read operation. For this, a feedback transistor is introduced in feedback path of back-to-back connected inverter pair. This feedback transistor remains off during write operation and remains on otherwise. To perform non-volatile, a combination of a transistor and a memristor (1T1M) is used. A brief discussion on existing 8T nvSRAM cells is presented in section 2.2. Thereafter, the working of Proposed design 1 during write, read, hold, store and restore operations is elucidated in section 2.3. This section also includes the timing waveform of Proposed design 1 during non-volatile operation. The performance parameters of Proposed design 1 are also analysed and compared with the considered 8T nvSRAM cells during different operations. Different design cases to reduce leakage power consumption of Proposed design 1 are also introduced. The findings are comprehended in section 2.4.

#### 2.2. Existing 8T nvSRAM cells

In this section, a brief review on 8T nvSRAM cell is carried out. The core of these cells is similar and comprise of back-to-back connected inverter pair to store single bit of data. The access transistors perform differential write and read operations. The difference resides in non-volatile functionality of the cells.

The available 8T nvSRAM cells resolve leakage issue of 6T2R cell [23] by adding a control transistor that eliminates the current path through memristor. The 8T2R cell [29], Rnv8T2R cell [26], 8T1R cell [35] and 8T1R cell [36] uses 1T1M structure at the internal nodes to perform non-volatile operation. The nvSRAM cells [29], [35] perform write operation through access transistors whereas, an additional path for write operation is formed through memristor in the nvSRAM cells reported in [26], [36].

Further, in Rnv8T2R cell [26], 8T1R cell [35] and 8T1R cell [36], the set and reset phases are required to perform store operation. It needs supply voltage and control signal value  $V_{SET}$ which is set voltage of memristor. Although, the 8T2R cell [29] does not need set/reset phase, it needs control signal value more than Vdd to perform store operation. The restore operation of 8T1R cell [35] requires a restore circuitry for the delayed activation of the supply voltage of inverters. In 8T1R cell [36], the restore operation is performed in two phases which are quite complex. Moreover, in nvSRAM cells [29], [36], memristor needs to initialize to its initial HRS state by performing reset operation.

From above discussion, it is observed that in 8T2R cell [29], the supply voltage more than Vdd is required to perform both store and restore operations. Also, an additional reset phase is required to initialize memristor to HRS state prior to store operation. In Rnv8T2R cell [26] and 8T1R cells [35], [36], the set and reset phases are required during store operation. Hence,

due to need of high supply voltage and multiple phases during store and restore operations, the store and restore power consumptions and complexity is increased.

Also, in most of the existing 8T nvSRAM cells [23], [26], [29], [35], [36] differential write operation is performed. The probability of discharging one of the bit line pair equals '1' which means that the activity factor of switching the bit line pair equals '1'. The bitline power consumption is given as  $P = \alpha_{WBL} * C_{BL} * V_{dd}^2 * f_{write}$  where  $\alpha_{WBL} = 1$ . The use of single bitline to perform write operation can reduce the switching activity factor  $\alpha_{WBL}$  to '0.5' which effectively reduces the active power consumption [52]. It also exploits the fact that most of the bits in SRAM are "zeros" for both data and instruction memories to reduce the write power consumption [53], [54]. Hence, it is required to introduce nvSRAM cell that exhibit simple store and restore operations and has reduced write power consumption.

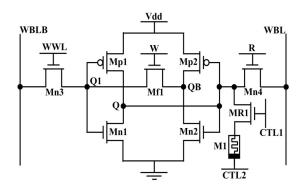

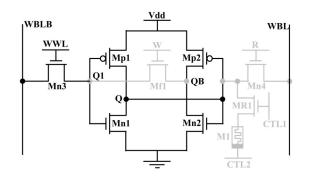

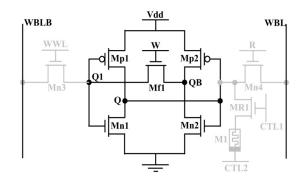

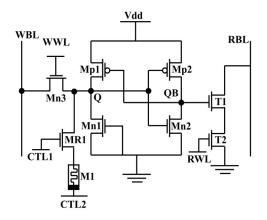

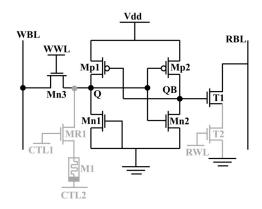

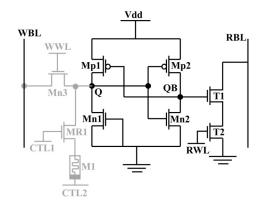

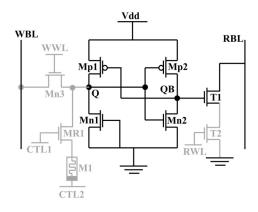

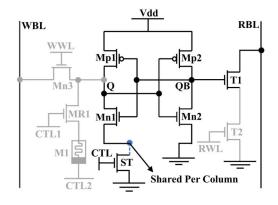

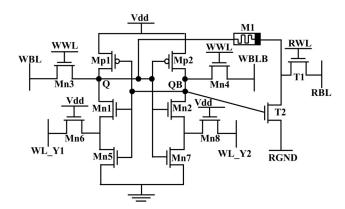

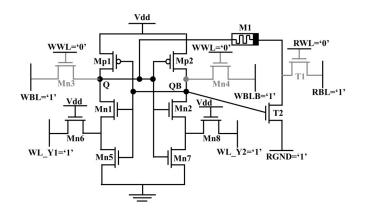

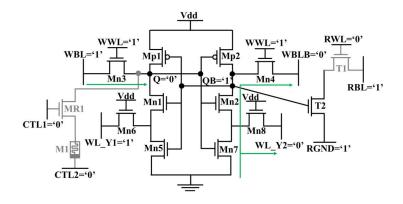

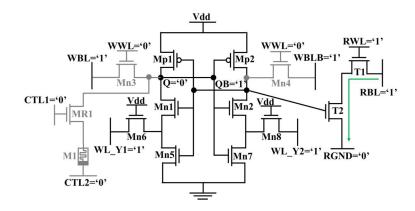

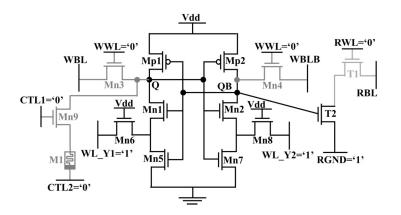

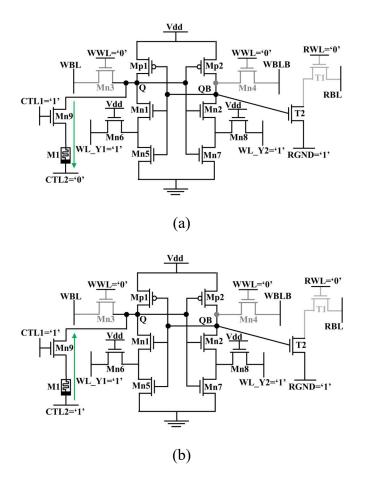

### 2.3. Proposed design 1

The Proposed design 1 is an eight transistor with one memristor nvSRAM cell as shown in Fig. 2.1. It exhibits single ended write and differential read operations through its bitline pair (WBL and WBLB). It consists of back-to-back inverters (Mn1-Mp1 and Mn2-Mp2), connected through a feedback transistor, to store the data on internal nodes Q and QB. The transistors Mn3 and Mn4 are the access transistors controlled by write wordline (WWL) and read signal (R), respectively. A feedback transistor Mf1, controlled by write signal (W), is introduced to exhibit single ended write operation by disconnecting the feedback connection between inverters. Thus, there exist a sequential storage of data on two internal nodes, thereby lowering the write power consumption of Proposed design 1. Alternatively, transistor Mf1 turned on during the read operation to retain the advantage of fast differential read as

# **Chapter 2: nvSRAM Cell with Improved Write Performance**

exhibited in considered 8T nvSRAM cells. The control signals CTL1 and CTL2 monitor the operation of 1T1M non-volatile structure.

Fig. 2.1. Schematic of Proposed design 1

# 2.3.1. Operation of Proposed design 1

In this subsection, the operation of Proposed design 1 is described during write, read, hold, store and restore operations. The status of control signals during each operation is summarized in Table 2.1.

| Signals | Operations                    |      |      |      |      |  |

|---------|-------------------------------|------|------|------|------|--|

|         | Write Read Hold Store Restore |      |      |      |      |  |

| WWL     | HIGH                          | HIGH | LOW  | LOW  | LOW  |  |

| R       | LOW                           | HIGH | LOW  | LOW  | LOW  |  |

| W       | LOW                           | HIGH | HIGH | HIGH | HIGH |  |

| CTL1    | LOW                           | LOW  | LOW  | HIGH | HIGH |  |

| CTL2    | LOW                           | LOW  | LOW  | LOW  | HIGH |  |

Table 2.1. Operating Condition of Proposed design 1

# Write operation

In a write operation, the two bitlines WBL and WBLB are pre-charged to Vdd prior to writing new data values in the Proposed design 1. The control signals are asserted as mentioned in Table 2.1. The resulting structure represents cascade of two inverters as shown in Fig. 2.2. The new data loaded on the WBLB line gets stored at node Q1 through transistor Mn3, which is then updated sequentially at internal nodes Q and QB through the two inverters (Mn1-Mp1, Mn2-Mp2).

During a write '0' operation, WBLB remains at Vdd (logic 1) and the cascade of two inverters stores logic '0' and logic '1' at nodes Q and QB sequentially. Thus, it can be noted here that the Proposed design 1 eliminates the need of discharging of WBL bitline in contrast to considered 8T nvSRAM cells. This reduces the activity factor  $\alpha_{WBL}$  of the bitlines and reduces write power of the Proposed design 1 in a write '0' operation. Alternatively, in write '1' event, the WBLB line discharges, in such cases Proposed design 1 consumes the same power as the considered 8T nvSRAM cells.

Fig. 2.2. Proposed design 1 during write operation

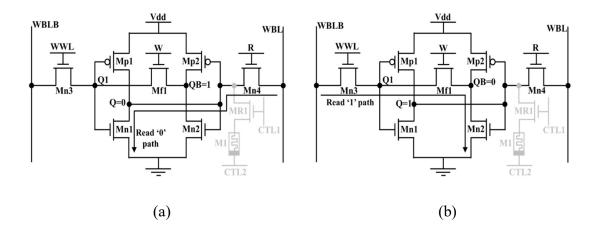

### **Read operation**

The Proposed design 1 exhibits differential read operation. The bitlines WBL and WBLB are pre-charged to Vdd prior to read operation. The control signals are asserted as enlisted in Table 2.1. Depending on the value stored at internal nodes, a discharge path is formed through either of the two bitlines, as illustrated in Fig. 2.3. For a read '0', WBL discharges through Mn4 and Mn1 as depicted in Fig. 2.3(a). Alternatively, in a read '1' event, WBLB

### **Chapter 2: nvSRAM Cell with Improved Write Performance**

discharges through a path consisting of three transistors Mn3, Mf1 and Mn2 as represented in Fig. 2.3(b). The difference in number of transistors in discharging requires optimum sizing of transistors.

Fig. 2.3. Proposed design 1 during (a) read '0' and (b) read '1' operation

### **Hold operation**

The control signals are asserted as tabulated in Table 2.1 during hold operation. The access transistors remain off in this operation. The data is stored in the Proposed design 1 by back-to-back connected inverter pair as feedback transistor Mf1 is working as shown in Fig. 2.4.

Fig. 2.4. Proposed design 1 during hold operation

### Non-volatile operation

The non-volatile operation of Proposed design 1 comprises of store, power down and restore operations. It is performed after write (logic '1' or logic '0') operation. It is performed to

mention that the initial state of memristor M1 is HRS irrespective of the internal node content.

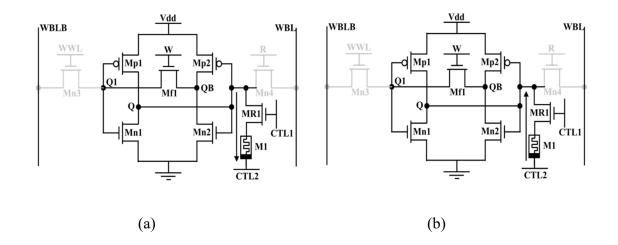

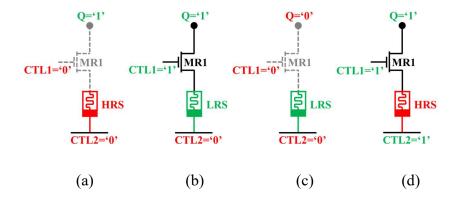

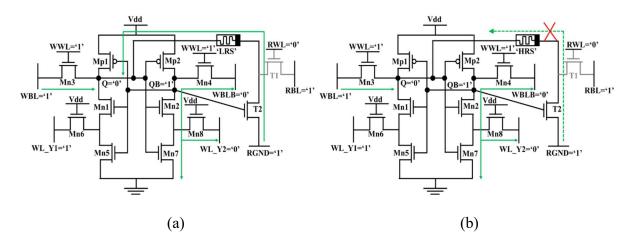

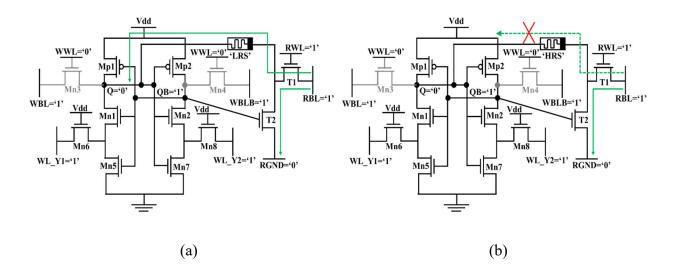

In store operation, the signals (CTL1, W) and CTL2 are asserted HIGH and LOW, respectively. The schematic for Proposed design 1 during store operation is shown in Fig. 2.5(a). Assuming the logic '1' is stored on internal node Q, the memristor states are depicted in Fig. 2.6. In this case, the internal node Q stores logic '1', the memristor M1 changes its state from HRS to LRS as there is a negative potential across the it. During power down, the supply voltage is turned off and all the control signals are asserted LOW. Due to this, the internal nodes Q and QB lose their data while the memristor M1 maintains its LRS state. In restore operation, the supply voltage is turned on again. The control signals W, CTL1 and CTL2 are asserted HIGH while other control signals remain LOW. The schematic of Proposed design 1 during restore operation is depicted in Fig. 2.5(b). As memristor M1 is in LRS state, there is a large flow of current through transistor MR1 and the internal node Q is restored to logic '1'. The memristor M1 changes its state from LRS to HRS, which is also its initial state.

Fig. 2.5. Proposed design 1 during (a) store and (b) restore operation

Fig. 2.6. State of memristor during non-volatile operation (a) initial (b) store (c) power down and (d) restore for logic '1'

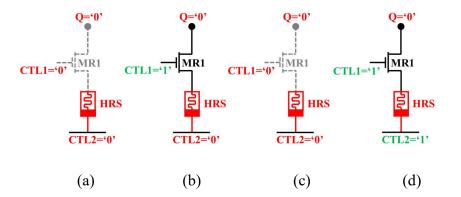

Similarly, the states of memristor during the non-volatile operation for logic '0' is shown in Fig. 2.7. As the internal node Q is at logic '0', there is zero potential difference across memristor M1 and, hence, it does not change its state during store operation and remain in HRS. After, the store operation, power down occurs and internal node data is lost. After power down, the restore operation is carried out. As memristor M1 is in HRS state, a low current flow through it which is not sufficient to raise the potential of internal node Q and it remains at logic '0'. It can be observed that memristor M1 remains in HRS after restore operation. Thus, the Proposed design 1 does not require resetting of memristor after restore which is necessary in the considered 8T nvSRAM cells.

Fig. 2.7. State of memristor during non-volatile operation (a) initial (b) store (c) power down and (d) restore for logic '0'

# 2.3.2. Simulation results and discussion

The SPICE simulations are carried out using 32nm PTM model to analyse the performance of Proposed design 1. The memristor model suggested in [55] is used to analyse the non-volatile performance. The Proposed design 1 and considered 8T nvSRAM cells are designed for same RM and the corresponding aspect ratio of various transistors are enlisted in Table 2.2. In this section, first the timing waveform of Proposed design 1 is explained at Vdd = 1.0V. It is followed by the performance evaluation during different operations and its comparison with the considered 8T nvSRAM cells.

Table 2.2. Aspect ratio of various transistors of considered 8T nvSRAM cells and Proposed

| Transistor  | Aspect ratio (W/L) |                     |            |            |                   |  |  |

|-------------|--------------------|---------------------|------------|------------|-------------------|--|--|

| 11 ansistor | <b>8T2R</b> [29]   | <b>Rnv8T2R</b> [26] | 8T1R [35]  | 8T1R [36]  | Proposed design 1 |  |  |

| Mn1         | 256nm/32nm         | 256nm/32nm          | 256nm/32nm | 256nm/32nm | 166.4nm/32nm      |  |  |

| Mn2         | 256nm/32nm         | 256nm/32nm          | 256nm/32nm | 256nm/32nm | 211.2nm/32nm      |  |  |

| Mn3         | 128nm/32nm         | 128nm/32nm          | 128nm/32nm | 128nm/32nm | 83.2nm/32nm       |  |  |

| Mn4         | 128nm/32nm         | 128nm/32nm          | 128nm/32nm | 128nm/32nm | 64nm/32nm         |  |  |

| Mp1         | 64nm/32nm          | 64nm/32nm           | 64nm/32nm  | 64nm/32nm  | 64nm/32nm         |  |  |

| Mp2         | 64nm/32nm          | 64nm/32nm           | 64nm/32nm  | 64nm/32nm  | 128nm/32nm        |  |  |

| Mfl         | -                  | -                   | -          | -          | 256nm/32nm        |  |  |

| MR1         | 64nm/32nm          | 64nm/32nm           | 128nm/32nm | 64nm/32nm  | 64nm/32nm         |  |  |

| MR2         | 64nm/32nm          | 64nm/32nm           | 128nm/32nm | 64nm/32nm  | -                 |  |  |

| 1 •     | 1 |

|---------|---|

| design  |   |

| 4001B11 | - |

# **Timing waveform**

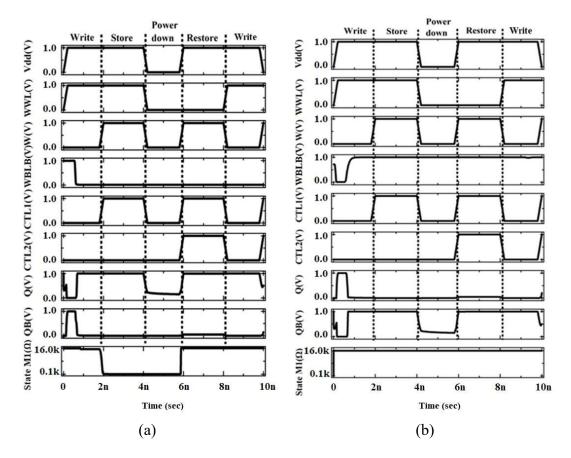

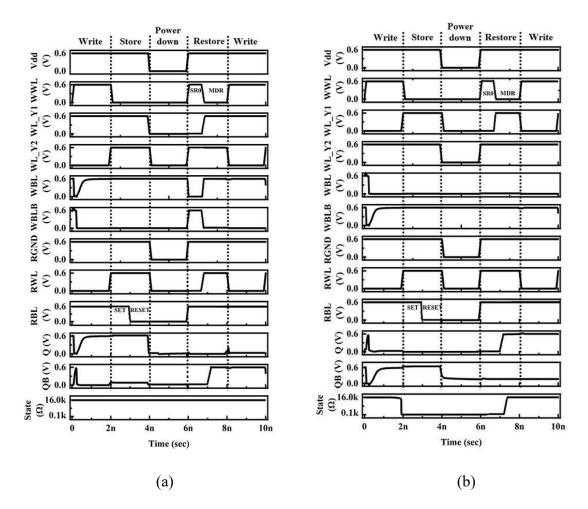

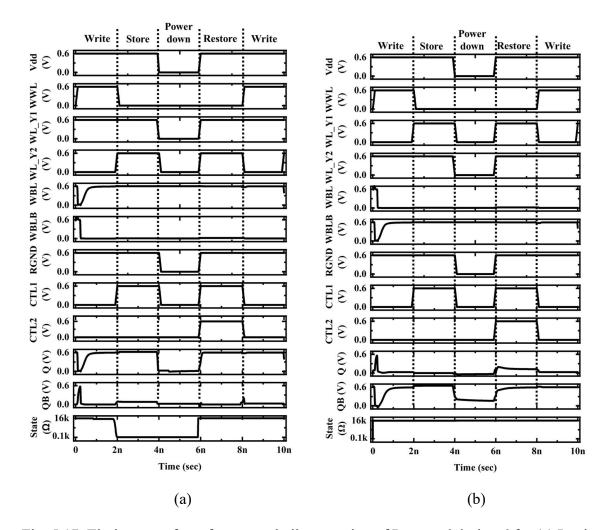

The timing waveform for the complete execution of store, power down and restore logic '1' in the Proposed design 1 is shown in Fig. 2.8(a). The time period for each operation is taken as 2ns [56]. The following observation can be made:

- a) The write '1' operation is performed during 0 to 2ns. The WBLB is discharged to ground and the signal WWL is asserted HIGH. The control signal W, CTL1 and CTL2 are asserted LOW. As shown in Fig. 2.8(a), the internal nodes Q and QB are written as logic '1' and logic '0', respectively.

- b) From 2ns to 4ns, the store operation takes place. The control signals (W and CTL1) and CTL2 are asserted HIGH and LOW, respectively such that the transistor MR1 turns on. Since internal node Q is at logic '1' and CTL2 is at ground potential, the memristor M1 changes its state from HRS to LRS.

- c) From 4ns to 6ns, the supply voltage is turned off and the control signals are asserted LOW. It can be observed that the internal node Q discharges but the memristor M1 retains its LRS state.

- d) Finally, from 6ns to 8ns, in the restore operation, the supply voltage is turned on and signals W, CTL1 and CTL2 are asserted HIGH. The internal node Q is charged back to Vdd i.e., logic '1'. It is due to the large flow of current through transistor MR1. After restore operation, the memristor M1 changes its state back to HRS which is its initial state.

Similarly, Fig. 2.8(b) shows the complete execution for store, power down and restore logic '0' in Proposed design 1. First, the write '0' operation takes place by keeping WBLB at Vdd. In store operation, as internal node Q is at logic '0', memristor M1 continues to remain in the HRS state due to zero potential difference across it. During power down, the supply voltage is turned off. The internal nodes lose their data, however, memristor M1 retain its HRS state. Subsequently, in the restore operation, internal node Q does not get charged as memristor is in HRS state but internal node QB attains logic '1' due to the back-to-back connection of inverters in the Proposed design 1. It is worth noting that after the restore operation, the memristor is in HRS.

# **Performance analysis**

Various performance parameters such as margin, delay and power consumption are evaluated for Proposed design 1 during different operations. The results are compared with considered 8T nvSRAM cells. The effect of supply voltage variation is also studied for completeness.

Fig. 2.8. Timing waveform for non-volatile operation of Proposed design 1 for (a) Logic '1'

and (b) Logic '0'

Write Performance Analysis

The write performance of the Proposed design 1 is analysed in terms of WM, write delay and write power consumption. The results are also compared with the considered 8T nvSRAM cells.

### **Chapter 2: nvSRAM Cell with Improved Write Performance**

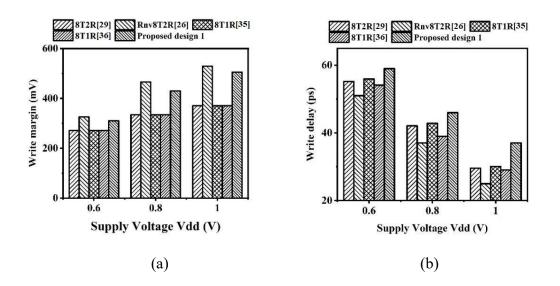

*Write margin (WM):* The WM for considered 8T nvSRAM cells and Proposed design 1 is analysed at Vdd = 1.0V. The value of WM is observed as 371mV, 529mV, 371mV, 371mV and 505mV for 8T2R cell [29], Rnv8T2R cell [26], 8T1R cell [35], 8T1R cell [36] and Proposed design 1, respectively. The improvement of 26.53% is observed in the WM of Proposed design 1 in comparison to 8T2R [29], 8T1R [35] and 8T1R [36] cells. The improvement in WM of Proposed design 1 may be attributed to the writing mechanism that disconnects that feedback connection of inverter pair and eases writing into the cell. The WM of Proposed design 1 is smaller than Rnv8T2R cell [26] by 4.53% which is due to presence of extra parallel write path in the later one.

*Write delay:* The write delay for considered 8T nvSRAM cell and Proposed design 1 is analysed at Vdd = 1.0V. The values are obtained as 29.56ps, 27ps, 30.05ps, 29.05ps and 35ps for 8T2R cell [29], Rnv8T2R cell [26], 8T1R cell [35], 8T1R cell [36] and Proposed design 1, respectively. It is noted that the write delay of Proposed design 1 is increased by 15.54%, 22.85%, 14.14% and 17% in comparison to 8T2R cell [29], Rnv8T2R cell [36], 8T1R cell [36], respectively. It is attributed to the fact that the new data is written on internal nodes of the Proposed design 1 through a cascade connection of inverters in contrast to the back-to-back connection of inverters as in the considered 8T nvSRAM cells.

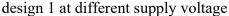

*Write power consumption:* The write power consumption of Proposed design 1 and considered 8T nvSRAM cells is evaluated for different write patterns i.e., 0 - 0, 1 - 0, 0 - 1 and 1 - 1 at Vdd = 1.0V. The observations are summarized in Table 2.3 and the following points are noted:

• The write power consumption of considered 8T nvSRAM cells remain almost same for all write patterns whereas the Proposed design 1 shows very low write

power consumption for 0 - 0 and 1 - 0 write patterns. This is due to the differential write operation in considered 8T nvSRAM cells against single ended write operation in Proposed design 1.

- The Proposed design 1 shows 99.5% and 96.03% power saving for write '0' with respect to considered 8T nvSRAM cells when the original cell data is '0' and '1', respectively. This is attributed to the fact that write '0' operation in Proposed design 1 does not require WBLB to discharge as exhibited in its counterparts.

- The write patterns 0 1 consumes more power than write pattern 1 1 for Proposed design 1 and considered 8T nvSRAM cells.

Table 2.3. Write power consumption ( $\mu w$ ) of considered 8T nvSRAM cells and Proposed design 1 at Vdd=1.0V

|                   | Write power consumption (µW) for different write patterns |        |        |        |  |  |

|-------------------|-----------------------------------------------------------|--------|--------|--------|--|--|

| nvSRAM cells      | 0 - 0                                                     | 1 - 0  | 0 - 1  | 1 - 1  |  |  |

| 8T2R [29]         | 98.83                                                     | 101.11 | 100.98 | 98.85  |  |  |

| Rnv8T2R cell [26] | 104.81                                                    | 109.78 | 110.88 | 104.45 |  |  |

| 8T1R [35]         | 98.51                                                     | 101.35 | 100.65 | 98.86  |  |  |

| 8T1R [36]         | 99.85                                                     | 102.01 | 101.56 | 99.15  |  |  |

| Proposed design 1 | 0.48                                                      | 4.35   | 102.31 | 99.73  |  |  |

The supply voltage variation study of write performance parameters is also carried out for the sake of completeness. The findings for WM and write delay are depicted in Fig. 2.9,

# Chapter 2: nvSRAM Cell with Improved Write Performance

whereas, the observations for write power consumption are shown in Fig. 2.10. With decrease in supply voltage, it may be noted that WM and write power consumption shows downward trend for all considered nvSRAM cells and Proposed design 1. For the write delay, however, all nvSRAM cells show an increasing trend with lowering supply voltage.

Fig. 2.9. Write margin and write delay of considered 8T nvSRAM cells and Proposed

Fig. 2.10. Write power consumption of considered 8T nvSRAM cells and Proposed design 1 with different write patterns (a) 0-0 (b) 1-0 (c) 0-1 and (d) 1-1 at different supply voltage

# Read Performance Analysis

The read delay and read power consumption are evaluated for Proposed design 1 during read operation. The results are also compared with considered 8T nvSRAM cells.

*Read delay:* The read delay of considered 8T nvSRAM cells and Proposed design 1 is analysed at Vdd = 1.0V. The values for read delays are observed as 39ps, 39ps, 39.6ps, 39.6ps and 47ps for 8T2R cell [29], Rnv8T2R cell [26], 8T1R cell [35], 8T1R cell [36] and Proposed design 1, respectively. The Proposed design 1 shows an increment of 17.02% in read delay in comparison to considered nvSRAM cells. This increase in read delay is due to the stack of three transistor formed during the read '1'operation as illustrated in Fig. 2.3(b). The considered 8T nvSRAM cells show comparable read delay values as their read operation is similar.

*Read power consumption:* The read power consumption of considered 8T nvSRAM cells and Proposed design 1 is analysed at Vdd = 1.0V. The values are found as

### **Chapter 2: nvSRAM Cell with Improved Write Performance**