ANALYTICAL MODELLING AND NUMERICAL SIMULATION OF PLASMA-ASSISTED GATE ALL AROUND CARBON NANOTUBE FIELD EFFECT TRANSISTOR

THESIS SUBMITTED TO

DELHI TECHNOLOGICAL UNIVERSITY FOR THE AWARD OF THE DEGREE OF

## **DOCTOR OF PHILOSOPHY**

By

Ms. MANSHA KANSAL (2K19/PHD/AP/508)

Under the supervision of

**PROF. SURESH C. SHARMA**

DEPARTMENT OF APPLIED PHYSICS DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042 (INDIA)

## **JUNE 2023**

© Delhi Technological University (DTU), 2023

# Dedicated to my loving family

DELHI TECHNOLOGICAL UNIVERSITY (Govt. of National Capital Territory of Delhi) Shahbad Daulatpur, Bawana Road, Delhi-110042

## CERTIFICATE

This is to certify that the thesis entitled "Analytical Modelling And Numerical Simulation of Plasma-Assisted Gate All Around Carbon Nanotube Field Effect Transistor" submitted by *Ms. Mansha Kansal* (2K19/PhD/AP/508) to Delhi Technological University (DTU), Delhi, India for the degree of Doctor of Philosophy, is a bonafide record of the research work carried out by her under my supervision and guidance. The work embodied in this thesis has been carried out in the Plasma & Nano-Simulation Lab, Department of Applied Physics, Delhi Technological University (DTU), Delhi, India. The work of this thesis is original and has not been submitted in parts or fully to any other Institute or University for the award of any other degree or diploma.

Prof. Suresh C. Sharma, Supervisor Department of Applied Physics, Delhi Technological University, Delhi-110042, India

Prof. A.S. Rao,

Head of the Department, Department of Applied Physics, Delhi Technological University, Delhi-110042, India

DELHI TECHNOLOGICAL UNIVERSITY (Govt. of National Capital Territory of Delhi) Shahbad Daulatpur, Bawana Road, Delhi-110042

## DECLARATION

I, Ms. Mansha Kansal, hereby certify that the thesis titled "Analytical Modelling and Numerical Simulation of Plasma-Assisted Gate All Around Carbon Nanotube Field Effect Transistor" submitted in the fulfilment of the requirements for the award of the degree of Doctor of Philosophy is an authentic record of my research work carried out under the supervision of *Prof. Suresh C. Sharma*. This work in the same form or any other form has not been submitted by me or anyone else earlier for any purpose. Any material borrowed or referred to is duly acknowledged.

Haushe 30.06.2023

Mansha Kansal (2K19/PhD/AP/508) Department of Applied Physics, Delhi Technological University, Delhi – 110042, India

## ACKNOWLEDGEMENT

Above all, I express my genuine thanks to the almighty for giving me immense strength and patience to work hard all these years.

I express my heartfelt gratitude to my grandparents, **Mr. Madan Gopal Kansal, Mrs. Rani Kansal, and Late Mr. Surender Kumar Jain**. My grandfather himself being from the Physics background always used to take updates from me every now and then if my paper got published. He used to take a lot of interest in the kind of journals I was sending my manuscript. He constantly pushed me to finish my research work in limited time. I believe my grandparents showered me with their immense blessings and strength all these years.

I wholeheartedly want to thank my guide, **Prof. Suresh C. Sharma, Professor**, Department of Applied Physics & Former Dean (Acad-PG) Delhi Technological University (DTU), for his excellent mentorship, research, patience, motivation, enthusiasm, immense knowledge, and continuous support all these years. Without his persistent efforts and guidance, this thesis would not have been accomplished. He has been a fatherly figure to me. He always tried to bring out the best in me. His guidance helped me do all the research and writing of this thesis. He is genuinely the best advisor and mentor and it is really difficult to find supervisors like him.

My sincere thanks also go to **Prof. Yogesh Singh**, Ex-Hon'ble Vice- Chancellor, DTU, **Prof. Jai Prakash Saini**, Hon'ble Vice-Chancellor, DTU and other officials for their valuable support and for providing ample facilities to conduct this research. I would also like to acknowledge the DTU's financial support to attend the 32<sup>nd</sup> International Conference on Diamond and Carbon Materials in Lisbon, Portugal in 2022.

I would also thank **Prof. Rinku Sharma**, Dean (Academic-PG), DTU, and **Prof. A.S. Rao**, Head of the Department of Applied Physics, DTU and all other faculty and staff members for their help and cooperation throughout my research. Thanks to the Department of Applied Physics, Delhi Technological University (DTU), for providing the required facilities so that I can work voraciously, barring the time limit. I want to pay high regard to my father, **Dr. Manish Kumar Kansal**, my mother, **Mrs. Kavita Kansal**, and my younger brother **Mr. Manan Kansal**, for their love, constant care, and emotional support throughout my life. It is because of my father that I am here. It is my father who has taught me Physics from the very beginning and motivated me to continue with this subject for so many years. He has guided me at every step of my career and has been my biggest support system. My mother has invested all her time in trying to make me a successful person. She has always taught me to work beyond my limits. My parents have always supported me in everything and provided me with the best of facilities for me to reach here. I owe a special and big thanks to my childhood best friend and partner, **Mr. Jaskirat Singh Arora**, for always being there and helping me at every possible step during all these years. This would not have been possible without him at all. I owe this to him. My family's cooperation, understanding, patience and encouragement were the sustaining factors in this challenging journey.

I express my gratitude to my seniors, **Dr. Umang Sharma, Ms. Anshu, Ms. Jyoti, Mr. Sagar Khanna, Ms. Shruti Sharma, Mr. Harender Mor** for their valuable suggestions and continuous help during the initial stage of my research work. I would also like to express huge and warm thanks to my other fellow lab mates **Mr. Aditya and Ms. Ritu** in Plasma & Nano Simulation Research Laboratory for their scientific inputs, fruitful discussions, motivation, and all the fun we had, kept me going in this challenging yet beautiful journey. I also explicitly thank my friends, **Ms. Priyanka, Mr. Yash Pathak, Dr. Aman Prasad** for their generous support. Their personal and professional help, moral support and encouragement have put me at ease. The time I spent with them will remain a memorable golden time in my life.

Janshe

Mansha Kansal

iv

## ABSTRACT

Carbon Nanotube Field-Effect Transistors (CNTFETs) are becoming the torch-bearers of advancements in the realm of electronics. The semiconductor industry's backbone, traditional silicon-based transistors, is reaching its scaling limits. Power consumption, heat dissipation, and quantum effects become increasingly pressing as the size of these transistors continues to decrease. CNTFETs may be able to help us get around these restrictions by leveraging the use of the distinct properties of Carbon Nanotubes (CNTs).

CNTFETs are desirable for use in cutting-edge electronics because of their excellent electrical characteristics. Due to their great carrier mobility, CNTFETs may provide rapid processing and enhanced efficiency. In response to the growing need for low-power electronic devices, their high current-carrying capacity makes it possible for these devices to function efficiently.

In addition, CNTFETs have potential applications in bioelectronics and sensing. Their great sensitivity and biocompatibility make them useful in biosensors, implantable devices, and bioelectronic interfaces. Precision detection and monitoring of biological species are leading to new possibilities in healthcare, diagnostics, and personalised medicine. In conclusion, the quest for high-performance, energy-efficient, flexible, and bio-compatible electronic devices has led to the development of CNTFETs as a solution to the limits possessed by conventional silicon-based transistors.

The thesis aims to shed light on the potential of Plasma-Assisted Gate-All-Around CNTFET technology to revolutionise the future of electronic devices by examining its development and many applications. The research demonstrates the effect of plasma parameters on the performance of a simulated device known as Plasma-Assisted Vertically Aligned Dual-Metal Carbon Nanotube Field-Effect Transistor (VA-DMCNFET). A vertically aligned semiconducting Carbon Nanotube (CNT), produced via the Plasma-Enhanced Chemical Vapour Deposition (PECVD) technology, has been used as the channel. A typical Si-based Nanowire Field-Effect Transistor (NWFET) may be compared to the proposed device, which demonstrates a

considerable increase in performance. The DC and analogue performance of the VA-DMCNFET is analysed for various plasma parameters corresponding to different values of CNT channel radius (for fixed CNT channel length) and varied values of CNT channel length (for fixed CNT channel radius). It has been found that lower values of plasma parameters are necessary for higher values of drain current, transconductance, output conductance, and cutoff frequency, as well as lower values of threshold voltage and channel resistance. On the other hand, higher values of plasma parameters are necessary for a better Ion/IoFF current ratio, early voltage, and gain of the proposed device. It is possible to increase the device's efficiency and, as a result, its applicability and performance in real-world settings by making alterations to the plasma parameters.

Further in this study, the simulation analysis of a novel device known as a Plasma-Assisted Dual-Material Stacked Gate-Oxide Carbon Nanotube Field Effect Transistor (DM-SGCNFET) is shown. This device has a stacked gate oxide structure that is composed of two oxides: SiO<sub>2</sub> and HfO<sub>2</sub>. The performance metrics of the simulated device are compared with a SiO<sub>2</sub>-based DM-CNFET for changing sets of plasma characteristics that correlate to different values of channel length. Comparing the DM-SGCNFET to the DM-CNFET, the in-depth study reveals that the former has superior characteristics in terms of the drain current, transconductance, output conductance, early voltage, gain, gate capacitance, improved switching ratio and lower channel resistance. The novel architecture of DM-SGCNFET paves the way for the device to be a suitable candidate for digital and analogue applications that need high efficiency. This work investigates the simulated device further for its linearity distortion performance. This is done by analysing the values of gm2, gm3, VIP2, VIP3, IIP3, IMD3, and the 1-dB compression point for varying plasma parameter values. The results show promising application potential for the simulated device in wireless communication systems.

In addition, this study develops a HfO<sub>2</sub> based Plasma-Assisted Gate All Around Carbon Nanotube Field Effect Transistor (GAA-CNTFET). The results of the study conclude that utilising HfO<sub>2</sub> results in improvements in all the observed performance metrics, including higher values for drain current, transconductance, output conductance, early voltage, and gate capacitance. The simulated device was put to

vi

study for sensing applications. This is achieved by implementing a cavity in the oxide layer and using the notion of dielectric modulation, which makes it possible to discover the change in performance characteristics of the device upon altering the dielectric permittivity of the molecule inside the cavity. The higher the dielectric constant value, the better the performance and the more sensitive the device will be. The findings of this research provide useful information for quantifying the device's potential uses in the sensing fields of biology, the environment, and other important sectors.

Thermal stability and conductivity shown by CNT is another fascinating area of research as it opens the doors for unprecedented applications. The study showcases the robustness and stability shown by a simulated DM-SGCNFET device by testing it at different temperature values for temperatures up to 500K. Precision-demanding industries such as aerospace, military, and heavy-scale industries can take benefit from the findings of this study to develop new-age solutions.

## ABBREVIATIONS

| CNT        | Carbon Nanotube                                      |  |  |

|------------|------------------------------------------------------|--|--|

| GAA        | Gate-All-Around                                      |  |  |

|            |                                                      |  |  |

| TCVD       | Thermal Chemical Vapour Deposition                   |  |  |

| PECVD      | Plasma Enhanced Chemical Vapor Deposition            |  |  |

| CNTFET     | Carbon Nanotube Field-Effect Transistor              |  |  |

| NWFET      | Nanowire Field-Effect Transistor                     |  |  |

| CMOS       | Complementary Metal Oxide Semiconductor              |  |  |

| VA-DMCNFET | Vertically Aligned Dual-Metal Carbon Nanotube Field- |  |  |

|            | Effect Transistor                                    |  |  |

| DM-SGCNFET | Dual-Material Stacked Gate-Oxide Carbon Nanotube     |  |  |

|            | Field Effect Transistor                              |  |  |

| DIBL       | Drain Induced Barrier Lowering                       |  |  |

| GAA-CNTFET | Gate-All-Around Carbon Nanotube Field Effect         |  |  |

|            | Transistor                                           |  |  |

| VACNTs     | Vertically aligned CNTs                              |  |  |

| MOSFET     | Metal Oxide Semiconductor Field Effect Transistor    |  |  |

| MOSFET     | Metal Oxide Semiconductor Field Effect Transistor    |  |  |

| RF         | Radio Frequency                                      |  |  |

| SCE        | Short Channel Effect                                 |  |  |

## LIST OF PUBLICATIONS

#### International journals

- Mansha Kansal, Suresh C. Sharma, "Investigation of Plasma-Assisted Stacked Gate-Oxide Gate All Around CNTFET (SG-GAA-CNTFET) with Temperature Variations for High Frequency and Wireless Applications" (Communicated).

- Mansha Kansal, Suresh C. Sharma, "Exploration of Novel Hafnium Oxide (HfO<sub>2</sub>) based Plasma-Assisted Gate All Around Carbon Nanotube FET (GAA-CNTFET) for high sensing applications", ECS Journal of Solid State Science and Technology, Volume 11, no. 10 (2022): 101002.

- **3. Mansha Kansal**, Suresh C. Sharma, "Performance Evaluation & Linearity Distortion Analysis for Plasma- Assisted Dual-Material Carbon Nanotube Field Effect Transistor with a SiO<sub>2</sub>-HfO<sub>2</sub> Stacked Gate-Oxide Structure (DM-SGCNFET)", **Silicon** (2022): 1-11.

- Mansha Kansal, Suresh C. Sharma, "Plasma-based Nanoarchitectonics for Vertically Aligned Dual-Metal Carbon Nanotube Field Effect Transistor (VA-DMCNFET) Device: Effect of Plasma Parameters on Transistor Properties", Applied Physics A, 128 (1)(2022): 1-11.

#### International peer reviewed proceedings

- Mansha Kansal, Suresh C. Sharma, "Numerical Simulation of Performance Metrics of Dual Metal Gate Carbon Nanotube Field Effect Transistor (DM-CNTFET) for Numerous Sensing Purposes", *Materials Today: Proceedings*, SI: ICAMN (2022).

- 2. Mansha Kansal, Suresh C. Sharma, "Simulation Based Analysis of Plasma-Assisted Carbon Nanotube Field Effect Transistor (CNTFET) for improved device metrics and applications", International Conference on Nanotechnology: Opportunities and Challenges, 2022 (ICNOC-2022).

- 3. Mansha Kansal, Suresh C. Sharma, "Impact of PECVD characteristics on metrics of a Plasma-Assisted Vertically Aligned Carbon Nanotube FET (VA-CNTFET) device," 2022 IEEE International Conference on Nanoelectronics, Nanophotonics, Nanomaterials, Nanobioscience & Nanotechnology (5NANO), 2022.

## CONTENTS

| Certificate             | i    |

|-------------------------|------|

| Candidate's declaration | ii   |

| Acknowledgement         | iii  |

| Abstract                | v    |

| List of Publications    | viii |

| List of Figures         | xi   |

| List of Tables          | XV   |

|                         |      |

## <u>Chapter 1</u>

#### Introduction

| 1.1 | Backg   | round and research motivation                      | 1  |

|-----|---------|----------------------------------------------------|----|

| 1.2 | Introdu | uction to Carbon Nanotube (CNT)                    | 2  |

| 1.3 | Structu | are of Carbon Nanotube                             | 4  |

| 1.4 | Types   | of Carbon Nanotube                                 | 4  |

|     | 1.4.1   | Single-walled Carbon Nanotube (SWCNTs)             | 5  |

|     | 1.4.2   | Multi-walled Carbon Nanotube (MWCNTs)              | 6  |

| 1.5 | Proper  | ties of Carbon Nanotube                            | 6  |

| 1.6 | Applic  | ations of Carbon Nanotube                          | 7  |

|     | 1.6.1   | Molecular electronics                              | 7  |

|     | 1.6.2   | Structural materials                               | 8  |

|     | 1.6.3   | Biomedical applications                            | 8  |

|     | 1.6.4   | Field-Effect Transistors                           | 8  |

| 1.7 | Synthe  | esis of Carbon Nanotubes                           | 9  |

|     | 1.7.1   | Plasma enhanced chemical vapour deposition (PECVD) | 9  |

|     |         | <b>1.7.1.1</b> Advantages of PECVD technique       | 12 |

| 1.8 | Plasma  | a and Plasma sheath                                | 12 |

| 1.9  | MOSE    | ET scaling and Moore's law                                   | 14 |

|------|---------|--------------------------------------------------------------|----|

| 1.10 | Introdu | action to Carbon Nanotube Field Effect Transistors (CNTFETs) | 14 |

| 1.11 | Overvi  | ew and significance of CNTFET technology                     | 16 |

| 1.12 | Multi-g | gate MOSFETs                                                 | 17 |

| 1.13 | Types   | of CNTFET                                                    | 17 |

|      | 1.13.1  | Back-gated CNTFET                                            | 17 |

|      | 1.13.2  | Top-gated CNTFET                                             | 18 |

|      | 1.13.3  | Suspended CNTFET                                             | 19 |

|      | 1.13.4  | Gate-all-around (GAA) CNTFET                                 | 19 |

| 1.14 | Why G   | ate-All-Around (GAA) CNTFET?                                 | 20 |

| 1.15 | Method  | ds for achieving GAA geometry                                | 21 |

| 1.16 | Strateg | ies for improving device performance                         | 22 |

|      | 1.16.1  | Channel engineering                                          | 22 |

|      | 1.16.2  | Gate engineering                                             | 22 |

|      |         | <b>1.16.2.1</b> Advantages of multi-material gates           | 24 |

|      | 1.16.3  | Gate and dielectric layer dimensions                         | 25 |

| 1.17 | Design  | factors for low-power and high-frequency applications        | 25 |

| 1.18 | Applic  | ations of CNTFET                                             | 25 |

|      | 1.18.1  | Wireless communications                                      | 26 |

|      | 1.18.2  | Sensing applications                                         | 27 |

|      | 1.18.3  | Biosensing applications                                      | 27 |

|      | 1.18.4  | Sensors in high-temperature and high-endurance environments  | 28 |

| 1.19 | Organi  | zation of thesis                                             | 29 |

|      | Refere  | ences                                                        | 31 |

|     | Plasma-based Nanoarchitectonics for Vertically Aligned Dual-Metal |    |

|-----|-------------------------------------------------------------------|----|

|     | Carbon Nanotube Field Effect Transistor (VA-DMCNFET) Device:      |    |

|     | Effect of Plasma Parameters on Transistor Properties              |    |

| 2.1 | Brief Outline                                                     | 37 |

| 2.2 | Introduction                                                      | 38 |

| 2.3 | Device Simulation                                                 | 39 |

| 2.4 | Results And Discussion                                            | 42 |

|     | 2.4.1   | Performance comparison between VA-DMCNFET and NWFET            | 42 |

|-----|---------|----------------------------------------------------------------|----|

|     | 2.4.2   | Evaluating role of plasma parameters on the performance of VA- | 44 |

|     |         | DMCNFET                                                        |    |

| 2.5 | Conclus | sion                                                           | 60 |

|     | Referen | ces                                                            | 61 |

Performance Evaluation & Linearity Distortion Analysis for Plasma-Assisted Dual-Material Carbon Nanotube Field Effect Transistor with a SiO<sub>2</sub>-HfO<sub>2</sub> Stacked Gate-Oxide Structure (DM-SGCNFET)

| 3.1 | Brief ( | Dutline                                                         | 65 |

|-----|---------|-----------------------------------------------------------------|----|

| 3.2 | Introdu | action                                                          | 66 |

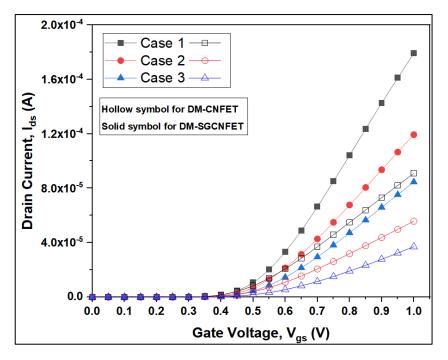

| 3.3 | Device  | Simulation                                                      | 68 |

| 3.4 | Result  | s and Discussion                                                | 71 |

|     | 3.4.1   | Performance evaluation of DM-SGCNFET with varying SiO2 oxide    | 71 |

|     |         | thickness                                                       |    |

|     | 3.4.2   | Performance comparison of DM-SGCNFET with DM-CNFET              | 73 |

|     | 3.4.3   | Impact of plasma parameters on linearity characteristics of DM- | 81 |

|     |         | SGCNFET                                                         |    |

| 3.5 | Conclu  | ision                                                           | 87 |

|     | Refere  | nces                                                            | 88 |

### Chapter 4

Exploration of Novel Hafnium Oxide (HfO<sub>2</sub>) based Plasma-Assisted Gate All Around Carbon Nanotube FET (GAA-CNTFET) for high sensing applications

| 4.1 | Brief outline           | 92 |

|-----|-------------------------|----|

| 4.2 | Introduction            | 93 |

| 4.3 | Device Simulation Model | 94 |

| 4.4 | Results and Discussion  | 98 |

|     | 4.4.1   | Impact of variation of Plasma Parameters for SiO2 and HfO2 based | 99  |

|-----|---------|------------------------------------------------------------------|-----|

|     |         | GAA-CNTFET                                                       |     |

|     | 4.4.2   | Dielectric modulation of HfO2 based GAA-CNTFET for sensing       | 103 |

|     |         | applications                                                     |     |

| 4.5 | Conclu  | sion                                                             | 112 |

|     | Referen | nces                                                             | 113 |

#### Performance Assessment of Plasma-Assisted DM-CNFET for Sensing Applications and Temperature Fluctuations

| 5.1 | Brief ( | Dutline                                                  | 117 |

|-----|---------|----------------------------------------------------------|-----|

| 5.2 | Introdu | action                                                   | 118 |

| 5.3 | Device  | e simulation                                             | 119 |

| 5.4 | Result  | s and Discussion                                         | 121 |

|     | 5.4.1   | Sensing applications with DM-CNFET                       | 121 |

|     | 5.4.2   | Temperature variation on DM-CNFET for high frequency and | 126 |

|     |         | wireless applications                                    |     |

| 5.5 | Conclu  | ision                                                    | 132 |

|     | Refere  | ences                                                    | 133 |

## Chapter 6

#### **Conclusion And Future Scope**

| 6.1 | Conclusion   | 136 |

|-----|--------------|-----|

| 6.2 | Future Scope | 139 |

## LIST OF FIGURES

## Chapter 1

| Figure No. | Description                                                      | Page Number |

|------------|------------------------------------------------------------------|-------------|

| 1.1        | Transformation of 2D graphene into various carbon                | 3           |

|            | nanostructures                                                   |             |

| 1.2        | Schematic of graphene lattice with $C$ as the chiral vector; $T$ | 4           |

|            | as the translation vector; and $a_1$ and $a_2$ as basis vectors, |             |

|            | respectively                                                     |             |

| 1.3        | Types of CNTs; SWCNT (singe-walled carbon nanotubes)             | 5           |

|            | and MWCNT (multi-walled carbon nanotubes)                        |             |

| 1.4        | Schematic of MW-PECVD setup                                      | 11          |

| 1.5        | Schematic of plasma sheath region                                | 13          |

| 1.6        | Carbon Nanotube Field Effect Transistor (CNTFET)                 | 15          |

| 1.7        | Different configurations of a MOSFET                             | 17          |

| 1.8        | Back-Gated Carbon Nanotube Field Effect Transistor               | 18          |

| 1.9        | Top-Gated Carbon Nanotube Field Effect Transistor                | 19          |

| 1.10       | Gate-All-Around Carbon Nanotube Field Effect Transistor          | 21          |

|            | (GAA-CNTFET)                                                     |             |

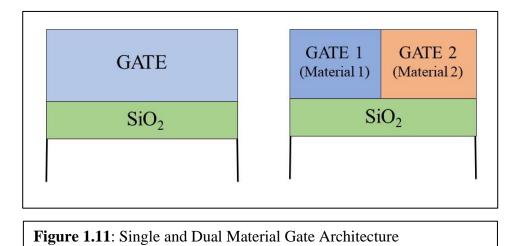

| 1.11       | Single and Dual Material Gate Architecture                       | 24          |

| Figure No. | Description                                                                                                                                                                                                                                                 | Page Number |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

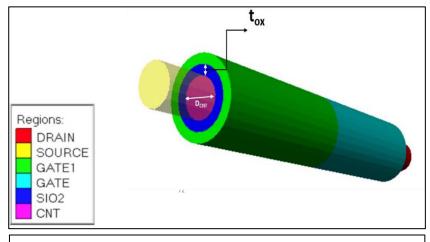

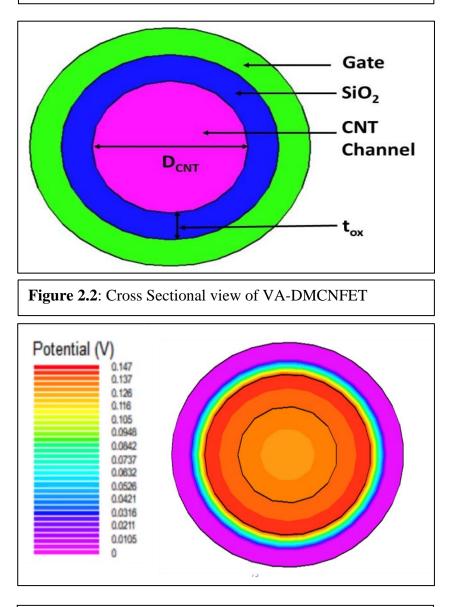

| 2.1        | 3-D structure of cylindrical VA-DMCNFET                                                                                                                                                                                                                     | 40          |

| 2.2        | Cross Sectional view of VA-DMCNFET                                                                                                                                                                                                                          | 40          |

| 2.3        | Potential contour profile of VA-DMCNFET with $V_{ds}$ = 0.0<br>V and $V_{gs}$ = 0.0V                                                                                                                                                                        | 40          |

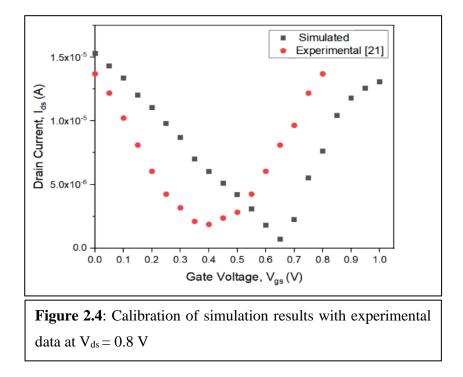

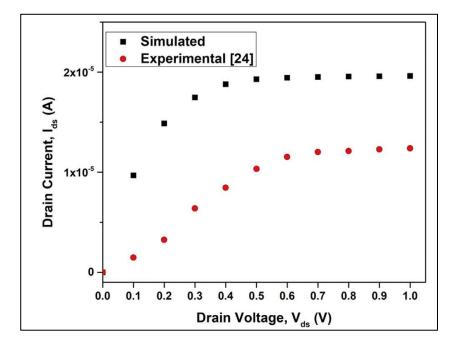

| 2.4        | Calibration of simulation results with experimental data at $V_{ds} = 0.8 V$                                                                                                                                                                                | 41          |

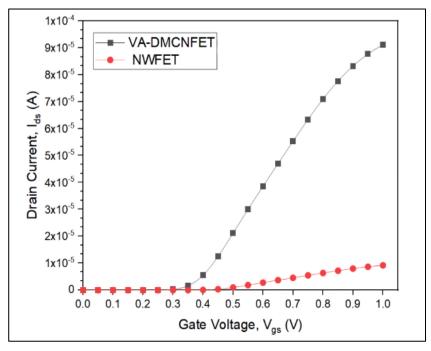

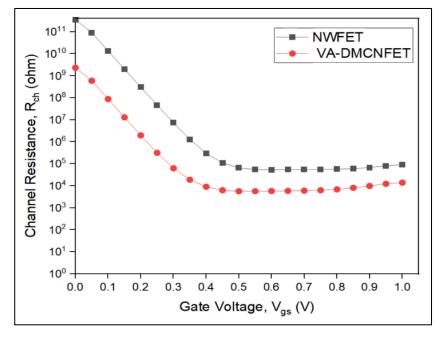

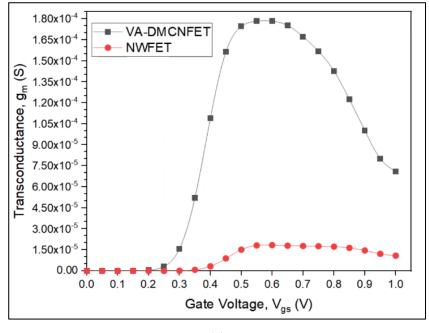

| 2.5        | $\begin{array}{c} Comparison \ between \ proposed \ device \ VA-DMCNFET \ and \\ NWFET \ having \ same \ parameters: \ Variation \ in \ (a) \ Drain \\ current \ I_{ds} \ with \ gate \ voltage \ V_{gs} \ (b) \ Channel \ Resistance \ R_{ch} \end{array}$ | 42-43       |

|      | with $V_{gs}$ (in log scale) (c) Transconductance $g_m$ with $V_{gs}$ at              |    |

|------|---------------------------------------------------------------------------------------|----|

|      | $V_{ds} = 0.5 V$                                                                      |    |

|      |                                                                                       |    |

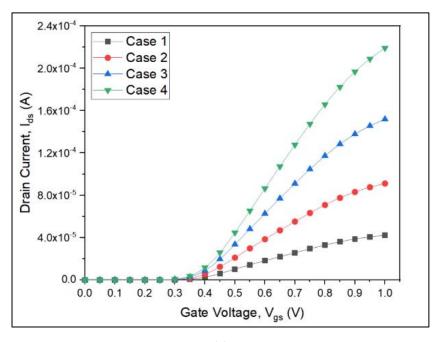

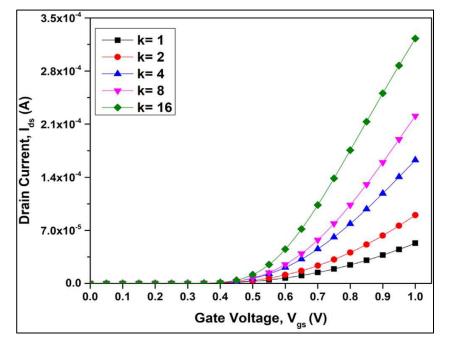

| 2.6  | Transfer characteristics for VA-DMCNFET for different                                 | 49 |

|      | values of plasma parameters corresponding to different                                |    |

|      | values of (a) channel radius (in nm) (Table 2.2), (b) channel                         |    |

|      | length (in $\mu$ m) (Table 2.3) at V <sub>ds</sub> = 0.5V.                            |    |

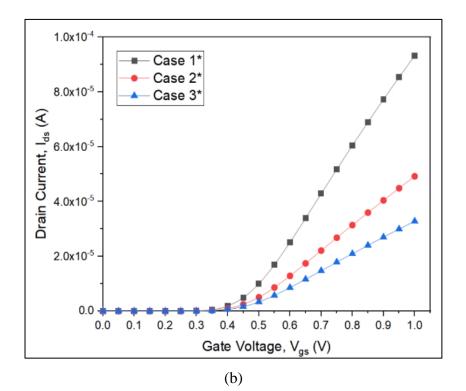

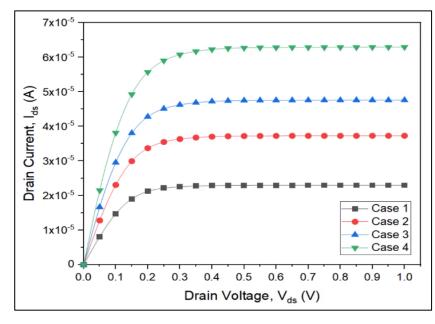

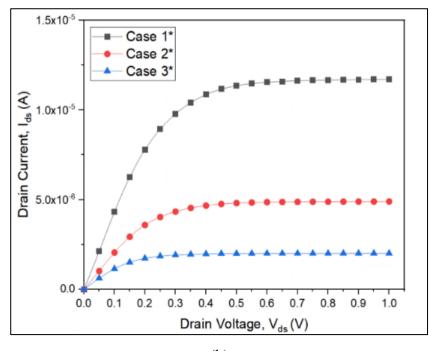

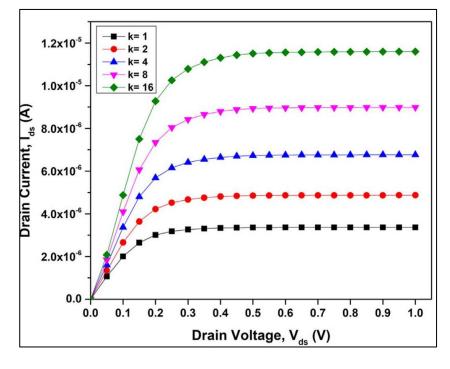

| 2.7  | Output characteristics of VA-DMCNFET for different                                    | 50 |

|      | values of plasma parameters corresponding to different                                |    |

|      | values of (a) channel radius (in nm) (Table 2.2), (b) channel                         |    |

|      | length (in $\mu$ m) (Table 2.3) at V <sub>gs</sub> = 0.5 V                            |    |

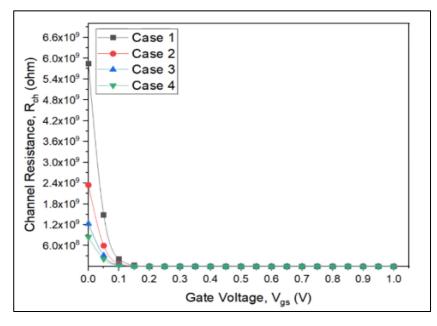

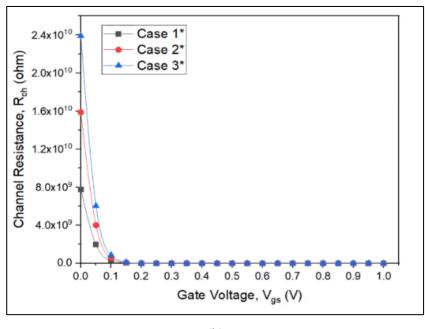

| 2.8  | $R_{ch}$ vs $V_{gs}$ for different values of plasma parameters                        | 51 |

|      | corresponding to different values of (a) channel radius (in                           |    |

|      | nm) (Table 2.2), (b) channel length (in $\mu$ m) (Table 2.3) at                       |    |

|      | $V_{ds} = 0.5 V$                                                                      |    |

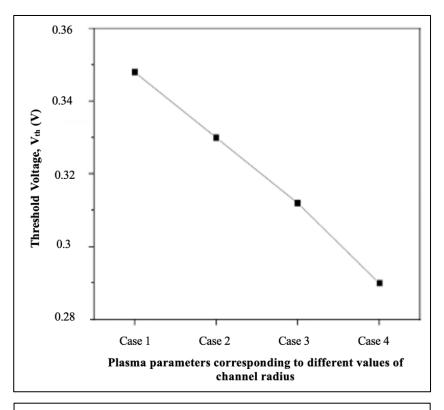

| 2.9  | Variation of V <sub>th</sub> for different values of plasma parameters                | 52 |

|      | corresponding to different values of channel radius (in nm)                           |    |

|      | (Table 2.2) at $V_{ds} = 0.1 V$                                                       |    |

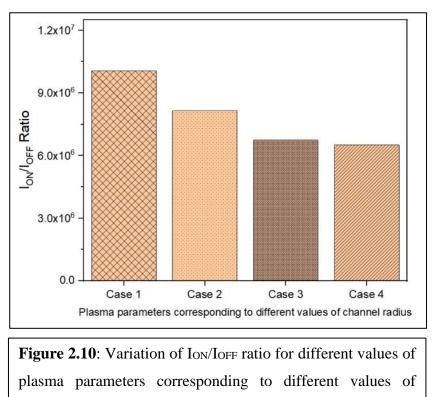

| 2.10 | Variation of $I_{ON}/I_{OFF}$ ratio for different values of plasma                    | 52 |

|      | parameters corresponding to different values of channel                               |    |

|      | radius (in nm) (Table 2.2) at $V_{ds} = 0.5 V$                                        |    |

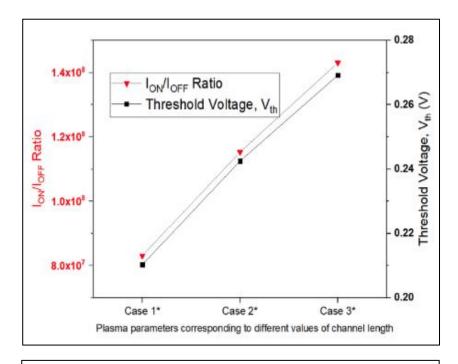

| 2.11 | Variation of Threshold voltage, $V_{th}$ and $I_{\text{ON}}/I_{\text{OFF}}$ ratio for | 53 |

|      | different values of plasma parameters corresponding to                                |    |

|      | different values of channel length (in $\mu$ m) (Table 2.3) at                        |    |

|      | $V_{ds} = 0.5 V$                                                                      |    |

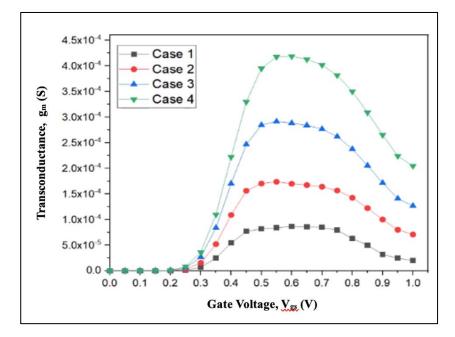

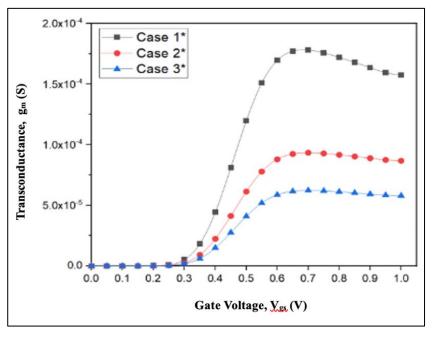

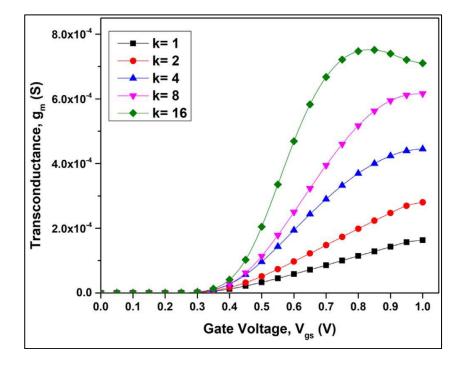

| 2.12 | $g_m$ vs $V_{gs}$ for different values of plasma parameters                           | 54 |

|      | corresponding to different values of (a) channel radius (in                           |    |

|      | nm) (Table 2.2) (b) channel length (in $\mu$ m) (Table 2.3) at                        |    |

|      | $V_{ds} = 0.5 V$                                                                      |    |

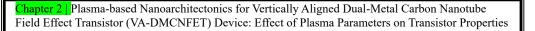

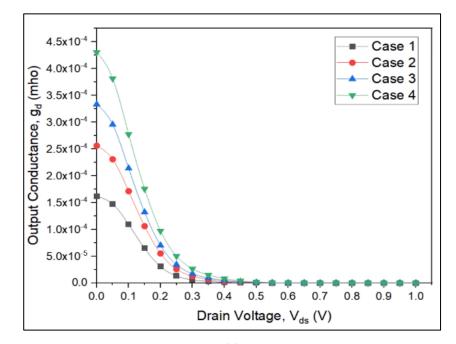

| 2.13 | $g_d$ vs $V_{ds}$ for different values of plasma parameters                           | 56 |

|      | corresponding to different values of (a) channel radius (in                           |    |

|      | nm) (Table 2) (b) channel length (in $\mu$ m) (Table 3) at V <sub>gs</sub> =          |    |

|      | 0.5 V                                                                                 |    |

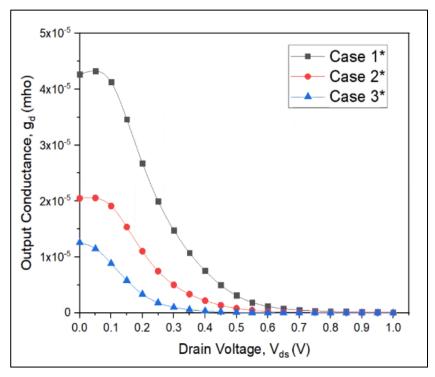

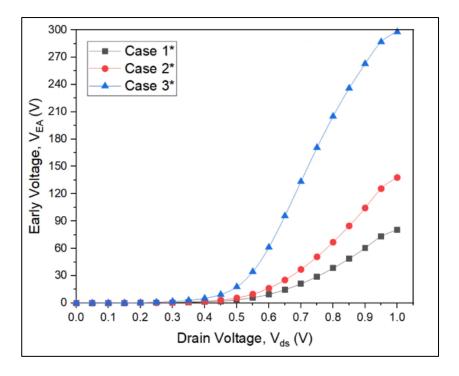

| 2.14 | $V_{EA}$ vs $V_{ds}$ for different values of plasma parameters                        | 57 |

|      | corresponding to different values of (a) channel radius (in                           |    |

| L    |                                                                                       | I  |

|      | nm) (Table 2.2) (b) channel length (in $\mu$ m) (Table 2.3) at $V_{gs} = 0.5 \text{ V}$ |    |

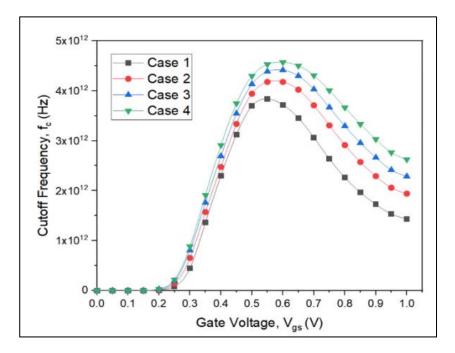

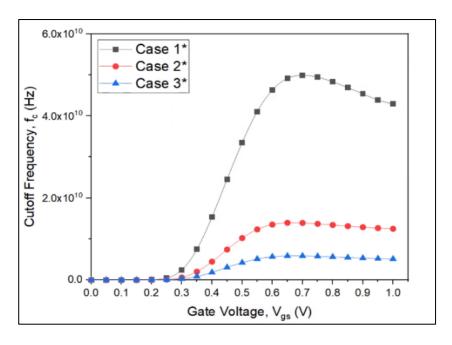

|------|-----------------------------------------------------------------------------------------|----|

| 2.15 | $f_c$ vs $V_{gs}$ for different values of plasma parameters                             | 59 |

|      | corresponding to different values of (a) channel radius (in                             |    |

|      | nm) (Table 2.2) (b) channel length (in $\mu$ m) (Table 2.3) at                          |    |

|      | $V_{ds} = 0.5 V$                                                                        |    |

| Figure No. | Description                                                                         | Page Number |

|------------|-------------------------------------------------------------------------------------|-------------|

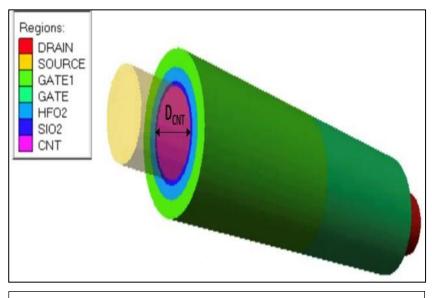

| 3.1        | 3-D view of the proposed DM-SGCNFET                                                 | 68          |

| 3.2        | Depiction of cross-sectional view of DM-SGCNFET                                     | 68          |

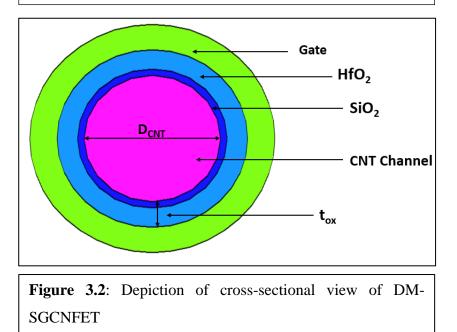

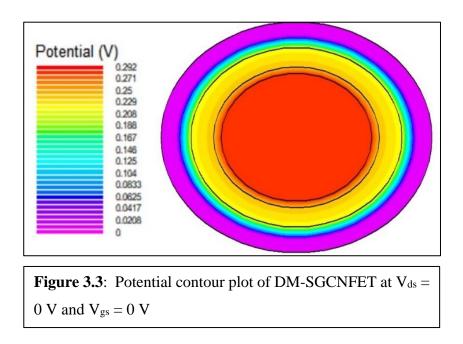

| 3.3        | Potential contour plot of DM-SGCNFET at $V_{ds} = 0 V$ and $V_{gs}$                 | 69          |

|            | = 0 V                                                                               |             |

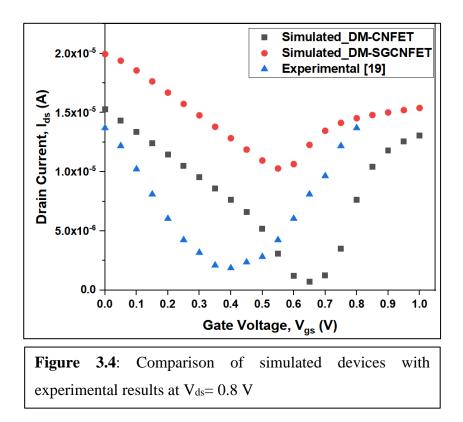

| 3.4        | Comparison of simulated devices with experimental results at                        | 70          |

|            | $V_{ds} = 0.8 V$                                                                    |             |

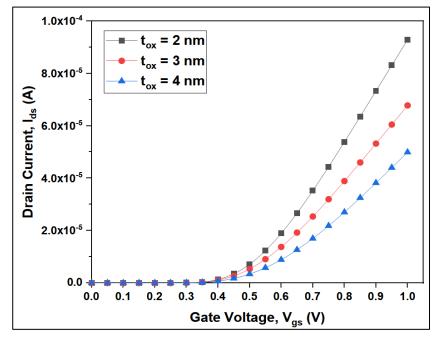

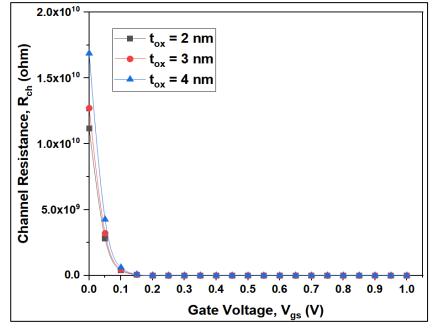

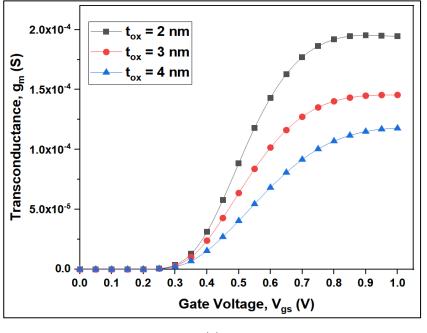

| 3.5        | Impact of oxide thickness variation on SiO <sub>2</sub> based DM-                   | 72-73       |

|            | CNFET: (a) Drain current $I_{ds}$ v/s gate voltage $V_{gs}$ (b) Channel             |             |

|            | Resistance $R_{ch}  v/s \; V_{gs} $ (c) Transconductance $g_m  v/s \; V_{gs} $ (at  |             |

|            | constant $V_{ds} = 0.8 V$ )                                                         |             |

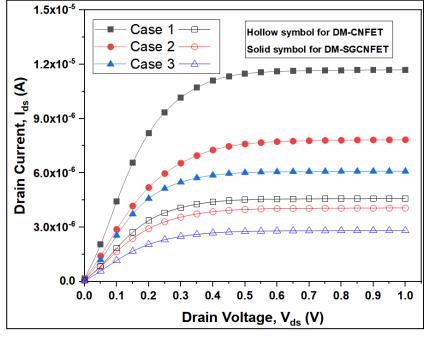

| 3.6        | Impact of plasma parameters variation (Table 2) on (a) transfer                     | 76          |

|            | characteristics at $V_{ds}$ = 0.8 V (b) output characteristics at $V_{gs}$ =        |             |

|            | 0.5 V                                                                               |             |

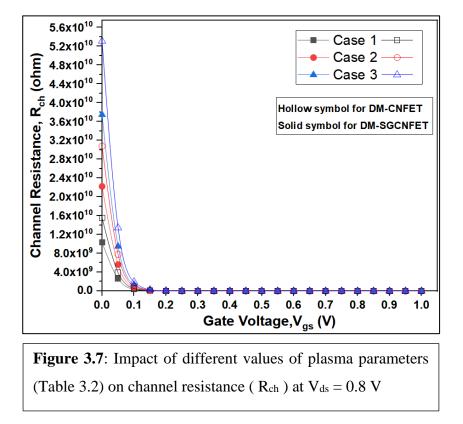

| 3.7        | Impact of different values of plasma parameters (Table 3.2) on                      | 77          |

|            | channel resistance ( $R_{ch}$ ) at $V_{ds} = 0.8 \ V$                               |             |

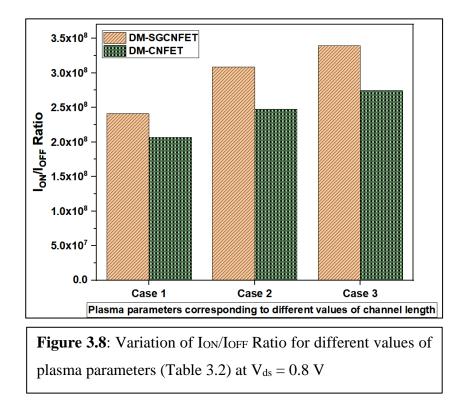

| 3.8        | Variation of I <sub>ON</sub> /I <sub>OFF</sub> Ratio for different values of plasma | 78          |

|            | parameters (Table 3.2) at $V_{ds} = 0.8 V$                                          |             |

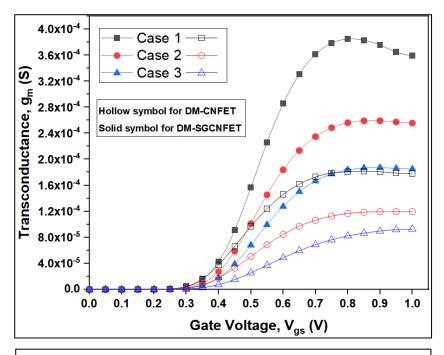

| 3.9        | Impact of plasma parameters variation (Table 3.2) on                                | 79          |

|            | transconductance ( $g_m$ ) at $V_{ds} = 0.8 V$                                      |             |

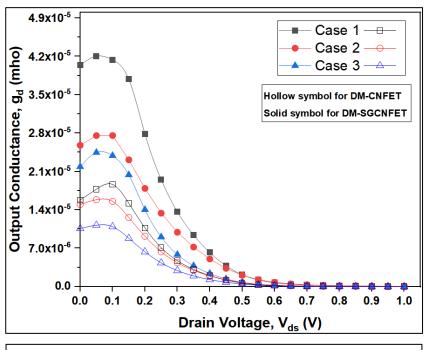

| 3.10       | Impact of plasma parameters variation (Table 3.2) on output                         | 79          |

|            | conductance ( $g_d$ ) at $V_{ds} = 0.8 V$                                           |             |

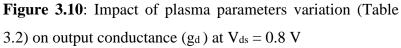

| 3.11       | Impact of different values of plasma parameters (Table 3.2) on                      | 80          |

|            | early voltage ( $V_{EA}$ ) at $V_{gs} = 0.5 V$                                      |             |

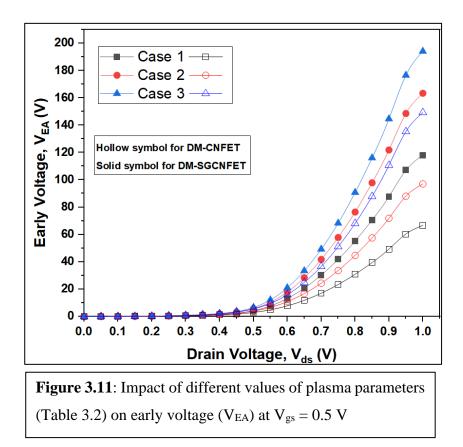

| 3.12 | $\label{eq:gamma} \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                 | 81    |

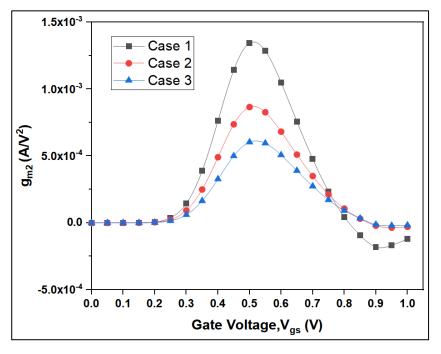

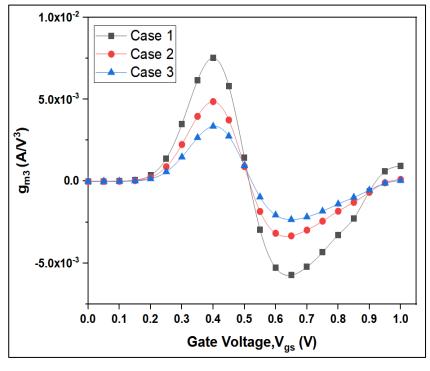

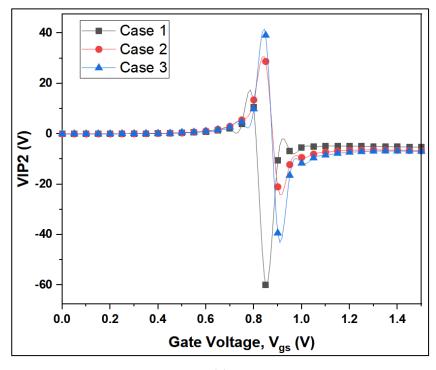

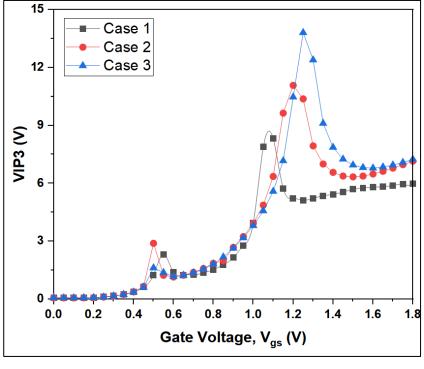

|------|-------------------------------------------------------------------------------------------------------------------------|-------|

| 3.13 | Impact of plasma parameters variation (Table 3.2) on (a) $g_{m2}$<br>(b) $g_{m3}$ (c) VIP2 (d) VIP3 at $V_{ds} = 0.8$ V | 83-84 |

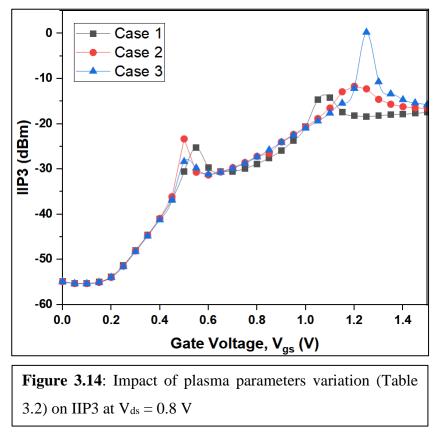

| 3.14 | Impact of plasma parameters variation (Table 3.2) on IIP3 at $V_{ds} = 0.8 \text{ V}$                                   | 85    |

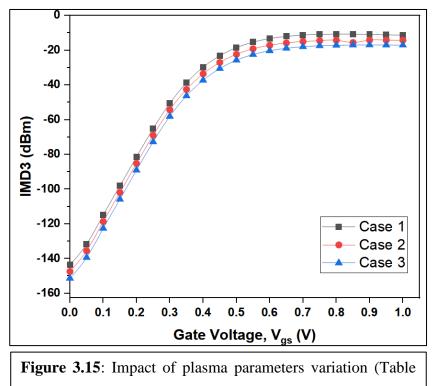

| 3.15 | Impact of plasma parameters variation (Table 3.2) on IMD3 at $V_{ds} = 0.8 \text{ V}$                                   | 86    |

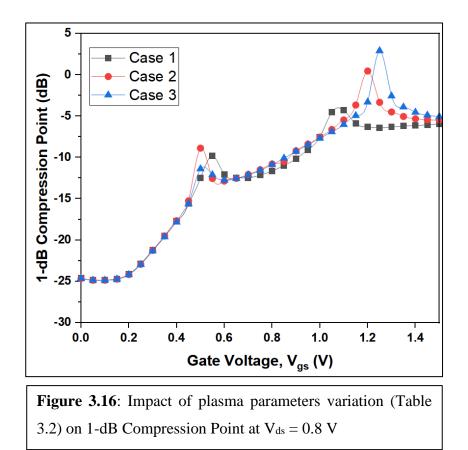

| 3.16 | Impact of plasma parameters variation (Table 3.2) on 1-dB<br>Compression Point at $V_{ds} = 0.8 V$                      | 86    |

| Figure No. | Description                                                                                                                                                                                                                                      | Page Number |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

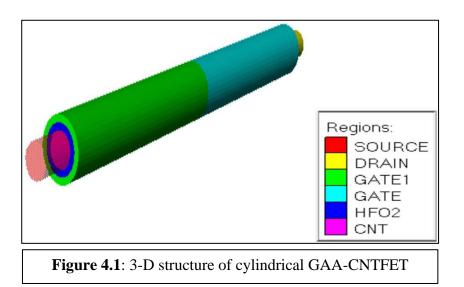

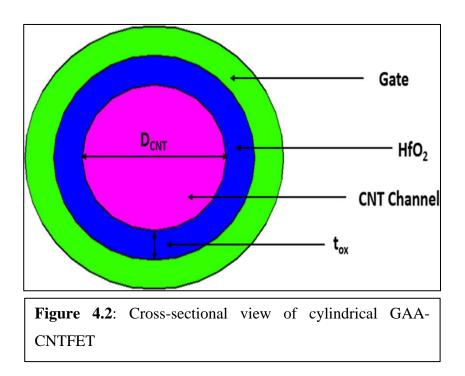

| 4.1        | 3-D structure of cylindrical GAA-CNTFET                                                                                                                                                                                                          | 96          |

| 4.2        | Cross-sectional view of cylindrical GAA-CNTFET                                                                                                                                                                                                   | 96          |

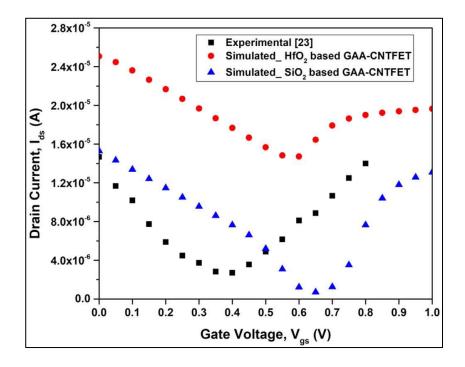

| 4.3        | Comparison of simulated devices with (a) experimental results<br>by Kansal and Sharma (Theoretical) and Yang and Mohanram<br>(Experimental) [22,23] at $V_{ds} = 0.8$ V (b) experimental results<br>by Franklin et al. [24] at $V_{ds} = 0.75$ V | 97          |

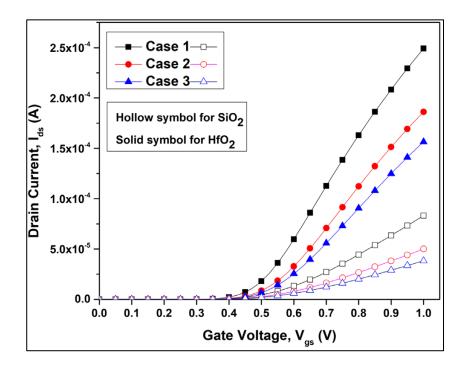

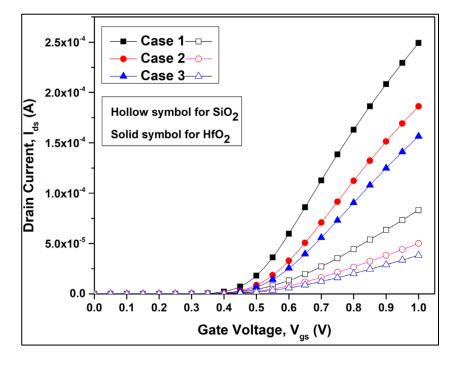

| 4.4        | Impact of variation of plasma parameters (Table 4.2) for both $SiO_2$ and $HfO_2$ based GAA-CNTFET on (a) transfer characteristics at $V_{ds} = 0.8$ V (b) output characteristics at $V_{gs} = 0.5$ V                                            | 100         |

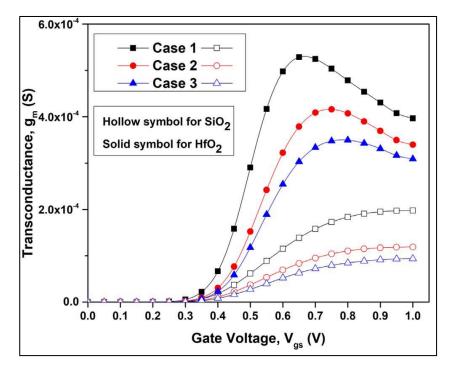

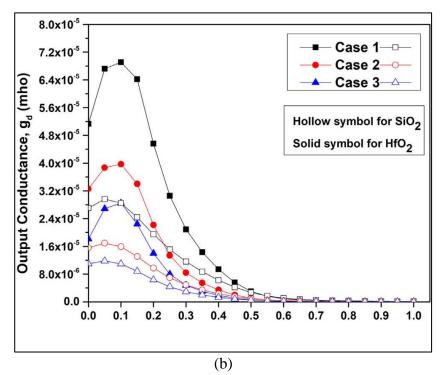

| 4.5        | Impact of variation of plasma parameters (Table 4.2) for both $SiO_2$ and $HfO_2$ based GAA-CNTFET on (a) transconductance, $g_m$ at $V_{ds} = 0.8$ V (b) output conductance, $g_d$ at $V_{gs} = 0.5$ V                                          | 101         |

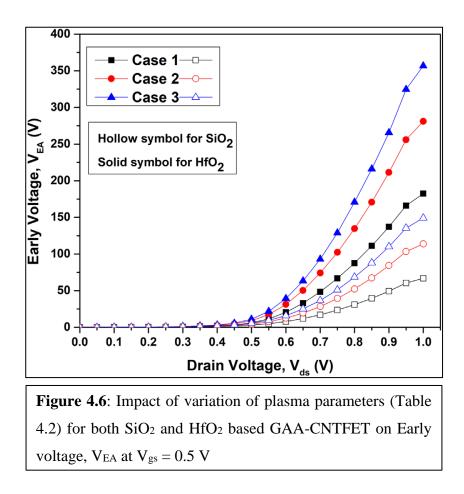

| 4.6        | Impact of variation of plasma parameters (Table 4.2) for both SiO <sub>2</sub> and HfO <sub>2</sub> based GAA-CNTFET on Early voltage, $V_{EA}$ at $V_{gs} = 0.5 \text{ V}$                                                                      | 102         |

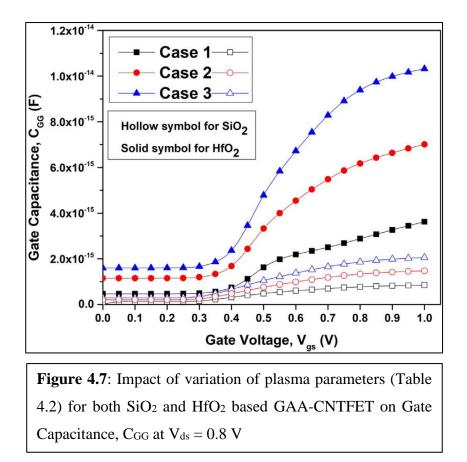

| 4.7        | Impact of variation of plasma parameters (Table 4.2) for both $SiO_2$ and $HfO_2$ based GAA-CNTFET on Gate Capacitance, $C_{GG}$ at $V_{ds} = 0.8$ V                                                                                             | 103         |

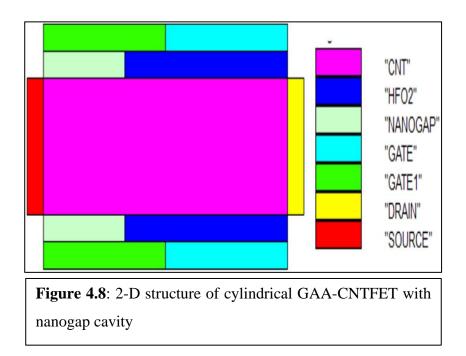

| 4.8        | 2-D structure of cylindrical GAA-CNTFET with nanogap cavity                                                                                                                                                                                      | 104         |

| 4.9  | Impact of variation of dielectric constant on (a) transfer                    | 105     |

|------|-------------------------------------------------------------------------------|---------|

|      | characteristics at $V_{ds}$ = 1.0 V (b) output characteristics at $V_{gs}$ =  |         |

|      | 0.5 V                                                                         |         |

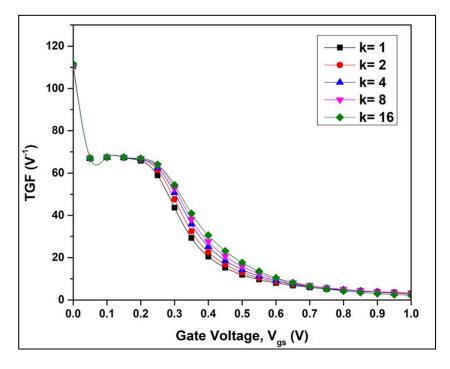

| 4.10 | Impact of variation of dielectric constant on (a) $g_m$ (b) TGF at            | 106     |

|      | $\mathbf{V}_{\mathrm{ds}}=1.0~\mathbf{V}$                                     |         |

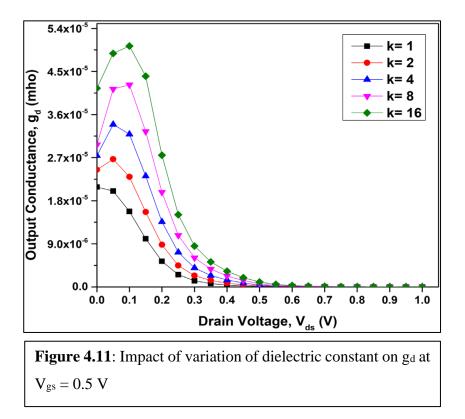

| 4.11 | Impact of variation of dielectric constant on $g_d$ at $V_{gs} = 0.5 V$       | 107     |

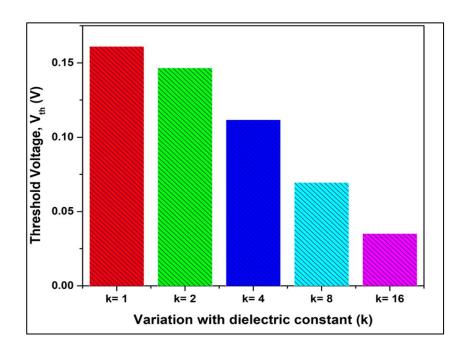

| 4.12 | Impact of variation of dielectric constant on (a) Threshold                   | 108     |

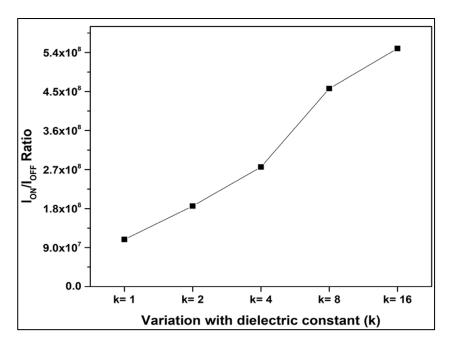

|      | voltage, $V_{th}$ (b) $I_{ON}/I_{OFF}$ Ratio at $V_{ds} = 1.0 \text{ V}$      |         |

| 4.13 | Impact of variation of dielectric constant on (a) Drain Current               | 109     |

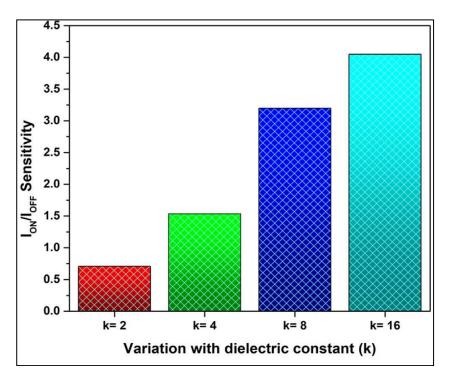

|      | Sensitivity (b) $I_{ON}/I_{OFF}$ Sensitivity at $V_{ds} = 1.0 V$              |         |

| 4.14 | Impact of variation of dielectric constant on (a) C <sub>GG</sub> (b) Cut-off | 110-111 |

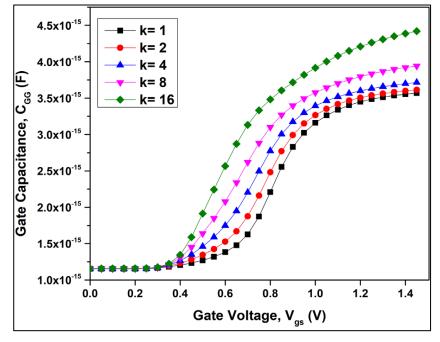

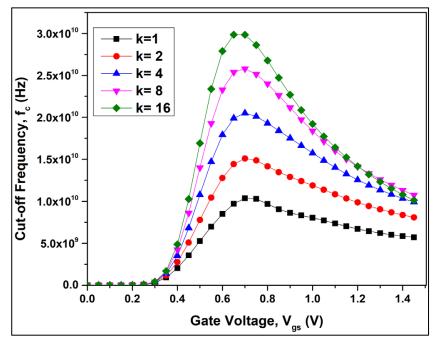

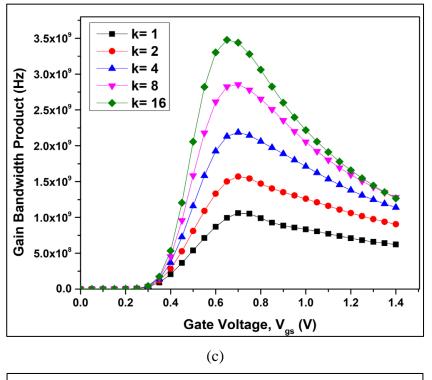

|      | Frequency $f_c(c)$ Gain Bandwidth Product at $V_{ds} = 0.8$ V                 |         |

| Figure No. | Description                                                                                                              | Page Number |

|------------|--------------------------------------------------------------------------------------------------------------------------|-------------|

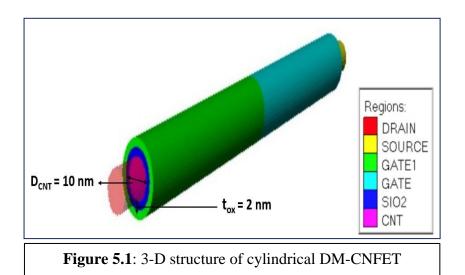

| 5.1        | 3-D structure of cylindrical DM-CNFET                                                                                    | 120         |

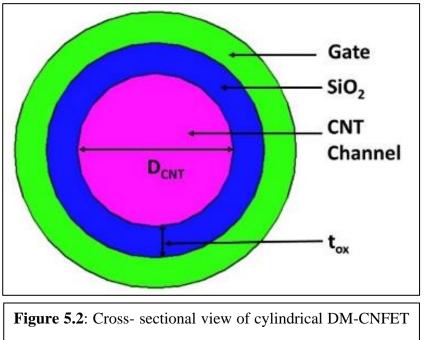

| 5.2        | Cross- sectional view of cylindrical DM-CNFET with 1.5 $\mu$ m in length and 5 nm in radius                              | 120         |

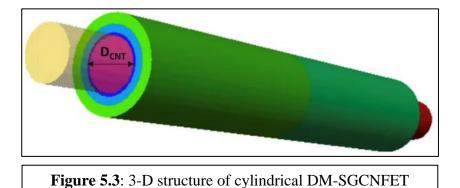

| 5.3        | 3-D structure of cylindrical DM-SGCNFET                                                                                  | 121         |

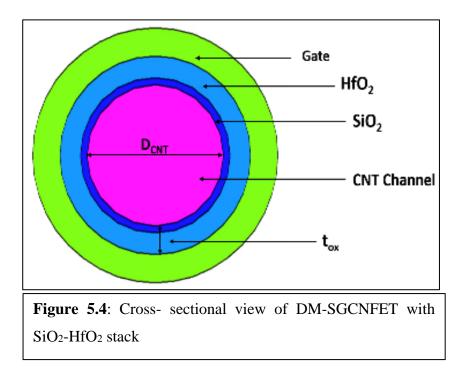

| 5.4        | Cross- sectional view of DM-SGCNFET with SiO <sub>2</sub> -HfO <sub>2</sub> stack                                        | 121         |

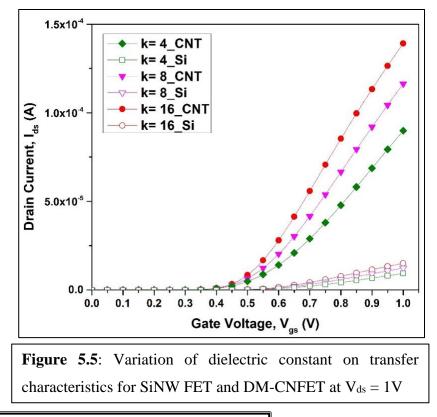

| 5.5        | Variation of dielectric constant on transfer characteristics for SiNW FET and DM-CNFET at $V_{ds} = 1V$                  | 122         |

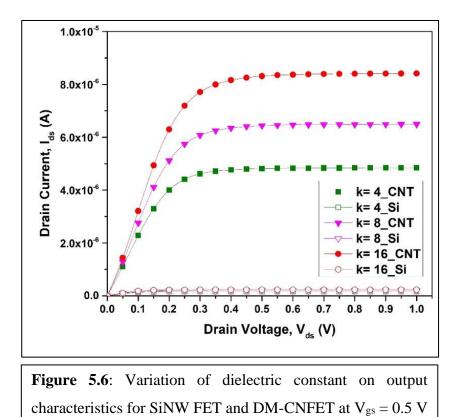

| 5.6        | Variation of dielectric constant on output characteristics for SiNW FET and DM-CNFET at $V_{gs} = 0.5 \text{ V}$         | 123         |

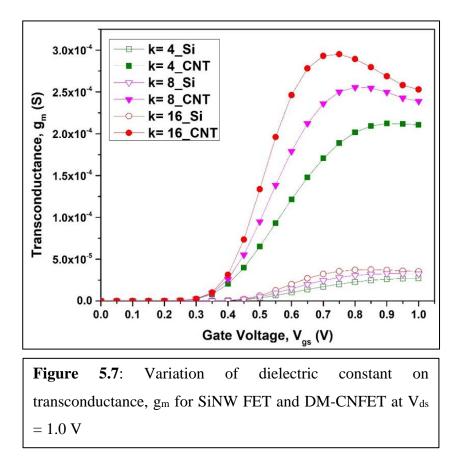

| 5.7        | Variation of dielectric constant on transconductance, $g_m$ for SiNW FET and DM-CNFET at $V_{ds} = 1.0$ V                | 123         |

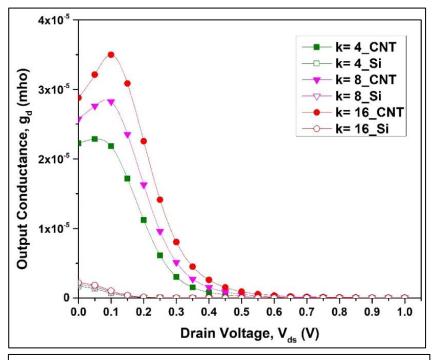

| 5.8        | Variation of Variation of dielectric constant on output conductance, $g_d$ for SiNW FET and DM-CNFET at $V_{gs} = 0.5$ V | 124         |

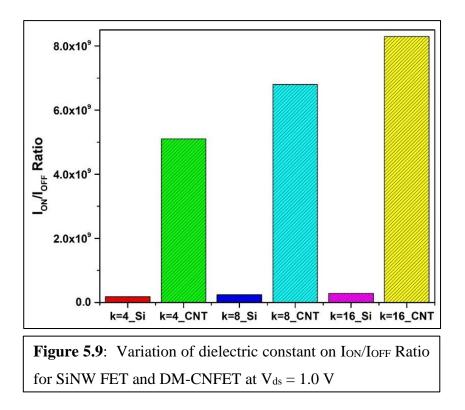

| 5.9        | Variation of dielectric constant on $I_{ON}/I_{OFF}$ Ratio for SiNW FET<br>and DM-CNFET at $V_{ds} = 1.0$ V              | 124         |

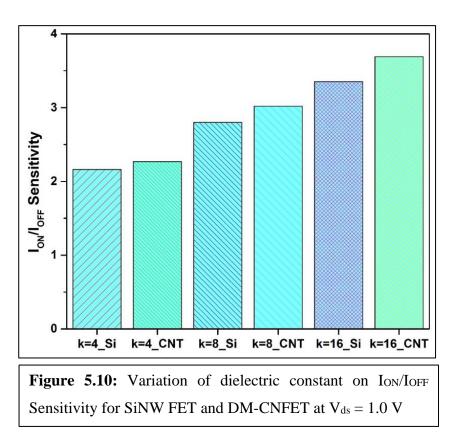

| 5.10       | Variation of dielectric constant on $I_{ON}/I_{OFF}$ Sensitivity for SiNW FET and DM-CNFET at $V_{ds} = 1.0$ V           | 125         |

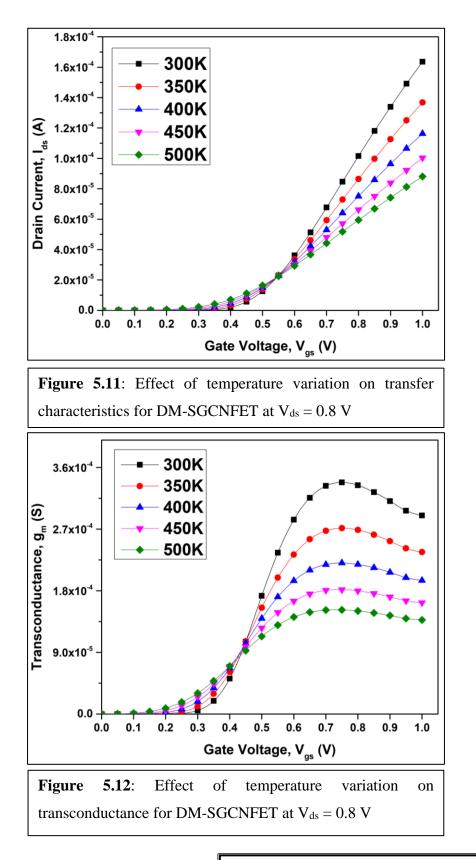

| 5.11 | Effect of temperature variation on transfer characteristics         | 127     |

|------|---------------------------------------------------------------------|---------|

|      | for DM-SGCNFET at $V_{ds} = 0.8 V$                                  |         |

| 5.12 | Effect of temperature variation on transconductance for             | 127     |

|      | DM-SGCNFET at $V_{ds} = 0.8 V$                                      |         |

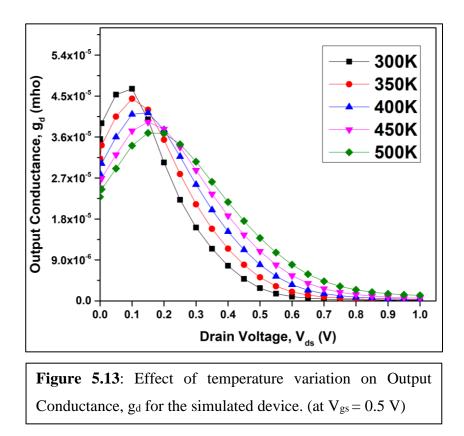

| 5.13 | Effect of temperature variation on Output Conductance, gd           | 128     |

|      | for the simulated device. (at $V_{gs} = 0.5 \text{ V}$ )            |         |

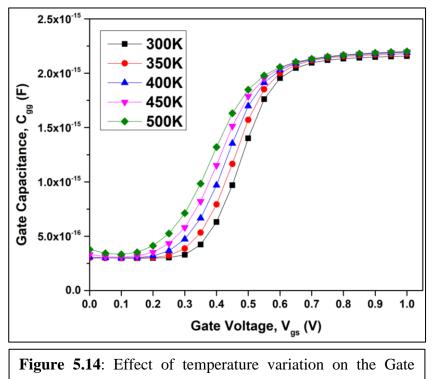

| 5.14 | Effect of temperature variation on the Gate Capacitance             | 128     |

|      | C <sub>GG</sub> of DM-SGCNFET                                       |         |

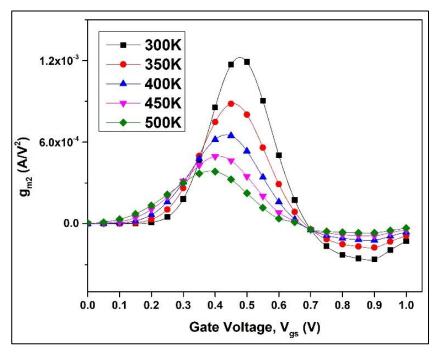

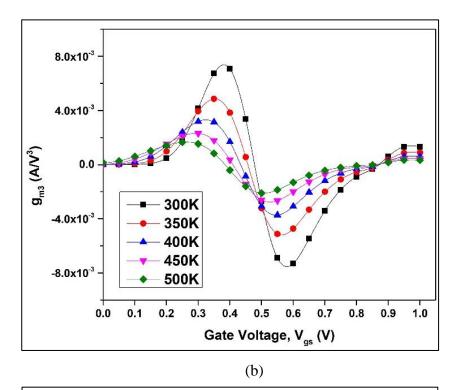

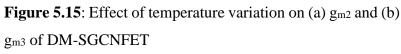

| 5.15 | Effect of temperature variation on (a) $g_{m2}$ and (b) $g_{m3}$ of | 129-130 |

|      | DM-SGCNFET                                                          |         |

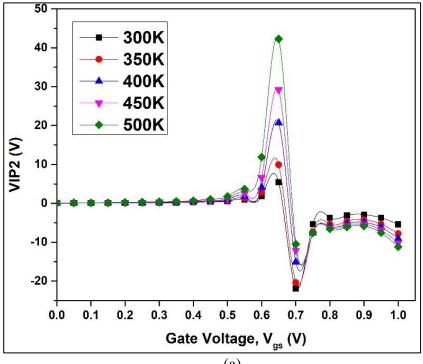

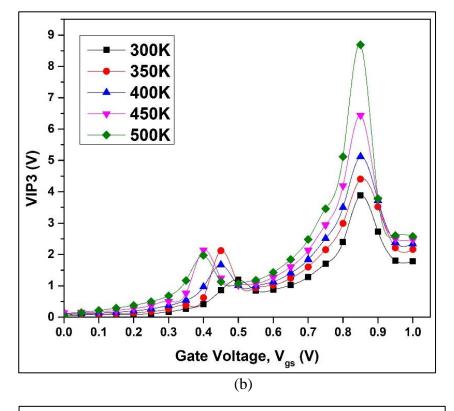

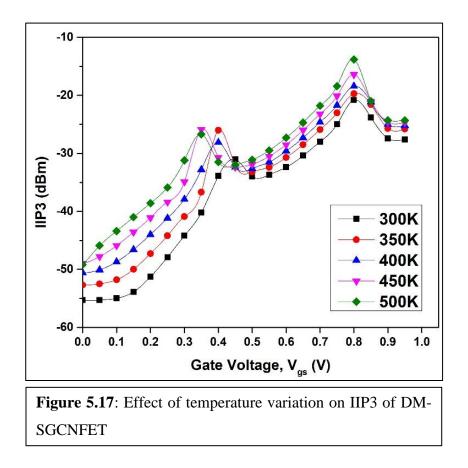

| 5.16 | Effect of temperature variation on (a) VIP2 and (b) VIP3            | 131     |

|      | of DM-SGCNFET                                                       |         |

| 5.17 | Effect of temperature variation on IIP3 of DM-SGCNFET               | 132     |

## LIST OF TABLES

## Chapter 2

| Table No. | Description                                                                                                                                      | Page No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1       | Device Specifications                                                                                                                            | 43       |

| 2.2       | Variation of Plasma parameters: $n_{eo}$ and $T_{eo}$ , $n_{io}$ and $T_{io}$ with channel radius (For a fixed value of channel length = 100 nm) | 45       |

| 2.3       | Variation of Plasma parameters: $n_{eo}$ and $T_{eo}$ , $n_{io}$ and $T_{io}$ , with channel length (For a fixed value of channel radius = 5 nm) | 45       |

| 2.4       | Summary Table                                                                                                                                    | 60       |

## Chapter 3

| Table No. | Description                                                   | Page No. |

|-----------|---------------------------------------------------------------|----------|

| 3.1       | Device Specifications                                         | 69       |

| 3.2       | Value of Plasma parameters corresponding to varying values of | 71       |

|           | channel length (at constant value of $R = 5 \text{ nm}$ )     |          |

| 3.3       | Review Table                                                  | 87       |

| Table No. | Description                                                    | Page No. |

|-----------|----------------------------------------------------------------|----------|

| 4.1       | Device Specifications                                          | 98       |

| 4.2       | Plasma parameters variation corresponding to varying values    | 98       |

|           | of channel length (at a constant value of $R = 5 \text{ nm}$ ) |          |

# 1

#### INTRODUCTION

#### **1.1 BACKGROUND AND RESEARCH MOTIVATION**

Advancements in nanoelectronics has made it possible to realise new-age electronic devices that are smaller, faster and more energy-efficient. The study of designing, developing, and ultimately deploying electrical components at the nanoscale level is known as nanoelectronics. The study and use of nanomaterials is now the most rapidly expanding area in material science and engineering.

At nanoscale dimensions, certain physical and chemical characteristics of materials are highlighted, leading to novel functionality of the synthesized electronic devices. Nanoelectronics has revolutionized several industries, including computer processing, sensing, energy, and medicine.

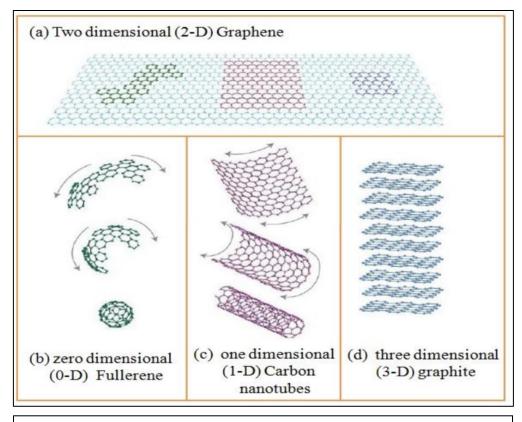

There are three primary configurations of elemental Carbon: Graphite, which consists of stacked planar graphitic sheets, Diamond, in which the carbon atoms are bonded tetrahedrally to each other in a massive three-dimensional structure and Fullerenes, a large and diverse class of hollow spheres, ellipses, and tubes made of  $sp^2$  hybridized carbon atoms [1,2]. The discovery of fullerenes [3] and carbon nanotubes (CNTs) [4] sparked the development of a new area of research, leading to an increase in our knowledge of physics, chemistry, and potential technological applications [5,6] of these carbon configurations. Carbon nanotubes (CNTs) are cylindrical nanostructures composed of carbon atoms arranged in a hexagonal lattice. Figure 1.1 shows transformation of 2D graphene into various carbon nanostructures. Each discovery, notably the most recent [7,8] ones, has forecasted a major shift in materials science and electronics. Single-walled carbon nanotube (SWCNT) production was rapidly demonstrated using a laser ablation approach [9]. Single-walled carbon nanotubes (SWCNTs) are the building blocks of multi-walled carbon nanotubes (MWCNTs). lijima [4] reported the finding of MWCNTs in the early 1990s. These are tubular carbon nanostructures that have been crystallized and stacked several times. They have

remarkable mechanical, electrical, and thermal properties and have gathered much interest from researchers.

Ever since their discovery, there has been a lot of enthusiasm for studies involving manufacturing, characterization, growth process, chemical modifications, and potential uses of CNTs. Extensive research has opened the door for CNTs to find applications in industries such as nanoelectronics, energy storage, composites, sensors, and biomedicine. Due to their superior electrical properties and scaling capabilities, CNTs are front runners to replace conventional channel materials and keep CMOS technology relevant for the modern age.

Nanoarchitectonics has made it possible to harness the special properties of CNTs into realisable electronic circuits. Incorporating CNTs into nanoarchitectonic frameworks, has opened the doors for exciting avenues in the near future.

#### **1.2 INTRODUCTION TO CARBON NANOTUBE (CNT)**

Carbon Nanotube (CNT) is a superior new-age composed of carbon atoms arranged in a cylindrical structure with a diameter in the nanometre range [10]. Since their discovery in 1991 [1], CNTs have sparked much interest from researchers owing to their distinct and superior material properties. Carbon nanotubes are the perfect answer to two big problem statements of conventional materials - scaling limitations and power limitations. They stands as the number one candidate to take advantage of rapid advancements in nanotechnology.

The unique abilities possessed by CNTs arise from their nanoscale dimensions and high aspect ratio. They exhibit exceptional mechanical strength along with superior electrical and thermal conductivity. Their versatility makes them an ideal material for testing and research applications.

The superior electrical conductivity of CNTs has great application potential. They are known to conduct electricity at exceptionally low resistance. Nanoelectronics has received a major boost owing to CNTs' exceptional electrical conductivity, with extensive work being done to integrate them with transistors, sensors, and other electrical components. Their high power capabilities are set to revolutionize the electronics industry as we know it. The thermal conductivity of CNTs is amongst the highest seen in current mainstream materials and has been another area of fascination. They are resistant to high temperatures, expanding their applications to usage in heat sinks, thermal management, and more. Their ability to conduct a high magnitude of current at high-temperature values makes them frontrunners for usage in innovative solutions for heatsink applications.

In conclusion, CNTs offer highly desirable research avenues owing to their superior material properties and application potential. The meteoric rise in the number of patent applications and academic courses on CNT is a testament to the excitement and interest shown by researchers around the globe ever since their discovery. A lot of unknowns need to be unlocked before CNTs are deployed for wide scale applications and start replacing conventional materials.

**Figure 1.1**: Transformation of 2D graphene into various carbon nanostructures [11].

#### **1.3 STRUCTURE OF CARBON NANOTUBE**

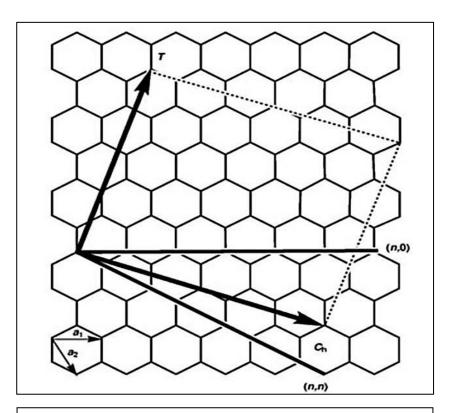

A CNT can be visualized as a rolled-up sheet of graphene. A graphene sheet comprises of carbon atoms bonded and arranged in a hexagonal mesh. The carbon-carbon bond strength provides CNTs with tough strength. The direction and angle of rolling of this graphene sheet affects the properties of resultant CNT. It affects its physical properties, such as diameter and chirality, which in turn affects its electrical properties. Figure 1.2 represents the schematic of the graphene lattice with C as the chiral vector; T as the translation vector; and  $a_1$  and  $a_2$  as basis vectors, respectively [12].

#### **1.4 TYPES OF CARBON NANOTUBE**

CNTs can be structurally characterized into three types - Single-Walled, Double-Walled and Multi-Walled Carbon Nanotubes. All of them have significantly different physical properties. The sizes of single-walled carbon nanotubes (SWCNTs), and

MANSHA KANSAL, Delhi Technological University

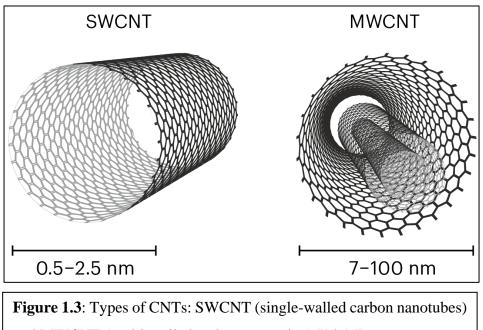

multi-walled carbon nanotubes (MWCNTs) are quite different, as shown in Figure 1.3. Despite minimal diameters, they have extremely high aspect ratios. Therefore, CNTs are considered to be quasi-one-dimensional materials [13]. There are typically two types of CNTs: (1) single-walled CNTs (SWCNTs), which have only one graphene layer, and (2) multi-walled CNTs (MWCNTs), which have nested co-axial arrays of single-walled CNTs that are spaced apart by an average of 0.34 nm, which is marginally more significant than the interlayer separation of graphite.

#### 1.4.1 SINGLE-WALLED CARBON NANOTUBES (SWCNTS)

Single-Walled Carbon Nanotubes are carbon atoms in a single hollowed-up graphene sheet. They have 1-2 nm diameters and an aspect ratio as high as 10<sup>4</sup>. The properties of SWCNTs are governed by two important metrics - diameter and chirality. Chirality is a measure of the orientation of the hexagon carbon lattice with respect to the tube axis. The chiral angle plays a crucial role in determining the electrical properties of the resultant CNT. Based on the chiral vector orientation, they can be both metallic and semiconductors.

and MWCNT (multi-walled carbon nanotubes) [14,15]

#### 1.4.2 MULTI-WALLED CARBON NANOTUBES (MWCNTS)

As the name suggests, MWCNTs consist of multiple sheets of graphene rolled to form concentric cylindrical tubes. They can be imagined as multiple SWCNTs rolled up over one another. They have unique properties with diameters ranging to 100 nm and an aspect ratio of  $10^3$ .

#### **1.5 PROPERTIES OF CARBON NANOTUBE**

Since CNTs have a high aspect ratio and a hollow structure, charge carriers move in one dimension in these materials. Their resistivity is  $10^{-6} \Omega$  cm at room temperature, much less than that of the resistivity of silver and copper [9,16]. The mobility of holes in semiconducting CNTs ( $\sim 2 \times 10^4 \text{ cm}^2/\text{Vs}$ ) is higher than that of electrons and holes in silicon ( $\sim 1.5 \times 10^3 \text{ cm}^2/\text{Vs}$ ) and ( $\sim 4.5 \times 10^2 \text{ cm}^2/\text{Vs}$ ). The CNTs also have a high current density ( $10^7$ - $10^9 \text{ A/cm}^2$ ) [17,18]. The experimental range for CNT Young's modulus [19,24] is 0.7-1.8 TPa, whereas theoretically [25] is 0.5-5 TPa. This shows that CNTs are more robust and stiffer than steel [26,27], with Young's modulus of about 0.18-0.2 TPa.

Numerous electronic devices can find CNT relevant because of its diameterdependent energy gap. CNT-based Field-Effect Transistors (FETs) feature metal electrodes linked via a CNT on the high substrate point and topped by an insulating layer. CNTs have an inherent advantage over bulk semiconducting materials to function as the key component of a single electron transistor (SET) because the CNT's 1D nature constrains electron delivery in the nanostructure. CNT conductance is very sensitive to the electrostatic environment because of the enormous surface-to-volume ratio of CNTs.

Semiconducting CNTs can flip between conducting and non-conducting states, hence allowing them to precisely regulate electrical current flow, making them appropriate for use as transistors and other electronic devices.

Scalability and integration possibilities for CNTs are quite promising. Researchers have created methods for precisely arranging individual CNTs, making it possible to

fabricate integrated circuits, interconnects, and transistors based on CNTs. Controlling CNT chirality, large-scale synthesis, and assuring device repeatability are still some of the issues that need to be addressed.

The field of nanoelectronics has received a major boost since the rise of CNT. The creation of cutting-edge electronic devices and integrated circuits based out of CNTs are promising owing to their high electrical conductivity, bandgap flexibility, ambipolar behavior, and scalability.

#### **1.6 APPLICATIONS OF CARBON NANOTUBE**

Since its discovery, CNT has been labelled as a superior new-age material. Excellent electrical and thermal conductivity, high physical strength, and versatility are notable advantages it holds over its counterparts.

Owing to these properties, CNTs are studied for various applications – both for improvements in pre-existing solutions and the development of novel applications. Some of the most prominent applications currently being investigated for CNT usage are -

#### **1.6.1 MOLECULAR ELECTRONICS**

Molecular electronics is a fast-developing area that investigates using specific molecules or nanoscale materials as electrical device building blocks. CNTs have attracted much attention in molecular electronics. Owing to their great electrical conductivity and low resistance, they can function as nanoscale wires or interconnects in electronic circuits, allowing for the downscaling of electronic components.

CNTs may be incorporated into nanoscale transistors, switches, and sensors. They are well suited for nanoscale logic circuits due to their high carrier mobility, low power consumption, and temperature adaptability. More and more work is being done to create sophisticated electrical devices with high-density integration of CNTs.

CNTs have shown huge potential to function as molecular sensors. Their quick reaction time to external changes implies that they offer high sensitivity - a metric strongly

measured for high-performance sensors. Adding to this, they also benefit with quick reaction times, and the capacity to identify minute quantities of target molecules, thus making for an all-rounded sensor.

#### **1.6.2 STRUCTURAL MATERIALS**

CNTs have remarkable mechanical qualities. They are strong, rigid, and low-density making them very appealing for usage as a structural material. Composites reinforced with CNTs have demonstrated better mechanical characteristics, such as increased tensile strength, toughness, and thermal stability. Industries such as aerospace, automotive, and sports goods sectors, which need a strong yet lightweight material, may find CNTs useful.

#### **1.6.3 BIOMEDICAL APPLICATIONS**

CNTs are the frontrunners to revolutionise biosensing applications. To find infections and biomarkers, CNTs may also be employed as biosensors. Target molecules in biological samples can be detected selectively and sensitively by functionalizing the CNT surface with certain receptors or antibodies. CNT-based biosensors also have usages in food safety, environmental monitoring, and illness.

#### **1.6.4 FIELD-EFFECT TRANSISTORS**

Carbon Nanotube-based Field-Effect Transistors, often known as CNTFETs, offer enormous potential for use in electronics. CNTFETs are appealing for various applications, including high-performance logic circuits, flexible electronics, and lowpower devices [28,29].

Because of the nanoscale size of CNTs, CNTFETs can enable the miniaturization of electrical devices. They can produce ultra-compact, high-density integrated circuits, which can improve Internet of Things (IoT) applications, wearable electronics, and portable electronics.

Additionally, CNTFETs showcase excellent electrical performance, including high ON/OFF ratios and quick switching times.

CNTs offer a plethora of application possibilities in several industries. They are a frontrunner to revolutionize many industries and be the primary material of choice for more innovative solutions in the future.

#### **1.7 SYNTHESIS OF CARBON NANOTUBES**

Synthesis of CNTs can be done in various ways that allow for the controlled development of these unique nanostructures. A few well-known methods include Arc Discharge, Laser Ablation, Chemical Vapour Deposition (CVD), and Plasma-Enhanced Chemical Vapour Deposition (PECVD).

A common approach is CVD, which involves the catalyzed breakdown of carboncontaining gases at high temperatures. It makes it possible to create CNTs with greater customization, including single-walled and multi-walled carbon nanotubes (SWNTs and MWNTs). The Arc Discharge process creates MWNTs using a high-current arc between graphite electrodes. SWNTs are produced via laser ablation, which uses a high-temperature furnace to vaporize a graphite target.

#### **1.7.1 PLASMA ENHANCED CHEMICAL VAPOUR DEPOSITION (PECVD)**

While each synthesis technique mentioned above have their own unique advantages, the Plasma Enhanced Chemical Vapour Deposition (PECVD) technique has received much interest. PECVD offers flexibility in resultant CNT that no other synthesis method can.

Since heat is the principal source for chemical reactions, temperatures higher than  $750^{\circ}$ C are required for the CVD synthesis of CNTs. Microelectronics fabrication typically tops out at about  $400^{\circ}$ C –  $500^{\circ}$ C. Thus, this is much beyond that range. The PECVD technique of CNT synthesis is a low-temperature synthesis method. Plasma (a quasineutral state consisting of electrons, ionic species, neutrals, radicals, and others) generates energy that dissociates gaseous species. Vertically aligned CNTs (VACNTs) oriented in the direction normal to the substrate (along the electric field) by the electric field created by the plasma sheath are formed because of the PECVD technique [30,34]. Due to plasma etching of etchant species and ultra-long CNTs, the catalyst deactivation rate (i.e., the formation rate of the amorphous carbon layer over

the catalyst's active region) may be decreased. However, excessive etching can also be detrimental to CNT growth.

The formation of CNTs at high temperatures via Thermal Chemical Vapour Deposition (TCVD) is a vapor-liquid-solid mechanism. During the TCVD-CNT growth process, the catalyst is in a liquid drop state, and carbon species produced from the gaseous species are dissolved into it. The supersaturated eutectic liquid is used as a source of precipitation for the CNTs. It has been claimed that the activation energies necessary for synthesis in TCVD for ~ 700  $^{\circ}$ C are between ~ 1.2 – 1.8 eV.

The catalysts can remain solid at low temperatures, so a low-temperature CNT growing mechanism is required. The activation energies for low-temperature CNT growth [35] should be between  $\sim 0.2 - 0.4$  eV. This is close to the activation energies of carbon surface diffusion [36] on Ni (0.3 eV). The carbon diffusion on the catalyst's surface at low temperatures was suggested as the rate-limiting stage for plasma-assisted growth.

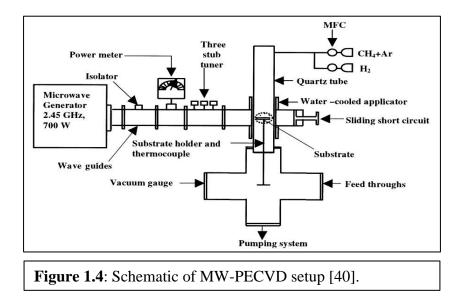

The PECVD method is simple, easy to control, uses low temperatures and pressure, and is the most popular method for synthesizing carbon-based nanostructures. The PECVD method, as mentioned above, uses plasma energy to synthesize CNTs. Some of these plasma sources include -

- Radio frequency plasma-enhanced chemical vapor deposition (RF-PECVD)

- Microwave plasma-enhanced chemical vapor deposition (MW-PECVD)

- Inductively coupled plasma-enhanced Chemical Vapour Deposition (IC-PECVD)

- Direct current plasma-enhanced chemical vapor deposition system (DC-PECVD)

Input power increases the electric field strength of the plasma sheath, causing highly energetic ion bombardments. In PECVD, the ion strikes the electrode and can cause a powerful ionization in the locality of the electrodes. The electric field then accelerates secondary electrons produced into the plasma sheath. This intense plasma causes nanotubes to be damaged. The plasma significantly influences CNT synthesis and ion bombardment of the substrate should be minimized. Luo *et al.* [37] investigated the

ion-bombardment effects and produced high-quality VACNTs using capacitively coupled PECVD by increasing the plasma parameters like input power and pressure.

In PECVD, plasma speeds up the chemical vapor deposition procedure and encourages CNT development. The plasma energy, which is commonly produced by radiofrequency or microwave excitation, is used to split precursor gases apart and produce the reactive species required for the formation of CNTs.

Figure 1.4 displays the schematic representation of the MW-PECVD system. A high frequency of up to 2.45 GHz generates plasma for MW-PECVD. The highly energetic electrons created by this high-density plasma speed up the dissociation of the gaseous species. The process produces hydrogen radicals by dissociating atomic hydrogen, which aids in the efficiently etching of amorphous carbon species and encourages the formation of CNT [38]. The plasma must be produced at high MW power and low pressures, or else the plasma will become unstable. In addition to creating bamboo-like nanotubes deposited using a MW-PECVD system, Srivastava et al. [39] also investigated the impact of gas compositions on the development and morphology of CNTs. It was thought that the composition of the gaseous plasma may regulate the growth of CNTs.

#### **1.7.1.1 ADVANTAGES OF PECVD TECHNIQUE**

Compared to other techniques, PECVD technique has several benefits for the manufacturing of CNTs.

- Scalability: PECVD is a highly scalable process, making it appropriate for the industrial-scale synthesis of CNT. By making deposition on bigger substrates, the synthesis of CNTs can be done for a bigger volume.

- **Precision Control of Growth Parameters:** With the help of Plasma Parameters, PECVD offers fine control over the growth of resultant CNTs. Plasma parameters can control the physical dimensions of CNT, which in turn affect the electrical and thermal conductivity of the material. PECVD offers the highest flexibility in resultant CNT properties, among other synthesis options.

- Accelerated development rates: Compared to traditional thermal CVD techniques, the plasma adds more energy to the development process, accelerating the growth of CNTs. Along with the scalability advantages, PECVD is a quick method of producing CNTs.

- Low Growth Temperatures: PECVD can produce CNTs at lower temperatures than conventional CVD techniques, which is useful for sensitive substrates. Additionally, this lower growing temperature improves synthesis control and lowers the chance of substrate breakdown.

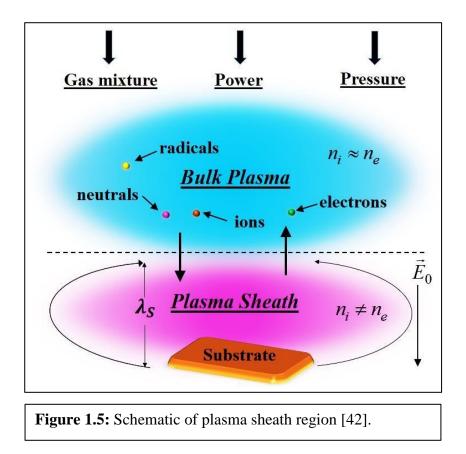

#### 1.8 PLASMA AND PLASMA SHEATH

Apart from solids, liquids, and gas, plasma is one of our universe's naturally occurring forms of matter. The state of matter is determined by the thermal energy of the atoms and molecules and the interparticle binding energy. The particle's binding energy is highest in solids, lowest in liquids, and almost non-existent in gases. When solids are heated, the thermal energy of their constituent particles outweighs their potential energy, causing bonds to dissolve and a solid-to-liquid phase change. Similarly to this, a liquid turns into gaseous form when heated. The atomic species of the gas develop very high thermal energy and collision with one another at very high temperatures (10,000 <sup>O</sup>K or over), which releases electrons from the atoms. The resulting state, often called plasma or ionized gas, compromises of electrons, ions, neutrals, and other

radical species. Although not all ionized gases may be considered plasma, they must meet specific requirements known as quasineutrality and collective behaviour [41] to be classified. When the ion number density and electron number density are in equilibrium in plasma with a length greater than the Debye length, the condition of quasineutrality is met. The Debye length, which is correlated with the electron density (n<sub>eo</sub>) and temperature (T), is the characteristic length over which the potential caused by a charge within plasma may be shielded.

If a substrate exists in a PECVD reactor, this quasineutrality occurs everywhere except at the boundary or wall. The plasma is in a high-energy state but is neutral since it is created by heating the gas or using electrical energy. Due to quasineutrality, no spacecharge zone forms within the bulk of the plasma. Due to higher temperature and lower mass than ions, electrons are far more mobile and have larger fluxes in plasma. The density of positively charged ions in the plasma sheath is marginally more than that of electron density. Figure 1.5 shows the region of the plasma sheath.

Creating this plasma sheath is essential for the PECVD technique of synthesizing nanostructures because the substrate or surface of the material also interacts with the plasma. In addition, nanostructures also develop in this plasma sheath area.

#### **1.9 MOSFET SCALING AND MOORE'S LAW**

Over the past few decades, there have been notable and game-changing breakthroughs in electronics, resulting in the creation of smaller, faster, and more effective electronic devices. The transistor size reduction has been a great triumph for the semiconductor industry. Faster, more potent, and more energy-saving electronic devices have been created as a result. The number of transistors per chip doubles every two years, according to Moore's Law, which explains why this is the case [43-45].

Traditional Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs), however, suffer considerable difficulties that prevent further scaling as transistor dimensions continue to decrease. The conventional MOSFET device is getting dangerously close to its scaling limitations. There are significant problems, such as Short-Channel Effects (SCEs), that need to be addressed [46]. Because of these SCEs, the subthreshold swing (SS) goes over the basic limit of MOSFETs, which is 60 mV/decade, and as a result, the leakage current goes up. In order to bring the supply voltage of the MOSFET down to a more manageable level, the threshold voltage must be lowered. The non-scalability of SS, on the other hand, causes a greater threshold voltage, and as a result, the leakage current increases at an exponential rate. It causes problems with the supply voltage scaling, consequently resulting in higher power consumption. Researchers worldwide have developed innovative ideas for materials and device engineering approaches to solve these problems [47-50].

### 1.10 INTRODUCTION TO CARBON NANOTUBE FIELD EFFECT TRANSISTORS (CNTFETs)

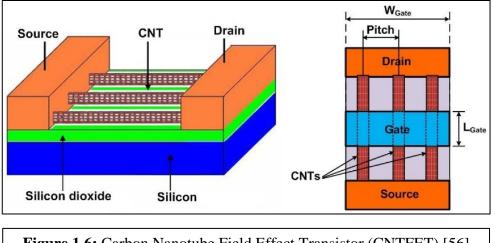

Advancements in transistor technology have paved the way for modern electronics. The performance and scalability of conventional silicon-based transistors is constrained by the increasing need for smaller, quicker, and more energy-efficient devices. In order to support the continued development of the semiconductor industry as conventional silicon-based transistors approach their physical limits, researchers and engineers have been looking into alternate materials and device topologies [51-52]. As a potential answer to the scaling problems facing the semiconductor industry, Carbon Nanotube Field-Effect Transistors (CNTFETs) have come to light. Immense research efforts are being poured into CNTFETs ever since their discovery for the development of next-generation devices for nanoelectronics [53-54]. A schematic diagram for CNTFET is shown in Figure 1.6.

In conclusion, CNTFET technology is of utmost importance to the electronics industry. It is a very attractive contender for the next generation of electronic devices due to its enhanced performance, capacity for scaling, adaptability, and suitability for beyond-CMOS applications [55]. Further research and development are required to overcome the unanswered questions and open the way for sophisticated, high-performance electronic systems.

Figure 1.6: Carbon Nanotube Field Effect Transistor (CNTFET) [56]

CNTs have extraordinary electrical characteristics. They show ballistic transport, which enables electrons to pass through the CNTs without scattering, and they have high carrier mobilities, which allow electrons to move quickly across the channels [57]. CNTFETs are intriguing for high-performance and low-power electronics because of their distinctive properties.

The adaptability of CNTFETs is another significant quality. They may be configured in various transistor topologies, including single-gate and multi-gate designs. They provide circuit designers additional options when designing circuits and facilitating integration into other electronic systems. Due to their adaptability, CNTFETs are suitable for various applications, including sensors, communication systems, memory devices, and logic circuits.

#### **1.11 OVERVIEW AND SIGNIFICANCE OF CNTFET TECHNOLOGY**

A CNTFET, as the name suggests, is a type of Field Effect Transistors (FET) that uses a CNT or arrays of CNTs in place of bulk silicon for the channel material. Source and drain electrodes are attached to it, and a gate electrode that is isolated from the CNT channel by an insulating layer regulates the current flow by altering the charge carriers in the CNT channel. The importance of CNTFETs is seen in their exceptional electrical characteristics. High carrier mobility provides for quick electron transit inside the CNT channels. Additionally, they have ballistic transport, which reduces energy waste and improves the device's functionality [54]. CNTFETs can flip between the ON and OFF states with low gate voltages, so they can function at low power levels and use relatively less power overall.

The control of electron transport through a carbon nanotube (CNT) channel by a gate voltage is crucial to the functioning of a CNTFET. The CNTFET can alternate between various operational modes by changing the gate voltage. The electrostatic potential prevents the flow of electrons from the source to the drain in the OFF state when the gate voltage is below a threshold value. The minimal gate voltage necessary to allow electron passage through the channel is known as the threshold voltage. As a result, the CNT channel experiences a high resistance condition, and barely any current flows through it. When the gate voltage is higher than the threshold in the ON state, the electrostatic potential inverts, letting the electrons pass through the CNT channel. As a result, a low resistance path is created, allowing a sizeable current to pass from the source to the drain. By regulating the gate voltage, the CNTFET can control the current flow through the channel. This characteristic leads to precise output control and easier implementation in amplifiers and logic circuits.

#### **1.12 MULTI-GATE MOSFETs**

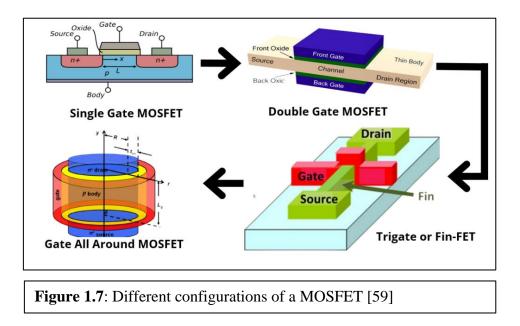

Multi-gate MOSFETs are proposed to mitigate the SCEs through improved electrostatic control over the channel region [58]. The multi-gate structure provides better channel electrostatic control, enhancing device performance. Figure 1.7 shows the different architectures of a MOSFET.

#### **1.13 TYPES OF CNTFET**

Depending on the structure and arrangement of the CNTs deployed, various CNTFETs exist. Each kind offers benefits and unique performance traits. To fully utilize the potential of these distinct CNTFET types in various applications, researchers are continually investigating and optimizing them.

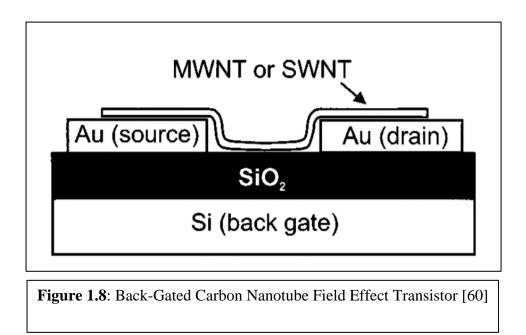

#### **1.13.1 BACK-GATED CNTFET**

One of the earliest synthesized designs of CNTFET is the back-gated CNTFET, also referred to as a bottom-gated CNTFET, as shown in Figure 1.8. It features a gate electrode positioned on the substrate's reverse side, across from the area where the CNTs are forming the channel. The semiconducting CNT is deposited in between two metal strips over the substrate. These metal strips act as a source and drain. To regulate the conductivity of the channel, the gate voltage is delivered via the substrate. Back-

gated CNTFETs are relatively easy to fabricate and effectively control the resultant transistor's electrical properties. However, the resultant transistors have problems of their own. Due to inadequate contact between the gate dielectric and CNT, turning the devices ON and OFF at low voltages is difficult. Additionally, a Schottky barrier arises at the metal-semiconductor interface due to the semiconducting properties of CNT, raising the contact resistance.

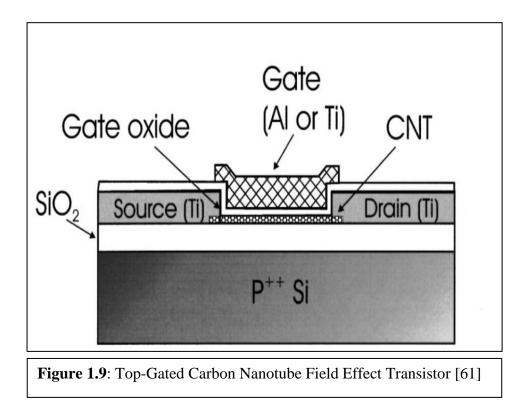

#### **1.13.2 TOP-GATED CNTFET**

In Top-Gated CNTFETs, also known as front-gated CNTFETs, the gate electrode is positioned on the top surface of the channel, as observed in Figure 1.9. The CNT channel is first deposited to a SiO<sub>2</sub> substrate. After that, high-resolution electron beam lithography is used to define and design the source and drain connections. The top-gate dielectric is subsequently applied to the nanotube by Atomic Layer Deposition (ALD) or evaporation. The process is completed by depositing the top gate contact on the gate dielectric.

Unlike back-gated CNTFET, the CNT channel in this configuration is immediately exposed to the gate voltage, with only a dielectric layer separating them. Compared with back-gated CNTFETs, it offers increased gate control and decreased contact resistance, thus improving device performance and reducing power consumption. It is also possible to create arrays of top-gated CNTFETs on the same wafer using this configuration. However, manufacturing top-gated CNTFETs is difficult since it requires precise alignment between the gate and the channel.

#### **1.13.3 SUSPENDED CNTFET**

In a suspended CNTFET, a CNT channel is suspended between two electrodes, which function as source and drain. The suspended arrangement reduces the impact of substrate-induced effects and improves electrostatic control over the channel. They offer improved electrical properties, such as decreased parasitic capacitance and increased carrier mobility, opening the doors for high-frequency applications.

#### 1.13.4 GATE-ALL-AROUND (GAA) CNTFET

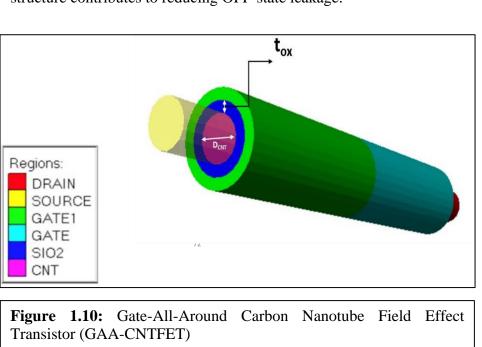

Gate-All-Around CNTFETs have attracted much interest lately due to their superior performance. The gate electrode wraps around the CNT channel in GAA CNTFETs, improving electrostatic control and minimizing SCEs [62]. This arrangement offers increased subthreshold swing, decreased leakage currents, and improved gate efficiency - all essential for producing high-performance transistor devices [62-64].

GAA CNTFETs are considered strong candidates for deploying advanced nanoscale technology.

#### 1.14 WHY GATE-ALL-AROUND (GAA) CNTFET?