## Impact of Variation in High-k Dielectric on Analog and Switching Performance of JL-GAA-SiNWFET

A DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE AWARD OF THE DEGREE

OF

MASTER OF SCIENCE

IN

PHYSICS

Submitted by:

**Kailash Chandra** (2K21/MSCPHY/24)

Grace L Haokip (2K21/MSCPHY/57)

Under the supervision of

#### PROF. RISHU CHAUJAR

#### DEPARTMENT OF APPLIED PHYSICS

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042 MAY, 2023

## **CANDIDATE'S DECLARATION**

We, Kailash Chandra (2K21/MSCPHY/24) and Grace L Haokip (2K21/MSCPHY/57), students MSc(Physics), hereby declare that the project Dissertation titled "Impact of Variation in High-k Dielectric on Analog and Switching Performance of JL-GAA-SiNWFET" which is submitted by us to the Department of Applied Physics, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Science is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship, or other similar title or recognition.

#### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

### CERTIFICATE

I, hereby certify that the project dissertation titled "Impact of Variation in High-K Dielectric on Analog and Switching Performance of JL-GAA-SiNWFET", submitted by Kailash Chandra (2K21/MSCPHY/24) and Grace L Haokip (2K21/MSCPHY/57) to the Department of Applied Physics, Delhi Technological University in partial fulfillment of the requirement for the award of the degree of Master of Science in Applied Physics, is a record of the project work carried out by the student under my supervision. This work has not been submitted partially or completely during any degree or diploma to this university or anywhere else, to the best of my knowledge.

Place: Delhi Prof. Rishu Chaujar

Date: May 2023 Supervisor

## PLAGIARISM REPORT

WORD COUNT CHARACTER COUNT

10779 Words 64802 Characters

PAGE COUNT FILE SIZE

40 Pages 1.8MB

SUBMISSION DATE REPORT DATE

May 29, 2023 2:44 AM GMT+5:30 May 29, 2023 2:43 AM GMT+5:30

## 5% Overall Similarity

The combined total of all matches, including overlapping sources, for each database.

2% Internet database · 2% Publications database

· Crossref database

· Crossref Posted Content database

· 3% Submitted Works database

## Excluded from Similarity Report

· Bibliographic material

· Cited material

Quoted material

Small Matches (Less then 10 words)

# 5% Overall Similarity Top sources found in the following databases: 2% Internet database · 2% Publications database · Crossref database · Crossref Posted Content database · 3% Submitted Works database TOP SOURCES The sources with the highest number of matches within the submission. Overlapping sources will not be repository.ntu.edu.sg <1% Internet Universiti Putra Malaysia on 2013-01-02 <1% Submitted works SASTRA University on 2022-07-05 <1% Submitted works no.overleaf.com <1% Internet Naser Fakhri, Mohammad Salay Naderi, Saeid Gholami Farkoush, Sana... Crossref dspace.unimap.edu.my <1% Internet Schmeiszer, D.. "Silicate formation at the interface of Hf-oxide as a hig... <1% Crossref Visvesvaraya Technological University, Belagavi on 2023-04-16 <1% Submitted works

| Internet Internet                                                                   | < |

|-------------------------------------------------------------------------------------|---|

| Middlesbrough College on 2020-03-26 Submitted works                                 | < |

| University of Cincinnati on 2022-11-04 Submitted works                              | < |

| University of Southampton on 2017-12-16 Submitted works                             | < |

| American University of the Middle East on 2021-05-02 Submitted works                | < |

| University of Leeds on 2009-12-02<br>Submitted works                                | < |

| B. Karthikeyan, M. Sakthiprakash, S. Sanjayrahul, V. Shivaprasad, N. Su<br>Crossref | < |

| Panjab University on 2014-01-23 Submitted works                                     | < |

| shodhgangotri.inflibnet.ac.in                                                       | < |

| De Montfort University on 2022-10-02<br>Submitted works                             | < |

| Mathieu Luisier, Olaf Schenk. "Gate-Stack Engineering in \$n\$-Type Ultr Crossref   | < |

| Rishu Chaujar, Mekonnen Getnet Yirak. "Sensitivity Investigation of Ju  Crossref    | < |

|                   | nal Institute of Technology, Silchar on 2022-05-07     | <1  |

|-------------------|--------------------------------------------------------|-----|

|                   | nam College of Further Education, London on 2023-04-26 | <1  |

|                   | acola State College on 2022-04-02                      | <1  |

| doku<br>Interne   | men.pub                                                | <1  |

| dspace<br>Interne | ce.lboro.ac.uk                                         | <1  |

| medi              | um.com                                                 | <1' |

## **ACKNOWLEDGEMENT**

We would like to express our sincere gratitude and deepest sense of regard to our supervisor, Prof. Rishu Chaujar, Department of Applied Physics, Delhi Technological University for providing his incessant expertise, inspiration, encouragement, suggestions, and the opportunity to work under his guidance. I am grateful for the constant help provided at every step of this project by all the lab members (Ph.D. scholars). We are also thankful to our family and colleagues for their invaluable support, care, and patience during this project. Lastly, I would thank Microelectronics Research Laboratory, Delhi Technological University for providing such a wonderful opportunity of working on this project.

| Place: Delhi |      | Kailash Chandra (2K21/MSCPHY/24) |

|--------------|------|----------------------------------|

| Date:        | 2023 | Grace L Haokip (2K21/MSCPHY/57)  |

#### **ABSTRACT**

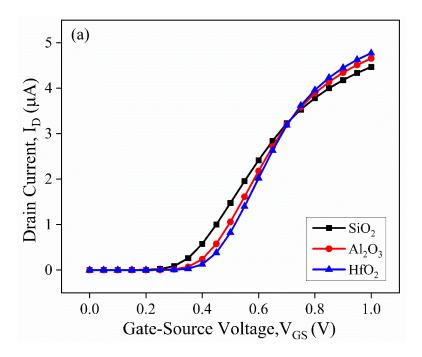

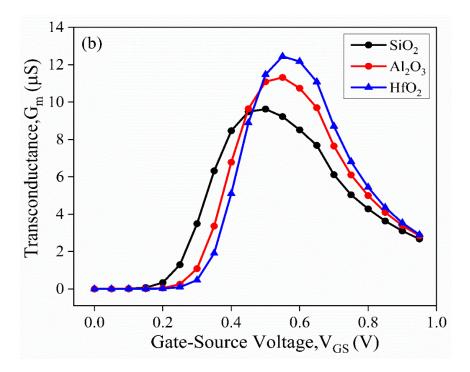

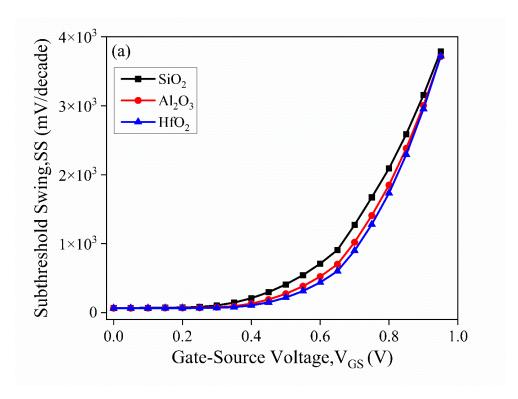

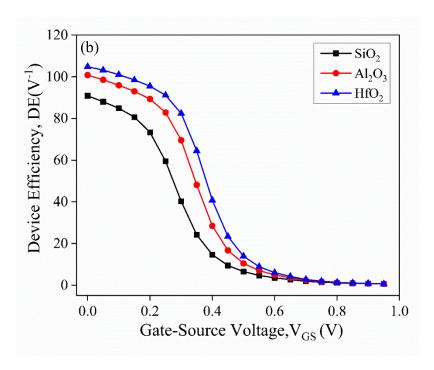

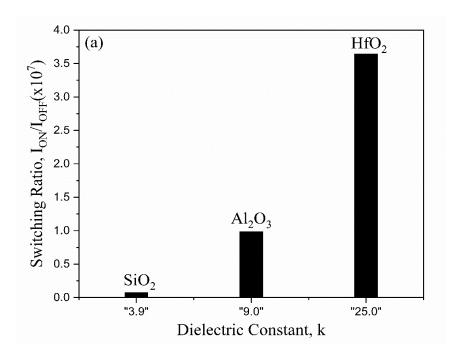

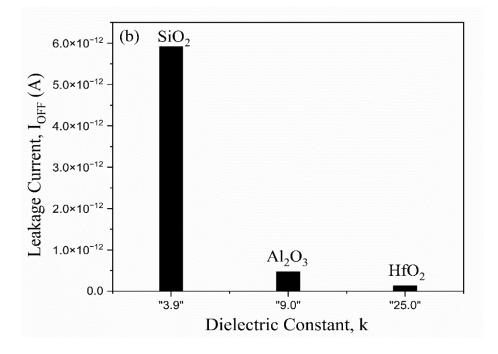

This paper examines how changing dielectric material in gate stack JL-GAA-SiNWFET device affects the analog performance. A comprehensive analysis has been carried out using the ATLAS-3D TCAD device simulator at low drain bias voltage (0.1V) and niobium as a gate electrode having a work function of 4.8eV. The study focuses on the impact of SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and HfO<sub>2</sub> dielectric materials on the analog parameters of the proposed device. The device analog characteristics such as I<sub>D</sub>-V<sub>G</sub>, transconductance (G<sub>M</sub>), subthreshold swing, device efficiency, switching ratio, and leakage current have been examined. The results show that HfO<sub>2</sub> performed best with 28.6%, 15.5%, and 48 times increase in respective transconductance, device efficiency, and switching ratio, and 6.4%, and 95.8% decrement in subthreshold swing and leakage current respectively than SiO<sub>2</sub>. This device uses interface oxide (SiO<sub>2</sub>) and dielectric oxide which is being varied, at the gate to prevent electron tunneling. These findings could be useful in the development of high-performance analog circuits for various applications, including sensor technologies and low-power electronics.

**Keywords**: Gate-all-around (GAA), Silicon nanowire field-effect transistors (SiNWFET)

# **CONTENTS**

| Candidate's Declaration                                                      | i    |

|------------------------------------------------------------------------------|------|

| Certificate                                                                  | ii   |

| Acknowledgment                                                               | vii  |

| Abstract                                                                     | viii |

| Contents                                                                     | ix-x |

| List of Tables                                                               | X    |

| List of Figures                                                              | xi   |

| List of Symbols and Abbreviations                                            | ivx  |

| Chapter 1: Introduction and Literature Review                                | 1    |

| 1.1 Introduction                                                             | 1    |

| 1.2 CMOS Technology: Developments and Challenges                             | 7    |

| 1.3 History of Transistor                                                    | 11   |

| 1.4Metal-oxide-semiconductor field effect transistor (MOSFET)                | 12   |

| 1.4.1 MOSFET operation                                                       | 14   |

| 1.4.2 Enhancement mode                                                       | 16   |

| 1.4.3 Depletion mode                                                         | 16   |

| 1.5 Disadvantages and limitations of conventional MOSFET                     | 17   |

| 1.5.1 Short channel effect                                                   | 17   |

| 1.5.2 Velocity saturation                                                    | 17   |

| 1.5.4 Surface scattering                                                     | 18   |

| 1.5.5 Hot carrier effects                                                    | 18   |

| 1.6 Gate All Around (GAA)                                                    | 19   |

| 1.6.1 Gate All-Around Field-Effect Transistors (GAA-FETs)                    | 20   |

| 1.6.2 Gate-All-Around Silicon Nanowire Field-Effect Transistor (GAA-SiNWFET) | 21   |

| 1.7 The Rationale for Selecting Silicon Nanowire                                                                                                         | 22        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1.8 Objective of the Research Work                                                                                                                       | 23        |

| Chapter 2: Device Structure and Simulation in Atlas Silvaco -3D                                                                                          | 24        |

| 2.1 ATLAS SILVACO-3D                                                                                                                                     | 24        |

| 2.2 Device Structure                                                                                                                                     | 25        |

| 2.2 Methodology                                                                                                                                          | 27        |

| Chapter 3 Result and Discussion                                                                                                                          | 28        |

| 3.1 Comparative Analysis of $I_D\text{-}V_G$ in JL-GAA-SiNWFET for Improved Performance                                                                  | 28        |

| 3.2 Comparative Analysis of Transconductance in JL-GAA-SiNWFET with Different Dielectric Materials                                                       | 30        |

| 3.3 Comparative Analysis of Subthreshold Swing in JL-GAA-SiNWFET with Different Ga<br>Materials                                                          | ate<br>31 |

| 3.4 Comparative Analysis of Device Efficiency in JL-GAA-SiNWFET with Different Gate Materials                                                            | 33        |

| 3.5 Comparative Analysis of Different Dielectric Materials in JL-GAA-SiNWFET with Different Gate Materials for Switching Performance and Leakage Current | 34        |

| Conclusion                                                                                                                                               | 36        |

| References                                                                                                                                               | 37        |

|                    |                      | LIST             | F TABLES  | •     |  |

|--------------------|----------------------|------------------|-----------|-------|--|

| <b>Table 2.1</b> 7 | Technology parame    | eters            |           | ••••• |  |

| Table 3.1 S        | Simulation results o | concerning all-d | ielectric |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

|                    |                      |                  |           |       |  |

## LIST OF FIGURES

- Figure 1.1- Intel's Microprocessor transistor count

- **Figure 1.2** Types of gates

- **Figure 1.3** N-MOS structure

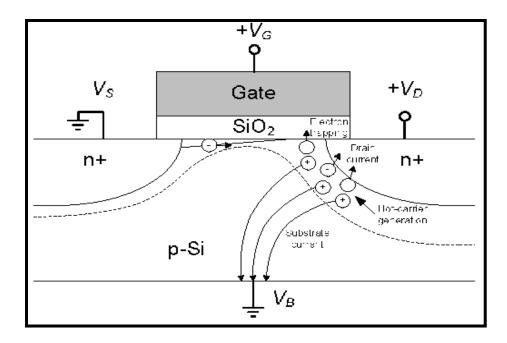

- **Figure 1.4** Basic structure of an n-channel MOSFET with electrons removed from the Si/SiO 2 interface due to the quantum-confinement effect

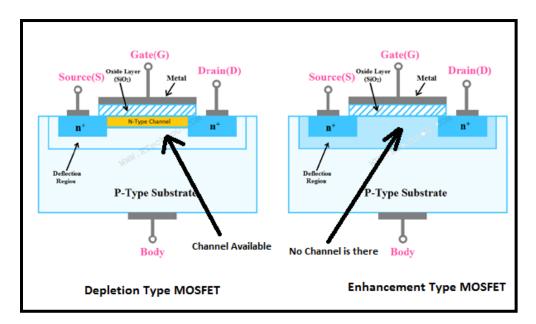

- **Figure 1.5** Types of MOSFET

- **Figure 1.6** Representation of Hot Carriers Effect

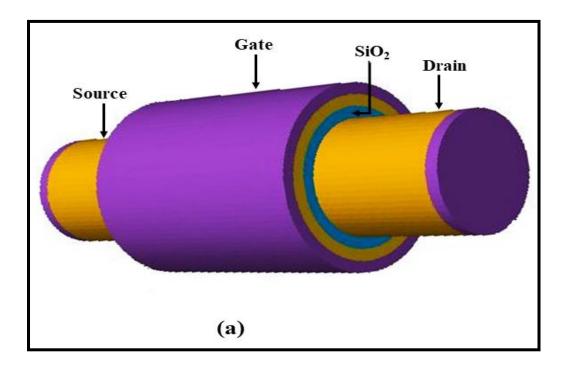

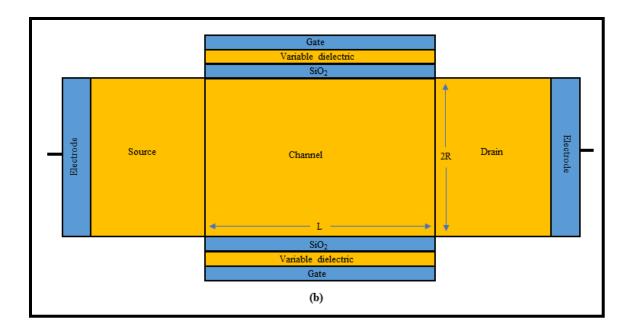

- **Figure 2.1** Junctionless gate all around silicon nanowire FET (a) JL-GAA-SiNWFET (b) cross-sectional view

- Figure 3.1 Transfer characteristics of drain current vs gate voltage at  $V_D$ = 0.1 V for JL-GAA-SiNWFET

- **Figure 3.2** The transconductance vs gate voltage graph for JL-GAA-SiNWFET at  $V_D$ =0.1V and channel length 20nm

- Figure 3.3 The subthreshold swing vs gate voltage graph for JL-GAA-SiNWFET at V<sub>D</sub>=0.1V.

- **Figure 3.4** The device efficiency vs gate voltage graph for JL-GAA-SiNWFET at V<sub>D</sub>=0.1V.

- Figure 3.5 The switching ratio vs dielectric material graph for JL-GAA-SiNWFET at  $V_D=0.1V$

- Figure 3.5 The leakage current vs dielectric material graph for JL-GAA-SiNWFET at  $V_D \!\!=\!\! 0.1 V$

# LIST OF SYMBOLS AND ABBREVIATIONS

| Symbol/Index     | Meaning/Abbreviation                                                   |  |  |  |

|------------------|------------------------------------------------------------------------|--|--|--|

| JL-GAA-SiNWFET   | Junction-less Gate All Around Silicon Nanowire Field Effect Transistor |  |  |  |

| MOSFET           | Metal Oxide Semiconductor Transistor                                   |  |  |  |

| POC              | Point of Care                                                          |  |  |  |

| CNT              | Carbon Nanotube                                                        |  |  |  |

| CMOS             | Complementary Metal Oxide Semiconductor                                |  |  |  |

| ЕОТ              | Equivalent Oxide Thickness                                             |  |  |  |

| ICs              | Integrated Circuits                                                    |  |  |  |

| ITRS             | International Technology Roadmap for Semiconductors                    |  |  |  |

| QLC              | Quad Level Cell                                                        |  |  |  |

| FTIR             | Fourier Transform Infrared Analysis                                    |  |  |  |

| SiO(N)           | Silicon Dioxide or Silicon Oxynitride                                  |  |  |  |

| CNTFETs          | Carbon Nanotube Field-Effect Transistors                               |  |  |  |

| $C_{\mathrm{g}}$ | Capacitance                                                            |  |  |  |

| DRAM             | Dynamic Random Access Memory                                           |  |  |  |

| SCEs             | Short Channel Effects                                                  |  |  |  |

| EDA              | Electronic Design Automation                                           |  |  |  |

| SRH              | Shockley-Read-Hall                                                     |  |  |  |

| $V_{\mathrm{D}}$ | Drain Voltage                                                          |  |  |  |

| ВЈТ              | Bipolar Junction Transistor                                            |  |  |  |

## **CHAPTER 1**

#### INTRODUCTION AND LITERATURE REVIEW

#### 1.1 Introduction

High dielectric constant gate oxides play a crucial role in metal oxide semiconductor transistors (MOSFETs) as they enable effective control of the transistor's behavior by the gate electrode. The dielectric constant, also referred to as the relative permittivity, plays a crucial role in determining the charge storage capability of the oxide material and influences the gate capacitance of the transistor. By using materials with high dielectric constants, it becomes possible to achieve larger gate capacitance, allowing for improved transistor performance and reduced power consumption.

In the past few years, there has been a growing need for high-performance transistors that consume less power. As a result, researchers have been actively exploring alternative gate oxide materials with higher dielectric constants compared to conventional silicon dioxide (SiO2). These high-k gate dielectrics offer several advantages, including improved transistor scalability, reduced leakage current, enhanced carrier mobility, and increased device reliability. Through the substitution of silicon dioxide (SiO2) with high-k materials like hafnium oxide (HfO2) and aluminum oxide (Al2O3), MOSFETs can overcome the limitations imposed by the thickness scaling of SiO<sub>2</sub> and achieve further miniaturization while maintaining optimal gate control.

The research on high-k gate oxides for metal oxide Si transistors aims to comprehensively investigate and comprehend the properties, fabrication methods, and performance attributes of various high-k materials. Through extensive exploration, scientists aim to gain insights into the influence of high-k gate dielectrics on crucial transistor parameters, including threshold voltage, subthreshold slope, on/off current ratio, and carrier mobility. By examining these factors, researchers seek to enhance the understanding and utilization of high-k materials in transistor design and optimization. Additionally, they analyze the compatibility of these materials with the existing semiconductor fabrication processes, identifying potential challenges and solutions for integrating high-k gate oxides into practical device structures. By gaining insights into the behavior and performance of high-k gate dielectrics, researchers aim to advance the development of next-generation metal oxide semiconductor devices with improved performance metrics, enabling further progress in areas such as integrated circuits, microelectronics, and nanoelectronics.

Over the last ten years, there has been an increasing fascination surrounding the subject of utilizing one-dimensional (1-D) structures such as silicon nanowires (SiNW), nanosheets, and carbon nanotubes (CNT) for point-of-care (POC) biomolecule applications. One of the key advantages of these structures is their ability to achieve high sensitivity, enabling the detection and targeting of biomarkers on surfaces[1]. SiNWs have shown great promise in this field. They possess several desirable characteristics, including compatibility with compact designs, integration into microelectronics, ease of mass fabrication, and the potential for rapid detection. These attributes make SiNWs an attractive choice for POC biomolecule applications. By employing SiNWs in field-effect transistors (FETs), researchers have been able to harness their high sensitivity and leverage their 1-D structure to detect and analyze biomarkers with precision. The FETs constructed using SiNWs exhibit exceptional performance, enabling efficient detection and analysis of biomolecules on surfaces.

The utilization of a high-k dielectric, specifically HfO<sub>2</sub>, in conjunction with SiO<sub>2</sub>, offers significant benefits in terms of improving transistor performance while maintaining control over interface characteristics[2]. One of the main advantages of incorporating a high-k dielectric layer is its higher permittivity or dielectric constant compared to SiO<sub>2</sub>. This high-k dielectric enables the gate oxide layer to be physically thicker while still providing the same level of effective capacitance. This reduction in leakage current is crucial for ensuring the efficient operation of transistors and minimizing power consumption. Additionally, the higher permittivity of the high-k dielectric allows for better gate control over the channel region, enabling enhanced transistor performance in terms of subthreshold swing, threshold voltage, and overall device speed. The interface properties play a crucial role in determining the overall device performance, including carrier mobility, threshold voltage stability, and reliability. The introduction of a high-k dielectric layer can help improve the interface quality, reducing interface trap densities and improving carrier mobility, which ultimately enhances the overall transistor performance. Furthermore, the integration of a high-k dielectric material like HfO<sub>2</sub> with SiO<sub>2</sub> enables better compatibility with modern semiconductor manufacturing processes. It provides a means to overcome the limitations of scaling SiO<sub>2</sub> gate oxides, which face challenges in maintaining desirable thickness and controlling gate leakage current as transistor dimensions continue to shrink. The high-k dielectric acts as a suitable replacement for SiO<sub>2</sub> in advanced CMOS technologies, allowing for continued transistor scaling while achieving improved device performance. Incorporating a high-k dielectric,

such as HfO<sub>2</sub>, on top of SiO<sub>2</sub> offers several advantages in transistor design. It enables improved performance by reducing gate leakage current, enhancing gate control, and optimizing interface characteristics. The utilization of a high-k dielectric layer provides a pathway for achieving higher-performance transistors while addressing the challenges associated with scaling traditional SiO<sub>2</sub> gate oxides.

Enhancing transistor performance and effectively managing interface characteristics are the primary advantages of incorporating a high-k dielectric, such as HfO2, in conjunction with SiO2. Hafnium dioxide (HfO<sub>2</sub>) has emerged as a highly suitable candidate for the gate stack material in the CMOS industry. It offers several advantages that make it a preferred choice for integration with (SiNWs) [1].

HfO2 offers significant advantages in terms of its compatibility with the CMOS fabrication process, making it an attractive choice. It can be efficiently integrated into wafer production, making it a time-efficient option for manufacturing. Additionally, the use of HfO2 in combination with SiNWs does not incur significant additional costs, making it an economically viable solution. The properties of HfO2, such as its high dielectric constant, make it particularly well-suited for gate stack applications. Its high-k value allows for a thinner gate oxide layer, which in turn enables higher electric fields and improved transistor performance. This leads to enhanced control over the gate electrode and improved device characteristics. Moreover, the integration of HfO2 with SiNWs brings additional benefits to the overall system. The combination takes advantage of the unique properties of SiNWs, such as their 1-D structure and high sensitivity, while leveraging the favorable characteristics of HfO2 as the gate stack material. This synergistic integration enhances the performance and functionality of the SiNW-based devices.

When compared to other gate insulator materials, hafnium oxide (HfO2) is a good choice because of its superior interface qualities, high recrystallization temperature, and great thermal stability [3]. Hafnium oxide (HfO2) as a gate insulator material offers several advantages over other alternatives, making it a favorable choice in advanced semiconductor devices. One key advantage is its excellent thermal stability, which refers to its ability to withstand high temperatures during device fabrication processes without undergoing significant structural or chemical changes. This thermal stability is crucial for maintaining the integrity and functionality of the gate insulator layer during various manufacturing steps. Additionally, HfO2 exhibits a high recrystallization

temperature, meaning it can resist crystal structure degradation or phase transformations at elevated temperatures. This property ensures the stability and reliability of the gate insulator material even under harsh operating conditions, preventing performance degradation and enhancing the overall lifespan of the device. Another significant advantage of HfO<sub>2</sub> is its superior interface qualities compared to other gate insulator materials. The interface between the gate insulator and the semiconductor channel region plays a critical role in determining the device's performance. HfO<sub>2</sub> demonstrates good interface quality, which refers to the interaction and compatibility between the gate insulator and the channel material. A high-quality interface reduces interface trap densities and enhances carrier mobility, leading to improved transistor performance in terms of speed, efficiency, and reliability. Furthermore, HfO<sub>2</sub> offers a wide bandgap and high dielectric strength, making it highly suitable for achieving effective dielectric isolation in semiconductor devices. Hafnium-based oxides, known for their wide bandgap, high dielectric strength, and excellent thermal stability, have emerged as favorable options for improved dielectric isolation [3]. The wide bandgap ensures that the gate insulator material has a large energy gap between the valence and conduction bands, resulting in reduced leakage currents and enhanced electrical insulation properties. The high dielectric strength allows HfO<sub>2</sub> to withstand high electric fields without breakdown, ensuring the reliability and longevity of the device. These properties make it a preferred choice in semiconductor technology, enabling the development of highperformance devices with improved reliability and scalability.

The characteristics of the insulator layers that act as a barrier between the semiconductor channel and the metal gate contacts play a crucial role in maintaining good electrostatics within a transistor. The equivalent oxide thickness (EOT), which represents the effective thickness of these insulator layers, is an important parameter to consider.

The continuous drive for low power consumption in integrated circuits (ICs) has led to significant scaling of transistors during the past few decades [5][6]. This scaling refers to the continuous reduction in the size of transistors, leading to increased transistor density on a chip. By scaling down the transistor size, the power consumption of the circuits can be reduced while maintaining or improving their performance.

The scaling of transistors involves reducing their dimensions, such as gate length and channel length, which results in several advantages. Firstly, smaller transistors allow for faster switching

speeds, enabling higher data processing rates in electronic devices. Secondly, the reduced size leads to a decrease in power consumption since smaller transistors require less energy to switch on and off. Moreover, scaling allows for increased transistor density, enabling the integration of more complex circuits on a single chip.

The continuous scaling of transistors has been made possible through advancements in semiconductor manufacturing techniques and the development of new materials. These advancements have allowed for the fabrication of transistors with smaller feature sizes, improved performance, and reduced power consumption. However, as transistors continue to shrink in size, new challenges arise, such as increased leakage currents and decreased control over device characteristics. These challenges necessitate the exploration of innovative design approaches and materials to maintain or enhance transistor performance while minimizing power consumption. This scaling has been essential in achieving faster switching speeds, higher transistor density, and improved performance. However, it has also presented new challenges that require ongoing research and development efforts to address.

[4], [5]. As devices are scaled down to sizes in the range of tens of nanometers, certain undesirable effects start to emerge in the electrical characteristics of these devices [3], [6]– [14]. One consequence is the threshold voltage roll-off, whereby as a device's dimensions decrease, the threshold voltage—the minimum voltage needed to activate a transistor—becomes less welldefined. This may lead to fluctuations in device performance and make it challenging to provide precise control over the switching behavior of the transistor. Drain-induced barrier lowering (DIBL), another effect, is the lowering of the energy barrier between a transistor's source and drain regions as a result of the drain voltage being applied. DIBL can lead to leakage currents and subthreshold conduction, affecting the overall performance and power efficiency of the device. Furthermore, as device sizes decrease, the leakage current through the transistor can increase. Leakage currents are unintended currents that flow through the device even when it is supposed to be in the off state. Increased leakage currents contribute to power dissipation and can limit the overall energy efficiency of the device. A shallower sub-threshold slope makes it more challenging to control the device accurately and can impact its performance and power consumption. In conclusion, scaling has both positive and negative consequences on electronic devices. While scaling improves power consumption, speed, functionality, cost per device, and chip density, it also lowers the cost per device. These impacts, which can affect the electrical properties and functionality of scaled-down devices, include threshold voltage roll-off, DIBL, rising leakage current, and sub-threshold slope deterioration. It is crucial to address these issues through innovative design approaches and materials to mitigate their negative impact and further enhance the performance and efficiency of scaled devices.

According to (ITRS), as the transistor length of the gate decreases to 5 nm, the EOT of the insulator layers should be scaled down to 0.5 nm. This reduction in EOT is particularly advantageous for ultrashort nanodevices in both their OFF and ON states. By achieving such tiny EOTs, improvements in gate electrostatic control are anticipated. This improvement allows for a lower subthreshold slope (SS) in the range of 80-90 mV/decade. Additionally, the increase in gate capacitance (Cg) resulting from the reduction in EOT leads to an increase in the inverse charge densities in the channel. This, in turn, leads to higher driving currents within the transistor. The increased driving currents contribute to improved performance and functionality of the transistor. These findings, as referenced in sources [15] and [16], emphasize the importance of optimizing the characteristics of insulator layers, particularly their EOT, for achieving better electrostatic control, lower subthreshold slope, and increased driving currents in nanodevices.

Band-to-band tunneling is a phenomenon that plays a significant role in influencing the performance of carbon nanotube field-effect transistors (CNTFETs), particularly when they are operated at low drain voltages. This unique form of tunneling involves the direct transfer of charge carriers across the energy bandgap of the semiconductor material, enabling current flow even in the absence of a traditional source-drain voltage difference. In the context of CNTFETs, the occurrence of band-to-band tunneling introduces new considerations and challenges to the device characteristics that are typically observed in conventional (FET). The impact of band-to-band tunneling on CNTFETs manifests in various aspects of device performance. Firstly, it alters the overall current-voltage characteristics of the transistor, deviating from the typical behavior observed in devices operating under conventional transport mechanisms. This can result in non-ideal subthreshold slopes, increased leakage current, and modified switching behavior. Furthermore, the presence of band-to-band tunneling introduces additional complexities in terms of device modeling and circuit design, requiring specialized techniques to accurately capture and simulate the behavior of these devices. Operating CNTFETs at low drain voltages exacerbates the

influence of band-to-band tunneling on device performance. At these voltage regimes, the contribution of tunneling currents becomes more pronounced, and their effects on device operation become more apparent. As a result, conventional device characteristics, which are primarily defined by the operation under higher voltage regimes, may not hold for CNTFETs when they are subjected to low drain voltages. The understanding of the impact of band-to-band tunneling in CNTFETs is crucial for optimizing their performance and advancing their applications. Researchers and engineers in the field strive to develop novel device architectures, material engineering strategies, and circuit design techniques that can mitigate the undesirable effects of tunneling currents and enhance the overall performance of CNTFETs. By addressing these challenges, it becomes possible to harness the unique properties of carbon nanotubes and leverage their potential for future nanoelectronics devices and technologies. The band-to-band tunneling significantly impacts the performance of carbon nanotube field-effect transistors (CNTFETs) when operated at low drain voltages and challenging conventional device characteristics [17].

## 1.2 CMOS Technology: Developments and Challenges

The law that Gordon E. Moore developed in 1965 asserts that the number of transistors we put on an IC or silicon chip doubles roughly every two years. Moore's Law is the name given to this observation [1]. Due to their potential for high performance and precise control over device current, silicon nanowire transistors have drawn interest. In CMOS technology, scaling the gate insulator has been found to improve transistor performance along with other device metrics. This strategy is in line with Moore's Law, which states that the number of transistors on an integrated circuit (IC) device will double every 18 months while power consumption decreases. The implementation of high-k and metal materials has been recognized as a significant advancement in transistor technology, allowing increased transistor density, enhanced device performance, and improved circuit functionality without escalating production costs. However, the reduction in silicon dioxide gate dielectric thickness approaches its physical limit as feature sizes decrease below 45 nm, leading to large gate leakage currents through direct tunneling. [18].

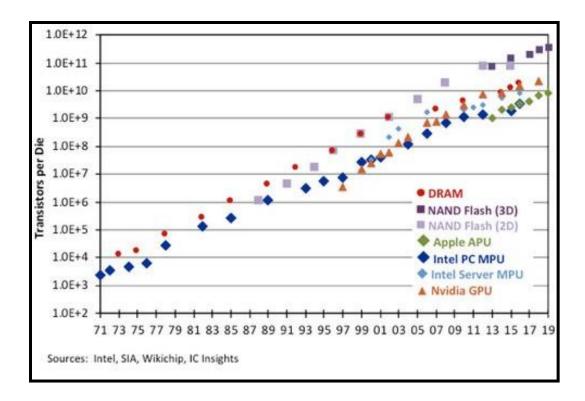

According to the data presented in the figure, the growth rates of transistor count in various integrated circuit (IC) products have exhibited notable trends over the past 10-15 years.

Figure 1.1 Intel's Microprocessor transistor count[19]

For instance, the transistor counts in dynamic random-access memory (DRAM) experienced a rapid increase, with an average growth rate of approximately 45% per year until the early 2000s. However, this growth rate subsequently decreased to around 20% through the emergence of the 16-gigabit (16 GB) generation in 2016 [20]. It is anticipated that the combination of QLC technology and advancements in 96-layer fabrication will enable 3D NAND to achieve a density of 1.5 TB in 2020. Furthermore, the introduction of 128-layer technology is expected to pave the way to produce 2-terabit (2Tb) chips. These observations indicate the continuous progression in transistor counts and memory densities within the semiconductor industry. Advancements in technology have allowed for significant increases in memory capacity, enabling the development of more powerful and higher-density IC products. Transistor counts in Intel's PC microprocessors increased by about 40% annually until 2010, but the rate then decreased to 50%. The mid-to late-2000s saw a brief lull in the increase of transistor counts for the company's server microprocessors (MPUs). However, it resumed an upward trajectory thereafter, with an average annual growth rate of approximately 25%. It is worth noting that Intel, the company in focus, ceased disclosing specific details regarding transistor counts starting from the year 2017[21]. Consequently, the

precise transistor count figures for Intel's server MPUs beyond that point are no longer publicly available.

In recent years, there has been significant tremendous research interest in exploring high-N gate dielectrics as potential alternatives to SiO<sub>2</sub> in advanced CMOS technologies. Therefore, an extensive effort has been devoted to investigating the properties and performance of these dielectric materials [22]. The MOSFET, which acts as the basic solid-state element, is a crucial component of modern microprocessors. To create MOS (CMOS), MOSFETs must be classified as either nFETs (which use electrons as the majority carriers) or pFETs (which use holes as the majority carriers). The gate oxide, which is often made of silicon dioxide or silicon oxynitride (SiO(N)), is what drives device performance and scaling. It is located at the center of the MOSFET. The thickness and quality of the gate oxide are of paramount importance in determining the overall performance characteristics of the MOSFET. Significant progress in CMOS technology has spurred the rapid and aggressive scaling of the MOSFET gate stack. This scaling approach aims to achieve higher device density and improved performance. By reducing the dimensions of the MOSFET gate stack, advancements have been made in packing more transistors onto a single chip, leading to increased device density. Additionally, scaling enables enhancements in device performance, such as faster switching speeds and reduced power consumption. The traditional poly-Si/SiO2 gate stack is reaching some practical limits. For example, the gate oxide thickness has stopped decreasing starting at the 90 nm node because the gate leakage current caused by tunneling and oxide breakdown is already quite high at this thickness of 1.2 nm [25]. Afterward, advanced gate stacks involving metal gate materials and a high-k dielectric may be required to overcome these limitations. However, the advanced gate stack's material engineering and process integration face significant difficulties. As a result, over the past 10 years, both academic and industrial research has attracted most of the focus.

The high-k dielectrics have two main benefits over traditional SiO (N) dielectrics because of their increased permittivity. First off, because the high-k dielectrics can be physically grown thicker while maintaining an equivalent oxide thickness (EOT) that is like SiO2, it offers a significant reduction in gate leakage and makes these materials acceptable for low-power applications [26, 27]. Second, high-k dielectrics may be able to achieve EOT values that are substantially lower than those achievable with traditional SiON dielectrics, which may allow for the restoration of transistor

scaling and the usage of lower gate voltages, respectively. The characteristics of the insulator layers which act as a barrier between the semiconductor channel and the metal gate contacts signify a crucial role to maintain excellent electrostatics within a transistor. The equivalent oxide thickness (EOT), which represents the effective thickness of these insulator layers, is an important parameter to consider [[3]. There was a significant global effort made at the beginning of the late 1990s to find a suitable high-k dielectric solution for the integration process into CMOS technology. Even though in 2001–2002 Hf-based high-k materials were the preferred dielectric [23]-[26]. Their launch was delayed by several issues with traditional CMOS techniques. However, thanks to recent advancements in materials and manufacturing techniques, this technology has become a reality as proven by the high-performance 45 nm semiconductor [27]- [30] including low-power 32 nm [28] and the outcomes of high-k/metal gate technology. The semiconductor industry is progressively looking into high-mobility substrates like Ge and III-V materials for CMOS technologies to further improve performance. This interest stems from recent advancements in high-k metal gate technology. By incorporating these high-mobility substrates into CMOS devices, there is a potential to achieve significant improvements in device performance, such as enhanced carrier mobility and faster transistor switching speeds. The utilization of high-k metal gate technology in conjunction with high-mobility substrates presents an exciting opportunity to push the boundaries of CMOS technology and unlock new possibilities for advanced electronic devices.

As technological nodes, gate lengths, and oxide thicknesses have shrunk, Short Channel Effects (SCEs) and gate leakage current have become significant challenges in semiconductor scaling. To address these non-ideal effects and enable continued scaling, the semiconductor industry has introduced various modifications to the traditional Si-based MOSFET structure. One prominent SCE is the Hot Carrier Effect, also known as Impact Ionization, which occurs in n-MOSFETs with shorter channel lengths. The enhanced lateral electric fields in these devices cause carrier electrons to gain higher energy, leading to the generation of electron-hole pairs and potential damage to the gate oxide material. To mitigate this effect, physical separation between the channel and substrate, along with the use of thick high-oxide layers, is employed. Gate Oxide Breakdown is the other concern that is associated with aggressive transistor scaling. As the gate oxide thickness decreases with each transistor generation, electrostatic breakdown becomes more likely, posing a threat to device reliability. The adoption of thick high-gate oxides helps address this issue while maintaining the required gate capacitance for scaling. Additionally, thicker gate oxides reduce gate

leakage current by minimizing Quantum Mechanical tunneling at the channel-oxide interface. These measures contribute to enhancing device performance, reducing non-ideal effects, and ensuring the reliability of scaled transistors. Silicon-based microelectronics devices have permeated almost every area of our daily lives during the past few decades. This has been made possible by repeatedly achieving for the individual MOSFET devices the features of quicker speed, higher density, and lower power. Therefore, for the past forty years, engineers have concentrated on "scaling," which is the reduction in each device size. The scaling behavior has adhered to the well-known Moore's rule, which states that the number of devices on an integrated circuit would double over a 1.5–2-year period. [67].

### 1.3 History of Transistor

Transistors are semiconductor devices with at least three terminals for connecting to electrical circuits. In the normal instance, the third terminal regulates how much current moves between the other two terminals. At Bell Laboratories in Murray Hill, New Jersey, the first transistor was successfully demonstrated on December 23, 1947. The three men that share credit for developing the transistor are William Shockley, John Bardeen, and Walter Brattain. Transistor types include (BJT) and (FET) [51].

The FET, based on the principle proposed by Julius Edgar Lilienfeld in 1925, saw its first working implementation in 1947. Shockley further advanced the technology by introducing the bipolar junction transistor in 1948, leading to its widespread use in the early 1950s and marking a significant milestone in transistor development. Then in 1951, there became a sudden big innovation in the transistor when William Shockley developed a junction transistor. Further with time more growth happened in the sector of transistor developed Planer Transistors. In 1958 Silicon Transistors became a replacement for Germanium as it was getting broken at high temperatures which worked just like a germanium junction transistor. The MOSFET was created in 1959 by Mohamed Atalla and Dawon Kahng at Bell Labs, and it revolutionized the industry. MOSFETs offered improved power efficiency, leading to their mass production and widespread adoption in various applications. These have a N or P-type semiconductor channel that passes via a ridge on top of the other kind. Even though MOSFETs are simpler to manufacture on an integrated circuit or microprocessor than junction transistors, they quickly replaced them as the

favored kind of transistor. Today, the MOSFET stands as the most extensively manufactured device in history, solidifying its pivotal role in modern electronics.

## 1.4 Metal-oxide-semiconductor Field Effect Transistor (MOSFET)

The fundamental MOS transistors featured a metal gate material, silicon dioxide as the insulator, and a semiconductor substrate, giving rise to the name MOS (Metal Oxide Semiconductor) transistor. On the other hand, the name "FET" refers to the process by which an electric field is applied across the gate oxide to turn the gate on and off. In this transistor configuration, two regions are biased at varying potentials, with the lower potential region serving as the source and the higher potential region acting as the drain. The electric field delivered to the gate terminal, which governs the flow of current across the channel between the source and drain regions, is the foundation of the MOSFET's operation. The electric field modifies the conductivity of the channel when a voltage is applied to the gate, allowing the transistor's behavior to be precisely controlled. The use of silicon dioxide as the gate insulator in early MOS transistors provided reliable isolation between the gate and the channel. This enabled efficient switching and low power consumption. As semiconductor technology advanced, new gate dielectric materials with greater dielectric constants known as high-k dielectrics were introduced throughout time. These materials offer improved gate control and reduced leakage current, enabling further performance enhancements in MOSFET's ability to operate at lower power levels compared to other transistor technologies, coupled with its scalability and compatibility with integrated circuit fabrication processes, has made it the most widely manufactured device in history. Overall, the combination of a metal gate, oxide insulator, and semiconductor substrate in the MOSFET architecture, along with its field-effect operation, has paved the way for the advancement and widespread adoption of modern transistor technology. A MOS transistor has four terminals and is categorized as having a drain, gate, source, and body [31]. The integration of high dielectric constant (high-k) materials as gate oxides in metal oxide silicon transistors offers potential improvements in gate capacitance, leakage current reduction, carrier mobility, and overall device performance [32]. Challenges include compatibility with fabrication processes, interface quality, and oxide layer defects. Ongoing research focuses on optimizing high-k gate oxides for reliability, thermal stability, and interface quality. Advancements in integrated circuits and microelectronics have been achieved with high-k gate oxides, driving progress in nanoelectronics and semiconductor technology.

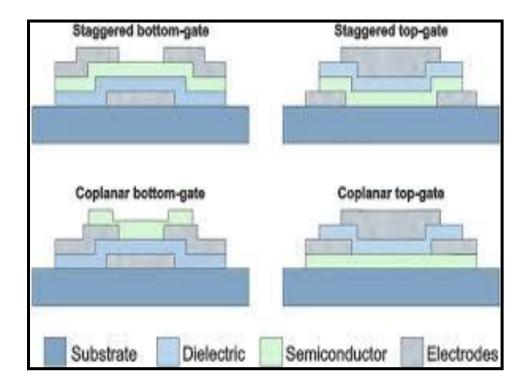

As shown in Figure 1.2, there are four fundamental types of FET structures based on the location of the contact electrodes: coplanar top gate, coplanar bottom gate, and staggered top gate.

Figure 1.2 Types of Gates [33].

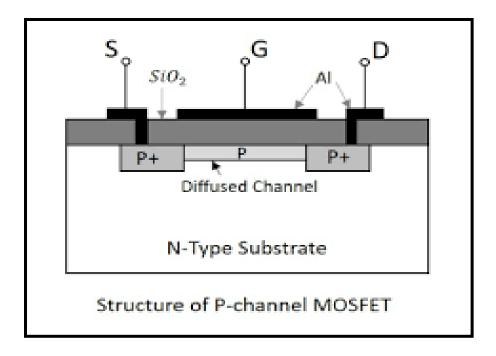

The semiconductor is positioned between the source and drain electrodes in all the configurations, and the dielectric layer is sandwiched between the gate electrode and the semiconducting layer. Figure 1.3 illustrates the design of a MOSFET, a key component in Very Large-Scale Integration (VLI) systems. Researchers in the field are actively focused on reducing the size of transistors to enhance their efficiency. In today's semiconductor and microprocessor industry, there is a growing trend toward employing numerous nano-scaled transistors that offer low power consumption and cost-effective designs. However, scaling down devices to the nanoscale introduces challenges such as Short Channel Effects (SCEs), tunneling effects, and threshold voltage variations, which can hinder efficiency and complicate manufacturing processes. This review article not only addresses the problems and potential solutions related to scaling but also provides a comprehensive analysis of silicon nanowire transistors and other novel nano Field-Effect Transistors (FETs) [34]. By examining these unique nano FETs, this review aims to shed light on the advancements and potential breakthroughs in the field of transistor technology.

Figure 1.3 N-MOS structure [35].

#### 1.4.1 MOSFET Operation

The MOSFET, a type of encapsulated transistor, is produced through controlled oxidation processes, typically using silicon as the semiconductor material. When a voltage is applied, it induces charges on the metal plates, like a parallel plate capacitor, and generates counter charges in the interfacial layer of the semiconductor, as expected and anticipated [36]. This phenomenon is known as the capacitive coupling effect and forms the basis of the operation of a MOSFET. By manipulating the voltage applied to the metal gate, the charges in the semiconductor layer can be modulated, allowing for precise control of the transistor's conductivity. The controlled oxidation process ensures the formation of a thin insulating layer, typically silicon dioxide, between the metal gate and the semiconductor, preventing direct electrical contact. This insulating layer acts as a barrier, enabling the transistor to switch on and off by varying the voltage on the gate terminal. The ability to regulate the direction of current through the transistor makes the MOSFET a vital component in modern electronic devices and integrated circuits, offering high performance, low power consumption, and compact size.

Controlling the voltage and current flow between the sources and drain terminals is the main goal of a MOSFET. It achieves this through the operation of a MOS capacitor, which functions as a

switch. The semiconductor can change from p-type to n-type when a positive or negative gate voltage is applied. It is situated beneath the oxide layer on the semiconductor surface, between the source and drain terminals. The holes beneath the oxide layer are pulled down towards the substrate when a positive gate voltage is supplied because of repelling forces. This causes the creation of a depletion area, which is inhabited with bound negative charges linked to the acceptor atoms and opens the channel for electrons. Additionally, electrons from the n+ source and drain regions are drawn into the channel by the positive voltage. Current can freely flow when there is a voltage placed between the source and drain, and the gate controls the movement of the electrons inside the channel. Instead of a positive voltage, a hole channel forms beneath the oxide layer if a negative voltage is supplied [31]. This alternative configuration allows for the modulation of current flow in a different manner. By manipulating the gate voltage, the MOSFET can effectively switch between different operating modes, enabling precise control over the voltage and current flow between the source and drain terminals. This characteristic makes MOSFETs an essential component in various electronic devices and systems.

Figure 1.3 Basic structure of an n-channel MOSFET with electrons removed from the Si/SiO 2 interface due to the quantum-confinement effect [37].

The primary capability of the MOSFET is to generate and change a conducting layer comprised of minority carriers at the semiconductor—oxide interface [36]. When Vg>0 is applied, holes begin to move away from the common region because a p-type substrate is employed in n-MOS transistors [31]. The depletion layer penetrates the substrate deeper, and electrons begin to inject,

producing a pathway when the gate voltage is increased higher. For an n-type substrate, the channel created by a p-MOS transistor is made up of holes. MOSFETs are classified into two categories based on how they operate [38].

#### 1.4.2 Enhancement mode

In enhancement mode, the absence of a gate voltage results in no conducting channel between the metal regions, rendering the MOSFET in an "off" state. To initiate the conducting channel and activate the MOSFET, a minimum gate voltage, known as the threshold voltage, must be applied. To enable the MOSFET's desired functionality in electronic circuits and devices, this gate voltage induces the development of a conducting channel, allowing current to pass between the source and drain terminals.

#### 1.4.3 Depletion mode

The depletion-mode MOSFET operates differently from the enhancement-mode MOSFET in terms of the presence of a conducting channel. Even without a gate voltage, the depletion-mode MOSFET already possesses a conducting channel (inversion layer).

Figure 1.4 Types of MOSFET [39].

The threshold voltage plays a crucial role in controlling the device's operation, allowing it to be turned off when the applied gate voltage exceeds the threshold voltage. This behavior enables the depletion-mode MOSFET to serve as a switch or amplifier in various electronic applications.

### 1.5 Disadvantages and limitations of conventional MOSFET

Conventional bulk metal-on-silicon (MOS) devices are commonly used in large-scale integrated circuits. However, due to their reduced size, they are not ideal for small-channel applications. Due to the presence of both gate-drain and gate-source overlap, the device's longitudinal field is increased. Short-channel devices offer advantages such as improved processing speed, lower operating potential, and higher transistor density. However, they may also exhibit drawbacks including poor frequency response, limited linearity, and susceptibility to damage from static electricity. These considerations should be considered when designing and utilizing FET-based circuits [40][31].

#### 1.5.1 Short channel effect

The control of electrostatics in MOSFETs varies depending on the channel length. Long-channel MOSFETs rely on the gate electrode for regulating the channel, while short-channel MOSFETs involve the active participation of the source and drain regions. The reduction in channel size in short-channel devices results in increased drain current and a lower threshold voltage, which can impact the switching behavior and energy efficiency of the MOSFET [31].

#### 1.5.2 Velocity saturation

In a short channel device, the lateral electric field experiences significant growth, leading to the saturation of charge carrier velocity at approximately  $10^7$  cm/sec. This saturation effect has implications for the device current, which tends to be smaller than the drain current predicted by the mobility model [40]. Due to the increased lateral electric field in short-channel devices, the mobility of the charge carriers reaches a saturation point. Beyond this limit, the rate of growth of the carriers' velocity with the applied electric field is no longer linear. Consequently, the device current achieved in practice is lower than what would be expected based on the mobility model, which assumes a linear relationship between carrier velocity and electric field. The saturation of charge carrier velocity at around  $10^7$  cm/sec in short channel devices is an important consideration

in their performance analysis. It influences the actual current flow and should be considered when predicting the device behavior and optimizing circuit designs [40].

#### 1.5.4 Surface scattering

In short-channel MOSFETs, the inversion layer that forms in the device is confined to a narrow region near the silicon-insulator interface. As the lateral electric field intensifies within the channel and the vertical electric field is applied, the charge carriers undergo acceleration towards the drain region. However, this acceleration also leads to collision events among the charge carriers, resulting in a degradation of their mobility. This phenomenon is commonly referred to as surface scattering. Surface scattering in short-channel MOSFETs has a significant impact on the device's performance. It causes a reduction in the drain current compared to what would be expected based solely on the mobility of the charge carriers. The collisions between charge carriers during their journey from the source to the drain hinder their overall mobility and affect the efficiency of the device [41]. Understanding and mitigating the effects of surface scattering is crucial in the design and optimization of short-channel MOSFETs. By addressing this phenomenon, researchers and engineers can work towards improving the performance and efficiency of these devices in practical applications.

#### 1.5.5 Hot carrier effects

The carriers move at rapid speeds in short-channel devices because the electric field intensity in the channel areas grows. The high kinetic energy acquired by the carriers in this process can give rise to a phenomenon known as impact ionization. Impact ionization can cause degradation of the insulator layer, leading to gate leakage current. The carriers responsible for this phenomenon are referred to as hot carriers. The presence of hot carriers in short-channel devices can have several undesirable effects. One such effect is the generation of substrate current, which refers to the flow of current through the substrate material. This substrate current can impact the overall performance and reliability of the device [41]. Understanding and managing the effects of hot carriers is crucial in the design and optimization of short-channel devices. Researchers and engineers strive to develop strategies to mitigate the impact of hot carriers, such as incorporating suitable materials and structures that can handle the high-energy carriers more effectively and minimize the associated degradation and leakage currents.

Figure 1.5 Representation of Hot Carriers Effect [42].

## 1.6 Gate-All-Around (GAA)

By employing many gate transistors, the adverse effects of small channels are significantly mitigated, resulting in improved performance. The nanowire itself acts as the substrate in silicon nanowire transistors [43]. Nanowires exhibit various device shapes, such as rectangular and cylindrical configurations. The utilization of Nanowires in transistor design offers several advantages. The cylindrical or gate-all-around structures enable better control over the channel region, facilitating enhanced electrostatics and reduced leakage currents. Moreover, the compact size of Nanowire transistors allows for higher transistor density on a chip, enabling the integration of more functionality and improved overall performance in electronic devices. The development and optimization of Nanowire-based transistor technologies continue to be an area of active research and innovation in the field of semiconductor devices.

#### 1.6.1 Gate All-Around Field-Effect Transistors (GAA-FETs)

These transistors have a unique structure where the gate region completely wraps around the channel, offering distinct advantages over traditional transistor designs [44], [45]. This innovative configuration allows for improved control over the flow of current through the channel, resulting in enhanced device performance. By enclosing the channel region with the gate material, GAA-FETs provide better electrostatic control, minimizing leakage currents and improving the

transistor's ability to switch on and off. This enhanced control over the channel allows for higher device efficiency, reduced power consumption, and improved overall performance. GAA-FETs have shown promise in maintaining their performance characteristics due to the improved electrostatic control provided by the fully wrapped gate structure. This scalability is crucial in enabling the continued advancement of integrated circuits, as it allows for the realization of smaller, faster, and more power-efficient electronic devices. By investigating novel gate materials, dielectrics, and channel materials, researchers aim to further enhance the transistor's functionality, reduce power consumption, and improve reliability. This unique configuration of GAA-FETs with a fully wrapped gate structure represents a significant advancement in transistor design and offers improved electrostatic control, scalability, and performance characteristics, making GAA-FETs a promising candidate for future nanoelectronics devices. GAA-FETs offer distinct advantages in terms of mitigating short-channel resistance [44], [45]. GAA-FETs address this challenge by utilizing a fully wrapped gate structure that surrounds the channel region from all sides. This unique architecture provides superior electrostatic control over the channel, effectively minimizing short-channel effects. Compared to other gate structures like omega gate, double gate, and single gate, GAA-FETs demonstrate enhanced performance characteristics in terms of reducing short channel resistance. The comprehensive wrapping of the gate around the channel in GAA-FETs ensures improved gate control, reduced leakage currents, and enhanced switching characteristics. These advantages make GAA-FETs well-suited for future scaling technology nodes were maintaining device performance in the face of shrinking channel lengths is of utmost importance. By improving short-channel resistance and overall device performance, GAA-FETs hold great potential for enabling the realization of advanced and highly efficient electronic systems in the future. Continued research and advancements in GAA-FET technology will further solidify their position as a leading contender in the field of nanoelectronics.

Despite their promising advantages, GAA-FETs are not without drawbacks and thus two significant challenges are associated with GAA-FETs which are high leakage current and subthreshold slope, which can limit their suitability for low-power applications and steep switching requirements [44]. High leakage current in GAA-FETs compromises energy efficiency and is unsuitable for low-power applications. Achieving a low subthreshold slope is challenging in GAA-FETs, affecting switching efficiency. Alternative transistor designs are needed for low-power and fast-switching applications. Researchers are working on reducing leakage current through gate

dielectric optimization and surface defect minimization. Improving the subthreshold slope requires advancements in gate engineering. By addressing the issues of high leakage current and subthreshold slope, GAA-FETs can become more suitable for a wider range of applications, including low-power and steep-switching scenarios. Ongoing research and development efforts are focused on optimizing GAA-FET designs and exploring innovative solutions to overcome these limitations, ultimately enhancing their performance, and expanding their applicability in various electronic systems.

#### 1.6.2 Gate-All-Around Silicon Nanowire Field-Effect Transistor (GAA-SiNWFET)

The high-k dielectric serves the purpose of isolating the gate from the channel. However, any variation in the high-k dielectric can give rise to several issues that impact the performance of the transistor. Firstly, variations in the high-k dielectric can result in reduced transconductance. This reduction occurs due to a decrease in the effective gate capacitance, which directly affects the ability of the transistor to amplify the input signal. Secondly, there is the possibility of an increased off-leakage current. The transistor may experience larger leakage currents when it should be in the off-state due to variations in the high-k dielectric. The overall power efficiency of the gadget may suffer as a result of this leakage current. The reduced switching speed of the transistor is another effect of high-k dielectric variation. The switching rate relates to how quickly the transistor can transition between its on and off states. If the high-k dielectric is not uniform, it can impede the efficient and rapid switching of the transistor. Furthermore, variation in the high-k dielectric can contribute to increased crosstalk between neighboring transistors. Crosstalk refers to the unwanted coupling or interference between adjacent transistors, which can negatively impact their performance and introduce noise into the system.

JL-GAA-SiNWFETs hold significant promise for future high-performance and low-power electronics. When compared to other transistor designs such as GAA-MOSFETs and bulk MOSFETs, JL-GAA-SiNWFETs exhibit improved sensitivity [46]. They offer advantages like a larger effective channel width, reduced short-channel effects, and enhanced scalability. However, it's important to note that the choice of dielectric material greatly influences the performance of JL-GAA-SiNWFETs. High-k dielectrics have emerged as a potential solution to enhance the performance of JL-GAA-SiNWFETs. These high-k dielectrics offer distinct advantages over traditional SiO<sub>2</sub> (silicon dioxide) dielectrics, thereby addressing certain limitations. One key

advantage of high-k dielectrics is their higher dielectric constant compared to SiO<sub>2</sub>. The dielectric constant, also known as the relative permittivity, evaluates a material's capacity to store electrical energy. With an increased dielectric constant, high-k dielectrics enable a thinner gate oxide layer to be used in the transistor structure. This reduction in oxide thickness allows for better electrostatic control of the device, leading to improved performance. Additionally, the higher dielectric constant of high-k materials facilitates a higher electric field across the gate oxide. This increased electric field enhances the transistor's ability to control the flow of current through the channel, resulting in enhanced device characteristics, such as improved carrier mobility and subthreshold behavior. Another significant advantage of high-k dielectrics is their lower leakage current. By employing high-k dielectrics, the leakage current can be minimized due to their lower leakage properties, which contribute to higher power efficiency and reduced energy consumption. The utilization of high-k dielectrics in JL-GAA-SiNWFETs presents an opportunity to overcome the limitations associated with SiO<sub>2</sub> dielectrics. The superior properties of high-k dielectrics, including their higher dielectric constant, thinner gate oxide, higher electric field, and lower leakage current, collectively contribute to enhanced transistor performance, improved power efficiency, and better overall device characteristics. These findings from various studies and research papers [45], [14] underscore the potential of high-k dielectrics as a viable approach to optimize the performance of JL-GAA-SiNWFETs and pave the way for advancements in high-performance nanoelectronics devices.

## 1.7 The Rationale for Selecting Silicon Nanowire

Silicon CMOS is perhaps the nanoelectronics industry's favored technology for several decades. Because of their exceptionally high qualities, MOSFETs have evolved into one of the most important phenomenon components of VLSI. A MOSFET's channel length is lowered during scaling down the device; deviations from long channel behavior have been predicted. And because of their greatly improved electrical and optical features along with the presence of the semiconductor business, silicon nanowire transistors have gotten a lot of interest as a potential replacement for traditional MOSFETs. It was reported that the carrier mobility of small-diameter SiNWs is high and the ability to fabricate high-performance field-effect transistors FETs requires high carrier mobility. Since silicon nanowires SiNWs consist of a ratio of high surface-to-vol.,

comparatively, a little electrical field applied to the gate can readily control mass carriers and it has also been found that these SiNWs-related nano FETs are extremely sensitive [47].

### 1.8 Objective of the Research Work

In our research study, we aimed to investigate how variations in high-k dielectric materials impact the analog and switching performance of JL-GAA-SiNWFETs (Gate-All-Around Silicon Nanowire Field-Effect Transistors). To conduct our analysis, we utilized the ATLAS SILVACO-3D simulator and performed simulations at a low bias drain voltage of 0.1V. For the gate electrode, we used Niobium with a work function of 4.8 eV.

Our study focused on evaluating several key parameters to assess the performance of JL-GAA-SiNWFETs. These parameters included Id-Vg (drain current versus gate voltage), transconductance (measurement of how the output current changes in response to a change in the input voltage), subthreshold swing, device efficiency, switching ratio, and leakage current. Through our simulations and analysis, we discovered that the HfO<sub>2</sub> (hafnium oxide) dielectric material outperformed SiO<sub>2</sub> (silicon dioxide) and Al<sub>2</sub>O<sub>3</sub> (aluminum oxide) in all evaluated parameters. This indicates that HfO<sub>2</sub> is the most suitable high-k dielectric material for enhancing the performance of JL-GAA-SiNWFETs.

Furthermore, our study explored an alternative approach to achieve a dielectric layer on a smaller width by utilizing a stack formation. We applied SiO<sub>2</sub> as the first layer in the stack, as it demonstrated better compatibility with Si nanowires. The second dielectric layer was varied and studied using SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, and HfO<sub>2</sub>. This combination resulted in effective oxide thickness (EOT) values of 1nm, 0.7nm, and 0.6nm, respectively.

Overall, our research highlights the significance of high-k dielectric variations in influencing the analog and switching performance of JL-GAA-SiNWFETs. The findings indicate that HfO<sub>2</sub> exhibits superior characteristics compared to SiO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>, showcasing its potential for optimizing device performance. The utilization of dielectric stack formations also provides a viable approach for achieving desired oxide thickness on smaller device dimensions.

### **CHAPTER 2**

# DEVICE STRUCTURE & SIMULATION IN ATLAS SILVACO-3D

#### 2.1 ATLAS SILVACO-3D

ATLAS SILVACO-3D is a powerful software tool used for the three-dimensional (3D) simulation of semiconductor devices. Silvaco Inc., a well-known electronic design automation (EDA) software supplier, created it. The software is specifically designed for advanced process technologies and enables engineers and researchers to model, analyze, and optimize the performance of semiconductor devices in a 3D environment. The production of semiconductor devices, including oxidation, diffusion, ion implantation, removal, coating, and lithography, can be simulated using this software. This is a sizable collection of extremely sophisticated tools, including ATLAS, that support the design and creation of all varieties of semiconductor and VLSI devices. This module can simulate many semiconductor devices in 2D and 3D, including MOSFETs, HEMTs, and solar cells [48].

ATLAS SILVACO-3D provides a comprehensive suite of simulation capabilities that accurately simulate the behavior of various semiconductor devices, including transistors, diodes, solar cells, sensors, and more. It employs advanced numerical algorithms and physics-based models to capture the complex interactions between electrical, thermal, and optical phenomena within the device structures. The software allows users to define the geometric layout of the device, specify material properties, and define the operational conditions and boundary conditions. It then solves the governing equations using numerical techniques to simulate the electrical behavior of the device under different operating conditions. This includes modeling carrier transport, charge generation and recombination, electrostatics, quantum effects, and other relevant physical phenomena. ATLAS SILVACO-3D offers a wide range of analysis capabilities, such as current-voltage (IV) characteristics, capacitance-voltage (CV) characteristics, charge transport analysis, breakdown voltage analysis, thermal analysis, and more. It provides detailed insights into device performance, allowing engineers to optimize design parameters and assess the impact of process variations and design modifications. The software also offers a user-friendly graphical interface that facilitates device setup, visualization of simulation results, and post-processing of data. It supports efficient parallel computing to expedite simulation times and provides various data analysis and visualization tools to aid in result interpretation.

ATLAS SILVACO-3D is widely used in the semiconductor industry and academic research for the design and optimization of advanced semiconductor devices. Its accurate 3D simulation capabilities contribute to the development of more efficient, reliable, and high-performance electronic devices across various application domains.

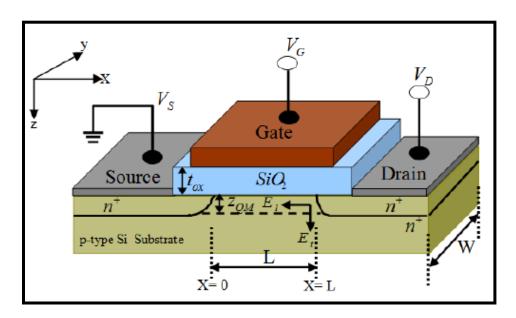

### 2.2 Device Structure

Figure 2.1 depicts the proposed structure of our device, showcasing its key dimensions and layers. The entire device measures 42nm in length, with a channel length of 20nm. At the interface, there is an oxide layer composed of SiO<sub>2</sub>. The device features a metal gate, which has a thickness denoted as T1. Additionally, there are varying dielectric layers with a thickness denoted as T2, and an interfacial oxide layer (SiO<sub>2</sub>) with a thickness denoted as T3. The channel diameter, represented as 2R, is also the thickness of the silicon layer.

In all simulations, the gate length remains consistent at 20nm. Similarly, the varying oxide layer and interfacial oxide layer maintain a length of 20nm. The source and drain regions measure 10nm each, while the electrodes at both ends have a length of 1nm. For a comprehensive overview, please refer to Table 1, which lists all these parameters for reference and further analysis.

By providing these detailed dimensions and layer thicknesses, the structure of the device is clearly outlined, enabling researchers and engineers to understand the physical characteristics and design considerations of the proposed device configuration.

Figure 2.1 - Junctionless gate all around silicon nanowire FET (a) JL-GAA-SiNWFET (b) cross-sectional view.

Table 2.1: Technology parameters

| Device Parameters                                                                               | JL-GAA-SiNWFET            |

|-------------------------------------------------------------------------------------------------|---------------------------|

| Channel length (nm)                                                                             | 20.00                     |

| Diameter of silicon film (nm)                                                                   | 20.00                     |

| The thickness of varied oxide and interface oxide respectively, (nm)                            | 0.5 & 0.5                 |

| Length of Source and Drain, (nm)                                                                | 10.00                     |

| Length/Thickness of electrode, (nm)                                                             | 1.00                      |

| Thickness of varied oxide and SiO <sub>2</sub> respectively, (nm)                               | 0.5 & 0.5                 |

| Dielectric of SiO <sub>2</sub> , Al <sub>2</sub> O <sub>3</sub> , HfO <sub>2</sub> respectively | 3.9, 9, 25                |

| Gate work-function of Niobium, (eV)                                                             | 4.8                       |

| Doping of Channel, Source, and Drain, (N-type)                                                  | $10^{19} \text{ cm}^{-3}$ |