## TCAD Analysis and Modelling of Gate Stack Gate-All-Around Junctionless Nanowire Field-Effect Transistor for Sensing Applications

THESIS SUBMITTED TO DELHI TECHNOLOGICAL UNIVERSITY FOR THE AWARD OF THE DEGREE OF

#### **DOCTOR OF PHILOSOPHY**

By

#### **MEKONNEN GETNET YIRAK**

## (2k18|PhD|AP|31)

Under the Supervision of

## **PROF. RISHU CHAUJAR**

## DEPARTMENT OF APPLIED PHYSICS DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042 (INDIA) SEPTEMBER 2023

## © DELHI TECHNOLOGICAL UNIVERSITY, DELHI, 2023 ALL RIGHTS RESERVED

## This thesis is dedicated to my parents,

For their endless support and encouragement.

#### **DELHI TECHNOLOGICAL UNIVERSITY**

#### (Formerly Delhi College of Engineering)

Department of Applied Physics Shahbad Daulatpur, Bawana Road, Delhi-110042, India

**CERTIFICATE**

This is to certify that the thesis entitled "TCAD Analysis and Modelling of Gate Stack Gate-All-Around Junctionless Nanowire Field-Effect Transistor for Sensing Applications," being submitted by Mekonnen Getnet Yirak (Reg. No. 2K18/PhD/AP/31), to Delhi Technological University, Bawana Road, Delhi-110042 (India), for the award of degree of DOCTOR OF PHILOSOPHY is a bonafide record of the research work carried out by him under my supervision and guidance. According to University standards, the thesis is complete. It is further certified that the work embodied in this thesis is original and has neither partially nor fully submitted to any other Institute or University for the award of any other degree or diploma.

Prof. Rishu Chaujar (Supervisor) Professor Department of Applied Physics Delhi Technological University, Delhi-110042, India. Prof. A.S.Rao Professor & Head Department of Applied Physics Delhi Technological University, Delhi-110042, India.

#### **DELHI TECHNOLOGICAL UNIVERSITY**

#### (Formerly Delhi College of Engineering)

Department of Applied Physics Shahbad Daulatpur, Bawana Road, Delhi-110042, India

**DECLARATION**

I, Mekonnen Getnet Yirak, hereby certify that the thesis titled "TCAD Analysis and Modelling of Gate Stack Gate-All-Around Junctionless Nanowire Field-Effect Transistor for Sensing Applications," submitted in the fulfilment of the requirements for the award of the degree of Doctor of Philosophy is an authentic record of my research work carried out under the supervision of **Prof. Rishu Chaujar**. This work in the same form or any other form has not been submitted by me or anyone else earlier for any purpose. Any material borrowed or referred to is duly acknowledged.

> Mekonnen Getnet Yirak (2K18/PhD/AP/31) Department of Applied Physics Delhi Technological University, Delhi-110042, India.

## **ACKNOWLEDGMENT**

This thesis is the culmination of my Ph.D. journey, and now is the time to thank all those who have helped me and made this journey an unforgettable experience for me.

First and foremost, I thank you, GOD, for all of your blessings, including life, health, and the incredible energy you have given me to help me achieve my professional goals.

I wholeheartedly want to thank my guide, **Prof. Rishu Chaujar**, Professor, Department of Applied Physics Delhi Technological University (DTU), for her excellent mentorship, research, patience, motivation, immense knowledge, and continuous support all these years. This thesis would not have been accomplished without her persistent efforts and guidance. Her advice helped me in research and writing of this thesis. She is genuinely the best advisor and mentor with her management skills and enthusiasm.

I would also thank **Prof. Suresh C. Sharma, Prof. Rinku Sharma, and Prof. A.S. Rao,** previous and current heads of the Department of Applied Physics, DTU, and all other academic and staff members for their assistance and cooperation throughout my research and coursework. Thanks to the Department of Applied Physics, Delhi Technological University (DTU), for giving me the necessary resources to work as efficiently as possible within the time limits.

I would also like to express tremendous and heartfelt appreciation to my colleagues in the Microelectronics Research Laboratory for their scientific contributions, fruitful talks, motivation, and all the fun we had kept me going on this tough yet incredible journey. I would like to thank them for their scientific contributions, fruitful discussions, motivation, and all the fun we had. Throughout the past several years' highs and lows, I have maintained my sanity thanks to our joy. Their personal and professional assistance, encouragement, and moral support have helped me feel more at peace. My time spent with them will always be one of my life's most memorable and enjoyable periods.

I would like to show my appreciation to my parents, Mr. Getnet Yirak and Mrs. Lakech Fentie, as well as all my sisters and brothers, for the love, continual care, and emotional support they gave me during my entire life. Their unwavering trust in me and confidence have always been driving forces in pursuing my goal. I would like to express my gratitude to my wife, Mrs. Selam Yismaw, and our kids, Samrawit Mekonnen, Sofoniyas Mekonnen and Mahider Mekonnen for all the love, attention to detail, and emotional support they have provided to me throughout my

life. In this difficult path, my family's cooperation, understanding, patience, and encouragement were the nourishing ingredients that played an important role.

I want to acknowledge **Ministry of Science and higher education (MOSHE), Government of Ethiopia, and Debre Tabor University, Debre Tabor, Ethiopia,** for providing financial support during my research work.

## **Table of Contents**

| LIST OF FIGURES                                                                      | XI    |

|--------------------------------------------------------------------------------------|-------|

| LIST OF TABLES                                                                       | xvı   |

| NOMENCLATURE / TERMINOLOGY                                                           | XVII  |

| ABSTRACT                                                                             | XVIII |

| LIST OF PUBLICATIONS                                                                 | ХХІ   |

| 1.1 INTRODUCTION                                                                     |       |

| 1.2 MOSFET Scaling (Review Literature)                                               |       |

| 1.2.1 Reasons for scaling                                                            |       |

| 1.3 Short Channel Effects in MOSFETs                                                 |       |

| 1.3.1 Drain-Induced Barrier Lowering                                                 |       |

| 1.3.2 Punchthrough                                                                   |       |

| 1.3.3 Higher Subthreshold Conduction                                                 |       |

| 1.3.4 Impact Ionization and Hot Electron Effect                                      |       |

| 1.3.5 Channel Length Modulation (CLM)                                                | 8     |

| 1.3.6 Velocity Saturation                                                            | 8     |

| 1.3.7 Gate Oxide Leakage                                                             | 9     |

| 1.3.8 Band-to-Band Tunnelling                                                        |       |

| 1.3.9 Mobility Degradation (Surface Scattering)                                      | 9     |

| 1.4 ENGINEERING SCHEMES TO REDUCE SHORT CHANNEL EFFECTS                              | 10    |

| 1.4.1 Gate Dielectric Engineering                                                    |       |

| 1.4.2 Gate Electrode Engineering                                                     | 12    |

| 1.4.2.1 Need for Metal Gates in MOSFET                                               | 13    |

| 1.4.3 Junctionless Transistor (Gated Resistor)                                       |       |

| 1.4.4 Latest Device Structures Proposed to Overcome Short Channel Effects.           |       |

| 1.4.4.1 Silicon on Insulator (SOI) MOSFET                                            |       |

| 1.4.4.2 Double Gate (DG) MOSFET                                                      |       |

| 1.4.4.3 Triple Gate (TG) MOSFET                                                      |       |

| 1.4.4.4 Gate All Around (GAA) NWFET                                                  |       |

| 1.5 DEVICE SIMULATION                                                                |       |

| 1.0 RESEARCH GAPS                                                                    |       |

| 1.7 Objectives of the Study                                                          |       |

| 1.8 ORGANIZATION OF THE THESIS                                                       | 28    |

| REFERENCES                                                                           |       |

| SENSITIVITY INVESTIGATION OF JUNCTIONLESS GATE-ALL-AROUND SILICON NANOWIRE FIELD-EFF | ECT   |

| TRANSISTOR-BASED HYDROGEN GAS SENSOR                                                 |       |

| 2.1 INTRODUCTION                                                                     | 40    |

| 2.2 Device Structure and Simulation Models                                           | 41    |

| 2.2.1 Device Structure                                                               |       |

| 2.2.2 Simulation Models                                                              | 42    |

| 2.2.3 Function description                                                           | 43    |

| 2.3 Two-Dimensional Analytical Subthreshold Model                                    | 44    |

| 2.3.1 Surface Potential and Subthreshold Current Modeling                            | 44    |

| 2.3.2 Threshold Voltage (V <sub>th</sub> ) Modeling                                  |       |

| 2.4 SIMULATION RESULTS AND DISCUSSION                                                | 48    |

| 2.4.1 Change in Drain Current                                                        | 48    |

| 2.4.2 Surface Potential-Based Sensing                                                | 49    |

| 2.4.3 Electron Mobility-Based Sensing                                                | 50    |

| 2.4.4 Sensitivity Parameters ( $\Delta V th$ and SIOFF ratio)                                                                                                             |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| REFERENCES                                                                                                                                                                |        |

| SENSITIVITY ANALYSIS OF BIOMOLECULE NANO-CAVITY IMMOBILIZATION IN DIELECTRIC MODULAT<br>HYBRID METAL GATE-ALL-AROUND JUNCTIONLESS NWFET BIOSENSOR FOR DETECTING VARIOUS D |        |

| 3.1 INTRODUCTION                                                                                                                                                          | 63     |

| 3.2 Device Structure and Simulation Models                                                                                                                                | 66     |

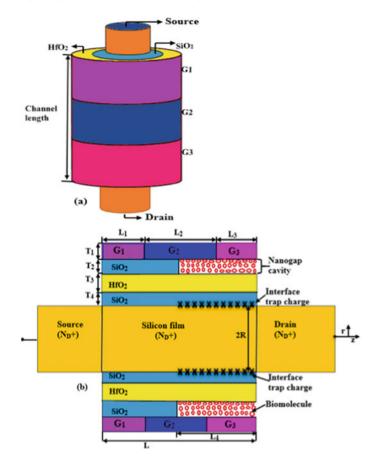

| 3.2.1 Device Structure                                                                                                                                                    | 66     |

| 3.2.2 Device Simulation                                                                                                                                                   |        |

| 3.2.3 Suggested fabrication steps for a semiconductor device                                                                                                              |        |

| 3.3 RESULTS AND DISCUSSION                                                                                                                                                |        |

| 3.3.1 Comparative Analysis on Dielectric Modulated Double - and Triple -Hybrid Metal GAA -JL -NV                                                                          |        |

| Biosensors on Electrical Transfer Characteristics                                                                                                                         |        |

| 3.3.2 Sensitivity for different biomolecules                                                                                                                              |        |

| 3.3.3 Assessment of the Linearity Performance                                                                                                                             |        |

| 3.4 SUMMARY                                                                                                                                                               | 87     |

| REFERENCES                                                                                                                                                                |        |

| EFFECT OF TRAP CHARGES ON DIELECTRIC MODULATED TRIPLE HYBRID METAL GATE JUNCTIONLESS<br>AROUND SILICON NANOWIRE FET BASED BIOSENSOR                                       |        |

| 4.1 INTRODUCTION                                                                                                                                                          | 06     |

| 4.2 Device Structure and Simulation Models                                                                                                                                |        |

| 4.2 Device Structure                                                                                                                                                      |        |

| 4.2.2 Simulation Models                                                                                                                                                   |        |

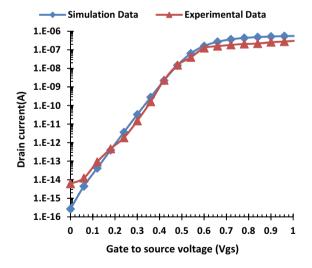

| 4.3 Results and Discussion                                                                                                                                                |        |

| 4.3 Resolt's AND Discossion<br>4.3.1 Impact of Localized Charges on Transfer Characteristics                                                                              |        |

| 4.3.2 Impact of Localized Charges on Analog Performance                                                                                                                   |        |

| 4.3.3 Sensitivity for different biomolecules                                                                                                                              |        |

| 4.3.3.1 Impact of ITCs on Surface Potential-Based Sensitivity                                                                                                             |        |

| 4.3.3.2 Impact of ITCs on Transfer Characteristics and Sensitivity                                                                                                        |        |

| 4.3.3.3 Impact of ITCs on Analog Performance                                                                                                                              |        |

| 4.4 SUMMARY                                                                                                                                                               |        |

| REFERENCES                                                                                                                                                                |        |

| NUMERICAL MODELING FOR TRIPLE HYBRID GATE OPTIMIZATION DIELECTRIC MODULATED JUNCTI<br>GATE ALL AROUND SINWFET BASED URICASE AND ChOX BIOSENSOR                            | ONLESS |

|                                                                                                                                                                           |        |

| 5.1 INTRODUCTION                                                                                                                                                          |        |

| 5.2 DEVICE STRUCTURE AND SIMULATION MODELS                                                                                                                                |        |

| 5.2.1 Device Structure                                                                                                                                                    |        |

| 5.2.2 Simulation Models                                                                                                                                                   |        |

| 5.3 POTENTIAL AND SUBTHRESHOLD CURRENT MODELING                                                                                                                           |        |

| 5.3.1 Surface potential analysis                                                                                                                                          |        |

| 5.3.2 Subthreshold Current Modelling                                                                                                                                      |        |

| 5.3.3 Threshold voltage (Vth) Modeling                                                                                                                                    |        |

| 5.4 Results and Discussion                                                                                                                                                |        |

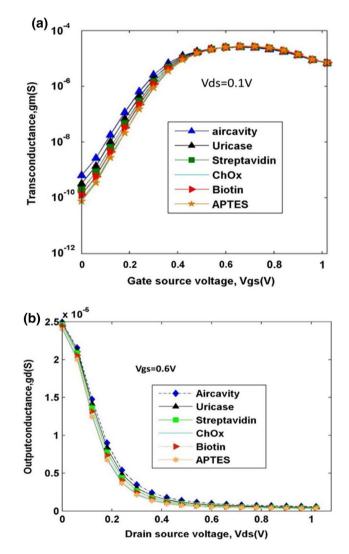

| 5.4.1 Transfer characteristics                                                                                                                                            |        |

| 5.4.2 Impact of work-function $\Phi M$ on the sensitivity (S)                                                                                                             |        |

| 5.4.3 Transconductance (gm) and output conductance (gd)                                                                                                                   |        |

| 5.5 SUMMARY                                                                                                                                                               | 153    |

| REFERENCES                                                                                                                                                                |        |

| SUMMARY AND FUTURE SCOPE OF THE WORK |  |

|--------------------------------------|--|

| 6.1 SUMMARY                          |  |

| 6.2 FUTURE SCOPE                     |  |

## **List of Figures**

## Chapter-1

| Figure 1. 1. Moore's law illustration: transistor counts (number) versus dates of introduction. The graph |

|-----------------------------------------------------------------------------------------------------------|

| shows that counts double every two years[16]                                                              |

| Figure 1. 2. Depicts the need for increased data speeds while simultaneously increasing demand for        |

| billions of devices [18]                                                                                  |

| Figure 1.3. Illustrates Drain-Induced Barrier Lowering (DIBL)[29].                                        |

| Figure 1.4. Illustrates a schematic diagram for punch-through[30]                                         |

| Figure 1.5. Shows channel length modulation(CLM[25]                                                       |

| Figure 1. 6: Vertical electric field in a short channel MOSFET and surface scattering[50]10               |

| Figure 1. 7. Illustrates Gate Stack Architecture[62]                                                      |

| Figure 1.8. Double material gate (DMG) FET structure[69]                                                  |

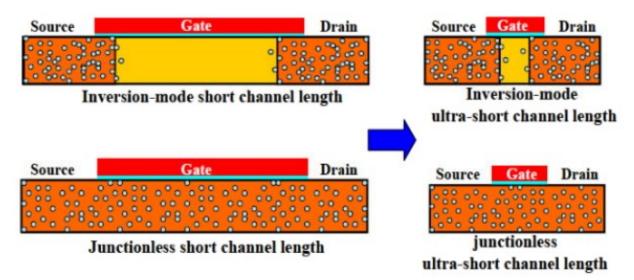

| Figure 1. 9. Source and drain doping of an inversion-mode and junctionless transistor with a short and    |

| ultra-short channel, adapted from[86]1                                                                    |

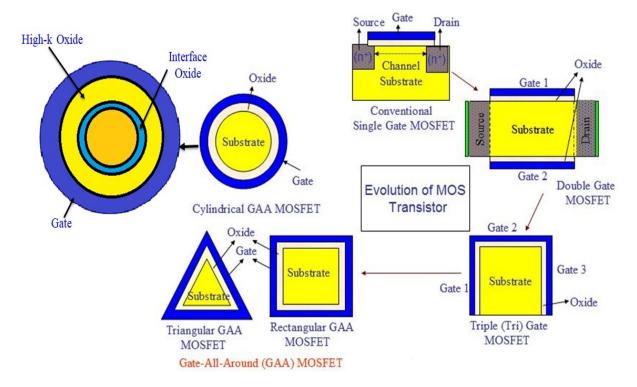

| Figure 1. 10. Illustrates the development of the device architecture from the single-gated planar to the  |

| fully GAA NWMOSFETs[85], [87]10                                                                           |

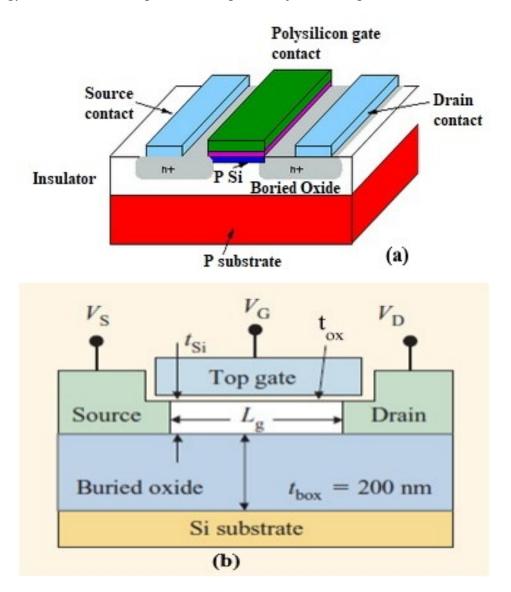

| Figure 1. 11. Illustrates SOI MOSFET (a) 3-D view, (b) 2-D schematic structure [85]                       |

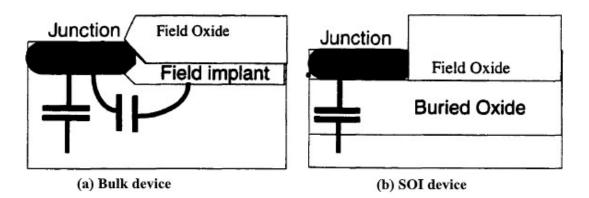

| Figure 1. 12. Depicts parasitic junction capacitances in bulk and SOI MOSFETs [89]                        |

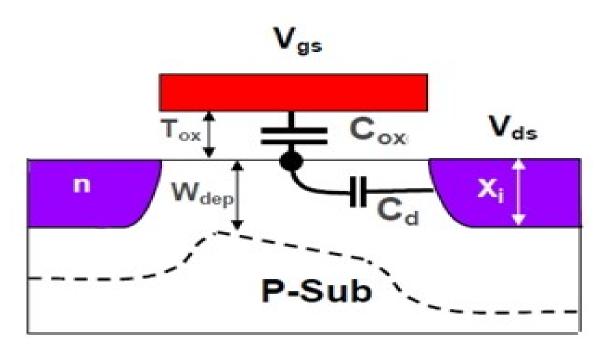

| Figure 1. 13. Schematic of the two-capacitor network in MOSFET [89]                                       |

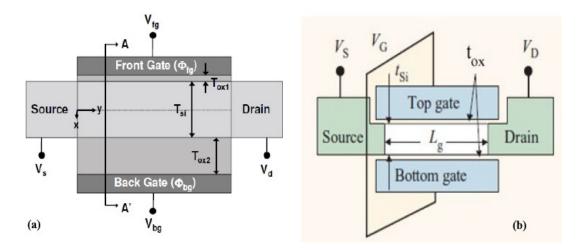

| Figure 1. 14. Structure of (a) Asymmetric, (b) Symmetric Double gate MOSFET [92]22                        |

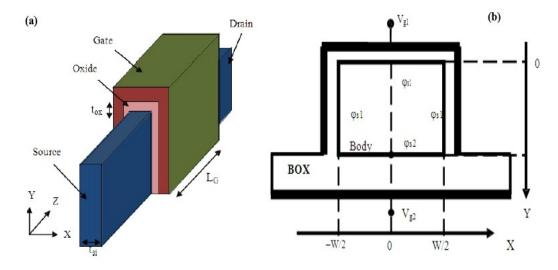

| Figure 1. 15. Illustrates basic (a) 3D structure model, (b) cross-sectional view of Triple Gate SO        |

| MOSFET[98]                                                                                                |

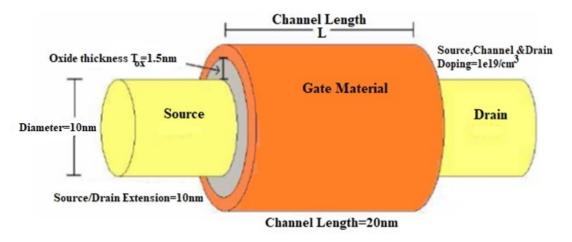

| Figure 1. 16. Illustrates 3D schematic structure of a cylindrical JL GAA-SiNWFET[107]24                   |

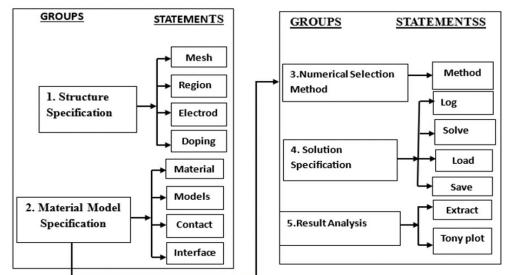

| Figure 1. 17. Illustrates the basic flow chart applied during the proposed device simulation[115]2        |

|                                                                                                           |

## Chapter-2

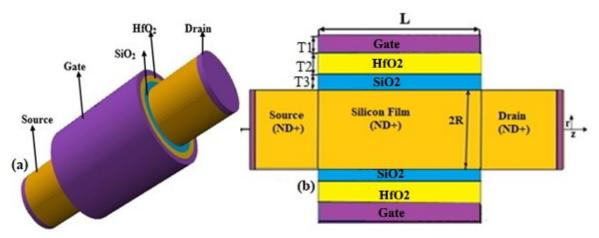

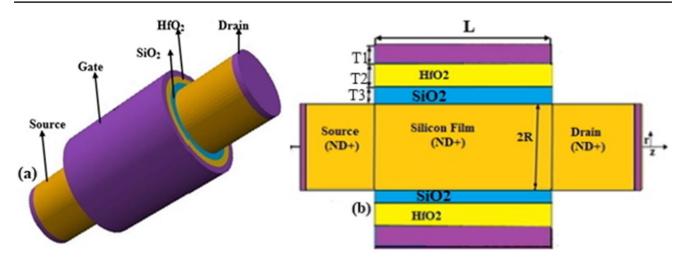

| Figure 2. 1. illustrates (a) a schematic of 3D structure and (b) 2D cross-sectional view for a p-type        |

|--------------------------------------------------------------------------------------------------------------|

| substrate cylindrical JL-GAA-SiNWFET-based hydrogen sensor[30]42                                             |

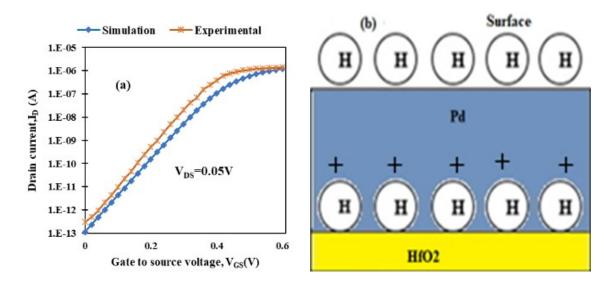

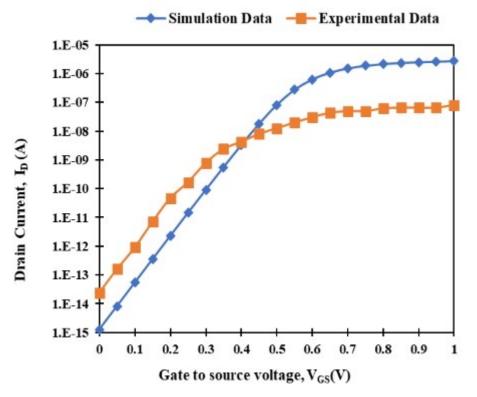

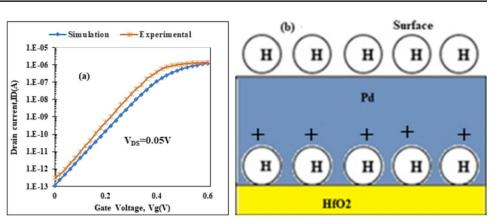

| Figure 2. 2. Depicts (a) Calibration of simulation results at $V_{DS}$ =0.05V with experimental results [34] |

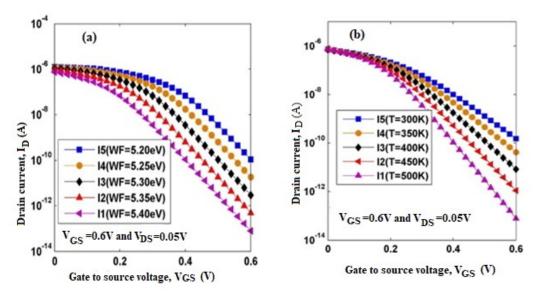

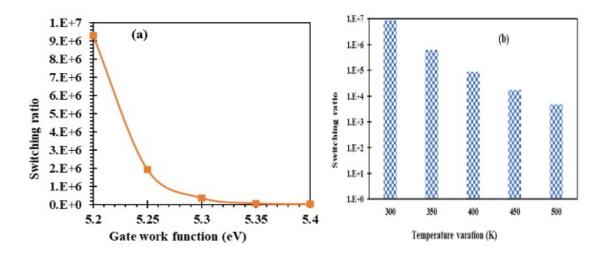

| and (b) 2D Electrical dipole formation at the Pd/HfO <sub>2</sub> interface44                                |

| Figure 2. 3. Illustrates the impact of (a) palladium (Pd) work function and (b) Temperature on ID-VG for     |

| p-channel cylindrical JL SiNWFET [30]49                                                                      |

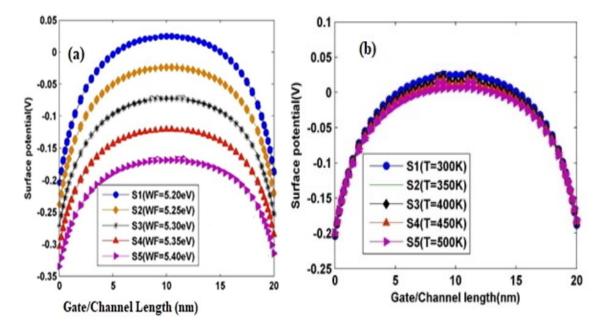

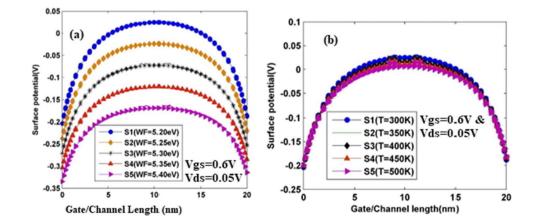

| Figure 2. 4 depicts the effect of (a) palladium (Pd) work function and (b) Temperature on surface potential  |

| (V) for p-channel cylindrical JL SiNWFET [30]50                                                              |

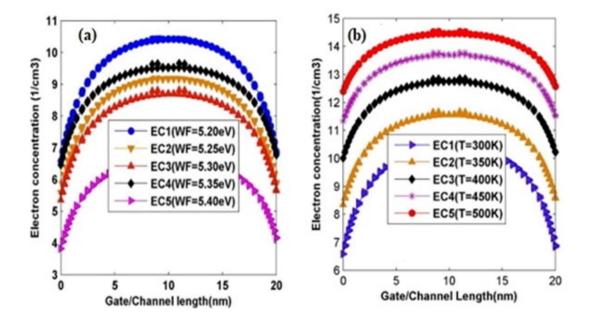

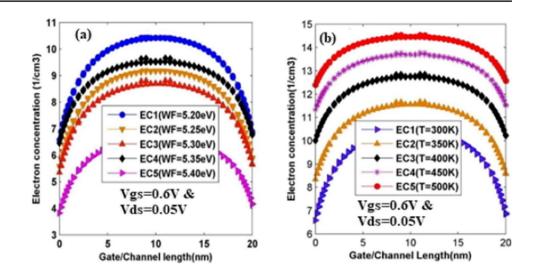

| Figure 2. 5. Effects of (a) palladium (Pd) gate work- function and (b) Temperature variation on electron          |

|-------------------------------------------------------------------------------------------------------------------|

| concentration (1/cm <sup>3</sup> ) for p-channel cylindrical JL-SiNWFET [30]                                      |

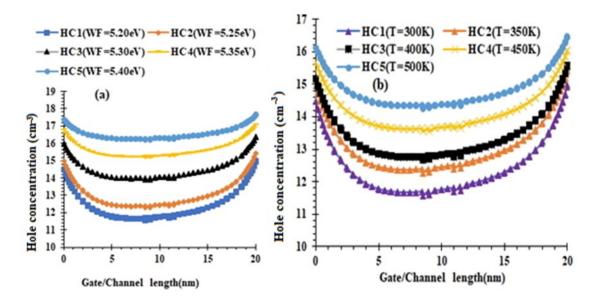

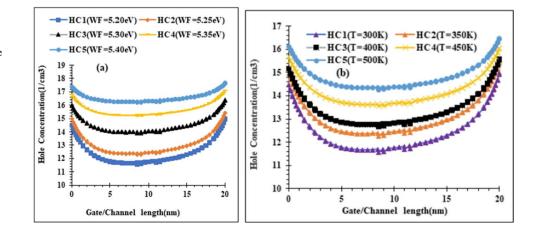

| Figure 2. 6. Impacts of (a) palladium (Pd) work function and (b) Temperature variation on hole                    |

| concentration (1/cm <sup>3</sup> ) for p-channel substrate cylindrical JL-SiNWFET [30]                            |

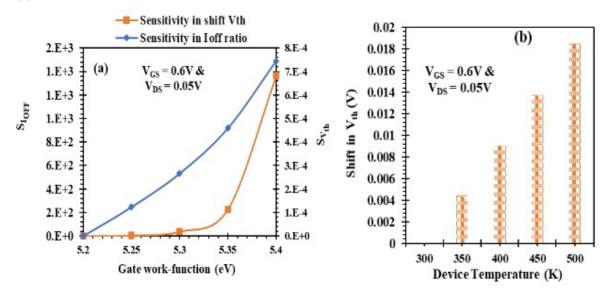

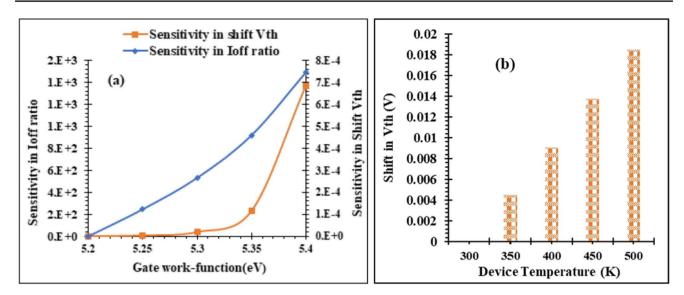

| Figure 2. 7. Depicts the impact of (a) palladium (Pd) metal gate work and (b) Temperature on the I <sub>OFF</sub> |

| ratio for p-channel substrate cylindrical JL-SiNWFET [30]53                                                       |

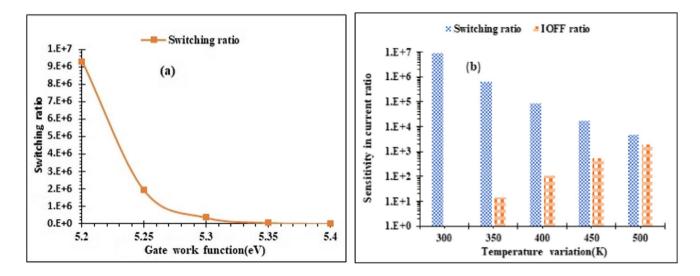

| Figure 2. 8. Illustrate impact of (a) palladium (Pd) metal gate work function on switching ratio and (b)          |

| Temperature on shifting threshold voltage for p-channel substrate cylindrical JL-SiNWFET [30]54                   |

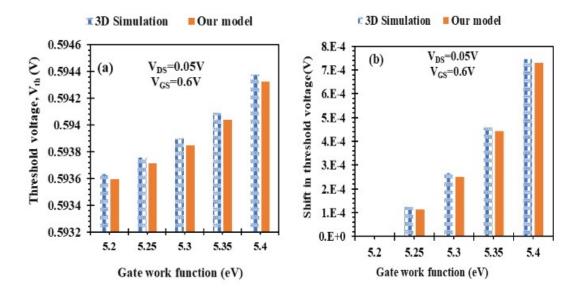

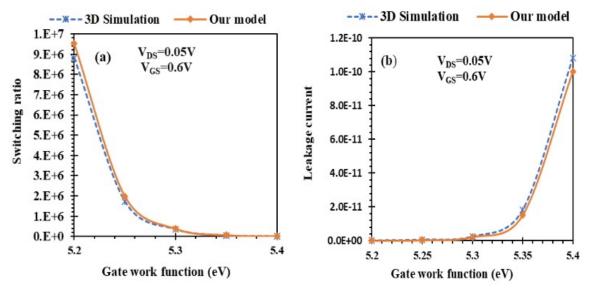

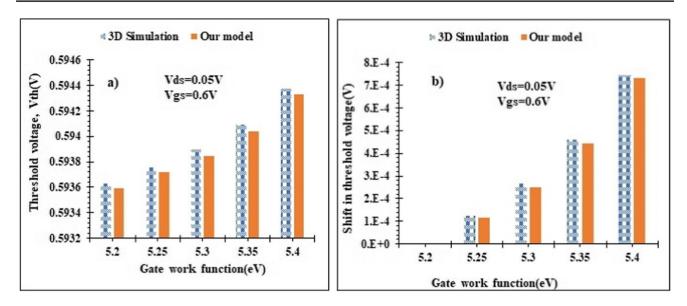

| Figure 2.9. Shows the effect of palladium (Pd) work function variation on (a) the threshold voltage $(V_{th})$    |

| and (b) the shift in the threshold voltage $\Delta V$ th for p-channel cylindrical JL-SiNWFET [30]54              |

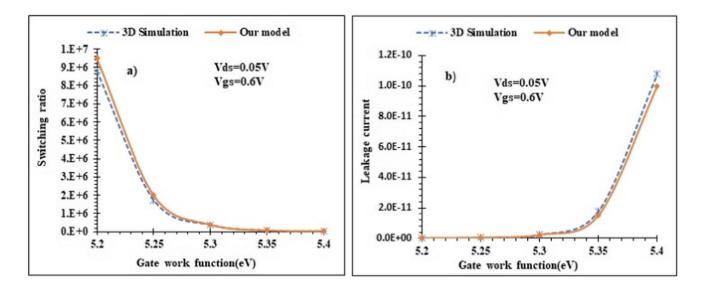

| Figure 2. 10. Shows the impact of palladium electrode work function (Pd), (a) on the switching ratio,             |

| and (b)leakage current cylindrical p-channel substrate JL-SiNWFET [30]55                                          |

## Chapter-3

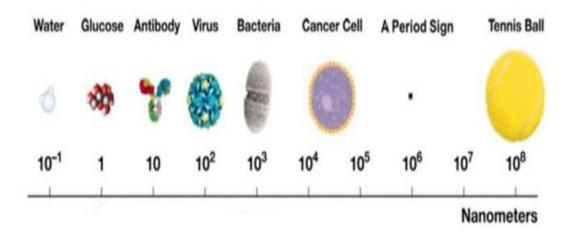

| Figure 3. 1. Illustrates the size of biological species for characterization and electrical detection with          |

|---------------------------------------------------------------------------------------------------------------------|

| NWFET-based biosensors [61]                                                                                         |

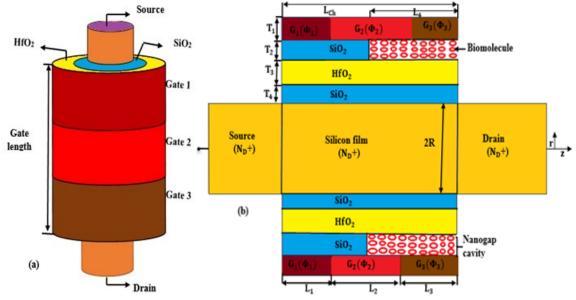

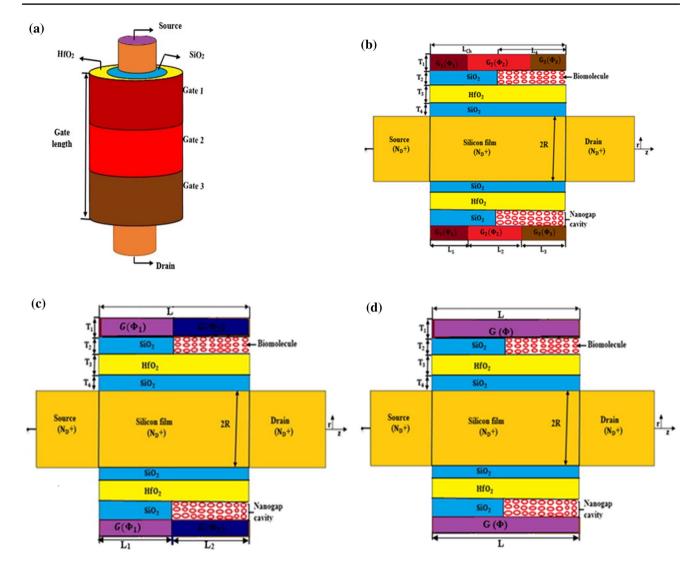

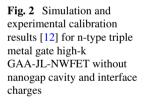

| Figure 3. 2. Depicts (a) 3D schematic diagram and (b) 2D cross-sectional interpretations of n-substrate             |

| channel JL-DM triple-hybrid metal gate-all-around NWFET biosensor [69]67                                            |

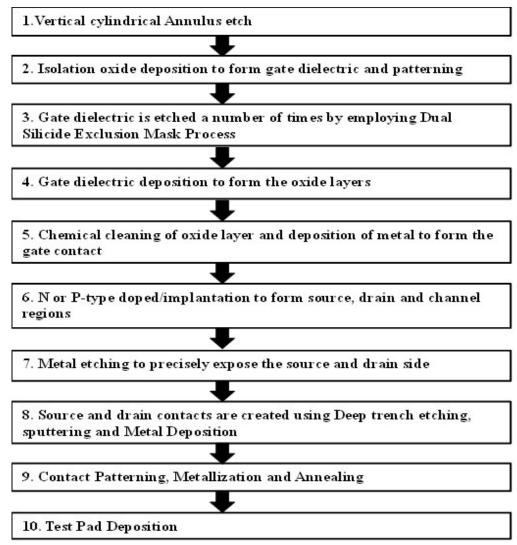

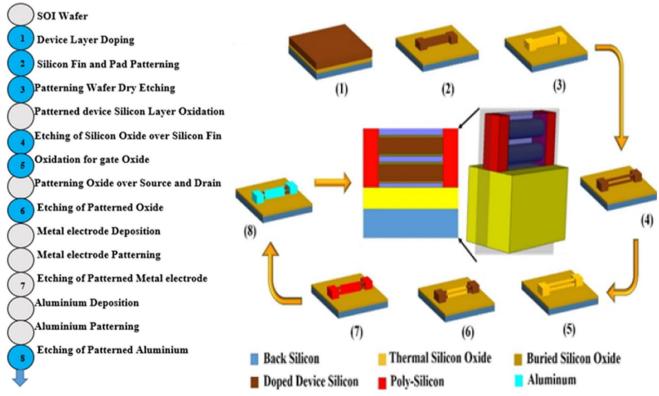

| Figure 3. 3. illustrates the suggested fabrication step flow chart [23], [78], [83]                                 |

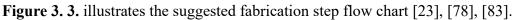

| Figure 3. 4. illustrates biosensing principle flowchart [79]71                                                      |

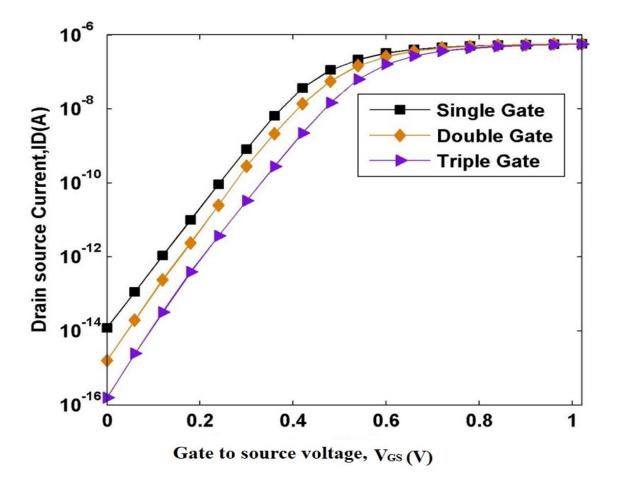

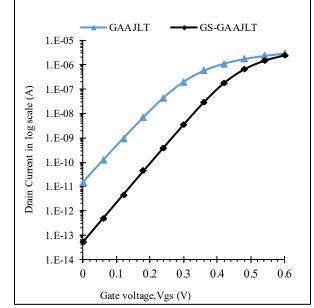

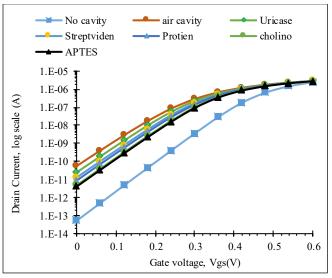

| Figure 3. 5. Shows the simulation results of $I_D$ vs $V_{GS}$ for n-substrate channel dielectric modulated unique, |

| double, and triple hybrid cylindrical metal gate JL-NWFET in a log file at ( $V_{DS}$ =0.05V) [59]72                |

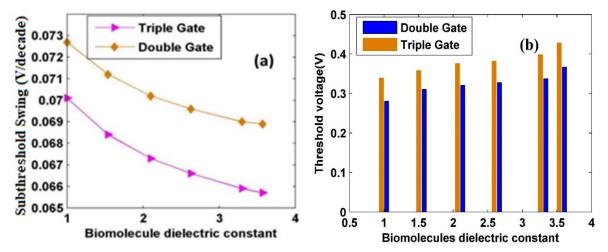

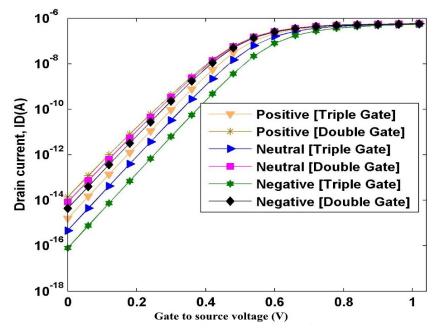

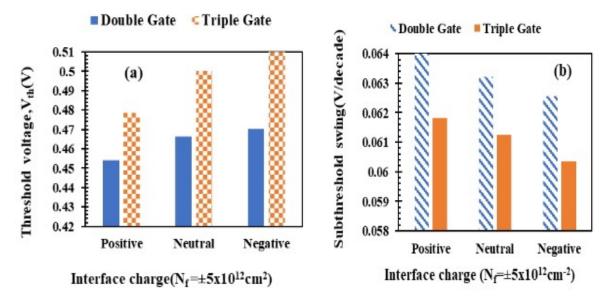

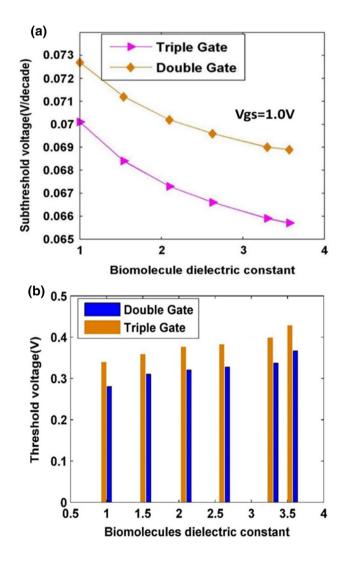

| Figure 3. 6. Impacts of biomolecules on (a) subthreshold slope (b) threshold voltageVth for n-substrate             |

| channel double and triple hybrid metal gate all around junctionless NWFET at a constant (VDS =                      |

| 0.05V and VGS = 1.0V) [59]                                                                                          |

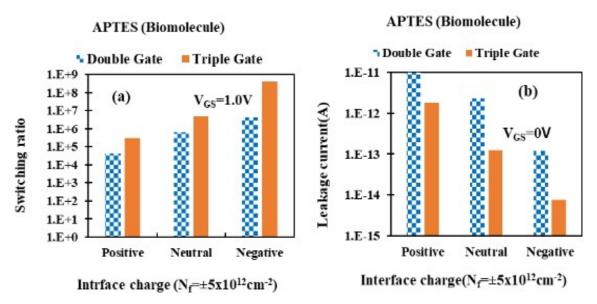

| Figure 3. 7. Depicts (a) drain current (ID-VG) and (b) leakage current comparison, including different              |

| biomolecules for n-substrate channel double and triple hybrid metal gate all around JL-NWFET at (VDS =              |

| 0.05V and VGS = 1.0V), [59]74                                                                                       |

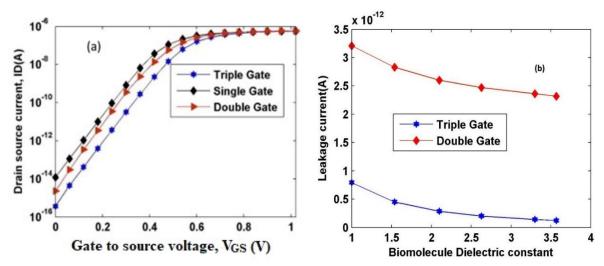

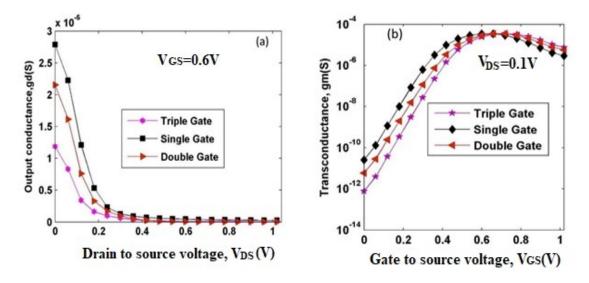

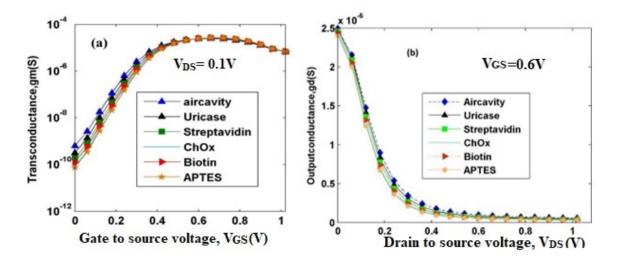

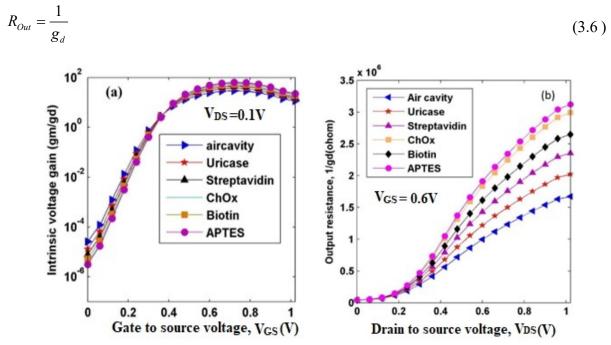

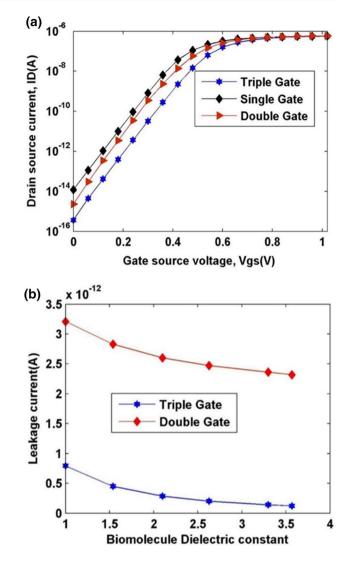

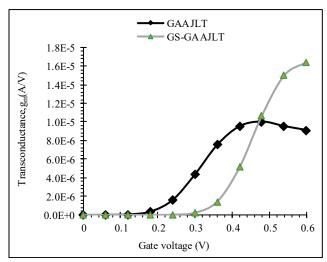

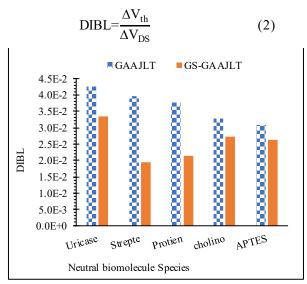

| Figure 3. 8. Depicts (a) output conductance $(g_d)$ and (b) Transconductance $(g_m)$ comparison for n-              |

| substrate channel single, double and triple hybrid metal gate all around JL-NWFET [59]75                            |

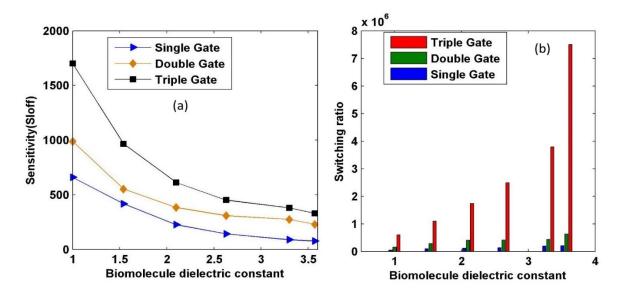

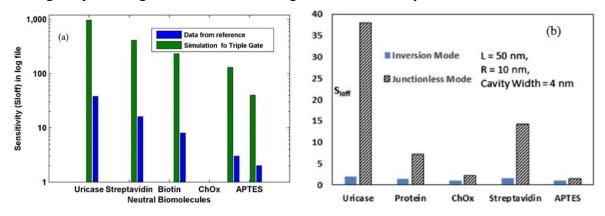

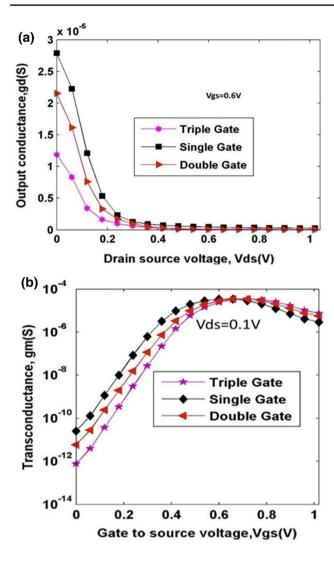

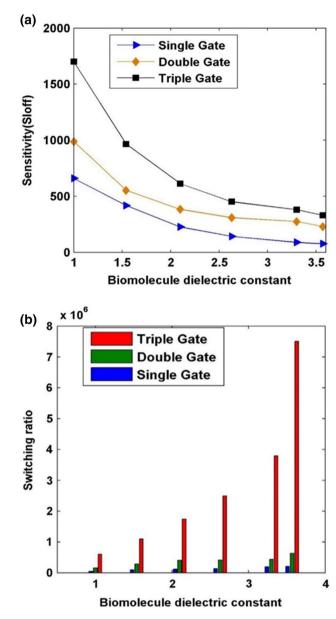

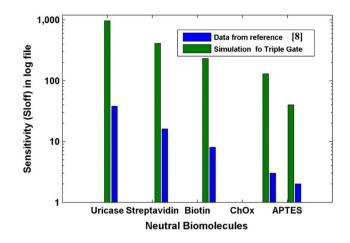

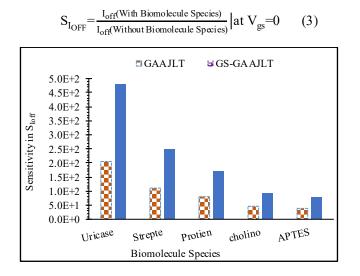

| Figure 3. 9. illustrates the effect of biomolecules on (a) the sensitivity (Sloff) and (b) switching ratio for      |

| n-substrate single, double, and triple hybrid metal gate all around JL-NWFET at (VDS =                              |

| 0.05V and VGS = 1.0V) [59]76                                                                                        |

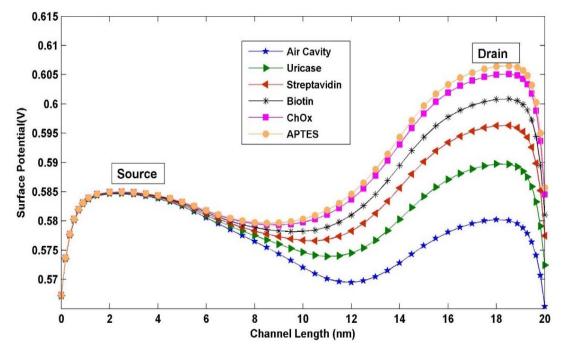

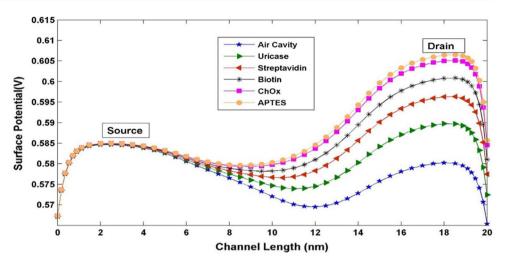

| Figure 3. 10. illustrates the effect of different biomolecules on the surface potential for n-substrate             |

| channel DM-THMG -GAA-JL-NWFET at ( $VGS = 1.0V$ and $VDS = 0.05V$ ) [59]                                            |

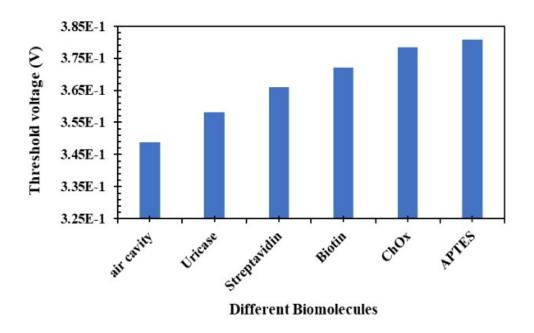

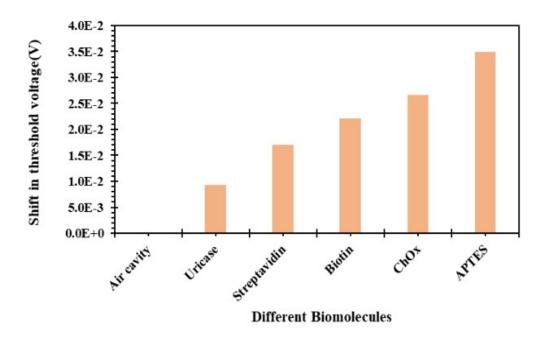

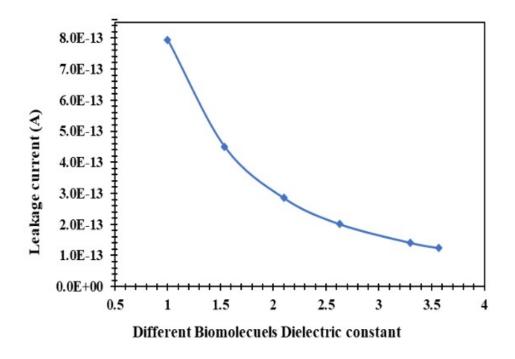

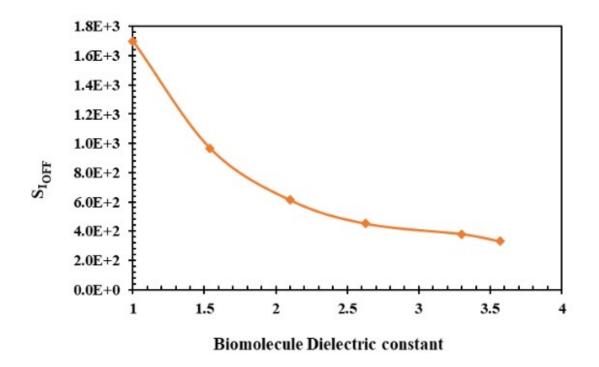

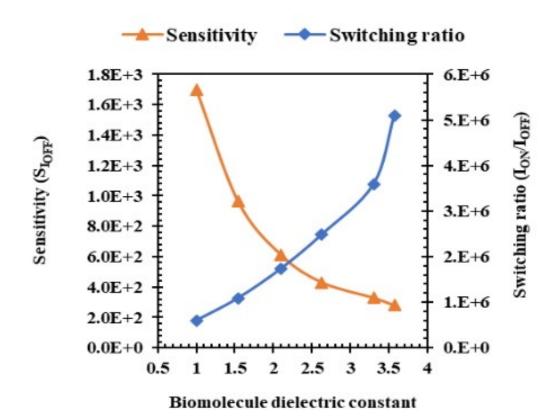

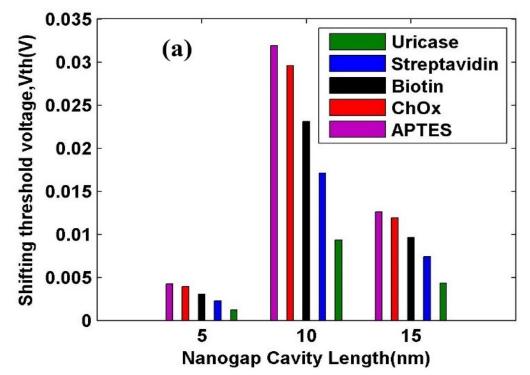

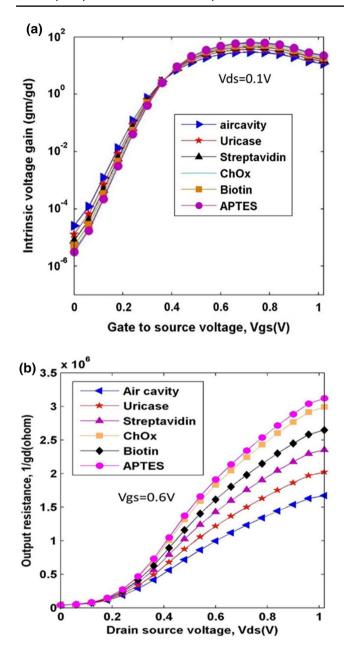

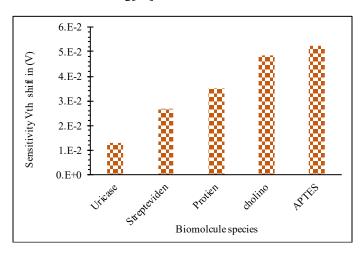

Figure 3. 11. illustrates the effect of different biomolecules on the threshold voltage for n-substrate Figure 3. 12. illustrates the effect of different biomolecule shifts in threshold voltage for n-substrate Figure 3. 13. illustrates the effect of different biomolecules on leakage current for n-substrate channel DM-THMG -GAA-JL-NWFET at (VGS = 1.0V and VDS = 0.05V) [59].....80 Figure 3. 14. illustrates the effect of different biomolecules on leakage current shift for n-substrate Figure 3. 15. illustrates the effect of different biomolecules on leakage current shift and switching ratio for n-substrate channel DM-THMG -GAA-JL-NWFET at (VGS = 1.0V and VDS = 0.05V) [59]. .....82 Figure 3. 16. illustrates the effect of different biomolecules on leakage current shift and switching ratio for n-substrate channel DM-THMG -GAA-JL-NWFET at (VGS = 1.0V and VDS = 0.05V) [59]. .....83 Figure 3. 17. illustrates sensitivity(SIOFF) comparison DM-THMG -GAA-JL-NWFET with available Figure 3. 18. illustrates impacts of biomolecules on (a) Transconductance (gm) log file and (b) Output conductance (gd) for DM-THMG -GAA-JL-NWFET biosensor[59].....85 Figure 3. 19. illustrates impacts of biomolecules on (a) intrinsic voltage gain (gm/gd) log file and (b) output resistance (1gd) for DM-THMG -GAA-JL-NWFET biosensor [59]......86

#### **Chapter-4**

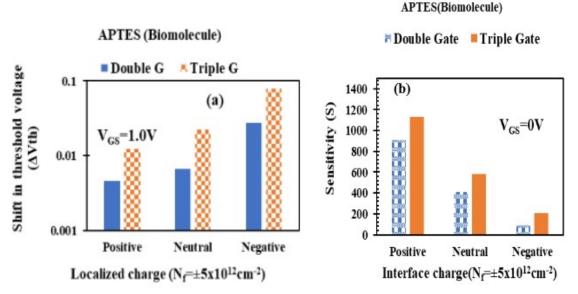

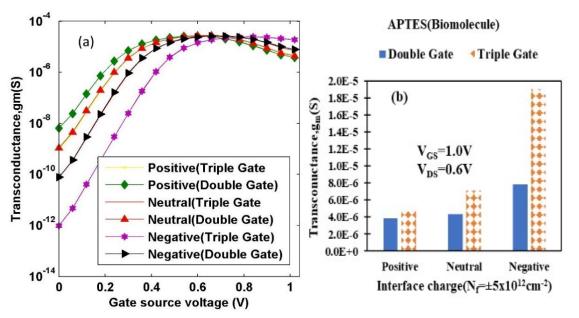

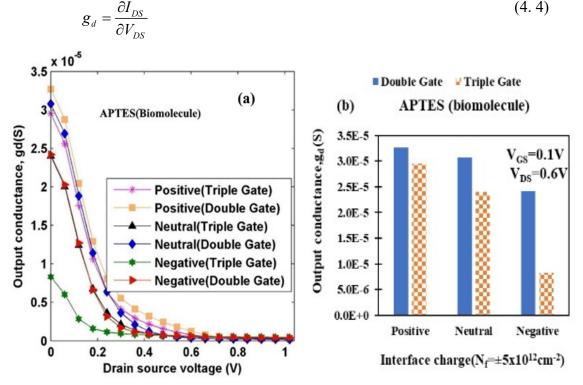

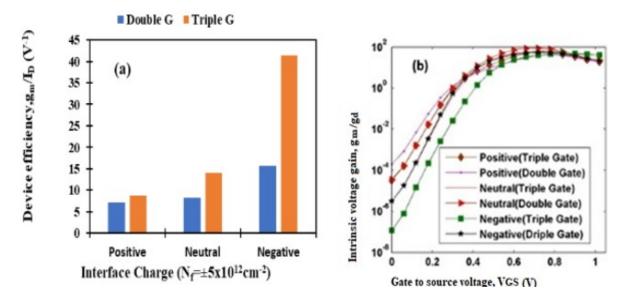

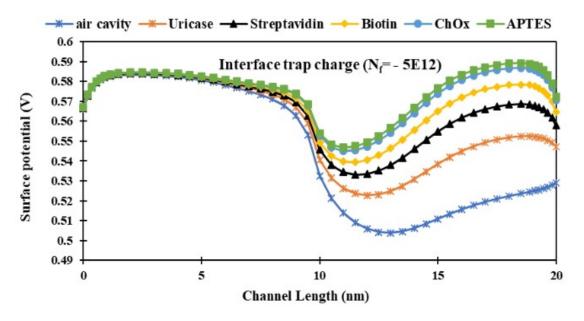

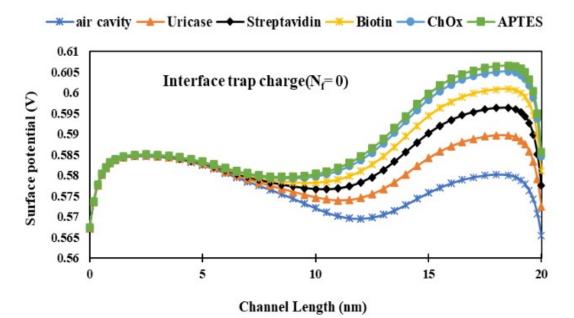

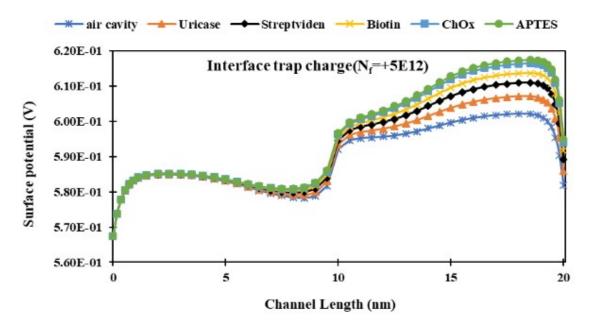

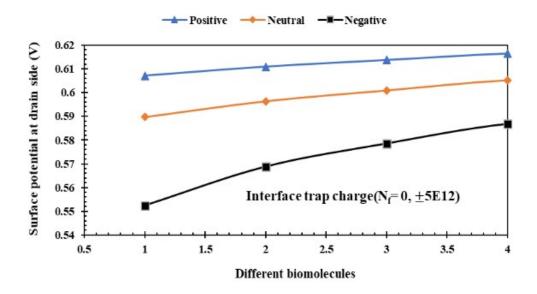

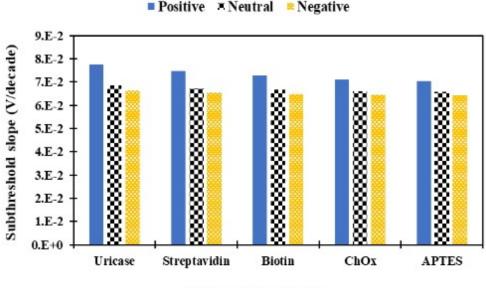

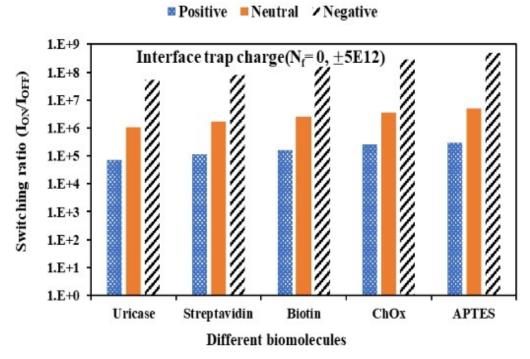

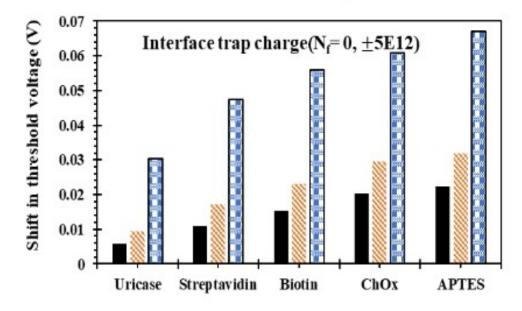

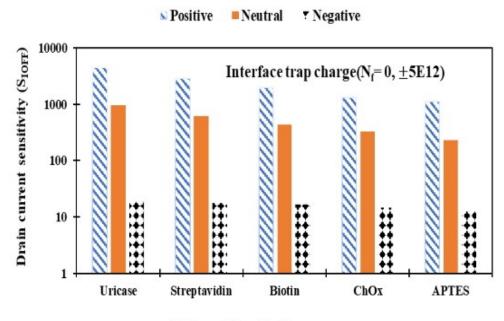

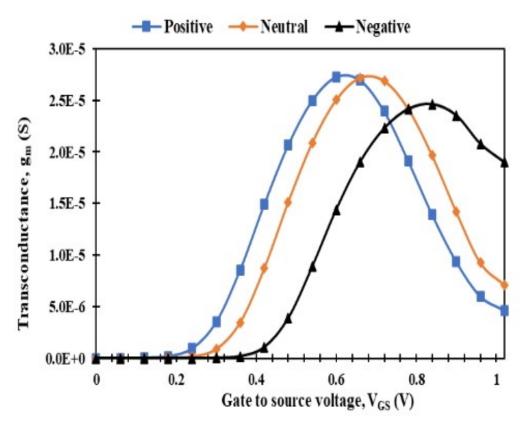

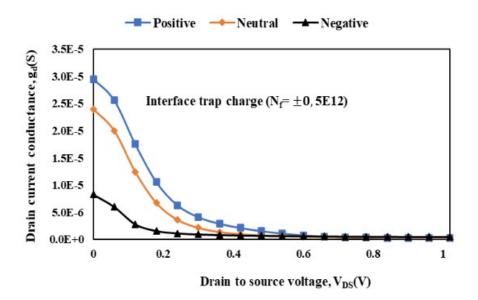

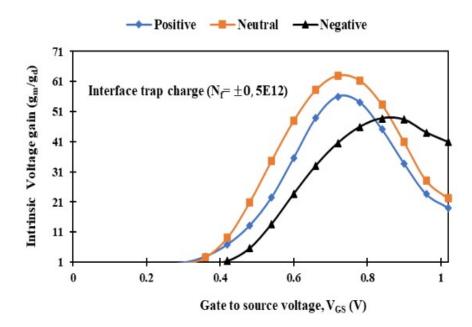

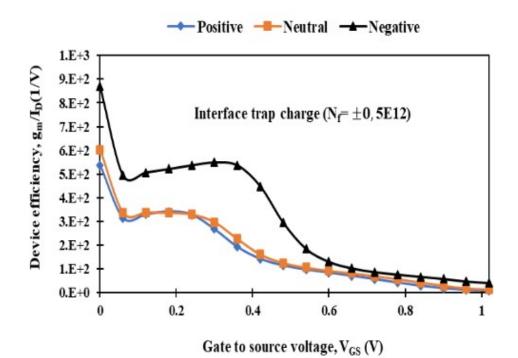

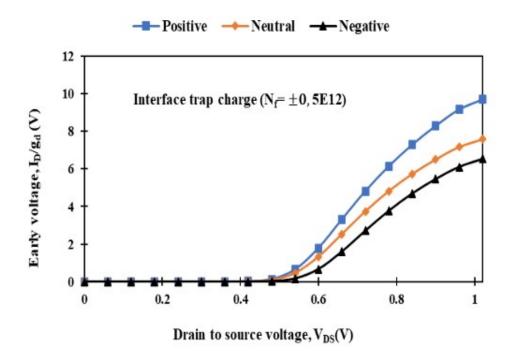

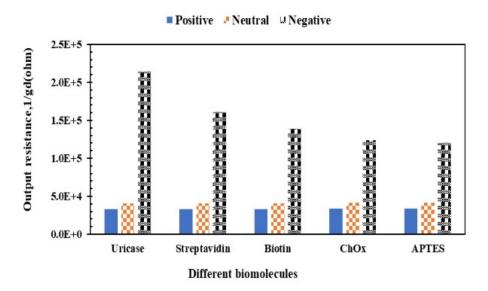

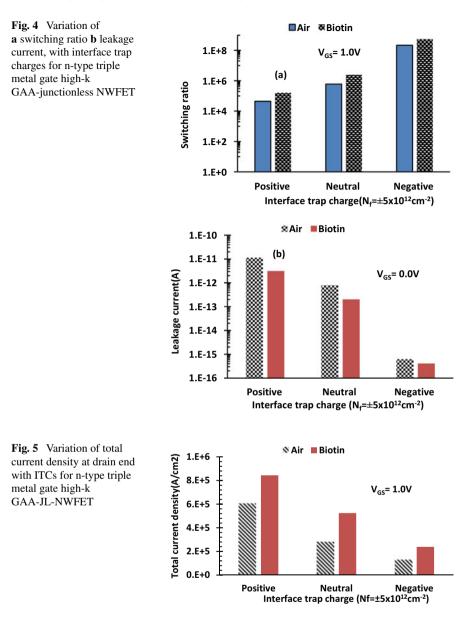

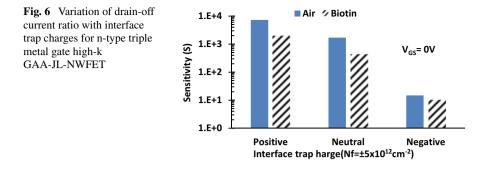

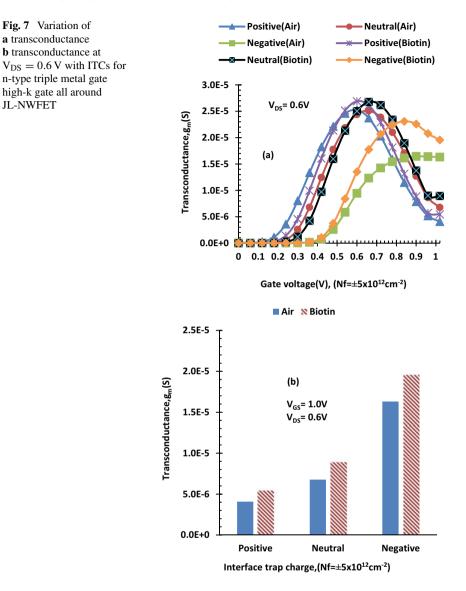

Figure 4. 8. Variation of output conductance along ITCs for n-type double and triple hybrid metal gate Figure 4.9. Variation of (a) device efficiency and (b) intrinsic voltage gain along ITCs for n-type double and triple hybrid metal GAA-JL NWFET, (VDS = 0.6V and VGS = 1.0V)......109 Figure 4. 10. Describes the effect of different biomolecules on surface potential as a function of channel length in the case of negative ITC for n-substrate THM-GAA-JL-NWFET[2], (VGS = 1.0V and VDS = Figure 4. 11. Describes the effect of different biomolecules on surface potential as a function of channel length without ITC for n-substrate THM-GAA-JL-NWFET[2], (VGS = 1.0V and VDS = 0.05V). ..... 111 Figure 4. 12. Describes the effect of different biomolecules on surface potential as a function of channel length in the case of positive ITC for n-substrate THM-GAA-JL-NWFET [2], (VGS = 1.0V and VDS = Figure 4. 13. Describes the effect of interface trap charges on surface potential in the case of different Figure 4. 14. Describes the effect of different biomolecules on subthreshold slope in the case of interface trap charges for n-substrateTHM-GAA-JL-NWFET[2], (VGS = 1.0V and VDS = 0.05V). ..... 114 Figure 4. 15. Describes the effect of different biomolecules on the switching ratio in the case of interface trap charges for n-substrate THM-GAA-JL-NWFET [2], (VGS = 1.0V and VDS = 0.05V). ..... 115 Figure 4. 16. Describes the effect of different biomolecules on shift threshold voltage in the case of Figure 4. 17. Describes the effect of different biomolecules on drain current sensitivity in the case of interface trap charge for n-type THM-GAA-JL-NWFET [2], (VGS = 1.0V and VDS = 0.05V). ...... 117 Figure 4. 18. Describes the effect of localized trap charges on transconductance for n-type THM-GAA-Figure 4. 19. Describes the effect of localized trap charges on drain conductance for n-type THM-GAA-Figure 4. 20. Describes the effect of localized trap charges on intrinsic voltage gain for n-type triple Figure 4. 21. Describes the effect of localized trap charges on device efficiency for n-type THM-GAA-Figure 4. 22. Describes the effect of localized trap charge on early voltage for n-type THM-GAA-JL-Figure 4. 23. Describes the effect of different biomolecules on output resistance in the case of interface trap charges for n-type THM-GAA-JL-NWFET [2], (VGS = 1.0V and VDS = 0.05V)......122

## Chapter-5

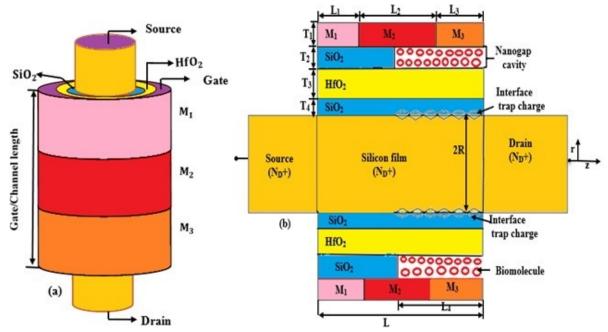

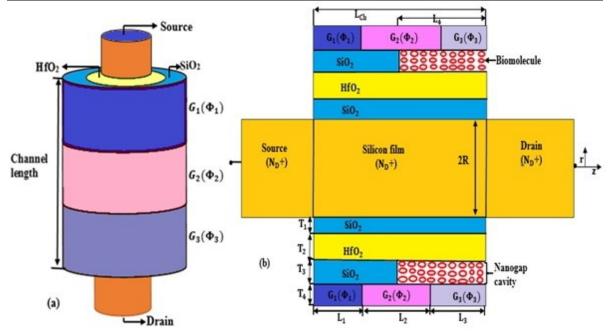

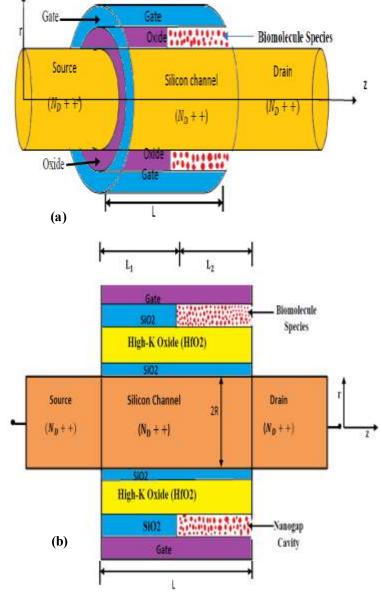

| Figure 5. 1. Illustrates (a) 3D representation diagram and (b) 2D view of n-type triple hybrid metal gate    |

|--------------------------------------------------------------------------------------------------------------|

| dielectric modulated gate all around JL-NWFET                                                                |

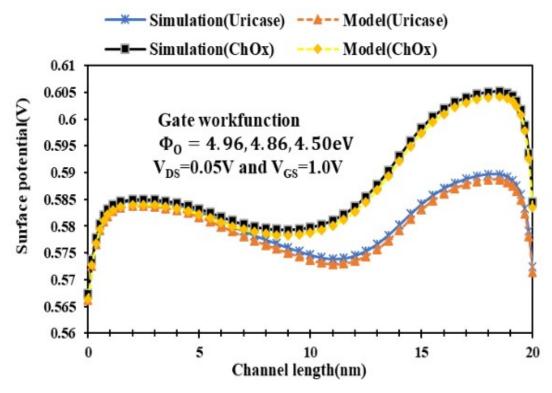

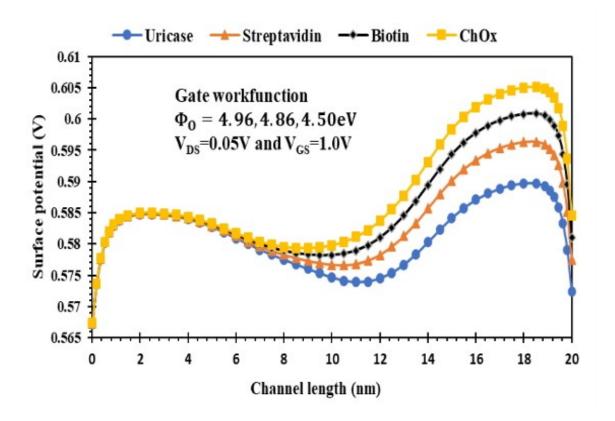

| Figure 5. 2. Illustrates analytical and simulating results of surface potential along the channel for n-type |

| THM GAA-JL-SiNWFET, (VGS = 1.0V and VDS = 0.05V)140                                                          |

| Figure 5. 3. Illustrates impact of different biomolecules on surface potential along the channel for n-type  |

| THM GAA-JL-SiNWFET, (VGS = 1.0V and VDS = 0.05V)141                                                          |

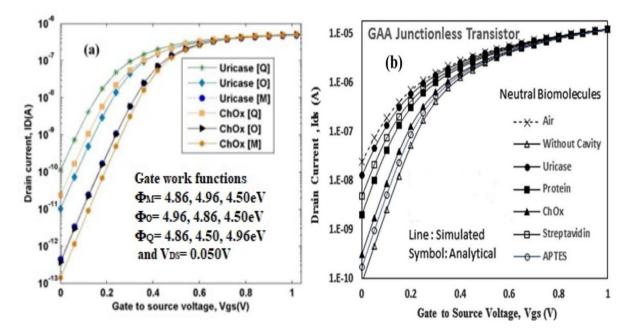

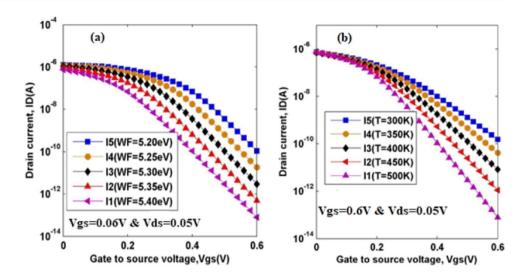

| Figure 5. 4. Effect of different gate electrode work-function and dielectric materials on ID-VG and (a)      |

| proposed device and (b) referenced work [55] biosensor devices, (VDS = 0.05V)                                |

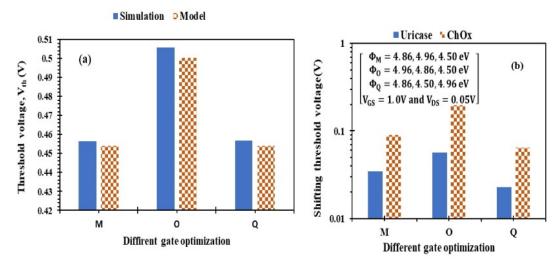

| Figure 5. 5. Effect of different gate engineering on (a) threshold voltage and (b) shifting                  |

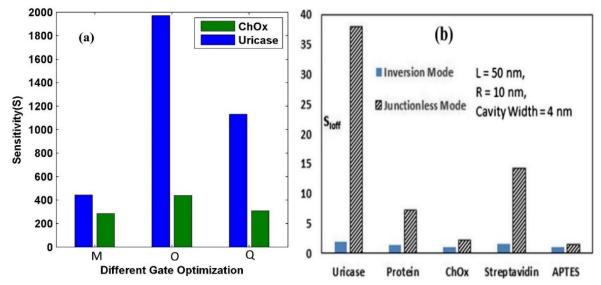

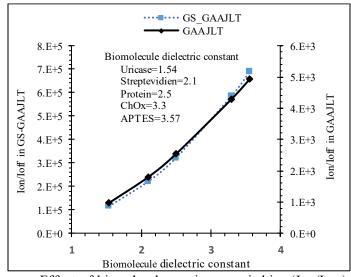

| Figure 5. 6. Sensitivity parameter (SIOFF) for (a) THM GAA-JL-SiNWFET device and (b) existing                |

| work[55], VGS = 1.0V and VDS = 0.05V)                                                                        |

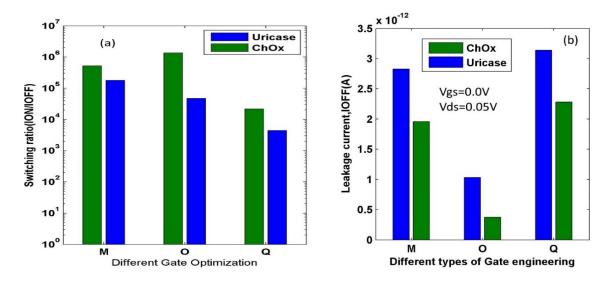

| Figure 5. 7. Impact of different gate engineering on (a) switching ratio and (b) leakage current in the case |

| of uricase and ChOX biomolecules for n-type THM GAA-JL-NWFET, (VDS = $0.05V$ and VGS = $1.0V$ ).             |

|                                                                                                              |

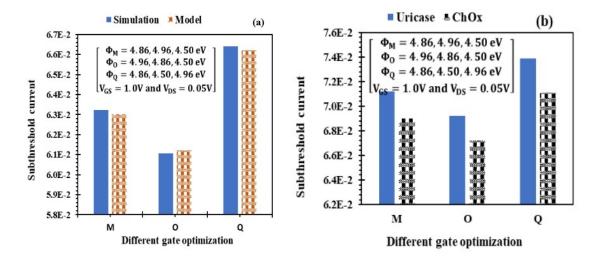

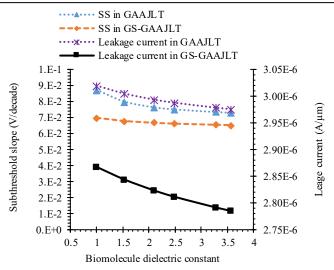

| Figure 5. 8. Effect of different gate engineering on (a) analytical and simulation result of subthreshold    |

| slope and (b) variation of subthreshold slope in the case of uricase and ChOX biomolecules for n-type        |

| THM GAA-JL-NWFET, (VDS = 0.05V and VGS = 1.0V)146                                                            |

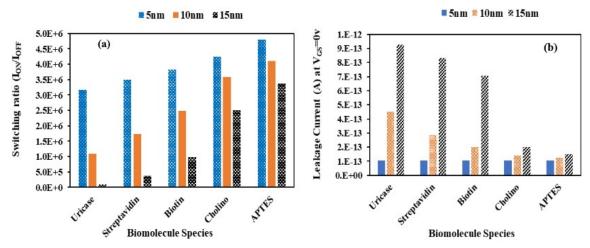

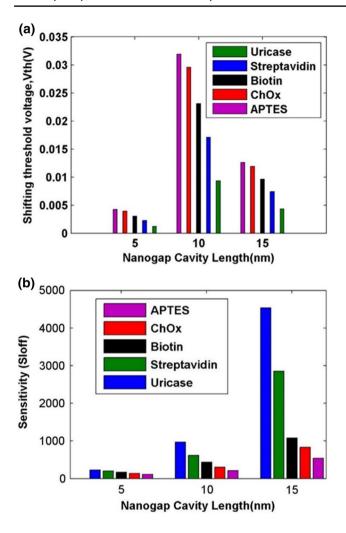

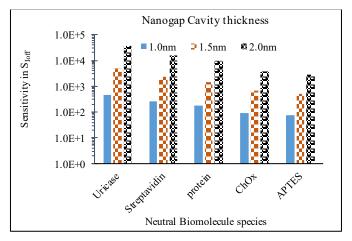

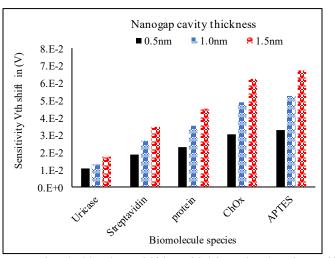

| Figure 5. 9. Directs the impact of nanogap cavity length variation on (a) switching ratio and (b) leakage    |

| current in the case of different biomolecules in n-type THM GAA-JL-NWFET, (VDS =                             |

| 0.05V and VGS = 1.0V)                                                                                        |

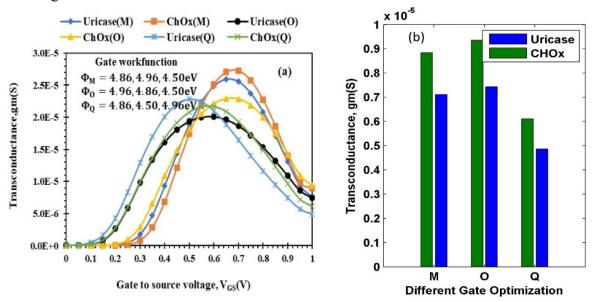

| Figure 5. 10. Effect of different gate engineering on transconductance (a) with gate voltage and (b) at      |

| (VDS = 0.6V  and  VGS = 1.0V) in the case of including uricase and ChOX biomolecules for n-type THM          |

| GAA-JL-NWFET148                                                                                              |

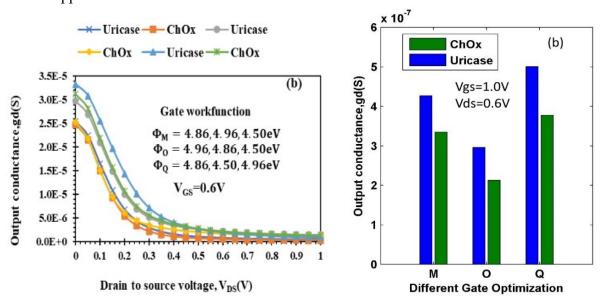

| Figure 5. 11. Effect of different gate engineering on (a) Drain conductance as a function of gate voltage    |

| and (b) at $(VDS = 0.6V \text{ and } VGS = 1.0V)$ for n-type THM GAA-JL-NWFET149                             |

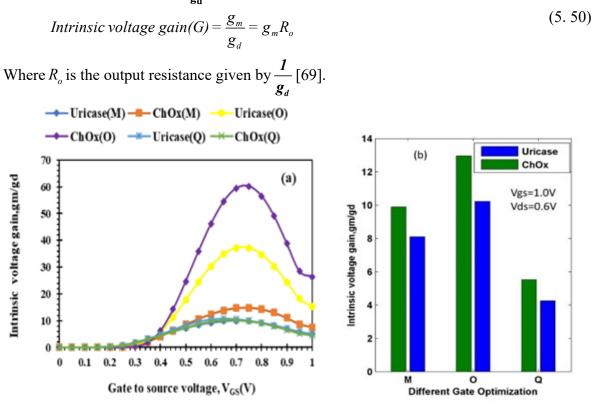

| Figure 5. 12. Effect of different gate engineering on (a) intrinsic voltage gain vs gate voltage and (b) at  |

| (VDS = 0.6V and VGS = 1.0V) for n-type THM GAA-JL-NWFET150                                                   |

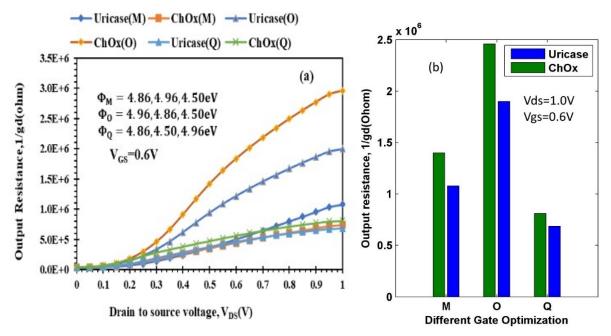

| Figure 5. 13. Impact of different gate engineering on (a) output resistance vs gate voltage and (b) at       |

| (VDS = 0.6V and VGS = 1.0V) for n-type THM GAA-JL-NWFET151                                                   |

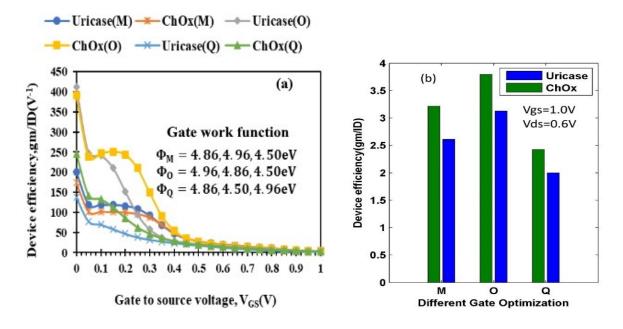

| Figure 5. 14. Effect of different gate engineering on (a) device efficiency vs gate voltage and (b) at       |

|                                                                                                              |

| (VDS = 0.6V and VGS = 1.0V) for n-type THM GAA-JL-NWFET152                                                   |

## **List of Tables**

## Chapter-1

| Table 1. 1: High-performance logic design requirements table. Information obtained from the 2003 ITRS. |

|--------------------------------------------------------------------------------------------------------|

|                                                                                                        |

| Table 1. 2: Shows different models available in ATLAS to model various physical phenomena [115]26      |

#### Chapter-2

| Table 2. 1: Physical parameter setting for simulation structure                                   |  |

|---------------------------------------------------------------------------------------------------|--|

| Table 2. 2: Palladium electrode gate sensitivity comparison shows the p-channel substrate of bulk |  |

| MOSFET, GAA-MOSFET, and cylindrical JL-SiNWFET56                                                  |  |

## Chapter-3

Table 3. 1: Designed parameters of GAA-JL-NWFETs with double and triple hybrid metal gates.

### Chapter-4

| <b>Table 4. 1:</b> Describes the proposed device structural parameters                                 |

|--------------------------------------------------------------------------------------------------------|

| Table 4. 2: Impact of localized charges on IOFF, ION, and ION/IOFF for different biomolecules (Uricase |

| $\epsilon = 1.54$ , Biotin $\epsilon = 2.10$ , and APTES $\epsilon = 3.57$ )                           |

### Chapter-5

| Table 5. 1: Designed parameters for THM-high-k GAA-JL-SiNWFE.         Table 5. 2: Model parameters applied in the simulations [47]. |       |

|-------------------------------------------------------------------------------------------------------------------------------------|-------|

| Table 5. 3: Constant parameters applied in this simulation [47].                                                                    | . 135 |

| Table 5. 4: Illustrates dielectric constants for different biomolecules[45].                                                        | . 140 |

| Table 5. 5: Summarizes a comparison between the performance indicators for the two dielectric mate                                  | rials |

| (uricase and ChOX) for n-type THM GAA-JL-NWFET at a constant gate-to-source voltage (VGS = $1$ .                                    | .0V). |

|                                                                                                                                     | .152  |

## **Nomenclature / Terminology**

| GIDL            | Gate-induced-drain leakage                          |

|-----------------|-----------------------------------------------------|

| DIBL            | Drain-induced-barrier-lowering                      |

| DGJLT           | Double-gate-junctionless-transistor                 |

| DGJLI           |                                                     |

|                 | Double-layer gate stack                             |

| EOT             | Effective oxide thickness                           |

| GAA             | Gate all around                                     |

| SiNW            | Silicon Nanowire                                    |

| IM              | Inversion-mode                                      |

| JLT             | Junctionless transistor                             |

| LPCVD           | Low-pressure-chemical-vapor-deposition              |

| MOSFET          | Metal-oxide-semiconductor field-effect transistor   |

| Mug-FET         | Multiple gate field effect transistor               |

| SCEs            | Short channel effects                               |

| SOI             | Silicon on insulator                                |

| SS              | Subthreshold swing                                  |

| CLM             | Channel length modulation                           |

| V <sub>th</sub> | Threshold Voltage                                   |

| V <sub>GS</sub> | Gate source Voltage                                 |

| DGMOS           | Double-gate metal-oxide-semiconductor               |

| V <sub>DS</sub> | Drain Source Voltage                                |

| ITRS            | International roadmap for semiconductors            |

| BTBT            | Band to band tunneling                              |

| TCAD            | Technology computer-aided design                    |

| TFET            | Tunnel field-effect transistor                      |

| High-K          | High dielectric material/high dielectric gate oxide |

| CMOS            | Complementary metal oxide semiconductor             |

|                 | 1 J                                                 |

## Abstract

Continuous market demand drives device engineers to create Integrated Circuits (ICs) with low power dissipation and low fabrication complexity. Nanoelectronics technology is approaching the atomic/physical device limits due to the increasing demands of semiconductor chips. Significant technological development has been in the integrated circuit industry over the past few decades. Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is a crucial Integrated Circuits (IC) component. The integrated circuit doubled the number of on-chip transistors every generation, reducing physical device size. It has attracted numerous novel structures and MOSFET devices. However, scaling presents numerous challenges as it approaches the nanometre regime. It causes threshold voltage roll-off, short channel effect (SCEs), increases body-bias impact, and other negative consequences. SiO<sub>2</sub> gate oxides, in particular, have already reached a few atom lengths and thicknesses, resulting in increased power dissipation due to the quantum mechanical tunnelling effect.

Therefore, new materials and novel device architectures are necessary to guarantee the final scaling in device dimensions and sustain the anticipated performance benefit from the scaling. One of the most promising device architectures for extending the scaling of the CMOS device is the Gate All Around (GAA) MOSFET, which provides better hot carrier reliability than the Bulk MOSFET due to improved gate control and the best electrostatic control of the channel. Serious challenges with the device and circuit dependability are caused by scaling trends in MOSFETs, operating constraints, process damage, and radiation damage. At the Si-SiO<sub>2</sub> interface of the MOSFET, all of these degradation mechanisms lead to the formation of interface traps and localized charges. For instance, hot-carrier-induced deterioration in the form of interface traps in nanoscale MOSFETs caused by impact ionization in the channel near the drain junction has become a significant reliability issue since it reduces the design margin for circuits. Even a minuscule amount of interface traps/charges might negatively impact the device's performance due to the rising integration density of integrated circuits and the reduction in device size. Understanding MOSFET-level degradation, developing analytical models that include the effects of interface charges, and investigating new device architectures and techniques that are selfsufficient in preventing the formation of interface traps are crucial for improving overall design efficiency.

Newly designed device structure, like multi-gate architecture, helps reduce leakage currents, interface trap charges, and other detrimental short-channel effects. For instance, the Gate All

Around (GAA) structure is considered to be one of the best multiple gate structures as it shows better gate controllability, suppressed floating body effect, and excellent CMOS compatibility, even at the nanoscale regime. Also, in short-channel devices, the fabrication complexity due to a steep source/drain and channel junctions is difficult. Other impacts like short channel effects and hot carriers are undesirably increasing when device design goes near and below the 20nm technology node. As a result of these factors, the junctionless transistor has been developed as a superior replacement for the junction-based transistor in addition to its remarkable properties. Since the source, channel, and drain regions are all uniformly strongly doped, no junctions can form, resolving the problem of impurity diffusion. With this in mind, a novel Junctionless Surrounding metal Gate Stack Nanowire FET Sensor device was designed to incorporate multigate MOSFETs' advantages for high-sensing applications. This thesis investigates the sensitivity of junctionless gate stack Gate All Around NWFET devices and how they behave when subjected to hot carrier-induced interface localized charges. For instance, impact of localized charge on device electrical characteristics, such as I<sub>OFF</sub> switching ratio, drain currents, transconductance (g<sub>m</sub>), output conductance (g<sub>d</sub>), surface potential, intrinsic voltage gain, output resistance, device efficiency, and device sensitivity (shifting threshold voltage and subthreshold current ratio) have been examined.

A 2D analytic model was also developed for surface potential, drain current and threshold voltage using the superposition theorem by applying the boundary conditions and validating at different silicon film radius channel lengths. The analytical model has been validated at different channel lengths and silicon film radii. The effect of varying gate work functions (gate optimization technique) on the performance of the device sensitivity was also studied. In addition to localized charge, the gate leakages seriously hamper the device performance at shorter channel lengths and impact the device sensitivity or performance; Due to this, a novel device architecture, "cylindrical Metal Gate (CMG) Dielectric Engineered (DE) JLNWFET," was developed to improve device efficiency and sensitivity. In this direction, high Channel uniformly doping single/ dual/triple hybrid gate material engineering GAA NWFETsensors were designed to enhance their current driving capability and transconductance without increasing the electric field at the drain side. When MOS devices are utilized in sensing applications, the dielectric, which determines the performance and reliability of the device, also plays a crucial role. In this work, gate stack metal gate electrode GAA JL NWFET for various sensing applications has been investigated. Gate stack GAA JL NWFET with catalytic metal gate is studied for its use as a hydrogen gas sensor. Gate stack GAA JL NWFET with a nanocavity region for dielectric has

been investigated for dielectric modulation-based biosensor applications. Also, an analytical model for gate stack GAA JL NWFETs with varied gate electrode engineering is established to study the impact of different gate electrodes on the performance of Gate stack GAA JL NWFET devices; analytical results are verified with device simulation results. Gate stack GAA JL NWFET shows much higher sensitivity for biosensing and hydrogen gas sensing in the subthreshold region as compared to conventional bulk MOSFET. The junctionless gate stack GAA NWFET' is a promising device architecture for creating a low-power, extremely sensitive, and nanoscale CMOS-compatible biosensor and hydrogen gas sensor due to its high surface-to-volume ratio, low leakage current, and almost optimal subthreshold slope (SS) close to (60 mV/decade).

## **List of Publications**

#### Articles in International Journal:

- Mekonnen Getnet and Rishu Chaujar, "Sensitivity Investigation of Junctionless Gateall-around Silicon Nanowire Field-Effect Transistor-Based Hydrogen Gas Sensor," <u>Silicon Journal</u>, Vol.15, pp.609-621, Springer (SCIE, IF-2.941), 2022.

- Mekonnen Getnet and Rishu Chaujar, "Sensitivity Analysis of Biomolecule Nanocavity Immobilization in a Dielectric Modulated Triple-Hybrid Metal Gate-All-Around Junctionless NWFET Biosensor for Detecting Various Diseases", <u>Journal of Electronic Materials</u>, Vol.51, No.5, pp.2236-2247. Springer (SCIE, IF-<u>2.047</u>), 2022.

- Mekonnen Getnet and Rishu Chaujar, "Numerical Modelling for triple hybrid gate optimization dielectric modulated junctionless gate all around SiNWFET based uricase and ChO<sub>X</sub> biosensor," *Journal of Electronic Materials (Springer)*, Submitted, 2023.

- Mekonnen Getnet and Rishu Chaujar, "Effect of trap charges on Dielectric Modulated Triple Hybrid Metal Gate Junctionless Gate All Around Silicon Nanowire FET based APTES & Biotin Biosensor", <u>Silicon Journal (Springer)</u>, (Submitted), 2023.

#### International Conference Proceedings:

- Mekonnen Getnet and Rishu Chaujar, "TCAD Analysis and Modelling of Gate-Stack Gate All Around Junctionless Silicon NWFET-Based Bio-Sensor for Biomedical Application," 2<sup>nd</sup> International Conference on IEEE VLSI Device, Circuit, and System (VLSI-DCS), on July 18<sup>th</sup> -19<sup>th</sup>, 2020.

- Mekonnen Getnet and Rishu Chaujar, "Interface Trap Charge Analysis of Junctionless Triple Metal Gate High-k Gate All Around Nanowire FET-Based Biotin Biosensor for Detection of Cardiovascular Diseases," 7<sup>th</sup> International Conference on Microelectronics, circuits, and systems, on July 25<sup>th</sup> -26<sup>th</sup>, 2020.

#### **Book Chapter Contribution:**

- Mekonnen Getnet and Rishu Chaujar, "Demand of Low power-driven FET as Biosensors in Biomedical applications," published in <u>CRC Press Taylor & Francis</u> <u>Group, USA</u>, <u>pp.255-272</u>, 2022.

- 2. Mekonnen Getnet and Rishu Chaujar, "TFET: "Operation Principle and Fabrication of TFET," Under Production in <u>Wiley</u>, 2023.

- **3.** Mekonnen Getnet and Rishu Chaujar, "Fundamental of Emerging Nano-Materials (Graphite, Graphene, CNT, Insulators and High-k Materials and Perovskite Materials including their applications)," Under Production in <u>Springer Nature</u>, 2023.

## **CHAPTER -1**

#### **1.1 Introduction**

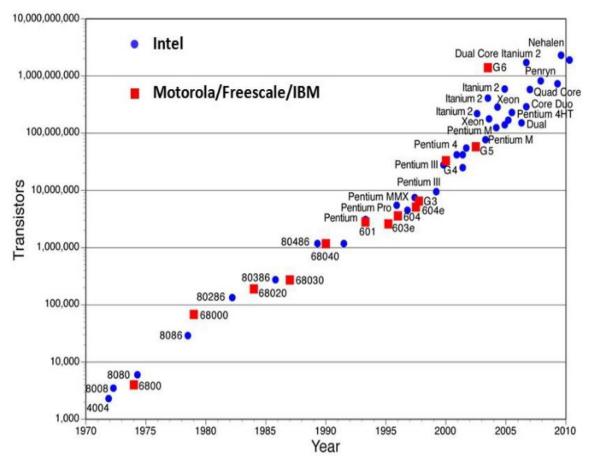

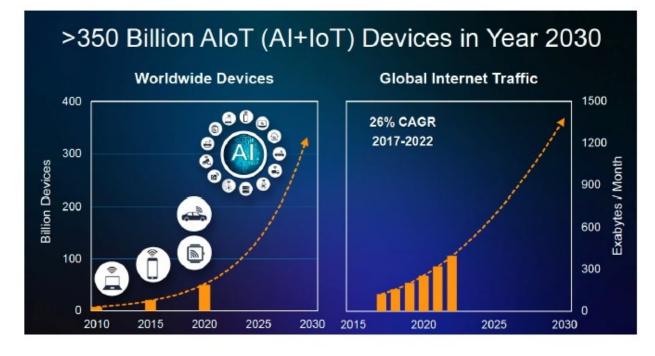

The international economy has been driven by computing and communication technology over the last decade. The electronics industry currently accounts for more than 10% of the global economy, and this number is continuously rising[1]. In 1947, Bell Labs' own Bardeen, Brattain, and Shockley developed the first solid-state device, a bipolar point-contact transistor on a Germanium (Ge) substrate[2]. This development marked the beginning of a revolution in the semiconductor industry. Bipolar transistors have almost been superseded by complementary metal oxide semiconductor (CMOS) field-effect transistors due to the former's reduced power consumption and technological advantages. Gordon Moore stated in 1965 that with improved characteristics, the number of transistors per chip would double every 18 months[3]. Interestingly, as illustrated in Figure 1. 1, the semiconductor manufacturing industry has proven this rule over five decades. With lower dimensions for higher packing density, ultralow power dissipation, and higher circuit speed, CMOS technology has established itself as the industry standard. Over the past few decades, the IC industry has expanded astronomically due to MOS transistors' rapid and ongoing scaling [4]. As illustrated in Figure 1. 2, industry consumers raised their need for faster data rates, which supported the demand for additional electronic devices[5]. However, as transistor dimensions continue to reduce in order to attain better dynamic read-only memory (DRAM) chip density and microprocessor speed, conventional single-gate MOSFETs encounter performance problems due to short channel effects and gate leakage currents[6]. When conventional MOSFETs are downscaled to the submicrometer range, the device size and isolation length roughly match the depletion widths, which causes short channel effects (SCE), which can have serious consequences, including reducing the threshold voltage and increasing substrate bias effect[7]. Due to short channel effects and gate leakage currents, conventional single-gate MOSFETs struggle to meet the needed performance as transistor dimensions continue to shrink to attain greater DRAM chip density and microprocessor speed[8]. Gate control, current output, the power-to-performance ratio, and variation and dependability are some of the challenges associated with scaling the device down to a technology node smaller than 22 nm [9]. The gate control challenges are the SCEs (which include gate-induced drain leakage, drain-induced barrier lowering, and subthreshold slope degradation, amongst other things) that produce unacceptable leakage and subthreshold characteristics [10]. When the MOS downscaling approaches the fundamental limitations, unique materials and novel device architectures are required to achieve the ultimate scale in device dimensions and preserve anticipated performance gain [11]. For low-power applications, Gate All Around (GAA) MOSFETs have proven to be the most promising device structure for extending the scaling of the CMOS device due to their superior intrinsic RF scaling capability, excellent subthreshold characteristics, and excellent electrostatic control [12]. In addition to resilience to short-channel effects, tunnelling and reliability are critical concerns for nanoscale devices[13]. Device performance deterioration caused by interface traps resulting from hot carrier/radiation/process damage poses major reliability concerns[14]. Therefore, it is necessary to address these reliability challenges to estimate and optimize device

performance deterioration. The current delivered through the channel must be raised to improve device performance for each technological generation[15]. The industry has developed methods for improving mobility, such as strained silicon, an alternative gate electrode, and even substitute channel materials like silicon or germanium nanowires. GAA MOSFETs are being evaluated for numerous sensing applications due to their effective gate control and excellent surface-to-volume ratio. This chapter discusses various scaling challenges, like short-channel effects and different engineering schemes to reduce those challenges. **Figure 1.1** illustrates Moore's law by plotting transistor counts (number) versus product launch dates. According to the graph, the count increases by a factor of two every two years [16].

Figure 1. 1. illustrates Moore's law by plotting transistor counts (number) versus product launch date [16].

## **1.2 MOSFET Scaling (Review Literature)**

Silicon CMOS has developed as the dominating technology in the microelectronics industry over the last 25 years[17]. Over several technological generations, the concept of device scaling has been constantly implemented, resulting in consistent improvements in device density and performance. The scaling pattern outlined in the ITRS roadmap (ITRS97) is shown in **Table 1.1** [18].

| Year in Production                  | units             | 2007               | 2008               | 2009               | 2010               | 2012               | 2013               | 2015               | 2016               | 2018               |

|-------------------------------------|-------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

| Physical Gate Length                | nm                | 25                 | 22                 | 20                 | 18                 | 14                 | 13                 | 10                 | 9                  | 7                  |

| EOT (Equivalent<br>Oxide Thickness) | А                 | 9                  | 8                  | 8                  | 7                  | 7                  | 6                  | 6                  | 5                  | 5                  |

| Gate Layer Thickness value          | А                 | 4                  | 4                  | 4                  | 4                  | 4                  | 4                  | 4                  | 4                  | 4                  |

| Gate Dielectric<br>Thickness Value  | А                 | 13                 | 12                 | 12                 | 11                 | 11                 | 10                 | 10                 | 9                  | 9                  |

| Maximum Gate<br>Leakage Limit       | A/cm <sup>2</sup> | 9.3E <sup>+2</sup> | 1.1E <sup>+3</sup> | 1.2E <sup>+3</sup> | 1.9E <sup>+3</sup> | 2.4E <sup>+3</sup> | 7.7E <sup>+3</sup> | 1.0E <sup>+4</sup> | 1.9E <sup>+4</sup> | 2.4E <sup>+4</sup> |

| Power Supply Voltage                | V                 | 1.1                | 1                  | 1                  | 1                  | 0.9                | 0.9                | 0.8                | 0.8                | 0.7                |

| Saturation Threshold<br>Voltage     | V                 | 0.18               | 0.17               | 0.16               | 0.15               | 0.14               | 0.11               | 0.12               | 0.10               | 0.11               |

| Source/Drain Leakage<br>Current     | uA/um             | 0.07               | 0.07               | 0.07               | 0.1                | 0.1                | 0.3                | 0.3                | 0.5                | 0.5                |

**Table 1. 1.** High-performance logic design requirements table. Information obtained from the 2003 ITRS.

Source: 2020 IEEE ISSCC, Cisco VNI Global IP Traffic Forecast 2017-2022

Figure 1. 2. Depicts the need for increased data speeds while simultaneously increasing demand for billions of devices [18].

#### 3.2.1 Reasons for scaling

- Scaling down the MOSFET device enables the integration of additional transistors on a single chip, increasing the chip's packing density. This is especially significant in modern semiconductor technologies, with limited chip space. This opens up the possibility of making larger chips with greater functionality in the same space [3], [19] or smaller chips with the same functionality.

- Better performance can be achieved as a result of the fact that smaller devices often have shorter channel lengths. This, in turn, leads to faster switching speeds and enhanced performance.

- When MOSFET devices are shrunk in size, the operating voltage drops along with it, resulting in lower power usage.

- Scaling down MOSFET devices is a logical development in the history of semiconductor technology since they are compatible with modern fabrication techniques, which makes it easier to build smaller devices with higher accuracy [19], [20].

In general, scaling down MOSFET devices enables improved performance, increased packing density, lower power consumption, decreased cost, and compatibility with advanced production techniques. Because of these benefits, it has become an integral component of semiconductor technology.

These developments are causing an uptick in the need for portable systems with high processing and integration capacity. However, as MOSFETs are shrinking to deep submicron dimensions, the integrated circuit industry is finding it increasingly challenging to continue scaling at the same rate it has in the past. This is due to the small dimensions and the fact that certain vital devices, materials, and process limits are being approached[18]. Moreover, new materials with their learning curves for production will likely be introduced at future technology nodes, complicating scaling at these nodes even further. For instance, the need for low voltages and the complexity of the device fabrication process limit the size reduction of MOSFET transistors[21]. Excessive gate leakage current, boron penetration from the P+ polysilicon gate electrode into the MOSFET channel, and the growing destructive impact of polysilicon depletion in the polysilicon gate electrodes are all issues that have arisen as a result of the shrinking gate dielectric thickness[18]. In addition, projections show that as transistor sizes get smaller, the electron and hole mobility in the inversion layer will drop below what is required to achieve the desired transistor performance. Finally, the conventional planar bulk MOSFET itself will likely become insufficient to meet transistor requirements, mainly due to the difficulty in effectively controlling short-channel and quantum effects and statistical variability for very small transistors. To address these issues, numerous technological innovations were being explored (termed "potential solutions" in the ITRS)[20]. The development and implementation of these technological innovations into manufacturing will necessitate substantial improvements to computational modelling and characterization techniques and capabilities. Also, it won't be easy to achieve the required precision and accuracy in measuring the increasingly miniaturized transistor dimensions[18]. For instance,

the generation of traps, interface states, fixed charges, and defects in the oxide bulk or at the Si-SiO<sub>2</sub> interface is a common source of reliability issues in addition to heat removal and cooling becoming worse because the magnitude of power dissipated per unit area is increased[22]. Interface charges can be caused by various damage mechanisms, including but not limited to stress-induced damage, process-induced damage, damage caused by heat carriers, and damage caused by radiation [23]. As a result, understanding the degradation of CMOS devices and circuits due to various types of damage (e.g., radiation damage, stress/hot carrier/process damage) is required for the successful use of CMOS-based circuits. Therefore, a brief review of scaling challenges (short-channel effects) and their device implications is needed. The following section examines the various short-channel effects raised due to deep submicron dimensions MOSFET scaling.

#### **1.3 Short Channel Effects in MOSFETs**

A MOS transistor is considered short when its effective channel length ( $L_{eff}$ ) is less than or equal to the depletion width of its source and drain junctions. In this instance, the potential distribution in the channel is influenced not only by the device's standard electric field but also by the device's lateral electric field. As a result, the channel area of a short-channel MOSFET is affected by the source/drain (S/D) as much as it is by the gate, leading to a complex 2dimensional geometry in the depletion zone. This causes the short-channel effects listed in the following [7], [24]. Using a single gate to control the silicon region makes it challenging to eliminate these effects in ultra-short channel lengths, but it is possible to reduce them [7]. Researchers have attempted to reduce them using various techniques such as channel engineering, gate engineering, implementing different architectures with different working physics, and so on.

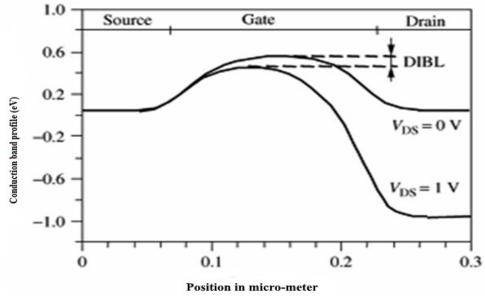

#### **1.3.1 Drain-Induced Barrier Lowering**

This phenomenon occurs when the gate voltage is less than the device's threshold voltage. As shown in **Figure 1.3**, the depletion region under the drain can lower the potential barrier from the source-to-channel junction as the voltage drop between the source and drain increases [25]. More electrons can be injected into the channel region if the barrier between the source and channel is lowered. So, the gate has less effect over the channel current, and the threshold voltage drops[26]. Because of the inherent potential between the channel and the S/D regions, the channel is depleted even before a positive bias is applied to the gate. This potential is known as inherent potential. Drain-induced barrier lowering (DIBL) [27] describes a phenomenon in which the p-n junctions between the S/D and the channel are biased in the opposite direction, amplifying this effect [27]. When the gate length is shortened, the unwanted coupling between the S/D region and the channel grows, lowering the transistor's threshold voltage [22].

Figure 1.3. Illustrates Drain-Induced Barrier Lowering (DIBL) [29].

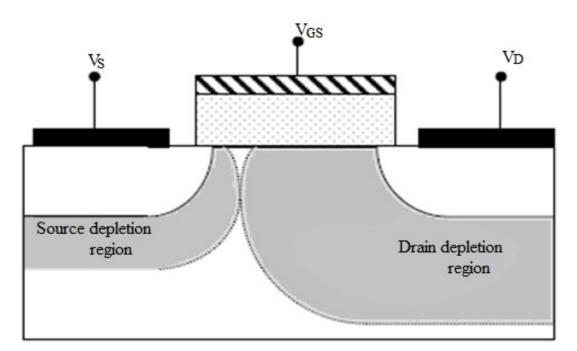

#### 1.3.2 Punchthrough

A punch-through occurs when the source and drain depletion regions meet [30]. When the depletion areas cross, as shown in **Figure 1.4**, space-charge-limited current flows between the drain and the source. The drain bias and substrate doping are both critical for punch-through. The main reason for transistor punch-through is that current transport occurs deeper within bulk and away from the gate, leading to increased subthreshold leakage current and increased power consumption [19]. Punchthrough current (subthreshold leakage current) is highly sensitive to source/drain junction depths and applied drain voltage [19]. To prevent punch-through, higher substrate doping and spatially restricted dopant implantations, such as halo or pocket implantations, are required [31]. On the other hand, a higher doping level would result in a more significant rise in the tunnelling current that flows between the source and drain p-n junctions and the substrate [32].

Figure 1.4. Illustrates a schematic diagram for punch-through [30].

The depletion region can be made smaller by reducing the drain bias to prevent punch-through, higher substrate doping is required [31].

#### **1.3.3 Higher Subthreshold Conduction**

Subthreshold conduction is the term used to describe the flow of current between the source and drain of a MOSFET while the transistor is operating in the subthreshold area, which is also referred to as the weak-inversion region. This current is also known as subthreshold leakage or subthreshold drain current. This phenomenon occurs when the voltage from the gate to the source is less than the threshold voltage [24], [27]. As MOSFET geometries get smaller, the gate voltage that can be used must also decrease to keep the devices reliable. Reducing the MOSFET's threshold voltage is also essential to maintain performance. When the threshold voltage of a transistor is lowered, the available voltage swing becomes too small to allow for a complete turn-off to turn-on shift, thus leading to an increasing subthreshold current. When designing circuits, it is necessary to strike a balance between a high current in the "on" case and a low current in the "off" case [24].

#### **1.3.4 Impact Ionization and Hot Electron Effect**

The process by which one energetic charge carrier in a material loses energy due to the formation of other charge carriers in that material is referred to as impact ionization [33]. In semiconductors, the production of an electron-hole pair occurs when an electron (or a hole) with enough kinetic energy dislodges (knocks) a bound electron from its position in the valence band and promotes it to a condition in the conduction band [34]. When a MOS device conducts in saturation, the channel injects many carriers into the drain depletion region. The high field

around the drain speeds up these carriers, and some of them, through impact ionization, become hole-electron pairs[24]. Carriers travelling from the source to the drain might receive sufficient energy to generate impact ionization, producing electron-hole pairs in silicon and overcoming the interfacial energy barrier [33], [35]. When carriers are injected into a gate dielectric, this produces device degradation, which reveals itself as a change in the threshold voltage and a reduction in the drain current [33]. As a result, the transistor lifetime is significantly shortened due to hot carrier injection (HCI). To minimize this impact, the gate oxide separating the gate and channel should be as thin as possible to boost on-state channel conductivity and performance and decrease off-state subthreshold leakage. However, electron tunnelling between the gate and channel happens with today's gate oxides, which have a thickness of about 1.2 nm, leading to increased power consumption[36].

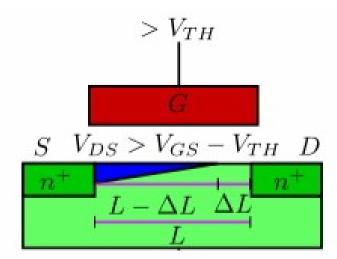

#### **1.3.5 Channel Length Modulation (CLM)**

It is helpful to visualize the MOSFET channel as consisting of two separate parts: the first part runs from the source to the saturation point, and the second component runs from the saturation point to the drain [25]. The saturation point of a channel gets closer to the source when the drain bias is increased. Thus, the effective channel length shortens, and the drain current grows even at saturation as a function of the drain voltage. The decrease in channel length is an increasing function of the V<sub>DS</sub>-V<sub>DSAT</sub>, leading to the channel length modulation (CLM) effect [26]. As can be seen in **Figure 1.5**, the pinch point in the channel shifts from the drain terminal to the source terminal. When the effective channel length ( $L_{eff} = L-\Delta L$ ) decreases, the drain current increases for a given drain to source voltage ( $V_{DS}$ )[25].

Figure 1.5. Shows channel length modulation(CLM[25].

#### **1.3.6 Velocity Saturation**

Charge carriers' velocity, such as electrons or holes, is proportional to the electric field that drives them, but this is only applicable to small fields[37]. When the field strength increases, their velocities tend to saturate. As gate length decreases, the longitudinal electric field (E) between the source and drain increases, and carrier drift velocity ( $V_D$ ) varies according to the lateral electric field[38], [39]. The rate of phonon emission increases with increasing electric

field strength, and velocity saturation occurs when the rate of energy gained from the electric field equals the rate of energy loss to the crystal via phonons[40]. So, for sufficiently high fields along the channel, the carrier velocity, ( $V = \mu E$ ), eventually saturates at a value of about 10<sup>7</sup> cm/s(for silicon channels)[27]. Here,  $\mu$  and E denote the carrier mobility and electric field, respectively[41]. Therefore, saturation velocity affects the transistors' voltage transfer characteristics greatly because, at saturation velocity, they no longer obey Ohm's law[25], [27]. This effect increases the time a MOSFETS carrier travels the channel[25].

#### 1.3.7 Gate Oxide Leakage

Because of its excellent interfacing capability with silicon material,  $SiO_2$  is a very popular gate insulator used in MOSFETs[26]. However, gate oxide thickness has already approximated to 1 nm or less due to dimension scaling for better device performance. When the gate oxide thickness is less than ~1 nm, the probability of tunnelling increases, resulting in an increase in oxide leakage current and quantum tunnelling effect [42], [43]. In recent times, to minimize direct tunnelling leakage current, high-k dielectric materials have been used[44]. To date, researchers have determined that hafnium oxide (HfO<sub>2</sub>), hafnium silicates (HfSiON), and zirconium oxides (ZrO<sub>2</sub>) are the most promising candidate dielectrics for thinner gate oxide MOSFET device structures to minimize short channel effect [45], [46].

#### 1.3.8 Band-to-Band Tunnelling

The term "tunnelling" refers to a process in quantum mechanics that includes the movement of electrons through potential energy barriers [47]. Band-to-band tunnelling is the process that takes place when electrons move from the valence band to the conduction band (or vice versa) via the forbidden energy band gap [47]–[49]. This occurs as the oxide thickness decreases and the electric fields increase between the gate and drain regions of the semiconductor device. If the gate voltage is low and the drain bias is high, the electric field in the region where the gate and drain overlap will be larger. This band-to-band tunnelling probability is activated due to the overlap region, which is located where the valance band and the conduction band of the drain overlap [23]. Gate-induced drain leakage [32] may occur when electron-hole pairs are swept by band-to-band tunnelling into the drain and substrate regions.

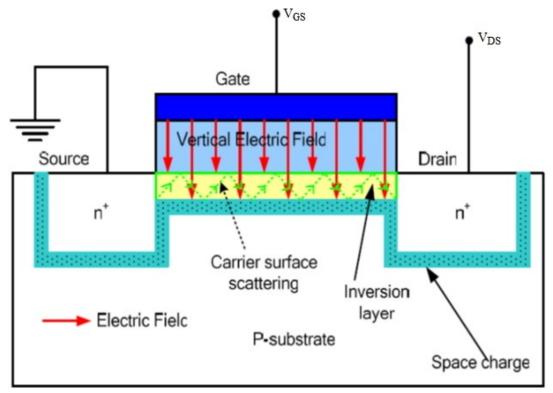

#### **1.3.9 Mobility Degradation (Surface Scattering)**

The gate-induced vertical electric field acts on carriers as they move along the channel under the influence of the horizontal electric field, pushing carriers towards the gate oxide and encouraging or motivating them to crash into the oxide channel interface [50]. Due to an imperfect oxide channel interface, carriers lose mobility [51]. This effect, known as surface scattering, causes a decrease in mobility, impacting the drain current and transconductance[38].

**Figure 1.6**: Shows the vertical electric field and surface scattering in a short channel MOSFET [50].

## 1.4 Engineering schemes to reduce short channel effects

As previously discussed, both lateral and vertical dimensions (gate oxide thickness and junction depth) should be reduced to increase device packing density and device performance. However, producing MOSFETs with deep micrometre (nanometer) channel lengths is complex and will cause several challenges. In order to address scaling issues that have been encountered, there are potential solutions, such as the addition of new materials and new structures. Therefore, it is necessary to develop new silicon technology that incorporates a wide range of technological improvements. Here, we'll review some engineering techniques designed to improve conventional devices' electrical efficiency.

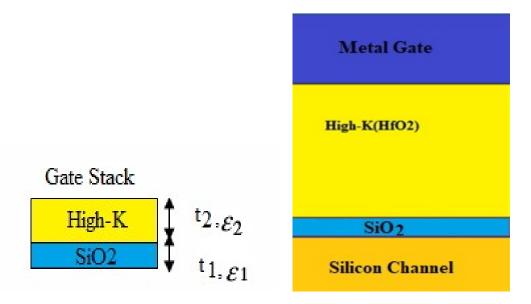

### 1.4.1 Gate Dielectric Engineering

Since the 1960s,  $SiO_2$  has been the gate insulator of choice for silicon MOSFETs. Over the period of this time, the oxide thickness has shrunk, going from 300 nm for 10 nm technology to 1.2 nm for 65 nm technology [37], [52]. The reason for reducing oxide thickness is to obtain greater oxide capacitance ( $C_{OX}$ ), which increases on-current ( $I_{ON}$ ) and is desirable for maximizing circuit speed and controlling threshold voltage roll-off ( $V_{th}$ ) in the presence of decreasing channel length[53]. Because of the thin oxide layer, electrons from strongly inverted surfaces can tunnel into or through the SiO<sub>2</sub> layer. This phenomenon, known as gate-induced drain leakage (GIDL), is what causes tunnelling current through decreased gate oxide thickness [54]. This takes place as a consequence of the thin oxide layer, which causes the breadth of the

potential barrier to be relatively narrow. The tunnelling leakage current becomes the dominant limiting factor when SiO<sub>2</sub> gate oxide is thinner than 1.5 nm. In a short channel device, drain electric field is strong, which causes thinner gate oxide to be destroyed and leads to a leakage current [49]. Below 1nm gate oxide thickness or decreases rapidly with the new technologies, the gate leakage current will become more prominent, increasing exponentially as a function of the gate oxide thickness and applied drain-source voltage[50]. In order to solve these significant problems, high-gate dielectrics have been employed in place of SiO<sub>2</sub> gate dielectrics and the physical thickness of the dielectric layer will be kept broad. This has the effect of lowering the gate leakage current while keeping the capacitance value the same [42], [43], [55], [56]. These materials make it possible to have a high physical thickness while keeping a tiny effective oxide thickness (EOT), making it possible to scale the EOT for future generations of MOS devices [55]. The equivalent oxide thickness (EOT) refers to the thickness of a layer of  $SiO_2$  that has the same capacitance as the high-k dielectric layer [57][58]. Increased gate control over the channel is possible by using high-k dielectric materials<sup>[44]</sup>. Still, these improvements are not without drawbacks due to imperfections such as interface traps, fixed bulk charges, low interface carrier mobility, and phase stability issues[57][59]. SiO<sub>2</sub> forms a thin interfacial layer on silicon because no other dielectric material can create a native oxide on the silicon[60]. For the purpose of immobilizing biomolecules in the cavity region, a substantial layer of SiO<sub>2</sub> serves as a binding agent layer. As a consequence of this, as can be seen in Figure 1. 7, the majority of these unique dielectrics now consist of a thick High-k layer sandwiched between a thin SiO<sub>2</sub> interfacial layer and a poly-Si or metal gate electrode [61]. Depending on the physical layer thickness and k values, the applied gate voltage is dipped(dropped) over the interfacial SiO<sub>2</sub> and high-k layers.

Figure 1. 7. Illustrates Gate Stack Architecture[62].

Therefore, the extra-thin low-k interlayer enhances the quality and stability of the interface in a stacked gate architecture. Adding a low-k layer to a stacked gate architecture with the same EOT significantly reduces the fringing electric field. Because of the continuity of the displacement, the high fringing fields are electrically focused into the low-k dielectric layer,

which may alter the relative fringing field effect on the device's characteristics[63]. In gate stack architecture, the formula will decide the effective thickness(EOT)[42], [57] shown below.

$$(EOT) = t_{high-k} \left( \frac{k_{SiO_2}}{k_{high-k}} \right) + t_{low-k}$$

(1.1)

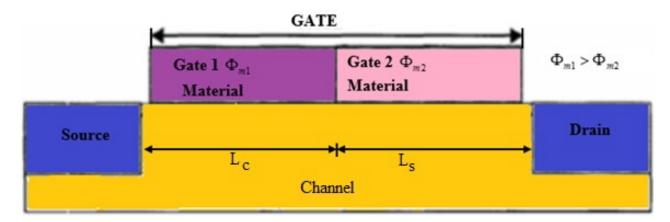

#### 1.4.2 Gate Electrode Engineering

Leakage currents have become an issue in VLSI MOS technology due to the ongoing scaling of gate lengths, gate oxides, and threshold voltages. These currents need to be relieved (controlled) so that the problem may be addressed. Power dissipation is another problem, especially for small devices, because of the leakage currents [45]. The electric field distribution along the channel affects MOSFET gate transport efficiency [51]. In a field effect transistor, electrons have a slow initial velocity as they enter the channel, but their speed rapidly increases as they move closer to the drain [64]. Because the maximum electron drift velocity is attained closest to the drain, the electrons move very quickly in that region; nevertheless, they move relatively slowly, closest to the source. This is due to the fact that the highest electron drift velocity is reached closest to the drain. As a consequence, the speed of the device is impacted by the comparatively slow electron drift velocity in the channel that is located close to the source region. as a result of the depletion effects brought about by the polysilicon gate [65]. To provide no depletion effect and significantly improved threshold voltage control, a polysilicon gate must be replaced by a metal gate electrode [66]. As a result, different architecture like double gate material MOSFET was proposed to improve the gate transport efficiency and lower the SCEs[37], [67], as shown in Figure 1.8. To improve carrier velocity, the electric field profile of the channel is optimized to be larger near the source end and smaller near the drain end [68].

Figure 1.8. Illustrates double material gate (DMG) MOSFET structure [69].

An accelerating force is provided for charge carriers in the channel by the difference in work function of the double material gate between the two laterally contacting gate materials of lengths  $L_c$  and  $L_s$ . This difference also serves as a screening effect, which helps suppress SCEs.

One of the gate materials serves as a control gate with metal work-function  $\phi_{M1}$  and the other as a screening gate with work-function  $\phi_{M2}$  which should be less than  $\phi_{M1}$  [37]. For improved carrier transport efficiency and a higher drain current, screening the control gate from drain potential changes reduces the hot electron effect by lowering the electric field [45].

# **1.4.2.1** Need for Metal Gates in MOSFET a) Poly-Si gate depletion effect