# ANALYSIS AND CONTROL OF MULTILEVEL INVERTER FOR POWER QUALITY IMPROVEMENT

A Thesis Submitted in Partial Fulfillment of the Requirements for the Award of the Degree of

### **DOCTOR OF PHILOSOPHY**

Submitted by

PRAVEEN BANSAL (Enrollment No. 2k18/PhD/EE/08)

Under the Supervision of

Dr. Alka Singh Professor Department of Electrical Engineering DTU,Delhi-110042

DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY Bawana Road, Delhi-110042, India July-2023

#### DECLARATION

I hereby certify that the work which is presented in this thesis entitled "Analysis and Control of Multilevel Inverter for Power Quality Improvement" submitted in partial fulfillment of the requirements for the award of the degree of Doctor of Philosophy in the Department of Electrical Engineering, Delhi Technological University, Delhi. This is an authentic record of my own work carried out under the supervision of Dr. Alka Singh. The matter presented in this thesis has not been submitted elsewhere for the award of a degree

**Praveen Bansal** (2k18/PhD/EE/08)

Place: Delhi

Date: \_\_/\_\_/\_\_\_\_

#### CERTIFICATE

On the basis of candidates' declaration, I hereby certify that the work which is presented in this thesis entitled "Analysis and Control of Multilevel Inverter for Power Quality Improvement" submitted to the Department of Electrical Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirements for the award of degree of Doctor of Philosophy, is an original contribution with the existing knowledge and faithful record of the research work carried out by him under my guidance and supervision.

To the best of my knowledge, this work has not been submitted in part or full for the award of any degree elsewhere

Dr. Alka Singh Professor Department of Electrical Engineering DTU, Delhi-110042

The PhD viva-voce of Mr. Praveen Bansal, research scholar has been held on \_\_\_\_\_

Signature of

Signature of

Supervisor

Head, Dept. of Electrical Engg.

#### ACKNOWLEDGEMENTS

I want to express my deep and sincere gratitude to my supervisor, Prof. Alka Singh, for her valuable guidance and continuous monitoring of my research work. It was a great honor to pursue my research work under her supervision. **Prof. Alka Singh** has been the motivating and inspiring factor behind my research work. Her vigor and hunger to perform in an adverse situations have inspired me to strive for excellence and her driving force to complete my research work. Working under her supervision is a lifetime experience, and I humbly acknowledge gratitude for her support.

I want to thank **Prof. Pragati Kumar,** HOD (EE), for his kind support. I would also like to convey my sincere gratitude to **Prof. Jitendra Nath Rai**, Professor DTU, who has taught me the relevant coursework. I want to thank the SRC members, mainly Prof. Majid Jamil, who has given me valuable guidance and advice to improve the quality of my research work. I am highly thankful to the Power System Lab Komal Singh staff member for providing me with immense facility and assistance to carry out my research. I want to thank other office staff, Central Library and Computer Centre staff members for their valuable cooperation and support. I would also like to thank **Dr.R. K.Pandit (Director)** of MITS, Gwalior (M.P.) for granting permission to enroll in Ph.D programe under twinning arrangement of TEQIP-III project.

I want my sincere thanks to **Dr. Prakash Chittora** and **Dr. Hemant Saxena**, who have guided me to develop hardware at the initial level of my research work. I am incredibly grateful to my research group and friends Allu Bhargava, Amarendra Pandey, Sudhanshu Mittal, Vineet, and Kanchan Rai for their valuable assistance, cooperation, and excellent source of learning. If I get any success today for my research work, the entire credit should go to my mother, **Smt. Pushpa Lata Bansal**, father **Shri L.N. Bansal**, my elder brother **Mr. Shailesh Bansal** and younger brother **Mr. Sudeep Bansal**. I sincerely convey my gratitude to my wife, **Monika**, and son **Saaksh** who has encouraged me to carry out my research work. I want to thank other family members who directly or indirectly support my research work.

Lastly, I thank Mother Nature and Almighty God for allowing me to pursue doctoral studies.

Place : Delhi

Date: : \_\_/\_\_/

Praveen Bansal Research Scholar 2k18PHDEE08

#### ABSTRACT

Modern power distribution systems face two challenges from increasing electronic-based loads and integrating renewable energy sources. Distribution networks experience problems with current-based power quality as a result of these power-related electronic devices. Power quality problems include issues like poor power factor, load imbalance, harmonics in the supply current, voltage regulation, and others. To mitigate these issues, a shunt active power filter (SAPF) is used. This can be done by a number of controllers. In the case of a normal grid condition, the unit-in-template approach can be utilized to extract the synchronization signals. When the grid deteriorates due to voltage sag, swell, distortion, and DC offset problems present in the grid. Therefore, it is also essential to employ effective PLL algorithms to estimate synchronization template signals..

The grid-connected system is connected to the point of common coupling (PCC) via a voltage source converter, and the non-linear loads are also connected. Due to their efficiency and compactness, the power electronic-based loads are growing every day. Reactive power is drawn by the non-linear loads, which lowers the quality of the power and introduces harmonics into the system, which increases losses. To address the aforementioned problems, SAPF is built and configured to perform power factor correction, reactive power compensation, and harmonic mitigation. In order to enhance the power quality in distribution systems, it is advised to comply to a range of international standards based on IEEE and IEC. IEEE-519 standards for grid current harmonic mitigation should be followed. According to the IEEE-519 standard, the Total Harmonic Distortion Factor in grid current should be less than 5%. In addition, the IEEE-1547 standard mentions the allowable harmonic content that can be injected by PV systems when connected to the grid.

In this thesis work, the SAPF is created for single-phase distribution systems utilizing Matlab Simulink software. Dynamic load conditions evaluate the effectiveness. In a single-phase system, a 5-level cascaded H-Bridge Multilevel Inverter replaces the standard 2-level inverter. MLI has a number of benefits over a normal 2-level inverter since it switches operated at a lower frequency and experiences fewer switching losses. The harmonic content decreases as the number of levels rises. The CHB-MLI system has the necessary flexibility

thanks to its modular design. A phase-shifted pulse width modulation technique produces the gate pulses by comparing the generated reference currents with the actual supply current signals.

The performance of the SAPF is dependent on the different control algorithms used to extract the harmonics from the non-linear load current. In the literature, various conventional and adaptive control techniques are addressed. The performance of the control algorithm is assessed using a number of important considerations, such as the degree of computational complexity, the degree of filtration, oscillations, overshoot, settling time, mean square error, phase-locked loop (PLL) requirement, memory requirement, and the THD obtained in grid current and convergence behavior of fundamental load current under dynamic conditions. To enhance the power quality of distribution networks, SAPF needs to be appropriately controlled for further processing and control. Its controller is based on extracting the fundamental component of load current for the generation of reference current. This thesis involves designing new control algorithms to retrieve the fundamental load current algorithms.

The SAPF efficiency is also impacted by how precisely the control algorithm extracts the reference current and compensates for the harmonics produced by the load. The areas of active noise cancellation, signal enhancement, noise filtering, echo cancellation, etc., have all been covered by adaptive signal processing techniques over the past few decades. Least Mean Square (LMS), Synchronous Reference Frame Theory (SRFT), and Notch Filter are common algorithms used for the estimation of fundamental component of load current components. A method of parallel tangent (PARTAN-LMS) algorithm has been developed to operate under distorted grid conditions, and some advanced adaptive control algorithms, such as Normalized Least Mean Absolute Third (NLMAT), Normalized Huber (NHuber), and Robust Shrinkage Affine Projection Sign Algorithm (RSAPS), have also been implemented.

The grid must be synchronized with power electronic converters for effective control. The voltage-based electrical quality of Indian systems can occasionally be problematic. Harmonics, phase angle jumps, frequency shifts, voltage sag, swell, and DC offset are

common issues with voltage signals used for synchronization. To resolve these voltagebased power quality problems, open-loop and closed-loop synchronization approaches can be applied. Phase-locked loops are a frequently employed part of synchronization techniques. The phase-locked loop technique is required for quick and accurate detection of the grid phase angle and frequency for integration. The chosen method of synchronization has an impact on the stability and accuracy of the control system. Grid collapse could result from inaccurate PLL information. It is necessary to look for an appropriate PLL that can be applied in real-time, has a simpler structure, and can address the weak grid problems. For the 5-Level CHB-MLI controller to operate, the synchronization controller also keeps track of grid voltage, phase, and frequency information.

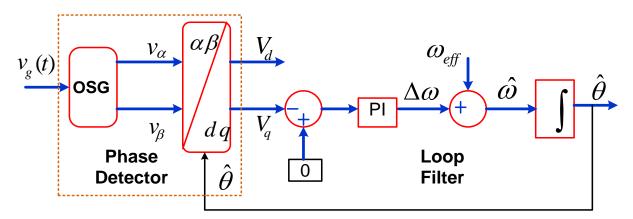

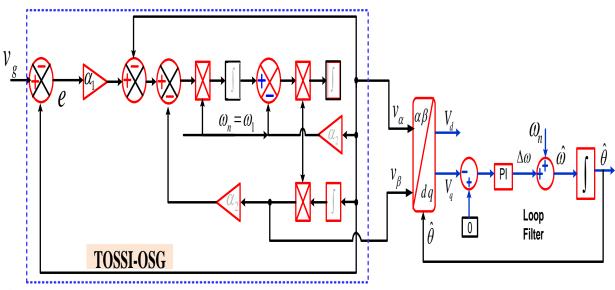

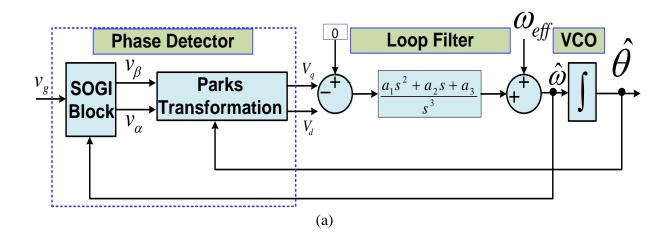

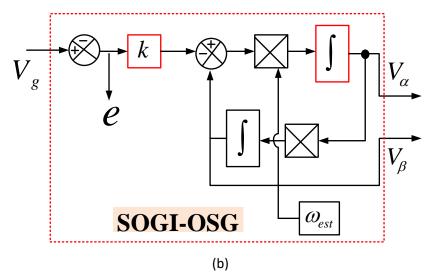

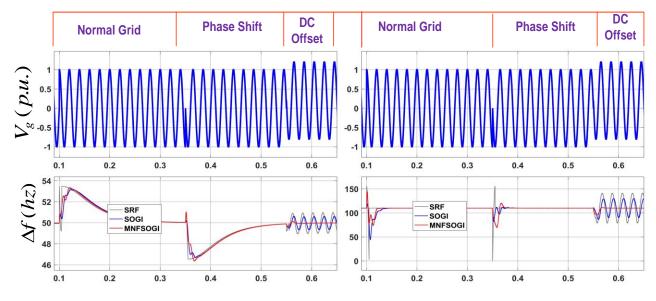

This thesis presents three grid-synchronization techniques for single-phase systems: Synchronous Reference Frame Theory (SRF-PLL), Second Order Generalized Integrator (SOGI-PLL), and Third Order Sinusoidal Integrator (TOSSI-PLL). SRF-PLL is the traditional and frequently employed PLL under typical circumstances. However, this PLL does not accurately track frequency and phase angle when the grid is distorted. Therefore, finding alternatives to SRF-based PLLs is essential. For handling various grid anomalies, orthogonal signal generator (OSG) based PLL has been widely used and implemented in recent years.

Additionally, compared to SRF-PLL, its tracking capability is quite good and accurate. The most commonly used OSG- PLL is SOGI-PLL, but its performance deteriorates especially in DC-offset conditions; therefore, one more PLL, i.e., TOSSI-PLL, has been implemented to tackle grid abnormalities which exhibits good performance as compared to SRF-PLL and SOGI-PLL. The findings of extensive mathematical modeling, simulations and experiments have been presented in this thesis. The effectiveness of the synchronization algorithms has been demonstrated through simulation and experimental testing under various grid voltage conditions such as voltage sag and swells, phase shift, and DC offset and also tested under sudden load variations

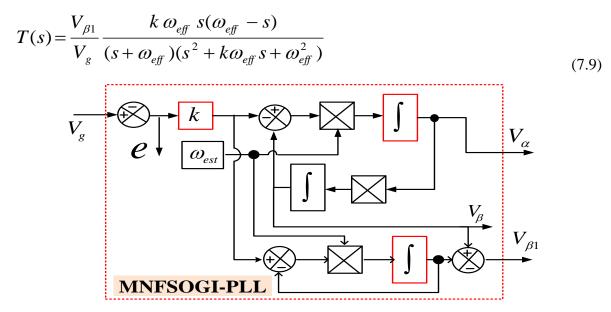

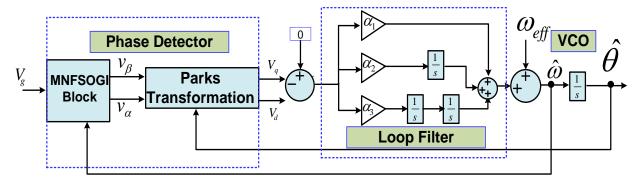

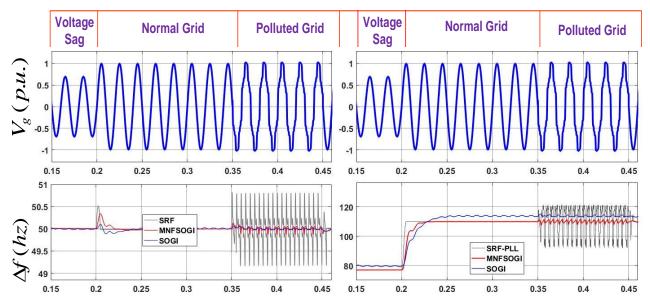

In grid-connected systems, photovoltaic (PV) based voltage source converters (VSC) serve the dual purposes of bidirectional active power transfer to the grid and load. They can be controlled to achieve grid current balancing, harmonic reduction, reactive power balance, and improvement of the supply side power factor to unity. The PV source can be integrated through a DC-DC boost converter using the double-stage topology, or it can be linked directly to the VSC at its DC link using the single-stage topology. Fewer devices are required in a single stage, and it offers improved control. Additionally, because of independent Maximum Power Point Tracking, it has an increased operation region and more flexibility. In this thesis, a single-stage, single-phase grid-connected system has been presented. The PV arrays are connected to the DC link side of the 5-Level CHB-MLI. The proposed system can operate in two modes, day and night. During the day, the active power is injected into the grid, and during the night, the solar arrays are disconnected; the SAPF will do the harmonics compensation and make the system power factor unity. The system is tested under distorted grid conditions. Two PLLs viz. SRF-PLL and Modified Notch Filter SOGIPLL (MNFSOGI-PLL) is implemented to generate the unit template and reference current. The SRF-PLL fails to work in distorted grid conditions, but MNFSOGI-PLL exhibits good performance under the distorted grid, especially to handle DC offset. To enhance the quality of the power, offer reactive power compensation, and inject active power into the grid, these system configurations will be implemented and analyzed using simulation models and experimental prototypes.

# **Table of Contents**

| Declaration           | i     |

|-----------------------|-------|

| Certificate           | ii    |

| Acknowledgements      | iii   |

| Abstract              | iv    |

| Table of Contents     | ix    |

| List of Figures       | xv    |

| List of Tables        | xxiv  |

| List of Abbreviations | xxv   |

| List of Symbols       | xxvii |

### 1. Introduction

|    | 1.1 General Introduction                                             | 1  |

|----|----------------------------------------------------------------------|----|

|    | 1.2 Modern Distribution System and Power Quality                     | 2  |

|    | 1.3 State of Art                                                     | 3  |

|    | 1.4 Scope of Work                                                    | 6  |

|    | 1.5 Outline of Chapters                                              | 9  |

| 2. | Literature Survey                                                    | 11 |

|    | 2.1 General Introduction                                             | 11 |

|    | 2.2 Literature Survey on Various Power Quality (PQ) issues           | 11 |

|    | 2.3 Literature Survey on Various Inverter Topologies                 | 13 |

|    | 2.4 Literature Survey on Grid Synchronization Schemes                | 14 |

|    | 2.5 Literature Survey on Adaptive Control Algorithms for SAPF        | 15 |

|    | 2.6 Literature Survey on Grid Connected PV based Distribution System | 18 |

|    | 2.7 Identified Research Gap                                          | 20 |

|    | 2.8 Research Objectives                                              | 20 |

|    | 2.9 Conclusion                                                       | 21 |

| 3. | Designing  | g and Development of Single Phase Multilevel Inverter      | 20 |

|----|------------|------------------------------------------------------------|----|

|    | Based Sh   | unt Active Power Filter                                    |    |

|    | 3.1 Introd | uction                                                     | 23 |

|    | 3.2 Differ | ent topologies of conventional Multilevel Inverters        | 25 |

|    | 3.2.1      | Diode Clamped Multilevel Inverter                          | 26 |

|    | 3.2.2      | Flying Capacitor Multilevel Inverter                       | 27 |

|    | 3.2.3      | Cascaded H-Bridge Multilevel Inverter                      | 28 |

|    | 3.3 Propos | sed Five-Level MLI based System Configuration              | 32 |

|    | 3.4 Design | n and development of Shunt Compensator                     | 34 |

|    | 3.4.1      | Design of DC link Capacitor                                | 34 |

|    | 3.4.2      | Design of Interfacing Inductor                             | 34 |

|    | 3.4.3      | Calculation of reference DC link voltage                   | 34 |

|    | 3.4.4      | Design and development of Current Sensor                   | 35 |

|    | 3.4.5      | Design and development of Voltage Sensor                   | 35 |

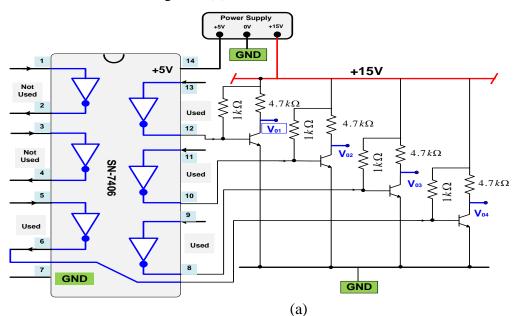

|    | 3.4.6      | Design of Amplifier Circuit                                | 37 |

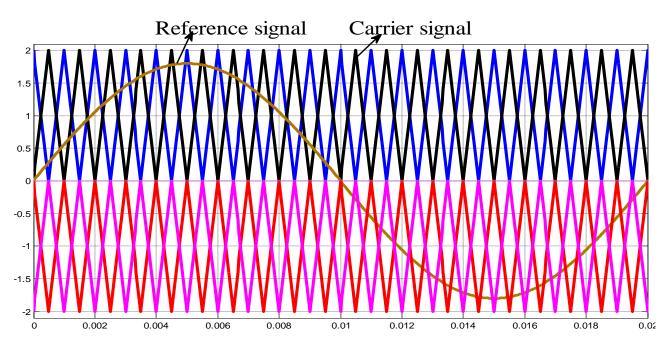

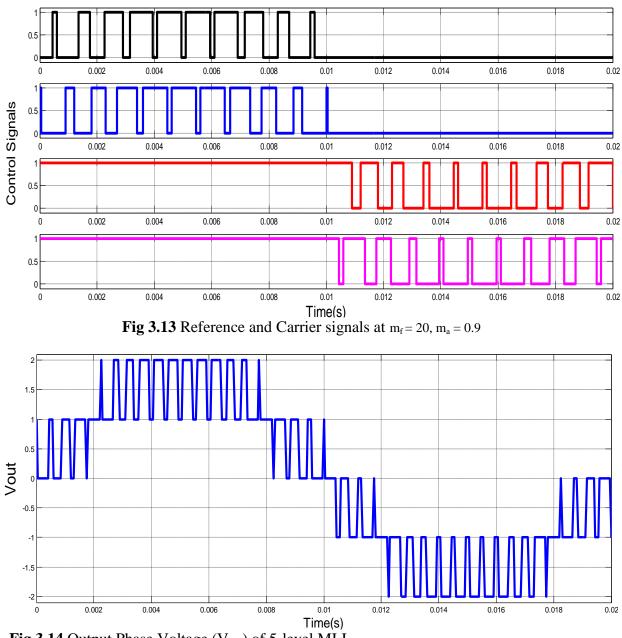

|    | 3.4.7      | Design of Phase Shifted PWM Scheme                         | 38 |

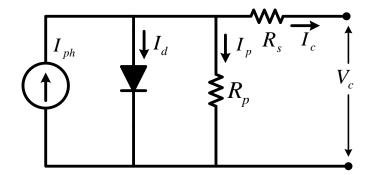

|    | 3.4.8      | Design of PV array module                                  | 39 |

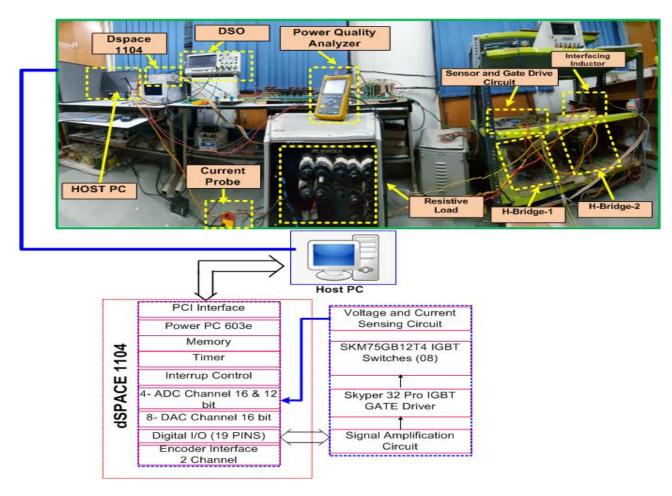

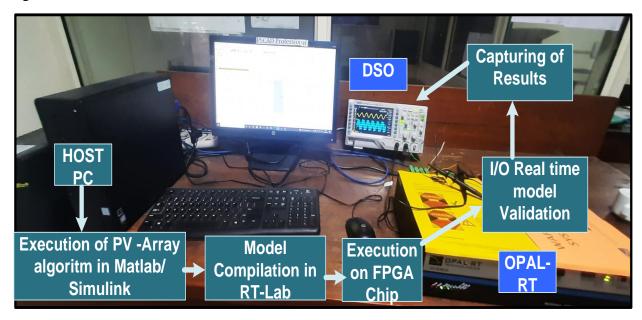

|    | 3.4.9      | Experimental Hardware Setup                                | 42 |

|    | 3.5 Comp   | arison between Conventional 2-level and 5-Level Multilevel | 43 |

|    | Inverte    | er                                                         |    |

|    | 3.5.1      | Loss calculation in CHB-MLI and Conventional 2-level       | 46 |

|    |            | inverter                                                   |    |

|    | 3.6 Conclu | usion                                                      | 49 |

|    |            |                                                            |    |

| 4. | Performa   | nce Evaluation of MLI based SAPF using Conventional        | 51 |

|    | Control 7  | Techniques                                                 |    |

|    | 4.1 Introd | uction and Basic Compensation principles of SAPF           | 51 |

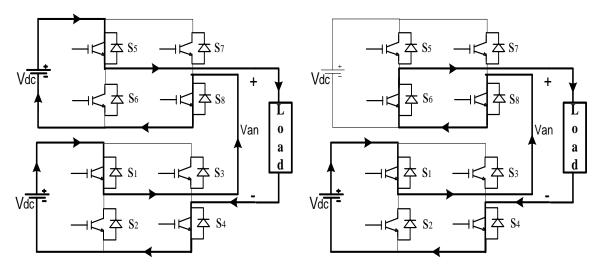

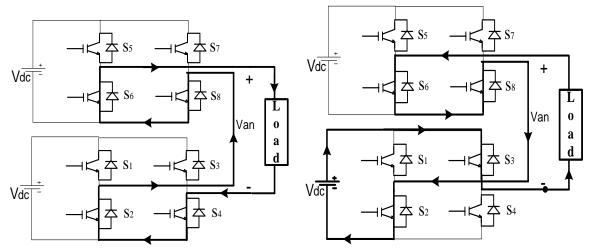

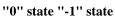

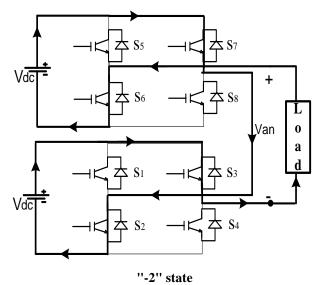

|    | 4.2 Switch | ning Configurations of 5-Level CHB-MLI                     | 53 |

|    | 4.3 Operat | tion of 5-Level Shunt Active Power Filter                  | 54 |

|    | 4.4 Genera | alized Structure of Control Algorithm                      | 56 |

|    | 4.5 Estima | ation of switching losses for CHB-MLI                      | 57 |

| 4.6 Estimation of Unit Vector template                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 4.7 Generation of firing pulses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 58                                                                                             |

| 4.8 Extraction of fundamental component of load current using Least                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59                                                                                             |

| Mean Square Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                |

| 4.8.1 Mathematical Formulation of Adaptive Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 59                                                                                             |

| 4.8.2 Simulation Results of LMS Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60                                                                                             |

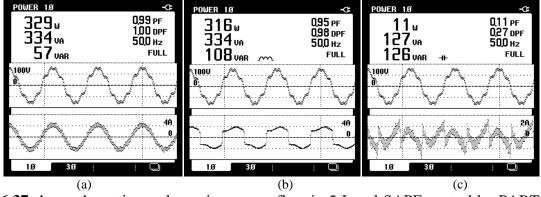

| 4.8.3 Experimental Results with LMS Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62                                                                                             |

| 4.9 Extraction of fundamental component of load current using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66                                                                                             |

| Synchronous Reference Frame Theory (SRFT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                |

| 4.9.1 Simulation Results of SRFT Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                                                                                             |

| 4.9.2 Experimental Results with SRFT Control Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69                                                                                             |

| 4.10 Introduction to Notch Filter (NF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72                                                                                             |

| 4.10.1 Simulation Results with Notch Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74                                                                                             |

| 4.10.2 Experimental Results of Notch Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76                                                                                             |

| 4.11 Comparative analysis of LMS, SRFT and Notch Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                |

| 4.12 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82                                                                                             |

| 4.12 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82                                                                                             |

| 4.12 Conclusion<br>Performance Evaluation of MLI based SAPF using Advanced                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 82                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82<br>83                                                                                       |

| Performance Evaluation of MLI based SAPF using Advanced                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                |

| Performance Evaluation of MLI based SAPF using Advanced<br>Adaptive Control Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                |

| Performance Evaluation of MLI based SAPF using Advanced<br>Adaptive Control Algorithms<br>5.1 Introduction and Single phase Grid connected system for 5-Level                                                                                                                                                                                                                                                                                                                                                                                            | 83                                                                                             |

| Performance Evaluation of MLI based SAPF using Advanced<br>Adaptive Control Algorithms<br>5.1 Introduction and Single phase Grid connected system for 5-Level<br>SAPF                                                                                                                                                                                                                                                                                                                                                                                    | 83<br>83                                                                                       |

| <ul> <li>Performance Evaluation of MLI based SAPF using Advanced</li> <li>Adaptive Control Algorithms</li> <li>5.1 Introduction and Single phase Grid connected system for 5-Level SAPF</li> <li>5.2 Generalized Structure of Control Algorithm</li> </ul>                                                                                                                                                                                                                                                                                               | 83<br>83<br>84                                                                                 |

| <ul> <li>Performance Evaluation of MLI based SAPF using Advanced</li> <li>Adaptive Control Algorithms</li> <li>5.1 Introduction and Single phase Grid connected system for 5-Level SAPF</li> <li>5.2 Generalized Structure of Control Algorithm</li> <li>5.3 Extraction of fundamental component of load current from control</li> </ul>                                                                                                                                                                                                                 | 83<br>83<br>84                                                                                 |

| <ul> <li>Performance Evaluation of MLI based SAPF using Advanced</li> <li>Adaptive Control Algorithms</li> <li>5.1 Introduction and Single phase Grid connected system for 5-Level SAPF</li> <li>5.2 Generalized Structure of Control Algorithm</li> <li>5.3 Extraction of fundamental component of load current from control algorithms</li> </ul>                                                                                                                                                                                                      | 83<br>83<br>84<br>85                                                                           |

| <ul> <li>Performance Evaluation of MLI based SAPF using Advanced</li> <li>Adaptive Control Algorithms</li> <li>5.1 Introduction and Single phase Grid connected system for 5-Level SAPF</li> <li>5.2 Generalized Structure of Control Algorithm</li> <li>5.3 Extraction of fundamental component of load current from control algorithms</li> <li>5.3.1 Non-linear Adaptive Normalized Least Mean Absolute</li> </ul>                                                                                                                                    | 83<br>83<br>84<br>85                                                                           |

| <ul> <li>Performance Evaluation of MLI based SAPF using Advanced</li> <li>Adaptive Control Algorithms</li> <li>5.1 Introduction and Single phase Grid connected system for 5-Level SAPF</li> <li>5.2 Generalized Structure of Control Algorithm</li> <li>5.3 Extraction of fundamental component of load current from control algorithms</li> <li>5.3.1 Non-linear Adaptive Normalized Least Mean Absolute Algorithm Third (NLMAT)</li> </ul>                                                                                                            | 83<br>83<br>84<br>85<br>85                                                                     |

| <ul> <li>Performance Evaluation of MLI based SAPF using Advanced Adaptive Control Algorithms</li> <li>5.1 Introduction and Single phase Grid connected system for 5-Level SAPF</li> <li>5.2 Generalized Structure of Control Algorithm</li> <li>5.3 Extraction of fundamental component of load current from control algorithms</li> <li>5.3.1 Non-linear Adaptive Normalized Least Mean Absolute Algorithm Third (NLMAT)</li> <li>5.3.1.1 Simulation Results with NLMAT Algorithm</li> </ul>                                                            | 83<br>83<br>84<br>85<br>85<br>85                                                               |

| <ul> <li>Performance Evaluation of MLI based SAPF using Advanced Adaptive Control Algorithms</li> <li>5.1 Introduction and Single phase Grid connected system for 5-Level SAPF</li> <li>5.2 Generalized Structure of Control Algorithm</li> <li>5.3 Extraction of fundamental component of load current from control algorithms</li> <li>5.3.1 Non-linear Adaptive Normalized Least Mean Absolute Algorithm Third (NLMAT)</li> <li>5.3.1.1 Simulation Results with NLMAT Algorithm</li> <li>5.3.1.2 Experimental Results with NLMAT Algorithm</li> </ul> | <ul> <li>83</li> <li>83</li> <li>84</li> <li>85</li> <li>85</li> <li>87</li> <li>89</li> </ul> |

|    | Huber (NHuber) Adaptive Control Algorithm                          | 92  |

|----|--------------------------------------------------------------------|-----|

|    | 5.3.2.2 Simulation Results with NHuber algorithm                   | 94  |

|    | 5.3.2.3 Experimental Results with NHuber Algorithm                 | 97  |

|    | 5.3.3 Robust Shrinkage Affine Projection Sign (RSAPS) Control      | 99  |

|    | Algorithm for 5-level shunt compensation                           |     |

|    | 5.3.3.1 Mathematical analysis of Robust Shrinkage Affine           | 100 |

|    | Projection Sign (RSAPS) Algorithm                                  |     |

|    | 5.3.3.2 Simulation Results with RSAPS Algorithm                    | 102 |

|    | 5.3.3.3 Experimental Results with RSAPS Algorithm                  | 105 |

|    | 5.4 Comparative Performance of NLMAT, NHuber and RSAPS             | 108 |

|    | Algorithms                                                         |     |

|    | 5.5 Conclusion                                                     | 110 |

|    |                                                                    |     |

| 6. | Performance Evaluation of MLI based SAPF under Distorted Grid      | 113 |

|    | Conditions                                                         |     |

|    | 6.1 Introduction and Synchronous Reference Frame Theory (SRFT-PLL) | 114 |

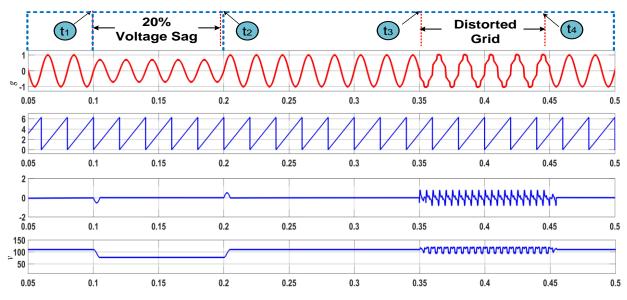

|    | 6.1.1 Simulation Results with SRF-PLL                              | 115 |

|    | 6.1.1.1 Case I: Under distorted Grid and Voltage Sag               | 115 |

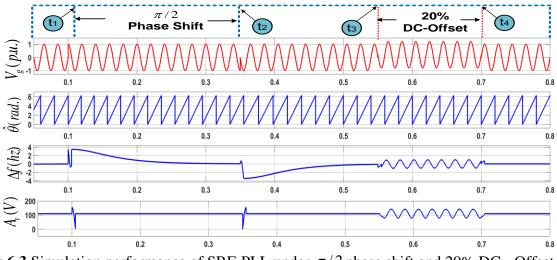

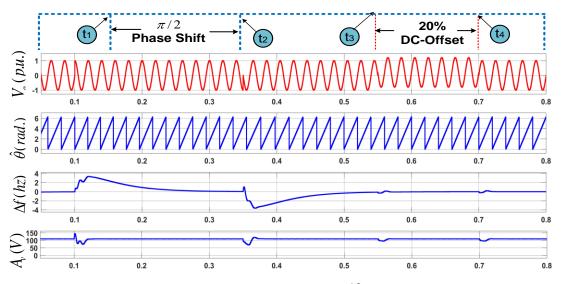

|    | 6.1.1.2 Case II: Phase Shift of $\pi/2$ and 20% DC-offset          | 116 |

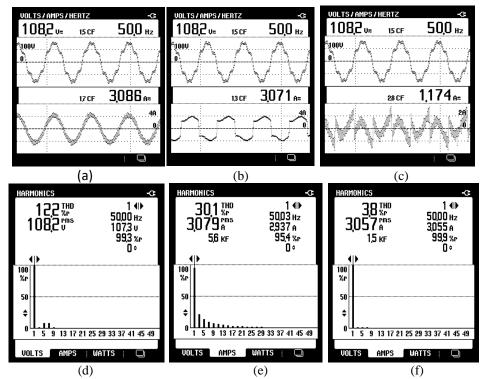

|    | 6.1.2 Experimental results with SRF-PLL                            | 117 |

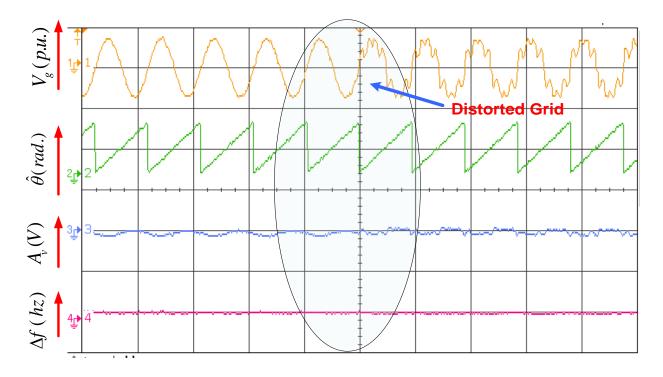

|    | 6.1.2.1 Case I: Distortion in Grid Voltage                         | 117 |

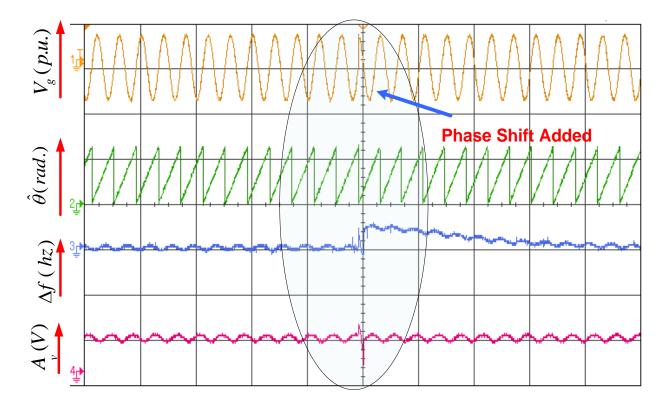

|    | 6.1.2.2 Case II: Phase Shift of $\pi/2$                            | 117 |

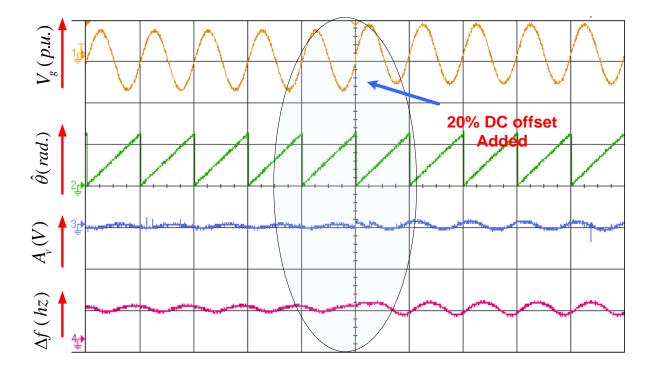

|    | 6.1.2.3 Case III: DC-Offset                                        | 118 |

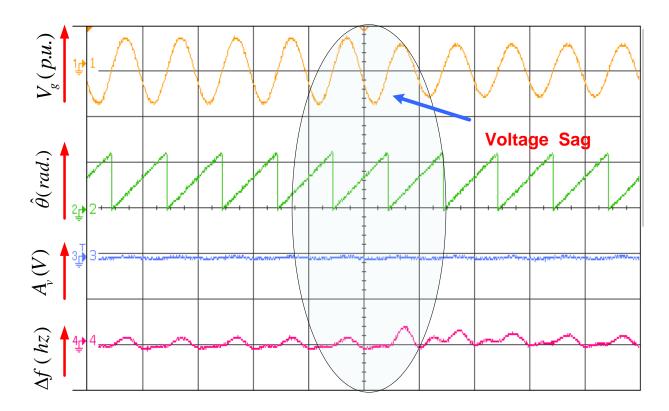

|    | 6.1.2.4 Case IV: Voltage Sag and Swell                             | 119 |

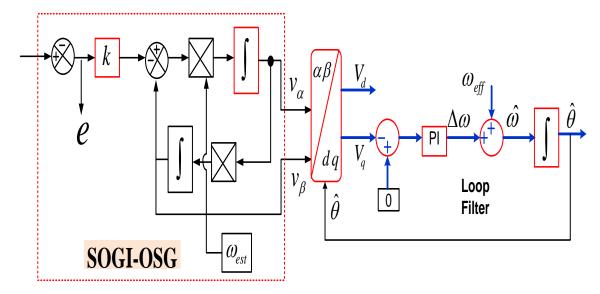

|    | 6.2 Second Order Generalized Integrator (SOGI-PLL)                 | 119 |

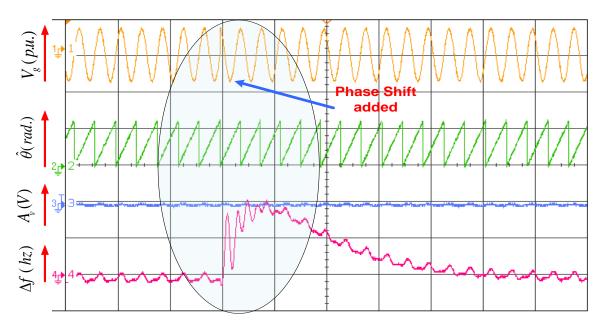

|    | 6.2.1 Simulation Results of SOGI-PLL                               | 121 |

|    | 6.2.1.1 Case I: Grid harmonics and Voltage Sag                     | 122 |

|    | 6.2.1.2 Case II: Phase Shift of $\pi/2$ and 20% DC-offset          | 122 |

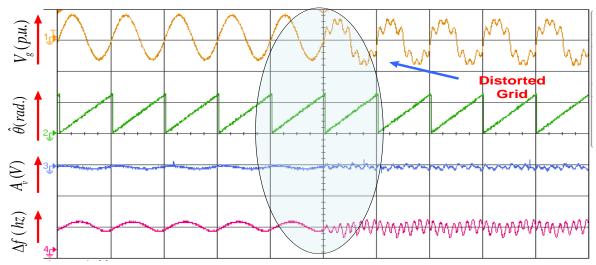

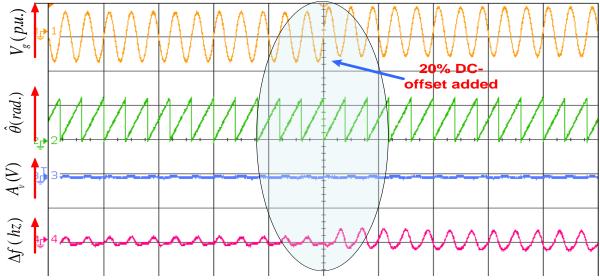

|    | 6.2.2 Experimental results with SOGI-PLL                           | 123 |

|    | 6.2.2.1 Case I: Distortion in Grid Voltage                         | 123 |

|    |                                                                    |     |

| 6.2.2.2 Case II: Phase Shift of $\pi/2$                       | 124 |

|---------------------------------------------------------------|-----|

| 6.2.2.3 Case III: DC-Offset                                   | 124 |

| 6.2.2.4 Case IV: Voltage Sag and Swell                        | 125 |

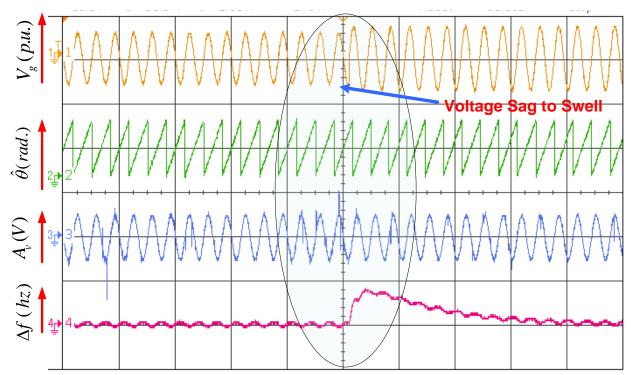

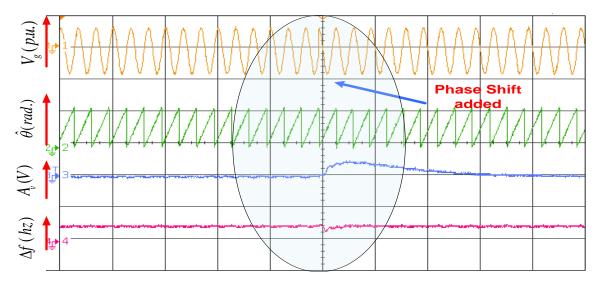

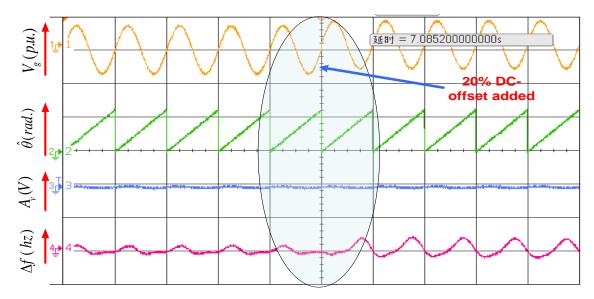

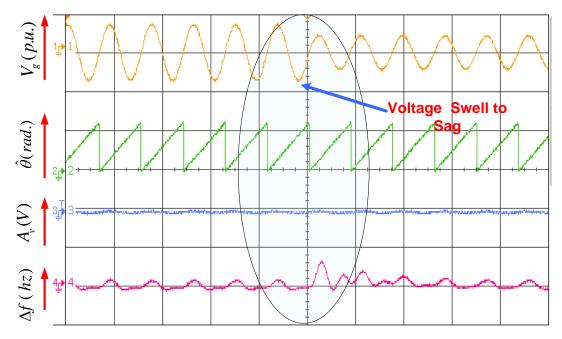

| 6.3 Third order sinusoidal integrator (TOSSI-PLL)             | 126 |

| 6.3.1 Simulation Results of TOSSI-PLL                         | 128 |

| 6.3.1.1 Case I: Grid harmonics and Voltage Sag                | 129 |

| 6.3.1.2 Case II: Phase Shift of $\pi/2$ and 20% DC-offset     | 129 |

| 6.3.2 Experimental results with TOSSI-PLL                     | 129 |

| 6.3.2.1 Case I: Distortion in Grid Voltage                    | 130 |

| 6.3.2.2 Case II: Phase Shift of $\pi/2$                       | 130 |

| 6.3.2.3 Case III: DC-Offset                                   | 132 |

| 6.3.2.4 Case IV: Voltage Sag and Swell                        | 132 |

| 6.4 Comparison of SRF-PLL, SOGI-PLL and TOSSI-PLL             | 133 |

| 6.5 Extraction of fundamental component of load current using |     |

| PARTAN-LMS algorithm under Distorted Grid Conditions          | 136 |

| 6.5.1 Simulation Results with PARTAN-LMS Algorithm            | 141 |

| 6.5.2 Experimental Results of PARTAN-LMS Algorithm            | 145 |

| 6.6 Comparative Analysis of PARTAN-LMS algorithm with         |     |

| Conventional Algorithms                                       | 148 |

| 6.7 Conclusion                                                | 150 |

|                                                               |     |

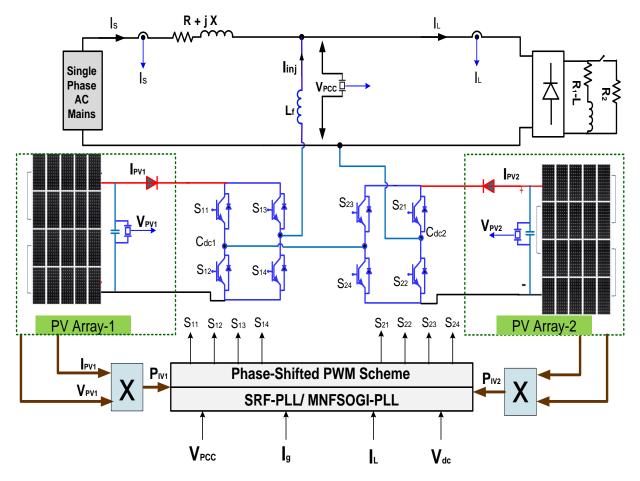

# 7. Power Quality Improvement using Single Phase MLI based Grid Connected PV System 7.1 Introduction and Single stage Grid connected PV system 7.1.1 Extraction of fundamental component of load current

| 7.1.2 Maximum Power Tracking Concept                               | 155 |

|--------------------------------------------------------------------|-----|

| 7.1.3 Estimation of Feed Forward Current                           | 157 |

| 7.1.4 DC Loss calculation and generation of reference current      | 157 |

| 7.2 Performance of PV integrated Single Phase SAPF using SRFT –PLL | 158 |

153

153

154

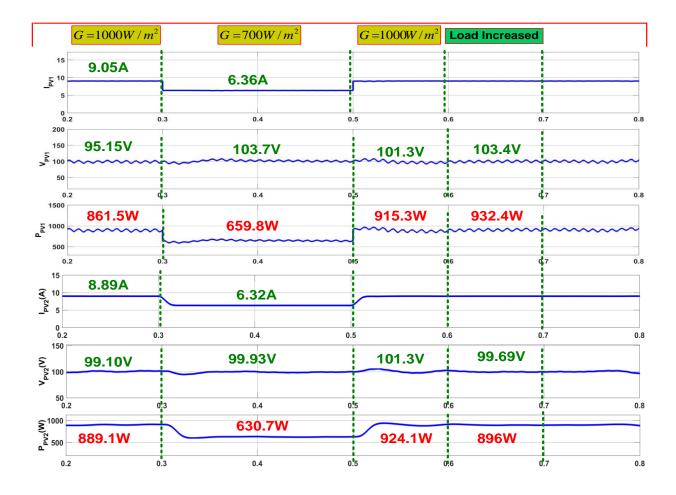

7.2.1 Simulation Results Of Single Phase Single Stage PV Array

|      |            | Based SRF-PLL under Normal Grid Conditions                   | 159 |

|------|------------|--------------------------------------------------------------|-----|

|      | 7.2.2      | Simulation Results of Single-Phase Single-Stage PV Array     |     |

|      |            | based SRF-PLL under Distorted Grid Conditions                | 162 |

|      | 7.2.3      | Experimental Results Of Single Phase Single Stage Integrated | 166 |

|      |            | PV System Based SRF-PLL under Normal Grid Conditions         |     |

|      | 7.2.4      | Experimental Results of Single Phase single stage grid       | 168 |

|      |            | connected PV system distorted grid conditions for SRFT-PLL   |     |

| 7    | .3 Perfor  | mance of PV integrated Single Phase SAPF using MNFSOGI-      | 168 |

|      | PLL        |                                                              |     |

|      | 7.3.1      | Simulation results with Single-Phase Single Stage PV Array   | 172 |

|      |            | based MNFSOGI-PLL under Normal Grid Conditions               |     |

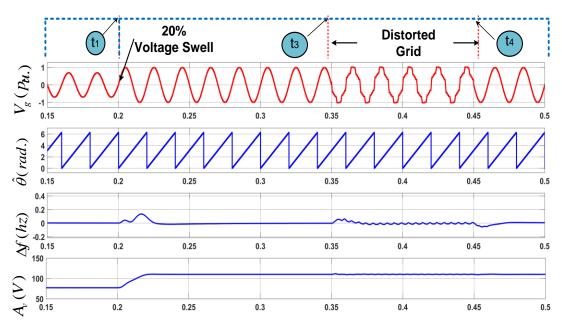

|      | 7.3.2      | Simulations results with Single phase single stage PV array  | 175 |

|      |            | based MNFSOGI-PLL under distorted grid conditions            |     |

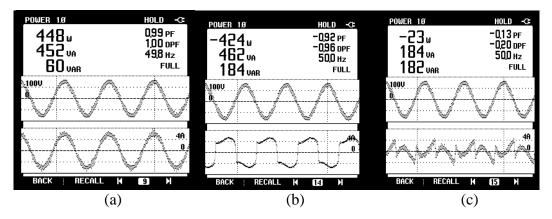

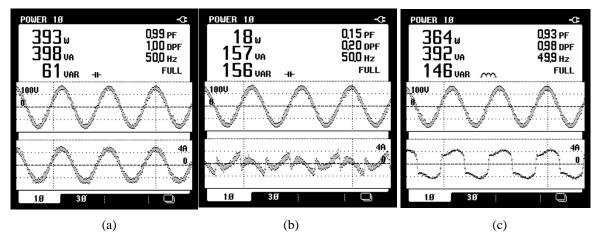

|      | 7.3.3      | Experimental Results of Single Phase Single Stage PV Array   | 178 |

|      |            | Based MNFSOGI-PLL under Normal Grid Conditions               |     |

|      | 7.3.4      | Experimental Results of Single Phase Single Stage PV Array   | 180 |

|      |            | Based MNFSOGI-PLL under Distorted Grid Conditions            |     |

| 7    | .4 Comp    | parative Performance of PLL algorithm in Single Phase PV     | 181 |

|      | Integra    | ated Grid Connected System                                   |     |

| 7    | .5 Concl   | usion                                                        | 183 |

|      |            |                                                              |     |

| 8. N | Main Coi   | nclusions and Future Scope                                   | 185 |

| 8    | 8.1 Concl  | usions                                                       | 185 |

| 8    | 8.2 Future | eScope                                                       | 188 |

| P    | ublicatio  | n                                                            | 190 |

| R    | eference   | 8                                                            | 191 |

# LIST OF FIGURES

| S.No. | Title                                                                           | Page No. |

|-------|---------------------------------------------------------------------------------|----------|

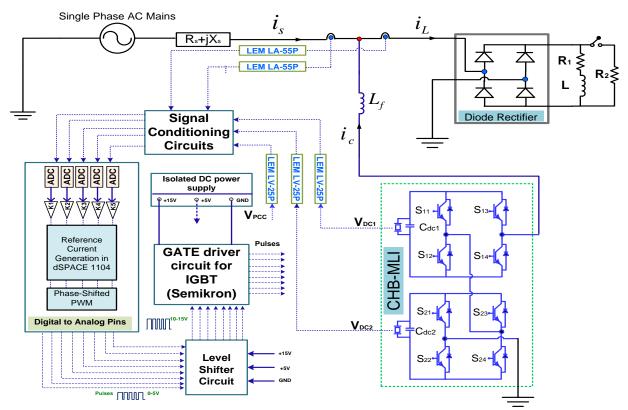

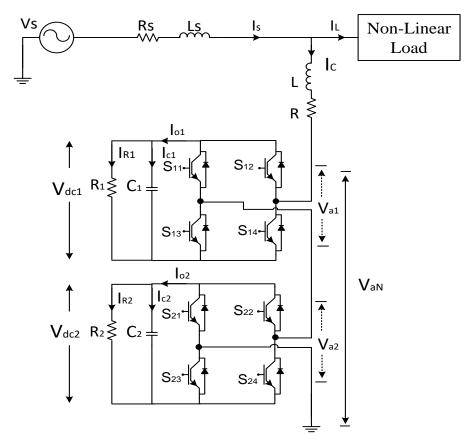

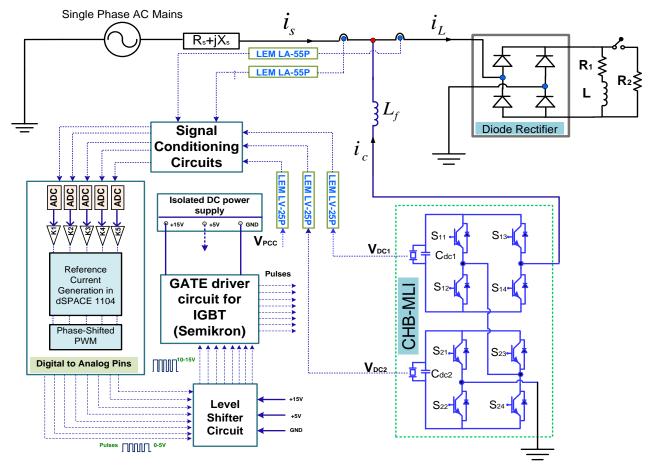

| 3.1   | Proposed System configuration                                                   | 23       |

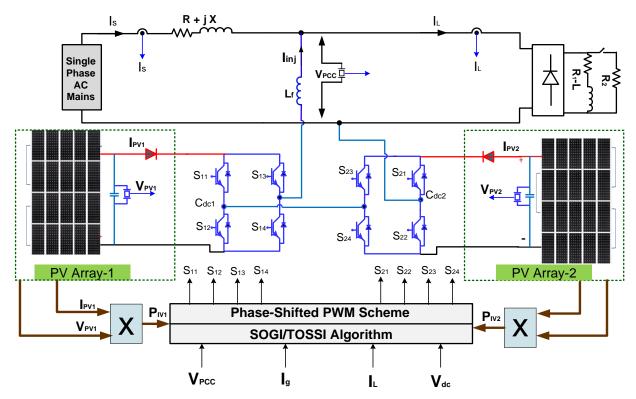

| 3.2   | Single Stage grid connected PV system for 5-level CHB-MLI.                      | 24       |

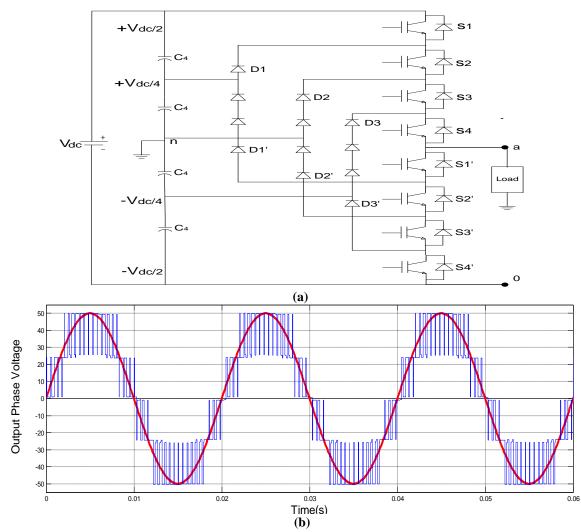

| 3.3   | (a) Generalized structure of 5-level DCMLI (b) 5-level output voltage           | 26       |

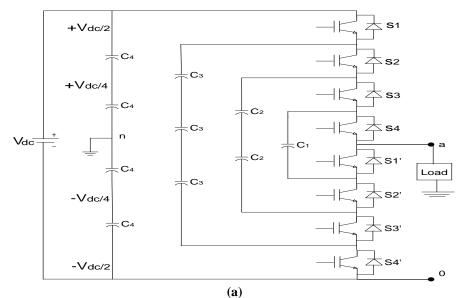

| 3.4   | (a) Single-Phase Capacitor-clamped multilevel inverter for 5-level (b)          | 28       |

|       | Output Phase voltage of five-level MLI                                          |          |

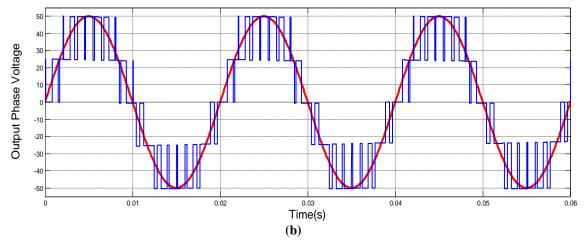

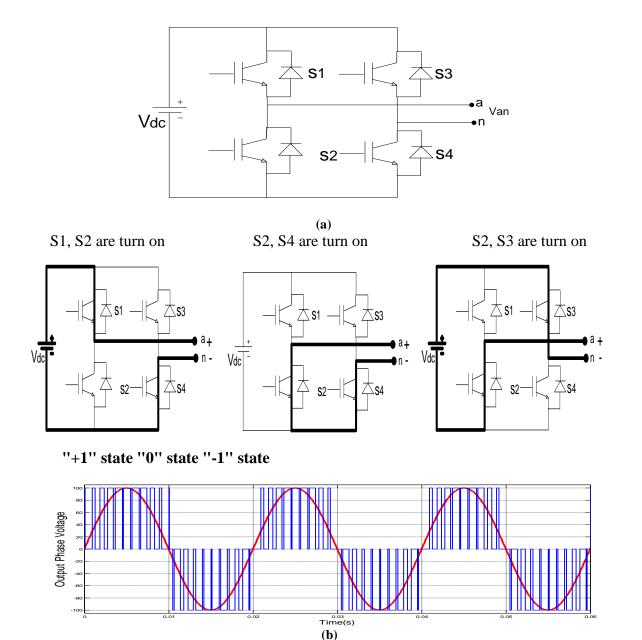

| 3.5   | Topology of the three-level Cascade H-Bridge inverter (a) In single-            | 29       |

|       | phase (b) Switching states                                                      |          |

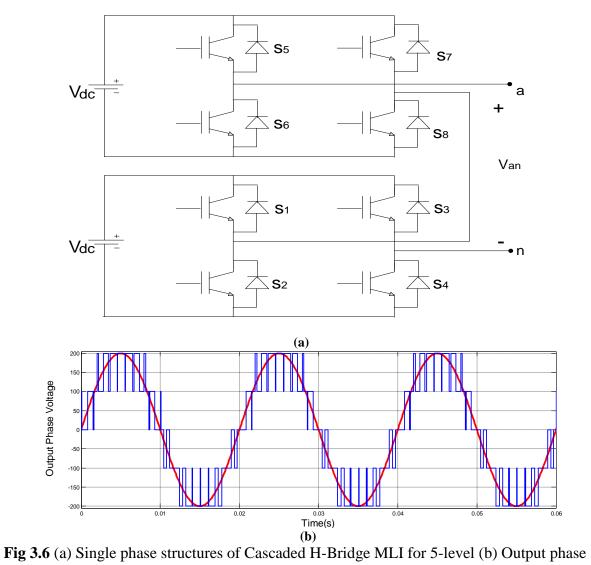

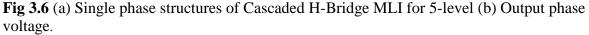

| 3.6   | (a) Single phase structures of Cascaded H-Bridge MLI for 5-level (b)            | 30       |

|       | Output phase voltage                                                            |          |

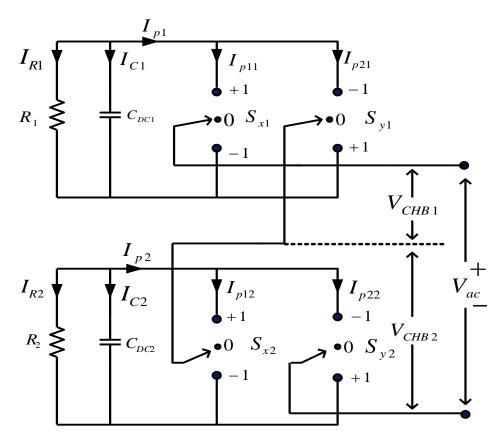

| 3.7   | CHB-MLI for 5-level Switching states                                            | 31       |

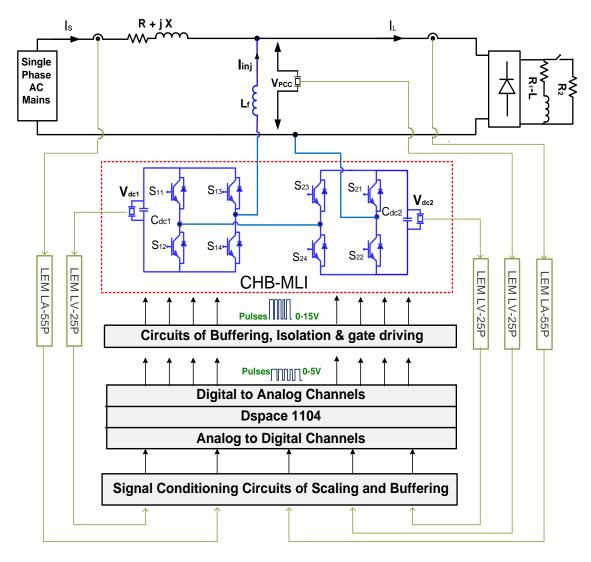

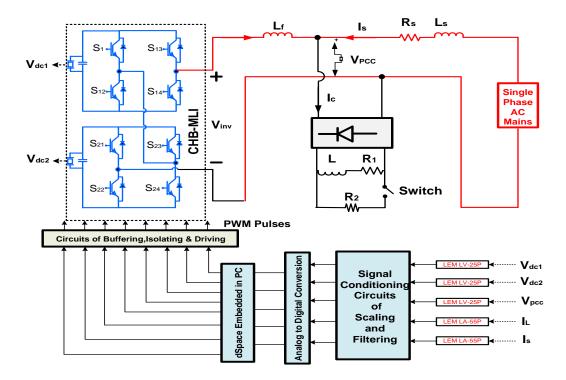

| 3.8   | Schematic of CHB-MLI based Shunt Filter                                         | 33       |

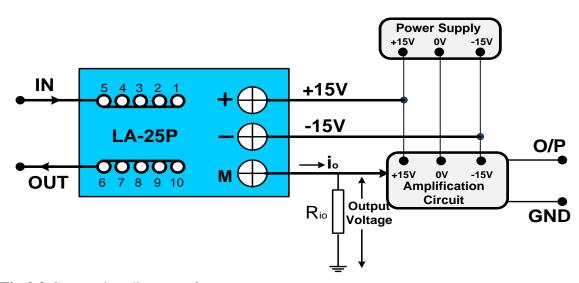

| 3.9   | Connection diagram of current sensors                                           | 35       |

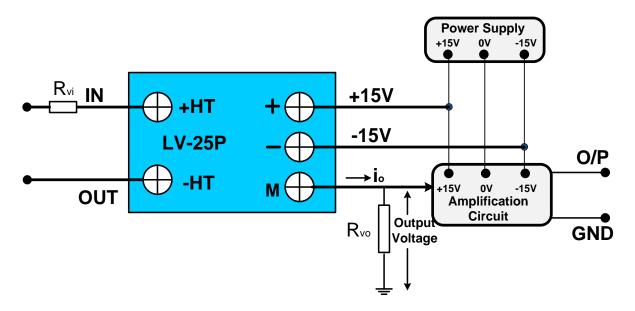

| 3.10  | Connection diagram of voltage sensors                                           | 36       |

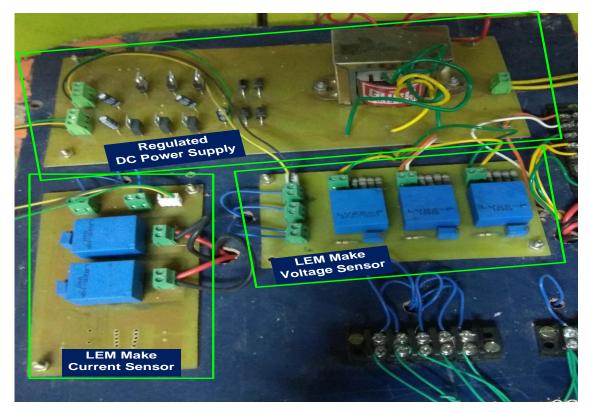

| 3.11  | Experimental connection of Current and Voltage sensors                          | 36       |

| 3.12  | (a) Amplification Circuit diagram (b) Practical Implementation of               | 37       |

|       | Amplification circuit driver circuit                                            |          |

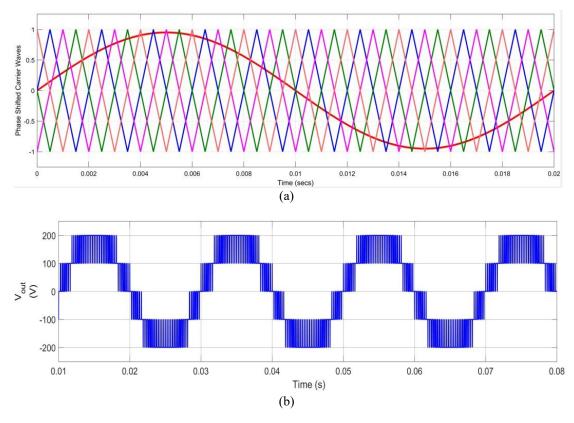

| 3.13  | Reference and Carrier signals at $m_f = 20$ , $m_a = 0.9$                       | 39       |

| 3.14  | Output Phase Voltage (Vout) of 5-Level MLI                                      | 39       |

| 3.15  | Single Diode model of PV array                                                  | 40       |

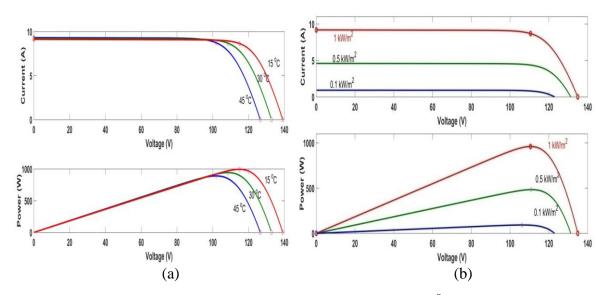

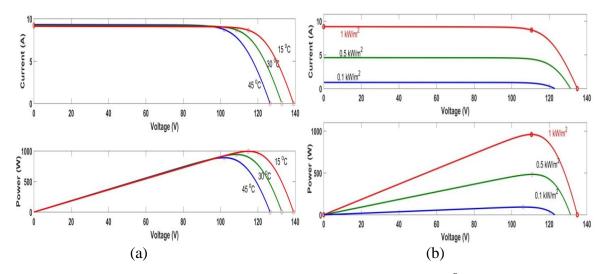

| 3.16  | I-V and P-V Characteristics (a) Fixed temperature of 25°C at varying            | 42       |

|       | irradiance (b) Fixed irradiance of 1000w/m <sup>2</sup> at varying temperatures |          |

| 3.17  | Scaled down prototype model of proposed system                                  | 43       |

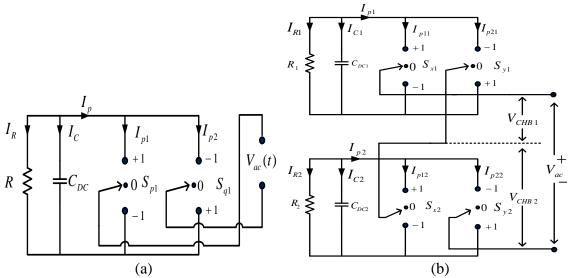

| 3.18  | (a) Circuit of conventional 2L inverter (b) Circuit of 5L CHB-MLI               | 44       |

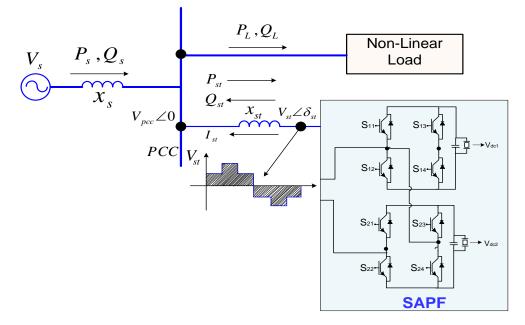

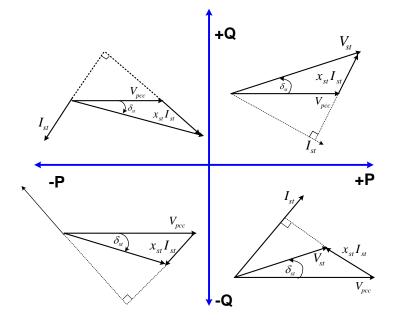

| 4.1   | Schematic of single-phase distribution system                                   | 52       |

| 4.2   | Operating Characteristics of SAPF                                               | 52       |

| 4.3   | Generalized circuit of 5-level MLI                                              | 53       |

| 4.4   | Schematic diagram of the proposed system                                        | 55       |

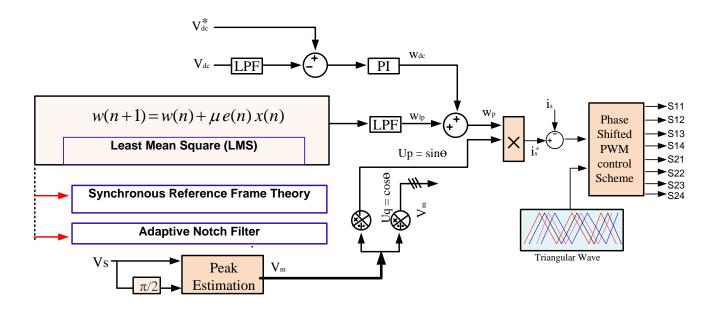

| 4.5   | DSP implementation of conventional algorithms                                   | 56       |

| 4.6  | Phase shifted scheme for 5-level CHB-MLI and output voltage of 5-level CHB-MLI                                            | 59 |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

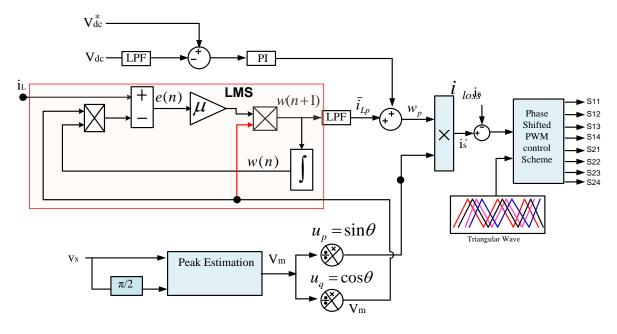

| 4.7  | Control block implementation of LMS algorithm                                                                             | 60 |

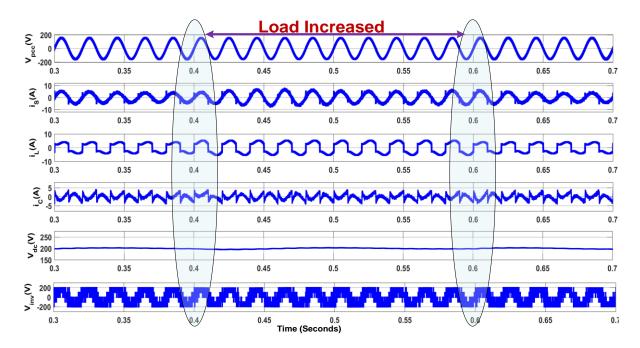

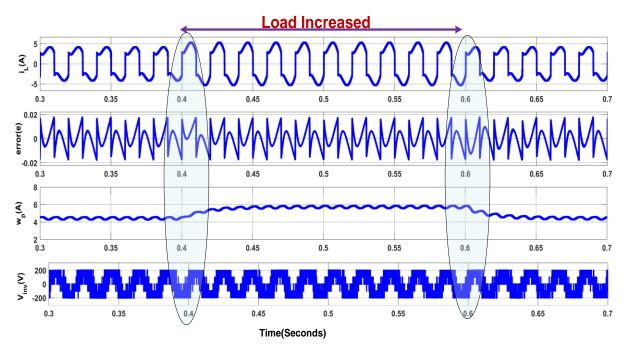

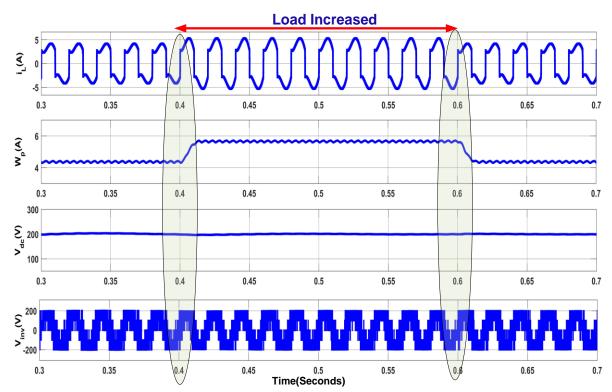

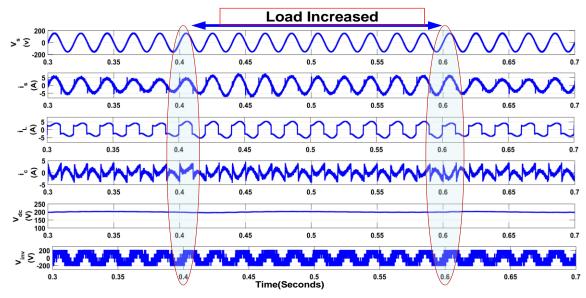

| 4.8  | Simulated waveforms of $v_s$ , $i_s$ , $i_L$ , $i_C$ , $V_{dc}$ and $v_{inv}$ during load variation at                    | 61 |

|      | t=0.4s and t=0.6s with LMS algorithm                                                                                      |    |

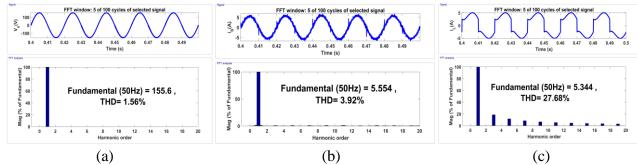

| 4.9  | Waveforms of $v_s$ , $i_S$ and $i_L$ along with THD analysis                                                              | 61 |

| 4.10 | Simulation Results of load current $i_L(A)$ , $w_p(A)$ , $i_C(A)$ and $V_{dc}(V)$ with                                    | 62 |

|      | LMS algorithm                                                                                                             |    |

| 4.11 | Steady state simulated waveforms of $V_s$ w.r.t $i_s$ , $i_L$ , $i_C$ ) with LMS                                          | 63 |

|      | algorithm                                                                                                                 |    |

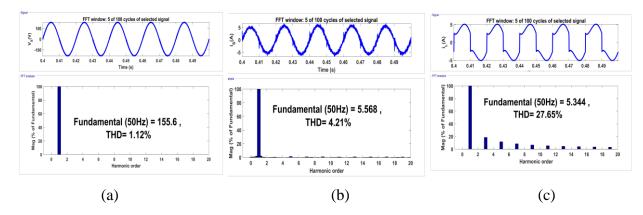

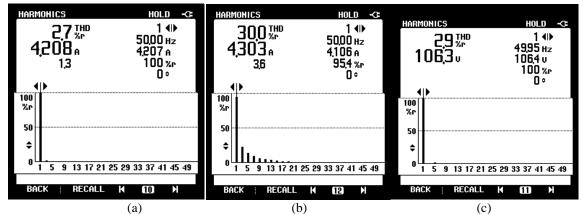

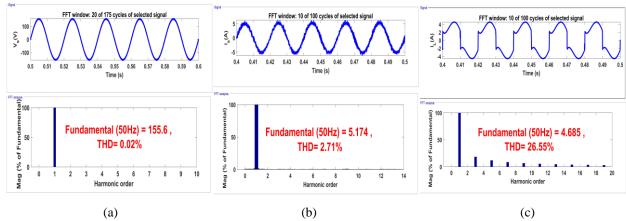

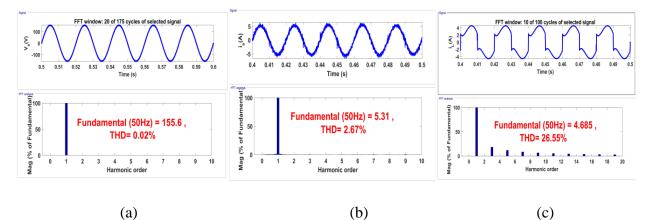

| 4.12 | Steady state THD analysis of $i_s$ , $i_L$ , $V_s$ ) with LMS algorithm                                                   | 63 |

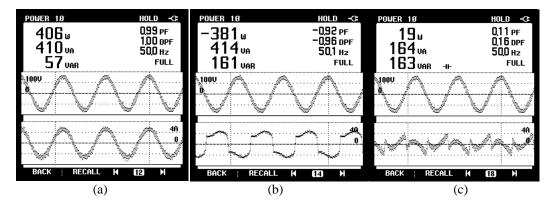

| 4.13 | Steady state active and reactive power in source, load and compensator                                                    | 64 |

|      | side with LMS algorithm                                                                                                   |    |

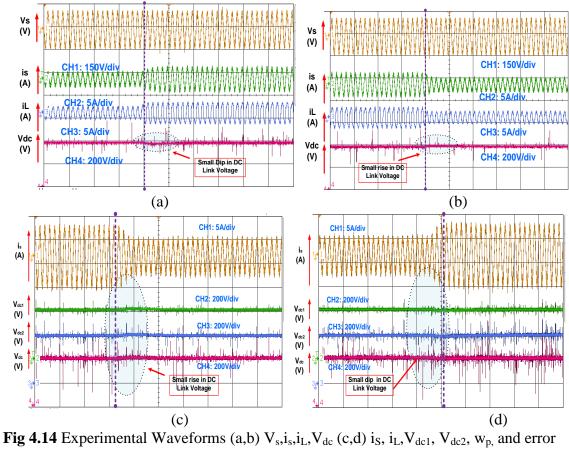

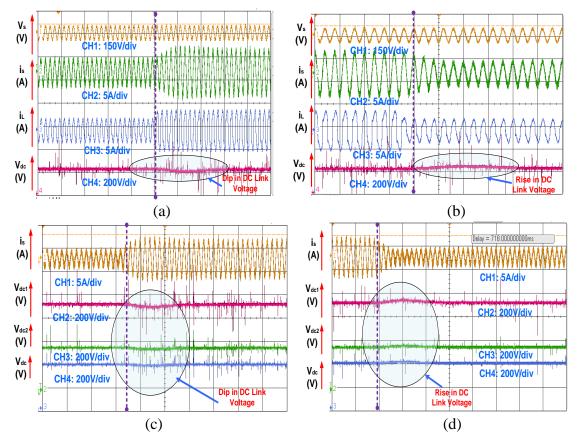

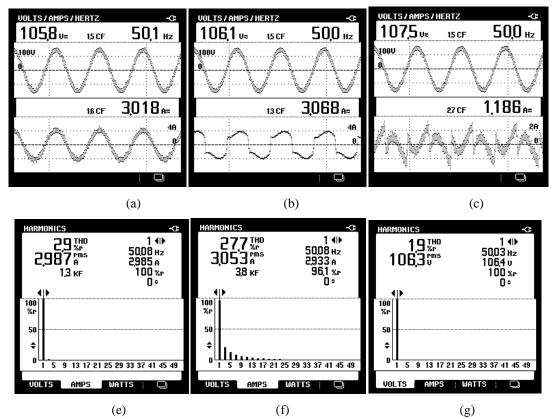

| 4.14 | Experimental Waveforms (a,b) $V_s$ , $i_s$ , $i_L$ , $V_{dc}$ (c,d) $i_S$ , $i_L$ , $V_{dc1}$ , $V_{dc2}$ , $w_{p_1}$ and | 65 |

|      | error under dynamic load variations                                                                                       |    |

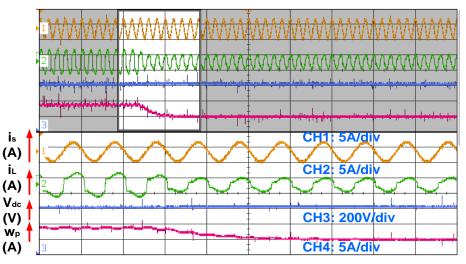

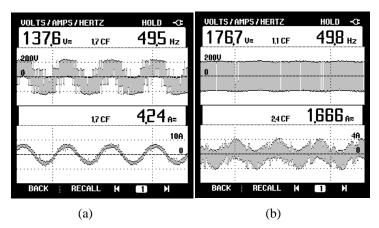

| 4.15 | Experimental waveforms of $is, i_L, V_{dc}, w_p$ under dynamic load variations                                            | 65 |

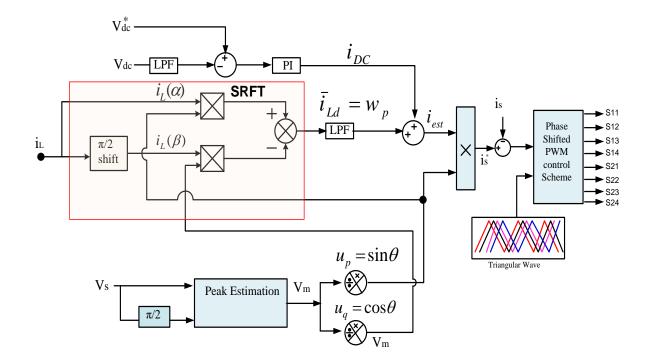

| 4.16 | Block diagram of SRFT control algorithm                                                                                   | 67 |

| 4.17 | Simulated waveforms of $V_{s},\!i_{s},\!i_{L},\!i_{C},V_{dc}$ and $V_{inv}$ during load variation at                      | 68 |

|      | t=0.4s and t=0.6s with SRFT                                                                                               |    |

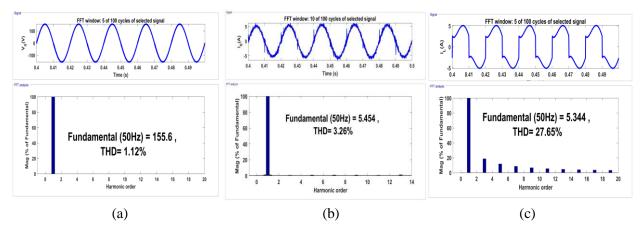

| 4.18 | Waveforms of $v_s i_s$ and $i_L$ along with THD analysis with SRFT                                                        | 68 |

|      | algorithm                                                                                                                 |    |

| 4.19 | Simulation Results of load current $i_L(A)$ , $w_p(A)$ , $i_C(A)$ and $V_{dc}(V)$ with                                    | 69 |

|      | SRFT                                                                                                                      |    |

| 4.20 | Steady state performance of system (a) $v_{S}$ and $i_{S}\left(b\right)v_{S}$ and $i_{L}$ (c) $v_{S}$ and                 | 70 |

|      | $i_{C}$ along with harmonic spectrum (d) %THD of $i_{S}$ (e) %THD of $i_{L}$ and                                          |    |

|      | (f) % THD of v <sub>s</sub> using SRFT                                                                                    |    |

| 4.21 | Waveforms of active and reactive power flow in the system using SRFT                                                      | 70 |

| 4.22 | Dynamic performances with SRFT algorithm                                                                                  | 71 |

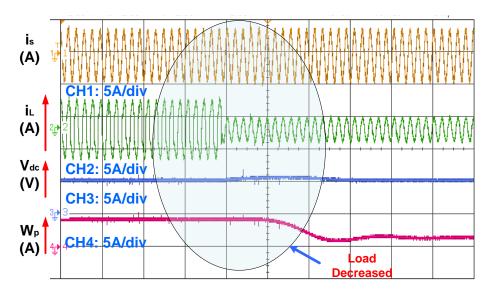

| 4.23 | Dynamic behaviour of the proposed system $i_S(A)$ . $i_L(A)$ , $V_{DC}$ and $w_p$                                         | 72 |

|      | under decrease in load with SRFT algorithm                                                                                |    |

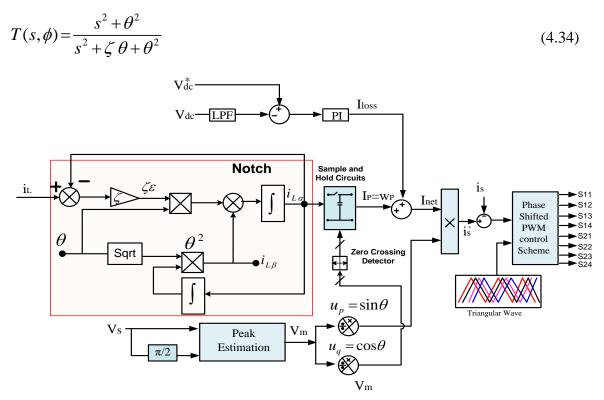

| 4.24 | Control algorithms Digital implementation in dSPACE 1104 processor                                                        | 72 |

|      |                                                                                                                           |    |

with Notch filter

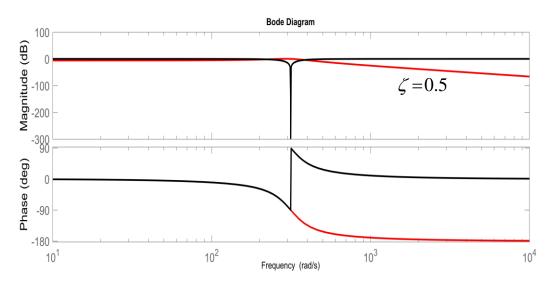

| 4.25       | Bode diagram of Notch Filter                                                                           | 73  |

|------------|--------------------------------------------------------------------------------------------------------|-----|

| 4.26       | Simulated waveforms of $v_s$ , $i_s$ , $i_L$ , $i_C$ , $V_{dc}$ and $V_{inv}$ during load variation at | 74  |

|            | t=0.4s and t=0.6s with Notch Filter                                                                    |     |

| 4.27       | Waveforms of $v_s i_s$ and $i_L$ along with THD analysis with Notch Filter                             | 75  |

| 4.28       | Simulation Results of load current $i_L(A)$ , $W_p(A)$ , $V_{dc}(V)$ and $V_{inv}(V)$                  | 75  |

|            | with Notch Filter                                                                                      |     |

| 4.29       | Steady state simulated waveforms of $V_s$ w.r.t $i_s$ , $i_L$ , $i_C$ with Notch filter                | 76  |

| 4.30       | Steady state THD analysis of $i_s$ , $i_L$ , $V_s$ with Notch filter                                   | 76  |

| 4.31       | Steady state active and reactive power in source, load and compensator                                 | 77  |

|            | side with Notch filter                                                                                 |     |

| 4.32       | Shows the output voltage waveform of 5-level MLI w.r.t $i_{s}$ and output $% i_{s}$                    | 77  |

|            | voltage of 2-level inverter w.r.t ic with Notch filter                                                 |     |

| 4.33       | Dynamic behaviour of the system with Notch filter                                                      | 78  |

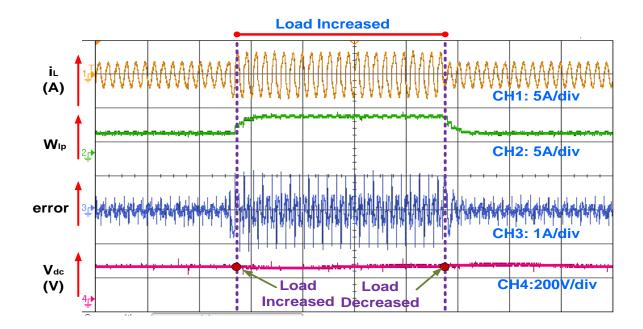

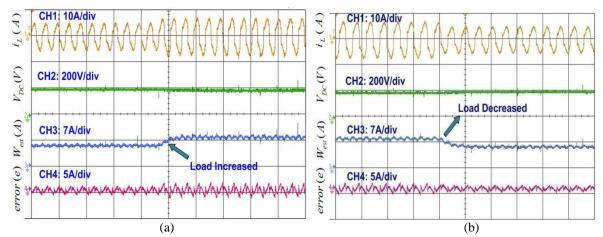

| 4.34       | Dynamic behaviour of the Notch filter $i_L$ , $w_{lP}$ , error(r) and $V_{dc}$ under                   | 79  |

|            | increase and decrease in load                                                                          |     |

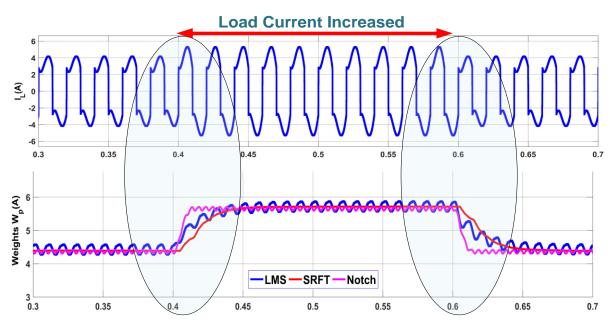

| 4.35       | Simulation based performance comparison of fundamental weights                                         | 80  |

|            | under varying load during t=0.4s to 0.6s with LMS, SRFT and Notch                                      |     |

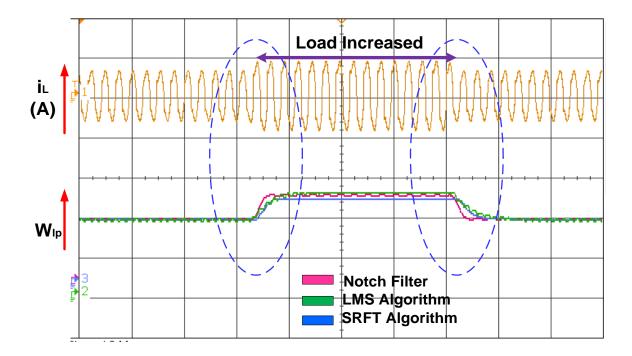

| 4.36       | Experimental based performance comparison of fundamental weights                                       | 80  |

|            | under varying load with LMS, SRFT and Notch                                                            |     |

| 5.1        | Schematic of the proposed system                                                                       | 83  |

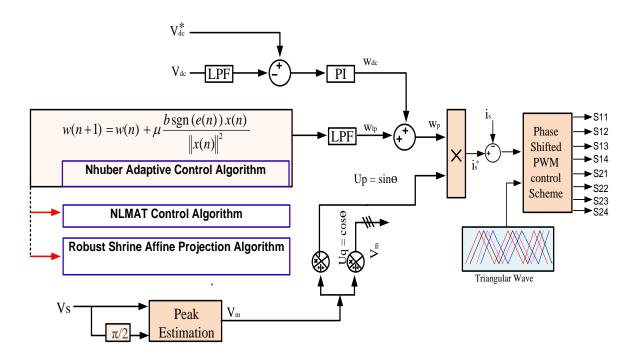

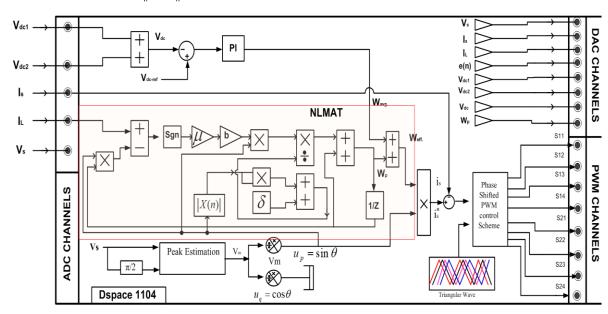

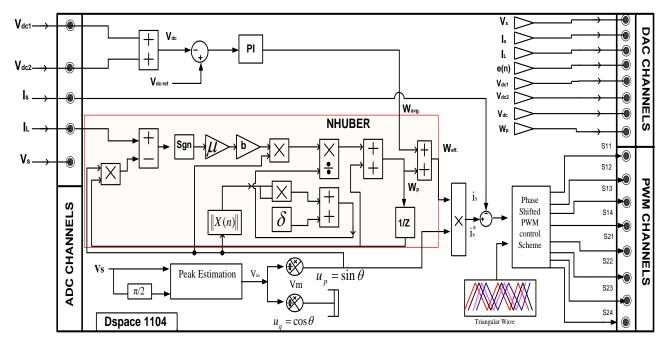

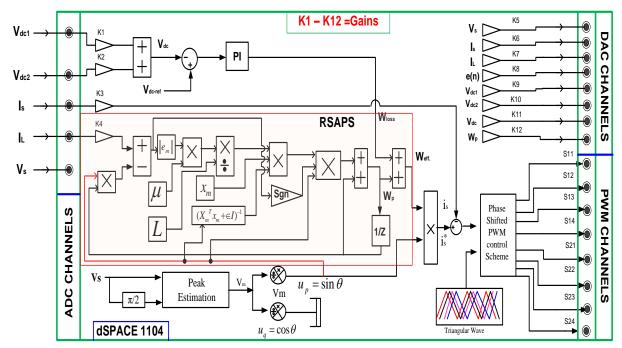

| 5.2        | DSP implementation of advanced adaptive control algorithms on CHB-                                     | 84  |

|            | MLI                                                                                                    | _   |

| 5.3        | DSP implementation of NLMAT control algorithm using dSPACE-                                            | 86  |

|            | 1104                                                                                                   | 07  |

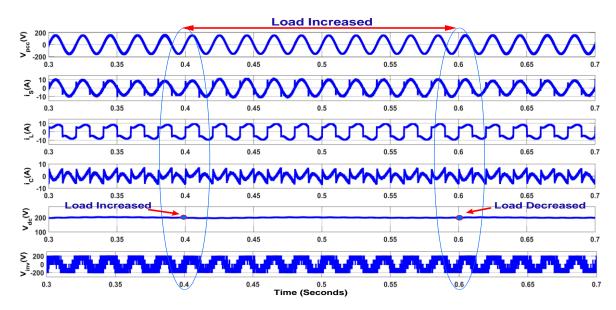

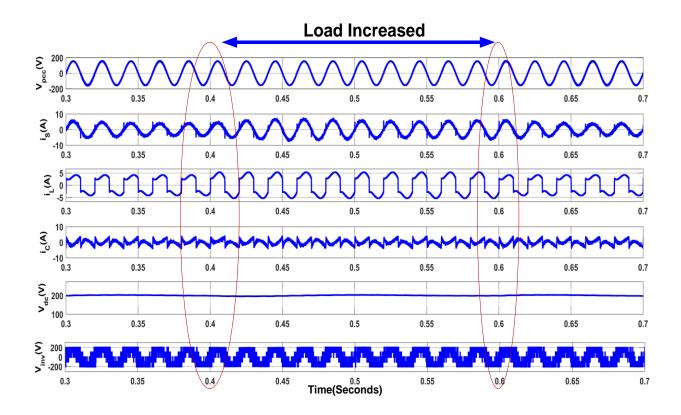

| 5.4        | Simulated waveforms of $v_s, i_s, i_L, i_C, V_{inv}$ and $V_{dc}$ during load variation at             | 87  |

|            | t=0.6s and t=1s with NLMAT Algorithm                                                                   | 0.0 |

| 5.5        | Simulated waveforms of $v_s, i_s, i_L, i_C, V_{inv}$ and $V_{dc}$ during load variation at             | 88  |

| <b>F</b> - | t=0.6s and t=1s with NLMAT Algorithm                                                                   | 0.0 |

| 5.6        | Waveforms of $V_s$ , $i_s$ and $i_L$ along with THD analysis with NLMAT                                | 88  |

|            | Algorithm                                                                                              |     |

| 5.7  | Steady state results of source current (i <sub>s</sub> ), load current (i <sub>L</sub> ) and compensating current (i <sub>c</sub> ) with respect to PCC voltage( $V_{pcc}$ ) and associated THD values | 89  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.8  | Active and Reactive power in source, load and compensator side with                                                                                                                                    | 90  |

|      | NLMAT algorithm                                                                                                                                                                                        |     |

| 5.9  | Output voltage waveform of 5-level MLI w.r.t $i_{s}$ and output voltage of                                                                                                                             | 90  |

|      | 2-level inverter w.r.t $i_c$ with NLMAT Algorithm                                                                                                                                                      |     |

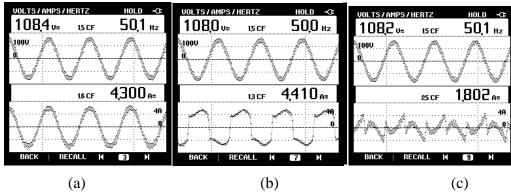

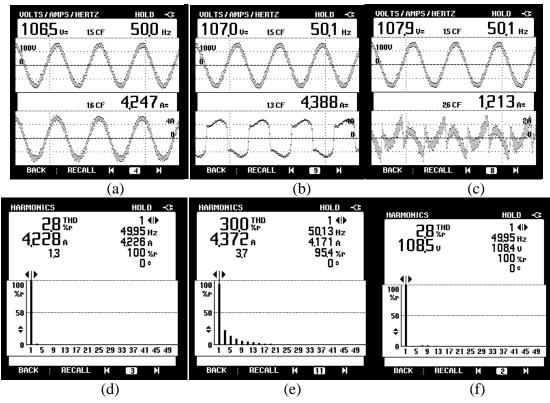

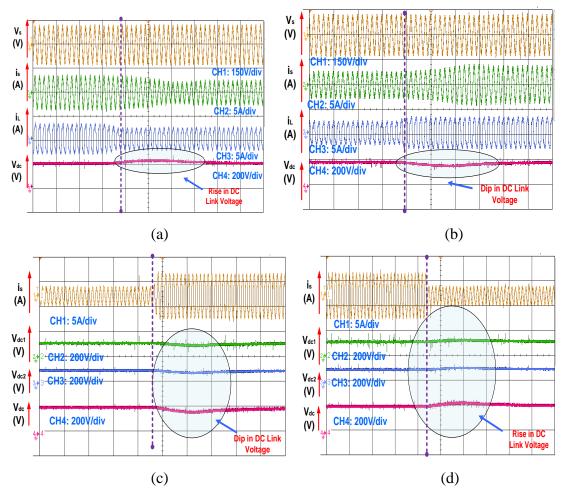

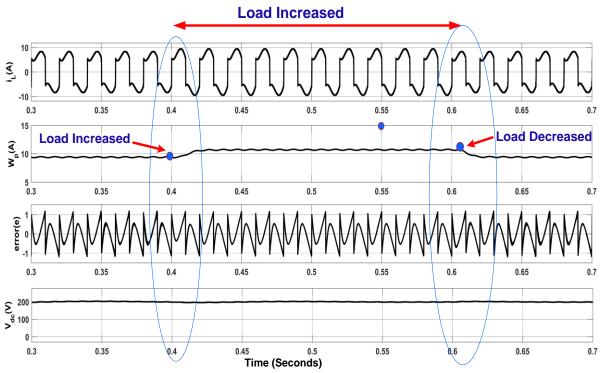

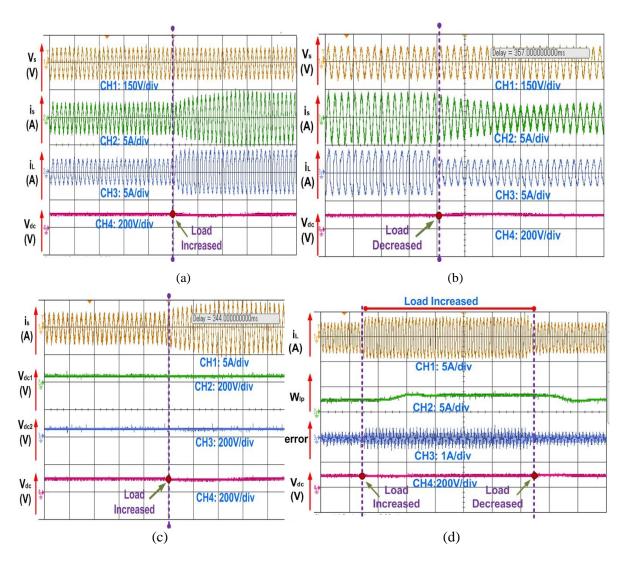

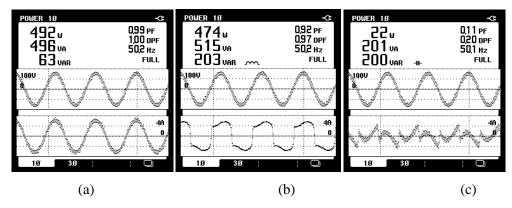

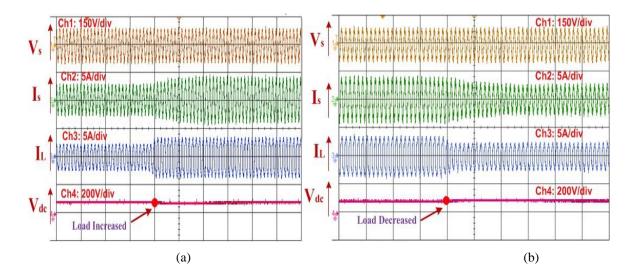

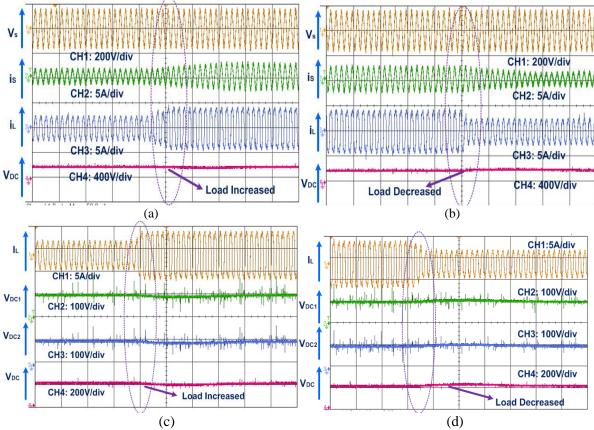

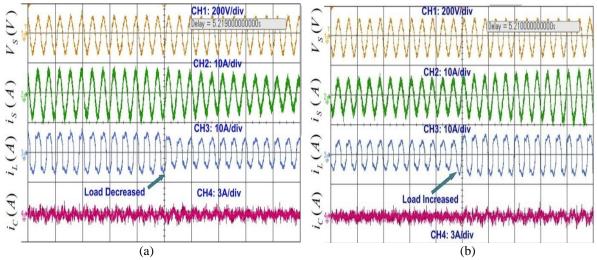

| 5.10 | Experimental waveforms of (a,b) Vs,is,iL,Vdc (c,d) $i_S$ , $i_L$ ,V <sub>dc1</sub> ,V <sub>dc2</sub> , $w_p$                                                                                           | 91  |

|      | and error under dynamic load variations with NLMAT algorithm                                                                                                                                           |     |

| 5.11 | Reference supply current estimation using N-Huber Algorithm using                                                                                                                                      | 92  |

|      | dSPACE-1104 under normal grid condition                                                                                                                                                                |     |

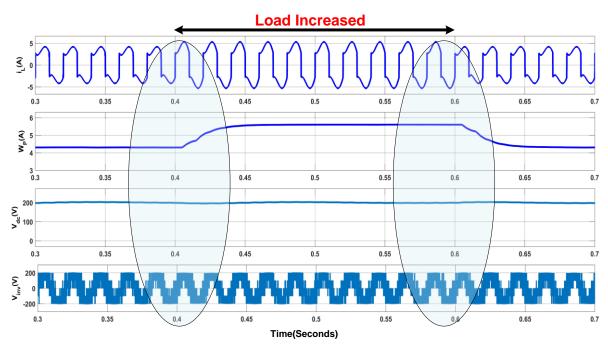

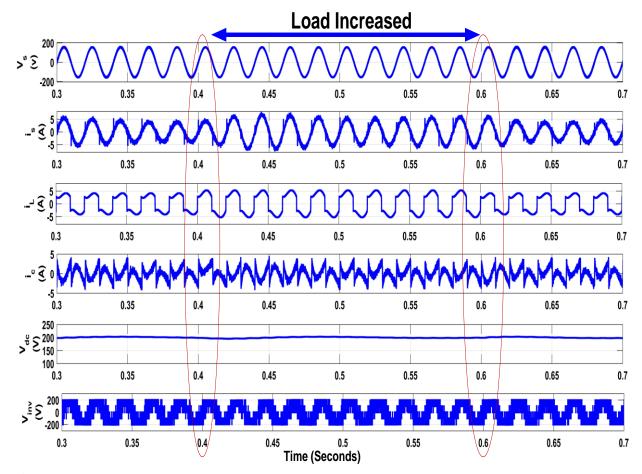

| 5.12 | Simulated waveforms of $V_s$ , $i_s$ , $i_L$ , $i_c$ , $V_{dc}$ , $V_{inv}$ during sudden load variation                                                                                               | 93  |

| 5.13 | at t=0.4s and t=0.6 s with NHuber algorithm<br>Simulation waveforms of $i_L$ , weights $(w_p)$ , error (e) and $V_{dc}$ during                                                                         | 96  |

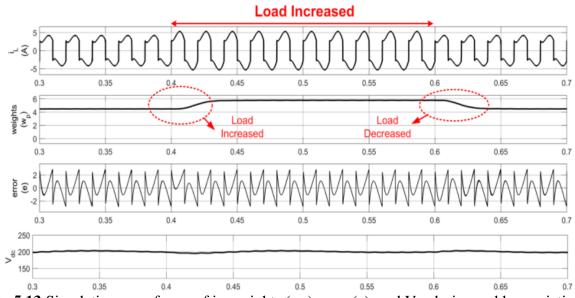

|      | sudden variation of load at $t=0.4s$ and $t=0.6s$ with NHuber algorithm                                                                                                                                |     |

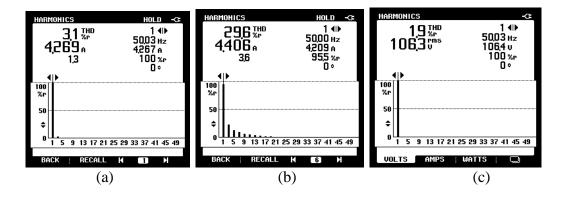

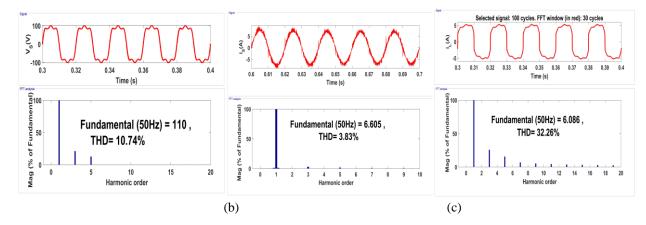

| 5.14 | Harmonic spectra of (a) PCC voltage, Vs, (b) grid current is, (c) load                                                                                                                                 | 96  |

|      | current, i <sub>L</sub> in PFC mode with NHuber algorithm                                                                                                                                              |     |

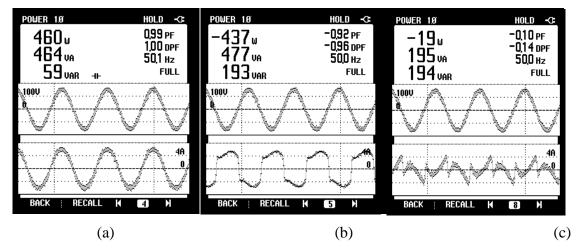

| 5.15 | Steady state active and reactive power in source, load and compensator                                                                                                                                 | 97  |

|      | side with NHuber algorithm                                                                                                                                                                             |     |

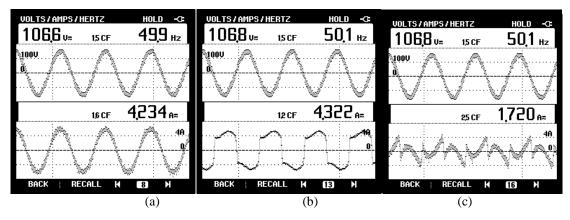

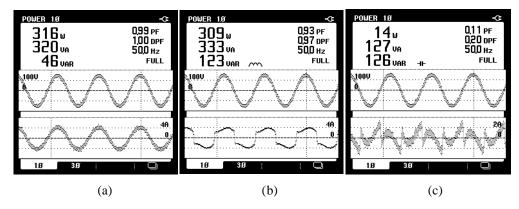

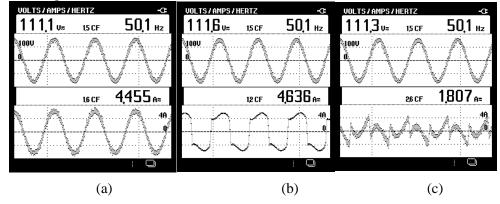

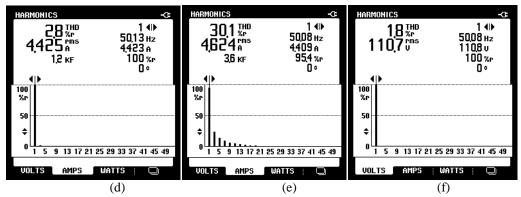

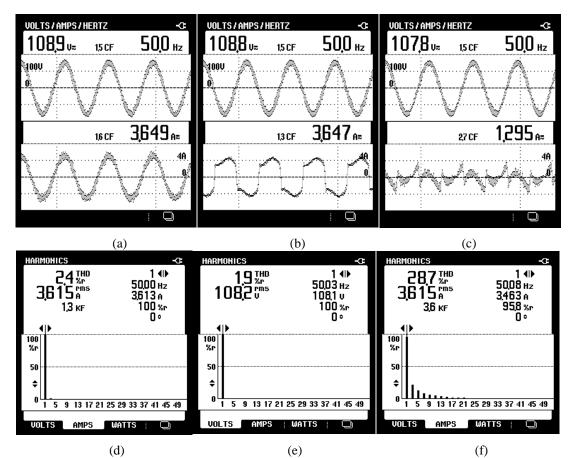

| 5.16 | Steady state results of source current (is), Load current (iL), and compensating current (ic) with respect to PCC voltage(Vpcc) and associated THD values                                              | 97  |

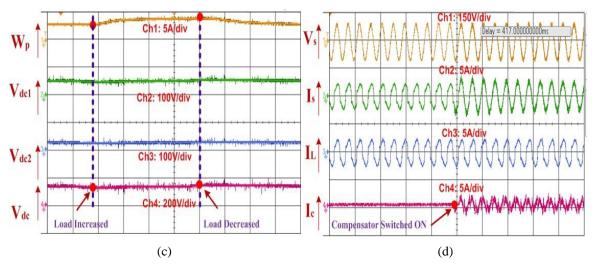

| 5.17 | Weights( $w_p$ ), dc link voltage of capacitor 1 ( $V_{dc1}$ ), dc link voltage of                                                                                                                     | 98  |

|      | capacitor-2 (V_{dc2}) and total dc link voltage (V_{dc}), source voltage (V_s),                                                                                                                        |     |

|      | source current (is),load current (iL) and compensating current (ic) with                                                                                                                               |     |

|      | Nhuber Algorithm                                                                                                                                                                                       |     |

| 5.18 | Detailed block diagram of proposed controller with RSAPS Algorithm                                                                                                                                     | 99  |

| 5.19 | Simulated waveforms of $V_s$ , $i_s$ , $i_L$ , $i_c$ , $V_{dc}$ , $V_{inv}$ during sudden load variation                                                                                               | 103 |

|      | at t=0.4s and t=0.6 s with RSAPS algorithm                                                                                                                                                             |     |

| 5.20 | Intermediate system behaviour under dynamic load change at t=0.4s and                                                                                                                                  | 104 |

|      | t=0.6s with RSAPS algorithm                                                                                                                                                                            |     |

| 5.21 | Harmonic spectra of (a) PCC voltage, Vs, (b) grid current is, (c) load                                                                                                                                 | 104 |

|      |                                                                                                                                                                                                        |     |

current,  $i_{L} \text{in}\ \text{PFC}$  mode with RSAPS algorithm

| 5.22 | 2 Steady state performance of system (a) $V_S$ and $i_S\left(b\right)V_S$ and $i_L$ (c) $V_S$ |     |  |

|------|-----------------------------------------------------------------------------------------------|-----|--|

|      | and $i_C$ along with harmonic spectrum (d) %THD of $i_S$ (e) %THD of $V_S$                    |     |  |

|      | and (f) % THD of $i_L$                                                                        |     |  |

| 5.23 | Steady state active and reactive power in source, load and compensator                        | 106 |  |

|      | side with RSAPS algorithm                                                                     |     |  |

| 5.24 | Dynamic behaviour of the proposed system with RSAPS algorithm                                 |     |  |

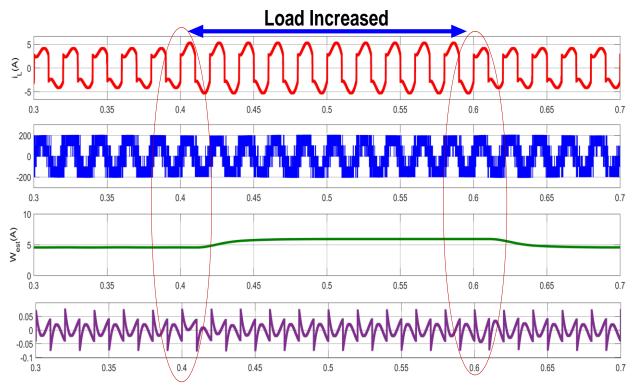

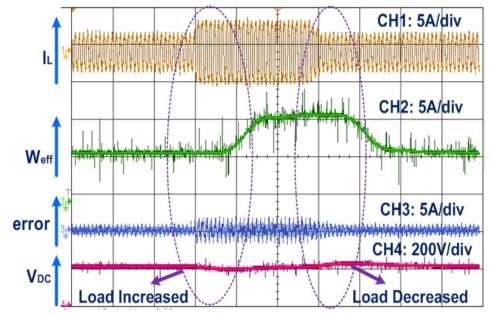

| 5.25 | 5.25 Dynamic behaviour of the proposed system (a) $I_L$ , $w_{eff}$ , error(e) and            |     |  |

|      | $V_{DC}$ under increase and decrease in load with RSAPS algorithm                             |     |  |

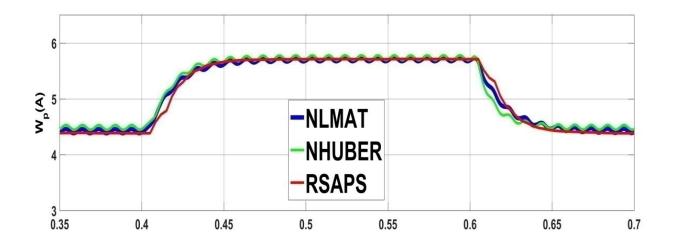

| 5.26 | 26 Simulation based performance comparison of fundamental weights                             |     |  |

|      | under varying load during t=0.4s to 0.6s with NLMAT, NHuber,                                  |     |  |

|      | RSAPS                                                                                         |     |  |

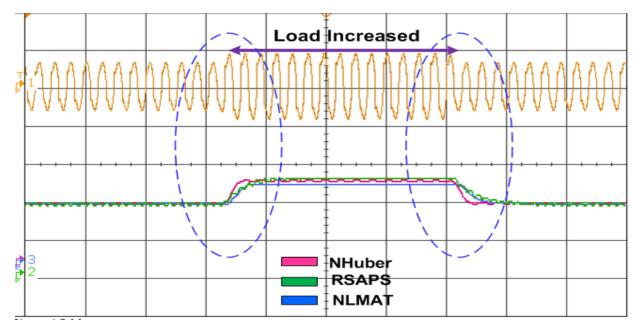

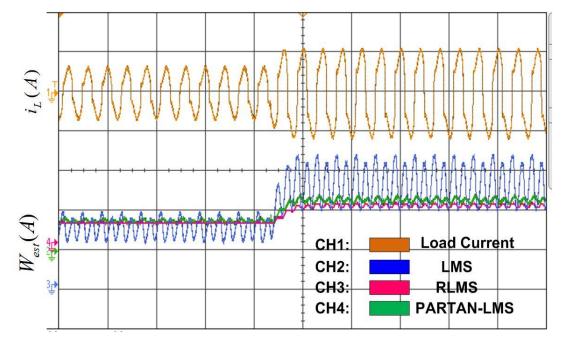

| 5.27 | Experimental based performance comparison of fundamental weights                              | 109 |  |

|      | under varying load with NLMAT, NHuber, RSAPS                                                  |     |  |

| 6.1  | Generalized block diagram of SRF-PLL 1                                                        |     |  |

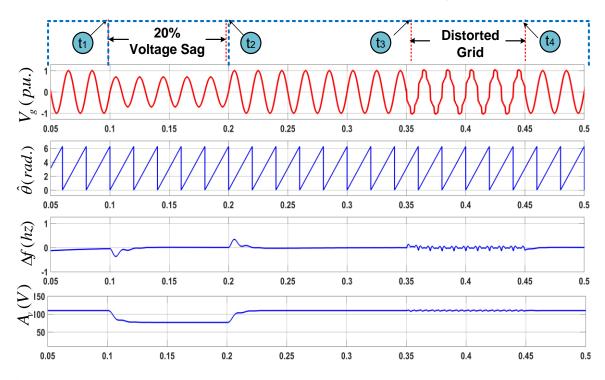

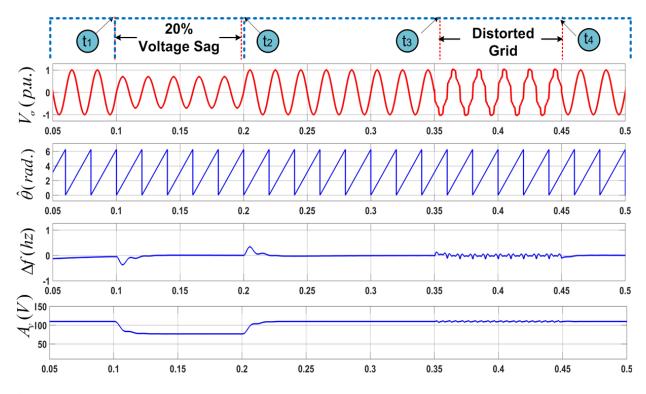

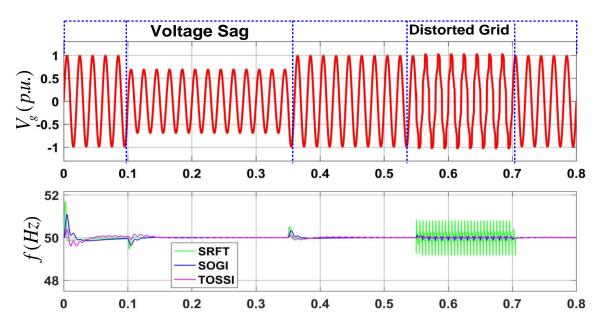

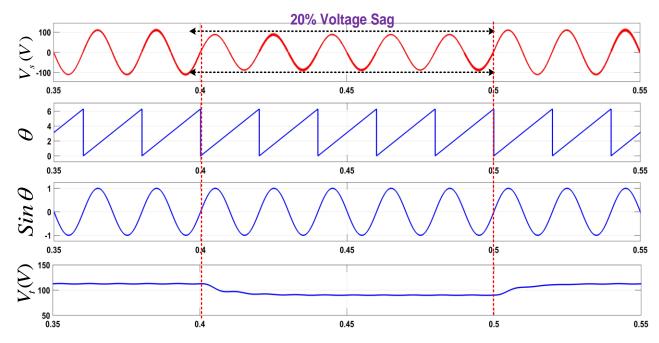

| 6.2  | 6.2 Simulation performance of SRF-PLL under 20% voltage sag and                               |     |  |

|      | distorted grid                                                                                |     |  |

| 6.3  | Simulation performance of SRF-PLL under $\pi/2$ phase shift and 20%                           | 116 |  |

|      | DC - Offset                                                                                   |     |  |

| 6.4  | Experimental performance of SRF-PLL under distorted grid conditions                           | 117 |  |

| 6.5  | Experimental performance of SRF-PLL under phase shift of $\pi/2$                              | 118 |  |

| 6.6  | .6 Experimental performance of SRF-PLL under 20% DC-offset in grid                            |     |  |

|      | voltage                                                                                       |     |  |

| 6.7  | Experimental performance of SRF-PLL under grid voltage variation                              | 119 |  |

|      | from Sag to Swell                                                                             |     |  |

| 6.8  | Basic Structure of SOGI-PLL                                                                   | 120 |  |

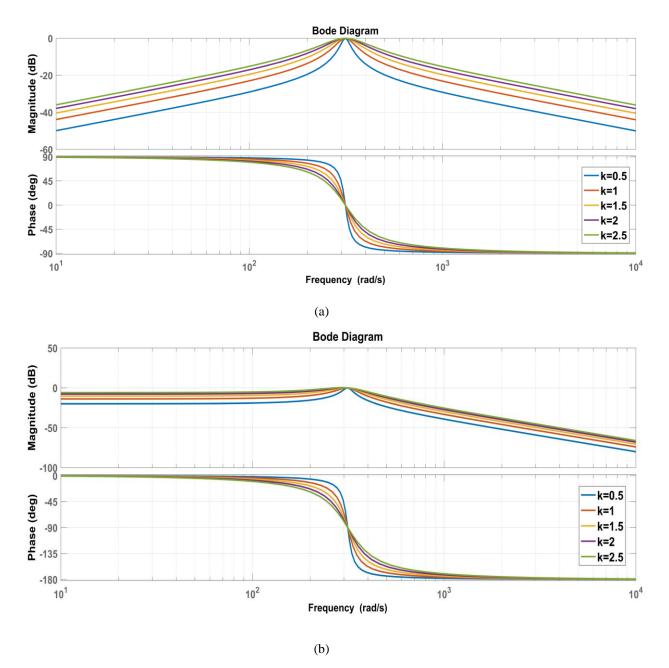

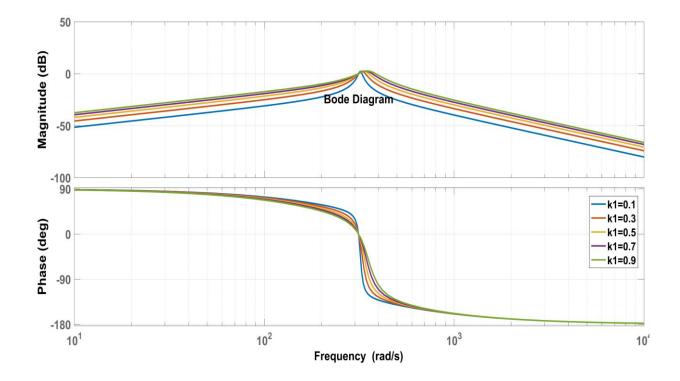

| 6.9  | Bode plots for (a) In-phase component $T_{\alpha}(s)$ (b) Quadrature                          | 121 |  |

|      | component $T_{\beta}(s)$                                                                      |     |  |

| 6.10 | Simulation performance of SOGI-PLL under 20% voltage sag and                                  | 122 |  |

|      | distorted grid                                                                                |     |  |

|      |                                                                                               |     |  |

xix

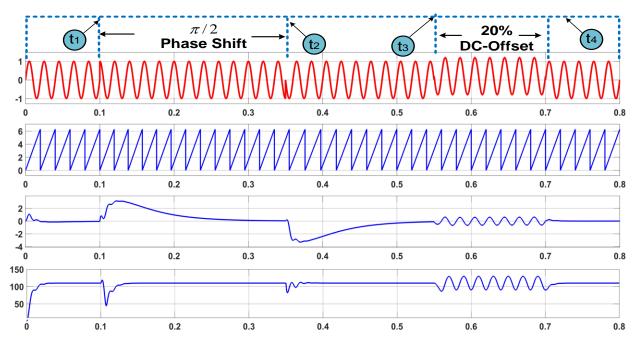

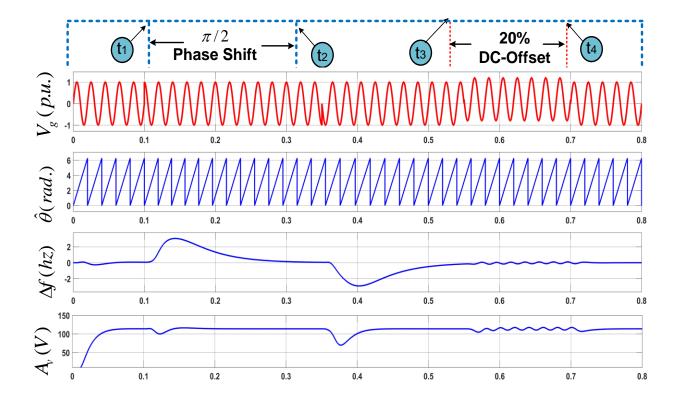

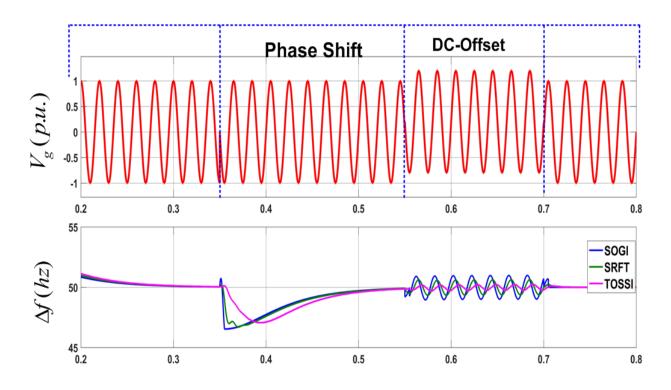

| 6.11 | Simulation performance of SOGI-PLL under $\pi/2$ phase shift and 20% | 123 |  |  |

|------|----------------------------------------------------------------------|-----|--|--|

|      | DC - Offset                                                          |     |  |  |

| 6.12 | Experimental performance of SOGI-PLL under distorted grid            | 124 |  |  |

|      | conditions                                                           |     |  |  |

| 6.13 | Experimental performance of SOGI-PLL under phase shift of $\pi/2$    |     |  |  |

| 6.14 | Experimental performance of SOGI-PLL under 20% DC-offset in grid     |     |  |  |

|      | voltage                                                              |     |  |  |

| 6.15 | 5 Experimental performance of SOGI-PLL under grid voltage variation  |     |  |  |

|      | from swell to sag                                                    |     |  |  |

| 6.16 | Generalized Block diagram of TOSSI-PLL 12                            |     |  |  |

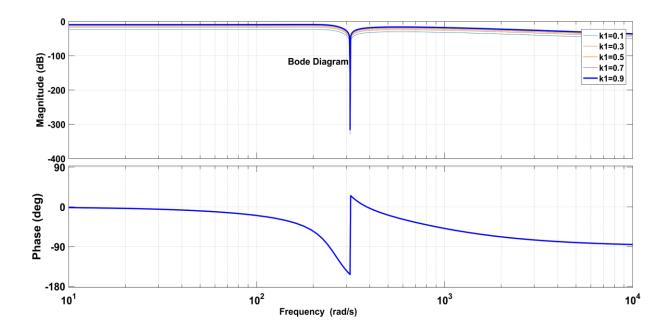

| 6.17 | Bode plot of TOSSI –PLL for in-phase component $T_{\alpha}(s)$       |     |  |  |

| 6.18 | Bode plot of TOSSI –PLL for quadrature component $T_{\beta}(s)$      |     |  |  |

| 6.19 | Simulation performance of TOSSI-PLL under 20% voltage sag and        | 129 |  |  |

|      | distorted grid                                                       |     |  |  |

| 6.20 | Simulation performance of SOGI-PLL under $\pi/2$ phase shift and 20% | 130 |  |  |

|      | DC - Offset                                                          |     |  |  |

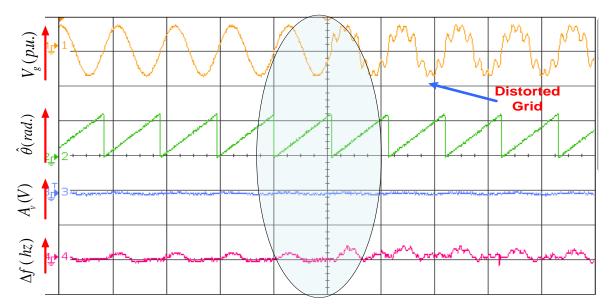

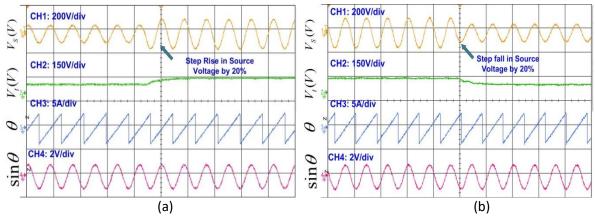

| 6.21 | Experimental performance of TOSSI-PLL under distorted grid           | 131 |  |  |

|      | conditions                                                           |     |  |  |

| 6.22 | Experimental performance of TOSSI-PLL under phase shift of $\pi/2$   | 131 |  |  |

| 6.23 | Experimental performance of TOSSI-PLL under 20% DC-offset in grid    |     |  |  |

|      | voltage                                                              |     |  |  |

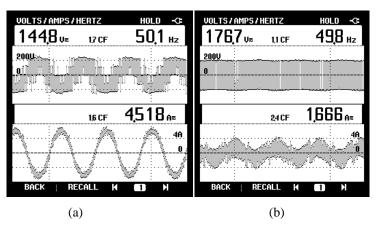

| 6.24 | Experimental performance of TOSSI-PLL under grid voltage variation   | 133 |  |  |

|      | from Swell to Sag                                                    |     |  |  |

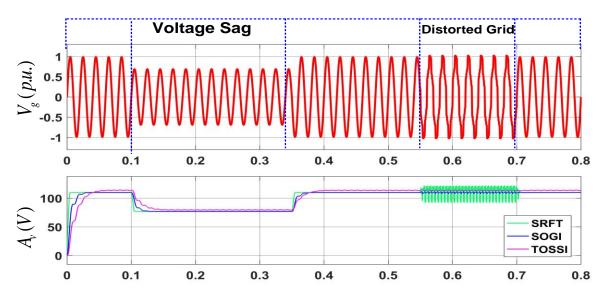

| 6.25 | Frequency Variation of SRF-PLL, SOGI-PLL & TOSSI-PLL under           | 134 |  |  |

|      | voltage sag/swell and distorted grid                                 |     |  |  |

| 6.26 | Amplitude Variation of SRF-PLL, SOGI-PLL & TOSSI-PLL under           | 134 |  |  |

|      | voltage sag/swell and distorted grid                                 |     |  |  |

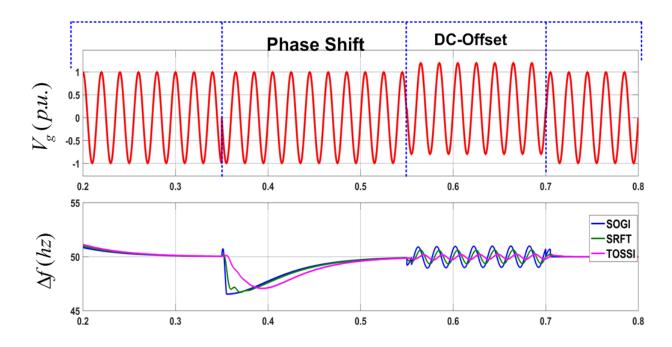

| 6.27 | Frequency Variation of SRF-PLL, SOGI-PLL & TOSSI-PLL under           | 135 |  |  |

|      | phase shift and DC-offset                                            |     |  |  |

| 6.28 | Amplitude Variation of SRF-PLL, SOGI-PLL & TOSSI-PLL under           | 135 |  |  |

ХХ

phase shift and DC-offset

|      | Finit sint much control                                                                                                                                                           |      |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

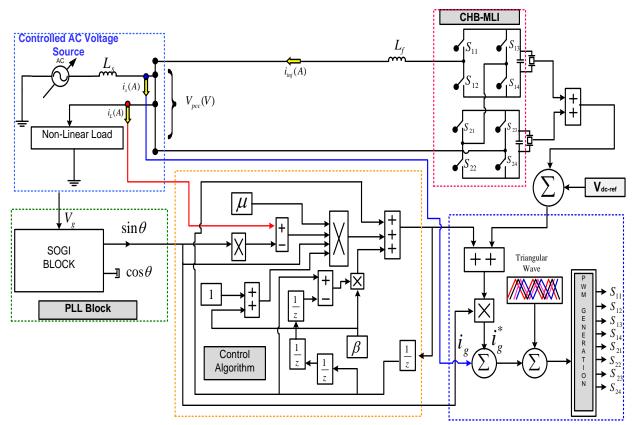

| 6.29 | System configuration of PARTAN-LMS Algorithm                                                                                                                                      | 137  |  |

| 6.30 | Control Scheme block diagram of PARTAN-LMS Algorithm                                                                                                                              |      |  |

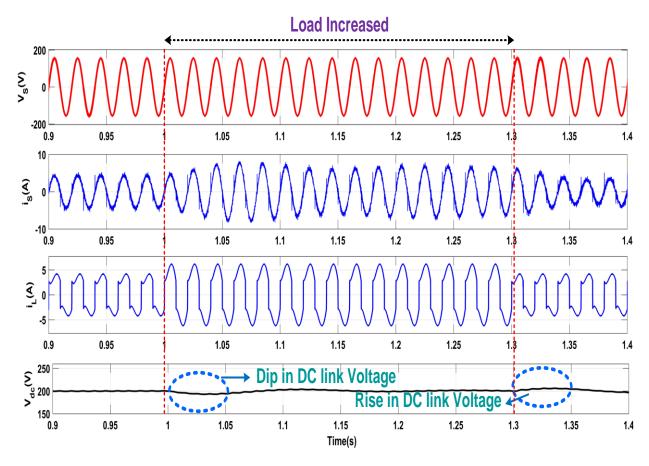

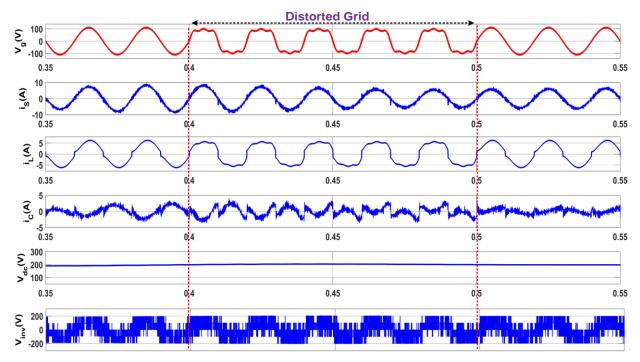

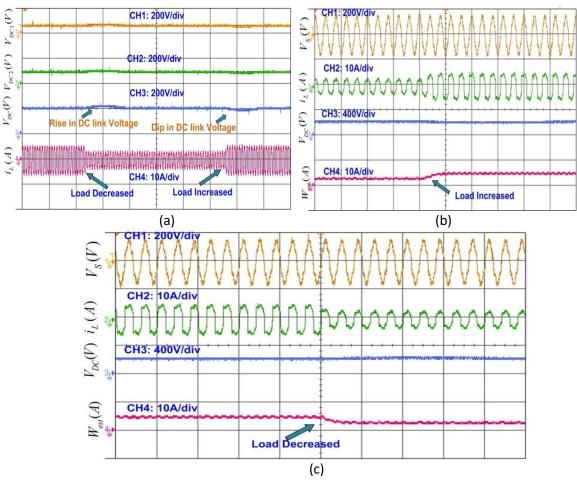

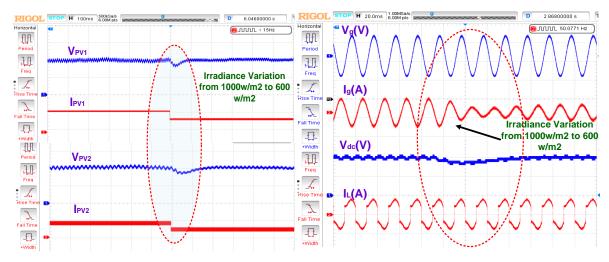

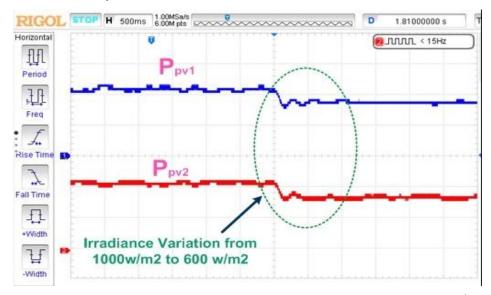

| 6.31 | Simulation results of grid voltage $v_g(V)$ , grid current $i_g(A)$ , load current $i_L(A)$ and total DC link voltages $V_{dc}(V)$                                                |      |  |

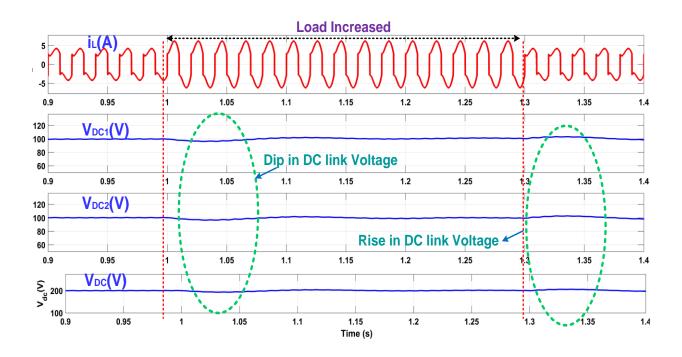

| 6.32 | Dynamic waveforms of $i_L(A)$ , $V_{DC1}(V)$ , $V_{DC2}(V)$ and $V_{DC}(V)$ under step                                                                                            | 143  |  |

| 6.00 | change in load at t=1s and t=1.3s                                                                                                                                                 | 1.10 |  |

| 6.33 | Waveforms of $V_{pcc}(V)$ , phase angle $\theta$ , unit sine templates in $\theta$ estimated                                                                                      | 143  |  |

|      | voltage amplitude $V_t(V)$ under voltage swell at t=0.4s to 0.5s                                                                                                                  |      |  |

| 6.34 | Dynamic state waveforms of $V_{pcc}(V)$ , $i_S(A)$ , $i_L(A)$ , $i_C(A)$ , $V_{DC}(V)$ and                                                                                        | 144  |  |

|      | $V_{inv}(V)$ under distorted grid voltage and varying load                                                                                                                        |      |  |

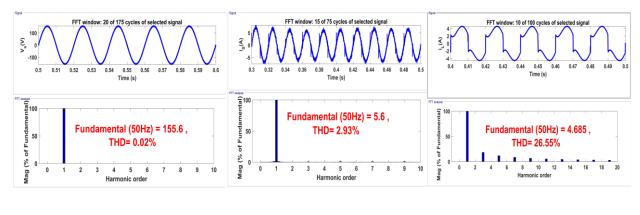

| 6.35 | Harmonic spectrum THD of (a) Source Voltage $v_S(V)$ (b) Source                                                                                                                   | 144  |  |

|      | Current $i_{S}(A)$ (c) Load current $i_{L}(A)$ under distorted grid                                                                                                               |      |  |

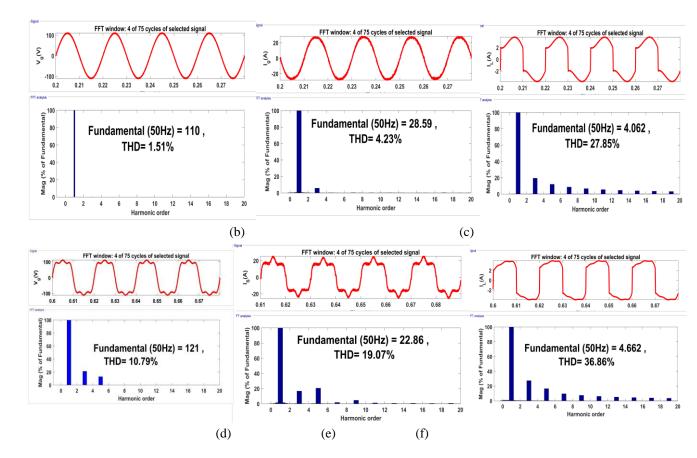

| 6.36 | Harmonic spectrum (THD) analysis (a) $v_s(V)$ with $i_s(A)$ (b) $v_s(V)$ with $i_L(A)$ (c) $v_s(V)$ with $i_C(A)$ (d) THD of $v_s(V)$ (e) THD of $i_L(A)$ and (f) THD of $i_s(A)$ | 145  |  |

| 6.37 | Active and Reactive power flow in 5-Level SAPF control by PARTAN-                                                                                                                 | 146  |  |

| 0.57 | LMS                                                                                                                                                                               | 140  |  |

| 6.38 | Experimental waveforms of $V_s(V)$ , $i_s(A)$ , $i_L(A)$ and $i_C(A)$ under varying                                                                                               | 146  |  |

| 0.50 | load and distorted grid                                                                                                                                                           | 140  |  |

| 6.39 | Variation in DC link voltages, source current, load current and                                                                                                                   | 147  |  |

| 0.39 |                                                                                                                                                                                   | 147  |  |

| 6 40 | fundamental estimated weights                                                                                                                                                     | 147  |  |

| 6.40 |                                                                                                                                                                                   |      |  |

| 6.41 | Intermediate results of w <sub>est</sub> , error with reference to DC link voltage and                                                                                            | 148  |  |

|      | load current under varying load                                                                                                                                                   |      |  |

| 6.42 | Performance comparisons of weights using different adaptive                                                                                                                       | 149  |  |

|      | algorithms w.r.t load current                                                                                                                                                     |      |  |

| 7.1  | Single Stage grid connected PV system for 5-level CHB-MLI                                                                                                                         | 154  |  |

| 7.2  | I-V and P-V Characteristics (a) Fixed temperature of 25°C at varying                                                                                                              | 155  |  |

|      | irradiance (b) Fixed irradiance of $1000$ W/m <sup>2</sup> at varying temperatures                                                                                                |      |  |

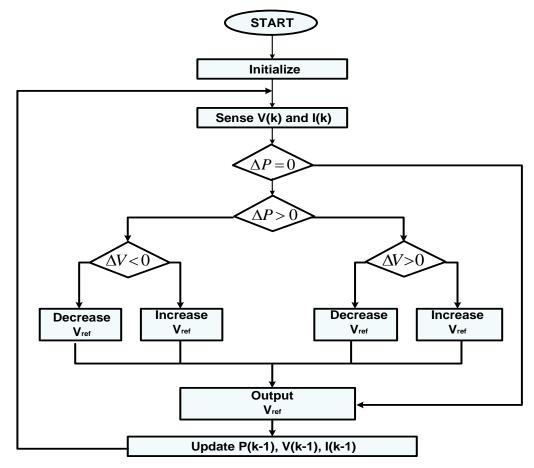

| 7.3  | Flow chart of P &O algorithm                                                                                                                                                      | 156  |  |

|      |                                                                                                                                                                                   |      |  |

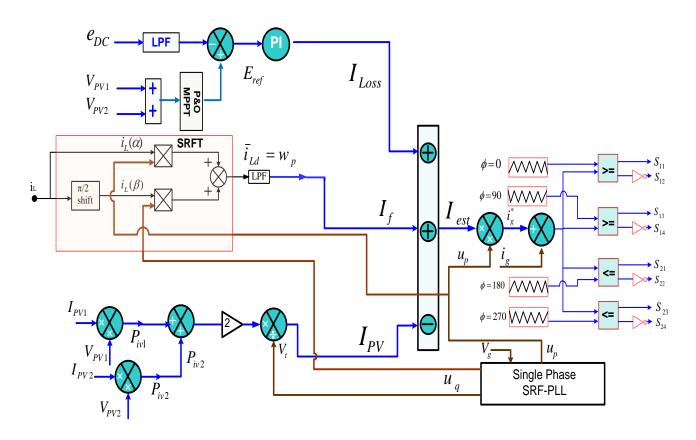

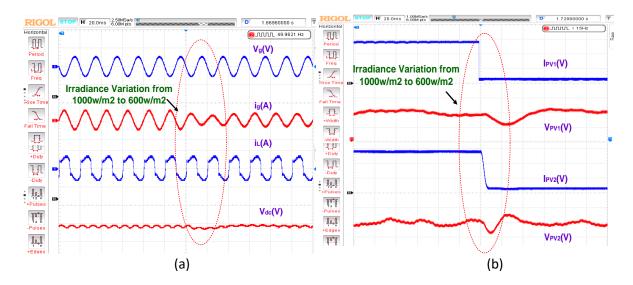

| 7.4  | Single Phase single stage PV array based SRFT-PLL                                                                                                                                                | 158 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

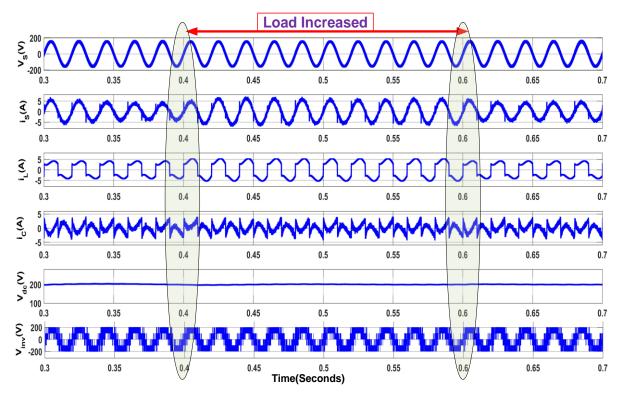

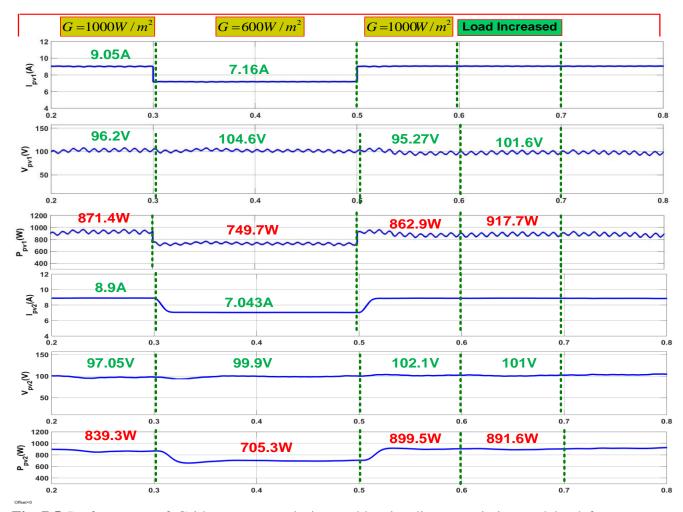

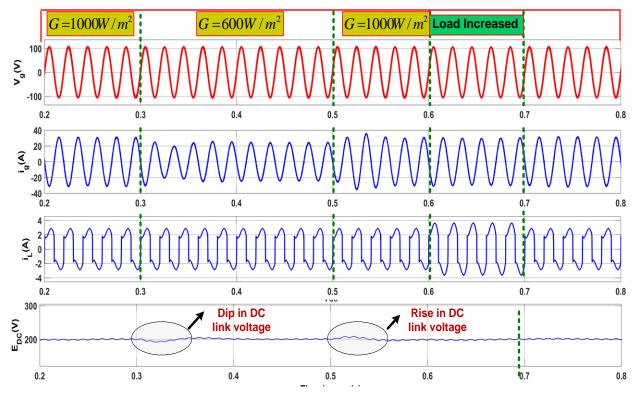

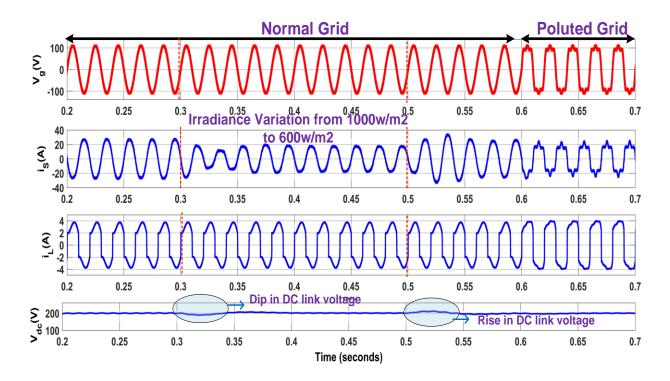

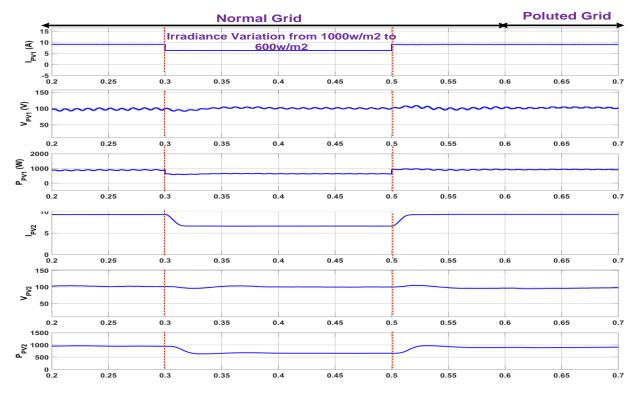

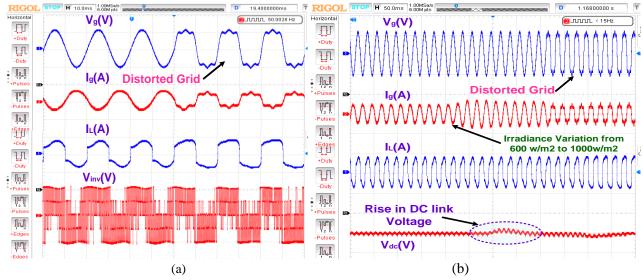

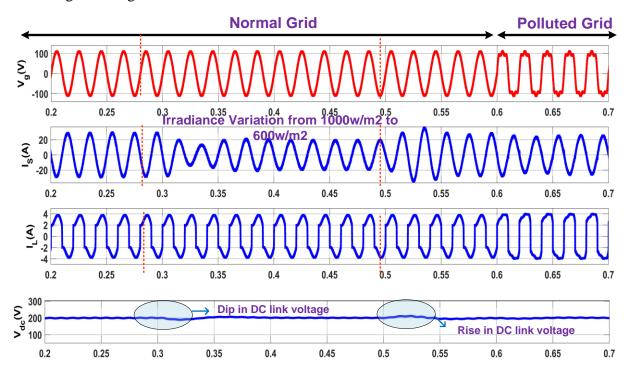

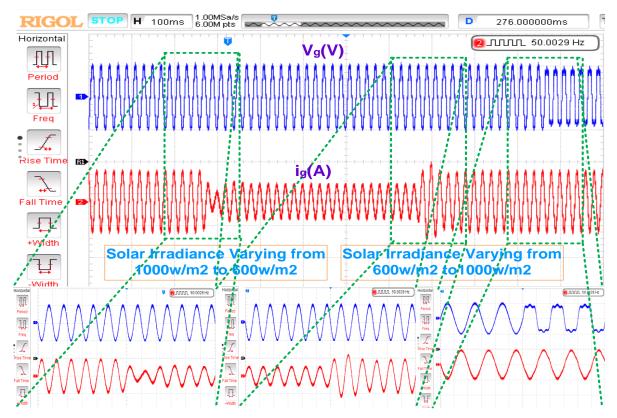

| 7.5  | Performance of Grid parameters during sudden irradiance variation and                                                                                                                            | 160 |

|      | load for SRFT-PLL                                                                                                                                                                                |     |

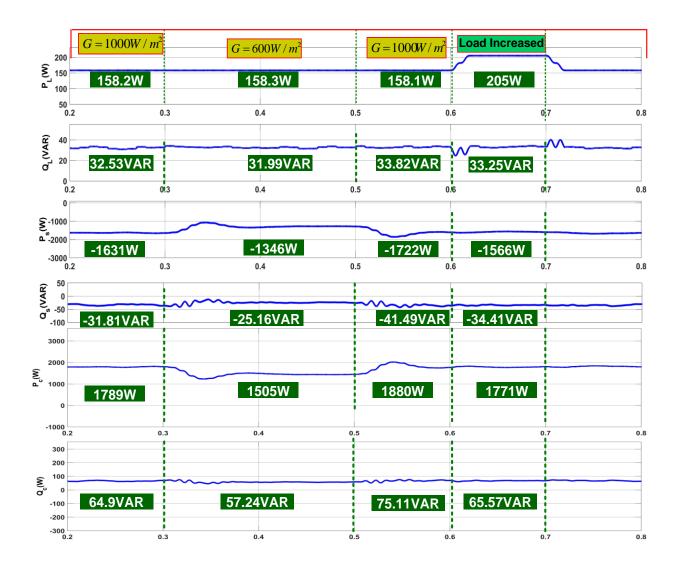

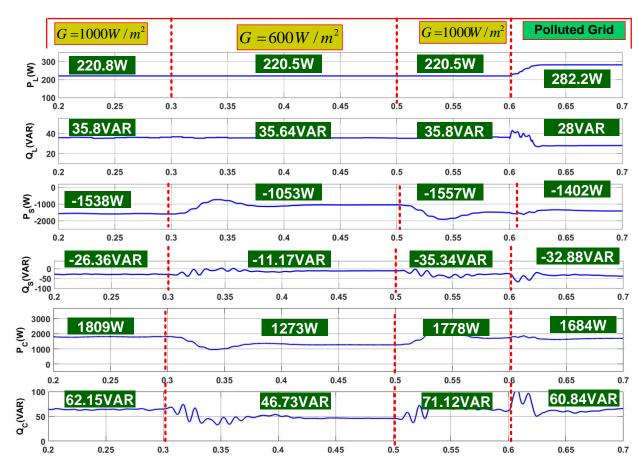

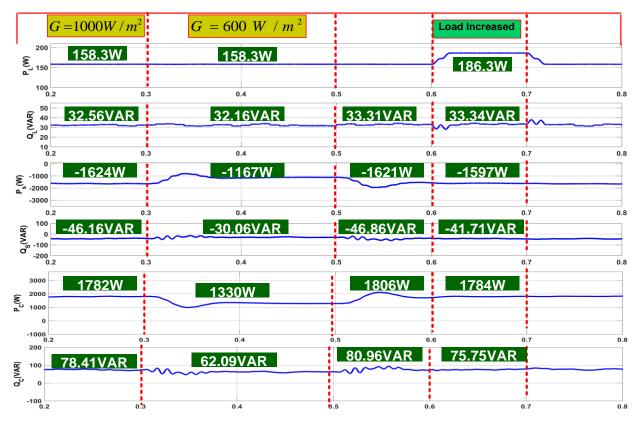

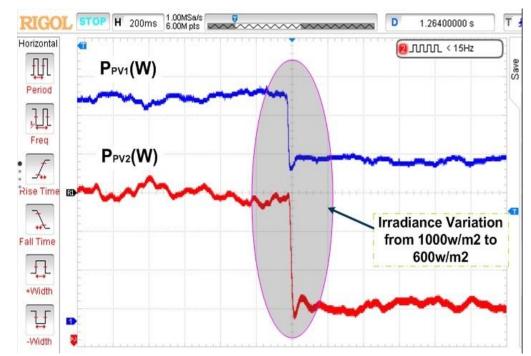

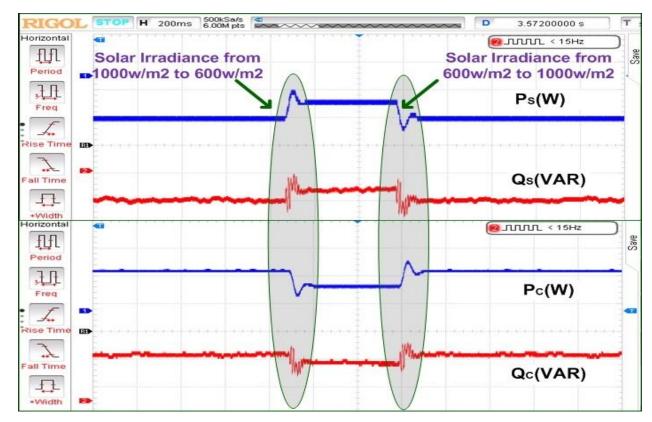

| 7.6  | Simulation results of source power ( $P_s, Q_s$ ), load power ( $P_L, Q_L$ ) and                                                                                                                 | 161 |

|      | compensating power $(P_c, Q_c)$ under sudden variation of Irradiance and                                                                                                                         |     |

|      | Load                                                                                                                                                                                             |     |

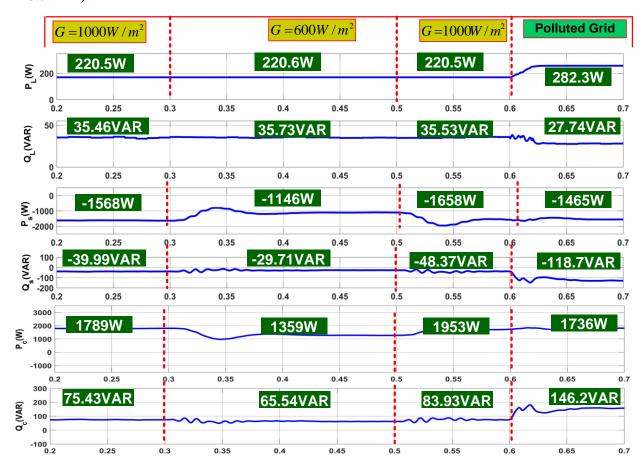

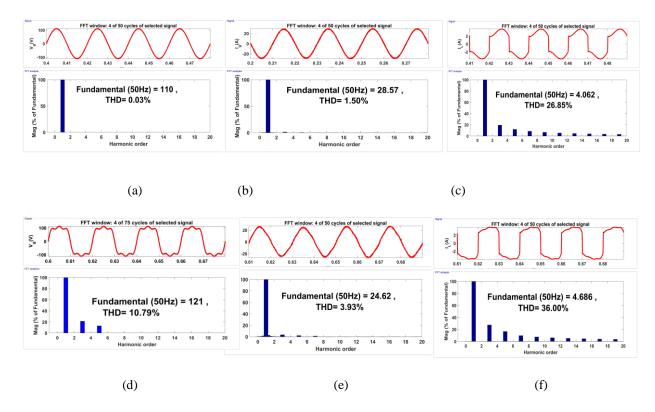

| 7.7  | Simulation of parameters for single phase grid connected system under                                                                                                                            | 162 |