# ANALYSIS OF DIFFERENT POWER FACTOR CORRECTED CONVERTERS

# A DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

# FOR THE AWARD OF THE DEGREE

OF

# MASTER OF TECHNOLOGY

IN

# POWER ELECTRONICS AND SYSTEMS

Submitted by:

# SANJEEV SHARMA

2K21/PES/13

Under the supervision of

# **MR. SAURABH MISHRA**

(Assistant Professor, EED, DTU)

MR. HIMANSHU SINGH

(Assistant Professor, EED, DTU)

# DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042 MAY, 2023

#### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

# **CANDIDATE'S DECLARATION**

I hereby certify that the workcontained herein Major Project-II entitled "ANALYSIS OF DIFFERENT POWER FACTOR CORRECTED CONVERTERS" in fulfilment of the requirement for the award of the degree of Master of Technology in Power System and submitted to the Electrical Engineering department, Delhi Technological University, Delhi, is a genuine record of my own work which is carried out under supervision of Asst. Prof. Saurabh Mishra and Asst. Prof. Himanshu Singh during the period of July 2021 to May 2023.

I have not submitted the information contained in this report for any other award of degree or to any other Institute/University.

DATE: PLACE:

SANJEEV SHARMA (2K21/PES/13)

# DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

#### **CERTIFICATE**

I hereby certify that the project Dissertation titled "ANALYSIS OF DIFFERENT POWER FACTOR CORRECTED CONVERTERS" which is submitted by Sanjeev Sharma, Roll No. 2K21/PES/13, Department of Electrical Engineering, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

MR. SAURABH MISHRA SUPERVISOR (Assistant Prof., EED, DTU) MR. HIMANSHU SINGH SUPERVISOR (Assistant Prof., EED, DTU)

#### ABSTRACT

This thesis presents a thorough examination of power factor corrected converters, with a specific focus on five distinct topologies: Boost PFC Converter, ILDB PFC Converter, SBBPFC, BLSB PFC Converter, and TTMPB PFC Converter. The primary aim of this study is to assess and compare the performance of these converters in relation to power factor correction, efficiency, and other relevant parameters. The initial portion of the thesis provides an overview of power factor correction techniques, emphasizing the significance of achieving a high-power factor in modern power electronic systems. It discusses the limitations of conventional rectifiers and emphasizes the necessity for PFC converters to adhere to regulatory standards and enhance overall system efficiency.

Finding ways to enhance the input current (I<sub>in</sub>) waveform while preventing phase displacement has occupied a significant portion of power electronics research over the past two decades. Choosing the two most important 1- phase Power Factor Correction (PFC) topologies is the thesis's main goal. The Boost PFC Converter and the ILDB PFC converter are the investigated topology under the performance. In Simulink/MATLAB, the all investigated topologies performances are simulated. Additionally offered are efficiency evaluation and loss analysis. The simulation outcomes show that the BPFC converter topology with interleaved boost exhibits a somewhat greater efficiency. This innovative interleaving method optimizes CRM for each step. accurate 180-degree phase shift and natural current sharing. The subsequent sections concentrate on each individual converter topology. Each topology is elaborated upon in detail, encompassing its operating principle, control strategy, and critical design considerations. Mathematical models for each converter are derived, and simulation models are constructed to analyse their steady-state and dynamic characteristics. The simulation outcomes are validated through experimental tests conducted on prototype hardware.

A comparative analysis is carried out to evaluate the performance of the various PFC converter topologies. Parameters such as power factor, total harmonic distortion (THD), efficiency, and component stresses are considered in the comparison. Furthermore, the impact of load conditions and input voltage variations on converter performance is

investigated. Through the analysis and comparison, the strengths and limitations of each converter topology are identified. The findings provide valuable insights into the suitability of these converters for diverse applications, while taking into account factors such as cost, complexity, efficiency, and power density.

Lastly, recommendations are provided to aid in the selection of the most appropriate PFC converter topology based on specific application requirements. This study contributes to the existing knowledge by delivering a comprehensive analysis and comparison of five distinct PFC converter topologies, thereby facilitating well-informed decision-making in the design and implementation of power factor correction solution.

# **LIST OF FIGURES**

| Fig. 1.1 Importance of Power Factor                                                                                                                   | 2      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Fig. 1.2 Schematic of PFC for Battery charging                                                                                                        | 2      |

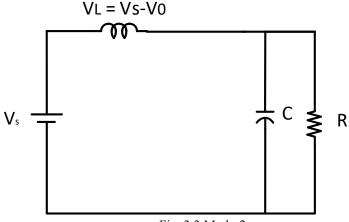

| Fig. 3.1 Schematic of Boost PFC Converter                                                                                                             | 13     |

| Fig. 3.2 Mode-1                                                                                                                                       | 14     |

| Fig. 3.3 Mode-2                                                                                                                                       | 15     |

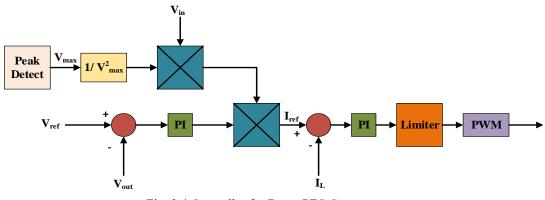

| Fig. 3.4 Controller for Boost PFC Converter                                                                                                           | 17     |

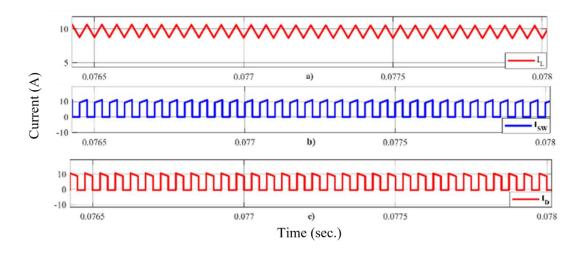

| Fig. 3.5 Current Waveform Boost PFC(BPFC) topology a). Inductor current(IL) b).                                                                       | Switch |

| Current c).Diode Current                                                                                                                              | 22     |

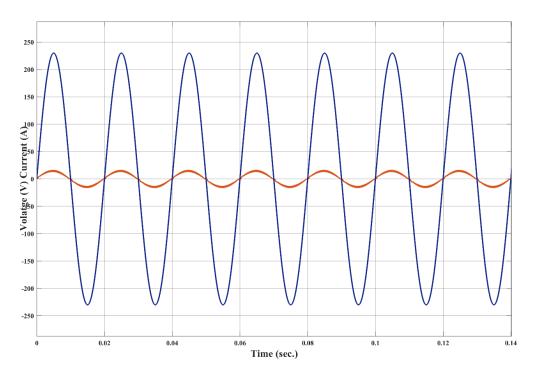

| Fig. 3.6 Input Current and Voltage Waveform for Boost PFC(BPFC) topology                                                                              | 22     |

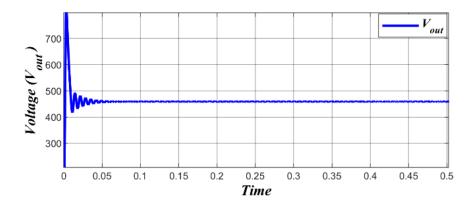

| Fig. 3.7 Output Voltage Waveform Boost PFC topology (BPFC)                                                                                            | 23     |

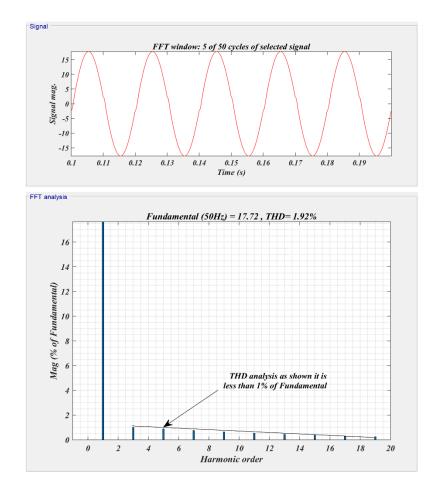

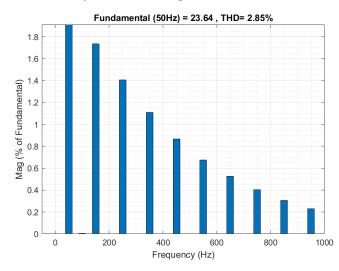

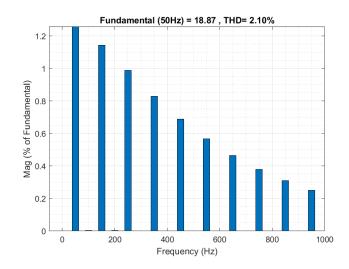

| Fig. 3.8 THD analysis of Boost PFC Converter                                                                                                          | 23     |

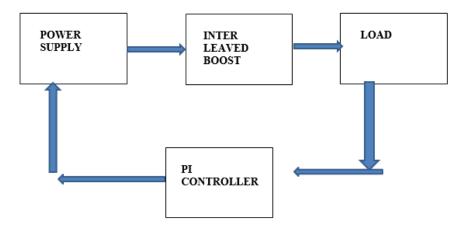

| Fig. 4.1 Block diagram Interleaved Boost                                                                                                              | 27     |

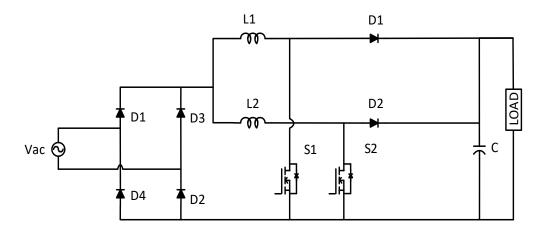

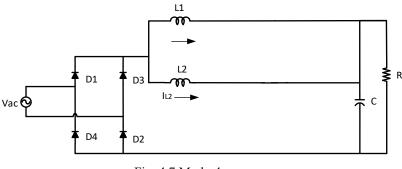

| Fig. 4.2 Schematic of Interleaved Boost PFC Converter                                                                                                 | 28     |

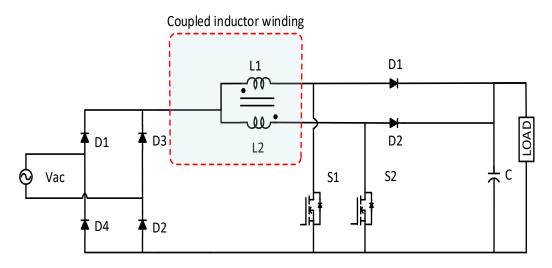

| Fig. 4.3 Interleaved Boost PFC Converter with coupled inductor                                                                                        | 29     |

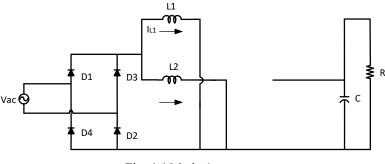

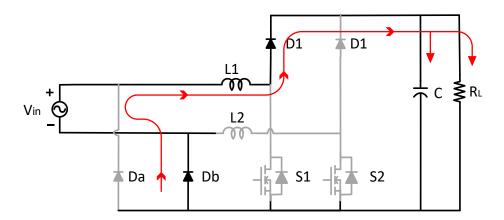

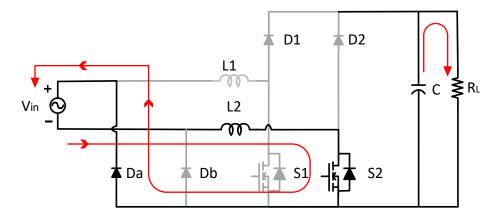

| Fig. 4.4 Mode-1                                                                                                                                       | 30     |

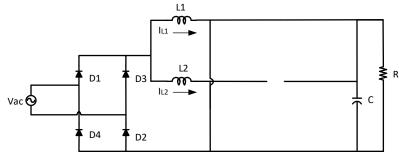

| Fig. 4.5 Mode-2                                                                                                                                       | 31     |

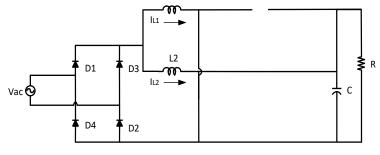

| Fig. 4.6 Mode-3                                                                                                                                       | 31     |

| Fig. 4.7 Mode-4                                                                                                                                       | 31     |

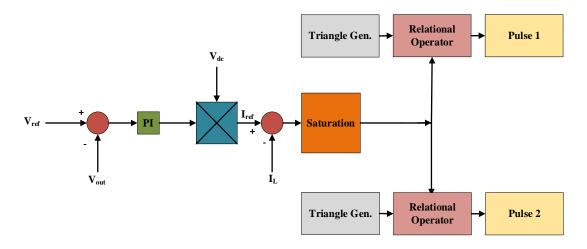

| Fig. 4.8 Interleaved Boost PFC Controller                                                                                                             | 32     |

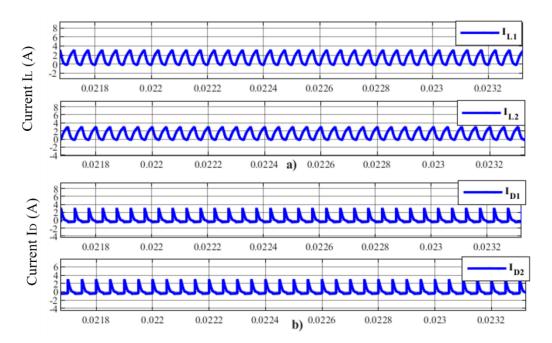

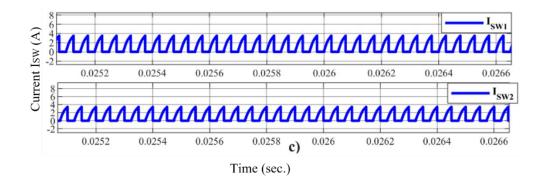

| Fig. 4.9 Current Waveform Interleaved Boost PFC(IBPFC) topology a). In                                                                                | ductor |

| current(I <sub>L1</sub> &I <sub>L2</sub> ) b).Switch Current(I <sub>SW1</sub> &I <sub>SW2</sub> ) c).Diode Current(I <sub>D1</sub> &I <sub>D2</sub> ) | 36     |

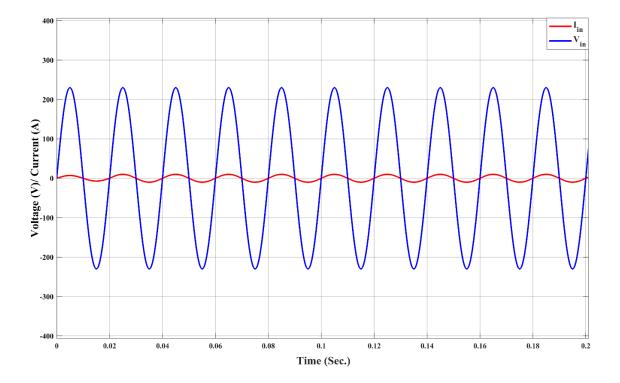

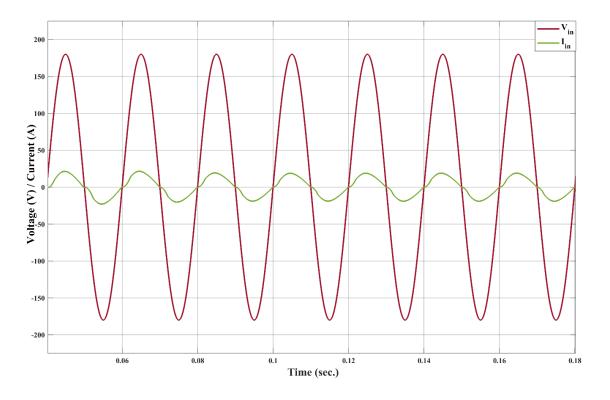

| Fig. 4.10 Input Current and Voltage Waveform for Interleaved Boost PFC topology                                                                       | 36     |

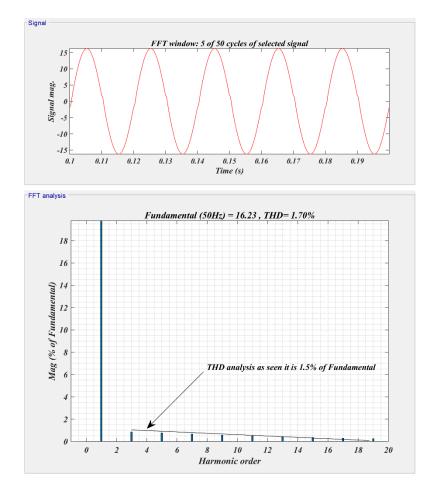

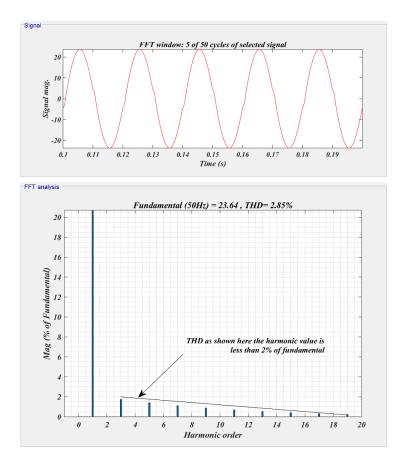

| Fig. 4.11 THD analysis of Interleaved Boost PFC Converter                                                                                             | 37     |

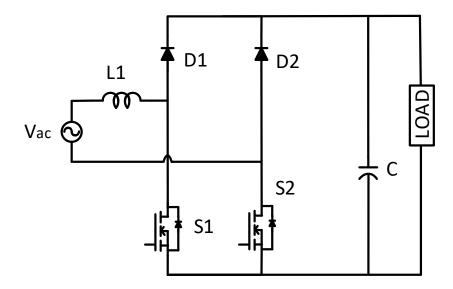

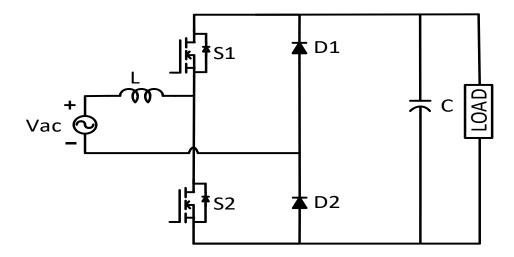

| Fig. 5.1 Schematic of Semi-Bridgeless Boost PFC Converter                                                                                             | 42     |

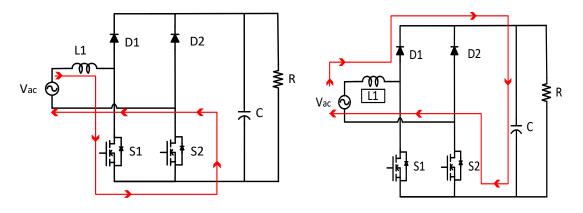

| Fig. 5.2 Operating Mode-1                                                                                                                             | 43     |

| Fig. 5.3 Operating Mode-2                                                                                                                             | 44     |

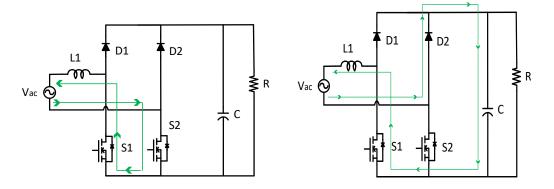

| Fig. 5.4 Operating Mode-3                                                                                                                             | 44     |

| Fig. 5.5 Operating Mode-4                                                                                                                             | 45     |

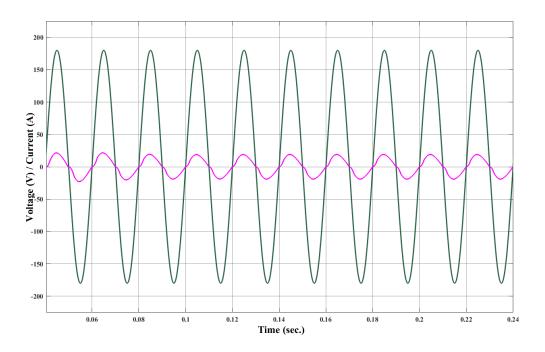

| Fig. 5.6 Input Current and Voltage Waveform for Semi-Bridgeless Boost PFC topolo                                                                      | gy .49 |

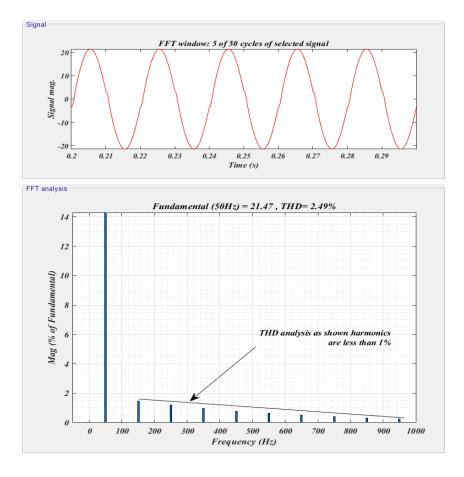

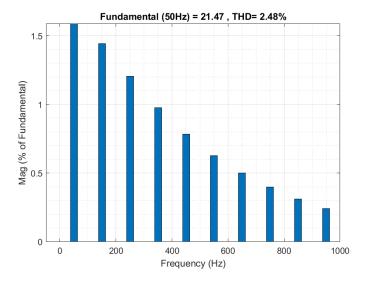

| Fig. 5.7 THD analysis of Semi-Bridgeless Boost PFC Converter                                                                                          | 50     |

| Fig. 5.8 Zoom out view of harmonic distortion                                                                                                         | 50     |

| Fig. 6.1 Schematic of Bridgeless Boost PFC Converter                                                                                                  | 54     |

| Fig. 6.2 Operating Mode 1-2 for positive cycle                                | .55 |

|-------------------------------------------------------------------------------|-----|

| Fig. 6.3 Operating Mode 3-4 for negative cycle                                | .55 |

| Fig. 6.4 Input Current and Voltage Waveform for Bridgeless Boost PFC topology | .57 |

| Fig. 6.5 THD analysis of Bridgeless Boost PFC Converter                       | .58 |

| Fig. 6.6 Zoom out view of harmonic distortion                                 | .58 |

| Fig. 7.1 Schematic of Totem-Pole Boost PFC Converter                          | .62 |

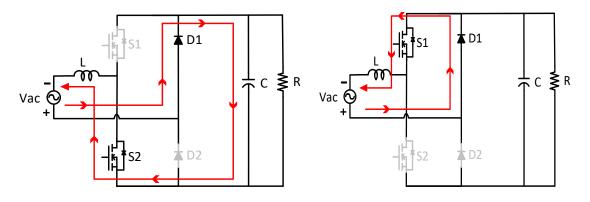

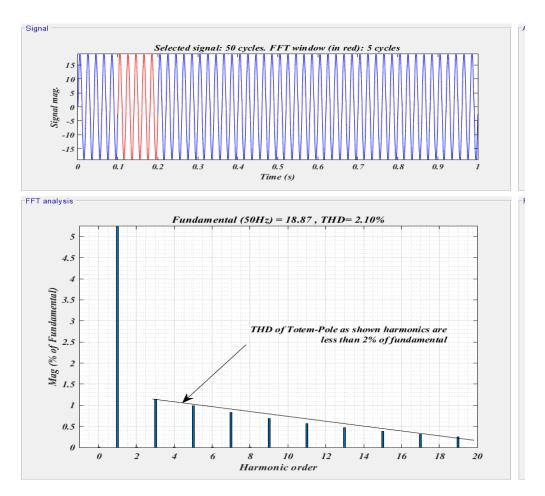

| Fig. 7.2 Operating Mode 1-2 for positive cycle                                | .63 |

| Fig. 7.3 operating Mode 3-4 for negative half cycle                           | .63 |

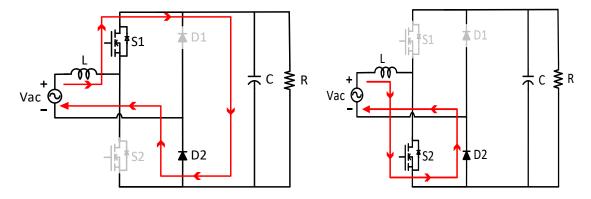

| Fig. 7.4 Input Current and Voltage Waveform for Totem-Pole Boost PFC topology | .66 |

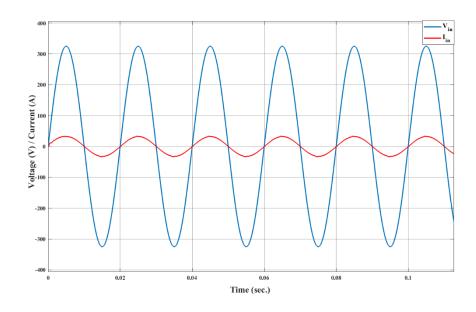

| Fig. 7.5 THD of Totem-Pole Boost PFC Converter                                | .66 |

| Fig. 7.6 Zoom out view of harmonic distortion                                 | .67 |

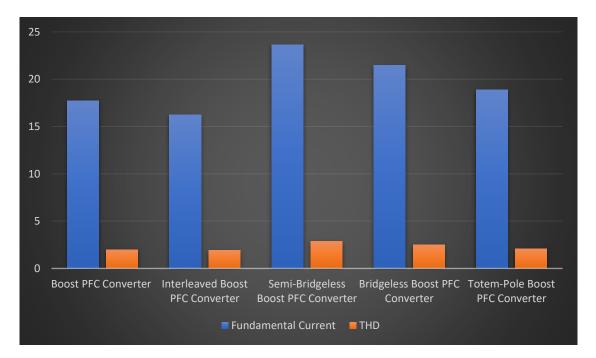

| Fig. 8.1 Comparison of Different Converter w.r.t Fundamental current and THD  | .70 |

# LIST OF TABLES

| Table 3.1 Boost PFC Converter Specifications         |    |  |

|------------------------------------------------------|----|--|

| Table 4.1 Interleaved Boost Converter Specifications |    |  |

| Table 5.1 comparison of control Techniques           | 46 |  |

| Table 8.1 Comparison of Different Topology           | 71 |  |

# **Table of Contents**

**Candidate's Declaration**

Certificate

Abstract

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fig. 1.1 Importance of Power Factor2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Fig. 1.2 Schematic of PFC for Battery charging2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 3.1 Schematic of Boost PFC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Fig. 3.2 Mode-114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Fig. 3.3 Mode-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 3.4 Controller for Boost PFC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Fig. 3.5 Current Waveform Boost PFC(BPFC) topology a). Inductor current(IL) b).Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Current c).Diode Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Fig. 3.6 Input Current and Voltage Waveform for Boost PFC(BPFC) topology22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Fig. 3.7 Output Voltage Waveform Boost PFC topology (BPFC)23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Fig. 3.8 THD analysis of Boost PFC Converter23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fig. 4.1 Block diagram Interleaved Boost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

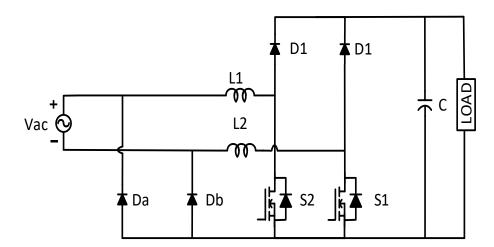

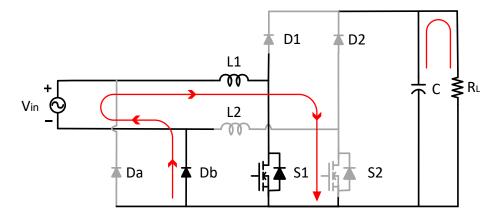

| Fig. 4.2 Schematic of Interleaved Boost PFC Converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Fig. 4.3 Interleaved Boost PFC Converter with coupled inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fig. 4.4 Mode-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 4.5 Mode-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 4.6 Mode-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 4.7 Mode-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 4.8 Interleaved Boost PFC Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Fig. 4.9 Current Waveform Interleaved Boost PFC(IBPFC) topology a). Inductor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $current(I_{L1}\&I_{L2}) b). Switch Current(I_{SW1}\&I_{SW2}) c). Diode Current(I_{D1}\&I_{D2})36 b) \\ = 0.125 (I_{D1}\&I_{D2}) (I_{D1}&I_{D2}) (I_{D2}&I_{D2}) (I_{D1}&I_{D2}) (I_{D1}&I_{D2}) (I_{D2}&I_$ |

| Fig. 4.10 Input Current and Voltage Waveform for Interleaved Boost PFC topology36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Fig. 4.11 THD analysis of Interleaved Boost PFC Converter                              |

|----------------------------------------------------------------------------------------|

| Fig. 5.1 Schematic of Semi-Bridgeless Boost PFC Converter42                            |

| Fig. 5.2 Operating Mode-143                                                            |

| Fig. 5.3 Operating Mode-244                                                            |

| Fig. 5.4 Operating Mode-344                                                            |

| Fig. 5.5 Operating Mode-445                                                            |

| Fig. 5.6 Input Current and Voltage Waveform for Semi-Bridgeless Boost PFC topology .49 |

| Fig. 5.7 THD analysis of Semi-Bridgeless Boost PFC Converter                           |

| Fig. 5.8 Zoom out view of harmonic distortion                                          |

| Fig. 6.1 Schematic of Bridgeless Boost PFC Converter                                   |

| Fig. 6.2 Operating Mode 1-2 for positive cycle                                         |

| Fig. 6.3 Operating Mode 3-4 for negative cycle                                         |

| Fig. 6.4 Input Current and Voltage Waveform for Bridgeless Boost PFC topology          |

| Fig. 6.5 THD analysis of Bridgeless Boost PFC Converter                                |

| Fig. 6.6 Zoom out view of harmonic distortion                                          |

| Fig. 7.1 Schematic of Totem-Pole Boost PFC Converter                                   |

| Fig. 7.2 Operating Mode 1-2 for positive cycle                                         |

| Fig. 7.3 operating Mode 3-4 for negative half cycle                                    |

| Fig. 7.4 Input Current and Voltage Waveform for Totem-Pole Boost PFC topology66        |

| Fig. 7.5 THD of Totem-Pole Boost PFC Converter                                         |

| Fig. 7.6 Zoom out view of harmonic distortion                                          |

| Fig. 8.1 Comparison of Different Converter w.r.t Fundamental current and THD70         |

#### **CHAPTER 1**

#### **1 INTRODUCTION**

For pure sinusoidal waveforms, Power factor is defined as the ratio of the apparent power in the circuit supplied by to the active power flowing to the load  $Powerfactor = \frac{realpower}{reactivepower}$ (1.1)

which is a dimensionless number between 0 and 1

*pfc* is a technique used to eliminate input current harmonics and line current ( $I_L$ ) sinusoidal and in phase with the line voltage in order to meet the standard. Additionally, PFC is a method of reducing the negative impacts of electrical loads that produce power factors below unity ( $pf \le 1$ ). The perceived/apparent power given to the load is more than the actual power that the load absorbs when its power factor (PF) value is below unity.

In theory, pf should be  $\cos \varphi$ , but in fact, nonlinear loads cause the source current to be no sinusoidal, therefore theoretically pf is:

$$PF = K_D \cos \varphi \tag{1.2}$$

where  $\cos \varphi$  is the line voltage ( $V_{L}$ ) and current's displacement factor. and  $K_D = \frac{I_{1:rms}}{I_{rms}}$  is called as the distortion factor which provides information on the harmonic limit of the fundamental current.

moreover, the mathematical relationship between the distortion factor and THD;

$$K_D = \frac{1}{\sqrt{1 + THD^2}} \tag{1.3}$$

Where, THD is the Total harmonics distortion and we can calculate THD with the help of below condition,

$$THD = \frac{\sqrt{\sum_{j=2}^{\infty} I_{nrms}^2}}{I_{1rms}}$$

(1.4)

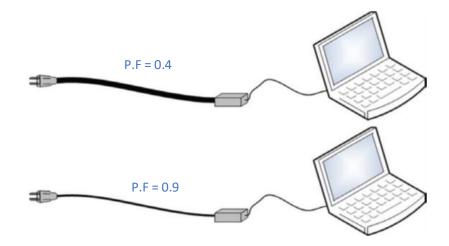

With the exception of the DBR, passive PFC uses entirely passive components to enhance the line current's form[1]-[2]. It should be clear that the output voltage cannot be controllable. Despite being straightforward, passive PFC converters have drawbacks that prevent them from being used in industrial settings fig. 1.1 shows the importance of power factor in today's world. These drawbacks include poor dynamic response, a lack of voltage regulation, input current shapes that rely on the load, and reduced power factor.

In active PFC, active switches are used with reactive components to improve line current shaping efficiency and produce adjustable output voltage.

Fig. 1.1 Importance of Power Factor

The APFC solutions are further divided into two types based on switching frequency: *In low-frequency* switching occurs at low-order harmonics of the line frequency in an active PFC and is synchronized to the line voltage.[1]

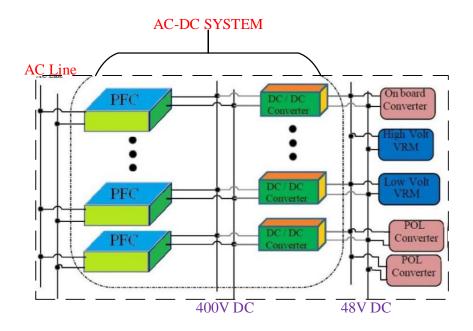

Fig. 1.2 Schematic of PFC for Battery charging

Power factor adjustment is a crucial component of effective energy management that can have a positive impact on businesses, homes, and the environment fig. 1.2 shows the schematic of PFC for battery charging. The following are some of the most significant justifications for the significance of power factor correction:

Enhancing electrical system's energy efficiency is one of the key benefits of power factor adjustment. Low power factor indicates that a system is consuming more energy than is required to complete a task, which increases energy costs and decreases efficiency. Power factor correction entails the installation of capacitors or other devices. Power factor adjustment can dramatically lower energy expenditures and encourage the usage of sustainable energy by minimising wasted energy[2]. Greater Equipment Lifespan: When running at a low power factor, electrical equipment, including motors, transformers, and other devices, might experience decreased efficiency and greater wear and tear. By lessening the stress brought on by reactive loads, power factor adjustment can help to increase the equipment's lifespan. As a result, electrical systems may operate more reliably and with lower maintenance costs.

Reduced Power Interruptions: Voltage fluctuations can occur in electrical systems with a low power factor, which can cause power outages, equipment damage, and other issues. Power factor correction works to increase the power factor, which helps to stabilise voltage levels and lessen the likelihood of power outages. Regulation Compliance: In many nations, companies are required to keep a specific power factor in order to follow rules and stay out of trouble. Businesses can comply with these standards and avoid expensive fines by using power factor correction. Benefits for the Environment: By lowering energy waste and increasing efficiency, power factor correction can assist lower greenhouse gas emissions and encourage the use of sustainable energy. This can help with efforts to prevent climate change and lessen the negative effects of human activity on the environment.

In general, power factor adjustment is a crucial component of effective energy management that can have a positive impact on the economy, the environment, and homes and companies. Power factor correction can decrease costs, boost output, and protect the environment by enhancing energy efficiency, increasing the lifespan of electrical equipment, minimising power outages, adhering to laws, and supporting sustainable energy use

#### **1.1 Motivation**

Almost all electronic devices have different power ratings, and the incredible need for power sources for such devices presents a challenging problem to the power engineer. Regulated DC bus bar voltage is a concept introduced by the AC-DC APFC converters system. With regard to power distribution and management, this satisfies the need for greater currents as well as the dynamic properties of AC-DC systems. It is too humble when taking into account high efficiency, high power density, fast dynamic reaction, etc. for specialised applications, such as power supplies for telecom and computer servers. However, it is conceivable to transfer electrical power from the power grid to the consumer end at a cheap cost and with high efficiency, given that Power Electronic Converters are created with cutting-edge, appropriate control methods.

Due to the intensive switching operations, the magnetic components used in converters are getting smaller. This translates into advantages in power electronics' price, size, and performance, and as a result, these devices are more common in modern commercial, industrial, military, residential, and aerospace settings. Galvanic isolation installation by DPS is crucial for protection and the attainment of flexible system configuration. All the aforementioned perfections can be accomplished by adding active PFC converters into DPS. The most practical three-phase PFC converter is the traditional hard-switched PWM threephase boost rectifier; however, all of the known soft-switching approaches are cumbersome and ineffective. Significant turn-on losses are brought on by the diode reverse recovery issue, and significant turn-off losses are brought on by the slow devices' current tail issues, such as the IGBT, which is recommended for three-phase high power applications. These motivations constitute the basis of this dissertation's goal, which is to create a number of high-performance PFC approaches to outperform the current ones in the aforementioned areas. The active PFC converters for DPS can perform better thanks to ongoing research to provide improved efficiency, quick dynamic response, and high-power inflation with strict regulatory regulations. In this thesis study, some control approaches and a straightforward elongation PWM technique are examined. And the research work is used in AC-DC PFC.

# **CHAPTER 2**

#### **2** LITERATURE REVIEW

#### 2.1 Introduction

Switch-Mode Power Converters (SMPC) modelling and analysis utilising averaged statespace equations. State space averaged equations have been introduced, which is thought to be a significant step forward for SMPCs. The strategy let the designers to explain the behaviour of the switching power converter using a single linear circuit model. Regardless of the original converter topology, the circuit model's topology is the same. To allow different converter topologies, just the model element values are altered. [3]

In 1986 saw the publication of a NASA-sponsored academic research report on the use of SMPC to adjust for low-quality input current waveforms of capacitive input filters off-line power supply and is listed as reference [4].

current shaping and power factor correction (PFC) for off-line power converters are covered by a number of U.S. patents. The input current is detected, integrated, and contrasted with an erroneous voltage produced from the Boost Converter's output. Through a separate driver stage, the comparator's output is gated to the Boost Switch. The rectified sinusoidal AC voltage envelope automatically follows the chopped input current envelope. The patent stated that the increased PF can surpass 95% thanks to additional duty cycle management Boost Switch. For chopped input waveform's switching frequency components to be removed, a line filter is required.

Following a brief discussion of the benefits and drawbacks of each control circuit, the "Regulation Band" control circuit was suggested as the inner current controller.

The advantage of employing these converters is that current shaping can be accomplished without loop. The advantage of employing these converters is that current shaping can be accomplished without an explicit current control loop. Voltage regulation still depends on the DC voltage control loop. Since each switching cycle requires the inductor current to vary from zero to its greatest peak, the discontinuous conduction mode is not preferred for high power applications. For these types of converters, the current distortion is extremely significant. This behaviour is the same as the CCM boost converter's delay angle effect with average current controller.

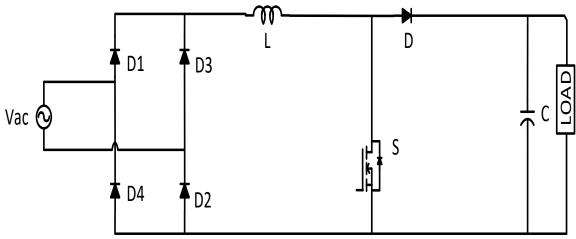

#### 2.2 Boost PFC Converter

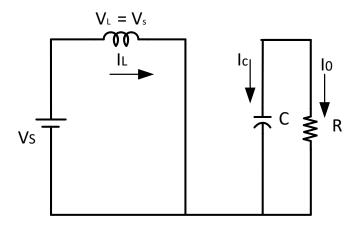

The boost PFC converter topology uses a dedicated diode bridge to rectify the AC input voltage to DC, which is then followed by the boost section. Because of its step-up conversion ratio, the input voltage's amplitude VAC is never greater than the output voltage  $V_o$ . MATLAB/Simulink was used to implement the Boost PFC Converter topology and its controller on hardware. The controller, a component of the software implementation, seeks to make the converter input current follow the sinusoidal waveform of the input voltage, regardless of the output power. It will not be discussed here because it is not the focus of this study, although details may be found in [5].

With some ripple at the output terminal voltage, the boost converter keeps the output voltage constant However, as the power level rises, the diode-bridge losses increase, decreasing the converter's efficiency. At high power levels, it also has a heat dissipation issue. The power range is constrained for higher power levels by the increase in inductor size. Thermal management, power losses, and Conduction losses, issues are the drawbacks of this design. Every switching cycle, the current flows through three semiconductor devices—two diodes in series with diode D or switch S1—resulting in conduction losses. Because of the greater voltage drops across the employed diodes when it is used at low loads and the resulting need for thermal management of the diode bridge when it is operated at higher loads, it is less efficient.

Compared to other topologies, this converter topology has a bigger input current ripple, but it is simpler to operate. The inductor is operating in continuous conduction mode, and the average current control mechanism is being used Which is followed by a current controller which control the inductor current and also maintain the sinusoidal waveshape and finally the output is given to the PWM block and which is connected to the Gate Terminal of the MOSFET. This is the complete control block diagram of a PFC Boost Converter, Here First we need to detect the value of AC input Voltage.

#### 2.3 Interleaved Boost PFC Converter

Paralleled semiconductors are advantageous for the boost interleaved converter. Additionally, it lowers the output capacitor's high frequency ripple, although the input diode bridge rectifiers' heat management remains a challenge. [6]

The reduction in inductor magnetic volume is made possible by the cancellation of inductor ripple current. The cancellation of inductor ripple current allows for a reduction in the magnetic volume of the inductor. However, a decrease in magnetic volume does not directly

result from a decrease in energy storage [5]-[6]. The boost interleaved PFC converter topology is presented in Fig 2. The AC input voltage is rectified to DC using a specialised diode bridge, which is followed by two parallel Boost PFC Converters that operate 180° out of phase.

The two input inductor currents add up to form the input current. The inductors' ripple currents tend to cancel each other out since they are out of phase, which lowers the input ripple current brought on by the boost switching action. The phase shift for each branch equals 360°/N, if there are N parallel branches. Paralleled semiconductors are advantageous in the boost interleaved PFC converter. The output capacitor high frequency ripple is decreased because the input current is the total of two inductor currents, however the input diode bridge rectifiers' heat management remains an issue.

A reference voltage is used to compare the measured DC bus. For zero error DC bus voltage regulation, the resulting voltage error is then sent into a Proportion Integral voltage controller. The inner controller receives the controller's output, which is the amplitude of the reference supply current. Additionally, in order to mimic the behaviour of a pure resistor. For this, an analogy multiplier is employed. The  $I_{ref}$  is then deducted from the detected inductance current, and the current is subsequently limited.

Finally, this converter has a low high-frequency ripple output capacitor. The very high localised loss and subsequent heat management issue for the input diode bridge rectifiers, as with the single PFC boost, are this topology's biggest drawbacks.

#### 2.4 Semi-Bridgeless Boost PFC Converter