2023

# AXI BASED IP BLOCK VERIFICATION USING UVM A DISSERTATION REPORT

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTSFOR THE AWARD OF THE DEGREE

OF

### **MASTER OF TECHNOLOGY**

IN

### **VLSI DESIGN & EMBEDDED SYSTEM**

SUBMITTED BY:

**SUMER SAINI**

2K21/VLS/19

UNDER THE SUPERVISION OF

Dr. ALOK KUMAR SINGH PROFESSOR

**ELECTRONICS & COMMUNICATION ENGINEERING** DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

### MAY 2023

### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering)Bawana Road, Delhi-110042

# CANDIDATE'S DECLARATION

I, Sumer Saini, Roll No. 2K21/VLS/19 student of M. Tech (VLSI & Embedded systems), hereby declare that the project Dissertation titled **"AXI Based IP Block Verification using UVM"** which is submitted by me to the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology is unique and has not been copied without proper citation. This work has never before been used to give a degree, diploma associateship, fellowship, or other equivalent title or recognition.

Place: Delhi Date: 1-05-2023 Sumer Saini (2K21/VLS/19)

# ELECTRONICS & COMMUNICATION ENGINEERING

### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

### **CERTIFICATE**

I hereby certify that the Project Dissertation titled "**AXI Based IP Block Verification using UVM**" which is submitted by **Sumer Saini**, **2K21/VLS/19**, to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the prerequisite for the award of the degree of Master of Technology, is a documentation of the student's projectwork completed under my supervision. To the best of my knowledge, this work hasnever been submitted in part or in full for any degree or diploma at this university or anywhere else.

Place: Delhi Date: 1-05-2023 SUPERVISOR Dr A. K. Singh, Professor (ECE)

#### ABSTRACT

In modern VLSI, a DUT may have multiple interfaces. Each of these interfaces may have different UVM objects associated with them. In an SoC there are no. of IP blocks which are connected to each other with the help of interfaces. One such interface which is most commonly used is AXI interface. This project involves the verification of an AXI interface module that acts as an initiator or target depending on the upstream or downstream transaction. The module converts commands from the FIFO BFM or AXI BFM to AXI transactions or FIFO transactions. The testbench development is based on System Verilog using UVM methodology to create a constrained random test environment for faster verification. The testbench includes bus functional models of AXI and FIFO interfaces, which act as initiators/targets on the DUT's interfaces.

The AXI interface is a widely used interface in digital designs and is popularly used for interconnecting different IPs within a SoC or FPGA. The AXI interface is complex, and verification of designs with AXI interfaces is challenging. The primary goal of this project is to verify the AXI interface module, which acts as an initiator or target depending on the upstream or downstream transaction. The AXI interface module converts the commands from the FIFO BFM or AXI BFM to AXI transactions or FIFO transactions. The verification is done using the UVM methodology, which creates a constrained random test environment, which helps in faster verification. The testbench includes bus functional models of AXI and FIFO interfaces, which act as initiators/targets on the DUT's interfaces.

The AXI interface is a high-performance, high-frequency, and low-latency interface used in digital designs. The AXI interface provides the features of burst transfers, read and write data transfers, and different transfer sizes, including 8-bit, 16-bit, 32-bit, and 64-bit transfers. The AXI interface

also provides various features like data caching, out-of-order execution, and multiple outstanding transactions.

The AXI interface module that is being verified in this project acts as an initiator or target depending on the upstream or downstream transaction. The module converts the commands from the FIFO BFM or AXI BFM to AXI transactions or FIFO transactions. The module is complex, and verifying its functionality requires a robust testbench.

The UVM methodology is widely used for the verification of digital designs. The UVM methodology provides a standardized way of developing testbenches and allows for the creation of a constrained random test environment. The UVM methodology is based on the Object Oriented Programming(OOPs) concept, and it includes classes, objects, and virtual sequences. The testbench is an integral part of the verification process. The testbench includes the bus functional models of AXI and FIFO interfaces, which act as initiators/targets on the DUT's interfaces. The testbench verifies the functionality of the AXI interface module by generating random transactions and comparing the results with the expected output. The testbench also includes assertions and coverage to check the correctness and completeness of the verification process.

In this project verification of AXI interface using IP system interface has done. In this entire designtwo units are there i.e initiator and target for upstream and downstream transactions.

### ACKNOWLEDGEMENT

A successful project can never be prepared by the efforts of the person to whom the project is assigned, but it also demands the help and guardianship of people who helped in completion of the project. We would like to thank all those people who have helped us in this research and inspired us during our study.

With profound sense of gratitude, we thank Dr A. K. Singh, Professor (ECE), our Research Supervisors, for his encouragement, support, patience and guidance in this project work. We heartily appreciate the guidance given by him in the project presentation that has improved our presentation skills with his comments and advices. We take immense delight in extending Our acknowledgement to our families and friends who have helped us throughout this projectwork.

Sumer Saini 2K21/VLS/19

# CONTENTS

| Cand   | lidate's Declaration                        | ii   |  |

|--------|---------------------------------------------|------|--|

| Certi  | ficate                                      | iii  |  |

| Absti  | act                                         | iv   |  |

| Ackn   | owledgement                                 | vi   |  |

| Conte  | ents                                        | vii  |  |

| List o | f Tables                                    | viii |  |

| List o | of Figures                                  | х    |  |

| List o | of Abbreviations                            | xi   |  |

| CHA    | PTER 1: INTRODUCTION                        | 12   |  |

| 1.1    | UVM CLASSES                                 | 13   |  |

| 1.2    | UVM OBJECT                                  | 13   |  |

| 1.3    | UVM TRANSACTION                             | 13   |  |

| 1.4    | AXI INTERFACE(DUT)                          | 14   |  |

| CHA    | PTER 2: AXI INTERFACE TESTBENCH ENVIRONMENT | 20   |  |

| 2.1    | TEST CLASS                                  | 20   |  |

| 2.2    | FIFO ENVIRONMENT                            | 21   |  |

| 2.3    | FIFO SEQUENCE ITEM                          | 22   |  |

| 2.3.1  | FIFO BFM DRIVER                             | 22   |  |

| 2.3.2  | FIFO SEQUENCE                               | 23   |  |

| 2.4    | FIFO SEQUENCER                              | 24   |  |

| 2.5    | FIFO BFM MONITOR                            | 25   |  |

| 2.6    | TESTBENCH SCOREBOARD                        | 25   |  |

| CHA    | CHAPTER 3: ENHANCEMENTS                     |      |  |

| CHA    | PTER 4: SIMULATION AND CONCLUSION           | 54   |  |

| Refer  | rences                                      | 60   |  |

# LIST OF TABLES

Table 1.1 UVM MACROS

13

# LIST OF FIGURES

| Fig 1.1 | AXI interface                             | 16 |

|---------|-------------------------------------------|----|

| Fig 1.2 | UVM class hierarchy                       | 19 |

| Fig 2.1 | UVM testbench hierarchy                   | 21 |

| Fig 2.2 | UVM driver                                | 22 |

| Fig 2.3 | UVM sequence                              | 23 |

| Fig 2.4 | UVM sequence methods                      | 23 |

| Fig 2.5 | Sequencer                                 | 24 |

| Fig 2.6 | Scoreboard monitor communication          | 26 |

| Fig 2.7 | UVM testbench                             | 26 |

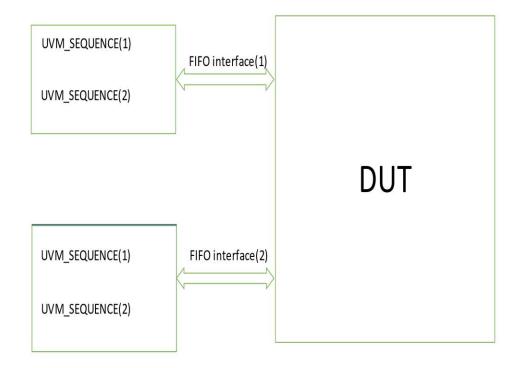

| Fig 3.1 | Approach to allow concurrent transactions | 30 |

| Fig 3.2 | Coverage convergence                      | 32 |

| Fig 3.3 | Functionality to be covered from design   | 37 |

| Fig 3.4 | A snippet of coding of covergroups        | 39 |

| Fig 3.5 | Running of a single test in UVM Environment | 40 |

|---------|---------------------------------------------|----|

| Fig 3.6 | Result of single test                       | 40 |

| Fig 3.7 | Result of sanity checks                     | 41 |

| Fig 3.8 | Regression runs result                      | 42 |

| Fig 3.9 | Multiple sequences started parallely        | 46 |

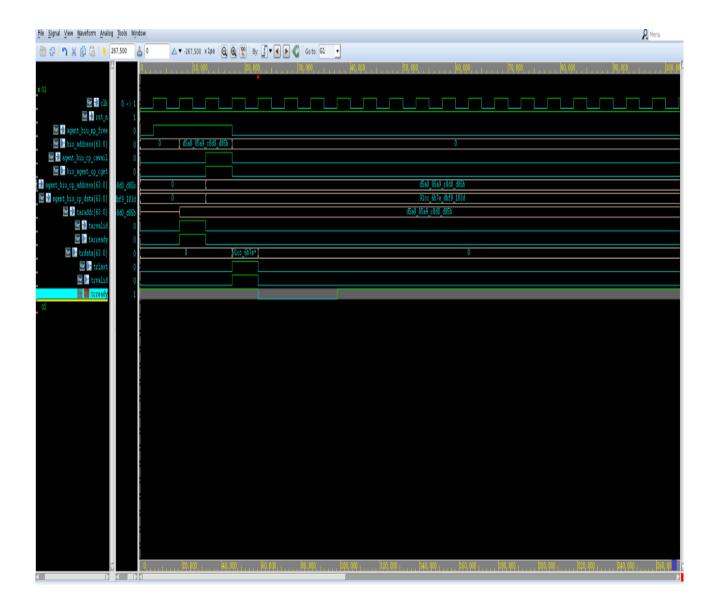

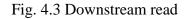

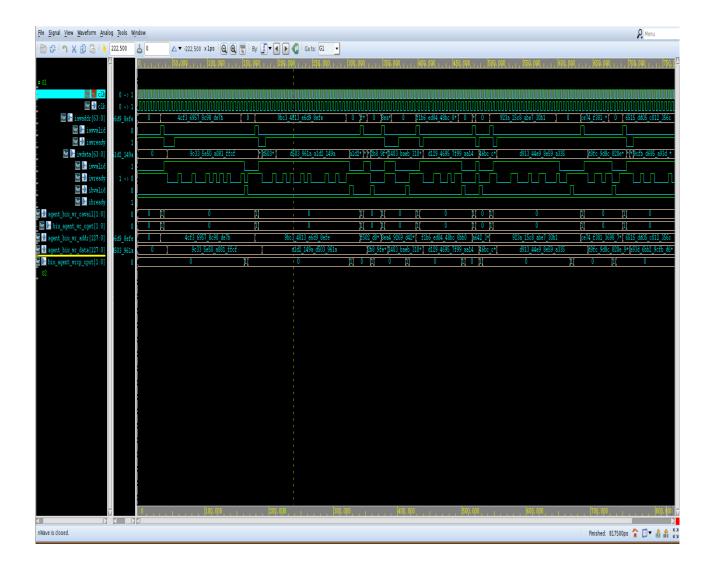

| Fig 4.1 | Upstream write                              | 53 |

| Fig 4.2 | Downstream write                            | 54 |

| Fig 4.3 | Downstream Read                             | 55 |

| Fig 4.4 | Single interface multiple write             | 56 |

| Fig 4.5 | Downstream pipelining write                 | 57 |

# LIST OF ABBREVIATIONS

# S.No Abbreviation Full Name

| 1.  | UVM  | Universal Verification Methodology        |  |

|-----|------|-------------------------------------------|--|

| 2.  | OVM  | Open Verification Methodology             |  |

| 3.  | AXI  | Advanced Extensible Interface             |  |

| 4.  | FIFO | First In First Out                        |  |

| 5.  | BFM  | Bus Functional Model                      |  |

| 6.  | DUT  | Design Under Test                         |  |

| 7.  | TLM  | Transaction level Modelling               |  |

| 8.  | DUV  | Design Under Verification                 |  |

| 9.  | DSP  | Digital Signal Processing                 |  |

| 10. | SOC  | System On Chip                            |  |

| 11. | AMBA | Advanced Microcontroller Bus Architecture |  |

| 12. | APB  | Advanced Peripheral Bus                   |  |

| 13. | AHB  | Advanced High performance Bus             |  |

| 14. | IP   | Intellectual Property                     |  |

| 15. | VLSI | Very Large-Scale Integration              |  |

| 16. | FPGA | Field Programmable Gate Arrays            |  |

# **CHAPTER 1**

# **INTRODUCTION**

The UVM is a standardized methodology for verifying integrated circuit designs. It is derived mainly from the OVM. The UVM class library brings much automation to the SystemVerilog language, such as sequences and data automation features. Unlike the previous methodologies developed independently by the simulator vendors, UVM is an Accellera standard with support from multiple vendors. The UVM class library consists of the following components:

- Components: The UVM component library provides a set of base classes for building verification components, such as drivers, monitors, and scoreboards.

- Sequences: The UVM sequence library provides a set of classes for generating stimulus and checking for responses.

- Transaction-level modeling (TLM): The UVM TLM library provides a set of classes for modeling the interface between the DUV and the verification environment.

- Reporting: The UVM reporting library provides a set of classes for generating reports about the verification environment.

- Utilities: The UVM utilities library provides a set of classes for common tasks, such as creating and managing objects. The UVM class library can be used to create a well-structured and reusable verification environment. The UVM class library is a powerful tool for verifying integrated circuit designs.

- Increased productivity: UVM can help to increase productivity by providing a set of reusable components and a standardized methodology.

- Improved quality: UVM can help to improve quality by providing a more structured and organized verification environment.

In the coming years, there will be an enormous growth in the demand for data and network capacity. The development of fifth-generation communication technology (5G) can offer peak data speeds of up to 20Gbps with extremely low latency of 1ms. Future applications for high-performance computing include wireless communication, multimedia processing, atmospheric simulation, and high-performance graphics. DSP will be crucial in this since it offers powerful

computational capability on a big scale. Direct access to storage no longer meets the demands for data access speed due to the growing demand for storage space and access bandwidth in 5G applications [1].

Mandating a universal convention in verification techniques encouraged the development of generic verification components that were portable from one project to another. This promoted cooperation and sharing of techniques among the user base. It also encouraged the development of verification components that were generic enough to be easily extended and improved without modifying the original code.

Here are some of the benefits of using generic verification components:

- Portability: Generic verification components can be used in different projects without having to be modified. This saves time and effort, and it also helps to ensure that the verification environment is consistent across projects.

- Reusability: Generic verification components can be reused in different projects, which can further save time and effort.

- Extensibility: Generic verification components can be easily extended to accommodate new features or changes to the design. This makes it easier to keep the verification environment up-to-date with the design.

- Maintainability: Generic verification components are easier to maintain than customdeveloped components. This is because they are well-documented and well-tested, and they have a large user base that can provide support.

Directed Testbench design was a conventional way to verify design but today's design is highly complex and it is impossible to handle verification with directed testbench. As the complexity of the design increases, bugs in the design also rise. Now it has become a necessity to replace the conventional test with an advanced and automated verification environment in order to reduce time and reliability.

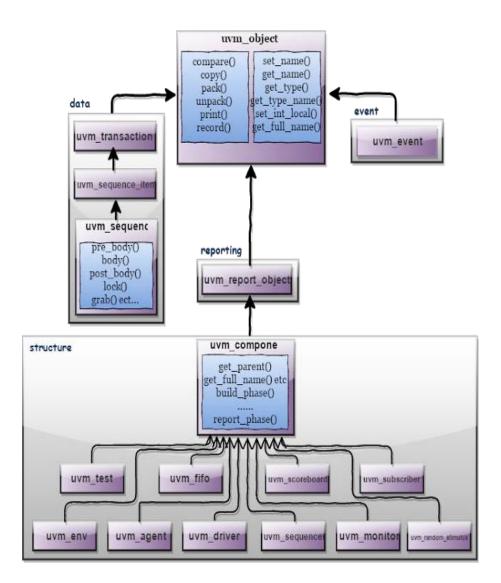

### 1.1 UVM Classes

UVM have three main classes,

- uvm\_object class

- uvm\_transaction class

• uvm\_component class

A factory is a commonly-used concept in object-oriented programming. It is an object that is used for instantiating other objects. The UVM factory is a mechanism that allows users to create UVM objects and components. There are two ways to register an object with the UVM factory:

- In the declaration of class A, one can invoke the uvm\_object\_utils(A) or uvm\_component\_utils(A) registration macros.

- Otherwise, the uvm\_object\_registry(A,B) or uvm\_component\_registry(A,B) macros can be used to map a string B to a class type A.

| name            | function                  | related to      | parameters          | Purpose                                                                                        | Type of Macro                                               |

|-----------------|---------------------------|-----------------|---------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| `uvm_creat<br>e | object<br>constructo<br>r | `uvm_send       | Sequence or<br>Item | to create the object and<br>allow user to set values<br>via overloading or<br>parameterpassing | -                                                           |

| `uvm_send       | processor                 | `uvm_creat<br>e | Sequence or<br>Item | processes what is created<br>by `uvm_create without<br>randomization                           | Sequence Action<br>Macros for Pre-<br>Existing<br>Sequences |

| `uvm_do         | processor                 | `uvm_creat<br>e | Sequence or<br>Item | executes class or item<br>with randomization                                                   | Sequence action macro                                       |

### UVM allows the use of Macros

### **1.2** UVM\_OBJECT

Core class based operational methods (create, copy, clone, compare, print, record, etc..), instance identification fields (name, type name, unique id, etc.) and random seeding were defined in it. All uvm\_transaction and uvm\_component were derived from the uvm\_object. In the context of hardware verification, UVM (Universal Verification Methodology) is a popular standardized verification methodology that is used to verify complex digital designs. UVM is built on top of SystemVerilog and provides a set of classes and methodologies for building reusable, scalable, and efficient testbenches. One of the key concepts in UVM is the UVM object. A UVM object is an instance of a class derived from the uvm\_object base class. UVM objects are used to represent various elements in a digital design, such as registers, memories, and other functional blocks.

UVM objects are typically created dynamically during the simulation and are managed by the UVM factory. The UVM factory is responsible for creating and deleting UVM objects, as well as maintaining a hierarchy of UVM objects. UVM objects are designed to be reusable and configurable. They can be extended to include additional functionality or modified to meet specific verification requirements. UVM objects can also be used to communicate between different parts of a testbench or to pass data between different phases of the UVM methodology. Overall, UVM objects provide a powerful and flexible mechanism for building modular and reusable testbenches that can be used to verify complex digital designs.

### **1.3** UVM\_TRANSACTION

• Used in stimulus generation and analysis.

### **1.4 AXI INTERFACE**

Modern SOCs mostly use communication protocols from the AMBA family to create synchronised communication, including APB, AHB, and AXI. Because verification is often projected to take up 70% of the whole project time, compared to the design stage's 30%, it becomes a very difficult work to complete throughout the creation of these sorts of SOCs. So, with the aid of a special

testing environment known as testing IP, several engineers are involved in evaluating an on-chip communication protocol associated functional qualities and the synchronisation between the IP's they connect [2].

The AXI interface module is to provide a protocol conversion between AXI initiator / target bus to AXI transactions or fifo transaction which is fundamentally a simple command for hostinterface main data bus transferring register access or DMA cycles to / from SoC. According to, whether DUT is working as an initiator or target which is decided by the signals it receives from AXI bfm or fifo bfm. The AXI interface is a high-performance, high-frequency, and low-latency interface used in digital designs. The AXI interface provides the features of burst transfers, read and write data transfers, and different transfer sizes, including 8-bit, 16-bit, 32-bit, and 64-bit transfers. The AXI interface also provides various features like data caching, out-of-order execution, and multiple outstanding transactions. The two-way handshake mechanism is the foundation of the AXI interface. To let the slave know that the address or data on the channel is genuine, the master sends a valid signal. Slave notifies master that it is prepared to take the data by sending a ready signal. In order for a write transaction to take place, the master must first communicate the necessary address and control information over the write address channel. The write data channel, which can be 32 or 64 bits in size and is where the actual data transmission happens, transports write data from master to slave. Slave asserts the rvalid signal to indicate that the data on the read channel is valid. The master device will assert the rready signal, and the master device will read the data [3].

#### Fig. 1.1 AXI IP interface

AXI initiator interface AXI slave

The working of DUT is as follows :

- The DUT will present upstream request when there is command available from the upstream command FIFO (rd\_avail / wr\_avail), and pop the command out of the FIFO when the command get (rd\_cget / wr\_cget) is asserted.

- AXI interface component will map command avail to the read / write address channel "AxVALID" signal, and return command get (wr\_cget) based on the corresponding read / write address channel "AxREADY" signal.

- i. If the command indicates write data is associated, AXI interface component will assert the write data channel "WVALID" signal 1 clock after command get (wr\_cget) assertion, and continuously popping out the data from the upstream data FIFO for that transaction to AXI data bus, provided the corresponding write data channel "WREADY" signal is also asserted continuously. Given there is no data get signal to the fifo bfm, if "WREADY" signal is de- asserted anytime when the "WVALID" signal is asserted for that transaction, the continuous data popping out will need to be re-directed to a streaming data FIFO instead, and replay from this streaming data FIFO to the AXI data bus when the "WREADY" signal is asserted later.

- The DUT will present downstream request put where there is a command free (p\_free / np\_free) from the downstream command FIFO.

- a. AXI interface component will map command free (p\_free / np\_free) to the read / write address channel "AxREADY" signal, and return command put (p\_cput / np\_cput) based on the corresponding read / write address channel "AxVALID" signal.

- AXI interface component will assert the write data channel "WREADY" signal 1 clock after command put, and start returning data put (p\_dput) based on the corresponding write data channel "WVALID" signal if the command indicates write data is associated.

- 3. The AXI interface will present downstream read completion command put (rdcp\_cput) when the readresponse is returned.

- a. AXI interface component will always assert read data channel "RREADY" signal, and based on the corresponding read data channel "RVALID" signal, it evaluates / stores all the read data in a

streaming data FIFO to decide the consolidated completion status; only then generate the read completion command put (rdcp\_cput), followed by the data put (rdcp\_dput) from the streaming FIFO.

- 4. The AXI interface will present upstream completion when there is command available from the upstream completion FIFO (rdcp\_cavail), and pop the command out of the FIFO when the completion get (rdcp\_cget) is asserted.

- a. If the command indicates write data is associated, AXI interface component will assert command get (cp\_cget) on the first assertion of the upstream completion FIFO avail (cp\_cavail), only then assert read data channel "RVALID" signal 1 clock later, and continuously popping out the data from the upstream data FIFO for that transaction to AXI data bus, provided the corresponding read data channel "RREADY" signal is also asserted continuously. Given there is no data get signal to the fifo bfm, if "RREADY" signal is de-asserted anytime when the "RVALID" signal is asserted for that transaction, the continuous data popping out will need to be re-directed to a streaming data FIFO instead, and replay from this streaming data FIFO to the AXI data bus when the "RREADY" signal is asserted later.

- b. AXI interface component will always assert write response channel "BREADY" signal, and return write completion put (wrcp\_cput) based on the corresponding write response channel "BVALID" signal.

- c. The AXI interface agent will need to add write completion support so that it can fence any status update that depending on upstream write until the corresponding write response / completion has been received. Need to be able to pipeline multiple upstream write outstanding before receiving the first write completion.

Fig. 1.2 UVM class hierarchy

# **CHAPTER 2**

# AXI INTERFACE TESTBENCH ENVIRONMENT

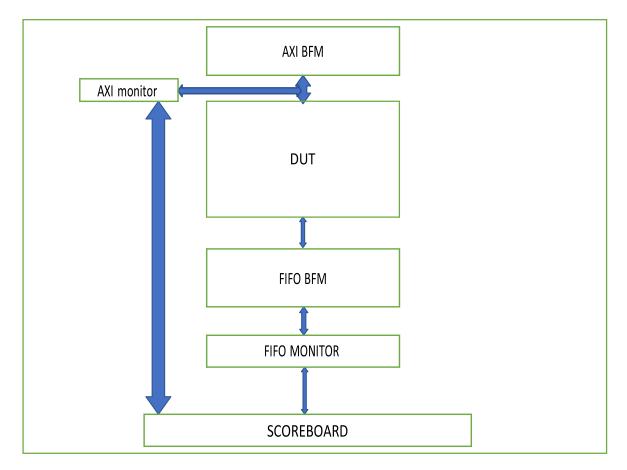

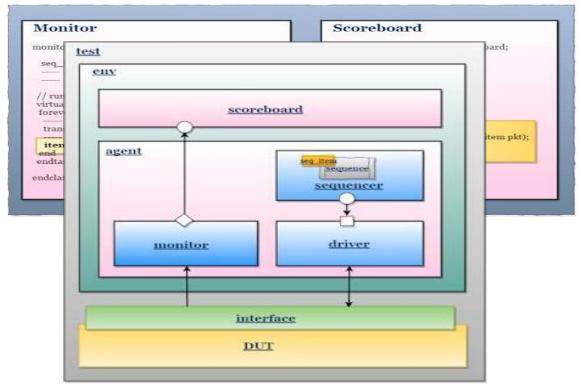

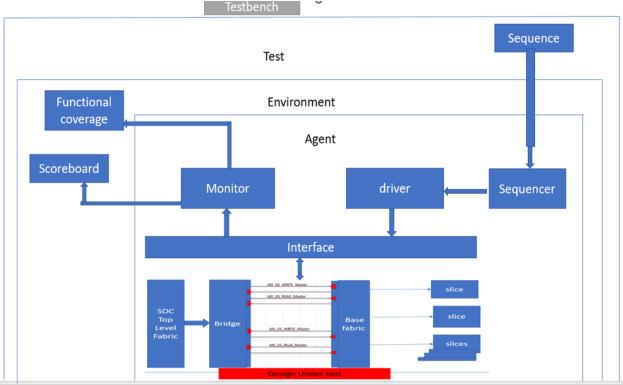

Below is testbench verification environment.

Fig. 2.1 Verification environment

### 2.1 TEST CLASS

In our testbench verification environment there are several test classes which are specific to the test casesused to verify the various scenarios.

Inside the test class in a fork join loop inside run phase we are connecting sequences and sequencer. Then the sequence items are randomized according to the constraints defined inside the sequence file instantiated in the test class.

The verification environment is starts to execute when the run\_test("my\_test") method is called, this method is defined in a top module. To run particular test case we need to pass that particular test case name as argument while calling run\_test.

### 2.2 FIFO BFM ENVIRONMENT

FIFO environment includes fifo sequence\_item class ,fifo\_sequencer class, driver class and monitor class.

#### 2.3 FIFO SEQUENCE ITEM

This class is responsible for generating stimulus and for the randomization of the signals. Constraints can also be defined according to the test case need.

### 2.3.1 FIFO BFM DRIVER

In FIFO Driver below logic is being used.

In run\_phase () reset and drive\_data task are being called.

In reset task reset of all signals is being done.

In Drive data below logic is used. Here Fork Join\_any is being used in forever loop.

In run phase drive data logic is used, so during run phase driver call get data to get input signals from the sequence item through sequencer. Now after getting signal values driver logic checks for some conditions inside forever loop then according to the sequence values driver decides whether it is a upstream transaction or downstream transaction.

1. From sequence we can set values of sequence item variables like wr\_cavail to 1 tostart upstream write transaction or start\_rd\_trans to 1 to start upstream read transaction.

2. If from sequence reset variable in sequence item is set to 1 then reset begin end loop comes into effect and reset is passed from driver to interface.

3. Interface is set inside top module using config db and according to need interface can be accessed by using get command inside class and components, by providing proper context and path

hierarchy while using set and get commands.

4. Driver is responsible for the conversion of signal level transaction to the pin level transaction.

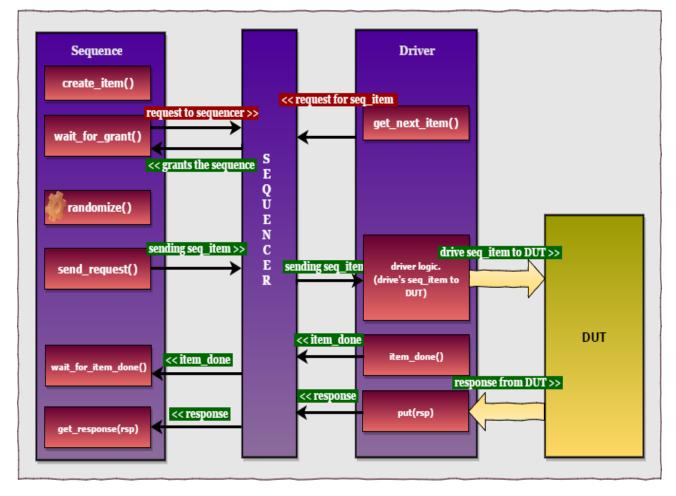

### 2.3.2 FIFO SEQUENCE

FIFO sequence generates the stimulus for the test cases defined. In our testbench we are generating stimulus for upstream and downstream transactions. Other than this we have to check different scenarios like reading and writing data to and from a memory or vice versa, parallel upstream and downstream transactions, multiple read write, so in these scenarios we need to put constraints on the signals inside thesequence class. For all these different test cases we made different sequence files which generates the signals according to the test. Sequence executes when we connect the sequence and sequencer inside testcase.

Fig. 2.3 FIFO sequence

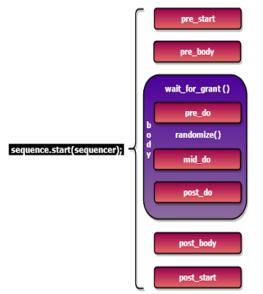

Fig. 2.4 UVM sequence methods

Inside the body method of sequence, logic of generation and sending sequence item is written. Steps used for the communication between sequence and driver,

- 1. create item

- 2. wait for grant(optional).

- 3. randomization.

- 4. send request.

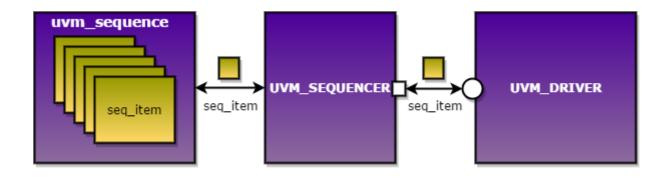

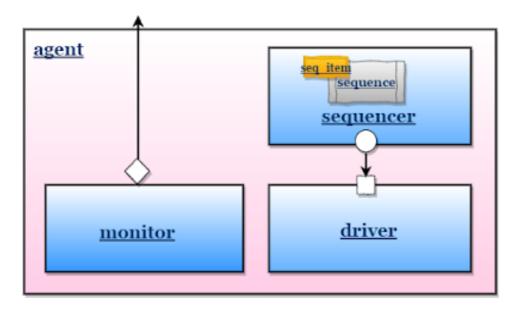

### 2.4 FIFO SEQUENCER

FIFO sequencer send the data generated by the sequence to the driver. Communication between driver and sequencer is done using TLM interface. Ports and exports are defined in driver and

sequencer respectively for the transaction.

Fig 2.5 FIFO sequencer

### 2.5 FIFO MONITOR

Interface is set inside the top module using config db. Monitor access the data from the DUT with the help of virtual interface through get config db. Monitor is responsible for the conversion of signal level orpin level activity to transaction level. Monitor uses analysis port and virtual interface handle that pointsto the DUT signals. Monitor in our environment collecting data and send that data to scoreboard and also inside monitor class data is sampled for the functional coverage.

### 2.6 TESTBENCH SCOREBOARD

In the scoreboard we receives the values as fifo bfm monitor and AXI response. Monitoring scoreboard communication typically involves the use of various technologies and methods to track and receive real-time updates from the scoreboard. Here's a general overview of how it happens:

1. Scoreboard Display: The scoreboard at a sports event typically displays information such as

scores, game time, team names, and sometimes additional statistics like fouls, timeouts, or player stats. This information is usually displayed electronically using LED panels or similar display technologies.

2. Data Collection: To monitor scoreboard communication, data needs to be collected from the scoreboard. This can be done through different means:

a. Scoreboard API: Some modern scoreboards provide an Application Programming Interface (API) that allows authorized users or developers to access the scoreboard data directly. Through the API, users can retrieve real-time updates and game information programmatically.

b. Data Feeds: Scoreboard providers or sports organizations may offer data feeds that deliver the scoreboard information in a standardized format. These data feeds can be accessed by subscribing to their services and receiving regular updates via the internet.

c. Manual Input: In some cases, individuals manually observe the scoreboard and enter the information into a monitoring system. This method is less common for real-time monitoring but may be used for smaller events or when automated options are not available.

3. Data Processing: Once the scoreboard data is collected, it needs to be processed to extract relevant information. This may involve parsing the data feed, converting it into a usable format, and storing it in a database or memory for further analysis.

4. Communication and Display: The processed scoreboard data is then communicated to the endusers or displayed on various platforms. This can be done through websites, mobile apps, social media, or any other medium that allows users to access the live scores and game information.

5. Real-Time Updates: To ensure up-to-date information, the monitoring system continuously fetches and updates the scoreboard data at regular intervals or in real-time. This could be achieved through automated processes that periodically retrieve new data or through push notifications sent by the scoreboard provider. It's important to note that the specific implementation of scoreboard monitoring can vary depending on the event, the scoreboard technology used, and the available resources or platforms for data retrieval and communication. Inside the scoreboard two queues are created to store the values getting from fifo bfm monitor andAXI response. If condition is used to

drive the compare logic but comparison is done based on triggering of anevent which is triggered only when both queues get data. Communication between monitor and scoreboard is done by TLM analysis portScoreboard compares the values, Values received from fifo monitor and Values received as AXI response

Fig. 2.6 Monitor scoreboard communication

Fig. 2.7 Testbench environment

### **CHAPTER 3**

### **ENHANCEMENTS**

In existing test cases, some of the functionalities of the design are not covered. So enhancements needs to be done in testbench ,which are given below :

1. AXI BFM Functional Coverage is not enabled. There is no local coverage present as well (for AXI interface). This is a coverage gap and it should have the AXI interface coverage as well to ensure we are sending all the possible stimulus as per DUT specifications.

a. Analyze Existing Coverage for AXI side.

b. Enable AXI coverage on AXI interface.

2. There are delays all over the place in the test stimulus. These delays needs to be removed to check if back to back request scenarios are properly covered.

3. There are no delays modeled in the handshake signals on the FIFO interface. All the handshakes are honored immediately. Actual RTL might behave differently.

4. Multiple transactions on a single interface are not enabled. The DUT has the capability of issuing multiple transactions before the previous transactions are completed(upstream). In the current testbench, the transactions are serialized and sent one after another.

5. For Downstream Transactions, there is no pipelining realized. Downstream transactions are put on the interface one at a time when all the phases of a previous transaction are over. In an actual scenario, the agent may issue another transaction while the current transaction is in progress. The DUT has ways to backpressure this second transaction until the processing of the first transaction is over.

6. rd\_cavail, wr\_cavail are always set to 1. In the actual RTL, they would be toggling and when a downstream transaction arrives, the npfree might be 0 and at a later time, it might toggle to 1 to allow the transaction.

These kind of scenarios are not exercised. Similarly, a lot of other signals are always constrained to a fixed values in the tests. There are tests which might use another values, but they are very minimal.

7. The randomization done on the traffic seems to be minimal.

8. Lot of places in the code, Testplusargs WRITE\_DOWN and READ\_DOWN command line argument is used even for the building/connecting the components and driving the transactions on the DUT interface. For Downstream read and write transactions, arguments are used to start the transaction ( driver code to get the next transaction and drive it has these arguments used). Generally, the construction/connection of the testbench components and agent specific tasks do not depend on the test specific simulation arguments.

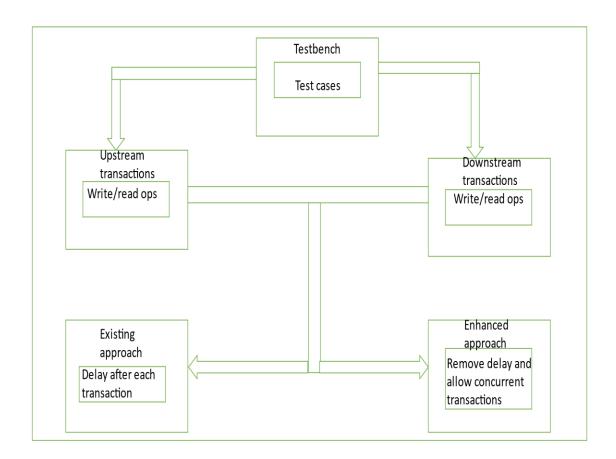

#### **Delay removal enhancement**

In an existing testbench, there are several test cases that involve multiple transactions occurring simultaneously or sequentially. These transactions include both upstream and downstream read/write operations. It is essential to test the performance of a design after achieving good functional coverage or covering all the functionalities and corner cases. The performance of a design depends on how efficiently and quickly it can handle transactions back-to-back or in parallel. However, the current approach in the testbench involves adding a delay after each transaction before initiating the next one. This delay-based approach is not an ideal method to test a design's performance.

To test a design's performance accurately, it is essential to simulate realistic traffic scenarios that involve multiple transactions happening concurrently without any delay. Such scenarios can help identify any potential bottlenecks and issues in the design, which may not be apparent during functional testing. Additionally, it is essential to test the design with a higher workload to determine its maximum throughput and scalability.

In conclusion, the existing testbench's approach of adding delays after each transaction may not provide accurate performance testing results. To test a design's performance accurately, it is essential to simulate realistic traffic scenarios involving multiple transactions happening concurrently without any delay and test the design with a higher workload to determine its maximum throughput and scalability.

Another critical aspect of performance testing is to determine the design's latency and response time. Latency refers to the time it takes for a request to reach the design and for the design to respond, while response time refers to the time it takes for the design to complete a transaction after receiving a request. Both latency and response time can significantly impact a design's overall performance and user experience. Therefore, it is essential to measure and analyze these metrics during performance testing.

In addition to latency and response time, it is also crucial to monitor the design's resource utilization during performance testing. The resource utilization can help identify if the design is efficiently utilizing its available resources, including CPU, memory, and I/O. If a design is underutilizing its resources, it may indicate an opportunity to optimize the design further. On the other hand, if a design is overutilizing its resources, it may indicate potential performance and scalability issues. Therefore, monitoring the design's resource utilization during performance testing can provide valuable insights into the design's efficiency and scalability. To address the performance issue in the existing testbench, the delays after each transaction were removed. However, upon removing the delays, it was discovered that almost half of the test cases were no longer working. This unexpected outcome can be attributed to the fact that some components of the testbench, such as the driver and sequence components, had delays built into their functionality. By removing these delays, the behavior of the testbench was significantly altered, leading to test failures.

To resolve this issue, the testbench components were carefully analyzed to identify which components required a delay to function correctly. The delay values were then adjusted, and the testbench was retested to ensure that all test cases were working as expected. The process of identifying and adjusting the delay values required a significant amount of effort and expertise, as it was critical to strike a balance between achieving good performance and ensuring that all test cases were functioning correctly.

In conclusion, removing delays from a testbench to improve performance can have unintended consequences on the testbench's functionality. Careful analysis and adjustment of delay values may be required to ensure that all test cases are working correctly while achieving good performance.

Fig 3.1 approach to allow concurrent transactions

As shown in the diagram, the current approach in the testbench involves adding a delay after each transaction before initiating the next one. This delay-based approach is not an ideal method to test a design's performance since it does not simulate real-world scenarios where transactions occur concurrently or back-to-back. The enhanced approach is to remove the delay and allow concurrent transactions to occur. This approach will provide a more realistic simulation of the design's performance and ensure that it can handle multiple transactions efficiently and quickly.

It is important to note that removing the delay and allowing concurrent transactions in the testbench can increase the complexity of the test environment. This complexity can result in issues such as race conditions, deadlocks, or other synchronization problems that may affect the test results. Therefore, it is essential to carefully design and implement the testbench to handle these scenarios and ensure that the results accurately reflect the design's performance. Additionally, it is recommended to use performance metrics such as throughput, latency, and response time to evaluate the design's performance accurately. By following these best practices, the testbench can provide reliable and accurate results that reflect the design's ability to handle concurrent transactions and deliver optimal performance.

In the context of the design verification process, the test stimulus is a critical component of the testing infrastructure. It generates a sequence of input signals that are applied to the DUT to verify its functionality. In this module, the test stimulus includes delays all over the place, which can impact the accuracy and effectiveness of the verification process. These delays can cause issues such as missed coverage or incorrect functionality. Therefore, it is important to remove these delays to ensure that back-to-back request scenarios are properly covered.

Back-to-back request scenarios refer to a situation where two requests are made in close proximity to each other without any delays between them. This is a common scenario in real-world applications and it is essential that the verification process covers these scenarios thoroughly. However, the delays present in the test stimulus can prevent the back-to-back request scenarios from being properly covered. The delays can cause a delay between the requests, resulting in a gap that is not representative of real-world scenarios. To address this issue, the delays need to be removed from the test stimulus. This can be achieved by modifying the test stimulus code to eliminate the delays. Once the delays are removed, the back-to-back request scenarios can be tested thoroughly to ensure that the DUT behaves as expected. This is essential for verifying the functionality of the DUT in real-world scenarios, as back-to-back requests are a common occurrence in many applications. By ensuring that these scenarios are properly covered, the DUT.

### Enabling and analyzing functional coverage

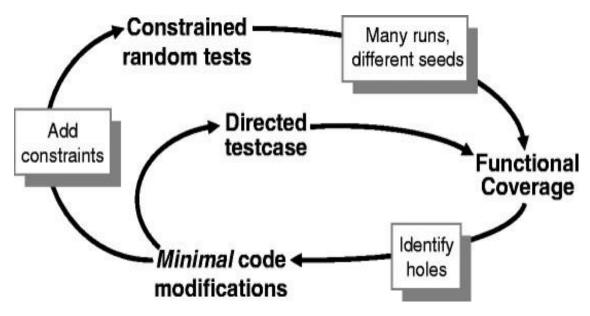

Let's say you have a block you need to verify. How do you know that the stimulus you are about to use is exhaustive enough and that you have covered the necessary scenarios/situations to prove it is working correctly? This is where functional coverage comes in. SystemVerilog's functional coverage constructs allow you to quantify the completeness of your stimulus by recording the values that have occurred on your signals. It is the consequence of Moore's law and present-day market requirement (low cost products having more functionality and smaller size with better battery performance). In this context, designing a baseband with a lot of features results in very complex and sophisticated design, which can be prone to hidden bugs. Before going for the silicon process, one should complete the verification. So that the outcome product can be reliable and bug free. To ensure this, the verification and development goes hand-in- hand. In verification the Functional Coverage tells how much of the design specification(scenarios) has been exercised.

This type of verification perceives the design from a system or user point of view. Above figure shows the feedback loop to analyze the coverage results and decide on which actions to take in order to converge on 100% coverage. The first choice is to run existing tests with more seeds; the second is to build new constraints. Only resort to creating directed tests if absolutely necessary.Back when we exclusively wrote directed tests, the verification planning was limited. If the design specification listed 100 features, all you had to do was write 100 tests. Coverage was

implicit in the tests — the "register move" test moved all combinations of registers back and forth. Measuring progress was easy: if you had completed 50 tests, you were halfway done. With CRT(Constrained Random test), we are freed from hand crafting every line of input stimulus, but now we need to write code that tracks the effectiveness of the test with respect to the verification plan. However we are still more productive, as we are working at a higher level of abstraction. We have moved from tweaking individual bits to describing the interesting design states. Reaching for 100% functional coverage forces us to think more about what we want to observe and how we can direct the design into those states.

To gather the coverage data run the same random testbench over and over, simply by changing the random seed to generate new stimulus. Each individual simulation generates a database of functional coverage information, the trail of footprints from the random walk. You can then merge all this information together to measure your overall progress using functional coverage as shown in Figure 1.9. The analysis of coverage data is done to decide how to modify the tests. If the coverage levels are steadily growing, it just needs to run existing tests with new random seeds, or even just run longer tests. If the coverage growth has started to slow, adding additional constraints to generate more "interesting" stimuli. When it becomes constant after some time, some parts of the design are not being exercised, so more tests need to be created. Lastly, when functional coverage for some areas of your design is skipped. Don't be in too big of a rush to reach 100% coverage, which just shows that bugs are looked in all the usual places. While verifying a design, take many random walks through the stimulus space; this can create many unanticipated combinations.

Functional coverage is a crucial aspect of the Universal Verification Methodology (UVM) that enables the verification engineers to measure the completeness of their verification environment. Functional coverage is a measure of the degree to which the design functionality has been exercised by the test cases during verification. It helps to ensure that the design meets the functional specifications and requirements. Functional coverage is typically implemented as a set of coverage points that represent the key functional aspects of the design. These coverage points can be defined at different levels of abstraction, such as module, block, or system level, depending on the complexity of the design and the verification goals. It plays a vital role in the verification process. It provides feedback on the effectiveness of the test suite and helps to identify areas of the design that have not been thoroughly tested. By measuring the completeness of the verification, functional coverage helps to increase the confidence in the correctness of the design. Additionally, it helps to prioritize the verification efforts by focusing on the areas that have low coverage, which in turn saves time and resources.

UVM provides a built-in functional coverage mechanism that allows verification engineers to define coverage models and collect coverage data during simulation. The UVM coverage model is a hierarchical structure that consists of coverage groups, coverage points, and coverage bins. Coverage groups represent the different aspects of the design that need to be covered, such as signals, transactions, or functions. Coverage points are the individual coverage items within a group, such as specific signal transitions or function calls. Coverage bins are the data containers that collect the coverage data for each coverage point. The UVM coverage model is defined in the coverage class, which is derived from the uvm\_coverage\_base class. The coverage class provides methods for defining coverage groups, coverage data can be analyzed and reported using different tools, such as the UVM built-in coverage report, third-party coverage tools, or custom scripts.

In order to use the UVM coverage mechanism, the verification engineer needs to create a coverage model that reflects the design functionality and the verification goals. The coverage model should be defined in a separate file, which is then connected to the testbench using the uvm\_config\_db mechanism. During simulation, the coverage model is activated using the uvm\_report\_coverage() method, which enables the collection of coverage data. The coverage data is then analyzed and reported at the end of the simulation using the uvm\_coverage\_report class. Functional coverage includes :

#### 1. Statement Coverage

Statement coverage is the most basic coverage type that checks whether every statement in the code has been executed at least once. This coverage type is usually used at the module or block level to ensure that all the statements in a design have been exercised.

2. Branch Coverage

Branch coverage checks whether all the possible branches in the code have been executed at least once. This coverage type is useful in identifying untested paths in a design that may lead to unexpected behavior.

#### 3. Condition Coverage

Condition coverage checks whether all the possible Boolean conditions in the code have been exercised at least once. This coverage type is used to ensure that all the decision points in a design have been tested.

#### 4. Toggle Coverage

Toggle coverage is used to ensure that every bit in the design has been toggled at least once. This coverage type is essential in designs where certain bits may be unused and may not be exercised during normal operation.

#### 5. Finite State Machine (FSM) Coverage

FSM coverage is used to ensure that all the states and transitions of an FSM have been exercised at least once. This coverage type is used in designs that contain state machines to ensure that all the possible sequences of states and transitions have been tested.

### 6. Assertion Coverage

Assertion coverage checks whether all the assertions in the design have been evaluated as true or false during simulation. This coverage type is used to ensure that all the assertions in a design have been tested.

### 7. Code Coverage

Code coverage combines statement, branch, and condition coverage to ensure that all the code in a design has been executed at least once. This coverage type is used to ensure that all the executable code in a design has been tested.

This project involves two Bus Functional Models (BFMs), namely, the FIFO BFM and the AXI BFM. To enable functional coverage of the AXI interface, several coverage-related signals need to be set, such as toggle coverage and FSM coverage. Meanwhile, for the functional coverage of the FIFO interface, the signals are sampled inside the FIFO monitor using a task from the interface. The collected data is then sent to a functional coverage class, which is included inside the FIFO BFM. This functional coverage class includes all the signals for which coverage is required. The AXI interface requires toggle coverage and FSM coverage to be set. Toggle coverage is a coverage

type that ensures that every bit in the design has been toggled at least once. This coverage type is essential in designs where certain bits may be unused and may not be exercised during normal operation. FSM coverage is used to ensure that all the states and transitions of a finite state machine (FSM) have been exercised at least once. This coverage type is used in designs that contain state machines to ensure that all the possible sequences of states and transitions have been tested.

On the other hand, for the functional coverage of the FIFO interface, the signals are sampled inside the FIFO monitor using a task from the interface. The collected data is then sent to a functional coverage class, which is included inside the FIFO BFM. This functional coverage class includes all the signals for which coverage is required. Inside the functional coverage class, different cover groups are defined which include coverpoints for all the signals. Inside the coverpoints, bins, cross, transition, and toggle coverage points are present. These coverpoints capture the various aspects of the signal behavior during simulation, such as the number of times a particular signal value occurs, the relationship between two or more signals, the transition of a signal from one value to another, and the number of times each bit in the signal has changed its value. The bins capture the number of times a particular signal value occurs during simulation. Cross coverage captures the relationship between two or more signals, while transition coverage captures the transition of a signal from one value to another. Toggle coverage captures the number of times each bit in the signal has changed its value. To ensure proper functional coverage and to check every corner case some points to be followed:

1. Identify all the design features: Review the design specifications to identify all the interfaces, inputs, outputs, and other important features.

2. Define coverpoints and cross coverage: Define coverpoints for each signal in the design and define cross coverage to capture the relationships between signals.

3. Define bins and sampling intervals: Define bins to capture the different values that a signal can take, and determine how frequently the signal is sampled during simulation.

4. Use randomization and constraint randomization: Generate random scenarios during simulation by using randomization and constraint randomization.

5. Use scenario-based testing: Define a set of scenarios based on real-world use cases that the design should be able to handle.

6. Use code coverage tools: Use code coverage tools to ensure that all the code in the design has been exercised during simulation.

#### Methodology Work done

This section explains about the methodology followed in the course of the development of this project. It has been divided into AXI Protocol understanding and functional coverage test planning, Functional Coverage coding and compile clean. Simulation and checking mechanism both for Single flow test and Multi test regression followed by Results and Future work .

## 1) <u>AXI Protocol understanding and functional coverage test planning</u> :

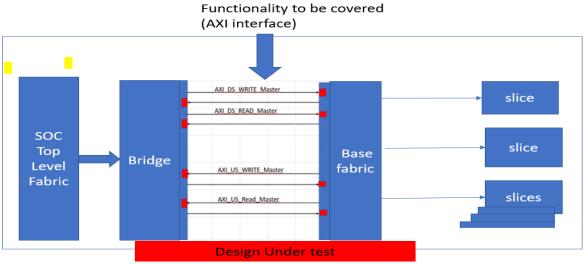

First a basic understanding of AXI protocol is required to further go ahead in this project. Handshaking was to be understood clearly so that source and destination are in sync. After gaining understanding of AXI functional coverage test planning was done which included deciding on the functional coverage region as shown in figure 3.3. Here the region between bridge and fabric is chosen. The red dots here represent the ports which we are tapping for functional coverage.

Fig. 3.3 Functionality to be covered from the design

Due to the fact that it accepts transactions from the generator and sends them to the AXI interface, BFM is crucial in the verification environment. The AXI interface that connects the master and the slave is in charge of ensuring that the necessary handshaking occurs during communication [4]. The AXI interface will be used for all outputs as it contains all transaction-related signals. The signals handshaking and valid transactions are continuously monitored. The monitor is made in accordance with the fact that memory is where most transactions are concentrated.

Based on this tapping four covergroups are decided to be created which carries the downstream and upstream transaction. For downstream two covergroups which cover the transaction from the bridge(master) to fabric(slave) and are named as master2slave\_ds sampled on the basis of slave clock slave2master\_rsp\_read\_ds sampled on the basis of fabric clock. Similarly for upstream two covergroups which cover the transaction from the fabric(slave) to bridge(master) and are named as slave2master\_us sampled on the basis of fabric clock and master2slave\_rsp\_read\_us sampled on the basis of bridge clock. Post this coverpoints and bins for each covergroup are decided based on the test plan and the input of the design team and collected.

| covergroup master2slave_ds @()  | posed          | <pre>dge clk_at_fabric);</pre> |  |  |  |  |  |

|---------------------------------|----------------|--------------------------------|--|--|--|--|--|

| ds_awaddr: coverpoint ds_awadd  | dr{            |                                |  |  |  |  |  |

| bins                            | $\mathbf{A} =$ | { h8000000xxxxx} ;             |  |  |  |  |  |

| bins                            | $\mathbf{B} =$ | { h8000000xxxxx} ;             |  |  |  |  |  |

| bins                            | C =            | { h8000000xxxxx} ;             |  |  |  |  |  |

| bins                            | D =            | { 'h8000000xxxxx} ;            |  |  |  |  |  |

| bins                            | $\mathbf{E} =$ | { h8000000xxxxx} ;             |  |  |  |  |  |

| bins                            | $\mathbf{F} =$ | { h8000000xxxxx} ;             |  |  |  |  |  |

| bins                            | 0 =            | { 'h8000000xxxxx} ;            |  |  |  |  |  |

| bins                            | 1 =            | { h8000000xxxxx} ;             |  |  |  |  |  |

| bins                            |                | { 'h8000000xxxxx} ;            |  |  |  |  |  |

| bins                            | G =            | { h8000000xxxxx} ;             |  |  |  |  |  |

| bins                            | Ħ =            | { h8000000xxxxx} ;             |  |  |  |  |  |

| bins                            | I —            | { 'h8000000xxxxx} ;            |  |  |  |  |  |

| bins                            | J =            | { h8000000xxxxx} ;             |  |  |  |  |  |

| bins                            | к =            | { h8000000xxxxx} ;             |  |  |  |  |  |

| bins                            | I =            | { 'h800000xxxxxx} ;            |  |  |  |  |  |

| }                               |                |                                |  |  |  |  |  |

|                                 |                |                                |  |  |  |  |  |

| ds_awid:coverpoint ds_awid{     |                |                                |  |  |  |  |  |

| bins aw:                        | id =           | {x,z};                         |  |  |  |  |  |

| }                               |                |                                |  |  |  |  |  |

| ds awsize:coverpoint ds awsize{ |                |                                |  |  |  |  |  |

| bins awsize_a ={3'hx};          |                |                                |  |  |  |  |  |

| bins a                          | awsiz          | $ze b = \{3'hx\};$             |  |  |  |  |  |

| bins a                          | awsiz          | $ze_c = \{3'hx\};$             |  |  |  |  |  |

| }                               |                |                                |  |  |  |  |  |

| endgroup                        | mas            | ster2slave_ds                  |  |  |  |  |  |

|                                 |                |                                |  |  |  |  |  |

**2**Functional Coverage Coding and compile clean:

Fig. 3.4 A snippet of coding of covergroups.

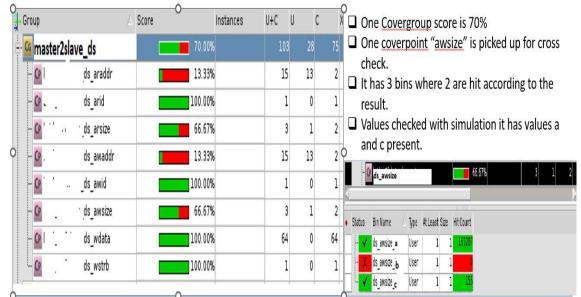

Total of four covergroups are coded with first covergroup 8 coverpoints 86 bins , second covergroup with 6 coverpoints and 84 bins, third covergroup with 9 coverpoints and 200 and fourth covergroup with 6 coverpoint and 200 bins. After coding was done then the code was compiled and checked for errors. Initially some syntax errors were seen such as missing colons, ending statements etc. After minor changes the code was successfully compiled.

## **3** <u>Simulation and checking mechanism:</u>

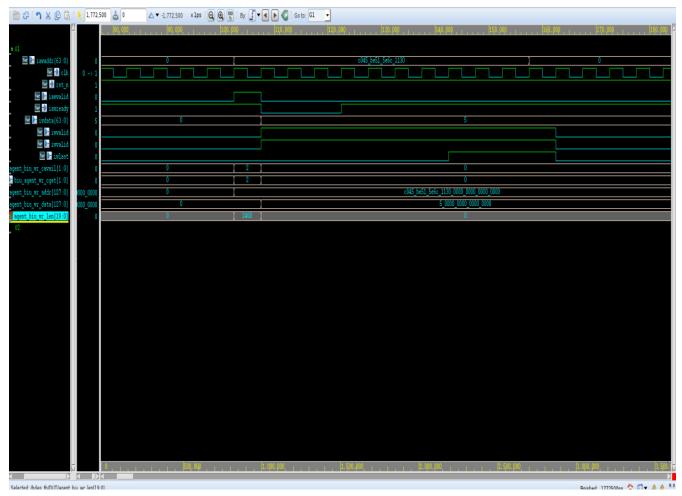

Single flow test check : After successful compilation it was required to run the code and see its result. A single test was run on the DUT through a typical UVM environment as shown in figure 3.4 which involves Sequencer which carries the sequences to the driver class. These sequences are then moved to the DUT where they are processed and their result is obtained which is picked

up by the monitor. Now the monitor's job is to transport this information to the scoreboard and functional coverage database. Here functional coverage is the database which collects all the data of bins hit or not % of both functional coverage/coverpoint.

Fig. 3.5 Running of a single test in UVM Environment

Now the results of the single test obtained are checked to check whatever data present in the functional coverage database is the same as data in simulation. As represented in figure 3.5 total coverage data is seen and a particular coverpoint "ds\_awsize" is picked up.

Fig. 3.6 Result of single test

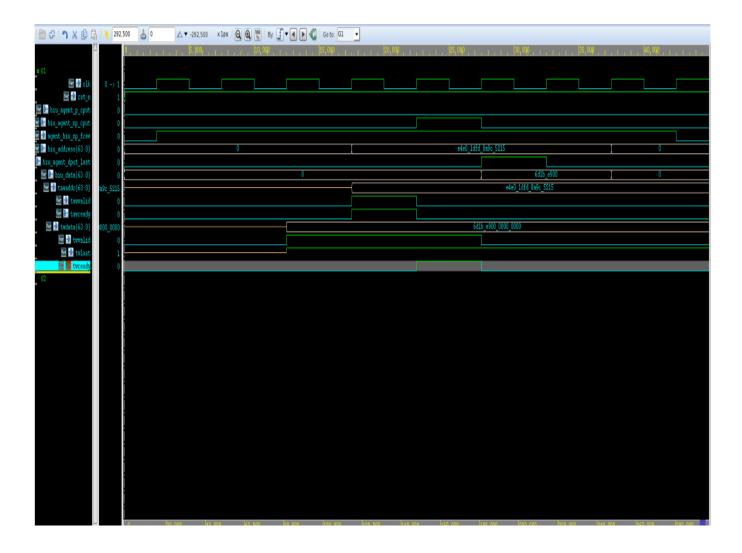

Now the value of ds\_awsize is cross checked in the simulation which is found to be similar as the bin values hit. Only for those values present in simulation the bins are hit. After this cross checking we came across that a major number of bins are still unhit. To gain more confidence in the code a sanity check to ensure aminimum number of bins are hit.

a) Sanity Check : Before enablement of the coverage code a sanity check is carried out to gain some confidence in the code. Once a minimal number of bins were hit the coverage was enabled for normal regression run. Here minimal number refers to some bins of each coverpoint being targeted such as toggling of bits, some address bins, some bins containing length, etc based on the simulation result. The result of simulation is cross checked with that of bins hit in the coverage. After this confidence only it was enabled for regression run and the data after run was collected effectively as shown in figure 3.7. As most number of bins were found to be hit the code was processed to be used for regression run.

| score       weight       GOAL       AT LEAST       PER ALTO BIN PRINT       Based on the sanity         82.28       1       100       64       64       check run it can be observed minimum         Summary for Group slave2master_us       number of bins are hit. |                    |      |         |              |      |        |         |              |         | score weight GOAL ATLEAST PER AUTO BIN PRINT<br>INSTANCE MAX MISSING COMMENT<br>100.00 1 100 1 0 64 64 the simulation as<br>done in case of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|---------|--------------|------|--------|---------|--------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Variables 378                                                                                                                                                                                                                                                        | COVERED COVERED PE | 2.28 |         |              |      | 110    |         |              |         | single test run.<br>Summary for Group slave2master_read_rsp_us                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| /ariables for Grou                                                                                                                                                                                                                                                   |                    |      | COVERED | -<br>PERCENT | GOAL | WEIGHT | ATIFAST | AUTO BIN MAX | COMMENT | CATEGORY EXPECTED UNCOVERED COVERED PERCENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Awaddr                                                                                                                                                                                                                                                               | 128                |      |         |              |      |        | 1       |              | 0       | Variables 98 0 98 100.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| awburst                                                                                                                                                                                                                                                              | 1                  |      | 1       | 100.00       | 100  | 1      | 1       |              | 0       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Awlen                                                                                                                                                                                                                                                                | 7                  | 2    | 2 5     | 71.43        | 100  | 1      | 1       | (            | 0       | White the for the second |

| awsize                                                                                                                                                                                                                                                               | 3                  | 0    | 3       | 100.00       | 100  | 1      |         | (            | 0       | Variables for Group slave2master read rsp us                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |