# DESIGN AND IMPLEMENTATION OF EFFICIENT MATRIX MULTIPLICATION USING VARIOUS ARCHITECTURE

A DISSERTATION REPORT

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTSFOR THE AWARD OF THE DEGREE

OF

## **MASTER OF TECHNOLOGY**

IN

# **VLSI DESIGN & EMBEDDED SYSTEM**

SUBMITTED BY:

### SHIVAM KUMAR

2K21/VLS/17

UNDER THE SUPERVISION OF

**Dr. J.Panda** PROFESSOR

# **ELECTRONICS & COMMUNICATION ENGINEERING**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

MAY 2023

Shivam Kumar

# ELECTRONICS & COMMUNICATION ENGINEERING

### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

### **CANDIDATE'S DECLARATION**

I, Shivam, Roll No. 2K21/VLS/17 student of M. Tech (VLSI Design & Embedded system), hereby declare that the project Dissertation titled **"Design and Implementation of efficient Matrix Multiplication using various architecture"** which is submitted by me to the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology is unique and has not been copied without proper citation. This work has never before been used to give a degree, diploma associateship, fellowship, or other equivalent title or recognition.

Place: Delhi

Shivam Kumar

Date: May 29, 2023

# ELECTRONICS & COMMUNICATION ENGINEERING

### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

### **CERTIFICATE**

I hereby certify that the Project Dissertation titled "Design and Implementation of efficient Matrix Multiplication using various architecture" which is submitted by Shivam Kumar, 2K21/VLS/17, to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the prerequisite for the award of the degree of Master of Technology, is a documentation of the student's projectwork completed under my supervision. To the best of my knowledge, this work hasnever been submitted in part or in full for any degree or diploma at this university or anywhere else.

Place: Delhi Date: May 29, 2023, Dr. J.Panda

### SUPERVISOR

Professor Department of ECE, DTU

### ACKNOWLEDGMENT

First and foremost, I would like to express my heartfelt gratitude to my mentor **Dr. J.Panda** for helping me on each step of this research, due to his continuous help and support I completed this research. His patience, motivation, ambition, and wide knowledge aided me throughout the research and dissertation writing process. Without his guidance, Icould not have imagined completing this research. His suggestions and the way of managing the work were the most important key points, which made my path clear. He helped me use my full potential because of that I tried my best to get the maximum for this project. I am extremely grateful to him for guiding me throughout the project. I am thankful to Electronics Department and faculty for helping me, and thankful to myfriends who helped me directly and indirectly in my research.

Shivam Kumar 2K21/VLS/17 MTech: VLSI Design and Embedded System (2021-2023)

## ABSTRACT

The semiconductor industry plays a crucial role in the design and manufacture of integrated circuits (ICs) used in a wide range of electronic devices. VLSI technology allows for the integration of millions of transistors onto a single chip, enabling the creation of highly complex and powerful devices such as computers, smart phones, and other electronic devices. The VLSI industry is a key driver of innovation in the electronics industry and has played a major role in the development of new technologies and the proliferation of electronic devices in our daily lives. Consequently, area, speed, and power play a critical role in any circuit design .A circuit must be created to meet the present trend's requirements with minimal space and minimal time limitations.

Matrix multiplication is of significant importance in various fields and applications. Matrix multiplication plays a fundamental role in linear algebra, solving system of linear equations, data analysis and machine learning, computer graphics and computer vision, network theory and graph algorithm, etc. This thesis gives a thorough investigation into how the Wallace tree multiplier, Vedic multiplier, and parallel prefix adders might be combined to enhance matrix multiplication performance. These techniques contribute to achieving significant speed improvements, reduced and optimized resource utilization. The findings of this study add to understanding of digital circuit design by offering suggestions for choosing and incorporating effective multiplication methods for matrix operations. The thesis provides helpful advice to researchers and designers of digital circuits by explaining the trade-offs, benefits, and drawbacks of the integrated architecture.

Firstly, Ripple Carry adders, Kogge Stone adders, and Han Carlson adders have been designed and analyzed. After that, the Wallace tree multiplier and Vedic multiplier are designed using these adders. By combining both multiplier and adder, matrix multiplication designs, analyses the performance data, and interprets the results obtained from the experiments. Using the ISE Design Suite tools in Verilog, all circuits are created and simulations are run. The XC6SLX150T are the devices used for synthesis.

# CONTENTS

| Candid    | ate's Declaration                            | i   |

|-----------|----------------------------------------------|-----|

| Certific  | ate                                          | ii  |

| Acknow    | vledgment                                    | iii |

| Abstrac   | et                                           | iv  |

| Conten    | t                                            | v   |

| List of l | Figures                                      | vii |

| List of [ | Tables                                       | xi  |

| List of a | abbreviations                                | xii |

|           | CHAPTER 1 INTRODUCTION                       | 1   |

| 1.1       | Motivation                                   | 2   |

| 1.2       | Objective                                    | 3   |

| 1.3       | Thesis Organization                          | 3   |

|           | CHAPTER 2 LITERATURE REVIEW                  | 5   |

| 2.1       | Previous Reported Work                       | 5   |

|           | CHAPTER 3 CHARACTERISTICS COMPARISON FOR     | 8   |

|           | DIFFERENT ADDERS                             |     |

| 3.1       | Ripple Carry adder                           | 8   |

| 3.2       | Parallel Prefix Adder                        | 9   |

| 3.3       | Kogge Stone Adder                            | 10  |

| 3.4       | Han Carlson Adder                            | 11  |

| 3.5       | Simulation and Synthesis Results             | 12  |

| 3.6       | Important Outcomes                           | 17  |

|           | CHAPTER 4 DESIGN AND ANALYSIS OF MULTIPLIERS |     |

|           | USING DIFFERENT PARALLEL PREFIX ADDERS       |     |

| 4.1.      | Multiplier                                   | 19  |

| 4.1.1     | Wallace Tree Multiplier                      | 19  |

| 4.1.2     | Urdhva Tiryagbhyam Vedic Multiplier          | 21  |

v

| 4.2   | Simulation and Synthesis Results                                                                                                  | 24 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2.1 | Wallace Tree Multiplier using Ripple Carry Adder                                                                                  | 24 |

| 4.2.2 | Wallace Tree Multiplier using Kogge Stone Adder                                                                                   | 25 |

| 4.2.3 | Wallace Tree Multiplier using Han Carlson Adder                                                                                   | 27 |

| 4.2.4 | Vedic Multiplier using Ripple Carry Adder                                                                                         | 28 |

| 4.2.5 | Vedic Multiplier using Kogge Stone Adder                                                                                          | 30 |

| 4.2.6 | Vedic Multiplier using Han Carlson Adder                                                                                          | 31 |

| 4.5   | Important Outcomes                                                                                                                | 34 |

|       | CHAPTER 5 DESIGN AND COMPARISON OF MATRIX<br>MULTIPLICATION USING WALLACE TREE AND VEDIC<br>MULTIPLIER WITH PARALLEL PREFIX ADDER | 35 |

| 5.1   | Fundamentals of Matrix Multiplication                                                                                             | 36 |

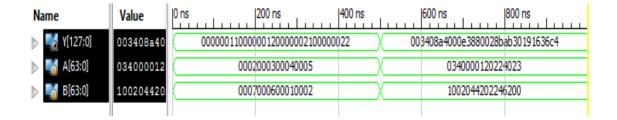

| 5.2   | Simulation and Synthesis Results                                                                                                  | 36 |

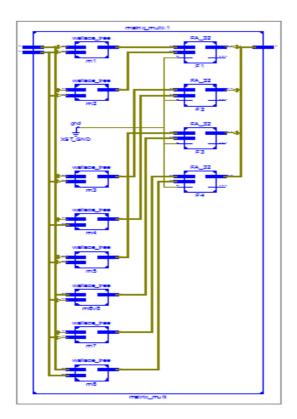

| 5.2.1 | Matrix multiplication using Wallace Tree Multiplier and RCA                                                                       | 36 |

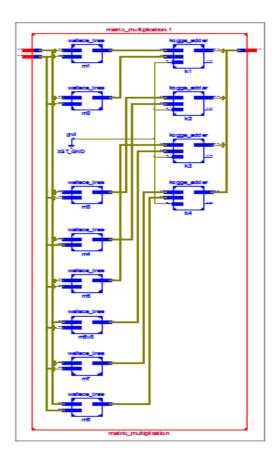

| 5.2.2 | Matrix multiplication using Wallace Tree Multiplier and KSA                                                                       | 38 |

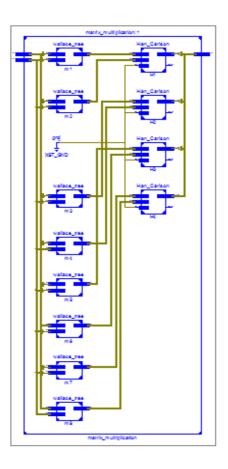

| 5.2.3 | Matrix multiplication using Wallace Tree Multiplier and HCA                                                                       | 39 |

| 5.2.1 | Matrix multiplication using Vedic Multiplier and RCA                                                                              | 41 |

| 5.2.2 | Matrix multiplication using Vedic Multiplier and KSA                                                                              | 42 |

| 5.2.3 | Matrix multiplication using Vedic Multiplier and HCA                                                                              | 44 |

| 5.3   | Important Outcomes                                                                                                                | 47 |

|       | CHAPTER 6 CONCLUSION AND FUTUR SCOPE                                                                                              | 48 |

| 6.1   | Conclusion                                                                                                                        | 48 |

| 6.2   | Future Scope                                                                                                                      | 49 |

|       | REFERENCES                                                                                                                        | 50 |

# LIST OF FIGURES

| Figure Name                                                 | Page No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Block diagram of Ripple Carry adder                         | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Graphical Representation of 16 bit Kogge Stone adder        | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Graphical Representation of 16 bit Han Carlson Adder        | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Device utilization of Ripple Carry Adder                    | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Schematic of Ripple Carry Adder                             | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Delay Report of Ripple Carry Adder                          | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Simulation Result of Ripple Carry Adder                     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Device utilization of Kogge Stone Adder                     | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Schematic of Kogge Stone Adder                              | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Delay Report of Kogge Stone Adder                           | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Simulation Result of Kogge Stone Adder                      | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Device utilization of Han Carlson Adder                     | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Schematic of Han Carlson Adder                              | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Delay Report of Han Carlson Adder                           | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Simulation Result of Han Carlson Adder                      | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

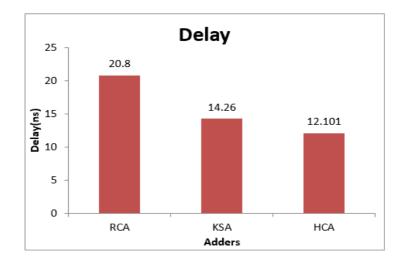

| Delay comparison graph for Adders                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

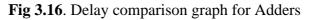

| Area comparison graph for Adders                            | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Graphical Representation Of 8X8 bit Wallace Tree Multiplier | r 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Flow diagram of Wallace Tree Multiplier                     | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2X2 Gate level netlist of Vedic Multiplier                  | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                             | Block diagram of Ripple Carry adder<br>Graphical Representation of 16 bit Kogge Stone adder<br>Graphical Representation of 16 bit Han Carlson Adder<br>Device utilization of Ripple Carry Adder<br>Schematic of Ripple Carry Adder<br>Delay Report of Ripple Carry Adder<br>Device utilization of Kogge Stone Adder<br>Device utilization of Kogge Stone Adder<br>Schematic of Kogge Stone Adder<br>Delay Report of Han Carlson Adder<br>Device utilization of Han Carlson Adder<br>Delay Report of Han Carlson Adder<br>Delay Report of Han Carlson Adder<br>Delay Report of Han Carlson Adder<br>Delay comparison graph for Adders<br>Area comparison graph for Adders<br>Graphical Representation Of 8X8 bit Wallace Tree Multiplier |

| Fig. 4.4  | Block diagram of NXN bit Vedic Multiplier               | 23 |

|-----------|---------------------------------------------------------|----|

| Fig. 4.5  | Device utilization of Wallace Tree Multiplier using RCA | 24 |

| Fig. 4.6  | Delay Report of Wallace Tree Multiplier using RCA       | 24 |

| Fig. 4.7  | Schematic of Wallace Tree Multiplier using RCA          | 25 |

| Fig. 4.8  | Simulation Result of Wallace Tree Multiplier using RCA  | 25 |

| Fig. 4.9  | Device utilization of Wallace Tree Multiplier using KSA | 25 |

| Fig. 4.10 | Delay Report of Wallace Tree Multiplier using KSA       | 26 |

| Fig. 4.11 | Schematic of Wallace Tree Multiplier using KSA          | 26 |

| Fig. 4.12 | Simulation Result of Wallace Tree Multiplier using KSA  | 27 |

| Fig. 4.13 | Device utilization of Wallace Tree Multiplier using HCA | 27 |

| Fig. 4.14 | Delay Report of Wallace Tree Multiplier using HCA       | 27 |

| Fig. 4.15 | Schematic of Wallace Tree Multiplier using HCA          | 28 |

| Fig. 4.16 | Simulation Result of Wallace Tree Multiplier using HCA  | 28 |

| Fig. 4.17 | Device utilization of Vedic Multiplier using RCA        | 28 |

| Fig. 4.18 | Delay Report of Vedic Multiplier using RCA              | 29 |

| Fig. 4.19 | Schematic of Vedic Multiplier using RCA                 | 29 |

| Fig. 4.20 | Simulation Result of Vedic Multiplier using RCA         | 30 |

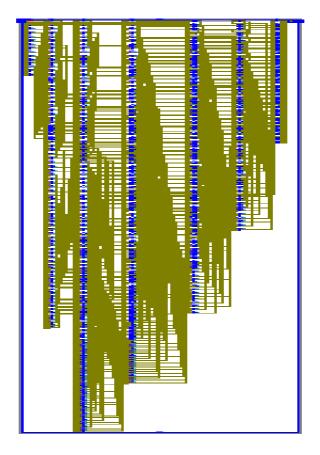

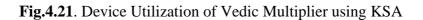

| Fig. 4.21 | Device utilization of Vedic Multiplier using KSA        | 30 |

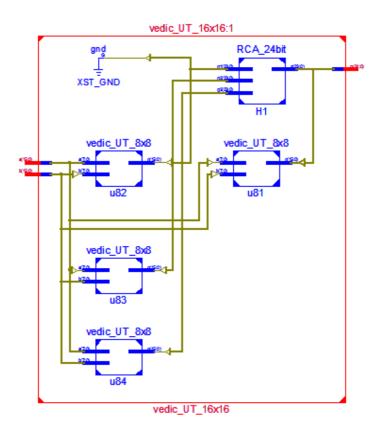

| Fig. 4.22 | Delay Report of Vedic Multiplier using KSA              | 30 |

| Fig. 4.23 | Schematic of Vedic Multiplier using KSA                 | 31 |

| Fig. 4.24 | Simulation Result of Vedic Multiplier using KSA         | 31 |

| Fig. 4.25 | Device utilization of Vedic Multiplier using HCA        | 31 |

| Fig. 4.26 | Delay Report of Vedic Multiplier using HCA              | 32 |

| Fig. 4.27 | Schematic of Vedic Multiplier using HCA                 | 32 |

| Fig. 4.28 | Simulation Result of Vedic Multiplier using HCA         | 33 |

|           |                                                         |    |

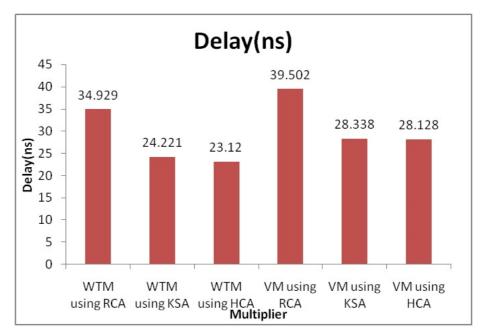

| Fig. 4.29 | Delay comparison graph for multiplier                                                | 33 |

|-----------|--------------------------------------------------------------------------------------|----|

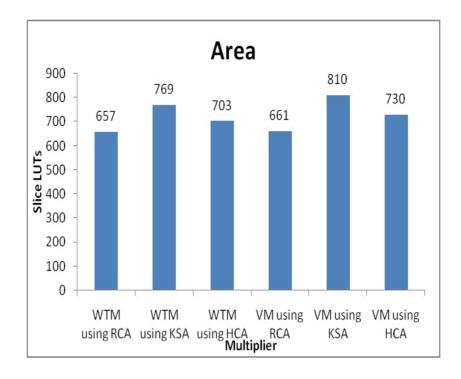

| Fig. 4.30 | Area comparison graph for multiplier                                                 | 34 |

| Fig. 5.1  | Device utilization of Matrix multiplication using Wallace Tree<br>Multiplier and RCA | 36 |

| Fig. 5.2  | Delay Report of Matrix multiplication using Wallace Tree<br>Multiplier and RCA       | 37 |

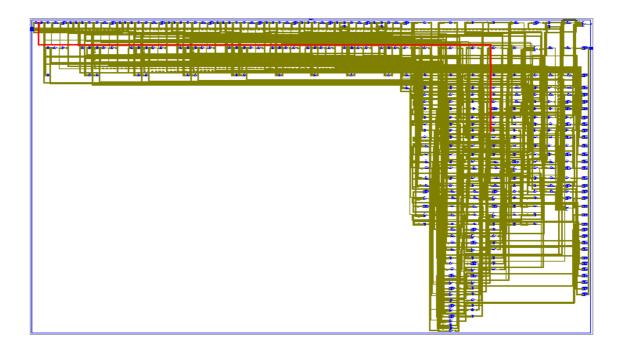

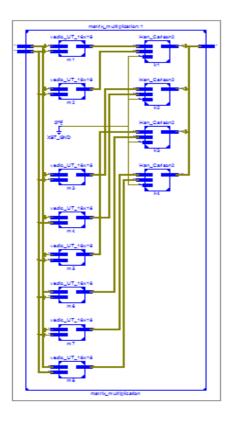

| Fig. 5.3  | Schematic of Matrix multiplication using Wallace Tree                                | 37 |

|           | Multiplier and RCA                                                                   |    |

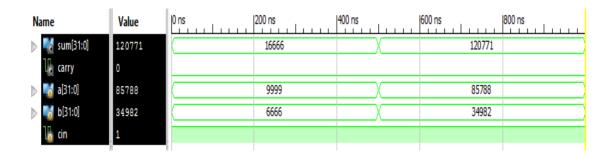

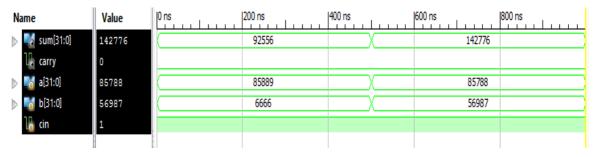

| Fig. 5.4  | Simulation Result of Matrix multiplication using Wallace Tree<br>Multiplier and RCA  | 38 |

| Fig. 5.5  | Device utilization of Matrix multiplication using Wallace Tree<br>Multiplier and KSA | 38 |

| Fig. 5.6  | Delay Report of Matrix multiplication using Wallace Tree<br>Multiplier and KSA       | 38 |

| Fig. 5.7  | Schematic of Matrix multiplication using Wallace Tree                                | 39 |

|           | Multiplier and KSA                                                                   |    |

| Fig. 5.8  | Simulation Result of Matrix multiplication using Wallace Tree<br>Multiplier and KSA  | 39 |

| Fig. 5.9  | Device utilization of Matrix multiplication using Wallace Tree<br>Multiplier and HCA | 39 |

| Fig. 5.10 | Delay Report of Matrix multiplication using Wallace Tree<br>Multiplier and HCA       | 40 |

| Fig. 5.11 | Schematic of Matrix multiplication using Wallace Tree                                | 40 |

|           | Multiplier and HCA                                                                   |    |

| Fig. 5.12 | Simulation Result of Matrix multiplication using Wallace Tree<br>Multiplier and HCA  | 41 |

| Fig. 5.13 | Device utilization of Matrix multiplication using Vedic Multipli<br>and RCA<br>ix    | 41 |

| Fig. 5.14 | Delay Report of Matrix multiplication using Vedic Multiplier ar<br>RCA      | 41 |

|-----------|-----------------------------------------------------------------------------|----|

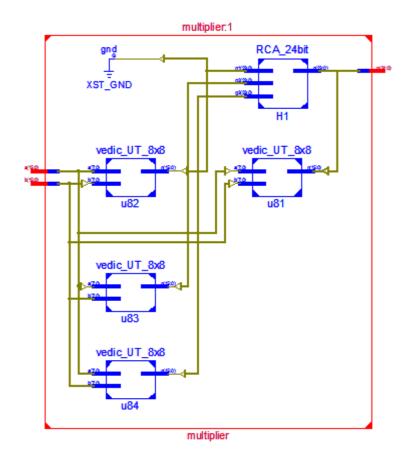

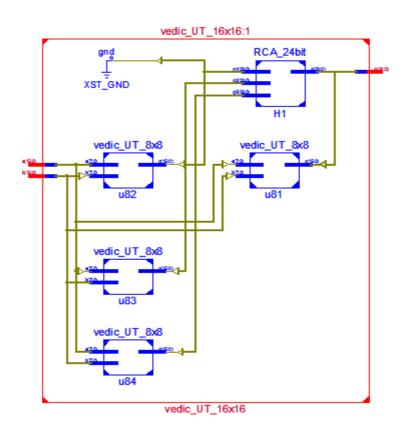

| Fig. 5.15 | Schematic of Matrix multiplication using Vedic Multiplier and RCA           | 42 |

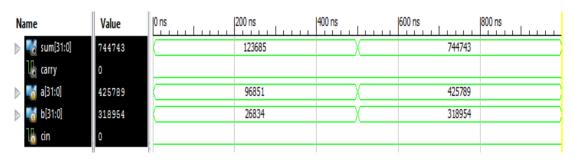

| Fig. 5.16 | Simulation Result of Matrix multiplication using Vedic Multipli<br>and RCA  | 42 |

| Fig. 5.17 | Device utilization of Matrix multiplication using Vedic Multipli<br>and KSA | 42 |

| Fig. 5.18 | Delay Report of Matrix multiplication using Vedic Multiplier ar KSA         | 43 |

| Fig. 5.19 | Schematic of Matrix multiplication using Vedic Multiplier and KSA           | 43 |

| Fig. 5.20 | Simulation Result of Matrix multiplication using Vedic Multipli<br>and KSA  | 44 |

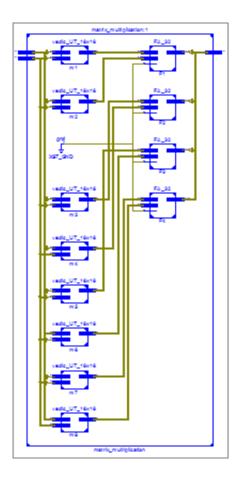

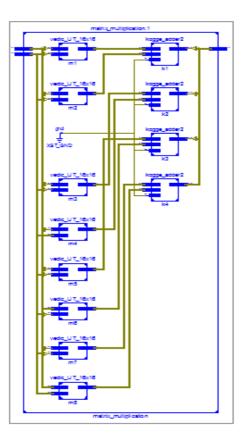

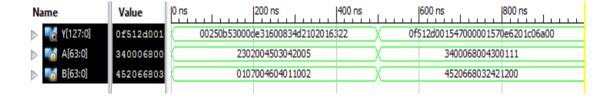

| Fig. 5.21 | Device utilization of Matrix multiplication using Vedic Multipli<br>and HCA | 44 |

| Fig. 5.22 | Delay Report of Matrix multiplication using Vedic Multiplier ar<br>HCA      | 44 |

| Fig. 5.23 | Schematic of Matrix multiplication using Vedic Multiplier and HCA           | 45 |

| Fig. 5.24 | Simulation Result of Matrix multiplication using Vedic Multipli<br>and HCA  | 45 |

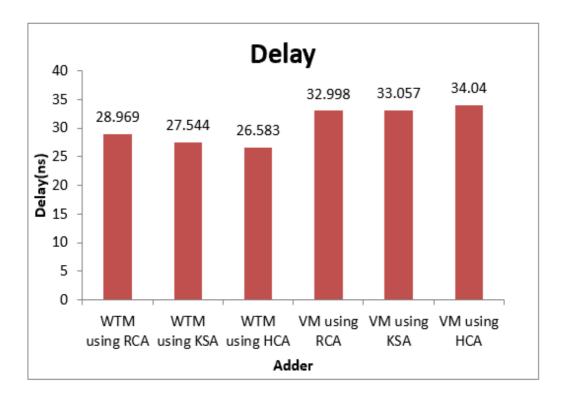

| Fig. 5.25 | Delay comparison graph for Matrix Multiplication                            | 46 |

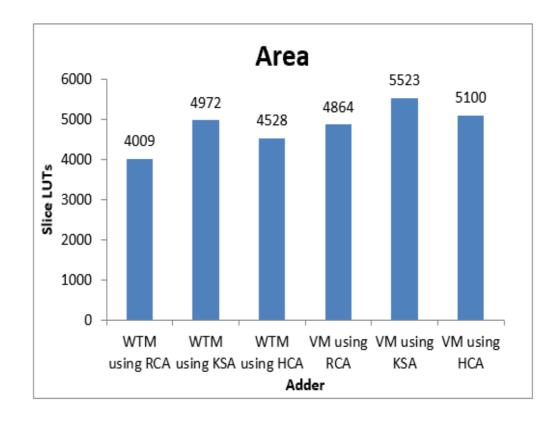

| Fig. 5.26 | Area comparison graph for Matrix Multiplication                             | 46 |

|           |                                                                             |    |

# LIST OF TABLES

| Tab No.  | Table Name                                                                                     | Page No. |  |

|----------|------------------------------------------------------------------------------------------------|----------|--|

| Tab. 3.1 | Comparative Analysis of Delay and Area of Adders                                               | 16       |  |

| Tab. 4.1 | Comparative Analysis Of Wallace Tree Multiplier<br>And Vedic Multiplier using Different Adders | 33       |  |

| Tab. 5.1 | Comparative Analysis Of Matrix Multiplication using using Different Multipliers                | 45       |  |

# LIST OF ABBREVIATIONS

| S.No. | Abbreviation | Full Name                     |  |

|-------|--------------|-------------------------------|--|

|       |              |                               |  |

|       |              |                               |  |

| 1.    | VLSI         | Very Large-Scale Integration  |  |

| 2.    | RCA          | Ripple Carry Adder            |  |

| 3.    | KSA          | Kogge Stone                   |  |

| 4.    | НСА          | Han Carlson Adder             |  |

| 5.    | WTM          | Wallace Tree Multiplier       |  |

| 6.    | VM           | Vedic Multiplier              |  |

| 7.    | DSP          | Digital Signal Processing     |  |

| 8.    | PPA          | Parallel Prefix Adder         |  |

| 9.    | UTM          | Urdhva Tiryakbhyam multiplier |  |

## **CHAPTER 1**

### **INTRODUCTION**

Multipliers are essential arithmetic units in the VLSI (Very Large Scale Integration) industry, particularly in digital signal processing (DSP), communication systems, image processing, and various other applications. They are responsible for performing multiplication operations, which are fundamental to numerous computational tasks. The VLSI industry continually works on developing advanced multiplier architectures to enhance speed, power efficiency, and area utilization. Emerging technologies such as approximate computing and approximate multipliers contribute to achieving a balance between accuracy and computational efficiency. Overall, multipliers are indispensable components in the VLSI industry, enabling efficient multiplication operations in various applications and driving ongoing research and development.

In many computer applications, matrix multiplication is an essential operation, especially in the areas of linear algebra, image processing, machine learning, and scientific computing. The need for effective and optimized matrix multiplication algorithms grows as the size and complexity of matrices continue to increase. There is a growing need for effective and optimized methods for matrix operations as the need for high-performance computing keeps rising. In this work, to create a comprehensive framework for high-performance matrix multiplication and multiplication operations in digital circuit designs, investigate the integration of parallel prefix adders alongside the Wallace tree multiplier and Vedic multiplier.

The Wallace tree multiplier and Vedic multiplier are most effective multiplication. The Wallace tree multiplier reduces the number of partial products and offers faster multiplication speeds by utilizing a combination of carry-save adders and carry-propagate adders. Similarly, the Vedic multiplier leverages simple arithmetic operations, inspired by ancient Indian mathematics principles, to achieve high-speed multiplication with fewer logic gates compared to conventional multipliers.

We suggest using parallel prefix adders into the architecture of matrix multiplication and the multiplier. Carry propagation is parallelized via parallel prefix adders, also known as carry-look-ahead adders, which significantly increase speed. Parallel prefix adders reduce the critical route time by efficiently allocating and computing the carries in parallel, which improves overall performance.

For the purpose of creating an optimized framework for matrix multiplication and multiplication operations in digital circuit designs, this thesis investigates the synergistic integration of the Wallace tree multiplier, Vedic multiplier, and parallel prefix adders. Utilizing each component's advantages will increase throughput, decrease latency, and enhance power efficiency.

Partitioning the input matrices, using the implemented multipliers to create partial products, and implementing parallel prefix adders for effective accumulation and carry propagation are all part of the suggested methodology. We hope to significantly increase matrix multiplication and multiplication operations performance by parallelizing the computation and reducing the critical path delay. All the design and simulation are performed in Verilog using ISE Design Suite tool. The selected board is XC6SLX150T.

#### 1.1 Motivation

A variety of computer activities, from scientific simulations to machine learning algorithms, can be significantly sped up by using efficient matrix multiplication and multiplication processes. Traditional multiplication methods may become a bottleneck when data amount and complexity rise, reducing system performance as a whole. Therefore, there is a strong motivation to explore novel approaches that can enhance the efficiency and speed of matrix multiplication operations in digital circuit designs.

The Wallace tree multiplier and Vedic multiplier have already shown potential for accelerating multiplication and lowering the incidence of partial products. Additional methods must be investigated, though, in order to improve the performance of these multipliers and enable quicker matrix multiplication. Due to the parallelization of the carry propagation mechanism, parallel prefix adders have seen notable speed gains.

The necessity to create an optimized framework that incorporates the benefits of the Wallace tree multiplier, Vedic multiplier, and parallel prefix adders served as the driving force for this work. The aim of this work is to increase throughput, decrease latency, and reduce area in matrix multiplication and multiplication operations by utilizing the parallel computing capabilities of the adders coupled with effective multiplication strategies. The outcome of this research has the potential to benefit various domains that heavily rely on matrix operations, providing faster and more energy-efficient solutions for processing

large-scale matrices leading to advancements in various domains. Furthermore, the insights gained from this research can contribute to the ongoing development of efficient arithmetic units and computing architectures, paving the way for future advancements

#### 1.2 Objective

New questions, ideas, and understandings can arise as a result of an analysis of the available data. Exploring uncharted territory is the main objective of research in order to find new opportunities.

#### Primary objectives of this research project are as follows:

- To design and implement an efficient matrix multiplication algorithm using the Wallace tree multiplier, Vedic multiplier, and parallel prefix adders in digital circuit designs.

- To understand the working of multipliers and which ones perform the best, a comparison is done between Wallace tree multiplier and Vedic multiplier. To enhance the performance of multiplier, parallel prefix adder (Kogge Stone and Han Carlson adder) are used.

- To validate the correctness and accuracy of the matrix multiplication algorithm by comparing the results with established mathematical solutions.

- To contribute to the body of knowledge in the field of digital circuit design by investigating the synergistic integration of the Wallace tree multiplier, Vedic multiplier, and parallel prefix adders for effective matrix multiplication operations

By accomplishing these objectives, this effort gives a thorough understanding of the functionality, effectiveness, and applicability of the integrated framework. By enabling more effective and optimized matrix operations across a range of computing domains, the research's results and insights will boost digital circuit design methodologies.

#### **1.3 Thesis Organization**

This thesis is divided into six chapters. The thesis is organized as follows: Chapter 2 provides the literature review and the technology gap. Chapter 3 is a comprehensive review of the Ripple Carry adder, the Kogge Stone adder, and the Han Carlson adder. Chapter 4 examines the comparison of the Wallace tree multiplier and the Vedic

multiplier using different adders. Chapter 5 depicts the design of matrix multiplication and its analysis on the basis of performance and area. The conclusion and future scope are presented in Chapter 6.

- CHAPTER 1- Provides a basic overview of matrix multiplication, multiplier and parallel prefix adder operation. In this chapter discussion areas are thesis's objective, motivation, methodology, and thesis organization.

- CHAPTER 2- This chapter provides a detailed overview of earlier research on parallel prefix adders and multiplication. According to published research, Vedic and Wallace tree multipliers are faster multipliers than traditional ones. Additionally, Han Carlson and Kogge Stone PPAs are quicker than Ripple carry adder.

- CHAPTER 3- This chapter covers the details of the implementation of Adder used in this work. The design and performance evaluation of the Kogge Stone, Ripple Carry, and Han Carlson adders are covered in this chapter.

- CHAPTER 4- This chapter covers the description of the Wallace tree and the Vedic multiplier. Both multipliers are designed using different adders (discussed in the previous chapter) and compared for their performance.

- CHAPTER 5- This chapter presents the methodology employed in this research, including the design and integration of the matrix multiplication algorithm. This chapter describes the implementation of matrix multiplication using multipliers (discussed in chapter 4) and comparison between area and delay.

- CHAPTER 6- This chapter contains the important outcomes of every chapter along with the future work.

In order to explore the directions for our current work, a comprehensive list of references is supplied at the end of the thesis.

## **CHAPTER 2**

### LITERATURE REVIEW

Literature review is essential when conducting research. It helps to establish a solid understanding of the topic and acknowledge the contributions of other scholars in the field. It also helps to identify contradictions, research gaps, conflicting findings, and unresolved issues that exist within the current body of knowledge. This information guides the researcher in formulating research questions and designing studies that address these gaps and contribute to the advancement of knowledge in the field.

This chapter is categorized into two sections: (1) previous reported work, and (2) technical gaps.

### 2.1 PREVIOUS REPORTED WORK:

Y. d. Ykuntam, K. Pavani and K. Saladi [1], proposed new and innovative architecture for the Wallace tree multiplier, which employs parallel prefix adders (PPAs) to perform the final addition step of partial products. They put forward five distinct structures for the Wallace tree multiplier, each incorporating a different type of adder.Detailed analysis of the proposed designs in terms of area and delay compared to traditional multiplier designs is completed.

S. Lad and V. S. Bendre [2], present an in-depth analysis of several Vedic sutras and their application in multiplier design. They discuss the design methodology, implementation details, and optimization techniques used to achieve high-performance multipliers. The performance metrics considered include area utilization, power consumption, and speed. The designs for the 16-bit sutras are implemented using Verilog language and evaluated. Comparative analysis is conducted with existing research work to assess the performance of the proposed sutras for better speed, area and power.

M. Kivi Sona and V. Somasundaram [3], propose a multiplier using Vedic mathematics based on Nikhilam architecture to improve the speed of operation and compares different architectures, including the existing Wallace Tree and Vedic mathematics based on Urdhva Tiriyagbhyam, with the proposed design to evaluate metrics such as area utilization, power consumption, and speed

T. Gupta and J. B. Sharma [4], The authors propose a Han-Carlson adder-based Vedic multiplier architecture that utilizes the Urdhva-Tiryakbhyam sutra from Vedic multiplication and the Han-Carlson adder, known for its high-speed performance. The authors implement a 64x64 bit Vedic multiplier using VHDL and compare the implementation results with conventional Vedic multipliers employing different adders. The results show that the proposed architecture offers improved delay, reduced hardware utilization (LUTs), and lower complexity

N. Kumar M., R. S. Adithyaa, B. Kumar D. and T. Pavithra [5], proposes a 16x16-bit Wallace Tree Multiplier using the Kogge Stone Adder and modified approximate Full Adder for improved performance. Performance analysis considers factors such as speed, area utilization, and power consumption.

A. Raju and S. K. Sa [6], The research focuses on using the Kogge Stone Adder (KSA) as a key component in multiplier architectures. The paper investigates different multiplier designs based on the KSA, exploring their performance characteristics and comparing them to conventional multiplier architectures. The author proposes multipliers utilizing the KSA, which exhibit improved performance in terms of speed and efficiency compared to conventional multiplier architectures.

P. Gulati, H. Yadav and M. K. Taleja [7], present a comparison of the three adders based on several performance metrics. The results obtained from the simulation and analysis provide insights into the performance trade-offs and advantages of using each adder. The paper contributes to the understanding of the performance characteristics of different adders in Vedic multiplier designs, which can help guide the selection and implementation of appropriate adders for Vedic multipliers in various applications.

S. Dubey and G. Verma [8], presents a comparison of different 4-bit adders in terms of power consumption, device utilization, and delay. The focus is on assessing the performance of the adders and identifying the adder that provides the best overall results. The Han Carlson Adder (HCA) is the best choice among the 4-bit adders evaluated for power consumption, device utilization, and delay. It operates based on parallel prefix computation and requires less area than the RCA, making it an efficient and effective solution for achieving high-quality results with reduced resource utilization.

R. Shanmuganathan and K. Brindhadevi [9], This study compares three different types of multiplier architectures using VHDL code and low power design methods. The Wallace tree multiplier is chosen for its high-speed operation. The Baugh Wooley multiplier is used for signed multiplication with reduced delay. The array multiplier is considered for its impact on delay, with less significance on area. This study contributes to the understanding of various multiplier architectures and their suitability for different application scenarios.

R. Anjana, B. Abishna, M. S. Harshitha, E. Abhishek, V. Ravichandra and M. S. Suma [10], present a novel approach to designing a Vedic multiplier by incorporating a Kogge-Stone adder. The results demonstrate that the Vedic multiplier with the Kogge-Stone adder outperforms the conventional multipliers on the metrices of speed and area, contributing to faster computation and improved performance. The experimental analysis reveals that the proposed Vedic multiplier achieves a balance between speed and area efficiency, making it suitable for various applications, including digital signal processing.

A. Sundhar, S. D. Tharshini, G. Priyanka, S. Ragul and C. Saranya [11], proposes a 16x16 multiplier architecture uses a 15-4 compressor and Kogge-Stone adder to enhance its performance. Results indicate that the proposed multiplier architecture using the 15-4 compressor and Kogge-Stone adder outperforms the multiplier architecture with a parallel adder in terms of speed. The Kogge-Stone adder contributes to faster computation, making the proposed architecture more efficient. These findings suggest potential applications in fields such as video and image processing.

M. N. Chandrashekara and S. Rohith [12], presents a promising approach to designing efficient multipliers using Vedic mathematics and the Modified Carry Save Adder. The objective is to develop a multiplier that can compute the product of two 8-bit binary numbers with high speed and efficiency. The results demonstrate that the Vedic multiplier utilizing the Urdhva Tiryagbhyam sutra with MCSA outperforms other multipliers in terms of speed

## **CHAPTER 3**

# CHARACTERISTIC COMPARISON FOR DIFFERENT ADDERS

The adder is an essential part of digital circuits and is used for a variety of tasks, from simple computations to complicated ones, including basic arithmetic. It is crucial in many areas, including computer architecture, signal processing, cryptography, , because it enables effective data manipulation, processing, and arithmetic operations.

The performance of the multiplier depends on the speed and efficiency of the adder used in the design. Faster and more efficient adders can significantly improve the performance of the multiplier and reduce the overall delay in the computation. Therefore, the design and implementation of the adder are crucial to achieving high-speed and highperformance multipliers. A parallel prefix adder (PPA) is a type of adder circuit that is used to perform fast and efficient addition of binary numbers.. Careful consideration and selection of the appropriate adder architecture are crucial for achieving high-performance multipliers.

#### This chapter is organized in five sections:

- The basic adder Ripple Carry adder, which is defined in section 3.1.

- A discussion of the parallel prefix adder and its kinds is covered in Section 3.2.

- The implementation and analysis of Kogge Stone adder and Han Carlson adder are discussed in Section 3.3 and 3.4 respectively.

- Section 3.5 of the chapter discusses comparisons and the results

#### **3.1 Ripple Carry Adder**

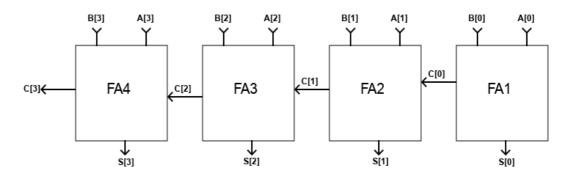

A ripple carry adder is a fundamental adder to add binary digits. The carry bit ripples or propagates through the stages of the adder, hence the name "ripple carry" adder. A chain of numerous full adders joined together forms the ripple carry adder. A carry-in bit, the matching bits from the numbers being added, two input bits, and the whole adder are all required. The carry from each full adder is fed into the carry-in for the next full adder in the chain as shown in Fig.3.1

Fig. 3.1 Block diagram of Ripple Carry adder

#### **3.1 Parallel Prefix Adders**

Parallel Prefix Adders (PPA) are fast adders that are derived from Carry Look Ahead Adders. In this paper, PPA is used because it can perform parallel addition which means the partial additions can be computed parallel resulting in a significant reduction in the addition time [6]. This is in contrast with the traditional Ripple Carry Adder which performs Sequential addition and the consequent stage has to wait for the previous stage to complete.

Each stage in the parallel prefix adder performs parallel operations on different subsets of the input bits. The final carry-out is then calculated by prefixing the carry-out bits from each stage. The parallel prefix adder works by performing parallel computations within each group to calculate the carries. These computed carries are then passed to the next group, where they are combined with the corresponding inputs to compute the next level of carries. This process continues until the final carry-out bits are obtained.

Parallel Prefix Adder typically consists of 6 stages:

- Input preparation: The binary numbers to be performed operation are spilt into groups of bits. Each groups have a subset of input number.

- Perform parallel computation: To calculate the carries inside each group, parallel computations are used. Depending on the particular parallel prefix adder architecture, several methods, such as AND gates, XOR gates, and other logic circuits, can be used to do the carry calculation.

- Carry Propagation: To calculate the carries inside each group, parallel computations are used. Depending on the particular parallel prefix adder architecture, several methods, such as AND gates, OR gates, and other logic circuits, can be used to do the carry calculation.

- Carry Combination: The final carry-out bits are created by prefixing the carry bits from each group. This entails creating a precise pattern, frequently like a tree, connecting the carry outputs of each group to the inputs of the higher-order groups.

- Generate Sum bits: The input bits and the carry bits are combined in a straightforward XOR procedure to determine the sum bits. For each bit position, this can be done in parallel.

- Final Carry Out: The most significant carry-out piece of the addition operation is represented by the carry-out from the highest-order group.

The two main parallel prefix adders are explored in this chapter. Kogge Stone adder and Han Carlson adder are most efficient and faster adders in parallel prefix adder.

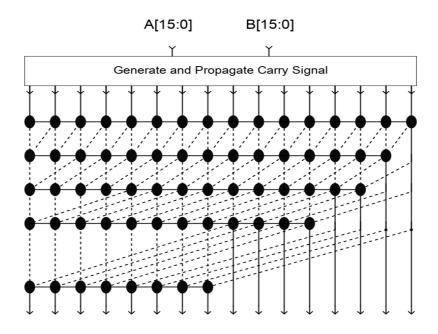

#### 3.3 Kogge Stone Adder

The Kogge-Stone adder is a type of parallel prefix adder that efficiently computes the carry bits in parallel and combines them in a prefix manner to perform fast addition of binary numbers. In contrast to ripple carry adders, the Kogge-Stone adder uses parallelism and effective carry propagation to produce quicker addition. By parallelizing carry computations and reducing the ripple carry effect, it decreases the critical path delay.

Kogge Stone adder can broadly split into three stages. The first stage is the processing stage, in which the propagate and generate signals are calculated using each bit of the pair-bit signal.

$$P_i = A_i \text{ xor } B_i$$

$$G_i = A_i \text{ and } B_i$$

The second step generates carries by utilizing each bit individually and in parallel. This is utilized for carry generation and carries propagation in the intermediate stage logically and is referred to as the carry generation stage.

$$CP_{i:j} = P_{i:k+1} \text{ and } P_{k:j}$$

CGi:j = G<sub>i:k+1</sub> or ( P<sub>i:k+1</sub> and G<sub>k:j</sub> )

In last step, sum and carry are calculated and this step is known as post processing stage.

$$Si = P_i \text{ xor } Ci-1$$

$C_{i-1} = (P_i \text{ and } C_i) \text{ or } G_i$

Fig. 3.2 Graphical Representation of 16-bit Kogge Stone adder

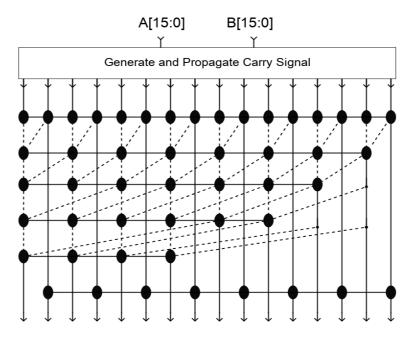

#### 3.4 Han Carlson Adder

Han Carlson adder is similar to Kogge Stone adder. The adder has the benefit of using fewer cells and being shorter. To calculate the odd numbered prefixes, the Han-Carlson adder starts with a Brent-Kung stage, moves through Kogge-Stone stages, and finishes with another Brent-Kung stage. As a result, the complexity is reduced at the cost of an extra stage merging the carry. Due to fewer cells, the speed is fastest in all parallel prefix adder. The graphical representation of the Han Carlson adder is shown in Fig.3.3.

Fig. 3.3 Graphical Representation of 16-bit Han Carlson adder

### 3.5 Simulation and Synthesis Results

In this section a comparative analysis of 32-bits Ripple Carry Adder, Kogge Stone Adder and Han Carlson Adder are performed. The factors that are considered for comparison are area and delay. Through this detailed analysis, we aim to provide insights into the performance characteristics of different adders and assist in making informed design choices for multiplier implementations.

| Dev                               | ice Utilization Summary (esl | tima | ited values) |             |  |

|-----------------------------------|------------------------------|------|--------------|-------------|--|

| Logic Utilization                 | Used                         |      | Available    | Utilization |  |

| Number of Slice LUTs              |                              | 49   | 92152        |             |  |

| Number of fully used LUT-FF pairs |                              | 0    | 49           |             |  |

| Number of bonded IOBs             |                              | 98   | 396          |             |  |

FI

0%

0%

24%

#### 3.5.1 Ripple Carry Adder

Fig 3.4 : Device utilization of Ripple Carry Adder

Fig 3.5 : Schematic of Ripple Carry Adder

|              |        | Gate     | Net   |                                                  |

|--------------|--------|----------|-------|--------------------------------------------------|

| Cell:in->out | fanout | Delay    | Delay | Logical Name (Net Name)                          |

|              |        |          |       |                                                  |

| IBUF:I->0    |        |          |       | a_1_IBUF (a_1_IBUF)                              |

| LUT5:I0->0   | 3      | 0.203    | 0.755 | F2/carry1 (c1)                                   |

| LUT5:I3->0   | 3      |          | 0.755 | F4/carry1 (c3)                                   |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F6/carry1 (c5)                                   |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F8/carry1 (c7)                                   |

| LUT3:I1->0   | 2      | 0.203    | 0.721 | F9/carry1 (c8)                                   |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F11/carry1 (c10)                                 |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F13/carry1 (c12)                                 |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F15/carry1 (c14)                                 |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F17/carry1 (c16)                                 |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F19/carry1 (c18)                                 |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F21/carry1 (c20)                                 |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F23/carry1 (c22)                                 |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F25/carry1 (c24)                                 |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F27/carry1 (c26)                                 |

| LUT5:I3->0   | 3      | 0.203    | 0.755 | F29/carry1 (c28)                                 |

| LUT5:I3->0   | 2      | 0.203    | 0.721 | F31/carry1 (c30)                                 |

| LUT3:I1->0   | 1      | 0.203    | 0.579 | F32/carry1 (carry_OBUF)                          |

| OBUF:I->0    |        | 2.571    |       | carry_OBUF (carry)                               |

| Total        |        | 20.800ns |       | ns logic, 13.556ns route)<br>logic, 65.2% route) |

Fig 3.7: Simulation Result of Ripple Carry Adder

### 3.5.2 Kogge Stone Adder

| Device Utilization Summary (estimated values) |      |           |             |  |

|-----------------------------------------------|------|-----------|-------------|--|

| Logic Utilization                             | Used | Available | Utilization |  |

| Number of Slice LUTs                          | 139  | 92152     | 0%          |  |

| Number of fully used LUT-FF pairs             | 0    | 139       | 0%          |  |

| Number of bonded IOBs                         | 98   | 396       | 24%         |  |

Fig 3.8: Synthesis Result of Kogge Stone Adder

Fig 3.9: : Schematic of Kogge Stone Adder

| Cell:in->out | fanout | Gate<br>Delay | Delay | Logical Name (Net Name)                         |

|--------------|--------|---------------|-------|-------------------------------------------------|

| IBUF:I->0    | 5      | 1.222         | 0.819 | a 2 IBUF (a 2 IBUF)                             |

| LUT2:I0->0   | 2      | 0.203         | 0.981 | Mxor p2 xo<0>1 (p2)                             |

| LUT6:I0->0   | 4      | 0.203         | 0.912 | c2 (c2)                                         |

| LUT5:I2->0   | 3      | 0.205         | 0.879 | c6 (c6)                                         |

| LUT6:I3->0   | 2      | 0.205         | 0.721 | c141 (c141)                                     |

| LUT4:I2->0   | 2      | 0.203         | 0.845 | c142 (c14)                                      |

| LUT6:I3->0   | 2      | 0.205         | 0.721 | c221 (c221)                                     |

| LUT4:I2->0   | 1      | 0.203         | 0.808 | c222 (c22)                                      |

| LUT6:I3->0   | 1      | 0.205         | 0.580 | c303_SW0 (N14)                                  |

| LUT6:15->0   | 1      | 0.205         | 0.580 | c303 (c30)                                      |

| LUT3:12->0   | 1      | 0.205         | 0.579 | Mxor_sum<31>_xo<0>1 (sum_31_OBUF)               |

| OBUF:I->O    |        | 2.571         |       | sum_31_OBUF (sum<31>)                           |

| Total        |        | 14.260ns      |       | ns logic, 8.425ns route)<br>logic, 59.1% route) |

Fig 3.10: Delay Report of Kogge Stone Adder

Fig 3.11: : Simulation Result of Kogge Stone Adder

### 3.5.3 Han Carlson Adder

| Device Utilization Summary (estimated values) |      |           |             |  |  |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|--|--|

| Logic Utilization                             | Used | Available | Utilization |  |  |  |  |

| Number of Slice LUTs                          | 105  | 2400      | 4%          |  |  |  |  |

| Number of fully used LUT-FF pairs             | 0    | 105       | 0%          |  |  |  |  |

| Number of bonded IOBs                         | 98   | 102       | 96%         |  |  |  |  |

Fig 3.12 : Device utilization of Han Carlson Adder

Fig 3.13 : Schematic of Han Carlson Adder

| Cell:in->out | fanout | Gate<br>Delay | Net<br>Delay | Logical Name (Net Name)                         |

|--------------|--------|---------------|--------------|-------------------------------------------------|

| IBUF:I->0    | 3      | 1.222         | 0.898        | a 5 IBUF (a 5 IBUF)                             |

| LUT4:I0->0   | 3      | 0.203         | 0.995        | p4 51 (p4 5)                                    |

| LUT5:I0->0   | 3      | 0.203         | 0.879        | p4 71 (p4 7)                                    |

| LUT3:I0->0   | 1      | 0.205         | 0.924        | g0_73 (g0_7)                                    |

| LUT6:I1->0   | 3      | 0.203         | 0.879        | c111 (c11)                                      |

| LUT5:12->0   | 3      | 0.205         | 0.879        | c191 (c19)                                      |

| LUT6:I3->0   | 2      | 0.205         | 0.845        | c271 (c27)                                      |

| LUT3:I0->0   | 1      | 0.205         | 0.579        | Mxor sum<28> xo<0>1 (sum 28 OBUF)               |

| OBUF:I->0    |        | 2.571         |              | sum_28_OBUF (sum<28>)                           |

| Total        |        | 12.101ns      | •            | ns logic, 6.879ns route)<br>logic, 56.8% route) |

Fig 3.14 : Delay Report of Han Carlson Adder

Fig 3.15: Simulation Result of Han Carlson Adder

Table 3.1 shows Comparative Analysis of Delay and Area of Adders

| Adders             | Delay(ns) | Area(LUT) |

|--------------------|-----------|-----------|

| Ripple Carry Adder | 20.8      | 49        |

| Kogge Stone Adder  | 14.26     | 139       |

| Han Carlson Adder  | 12.101    | 105       |

### **3.6 Important Outcomes:**

In this chapter, the design and analyses of several adders are carried out and compared to determine the optimal option for the best performance.

- The Ripple Carry, Kogge Stone and Han Carlson adder are design and simulated.

- Delay and Area have been calculated and plotted.

- Performing addition using Han Carlson adder can reduce delay up to 40%.

- In terms of area, the ripple carry adder utilized space better than the parallel prefix adder

# **CHAPTER 4**

# DESIGN AND ANALYSIS OF MULTIPLIER USING DIFFERENT PARALLEL PREFIX ADDER

Multiplication operation is an essential component in a processing unit that is widely employed in numerous disciplines, including engineering, physics, computer science, and many others. Numerous multiplication operations are required by many algorithms. The effectiveness and speed of these operations directly affect the system's overall performance.

Improving the performance of a multiplier can bring several benefits, such as:

- Faster Calculation: The time needed to perform multiplication operations can be decreased by optimizing a multiplier, which could result in quicker calculation times.

- Reduced power consumption: Reduced power consumption from faster computing is also beneficial for battery-operated gadgets and low-power systems.

- Increased accuracy: In many applications, like digital signal processing and image processing, higher levels of accuracy are required, and high-performance multipliers are able to perform multiplication operations with these levels of accuracy.

- Improved system throughput: The throughput of the entire system can be boosted by optimizing the performance of a multiplier, which is crucial in highperformance computing systems.

In this chapter, we will discuss different multipliers and how to improve their performance by using a faster adder.

The following is the arrangement of this chapter:

- Efficient Multiplier to be designed and the implementation of Wallace Tree and Vedic Multiplier is described in Section 4.1.

- In section 4.2, simulated and synthesized results are presented,

- Performance comparison of the implemented Multipliers in terms of Delay and Area discussed in section 4.3.

#### 4.1 Multiplier

Wallace tree multiplier and the Vedic Urdhva Tiryakbhyam Multiplier (UTM) are two fastest multipliers used in digital circuit. The Wallace tree multiplier is based on the Wallace tree algorithm, a quick multiplication method that minimizes the number of partial products needed to compute the final result. The Vedic UTM, on the other hand, is based on prehistoric Indian mathematics systems that use particular formulas and procedures to execute multiplication. It utilizes various sutras and sub-sutras to simplify the process by breaking it into smaller steps.

For and efficient multiplication, it is important to increase the performance of the adders involved. A series of additions are required for multiplication, and the pace at which these additions are completed directly affects the total time required for multiplication. The speed of the adder becomes significant when multiplying huge numbers or carrying out multiplication operations in high-performance computing systems. In this chapter, all the adders that were discussed in the previous chapter are used to improve the performance of multipliers. By using the faster adder in the multiplier, we can improve throughput, reduce execution time, enhance computational efficiency, and impact complex operations.

#### 4.1.1 Wallace Tree Mutliplier

The Wallace tree multiplier is based on the concept of 'tree reduction," which involves decreasing the number of partial products that must be combined to create the final product. This algorithm allows for efficient carry propagation in parallel processing. It reduces the overall area footprint of the circuit by minimizing the number of logic gates needed. It continues to be widely utilized in a range of applications where efficient and fast multiplication operations are essential.

The steps involved in a Wallace tree multiplier's operation are as follows:

- Partial products generation: A series of AND gates is used to multiply the binary digits of the multiplicand by the binary digits of the multiplier. The resulting partial products are arranged in columns.

- Reduction of partial products: To create a set of sums and carries, the partial products are reduced using a succession of half-adders and full-adders

- Final Addition: A succession of full adders is used to condense the Wallace tree into a single total.

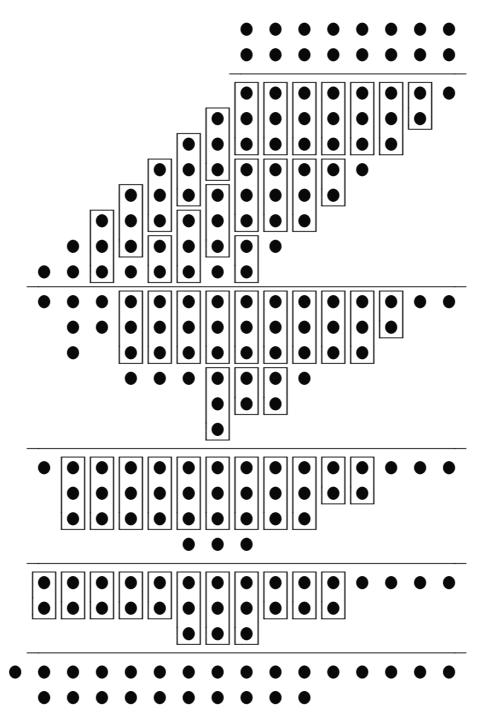

Overall, utilizing digital circuits, the Wallace tree multiplier is a very effective approach to multiplying two binary values. The graphical representation of 8-bits Wallace tree multiplier shows in Fig.4.1

Fig. 4.1 Graphical Representation Of 8X8 bit Wallace Tree Multiplier

The Wallace Tree Multiplier is constructed by generating partial products where both the input numbers are multiplied by passing through AND gates. Further reduction of the partial products is carried out by adding them using half adders and full adders. This

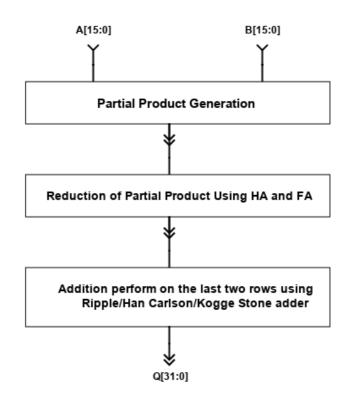

reduction is carried out till the last two rows are received. To achieve a faster addition, the last two rows are added using Kogge Stone adder and Han Carlson Adder (discussed in previous chapter). Fig.4.2 depicts the flow diagram for generating the Wallace Tree Multiplier.

Fig 4.2. Flow diagram of Wallace Tree Multiplier

The variation in performance of the Wallace Tree multiplier due to changes in the adder will be discussed in Section 4.3.

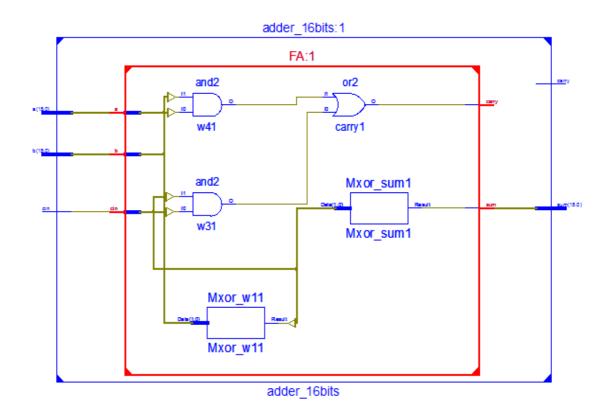

#### 4.1.2 Urdhva-Tiryakbhyam Vedic Multiplier

The Vedic multiplier is a sort of multiplier derived from the Vedic mathematics of ancient India. It offers a different way to carry out multiplication operations using particular formulas and methods. Comparing the Vedic multiplier to conventional multiplication algorithms, there are a number of benefits, including simplicity, speed, and efficiency. To make multiplication easier, it applies a variety of sutras (formulas) and subsutras (corollaries) from Vedic mathematics. It is one of the most used and fastest sutras in Vedic mathematics. According to the sutra, there is a quick and easy method for multiplying two-digit numbers that entails multiplying the vertical and crosswise components and adding the results.

The basic steps of the Vedic multiplier algorithm for multiplication are as follows:

- Depending on place values, divide the multiplicand and multiplier into their appropriate halves.

- Perform cross-multiplication between the corresponding parts of the multiplicand and the multiplier. In order to do this, numbers must be multiplied both vertically and diagonally, and the partial products must be arranged in a particular way.

- Vertical additions are used to add up the cross-multiplication step's partial products.

- Any necessary carries from each vertical addition are carried forward.

- The final output is created by combining the results.

Given below is an example to illustrate multiplication:

Multiply A1A0 by B1B0

- Multiply the rightmost vertical terms A0 and B0. Write the output A0B0 on the rightmost part of the answer

- Multiply the leftmost vertical terms A1 and B1. Write the output A1B1 on the leftmost part of the answer

- Then multiply the cross-wise terms i.e.A1B0 and A0B1. Add the two results (A1B0+A0B1). If the resultant is a 2digit, then the leftmost digit of this term will be carried forward to the left

- The final result is as follows: (A1B1) +(A1B0+A0B1) +(A0B0)

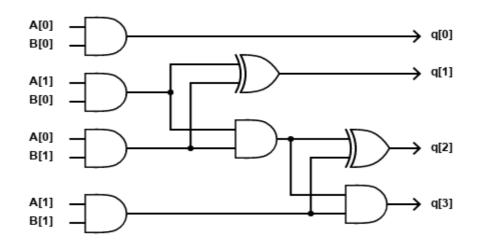

The gate level implementation of 2x2 Vedic Multiplier as shown in Fig.4.3

Fig.4.3: 2x2 Gate level netlist of Vedic Multiplier

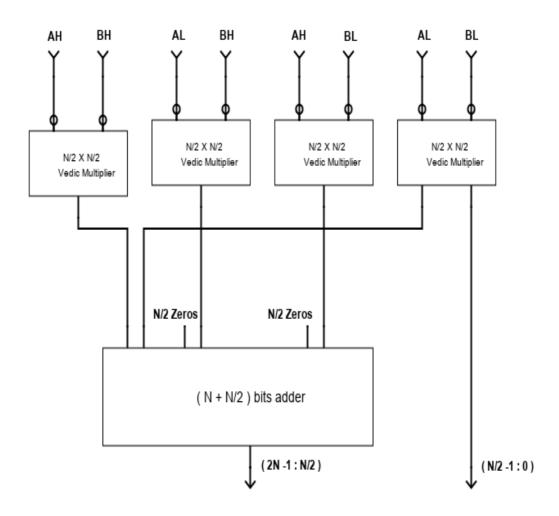

In order to construct an N-bit Vedic Multiplier, the input values A and B are split into two equal parts. These parts are referred to as AH, AL, BH, and BL, representing the Most Significant Bits (MSB) and Least Significant Bits (LSB) respectively. This division allows the creation of an N x N size Vedic multiplier, as depicted in Figure 4.4. are utilized as inputs for four Vedic Multipliers, each of size N/2. These outputs are then fed into four additional Vedic Multipliers, this time with a size of N/4. The N/4 size Vedic Multipliers are further split into four Vedic Multipliers of size N/8, following a similar pattern [2]. This continues until the splitting reaches a block size of 2x2, as depicted in the block diagram shown in the figure. Finally, the outputs of the four N/2 x N/2 multipliers are inputted into an adder with (N + N/2) bits.