# A COMPARATIVE ANALYSIS AND DESIGN OF DYNAMIC LATCHED COMPARATORS

#### A PROJECT REPORT

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

# MASTER OF TECHNOLOGY IN VLSI DESIGN AND EMBEDDED SYSTEM

Submitted by:

Mahima Singh Yadav 2K21/VLS/25

Under the supervision of

**Dr. Rajesh Birok**

# **ELECTRONICS AND COMMUNICATION ENGINEERING**

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

MAY, 2023

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

# **CANDIDATE'S DECLARATION**

I, Mahima Singh Yadav Roll No. 2K21/VLS/25, of M.Tech. VLSI Design and Embedded System, hereby declare that the project Dissertation titled "A comparative analysis and design of dynamic latched comparators" which is submitted by me to the Department of Electronics and Communication Engineering, Delhi Technological University, is original and not copied from any source without proper citation. This work has never been the foundation for the awarding of a Degree, Diploma, Associateship, Fellowship, or other similar title or recognition.

Place: Delhi

Date: 31/05/2023

#### MAHIMA SINGH YADAV

ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

# **CERTIFICATE**

I hereby certify that the Project Dissertation titled "A comparative analysis and design of Dynamic Latched Comparators" submitted by Mahima Singh Yadav, Roll No. 2K21/VLS/25 of Department of electronics and Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the student under my supervision. To the best of my knowledge, this work has not been submitted in part or full for any degree or diploma to this University or elsewhere.

Place: Delhi Date: 31/05/2023 DR. RAJESH BIROK SUPERVISOR

# ACKNOWLEDGEMENT

I wish to express my sincere thanks and heartfelt gratitude to **Dr. Rajesh Birok** for his indispensable guidance, valuable time, crucial suggestions, corrections, and encouragement that accounts for the successful completion of this project. He has always been a source of inspiration. We also extend our gratitude towards **Prof. O.P Verma** (HOD ECE) for giving me this opportunity.

I'd also like to express my gratitude to all of the teaching and non-teaching personnel at the Department of Electronics and Communication Engineering, Delhi Technological University for their direct and/or indirect input assistance during the project.

Finally, I'd like to express my gratitude to my family, who has been a continual source of inspiration for me. Not to mention my friends' support in this respect, who were always willing to lend a hand or have a conversation with us.

#### MAHIMA SINGH YADAV

# ABSTRACT

In an attempt to study various comparators, a comparative analysis of different dynamic latch comparators have been performed. The performance of the conventional dynamic latch comparator, Double tail dynamic latch comparator, charge sharing dynamic comparator and modified double tail dynamic latch comparator have been done to display the improvements achieved. Further a new circuit has been proposed displaying the same functionality.

Transient analysis has been observed for each circuit. Effect of delay on circuit's robustness in form of Monte Carlo Simulations has been performed. As the need for low power, high speed comparator's is of utmost importance day by day, the circuits present a vivid picture of their performance.

All the simulations are carried out using Cadence Virtuoso tool with a supply voltage of 1.5V, differential input voltage of 20mv and common mode voltage of 1.2V in 130 nm CMOS technology node at a temperature of 27-degree Celsius.

# CONTENTS

| Candiddate's Declaration                                                                                                                                                               | ii                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Certificate                                                                                                                                                                            | iii                        |

| Acknowledgement                                                                                                                                                                        | iv                         |

| Abstract                                                                                                                                                                               | v                          |

| Contents                                                                                                                                                                               | vi                         |

| List of Figures                                                                                                                                                                        | viii                       |

| List of Tables                                                                                                                                                                         | ix                         |

| List of Symbols, Abbreviations                                                                                                                                                         | Х                          |

| CHAPTER 1 INTRODUCTION                                                                                                                                                                 | 1                          |

| 1.1 Overview                                                                                                                                                                           | 1                          |

| <ul> <li>1.2 Basics of CMOS Comparator <ol> <li>1.2.1 Definition</li> </ol> </li> <li>1.3 Tools Used</li> <li>1.4 Organization of work</li> </ul> <li>CHAPTER 2 LITERATURE SURVEY</li> | 1<br>2<br>3<br>3<br>4      |

| 2.1 Literature Review                                                                                                                                                                  | 4                          |

| CHAPTER 3 COMPARATOR CHARACTERISTICS                                                                                                                                                   | 8                          |

| 3.1 Static Characteristics                                                                                                                                                             | 8                          |

| <ul> <li>3.1.1 Gain</li> <li>3.1.2 Resolution</li> <li>3.1.3 Offset</li> <li>3.1.4 Noise</li> <li>3.1.5 Input Common Mode Range(ICMR)</li> <li>3.2 Dynamic Characteristics</li> </ul>  | 8<br>9<br>9<br>9<br>9<br>9 |

| <ul><li>3.2.1 Propagation Delay</li><li>3.2.2 Slew Rate</li></ul>                                                                                                                      | 10<br>10                   |

| CHAPTER 4 METHODOLOGY AND IMPLEMENTATION                                                                                                                                               |                            |

| 4.1 Architecture of Conventional Dynamic Latched Comparator                                                                                                                            | 12                         |

| 4.2 Architecture of Double Tail Dynamic Latched Comparator                                                                                                                             | 13                         |

| 4.3 Architecture of Modified Double Tail Dynamic Latched Comparator                                                                                                                    | 14                         |

| 4.4 Architecture of Shared Charge Logic Dynamic Latched Comparator                                                                                                                     | 16                         |

| 4.5 Architecture of Proposed Dynamic Latched Comparator | 18       |

|---------------------------------------------------------|----------|

| CHAPTER 5 SIMULATION RESULTS AND ANALYSIS               | 17       |

| 5.1 Specifications                                      | 20       |

| 5.2 Transient Analysis                                  | 20       |

| 5.3 Power Consumption                                   | 26       |

| 5.4 Delay                                               | 29       |

| 5.5 Power Delay Product                                 | 29       |

| 5.6 Monte Carlo Simulations                             | 30       |

| 5.7 Histogram for Delay                                 | 35       |

| CHAPTER 6 CONCLUSION AND FUTURE SCOPE<br>REFERENCES     | 40<br>41 |

| PUBLICATION DETAILS                                     | 46       |

| PROOF OF INDEXING                                       | 47       |

| PROOF OF ACCEPTANCE                                     | 48       |

| PLAGIARISM REPORT                                       | 49       |

# LIST OF FIGURES

- Fig 1.1 Schematic of Comparator

- Fig 1.2 Ideal Voltage transfer characteristics of comparator

- Fig 2.1 STDLC

- Fig 2.2 DTDLC

- Fig 2.3 MDTDLC

- Fig 2.4 SCDLC

- Fig 3.1 First-Order Model of Comparator

- Fig 3.2 Comparator's propagation Delay

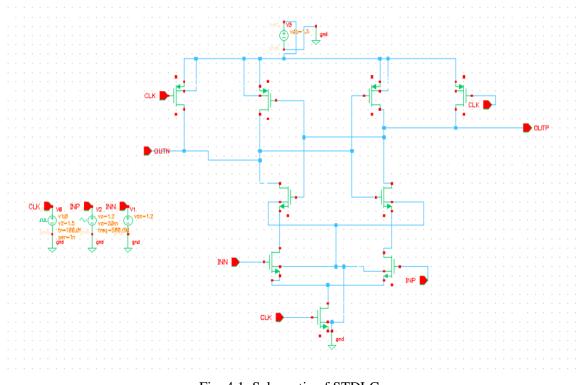

- Fig 4.1 Schematic of STDLC

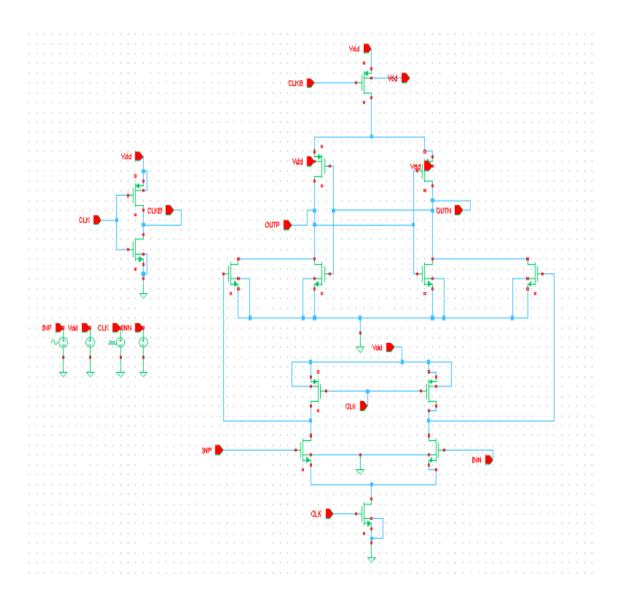

- Fig 4.2 Schematic of DTDLC

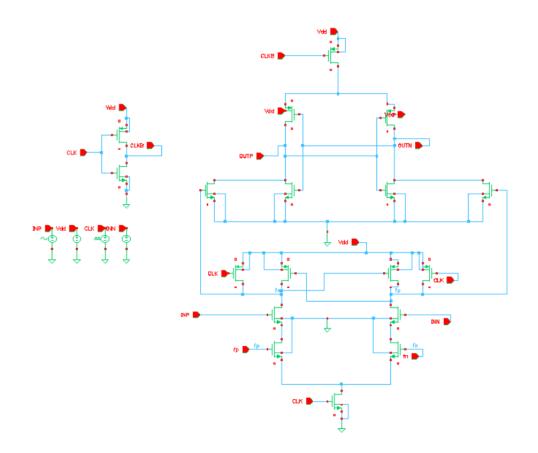

- Fig 4.3 Schematic of MDTDLC

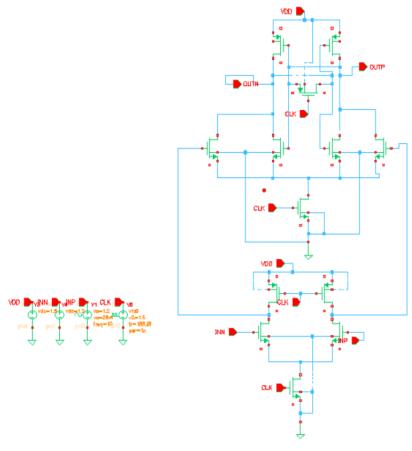

- Fig 4.4 Schematic of SCDLC

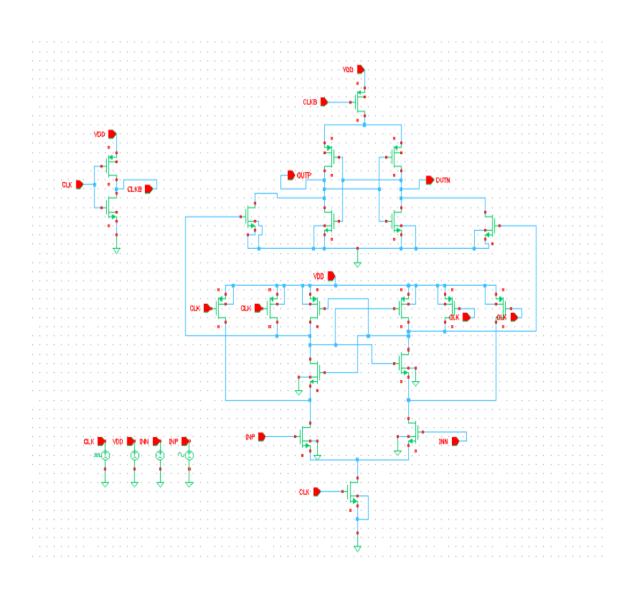

- Fig 4.5 Schematic of PDLC

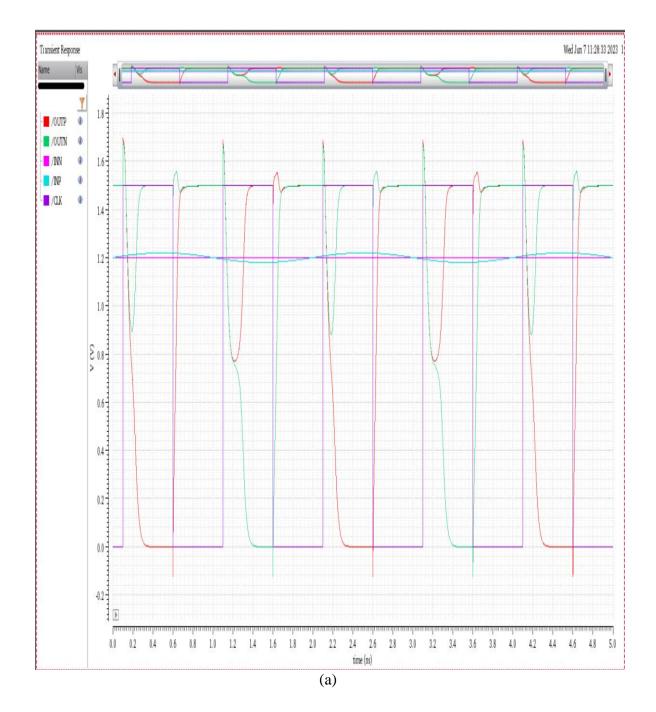

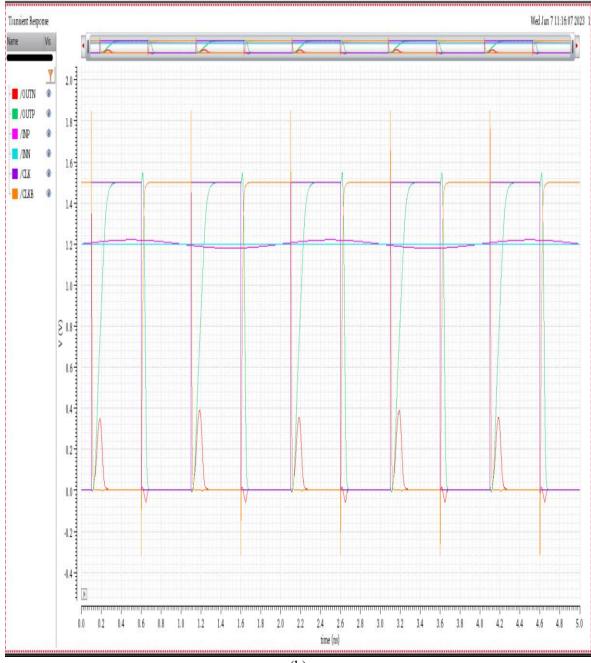

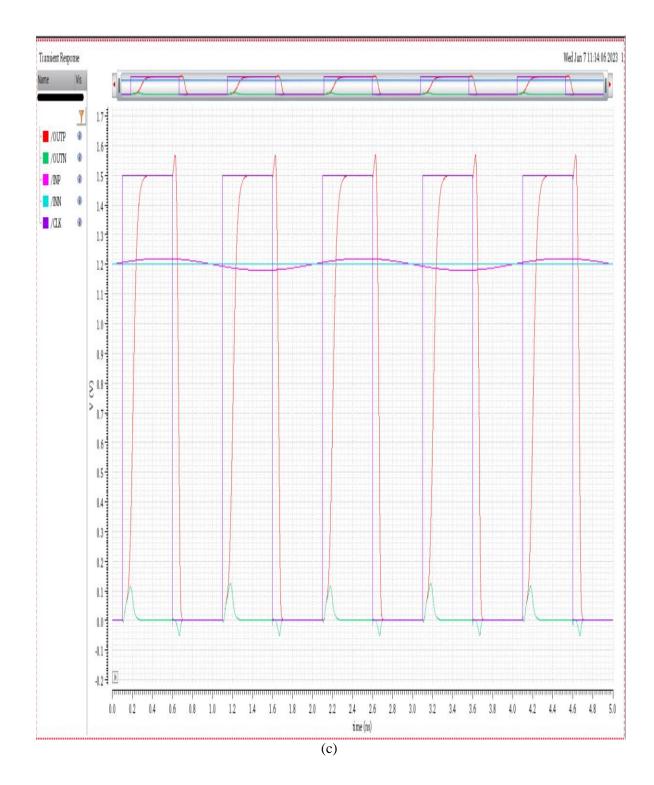

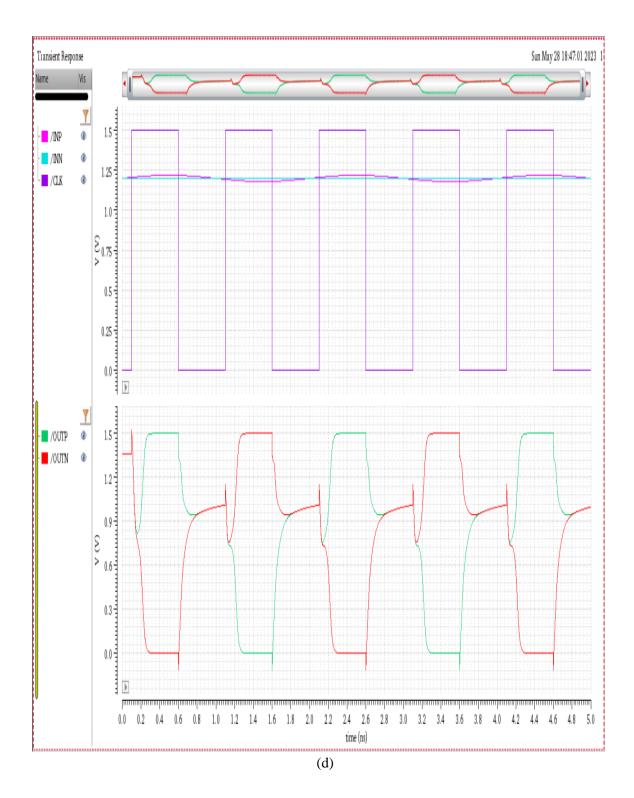

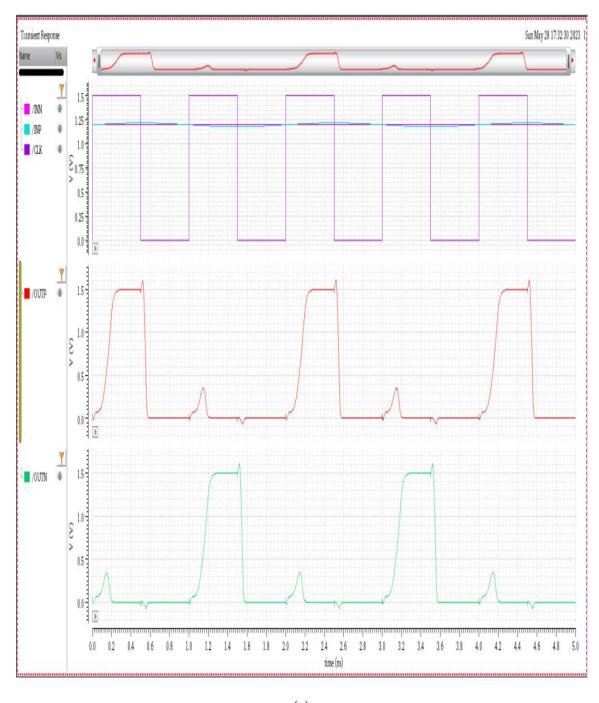

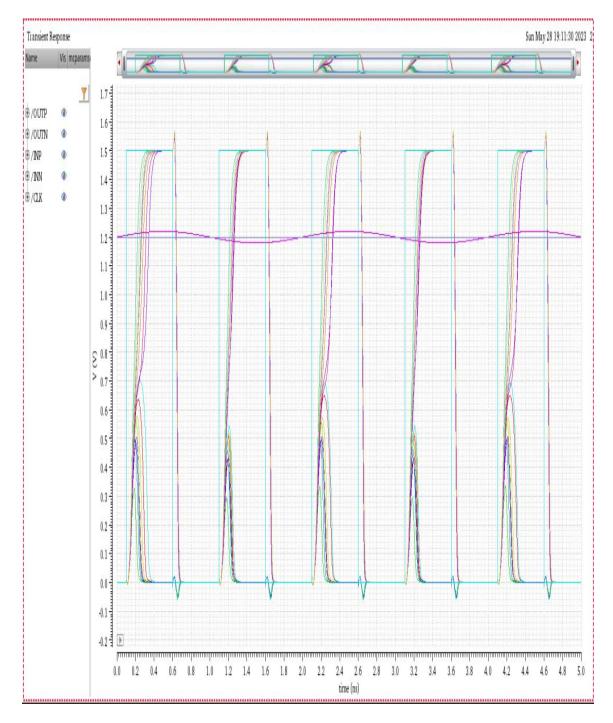

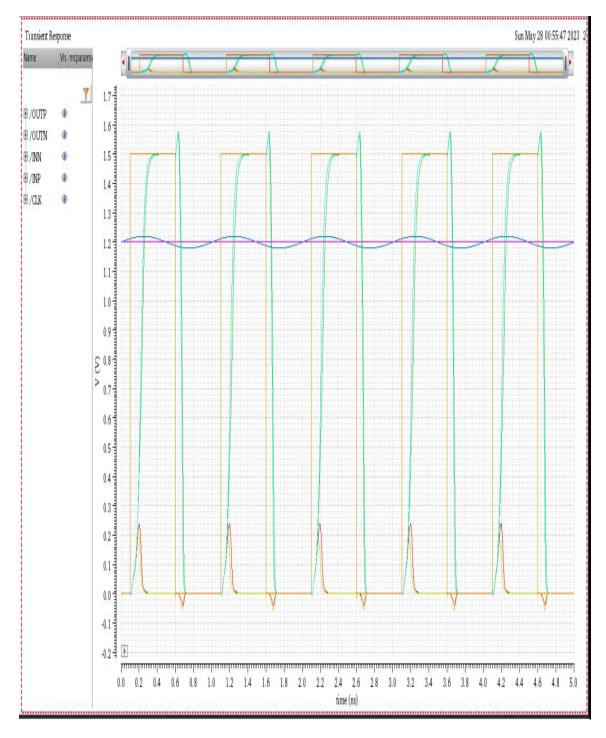

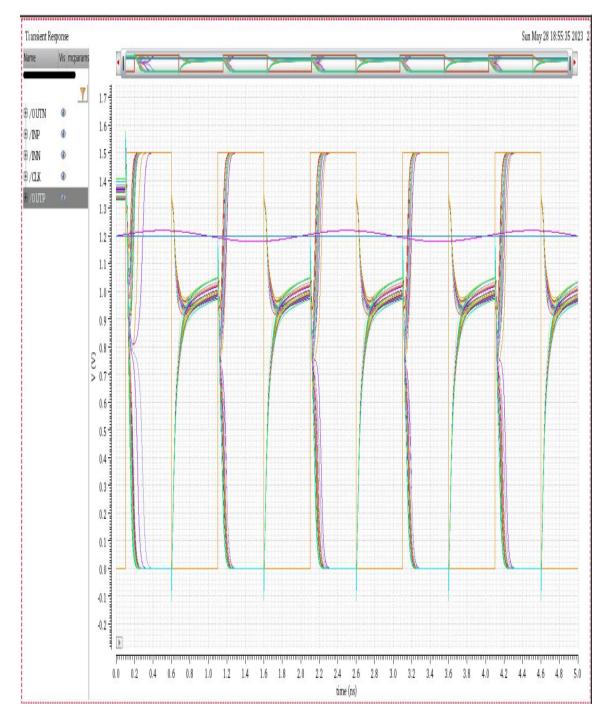

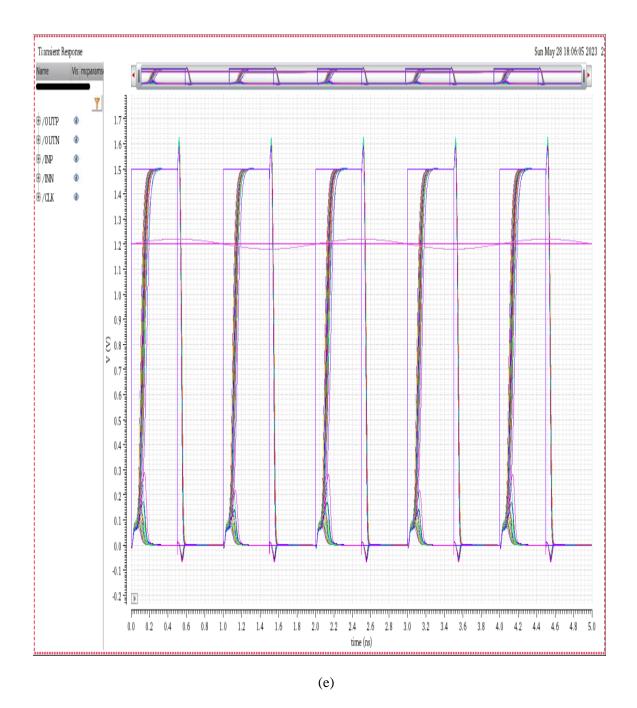

Fig 5.1 Transient analysis of (a)STDLC (b) DTDLC (c) MDTDLC (d) SCDLC (e) PDLC

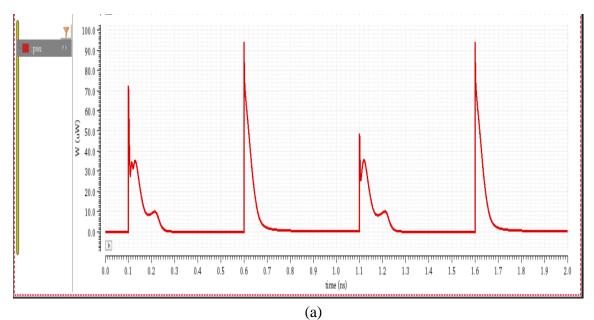

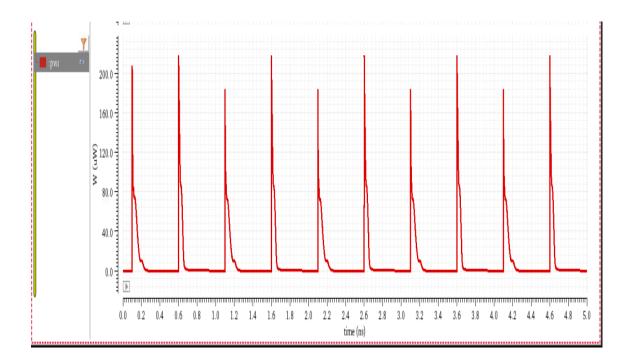

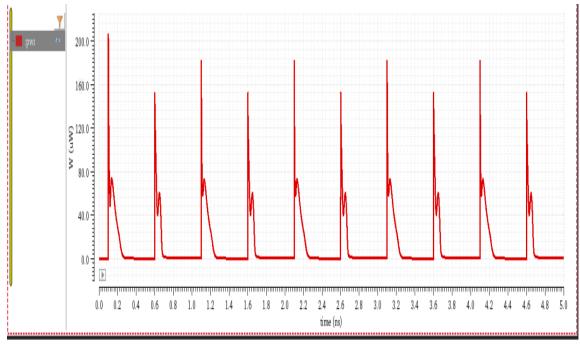

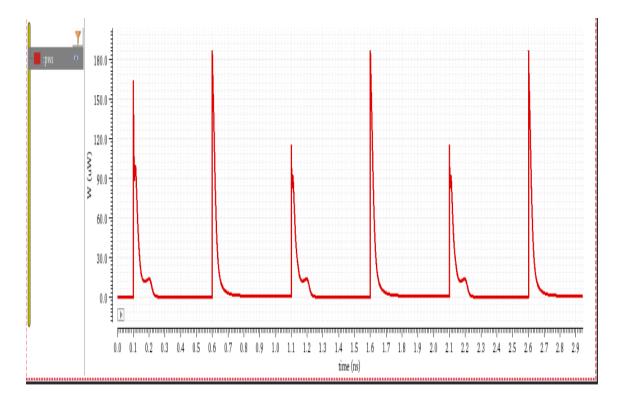

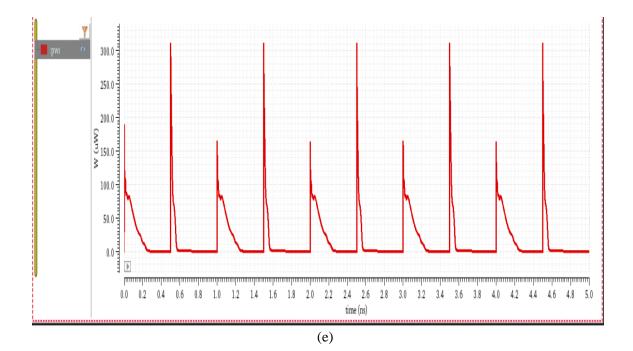

- Fig 5.2 Power of: (a) STDLC (b) DTDLC (c) MDTDLC (d) SCDLC (e) PDLC

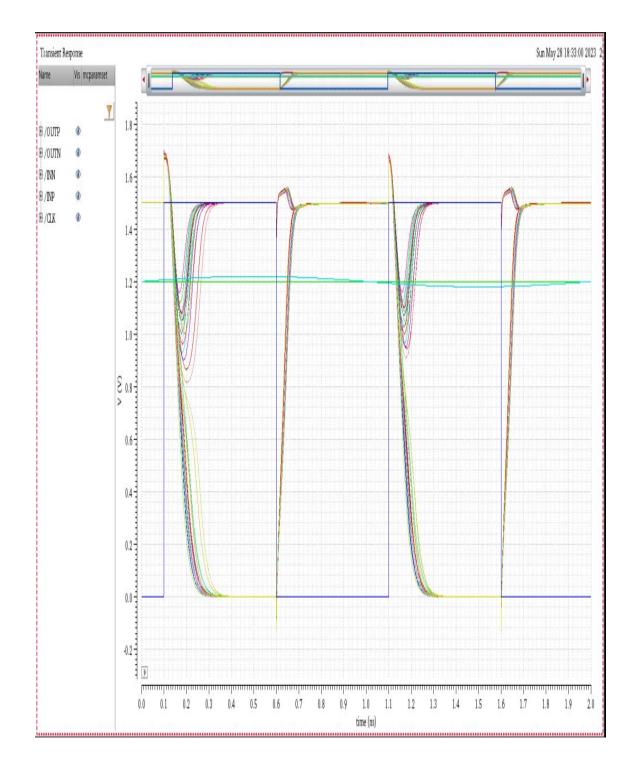

- Fig5.3 Monte Carlo Simulations of (a) STDLC(b)DTDLC (c)MDTDLC

- (d)SCDLC(e)PDLC

Fig 5.4 Histogram for Power for: (a) STDLC, (b) DTDLC, (c) MDTDLC (d) SCDLC (e)PDLC

# **List of Tables**

Table 5.1: Power Comparison

Table 5.2: Delay Comparison

Table 5.3: Power Delay Product (PDP) comparison

Table 5.4: Variation of parameters for different architecture

# List of Symbols, Abbreviations

- NMOS: N Channel Metal Oxide Semiconductor

- PMOS; P Channel Metal Oxide Semiconductor

- CMOS: Complementary Metal Oxide Semiconductor

- STDLC: Single Tail Dynamic Latched Comparator

- DTDLC: Double Tail Dynamic Latched Comparator

- MDTDLC: Modified Double Tail Dynamic Latched Comparator

- SCDLC: Shared Charge Dynamic Latched Comparator

- PDLC: Proposed Dynamic Latched Comparator

- PDP: Power Delay Product

- ADC: Analog to digital Converter

- IC: Integrated Circuit

# CHAPTER 1 INTRODUCTION

## **1.1 Overview**

The need for portable battery-operated gadgets is rising in the modern age, and low voltage methods for high-speed purposes are taking a significant hit. Typical portable electronics devices, such as wireless communication systems, cell-operated healthcare gadgets, etc., are being developed with the rapid rise of semiconductor technology. One of the most crucial elements in any of these applications is battery life. Low power, low voltages are therefore extremely necessary. By adopting a wider oxide film or greater supply levels, IC costs can be decreased as well. Low voltage & low power comparator are often highly critical and necessary in integrated circuits where ADC or DAC plays a vital role. The goal application's execution, which depends on the construction modelling and kind of it, is significantly impacted by the comparator. The resolution and efficiency of the Analog to digital converter are directly impacted by the comparison device's input signal band; associated input offset value, and latency. As we focus on the process variances, lower feature size techniques, the device's efficiency level will be substantially impacted. Comparators are categorised into many types depending on their behaviour, usefulness, such as continuous or discrete time comparators, voltage based or current-based comparators. Detection of signals are other uses of comparators.

#### **1.2 Basics of CMOS Comparator**

After op - amps, comparators are arguably the most commonly employed electrical circuits globally. Comparators are often employed in high quantities in analogue to digital converters since they are known as 1-bit ADC. To begin the A/D transition, the input must initially be sampled. The digital version of the analogue input is then calculated using the sampled signal and a set of comparators. The comparator's judgement reaction time governs how quickly it can convert data. In addition, comparators are used for a variety of different purposes, including as data transmission, zero-crossing sensors, peak

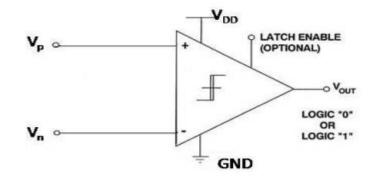

detection systems, switching voltage controllers. A CMOS comparator's fundamental capabilities include determining if a signal is larger or lesser than 0 as well as comparing an input signal to a given signal and producing binary output as a consequence of the comparison. Figure 1.1 depicts the representation schematically and the fundamental functioning of a voltage comparator, which may be viewed as a circuitry for making decisions..

#### **1.2.1 Definition**

A circuitry that generates a binary output depending on comparison of an analog signal with an other analog signal or else reference voltage is known as comparator.

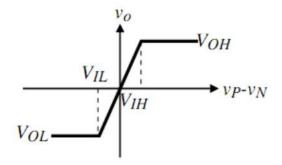

Fig. 1.1: Comparator Schematic [14]

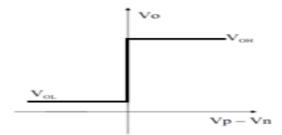

Fig 1.2: Ideal voltage transfer characteristic of comparator [14]

The design representation for the comparator is shown in Figure 1.1, and its ideal transfer properties are shown in Figure 1.2. Vn is reference voltage (fixed Voltage level) supplied to the comparator's negative end, and the input signal (pulse voltage) sent to the comparator's positive input end is denoted by Vp. So, when Vp, the comparator's input, is at a voltage

higher than Vn, the reference value, the comparator's result is a logic high, but if Vp is at a voltage lower than that of Vn, the comparator's result is a logic low.

$\label{eq:case_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_state_s$

## **1.3 TOOLS USED**

Tools used for carrying out the project are Cadence Virtuoso . Cadence Virtuoso is used for constructing the schematics and simulating them to observe their characteristics.

#### **1.4 ORGANIZATION OF WORK**

The description of how the work was structured during the project's accomplishment has been demonstrated:

In this report, a dynamic comparator is compared, and the results indicate decreased power usage and delay.

The review of literature and list of different comparators are presented in **Chapter 2**. The comparator's characteristics and features are described in **Chapter 3**. In **Chapter 4**, the comparators are analysed, and their functionality is explained. The simulation based observations of the transients, and result deduced are presented pictographically in **Chapter 5**. The related conclusion and future plan for the project are covered in **Chapter 6**

# **CHAPTER 2**

## LITERATURE SURVEY

#### **2.1 LITERATURE REVIEW**

Researchers have developed an analog comparator over the past few decades utilising some great ideas. Jeon and Kim have helped with the creation of a dynamic latch comparator [3]. It can decrease hysteresis response, power usage, and latch offset value & delay.

#### [A] Conventional Dynamic Latch comparator:

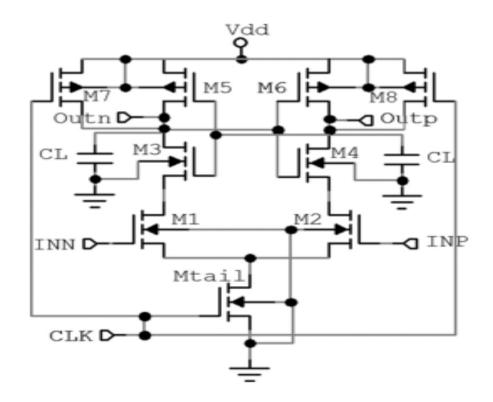

Figure 2.1 shows the traditional dynamic comparator [7]. It was originally brought out by Kobayashi, Nogami, and others. The dynamic latch comparator recreates the input value into a full fledged digital level output signal via a positive feedback technique [1]. Since it is a clock regeneration comparator, high-speed ADC frequently uses this.

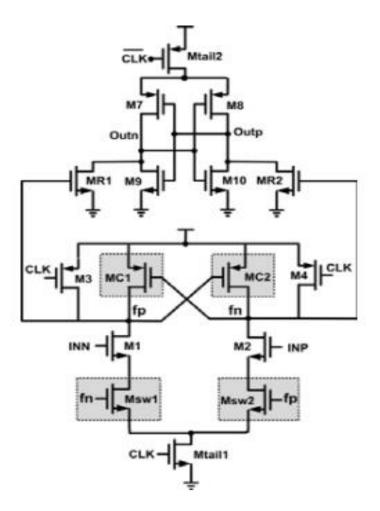

Fig. 2.1: STDLC [1]

## [B] Double Tail-Dynamic latched Comparator:

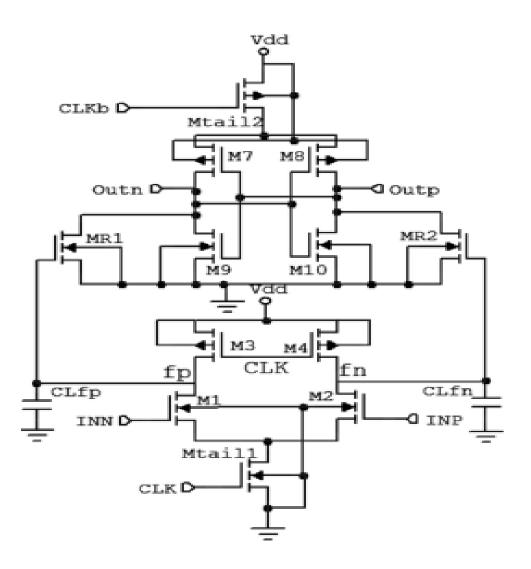

The researchers who looked at this circuit were Schinkel, Mensink, Klumperink, et al. [6] Compared to a traditional dynamic comparator, this one requires less mounting and can operate at a low voltage supply. This circuit has two tail transistors: Mtail1 is short and enables a low current in input side for low offset, while Mtail2 is broad and provides considerable current during the latching phase, leading to quick latching (Fig. 2.2).

Fig. 2.2: DTDLC [1]

## [C] Modified Double Tail Dynamic Latched Comparator

It has been observed that the disparity in terminal voltage at fn and fp has an influence on the rate of latch regeneration in traditional double tail comparator. The efficacy of the comparator will rise if the variation in voltage magnitude at the terminal is greater. To accomplish it, two control transistors were cross-coupled in parallel to M3, M4 as illustrated in Fig 2.3. Mashhadi et al. [9] developed and researched the architecture of modified double tail.

Fig. 2.3: MDTDLC [9]

# [D] Shared charge Logic Dynamic Latch Comparator:

Savani and Devashrayee et al.[1] presented the dynamic latch comparator to enhance the performance index of conventional comparator based on the examination of STDLC and DTDLC and the addition of the basic notion of shared charge logic. Simulation using 130 nm CMOS technology was done, and the outcomes showed characteristics like latency, power, and PDP had been reduced. Fig. 2.4 contains a representation of the architecture under discussion.

Fig. 2.4: SCDLC [1]

# CHAPTER 3 COMPARATOR CHARACTERISTICS

Both the static as well as dynamic features of the comparator will be looked upon in this section.

The optimal attributes of the comparator are depicted in Figure 3.1.

#### **3.1 Static Characteristics:**

Gain, output high (VOH) and low states (VOL), , Offset ,Input Resolution, Noise make up static characteristics.

#### 3.1.1 Gain:

The gain of comparator is expressed as follows:

Gain =

$$A_v = \lim_{\Delta V \to 0} \frac{V_{OH} - V_{OL}}{\Delta V}$$

where  $\Delta V$  is the input voltage change

First-Order Model for a Comparator:

Figure 3.1 First-Order Model of Comparator [14]

VIH= Value of the smallest possible input voltage for which the output voltage is VOH VIL= Value of the largest possible input voltage for which the output voltage is VOL.

The voltage gain is

$$A_v = \frac{V_{OH} - V_{OL}}{V_{IH} - V_{IL}}$$

**3.1.2 Resolution**: In order to make the output fluctuate to acceptable binary levels, the input voltage must shift. That change in input voltage is termed as resolution.

**3.1.3 Offset:** It can be categorised in two ways visually (i) systematic offset and (ii) random offset. Misaligned input transistors (misconfigured threshold levels and mismatched transconductance parameter  $\beta = \mu Cox W/L$ ) cause offset in operational amplifiers and comparators.

a) **Input Offset Current**: The variation amongst the various currents reaching the input ends of a balanced amplifier is termed input offset current.

b) Input Offset Voltage: The potential that has to be supplied between the input ports in order to balance the amplifier is referred as the input offset voltage.c) Output Offset Voltage: When the two input ends are connected to ground, the output offset potential is the dc voltage that is produced at the output node.

**3.1.4 Noise:** A comparator's noise is analyzed as if it was bias in the transition area. Jitter is brought on by an ambiguity in the transition area brought on by noise.

**3.1.5 Input Common Mode Range (ICMR):** It could be described as the input voltage range when the comparator operates correctly and satisfies all necessary requirements.

## **3.2 Dynamic Characteristics:**

Gain and Propagation delay make up the comparator's dynamic properties.

#### 3.2.1 Propagation delay:

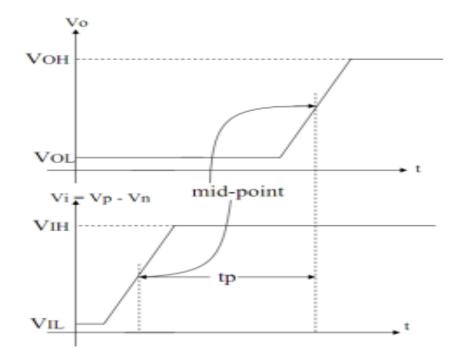

Figure 3.2: Comparators Propagation delay

How quickly an amplifier reacts to given input is referred to as the propagation delay. Propagation delay, expressed simply, is the interval between an input and an output. The propagation time delay characteristics of the comparator are shown in Fig. 3.2. It is estimated as follows:

Propagation time delay= (Rising Propagation Delay + Falling Propagation Delay ) /2

**3.2.2 Slew Rate:** Slew rate is the rate at which the voltage at output node changes in relation to time.

#### SR = dVout/dt

The dynamics might be constrained by the slew rate if the speed of rising or falling off a comparator increases significantly. The Slew rate can be stated with following result:, I=C dV/dt wherein I is the capacitor's current ,V is the voltage applied across it. The voltages speed also gets constrained if the current does. Consequently, we have the following for a comparator with a slew rate limit:

$$t_p = \Delta T = \Delta V/SR = (VOH-VOL)/2*(SR)$$

wherein SR= comparator's slew rate.

# **CHAPTER 4**

# METHODOLOGY AND IMPLEMENTATION

# 4.1 Architecture of Conventional single tail current dynamic latch comparator:

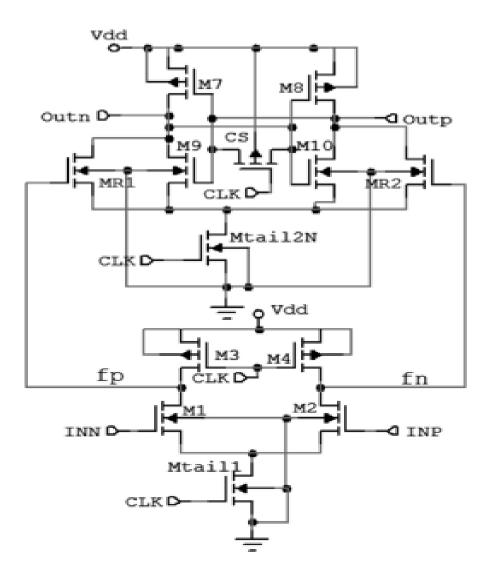

Figure 4.1 depicts the schematic structure of a typical dynamic latch comparator with a single tail current. It has large input impedance, rail-to-rail output fluctuation, and no static power usage. The reset phase as well as regeneration phase are the two distinct parts of the comparator's functioning. CLK is low and M9 transistor is off during the reset phase. The reset transistors (M4, M8) are switched ON during this stage, pulling both the Outn and Outp output terminals to Vdd. This criterion is the prerequisite for the evaluation step. During the reset phase, the M4, M8 transistors are employed to achieve a correct logical level at the output node.

Fig. 4.1: Schematic of STDLC

Transistor M9 is switched ON while transistors M4, M8 are turned off when CLK changes to Vdd, and the circuit enters the comparison phase. The output nodes Outp and Outn, which were precharged to VDD in the preceding reset phase, begin dropping at separate paces. The corresponding/relative input voltage values, or INN and INP, determines the rate of discharge. Presuming that VINP is more than VINN, the Outp terminal would drop more quickly than Outn. Within that scenario, the Outp terminal (which is emptied by the transistor M5's drain current) reaches Vdd - |Vthp| prior to the Outn terminal reaching this potential. Transistor M6 in this example, switches ON to start the regeneration process brought on by cross-coupled inverter. Outp entirely drops to ground after being fully charged Outn to Vdd.

#### **4.2** Architecture of Double Tail dynamic latch comparator (DTDLC):

The design structure of a traditional dynamic latch comparator based on dual tail current is shown in Figure 4.2 [1]. The comparator has 2 distinct tail currents as well as fewer stacked transistors as compared to a comparator with single tail current. Lower tail current in differential phase for smaller offset and higher tail current during latch phase for rapid latching are both separately enhanced by double tail. The comparator operates as follows. Phase of reset: When CLK = 0, transistors M1 and M10 are switched OFF, and transistors M12 and M11 begin precharging two intermediate nodes, fn and fp, to produce voltage Vdd, this is known as the precharging phase. Eventually, intermediate transistors MR5 and MR7 cause output nodes Outn and Outp to discharge to the ground.

Phase of evaluation: When CLK changes to Vdd, transistors M1, M10 switches on, transistors M11, M12 are switches OFF, and voltage at nodes fp and fn begin to drop at a speed determined by the tail current and equivalent capacitive load at node fn (fp). This creates differential potential values among fn and fp. Transistors at the intermediate phase transmit the voltage to inverter that are cross-coupled, while at same moment, transistors M5, MR7 offer safeguard by lowering kickback noise.

Fig. 4.2: Schematic of DTDLC

## 4.3 Architecture of Modified Double tail dynamic latched comparator:

The design for the modified double-tail dynamic latch comparator is shown in Fig. 4.3. The improved comparator is constructed using double-tail architecture due to the structure's superior functioning in low-power usage. The comparator's primary goal is to raise Vfn/fp in order to accelerate regeneration of latch. To accomplish this, two control transistor (M11 , M12) are cross-coupled in parallel with M15 and M16 in the first stage.

Fig. 4.3: Schematic of MDTDLC

The comparator works in the manner described ahead. M15 and M16 pull both the fn, fp nodes to supply voltage in the reset phase (CLK = 0, M1, Mtail10 are off to prevent static power), which turns off M11 and M12. Both of the latch output signals are reset to zero by intermediary stage transistors M5 and M7. The comparator operates as : M15 and M16 pull the fn , fp nodes to supply voltage in the reset stage (CLK = 0, M10, M1 are off to prevent static power), which turns off M11 and M12. Both of the latch outputs are reset upto zero by intermediary stage transistor M5 and M7.

M15, M16 are turned off in the decision-making stage (CLK = VDD, M1, M10 are on). Moreover, the controlling transistor remain still off at the start of the stage. Based on voltage levels at input, fn, fp begin to decline at varying speeds. If Vinp > Vinn, then fn would decline faster than fp (as M17 provides larger current as that of M18). The associated PMOS transistor M11 begins to switch on as longer as fn keeps dropping,

bringing the fp node up to supply voltage. As a result, M12 is off, enabling fn to drop entirely.

In this structure, shortly after comparator senses, for example, that node fn drops quickly, transistor (M11) turns on, pulling the terminal fp to supply voltage, in contrast to standard dual dynamic comparator, in which Vfn/fp is function of gm of input transistor and voltage level difference at input. As a result, as time progresses, the gap among fn, fp rises exponentially, which reduces regeneration period of latch. The thing to keep in mind is when one of the control transistor (like M11) goes active, current from power supply is pulled to the ground through the input and tail transistor (such M11, M18, and M10), which causes static power usage. Two nMOS transistors M17 and M18 are employed underneath the input transistors to solve this problem. The two transistors are on at the start of the decisive stage and fn, fp start to drop at varying rates since both nodes are pre-charged to supply voltage. Control transistors will respond in a way to enhance their potential gap the moment comparator senses that any of the fn or fp node is draining more quickly. If fp were to be lifting up to supply voltage and fn needed to be fully discharged, the switch in fp's charging route would be open, while the switch attached to fn would be closed to facilitate for the full dropping of the fn terminal. Stating in different terms, M17, M18 and control transistor operate in a manner that mimics the action of latch.

#### 4.4 Architecture of Shared charge double tail comparator:

The schematic of architecture of shared charge DLC is depicted in fig. 4.4. Distinct kinds of reset mechanisms are employed during the reset stage of all dynamic latched comparators to produce a logically valid value during the evaluation stage. In this reset method, output nodes are either drained to ground or pulled up to VDD. While in Dual Tail DLC, the output terminals are drained to GND, in Single tail DLC, they are charged to supply voltage. One output node of the comparator is at zero voltage and the other is at VDD once the evaluation step is finished. In the reset phase of the designs that were covered earlier, output ends are either fully drained to GND or charged upto supply voltage. The next evaluation stage begins from the zero voltage or the supply voltage, demanding a prolonged time to obtain the evaluation's ultimate result and utilizing more energy. Discharging one node or charging another node also uses more energy during the subsequent reset stage.

The comparator's main concept is to hold the charge using the improved reset mechanism, which reduces latency & energy. The name of this methodology is shared charge logic. A pass transistor is utilised in this method amongst 2 output nodes.

Fig. 4.4: Schematic of SCDLC

During the reset stage, the pass transistor distributes the charge among its two nodes. The input signal may be assessed more quickly during the regeneration stage since the output won't drop below the threshold value level due to the charges distributed by both load capacitances. It accelerates the process. The results of the execution demonstrate a substantial reduction in delay and power saving as a result of this method. Transistors M11, M3 are turned OFF to prevent any consumption of static power once CLK is at zero

voltage. Transistors M10, M8 bring the nodes fn , fp to VDD during this stage. Therefore, resultantly it switches ON transistors M1 and MR4.

In this reset stage, transistor M5 connects the two output nodes Outn and Outp, converting it into a shared charge transistor that distributes the charge between Outn, Outp.

The circuit starts to evaluate when the CLK gets close to VDD. Transistors M11 and M3 are switched ON during this stage, whereas reset transistors M8, M10 are switched OFF. Now, in accordance with the speed determined by input voltages, the fn and fp terminals begin draining via the transistors M13 and M12 at varying rates.

Assuming VINN is greater than VINP, fp decreases more quickly than fn. If we consider the input voltage to be in the opposite state, this event would be different. The main functional difference between this design and others is that in the evaluation stage, decisions are made when both output nodes are almost at 50% the VDD value rather than at two extreme voltage values. Even though the output node's starting status is at 1/2 the voltage supply level, it requires less time to evaluate and uses less power.

#### **4.5 Proposed Dynamic Latched Comparator:**

This comparator, like other comparators, operates in two distinct stages. During the reset phase, CLK = 0 and CLK = VDD, therefore both tail transistors are turned off, and the drain and source terminals of F3 and F4 are charged to VDD through F5,F7, and F6,F8. If OUTP and OUTN have any accumulated charge from earlier cycles, they are discharged to ground through F13 and F14. Clock cycles are now reversed during the assessment phase, and tail transistors are turned on. The conductances of paths F1 and F2 are affected by the voltages VINP and VINN. Fa will switch off F4 and turn on F10, causing node Fb to be at VDD, which will turn off F9 and turn on F3 to allow the Fa node to be totally drained. As long as node Fb is turned on, OUTP will discharge to ground through F14.OUTP will also switch on F11 and turn off F15, keeping OUTN at VDD. OUTN will cause F12 to switch off, so disconnecting the charging channel of OUTP, and will turn on F16 to assist OUTP in being entirely drained.

To ensure the specified precision of comparison, two distinct clocks are required, with correct synchronization between them. During the reset phase, the top level transistor prevents any power use. The figure is shown in Fig 4.5.

Fig. 4.5: Schematic of PDLC

# **CHAPTER 5**

# SIMULATION RESULTS AND ANALYSIS

#### **5.1 SPECIFICATIONS**

Simulations were performed on the Cadence Virtuoso tool by constructing schematics for all architectures of dynamic-latched comparators. The analyses were done 130 nm technology node.

Temperature: 27-degree centigrade

Offset voltage: 1.2 V

*VDD* : 1.5V

*INP:* It is a sine wave with frequency 0.5Ghz ,an offset voltage of 1.2 V and amplitude of 20 mV.

*INN*: It is DC voltage of 1.2 V

*CLK*: It is a clock wave of duration 5ns with rise time and fall time 0.1ps and its pulse width of 0.5ns and time period of 1ns.

#### **5.2 TRANSIENT ANALYSIS**

All the 5 architecture's transient analysis was done to verify the correct functioning of the circuit. The models were simulated using the same input data signal and a similar common mode input voltage to ensure the reliability of the performance comparison results. The simulation outputs are depicted in Fig. 5.1.

(b)

(e)

Fig. 5.1: Transient analysis of (a)STDLC (b) DTDLC (c) MDTDLC (d) SCDLC (e) PDLC

# **5.3 POWER CONSUMPTION**

A visual comparison of the five models in terms of power consumption is shown. in Fig. 5.2.

Fig. 5.2: Power of: a) STDLC, (b) DTDLC, (c) MDTDLC (d) SCDLC (e) PDLC

| Architecture | Total Average Power |

|--------------|---------------------|

| STDLC        | 5.269µW             |

| DTDLC        | 10.28µW             |

| MDTDLC       | 11.36µW             |

| SCDLC        | 7.927µW             |

| PDLC         | 17.69µW             |

Table. 5.1. Power Consumption

## 5.4 DELAY

| Architecture | Delay    |

|--------------|----------|

| STDLC        | 58.63ps  |

| DTDLC        | 65.62ps  |

| MDTDLC       | 85.65ps  |

| SCDLC        | 70.205ps |

| PDLC         | 106.68ps |

Table. 5.2: Delay comparison

# **5.5 POWER DELAY PRODUCT:**

| Architecture | PDP(f) |

|--------------|--------|

| STDLC        | 0.3089 |

| DTDLC        | 0.674  |

| MDTDLC       | 0.9729 |

| SCDLC        | 0.5565 |

| PDLC         | 1.887  |

Table. 5.3: Power Delay Product(PDP) comparison

# **5.6 MONTE CARLO SIMULATIONS:**

(b)

(c)

(d)

Fig 5.3:Monte Carlo Simulations of: a) STDLC, (b) DTDLC, (c) MDTDLC (d) SCDLC (e)PDLC

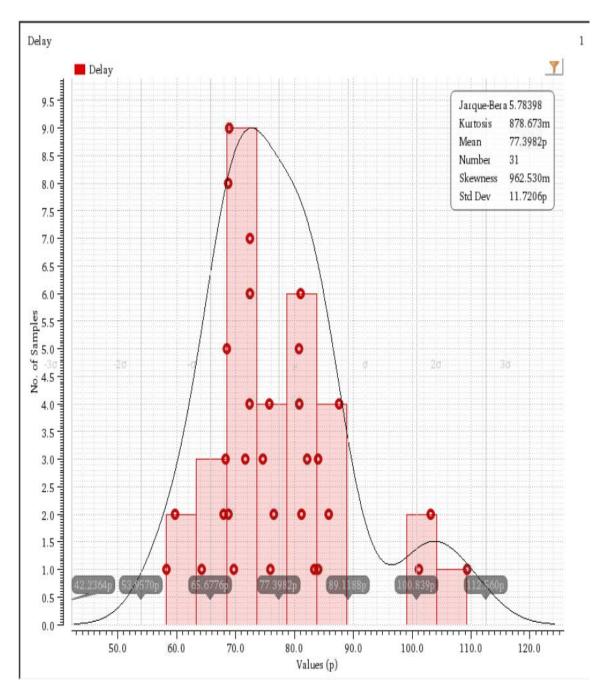

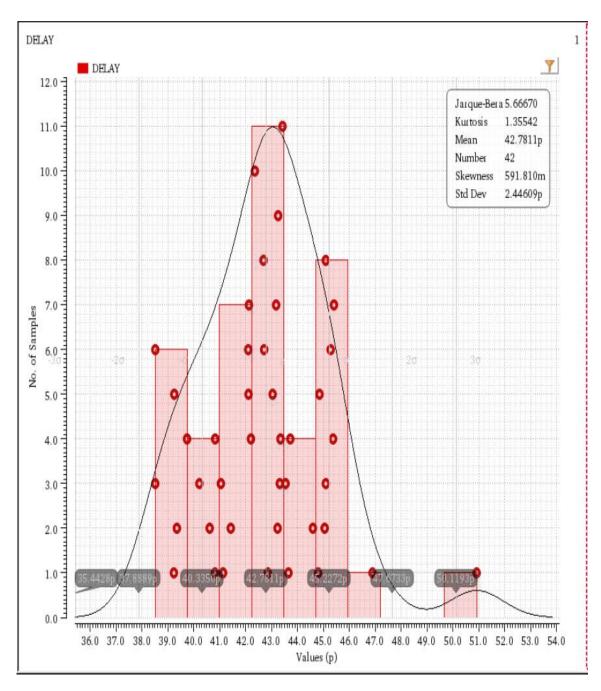

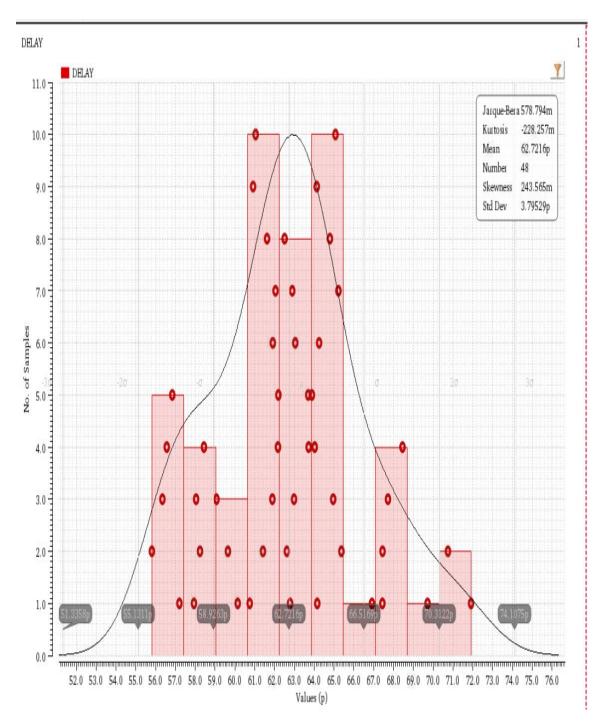

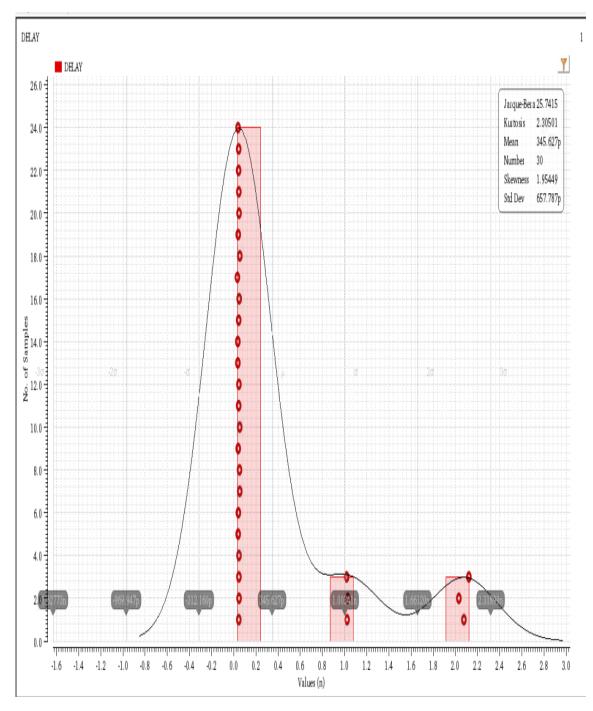

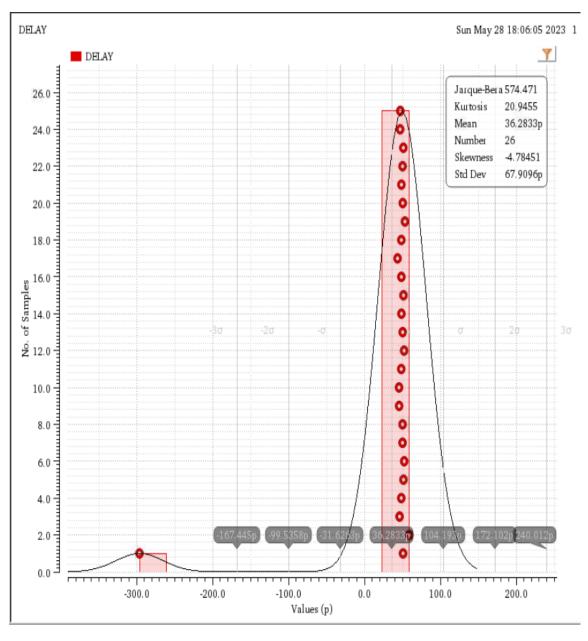

# 5.7 HISTOGRAM FOR DELAY:

35

(a)

(b)

(c)

(d)

(e)

Fig. 5.4: Histogram for Power for: a) STDLC, (b) DTDLC, (c) MDTDLC (d) SCDLC (e)PDLC

## **CHAPTER 6**

#### **CONCLUSION AND FUTURE SCOPE**

To summarize, dynamic comparators have been investigated with various existing architecture. Simulation of the comparator shows that shared charge logic based comparator has significantly lesser power along with high operation speed and consequently it outcomes as a notably lower power-delay product (PDP). There were improvements seen in every subsequent comparator.

| Architecture | Yield | Mean      | Standard Deviation |

|--------------|-------|-----------|--------------------|

| STDLC        | 62%   | 77.39ps   | 11.721             |

| DTDLC        | 84%   | 42.781ps  | 2.44               |

| MDTDLC       | 96%   | 60.721ps  | 3.7995             |

| SCDLC        | 60%   | 345.627ps | 657.787            |

| PDLC         | 52%   | 36.283p   | 67.99096           |

Table 5.4: Variation of parameters for different architecture

#### **Future Work:**

We can compare all the simulated circuits at different technology nodes and can compare the relative changes. We can incorporate newer technologies of FINFET in the transistors used in the circuits and check for further enhancements. There is also a possibility of analysing these circuits using transmission gates.

#### REFERENCES

- Savani, V., & Devashrayee, N.M. (2018). Design and analysis of low-power high-speed shared charge reset technique based dynamic latch comparator. *Microelectron. J.*, 74, 116-126.

- [2] Varshney, V., & Nagaria, R. K. (2020). Design and analysis of ultra high-speed low-power double tail dynamic comparator using charge sharing scheme. AEU-International Journal of Electronics and Communications, 116, 153068.

- [3] Allen, P. E., & Holberg, D. R. (2002). CMOS analog circuit design (2nd ed.). Oxford: Oxford University.

- [4] Gandhi, P. P., & Devashrayee, N. M. (2018). A novel low offset low power CMOS dynamic comparator. Analog Integrated Circuits and Signal Processing, 96(1), 147-158.

- [5] Savani, V., & Devashrayee, N. M. (2014). Performance analysis and characterization of shared charge and clocked-latch based comparator using 90-nm technology. Journal of VLSI Design Tools & Technology, 4, 20–26.

- [6] Schinkel, D., Mensink, E., Klumperink, E., van Tuijl, E., & Nauta, B. (2007). A double-tail latch-type voltage sense amplifier with 18 ps setup ? hold time. In 2007 IEEE international solidstate circuits conference. Digest of technical papers (pp. 314–605). doi: 10.1109/ISSCC.2007.373420.

- [7] T. Kobayashi, K. Nogami, T. Shirotori and Y. Fujimoto, "A current-controlled latch sense amplifier and a static power saving input buffer for low-power architecture," IEEE J. Solid State Circuits, vol. 28, pp. 523-52, April 1993.

- [8] Dubey, A. K., & Nagaria, R. K. (2019). Low-power high-speed CMOS double tail dynamic comparator using self-biased amplification stage and novel latch stage. Analog Integrated Circuits and Signal Processing, 101(2), 307-317.

- [9] Babayan-Mashhadi, S., & Lotfi, R. (2014). Analysis and design of a low-voltage low-power double-tail comparator. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 22, 343–352. doi:10.1109/TVLSI.2013.2241799

- [10] Goll, B., & Zimmermann, H. (2009). A comparator with reduced delay time in 65-nm CMOS for supply voltages down to 0.65 V. IEEE Transactions on Circuits and Systems II: Express Briefs, 56, 810–814. doi:10.1109/TCSII.2009.2030357.

- [11] Jeon, H., & Kim, Y. B. (2010, May). A low-offset high-speed double-tail dual-rail dynamic latched comparator. In Proceedings of the 20th symposium on Great lakes symposium on VLSI (pp. 45-48).

- [12] Figueiredo, P. M., & Vital, J. C. (2006). Kickback noise reduction techniques for CMOS latched comparators. IEEE Transactions on Circuits and Systems II: Express Briefs, 53, 541–545. doi:10. 1109/TCSII.2006.87530.

- [13] Babayan-Mashhadi, S., & Lotfi, R. (2012). An offset cancellation technique for comparators using body-voltage trimming. Analog Integrated Circuits and Signal Processing, 73, 673–682. doi:10. 1007/s10470-012-9925-5.

- [14] Nikoozadeh and B. Murmann, "An Analysis of Latch Comparator Offset Due to Load Capacitor Mismatch," IEEE Trans. Circuits Syst. II: Exp. Briefs, vol. 53, no. 12, pp. 1398-1402, Dec. 2006

- [15] M. M. Hossain and S. N. Biswas, "Analysis and Design of a 32nm FinFET Dynamic Latch Comparator," 2019 5th International Conference on Advances in Electrical Engineering (ICAEE), Dhaka, Bangladesh, 2019, pp. 49-54

- [16] Miyahara, M., Asada, Y., Paik, D., & Matsuzawa, A. (2008, November). A low-noise selfcalibrating dynamic comparator for high-speed ADCs. In 2008 IEEE Asian Solid-State Circuits Conference (pp. 269-272). IEEE.

- [17] Lei, K. M., Mak, P. I., & Martins, R. P. (2013). Systematic analysis and cancellation of kickback noise in a dynamic latched comparator. Analog Integrated Circuits and Signal Processing, 77, 277-284.

- [18] Uthaichana, P., & Leelarasmee, E. (2003, October). Low power CMOS dynamic latch comparators. In TENCON 2003. Conference on Convergent Technologies for Asia-Pacific Region (Vol. 2, pp. 605-608). IEEE.

- [19] Lin, Y., Doris, K., Hegt, H., & Van Roermund, A. (2012, May). A dynamic latched comparator for low supply voltages down to 0.45 V in 65-nm CMOS. In 2012 IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 2737-2740). IEEE.

- [20] Cusinato, P., Bruccoleri, M., Caviglia, D. D., & Valle, M. (1998). Analysis of the behavior of a dynamic latch comparator. IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications, 45(3), 294-298.

- [21] Folla, J. K., Crespo, M. L., Wembe, E. T., Bhuiyan, M. A., Cicuttin, A., Essimbi, B. Z., & Reaz, M. B. (2021). A low-offset low-power and high-speed dynamic latch comparator with a preamplifier-enhanced stage. IET Circuits, Devices & Systems, 15(1), 65-77.

- [22] Rahman, L. F., Reaz, M. B. I., Yin, C. C., Marufuzzaman, M., & Rahman, M. A. (2014). A high-speed and low-offset dynamic latch comparator. The Scientific World Journal, 2014.

- [23] Sangeetha, R., Vidhyashri, A., Reena, M., Sudharshan, R. B., & Ajayan, J. (2019, March). An overview of dynamic cmos comparators. In 2019 5th International Conference on Advanced Computing & Communication Systems (ICACCS) (pp. 1001-1004). IEEE.

- [24] Solis, C. J., & Ducoudray, G. O. (2010, August). High resolution low power 0.6 μm CMOS 40MHz dynamic latch comparator. In 2010 53rd IEEE international midwest symposium on circuits and systems (pp. 1045-1048). IEEE.

- [25] Chevella, S., O'Hare, D., & O'Connell, I. (2020). A low-power 1-V supply dynamic comparator. IEEE Solid-State Circuits Letters, 3, 154-157.

- [26] Halim, I. S. A., & Abidin, N. A. N. B. Z. (2011, September). Low power CMOS charge sharing dynamic latch comparator using 0.18 μm technology. In 2011 IEEE regional symposium on micro and nano electronics (pp. 156-160). IEEE.

- [27] Miyahara, M., & Matsuzawa, A. (2009, November). A low-offset latched comparator using zero-static power dynamic offset cancellation technique. In 2009 IEEE Asian Solid-State Circuits Conference (pp. 233-236). IEEE.

- [28] Huang, Y., Schleifer, H., & Killat, D. (2013, September). Design and analysis of novel dynamic latched comparator with reduced kickback noise for high-speed ADCs. In 2013 European Conference on Circuit Theory and Design (ECCTD) (pp. 1-4). IEEE.

- [29] Kapadia, D. N., & Gandhi, P. P. (2013, April). Implementation of CMOS charge sharing dynamic latch comparator in 130nm and 90nm technologies. In 2013 IEEE Conference on Information & Communication Technologies (pp. 16-20). IEEE.

- [30] Bindra, H. S., Lokin, C. E., Annema, A. J., & Nauta, B. (2017, September). A 30fJ/comparison dynamic bias comparator. In ESSCIRC 2017-43rd IEEE European Solid State Circuits Conference (pp. 71-74). IEEE.

- [31] Jung, Y., Lee, S., Chae, J., & Temes, G. C. (2011). Low-power and low-offset comparator using latch load. Electronics Letters, 47(3), 1.

- [32] Hassanpourghadi, M., Zamani, M., & Sharifkhani, M. (2014). A low-power low-offset dynamic comparator for analog to digital converters. Microelectronics Journal, 45(2), 256-262.

- [33] Rabbi, F., Das, S., Hossain, Q. D., & Pathan, N. S. (2018, February). Design of a low-power ultra high speed dynamic latched comparator in 90-nm CMOS technology. In 2018 International Conference on Computer, Communication, Chemical, Material and Electronic Engineering (IC4ME2) (pp. 1-4). IEEE.

- [34] Bala Dastagiri, N., Hari Kishore, K., Gunjan, V. K., & Fahimuddin, S. (2018). Design of a low-power low-kickback-noise latched dynamic comparator for cardiac implantable medical device applications. In Proceedings of 2nd International Conference on Micro-Electronics, Electromagnetics and Telecommunications: ICMEET 2016 (pp. 637-645). Springer Singapore.

- [35] Jeon, H. (2010). Low-power high-speed low-offset fully dynamic CMOS latched comparator (Doctoral dissertation, Northeastern University).

- [36] Murali Krishna, G., Karthick, G., & Umapathi, N. (2020, October). Design of dynamic comparator for low-power and high-speed applications. In ICCCE 2020: Proceedings of the 3rd International Conference on Communications and Cyber Physical Engineering (pp. 1187-1197). Singapore: Springer Singapore.

- [37] Saroja, G., & Satyanarayana, M. (2016). Design of high performance CMOS dynamic latch comparator. International Journal of Engineering Reseach Application, 6(10), 1-9.

- [38] McCarroll, B. J., Sodini, C. G., & Lee, H. S. (1988). A high-speed CMOS comparator for use in an ADC. IEEE Journal of Solid-State Circuits, 23(1), 159-165.

- [39] Bekal, A., Joshi, R., Goswami, M., Singh, B. R., & Srivatsava, A. (2015, July). An improved dynamic latch based comparator for 8-bit asynchronous SAR ADC. In 2015 IEEE Computer Society Annual Symposium on VLSI (pp. 178-182). IEEE.

- [40] Tang, X., Shen, L., Kasap, B., Yang, X., Shi, W., Mukherjee, A., ... & Sun, N. (2020). An energy-efficient comparator with dynamic floating inverter amplifier. IEEE Journal of Solid-State Circuits, 55(4), 1011-1022.

- [41] Sumanen, L., Waltari, M., & Halonen, K. (2000, December). A mismatch insensitive CMOS dynamic comparator for pipeline A/D converters. In ICECS 2000. 7th IEEE

International Conference on Electronics, Circuits and Systems (Cat. No. 00EX445) (Vol. 1, pp. 32-35). IEEE.

- [42] Xu, D., Xu, S., & Chen, G. (2015). High-speed low-power and low-power supply voltage dynamic comparator. Electronics Letters, 51(23), 1914-1916.

- [43] Bandla, K., Harikrishnan, A., & Pal, D. (2020, February). Design of Low Power, High Speed, Low Offset and Area Efficient Dynamic-Latch Comparator for SAR-ADC. In 2020 International Conference on Innovative Trends in Communication and Computer Engineering (ITCE) (pp. 299-302). IEEE.

- [44] Jerome, F. K., Evariste, W. T., Bernard, E. Z., Crespo, M. L., & Cicuttin, A. (2021, March). A compact 20GHz dynamic latch comparator in 65nm CMOS process. In 2021 18th International Multi-Conference on Systems, Signals & Devices (SSD) (pp. 1177-1181). IEEE.

- [45] Boni, A., Chiorboli, G., & Morandi, C. (2000). Dynamic characterisation of high-speed latching comparators. Electronics Letters, 36(5), 1.

# **PUBLICATION DETAILS**

**Paper Name:** A COMPARATIVE ANALYSIS AND DESIGN OF DYNAMIC LATCH COMPARATORS

**Publication Name:** International Conference on Smart Technology, Electrical and Electronics Engineering (ICSTEEE - 2023)

**Indexing:** This conference is Associated with UGC Care listed and Scopus Indexed International journals.

All registered conference papers will be published Conference proceeding (Having ISBN Number) and the extended versions of the papers will be published in related reputed **Scopus/ SCI/WoS/UGC** Care Listed international journals.

Status: Accepted

### **PROOF OF INDEXING**

#### Welcome

International Conference on Smart Technology, Electrical and Electronics Engineering (ICSTEEE - 2023) will be held in Chennai, India on 12th August 2023 to share the ideas in globally trending technologies in Business Management and Social Science and many more.

The key motive of ICSTEEE – 2023 is to provide a world-class platform for the global participants to share their ideas and experience in person with their peers expected to join from different parts of the world. In addition, this gathering will help the delegates to establish research or business relations as well as to find international linkage for future collaborations in their career path. We hope that ICSTEEE – 2023 outcome will lead to significant contributions to the knowledge base in these up-to-date scientific fields in scope.

Paper submission: click here or mail us info.irfconference@gmail.com for (listeners or paper presentation)

The Organizer of this Conference-IRF Conference (International Research Forum for Engineers and Researchers) is a unique global forum for researchers with cross-disciplinary interests to meet and interact has been organizing various conferences, seminars, scientific events since 2012 across the globe. Research papers using theoretical, quantitative, qualitative, or mixed-methods approaches are encouraged as are those using interdisciplinary approaches.

Publication in Journals: This conference is Associated with UGC Care listed and Scopus Indexed International journals.

All registered conference papers will be published Conference proceeding (Having ISBN Number) and the extended versions of the papers will be published in related reputed **Scopus/ SCI/WoS/UGC** Care Listed international journals Ctivate Win

# **PROOF OF ACCEPTANCE**

#

IRF Conference

📼 Wed, May 17, 5:34 PM (12 days ago) 🛛 🕁 🖌 🚦

Greetings and best wishes for the day!!

Our International Conference has accepted your research paper with Paper ID (IF-ICSTEEE-CHNNAI-120823-4640)

Paper Title: A COMPARATIVE ANALYSIS AND DESIGN OF DYNAMIC LATCH COMPARATORS

Register Now in the link below

Online payment link http://iraj.in/PAYMENT/all\_payment.php

# PLAGIARISM REPORT

| 🔁 turnitin                                       | Similarity Report ID: oid:27535:36505666     |

|--------------------------------------------------|----------------------------------------------|

| PAPER NAME THESIS_PLAG.docx                      | AUTHOR<br><b>mahi</b>                        |

| WORD COUNT<br>5169 Words                         | CHARACTER COUNT 27511 Characters             |

| PAGE COUNT<br><b>47 Pages</b>                    | FILE SIZE 7.5MB                              |

| SUBMISSION DATE<br>May 30, 2023 3:07 PM GMT+5:30 | REPORT DATE<br>May 30, 2023 3:08 PM GMT+5:30 |

### • 19% Overall Similarity

The combined total of all matches, including overlapping sources, for each database.

- 13% Internet database

- 11% Publications database

Crossref database

- Crossref Posted Content database

- 11% Submitted Works database

#### • Excluded from Similarity Report

- Bibliographic material

- · Small Matches (Less then 8 words)

- Quoted material