## **Post Silicon Functional Validation: PCIe**

# SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

MASTER OF TECHNOLOGY

## VLSI DESIGN AND EMBEDDED SYSTEMS

Submitted by

Suraj Singh 2K21/VLS/20

Under the supervision of **Dr. M S Choudhary**

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering)BawanaRoad, Delhi-110042

MAY, 2023

## DECLARATION

I, Suraj Singh hereby declare that the work presented in this thesis entitled "Post Silicon Functional Validation : PCIe" in partial fulfillment of the requirement for the award of degree of Master of Technology (VLSI Design and Embedded Systems) submitted at Electronics & Communication Department, Delhi Technological University (DTU), Delhi. The matter presented in this has not been submitted either in part or full to any other university or institute for the award of any other degree.

Place : Delhi Date : -05-2023 Suraj Singh (2K21/VLS/20)

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering)BawanaRoad, Delhi-110042

## CERTIFICATE

I hereby certify that the major project Dissertation titled "Post Silicon Functional Validation: PCIe" which is submitted by Suraj Singh, Roll No. 2K21/VLS/20 of Electronics & Communication Department, Delhi Technological University (DTU), Delhi in partial fulfillment of the requirement for the award of degree of Master of Technology, is a record of the project work carried out by the students under my supervision to the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date: -05-2023 SUPERVISOR Dr. M S Choudhary

## ACKNOWLEDGEMENT

I take this opportunity to express my gratitude to my guide **Dr. M S Choudhary**, Professor, Department of Electronics and Communication Engineering, Delhi Technological University (DTU) for his guidance and constant encouragement throughout the course of this project.

I would also like to thank **Prof. O P Verma**, Head of Department, Electronics & Communication Engineering, Delhi Technological University for giving such an opportunity of internship at Intel Corporation Pvt. Ltd and rendering all kinds of supports throughout the project work.

Last but not the least I thank my family, friends, and colleagues for their timely help and valuable suggestions.

Place: Delhi Date : -05-2023 Suraj Singh (2K21/VLS/20)

## ABSTRACT

Post Si validation is one of the most important and crucial step in the PRQ of the product into the market. As, in this era, there are a lot of IPs or peripherals are present on the SoC and also contains complex circuitry on in the chip. Major chunk of the silicon chip constitutes analog and digital circuits which contains high speed input output link interface called PCIe and other parallel links for example DDR. Validation of this link interface IPs are very hard to validate as the observability of the signals are very less in the post Si domain.

This thesis proposes functional validation of high speed serial links such as PCIe to improve the quality and Performance of the IP in the SoC with the help of correct debug tools. And, also describes the systematic approach to validate the IP in a correct way and to meet the market timing constraints

## **TABLE OF CONTENT**

| Sr No      | Name                                                                              | Page No    |

|------------|-----------------------------------------------------------------------------------|------------|

|            | Certificate                                                                       | <i>ii</i>  |

|            | Declaration                                                                       | <i>iii</i> |

|            | Acknowledgement                                                                   | iv         |

|            | Abstract                                                                          | v          |

|            | List of Figures                                                                   | viii       |

|            | List of Abbreviations                                                             | x          |

| 1.         | Introduction                                                                      | 7          |

| 1.1.       | Major Steps in Post Silicon Validation                                            | 9          |

| 1.2.       | Need of Post Silicon Validation                                                   |            |

| 2.         | Overview of PCIe                                                                  | 14         |

| 3.1        | Introduction                                                                      | 14         |

| 3.2.       | PCIe Topology                                                                     | 15         |

| 3.3.       | Layered Architecture                                                              | 16         |

| 3.         | Errors Associated with PCIe                                                       |            |

| 4.         | PCIe: Link Training and Initialization                                            |            |

| 5.1        | Different States of PCIe LTSSM                                                    | 24         |

| 5.2        | Power States associated with PCIe Link                                            |            |

| 6.3        | PCIe Configuration Register associated with LTSSM                                 |            |

| 5.         | System Power State and Device State                                               |            |

| 7,         | Statement Of Problem Based On Identified Research Gaps                            |            |

| 8.         | Post Silicon Validation Paradigm                                                  |            |

| 8.1        | Tools Used for Execution and Debugging in Post Silicon validation                 |            |

| 9.         | Work done, partial simulation/hardware implementation, partial Results and Discus | ssion38    |

| 9.1<br>9.2 | Overview of Work Done<br>Test Cases implemented with OSBV                         |            |

| 9.3        | Test Cases implemented with Synthetic                                             |            |

| 10   | Conclusion   | 44 |

|------|--------------|----|

| 10.1 | Future Scope | 44 |

| 11   | References   | 47 |

## Table of Figures

| Sr No  | Description                         | Page No |

|--------|-------------------------------------|---------|

| Fig1.  | Intel SoC Architecture              | 7       |

| Fig2.  | Validation loop                     | 9       |

| Fig3.  | Comparison between Domains          |         |

| Fig4.  | CEM and M.2 Slots                   | 14      |

| Fig5.  | PCIe Gen Speed depending upon Lanes |         |

| Fig6.  | PCIe Tree Topology                  | 15      |

| Fig7.  | Layered Architecture                | 16      |

| Fig8.  | Types of Transaction                | 16      |

| Fig9.  | Transaction Layer and TLP           | 17      |

| Fig10. | TLP Field                           |         |

| Fig11  | DLLP                                |         |

| Fig12  | PHY Layer                           |         |

| Fig13  | Types of PCIe Error                 | 21      |

| Fig14  | Message Packet                      | 21      |

| Fig15  | Error Message                       |         |

| Fig16  | Completion TLP                      |         |

| Fig17  | LTSSM                               | 23      |

| Fig18  | Link going from Detect to Polling   | 24      |

| Fig19  | Polling State                       | 25      |

| Fig20  | Configuration State                 |         |

| Fig21  | L0 State                            |         |

| Fig22 | L0s State                         | 27   |

|-------|-----------------------------------|------|

| Fig23 | L1 State                          | 27   |

| Fig24 | Link Capability Register          | 28   |

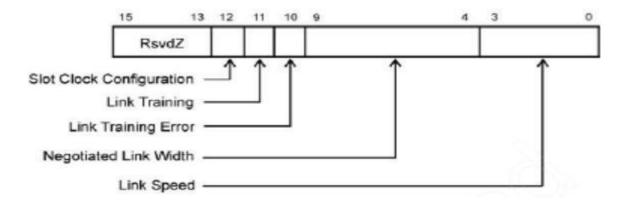

| Fig25 | Link Status Register              | .29  |

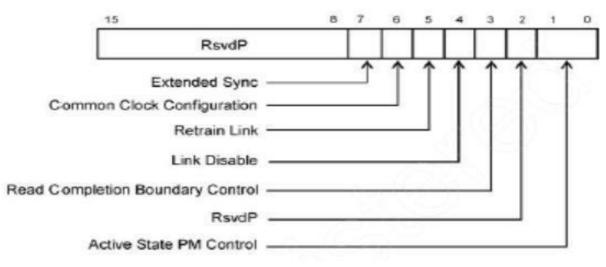

| Fig26 | Link Control Register             | . 29 |

| Fig27 | State and Link State              | . 32 |

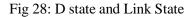

| Fig28 | D state and Link State            | . 32 |

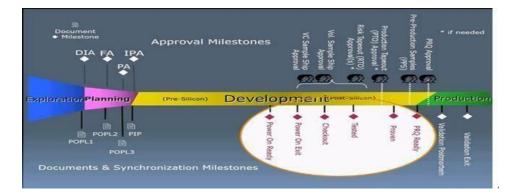

| Fig20 | Phases in Post Silicon Validation | 34   |

| Fig30 | TLA GUI                           | 36   |

| Fig31 | Protocol Analyzer GUI             | 37   |

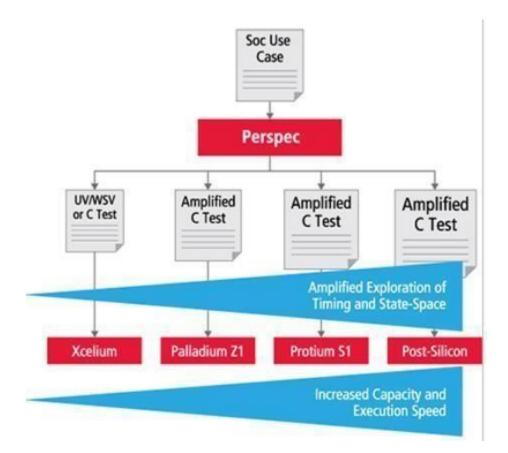

| Fig32 | Perspec Tool                      | 45   |

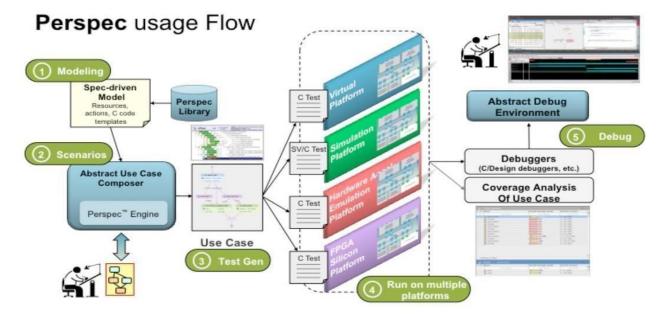

| Fig33 | Perspec tool Flow                 | 45   |

## ABBREVIATIONS

| SoC: System on Chip                             |

|-------------------------------------------------|

| GPU: Graphics Processor Unit                    |

| CPU: Central Processing Unit                    |

| RVP: Reference validation platform              |

| PCIe: Peripheral component Interconnect Express |

| PO: Power On                                    |

| POE: Power on Exit                              |

| TLP: Transaction Layer Packet                   |

| DLLP: Data Link Layer Packet                    |

| PHY: Physical Layer                             |

| PRQ: Product Release Qualification              |

| OSBV: OS based Validation                       |

| I/O: Input Output                               |

| DMI: Direct Media Interface                     |

| TLA: Tektronix Logic Analyzer                   |

## **1. INTRODUCTION**

A System of Chip (SoC) involves various kinds of IPs or integrated circuits which contains different memory controllers (SRAM, ROM, etc.) and other peripherals. It also contains various digital, analog and mixed signal circuitry which are responsible for intended functionality of the SOC.

The major advantage of using the SOC is that size of whole circuitry become small and also consumes less power.

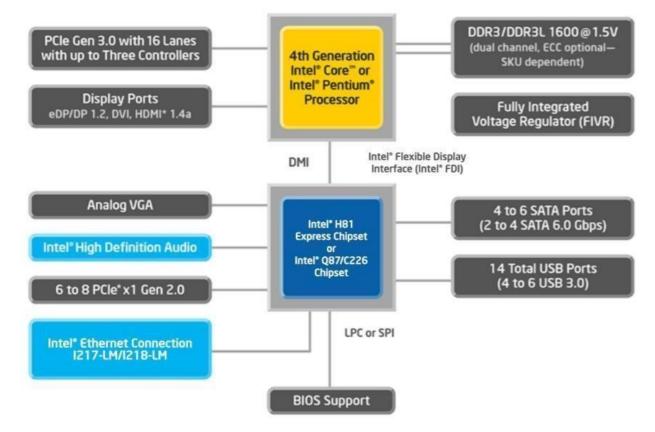

The Basic architecture of Intel SoC contains a microprocessor and other supporting Intellectual property that enables a building block for variety of computing system. Intel architecture consists of important parts: a microprocessor chip and the companion chip which also known as Platform Control Hub. The microprocessor chip and the companion chip are connected via interface called DMI.

Figure 1: Intel SoC Architecture

The high speed I/O interface used in the Intel architecture is PCIe interface. The Number of PCIe lanes depends upon the type of processor used. The maximum common width of PCIe lane is 16 as it is supported by PCIe graphics card.

The PCIe uses differential signals as DMI uses. PCIe supports highest data rates up to Gen5 Speed nowadays.

Post silicon validation is the last step in semiconductor chip industry before launching the product into the market. Functional Validation (FV) is one of the most important part of post silicon validation. The goal of this step is to validate the functionality of the silicon chip with respect to the specification provided for the exact SoC (System on Chip) design. Thus making sure that the product is functional well by considering end user case scenario. This will make a product successful in the market.

Post-Silicon validation of a SoC comprises of various types of validation, which includes system validation (SV), functional validation (FV), and electrical validation (EV) and so on. Different category of validation focus on different parameters and execute in parallel. Ultimately, post-silicon validation aims to qualify a product over all process corners as well as operating conditions. At the end of post-silicon validation, a Product Release Qualification (PRQ) decision is made according to the risk assessment of how many systems fail according to the specifications. In a product's life cycle, the PRQ decision is an important milestone after which the product is released into the market.

The aim of Post Silicon Validation is to guarantee that the silicon chip works properly under real operating environment while executing real software, identify and correct the faults and errors that may have untouched due to the capability of Pre silicon Validation. Validation (Post Silicon) is a method in which the chip is made to undergo end user case scenario/tests for all accuracy and correctness with respect to its function in an experimental lab environment. This is done through using the actual silicon chip which is put together on a reference validation platform along with all other hardware which are part of the system for which, the chip has designed for.

Validation has become the major challenging task for companies validating IP and SoC products to meet the customer requirements. The complexity of modern SoC creates an enormous validation challenge which can only be met through the application of advanced validation techniques and optimal reuse. It is pointed out that post silicon validation stage is one of the important task or the level for a product before it comes out in the market because there are so many bugs which remain un addressed during the pre-silicon verification which can create huge problem to the end user.

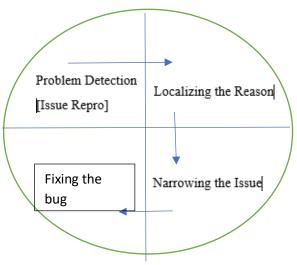

#### 1.1. Major Steps in Post Silicon Validation

There are 4 major steps:

1. Reproducing the problem by executing various test cases and also by using real time end user application

Example: booting to OS, running games or any other heavy application, until the system failure reproduce (example: system hung, crash or any other machine error).

2. Identifying the reason/issue that cause a system failure.

Example: an application/system flow got break/crash might be due to any IP present on the SoC.

3. Addressing the root cause of the failure.

Example: Isolating the issue into a single reason.

4. Fixing of the issue/failure using various techniques like by providing different patches like BIOS, or firmware update.

Figure 2: Validation loop

Each of these four phases poses significant challenges like reduce time to validate and improve robustness, improve the throughput, reduce time to debug.

To reduce the time of validation in post silicon can be done by structuring your strategy in an organized way can help you and in return you can deploy your product in to the market on time and quickly.

Hence, above mention above steps can help to achieve your goals easily.

#### 1.2. Need of Post Silicon Validation

1. To deploy product into the market we can trust fully on the pre-si verification as there are lot of bugs which get un addressed in this domain. As, in pre-si is done various software/emulators which are way slower than a real silicon chip. Pre- si can give advantage in verifying individual logic of the chip but it reaches its limitation in terms of verifying full chip models. Hence, lots of issues get detected in post-si rather than the pre-si.

2. As the technology is increasing day by day therefore the complexity of the SoC is also increasing. Hence, the handshake between various components of design and electrical block of the system is become important, e.g., process variation, signal health (noise and cross talk) and thermal effects. Such handshake can lead to system malfunctioning/or not functioning properly and these bugs are considered as electrical bugs. Hence, handling of these errors become very difficult in the pre silicon verification.

3. Despite of manufacture defect, post-si errors may be reproduce by the repeatedly handshaking of the various IPs presents on the SoC with platform parameters which can result into logical errors or malfunction of the SoC. To create an error handling mechanism for these bugs become very difficult.

| Pre-silicon<br>verification                                                                            | Manufacturing<br>testing                                                              | Post-silicon<br>validation                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Excellent<br>controllability and<br>observability because<br>any signal can be<br>accessed             | Controllability<br>and<br>observability<br>primarily through<br>scan DFT              | Insufficient<br>controllability and<br>observability due<br>to limited access<br>to internal<br>signals. Scan<br>DFT useful for<br>certain cases<br>when a failure<br>caused by a bug<br>is repeatable. |

| Complex physical<br>effects difficult to<br>model                                                      | Several defect<br>models exist                                                        | Accounts for<br>signal-integrity,<br>process<br>variations, non-<br>determinism                                                                                                                         |

| Simulation of full-chip<br>designs very slow;<br>formal verification<br>only selectively<br>applicable | Generally very<br>fast (few<br>seconds to<br>minutes per<br>chip)                     | Silicon speed<br>orders of<br>magnitude faster<br>than simulation                                                                                                                                       |

| Some metrics exist<br>(e.g., code coverage,<br>assertion coverage,<br>mutation coverage)               | Test Metrics<br>(e.g., stuck-at,<br>transition, N-<br>detect coverage)<br>widely used | Coverage metrics<br>for post-silicon<br>validation: Open<br>research question                                                                                                                           |

| Bug fixing<br>inexpensive                                                                              | Bug fixing not<br>the primary<br>objective                                            | Bug fixing can be expensive                                                                                                                                                                             |

Fig 3: comparison between the domain

## 2. OVERVIEW OF PCIE

## **2.1. Introduction**

PCIe stands for Peripheral Component Interconnect Express. This IP is used for attaching peripheral devices such as (SSD, GFx Card, Memory Controllers, etc.) onto a computer motherboard. These are the hard wired links which are embedded onto a SoC platform. This can be also used as addressing mechanism that discovers and configures devices into a system. PCIe is a high performance, input output interconnect for the peripherals in computing and communication platforms.

It is a serial point to pint interconnect between two devices. PCIe Slot comes in two configurations i.e., M.2 and CEM slot.

Fig 4: M.2 and CEM Slots

PCIe implements packet based protocol for information transfer. This IP also give scalable performance based on number of signal lanes implemented on the PCIe interconnect.

| PCI Express | Transfer Throughpu |            |           | ghput      | put       |  |

|-------------|--------------------|------------|-----------|------------|-----------|--|

| Version     | Rate               | x1         | x4        | x8         | x16       |  |

| 1.0         | 2.5 GT/s           | 250 MB/s   | 1.0 GB/s  | 2.0 GB/s   | 4.0 GB/s  |  |

| 2.0         | 5 GT/s             | 500 MB/s   | 2.0 GB/s  | 4.0 GB/s   | 8.0 GB/s  |  |

| 3.0         | 8 GT/s             | 984.6 MB/s | 3.94 GB/s | 7.88 GB/s  | 15.8 GB/s |  |

| 4.0         | 16 GT/s            | 1969 MB/s  | 7.88 GB/s | 15.75 GB/s | 31.5 GB/9 |  |

The above fig demonstrates the PCIe gen speed upon the number lanes implemented upon the system/SoC.

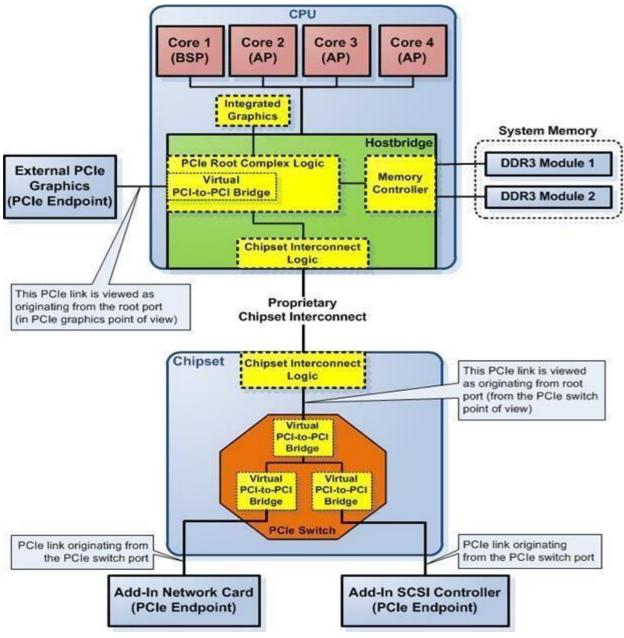

## 2.2. PCIe: Topology

PCIe is a set of wires which can contain up to 32 PCIe devices and each device can have 8 functions. PCIe topology is an upside down tree model. Every device sits on a bus and these devices can have one or two functions and each function is a standalone function. Every function is independent instantiation of a PCIe device. PCIe can support 256 buses, 32 devices and 8 function.

Fig 6: PCIe Tree Topology

#### 2.3. PCIe: Layered Architecture

PCI Express has been implemented as a layered architecture. This layered architecture has been broken into 3 layers i.e., Transaction layer, Data Link Layer, Physical layer. Physical layer has been divided into 2 blocks: Logical and Electrical.

| Configuration/OS | PCI Plug and Play Model                         |

|------------------|-------------------------------------------------|

| Software         | PCI Software Driver Model                       |

| Transaction      | Packet-based Protocol                           |

| Link             | Data integrity                                  |

|                  |                                                 |

| Physical [       | Point-to-point, serial, differential, hot plug  |

| Mechanical       | Various lane widths, interoperable form factors |

|                  |                                                 |

Fig 7: Layered Architecture

## Software Layer

This layer is responsible for instantiating various different types of transaction such as Posted and Non posted transaction to the devices which are connected on the PCIe link. PCI Express maintains backward compatibility with PCI. This layer generates the address mechanism which helps to discover the devices which are connected onto the system.

Types of Transaction generated by the layer:

- Non Posted: These are the transaction where the requester expects to receive a completion TLP (Transaction Layer Packet) from the device completing the request.

- Posted: Transaction where the requester does not expect to and will not receive a completion TLP.

| Transaction Type                        | Non-Posted or Posted |  |

|-----------------------------------------|----------------------|--|

| Memory Read                             | Non-Posted           |  |

| Memory Write                            | Posted               |  |

| Memory Read Lock                        | Non-Posted           |  |

| IO Read                                 | Non-Posted           |  |

| IO Write                                | Non-Posted           |  |

| Configuration Read (Type 0 and Type 1)  | Non-Posted           |  |

| Configuration Write (Type 0 and Type 1) | Non-Posted           |  |

Fig 8: Types of Transaction

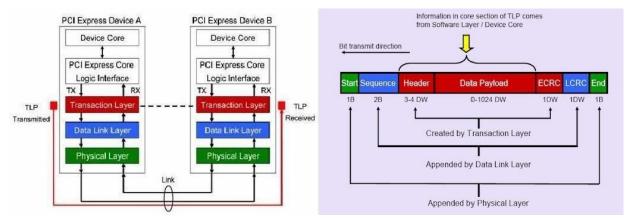

## Transaction Layer

This layer begins the process of building the transaction as a Packet which has to be send from one device to another. Types of transaction this layer request such as:

- Memory Read(MRd) or Memory Write (MRw): used to transfer data from or to a memory mapped location.

- I/O Read (IORd) or I/O Write (IOWr): used to transfer data from or to an I/O location. These transactions are restricted to support legacy end point device.

- Configuration Read (CfgRd) or Configuration Write (CfgWr): used to discover device capabilities, program features and check status in the 4KB PCI express configuration space.

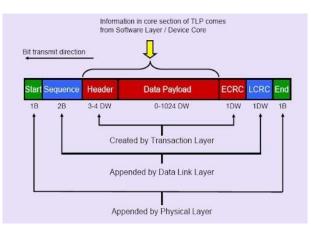

This layer is responsible for TLP creation on transmit side and TLP decoding on receiver side. This layer is responsible for Quality of service, Flow control, Transaction Ordering.

Fig 9: Transaction layer and TLP Assembly

Fig10: TLP field

#### Date Link Layer

This Layer is responsible for reliable conveying the TLPs to the Physical layer. This layer appends transaction layer packet sequence number and error detection cyclic redundancy codes (CRCs) to the data packets to maintain the data integrity between the chip set and the I/O controller.

This layer is responsible for DLLP creation on transmit side and DLLP decoding on receiver side. This layer is responsible for link error detection and correction and for ack/nak protocol.

This layer supports the link data integrity using ACK/NAK support and it also support low level power management.

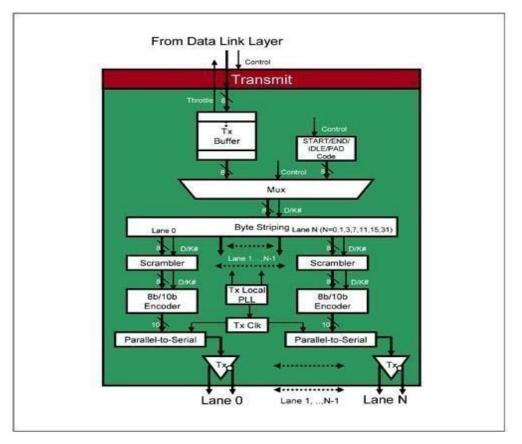

#### Physical Layer

Implements the dual simplex PCI Express channels. The physical layer sits at the bottom of the interface between external physical link and data link layer. It converts the outbound packets into a serialized bit stream that is clocked onto all the lanes of the link. This layer also recovers all the bit stream from all the lanes of the link at the receiver side.

The contents of the layer are conceptual and don't precise logic blocks but to the extent that designers do partition them to match the spec because of increasing high data transfer rates. This layer is also responsible for the bit, byte and symbol lock on the link.

Fig 12: Phy layer

As mentioned above the physical layer contains two blocks i.e. Logical and Electrical Block. Below points explain the functionality of the blocks.

Logical Block:

- 1. Encoding/Decoding/Scrambling

- 2. Reset, initialization

Electrical Block:

- 1. Tx and Rx

- 2. Clks, PLL and Data Recovery

- 3. Low Level Link Power Control (L0, L0s, L1, L2)

## 4. ERRORS ASSOCIATED WITH PCIE LINK

PCIe IP provides great mechanism for error handling and logging. This feature provides great debugging method to identifying errors associated with the PCIe link, device specific errors and SoC failures which is caused by the PCIe IP.

There are 2 two types of errors associated with the PCIe:

- 1. Uncorrectable Errors: these errors are further divided into 2 categories i.e., Non fatal errors which are handled by the device software and Fatal errors which are handled by the system software.

- 2. Correctable Errors: these errors are handled by hardware itself.

Uncorrectable Non-Fatal errors do not affect the PCIe fabric. PCIe fabric continues to work properly without any bug. In these type of errors, the data packet might lost or get corrupted. These type of error can't be fixed by the PCIe hardware.

Example of uncorrrectabke non-fatal error:

- Unsupported Request

- Unexpected Completion

- Completion Timeout

- Poisoned TLP

Uncorretable Fatal Errors can be corrected by the PCIe link reset as these errors get generated when link become unreliable to send the data on the link.

Example of uncorrectable fatal errors:

- Link Training error

- Malformed TLP

- De Skew Buffer Full

| Type of error                | Errors examples                | Pcie layer at which error<br>found |  |

|------------------------------|--------------------------------|------------------------------------|--|

| Correctable                  | Receiver Error                 | Physical                           |  |

| Correctable                  | Bad TLP                        | Link                               |  |

| Correctable                  | Bad DLLP                       | Link                               |  |

| Correctable                  | Replay Time-out                | Link                               |  |

| Correctable                  | Replay Number<br>Rollover      | Link                               |  |

| Uncorrectable - Non<br>Fatal | Poisoned TLP Received          | Transaction                        |  |

| Uncorrectable - Non<br>Fatal | ECRC Check Failed              | Transaction                        |  |

| Uncorrectable - Non<br>Fatal | Unsupported Request            | Transaction                        |  |

| Uncorrectable - Non<br>Fatal | Completion Time-out            | Transaction                        |  |

| Uncorrectable - Non<br>Fatal | Completion Abort               | Transaction                        |  |

| Uncorrectable - Non<br>Fatal | Unexpected<br>Completion       | Transaction                        |  |

| Uncorrectable - Fatal        | Training Error                 | Physical                           |  |

| Uncorrectable - Fatal        | DLL Protocol Error             | Link                               |  |

| Uncorrectable - Fatal        | Receiver Overflow              | Transaction                        |  |

| Uncorrectable - Fatal        | Flow Control Protocol<br>Error | Transaction                        |  |

| Uncorrectable - Fatal        | Malformed TLP                  | Transaction                        |  |

## Fig 13: Types of PCIe errors

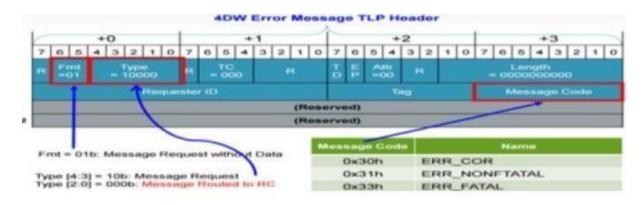

PCIe errors can be displayed by two methods:

1. By the Message transaction: which report the error to host.in this message packet there is a code field which signify the type of error.

Fig 14: Message Packet

Above TLP is routed towards the Root Complex.

| Message<br>Code | Name       | Description                                                    |

|-----------------|------------|----------------------------------------------------------------|

| 30h             | IFRR COR   | used when a PCI Express device detects a<br>correctable error  |

| 31h             |            | used when a device detects a non-fatal,<br>uncorrectable error |

| 33h             | IFRR FAIAI | used when a device detects a fatal,<br>uncorrectable error     |

Fig 15: Error Message

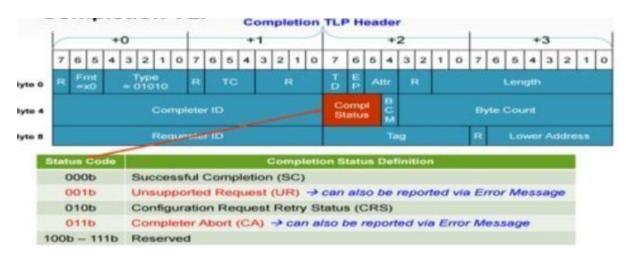

2. With the help of Transaction Completion: the acknowledgment packet which receiver send to the transmitter also has an error field in the packet.

Fig 16: Completion TLP

All above mentioned errors can be fixed by firmware software/ other patches form phy/BIOS.

## 5. PCIE: LINK TRAINING AND INITIALIZATION

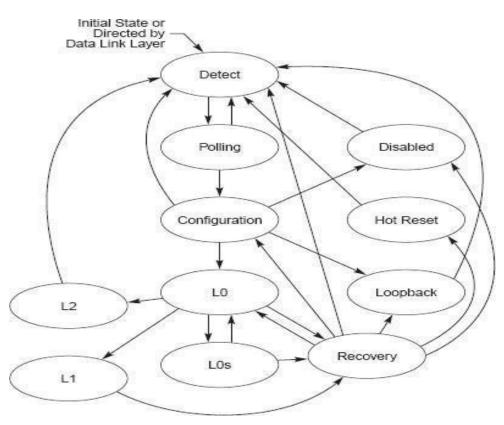

PCIe uses a Link training and initialization mechanism called LTSSM. This LTSSM process is control by the Physical layer. Therefore, link should get initialized properly before routing the data packets on the PCIe link. This process gets initialized automatically when the platform comes out of the reset.

PCIe port/link required to go through a series of link training before can be used to transfer or receiving the data.

Fig 17: LTSSM

The above LTSSM process is also followed when link configuration/equalization happens between the device and the controller for synchronization to make link stable. This LTSSM link training can also be used to recover unstable link to stable link.

## 5.1 Different States of PCIe LTSSM

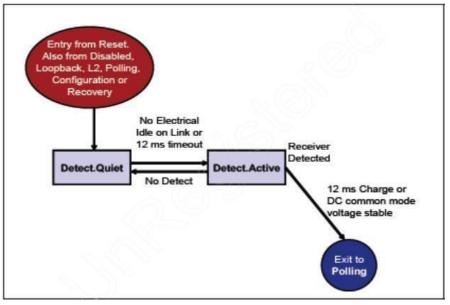

#### LTSSM - Detect State

This is the first state of the LTSSM FSM when the link comes out of the reset. When the link comes out of the reset it detects whether the other device is present or absent on the other side of the link. Detect state can be entered from other states also depending upon the scenario of the link.

Below figure explains the Detect State:

Fig 18: Link going from Detect to Polling

This is first state where PCIe link enters after the system comes out of the reset. Or, the host reset is executed by the software layer of the device/the root port controller. The link can be enter detect state from the following state:

- L2 State

- Disable State

- Recovery

- Polling

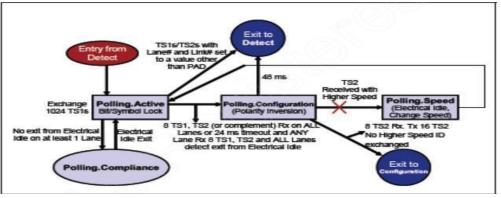

## LTSSM - Polling State

Polling state is the first state in the process of link Initialization. In this state, training sequence ordered sets (TS1 and TS2) gets exchanged between devices i.e. transmitting device and the receiver device.

This ordered sets gets exchanged on all the lanes which are present between the devices. These ordered set get only exchanged when bit / symbol lock get achieved.

Below fig explains what happen inside the polling state:

Fig 19: Polling State

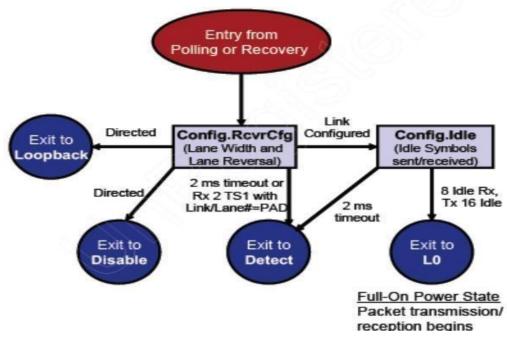

## LTSSM – Configuration State

This is the state where the lane number and link number get assigned between the different devices. In this state the upstream port (Root Complex) sends the TS1 ordered sets to the downstream device for begin the process of link and lane numbering. Once, this is done then TS2 packets get exchanged to determine the lane width.

Fig 20: Configuration State

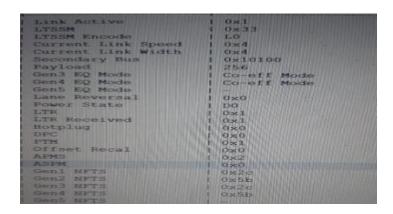

#### LTSSM - L0 State

L0 state is the active state of the PCIe which means the link is properly established between the devices. And, the link is ready to use for the transferring of data between the devices.

Below is the example when all the parameters get set properly when the link is in L0:

Work done:

Fig 21: L0

## 5.2 Power States associated with PCIe Link

There are different types of power states associated with the PCIe link as follows:

- L0s: L0s is the low power standby state of the link. Link can be entered in this state whenever it detects some idle time on the link by exchanging EIOS ordered sets. In this state both or either TX or RX can be in L0s. And, this is the state in which there is no need to tell the higher layer i.e., software layer.

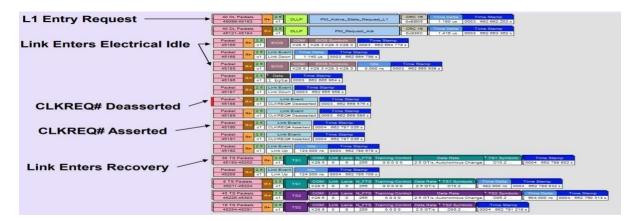

- L1: L1 is the conventional low power state of the PCIe link. This state can be achieved when ASPM is enabled. ASPM refers to Automatic State Power Management module which is present on the SOC. Here, the link can only be go into L1 when both the TX and RX agrees to go in the low power because here we have initimate the higher layer of the device also. And, this intimation is done by sending the PM\_Request\_DLLP from the device to the other device who is sitting at the farther end of the link.

- L1.1 and L1.2: L1.1 and L1.2 is the lowest power substate of the PCIe link. This link state can only be achieved when below 2 mentioned conditions are met:

- The LTR value of the device should be greater than the LTR threshold value which is programmed by the BIOS.

- CLKREQ# should be de-asserted.

Below are some the captures which are taken by the Protocol analyzer which demonstrates low power states:

• L0s:

|                           | Packet Re 2.5 Cink Event<br>166438 X1 Link Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mrd Trans initiated       | 230 Packets R+ 25 F13 COM F13 Symbols Time Delta Time Stamp<br>166439-166670 R+ 25 K28 5 K28 1 K28 |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                           | Link Tra         Ref         X1         Mem         MRd(32)         Length         Requester(0)         Tag         Address         1st BE         Last BE         VC ID         Explicit ACK           3         3796         Mem         00 00000         1         00 02:0         0x18         DE102500         0x1         0x0         0         Packet #16671         Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                           | Packet         Rr         2.6         TLP         Mem         MRd(32)         Length         Requested/D         Tag.         Address         1st BE         Last BE         LCRC         Time De           166520         x11         3796         00 00000         1         00 02 0         0x18         DE102500         0x1         0x41 C067E3         1.280 p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                           | Packet Rr 2.5 DLLP ACK AckNak_Seq_Num CRC.16 Time Data Time Stamp<br>166671 X1 DLLP 3796 0x7C92 128 000 ns 0059 738 082 008 s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Cp received               | Link Tra         Re         2.5         TLP         Cpl         CplD         Length         Requester/D         Tag         CompletenD         Status         BCM         Byte Crit         Link Addr         Data           d         732         732         10 01010         1         00.02.0         0x18         04.00.0         Sc         0x0 000000001 000000001         1 diversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Detected idle time (EIOS) | Packet Re. 2.5 EDG COM EDG Symbols Time Delta Time Stamp<br>166674 R. 2.1 EDG K28.5 K28.3 K28.3 K28.3 K28.3 192.000 ns 0059.738.082.808 s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                           | Spit Tra         Re         2.5         Mem         MRd(32)         RequestedD         CompletenD         Tag         IC         VO.010         Address         Status         Outs           1         00.00000         00.02.0         04.00.0         0x10         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Link down (LOs)           | Packat Re 26 Link Event<br>1966/76 Re 21 Link Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                           | Packet R+ 2.6 Link Event<br>166677 R+ x1 Link Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                           | 239 Packets R+ 2.5 F15 Symbols 166678-166917 R+ 2.5 K28 5 K28 1 K2   |

|                           | Packet<br>166921         Re.         2.5<br>x1         COM/<br>EIOS Symbols         Time Data         Time Stamp           40 000 ns         0059 . 736 088 128 s         40 000 ns         0059 . 736 088 128 s         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Fig 22: L0s State

• L1:

Fig 23: L1 State

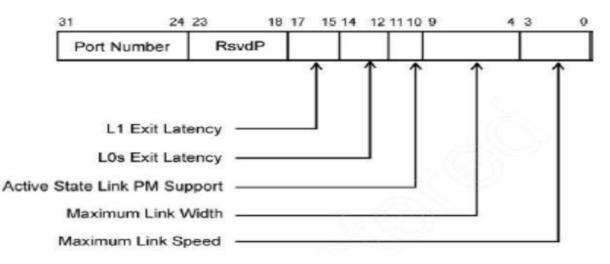

## **5.3 PCIe Configuration Register related to LTSSM**

This section describes some of the registers which are get configured during the link initialization and training of the PCIe link.

- Link Capability Register

- Link Status Register

- Link Control Register

## Link Capability Register

Below fig describes the structure of link capability register.

Fig 24: Link Capability register

<u>Maximum link speed</u> field specifies the maximum speed of a PCIe link which it can provide for data transmission. For example: if the field is set to 0010b that means the link set at Gen2 speed.

<u>Maximum link width</u> field specifies the width of the link. And, this register is updated by hardware when the ltssm start from the detect state or it is hard-wired. For example: 010000b: x16 width

Link Status Register

Below fig describes the structure of link status register.

Fig 25 : Link Status Register

Link status register describes the status of the link after the polling state when all the negotiation between the controller and the device.

Link speed field is updated during the polling state on which both the Tx and Rx has agreed upon.

<u>Negotiated Link width</u> field represented the actual width of the link. Example: if controller exhibits **x8** and device exhibits x4 then the nlw will be x4.

<u>Link training error</u> field specifies the training errors which can be occurred during link initialization or training. Example: if the link gets stuck in any of the LTSSM says(Recovery) then this field will get updated.

## Link Control Register

Below fig describes the structure of link control register.

Fig 26: Link Control Register

Link Control Register is responsible for the controlling the state of the link like want to disable the link or retrain the link at appropriate speed or configuration.

Link Disable field is both read and write enable. This field is used to disable the link or check if the link is enable or disable.

<u>Retrain Link</u> field this field is very helpful in training the link from any error if it occurred on the link.

Extend Sync field is used for sending the fast training sequence ordered sets (FTS) in L0s state of the link following by the SKIPOS in L0.

## 6. SYSTEM POWER STATE AND DEVICE POWER STATE

In the desktop/mobile segment SoC provide several system state and device states in order to save the power. Advanced Configuration and Power state (ACPI) provides to save the power.

ACPI system state varies from S0(full operational state) to S5 (lowest power saving state). The transition of system state is totally controlled by the operating system; based on the input given by the user as Sleep/Hibernate or enter into low power state when there is inactivity timeout. When the system is in S0 considered as active operational and when it is in S5 considered as shutdown mode.

The system can only be transits from S5 to S0 only by the wake event from the OS. All these S- states have their different latencies for entry and exit. Below mention items relates the possible link states of PCIe:

- S0(operational state): this state is the fully operational working state of the system. In this state system can enter into low power mode. From here the system can enter C2/3 with the support of PCIe IP through the flow credit mechanism. The downstream devices consume the flow credits which indicates to BME on the system. Then the control logic of the power management decides to go into low power state.

- S1 Standby State: this state is considered as the stand by state and the entry and exit latency of this state is very less. In this state all the clocks and PLLs are on but depending on the system parameters devices can go into lower power device state and PCIe link will be in either L1 or L0s state.

- S3 (Sleep State) and S4 (Hibernate State): S3 is the low latency state of the system. In this state only memory contents get saved and other device contents go for a toss. S4 is lowest deep sleep state of the system with longest latency of entry/exit flow. In this state all the system contents get saved into main memory of the system. All the clocks and PLLs get shutdown except the wake logic. The PCIe link can enter into L2 or L3 depending upon the endpoint capability.

- S5 (Shutdown State): S5 is the complete shutdown state of a system in which no content of the system gets saved. This state requires full boot process to wake up.

Below table explains the relationship between the system and PCIe link state:

| S-state    | Permissible L-state                                 |  |

|------------|-----------------------------------------------------|--|

| <b>S</b> 1 | L0s or L1                                           |  |

| S1/POS     | 1.2                                                 |  |

| S3         | L2 or L3, where L2/L3 Ready is a transitional state |  |

| S4         | L2 or L3, where L2/L3 Ready is a transitional state |  |

| <b>S</b> 5 | L2 or L3, where L2/L3 Ready is a transitional state |  |

#### Fig 27: State and L State

#### **Device Power State**

ACPI also specifies the Different Power or D states of the device. Below mentioned points will explain the relation between the PCIe link state and Device D state:

- D0: this state is the full ON state of the device in which it is fully operational. In this state PCIe link can be in L0s or in L0. For example, link is configured to go in L0s then ASPM will transit the TX, RX of both the side into L0s. The link can go into L1 either through hardware ASPM or by the OS make device to go into D1, D2 State.

- D1, D2: In both D1 or D2 state the PCIe link should be in L1 state. The only difference between D1 and D2 state is power saving percentage. D2 save more power than D1.

- D3: D3 is the lowest deep sleep D state of the device in which device become totally un operational. As all the power supply to the device get cut off and it is also known as run time D3 state. And in this state the PCIe link will be in L2. And, device can only be exit to D0 by the Wake signal or the PERST signal on the PCIe link.

Below table explains the relationship between the system and PCIe link state:

| Downstream Component<br>D-state | Permissible Upstream<br>Component D-state | Permissible L-state |

|---------------------------------|-------------------------------------------|---------------------|

| D0                              | D0                                        | L0, L0s, or L1      |

| D1                              | D0-D1                                     | LI                  |

| D2                              | D0-D2                                     | L1                  |

| D3 <sub>hot</sub>               | D0-D3 <sub>hot</sub>                      | L1 or L2/L3 ready   |

| D3 <sub>cold</sub>              | D0-D3 <sub>cold</sub>                     | L2 or L3            |

## 7. STATEMENT OF PROBLEM BASED ON IDENTIFIED RESEARCH GAPS

There are increasingly number of digital/analog/mixed signal circuits in microprocessors and SOCs. A major chunk of mixed-signal circuits are high-speed I/O links, including serial buses such as PCIE and parallel buses such as DDR. Post-si validation is a major step for any product manufacturing industry who is engaged in releasing the products like mobile or desktop into the market. Post-silicon validation of high-speed input/output (HSIO) links can be crucial for making a product release qualification. Peripheral component interconnect express (PCIe) is a high-performance serial interconnect architecture widely used in the computer industry, and one of the most complex HSIO IP. PCIe data rates or throughput increases on every new generation.

PCI-Express (PCIe) is mainstream interface of today's system of chip which requires high speed data transmission with high performance and throughput. It is being used immensely in different applications like computer cards, graphic cards, automotive, networking, and industrial and consumer applications. In automobile world or automotive applications, PCIe is useful for processing of data coming at a very high speed from real-time graphics and video processing. And hence, all these reasons make PCIe as an important part of today application.

Therefore, PCIe IP should be validated in all the possible scenarios like:

- 1. The link should always be stable and be in L0 State.

- 2. The link should work properly even with the power management flows enabled.

- 3. The link should work in all operating condition i.e.; it should be independent of process variation (PVT).

Thus, post si validation boundaries have exponentially increased in latest multi-core projects, not only due to their complex architecture, but also because the PRQ (Product release Qualification) demands keep getting smaller, as measured from first available prototype units until high-volume manufacturing approval. CPU validation complexity increases are due to the need to support existing legacy features while adding new features like new macro-instructions, new micro-architectural functionality and new power management mechanism.

Therefore, this report gives the solution of this problem that how using these debugging tools in effective way leads to good validation in terms of performance and accuracy.

## 8. POST SILICON VALIDATION PARADIGM

## Post Silicon Validation Paradigm

Post silicon validation paradigm is a process which is followed for validating the IPs on the soc. And, this process is the base on which we will design our validation strategy for an IP which present in the soc.

The post silicon validation paradigm involves 6 phases such as:

- Power On Ready

- Power on Exit

- Volume Validation

- Tested

- o Proven

- PRQ Ready

Fig29: Phases in Post Silicon Validation

## Power on Ready

Power on is a crucial event and very first step in a project towards the feature enablement and validation. Power On enables volume deployment of silicon and platform for further detailed validation. Power on event helps to bring out early critical issues with silicon and helps to judge the initial health of the silicon.

#### Power on Exit

Once Power on scope and schedule is defined. Power on exit criteria (Goals) needs to communicate to all the stakeholders by power on lead. Power on exit goals are measured mainly on four vectors i.e., functional, stress and stability.

## Volume Validation

After Power On exit phase then Checkout happens i.e., the volume validation starts by the all stake holders that means the SUT remains under test for long no test iteration cycle.

## Tested and Proven

In tested and proven phase we identify no of bugs that are detected and the no of bugs that get fixed in the silicon. A report is made by the project owner and to represented to the management. And from this efficiency and quality of validation gets measured.

## PRQ Ready

PRQ ready refers to the Production Ready Quality i.e., the quality silicon is ready and can be go into the market and can be used by the end user. This silicon is free from all hardware and software bugs.

#### 8.1 Tools Used for Execution and Debugging in Post Silicon Functional Validation

The functional validation is carried out by two types of validation i.e. windows based validation and other is using the synthetic content.

Windows based Validation (OSBV) involves some OS based application which run SUT which keep the system under test for a long time to find the bugs. The OSBV application that are used for e.g.: SOLAR, RW etc.

SOLAR: This application is used to Sx cycling that means to test PM flows on the RVP and keeps the SUT under stress. PM flows involves: warm reset, cold reset and SX cycling such as S3, S4, and S5.

RW: This is a RW tool which is used to check the device enumeration in the PCIe which gives the information about the devices connected to the PCIe slot on the system. This application gives the information about the BDF of the device that is connected on the system.

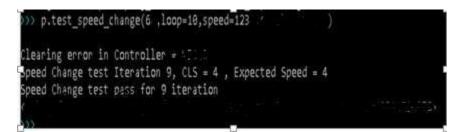

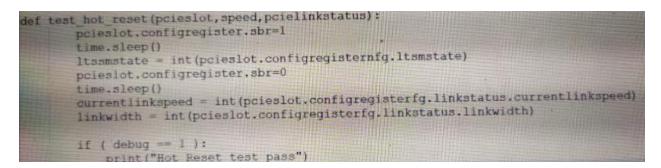

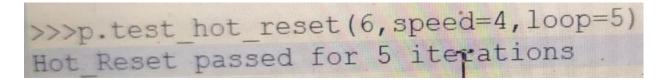

Synthetic Content Validation refers to the test cases which are written in a high level language like Python. This type of content is used to validate the link status, features and registers of the PCIe IP. And, also validates the functionality of the IP in low power states. This type of content involves the features like link enable/disable, speed change, hot reset etc. And to run this type of content we need hardware probes like DCI, XDP which connects on to the system and gives the access to the register of the IP.

There is another tool called Status Scope Dump which is used to analyze and collect the logs when the system gets unexpectedly shut down or getting a blue screen error. Now there are some hardware tools which are used for debugging such as:

#### TLA: Tektronix Logic Analyzer

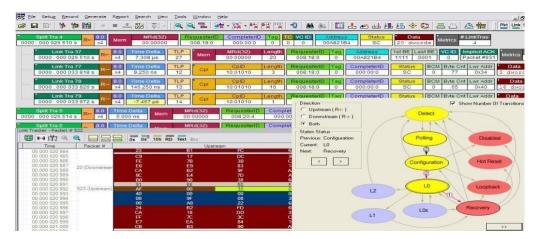

This tool used to detect and analyze the link state of the PCIe link and also can be used to measure the latencies of the different states of the link. Below fig explains the output window of the TLA.

Fig30 : TLA GUI

Oscilloscope : this tool is used to measure different voltage signal or the power to the PCIe slot.

And to debug at the traffic level / the packets which are getting exchanged between the Tx and Rx then we use Lecroy Protocol analyzer

Fig 31: Lecroy Protocol Analyzer

# 9. Work done, partial simulation/hardware implementation, partial Results and Discussion.

#### 9.1 Overview of work done

In functional validation of PCIe it requires three types of work to do as:

- Implementing PCIe and System validation test cases which have dependency on PCIe.

- Creating all the end user case scenario before the product got PRQ.

- Analyzing and debugging of the cases to resolve the bug.

- All these test cases

#### 9.2 Test cases implemented with OSBV

Scenario 1: To test PCIe devices get enumerated when connect on the SoC/System

Passing Criteria : All the devices should get there unique BDF (Bus,Device,Function) that means no device should get unaddressed.

To check this scenario we have a tool called Read Write which gives all the information about BDF assigned to each device.

RW Tool: This is an application which is used for verifying the enumeration of the device such as BDF of the device and also to verify the device Id.

•

| 🔣 PCI                                                                                                                                                               |                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| E E E I C                                                                                                                                                           | Refresh                                              |

| Bus 00, Device 1C, Function 04 - Intel Corporation PCI-to-PCI Bridge (PCIE)                                                                                         | Info Text Summary                                    |

| Bus 00, Device 1C, Function 04 - Intel Corporation PCI-to-PCI Bridge (PCIE)<br>Bus 00, Device 1C, Function 05 - Intel Corporation PCI-to-PCI Bridge (PCIE)          | Device/Vendor ID 0x1D188086<br>Bevision ID 0x85      |

| Bus 00, Device 1C, Function 07 - Intel Corporation PCI-to-PCI Bridge (PCIE)                                                                                         | Class Code 0x060400                                  |

| Bus 00, Device 1D, Function 00 - Intel Corporation EHCI USB Controller<br>Bus 00, Device 1E, Function 00 - Intel Corporation PCI-to-PCI Bridge                      | Cacheline Size 0x10<br>Latency Timer 0x00            |

| Bus 00, Device 1F, Function 00 - Intel Corporation ISA Bridge                                                                                                       | Interrupt Pin INTA                                   |

| Bus 00, Device 1F, Function 02 - Intel Corporation AHCI Controller                                                                                                  | Interrupt Line IRQ17<br>BAR1 0x0000000               |

| Bus 00, Device 1F, Function 03 - Intel Corporation SMBus Controller<br>Bus 00, Device 1F, Function 06 - Intel Corporation Data Acquisition/Signal Processing C      | BAR2 0x0000000                                       |

| Bus 01, Device 00, Function 00 - Altera Corporation Controller (PCIE)                                                                                               | Primary Bus# 0x00<br>Secondary Bus# 0x09             |