# DESIGN AND ANALYSIS OF A LOW POWER AND HIGH PERFORMANCE 10T SRAM CELL AT 32 NM TECHNOLOGY NODE

A DISSERTATION REPORT

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE

OF

## **MASTER OF TECHNOLOGY**

IN

**VLSI DESIGN & EMBEDDED SYSTEMS**

SUBMITTED BY:

### **PUNEET YADAV**

### 2K21/VLS/21

UNDER THE SUPERVISION OF

### **Prof. POORNIMA MITTAL**

ELECTRONICS & COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)Bawana Road, Delhi-110042

MAY 2023

**Puneet Yadav**

## **ELECTRONICS & COMMUNICATION**

### ENGINEERING

#### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)Bawana Road, Delhi-110042

### **CANDIDATE'S DECLARATION**

I, Puneet Yadav, Roll No. 2K21/VLS/21 student of M. Tech (VLSI & Embedded systems), hereby declare that the project Dissertation titled **"Design and Analysis of a Low Power and High Performance 10T SRAM Cell at 32 nm Technology node"** which is submitted by me to the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology is unique and has not been copied without proper citation. This work has never been used to give a degree, diploma associateship, fellowship, or other equivalent title or recognition.

Place: Delhi Date: 30<sup>th</sup> May, 2023 Puneet PUNEET YADAV 2K21/VLS/21

# **ELECTRONICS & COMMUNICATION**

### ENGINEERING

#### DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)Bawana Road, Delhi-110042

### **CERTIFICATE**

I hereby certify that the Project Dissertation titled "Design and Analysis of a Low Power and High Performance 10T SRAM Cell at 32 nm Technology node" which is submitted by Puneet Yadav, 2K21/VLS/21, to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the prerequisite for the award of the degree of Master of Technology, is a documentation of the student's projectwork completed under my supervision. To the best of my knowledge, this work has never been submitted in part or in full for any degree or diploma at this university or anywhere else.

Prof. Poornima Mittal

Supervisor, ECE, DTU

Place: Delhi Date: May 30, 2023

## ACKNOWLEDGMENTS

With immense pleasure, I take this opportunity to express sincere gratitude to my supervisor, **Prof. Poornima Mittal** for her support, guidance, and words of encouragement throughout the present study. She has brought out the best in me through her exemplary guidance and invaluable support at every step of my research work.

With profound honor, I would like to express my heartfelt appreciation to the esteemed Head of the Department, Prof. O. P. Verma for his exceptional leadership, guidance, and support throughout my academic journey. Under your guidance, the department has flourished, providing us with a stimulating and enriching learning environment.

I would also like to express my deepest gratitude to the exceptional faculty members who have played a pivotal role in my educational journey. Your dedication, knowledge, and unwavering support have shaped my path and laid a strong foundation for my future endeavors. Thank you for your invaluable contributions, and I am truly honored to have been your student.

I am also thankful to Ph.D. scholars Bhawna Rawat and Yogita Chopra for their constant support and encouragement. My heartfelt thanks are also due to my M. Tech classmates Mahima, Shivam, Stuti, Manisha, and Deberjeet for their endearment and association that brightened the days of my research work.

From the core of my heart, I wish to acknowledge my father Dr. G.S. Yadav, mother Seema Yadav, sister Dr. Pooja Yadav and brother-in-law Dr. Prem Chand Gyani who always stood by my side throughout my study. I am deeply indebted for their invaluable contribution to what I am as a person.

Closing with a note of thanks to all those who strive every day for the development of India and have the wish to see it growing each day because that is our combined goal as a nation.

> Puneet Yadav 2K21/VLS/21 MTech: VLSI Design and Embedded System (2021-2023)

## ABSTRACT

Memory is known to be one of the most crucial parts of any electronic system. However, a class of memory called the cache memory is even more crucial among the type of memories since it is the one working closely in synchronization with the central processing unit. There are millions of SRAM cells inside cache memory. SRAM cells must therefore possess a few essential attributes for cache memory to be reliable, including low dynamic and static power consumption, high data stability, and low read latency.

A comprehensive review of the design and analysis of SRAM cells are performed, focusing on the fundamental building block, the SRAM cell, and its critical performance parameters. The aim is to provide a concise overview of the key concepts and challenges involved in SRAM cell design, highlighting recent advancements and future directions. The review begins with an introduction to SRAM and its significance in various applications. It explores the basic structure and operation of an SRAM cell, emphasizing the importance of stability, read and write capabilities, and power consumption. The different SRAM cell topologies are discussed, along with their advantages and trade-offs. The critical design considerations of SRAM cells, including noise immunity, process variations, and leakage current. Various techniques for improving the stability of SRAM cells, such as the use of feedback and assist circuits, are examined. Moreover, the impact of scaling technologies, such as process technology nodes and transistor scaling, on SRAM cell performance is explored.

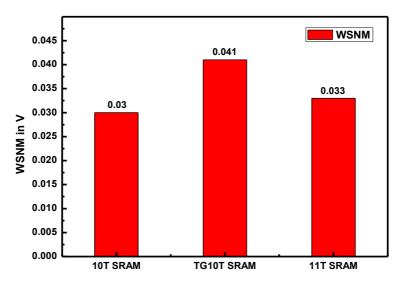

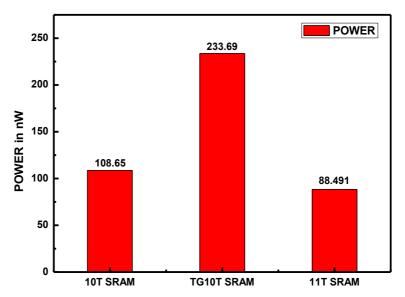

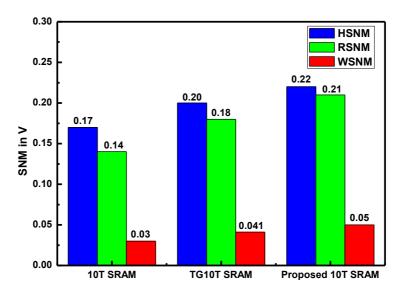

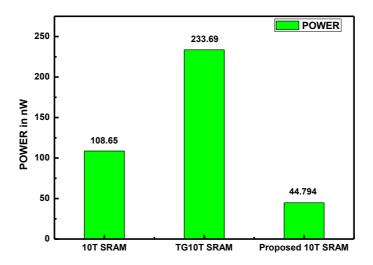

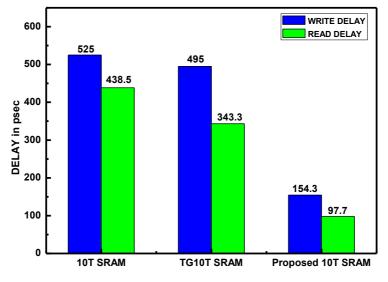

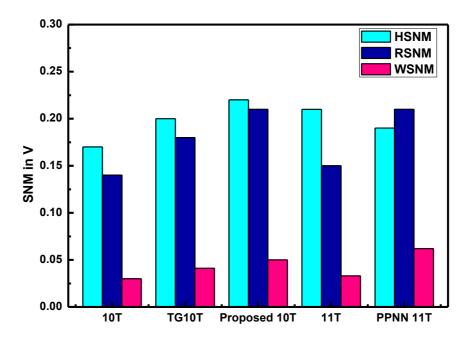

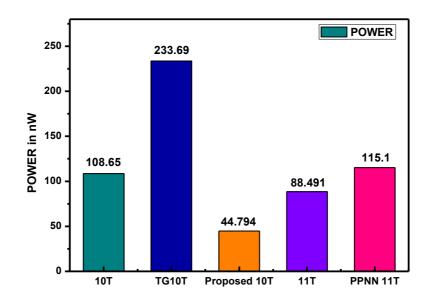

Additionally, the analysis of SRAM cell performance metrics, including read and write access times, write margin, stability, and power dissipation have been studied. The influence of key parameters, such as supply voltage, transistor sizing, and load capacitance, on these metrics is discussed. Furthermore, the impact of process variations on yield and reliability is addressed, along with reliability-enhancement techniques. To successfully incorporate these qualities, a comparative analysis of different 10T and 11T SRAM cells has been performed. The performance of the conventional TG10T and 11T SRAM models are compared to the 10T SRAM to showcase enhancements obtained. TG10T SRAM cell deploys two transmission gates instead of two NMOS access

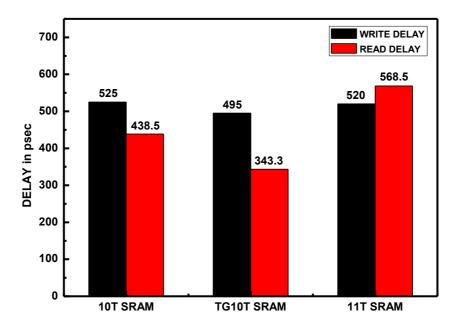

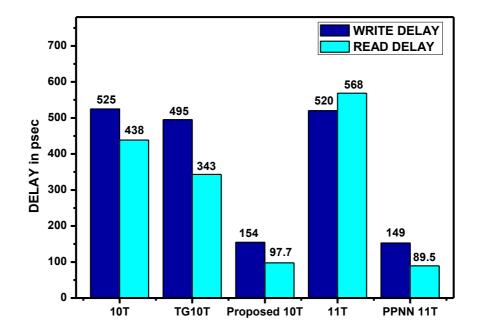

transistors to strengthen writing ability. It also employs two additional buffer transistors so that read stability can be enhanced. The TG10T SRAM cell is proven to be more enhanced in almost every aspect but it consumes more power. The read SNM and write SNM are found to be the largest in the TG10T SRAM cell. The power dissipated by the TG10T cell (i.e., 233.69nW) is approximately two times as compared to the 10T SRAM cell (i.e., 108.65nW) and 11T SRAM cell (i.e., 88.491nW). The analysis also shows that both read and write delay is minimal in TG10T SRAM cells. The read delay is 343.3 psec and the write delay is 494 psec respectively.

A 10T SRAM cell has been proposed and comparison between of different existing 10T and 11T SRAM cells has been performed. The power consumption and read-write behaviors of all the SRAM cells are studied. The power consumed by the TG10T cell (i.e., 233.69nW) is approximately two times in contrast to the 10T SRAM cell (i.e., 108.65nW) and five times when collated to the proposed 10T SRAM cell (i.e., 44.794nW). The analysis associated depicts that the read and write delay is minimum in the proposed 10T SRAM (i.e., 97.7psec & 154.3psec) respectively. All simulations are carried out using LTSPICE software operating at 0.5 Volt in 32 nm CMOS process technology. The proposed transmission gate based 10T SRAM cell consumes minimum power and has better overall read stability as compared to the other designs. The review concludes by highlighting emerging trends and challenges in SRAM cell design, including the exploration of novel device architectures, non-volatile SRAM, and low-power designs for energy-efficient computing systems. It emphasizes the need for continued research and innovation to address the increasing demands for higher density, lower power consumption, and improved reliability in future SRAM cell designs.

A comprehensive overview of the design and analysis of SRAM cells serves as a valuable resource for researchers, engineers, and students working in the field of digital integrated circuit design, offering insights into the current state of SRAM cell technology and potential future directions.

## CONTENTS

| Cano | didate  | 's Declaration                            | ii   |

|------|---------|-------------------------------------------|------|

| Cert | ificate |                                           | iii  |

| Ackr | nowled  | lgment                                    | iv   |

| Abst | ract    |                                           | v    |

| Cont | tent    |                                           | vii  |

| List | of Fig  | ures                                      | X    |

| List | of Tab  | bles                                      | xii  |

| List | of Abl  | previations                               | xiii |

|      |         | CHAPTER 1 INTRODUCTION                    | 1    |

| 1.1  |         | SRAM Array                                | 1    |

|      | 1.1.1   | Conventional Six Transistor Cell          | 3    |

|      | 1.1.2   | Data Hold Operation                       | 4    |

|      | 1.1.3   | Write Operation                           | 5    |

|      | 1.1.4   | Read Operation                            | 6    |

| 1.2  |         | Motivation                                | 8    |

| 1.3  |         | Objectives                                | 8    |

| 1.4  |         | Methodology                               | 9    |

| 1.5  |         | Thesis Organization                       | 10   |

|      |         | CHAPTER 2 LITERATURE REVIEW               | 12   |

| 2.1  |         | Comprehensive Summary of Past Work        | 12   |

| 2.2  |         | Research Gap                              | 20   |

|      |         | CHAPTER 3 CHARACTERISTIC COMPARISON       | 21   |

|      |         | FOR DIFFERENT EXISTING 10T AND 11T        |      |

|      |         | SRAM CELLS                                |      |

| 3.1  |         | Overview of SRAM Cells                    | 22   |

|      | 3.1.1   | 10T SRAM cell with Source biased inverter | 23   |

|      | 3.1.2   | Transmission gate based 10T SRAM cell     | 24   |

|      | 3.1.3   | Fully Differential 11T SRAM cell          | 25   |

|      | 3.1.4   | PPNN 11T SRAM cell                        | 26   |

| 3.2   | Cell Sizing                                                       | 28 |

|-------|-------------------------------------------------------------------|----|

| 3.3   | Transient Analysis                                                | 30 |

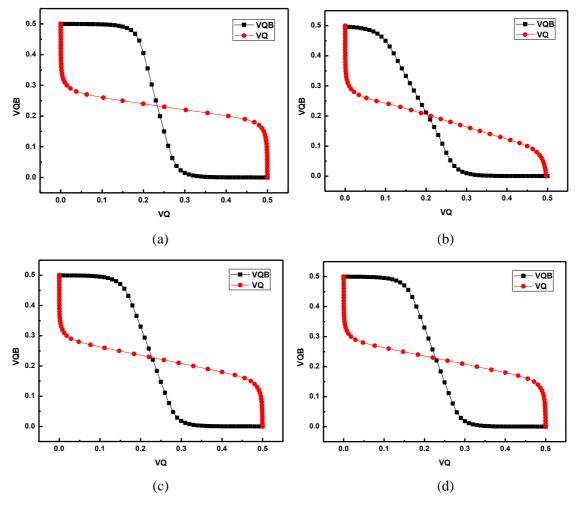

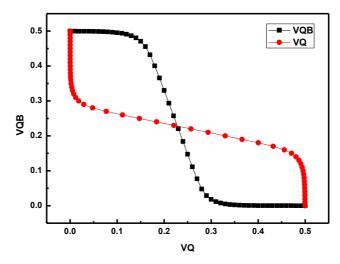

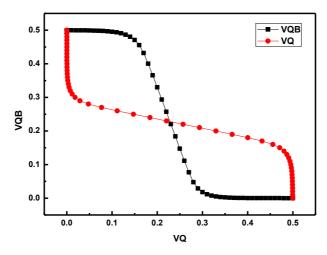

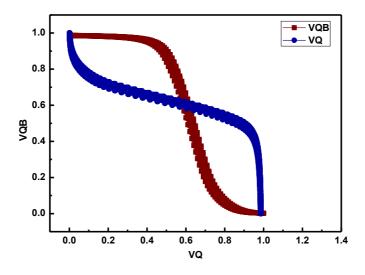

| 3.4   | Data Stability                                                    | 32 |

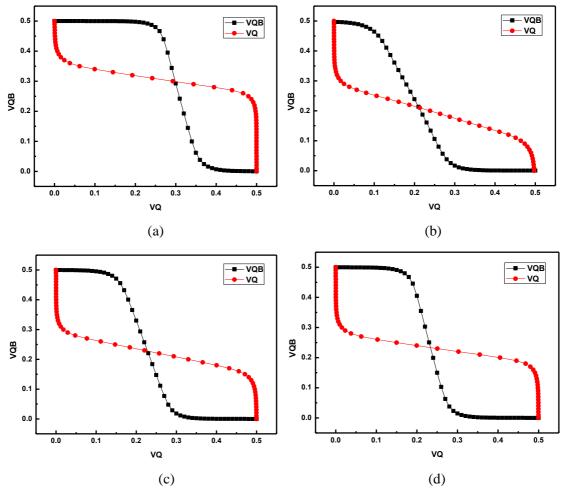

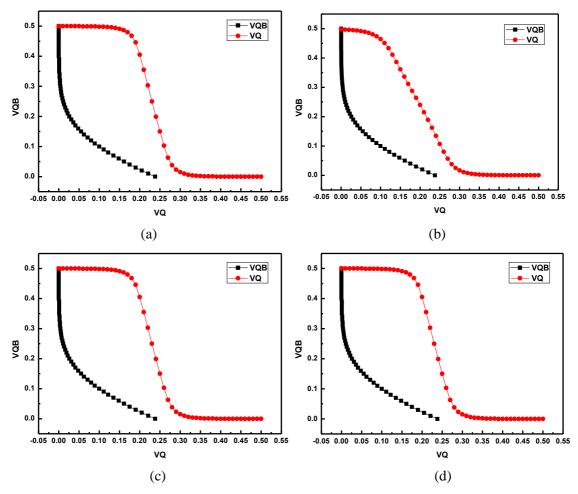

| 3.4.1 | Hold Static Noise Margin (RSNM)                                   | 32 |

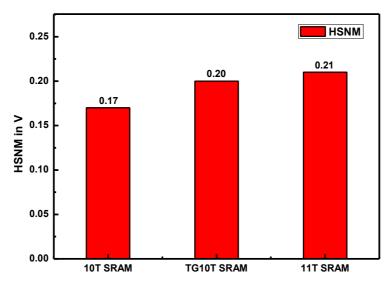

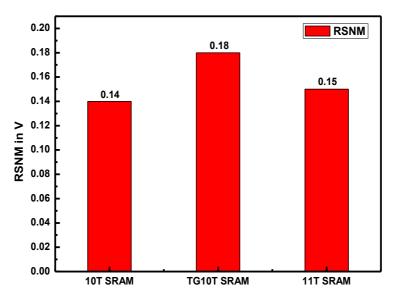

| 3.4.2 | Read Static Noise Margin (HSNM)                                   | 34 |

| 3.4.3 | Write Static Noise Margin (WSNM)                                  | 36 |

| 3.5   | Power Consumption                                                 | 38 |

| 3.6   | Read and Write Delay                                              | 39 |

| 3.7   | Important Results                                                 | 40 |

|       | CHAPTER 4 PROPOSED TRANSMISSION GATE                              | 42 |

|       | BASED 10T SRAM CELL                                               |    |

| 4.1   | Architecture and Working of Proposed 10T cell                     | 43 |

| 4.2   | Dimensions in the Proposed Cell                                   | 44 |

| 4.3   | Transient Analysis                                                | 46 |

| 4.4   | Data Stability                                                    | 47 |

| 4.4.1 | Hold Static Noise Margin                                          | 47 |

| 4.4.2 | Read Static Noise Margin                                          | 49 |

| 4.4.3 | Write Static Noise Margin                                         | 50 |

| 4.5   | Monte Carlo Analysis                                              | 51 |

| 4.6   | Important Results                                                 | 52 |

|       | <b>CHAPTER 5 PERFORMANCE COMPARISON OF</b>                        | 54 |

|       | PROPOSED CELL WITH OTHER EXISTING                                 |    |

|       | CELLS                                                             |    |

| 5.1   | Comparison of proposed cell with different 10T SRAM cells         | 54 |

| 5.1.1 | Data Stability                                                    | 55 |

| 5.1.2 | Power consumption                                                 | 56 |

| 5.1.3 | Read and Write Access Delay                                       | 57 |

| 5.2   | Comparison of proposed cell with different 10T and 11T SRAM cells | 59 |

| 5.2.1 | Data Stability                                                    | 59 |

| 5.2.2 | Power consumption                                                 | 61 |

| 5.2.3 | Read and Write Access Delay                                       | 62 |

| 5.3   | Important Results                                                 | 63 |

|     | CHAPTER 6 CONCLUSION AND FUTURE SCOPE | 65 |

|-----|---------------------------------------|----|

| 6.1 | Conclusion                            | 65 |

| 6.2 | Future Scope                          | 67 |

|     | PUBLICATION LIST                      | 69 |

|     | REFERENCES                            | 70 |

## **LIST OF FIGURES**

| Fig. No.  | Fig. No. Caption of Figure                                                                            |    |  |

|-----------|-------------------------------------------------------------------------------------------------------|----|--|

| Fig. 1.1  | Typical arrangement of an SRAM array                                                                  | 2  |  |

| Fig. 1.2  | Typical 6T SRAM cell                                                                                  | 3  |  |

| Fig. 1.3  | Transfer curves of the two inverters in an SRAM cell                                                  | 4  |  |

| Fig. 1.4  | Transient simulation of a write operation in a 6T SRAM cell                                           | 5  |  |

| Fig. 1.5  | Modified transfer curves of the inverter while writing (a)<br>Write Zero (b) Write One                | 5  |  |

| Fig. 1.6  | Transient simulation of a read operation                                                              | 6  |  |

| Fig. 1.7  | Modified transfer curves during a read operation                                                      | 7  |  |

| Fig. 3.1  | Schematic of 10T SRAM cell with source biased inverter                                                | 23 |  |

| Fig. 3.2  | Schematic of TG10T SRAM cell                                                                          | 24 |  |

| Fig. 3.3  | Schematic of Fully differential 11T SRAM cell                                                         | 26 |  |

| Fig. 3.4  | Schematic of PPNN 11T SRAM cell                                                                       | 27 |  |

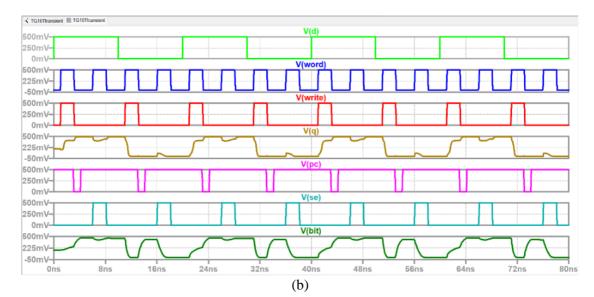

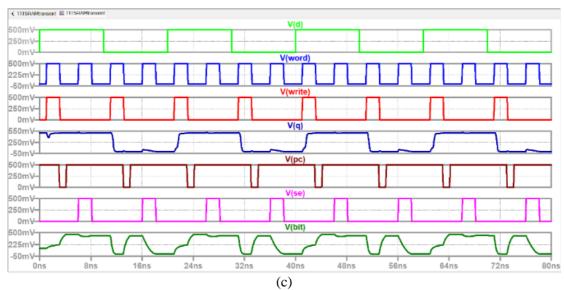

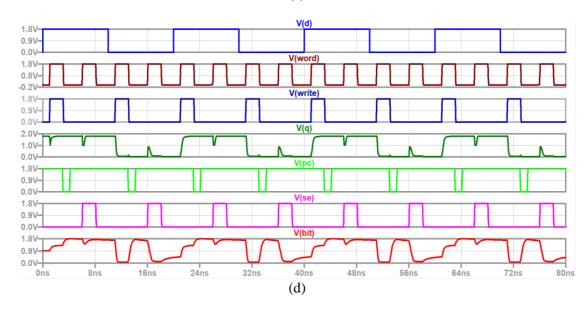

| Fig. 3.5  | Transient analysis of (a) 10T SRAM cell, (b) TG10T SRAM cell, (c) 11T SRAM cell, and (d) PPNN11T Cell | 31 |  |

| Fig. 3.6  | Butterfly curves for HSNM (a) 10T SRAM, (b) TG10T SRAM, (c)11T SRAM, and (d) PPNN11T Cell             | 33 |  |

| Fig. 3.7  | Comparison of HSNM of various SRAM cells                                                              | 34 |  |

| Fig. 3.8  | Butterfly curves for RSNM (a) 10T SRAM, (b) TG10T SRAM, (c)11T SRAM, and (d) PPNN11T Cell             | 35 |  |

| Fig. 3.9  | Comparison of RSNM of various SRAM cells                                                              | 36 |  |

| Fig. 3.10 | Butterfly curves for WSNM (a) 10T SRAM, (b) TG10T SRAM, (c)11T SRAM, and (d) PPNN11T Cell             | 37 |  |

| Fig. 3.11 | Comparison of WSNM of various SRAM cells                                                              | 38 |  |

| Fig. 3.12 | Comparison of Power Consumption of various SRAM cells                                                 | 38 |  |

| Fig. 3.13 | Comparison of Delay of various SRAM cells                                                             | 40 |  |

| Fig. 4.1 | Schematic of Proposed TG based 10T SRAM cell                                     | 43 |

|----------|----------------------------------------------------------------------------------|----|

| Fig. 4.2 | A conventional 6T cell illustrating SRAM sizing                                  | 44 |

| Fig. 4.3 | Transient analysis of the Proposed 10T cell                                      | 45 |

| Fig. 4.4 | Butterfly curve for HSNM of Proposed cell                                        | 48 |

| Fig. 4.5 | Butterfly curve for SNM of Proposed cell                                         | 49 |

| Fig. 4.6 | Butterfly curves for WSNM of Proposed cell                                       | 50 |

| Fig. 4.7 | Monte Carlo simulation of RSNM of proposed 10T cell                              | 52 |

| Fig. 5.1 | Comparison of Static Noise Margin for various 10T cells                          | 55 |

| Fig. 5.2 | Comparison of Power Consumption for various 10T cells                            | 56 |

| Fig. 5.3 | Comparison of Delay for various 10T cells                                        | 58 |

| Fig.5.4  | Comparison of Static Noise Margin of proposed cell with various 10T and 11 cells | 60 |

| Fig. 5.5 | Comparison of Power consumption of proposed cell with various 10T and 11 cells   | 61 |

| Fig. 5.6 | Comparison of Delay of proposed cell with various 10T and 11 cells               | 63 |

## LIST OF TABLES

| Table No. | Caption of Table                                           | Page<br>No. |

|-----------|------------------------------------------------------------|-------------|

| Table 2.1 | Parametric Analysis of various 9T and 11T SRAM cells       | 18          |

| Table 2.2 | Parametric Analysis of various 10T differential SRAM cells | 19          |

| Table 3.1 | Dimensions for 10T cell                                    | 28          |

| Table 3.2 | Dimensions for TG10T cell                                  | 28          |

| Table 3.3 | Dimensions for 11T cell                                    | 29          |

| Table 3.4 | Dimensions for PPNN 11T cell                               | 29          |

| Table 4.1 | Dimensions for Proposed 10T cell                           | 45          |

## LIST OF ABBREVIATIONS

| S. No. | Abbreviation | Full Name                       |  |  |  |  |

|--------|--------------|---------------------------------|--|--|--|--|

| 1.     | SRAM         | Static Random Access Memory     |  |  |  |  |

| 2.     | BL           | Bit Line                        |  |  |  |  |

| 3.     | BLB          | Bit Line Bar                    |  |  |  |  |

| 4.     | WL           | Word Line                       |  |  |  |  |

| 5      | WLB          | Word Line Bar                   |  |  |  |  |

| 6.     | SNM          | Static Noise Margin             |  |  |  |  |

| 7.     | HSNM         | Hold Static Noise Margin        |  |  |  |  |

| 8.     | RSNM         | Read Static Noise Margin        |  |  |  |  |

| 9.     | TG           | Transmission Gate               |  |  |  |  |

| 10.    | EN           | Enable                          |  |  |  |  |

| 11.    | MOS          | Metal Oxide Semiconductor       |  |  |  |  |

| 12.    | IC           | Integrated Circuit              |  |  |  |  |

| 13.    | SA           | Sense Amplifier                 |  |  |  |  |

| 14.    | Р            | Power                           |  |  |  |  |

| 15.    | Т            | Transistor                      |  |  |  |  |

| 16.    | ROM          | Read Only Memory                |  |  |  |  |

| 17.    | DRAM         | Dynamic Random Access<br>Memory |  |  |  |  |

| 18.    | SoC          | System on Chip                  |  |  |  |  |

| 19.    | ІоТ          | Internet of Things              |  |  |  |  |

| 20     | GND          | Ground                          |  |  |  |  |

| 21. | CMOS | Complementary Metal Oxide<br>Semiconductor |

|-----|------|--------------------------------------------|

| 22. | PMOS | P-type Metal Oxide Semiconductor           |

| 23. | NMOS | N- type Metal Oxide Semiconductor          |

| 24. | WL   | Word Line                                  |

| 25  | WLB  | Word Line Bar                              |

## CHAPTER 1 INTRODUCTION

SRAM (Static Random-Access Memory) cell is a fundamental building block of computer memory systems. It is a type of volatile memory that can store data as long as power is supplied to the system. The SRAM cell is known for its high speed and low power consumption, making it an essential component in various electronic devices, such as microprocessors, cache memories, and graphics cards. As the demand for faster and more efficient computing continues to rise in the future, SRAM cells are expected to play a crucial role in meeting these requirements[1]. With the increasing adoption of artificial intelligence, Internet of Things, and edge computing applications, the demand for SRAM cells is expected to grow even further, driven by the need for high-speed data processing, low-latency access, and power efficiency. Additionally, emerging technologies such as self-driving cars, smart cities, and advanced robotics will also contribute to the increased demand for SRAM cells in the future, making them a vital component in the evolving landscape of computing and information technology[2].

The chapter is divided into five sections. The first section (1.1) is about an SRAM array which is a key component of memory systems, consisting of multiple SRAM cells organized in a grid-like structure. It also contains multiple subsections describing a classical 6T SRAM cell with the hold, read, and write process explained in brief. The second section (1.2) is the motivation, which highlights this field being the area of interest for research. The third section (1.3) deals with the primary objectives of this research work. The fourth section (1.4) highlights the methodology. Lastly, the detailed organization of the thesis is presented in the fifth section (1.5).

#### 1.1 SRAM ARRAY

An SRAM array refers to the organization and structure of static random access memory cells within a memory module or chip. The SRAM array is responsible for storing and retrieving data in a random access manner, allowing for fast read and write operations.

The basic building block of an SRAM array is a single SRAM cell, which typically consists of six transistors[1]. These transistors form a flip-flop circuit that can store one bit of data. The SRAM array is constructed by arranging multiple SRAM cells in a grid-like pattern, with rows and columns forming the addressable locations of the memory.

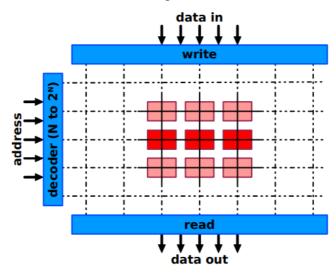

**Fig. 1.1** Typical arrangement of an SRAM array, showing the periphery (in blue) and the cells (in red), with one row of cells accessed (dark red)

The size of an SRAM array is defined by the number of rows and columns of SRAM cells. Each row represents a word line, and each column represents a bit line. The intersection of a row and column represents a specific memory location, where data can be stored or retrieved.

To read data from an SRAM array, the desired address is provided, activating the corresponding word line and allowing the stored data in the selected column to be accessed and read out. Similarly, writing data involves providing the address and data to be written, and activating the appropriate word line and bit line to store the new data in the desired memory location.

The organization and design of the SRAM array play a crucial role in determining the overall capacity, speed, and power consumption of the SRAM chip. Various techniques, such as hierarchical organization, pipelining, and multiplexing, can be employed to optimize the performance of the SRAM array and meet the requirements of different applications[3].

#### 1.1.1 Conventional Six-transistor Cell

The cell design is responsible for several vertical and horizontal control lines per cell. The most usual SRAM which consists of 6 transistors wants one horizontal line termed as word-line and one vertical line per cell named bit-line.

The conventional 6T cell is a crucial component of modern memory systems, widely used in processors, cache memories, and other digital circuits. It consists of six transistors organized in a cross-coupled latch configuration. The cross-coupled inverters form a feedback loop that allows the cell to retain its stored data without the need for constant refreshing.

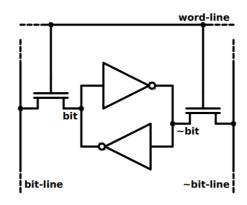

Fig. 1.2 Typical 6T SRAM cell

The 6T cells involves of two twisted inverters, the output of each inverter being coupled to the input of the supplementary one, as demonstrated in figure 1.2. This establishes dual internal nodes of the cell, bit and bitline\_bar. Every inverter is made up of one PMOS and one NMOS transistor named pull-up and pull-down transistor correspondingly. Along with the two inverters, additional two NMOS transistors called pass-gates link the interior nodes to the bit lines.

The 6T SRAM cell offers several advantages, including fast access times, low power consumption, and the ability to retain data if the power supply is maintained. However, it also has certain limitations, such as a larger area footprint compared to other memory technologies and increased vulnerability to noise and process variations. Despite these drawbacks, the conventional 6T SRAM cell remains a widely used and important component in digital systems due to its speed, reliability, and versatility.

#### 1.1.2 Data Hold Operation

The capacity of an SRAM cell to accumulate data depends on on the two twisted inverters. If WL= 0, the pass-gates are cut and can be ignored. If there is a 1 in bit, then the upper inverter will initialize bit\_bar to 0 and finally, the bottom inverter will initialise 1 in bit, emphasizing the original data, thus confirming a specified value is hold. The similar perceptive can be functional assuming that the original data kept in bit is a 0.

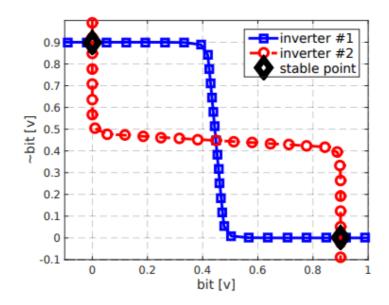

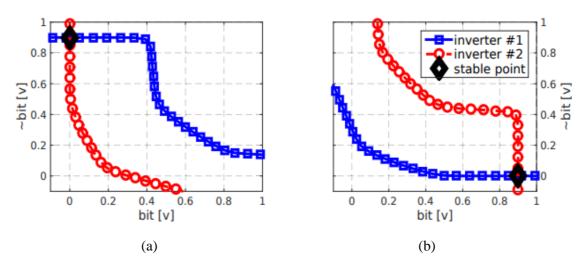

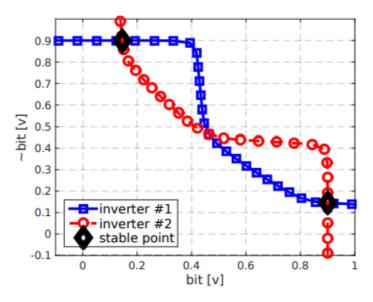

Fig. 1.3 Transfer curves of the two inverters in an SRAM cell

If the transfer curves are plotted, as seen in Figure 1.3, three intersections can be realized. The intersection in the center is not stable. The two additional points resemble the two likely values stored by the cell, either a zero or one.

The 6T cell depends on two transistor inverters to hold the data as this will produce the least area. However, the classic inverters could be substituted by supplementary designs, that will be also able to reserve two possible values. These diverse designs can be based on varying the dimensions of pull-up and pull-down transistors or dissimilar circuits including inverters with extra transistors such as Schmitt trigger, in order to boost features of the cell, like noise resilience and stability.

#### **1.1.3** Write Operation

The two-looped inverters at the core of the cell can accumulate both probable data. The need to trigger the wanted value to behold in the cells, which is called as the write operation.

The write operation begins by setting the word line to  $V_{DD}$ , which stimulates the pass gates. In the meantime, the edge on the top of Figure 1.1 sets the bitlines to the value to be written in the interior nodes of the cell. When an inverse value is written than the one being kept, the pass gate is imposing a value while the inverter is trying to hold the opposite one. The transistors must be sized so that the pass gate surpasses the inverter in order to attain a effective write.

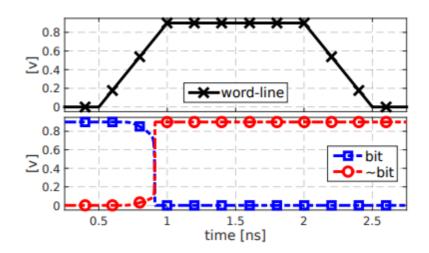

Fig. 1.4 Transient simulation of a write operation in a 6T SRAM cell

Fig.1.5 Modified transfer curves of the inverter while writing (a) Write Zero (b) Write One

A transient simulation of the write operation is illustrated Figure 1.4. The cell starts holding a one, as given by the initial values of interior nodes, bit =  $V_{DD}$  and bit\_bar = 0, whereas the inverse values need to be written, setting bitline = 0 and bitline\_bar =  $V_{DD}$ . By rising the word line from 0 to  $V_{DD}$  at t = 1 ns, the pass gates are initiated, writing the values in the bit lines to the interior nodes, swapping the voltage in bit and bit\_bar. After the word lines are tied back to ground, the cell holds the new value in the internal nodes.

The activated pass gates have the effect of changing the transfer curves of the inverter to the ones shown in Figure 1.4, leaving only one stable point where the transfer curves cross. This forces the cell to keep holding the data corresponding to that of the point after the write operation is finished. The voltage in the bit lines during the write operation, determines which stable point of the cell is selected, having the bit-line tied to the ground while bitline\_bar is set to  $V_{DD}$  forces a 0 as shown in figure 1.5 (a) while setting the opposite voltage forces a one as shown in Figure 1.5 (b).

#### **1.1.4 Read Operation**

Once a value is written to the cell and the cell is able to hold it, the remaining operation consists in retrieving the data stored in the cell. In addition to correctly reading the data, it's equally important to ensure the contents of the cell are not altered during the read operation.

Fig.1.6 Transient Simulation of a Read Operation

In the case of a 6T cell, as for the write, the read operation is triggered by rising the voltage of the word line from ground to  $V_{DD}$  which activates the pass gates. Instead of forcing the voltages of the bit lines, those are now pre charged to  $V_{DD}$  but then left floating. The pass gate connected to the internal node set to the ground will sink current from the bit line to which is connected, progressively discharging as shown in Figure 1.6.

The voltage difference between the two bit lines is sensed by the read periphery at the bottom in the figure 1.1 amplifying the difference to retrieve the data stored in the cell. The circuit is in charge of this is called sense amplifier, it usually needs a small voltage difference between the bit lines, typically about 10% of the supply voltage.

Fig.1.7 Modified transfer curves during a Read Operation

The transfer curves of the inverter are also altered during a read operation as shown in figure 1.7. The two curves cross three times with two stable points, which indicates that the contents will not be altered. However, the curves are much closer to each other compared to those in figure 1.3, which means that the stability is degraded and more vulnerable to noise, this can be seen too in figure 1.6 as the voltage of the internal nodes bit\_bar is altered during the read access.

#### **1.2 MOTIVATION**

The motivation for conducting research in 10T SRAM cells stems from the ever-growing need for high-performance and low-power memory solutions in modern computing systems. As technology advances and the demand for data-intensive applications such as artificial intelligence, virtual reality, and big data analytics increases, traditional 6T SRAM cells face limitations in terms of stability, leakage current, and power consumption. The 10T SRAM cell architecture offers a promising alternative, with its additional transistors providing enhanced stability, reduced leakage, and improved read and write capabilities. By investigating and understanding the characteristics of 10T SRAM cells, we can uncover their potential advantages and limitations, paving the way for more efficient and reliable memory designs for future computing systems.

The research in 10T SRAM cells is driven by the need to address the scaling challenges faced by conventional SRAM designs. As technology nodes continue to shrink, scaling down 6T SRAM cells becomes increasingly difficult due to various physical and electrical limitations. The introduction of additional transistors in the 10T SRAM cell architecture offers opportunities for better scalability and improved performance in advanced technology nodes. Exploring the behavior of 10T SRAM cells through static and dynamic analysis, circuit simulations, and characterization enables us to assess their feasibility in future technology generations. The research on 10T SRAM cells is motivated by the desire to overcome the limitations of current memory technologies and pave the way for more advanced and reliable memory solutions in the future.

#### **1.3 OBJECTIVE**

The objective of this research is to investigate and analyze the performance characteristics of SRAM cells. SRAM cells are integral components of modern digital systems, playing a crucial role in memory storage and data retrieval. With the increasing demand for high-speed and low-power memory solutions, it is essential to explore and understand the behavior of advanced cell designs. By focusing specifically on 10T cells, this research aims to explore their advantages, limitations, and potential applications. Through rigorous experimentation and analysis, the objective is to provide valuable insights and contribute to the advancement of SRAM technology for future computing systems.

#### Primary objectives of this research project are as follows:

• To Compare multiple SRAM designs for the same technology nodes, power supply, and transient time. This also helped to determine the trend of SRAM being used for low-power applications.

• To understand the working of SRAM cell and which one out performs the others, a comparison is done between existing structures and modified SRAM cell structure. A mathematical calculation is also performed for the PDP analysis. To establish which circuit had the best performance, SRAMs are compared, and their findings are illustrated.

• To design and analyze a modified SRAM cell structure that includes a back-to-back inverter, buffer transistors, and access transistors. For optimal performance, power analysis, delay analysis, and the data stability are all performed.

The emphasis of this research is to create an up-to-date better SRAM cell structure that uses low-energy and low-power components and may be used in low-power applications. Multiple SRAM cell topologies on the same technology node, with the same aspect ratios and transient times, were compared for this. Then, for the best performance, the existing SRAM cell designs are compared to the modified design.

#### **1.4 METHODOLOGY**

Comparative performance of the three SRAM cells have been performed which comprises of a 10T SRAM cell with source biased inverter, a transmission gate based 10T SRAM cell and a 11T SRAM cell. The TG10T SRAM cell is proven to be enhanced in almost every aspect but it consumes more power. The comparison is also performed for three different 10T SRAM cells which consist of a 10T cell with source biased inverter, a TG10T cell, and a proposed TG based 10T SRAM cell. The data stability, power consumption, and read delay along with the write delay of all the SRAM cells are studied.

A modified design is implemented and analyzed with several analyses. The proposed design has 10 transistors, four PMOS and six NMOS, and is divided into pull-up transistor, pull-down transistors and access transistors. The data stability, power consumption, and read delay along with the write delay of the proposed cell is studied. This thesis focuses into the standard SRAM structures. A variety of sense amplifier

parameters have also been defined and researched. The 10T SRAM cell offers improved stability, reduced write disturbance, and better noise immunity compared to the 6T SRAM cell. However, the increased complexity and additional transistors result in a larger cell area and higher power consumption. Therefore, the choice between the 6T and 10T SRAM cell depends on the specific design requirements and trade-offs in terms of area, power, and performance.

#### **1.5 THESIS ORGANIZATION**

This thesis is divided into five chapters. An SRAM array and classical 6T cell is defined in Chapter 1 as an introduction. The motivation, objective, methodology, and thesis organization are also included in Chapter 1. The literature review and the technology gap are discussed in Chapter 2. The third chapter examines a significant comparative analysis of different 10T and 11T SRAM cell. Chapter 4 examines the design and analysis of a proposed 10T SRAM cell, as well as its parameters and performance. In Chapter 5, a comparison of the previously reported SRAM cells from Chapter 3 is done with a modified design to demonstrate its enhanced performance as compared to other cells used for comparison. The conclusion and future scope are presented in Chapter 6.

**CHAPTER 1 -** Provides a basic overview of SRAM array and SRAM cells which are closely interconnected in memory systems, as well as how they operate at low power and low voltage. This chapter discusses the objective, motivation, methodology, and detailed organization of the thesis.

**CHAPTER 2** - The prior research on SRAM was detailed in this chapter. In the literature, every parameter is critically analyzed and summarizes existing academic literature and publications relevant to SRAM cells. The purpose of a literature review is to gain a comprehensive understanding of the current state of knowledge, identify gaps or inconsistencies in existing research, and provide a foundation for the researcher's own study.

**CHAPTER 3** - This chapter covers the comparative analysis of different 10T and 11T SRAM cell as well as their functionality, operation, and parameters. They were examined at 32nm technology nodes and 0.5V supply, depending on their structures, their

parameters such as static noise margin, read/write delay, and power consumption were compared.

**CHAPTER 4** - This chapter illustrates a proposed design of the 10T SRAM cell. It describes the design, and how it works. For this cell, major factors such as data stability, read/write delay, and power dissipation are determined. The Monte Carlo analysis is also performed for accessing the performance and reliability of proposed cell. All these analyses are performed to highlight the performance of the proposed cell.

**CHAPTER 5** - This chapter presents a detailed comparative analysis between the proposed 10T SRAM cell and other four existing 10T and 11T SRAM cells to demonstrate the higher action of the proposed design. The comparison is done on three parameters such as static noise margins, access delays, and power consumption.

**CHAPTER 6** - The dissertation is concluded with the overall conclusions and data of results drawn from the research work. It also includes future scopes of improvement related to the topic of research.

Finally, the list of publications contingent on the work carried out in this thesis isattached Later, the detailed list of references is presented which is used to refer to and site the previous research work to explore the directions for our present work.

# CHAPTER 2 LITERATURE REVIEW

Reviewing the reported work is always necessary. The aim of a literature review is to:

• Establish a foundation of knowledge about the topic

• Identify areas of previous expertise to minimize repetition and to give credit to other scholars

• Recognize previous studies contradictions, research gaps, main research conflicts, and unsolved concerns

This chapter is categorized into two sections. The first section (2.1) comprehensive summary of past work, and the technical gaps are covered in section 2.2.

### 2.1 COMPREHENSIVE SUMMARY OF PAST WORK

# • Low leakage 10T SRAM cell with improved data stability in deep sub-micron technologies, 2021

R. Krishna and P. Duraiswamy [1], Proposed a low leakage 10T SRAM cell with a source-biased inverter in deep sub-micron technologies. The source-biased inverter utilizes two extra transistors to alleviate the leakage power without raising the dynamic power. The extra transistors increase the source voltage decreasing the drain to source voltage. It gives limitation in leakage power consumption. Here, the assist techniques are also applied to enhance the stability.

# • Robust transmission gate-based 10T subthreshold SRAM for internet-of-things applications, 2022

E. Abbasian and M. Gholipour [2], Presented a transmission gate based 10T SRAM cell used in IoT applications. It is compared with 6T, TG-8T, and fully differential 8T cells when subjected to extreme PVT variations. The proposed cell uses a differential scheme to amplify the sense margin. It strengthens the write-ability by utilizing two TGs instead of two NMOS access transistors. It also employs two extra buffer transistors to improve

read stability. The proposed TG10T cell minimizes leakage power dissipation by means of a greater number of PMOS devices. The proposed cell renders better overall performance compared to other SRAMs which makes it appropriate for IoT applications.

# • A reliable low standby power 10T SRAM cell with expanded static noise margins, 2022

E. Abbasian, F. Izadinasab, and M. Gholipour [3], Proposed a reliable low standby power 10T SRAM cell with high read stability and write-ability. The proposed cell consists of a cross-coupled layout comprising of standard inverter with a stacked transistor and a Schmitt-trigger inverter with a double-length pull-up transistor. The cell eradicates the read disturbance as the read path is segregated from true internal storage nodes. The cell executes its write operation in pseudo differential form through a write bit line and control signal with a write-assist technique. The leakage power consumption shrinks in the proposed design.

# • A low power single bit-line configuration dependent 7T SRAM bit cell with process-variation-tolerant enhanced read performance, 2023

B. Rawat and P. Mittal [4], "Proposed a 7T bit cell for 32nm technology node at 0.3V supply voltage. The enhancement in performance of the presented cell is seen when compared with the pre-existing 6T, 7T, 8T, 9T, and 10T cells. The power analysis revealed that the 7T cell has the least read/write power dissipation. The layout of the presented design also occupies the least area compared to other counterparts. The tolerant analysis also depicts that the proposed cell sustains a decent performance under PVT variations.

#### • Energy-Efficient Single-Ended Read/Write 10T Near-Threshold SRAM, 2023

E. Abbasian and S. Sofimowloodi [5], Presented an energy efficient single-ended 10T near-threshold SRAM. The proposed design enhances read stability and write-ability through the aid of built in read-assist scheme and a power-gating technique. The energy and power consumption are reduced by using single-ended read/write operation and stacking of transistors in the core of cell. The simulation results for the proposed cell shows enhancement in read stability/writability, reduction in leakage power, improvement in read/write power and energy in comparison to conventional 6T cell. The area of the proposed design was larger than the conventional 6T SRAM.

#### A Novel Low-Power and Soft Error Recovery 10T SRAM Cell, 2023

C. Liu, H. Liu and J. Yang [6], Proposed a low power SRAM cell for soft error recovery. The proposed cell is compared to standard 6T cell which shows all the sensitive nodes can recover their data even when nodes flip at the same time. The proposed cell is free from read intervention. The presented cell consumes very low-holding power due to slight leakage current of the circuit. The problem in the presented unit is that it uses PMOS to drive '0' which causes the line voltage change to not to be in full swing. The simulation results show the proposed cell has good balance between performance, power, reliability and area and it is good choice for anti- radiation application.

• A comprehensive analysis of different 7T SRAM topologies to design a 1R1 W bit interleaving enabled and half select the free cell for 32 nm technology node, 2022

B. Rawat and P. Mittal [7], Presented a single-ended, dual port, 1R1W 7T SRAM cell which is designed after a detailed review of various counterparts. The static analysis discloses that the hold/read noise margins. Its performance is validated by Monte Carlo analysis and temperature variation analysis. When compared to other single-ended 5T, 6T, 7T, 8T, 9T, and 10T SRAM cells, the cell is proven to perform better. In comparison to the other cells, the ION/IOFF ratio is high since the leakage current is low.

# • Low power self-controllable voltage level and low swing logic based 11T SRAM cell for high-speed CMOS circuits, 2018

K. Gavaskar and U.S. Ragupathy [8], Designed a lower-power 11T SRAM cell where two voltage sources are used, one is connected to bitline\_bar whereas the other is connected to bit line. The dynamic power could be reduced by decreasing the swing voltage. The reduction in leakage current causes a decrease in static power dissipation. The voltage supplied is maximum to avoid the data retention difficulty to the circuit during the active mode. Also, reduced voltage is supplied during the standby mode. The simulation demonstrates SRAM cell dissipates lesser dynamic power as well as leakage current. The remarkable advancements procured in the results by the employment of SVL and low-swing logic will be applicable for future low power memory designs.

# • Single-bit line accessed high-performance ultra-low-voltage operating 7T static random-access memory cell with improved read stability, 2021

B. Rawat and P. Mittal [9], Proposed a single-bit line 7T bit cell designed at 32nm technology node at 0.3V supply voltage. On comparing the performance of the proposed cell against different 6T, 7T, 8T, and 10T SRAM bit cells, the hold static noise margin and read static noise margin were found to be better than the 6T cell. The writability also improved decreasing the leakage current compared to the 6T cell. Hence, it can be inferred that the proposed cell manifests all essential enhancements in performance compared to the other counterparts demonstrated in the paper.

#### • Low-power and high-speed SRAM cells for double-node-upset recovery, 2023

S.Cai, Y. Wen, C. Xie, W. Wang and F Yu [10], Presented radiation-hardened SRAM (i.e., LPDNUR and HSDNUR) which can self-recover from single-node and double-node upsets. LPDNUR uses a two-input C-element structure, which reduces the average power consumption because the stacked effect. Moreover, in order to reduce read access time (RAT) and write access time (WAT), the paper proposes HSDNUR, which uses a combination of NMOS and PMOS as the transistor for one-node data transmission, an approach that increases the current drive capability and reduces transmission delays.

# • Design of highly reliable radiation hardened 10T SRAM cell for low voltage applications, 2022

R. Shekhar and C.I. Kumar [11], Presented a novel 10T SRAM cell that has an energyefficient operation and is radiation-hardened with high static noise margins. The proposed cell reduces area as compared to other counterparts used in the paper for comparison. The cell also enhances the hold and read static noise margin whereas the write static noise margin remains almost the same. The memory cells are more open to single event upset (SEU) because of a reduction in supply voltage, decrease in critical charge, and dense ICs.

• A reliable and temperature variation tolerant 7T SRAM cell with single bit line configuration for low voltage application, 2022

B. Rawat and P. Mittal [12], Proposed a 7T cell which is of single-ended configuration. The hold/read static noise margin is fairly good for this cell. The reliability of this cell can be measured using Monte Carlo process variation and temperature variation. The results obtained for the proposed design are compared against various pre-existing 5T, 6T, 7T, and 8T cells to showcase the enhancements obtained by the proposed 7T cell. The power dissipation was found to be minimum in the proposed design as it requires a pulse width of a few nanoseconds to perform write and read operations successfully. Thus, the proposed cell shows advancement in performance when compared to its counterparts discussed in the paper.

# • Comparative analysis of 90 nm MOSFET and 18 nm FinFET based different multiplexers for low power digital circuits, 2020

N. Kumar, P. Mittal [13], In terms of latency, average power dissipation, and Power delay product, a comparison is done between FINFET-based Gate Diffusion Input and Pass Transistor based 2:1 Multiplexers. The power dissipation of a GDI-based mux is relatively low. GDI-based Mux has superior performance and lower power consumption. Because multiplexers can be employed in a variety of combinational circuits, improving the performance of the multiplexer is increase the overall performance of the circuit.

# • Design and performance improvement of low power SRAM using deep submicron technology, 2022

U. R. Shirode and R. D. Kanphade [14], Presented a design with performance improvement of low-power SRAM working at deep submicron technology to control the issues by employing a novel modified lector-based foot-driven stacked transistor domino logic SRAM cell design in which the modified lector technique uses both keeper and lector technique to reduce the leakage power in both modes i.e active mode and standby mode, thereby reducing layout area and the propagation delay. It is designed to improve the noise margin of SRAM and to overcome the zero output in AND gate thereby increasing the speed of the SRAM cell. The proposed cell attains a high read and write stability along with a high SRAM speed. The leakage current is reduced. Thus, the proposed design outperforms the existing method with greater stability and speed of cells.

#### • Static Noise Margin Analysis of 6T SRAM Cell, 2016

A. A. Jose and N. C. Balan [15], Presented a design with the SNM calculation and analysis of SRAM cells based on simulations performed in Cadence Virtuoso. The proposed cell has the compact structure of six transistors. The static noise margin is found with the help of butterfly curves for read, hold, and write operations.

# • Sizing-priority based low-power embedded memory for mobile video applications, 2016

S. A. Pourbakhsh, X. Chen, D. Chen, X. Wang, N. Gong and J. Wang [16], Presented a sizing-priority based memory design methodology for low-power mobile video applications. The investigation of size-dependent memory failure characteristics was performed and memory failure rate overhead was effectively reduced with low area utilization. A model was designed between memory failure and output quality, while introducing application output into the hardware design process.

#### • A single-ended low leakage and low voltage 10T SRAM cell with high yield, 2020

N. Eslami, B. Ebrahimi, E. Shakouri and D. Najafi [17], Presented a low leakage 10T single-ended SRAM cell in the sub-threshold region using FINFET technology that enhances the hold, read, and write stability. At low voltage the write-ability is raised by temporarily floating the data node, and the stability of the read operation is maintained approximately equal to the hold state by separating the data storage node from the read bit line (RBL) while using only a single transistor. The read stability is found to be higher than conventional 6T cell. Also, the proposed cell has the lowest static power dissipation.

#### • A 32 nm read disturb-free 11T SRAM cell with improved write ability, 2020

S. R. Mansore, R. S. Gamad and D. K. Mishra [18], Presented 11T SRAM cell with single read and differential write which has improved write-ability by interrupting its ground connection during a write operation. There is a separate read buffer that provides disturb-free read operation. The simulation results show that the proposed cell achieves a higher read static noise margin as compared to conventional 6T cell and PNN based 10T cell. The write static noise margin of the proposed design was found to be higher than 6T cell. The Proposed design consumes lesser read power as compared to PPN10T cell. Also, the leakage power is lesser. The Proposed 11T cell occupies larger area as compared to that of conventional 6T.

#### • Low power SRAM design with reduced read/write time, 2013

S. Yadav, N. Malik, A. Gupta, S. Rajput [19], Presented the design and analysis of Static Random-Access Memories (SRAMs), with a focus on minimizing delay and power consumption. Also, implemented the 6T SRAM cell which has a Read and write time, power consumption and delay have all been lowered. Bit-line parasitic capacitance

increases as memory capacity grows, delaying voltage sensing. To prevent this problem, apply efficient scaling approaches and further improve design performance.

• Design and analysis of a 32 nm PVT tolerant CMOS SRAM cell for low leakage and high stability, 2010

S. Lin, K. Yong-Bin and F. Lombardi [22] proposed a 9T SRAM cell that is primarily aimed at providing a robust and process-voltage-temperature variation tolerant cell with minimum leakage power consumption. The cell is also designed in such a way that the data stored on the cell is protected by high stability. The simulation findings validated that the tolerance and robustness. The results also revealed that the reported SRAM design consumes 33% lesser leakage power. It also showed that the delay being exhibited by the reported SRAM is on the lower side.

| S.  | Authors             | Tr.   | No. of  | Technolo | Supply  | Access | Leakage | SNM in mV   |

|-----|---------------------|-------|---------|----------|---------|--------|---------|-------------|

| No. |                     | Count | Bitline | gy node  | Voltage | Delay  | power   | (RSNM/HS    |

|     |                     |       | S       | (nm)     | (V)     | (psec) | (nW)    | NM/WM)      |

| 1.  | Lin <i>et al</i> .  | 9     | 2       | 32       | 0.6     | 82.04  | -       | -           |

|     | [5]                 |       |         |          |         |        |         |             |

| 2.  | Gavaskar            | 11    | 2       | 30       | 0.8     | 21.3   | 7.15    | -           |

|     | et al. [10]         |       |         |          |         |        |         |             |

| 3.  | Mansore             | 11    | 2       | 32       | 0.4     | 723.9  | 8.27    | -/113/254.5 |

|     | <i>et al</i> . [21] |       |         |          |         |        |         |             |

| 4.  | Oh <i>et al</i> .   | 9     | 1       | 22       | 0.32    | 256000 | 740     | 164/-/-     |

|     | [34]                |       |         | (FinFET) |         |        |         |             |

| 5.  | Lorenzo             | 11    | 1       | 65       | 1.2     | 778.3  | 46.42   | 179/179/331 |

|     | <i>et al</i> . [38] |       |         |          |         |        |         |             |

Table 2.1: Parametric Analysis of various 9T and 11T SRAM cells

The table 2.1 titled Parametric review of various 9T and 11T SRAM cells presents a summary of relevant studies investigating 9T and 11T SRAM cells that are either single ended or differential ended. These results align with previous research in the field, supporting the theory. The table underscores the importance of SRAM cells in the field of electronics and provides valuable insights for future studies.

| S.  | Authors             | Technology | Supply  | Access | Leakage | SNM in mV         |

|-----|---------------------|------------|---------|--------|---------|-------------------|

| No. |                     | node       | Voltage | Delay  | power   | (RSNM/HSNM/WM)    |

|     |                     | (nm)       | (V)     | (psec) | (nW)    |                   |

| 1.  | Krishna             | 32         | 1       | 916.7  | 0.00937 | 201/-/463         |

|     | <i>et al</i> . [1]  |            |         |        |         |                   |

| 2.  | Abbasian            | 16         | 0.36    | 340    | 1.15    | 29.8/87.3/        |

|     | <i>et al.</i> [2]   |            |         |        |         |                   |

| 3.  | Abbasian            | 16         | 0.7     | 299    | 11.79   | 225.5/225.5/356.6 |

|     | <i>et al.</i> [3]   |            |         |        |         |                   |

| 4.  | Abbasian            | 32         | 0.6     | 414    | 4.90    | 197/209/263       |

|     | <i>et al</i> . [5]  |            |         |        |         |                   |

| 5.  | Liu <i>et al</i> .  | 22         | 0.8     | 17.9   | 2.92    | 340/510/270       |

|     | [6]                 |            |         |        |         |                   |

| 6.  | Shekhar             | 65         | 0.4     | 278    | 3.38    | 117/57/220        |

|     | <i>et al</i> . [17] |            |         |        |         |                   |

| 7.  | Eslami et           | 10         | 0.2     | 150    | 2       | 63.5/63.5/107.8   |

|     | al. [20]            | (FINFET)   |         |        |         |                   |

Table 2.2: Parametric Analysis of various 10T differential ended SRAM cells

The table 2.2 titled Parametric review of various 10T differential ended SRAM cells presents a summary of relevant studies investigating 10T SRAM cells that are differential ended. These results align with previous research in the field, supporting the theory. The table underscores the importance of SRAM cells in the field of electronics and provides valuable insights for future studies.

#### 2.2 RESEARCH GAP

The 10T SRAM cells have gained attention as a promising alternative to conventional 6T SRAM cells due to their improved read stability and write ability but several research gaps still exist in this area. One significant research gap pertains to the area of write stability. While 10T SRAM cells offer improved read stability compared to conventional 6T SRAM cells, challenges remain in achieving robust write stability. The write operation in 10T SRAM cells is more susceptible to various noise sources. Exploring innovative techniques to enhance the write stability of 10T SRAM cells, while maintaining their improved read stability, is an active area of research. Addressing this research gap will not only improve the overall reliability of 10T SRAM cells but also facilitate their integration into high-performance memory subsystems.

A notable research gap in the 10T SRAM cells is the exploration of power-efficient design methodologies. While 10T SRAM cells exhibit desirable read stability characteristics, they often consume more power compared to traditional 6T SRAM cells due to the additional transistors and complex circuitry involved. Developing power-efficient design techniques specific to 10T SRAM cells is crucial for enabling their wider adoption in low-power and energy-constrained applications, such as mobile devices and Internet of Things (IoT) devices. Exploring new circuit architectures, voltage scaling techniques, and power management strategies tailored for 10T SRAM cells can help mitigate their power consumption while maintaining their performance and reliability. Bridging this research gap will unlock the full potential of 10T SRAM cells in power-sensitive applications, furthering the advancement of energy-efficient memory technologies.

### **CHAPTER 3**

# CHARACTERISTIC COMPARISON FOR DIFFERENT 10T AND 11T SRAM CELLS

The specific performance and characteristics of SRAM cells can vary depending on the implementation, process technology, and design considerations. These comparisons provide a general understanding of the differences between the 10T and 11T SRAM cells. The additional transistor in the 11T cell is usually used as an access transistor to improve read and write stability. The 11T SRAM cell offers better stability compared to the 10T SRAM cell. The additional access transistor in the 11T cell helps reduce the leakage current and improves the robustness of the stored data. The 10T SRAM cell typically exhibits faster read access times compared to the 11T SRAM cell.

The additional transistor in the 11T cell introduces additional capacitance, which can slightly slow down the read operation. Both the 10T and 11T SRAM cells provide similar write performance. However, the 11T SRAM cell may have a slight advantage due to improved stability, resulting in better write margin and reduced write-induced disturbances. The 10T SRAM cell generally consumes less power compared to the 11T SRAM cell. The additional transistor in the 11T cell increases the static power dissipation, contributing to higher overall power consumption. The 10T SRAM cell is more area-efficient than the 11T SRAM cell due to its simpler structure and fewer transistors.

The chapter is divided into seven sections. The first section (3.1) elaborates overview of SRAM cells in which conventional 10T cell, TG 10T cell, and 11T cell are discussed. The second section (3.2) mentions the dimension of all four cells, which highlights the technology node being used and the varying dimensions of pull-down, pull-up, and access transistors. The third section (3.3) deals with transient analysis to evaluate the behavior of SRAM cells during dynamic operations such as read and write operations. The fourth section (3.4) features data stability in which the butterfly curves HSNM, RSNM, and WSNM have been shown to evaluate robustness against noise and ensure reliable operation. The fifth section (3.5) shows the power comparison for each cell. The sixth section (3.6) demonstrates the comparison between the read and write delay respectively.

#### **3.1 OVERVIEW OF SRAM CELLS**

SRAM cells are a type of semiconductor memory used in computer systems, microprocessors, and other digital devices. Unlike dynamic RAM (DRAM), which requires periodic refreshing, SRAM is designed to retain data as long as power is supplied to the circuit. SRAM is known for its fast access times, low power consumption, and non-volatility.

An SRAM cell typically consists of transistors arranged in a flip-flop configuration. A brief overview of the components and operation of an SRAM cell are illustrated below:

a) **Cross-Coupled Inverter Pair:** The heart of an SRAM cell is a pair of cross-coupled inverters, which form a flip-flop. Each inverter consists of a PMOS (P-channel Metal-Oxide-Semiconductor) transistor and an NMOS (N-channel Metal-Oxide-Semiconductor) transistor.

**b) Bitlines:** The flip-flop is connected to two bitlines, namely a "bitline" and a "bitline bar" (complementary bitline). These lines are used to read and write data to the SRAM cell.

c) Wordlines: A wordline is used to control the access to the SRAM cell. When the wordline is activated, it enables the transfer of data between the bitlines and the flip-flop.

**d**) Access Transistors: Access transistors are fundamental components of SRAM, which are widely used for high-speed, volatile data storage in electronic devices. The access transistors act as switches that control the connection between the storage nodes and the storage capacitors. These transistors provide the means to read/write data in the cell. During a read operation, the access transistors connect the stored data to the bitlines, allowing the voltage levels to be sensed and retrieved. During a write operation, the access transistors enable the data to be written onto the storage capacitors by providing a path for the current flow. Access transistors in SRAM are designed to have fast switching characteristics and low leakage currents, ensuring reliable and efficient access to stored data.

SRAM cells are typically organized into arrays, forming larger memory banks with multiple cells. The size of an SRAM cell can vary depending on the technology node and design constraints. Smaller cell sizes enable higher memory density but may introduce challenges in terms of power consumption and stability. SRAM cells offer fast and efficient random access to data, making them suitable for cache memory, register files, and other applications where speed and low power consumption are crucial.

### 3.1.1 10T SRAM Cell with Source Biased Inverter

An SRAM cell is a circuit component capable of storing a single data bit which may either be 0 or 1. Also, it must be capable to read or write data, while there is a power supply. The 10T cell with a source-biased inverter, which consists of 10 transistors, will be utilized as a baseline for comparison with the other two models. A back-to-back CMOS inverter is used for storing data, and two access transistors are placed on either side of the inverter to facilitate reading from and writing to the cell [1]. Figure 3.1 illustrates the circuit.

Fig. 3.1 Schematic of 10T SRAM cell with source biased inverter

Even before turning on access transistors N5 & N6, the word line is triggered to '1'. The bit line is set the same as the data bit. The bitline\_bar is set the same as the complement of the data bit. This pulls data onto the two different nodes of in cross-coupled inverter.

Here, by utilizing a precharge circuit BL & BLB are pre-charged '1' to successfully read data from the SRAM cell [1]. Following this operation, for turning on access transistors N5 & N6, the word line is triggered to 1 according to the data on the nodes, so that either the BL or BLB is discharged to the GND. During hold mode, WWL and RWL are grounded to turn the access transistor OFF. Hence, the core of this cell is separated from bit lines. So, no read or write operation is performed.

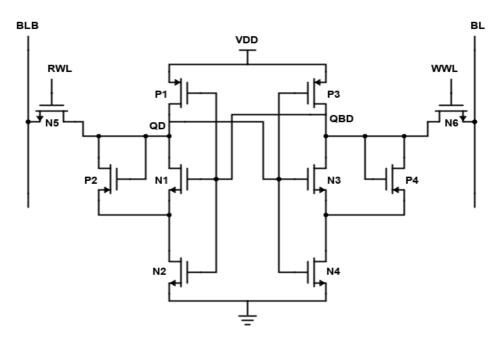

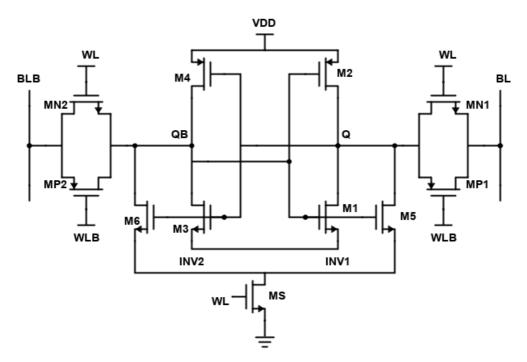

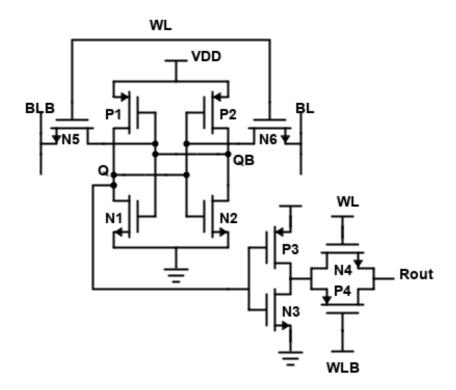

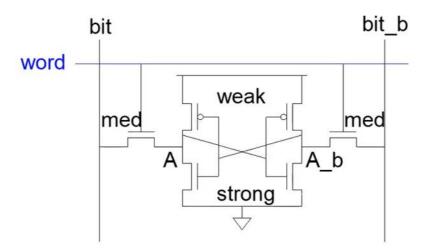

#### 3.1.2 Transmission Gate based 10T SRAM Cell

Figure 3.2 displays a TG10T SRAM Cell. The right inverter, which consists of M1 & M2, is constricted by QB, while the left inverter, which consists of M3 & M4, is by Q. Both Q and QB are storage nodes. A latch is created by the back to back inverters for holding data gathered in the cell. In addition, the TG10T cell consists of 2 transmission gates, TG 1 (MN1-MP1) and TG 2 (MN2-MP2), controlled by both word lines to the write capability [2]. The Read stability is improved by two buffer transistors, M6 & M5, which are gated by Q & QB [2]. The MS transistor which is driven by the Word line connects the source of the above transistor to GND. The nodes Q=0 and QB=1.

Fig. 3.2 Schematic of TG10T SRAM cell

When WL is 1 and WLB is 0, the bit lines can be accessed by switching the transmission gates. The MS transistor is also ON. Here, BL is at  $V_{DD}$  and BLB at GND, which writes

a '0'/'1' to QB/Q. The write operation is quicker because both strong logic "0" and strong "1" values are passed through the transmission gates. Through M1 & M5, node Q discharges whereas MS is initially brought to GND for a small duration of time. During this process, QB discharges via M3 & M6, where MS is '0'. The required data is thus successfully written to the storage nodes.

The BLB along with BL is precharged high before the read operation. Next, WLB is set to GND and WL is set to  $V_{DD}$ . This turns on the MS and transmission gates and discharges either of the bit lines to the ground. The other bit line remains at a precharged value of '1' initially in storage nodes QB and Q depending on the data stored [1]. Consider that node QB stores '1' and node Q stores '0'. The additional pull-down path makes the read operation faster, thus improving the RSNM, which helps discharge the voltage at the Q node [2]. During hold mode, WLB is  $V_{DD}$  and WL is GND for turning off the transistor MS and transmission gates. Thus, cell core is disconnected from the bit lines, and no reading or writing takes place.

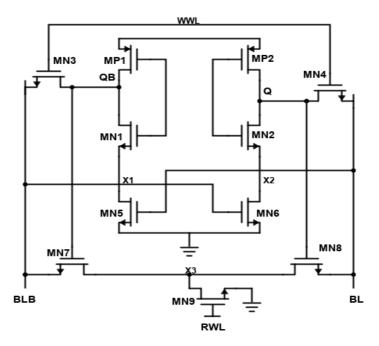

#### 3.1.3 Fully Differential 11T SRAM Cell

The 11T cell demonstrated in figure 3.3 is made up of the smallest-sized devices for reducing area overhead up to a maximum extent. Here, the read buffer of the cell (MN7-MN9) consists of oversized transistors to achieve minimum read latency as well as maximum stability in the read operation. are driven by bit lines. The bit lines drive the gate electrodes of transistors MN 5 & MN 6 which are serially connected [8]. The node X1 is high during the write operation. If 1 is to be written at QB, BLB is high and BL is GND. The transistor MN 5 turns OFF. So, the pull-down path of the left inverter is disconnected and node QB attains a higher value due to quick charging.

For a stack of two devices, if the bottom device is OFF and the top device is ON, a voltage is built at the internal node. Hence, node X1 is raised. The VX1 (positive) offers body effect and stacking which helps in diminishing the delay of the write signal during a write operation on rapidly charging node QB. The write operation mainly consists of a write driver, pull-up devices, and access devices while RWL is deactivated and WWL is activated [8]. Furthermore, BL turns OFF transistor MN 5 disconnecting the pull-down path while 1 is written at QB. This improves the write-ability of the cell by making the

write operation faster.

Before the read operation, bit lines are precharged, transistor MN 1 is ON, QB stores a 0 and Q stores a 1. The bitline\_bar drops through transistor MN 1 and MN 3, when WL is activated. Before the read operation, QB and Q are separated by disconnecting WWL, 0 in QB turns transistor MN 7 OFF, and 1 in Q turns transistor MN8 ON, which increases the internal node voltage X3 to a value larger than 0. When the word line for read is activated node X3 offers a body effect to transistor MN 8 [8].

Fig. 3.3 Schematic of Fully differential 11T SRAM cell

Due to positive VX3, the body-to-source voltage of transistor MN 8 becomes negative. This results in an increase in  $V_{th}$  of MN 8 which causes the drive strength to decrease. So, the time taken to discharge BL is more. Hence, the body effect offered to transistor MN 3 is much smaller comparably. During hold mode, RWL and WWL are grounded to switch OFF the access transistor. Hence, the core of the cell is deactivated from bit lines, and no read or write operation occurs.

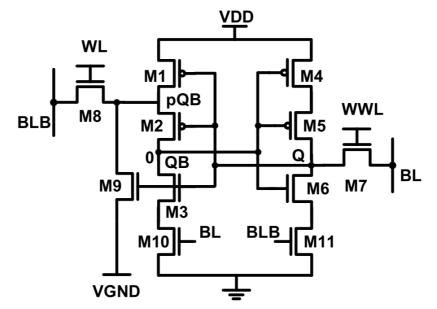

#### 3.1.4 PPNN 11T SRAM cell

The schematic of the proposed cell is shown in Fig. 3.4. It comprises two cross-coupled inverters (M1–M2–M3–M10 and M4–M5–M6–M11) to store one-bit data. Transistor M7 connects true

storage node Q and bit line BL when write word line WWL is asserted. Transistor M8 connects pseudo storage node pQB and bit line BLB when word line WL (row based) is enabled. Transistors M8 and M9 form a read buffer which discharges BLB when WL is high and virtual ground VGND (row based) is low. Note that, transistor M8 is kept ON during read as well as during write operations. Transistor M10 (M11) is controlled by BL (BLB) to disconnect storage node QB (Q) from ground terminal during write "0" (write "1").

Fig. 3.4 Schematic of PPNN 11T SRAM cell

In the hold mode, WL and WWL are disabled while BL, BLB and VGND are forced to  $V_{DD}$ . Data are held by the cross-coupled inverters and is decoupled from BL/BLB [18].

For reading the cell content, bit line BLB must be pre-charged to  $V_{DD}$ , WL is set high whereas WWL and VGND are kept low. As a result, BLB is discharged through M8 and M9 or remains at pre-charged value  $V_{DD}$  depending upon the data stored. For example, if a logic "1" is stored in the cell (Q = "1"), then BLB is discharged through M8 and M9 as shown in Fig. 3.4. However, BLB remains at a pre-charged level if a logic "0" (Q = "0") is stored in the cell.

For writing the data into the cell, WWL and WL are enabled while VGND is kept floating. Suppose that initially logic "1" is stored in the cell. Now, to write a "0" in the cell, bit lines BL and BLB are loaded with "0" and "1", respectively. As a result, node Q is discharged by BL through ON transistor M7. During the write "0" operation, OFF transistor M10 (BL = "0") leaves node QB isolated from the ground terminal resulting in a faster charge accumulation process at node QB. As a result, internal feedback eliminates charges rapidly from node Q and write "0" operation (Q = "0" and QB = "1") is performed. To understand the write "1" operation, let us assume that initially logic "0" (Q = "0") is stored in the cell. Now, to write a "1" in the cell, bit lines BL and BLB are loaded with "1" and "0", respectively, as shown in Fig. 3.4. This causes node QB is discharged by BL through ON transistors M2 and M8. During write "1" operation, OFF transistor M11 (BL B= "0") leaves node Q isolated from the ground terminal resulting in a faster charge accumulation process at node Q. Consequently, successful write "1" operation (Q = "1" and QB = "0") is performed

# **3.2 CELL SIZING**

The LTSPICE tool was used to perform simulations by constructing schematics of all three SRAM cells for comparison. Tables show the transistor sizes used in the 10T SRAM cell, TG10T SRAM cell, and 11T SRAM cell.

|                                           | Width (W) | Length (L) |

|-------------------------------------------|-----------|------------|

| P1, P3 (Pull-Up Transistors)              | 36n       | 32n        |

| N1, N2, N3, N4 (Pull-Down<br>Transistors) | 72n       | 32n        |

| N5, N6 (Access Transistors)               | 36n       | 32n        |

| P2, P4 (Buffer Transistors)               | 72n       | 32n        |

Table 3.1 Dimensions for 10T cell

### Table 3.2 Dimensions for TG10T cell

|                                       | Width (W) | Length (L) |

|---------------------------------------|-----------|------------|

| M2, M4(Pull-Up Transistors)           | 128n      | 32n        |

| M1, M3 (Pull-Down Transistors)        | 128n      | 32n        |

| MN1-MP1, MN2-MP2 (Access Transistors) | 36n       | 32n        |

| M5, M6 (Buffer Transistors)           | 320n      | 32n        |

The dimensions of an SRAM cell are critical in determining its overall performance, density, and power consumption. The size of an SRAM cell is typically measured in terms of its area, which is determined by the dimensions of the transistors and the storage capacitors within the cell. Shrinking the dimensions of the transistors, such as the gate length and width, allows for higher cell density and increased memory capacity. Since every other transistor is the smallest size feasible, the overall area of the circuit is significantly smaller.

|                                               | Width (W) | Length (L) |

|-----------------------------------------------|-----------|------------|

| MP1, MP2 (Pull-Up<br>Transistors)             | 32n       | 32n        |

| MN1, MN2, MN5, MN6<br>(Pull-Down Transistors) | 32n       | 32n        |

| MN3, MN4 (Access<br>Transistors)              | 32n       | 32n        |

| MN7, MN8 (Buffer<br>Transistors)              | 50n       | 32n        |

| MN9 (Buffer Transistor)                       | 64n       | 32n        |

Table 3.3 Dimensions for 11T cell

Table 3.4 Dimensions for PPNN 11T cell

|                             | Width (W) | Length (L) |

|-----------------------------|-----------|------------|

| M1, M2, M4, M5 (Pull-Up     | 32n       | 32n        |

| Transistors)                | 5211      | 5211       |

| M3, M6, M10, M11 (Pull-     | 64n       | 32n        |

| Down Transistors)           | 0411      | 3211       |

| M7, M8 (Access Transistors) | 64n       | 32n        |

| M9 (Buffer Transistor)      | 64n       | 32n        |

However, reducing the dimensions also brings challenges, such as increased leakage currents and reduced noise margins. Therefore, there is a constant trade-off between cell size, performance, and reliability. Advancements in semiconductor manufacturing processes have enabled the scaling of SRAM cells, leading to smaller dimensions and higher integration levels, contributing to the continuous improvement of memory capacity and speed in modern electronic devices.

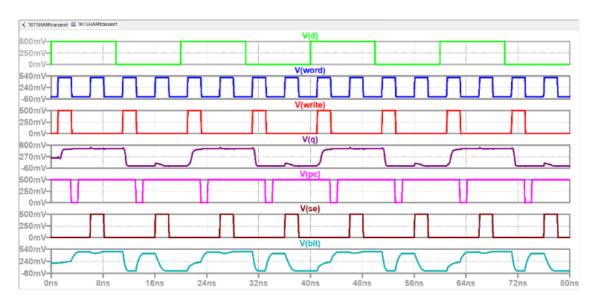

# **3.3 TRANSIENT ANALYSIS**

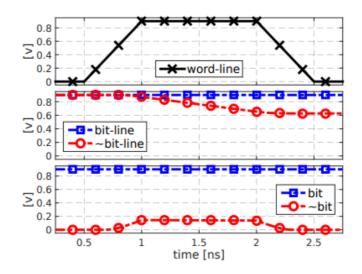

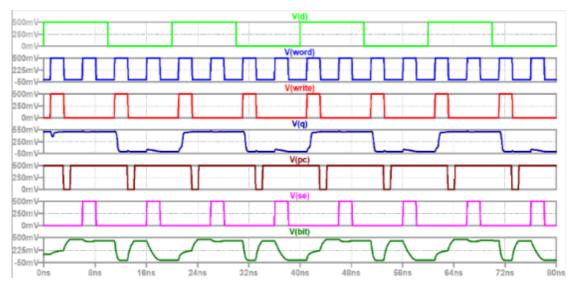

To ensure that the hold, read and write operations worked correctly, transient analysis was performed on all three models. Similar read/write signals, identical input data signals, and precharge signals for read and write bit lines were employed to simulate the models. For all models, identical sense amplifiers, precharge circuits and write drivers were adopted to ensure the reliability of performance comparison. The results of the simulation are demonstrated in Fig 3.5.

Transient analysis of an SRAM cell is a crucial step in understanding its dynamic behavior during read and write operations. During a read operation, the transient analysis focuses on the voltage and current responses of the cell as the stored data is accessed. The analysis considers factors such as the access transistor's switching characteristics, the voltage levels applied to the bitlines, and the capacitance of the storage nodes. By analyzing the transient response, it is possible to determine the read access time, which is the time taken for the stored data to stabilize on the bitlines and be correctly sensed.

Fig. 3.5 Transient analysis of (a) 10T SRAM cell, (b) TG10T SRAM cell, (c) 11T SRAM cell, and (d) PPNN11T Cell