# PERFORMANCE ANALYSIS OF AN IMPROVED 8T SRAM CELL FOR LOW POWER AND HIGH SPEED APPLICATIONS

A DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

## MASTER OF TECHNOLOGY

IN

## **VLSI DESIGN & EMBEDDED SYSTEMS**

Submitted by:

## **DEBERJEET USHAM**

## 2K21/VLS/05

Under the supervision of

## **Prof. POORNIMA MITTAL**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY

> (Formerly Delhi College of Engineering) Bawana Road, Rohini, Delhi- 110042

MAY 2023

2023

Deberjeet Usham

## DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **CANDIDATE'S DECLARATION**

I, Deberjeet Usham, Roll No. 2K21/VLS/05, student of M.Tech (VLSI Design & Embedded System), hereby declare that the Project Dissertation titled "PERFORMANCE ANALYSIS OF AN IMPROVED 8T SRAM CELL FOR LOW POWER AND HIGH SPEED APPLICATIONS" which is submitted by me to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is original and not derived from any source without appropriate citation. This work has not previously formed the basis for the award of any Degree, Diploma Associate-ship, Fellowship or other similar title or recognition.

Place: Delhi Date: 30<sup>th</sup> May, 2023 Deberjeet

DEBERJEET USHAM 2K21/VLS/05

## ELECTRONICS & COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **CERTIFICATE**

I hereby certify that the Project Dissertation titled "PERFORMANCE ANALYSIS OF AN IMPROVED 8T SRAM CELL FOR LOW POWER AND HIGH SPEED APPLICATIONS" which is submitted by Deberjeet Usham, Roll No. 2K21/VLS/05, Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is a record of the thesis work carried out by the student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date: 30<sup>th</sup> May, 2023 Pormina

Prof. Poornima Mittal SUPERVISOR, ECE, DTU, Delhi

## ACKNOWLEDGEMENT

To begin with, I am immensely grateful to my supervisor, **Prof. Poornima Mittal** (Dept. of ECE) for her unwavering support and invaluable guidance. I am truly fortunate to have had the opportunity to work under her mentorship. Her approachability and willingness to engage in meaningful discussions have fostered an environment of intellectual curiosity and critical thinking. Her constructive feedback, insightful suggestions, and challenges to my ideas have pushed me to expand my knowledge and enhance the quality of my work. It is because of her guidance that my work is in the present level. Secondly, I would like to acknowledge the support and assistance provided by the staff and faculty of Department of Electronics and communication. I am indebted to the librarians, research assistants, and administrative personnel who have provided assistance whenever needed. The research scholars of the department were always available whenever I had asked for help in my thesis. Lastly, I would like to thank my parents for supporting me patiently and motivating me in every circumstance.

Deberjeet Usham 2K21/VLS/05 MTech: VLSI Design and Embedded Systems (2021-2023)

## ABSTRACT

Memory is already known to be one of the most crucial parts of any electronic system. However, a class of memory called the cache memory is even more crucial amongst the type of memories since it is the one working closely in synchronization with the central processing unit (CPU). It is a faster and smaller memory and is also used to store data frequently used by the CPU. Its usage is inevitable in any system that performs computing digitally in any way. Cache memories consist of large arrays comprising millions of SRAM cells, which serve as the fundamental components of the cache memory system. As the ceiling of advancement of technology becomes higher, so does the demand of enhanced cache memories and hence the SRAM cells. Enhancement of these cells may be in the form of different parameters, but the crucial parameters that this paper will be focusing on are noise margins, access delay, power consumption, sturdiness to temperature and voltage drop variation, etc. Keeping the mentioned parameters as the guiding principle, a single ended, dual port SRAM cell architecture consisting of 8 transistors is proposed in this thesis work.

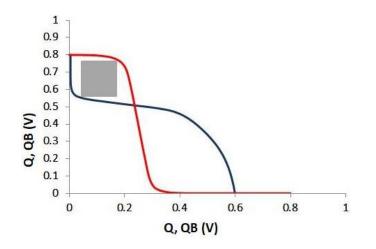

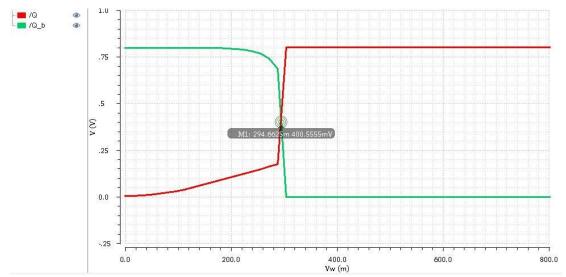

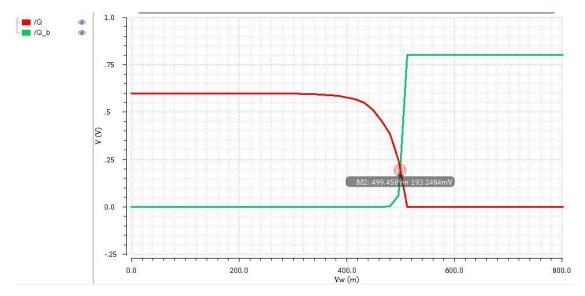

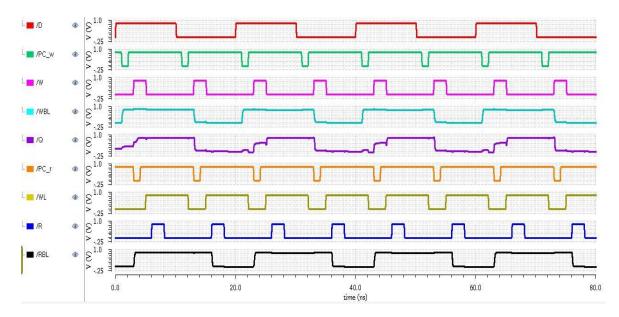

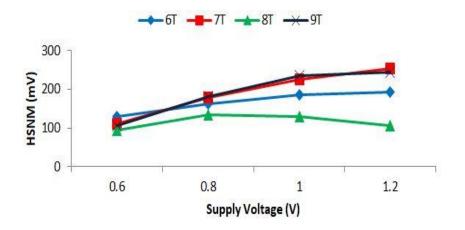

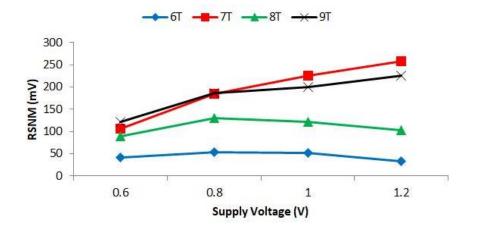

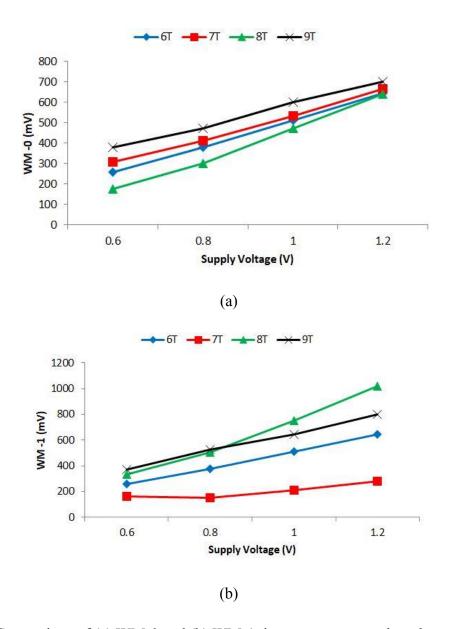

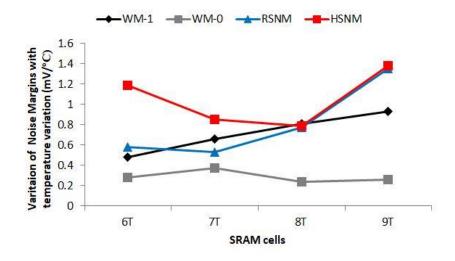

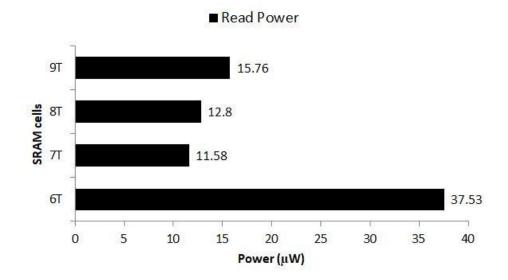

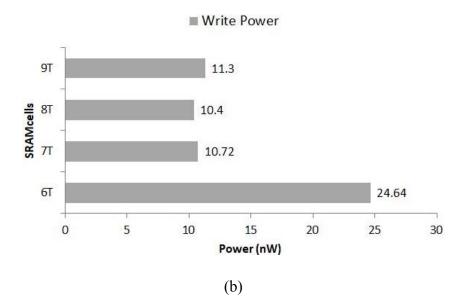

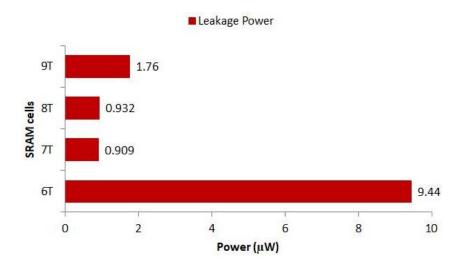

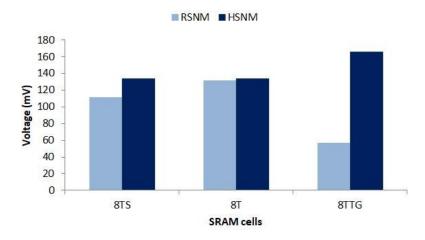

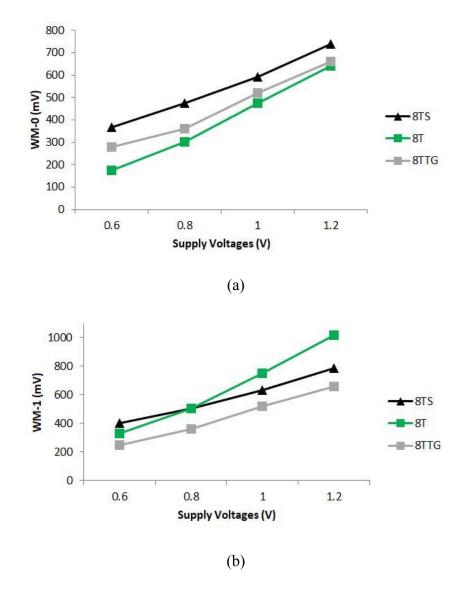

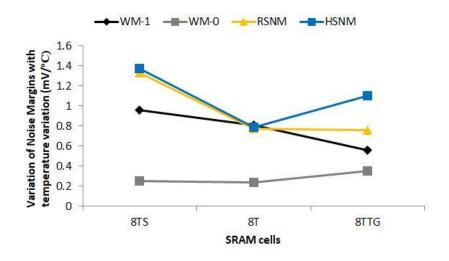

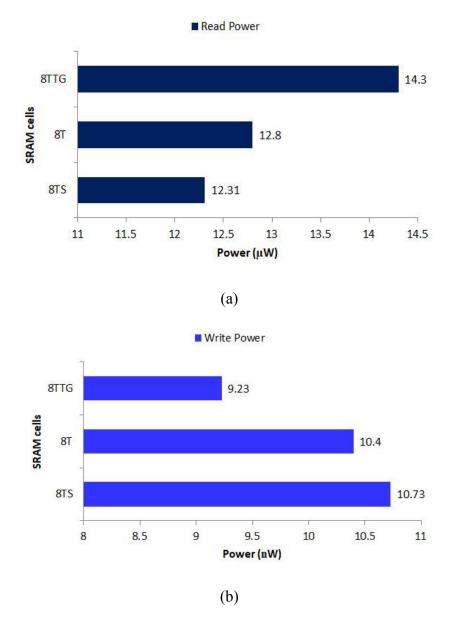

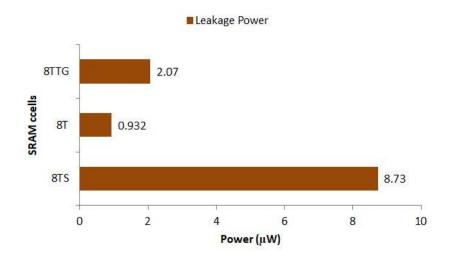

The memory cell under discussion incorporates several key design features to optimize its functionality. Firstly, it utilizes separate bitlines for read and write operations, ensuring independent and isolated functioning of these operations without any conflicts. Secondly, the storage node, formed by back-to-back inverters, remains undisturbed during read operations, resulting in enhanced data stability and reliability. Moreover, the cell employs dual VT (threshold voltage) transistors to minimize leakage power consumption, thereby improving energy efficiency. Lastly, the configuration of transistors within the cell is optimized to minimize the number of transistors in the read critical delay path, leading to reduced read delays and improved overall performance. These design considerations collectively contribute to the cell's efficiency, reliability, and speed, making it a valuable component for memory systems. However, upon closer inspection, this model suffers from a concerning shortcoming, that is, its write performance is very unsymmetrical, and lower than most of its counterparts. Thus, to make an improvement in this aspect and other aspects very crucial to SRAM functioning, another SRAM cell consisting of 8 transistors is proposed in this thesis work. The performance indicating parameters of the suggested cell is also compared alongside five other models using the same technology node, supply voltage and identical simulation conditions. After conducting transient analysis on the proposed SRAM cell, the results indicate a read delay of 83 picoseconds (pS) and a write delay of 126 pS. Analysis of power consumption shows that the proposed SRAM cell consumes dynamic read and write power of 12.8  $\mu$ W and 10.4 nW respectively and a static power consumption of 0.932  $\mu$ W. It was also observed to have static read noise margin of 140.8 mV and hold noise margin of 143.5 mV each and a write margin of 400.6 mV. Supply voltage variation to emulate voltage drop variation reveals variation of hold, read and write margin as shown in the graphical representations below. Further, temperature variations were simulated which showed that hold margin varied at 0.77 mV/°C, read margin at 0.79 mV/°C and write noise margins at 0.58 mV/°C.

## CONTENTS

| Candidate   | e's Declaration                                       | ii   |

|-------------|-------------------------------------------------------|------|

| Certificate |                                                       | iii  |

| Acknowle    | dgment                                                | iv   |

| Abstract    |                                                       | V    |

| Content     |                                                       | vii  |

| List of Fig | ures                                                  | X    |

| List of Ta  | bles                                                  | xiii |

| List of abl | previations                                           | xiv  |

|             | CHAPTER 1 INTRODUCTION                                | 1    |

| 1.1         | Memory Classification                                 | 2    |

| 1.2         | Motivation                                            | 3    |

| 1.3         | Objectives                                            | 4    |

| 1.4         | Methodology                                           | 4    |

| 1.5         | Tools Used                                            | 5    |

| 1.4         | Thesis Organization                                   | 5    |

|             | CHAPTER 2 LITERATURE REVIEW                           | 8    |

| 2.1         | Different Reported SRAM Cells                         | 8    |

| 2.2         | Review for Parameters of Different SRAM Cells         | 15   |

| 2.3         | Research Gap                                          | 17   |

|             | <b>CHAPTER 3 PARAMETRIC EXTRACTION</b>                | 18   |

|             | AND PERFORMANCE ANALYSIS OF                           |      |

|             | EXISTING SRAM CELLS                                   |      |

| 3.1         | Architecture of Different Existing SRAM Cells         | 18   |

| 3.1.1       | Conventional 6T SRAM cell                             | 18   |

| 3.1.2       | 7T SRAM cell                                          | 20   |

| 3.1.3       | Standard 8T SRAM cell                                 | 23   |

| 3.1.4       | Transmission Gate bases 8T SRAM cell                  | 25   |

| 3.1.5       | 9T SRAM cell                                          | 27   |

| 3.2         | Parameter Extraction of Different Existing SRAM Cells | 29   |

|     | 3.2.1 | Read Static Noise Margin (RSNM)                                                         | 29 |

|-----|-------|-----------------------------------------------------------------------------------------|----|

|     | 3.2.2 | Hold Static Noise Margin (HSNM)                                                         | 30 |

|     | 3.2.3 | Write Margin (WM)                                                                       | 32 |

|     | 3.2.4 | Transient Analysis                                                                      | 38 |

| 3.3 |       | Summary of Results                                                                      | 41 |

|     |       | CHAPTER 4 DESIGN AND ANALYSIS OF                                                        | 43 |

|     |       | PROPOSED 8T SRAM CELL                                                                   | 10 |

| 4.1 |       | Architecture of Proposed SRAM cell                                                      | 43 |

| 4.2 |       | Working Mechanism Of Proposed SRAM Cell                                                 | 46 |

|     | 4.2.1 | Write Operation                                                                         | 46 |

|     | 4.2.2 | Hold Operation                                                                          | 46 |

|     | 4.2.3 | Read Operation                                                                          | 47 |

| 4.3 |       | Static Noise Margins                                                                    | 48 |

|     | 4.3.1 | Read Static Noise Margin                                                                | 48 |

|     | 4.3.2 | Hold Static Noise Margin                                                                | 49 |

|     | 4.3.3 | Write Margin                                                                            | 50 |

| 4.3 |       | Transient Analysis                                                                      | 51 |

| 4.4 |       | Access Delay                                                                            | 52 |

| 4.5 |       | Summary of Results                                                                      | 53 |

|     |       | CHAPTER 5 STATIC AND DYANAMIC                                                           | 54 |

|     |       | PERFORMANCE COMPARISON OF DESIGNED                                                      | 01 |

|     |       | 8T CELL WITH EXISTING CELLS                                                             |    |

| 5.1 |       | Comparison of Proposed Cell with Other Existing Cells of Different<br>Transistor Counts | 54 |

|     | 5.1.1 | Read Static Noise Margin                                                                | 55 |

|     | 5.1.2 | Hold Static Noise Margin                                                                | 55 |

|     | 5.1.3 | Write Margin                                                                            | 56 |

|     | 5.1.4 | Read Access Delay                                                                       | 56 |

|     | 5.1.5 | Write Access Delay                                                                      | 57 |

|     | 5.1.6 | Supply Voltage Variations                                                               | 57 |

|     | 5.1.7 | Temperature Variations                                                                  | 59 |

viii

|     | 5.1.8 | Power Consumptions                                                                | 61 |

|-----|-------|-----------------------------------------------------------------------------------|----|

| 5.2 |       | Comparison of Proposed Cell with Other Existing Cells of Same<br>Transistor Count | 63 |

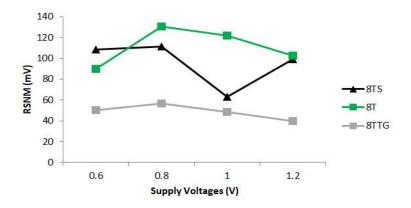

|     | 5.2.1 | Read Static Noise Margin                                                          | 63 |

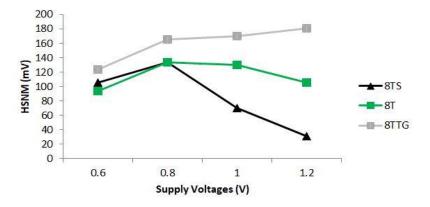

|     | 5.2.2 | Hold Static Noise Margin                                                          | 64 |

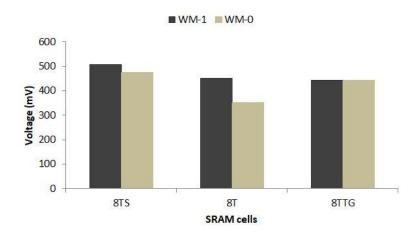

|     | 5.2.3 | Write Margin                                                                      | 64 |

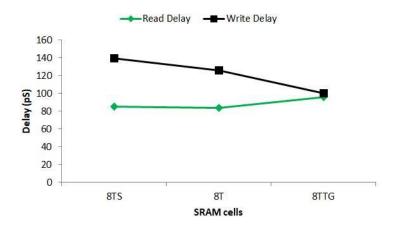

|     | 5.2.4 | Read Access Delay                                                                 | 65 |

|     | 5.2.5 | Write Access Delay                                                                | 65 |

|     | 5.2.6 | Supply Voltage Variations                                                         | 65 |

|     | 5.2.7 | Temperature Variations                                                            | 68 |

|     | 5.2.8 | Power Consumptions                                                                | 69 |

| 5.3 |       | Summary of Results                                                                | 71 |

|     |       | <b>CHAPTER 6 CONCLUSION AND FUTURE</b>                                            | 73 |

|     |       | SCOPE                                                                             |    |

| 6.1 |       | Conclusion                                                                        | 73 |

| 6.2 |       | Future Scope                                                                      | 74 |

|     |       | PUBLICATION LIST                                                                  | 76 |

|     |       | REFERENCES                                                                        | 77 |

# **LIST OF FIGURES**

| Fig. No.  | <b>Caption of Figure</b>                                                                                            | Page No. |

|-----------|---------------------------------------------------------------------------------------------------------------------|----------|

| Fig. 1.1  | Memory Classification                                                                                               | 2        |

| Fig. 3.1  | Schematic of Conventional 6T SRAM cell                                                                              | 18       |

| Fig. 3.2  | Schematic of 7T SRAM cell                                                                                           | 20       |

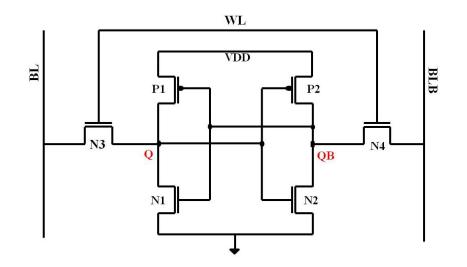

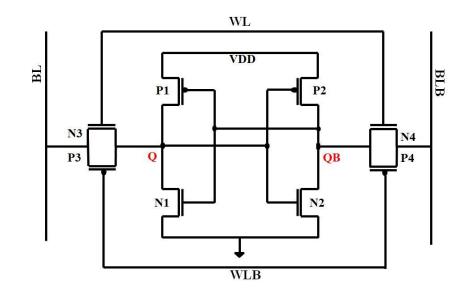

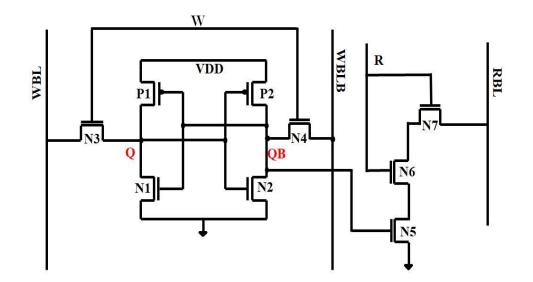

| Fig. 3.3  | Schematic of standard 8T SRAM                                                                                       | 23       |

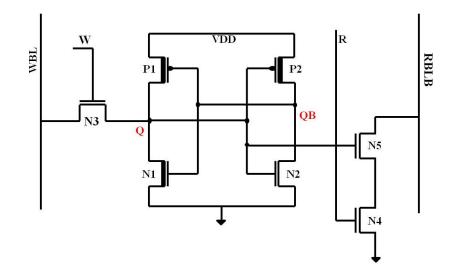

| Fig. 3.4  | Schematic of transmission gate based 8T SRAM cell                                                                   | 25       |

| Fig. 3.5  | Schematic of 9T SRAM cell                                                                                           | 27       |

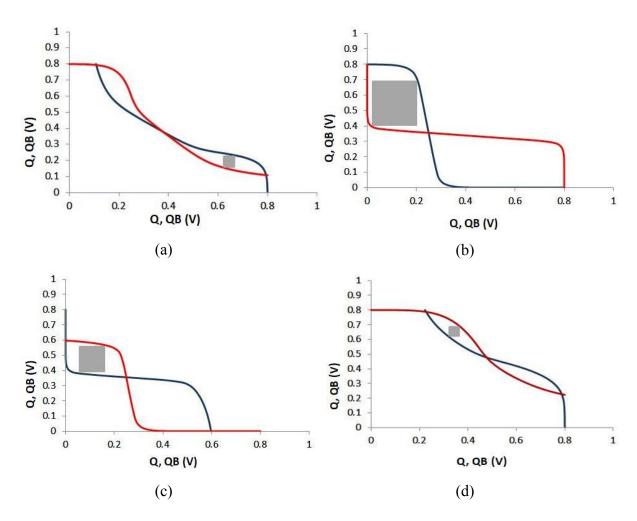

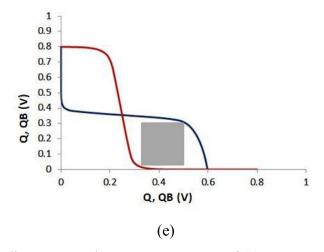

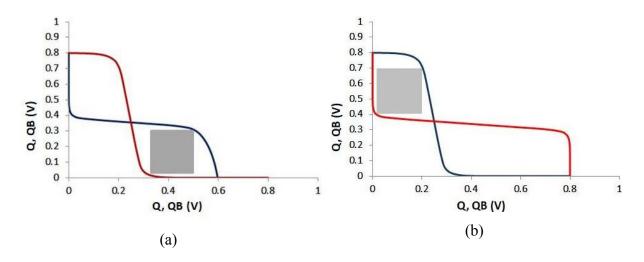

| Fig. 3.6  | Butterfly diagrams used to measure RSNM of (a) 6T SRAM,<br>(b) 7T SRAM, (c) 8TS SRAM, (d) 8TTG SRAM, (e) 9T<br>SRAM | 30       |

| Fig. 3.7  | Butterfly diagrams used to measure HSNM of (a) 6T SRAM,<br>(b) 7T SRAM, (c) 8TS SRAM, (d) 8TTG SRAM, (e) 9T<br>SRAM | 31       |

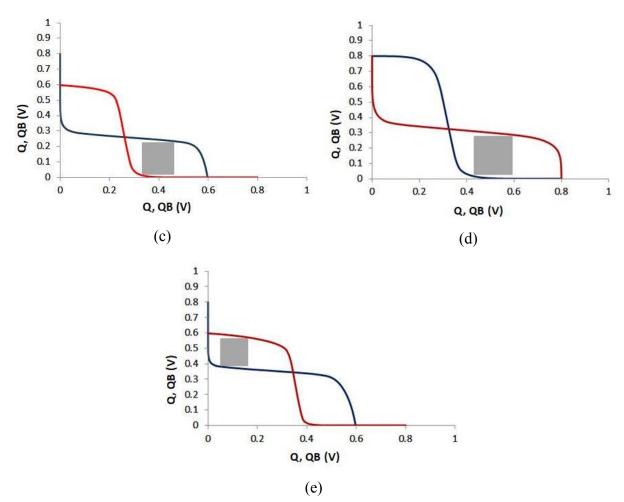

| Fig. 3.8  | (a)Write-1 Margin and (b) Write-0 Margin for 6T SRAM cell                                                           | 33       |

| Fig. 3.9  | (a) Write-1 Margin, (b) Write-0 Margin for 7T SRAM cell                                                             | 34       |

| Fig. 3.10 | (a) Write-1 Margin, (b) Write-0 Margin for standard 8T SRAM cell                                                    | 35       |

| Fig. 3.11 | (a) Write-1 Margin, (b) Write-0 Margin for 8TTG SRAM cell                                                           | 36       |

| Fig. 3.12 | (a) Write-1 Margin, (b) Write-0 Margin for 9T SRAM cell                                                             | 37       |

| Fig. 3.13 | Transient waveform of 6T SRAM cell                                                                                  | 38       |

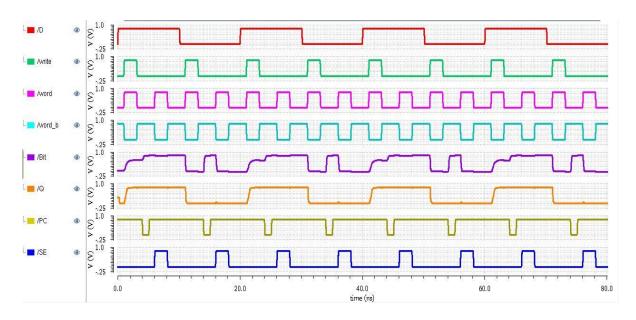

| Fig. 3.14 | Transient waveform of 7T SRAM cell                                                                                  | 39       |

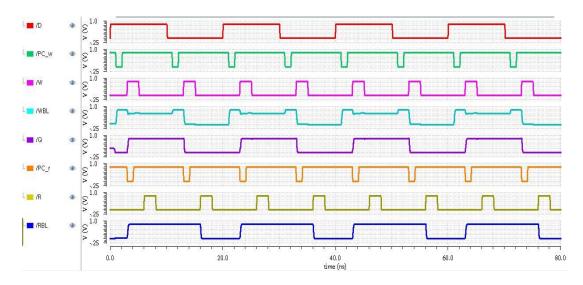

| Fig. 3.15 | Transient waveform of standard 8T SRAM cell                                                                         | 39       |

| Fig. 3.16 | Transient waveform of TG based 8T SRAM cell                                                                         | 40       |

| Fig. 3.17 | Transient waveform of 9T SRAM cell                                                                                  | 41       |

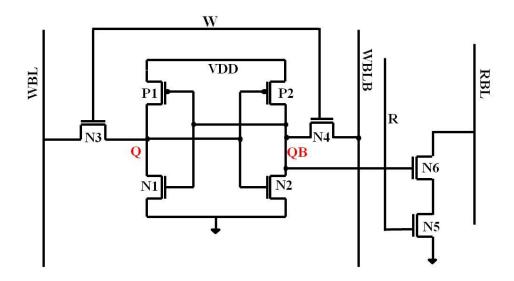

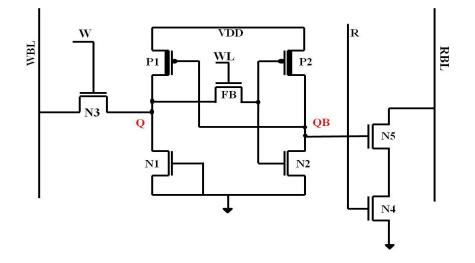

| Fig. 4.1  | Schematic of proposed 8T SRAM cell                                                                                         | 43 |

|-----------|----------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 4.2  | Schematic of proposed 8T SRAM cell during write operation.                                                                 | 46 |

| Fig. 4.3  | Schematic of proposed 8T SRAM cell during hold operation                                                                   | 47 |

| Fig. 4.4  | Schematic of proposed 8T SRAM cell during read operation                                                                   | 48 |

| Fig. 4.5  | Butterfly curve used to measure RSNM for proposed 8T SRAM cell                                                             | 49 |

| Fig. 4.6  | Butterfly curve used to measure HSNM for proposed 8T SRAM cell                                                             | 49 |

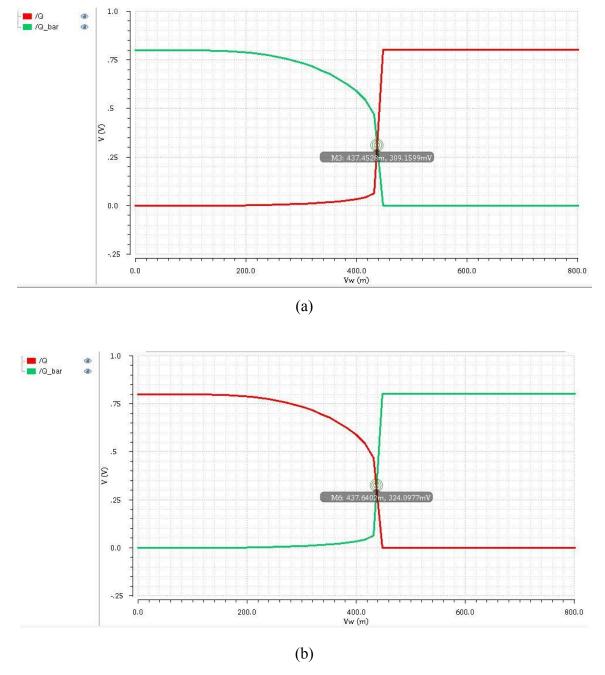

| Fig. 4.7  | Write-1 Margin for proposed 8T SRAM cell                                                                                   | 50 |

| Fig. 4.8  | Write-0 Margin for proposed 8T SRAM cell                                                                                   | 51 |

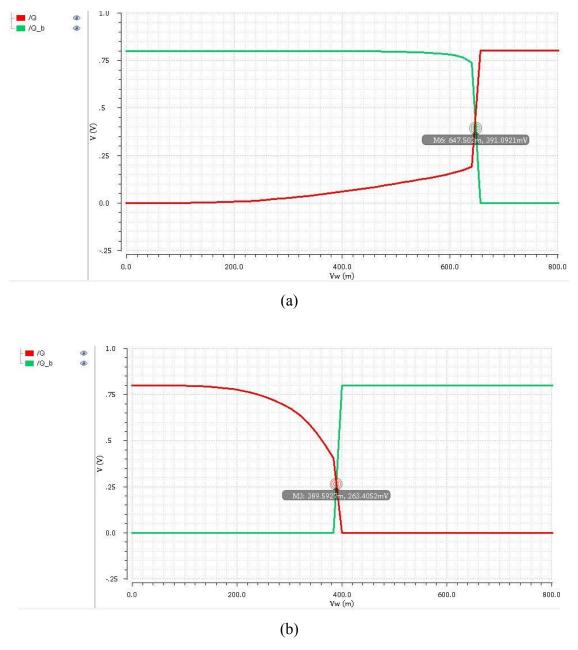

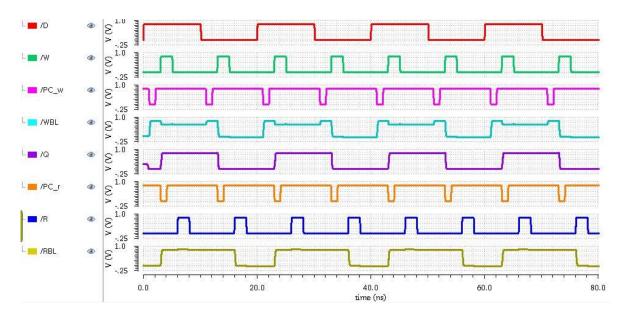

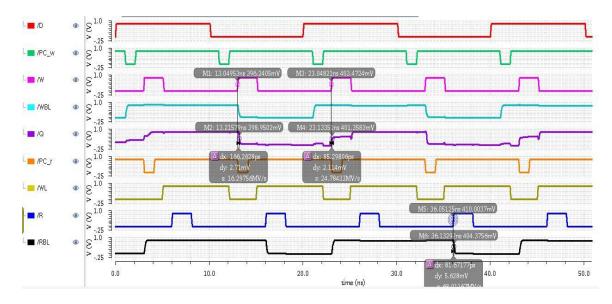

| Fig. 4.9  | Transient waveform of proposed 8T SRAM cell                                                                                | 52 |

| Fig. 4.10 | Access delay calculation from transient waveform for proposed 8T SRAM cell                                                 | 53 |

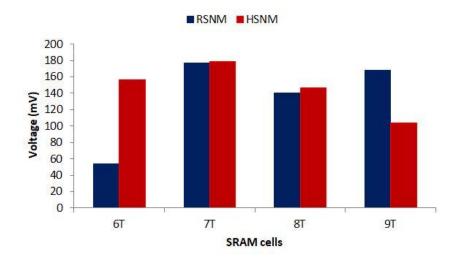

| Fig. 5.1  | Comparison of RSNM and HSNM of SRAM cells with varying transistor counts                                                   | 55 |

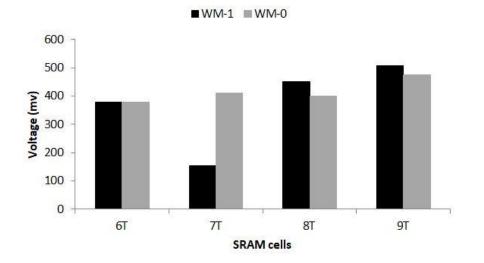

| Fig. 5.2  | Comparison of Write Margin of SRAM cells with varying transistor counts                                                    | 56 |

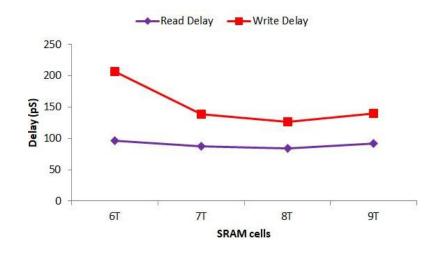

| Fig. 5.3  | Comparison of Read and Write delay of SRAM cells with varying transistor counts                                            | 57 |

| Fig.5.4   | Comparison of HSNM in response to supply voltage variations of SRAM cells with varying transistor counts                   | 58 |

| Fig. 5.5  | Comparison of RSNM in response to supply voltage variations of SRAM cells with varying transistor counts                   | 58 |

| Fig. 5.6  | Comparison of (a) WM-0 and (b) WM-1, in response to supply voltage variations of SRAM cells with varying transistor counts | 59 |

| Fig. 5.7  | Variation of Noise Margins with temperature of SRAM cells with varying transistor counts                                   | 60 |

| Fig. 5.8  | Comparison of dynamic (a) Read Power and (b) Write Power of SRAM cells with varying transistor counts                      | 62 |

| Fig. 5.9  | Comparison of static power consumption of SRAM cells with varying transistor counts                                        | 63 |

| Fig. 5.10 | Comparison of RSNM and HSNM of SRAM cells with same transistor count                                                       | 64 |

| Fig. 5.11 | Comparison of Write Margin of SRAM cells with same transistor count                                                        | 64 |

| Fig. 5.12 | Comparison of Read and Write delay of SRAM cells with same transistor count                                                  | 65 |

|-----------|------------------------------------------------------------------------------------------------------------------------------|----|

| Fig. 5.13 | Comparison of HSNM in response to supply voltage variations of various SRAM cells with same transistor count                 | 66 |

| Fig. 5.14 | Comparison of RSNM in response to supply voltage variations of various SRAM cells with same transistor count                 | 66 |

| Fig. 5.15 | Comparison of (a) WM-0 and (b) WM-1, in response to<br>supply voltage variations of SRAM cells with same transistor<br>count | 67 |

| Fig. 5.16 | Variation of Noise Margins with temperature of SRAM cells with same transistor count                                         | 68 |

| Fig. 5.17 | Comparison of dynamic (a) Read Power and (b) Write Power of SRAM cells with same transistor count                            | 70 |

| Fig. 5.18 | Comparison of static power consumption of SRAM cells with same transistor count                                              | 71 |

## LIST OF TABLES

| Table No. | Caption of Table                                             | Page No. |

|-----------|--------------------------------------------------------------|----------|

| Table 2.1 | Parametric analysis of various differential ended SRAM cells | 14       |

| Table 2.2 | Parametric analysis of various single ended SRAM cells       | 15       |

| Table 3.1 | Transistor sizing of conventional 6T SRAM cell               | 19       |

| Table 3.2 | Transistor sizing of 7T SRAM cell                            | 21       |

| Table 3.3 | Transistor sizing of standard 8T SRAM cell                   | 24       |

| Table 3.4 | Transistor sizing of transmission gate based 8T SRAM cell    | 26       |

| Table 3.5 | Transistor sizing of 9T SRAM cell                            | 28       |

| Table 4.1 | Transistor sizing of proposed 8T SRAM cell                   | 45       |

## LIST OF ABBREVIATIONS

| S.No. | Abbreviation | Full Name                   |

|-------|--------------|-----------------------------|

| 1.    | SRAM         | Static Random Access Memory |

| 2.    | BL           | Bit Line                    |

| 3.    | BLB          | Bit Line Bar                |

| 4.    | WL           | Word Line                   |

| 5.    | WLB          | Word Line Bar               |

| 6.    | TG           | Transmission Gate           |

| 7.    | SNM          | Static Noise Margin         |

| 8.    | RSNM         | Read Static Noise Margin    |

| 9.    | HSNM         | Hold Static Noise Margin    |

| 10.   | WM           | Write Margin                |

| 11.   | PVT          | Process Voltage Temperature |

| 12.   | RBL          | Read Bit Line               |

| 13.   | RBLB         | Read Bit Line Bar           |

| 14.   | WBL          | Write Bit Line              |

| 15.   | WBLB         | Write Bit Line Bar          |

| 16.   | R            | Read Signal                 |

| 17.   | W            | Write Signal                |

| 18. | PC     | Pre-Charge Signal                      |

|-----|--------|----------------------------------------|

| 19. | RAM    | Random Access Memory                   |

| 20. | ROM    | Read Only Memory                       |

| 21. | DRAM   | Dynamic Random Access Memory           |

| 22. | EPROM  | Erasable Programmable Read Only Memory |

| 23. | EEPROM | Electrically Erasable Read Only Memory |

| 24. | PROM   | Programmable Read Only Memory          |

## **CHAPTER 1**

## **INTRODUCTION**

Artificial intelligence (AI) is the recent buzz in today's technology world and the hype is rightly deserved, because AI is really the future. There aren't many things left that AI is not capable of doing. And with the advancement of AI, the amount of data to be stored and processed are going to become humungous. In the present technology market, the significance of memory has grown exponentially, with memory-intensive tasks being performed on various devices like mobile phones and computers. Cache memory, a critical component for memory-dependent systems, relies on the fundamental building unit known as the Static Random Access Memory (SRAM) cell [1]. From microcontrollers and System on Chips (SoCs) to personal computers and workstations, memory holds a paramount position in the functionality of diverse systems.

Amongst the different types of memory available, cache memory is one of the most crucial memories since it directly interacts with the Central Processing Unit (CPU) to temporarily store data that are often accessed by the CPU [2]. Thus, as the level of Artificial Intelligence and other technologies become more advanced, it is the cache memory and the memory in general that should be improved in order to facilitate the necessary advancements in technology. This would mean that the cache memories should become faster for the CPU to be able to store and retrieve data from at a much faster speed. Additionally, it should become more power efficient, more robust to noise to store data in a stable manner [2]. Also, the cache memory should be sturdy in response to temperature variance and also voltage variations caused by voltage drops in the power delivery network of chips are the need of the hour. Only when the cache memories perform to its full capacity, will AI live up to its full potential. Cache memories are fundamental components composed of arrays consisting of millions of Static Random Access Memory (SRAM) cells. These SRAM cells are responsible for storing data in a cache memory system, with each cell storing a single bit of data. The collective arrangement of these SRAM cells forms the structure of the cache

memory, allowing for efficient and high-speed data access and retrieval. [1]. So, each type of enhancement that would be demanded from the cache memories would only be achieved when the same enhancements are obtained from the SRAM cells.

This introductory chapter is distributed into six sections. Section 1.1 consists of the classification of different types of memory and where SRAM lies in it. Section 1.2 consists of the motivation, which highlights why the chosen field of research is important and relevant. Section 1.3 highlights the objectives of the research work. Section 1.4 gives a brief discussion about the methodology used to carry out this research work. Section 1.5 highlights the tool used to perform the research work. Lastly, section 1.6 presents the detailed organisation of the thesis.

### **1.1 MEMORY CLASSIFICATION**

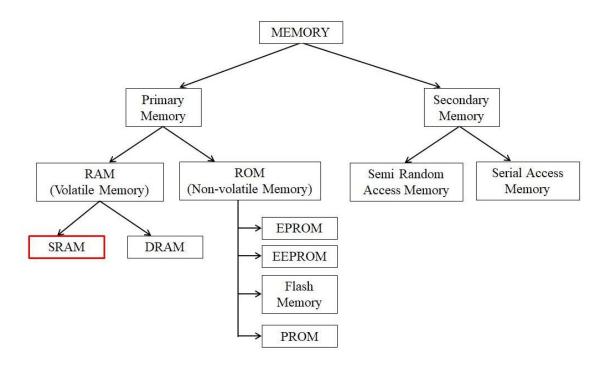

Memory can be classified into many different types. Fig. 1.1 graphically represents the classification of memory types.

Fig. 1.1: Memory Classification

First of all, SRAM belongs to the class of memory called primary memory. Within the primary memory, there are two types divided based on whether it is volatile or not. Volatile

memory, specifically referred to as Random Access Memory (RAM), is a class of memory that retains data only till it receives a continuous power supply. However, as soon as the supply of power is interrupted or cut off, the data stored in RAM is degraded very fast [2]. On the other side, ROM (Read Only Memory) stores its data even when power supply is cut off. The name Read Only Memory is often misleading because many ROM memories can be written to as well as read from. It thus is a non-volatile memory. The types of memories belonging to this class are Flash Memory, , EEPROM (Electrically Erasable Programmable Read Only Memory), PROM (Programmable Read Only Memory), EPROM (Electrically Programmable Read Only Memory) [3]. So, the SRAM (Static Random Access Memory) is a type of Random Access Memory which is rapid and dense in nature. The DRAM on the other hand is slow and compact. The SRAM stores its data in a back-to-back inverter whereas the DRAM stores its data on a capacitor, so it needs to be refreshed periodically.

There is also another broad class of memory called the secondary memory. Secondary memory is external storage that everlastingly saves data. The CPU can access primary memory data directly, while secondary memory data cannot be accessed. [4].

### **1.2 MOTIVATION**

There are certain features of an SRAM cell that has been the source of bad performances in the past existing SRAM architectures and hence improving these features would mean enhancing the SRAM cell. For instance, SRAM cells face challenges such as small noise margins and high power consumption. Their larger transistor count limits density, hindering the inclusion of more cells in a given area. While they offer fast access, achieving higher speeds can be difficult. Temperature and voltage variations contribute to higher noise parameter variations. These troubles are present in one or the other way in many existing SRAM cell architectures. Overcoming these troubles overall is the problem statement with regards to SRAM cell design. A common method researchers have taken up is to rigorously scale down the technology nodes.

However, along with the technology node scaling, supply voltages also must be scaled down so that field strength remains the same [1]. And with voltage scaling comes several adverse effects, such as the data held in the SRAM cell becoming more susceptible to noise and variability with respect to temperature, process, etc increasing. In addition to this, with decrease in supply voltage, leakage power that happens in standby mode starts to increase so much beyond its normal levels that it becomes comparable to dynamic power consumption. Additionally, a decrease in supply voltage causes access delays to worsen, which means reduction of speeds and frequency in which the memory would operate. In an attempt to solve these complications, researchers have resorted to using a greater number of transistors and a configuration of transistors different to the famous 6T SRAM cell [10]. However, more transistors would also mean a more area occupation and hence less dense memory arrays. So, it all comes down to managing these trade-offs to find the perfect fit that would be robust to noise and variations, less power consuming, fast and at the same be fairly low on the transistor count.

### **1.3 OBJECTIVES**

Having considered all the problems and concerns with regards to the design of an SRAM cell, it thus makes sense to dwell further into SRAM design and look for enhancements and modifications that can be made to the existing SRAM cell architectures and further make an effort to propose an improved SRAM cell that eases the complications stated in problem statements section. Thus the objectives of this thesis work are:

1. To review some important existing SRAM cell topologies, with an emphasis on how each architecture provides a unique form of improvement.

2. To propose a novel SRAM cell architecture that proves to be superior with regards to parameters such as Static Noise Margins (SNMs), power efficiency, access speed, sturdiness in response to temperature and supply voltage variations.

3. To compare the performances of the proposed SRAM cell architecture against that of some existing SRAM models that also acted as motivation towards the design of the architecture and are also similar in some aspects such as transistor configuration and count.

### **1.4 METHODOLOGY**

The methodology of this research begins with the parametric extraction and comprehensive review of fundamental existing SRAM cell architectures that consists of varying number of transistors. The review is comprehensive because all the SRAM cell architectures have been simulated using the same tool, same technology node and other identical aspects to understand their working in detail, to measure the performance indicating parameters individually. Here, five previously reported SRAM cell architectures are studied and reviewed, out of which two models have the same number of transistors as the proposed SRAM cell and three models have varying number of transistors in their respective designs. The knowledge gained from this extensive review is used to help in the design of our proposed SRAM model. The proposed model incorporates a technique where the mutual feedback between a pair of inverters is interrupted during a write process. During the write operation, the outputs of the inverters in the SRAM cell are not directly connected to the inputs of the other inverter, resulting in an isolated configuration. By cutting this feedback loop, the model aims to optimize the write operation and improve the overall performance of the system. This is done so that the write performance improves. Then, the proposed SRAM model is realised schematically in the software and simulated using the same tool and technology node. The simulation results are used to authenticate the correct functionality of the circuit and also to extract the performance indicating parameters. Then lastly, the proposed SRAM cell is put into test by comparing the measures of its performance indicating parameters with that of the existing SRAM cells. The comparative analysis results are utilized to validate the advantage of the proposed cell compared to the existing SRAM cells.

### **1.5 TOOLS USED**

The software used for carrying out the research is Cadence Virtuoso. The Cadence Virtuoso tool was used for constructing schematics of various SRAM cells and simulating them using the same technology node, identical supply voltage, same variation of temperature and supply voltage to observe their performance with regards to parameters such as Static Noise

Margins (SNMs), power consumption, access speed, sturdiness to variation of voltage and temperature.

## **1.6 THESIS ORGANIZATION**

The complete dissertation is organized into 6 chapters. Chapter 1 gives introduction of the thesis work that includes in its subsections, the background behind the research work amongst other things. Then Chapter 2 that includes literature survey and research gap. Chapter 3 includes detailed review and analysis of some existing SRAM cell architectures that also served as motivation towards the architecture of the suggested SRAM cell. Chapter 4 gives a thorough explanation on the methodology and implementation of the proposed work. Chapter 5 gives a comparison of performance of some important parameters of the proposed SRAM model against some existing models. Chapter 6 consists of conclusion and future scope. Each chapter consists of subsections.

- **CHAPTER 1**: This chapter highlights the importance of memory in today's technologically advanced world. It includes the following: basic classification of memory types, the motivation behind choosing such a topic as an area of interest for research, the methodology followed during the research work, details of the tools used and the objectives of the thesis work in a detailed manner.

- **CHAPTER 2**: A literature review of previous reported works is discussed in this chapter. It consists of brief reviews of different types of SRAM cell architectures with varying transistor counts, varying number of bitlines and ports. It also includes the research gap that we will be looking to exploit in this thesis work.

- **CHAPTER 3:** This chapter presents the comprehensive review of some existing SRAM cell architectures. The extensive review of each of the considered SRAM cell architectures is concluded with the complications that were observed in each of the designs and how each model looks to improve on the shortcomings of previous design.

- **CHAPTER 4:** This chapter elucidates the proposed SRAM cell model, discussing its design and operation. It also includes the simulation results of each of the considered performance indicating parameters.

- **CHAPTER 5:** This chapter offers a detailed comparative analysis between the proposed 8T SRAM cell and five existing cell models that motivated its design in some or the other way. The comparison is done on five primary parameters such as static noise margins, access delays, power consumption, response to temperature variation and supply voltage variation. There are sub parameters within each parameter also.

- **CHAPTER 6:** The dissertation is concluded with the overall conclusions and data of results drawn from the research work. It also includes future scopes of improvement related to the topic of research.

The list of publications related to the research done for this thesis is also attached. After that, a comprehensive list of references is provided, which is utilized to cite earlier study to determine the routes our current work should take.

## **CHAPTER 2**

## LITERATURE REVIEW

Genuine research ideas mostly stem from previous works reported by other researchers in the same field. So in order to perform a research work, it is always vital to go through the work that has been reported. A literature review's purpose is to:

- Build an initial basis for understanding the topic of research.

- Identify past areas of research to reduce duplication and give deserved recognition to works done by other researchers.

- Acknowledge the discrepancies, research gaps, major research disputes, and unresolved problems in earlier studies.

This chapter is distributed into two sections. Previously reported work is the section 2.1. Section 2.2 gives a complete review in a tabular form. Research gap in this area of study is discussed in the section 2.3.

## 2.1 DIFFERENT REPORTED SRAM CELLS

#### • "Implementation of Low-Power 6T SRAM Cell Using MTCMOS Technique", 2017

T. Tripathi, D.S. Chauhan, S.K. Singh and S.V. Singh [17] reported a 6T SRAM cell based on MTCMOS technique. The major intention of the innovation was to reduce leakage power consumption during idle mode. It uses two types of transistors with, one with high threshold voltage ( $V_T$ ) and the other with low  $V_T$ . The simulation results reported a significant reduction in leakage power consumption.

#### • "A Modified SRAM Based Low Power Memory Design", 2016

A. Pathak, D. Sachan, H. Peta, M. Goswami [18] reported another modified 6T SRAM cell that focused on reducing hold power consumption. The innovation in this architecture is the

usage of a tail transistor that enables reducing the short circuit power consumption by disconnecting the conductive trail from  $V_{DD}$  to  $V_{SS}$ . This extra transistor called the tail transistor additionally helps in reducing the off-state current (subthreshold current) because it basically helps in forming a stack configuration, thereby reducing subthreshold current. The findings from the simulation prove that the power consumption in hold mode is indeed reduced significantly. Statistical and corner analysis was also performed to determine the design's robustness.

# • "A Novel Approach to Design SRAM Cells for Low Leakage and Improved Stability", 2018

T. Tripathi, D..S Chauhan, S.K. Singh [19] proposed a novel modified 6T SRAM with the intention to have high speed, low leakage current and high stability. They used a combination of multi threshold CMOS and two finger MOS transistors to achieve the enhancements. The research findings indicate that the reported design of the SRAM cell exhibits a remarkable improvement in read stability, nearly 2.7 times higher, and a notable reduction in leakage current, approximately 1.85 times lower, when contrasted with the 6T SRAM cell. As a penalty, an increase in area was observed in the new design.

#### • "A robust and low power 7T SRAM cell design", 2015

K. Mehrabi, B. Ebrahimi and A. Afzali-Kusha [20] reported an SRAM cell consisting of 7 transistors offering enhanced stability during reading and writing processes. The separation of the read and write access transistors in the research addressed the persistent issue of conflicting sizing requirements, enabling the satisfactory execution of both read and write process in the SRAM cell. This innovative approach resolved the long-standing problem of accessing transistors by optimizing their sizing individually for improved performance. The cell also features enhanced read stability through the segregation of the internal node away from the read path, ensuring improved data integrity and reliability. Write ability is also enhanced due to the weakening of positive feedback by usage of virtual ground at one of the inverters in the process of writing onto the cell. The virtual ground in the design also helped reduce the leakage current by providing a stacking effect. The simulation results recorded an improvement of read stability and write ability by 80% and 54.9% respectively.

# • "Single Bit Line Accessed High Performance Ultra Low Voltage Operating 7T SRAM Cell with Improved Read Stability", 2021

B. Rawat and P. Mittal [21] presented a static random-access memory (SRAM) bit cell design comprising of 7 transistors. Notably, their design employed only one bitline for the process of both reading and writing from and to the cell, addressing the need for efficient memory access. The utilization of one bitline in the proposed cell design resulted in reduced activity factor during read and write operations. Compared to other single-ended SRAM cells with varying transistor counts ranging from a transistor count of 5 to 10, the proposed cell exhibited an improved Static Noise Margin (SNM) in all 3 scenarios of read, write, and hold mode. Leakage power was also found to be minimal.

# • "A comprehensive analysis of different 7T SRAM topologies to design a 1R1 W bit interleaving enabled and half select free cell for 32 nm technology node", 2022

B. Rawat, P. Mittal [22] also reported a novel single ended, dual port, 1R1W SRAM cell consisting of 7 transistors. The proposed model uses an extra transistor that enables cutting of mutual feedback connection between the two inverters whose output terminal are coupled to the input terminal of the other inverter and converting it into a cascade of two inverters. The reported SRAM cell model was compared with other 7T SRAM cell models and was found to have the best Hold and Read Static Noise Margin (RSNM/HSNM). Its static power consumption was also observed to be one of the lowest amongst the other existing cells. Process, Voltage and Temperature (PVT) analysis was also performed to prove superior reliability of the cell.

#### • "Leakage Power Attack-Resilient Symmetrical 8T SRAM Cell", 2018

R. Giterman, M. Vicentowski, I. Levi, Y. Weizman, O. Keren and A. Fish [23] proposed an 8T SRAM cell that is designed for low leakage power consumption. To alleviate the influence of leakage currents on stored data, the design of this cell increases two extra transistors to the design of the traditional 6T SRAM, thereby enhancing the stability and integrity of the data existing on the storage nodes. The findings of the simulation that

included Monte Carlo analysis indeed validated the reported SRAM cell's low leakage power.

• "Design and analysis of a 32 nm PVT tolerant CMOS SRAM cell for low leakage and high stability", 2010

S. Lin, K. Yong-Bin and F. Lombardi [5] proposed a 9T SRAM cell that is primarily aimed at providing a robust and process-voltage-temperature variation tolerant cell with minimum static power consumption. The cell is also designed so that the data stored on the cell is has high stability. The simulation findings validated that the tolerance and robustness. The results also revealed that the reported SRAM design consumes 33% lesser leakage power. It also showed that the delay being exhibited by the reported SRAM is on the lower side.

# • "Low leakage 10T SRAM cell with improved data stability in deep sub-micron technologies", 2021

In their study, Krishna and Duraiswamy [28] introduced a novel SRAM cell consisting of 10 transistors. The design incorporates two additional transistors to form a source-biased inverter, effectively reducing static power dissipation. By increasing the potential of the source terminal and decreasing the drain-to-source potential, the leakage power is minimized. The design also employs various assist techniques to enhance cell stability. Simulation results confirm the successful achievement of the design objectives.

# • "Robust transmission gate-based 10T subthreshold SRAM for internet-of-things applications", 2022

E. Abbasian and M. Gholipour [29], presented a complementary pass gate based 10T SRAM cell used in IoT applications. It is compared with other existing SRAM cell designs that are all subjected to the same extreme PVT variations. To enhance the sense margin, the proposed cell utilizes a differential scheme. It strengthens the write-ability by utilizing two complementary pass gates instead of two NMOS transistors used for accessing the nodes. In addition to the differential scheme, the proposed TG10T cell incorporates two additional buffer transistors to enhance read stability. Furthermore, the cell's design focuses on minimizing static power dissipation by utilizing more number of p-channel transistors. The

proposed cell renders better overall performance compared to other SRAMs which makes it appropriate for IoT applications.

# • "A reliable low standby power 10T SRAM cell with expanded static noise margins", 2022

E. Abbasian, F. Izadinasab, and M. Gholipour [30], proposed an SRAM cell that primarily focused on reducing power consumption during standby mode, or in other words the leakage power consumption. The proposed circuit consisted of 10 transistors. It also aimed to attain high read and write noise margins, emphasizing stability as a crucial aspect. The circuit's essential components are a Schmitt-trigger inverter with a pull-up transistor that is twice as long as other transistors and a cross-coupled inverter with stacked transistors. The design of the proposed SRAM cell includes an isolation mechanism that prevents disturbance to the stored data during a read operation by segregating the internal nodes away from the read path. The simulation results confirm the reduction in leakage power consumption achieved by the proposed design.

### • "A Novel Low-Power and Soft Error Recovery 10T SRAM Cell", 2023

C. Liu, H. Liu and J. Yang [31], proposed a 10T SRAM cell with the primary goal to decrease power consumption and increase resilience for soft error that may occur in the storage nodes. The innovation in the design is to add an extra PMOS transistor to facilitate full passage of logic '0'. Simulation results demonstrate that the power dissipation of the reported SRAM cell is significantly lower compared to other existing SRAM cell designs. Also, the resilience to soft-errors is proved. However, the shortcoming this proposed incurs is the increased area footprint because of the extra PMOS transistor used in the design.

# • "A reliable and temperature variation tolerant 7T SRAM cell with single bit line configuration for low voltage application", 2022

B. Rawat and P. Mittal [27], proposed a 7T cell which is of single-ended configuration. The reported cell demonstrates a satisfactory hold/read static noise margin, indicating its ability to maintain stable data storage and reliable read operations. The cell is architectured so that it is suited for low voltage applications. It uses just one bitline for each of the cell access

operations (read and write). The sturdiness of the suggested cell was validated using Monte Carlo analysis with respect to process and. The suggested cell was also contrasted with preexisting SRAM cells in order to prove that it indeed is superior with regards to the performance indicating parameters. The simulation results validated that the power dissipation was found to be minimal in the proposed design. This is mainly accredited to the fact that performing read and write operation required a pulse width of a few nanoseconds. Thus, the proposed cell exhibited superiority when compared to its counterparts.

#### • "A novel 8T SRAM cell with improved read-SNM", 2007

A. Sil, S. Ghosh and M. Bayoumi [32] reported an SRAM cell that consisted of 8 transistors and primarily focused on enhancement of cell stability. It aims to eliminate the impact of noise during read operation. The simulation results indicated a very high Read Static Noise Margin (RSNM) value of 468 mV where the supply voltage was 1.2 V. It also achieved a low power consumption, which is achieved mainly because of the use of low voltage to pre-charge the bitlines, which is much lower than the supply voltages. But the major concern is that multi domain designs are always difficult to realise and involves many practical issues.

## "A Single-Ended With Dynamic Feedback Control 8T Subthreshold SRAM Cell", 2015

C. B. Kushwah and S. K. Vishvakarma [33] proposed an 8T SRAM cell that has improved data stability in subthreshold region. The cell designed by the researchers has a single ended architecture with dynamic feedback control. This innovative configuration allows an increase of write margin to almost 1.4 times compared to that of the traditional 6T SRAM architecture at 300 mV. The read and hold SNMs are fairly improved compared to other existing SRAM cell designs. Write access delay was also found to be better for this design. Additionally, write power is also minimized in comparison to other designs. Overall the design was proved to be more suitable for low power applications.

#### • "Power-Gated 9T SRAM Cell for Low-Energy Operation", 2017

T. W. Oh, H. Jeong, K. Kang, J. Park, Y. Yang and S. -O. Jung [34] proposed an SRAM cell consisting of 9 transistors that uses the power gating transistors to reduce power

consumptions. The proposed cell makes use of an access buffer that is decoupled from read path. The cell also focused on improving soft error immunity by using bit interleaving and a virtual ground for each column of SRAM array. The simulation results reveals an enhanced Read Static Noise Margin (RSNM).

### • "Single-Ended Subthreshold SRAM with Asymmetrical Write/Read-Assist", 2010

M. -H. Tu, J. -Y. Lin, M. -C. Tsai, S. -J. Jou and C. -T. Chuang [37] proposed a novel 8T SRAM that makes use of a write assist scheme. It also uses a biasing technique that involves virtual ground. Additionally, it uses positive feedback sensing schemes. The main notion of the reported cell architecture is to improve the read and noise margins, and the access speeds. The architecture uses one bitline only for each of both read and write modes separately. The researchers assembled and array of 256x16 bits in order to test the cell's performances. The results proved that the read and write margins were improved significantly (up to 35% and 50% of supply voltage respectively).

### • "Single bit-line 11T SRAM cell for low power and improved stability", 2020

R. Lorenzo and R. Pailly [38] reported an 11T SRAM cell. It aims to achieve a minimal leakage power and improved write performance by making use of the innovation of power gating transistors and transmission gates. It also looks to resolve the issue of half select disturbance by using a virtual ground signal for a common row. This eliminates the undesired discharge of bitline in an accessed row, which results in decrease energy consumption. The model is compared to other existing SRAM cells of varying transistor counts starting from 6T to 9T to validate its parameters' performances. The simulation findigns revealed a notable enhancement in read static noise margins and write margins and a significant improvement in read and write delays.

## • "An 8T low-voltage and low-leakage half-selection disturb-free SRAM using bulk-CMOS and FinFETs", 2014

G. Pasandi and S. M. Fakhraie [39] proposed an 8T SRAM cell designed for low leakage power consumption. It is found to be functional at low supply voltages. It also focuses on making the SRAM cell array free from half- select disturbances during write operations by using a novel internal write-back technique. The simulation results also revealed an improvement of 0.58 and 0.67 in read and write power. The researchers also design the SRAM cell on FinFET technology because of which the simulation results showed that the FinFET variant is less sensitive to variations and also recorded a significant improvement (about twice) in Read SNM.

## 2.2 REVIEW FOR PARAMETERS OF DIFFERENT SRAM CELLS

In the two tables given below, the existing SRAM cell architectures that have been reviewed in this section are presented in a tabular column that summarises the measure of parameters of the cells. The cells are grouped into two broad classes, one class with differential ended design and the other with single ended design.

| S.  | Authors                 | Transi | Techn | Supply  | Access  | Leakage  | SNM                |

|-----|-------------------------|--------|-------|---------|---------|----------|--------------------|

| No. |                         | stor   | ology | Voltage | Delay   | power    | (RSNM/HSNM/WM      |

|     |                         | count  | node  |         |         |          | ) (in mV)          |

| 1.  | Tripathi et al.         | 6      | 45nm  | 0.8 V   | -       | 126.93   | 41.25/32.67/130.33 |

|     | [17]                    |        |       |         |         | pW       |                    |

| 2.  | Pathak <i>et al</i> .   | 6      | 45 nm | 0.8 V   | 11.4 pS | 5.68 pW  | -/-/205            |

|     | [18]                    |        |       |         |         |          |                    |

| 3.  | Tripathi et al.         | 8      | 55 nm | 0.6 V   | -       | 80 pW    | 59.94/45.32/176.98 |

|     | [19]                    |        |       |         |         |          |                    |

| 4.  | Giterman et al.         | 8      | 65 nm | 1.2 V   | -       | 2.808 nW | 205/460/445        |

|     | [23]                    |        |       |         |         |          |                    |

| 5.  | Lin <i>et al</i> . [5]  | 9      | 32 nm | 0.6 V   | 82.04   | -        | -                  |

|     |                         |        |       |         | pS      |          |                    |

| 6.  | Krishna et al.          | 10     | 32 nm | 1 V     | 916.7   | 9.37 pW  | 201/-/463          |

|     | [28]                    |        |       |         | pS      |          |                    |

| 7.  | Abbasian et al.         | 10     | 16 nm | 0.36 V  | 340 pS  | 1.15 nW  | 29.8/87.3/-        |

|     | [29]                    |        |       |         |         |          |                    |

| 8.  | Abbasian <i>et al</i> . | 10     | 16 nm | 0.7 V   | 299 pS  | 11.79 nW | 225.5/225.5/356.6  |

|     | [30]                    |        |       |         |         |          |                    |

Table 2.1: Parametric analysis of various differential ended SRAM cells

| 9. | Liu <i>et al.</i> [31] | 10 | 22 nm | 0.8 V | 17.9 pS | 2.92 nW | 340/510/270 |

|----|------------------------|----|-------|-------|---------|---------|-------------|

|----|------------------------|----|-------|-------|---------|---------|-------------|

Table 2.1 showcases all the differential ended SRAM cells with measurements of important performance indicating parameters. It also highlights the number of transistors used in the design, the technology node used and the supply voltage in which the circuit operates.

|                        |                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                | Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Leakage       | SNM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

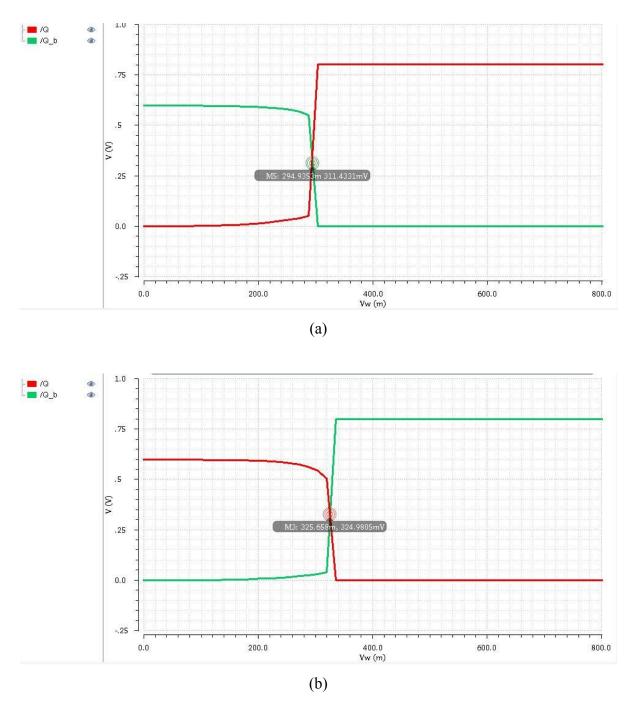

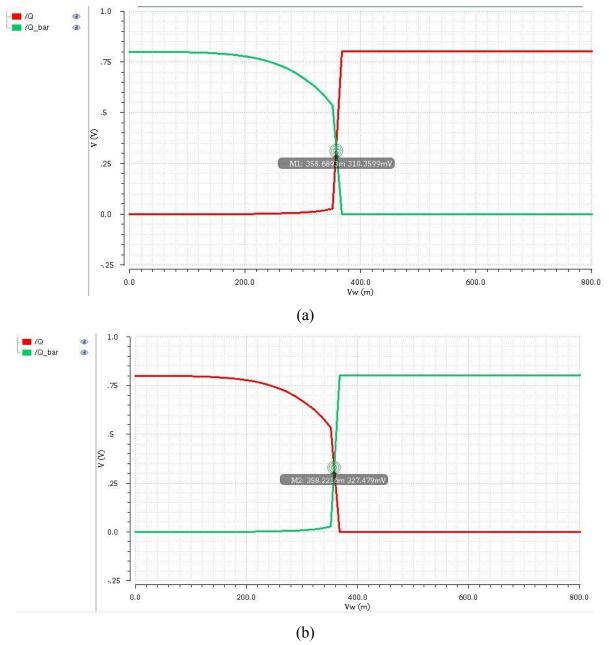

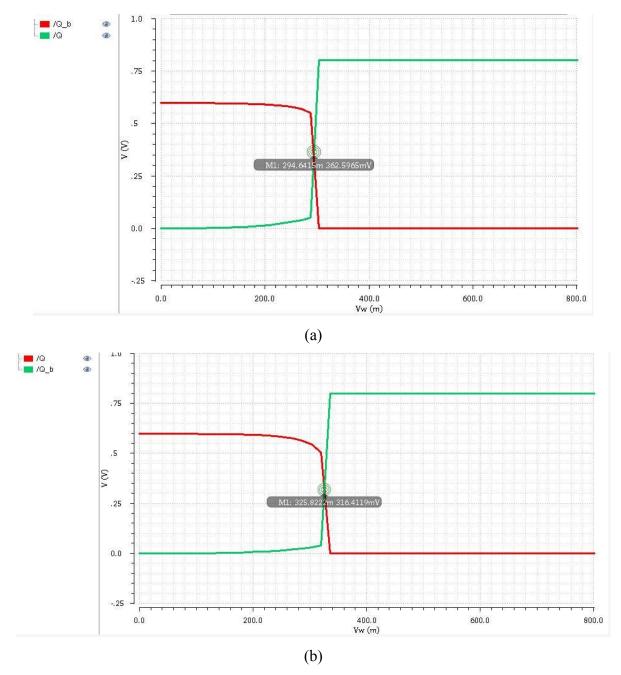

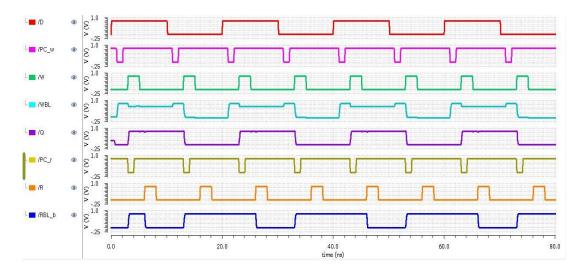

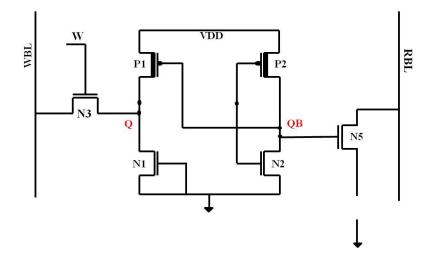

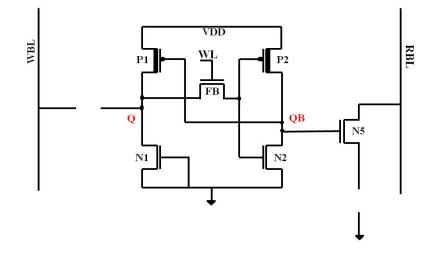

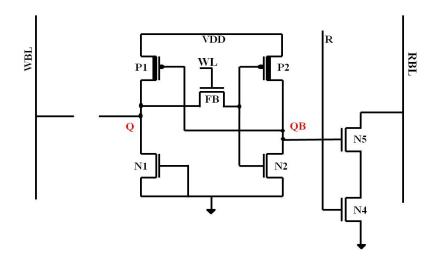

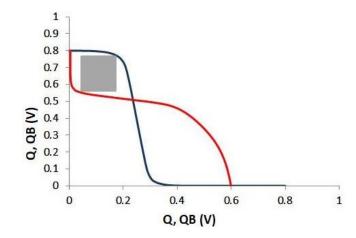

|                        | count                                                                                                                                                                                                                                                             | node                                                                                                                                                                                                                                                                                                                                                                                                           | Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | power         | (RSNM/HSN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |