### ANALYSIS, DESIGN AND IMPLEMENTATION OF DIGITAL CONTROL LOOP BASED ON TMS320F2812 DSP FOR BUCK AND SINGLE INPUT MULTI OUTPUT BOOST CONVERTER IN VOLTAGE CONTROL MODE

A PROJECT REPORT

# SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

### MASTER OF TECHNOLOGY IN POWER ELECTRONICS AND SYSTEMS

Submitted by

VANSHIKA JINDAL (2K20/PES/23)

Under the supervision of PROF. DHEERAJ JOSHI

DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi 110042

MAY, 2022

#### DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

#### **CANDIDATE'S DECLARATION**

I, VANSHIKA JINDAL, Roll No's – 2K20/PES/23 student of M.Tech (Power Electronics), hereby declare that the project Dissertation titled "Analysis, Design and Implementation of Digital control loop based on TMS320F2812 DSP for Buck and Single Input Multi Output Boost Converter in Voltage control mode" which is submitted by me to the Department of Electrical Engineering , Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of degree of Master of Technology, is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship or other similar title or recognition.

Place: Delhi

VANSHIKA JINDAL

Date: 31.05.2022

#### DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

#### CERTIFICATE

I hereby certify that the Project Dissertation titled "Analysis, Design and Implementation of Digital control loop based on TMS320F2812 DSP for Buck and Single Input Multi Output Boost Converter in Voltage control mode" which is submitted by Vanshika Jindal, Roll No's – 2K20/PES/23, Power Electronics, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi

Date: 31.05.2022

Dr. Dheeraj Joshi

SUPERVISOR

#### DEPARTMENT OF MECHANICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

#### ACKNOWLEDGEMENT

I wish to express our sincerest gratitude to Dr Dheeraj Joshi for his continuous guidance and mentorship that he provided us during the project. He showed us the path to achieve our targets by explaining all the tasks to be done and explained to us the importance of this project as well as its industrial relevance. He was always ready to help us and clear our doubts regarding any hurdles in this project. Without his constant support and motivation, this project would not have been successful. His dynamism, vision, sincerity and motivation have deeply inspired me. He has taught me the methodology to carry out the project and to present the project work as clearly as possible. It was a great privilege and honor to work and study under his guidance. I am extremely grateful for what he has offered me. Without the wise advice and able guidance, it would have been impossible to complete the dissertation in this manner. I would like to thank the staff members (Ms. Renu and Ms. Vandana) of Power Electronics Lab for co-operating with me and providing me with the best possible working environment for the assignment. I would like to extend my thanks to Mr Aashutosh Gupta, Dr. Aakash Seth and Dr. Arvind Goswami, PhD Scholar, Delhi Technological University, without the help of whom the dissertation would not have been completed. I would also like to thank all my friends for their help, moral support and encouragement provided by them during the completion of the dissertation work. I am extremely grateful to my parents and family members for their love, prayers, caring and sacrifices for educating and preparing me for my future.

Place: Delhi

Date: 31.05.2021

Vanshika Jindal

### Abstract

DC-DC power converters play an important role in powering telecom and computing systems. With the speed improvement and cost reduction of digital control, digital controller is becoming a trend for DC-DC converters in addition to existed digital monitoring and management technology. Design and implementation of digital controllers for a buck and SIMO Boost converters using linear control methods are investigated in this thesis. The small signal analysis of an ideal and non ideal Buck and SIMO Boost is being obtained using standard state space averaging techniques. Analog PI controllers were designed for generic DC-DC converters using different PI tuning rules and compensator design using frequency response considering stability. The digital control loop is designed and implemented using Direct and Indirect design approaches using various discrete conversion methods such as Forward euler, Backward euler and Tustin approximations. The validity of the non-isolated DC-DC converter with ratings 45W, 15V, 3A for SIMO Boost converter at 50 kHz frequency and 18W,12V, 1.5A for Buck converter at 20 kHz switching frequency are verified by simulations and experimental results for closed loop operation under variation in input voltage and load. Control algorithms using PI and Fuzzy-Sugeno controller are implemented using Texas Digital Signal Processors - TMS320F2812 and MATLAB/Simulink (version 2021b) platform has been utilized for simulation purpose. Limitations of practical implementation of digital control on DC-DC converters which includes the digital PWM resolution (limit cycles), the ADC sampling delay and limited control bandwidth of digital compensator is also discussed in this thesis.

### Contents

| Candidate's Declaration                                                                                                                                                                                                                                                                                                        | i                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Certificate                                                                                                                                                                                                                                                                                                                    | ii                                                    |

| Acknowledgement                                                                                                                                                                                                                                                                                                                | iv                                                    |

| Abstract                                                                                                                                                                                                                                                                                                                       | iv                                                    |

| Content                                                                                                                                                                                                                                                                                                                        | vi                                                    |

| List of Tables                                                                                                                                                                                                                                                                                                                 | vii                                                   |

| List of Figures                                                                                                                                                                                                                                                                                                                | х                                                     |

| 1       INTRODUCTION         1.1       Motivation         1.2       Literature review         1.3       Composition of the dissertation                                                                                                                                                                                        | 2                                                     |

| 2       NON-ISOLATED DC-DC CONVERTER TOPOLOG         2.1       Overview         2.2       Analysis of the Multiport Boost Converter         2.3       Single Input Single Output (SISO)         2.4       Single Input Multiple Output (SIMO)         2.4.1       Operating Modes         2.4.2       Buck converter Modelling | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| <ul> <li>3 DYNAMIC MODELLING OF NON-ISOLATED DC-I</li> <li>3.1 Dynamic Modelling and Analysis of SIMO converter</li></ul>                                                                                                                                                                                                      |                                                       |

| 4       VOLTAGE-MODE CONTROL OF SIMO BOOST DC-         4.1       Digital Controller Design and Simulation         4.1.1       Indirect design by Emulation         4.1.2       Direct Digital Design         4.1.3       Fuzzy Sugeno controller design                                                                        |                                                       |

| <b>5</b>     | $\mathbf{DS}$ | P IMPLEMENTATION FOR DIGITAL CONTROLLERS                                                   | <b>24</b> |

|--------------|---------------|--------------------------------------------------------------------------------------------|-----------|

|              | 5.1           | Introduction to Digital Signal Processor                                                   | 24        |

|              | 5.2           | Digital versus Analog Implementation                                                       | 24        |

|              | 5.3           | The TMS320F2812 DSP                                                                        | 25        |

|              |               | 5.3.1 Architecture of F2812 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 25        |

|              |               | 5.3.2 Peripherals of a DSP                                                                 | 28        |

|              |               | 5.3.3 PWM Generators and ADC of TMS320F2812                                                | 28        |

|              |               | 5.3.4 Practical Aspects of Digital Control- Choosing Sampling rate                         | 33        |

|              |               | 5.3.5 Filtering -anti aliasing Filter                                                      | 33        |

| 6            | SYS           | STEM HARDWARE DEVELOPMENT                                                                  | 37        |

|              | 6.1           | Power circuit Development                                                                  | 37        |

|              | 6.2           | Driver Circuit                                                                             | 38        |

|              | 6.3           | Voltage Sensor                                                                             | 39        |

|              |               | 6.3.1 Hardware Set-Up                                                                      | 39        |

|              | 6.4           | Design issues in Digital control                                                           | 40        |

|              |               | 6.4.1 Effect of Sampling frequency                                                         | 40        |

|              |               | 6.4.2 Limit cycles                                                                         | 42        |

| 7            | RES           | SULTS AND DISCUSSIONS                                                                      | 48        |

| •            |               | 7.0.1 Simulation results of SIMO Boost with PI and Fuzzy controller                        | 49        |

| 8            | COI           | NCLUSION AND FUTURE SCOPE                                                                  | 62        |

| 9            | PUI           | BLICATIONS                                                                                 | 63        |

| $\mathbf{A}$ | API           | PENDIX A                                                                                   | 64        |

| в            | API           | PENDIX B                                                                                   | 68        |

|              | B.1           | Code of control of SIMO boost converter                                                    | 68        |

## List of Tables

| 2.1 | Parameters of SIMO converter                                       | 7  |

|-----|--------------------------------------------------------------------|----|

| 7.1 | Closed loop results for synchronous Buck converter                 | 48 |

| 7.2 | Reading of Closed loop control of converter using PI controller    | 48 |

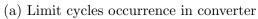

| 7.3 | Readings of converter with respect to Duty cycle variation         | 49 |

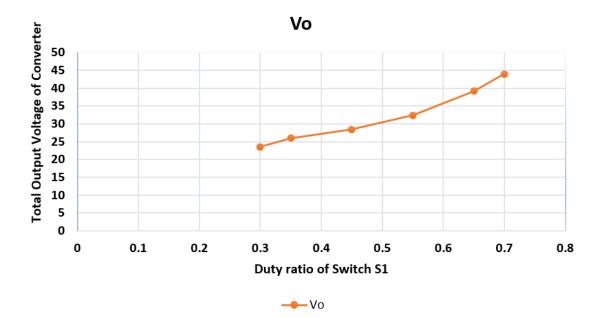

| 7.4 | Readings of converter with respect to Input voltage variation      | 50 |

| 7.5 | Reading of Closed loop control of converter using Fuzzy controller | 51 |

|     | BUCK CONVERTER DESIGN PARAMETERS                                   |    |

# List of Figures

| 2.1        | SISO Boost converter                                                                                                                                              | 6               |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

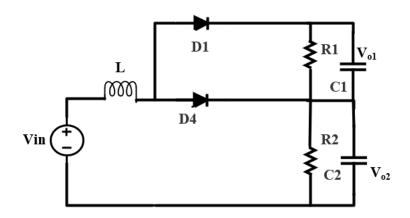

| 2.2        | SIMO Boost converter                                                                                                                                              | 7               |

| 2.3        | Gate pulses timing diagram                                                                                                                                        | 7               |

| 2.4        | switching state 1                                                                                                                                                 | 8               |

| 2.5        | switching state 2                                                                                                                                                 | 8               |

| 2.6        | switching state 3                                                                                                                                                 | 9               |

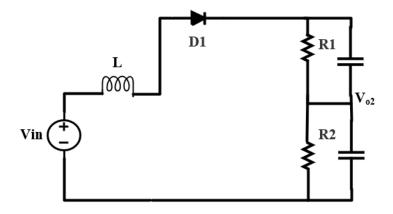

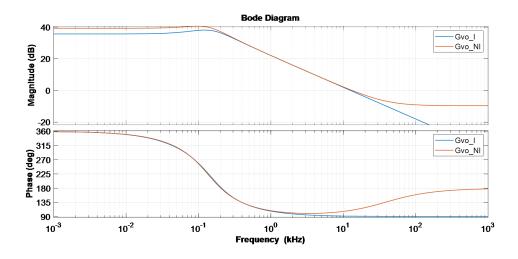

| 2.7        | Circuit diagram of a non-ideal Buck converter                                                                                                                     | 9               |

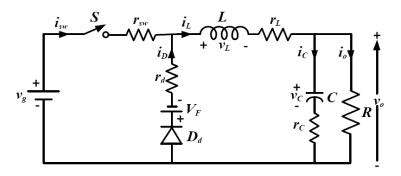

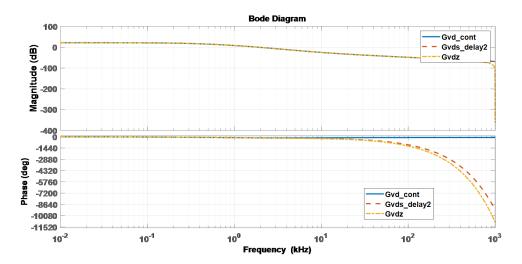

| 4.1        | Bode plot of an uncompensated loop gain for ideal and non ideal SIMO converter                                                                                    | 17              |

| 4.2        | Bode plot of PID compensator for SIMO converter                                                                                                                   | $17 \\ 17$      |

| 4.2<br>4.3 | Controller discretization using various methods                                                                                                                   | 19              |

| 4.3<br>4.4 | Bode plot of continuous transfer function with $20\mu$ sec and without delay,                                                                                     | 19              |

| 4.4        | discrete transfer function $\ldots \ldots \ldots$ | 20              |

| 4.5        | Bode plot of continuous transfer function with $30\mu$ sec and without delay,                                                                                     | 20              |

| 4.0        | discrete transfer function $\ldots \ldots \ldots$ | 20              |

| 4.6        | Transfer function of simo boost converter with time delay consideration                                                                                           | 20<br>21        |

| 4.0<br>4.7 | Synchronous buck converter comparsion between discrete-time model Gvdz                                                                                            | 21              |

| 4.1        | and the effective s domain model with delay into consideration $Gvds_{delay2}$                                                                                    |                 |

|            | and the enective's domain model with delay into consideration $Gva_{delay2}$<br>and $Gvd_{cont}$ (without delay)                                                  | 21              |

| 4.8        | Bode plot of PI controller for uncompensated, open loop gain and compen-                                                                                          | 21              |

| 4.0        | sated buck converter                                                                                                                                              | 22              |

| 4.9        | Block-diagram-of-fuzzy-logic-control-methodology                                                                                                                  | $\frac{22}{22}$ |

| 4.10       | Fuzzy rules table                                                                                                                                                 | $\frac{22}{23}$ |

| 4.10       | Output membership function                                                                                                                                        | $\frac{23}{23}$ |

| 4.11       |                                                                                                                                                                   | 20              |

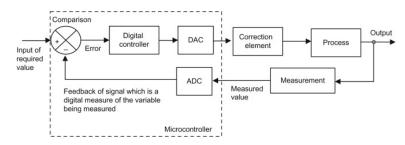

| 5.1        | DSP based Digital Control System Diagram                                                                                                                          | 24              |

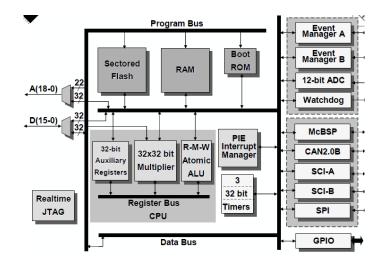

| 5.2        | C281x Block Diagram                                                                                                                                               | 25              |

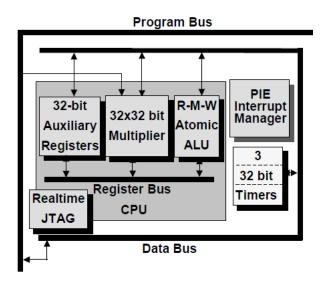

| 5.3        | C28x CPU                                                                                                                                                          | 26              |

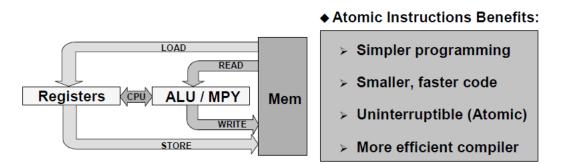

| 5.4        | Atomic Arithmetic Logic Unit                                                                                                                                      | 26              |

| 5.5        | TMS320F2812 Memory Map                                                                                                                                            | 27              |

| 5.6        | GPIO Pin Assignment                                                                                                                                               |                 |

| 5.7        | Event Manager block diagram                                                                                                                                       | 29              |

| 5.8        | General purpose Timer Block diagram                                                                                                                               | 30              |

| 5.9        | Generated Outputs and interrupts                                                                                                                                  | 30              |

| 5.10       | Dead-Band Functionality in EVA                                                                                                                                    | 30              |

| 5.11       | Deadband in PWM waves                                                                                                                                             | 31              |

| 5.12       | Asymmetric PWM waveform                                                                                                                                           | 31              |

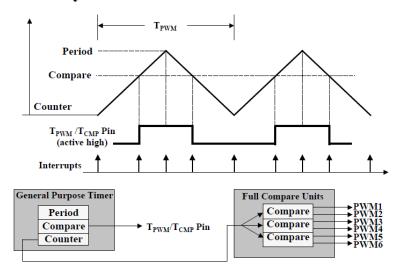

|            | Symmetric PWM Waveform                                                                                                                                            | 32              |

|            | Člock                                                                                                                                                             | 32              |

| 5.15       | GPIO Pin assignment                                                                                                                                               | 32              |

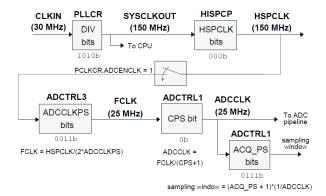

|      | Clock frequency Setting                                                    | 33 |

|------|----------------------------------------------------------------------------|----|

|      | PCLKCR Register                                                            | 34 |

|      | ADC block Diagram                                                          | 34 |

|      | ADC Clock Setting                                                          | 34 |

|      | Digital control loop sampling                                              | 35 |

|      | Nyquist Sampling theoram                                                   | 35 |

|      | Function of ideal LPF                                                      | 35 |

| 5.23 | Choice of Sampling Frequency                                               | 36 |

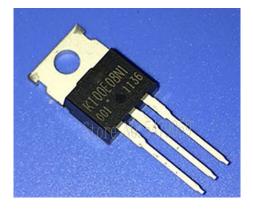

| 6.1  | MOSFET-TK100E10N1                                                          | 37 |

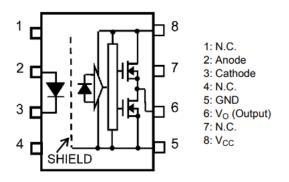

| 6.2  | TLP350H optocoupler internal circuit                                       | 38 |

| 6.3  | TLP350H optocoupler                                                        | 38 |

| 6.4  | Voltage Sensor                                                             | 39 |

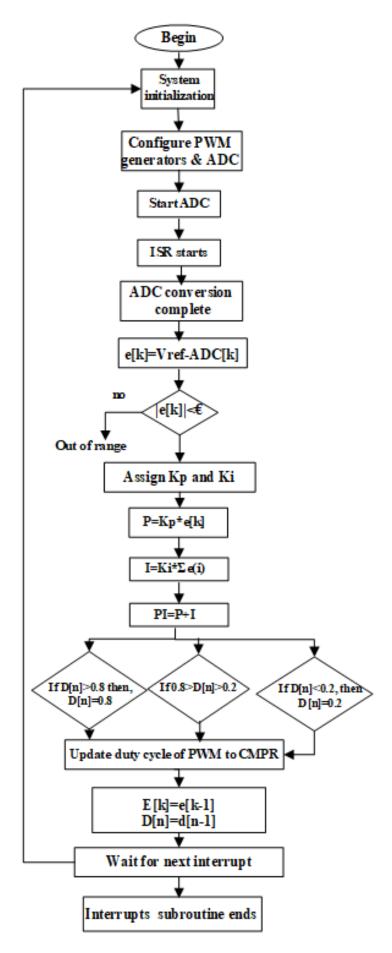

| 6.5  | Flowchart of implementation of Digital control                             | 41 |

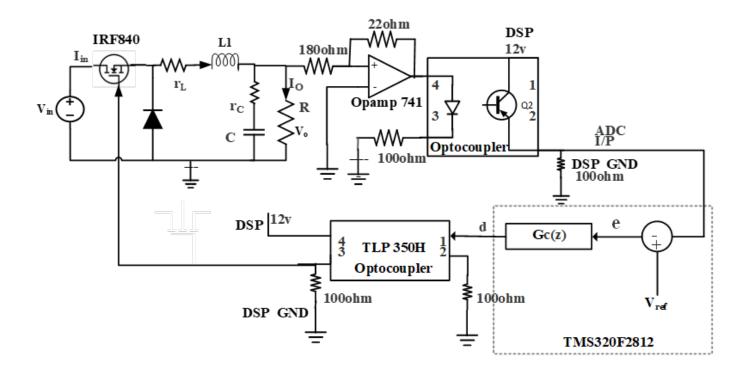

| 6.6  | Buck complete control circuit block diagram                                | 42 |

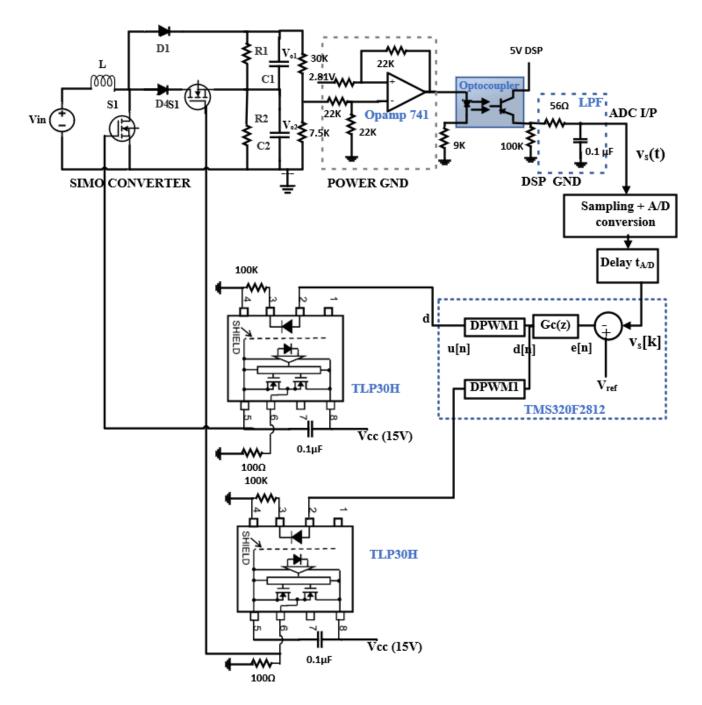

| 6.7  | SIMO boost complete control circuit block diagram                          | 43 |

| 6.8  | SIMO boost complete control circuit hardware setup                         | 44 |

| 6.9  | DSP TMS320F2812                                                            | 44 |

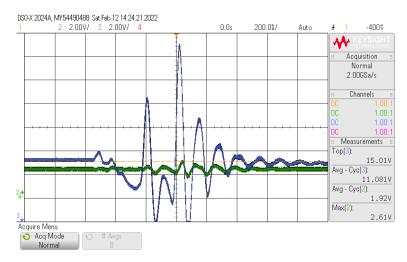

| 6.10 | Effect of change in Sampling frequency                                     | 45 |

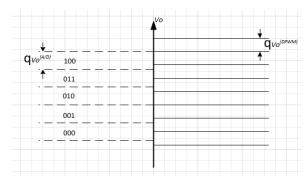

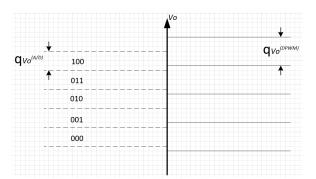

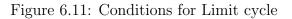

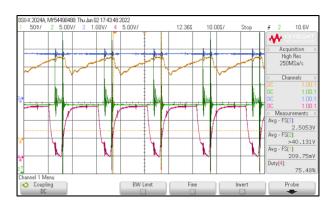

|      | Conditions for Limit cycle                                                 | 46 |

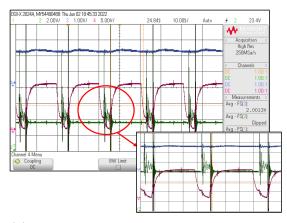

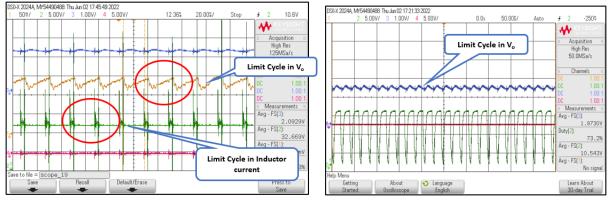

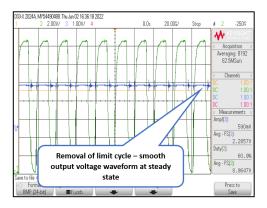

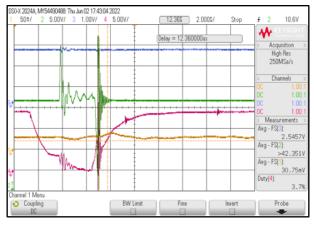

| 6.12 | Limit cycle in converter                                                   | 46 |

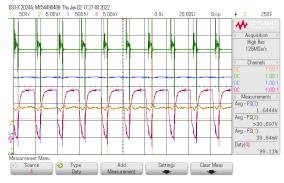

| 6.13 | No-limit cycles occurrence in converter                                    | 47 |

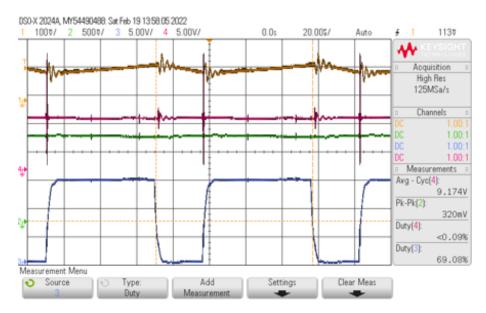

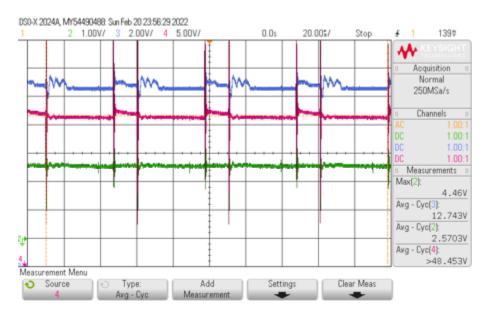

| 7.1  | Output Voltage with duty cycle variation                                   | 50 |

| 7.2  | Output voltage variation w.r.t Input voltage variation                     | 51 |

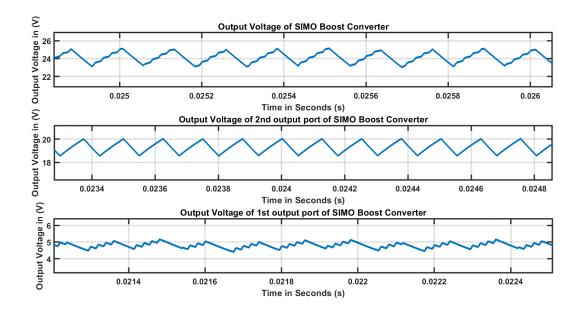

| 7.3  | Total output voltage, $V_{o1}$ and inductor current at 50 kHz              | 51 |

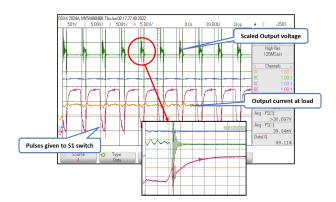

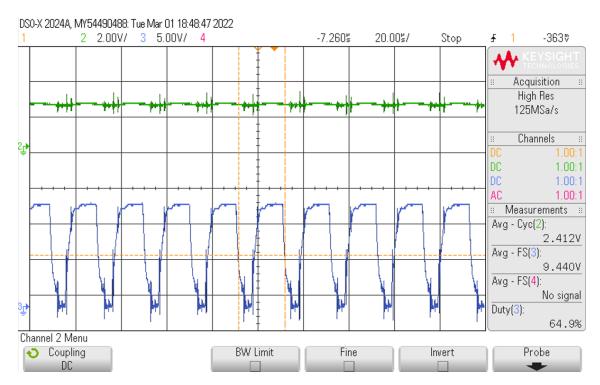

| 7.4  | Output current, both output voltages of converter and pulses given to S1.  | 52 |

| 7.5  | Total output, voltage sensor output and ADC sensed voltage (LPF output)    | 52 |

| 7.6  | Total Voltage output of a converter and scaled Output voltage              | 53 |

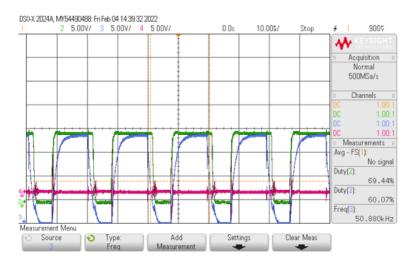

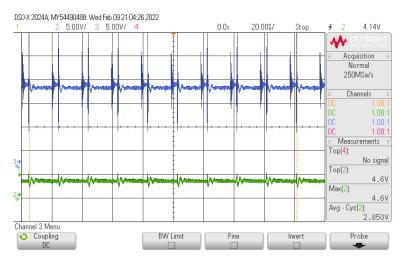

| 7.7  | PWM pulse at DSP output, PWM pulse at Optocoupler output (includes         |    |

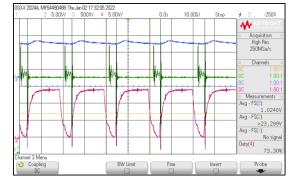

|      | delay at high frequency) at 50 kHz                                         | 53 |

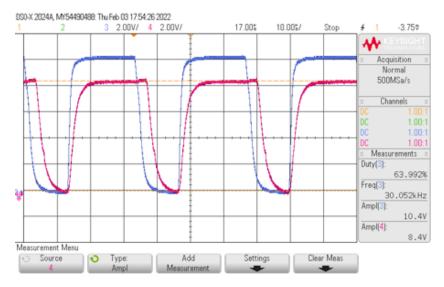

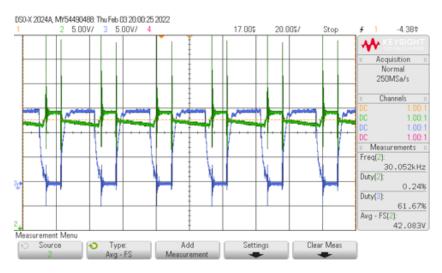

| 7.8  | PWM Pulse of S1 and S4 at 30 kHz                                           | 53 |

| 7.9  | Output voltage at 30kHz frequency                                          | 54 |

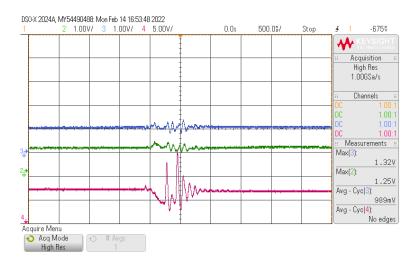

| 7.10 | Removal of Ripples and noise using LPF                                     | 54 |

| 7.11 | Total voltage output of converter and LPF output                           | 54 |

| 7.12 | Scaled output using sensor circuit                                         | 55 |

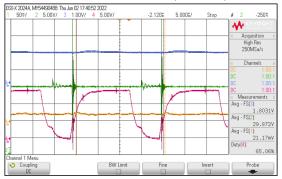

|      | Output Voltage (Scaled) of Converter and Pulses given by controller in     |    |

|      | Closed loop control (V ref as 2V) for SIMO Boost converter                 | 55 |

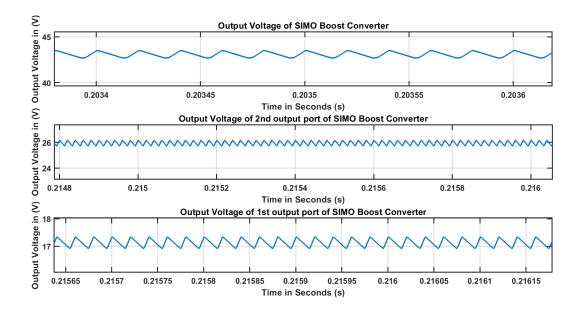

| 7.14 | Output voltage (total), and output voltage at both the output ports for PI |    |

|      | control for SIMO Boost converter                                           | 56 |

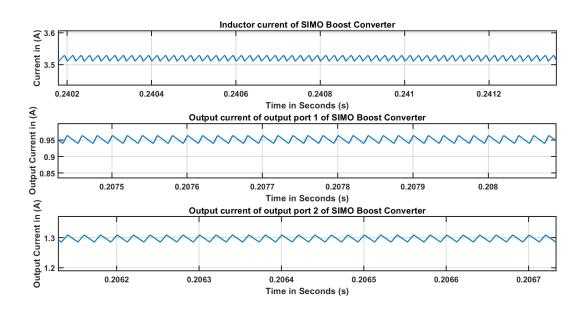

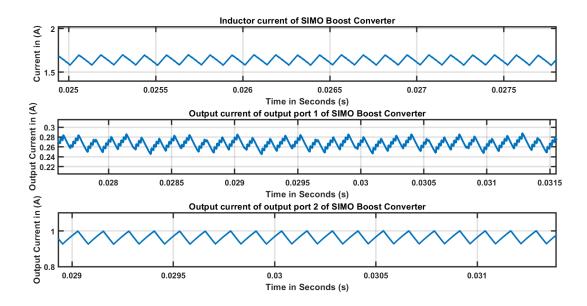

| 7.15 | Inductor current, Output current for both the output ports for PI control  |    |

|      | for SIMO Boost converter                                                   | 56 |

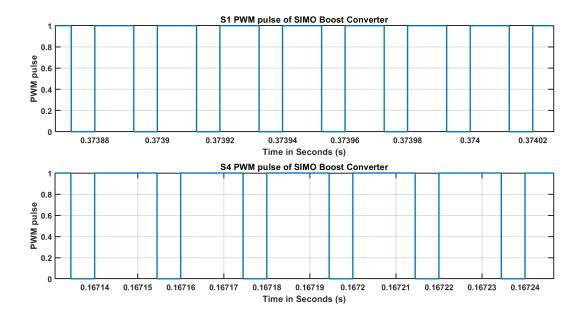

| 7.16 | Pulses for both the switches S1 and S4 for PI control for SIMO Boost       |    |

|      | converter                                                                  | 57 |

| 7.17 | Total output voltage, Output voltages for both the output ports with fuzzy |    |

|      | control for SIMO Boost converter                                           | 57 |

| 7.18 | Inductor current, Output current for both the output ports with fuzzy      |    |

|      | control for SIMO Boost converter                                           | 58 |

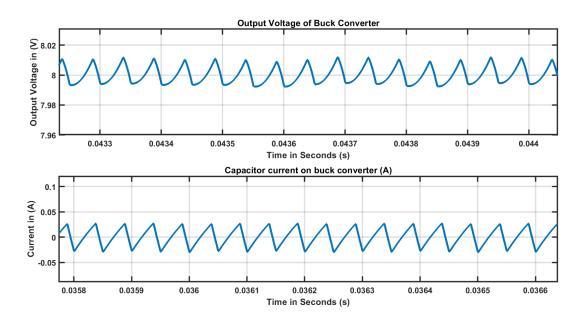

| 7.19 | Output voltage and Capacitor current in Buck converter with PI control .   | 58 |

|      |                                                                            |    |

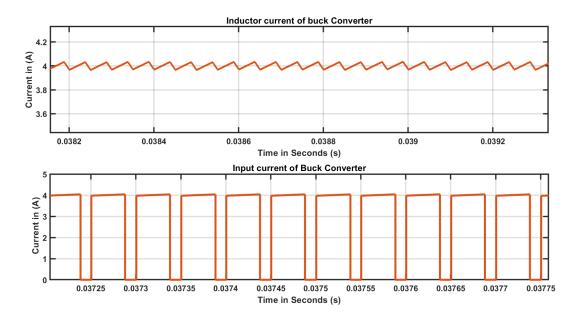

| 7.20                     | Inductor current and Input current of buck converter with PI control                                             | 59                   |

|--------------------------|------------------------------------------------------------------------------------------------------------------|----------------------|

| 7.21                     | Closed loop control using output voltage reference as 1.9V                                                       | 59                   |

| 7.22                     | Closed loop control using output voltage reference as 1.8V                                                       | 59                   |

| 7.23                     | Closed loop control using output voltage reference as 1.5V                                                       | 60                   |

| 7.24                     | Closed loop control of SIMO boost using Fuzzy controller with Vref as 2 V $$                                     | 60                   |

| 7.25                     | Closed loop control of SIMO boost using Fuzzy controller with Vref as 1.8 V                                      | 60                   |

| 7.26                     | Closed loop control of SIMO boost using Fuzzy controller with Vref as 2.5 V                                      | 61                   |

|                          |                                                                                                                  |                      |

|                          |                                                                                                                  |                      |

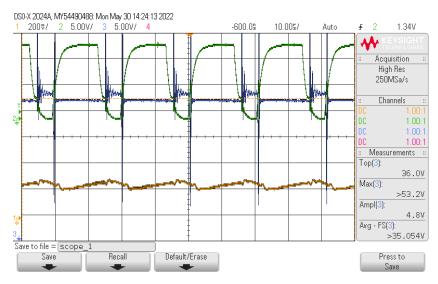

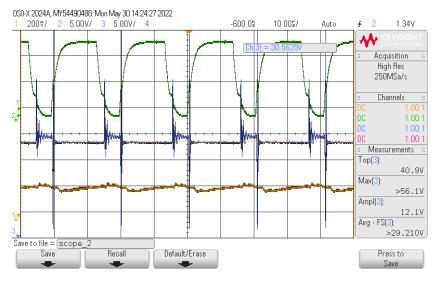

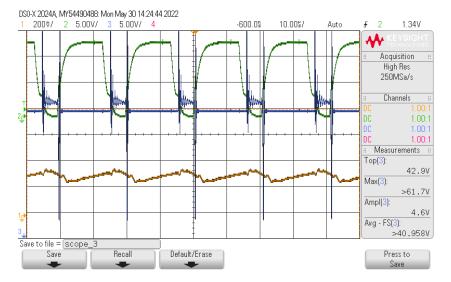

| A.1                      | Rating of MOSFET TK100E10N1                                                                                      | 65                   |

|                          | Rating of MOSFET TK100E10N1                                                                                      |                      |

| A.2                      |                                                                                                                  | 66                   |

| A.2<br>A.3               | Electrical Characteristics of MOSFET-TK100E10N1                                                                  | 66<br>66             |

| A.2<br>A.3<br>A.4        | Electrical Characteristics of MOSFET-TK100E10N1                                                                  | 66<br>66<br>66       |

| A.2<br>A.3<br>A.4<br>A.5 | Electrical Characteristics of MOSFET-TK100E10N1Source drain ratings of MOSFETAbsolute maximum ratings of TLP350H | 66<br>66<br>66<br>67 |

### Chapter 1

### INTRODUCTION

Switched mode DC DC converters converts DC input voltage to regulated DC output voltage efficiently. SMPS As Compared to linear power supplies provide more efficiency and power density. Energy storage elements called as capacitor and inductors are generally used for energy transfer and work as a low pass filter (LPF). Also, It is been observed that the buck converter and boost converter are the most fundamental topologies. Previously, the control methods used for DC-DC converters has been analog control techniques. However due to recent advances in technology, digital signal processors are preferred as they are relatively more immune to environmental changes such as temperature and aging components. More advanced algorithms can be implemented on a DSP as high sampling rate because of its special architecture and high performance. Priorly in power electronics systems, output voltage regulation has been achieved using analog control. Analog signals of the output voltage or output current are controlled by the analog transfer function using OPAMP with compensation network. Through this the output signal is controlled and regulation is obtained.

The analog-opamp compensation network regulates the duty ratio with respect to switching frequency used for driving the power switching devices. analog control system possess real time operation and provides control over very high bandwidth. It carries infinite voltage resolution theoretically. However, Analog control restricts for hardware expansion and design changes and advanced control techniques are used to improve performance required more analog components[1]. Analog integrated circuits are the traditional pillers for controllers for SMPS. Whereas digital controllers are used in majority of applications ranging from high voltage and high switching frequency. The ease in generating number of control signals with less complexities forces us to use micro-controllers and digital signal processors. Commonly, Boost converters are used to 'increase' the input voltage to higher level. It carries an unique ability to transfer the energy stored by inductor to capacitor and inturn to load. During the first switching cycle , energy is transferred to inductor and and when the switch is opened the energy stored in inductor is being transferred to load via capacitor. It finds application to portable electronic devices, fuel cell and battery power systems.[2]

The digital control loop is designed and implemented using direct and indirect approaches using various discrete conversion methods. The validity of the non-isolated DC-DC SIMO Boost converters and their performances are verified by simulation and experimental results for closed loop operation under variation in load. PI and PID control algorithms are implemented using Digital Signal Processors and MATLAB/Simulink platform has been utilized for simulation purpose.

One of the major drawbacks of the Digital control is Limited bandwidth caused by time delay in ADC conversion, PWM generation, Quantization and computational time delays. Straight forward predictive schemes are used to compensate the delay and hence increasing control loop bandwidth[3].

### 1.1 Motivation

In Power Electronics , Digital Signal Processing is an important research area which resolves the concerns related to design and algorithms. DSPs are commonly used in different control applications because of low cost and good performance characteristics. These are prominently used in audio signal, sensing circuits for voltage , current and position, signal processing etc. Better resolution, control with inherent sampling, ease to implement sophisticated control algorithms, less effect of environment changes are the few advantages of digital control.

Therefore, Digital control loop design is the focus of this thesis. Single Input Multiple Output boost converter is being modelled, designed and controlled in this thesis.

### **1.2** Literature review

The applications for power electronics are entering into consumer electronics such as , switched mode power supplies, battery storage systems, electric drives and machines, charging infrastructures , electric vehicle, power factor correction etc. As digital control is gaining importance , many semiconductor companies such as Texas Instruments, Analog Devices and Motorola have launched high computational processors for control applications.

The Digital Signal Processor are a very high speed processor , prominently used to handle Power Electronics and Systems applications such as PWM generation of analog signals and quadrature encoder circuit for speed and position estimation[4]. To produces a constant voltage output aligned with the requirements of load, a converter is required. Single input single output boost converter can provide us high dc voltage but with more losses in inductor, capacitor and main switch or diode. With this efficiency of the converter gets degraded and EMI problem come into play. This thesis presents Single input multi output unidirectional boost converters for two controlled output applications. This circuit also propose component count reduction and the main advantages of the SIMO converter is to get two regulated voltage output with low cost and lesser power losses along switching devices[5].

This thesis proposes suitable topology for power converters, model of converter, analysis of the three switching states , control strategies and digital control loop design. The circuit simulation and hardware with linear and non-linear controllers are presented in this thesis. The major applications of DC-DC converters are in battery charging and discharging , battery energy storage systems and power factor correction, renewable energy systems etc. DC-DC converter provides the uninterrupted power transfer to other devices using appropriate switching techniques. Due to advancement in power devices and converters, efficiency, high voltage operation and high switching frequency devices. This results for the need of GaN ans SiC based devices with lesser switching and conduction losses[6].

Also, Cross voltage regulation is oftenly seen in multi output converters which makes the analysis and design more complex. The Analysis, design, modelling and implementation of closed loop Digital controlles for SIMO Boost converters using TMS320F2812 DSP controller is performed. Control Techniques such as PI, PD and PID and Nonlinear- Fuzzy control are being discussed and implemented in this thesis using TI C2000 series DSP for SIMO boost converters[7]. Digital Control is a multi-disciplinary research which has its applications to Digital signal processing, speech analysis, audio processing and control of power converters, motor drives etc. Digital control Loop can be designed using tuning approaches, root locus method and bode plot methods using suitable gain, crossover frequency and phase margin. Digital control uses computer systems and microprocessors for processing analog signals. Digital control uses discrete-time models for processing and uses indirect control and direct control techniques for designing discrete controllers.

In the indirect design approach, analog controllers are initially designed using small signal models and then converted to digital controller using discretization methods such as Tustin, Backward Euler, Forward Euler etc. Tustin seems to have better discretization then other methods. Vallittu and Suntio have studied the constraints and advantages of digital control in power circuits[8]. The analysis of Boost converters starts with small signal modelling , averaging and perturbations, linearization of the converter's average inductor and voltage equations. Linear controllers can be designed using various methods using frequency responses and step response in time domain. The output voltage to duty ratio transfer function is obtained for ideal and non- ideal converter parameters. Digital controller can also be designed using direct method. In this method, the transfer function of converter is converted to discrete using Matlab.

The inclusion of non-idealities in boost converter results into right half plane Zero. This right half plane zero results a gain of 20dB/decade and a phase delay of 90°. Due to this Boost converter is termed as non-minimum phase function and it is difficult to control them relatively as compared to minimum phase function such as Buck converter. Due to addition of right half plane Zero, systems unstability increases and noise, disturbances enters the system. Therefore, Linear controllers are designed for operating point and controlling of Voltage is achieved[9].

However, it is difficult to control Non- minimum phase function such as Boost converter, non-linear controller are used and implemented using digital controllers. Artificial intelligence and Optimization Techniques are majorly used for controlling any parameter. One of them is Fuzzy which is a nonlinear controller and can adapt to time varying operating points. Viswanathan and Srinivasan have researched on fuzzy controller and its performances. It is been observed that fuzzy controller improves the performance in terms of overshoot and rise time of output voltage.With appropriate scaling , design and analysis fuzzy controllers are implemented for SIMO converter and closed loop control is validated. Limit cycles are generated due to the quantization and are difficult to predict. All the digital controllers are implemented on TMS320F2812 DSP using various peripherals such as EVM and ADC.

### **1.3** Composition of the dissertation

The dissertation is organized in five parts. The first part consists of Chapter 1, which gives an outline about the literature review on the developments related to single input multi-output DC-DC converters. The motivation, aim and objectives for pursuing the research has been described here.

The second part of this dissertation, comprising of Chapter 2 and Chapter 3, outlining the topology, analysis and dynamic modelling of the converters. Chapter 2 presents an overview of DC-DC converters followed by analysis of different topologies of multiport converters. Chapter 3 gives a detailed mathematical modelling and dynamic state space analysis of SIMO converter. Small signal modelling technique is used to form a dynamic model of SIMO converter.

In Chapter 4, digital controllers (PID and fuzzy) are designed for DC-DC SIMO Boost converters using linear and non linear control methods. The controllers are designed using Frequency response techniques via bode plots. The transformation of analog controller to digital controller using descretization methods are discussed and implemented using and implementation of digital controllers are also discussed in Chapter 5.

In Chapter 6 of this dissertation, the experimental hardware circuitry and in chapter 5, DSP controller from Texas Instruments is described in detail. Converter design specifications are also introduced here. Control strategies used to generate gate pulses are hereby discussed and structure of microcontroller used to generate those control signals are hereby presented.

Laboratory results for the buck and the boost converters are presented and compared in Chapter 7. In Chapter 8, the research is summarized with conclusions, observations and suggestions for future work are made.

### Chapter 2

### NON-ISOLATED DC-DC CONVERTER TOPOLOGY

This chapter introduces various DC-DC converter topologies based on buck, boost and Single output converter. The converter structure, operating principle and different modes of operation are presented and analyzed in detail.

### 2.1 Overview

Switched mode DC-DC converters is used for stepping up and stepping down the voltage from the input supply to its load output. It is classified in switched-mode power supply (SMPS) consisting of atleast two semiconductor devices (a transistor and a diode) and atleast one energy storing element i.e. either a capacitor or an inductor or may be a combination of both. Voltage ripples can be reduced by using capacitor filter at both input and output[10].

Basic working of boost converter relies on the principle of storing of energy in inductor from the supply side (dc or rectified ac) and then transferring it to the capacitor (or load itself). Therefore, output voltage steps up, resulting it to be greater than the input supply voltage. The basic circuit topology can be enhanced to give other variants of the boost converter. Here we are discussing non-isolated DC-DC converters which can be classified into two parts:

i. Single Input Single Output (SISO) ii. Single Input Multiple Output (SIMO)

Detailed analysis of these DC-DC converters will be done later in this chapter.

In single input single output (SISO) mode supply is from one input and here resistive load is taken as single output. This is a conventional form of DC-DC boost converter. Power transfer takes place between input supply (here a charged battery) and output load (resistive type) [2].

In single input multiple output (SIMO) mode single charged battery act as input supply and two or more resistive loads as output. This is a non-isolated SIMO converter topology and here power transfer occurs between one input supply and two resistive loads.

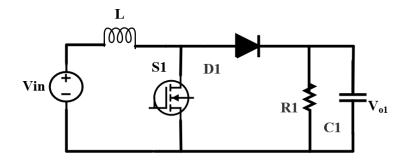

Figure 2.1: SISO Boost converter

### 2.2 Analysis of the Multiport Boost Converter

In a boost converter topology, conventional boost converters are merged for providing new topologies to get multiport converter. If we consider hybridizing alternate energy sources to be used as input sources for the converter which includes FC and ESS (here battery) then usage of each source accordingly can result in development of different topologies. Here we discuss detailed structure of each topology (i.e. conventional and proposed), its operating modes and useful mathematical equations. Classification of DC-DC Boost topology for non-isolated structure is as follows:

i. Single Input Single output Boost Converter (SISO)ii. Single Input Multiple Output Boost converter (SIMO)

### 2.3 Single Input Single Output (SISO)

Single input single output converter topology is the conventional converter topology. The converter structure is shown in Fig. 2.1. It considers just one input supply and one resistive load at the output. In this structure inductor stores energy in one cycle from the input supply and in the next cycle it delivers the energy stored to the loads at the output. The cycle period is decided by the duty of the switch used in the converter.

### 2.4 Single Input Multiple Output (SIMO)

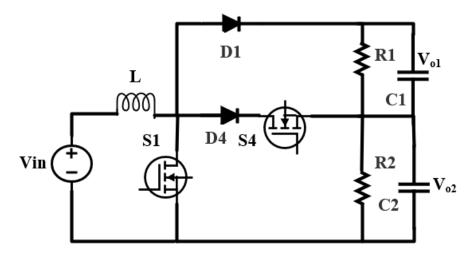

The multiport converter topology discussed above in Fig. 2.2 can be converted into SIMO converter structure. Considering just one input supply and two resistive loads as outputs we can simulate the structure of SIMO DC-DC converter.

In the fig.2.2, the SIMO converter has one-input two-output structure. In this figure,  $R_1$  and  $R_2$  are model equivalent resistances to denote either HEV system components or a multilevel inverter. Different types of multilevel inverters can be used in connection to this converter. HEVs have various DC-DC loads such as lightning or music system which can directly be feed from the converter output. But HEVs are difficult to operate with just one input supply as discussed earlier.

Figure 2.2: SIMO Boost converter

| Parameters                               | Values               |

|------------------------------------------|----------------------|

| Input voltage, Vin                       | 15V                  |

| Load resistances, $R_1, R_2$             | $18\Omega, 25\Omega$ |

| Output voltage                           | 45V                  |

| Inductance, $L/r_L$                      | $6mH/0.18\Omega$     |

| Capacitance, C1, $C2/r_C$                | $30/0.3\Omega$       |

| Frequency, f                             | 50kHz                |

| Switch- on resistance, $\mathbf{r}_{sw}$ | $0.044\Omega$        |

| Diode forward resistance, $r_d$          | $0.024\Omega$        |

| Diode forward Voltage drop, $V_d$        | 0.7V                 |

| Table 2.1: Parameters of SIMO converter |  |

|-----------------------------------------|--|

|-----------------------------------------|--|

### 2.4.1 Operating Modes

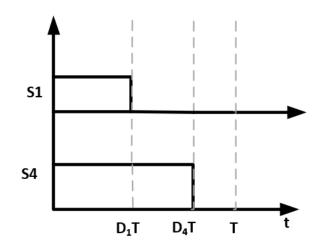

According to switching states of the switches, there are four different operating modes in one switching period as follows in figure 2.3.

Figure 2.3: Gate pulses timing diagram

#### 1) Switching State 1 ( $0 < t < D_1T$ ):

In this state, switches S1 and S4 are made active by giving gate pulses. Since S1 is ON, diodes D1 and D2 are made reverse biased, so switch S4 is turned OFF. Equivalent circuit of the proposed converter in this state is shown in Fig. 2.4. In this switching state,  $Vin_2$  charges inductor L, so inductor current increases. Simultaneously, in this state, capacitors C1 and C2 are discharged and deliver their stored energy to load resistances R1 and R2, respectively.

Figure 2.4: switching state 1

#### 2) Switching State 2 ( $D_1T < t < D_4T$ ):

In this switching state, switch S1 is turned OFF active and S4 is turned active. Since S1 is ON, diodes D1 and D2 are made reverse biased, so switch S4 is still inactive. Equivalent circuit diagram of proposed converter in this state is shown in Fig. 2.5. In this state, Vin1 charges inductor L, so inductor current furthermore increases. Simultaneously, capacitors C1 and C2 are discharged and delivers its stored energy to load resistances R1 and R2, respectively.

Figure 2.5: switching state 2

Figure 2.6: switching state 3

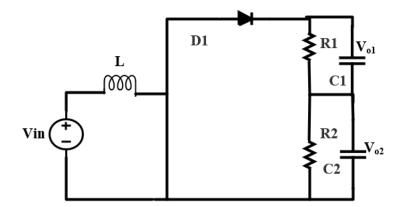

#### 3) Switching State 3 $(D_4T < t < T)$ :

In this state, switch S1 is turned inactive and switch S4 is turned OFF. Also, switch S4 is turned ON. Diode D4 is reversed biased. Equivalent circuit of proposed converter in this state is shown in Fig. 2.6. In this state, discharging on inductor L occurs and power is delivered to C1 and R1, so inductor current decreases. In this state, C1 is charged and C2 is discharged and delivers its stored energy to load resistance R2.

### 2.4.2 Buck converter Modelling

Based on the above procedure, mathematical modelling of buck converter can be done using state space averaging. The circuit diagram with non-idealities are shown in below figure 2.7.

Figure 2.7: Circuit diagram of a non-ideal Buck converter

$$\frac{\tilde{v}_o(s)}{d(s)} = C_c (sI - A)^{-1} B_d$$

(2.1)

$$\frac{\tilde{v}_{out}(s)}{d(s)} = \frac{V_{in}}{LCs^2 + s\left[\frac{L}{R} + r_LC\right] + \left[1 + \frac{r_L}{R}\right]}$$

(2.2)

$$\frac{\frac{v_o(s)}{d(s)}}{\frac{R(V_g + V_F - (r_{sw} - r_d)I_L}{LC(R + r_C)}(r_c C s + 1))}{s^2 + \left(\frac{1}{L}\left(r_x + r_L + \frac{r_c R}{R + r_C}\right) + \frac{1}{C}\left(\frac{R}{R + r_c}\right)\right)s + \left[\frac{r_L + r_x + R}{LC(R + r_c)}\right]}$$

(2.3)

The dynamic model for switched-on and off stage is obtained and averaged over switching cycle as per state space averaging technique. In the average model, small perturbations in the variables are introduced and then the model is linearized.

### Chapter 3

### DYNAMIC MODELLING OF NON-ISOLATED DC-DC CONVERTER

The objective of the control is to maintain tight regulation of output voltage in presence of input voltage or load current variations. Average small-signal modelling is based on averaging the converter's behaviour over switch on and off periods. The purpose of smallsignal modelling is to convert time varying nature of the converter into time invariant system model.

In this chapter, small signal modelling is discussed and the parameters of the converter circuit are introduced. For designing the best optimal controller, small signal modelling plays a vital role.[11]

### 3.1 Dynamic Modelling and Analysis of SIMO converter

#### 3.1.1 The Basic AC Modelling Approach

**Mode I**  $(0 < t < D_1T)$

The key steps in small signal ac model of PWM converter are being derived in this section, these include:

(1) Development of equations relating the low frequency averages of the inductor and capacitor.

- (2) Perturbation and linearization of the averaged equations

- (3) Construction of ac equivalent model

The analysis begins by determining the voltage and current waveforms of the inductor and capacitor. When the switch is in position 1, the inductor voltage and capacitor current are:

$$L\frac{di_{L}(t)}{dt} = V_{in} - (r_{L} + r_{sw})i_{L}$$

(3.1)

$$C_1 \frac{dv_{c1}(t)}{dt} = -\frac{V_{c1}}{(R_1 + r_{c1})} - \frac{I_{o1}R_1}{R_1 + r_{c1}}$$

(3.2)

$$C_2 \frac{dv_{c2}(t)}{dt} = -\frac{V_{c2}}{(R_2 + r_{c2})} - \frac{I_{o2}R_2}{R_2 + r_{c2}}$$

(3.3)

Mode II  $(D_1T < t < D_4T)$

$$L\frac{di_L(t)}{dt} = V_{in} - (r_L + r_{sw})i_L - V_d - i_{c2}r_{c2} - V_{c2}$$

(3.4)

$$C_1 \frac{dv_{c1}(t)}{dt} = -\frac{V_{c1}}{(R_1 + rc1)} - \frac{I_{o1}R_1}{R_1 + rc_1}$$

(3.5)

$$C_2 \frac{dv_{c2}(t)}{dt} = \frac{i_L R_L}{R_L + r_{c2}} - \frac{V_{c2}}{(R_2 + r_{c2})} - \frac{I_{o2} R_2}{R_2 + r_{c2}}$$

(3.6)

Mode III  $(D_4T < t < 1)$

$$L\frac{di_L(t)}{dt} = V_{in} - r_L i_L - V_d - i_{c1}r_{c1} - V_{c1} - i_{c2}r_2 - V_{c2}$$

(3.7)

$$C_1 \frac{dv_{c1}(t)}{dt} = \frac{i_L R_1}{R_1 + r_{c1}} - \frac{V_{c1}}{(R_1 + r_{c1})} - \frac{I_{o1} R_1}{R_1 + r_{c1}}$$

(3.8)

$$C_2 \frac{dv_{c2}(t)}{dt} = \frac{i_L R_2}{R_2 + r_{c2}} - \frac{V_{c2}}{(R_2 + r_{c2})} - \frac{I_{o2} R_2}{R_2 + r_{c2}}$$

(3.9)

#### 3.1.2 Averaging the Inductor and Capacitor waveforms

Averaging performs a low pass function to remove the switching ripple and harmonics. Then, applying small ripple approximation to the quantities having small ripple and are non pulsating like in inductor current and in capacitor voltages.

The equations below describes the low frequency component of the inductor current and capacitor voltage vary with time.

$$\langle v_L(t) \rangle_{T_s} = L \frac{d \langle i_L(t) \rangle_{T_s}}{dt} = V_{in} - (r_L + r_{sw} D_4) i_L - V_d (1 - D1) - i_{c1} r_{c1} (1 - D_4) - i_{c2} r_{c2} (1 - D_1) - V_{c2} (1 - D1) - V_{c1} (1 - D4)$$

$$\langle i_{c_1}(t) \rangle_{T_s} = C_1 \frac{d \langle v_{c_1}(t) \rangle_{T_s}}{dt} = -\frac{V_{c1}}{R_1 + r_{c1}} - I_{o1} \frac{R_1}{R_1 + r_{c1}} + i_L (1 - D4) \frac{R_1}{R_1 + r_{c1}}$$

(3.10)

$$\langle i_{c_2}(t) \rangle_{T_s} = C_2 \frac{d \langle v_{c_2}(t) \rangle_{T_s}}{dt} = -\frac{V_{c_2}}{R_2 + r_{c_2}} - I_{o_2} \frac{R_2}{R_2 + r_{c_2}} + i_L (1 - D1) \frac{R_2}{R_2 + r_{c_2}}$$

(3.11)

(3.12)

### 3.1.3 Perturbation and linearization

Equations above are nonlinear and time varying in nature i.e generated harmonics. Linearizing it by constructing a small signal model.

In small signal modelling method [30], the state variables, duty ratios, and input voltages contain two components, dc values (X, D, V) and perturbations  $(\hat{x}, \hat{d}, \hat{v})$ . So, the following equations for proposed converter are:

$$\langle i_L(t) \rangle_{T_s} = I_L + \hat{i}_L(t) \tag{3.13}$$

- $\langle v_{c1}(t) \rangle_{T_s} = V_{c1} + \hat{v}_{c1}(t) \tag{3.14}$

- $\langle v_{c2}(t) \rangle_{T_s} = V_{c2} + \hat{v}_{c2}(t) \tag{3.15}$

$$\langle i_{o1}(t) \rangle_{T_s} = I_{o1} + \hat{i}_{o1}(t)$$

(3.16)

$$\langle i_{o2}(t) \rangle_{T_s} = I_{o2} + \hat{i}_{o2}(t)$$

(3.17)

$$\langle d_1(t) \rangle = D_1 + \hat{d}_1(t)$$

(3.18)

$$\langle d_4(t) \rangle = D_4 + \hat{d}_4(t) \tag{3.19}$$

It is assumed that the perturbations are quite small and do not vary significantly during one switching period.

#### 3.1.4 Construction of Small-Signal Equivalent Circuit Model

Applying the averaging to four state equations multiplied with corresponding duty cycle value, and subsequently neglecting second-order terms, we find small-signal model equations that are presented as follows:

$$L\frac{d\hat{i}_{L}(t)}{dt} = \hat{i}_{L}(t)(-r_{L} - r_{sw}D_{4}) + (D4 - 1)\hat{v}_{c1}(t) + (D1 - 1)\hat{v}_{c2}(t) + (-r_{sw}I_{L} + i_{c1}r_{c1} - V_{c1})\hat{d}_{4}(t) + (V_{d} + i_{c2}r_{c2} - V_{c2})\hat{d}_{1}(t)$$

(3.20)

$$C_1 \frac{d\hat{v}_{c1}}{dt} = -\hat{v}_{c1}(t) \frac{1}{R_1 + r_{c1}} - \hat{i}_{o1}(t) \frac{R_1}{R_1 + r_{c1}} - \hat{d}_4(t) \frac{I_L R_1}{R_1 + r_{c1}} + \hat{i}_L(t) \frac{(1 - D4)R_1}{R_1 + r_{c1}} \quad (3.21)$$

$$C_2 \frac{d\hat{v}_{c2}}{dt} = -\hat{v}_{c2}(t) \frac{1}{R_2 + r_{c2}} - \hat{i}_{o2}(t) \frac{R_2}{R_2 + r_{c2}} - \hat{d}_1(t) \frac{I_L R_2}{R_2 + r_{c2}} + \hat{i}_L(t) \frac{(1 - D2)R_2}{R_2 + r_{c2}} \quad (3.22)$$

#### 3.1.5 The State Equation of a Network

The state space averaging approach is a canonical form of writing the different equation that describes a system. Thus, the system can be represented in a matrix form using a state-space model such taking  $i_L(t)$ ,  $v_{O1}(t)$ , and  $v_{O2}(t)$  as state variables. The state-space model is as follows [12]:

$$\frac{dX}{dt} = AX + BU \tag{3.23}$$

$$Y = CX + DU \tag{3.24}$$

where X represent state variable matrix, U represent control input matrix having  $d_1(t)$ ,  $d_3(t)$  and  $d_4(t)$ , and Y represents system output matrix having  $v_{O1(t)}$ ,  $v_T(t)$ . Thus, matrices X, Y and U are as follows:

$$X = \begin{bmatrix} \hat{i}_{L}(t) \\ \hat{v}_{o1}(t) \\ \hat{v}_{o2}(t) \end{bmatrix}, Y = \begin{bmatrix} \hat{v}_{o1}(t) \\ \hat{v}_{t}(t) \end{bmatrix}, U = \begin{bmatrix} \hat{d}_{4}(t) \\ \hat{d}_{1}(t) \\ \hat{v}_{in}(t) \\ \hat{i}_{o1}(t) \\ \hat{i}_{o2}(t) \end{bmatrix}$$

(3.25)

Substituting the A, B, C, and D matrices using equations (3.20-3.22) and state equations (3.23-3.24), and following results is obtained:

$$A = \begin{bmatrix} -\frac{(r_L + r_{sw}D_4)}{L} & \frac{D_4 - 1}{L} & \frac{D_1 - 1}{L} \\ \frac{R_1(1 - D_4)}{(R1 + r_{c1})C1} & \frac{-1}{(R1 + r_{c1})C1} & 0 \\ \frac{R_2(1 - D_1)}{(R2 + r_{c2})C2} & 0 & \frac{-1}{(R2 + r_{c2})C2} \end{bmatrix}$$

(3.26)

$$B = \begin{bmatrix} -\frac{V_{c1} + i_{c1}r_{c_1} - I_L r_{sw}}{L} & \frac{i_{c2}r_{c2} + V_d + V_{c_2}}{L} & \frac{1}{L} & 0 & 0\\ \frac{-R_1 I_L}{(R_1 + r_{c_1})C_1} & 0 & 0 & \frac{-R_1}{(R_1 + r_{c_1})C_1} & 0\\ 0 & -\frac{R_2 I_L}{(R_2 + r_{c2})C_2} & 0 & 0 & \frac{-R_2}{(R_2 + r_{c2})C_2} \end{bmatrix}$$

(3.27)

$$C = \begin{bmatrix} -\frac{R_1 r_{c1}(1-D_4)}{R_1 + r_{c1}} & \frac{R_1}{R_1 + r_{c1}} & 0\\ \frac{R_1 r_{c1}(1-D_4)}{(R_1 + r_{c1})C_1} + \frac{R_2 r_{c2}(1-D_1)}{(R_2 + r_{c2})C_2} & \frac{R_1}{R_1 + r_{c1}} & \frac{R_2}{(R_2 + r_{c2})C_2} \end{bmatrix}$$

(3.28)

$$D = \begin{bmatrix} -\frac{R_1 r_{c1} I_L}{R_1 + r_{c1}} & 0 & 0 & 0 & \frac{R_1 r_{c1}}{R_1 + r_{c1}} \\ -\frac{R_1 r_{c1} I_L}{(R_1 + r_{c1})} & -\frac{R_2 r_{c2} I_L}{(R_2 + r_{c2})} & 0 & -\frac{R_1 r_{c1}}{(R_1 + r_{c1})} & -\frac{R_2 r_{c2}}{(R_2 + r_{c2})} \end{bmatrix}$$

(3.29)

So, now the unknown parameters of above mentioned matrices are  $D_1$  and  $D_4$ . The values of duty applied to the switches is obtained by steady-state analysis which is shown in following equation:

$$\begin{bmatrix} -r_{sw}i_L + i_{c_1}r_{c_1} + V_{c_1} & V_d + i_{c_2}r_{c_2} + V_{c_2} \\ -i_L\frac{R_1}{R_1 + r_{c_1}} & 0 \\ 0 & -i_L\frac{R_2}{R_2 + r_{c_2}} \end{bmatrix} \begin{bmatrix} D4\\D1 \end{bmatrix} = \begin{bmatrix} V_{in} - i_Lr_L - V_d - i_{c_1}r_{c_1} \\ (V_{c_1} + I_{o_1} - i_L)\frac{R_1}{R_1 + r_{c_1}} \\ (V_{c_2} + I_{o_2} - i_L)\frac{R_2}{R_2 + r_{c_2}} \end{bmatrix}$$

(3.30)

The transfer function matrix of the converter is mentioned below which is obtained using state space averaging approach.

The small signal control to output transfer function by substituting the parameters as in table 3.1 is defined as :

$$G_{vd}(s) = \frac{v(s)}{d(s)} \tag{3.31}$$

This transfer function is found by setting the  $\hat{v}_g(s)$  variations to zero, and solving for the dependence of  $\hat{v}(s)$  on  $\hat{d}(s)$ .

$$G_{vdideal} = \frac{-78950s^2 - 4.866 \times 10^7 s + 6.831 \times 10^{10}}{s^3 + 2515s^2 + 2.484 \times 10^6 s + 1.128 \times 10^9}$$

(3.32)

$$G_{vdnonideal} = \frac{-0.3286s^3 - 78760s^2 - 3.663 \times 10^7 s + 8.332 \times 10^{10}}{s^3 + 2372s^2 + 2.135 \times 10^6 s + 9.134 \times 10^8}$$

(3.33)

The transfer function of buck converter is given below:

$$G_{vd}(s) = \frac{V_{out(s)}}{d(s)} = \frac{2417s + 1.714 \times 10^8}{s^2 + 9518s + 1.141 \times 10^7}$$

(3.34)

### Chapter 4

### VOLTAGE-MODE CONTROL OF SIMO BOOST DC-DC CONVERTER

The objective of the control loop is to obtain and maintain constant output voltage in spite of variations and disturbances in  $V_g(t)$  and  $i_{load}(t)$ . Therefore, negative feedback is introduced to build a circuit that adjusts the duty cycle to obtain output voltage desired regardless of the disturbances.

Design goals and specifications are considered for compensator design in-order to obtain better transient response and stability. This chapter presents the standard frequencydomain based compensator design to attain adequate stability i.e phase margin and improvement in bandwidth. The small signal model of the system is presented in previous section[13].

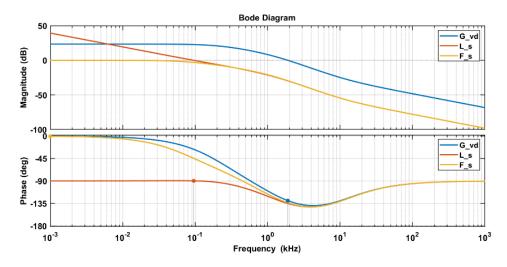

In this chapter, Combined PID compensator, called as lead lag compensator is designed to obtain both wide bandwidth control and zero steady state error. The crossover frequency  $(f_c)$  is restricted to be less that 10% of the converter's switching frequency  $f_s$ .

The target crossover frequency is set as  $f_c = 5kHz$  and a phase margin is set at  $\phi_m = 55^{\circ}$ . At  $f = f_C$ , uncompensated loop gain exhibits a phase of about 92°, implying that a lead-lag (PID) type compensator is required in the neighborhood of  $f_c$  to boost the phase margin by  $\theta = 85^{\circ}$ . Such compensation is obtained by forming a pole zero pair-

$$G_{PID}(s) = G_{PI\infty} \left( 1 + \frac{\omega_{PI}}{s} \right) G_{PD0} \left( \frac{1 + \frac{s}{\omega_z}}{1 + \frac{s}{\omega_p}} \right)$$

(4.1)

the maximum phase boost generated by the PD pole-zero pair occurs at,

$$(\omega)_{max} = \sqrt{\omega_z \omega_p} \tag{4.2}$$

Substituting  $\theta$  and target crossover frequency, the values for zero and pole,  $\omega_z$  and  $\omega_p$  shall be calculated.

$$(\omega)_z = \omega_c \sqrt{\frac{1 - \sin\theta}{1 + \sin\theta}} = 2\pi . (0.437)(kHz)$$

$$(4.3)$$

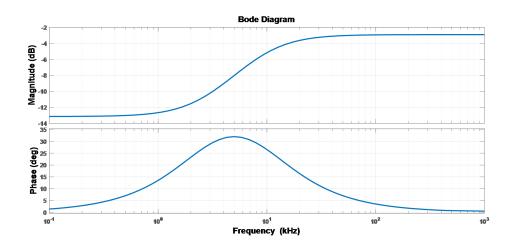

Figure 4.1: Bode plot of an uncompensated loop gain for ideal and non ideal SIMO converter

Figure 4.2: Bode plot of PID compensator for SIMO converter

$$(\omega)_p = \omega_c \sqrt{\frac{1+\sin\theta}{1-\sin\theta}} = 2\pi.(57.15)(kHz) \tag{4.4}$$

The DC gain  $G_{PD0}$  of the lead action is determined by imposing unity loop gain at the desired crossover frequency  $f_c$ ,

$$G_{PD0} = \frac{1}{\mid T(j\omega_c) \mid} \sqrt{\frac{1 + \left(\frac{\omega_c}{\omega_p}\right)^2}{1 + \left(\frac{\omega_c}{\omega_z}\right)^2}} = 0.0349$$

(4.5)

Bode plots of the lead compensation is:

Next, an integral action is introduced, the purpose of which is to null the steady state regulation error.  $\omega_{PI}$  is chosen 1/10th of  $\omega_c$ , that is  $2\pi . (0.5)(kHz)$  and  $G_{PI\infty} = 1$ .

#### **Digital Controller Design and Simulation** 4.1

This Chapter highlights the direct digital compensator design approach. Digital controllers are more convenient to implement on microprocessors than are continuous time controllers. Continuous time controllers must be implemented either using analog circuitry (op amps) or using numerical integration routines. Discrete-time controllers, on the other hand, are easily implemented using difference equations, i.e. simple computer software [1].

Two methods are available for design of digital controller, these are discussed below:

#### 4.1.1Indirect design by Emulation

Designing the Analog controller in the continuous domain by ignoring the effects of Sampling effect and delays in digital control loop and then converting into discrete compensator using discretization methods.

The PID compensator designed in previous section is given as:

$$G_c(s) = \frac{4.5538(s+2749)(s+3142)}{s(s+3.591\times10^5)}$$

(4.6)

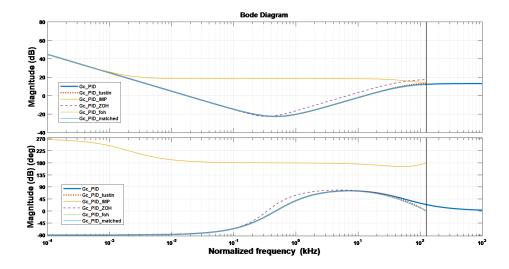

The bode plot for the compensator is shown in figure. This analog controller is the discretized by Bilinear (Tustin), Forward Euler and backward Euler using MATLAB. This generates the digital controller:

$$G_c(z) = \frac{2.6817(z - 0.9891)(z - 0.9875)}{(z - 0.164)(z - 1)}$$

(4.7)

$$G_c(z) = \frac{8.519 \times 10^{50} z^2 - 1.684 \times 10^{51} + 8.319 \times 10^{50} z}{1.871 \times 10^{50} z^2 - 1.054 \times 10^{50} z - 8.163 \times 10^{49}}$$

(4.8)

$$G_c(z) = \frac{8.721 \times 10^{50} z^2 - 1.724 \times 10^{51} + 8.519 \times 10^{50} z}{4.558 \times 10^{50} z^2 - 6.428 \times 10^{50} z + 1.87 \times 10^{50}}$$

(4.9)

The bilinear map,  $z = e^{sT} = \left(\frac{1+\frac{sT}{2}}{1-\frac{sT}{2}}\right)$ . inversely,  $s = \frac{1}{T}lnZ = \frac{2}{T_s}\frac{1-z^{-1}}{1+z^{-1}}$ Finally, the z domain PID gains are obtained from. Digital compensators z domain in additive form of PID transfer function is:

$$G_{PID}(Z) = K_p + \frac{K_i}{(1 - z^{-1})} + k_d(1 - z^{-1})$$

(4.10)

Converting multiplicative form to parallel form for PID controller using PID gains  $K_p$ ,  $K_i$ , and  $K_d$ .

Figure 4.3: Controller discretization using various methods

$$K_p = G_{PI\infty}G_{PD0}\left(1 + \frac{\omega_{PI}}{\omega_{PD}} - \frac{2\omega_{PI}}{\omega_p}\right)$$

(4.11)

$$K_i = 2G_{PI\infty}G_{PD0}\frac{\omega_{PI}}{\omega_p} \tag{4.12}$$

$$K_d = \frac{G_{PI\infty}G_{PD0}}{2} \left(1 - \frac{\omega_{PI}}{\omega_p}\right) \left(\frac{\omega_p}{\omega_{PD}} - 1\right)$$

(4.13)

The gain came out as  $0.0741, 6.09 \times 10^{-4}$  and 2.23 using the above equation.

$$G_{PID}(Z) = 0.0741 + \frac{6.09 \times 10^{-4}}{(1 - z^{-1})} + 2.23(1 - z^{-1})$$

(4.14)

### 4.1.2 Direct Digital Design

The continuous plant model is discretized with sampler and computational delays in control loop into account. Then, the discrete time controller is directly designed using frequency response like in continuous domain[14].

Converter plant model is Laplace form accounting time delay of  $10\mu$  sec of digital control loop is given as:

$$Gvd(z) = z^{-2} \frac{-0.01973z^3 + 0.01972z^2 + 0.01973z - 0.01972}{z^3 - 2.999z^2 + 2.997z - 0.9987}$$

(4.15)

Designing the PID controller for the above discrete converter model, we get:

$$G_{c}(z) = \frac{4.185z^{2} - 8.357z + 4.173}{z^{2} - 1.835z + 0.8352}$$

(4.16)

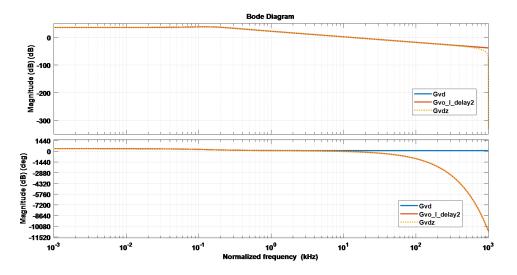

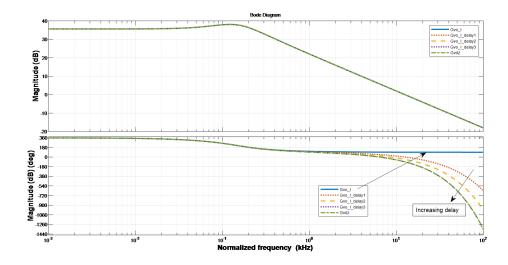

Figure 4.4: Bode plot of continuous transfer function with  $20\mu$  sec and without delay, discrete transfer function

Figure 4.5: Bode plot of continuous transfer function with  $30\mu$  sec and without delay, discrete transfer function

Mapping of it into s domain can be performed. Converting multiplicative form to parallel form for PID controller using PID gains  $K_p$ ,  $K_i$ , and  $K_d$ .

Figure 4.6: Transfer function of simo boost converter with time delay consideration

Figure 4.7: Synchronous buck converter comparison between discrete-time model Gvdz and the effective s domain model with delay into consideration  $Gvds_{delay2}$  and  $Gvd_{cont}$ (without delay)

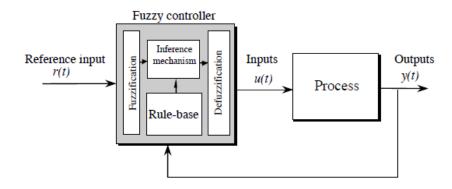

#### 4.1.3 Fuzzy Sugeno controller design

Fuzzy Logic controller are among the intelligent control techniques with applications ranging from DC-DC converter control to electric drives speed control. The methodology implemented in this thesis is using feedback output voltage to the controller. The error and change is error is respectively calculated and fed to controller.

Fuzzy set is widely being used in Power electronics application. It also serves a basis for Neural Network techniques which requires training of a model with input and output data.[15]

The fuzzy logic controller serves as intelligent controller for this propose. This methodology is applied in Buck, Boost and various other DC-DC converter. This controller is designed based on group of rules based on human knowledge and understanding. Therefore, the fuzzy controller provides the better steady state and transient performances than

Figure 4.8: Bode plot of PI controller for uncompensated, open loop gain and compensated buck converter

linear PI control. Fuzzy controller also improves the robustness of the systems. It involves four principal steps such as :

Figure 4.9: Block-diagram-of-fuzzy-logic-control-methodology

#### Fuzzification

This interface, which converts input data into suitable linguistic values; a knowledge base, which consists of a data base with the necessary linguistic definitions and the control rule set; a decision-making logic which, simulating a human decision process, infer the fuzzy control action from the knowledge of the control rules and linguistic variable definitions; a defuzzification interface which yields non fuzzy control action from an inferred fuzzy control action [15].

It also determines the degree of membership of the input values to defined fuzzy sets (linguistic variables). Absoulute error and differential error are defined as-

1. Absolute error Error = SetSpeed - CurrentSpeed

#### 2. Differential Vout error

This value is obtained by subtracting the previous error value from the current error value: dError = Error - LastError

The membership functions are triangular base and scaled to 0-1.

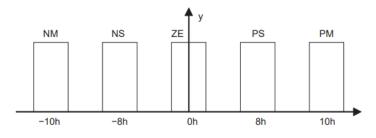

#### Fuzzy Logic Table Rules

|              |    | dError, X2[ ] |    |    |    |    |

|--------------|----|---------------|----|----|----|----|

|              |    | NM            | NS | ZE | PS | PM |

|              | NM | PM            | PM | PM | PS | ZE |

| Error, X1[ ] | NS | PM            | PM | PS | ZE | NS |

|              | ZE | PM            | PS | ZE | NS | NM |

|              | PS | PS            | ZE | NS | NM | NM |

|              | PM | ZE            | NS | NM | NM | NM |

Figure 4.10: Fuzzy rules table

Figure 4.11: Output membership function

#### Centroid Calculation Defuzzification Method

The result of the defuzzification must be a numeric value that determines the duty factor of the PWM signal that drives the motor. This value is obtained by finding the centroid point of the function that is the result of the multiplication of the output membership function and the output vector Y[].

## Chapter 5

# DSP IMPLEMENTATION FOR DIGITAL CONTROLLERS

## 5.1 Introduction to Digital Signal Processor

The Discrete control system controls the Power electronics through an output interface (OI). The output interface of the converter has ADC, DAC and PWM etc. These are less susceptible to external disturbances, noise, parameter variation and reliability and cost. This DSP can used to obtain last number of computation with small sampling time such as 1 ms. Also, DSP has application to complex control algorithms and offers good performance[16].

# 5.2 Digital versus Analog Implementation

Digital controllers are used in various applications through traditionally analog controllers were used. Digital controller accepts digitized voltage which is sampled using smaple and hold circuit and processed by control algorithms. It provids pwm pulsed to drive switching devices.

Figure 5.1: DSP based Digital Control System Diagram

Here, the few advantages and disadvantages of digital control are:-

- 1. Digital components are less prone to environmental variations and aging.

- 2. These are less sensitive to external harmonics and noise.

- 3. These is an ease to alter the hardware and alteration can be done easily.

4. Easy monitoring of systems and using IOT diagnostics can be done easily.

5. Some advanced control techniques, such as space vector modulation, adaptive control, fuzzy control, etc.

However, digital control systems are not without disadvantages when compared with analog control systems. Some of the disadvantages are as follows:

1. Finite Finite signal resolution due to the finite word length of the ADCs, and DACs or PWM outputs, which cause the output less accurate. Analog control gives infinite resolution of the measured signal.

2. Time delays in the control loop due to both the sampling of ADCs and computation of the control algorithm by the processors. Analog control can provide continuous processing of signal, thus allowing very high bandwidth.[17]

## 5.3 The TMS320F2812 DSP

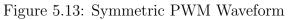

A Digital Signal processor is a single chip which has both processor and the embedded systems. It uses real time control with complex calculations. 8 stages are there for each instruction for final completion. The pipeline is filled with instruction and each instruction is executed per clock cycle. DSP has 150MHz frequency with 6.67ns time taken by each instruction. It is a first 32-bit 150MIPS DSP with on-chip flash memory and on-chip high-precision analog peripherals[18].

## 5.3.1 Architecture of F2812

The TMS320F2812 Block Diagram can be divided into 4 functional blocks:

- 1) Internal and External Bus System

- 2) Central Processing Unit (CPU)

- 3) Memory

- 4) Peripherals

Figure 5.2: C281x Block Diagram

#### The F2812 CPU

CPU execute most of instructions with register to register operations

Figure 5.3: C28x CPU

The CPU is able to execute most of the instructions to perform register-to-register operations and a range of instructions that are commonly used by micro controllers, e.g. byte packing and unpacking and bit manipulation in a single cycle. The architecture is also supported by powerful addressing modes, which allow the compiler as well as the assembly programmer to generate compact code that almost corresponds one-to-one with the C code.

Figure 5.4: Atomic Arithmetic Logic Unit

### Internal Bus Structure

The F2812 memory bus architecture contains:

- 1) A program read bus (22 bit address line and 32 bit data line)

- 2) A data read bus (32 bit address line and 32 bit data line)

- 3) A data write bus (32 bit address line and 32 bit data line)

The 32-bit-wide data busses enable single cycle 32-bit operations. This multiple bus architecture, known as a Harvard Bus Architecture enables the C28x to fetch an instruction, read a data value and write a data value in a single cycle. All peripherals and memories are attached to the memory bus and will prioritise memory accesses.

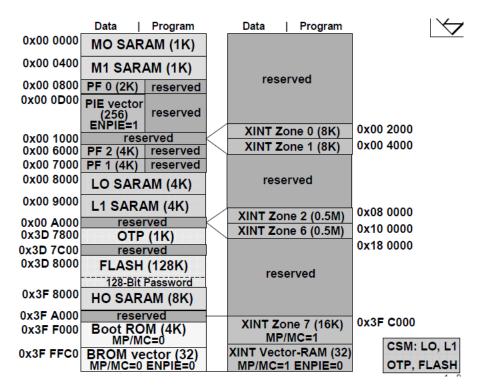

## Memory Map

The memory space on the F2812 is divided into program and data space. There are several different types of memory available that can be used as both program or data space. They include flash memory, single access RAM (SARAM), expanded SARAM, and Boot ROM which is factory programmed with boot software routines or standard tables used in math related algorithms. Memory space width is always 16 bit.

The F2812 uses 32-bit data addresses and 22-bit program addresses. This allows for a total address reach of 4G words (1 word = 16 bits) in data space and 4M words in program space.

Figure 5.5: TMS320F2812 Memory Map

### Interrupt Response

The fast interrupt response, with automatic "context" save of critical registers, resulting in a device that is capable of servicing many asynchronous events with minimal latency. Here "context" means all the registers you need to save so that you can go away and carry out some other process, then come back to exactly where you left. F2812 devices implement a zero cycle penalty to save and restore the 14 registers during an interrupt. This feature helps to reduce the interrupt service routine overheads.

The Peripheral Interrupt Expansion (PIE) – Unit allows the user to specify individual interrupt service routines for up to 96 internal and external interrupt events. All possible 96 interrupt sources share 14 maskable interrupt lines (INT1 to INT14), 12 of them are controlled by the PIE – module.

## 5.3.2 Peripherals of a DSP

#### Digital I/O Unit:

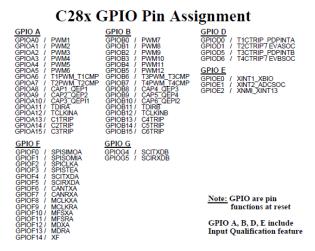

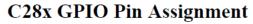

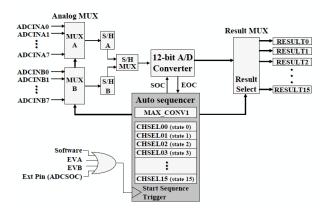

Integrated peripherals give the C28x an important advantage over other processors. All digital I/O's are grouped together into "Ports", called GPIO-A, B, D, E, F and G, means "general purpose input output".

Figure 5.6: GPIO Pin Assignment

All six GPIO-Ports are controlled by their pwm multiplex register, called GPxMUX (where x stands for A to F). Clearing a bit position to zero means selecting its digital I/O function, setting a bit to 1 means selecting the special function. Most of the peripheral signals are multiplexed with general-purpose I/O (GPIO) signals. This enables to use a pin as GPIO if the peripheral signal or function is not used. On reset, all GPIO pins are configured as inputs. One can then individually program each pin for GPIO mode or Peripheral Signal mode.

### 5.3.3 PWM Generators and ADC of TMS320F2812

#### **Event Manager**

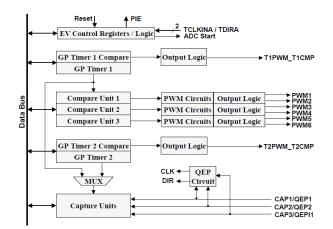

The F2812 has 2 Event Manager peripherals on-chip to provide a broad range of functions and features that are particularly useful in control applications. The event manager modules include general-purpose (GP) timers, full compare/ PWM units, capture units, and quadrature-encoder pulse (QEP) circuits. The 2 Event Manager modules are identical peripherals intended for multi-axis/digital control applications.

The event manager (EV) modules provide a broad range of functions and features that are particularly useful in motion control and motor control applications.

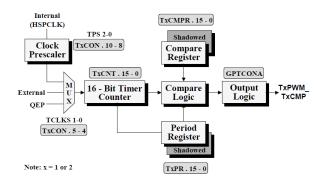

#### General-Purpose (GP) Timers

There are two GP timers. The GP timer x (x = 1 or 2 for EVA; x = 3 or 4 for EVB) includes:

Figure 5.7: Event Manager block diagram

1) A 16-bit timer, up-/down-counter, TxCNT, for reads or writes.

- 2) A 16-bit timer-compare register, TxCMPR, for reads or writes.

- 3) A 16-bit timer-period register, TxPR, for reads or writes.

4) A 16-bit timer-control register, TxCON, for reads or writes.

5) A selectable direction input pin (TDIRx) (to count up or down when directional up-/down-count mode is selected).

The GP timers can be operated independently or synchronized with each other. The compare register associated with each GP timer can be used for compare function and PWM-waveform generation. There are three continuous modes of operations for each GP timer in up- or up/downcounting operations.

Internal or external input clocks with programmable prescaler are used for each GP timer. GP timers also provide the time base for the other event manager sub modules: GP timer 1 for all the compares and PWM circuits, GP timer 2/1 for the capture units and the quadrature pulse counting operations. Double-buffering of the period and compare registers allows programmable change of the timer (PWM) period and the compare/PWM pulse width as needed [21].

Full-Compare Units There are three full-compare units on each event manager. These compare units use GP timer1 as the time base and generate six outputs for compare and PWM-waveform generation using programmable deadband circuit. The state of each of the six outputs is configured independently. The compare registers of the compare units are double-buffered, allowing programmable change of the compare/PWM pulse widths as needed.

#### Timers

CPU-Timers 0, 1, and 2 are identical 32-bit timers with presettable periods and with 16-bit clock prescaling. The timers have a 32-bit count down register, which generates an interrupt when the counter reaches zero. The counter is decremented at the CPU clock speed divided by the prescale value setting. When the counter reaches zero, it is automatically reloaded with a 32-bit period value.

$$f_{PWM} = \frac{f_{CPU}}{T1PR.TPS_{T1}.HISCP}$$

(5.1)

Figure 5.8: General purpose Timer Block diagram

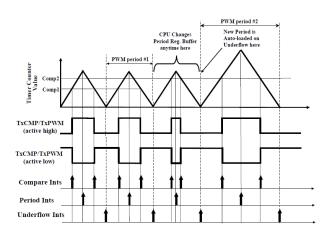

Figure 5.9: Generated Outputs and interrupts

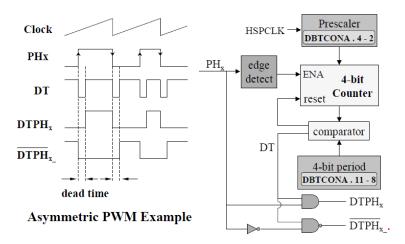

# Dead-Band Functionality (EVA)

Figure 5.10: Dead-Band Functionality in EVA

Figure 5.11: Deadband in PWM waves

with TPST1 = 1, HISCP = 2,  $f_{CPU} = 150MHz$  and a desired  $f_{PWM} = 50kHz$  we derive: T1PR = 1500

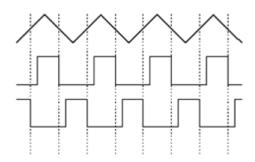

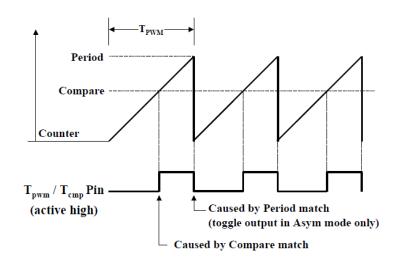

## Asymmetric PWM Waveform

Figure 5.12: Asymmetric PWM waveform

T1CMPR defines the width of the PWM-pulse.

#### Analogue Digital Converter

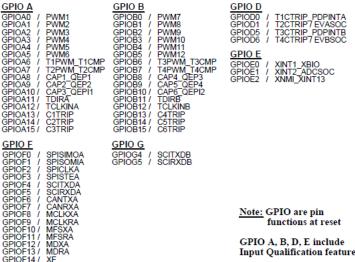

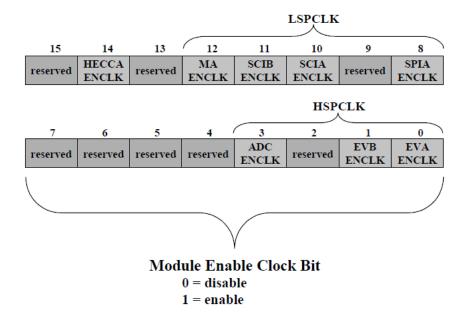

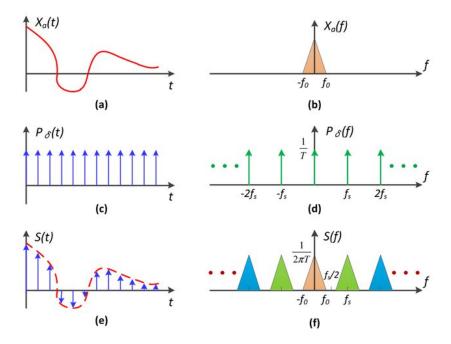

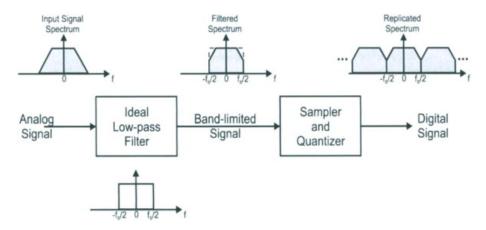

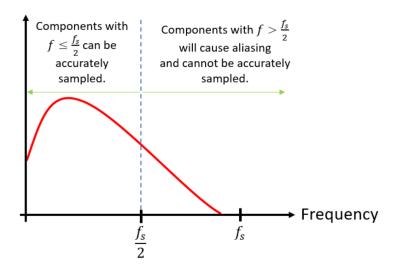

an important interface between the controller and the real world. Most physical signals such as temperature, humidity, pressure, current, speed and acceleration are analogue signals. The purpose of the ADC is to convert this analogue voltage in a digital number.