#### Realization of Some Analog Signal Processing/Generation Circuits Employing OTRAs

A Thesis Submitted to the Delhi Technological University for the award of Doctor of Philosophy

in Department of Electronics & Communication Engineering

by

#### Under the Supervision of Prof. Pragati Kumar & Prof. Data Ram Bhaskar

Department of Electrical Engineering Delhi Technological University Delhi-110042, India

DELHI TECHNOLOGICAL UNIVERSITY ALL RIGHTS RESERVED

June 2022

### Certificate

This is to certify that the thesis entitled "Realization of Some Analog Signal Processing/Generation Circuits Employing OTRAs" being submitted by Ms. Garima (2K11/Ph.D/EC/09) for the award of degree of Doctor of Philosophy in the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, is the record of students own work carried out by her under our supervision. The contents of this research work have not been submitted in part or fully to any other institute or university for the award of any degree.

Date: 27th June, 2022

**Prof. Pragati Kumar** Department of Electrical Engineering Delhi Technological University Delhi-110042, India **Prof. Data Ram Bhaskar** Department of Electrical Engineering Delhi Technological University Delhi-110042, India

### Acknowledgment

I take this opportunity to express my significant indebtedness, most profound sense of gratitude and heartiest thanks to my supervisors **Prof. Pragati Kumar** and **Prof. D. R. Bhaskar**, who kindly accepted to take me as Ph. D student and supported me with warm encouragement, patient guidance and fruitful discussions during the entire course of the research work. Their humane and warm personal approaches in all aspects, have given me the strength to carry out this research work on a steady and smooth course. I humbly acknowledge life time gratitude to them.

I would like to express my thanks to **Prof. N. S. Raghava**, HOD (ECE) and **Prof. Uma Nangia**, HOD (EE) for their kind support.

I would like to express my sincere thanks to **Prof. Raj Senani**, NSUT-Delhi and **Prof. Madhusudan Singh**, EED, DTU-Delhi, for their kind support, helpful advice and constructive suggestions.

More personally, I would like to express my sincere thanks to my colleagues **Dr**. **Ram Bhagat**, **Dr**. **Bhavnesh Jaint** EED, DTU-Delhi and **Dr**. **Alok Kumar Singh**, ECED, DTU-Delhi for their help and support throughout the present research work. I would also like to thank **Dr**. **Manoj Kumar** and **Dr**. **Ajishek Raj** for rendering their valuable help throughout the present work.

Also, I would like to extend my thanks to Mr. Upendra Kumar, Mr. Jagvir

Singh, Mr. Anil Butola, Mr. Abhishek and Deepak for providing and arranging all necessary help in Linear Integrated Circuits Lab for carrying out experimental work. I express my deep sense of gratitude to Mr. Ashutosh Jha, AGMATEL INDIA PVT. LTD. for arranging important measuring instruments for experimental works.

I am also grateful to all my family members who were always with me during my Ph.D. course and tolerated me.

Last, but not the least, I thank **Mother Nature** and **God Almighty** for providing me the opportunity for pursuing doctoral studies.

Garima (2K11/Ph.D/EC/09)

### Contents

| $\mathbf{C}$ | ertifi | cate            |           |                                                    | i    |

|--------------|--------|-----------------|-----------|----------------------------------------------------|------|

| A            | ckno   | wledgn          | nent      |                                                    | ii   |

| Li           | ist of | <b>Table</b>    | S         |                                                    | xv   |

| Li           | ist of | $\mathbf{Symb}$ | ols       | 2                                                  | xvi  |

| Li           | ist of | Abbre           | eviations | x                                                  | viii |

| Li           | ist of | Public          | cations   | 2                                                  | xix  |

| 1            | Intr   | roducti         | ion       |                                                    | 1    |

| 2            | Rea    | lizatio         | n of Sim  | ulated Inductors                                   | 32   |

|              | 2.1    | Introd          | luction . |                                                    | 32   |

|              |        |                 | 2.1.0.1   | Grounded lossy inductance simulators using OTRAs   | 33   |

|              |        |                 | 2.1.0.2   | Lossless grounded inductor simulators using OTRA . | 35   |

|              |        |                 | 2.1.0.3   | Generalised impedance simulators using OTRAs       | 37   |

|              | 2.2    | Groun           | ded Serie | s RL Simulator Using OTRA                          | 40   |

|              |        |                 | 2.2.0.1   | Realization of MOS Voltage Follower                | 41   |

|              |        |                 | 2.2.0.2   | Non-Ideal Analysis                                 | 41   |

|              |        |                 | 2.2.0.3   | Simulation Results                                 | 43   |

|              |        |                 | 2.2.0.4   | Application Example                                | 44   |

|              | 2.3    | Groun           | ided Para | llel Lossy Inductor Simulator Using OTRA           | 48   |

|              |        | 2.3.1           | Non-Ide   | al Analysis                                        | 49   |

|   |     |         | 2.3.1.1     | Application Examples of the proposed parallel lossy    |     |

|---|-----|---------|-------------|--------------------------------------------------------|-----|

|   |     |         |             | inductor                                               | 50  |

|   |     | 2.3.2   | Simulati    | ion and Experimental Results                           | 52  |

|   |     |         | 2.3.2.1     | Simulation Results                                     | 52  |

|   |     |         | 2.3.2.2     | Experimental Results                                   | 60  |

|   | 2.4 | Concl   | uding Rer   | narks                                                  | 64  |

| 3 | Nev | v Desig | gn of Ca    | pacitance Multiplier Circuit Using Single OTRA         | 69  |

|   | 3.1 | Introd  | luction .   |                                                        | 69  |

|   | 3.2 | New I   | Positive/ 1 | Negative Grounded Capacitance Multiplier               | 78  |

|   |     |         | 3.2.0.1     | MOS-C implementation of CM                             | 79  |

|   |     |         | 3.2.0.2     | Non-Ideal Analysis                                     | 80  |

|   |     |         | 3.2.0.3     | Application Examples                                   | 81  |

|   |     |         | 3.2.0.4     | Simulation Results and Matlab Evaluations              | 83  |

|   |     |         | 3.2.0.5     | Monte Carlo Simulation                                 | 86  |

|   |     |         | 3.2.0.6     | Process Corner and Temperature Analysis                | 89  |

|   |     |         | 3.2.0.7     | Magnitude and Phase Responses of MOS-C CM Cir-         |     |

|   |     |         |             | cuit                                                   | 91  |

|   |     |         | 3.2.0.8     | Time and Frequency Responses of Capacitance Can-       |     |

|   |     |         |             | cellation Scheme and First-Order LPF $\ . \ . \ . \ .$ | 93  |

|   |     |         | 3.2.0.9     | Experimental Results                                   | 96  |

|   | 3.3 | Concl   | uding Rer   | narks                                                  | 98  |

| 4 | Nev | v Real  | izations    | of Voltage Mode Second Order Biquadratic Filter        | ,   |

|   | Cor | nfigura | tions       |                                                        | 103 |

|   | 4.1 | Introd  | luction .   |                                                        | 103 |

|   |     | 4.1.1   | First Or    | der Filters using OTRAs                                | 104 |

|   |     | 4.1.2   | Second      | Order Filters using OTRAs                              | 106 |

|   |     |         | 4.1.2.1     | Single-Input-Single-Output Biquads                     | 106 |

|   |     |         | 4.1.2.2     | Single-Input-Multiple-Output Biquads                   | 109 |

|   |                                 |                                                                                              | 4.1.2.3                                                                                                                                                    | Multiple-Input-Single-Output Biquads                               |

|---|---------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|   |                                 |                                                                                              | 4.1.2.4                                                                                                                                                    | Multiple-Input-Multiple-Output Biquads 113                         |

|   |                                 | 4.1.3                                                                                        | Third ar                                                                                                                                                   | nd Higher order filters using OTRAs                                |

|   | 4.2                             | Propo                                                                                        | sed Single                                                                                                                                                 | e OTRA based second order filter configuration $\ . \ . \ . \ 118$ |

|   |                                 |                                                                                              | 4.2.0.1                                                                                                                                                    | Non-Ideal Analysis                                                 |

|   |                                 |                                                                                              | 4.2.0.2                                                                                                                                                    | Simulation Results                                                 |

|   | 4.3                             | Realiz                                                                                       | ation of S                                                                                                                                                 | IMO biquad filters and quadrature sinusoidal oscilla-              |

|   |                                 | tors us                                                                                      | sing OTR                                                                                                                                                   | As                                                                 |

|   |                                 |                                                                                              | 4.3.0.1                                                                                                                                                    | Non-ideal Analysis                                                 |

|   |                                 |                                                                                              | 4.3.0.2                                                                                                                                                    | Sensitivity Analysis                                               |

|   |                                 | 4.3.1                                                                                        | Propose                                                                                                                                                    | d VM Fully Uncoupled Quadrature Sinusoidal Oscillator 130          |

|   |                                 |                                                                                              | 4.3.1.1                                                                                                                                                    | Frequency Stability of the Quadrature Oscillators 132              |

|   |                                 |                                                                                              | 4.3.1.2                                                                                                                                                    | Simulation and Experimental Results                                |

|   |                                 | 4.3.2                                                                                        | Quadrat                                                                                                                                                    | ure Sinusoidal Oscillator                                          |

|   |                                 | Conch                                                                                        | uding Dor                                                                                                                                                  | narks                                                              |

|   | 4.4                             | Conci                                                                                        | uting her                                                                                                                                                  | IIAIKS                                                             |

| 5 |                                 |                                                                                              | 0                                                                                                                                                          |                                                                    |

| 5 |                                 | rd Ord                                                                                       | ler Sinus                                                                                                                                                  | soidal Oscillators Using OTRAs 151                                 |

| 5 | $\mathbf{Thi}$                  | rd Ord                                                                                       | ler Sinus                                                                                                                                                  | soidal Oscillators Using OTRAs 151                                 |

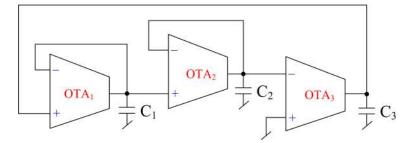

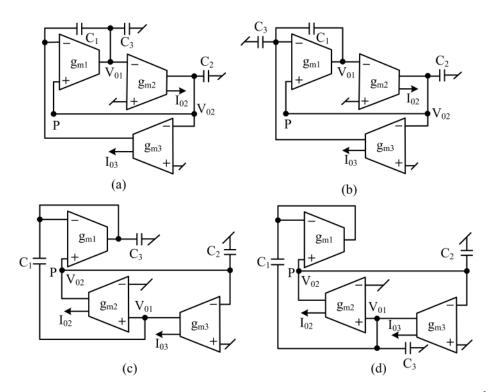

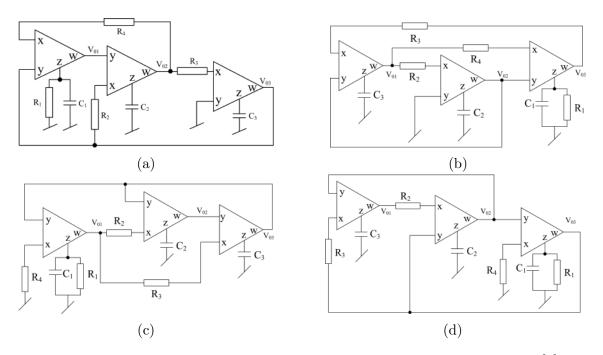

| 5 | <b>Thi</b><br>5.1               | <b>rd Ord</b><br>Introd<br>Third                                                             | ler Sinus<br>uction .<br>Order Os                                                                                                                          | soidal Oscillators Using OTRAs 151                                 |

| 5 | <b>Thi</b><br>5.1<br>5.2        | rd Ord<br>Introd<br>Third<br>Two N                                                           | ler Sinus<br>uction .<br>Order Os<br>New Thire                                                                                                             | soidal Oscillators Using OTRAs151                                  |

| 5 | <b>Thi</b><br>5.1<br>5.2        | rd Ord<br>Introd<br>Third<br>Two N                                                           | ler Sinus<br>uction .<br>Order Os<br>New Third<br>Employing                                                                                                | soidal Oscillators Using OTRAs       151                           |

| 5 | <b>Thi</b><br>5.1<br>5.2        | rd Ord<br>Introd<br>Third<br>Two N<br>tions I                                                | ler Sinus<br>uction .<br>Order Os<br>New Third<br>Employing                                                                                                | soidal Oscillators Using OTRAs       151                           |

| 5 | <b>Thi</b><br>5.1<br>5.2        | rd Ord<br>Introd<br>Third<br>Two N<br>tions I                                                | ler Sinus<br>uction .<br>Order Os<br>New Thiro<br>Employing<br>Non-Ide<br>5.3.1.1                                                                          | soidal Oscillators Using OTRAs       151                           |

| 5 | <b>Thi</b><br>5.1<br>5.2        | rd Ord<br>Introd<br>Third<br>Two M<br>tions I<br>5.3.1                                       | ler Sinus<br>uction .<br>Order Os<br>New Third<br>Employing<br>Non-Ide<br>5.3.1.1<br>Sensitivi                                                             | soidal Oscillators Using OTRAs       151                           |

| 5 | <b>Thi</b><br>5.1<br>5.2        | rd Ord<br>Introd<br>Third<br>Two N<br>tions I<br>5.3.1<br>5.3.2                              | ler Sinus<br>uction .<br>Order Os<br>New Third<br>Employing<br>Non-Ide<br>5.3.1.1<br>Sensitivi                                                             | soidal Oscillators Using OTRAs151                                  |

| 5 | <b>Thi</b><br>5.1<br>5.2        | rd Ord<br>Introd<br>Third<br>Two N<br>tions I<br>5.3.1<br>5.3.2<br>5.3.3                     | ler Sinus<br>uction .<br>Order Os<br>New Third<br>Employing<br>Non-Ide<br>5.3.1.1<br>Sensitivi<br>Simulati<br>5.3.3.1                                      | soidal Oscillators Using OTRAs151                                  |

| 5 | <b>Thi</b><br>5.1<br>5.2<br>5.3 | rd Ord<br>Introd<br>Third<br>Two N<br>tions I<br>5.3.1<br>5.3.2<br>5.3.3<br>Single           | ler Sinus<br>uction .<br>Order Os<br>New Third<br>Employing<br>Non-Ide<br>5.3.1.1<br>Sensitivi<br>Simulati<br>5.3.3.1<br>OTRA-b                            | soidal Oscillators Using OTRAs151                                  |

| 5 | <b>Thi</b><br>5.1<br>5.2<br>5.3 | rd Ord<br>Introd<br>Third<br>Two N<br>tions I<br>5.3.1<br>5.3.2<br>5.3.3<br>Single           | ler Sinus<br>uction .<br>Order Os<br>New Third<br>Employing<br>Non-Ide<br>5.3.1.1<br>Sensitivi<br>Simulati<br>5.3.3.1<br>OTRA-b<br>Control of              | Soidal Oscillators Using OTRAs151                                  |

| 5 | <b>Thi</b><br>5.1<br>5.2<br>5.3 | rd Ord<br>Introd<br>Third<br>Two N<br>tions I<br>5.3.1<br>5.3.2<br>5.3.3<br>Single<br>dent O | ler Sinus<br>uction .<br>Order Os<br>New Thiro<br>Employing<br>Non-Ide<br>5.3.1.1<br>Sensitivi<br>Simulati<br>5.3.3.1<br>OTRA-b<br>Control of<br>Effect of | soidal Oscillators Using OTRAs151                                  |

|   |     | 5.4.3   | Simulation Results   | 185 |

|---|-----|---------|----------------------|-----|

|   |     | 5.4.4   | Experimental Results | 186 |

|   | 5.5 | Conclu  | uding Remarks        | 190 |

| 6 | Cor | nclusio | ns and Future scope  | 197 |

|   | 6.1 | Conclu  | usions               | 197 |

|   |     |         |                      |     |

### List of Figures

| 1.1  | Symbolic notation of OTRA                                             | 4  |

|------|-----------------------------------------------------------------------|----|

| 1.2  | CMOS representation of OTRA proposed by Chen, Tsao and Chen [2]       | 5  |

| 1.3  | CMOS representation of OTRA presented by Salama and Soliman [3]       | 6  |

| 1.4  | CMOS representation of OTRA [8]                                       | 7  |

| 1.5  | DC characteristic of the OTRA                                         | 8  |

| 1.6  | Frequency responses of magnitude and phase of an OTRA $\ . \ . \ .$ . | 9  |

| 1.7  | CMOS representation of OTRA derived from $[15]$                       | 11 |

| 1.8  | DC characteristic of the OTRA presented in $[15]$                     | 11 |

| 1.9  | Frequency responses of magnitude and phase of an OTRA of $[15]$ $$ .  | 12 |

| 1.10 | OTRA realized using commercially available CFOA ICs [16] $\ .$        | 12 |

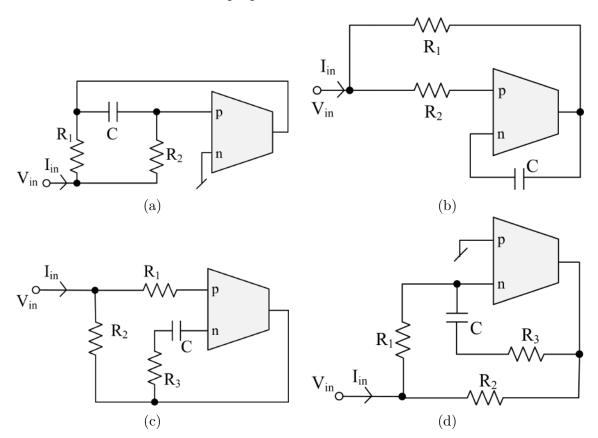

| 2.1  | Grounded lossy immitance simulator topologies presented in $[3]$      | 33 |

| 2.2  | Positive lossy inductor (parallel R-L) simulator presented in $[7]$   | 35 |

| 2.3  | Negative grounded inductance simulator using an OTRA reported in      |    |

|      | [10]                                                                  | 37 |

| 2.4  | Positive generalized impedance simulator presented in $[16]$          | 39 |

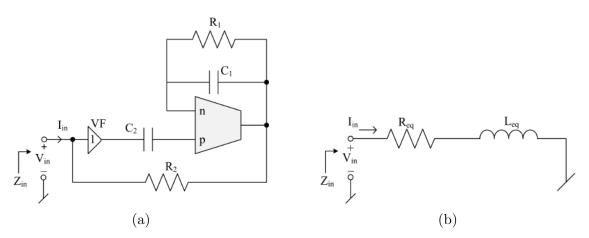

| 2.5  | (a) Proposed grounded series RL-Simulator (b) Its passive equivalent  | 40 |

| 2.6  | MOS implementation of VF $[18]$                                       | 41 |

| 2.7  | Non-ideal equivalent circuit of the proposed grounded series RL $$    | 42 |

| 2.8  | CMOS Realization of OTRA [20]                                         | 43 |

| 2.9  | (a) Magnitude response of simulated impedance (b) Phase response      |    |

|      | of simulated impedance                                                | 44 |

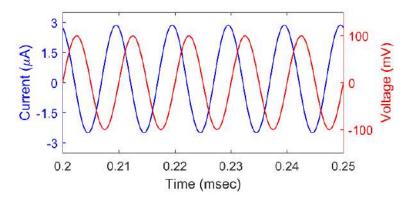

| 2.10 | Transient voltage and current responses of simulated impedance        | 45 |

| 2.11 | Voltage-mode LPF circuit as an application of the proposed grounded   |    |

|------|-----------------------------------------------------------------------|----|

|      | series RL simulator                                                   | 45 |

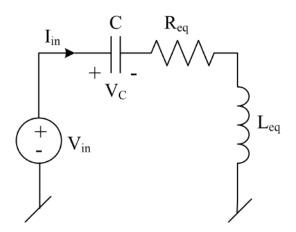

| 2.12 | Simulated inductor based LPF circuit                                  | 46 |

| 2.13 | (a) Magnitude response of LPF (b) Phase response of LPF $\hdots$      | 47 |

| 2.14 | (a) Proposed grounded lossy inductor circuit (b) Passive Equivalent   |    |

|      | of the proposed circuit                                               | 48 |

| 2.15 | Non-ideal model of OTRA [19]                                          | 49 |

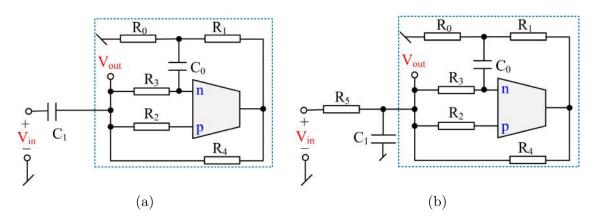

| 2.16 | Realization of (a) HPF and (b) BPF utilizing the proposed grounded    |    |

|      | lossy inductor                                                        | 51 |

| 2.17 | CMOS Realization of OTRA [21]                                         | 52 |

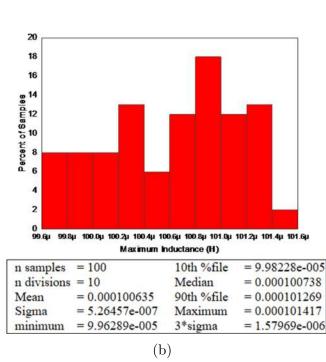

| 2.18 | (a) Simulated Magnitude Response of the proposed grounded lossy       |    |

|      | inductor (b) Simulated Phase Response of the proposed grounded        |    |

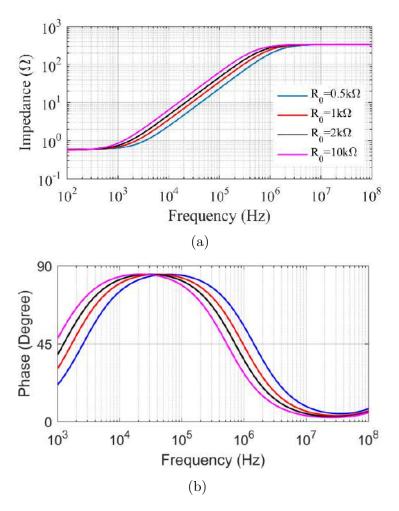

|      | lossy inductor                                                        | 53 |

| 2.19 | (a) Variation in magnitude of the proposed grounded lossy inductor    |    |

|      | (b) Variation in phase of the proposed grounded lossy inductor        | 54 |

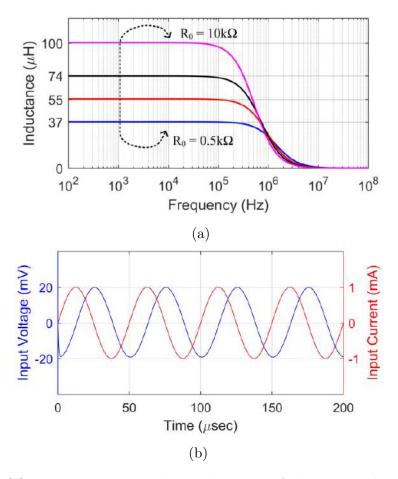

| 2.20 | (a) Variation in equivalent inductance of the proposed grounded lossy |    |

|      | inductor (b) Input transient current and voltage of the proposed      |    |

|      | grounded lossy inductor                                               | 55 |

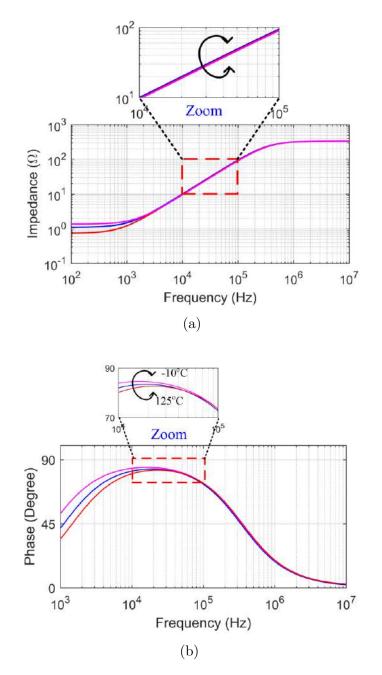

| 2.21 | (a) Simulated and theoretical magnitude responses of the proposed     |    |

|      | negative lossless inductor (b) Simulated and theoretical phase re-    |    |

|      | sponses of the proposed negative lossless inductor                    | 56 |

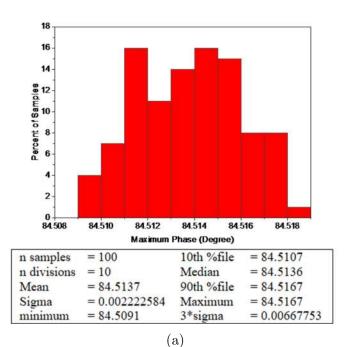

| 2.22 | (a) Histogram of maximum phase of the proposed grounded lossy in-     |    |

|      | ductor (b) Histogram of maximum inductance of the proposed grounded   |    |

|      | lossy inductor                                                        | 57 |

| 2.23 | (a) Magnitude response of the proposed grounded lossy inductor with   |    |

|      | different temperature (b) Phase response of the proposed grounded     |    |

|      | lossy inductor with different temperature                             | 58 |

| 2.24 | (a) Simulated frequency responses of HPF (b) Simulated frequency      |    |

|      | responses of BPF                                                      | 59 |

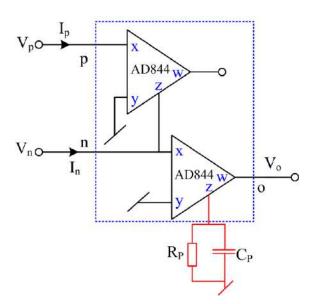

| 2.25 | OTRA implementation using off-the-shelf ICs AD844 [22]                  | 61 |

|------|-------------------------------------------------------------------------|----|

| 2.26 | Complete current excited OTRA realization using CFOAs $\ldots$ .        | 61 |

| 2.27 | Experimental input and output voltages of the proposed grounded         |    |

|      | lossy inductor                                                          | 62 |

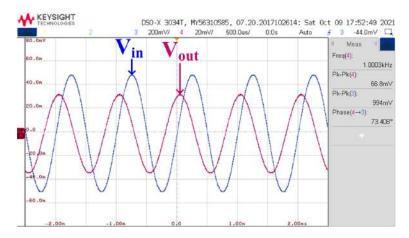

| 2.28 | Snapshot of the experimental setup for HPF                              | 62 |

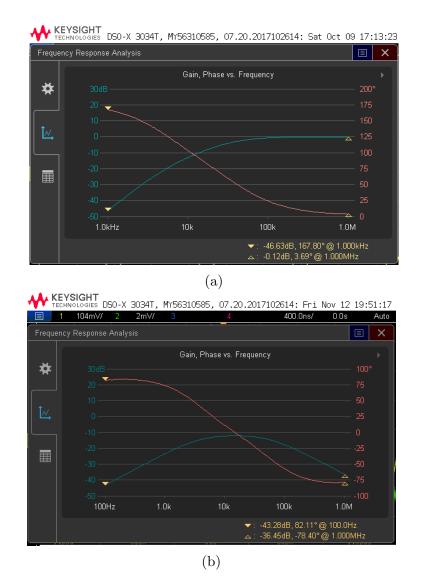

| 2.29 | (a) Experimental magnitude and phase response of HPF (b) Experi-        |    |

|      | mental magnitude and phase response of BPF $\ldots$                     | 63 |

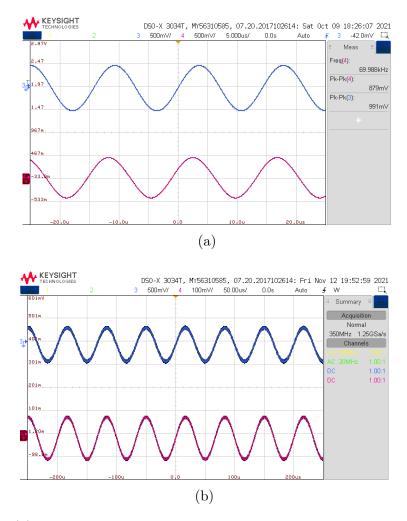

| 2.30 | (a) Experimental time response of input and output for HPF (b)          |    |

|      | Experimental time response of input and output for BPF                  | 64 |

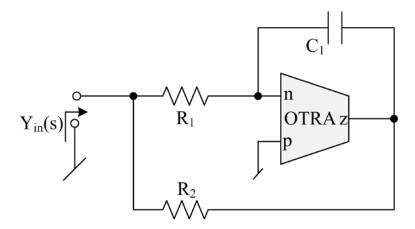

| 3.1  | Capacitance multiplier presented in [6]                                 | 72 |

| 3.2  | Negative capacitance multiplier reported in [13]                        | 74 |

| 3.3  | Grounded capacitance simulator presented in $[18]$                      | 75 |

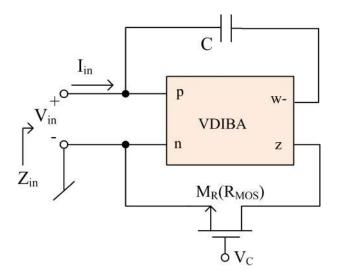

| 3.4  | Single VDIBA based capacitance multiplier presented in $[20]$           | 76 |

| 3.5  | Proposed capacitance multiplier circuit                                 | 78 |

| 3.6  | MOS implementation of linear resistance connected between inverting     |    |

|      | input and output terminal of OTRA [29]                                  | 79 |

| 3.7  | MOS-C implementation of proposed capacitance multiplier circuit         | 80 |

| 3.8  | Capacitance cancellation circuit [14]                                   | 81 |

| 3.9  | First-order LPF                                                         | 82 |

| 3.10 | CMOS Implementation of OTRA [31]                                        | 83 |

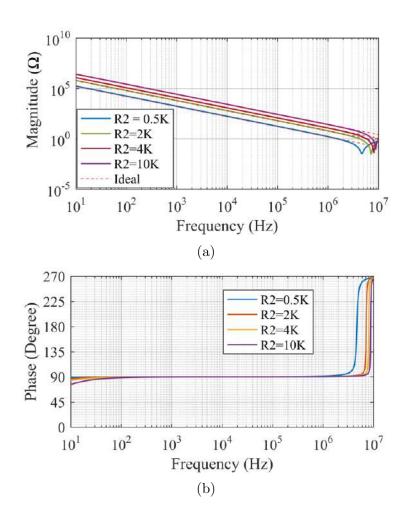

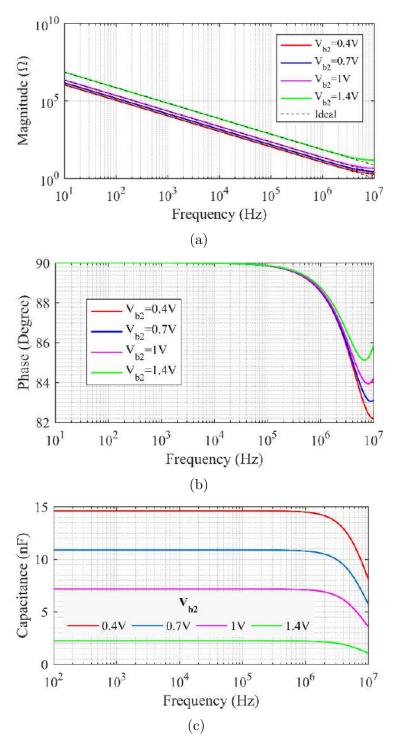

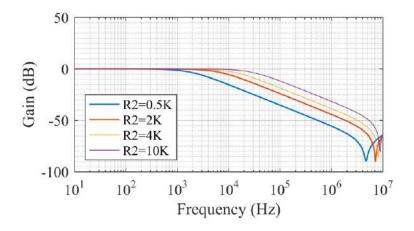

| 3.11 | Variation of (a) magnitude (b) phase (c) capacitance with $R_2$ for the |    |

|      | proposed positive CM                                                    | 85 |

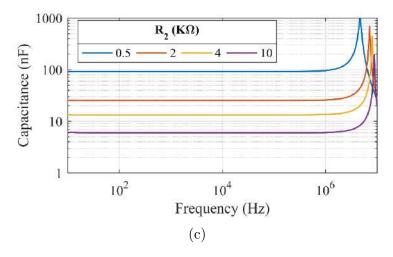

| 3.12 | Variation of (a) magnitude (b) phase with $R_2$ for the proposed nega-  |    |

|      | tive CM                                                                 | 86 |

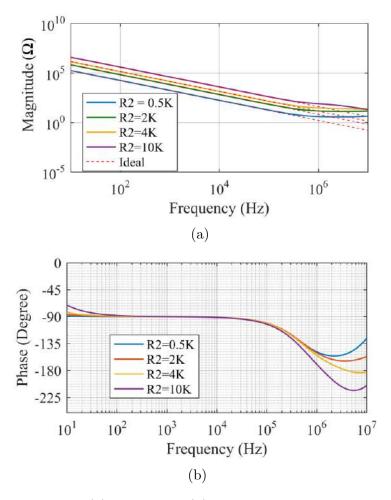

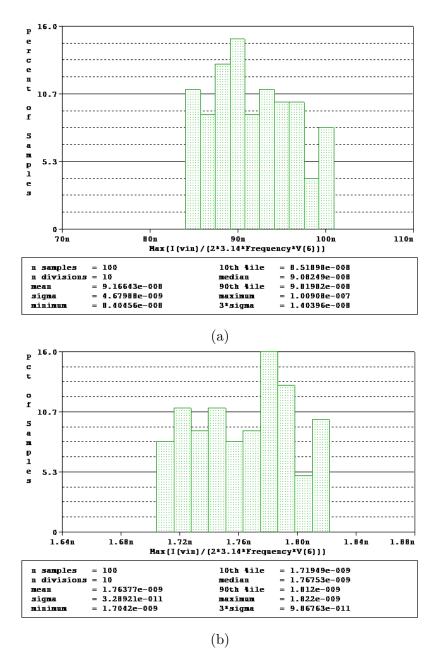

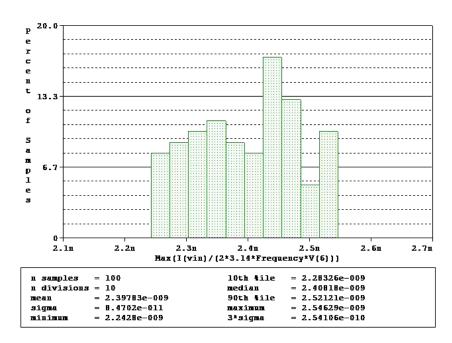

| 3.13 | Histogram of equivalent capacitance realized by positive CM with        |    |

|      | 10% tolerance in(a) $R_2$ (b) $C_0$                                     | 87 |

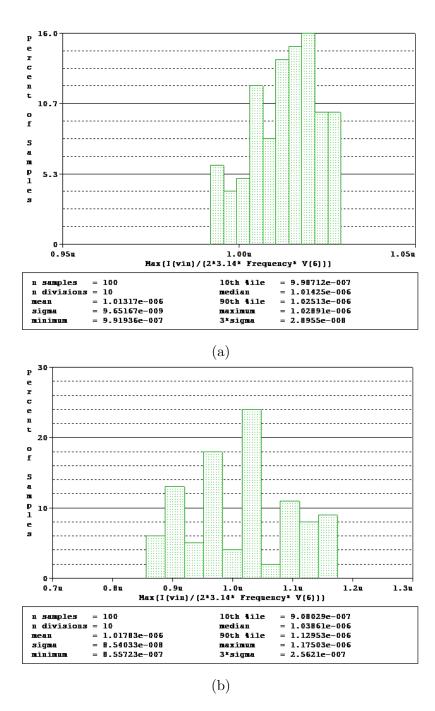

| 3.14 | Histogram of equivalent capacitance realized by negative CM with        |    |

|      | 10% tolerance in(a) $R_2$ (b) $C_0$                                     | 88 |

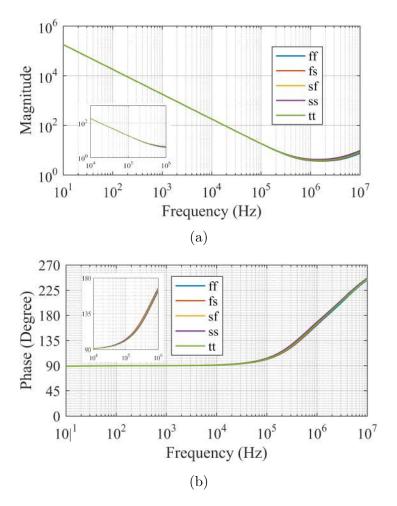

| 3.15 | Process corner analysis on (a) magnitude and (b) phase of positive CM   | 89 |

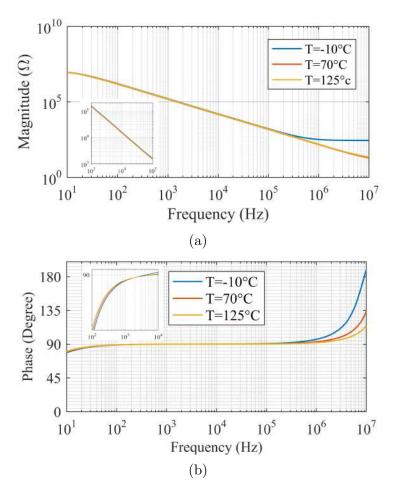

| 3.16 | Variation of (a) magnitude and (b) phase with temperature for posi-          |

|------|------------------------------------------------------------------------------|

|      | tive CM                                                                      |

| 3.17 | Variation of (a) magnitude and (b) phase with temperature for neg-           |

|      | ative CM                                                                     |

| 3.18 | MOS implementation of VF $[32]$                                              |

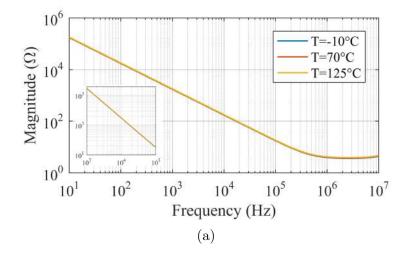

| 3.19 | (a) Magnitude and (b) phase of impedance and (c) capacitance for             |

|      | MOS-C CM circuit                                                             |

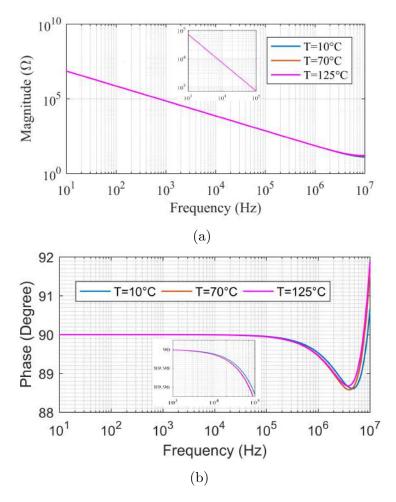

| 3.20 | Variation of (a) Magnitude and (b) phase of impedance with temper-           |

|      | ature for MOS-C CM circuit                                                   |

| 3.21 | Histogram of equivalent capacitance realized by using MOS-C equiv-           |

|      | alent of positive CM with 10% tolerance in $C_0$                             |

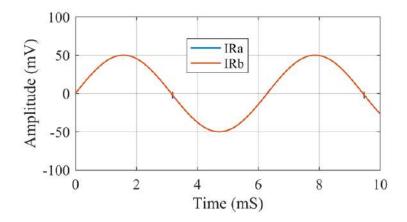

| 3.22 | Transient responses for current through $R_a$ and $R_b$                      |

| 3.23 | Simulated frequency responses of LPF for different multiplication fac-       |

|      | tors                                                                         |

| 3.24 | CFOA implementation of OTRA [33]                                             |

| 3.25 | Experimental frequency response of first-order low-pass filter 97            |

| 3.26 | Transient responses of first order low-pass filter                           |

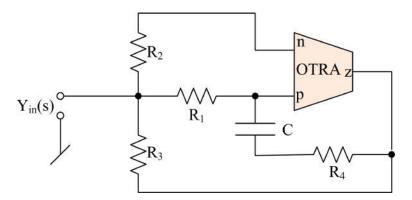

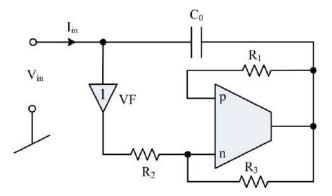

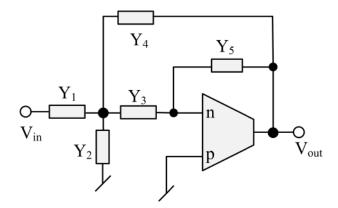

| 4.1  | Single OTRA-based generalized topology to realize first-order filters [1]104 |

| 4.2  | Single OTRA filter topology presented by Gocken and Cam $[7]$ 107            |

| 4.3  | Voltage-mode biquadratic filter configuration presented in $[9]$ 108         |

| 4.4  | OTRA based Sallen Key biquadratic filter configuration reported in           |

|      | [10]                                                                         |

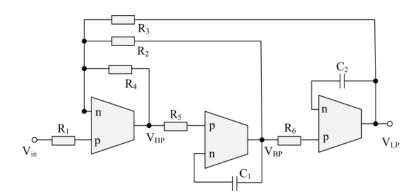

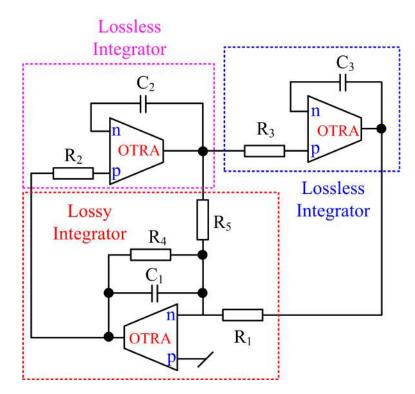

| 4.5  | KHN biquad using OTRAs presented by Soliman and Madian $\left[12\right]$ 109 |

| 4.6  | LP/BP filter employing two OTRAs [15]                                        |

| 4.7  | OTRA based universal filter presented in [18]                                |

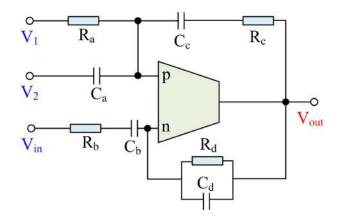

| 4.8  | Voltage mode MISO type universal filter configuration employing sin-         |

|      | gle OTRA [20]                                                                |

| 4.9  | OTRA based biquadratic filter presented in [25]                              |

| 4.10 | OTRA based third-order Chebychev lowpass filter configuration pre-                                                |

|------|-------------------------------------------------------------------------------------------------------------------|

|      | sented in [30]                                                                                                    |

| 4.11 | OTRA based third-order bandpass filter configuration presented in $[34]116$                                       |

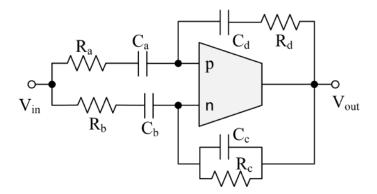

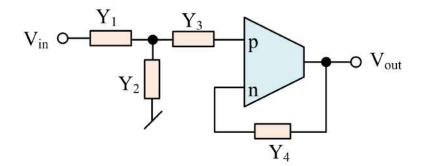

| 4.12 | Proposed filter configuration                                                                                     |

| 4.13 | CMOS realization of OTRA [41]                                                                                     |

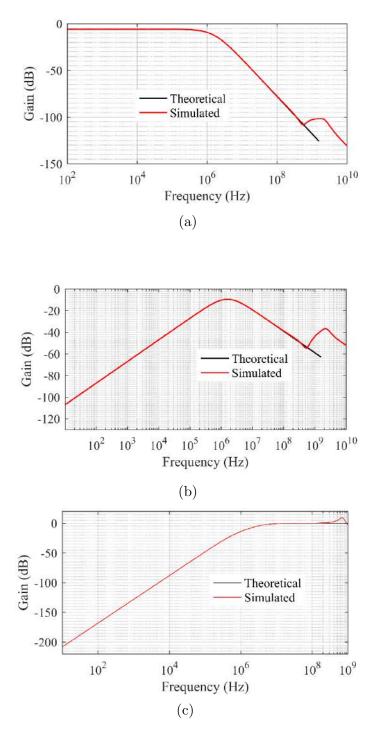

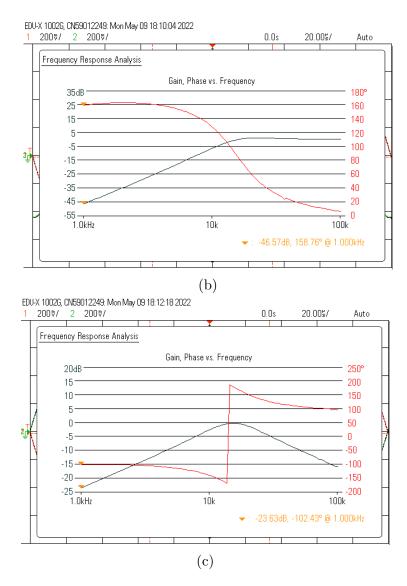

| 4.14 | (a) Gain Vs Frequency plot for LPF (b) Gain Vs Frequency plot for                                                 |

|      | BPF (c) Gain Vs Frequency plot for HPF                                                                            |

| 4.15 | (a) Time response of LPF (b) Time response of BPF (c) Time re-                                                    |

|      | sponse of HPF                                                                                                     |

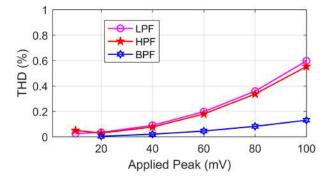

| 4.16 | Variations in THD with applied peak to peak input voltage 125                                                     |

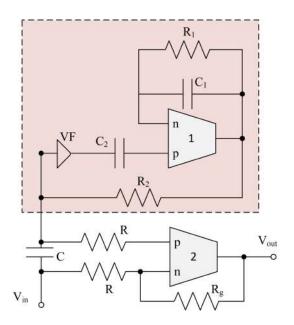

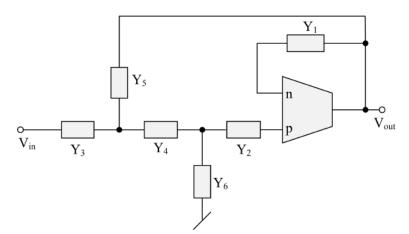

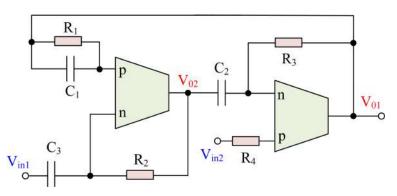

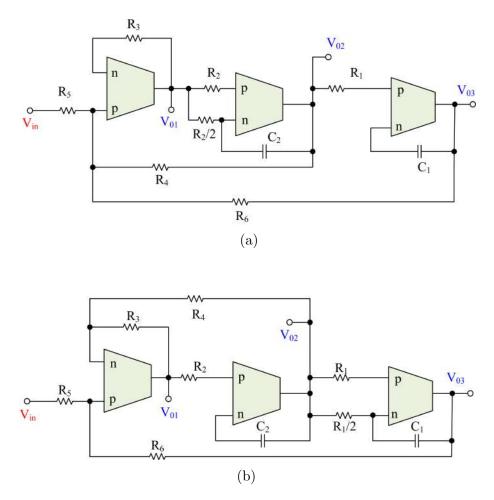

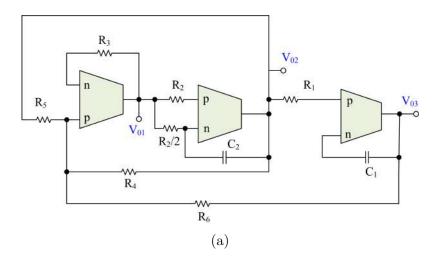

| 4.17 | Proposed single input multiple output filter configurations 126                                                   |

| 4.18 | Proposed quadrature sinusoidal oscillators                                                                        |

| 4.19 | CFOA implementation of OTRA                                                                                       |

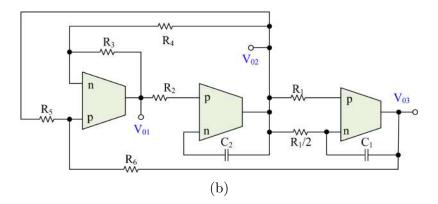

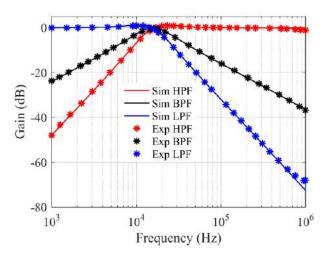

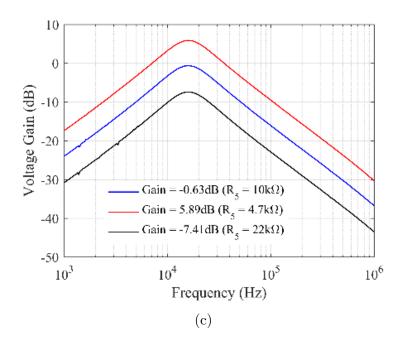

| 4.20 | Simulated and Experimental frequency responses of proposed filters $% \left( {{{\bf{n}}_{\rm{s}}}} \right)$ . 133 |

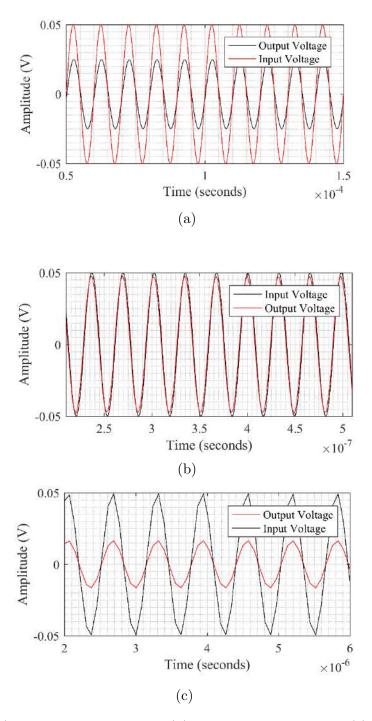

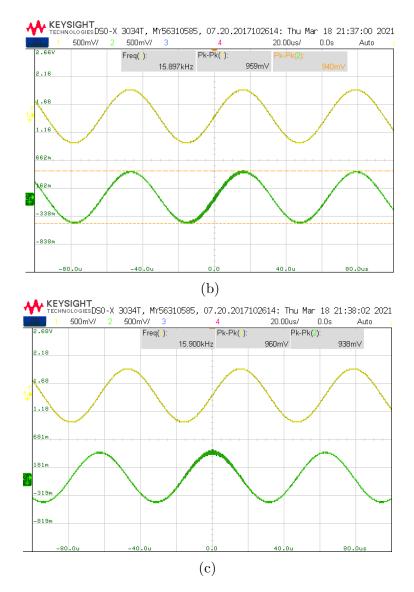

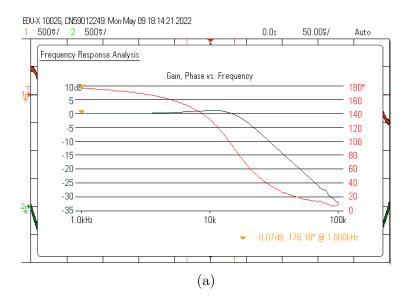

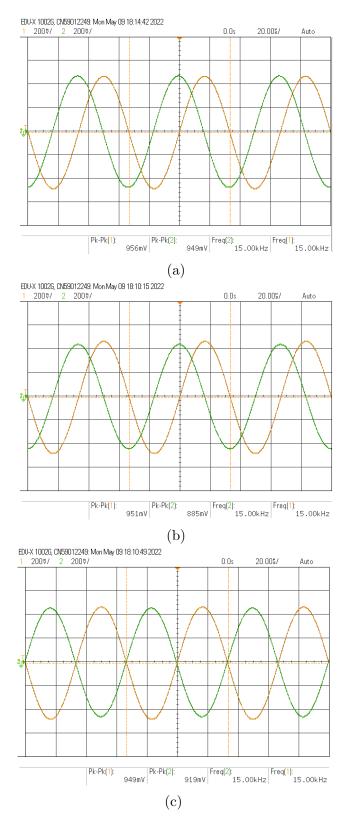

| 4.21 | (a) Transient input and output voltages of (a) HPF (b) BPF (c) LPF 134                                            |

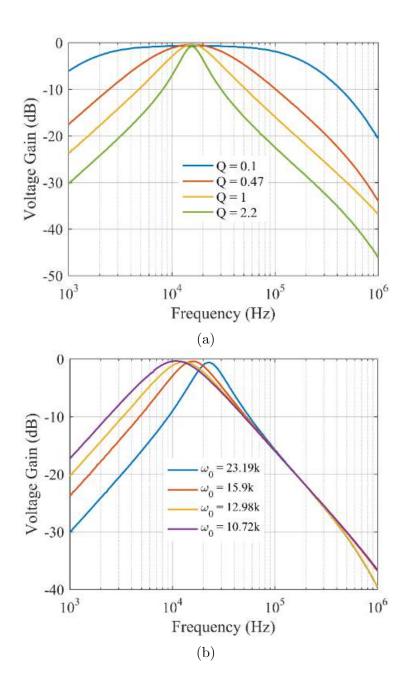

| 4.22 | (a) Tunability of Q with $\omega_0$ (b) Tunability of $\omega_0$ (c) Tunability of Gain 136                       |

| 4.23 | Frequency responses of the proposed filter shown in Fig. 4.18b (a)                                                |

|      | LPF (b) HPF (c) BPF                                                                                               |

| 4.24 | Time domain responses of the proposed filter shown in Fig. 4.18b (a) $(a)$                                        |

|      | LPF (b) HPF (c) BPF                                                                                               |

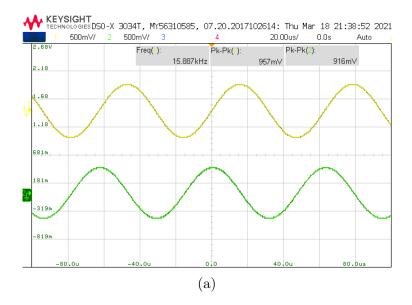

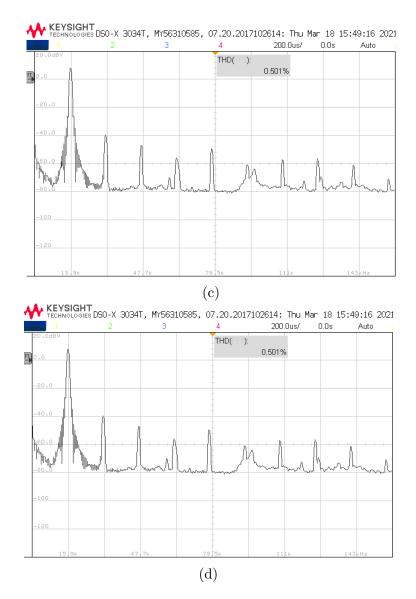

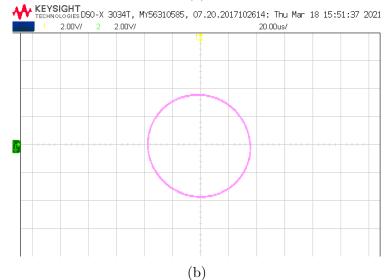

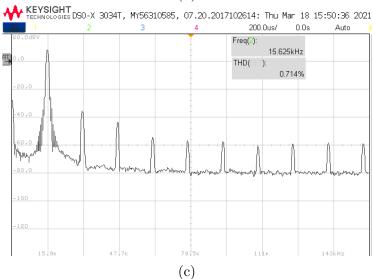

| 4.25 | (a) Experimental transient responses between quadrature voltage $V_{01}$                                          |

|      | and $V_{02}$ (b) Lissajous pattern (c) frequency spectrum of voltage $V_{01}$                                     |

|      | (d) Frequency spectrum of voltage $V_{02}$                                                                        |

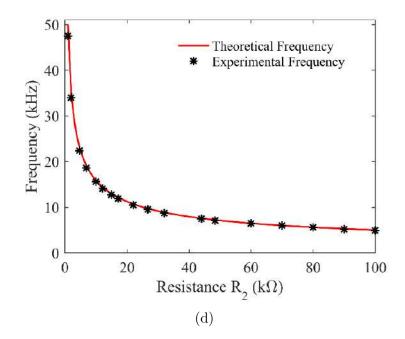

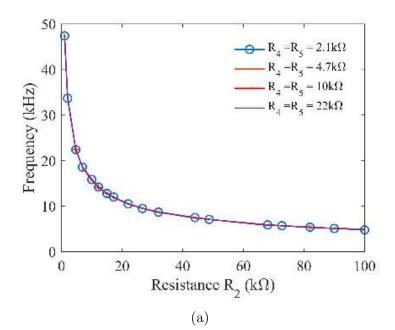

| 4.26 | (a) Experimental transient responses between quadrature voltage $V_{02}$                                          |

|      | and $V_{03}$ (b) Lissajous pattern (c) frequency spectrum of voltage $V_{03}$                                     |

|      | (d) Variation in frequency with resistor $R_2$                                                                    |

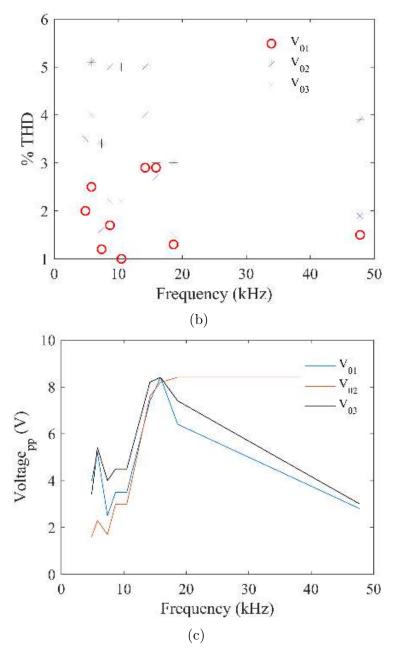

| 4.27 | (a) CO decoupled tuning of FO (b)Variation in THD with frequency                                                  |

|      | (c)<br>Variation in peak to peak voltage with frequency $\ldots$                                                  |

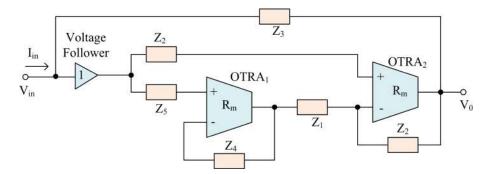

| 5.1  | TOQSO using OTAs reported by Prommee and Dehjan [2] 154                                                           |

| 5.2  | OTA-based TOQSOs reported by Bhaskar, Raj and Kumar [5] 155                        |

|------|------------------------------------------------------------------------------------|

| 5.3  | Four different configurations of TOQSOs employing CFOAs [8] 156                    |

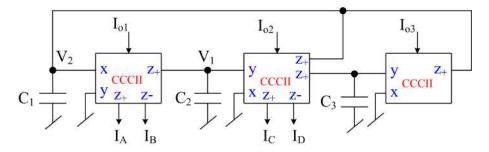

| 5.4  | Third-order sinusoidal oscillators using CCCIIs presented by Mahesh-               |

|      | wari [14]                                                                          |

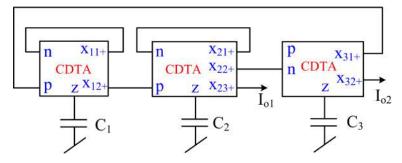

| 5.5  | Current mode TOQSO using CDTAs reported by Horng [22] 160                          |

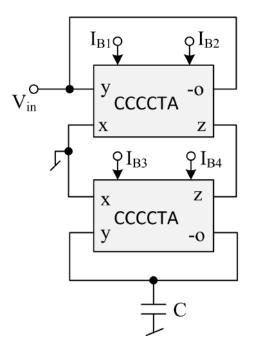

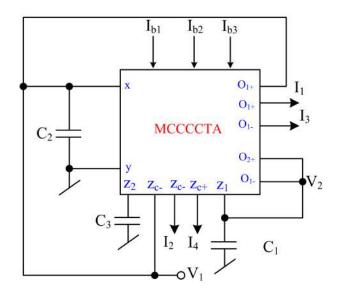

| 5.6  | Third-order quadrature sinusoidal oscillator using MCCCCTA pre-                    |

|      | sented by Kumngern and Chanwutitum [26]                                            |

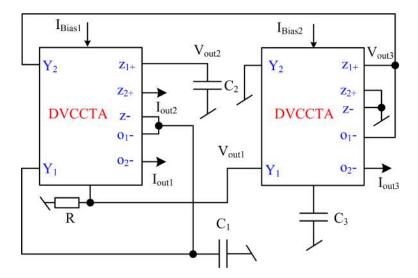

| 5.7  | Third-order quadrature sinusoidal oscillator using DVCCTAs pre-                    |

|      | sented by Pandey and Pandey [28]                                                   |

| 5.8  | Third-order sinusoidal oscillators employing OTRAs [42] $\ldots \ldots \ldots 166$ |

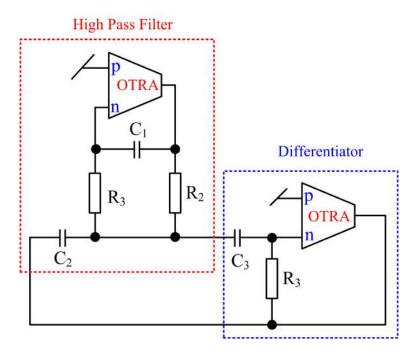

| 5.9  | Second order high pass filter and differentiator approach based TO-                |

|      | QSO using OTRAs [44]                                                               |

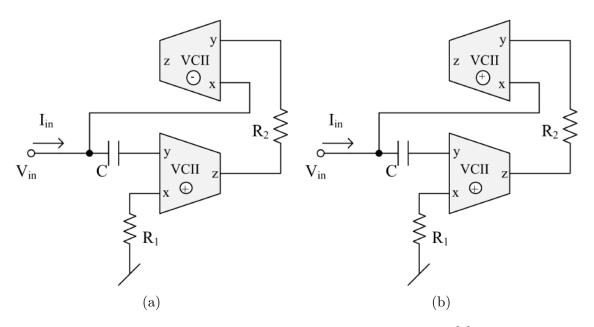

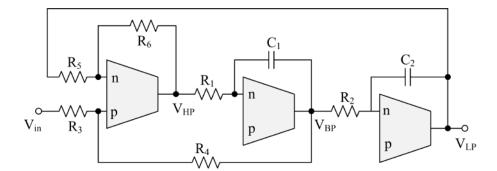

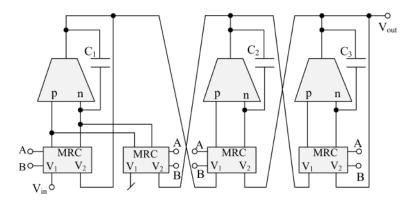

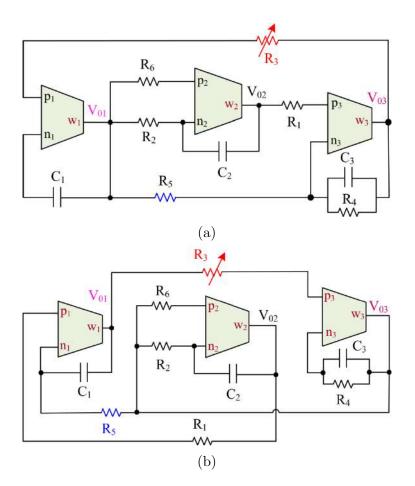

| 5.10 | Proposed new third order quadrature sinusoidal oscillator configurations 169       |

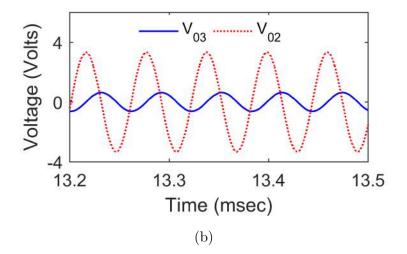

| 5.11 | Non-ideal model of OTRA implemented with AD844s [49] $\ldots \ldots 171$           |

| 5.12 | Implementation of OTRA using AD844 CFOAs                                           |

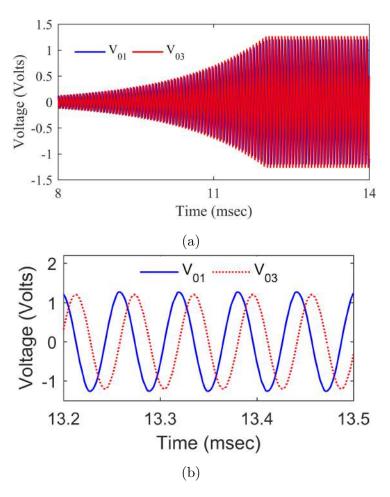

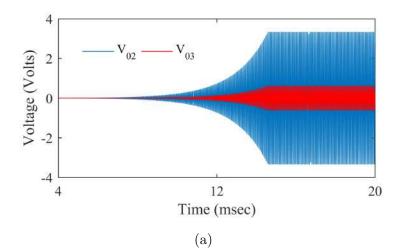

| 5.13 | Simulated transient and steady state responses of Fig. 5.10a $\ .$ 174             |

| 5.14 | Simulated transient and steady state responses of Fig. 5.10b $\ldots$ . 175        |

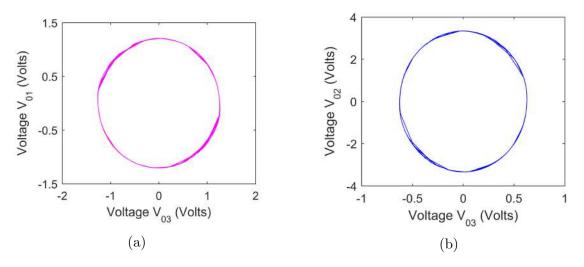

| 5.15 | Lissajous patterns of the proposed TOQSO (a)Fig. 5.10a, (b) Fig.                   |

|      | 5.10b                                                                              |

| 5.16 | Frequency spectrum of the proposed TOQSO (a)Fig. 5.10a, (b) Fig.                   |

|      | 5.10b                                                                              |

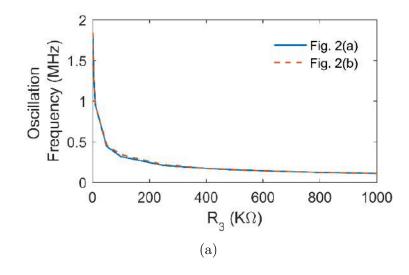

| 5.17 | Variation in frequency with resistor $R_3$ for both the proposed TOQ-              |

|      | SOs (b) %THD for the circuit shown in Fig. 5.10b                                   |

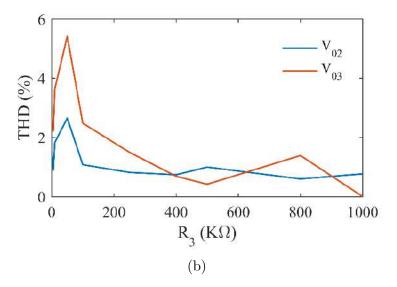

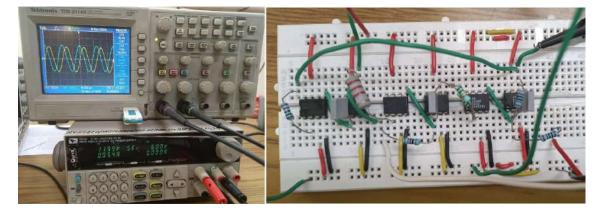

| 5.18 | Snapshot of the experimental set-up for Fig. 5.10b                                 |

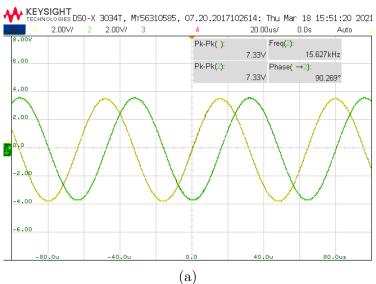

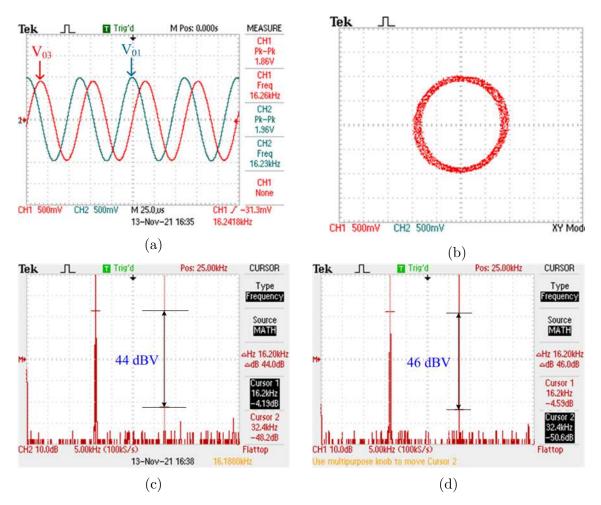

| 5.19 | Experimental results of Fig. 5.10 (a) Quadrature waveforms (b) Lis-                |

|      | sajous pattern (c) Frequency spectrum of $V_{01}$ and (d) Frequency spec-          |

|      | trum of $V_{03}$                                                                   |

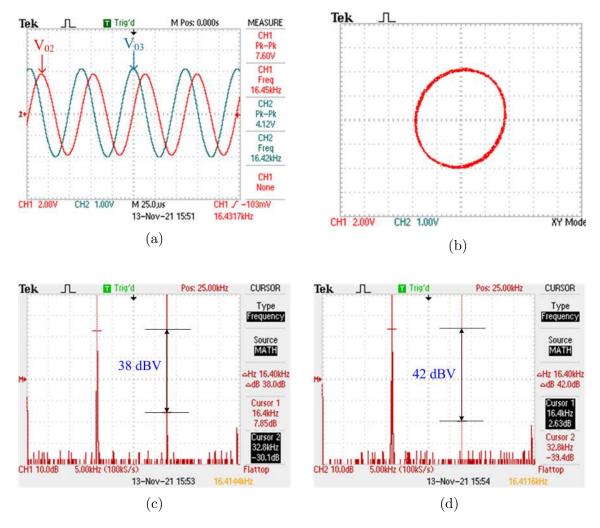

| 5.20 | Experimental results of Fig. 5.10b (a) Quadrature waveforms (b)                                                                                                                          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Lissajous pattern (c) Frequency spectrum of $V_{03}$ and (d) Frequency                                                                                                                   |

|      | spectrum of $V_{02}$                                                                                                                                                                     |

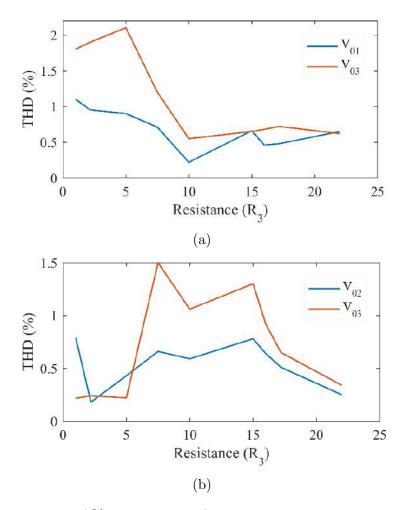

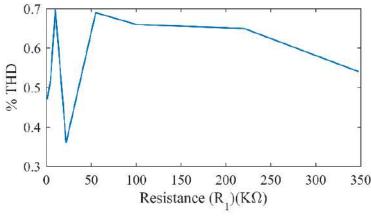

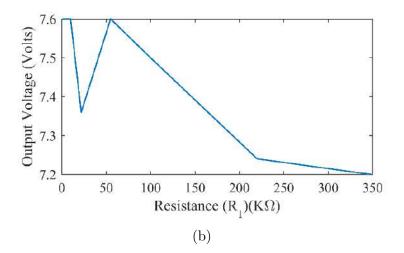

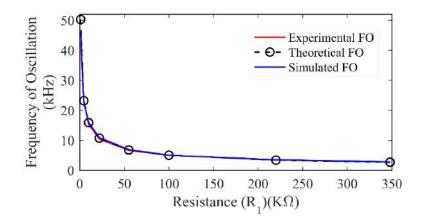

| 5.21 | Variation of %THD with $R_3$ for the quadrature output voltages for                                                                                                                      |

|      | the circuits of (a) Fig. 5.10a and (b) Fig. 5.10b $\ldots \ldots \ldots \ldots \ldots \ldots 180$                                                                                        |

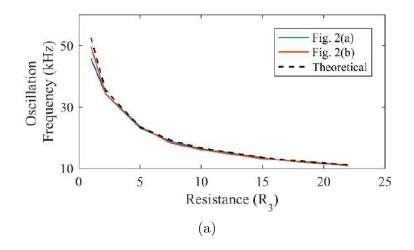

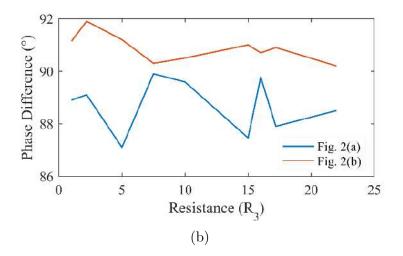

| 5.22 | (a) Variation in FO with resistor $R_3$ , (b) Phase difference between                                                                                                                   |

|      | the quadrature output voltages                                                                                                                                                           |

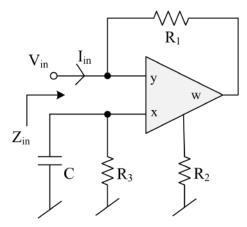

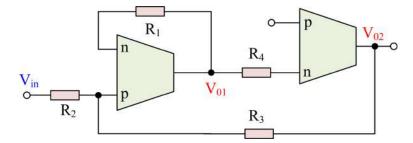

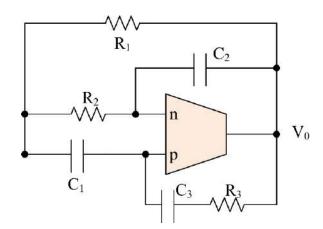

| 5.23 | Proposed third order sinusoidal oscillator configuration                                                                                                                                 |

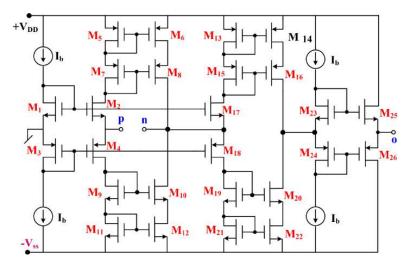

| 5.24 | CMOS OTRA                                                                                                                                                                                |

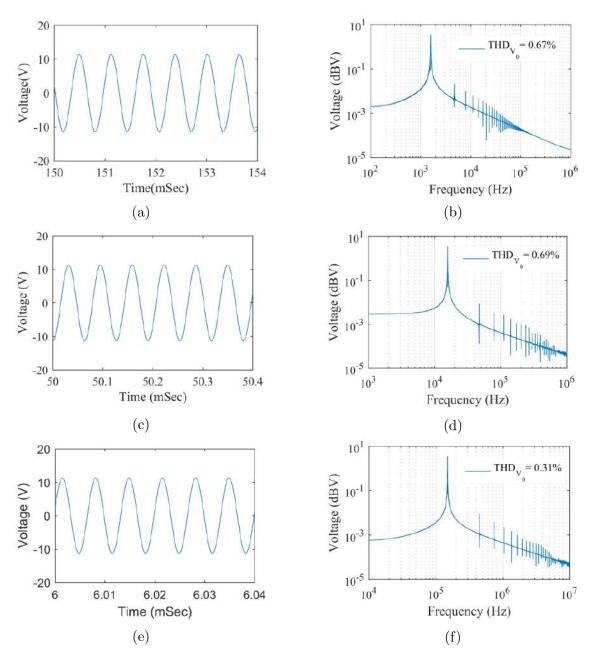

| 5.25 | Simulated steady state responses and their frequency spectra of the                                                                                                                      |

|      | circuit of Fig. 5.23                                                                                                                                                                     |

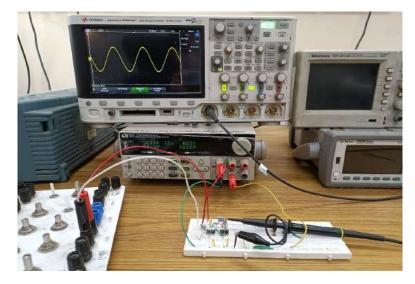

| 5.26 | Snapshot of the experimental set-up for Fig. 5.23                                                                                                                                        |

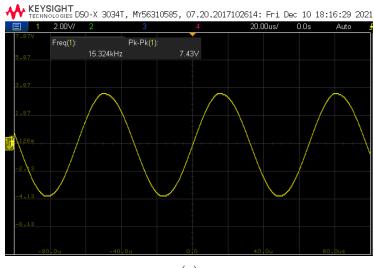

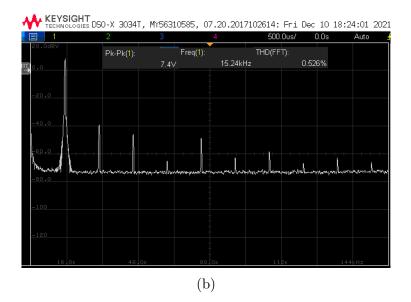

| 5.27 | Experimental results (a) time response of output voltage and (b) fre-                                                                                                                    |

|      | quency spectrum of the circuit of Fig. 5.23                                                                                                                                              |

| 5.28 | (a) Experimental variation of %THD with resistor $R_1$ (b) Experimen-                                                                                                                    |

|      | tal variation of output voltage with resistor $R_1 \ldots \ldots$ |

| 5.29 | Variation in FO for different values of resistor $R_1$                                                                                                                                   |

### List of Tables

| 1.1 | Aspect ratios of MOSFETs shown in Fig. 2.8                              |

|-----|-------------------------------------------------------------------------|

| 1.2 | Aspect ratios of MOSFETs shown in Fig. 1.7                              |

| 2.1 | Aspect ratios of MOSFETs shown in Fig. 2.8                              |

| 2.2 | Aspect ratios of MOSFETs shown in Fig. 2.17                             |

| 3.1 | Aspect ratios of MOSFETs shown in Fig. 3.10                             |

| 3.2 | Variation in capacitance with $R_2$                                     |

| 3.3 | Variation in capacitance with $V_{b2}$                                  |

| 4.1 | Aspect ratio of MOSFETs shown in Fig. 4.13                              |

| 4.2 | Sensitivities of filter parameters with respect to various passive com- |

|     | ponents                                                                 |

| 5.1 | Aspect ratios of MOSFETs shown in Fig. 5.24                             |

## List of Symbols

| $g_m$      | Transconductance           |  |

|------------|----------------------------|--|

| R          | Resistor                   |  |

| С          | Capacitor                  |  |

| $I_{Bias}$ | Bias Current               |  |

| ω          | Pole Frequency             |  |

| Q          | Quality Factor             |  |

| BW         | Bandwidth                  |  |

| Н          | Voltage Gain               |  |

| S          | Sensitivity                |  |

| Ω          | Ohm                        |  |

| $\mho$     | Mho                        |  |

| $g_p$      | Parasitic Transconductance |  |

| $R_p$      | Parasitic Resistance       |  |

| $C_p$      | Parasitic Capacitance      |  |

| $r_o$      | Output Resistance          |  |

| $C_o$      | Output Capacitance         |  |

| $\phi$     | Phase                      |  |

| $S^F$      | Stability Factor           |  |

| $I_D$    | Drain Current                        |

|----------|--------------------------------------|

| $V_{DS}$ | Drain to Source Voltage              |

| $V_{GS}$ | Gate to Source Voltage               |

| $V_{TH}$ | Threshold Voltage                    |

| $\mu_n$  | Surface Mobility                     |

| $C_{ox}$ | Gate Oxide Capacitance per Unit Area |

| W        | Width                                |

| L        | Length                               |

### List of Abbreviations

| ABB      | Active Building Block                                            |  |

|----------|------------------------------------------------------------------|--|

| IC       | Integrated Circuit                                               |  |

| Op-Amp   | Operational Amplifier                                            |  |

| ОТА      | Operational Transconductance Amplifier                           |  |

| CC       | Current Conveyor                                                 |  |

| CCII     | Second Generation Current Conveyor                               |  |

| MOCCCII  | Multiple Outputs Current Controlled Conveyor                     |  |

| DO-CCCII | Dual Output Current Controlled Current Conveyor                  |  |

| DDCC     | Differential Difference Current Conveyor                         |  |

| FDCCII   | Fully Differential Current Conveyor                              |  |

| DVCC     | Differential Voltage Current Conveyor                            |  |

| CFOA     | Current Feedback Operational Amplifier                           |  |

| FTFN     | Four Terminal Floating Nullors                                   |  |

| VDTA     | Voltage Differencing Transconductance Amplifier                  |  |

| CDTA     | Current Differencing Transconductance Amplifier                  |  |

| CCCCTA   | Current Controlled Current Conveyor Transconductance Amplifier   |  |

| DVCCTA   | Differential Voltage Current Conveyor Transconductance Amplifier |  |

| CFTA     | Current Follower Transconductance Amplifier                      |  |

| CDCTA                                         | Current Differencing Cascaded Transconductance Amplifier                                                                                                          |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MCCTA                                         | Modified Current Conveyor Transconductance Amplifier                                                                                                              |  |

| MISO                                          | Multiple-Input Single-Output                                                                                                                                      |  |

| A/D                                           | Analog to Digital Converter                                                                                                                                       |  |

| D/A                                           | Digital to Analog Converter                                                                                                                                       |  |

| VM                                            | Voltage Mode                                                                                                                                                      |  |

| $\mathcal{CM}$                                | Current Mode                                                                                                                                                      |  |

| TRM                                           | Transresistance Mode                                                                                                                                              |  |

| TCM                                           | Transconductance Mode                                                                                                                                             |  |

| TOQSO                                         | Third Order Quadrature Sinusoidal Oscillator                                                                                                                      |  |

| BJT                                           | Bipolar Junction Transistor                                                                                                                                       |  |

|                                               |                                                                                                                                                                   |  |

| MOSFET                                        | Metal Oxide Semiconductor Field Effect Transistor                                                                                                                 |  |

| MOSFET<br>CMOS                                | Metal Oxide Semiconductor Field Effect Transistor<br>Complementary Metal Oxide Semiconductor                                                                      |  |

|                                               |                                                                                                                                                                   |  |

| CMOS                                          | Complementary Metal Oxide Semiconductor                                                                                                                           |  |

| CMOS<br>GC                                    | Complementary Metal Oxide Semiconductor<br>Grounded Capacitor                                                                                                     |  |

| CMOS<br>GC<br>LPF                             | Complementary Metal Oxide Semiconductor<br>Grounded Capacitor<br>Low Pass Filter                                                                                  |  |

| CMOS<br>GC<br>LPF<br>HPF                      | Complementary Metal Oxide Semiconductor<br>Grounded Capacitor<br>Low Pass Filter<br>High Pass Filter                                                              |  |

| CMOS<br>GC<br>LPF<br>HPF<br>BPF               | Complementary Metal Oxide Semiconductor<br>Grounded Capacitor<br>Low Pass Filter<br>High Pass Filter<br>Band Pass Filter                                          |  |

| CMOS<br>GC<br>LPF<br>HPF<br>BPF<br>BRF        | Complementary Metal Oxide Semiconductor<br>Grounded Capacitor<br>Low Pass Filter<br>High Pass Filter<br>Band Pass Filter<br>Band Reject Filter                    |  |

| CMOS<br>GC<br>LPF<br>HPF<br>BPF<br>BRF<br>APF | Complementary Metal Oxide Semiconductor<br>Grounded Capacitor<br>Low Pass Filter<br>High Pass Filter<br>Band Pass Filter<br>Band Reject Filter<br>All Pass Filter |  |

# Chapter 1 Introduction

This thesis deals with "Realization of some analog signal processing/generation circuits employing operational transresistance amplifiers". Novel signal processing/generation circuits in voltage mode (VM) employing operational transresistance amplifiers (OTRAs) having several advantageous features not available simultaneously in circuit structures known earlier have been proposed.

Analog signal is basically a continuous time signal. Most of the signals encountered in real world are analog in nature. That is, the signals are function of a continuous variable, such as time or space, and usually take on values in a continuous range. Such signals may be processed directly by appropriate analog systems (such as filters or frequency analyzers) or frequency multipliers for the purpose of changing their characteristics or extracting some desired information.

The integrated circuit (IC) op-amp, though quite versatile, has few major limitations such as, constant and finite gain bandwidth product, slewing at high frequency (because of finite slew rate). Also, in many applications, the op-amp based designs require passive component matching constraints and, also, the number of components required is not canonic. To overcome the limitations of conventional op-amp circuits, several alternative new analog active building blocks (ABBs) have been proposed from time to time during the past four decades by researchers and circuit designers. Basically, Op-amp is a voltage controlled voltage source i.e., it has voltage output which depends on the differential voltage available at its input terminals. Almost all the active devices implement one of the following controlled sources namely, voltage controlled voltage source (VCVS), voltage controlled current source (VCCS), current controlled voltage source (CCVS) and current controlled current source (CCCS). Based on the classification of these controlled sources, there can be four modes of operation of the circuit namely, voltage mode, current mode, transimpedance mode and transconductance mode. A very comprehensive review of numerous active building blocks, along with a unified framework for development of new active building blocks with different features, has been presented by **Biolek**, **Senani**, **Biolkova** and **Kolka** in [1].

The input source of any amplifier is never ideal, having ideally zero (for voltage source) or infinite (for current source) output resistance. Similarly, the load on any amplifier can range from very low to very high. The circuit designer must have the option of choosing from any one of the following amplifiers (controlled sources):

#### 1. Voltage-controlled voltage source

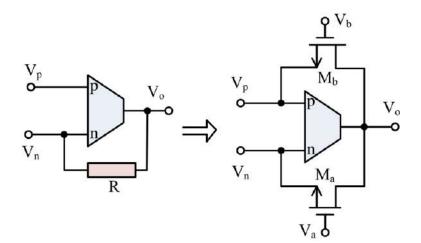

If the input source has a very low output impedance and the load impedance is very high, the amplifier must have very high input impedance (ideally infinite) and very low output impedance (ideally zero). This requirement is met by a voltage amplifier/ voltage controlled voltage source (VCVS). The active devices that come under this category have voltage as input and provide voltage output. Hence, they have a high input impedance and ideally zero output impedance. For example traditional operational amplifier, differential difference amplifier (DDA), voltage differencing buffered amplifier (VDBA), voltage differencing inverted buffered amplifier (VDIBA), etc. comes under this category.

#### 2. Voltage-controlled current source

If the input source has a very low output impedance and the load impedance is very low, the amplifier must have very high input impedance as well as very high output impedance. This requirement is met by a transconductance amplifier/ voltage controlled current source (VCCS). These devices operate at an input voltage and provide current output. They have a high input resistance and high output resistance. The operational transconductance amplifier (OTA), voltage differencing transconductance amplifier (VDTA), voltage differencing current conveyor (VDCC), etc is an example of this type of active device.

#### 3. Current-controlled current source

If the input source has a very high output impedance and the load impedance is very low, the amplifier must have very low input impedance (ideally zero) and very high output impedance (ideally infinite). This requirement is met by a current amplifier/ current controlled current source (CCCS). These devices are controlled by input current and have current outputs. Hence they exhibit ideally zero input impedance and very high output impedance. The most commonly used active devices under this category is the current-conveyor (CC), current differencing transconductance amplifier (CDTA), current differencing current conveyor (CDCC), dual X current conveyor transconductance amplifier (DXCCTA), current differencing cascaded transconductance amplifier (CDCTA), current controlled transconductance amplifier (CCTA), etc.

#### 4. Current-controlled voltage source

If the input source has a very high output impedance and the load impedance is very high, the amplifier must have very low input impedance as well as a low output impedance. This requirement is meant by a transresistance amplifier/ current controlled voltage source (CCVS).Here the input is a current source while at output voltage is produced. They have ideally zero input as well as output impedance. Current differencing buffered amplifier (CDBA), current differencing differential input buffered amplifier (CDDIBA), current differencing differential output buffered amplifier (CDDOBA), current differencing operational amplifier (CDOA), etc. are an example of this type of source. Operational transresistance amplifier (OTRA) is an active device that falls under this category, which has an ideally zero input and output impedances.

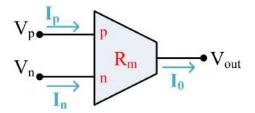

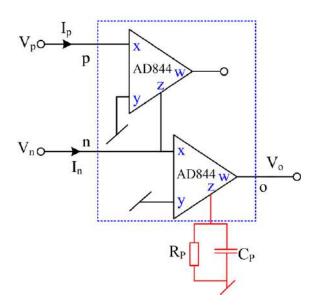

Over the past few years, numerous analog signal processing and generation circuits have been developed using an ABB called Operational transresistance amplifier (OTRA). OTRA is a differential current controlled voltage source characterised by ideally zero input impedance and zero output impedance. Because of the presence of virtual ground at the input terminals, the effect of parasitics is removed at the input terminals of OTRA due to which OTRA has received prominent attention in the design of filters, oscillators and non-linear analog applications. Also, its low output impedance facilitates easy cascadability. The symbolic representation of OTRA has been depicted in Fig. 1.1.

Figure 1.1: Symbolic notation of OTRA

OTRA is a three terminal active device having ideally zero input and zero output impedance. The characterizing terminal equations of an OTRA can be expressed in the matrix form as:

$$\begin{bmatrix} V_p \\ V_n \\ V_{out} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 0 & 0 \\ R_m & -R_m & 0 \end{bmatrix} \begin{bmatrix} I_p \\ I_n \\ I_{out} \end{bmatrix}$$

(1.1)

Thus, from equation (1.1), the output voltage  $(V_{out})$  of the OTRA can be written

as:

$$V_{out} = R_m (I_p - I_n) \tag{1.2}$$

where  $R_m$  is transresistance gain of OTRA whose ideal value is infinite. Whenever an appropriate negative feedback is present between output and the input terminals, thus forcing the device to operate in linear region, the very high value of  $R_m$  (ideally infinite) forces the differential input currents to zero. In any real implementation, however,  $R_m$  is a function of frequency, usually represented by a single pole model, as given in equation (1.3):

$$R_m(s) = \frac{R_0}{1 + \frac{s}{\omega_0}} \tag{1.3}$$

where  $R_0$  is dc transresistance gain and  $\omega_0$  is the angular pole frequency of first pole of OTRA.

#### Various Realizations of OTRA

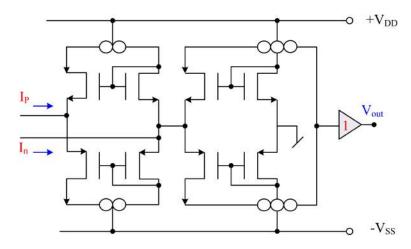

In 1992, **Chen**, **Tsao** and **Chen** proposed Operational Transresistance Amplifier (OTRA) as a versatile active building block and gave its first CMOS realization [2]. The structure was based on implementing the current-differencing operation by current mirrors as shown in Fig. 1.2.

Figure 1.2: CMOS representation of OTRA proposed by Chen, Tsao and Chen [2]

On the other hand, in 1999 Salama and Soliman in [3] presented a different CMOS realization of OTRA that is based on the cascaded connection of a modified differ-

ential current conveyor architecture to provide current-differencing operation where a common source amplifier has been used to provide high gain.

Figure 1.3: CMOS representation of OTRA presented by Salama and Soliman [3]

A bipolar representation of the OTRA has been presented by **Barthelemy, Koudobine** and **Van Landegehem** in [4]. The proposed circuit has a positive first generation current conveyor as the input stage followed by a translinear voltage follower.

**Ravindran, Savla, Younus** and **Ismail** in [5] have presented a low-voltage CMOS OTRA that employs low-voltage regulated cascode current mirror with a low-voltage regulated cascode load.

**Duruk** and **Kuntman** in [6] proposed a differential OTRA topology that can operate at very low power supply voltages where the basic input cell consists of class AB current mirror connection.

Another low voltage CMOS differential OTRA suitable for operation in sub-micron technologies has been presented by **Duruk**, **Gunes** and **Kuntman** in [7]. Its basic cell consists of six transistors, which form a low-voltage current mirror topology  $(M_1-M_6)$ .

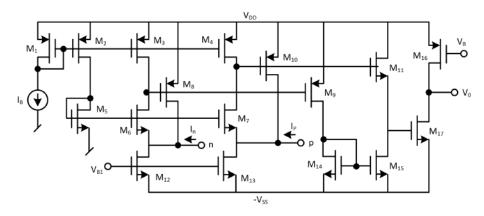

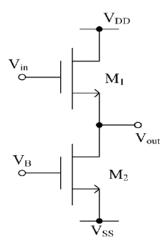

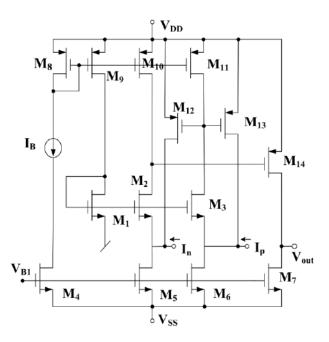

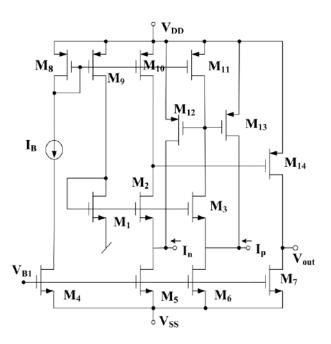

A structure that is most commonly used by others in realizing their OTRA based applications is the one presented by **Mostafa** and **Soliman** in 2006 [8], as shown in

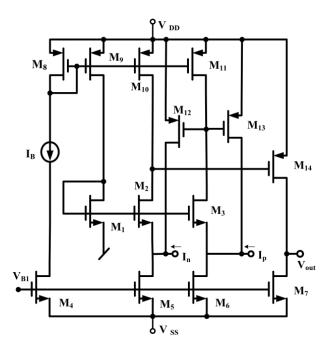

Figure 1.4: CMOS representation of OTRA [8]

Fig.1.4. It is based on the cascaded connection of the modified differential current conveyor and a common source amplifier, but comparatively, has smaller number of current mirrors than the OTRA presented in [3]. Assuming that each group of transistors (M1-M3), (M5 and M6), (M8-M11) and (M12 and M13) are matched and all the transistors operate in the saturation region, the circuit operation can be explained as follows. The current mirrors formed by (M8-M11) forces equal currents  $(I_B)$  in the transistors M1, M2 and M3 and thereby making their gate to source voltages equal and thus virtually grounding the input terminals. The current mirrors formed by the transistor pairs (M10 and M11) and (M12 and M13) provide the current differencing operation, while the common source amplifier (M14) achieves the high gain stage. The aspect ratios of the MOSFETs used in Fig. 1.4 are given in Table 1.1.

| MOSFETs                      | Aspect Ratio (W/L) in $\mu m$ |

|------------------------------|-------------------------------|

| $M_1 - M_3, M_{12} - M_{13}$ | 36/0.9                        |

| $M_4, M_7$                   | 3.6/0.9                       |

| $M_5, M_6$                   | 10.8/0.9                      |

| $M_8 - M_{11}$               | 18/0.9                        |

| $M_{14}$                     | 18/0.18                       |

Table 1.1: Aspect ratios of MOSFETs shown in Fig. 2.8

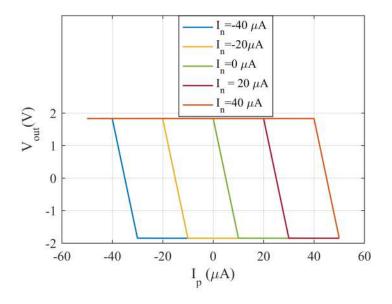

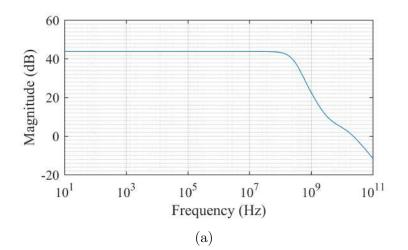

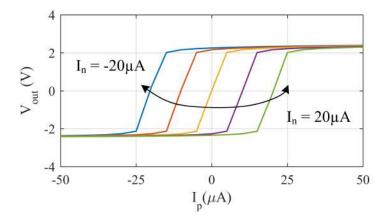

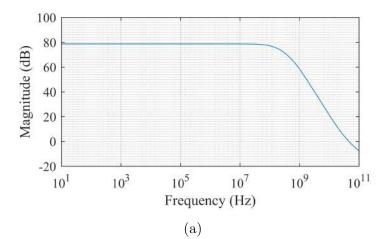

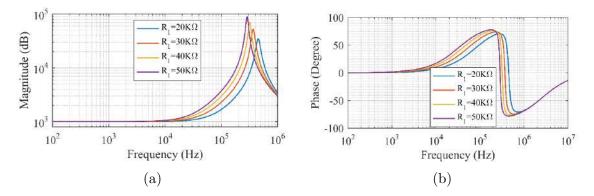

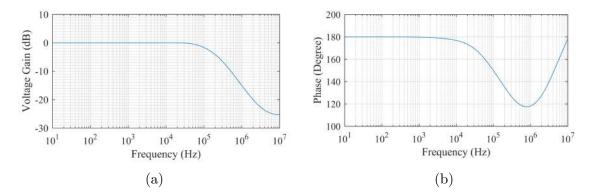

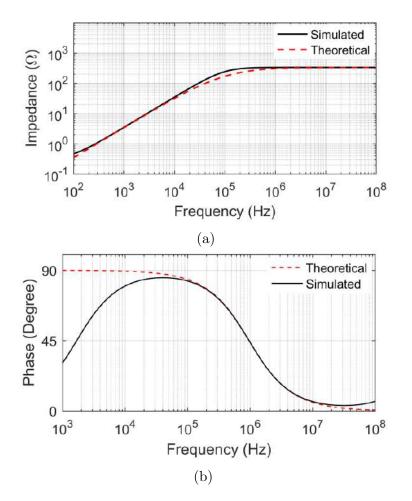

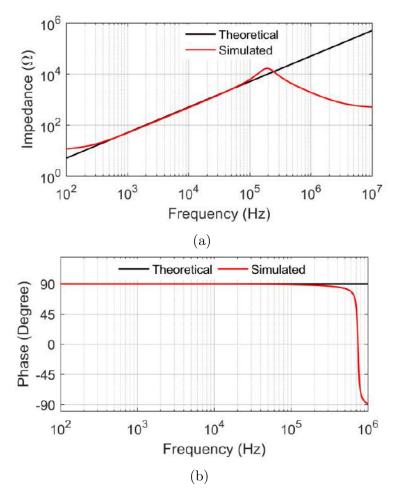

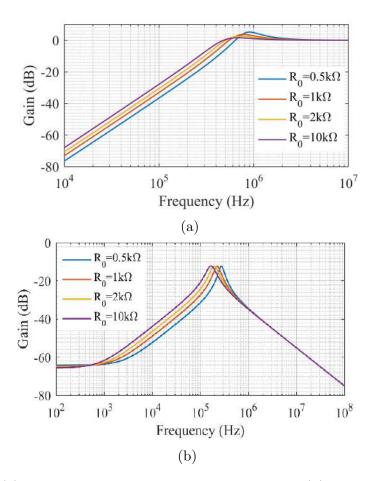

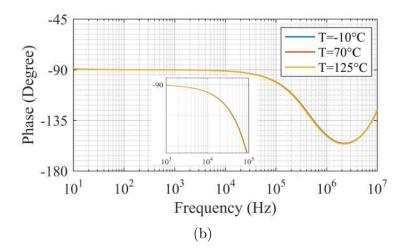

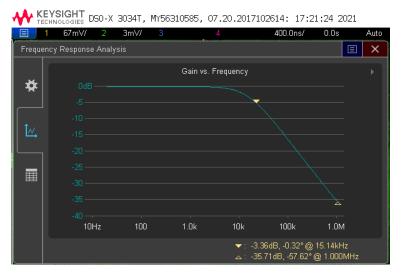

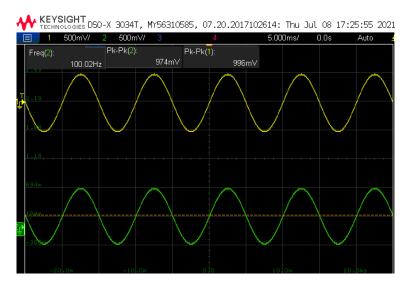

The DC transfer characteristic of Fig. 1.4 is shown in Fig. 1.5. The frequency responses of magnitude and phase of the OTRA have been displayed in Fig. 1.6.

Figure 1.5: DC characteristic of the OTRA

Figure 1.6: Frequency responses of magnitude and phase of an OTRA

A high open-loop transresistance gain OTRA has been reported by **Kafrawy** and **Soliman** in [9] that is based on the same input stage as in [8] while a differential gain stage is used instead of a common source amplifier and a compensation circuit is used to compensate the difference between the two drain voltages of the transistors  $M_2$  and  $M_3$ .

**Obaid**, **Tayyab** and **Chaudhary** in [10] have proposed a CMOS differential OTRA, that is a high open-loop gain differential OTRA employing a differential gain stage. This low-power wide-band OTRA is based upon a common source amplifier and a cascaded connection of the modified differential current conveyor (MDCC).

A modified representation of CMOS OTRA, has been presented by **Kafraway** and **Soliman** in [11], that is capable of providing two complementary voltage outputs by employing a differential gain stage instead of the common source amplifier as the output stage as given in [8].

A new approach to design a field-programmable CMOS OTRA has been presented by **Mittal, Kapur, Markan** and **Pyara** in [12], where all the MOSFETs have been replaced by floating gate MOSFETs to make the OTRA design programmable. Another CMOS architechture of OTRA using the sub-micron technology has been presented by **Pawade** and **Ghongade** in [13]

A gain tunable and low-power OTRA circuit based on FGMOS has been proposed by **Prasad, Gautam** and **Aggarwal** in [14] by replacing some of the MOSFETs in the conventional OTRA circuit of Mostafa and Soliman by two-input floating gate MOSFETs.

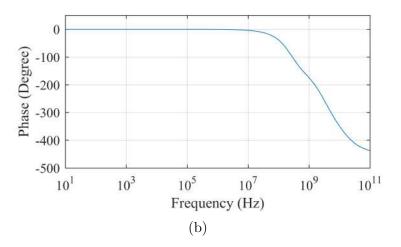

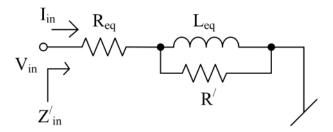

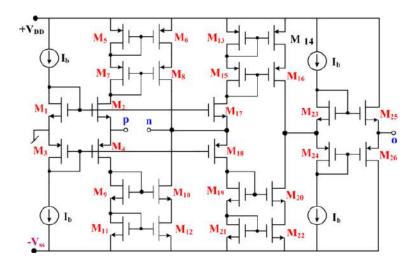

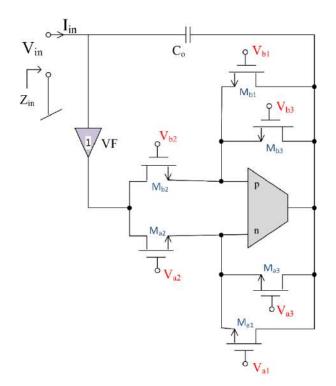

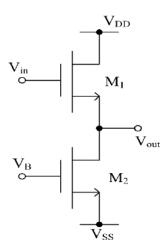

A CMOS implementation of OTRA, used in the present work apart from the CMOS implementation presented in [8] employing a current differencing unit and a translinear buffer [15] is shown in Fig. 1.7.

In Fig. 1.7, the current-differencing unit consists of two translinear voltage buffers formed by (M1-M4) and (M1,M3,M17,M18). The input terminals of both the buffers has been grounded resulting in a virtual ground at the p and n terminals. Furthermore, the cascode current mirrors formed by transistors  $(M_5 - M_8)$ ,  $(M_9 - M_{12})$ ,  $(M_{13} - M_{16})$  and  $(M_{19} - M_{23})$  provide high output impedance. The aspect ratios of MOSFETs used in Fig. 1.7 are given in Table 1.2.

| MOSFETs                            | Aspect Ratio (W/L) in $\mu m$ |

|------------------------------------|-------------------------------|

| $M_1, M_2, M_{17}, M_{23}, M_{25}$ | 50/0.5                        |

| $M_3, M_4, M_{18}, M_{24}, M_{26}$ | 100/0.5                       |

| $M_5 - M_{16}, M_{19} - M_{22}$    | 3.33/0.5                      |

Table 1.2: Aspect ratios of MOSFETs shown in Fig. 1.7

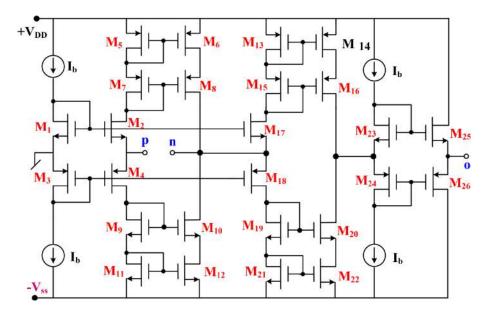

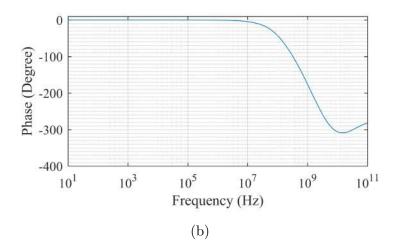

The DC characteristic and frequency responses of gain and phase of the OTRA shown in Fig. 1.7 are shown in Figs. 1.8 and 1.9 respectively.

Figure 1.7: CMOS representation of OTRA derived from [15]

Figure 1.8: DC characteristic of the OTRA presented in [15]

Figure 1.9: Frequency responses of magnitude and phase of an OTRA of [15]

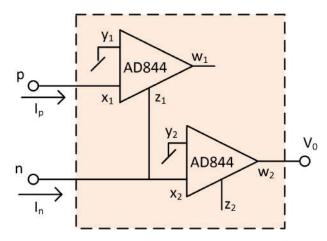

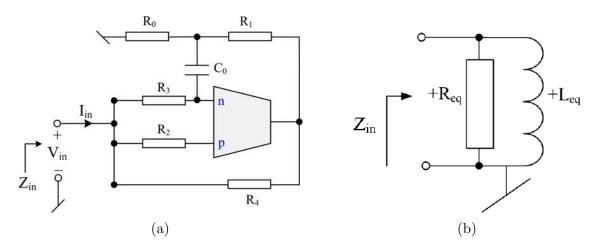

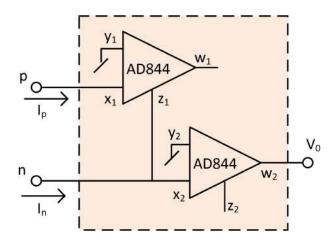

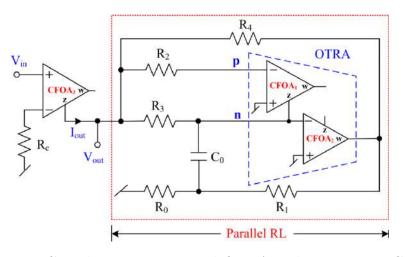

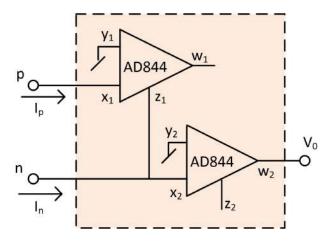

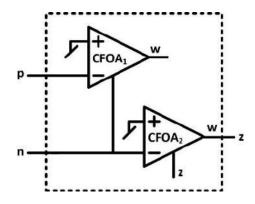

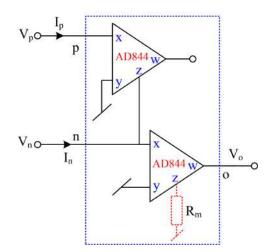

As of now, no integrated OTRA circuit has been made commercially available as an off-the-shelf IC. However, in practice, an alternate realization of OTRA is using the commercially available ICs (AD844) [16] the implementation of which has been displayed in Fig. 1.10.

Figure 1.10: OTRA realized using commercially available CFOA ICs [16]

#### Various Applications of OTRA

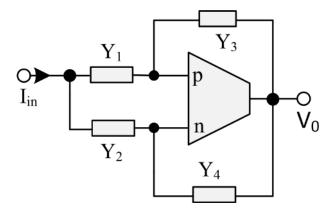

Numerous applications of OTRA and its various derivatives in analog signal processing and generation viz filters, oscillators/quadrature oscillators, simulated impedances and various non-linear functions have been reported in [17–129]. In the area of simulated impedance realization, the OTRA based circuits known so far can be broadly classified as grounded lossy inductance simulators [17–21], lossless grounded inductor simulators [22–27] and generalized impedance simulators [28–30, 32]. On the other hand, only one capacitance multiplier circuit using OTRA is available in the open literature [32].

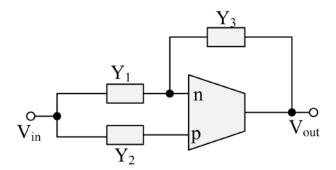

OTRA has been extensively used in the realization of continuous time filters. These filters can be broadly categorised depending on the order of the filter like first order filters [31, 33–37, 130], second-order filters [19, 38–58], third and higher order filters [59–71]. Recently, some fractional order and shadow filters have also been reported using OTRA [72–76]. The available second-order filters can further be classified as single-input-single-output (SISO) [38–42], single-input-multiple-output (SIMO) [19, 44–52], multiple-input-single-output (MISO) [53–57] and multiple-input-multipleoutput (MIMO)[58] type filters.

Sinusoidal oscillators using OTRA have also been a topic of extensive research as is evident from the available literature [16, 19, 77–103]. These oscillators can be classified as second order [19, 77–87, 89, 90, 93], third order [16, 88, 90–92, 94–98] and fractional order [99–101]. Multiphase sinusoidal oscillators using OTRA are also available in the literature [102, 103].

Interesting applications of the OTRA have been demonstrated in [104–113], in realizing a variety of relaxation oscillators and non-sinusoidal waveform generators.

Numerous other applications of OTRA like design of PD and PID controllers, precision rectifiers, analog multipliers, etc. have been given in [111, 114–129].

From a detailed perusal of the OTRA-based analog signal processing and generation circuits available in the open literature, it has been found that:

(i) No lossy series immittance simulator using OTRA is available in the literature.

- (ii) No single OTRA-based grounded lossy inductor circuit has been reported so far which can provide independent tunability of inductance with a single resistor without affecting its equivalent resistance and also utilizing the intrinsic property of the OTRA.

- (iii) No single OTRA-based capacitance multiplier circuit is available that is capable of realizing both positive as well as negative multiplication factors by changing the value of resistance used.

- (iv) No single OTRA-based second order filter configuration is present that employs canonic number of passive components while fully utilising the intrinsic property of the OTRA and without imposing any component matching constraints.

- (v) No third order quadrature sinusoidal oscillators based on OTRAs have been reported in the open literature so far, which can provide independent tunability of CO and FO utilizing intrinsic property of OTRA.

- (vi) No single OTRA-based third order sinusoidal oscillator employing canonic number of components have been presented that can provide independent tunability of CO and FO utilizing intrinsic property of OTRA.

Thus, the main objective of this work is to add new circuits with above mentioned features to the existing repertoire of the OTRA-based analog signal processing and generation circuits while fully utilising the intrinsic property of the OTRA.

The work presented in the thesis has been organized as follows:

In Chapter 2, we present two new grounded lossy inductor circuits employing OTRA along with some passive components. The first configuration is a new grounded series RL simulator configuration employing single OTRA, one voltage buffer, two

capacitors and two resistors. The designed inductance can be independently tuned without affecting the equivalent resistance. The second configuration is a new single OTRA-based grounded parallel immittance simulator (GIS) which has independent control on the value of the realized inductance while fully utilising the input terminals of the OTRA.

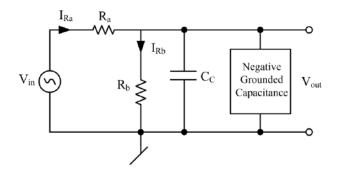

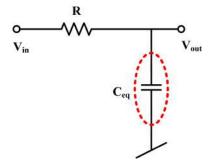

In Chapter 3, a new topology of a lossless grounded capacitance multiplier circuit using an OTRA, a voltage follower (VF), one capacitor and three (virtually grounded) resistors is presented. The proposed circuit is capable of realizing both positive as well as negative capacitance multiplication factors by changing the value of resistances used.

In **Chapter 4**, new biquad filter configurations employing OTRAs have been presented. The first circuit presents a single OTRA-based second order filter configuration employing canonic number of capacitors and relatively lower number of resistors as compared to previously reported filters utilising the intrinsic property of the OTRA without imposing any component matching constraints. In addition, two new structures of SIMO type biquad filter employing OTRAs have also been presented which realize a low pass filter (LPF), high pass filter (HPF) and band pass filter (BPF). Furthermore, the realized filters can easily be modified into quadrature sinusoidal oscillators capable of generating low frequency sinusoids with fully uncoupled condition and frequency of oscillation.

**Chapter 5** presents third order oscillators employing OTRAs. Two new TOQ-SOs employing OTRAs that can provide independent tunability of CO and FO utilizing intrinsic property of OTRA have been presented first. Afterwards, a single OTRA-based third order sinusoidal oscillator configuration with canonic number of passive components is also presented, that has independent tunability of CO and FO, under the equality of capacitance constraints.

Chapter 6 of the thesis presents a summary of the work presented and some suggestions for the further work.

## Bibliography

- D. Biolek, R. Senani, V. Biolkova, and Z. Kolka, "Active elements for analog signal processing: classification, review, and new proposals," *Radioengineering*, vol. 17, no. 4, pp. 15–32, 2008.

- [2] J.-J. Chen, H.-W. Tsao, and C.-C. Chen, "Operational transresistance amplifier using CMOS technology," *Electronics Letters*, vol. 28, no. 22, pp. 2087– 2088, 1992.

- [3] K. N. Salama and A. M. Soliman, "CMOS operational transresistance amplifier for analog signal processing," *Microelectronics Journal*, vol. 30, no. 3, pp. 235–245, 1999.

- [4] H. Barthélemy, I. Koudobine, and D. Van Landeghem, "Bipolar low-power operational transresistance amplifier based on first generation current conveyor," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 48, no. 6, pp. 620–625, 2001.

- [5] A. Ravindran, A. Savla, I. Younus, and M. Ismail, "A 0.8 V CMOS filter based on a novel low voltage operational transresistance amplifier," in *The 2002 45th Midwest Symposium on Circuits and Systems, 2002. MWSCAS-2002.*, vol. 3. IEEE, 2002, pp. III–III.

- [6] A. Duruk and H. Kuntman, "A new CMOS differential OTRA design for the low voltage power supplies in the sub-micron technologies," *Turkish Journal* of Electrical Engineering & Computer Sciences, vol. 13, no. 1, pp. 23–38, 2005.

- [7] A. Duruk, E. O. Güneş, and H. Kuntman, "A new low voltage CMOS differential OTRA for sub-micron technologies," *AEU-International Journal of Electronics and Communications*, vol. 61, no. 5, pp. 291–299, 2007.

- [8] H. Mostafa and A. M. Soliman, "A modified CMOS realization of the operational transresistance amplifier (OTRA)," *Frequenz*, vol. 60, no. 3-4, pp. 70–77, 2006.

- [9] A. K. Kafrawy and A. M. Soliman, "New CMOS operational transresistance amplifier," in *International Conference on Microelectronics*. IEEE, 2008, pp. 31–34.

- [10] H. M. Obaid, U. Tayyab, and S. M. Ch, "Design of a CMOS differential operational transresistance amplifier in 90 nm CMOS technology," *International Journal of Electronics and Communication Engineering*, vol. 11, no. 6, pp. 787–790, 2017.

- [11] A. K. Kafrawy and A. M. Soliman, "A modified CMOS differential operational transresistance amplifier (OTRA)," *AEU-International Journal of Electronics* and Communications, vol. 63, no. 12, pp. 1067–1071, 2009.

- [12] S. Mittal, G. Kapur, C. Markan, and V. Pyara, "Analog field programmable CMOS operational transresistance amplifier (OTRA)," in *Students Conference* on Engineering and Systems (SCES). IEEE, 2013, pp. 1–6.

- [13] A. Pawade and R. Ghongade, "Operational transresistance amplifier using submicron technology," International Journal of Advanced Research in Computer Science and Software Engineering, vol. 4, no. 2, 2014.

- [14] P. Prasad, S. Gautam, and B. Aggarwal, "FGMOS based gain tunable and low power OTRA circuit," in *International Conference on Computing, Power* and Communication Technologies (GUCON). IEEE, 2019, pp. 139–143.

- [15] A. K. Singh and P. Kumar, "A novel fully differential current mode universal filter," in 57th international Midwest symposium on circuits and systems (MWSCAS). IEEE, 2014, pp. 579–582.

- [16] C.-L. Hou, C.-W. Chang, and J.-W. Horng, "A quadrature oscillator employing the dominant poles of the OTRAs," *Journal of Advanced Engineering*, vol. 2, no. 3, pp. 185–187, 2007.

- [17] F. Kacar, U. Cam, O. Cicekoglu, H. Kuntman, and A. Kuntman, "New parallel immitance simulator realizations employing a single OTRA," in 45th Midwest Symposium on Circuits and Systems, 2002. MWSCAS-2002., vol. 1. IEEE, 2002, pp. I–303.

- [18] U. Çam, F. Kaçar, O. Cicekoglu, H. Kuntman, and A. Kuntman, "Novel grounded parallel immittance simulator topologies employing single OTRA," *AEU-International Journal of Electronics and Communications*, vol. 57, no. 4, pp. 287–290, 2003.

- [19] R. Senani, A. K. Singh, A. Gupta, and D. R. Bhaskar, "Simple simulated inductor, low-pass/band-pass filter and sinusoidal oscillator using OTRA," *Circuits and Systems*, vol. 7, no. 03, p. 83, 2016.

- [20] B. C. Nagar and M. Ghosh, "Single OTRA based immittance simulator and its application," in *International Conference on Communication and Signal Processing (ICCSP)*. IEEE, 2018, pp. 0050–0053.

- [21] U. Çam, F. Kaçar, O. Cicekoglu, H. Kuntman, and A. Kuntman, "Novel two OTRA-based grounded immitance simulator topologies," *Analog Integrated Circuits and Signal Processing*, vol. 39, no. 2, pp. 169–175, 2004.

- [22] S. Kilinc, K. N. Salama, and U. Cam, "Realization of fully controllable negative inductance with single operational transresistance amplifier," *Circuits, Systems and Signal Processing*, vol. 25, no. 1, pp. 47–57, 2006.

- [23] R. Pandey, N. Pandey, S. K. Paul, A. Singh, B. Sriram, and K. Trivedi, "New topologies of lossless grounded inductor using OTRA," *Journal of Electrical* and Computer Engineering, vol. 2011, 2011.

- [24] M. Ghosh and S. K. Paul, "Design of lossless grounded negative inductance simulator using single operational transresistance amplifier," *Revue Roumaine* des Sciences Techniques-Serie Électrotechnique et Énergétique, vol. 59, no. 4, pp. 381–390, 2014.

- [25] R. Pandey, N. Pandey, S. K. Paul, A. Singh, B. Sriram, and K. Trivedi, "Novel grounded inductance simulator using single OTRA," *International Journal of Circuit Theory and Applications*, vol. 42, no. 10, pp. 1069–1079, 2014.

- [26] A. Pramanik, "Design of operational transresistance amplifier based grounded active inductor and implementation of bandpass filter," in 2nd International Conference on Electronics and Communication Systems (ICECS). IEEE, 2015, pp. 842–844.

- [27] B. C. Nagar and S. K. Paul, "Negative inductance simulator using OTRA," in International Conference on Microelectronics, Computing and Communications (MicroCom). IEEE, 2016, pp. 1–3.

- [28] A. Gupta, R. Senani, D. R. Bhaskar, and A. K. Singh, "Otra-based grounded-FDNR and grounded-inductance simulators and their applications," *Circuits, Systems, and Signal Processing*, vol. 31, no. 2, pp. 489–499, 2012.

- [29] A. Gupta, R. Senani, D. Bhaskar, and A. Singh, "New OTRA-based generalized impedance simulator," *International Scholarly Research Notices*, vol. 2013, 2013.

- [30] B. C. Nagar and S. K. Paul, "Lossless grounded FDNR simulator and its applications using OTRA," Analog Integrated Circuits and Signal Processing, vol. 92, no. 3, pp. 507–517, 2017.

- [31] S. Kilinc and U. Cam, "Operational transresistance amplifier based first-order allpass filter with an application example," in 47th Midwest Symposium on Circuits and Systems, MWSCAS'04., vol. 1. IEEE, 2004, pp. I–65.

- [32] B. C. Nagar and S. K. Paul, "Lossless grounded admittance simulator using OTRA," Analog Integrated Circuits and Signal Processing, vol. 106, no. 3, pp. 649–659, 2021.

- [33] S. Kılınç and U. Çam, "Cascadable allpass and notch filters employing single operational transresistance amplifier," *Computers & Electrical Engineering*, vol. 31, no. 6, pp. 391–401, 2005.

- [34] C. Cakir, U. Cam, and O. Cicekoglu, "Novel allpass filter configuration employing single OTRA," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 52, no. 3, pp. 122–125, 2005.

- [35] F. Kaçar, "Operational transresistance amplifier based current-mode all-pass filter topologies," in 2009 Applied Electronics. IEEE, 2009, pp. 149–152.

- [36] K. Banerjee, A. Ranjan, and S. K. Paul, "New first order multifunction filter employing operational transresistance amplifier," in 2012 5th International Conference on Computers and Devices for Communication (CODEC). IEEE, 2012, pp. 1–3.

- [37] H. Gahlawat, H. Kumar, J. Kamnani, G. Dagar, and R. Pandey, "Voltage mode universal first order filter employing single OTRA," *i-Manager's Journal* on Electronics Engineering, vol. 5, no. 4, p. 24, 2015.

- [38] A. Gokcen and U. Cam, "MOS-C single amplifier biquads using the operational transresistance amplifier," AEU-International Journal of Electronics and Communications, vol. 63, no. 8, pp. 660–664, 2009.