# ANALYSIS AND DESIGN OF POSITIVE FEEDBACK SOURCE COUPLED LOGIC

Thesis submitted to the Delhi Technological University

for the Award of Degree of

**Doctor of Philosophy**

in

# **Electronics and Communication Engineering**

by *Ranjana Sivaram* (Enrollment No.:2K16/PHD/E&C/09)

Under the Supervision of

Prof. Neeta Pandey & Prof. Kirti Gupta

# **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

# DELHI TECHNOLOGICAL UNIVERSITY

# **DELHI-110042 INDIA**

January 2022

© Delhi Technological University-2022

All Rights Reserved

Delhi Technological University Formerly Delhi College of Engineering Shahbad Daulatpur, Bawana Road, Delhi -110042

# CERTIFICATE

This is to certify that the thesis entitled- "ANALYSIS AND DESIGN OF POSITIVE FEEDBACK SOURCE COUPLED LOGIC" submitted by Ranjana Sivaram (2K16/PhD/E&C/09) to the Department of Electronics and Communication Engineering, Delhi Technological University for the award of the degree of Doctor of Philosophy is based on the original research work carried out by her under our guidance and supervision. In our opinion, the thesis has reached the standards fulfilling the requirements of the regulations relating to the degree. It is further certified that the work presented in this thesis is not submitted to any other university or institution for the award of any degree or diploma.

Neile

**Prof. Neeta Pandey** Supervisor, Department of ECE Delhi Technological University Delhi-110042 India

ellepupt

**Prof. Kirti Gupta** Co-Supervisor, Department of ECE Bharati Vidyapeeth's College of Engg. Delhi-110063 India

**Prof. N.S. Raghava** Head of Department, Department of ECE Delhi Technological University Delhi-110042 India

### **CANDIDATE'S DECLARATION**

I hereby certify that the research work, which is being presented in the thesis, titled,

"ANALYSIS AND DESIGN OF POSITIVE FEEDBACK SOURCE COUPLED LOGIC" in fulfillment of requirements of the award of the degree of Doctor of Philosophy is an authentic record of my research work carried under the supervision of Prof. Neeta Pandey and Prof. Kirti Gupta. The matter presented in this thesis has not been submitted elsewhere in part or fully to any other University or Institute for the award of any degree.

payerne Ranjana Sivaram

(2K16/PHD/E&C/09)

#### ACKNOWLEDGMENTS

The support and expert advice of my supervisors Prof. Neeta Pandey, Department of Electronics and Communication Engineering (ECE), Delhi Technological University (DTU) and Prof. Kirti Gupta, Department of Electronics and Communication Engineering (ECE), Bharati Vidyapeeth's College of Engineering is acknowledged with deep gratitude. Their continuous motivation, time bound goals and frequent follow ups has helped me to stay focussed and I'm grateful for their supervision, continuous motivation, and their humanitarian considerations.

My sincere thanks to Prof. N.S. Raghava, Head, ECE department, DTU, Delhi for providing me with all the necessary facilities for the completion of my work. I am thankful to all the faculty members of the department for their timely advice, support and help on various occasions. I am also grateful to Prof. Jai Prakash Saini, Vice-Chancellor, DTU, Delhi, for providing the research environment in the institute. I am also thankful to all non-teaching staff at DTU, who have helped me directly or indirectly in completion of the Ph.D. work.

I would also like to thank my seniors and colleagues of the ECE department for their support, especially Mr. Gurumurthy, Mr. Bharat, Ms. Parveen, Ms. Garima, Ms. Neetika, Ms. Damyanti and Ms. Monica. In continuation, I feel this deep sense of respect for my parents, Dr.N.Sridhar and Mrs. Lalitha Sridhar, for having brought me up this far, and would like to express my gratitude for having inculcated in me a love for research. I would like to especially thank my sister, Shobhana, for motivating me to go on with my doctorate from time to time. Last but not the least I would like to thank my husband, Sivaram and my family for supporting me through this long journey.

Ranjana Sivaram v

#### ABSTRACT

The demand for consumer electronics, biomedical implantable systems, sensor nodes in sensor networks etc. have all contributed towards the drive for portable systems with long battery life. This in turn has driven the need for mixed signal integrated circuits with analog and digital logic on the same substrate as this reduces dimensions of the integrated circuits, reduces the cost and also allows operation at higher speed. However, the noise transmission from the digital part to the analog part which is sensitive to noise becomes a problem, because of the loss in accuracy of the analog circuits or the reduction of the dynamic range. In CMOS circuits, the noise is due to current peaks and voltage variations during the switching of logic states. To solve this, several solutions are proposed – in terms of layout, placement of pins and routing of signals and selection of alternate logic styles.

To address the switching noise, various low switching noise logic styles have emerged wherein power supply current is kept nearly constant during the switching event and/or working with smaller voltage swings. Some notable logic styles are current steering logic (CSL) style, current balance logic (CBL) style, folded source-coupled logic (FSCL) style and the source coupled logic (SCL) style.

The positive feedback source coupled logic (PFSCL) style, a variant of SCL, among these is an attractive alternative as it addresses the issue and is explored in this thesis for design modifications to improve the overall circuit performance. The work in this thesis encapsulates its analysis and design.

The PFSCL FC based gates help in accommodating complex logic function into a single gate, but requires larger footprint. The concept of multithreshold technique is incorporated and two topologies are presented. The former results in area advantage while the latter improves power consumption. The static and dynamic parameters are modelled and validated.

Next, a PFSCL Quadtail cell that can accommodate more inputs in a single gate is presented thereafter. The usefulness of the proposal is illustrated with a three input PFSCL XOR gate. The proposition is analysed for static and dynamic parameters. It is found that the proposed XOR gate topology outperforms the possible existing counterparts.

The presence of a constant current source in PFSCL causes static power consumption which restricts its application for battery constrained devices. The availability of dynamic PFSCL style is an effort made in this direction. This style, however, requires cascading of gates for multilevel realisation and also intermittent buffers for correct evaluation. Two schemes are worked out to address this – the former modifies the pull down network of existing D-PFSCL gate while the latter relies in inclusion of transmission gates.

The ultra-low power PFSCL gate is introduced in this work wherein low power supply is used and the constituent transistors operate in subthreshold region. The basic principles for design of PFSCL in subthreshold region are identified and trends are noted. From analysis and simulations it is noted that the circuits implemented using PFSCL style in subthreshold region offer more flexibility to the design of ultra-low power applications compared to those implemented using CMOS in subthreshold region.

All the propositions are validated through extensive simulative investigations.

# **Table of Contents**

| ACKNO     | WL   | EDGMENTS                                  |

|-----------|------|-------------------------------------------|

| ABSTRA    | АСТ  | V.                                        |

| Table of  | Cor  | itentsvii                                 |

| List of F | igur | esx                                       |

| List of T | able | SXV                                       |

| List of P | ubli | cationsxv                                 |

| Chapter   | 1    | Introduction1                             |

| 1.1       | Bac  | kground                                   |

| 1.2       | Pos  | itive Feedback Source Coupled Logic style |

| 1.3       | Mo   | tivation10                                |

| 1.4       | The  | esis Organization13                       |

| Chapter   | 2    | Existing PFSCL architectures              |

| 2.1       | Intr | oduction17                                |

| 2.2       | PFS  | SCL Style Fundamentals17                  |

| 2.2.      | 1    | PFSCL operation and analysis18            |

| 2.2.      | 2    | Realisation of Conventional PFSCL gates24 |

| 2.3       | PFS  | SCL fundamental cell architecture26       |

| 2.3.      | 1    | Fundamental cell operation and analysis   |

| 2.3.      | 2    | Implementation of gates                   |

| 2.4       | Dyı  | namic PFSCL (D-PFSCL)                     |

|           |      | viii                                      |

| 2.4.    | 1    | D-PFSCL operation and analysis                | .34 |

|---------|------|-----------------------------------------------|-----|

| 2.4.    | 2    | Realisation of gates                          | .36 |

| 2.5     | Con  | clusion                                       | .38 |

| Chapter | 3    | Multithreshold PFSCL Architecture             | .39 |

| 3.1     | Intr | oduction                                      | .41 |

| 3.2     | Proj | posed architecture-1                          | .41 |

| 3.2.    | 1    | Analysis                                      | .44 |

| 3.2.    | 2    | Simulations                                   | .50 |

| 3.3     | Proj | posed architecture-2                          | .58 |

| 3.3.    | 1    | Analysis                                      | .60 |

| 3.3.    | 2    | Simulations                                   | .61 |

| 3.4     | Sun  | nmary                                         | .66 |

| Chapter | 4    | Modified PFSCL architecture for higher fan-in | .68 |

| 4.1     | Intr | oduction                                      | .70 |

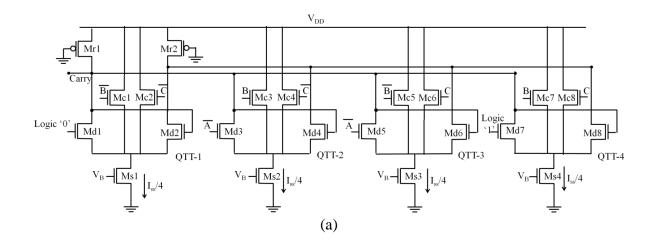

| 4.2     | Proj | posed Architecture-3                          | .70 |

| 4.2.    | 1    | Analysis                                      | .74 |

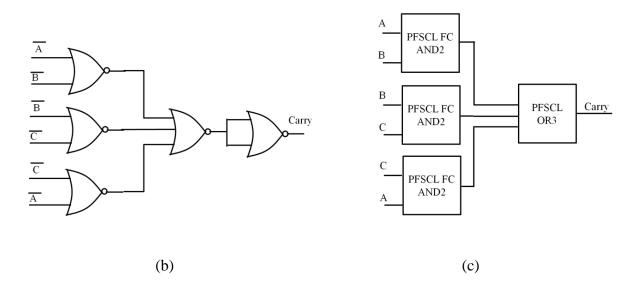

| 4.2.    | 2    | Simulations                                   | .82 |

| 4.3     | Con  | nclusion                                      | .88 |

| Chapter | 5    | Modified Dynamic PFSCL architectures          | .89 |

| 5.1     | Intr | oduction                                      | .91 |

| 5.2     | Proj | posed architecture-4                          | .91 |

| 5.2.1    | 1     | Analysis                 | 99  |

|----------|-------|--------------------------|-----|

| 5.2.2    | 2     | Simulations              | 100 |

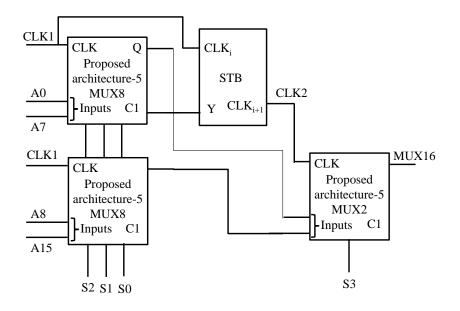

| 5.3      | Prop  | pposed Architecture -5   | 110 |

| 5.3.     | 1     | Analysis                 | 112 |

| 5.3.2    | 2     | Simulations              | 113 |

| 5.4      | Con   | nclusion                 | 124 |

| Chapter  | 6     | Subthreshold PFSCL gates | 126 |

| 6.1      | Intro | roduction                | 128 |

| 6.2      | Prop  | pposed architecture-6    | 128 |

| 6.2.     | 1     | Analysis                 | 130 |

| 6.2.2    | 2     | Simulations              | 134 |

| 6.3      | Con   | nclusion                 | 142 |

| Chapter  | 7     | Conclusion               | 143 |

| 7.1      | Con   | ncluding Remarks         | 145 |

| 7.2      | Ave   | enues for future work    | 147 |

| Referenc | ces   |                          | 149 |

# List of Figures

| Fig. 2.1 Basic architecture of a generic PFSCL gate                                                           | 7  |

|---------------------------------------------------------------------------------------------------------------|----|

| Fig. 2.2 PFSCL inverter [37]                                                                                  | 9  |

| Fig. 2.3 Voltage transfer characteristics of the PFSCL inverter                                               | 20 |

| Fig. 2.4 Linear half circuit                                                                                  | 21 |

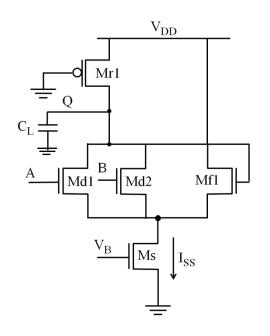

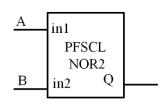

| Fig. 2.5 PFSCL style a) NOR2 b) NAND2 c) XOR2                                                                 | 26 |

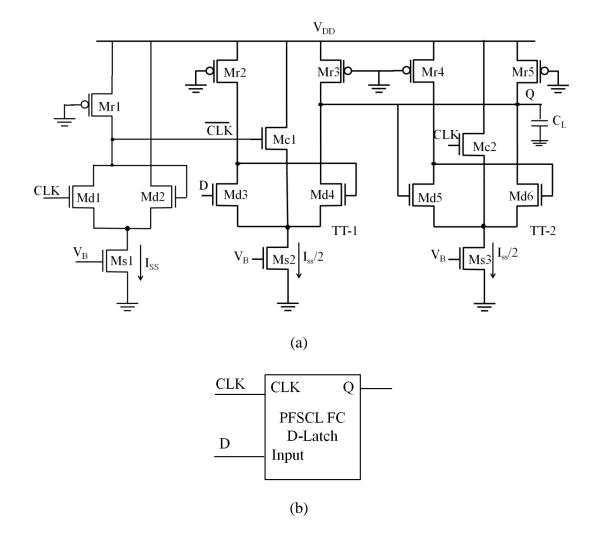

| Fig. 2.6 a) PFSCL FC based D-Latch [66] b) Block representation                                               | 27 |

| Fig. 2.7 Fundamental cell based OR2 gate                                                                      | 29 |

| Fig. 2.8 CLB [71]                                                                                             | 32 |

| Fig. 2.9 D-PFSCL inverter [67]                                                                                | 33 |

| Fig. 2.10 STB a) MOS schematic b) symbol                                                                      | 36 |

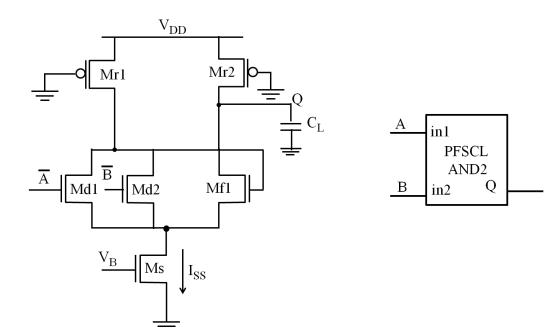

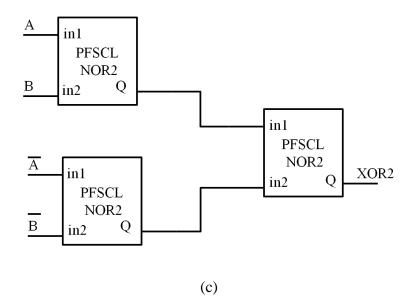

| Fig. 2.11 a) D-PFSCL NOR2 b) D-PFSCL NOR2 symbol c) D-PFSCL XOR2 gate [66]3                                   | 37 |

| Fig. 3.1 Proposed architecture-1 a) XOR2 gate b) Symbol                                                       | 12 |

| Fig. 3.2 Proposed architecture-1 generic gate                                                                 | 13 |

| Fig. 3.3 Linear half circuit of proposed architecture-1                                                       | 17 |

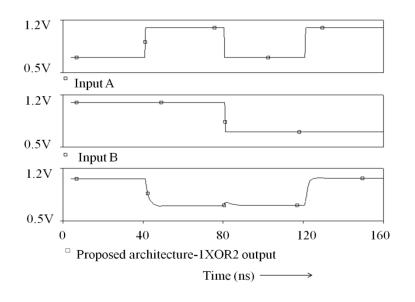

| Fig. 3.4 Simulation waveform of proposed architecture-1 based XOR2 gate                                       | 50 |

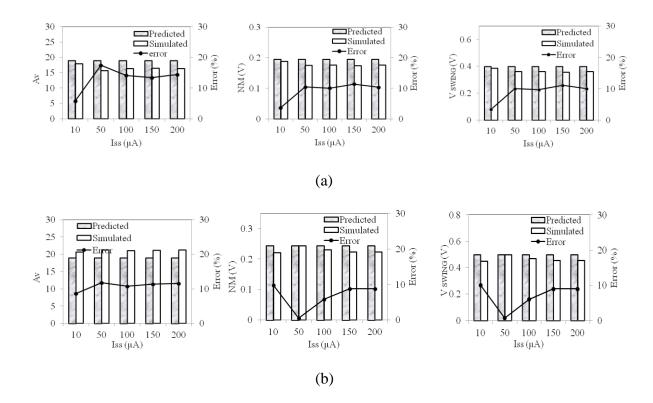

| Fig. 3.5 Predicted and Simulated results with error versus $I_{SS}$ for static parameters wi                  | th |

| V <sub>SWING</sub> of a) 0.4V and b) 0.5V                                                                     | 51 |

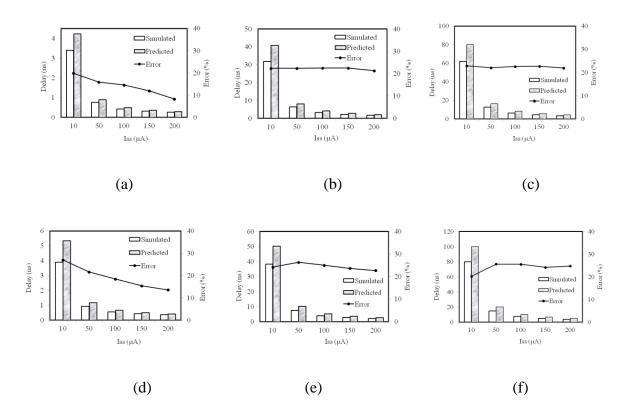

| Fig. 3.6 Predicted and Simulated results with error in delay versus $I_{SS}$ for a) $V_{SWING} = 0.4$         | V  |

| and $C_L=50 fF b$ ) $V_{SWING}=0.4V$ and $C_L=500 fF c$ ) $V_{SWING}=0.4V$ and $C_L=1 pF d$ ) $V_{SWING}=0.5$ | V  |

| and $C_L$ =50fF e) $V_{SWING}$ =0.5V and $C_L$ =500fF f) $V_{SWING}$ =0.5V and $C_L$ =1pF                     | 52 |

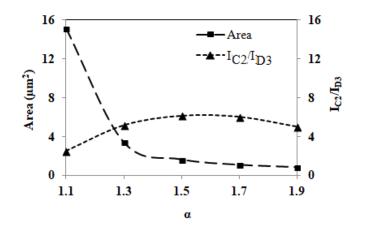

| Fig. 3.7 Area vs $I_{C2}/I_{D3}$ vs $\alpha$ for proposed architecture-1 based XOR2 gate                      | 53 |

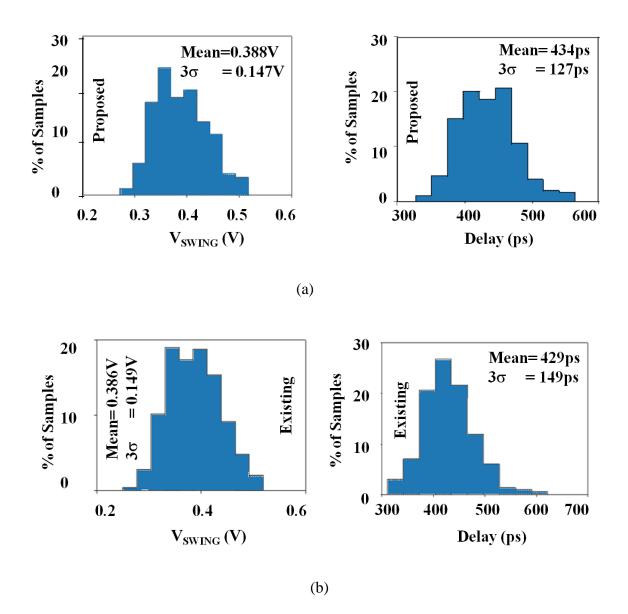

| Fig. 3.8 Monte Carlo results for $V_{SWING}$ and Delay for a) proposed and b) existing PFSC                   | Ľ  |

| FC based XOR2 gate                                                                                            | 54 |

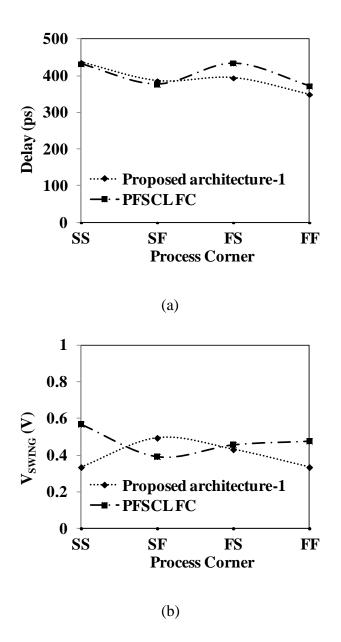

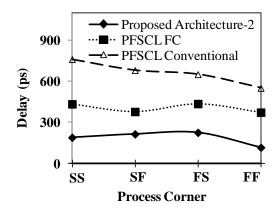

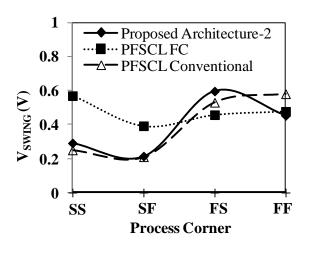

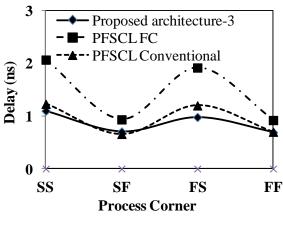

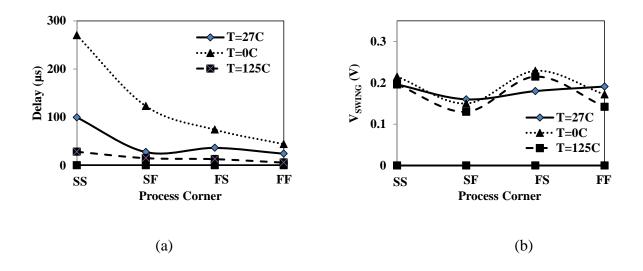

| Fig. 3.9 Impact of process corners on a) Delay and b) $V_{SWING}$                            |

|----------------------------------------------------------------------------------------------|

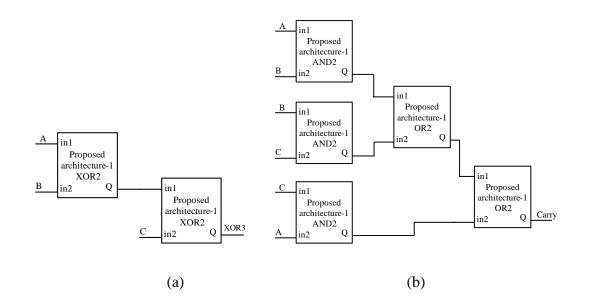

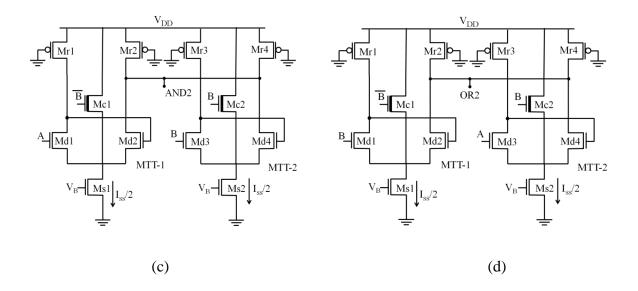

| Fig. 3.10 Proposed architecture-1 based a) Sum and b) Carry c) AND2 gate and d) OR2 gate     |

|                                                                                              |

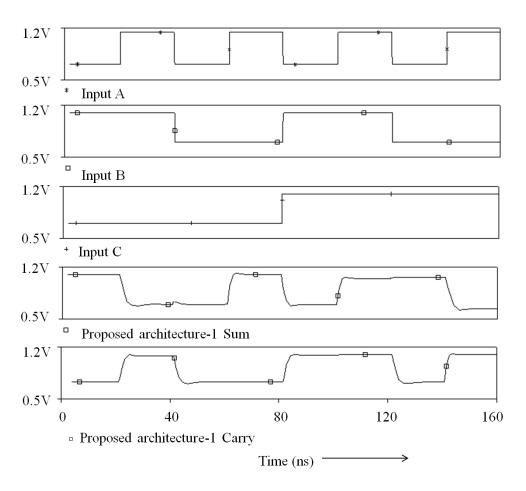

| Fig. 3.11 Simulation waveforms for Proposed architecture-1 full adder57                      |

| Fig. 3.12 Existing PFSCL FC based XOR2 gate                                                  |

| Fig. 3.13 Proposed architecture-2 based XOR2 gate                                            |

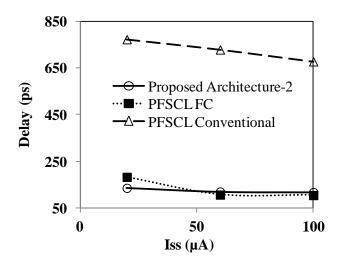

| Fig. 3.14 Propagation delay versus bias current for XOR2 gate                                |

| Fig. 3.15 Power consumption versus bias current for XOR2 gate63                              |

| Fig. 3.16 PDP versus bias current for XOR2 gate63                                            |

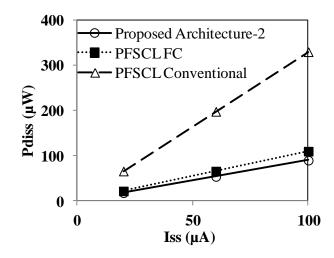

| Fig. 3.17 Monte Carlo analysis on Delay and Voltage swing of XOR2 gate based on a)           |

| proposed architecture-2 b) PFSCL FC c) conventional PFSCL                                    |

| Fig. 3.18 Effect of process corners on XOR2 gate a) Delay b) Voltage Swing65                 |

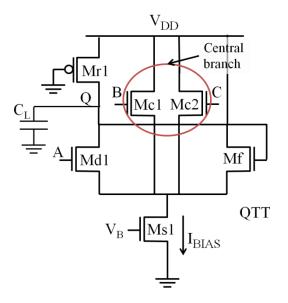

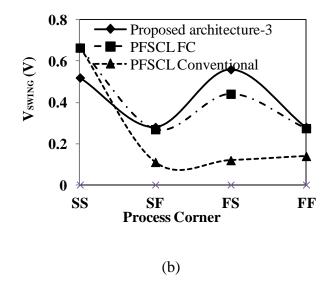

| Fig. 4.1 Quadtail cell- Basic structure of the proposed architecture-371                     |

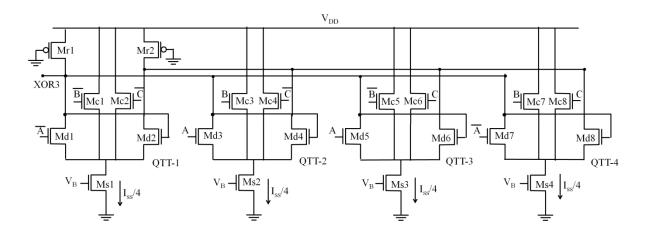

| Fig. 4.2 XOR3 based on a) proposed architecture-3 b) conventional PFSCL c) existing          |

| PFSCL FC73                                                                                   |

| Fig. 4.3 Proposed architecture-3 generic gate74                                              |

| Fig. 4.4 Linear half circuit of proposed architecture-379                                    |

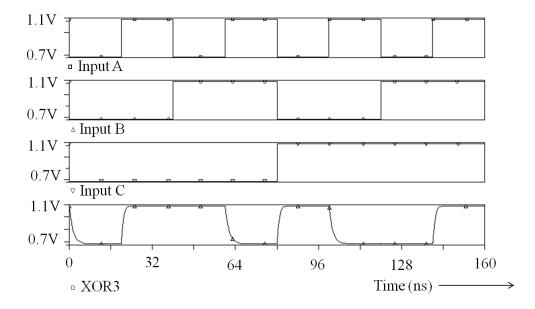

| Fig. 4.5 Simulation waveforms of the proposed architecture-3 XOR3 gate82                     |

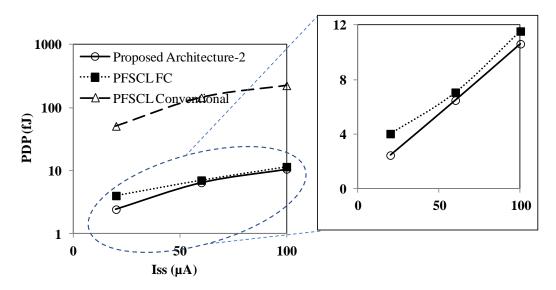

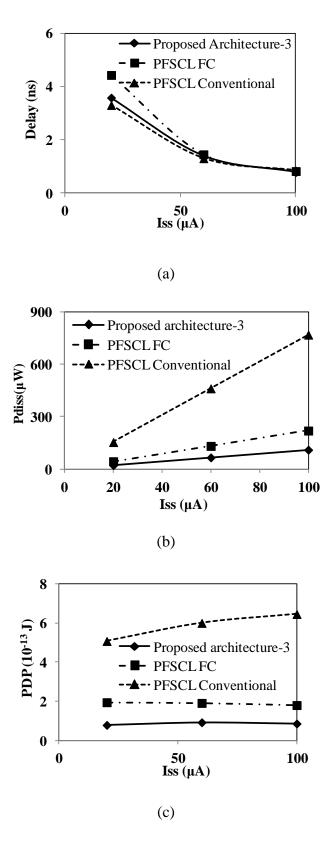

| Fig. 4.6 Performance comparison versus $I_{SS}$ a) Delay b) Power dissipation c) PDP of XOR3 |

| gate                                                                                         |

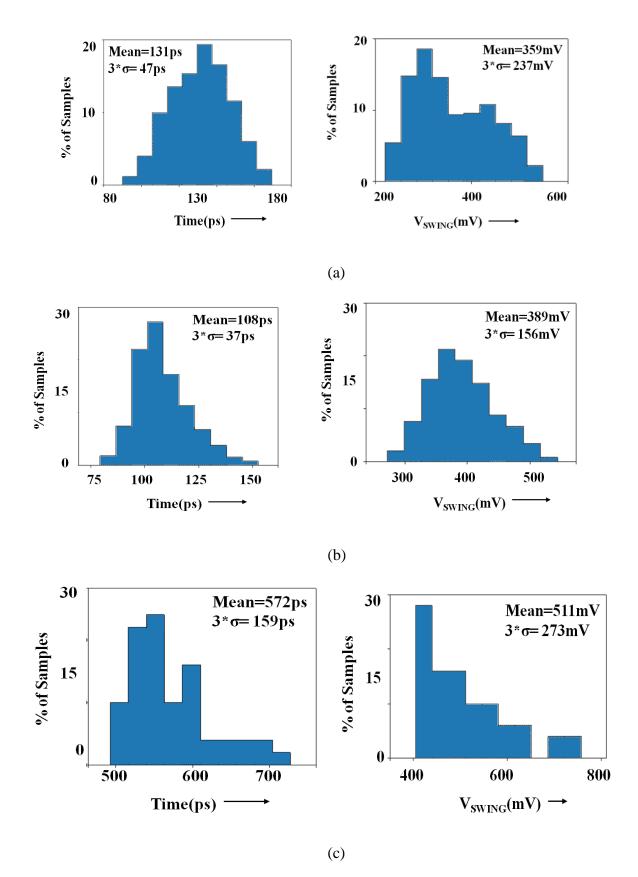

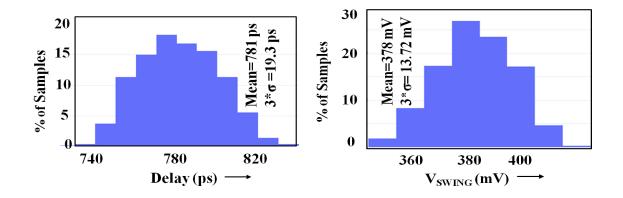

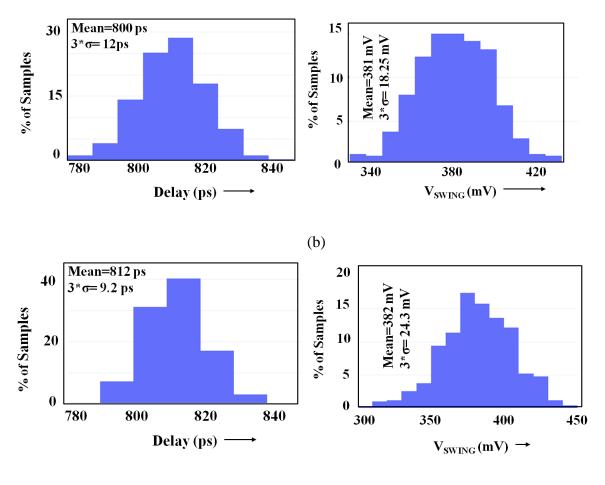

| Fig. 4.7 Impact of Monte Carlo for 500 runs a) Proposed architecture-3 b) PFSCL FC c)        |

| conventional PFSCL                                                                           |

| Fig. 4.8 Impact of process corners on the three architectures a) Delay and b) $V_{SWING}$    |

| Fig. 4.9 Carry a) Proposed architecture-3 b) Conventional PFSCL c) PFSCL FC87                |

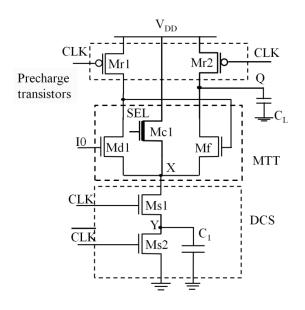

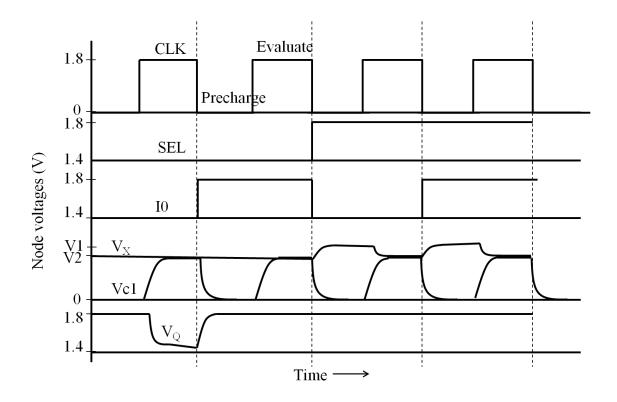

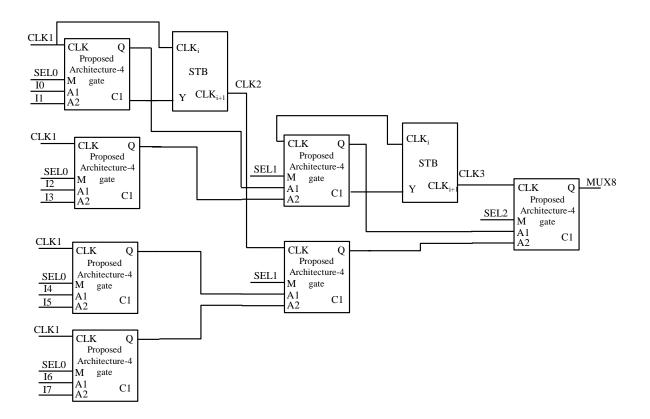

| Fig. 5.1 Modified schematic of a D-PFSCL with the addition of Mc192 xii                      |

| Fig. 5.2 Voltages at different nodes of modified D-PFSCL                                                      |

|---------------------------------------------------------------------------------------------------------------|

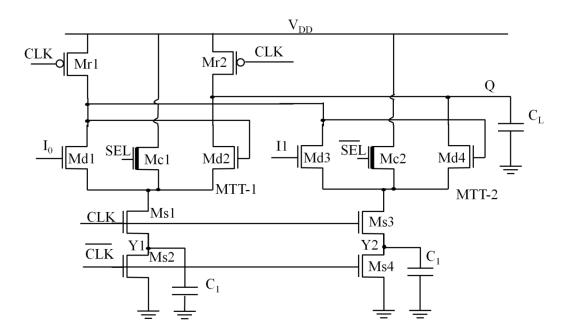

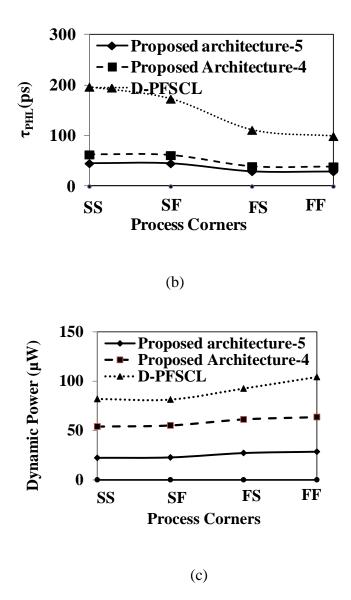

| Fig. 5.3 Complete schematic of the proposed architecture-4 MUX295                                             |

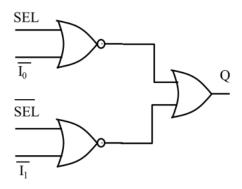

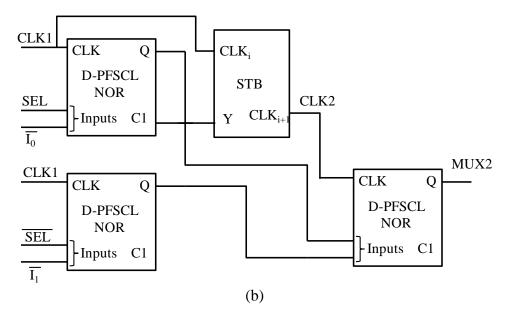

| Fig. 5.4 MUX2 a) Gate level schematic b) Existing D-PFSCL97                                                   |

| Fig. 5.5 Proposed architecture-4 generic gate                                                                 |

| Fig. 5.6 Proposed architecture-4 XOR2 gate                                                                    |

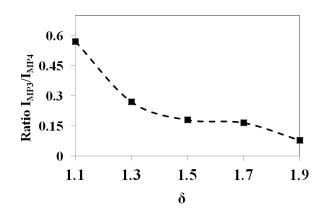

| Fig. 5.7 $I_{Md3}/I_{Mc2}$ for different values of $\alpha$                                                   |

| Fig. 5.8 Existing D-PFSCL XOR2 gate102                                                                        |

| Fig. 5.9 Simulation waveforms of the XOR2 gate102                                                             |

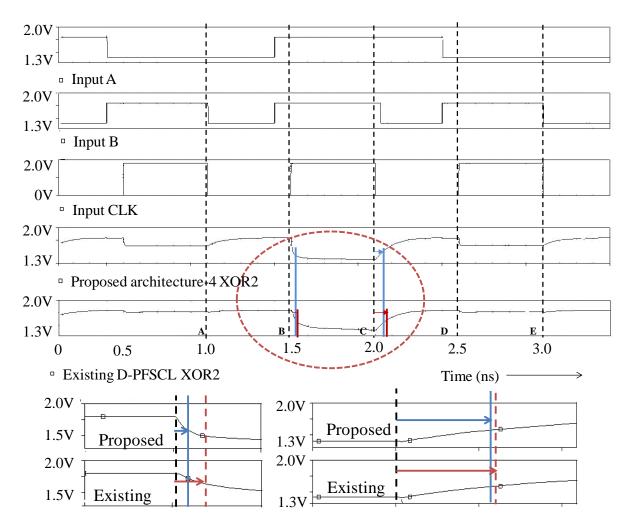

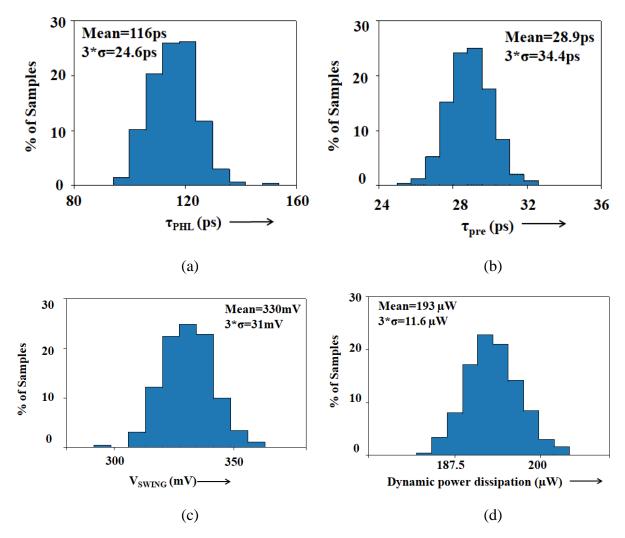

| Fig. 5.10 Proposed architecture-4 based XOR2 gate output under Monte Carlo analysis105                        |

| Fig. 5.11 Monte Carlo variation in Proposed architecture-4 XOR2 gate a) $\tau_{PHL}$ b) $\tau_{pre}$ c)       |

| V <sub>SWING</sub> d) Dynamic power dissipation106                                                            |

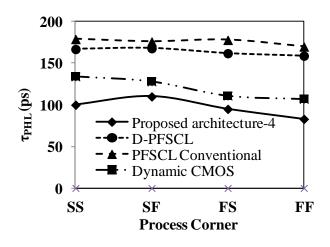

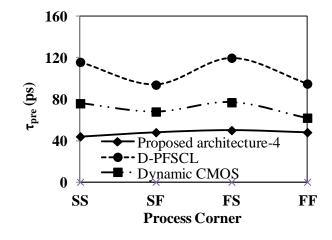

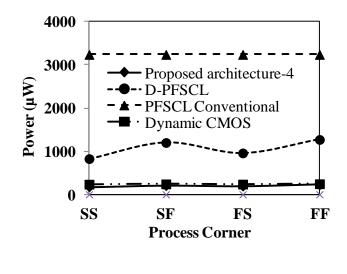

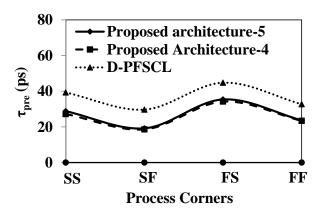

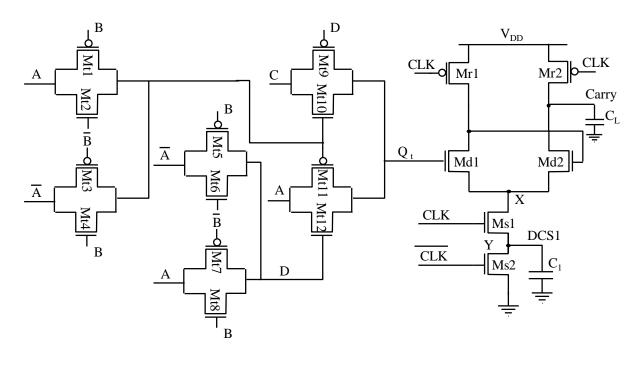

| Fig. 5.12 Process corner results of XOR2 gate a) $\tau_{PHL}$ b) $\tau_{pre}$ c) power108                     |

| Fig. 5.13 Block diagram of the proposed architecture-4 MUX8109                                                |

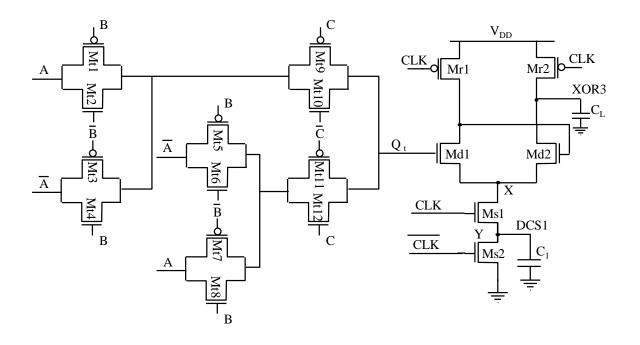

| Fig. 5.14 Proposed architecture-5 generic gate111                                                             |

| Fig. 5.15 Proposed architecture-5 MUX16 gate112                                                               |

| Fig. 5.16 XOR2 gate a) Proposed architecture-5 b) Proposed architecture-4 c) D-PFSCL [67]                     |

| d) Simulation waveforms e) Transitions at the proposed architecture-5 XOR2 gate output.116                    |

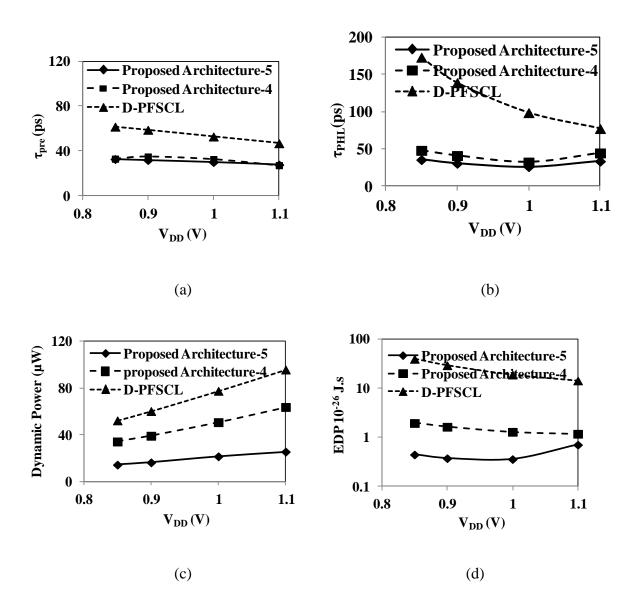

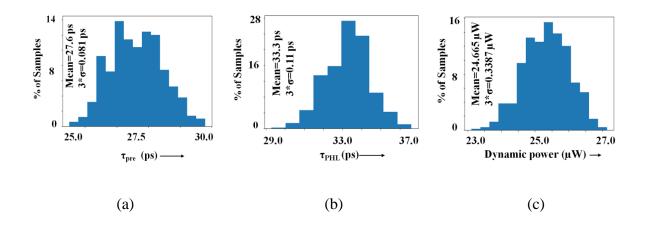

| Fig. 5.17 Performance with respect to power supply variations a) $\tau_{pre}$ b) $\tau_{PHL}$ c) dynamic      |

| power d) EDP118                                                                                               |

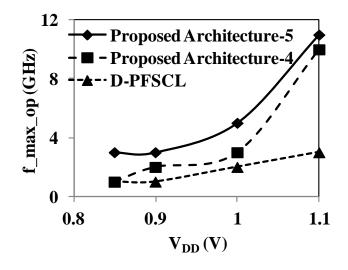

| Fig. 5.18 a) Maximum Operating frequency with respect to different supply voltages b)                         |

| Operating frequency with respect to dynamic power consumption119                                              |

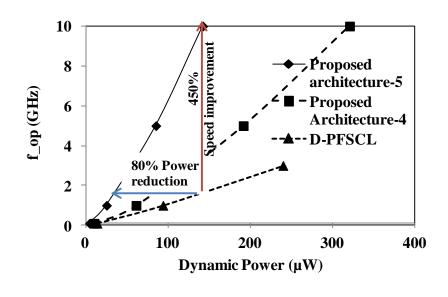

| Fig. 5.19 Monte Carlo simulation results (500 runs) for proposed architecture-5 XOR2 a) $\tau_{pre}$          |

| b) τ <sub>PHL</sub> c) dynamic power                                                                          |

| Fig. 5.20 Process corner results of the XOR2 gate in all the architectures a) $\tau_{pre}$ b) $\tau_{PHL}$ c) |

| dynamic power                                                                                                 |

| Fig. | 5.21 Full adder based on proposed architecture-5 a) XOR3 b) Carry               | 123 |

|------|---------------------------------------------------------------------------------|-----|

| Fig. | 6.1 ST-PFSCL inverter                                                           | 129 |

| Fig. | 6.2 Linear half circuit of ST-PFSCL inverter                                    | 133 |

| Fig. | 6.3 Simulation waveform of ST-PFSCL inverter                                    | 135 |

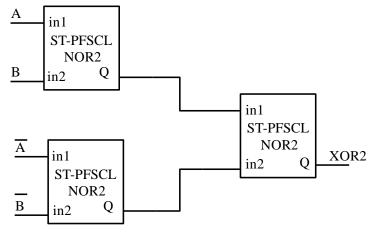

| Fig. | 6.4 ST-PFSCL a) NOR2 gate b) XOR2 gate                                          | 136 |

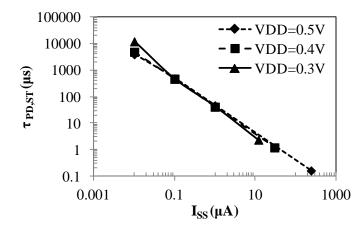

| Fig. | 6.5 Delay versus I <sub>SS</sub> of the ST-PFSCL XOR2 gate                      | 136 |

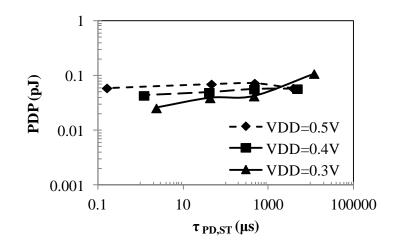

| Fig. | 6.6 PDP versus delay of the ST-PFSCL XOR2 gate                                  | 137 |

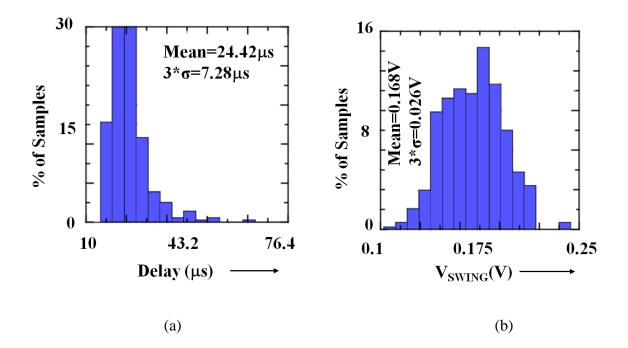

| Fig. | 6.7 Monte Carlo results for ST-PFSCL XOR2 a) Delay b) Voltage swing             | 138 |

| Fig. | 6.8 Process corner results of the ST-PFSCL XOR2 (a) Delay (b) $V_{SWING}$       | 139 |

| Fig. | 6.9 a) ST-PFSCL D latch gate b) ST-PFSCL divide-by-8 circuit                    | 140 |

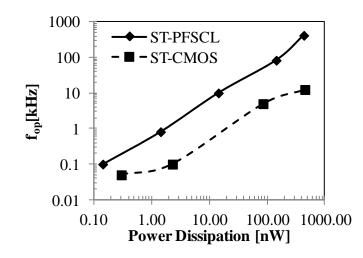

| Fig. | 6.10 Frequency of operation versus power dissipation of the divide-by-8 circuit | 141 |

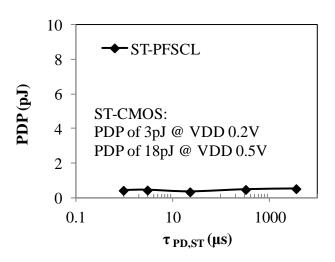

| Fig. | 6.11 PDP versus delay of the divide-by-8 circuit                                | 141 |

# List of Tables

| Table 2.1 Output voltages for various combinations of inputs    3                             | 0  |

|-----------------------------------------------------------------------------------------------|----|

| Table 2.2 Realisation of different logic functions using CLB                                  | 2  |

| Table 3.1 Performance summary of the full adder                                               | 7  |

| Table 3.2 Power Supply voltage V <sub>DDmin</sub> 6                                           | 1  |

| Table 4.1 Realisation of different 3 input logic functions based on proposed architecture-3.7 | 4  |

| Table 4.2 Working of proposed architecture-3 based XOR3 gate                                  | 7  |

| Table 4.3 Summary of results for a Full Adder    8                                            | 7  |

| Table 5.1 Summary of the proposed architecture-4 MUX2 operation                               | 6  |

| Table 5.2 Performance comparison    10                                                        | 3  |

| Table 5.3 Monte Carlo simulation results for the XOR2 gate in different styles         10     | 6  |

| Table 5.4 Performance summary of MUX8    10                                                   | 9  |

| Table 5.5 Performance Comparison of gates based on D-PFSCL, proposed architecture-4 an        | ıd |

| proposed architecture-511                                                                     | 7  |

| Table 5.6 Monte Carlo results for XOR212                                                      | 0  |

| Table 5.7 Performance Comparison of full adder based on existing D-PFSCL, propose             | d  |

| architecture-4 and proposed architecture-512                                                  | 4  |

# **List of Publications**

### **List of Journal Papers:**

- 1. Sivaram, Ranjana; Gupta, Kirti; Pandey, Neeta. "A new realisation scheme for dynamic PFSCL" *Integration* 75C (2020) pp. 169-177. (SCI Journal Impact Factor: 1.214)

- Sivaram, Ranjana; Gupta, Kirti; Pandey, Neeta. "Impact of multi threshold transistor in positive feedback source coupled logic (PFSCL) fundamental cell" Analog Integrated Circuits & Signal Process 109(2021) pp.173-185. (SCI Journal Impact Factor: 1.337)

### List of International Conference Papers:

- 1. Sivaram, Ranjana; Gupta, Kirti; Pandey, Neeta. "New improved low power triple tail cell with controlled current source" 2018 IEEE International Conference on Computing, Power and Communication Technologies (GUCON), pp. 1-5. IEEE, 2018.

- **2.** Sivaram, Ranjana; Gupta, Kirti; Pandey, Neeta "Low power design for source coupled logic gates" 2018 15th IEEE India Council International Conference (INDICON), pp. 1-5. IEEE, 2018.

- **3.** Sivaram, Ranjana; Gupta, Kirti; Pandey, Neeta, "**Power efficient architecture for PFSCL**" *2021 International Conference on Emerging Trends in Industry 4.0 (ETI 4.0)*, pp. 1-6.IEEE, 2021.

- **4.** Sivaram, Ranjana; Gupta, Kirti; Pandey, Neeta, **"Exploration of PFSCL in subthreshold region of operation for use in ultra low power applications" 2021 2nd International Conference for Emerging Technology (INCET). IEEE, 2021.**

### List of Journal papers under Communication:

Sivaram, Ranjana; Gupta, Kirti; Pandey, Neeta. "On Improving the Performance of Dynamic Positive-Feedback Source-Coupled Logic (D-PFSCL) through inclusion of Transmission Gates" *Microprocessors and Microsystems Journal*. Communicated. (SCI-E Journal Impact Factor 1.525) Chapter 1 Introduction

#### 1.1 Background

There is huge demand for electronic devices, especially portable and consumer electronics, which requires that as many logical functions as possible be implemented on the same chip in the form of System of Chip (SoC) so as to meet the speed and area requirements [1-7]. SoC designs reduce cost by saving on the total number of chips, and can yield significant performance improvements by reducing inter-chip communication time. Due to this, SoCs where both the analog and digital circuitry is on the same semiconductor die have nowadays become pervasive. The conventional CMOS logic style, used widely in SoCs, exhibits a large switching noise that lowers the performance of the analog building blocks and therefore it cannot be used on the same substrate with high-resolution analog circuits [8-10]. In order to successfully interface the digital and analog components of a system onto the same die, analog designers must either accept the noise inherent to CMOS digital circuits or try to isolate the digital and analog components as much as possible, making system level integration of SoC designs a challenging task. In order to isolate the noise generated by the digital system from the analog counterpart or to mitigate it, several techniques are available and these can be mainly be categorised in terms of - layout related methods, placement of pins and routing of signals, usage of alternate substrate material and usage of alternate logic styles [11-34].

Alternate logic styles that are suited to a mixed signal environment need to maintain a nearly constant current during the switching event and have reduced voltage swing in order to reduce the switching noise. The logic styles inheriting the features of maintaining constant current during switching activity are classified in four categories namely current balance logic (CBL) style [21-24], current steering logic (CSL) style [25-27], folded source coupled

logic (FSCL) style [7,28-30] and the MOS current mode logic style [31-34]. The CBL style is further classified into enhanced current balance logic (E-CBL) [22], complementary output current balance logic(C-CBL) [23], modified current balance logic (M-CBL) [24]. Similarly, the CSL style includes folded current steering logic (FCSL) [26], differential current steering logic (D-CSL) [27] whereas the enhanced folded source coupled logic (E<sup>2</sup>FSCL) [29], and enhancement source coupled logic [30] belongs to FSCL style. The CBL and FSCL based circuits use multiple current sources for logic function realisation whereas the CSL circuits works on larger voltage swing. The MOS current mode logic based circuits, which is based on the source-coupled pair of NMOS transistors, needs a single current source and works on smaller voltage swing; therefore it is a preferred choice for mixed signal IC applications. Also, MOS current mode logic or Source Coupled Logic (SCL), permits switching noise reduction by two orders of magnitude compared to standard CMOS logic [14-16].

The SCL gates are classified as differential or single-ended [35-37]. The former is based on the series-gating approach whereas in the latter the transistors share a common source and drain terminal and are source-coupled to a transistor whose gate is connected to reference voltage source [35, 37]. SCL gates are explored widely for building complex digital logic like ADCs, DACs, front end receivers, optical fiber front end transreceivers, arithmetic circuits etc [38-59].

### **1.2** Positive Feedback Source Coupled Logic style

An improved form of single-ended SCL style named as positive feedback source coupled logic (PFSCL) style is suggested in [37]. The logic style replaces the reference voltage source used in conventional single-ended SCL gates with a positive feedback to improve their performance. It is targeted towards high speed and low power dissipation and power efficient behaviour, and shows better performance compared to SCL. The logic style provides single

ended output and uses a NOR based architecture for implementing logic with a constant bias current per gate. The NOR based architecture is an advantage in that it allows operation of the gate at minimum supply voltage, which allows low power consumption requirements to be met. This also has the advantage that the PFSCL can work easily in deep submicron technologies, where the maximum power supply that is available is low. PFSCL style is explored in [60-68] in terms of design and analysis and further studied in terms of applications in arithmetic circuits, buffer, pipeline, latches, error detection and correction circuits in [69-79].

The paper [37] explains the working of the basic PFSCL gate and derives the expressions for static design parameters like small signal gain, noise margin and the voltage swing. The analytical delay model of PFSCL gates is also given in terms of the bias current, process parameters and the transistors' aspect ratios. Simulation results are shared which confirm that the proposed models are sufficiently accurate.

The analytical gate delay model for PFSCL is derived in [60] where the delay is given in terms of the associated parasitic capacitances at the output node. To derive the delay model of PFSCL gates the circuit is linearised around the logic threshold and circuit analysis is simplified through suitable approximation. Since the positive feedback in PFSCL gates significantly enhances the small-signal voltage gain, a much lower NMOS aspect ratio can be used to achieve the same value of small signal voltage gain, compared to conventional SCL logic. As a consequence, the contribution of NMOS parasitic capacitances to the output node is strongly reduced, and so, the delay reduces. Simulations in 350 nm are carried out to validate the delay model for PFSCL gates. For comparison, PFSCL gate based 5 stage ring oscillator is simulated against conventional SCL based 5 stage ring oscillator for same design parameters and it is found that PFSCL gates show better performance.

In [61-62], the issue of design of PFSCL gates is addressed as in today's scenario, delay, power and area occupied are all important design parameters that can be traded off against each other depending upon the specific application. This needs that interrelation between power, delay and area should be quantified and impact of variables like bias current, transistor dimensions for NMOS and PMOS on power, delay and area should be analysed. PFSCL gates offer lower delay compared to the traditional SCL gates. This excess of speed could also be exploited to save power consumption for an assigned speed requirement, thus allowing for a more flexible power-delay trade off management. Since the overall power consumption usually limits the number of gates that can be integrated in a mixed-signal chip, the reduction in the power consumption per gate allows for implementing more complex logic circuits for a given power budget of the digital section.

The delay expression is derived using the parasitic node capacitances and then, using the standard expressions for capacitances and some approximations according to meaningful cases in the design space, i.e., power-efficient, high-speed and low-power design, the delay is expressed in terms of the voltage swing and the bias current, which in turn define the gate power consumption. To validate the analytical expressions, simulations for different design cases like high speed, low power etc. are carried out and it is found that the analytical expressions are suitably accurate.

In [63], comparison between MOS Current Mode Logic (MCML) and PFSCL AND/OR/NOR gates is carried out through simulations in 180 nm to quantify the improvement offered by PFSCL gates in terms of delay, power and area. On the basis of simulations, it is found that for given power supply and bias current, PFSCL gates are faster and occupy lesser area compared to MCML gates.

6

In [64], hysteresis is utilised to improve the performance of PFSCL gates. To understand the impact of hysteresis, the noise margin of PFSCL gate is modelled from which it is found that hysteresis improves the noise margin. This implies that for a given noise margin, lower voltage swing will satisfy the noise margin requirement, in turn reducing the gate delay. For a given speed constraint, this reduction in delay due to hysteresis can be traded for reduction in power by reducing the bias current. Thus, use of hysteresis can make PFSCL gates more power efficient, which is important for high speed low power applications. Simulations were carried out to evaluate the accuracy of the noise margin model, which was verified. PFCSL gates were also simulated to verify the speed advantage under hysteresis.

In [65], a PFSCL style with higher speed than the existing PFSCL style is proposed where the load in existing PFSCL is replaced with a new load which exhibits capacitive coupling, which enhances the switching speed of the circuits. The capacitive coupling occurs between the output node and the gate of the PMOS load which speeds up the process of charging/discharging of the PFSCL gate. The mechanism of capacitive coupling is modelled and its effect on the propagation delay is described. On the basis of simulation of AND/NOR/OR gates based on proposed style versus conventional PFSCL based AND/NOR/OR gates; it is shown that the logic gates based on the propagation delay by 31 percent compared to existing PFSCL logic gates.

Implementation of logic gates based on conventional PFSCL is a NOR based implementation. This implies that, while PFSCL can implement OR/NOR functions easily as a single gate implementation, complex logical functions having sum-of-minterms expression requiring both AND/OR implementations are more difficult and require a multi-gate cascaded implementation. PFSCL multi-gate cascaded implementation adds to the delay and also increases the power dissipation due to the use of constant bias currents by each gate.

This factor negates a lot of the speed and power dissipation advantages of PFSCL. In [66], the use of triple-tail cell concept in conjunction with PFSCL, called the PFSCL fundamental cell, is proposed to solve the issue of multi gate implementation of complex logic. This is because triple-tail cell through the addition of control branch easily provides the AND functionality. Thus, by implementing PFSCL fundamental cell based gates, complex two input logic functions like XOR, multiplexer etc. including AND/NAND terms can be implemented without need for cascading the gates which in turn improves the delay and the power dissipation.

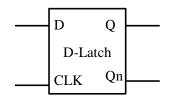

An efficient PFSCL fundamental cell based D-Latch is proposed and its performance is compared to PFSCL based D–Latch [66]. It is found that the proposed D-Latch shows lesser delay and lower power consumption compared to a PFSCL based D–Latch. Use of the triple-tail concept also reduces the number of stages and the gate count compared to conventional PFSCL based D–Latch.

In [69-74], an efficient circuit realisation scheme based on PFSCL style using generalized PFSCL fundamental cell, called the configurable logic block (CLB) is given and used to implement adder, serialiser, demultiplexer, linear feedback shift register (LFSR) and razor flip-flop respectively. From simulations carried out in CMOS 180 nm technology, it is seen that the proposed circuit utilising PFSCL fundamental cell architecture shows the best delay and power dissipation compared to conventional PFSCL based implementation.

PFSCL style suffers from the disadvantage of having constant bias current which contributes towards the power dissipation. With the increased need for power efficient circuits, a modification to the existing PFSCL style is proposed in [67] which addresses the issue. Here, a logic style called dynamic PFSCL (D-PFSCL) is introduced that uses dynamic current source in contrast to constant current source of PFSCL to attain lower power consumption. Two techniques to implement multi-stage D-PFSCL application are also suggested. Several D-PFSCL gates are simulated and compared with the respective PFSCL and significant power reduction is achieved for D-PFSCL gates. These gates also show an improvement in speed compared to existing PFSCL gates.

In [75], high speed and low power dissipation PFSCL based tristate buffers are proposed, which are important for bus implementation. The paper discusses existing PFSCL tristate buffers i.e. switch based and sleep based. While the sleep based tri state buffer is more power efficient than the switch based tristate, it suffers from incomplete isolation of the common output node from the tristate disabled buffers. Next in the paper, PFSCL tristate buffer switch based topologies are proposed where the output enable/disable switch is used to maintain the high impedance state and the load or the current source section is also modified to restrict the current flow during high impedance state. Four proposed topologies are simulated in CMOS 180nm and their parameters like propagation delay, power dissipation and output enable time are given. From simulation results, it is seen that one of the proposed topologies with modified current source section performs the best.

In [76], further improvements to high speed and low power dissipation PFSCL based tristate buffers as given in [75] are proposed. In the paper, the load section is modified to feed the enable signal to the PMOS load directly instead of adding a transistor in series to the load section to cut off the power supply to get tristate output. With this modified load section, three topologies are presented. Simulations are done to characterise the propagation delay, power dissipation and output enable time of the proposed topologies and these are compared against the topologies given in [75] as well as existing switch based topologies and it is found that one of the proposed topologies give the best performance. In [77], PFSCL based asynchronous pipeline implementation is explored based on both existing conventional PFSCL and a more efficient fundamental cell based PFSCL. Further, a new hybrid implementation of the pipeline is proposed. A FIFO sequencer is implemented using the three different architectures and it is observed that the hybrid implementation of asynchronous pipeline results in lesser number of gates as well as lower average power dissipation.

In [78], a clocked current comparator based on PFSCL is presented and its operation is verified through simulations using 90nm CMOS technology parameters. From simulations, it is seen that the proposed clocked current comparator is power efficient design.

In [79], the paper presents a modified configurable cell in PFSCL style that enhances the capability of existing configurable cell in realizing complex logic functions for the case when the fan-in increases. Three different realisation of magnitude comparator based on conventional NOR/OR gate, existing configurable cell and proposed modified configurable cell methods are introduced. The proposed modified configurable cell introduces one more transistor in the outer branch in parallel to the existing transistor and this leads to reduction in number of gates required to implement the magnitude comparator. SPICE simulations using TSMC CMOS 180nm technology parameters are used to verify functionality and compare the performance where the simulation results show that modified configurable cell-based comparator's performance is superior to its counterpart, thereby establishing the concept and its usefulness.

### 1.3 Motivation

One of the issues with PFSCL is that conventional NOR based implementation [37] leads to implementation of complex logic using multiple cascaded gates, where each is biased by constant current source, in turn leading to increased delay and power consumption. This issue can be resolved by exploring alternate implementation architectures for PFSCL style that support higher fan-in, optimise the implementation of complex logic circuits and thus lower the delay while also having beneficial effect on power consumption. An alternate implementation requiring lesser number of gates through which complex logic can be implemented is through PFSCL fundamental cell architecture [66]. Based on [66], any two input logic can be implemented in a single stage leading to power efficient design. Some improvement is suggested in [79] leading to further reduction in the number of gates required to implement a complex logic function. However, there is scope for more improvement in the performance in terms of delay, power and area. In SCL style, the multithreshold technique is explored with positive impact on performance parameters [48]. This has not been yet explored in PFSCL style. The impact on parameters like area, power and delay with the introduction of multithreshold technique in PFSCL fundamental cell architecture is explored in this thesis. Also, the implementation of any two input complex logic in PFSCL style can be carried out in a single stage using the PFSCL fundamental cell architecture, however, for implementation of logic function requiring higher fan in, it can be extended with the resultant advantage in performance and this is also explored in this thesis.

Another concern in modern VLSI design is that with the increased demand for portable electronics, the power consumption has to be as low as possible in order to limit overheating and facilitate portability, thus simplifying the design of packaging and heat dissipation. In the case of PFSCL style, where the static power consumption is a direct product of power supply and bias current, one of the ways to reduce the static power consumption is to explore D-PFSCL [67] further. The application of dynamic current source to various implementation architectures based on PFSCL style is expanded further in this thesis.

Another way in which the static power consumption can be reduced is by correspondingly reducing the supply voltage, and when the supply voltage is drastically reduced to the point where it is lower than the threshold voltage, the operation is in subthreshold region. Operation in this region has its own advantages and disadvantages. Logic circuit operation in the subthreshold region is explored for logic styles such as CMOS, SCL etc. in [81-100]. Operation of complex arithmetic circuits based on PFSCL has not yet been explored in the sub threshold region and this is explored in this thesis.

In this work, implementation of PFSCL style using different architectures is investigated to achieve the following objectives:

- a. Investigation into the effect of lower threshold voltage transistor in PFSCL based implementation

- b. Enhancement of conventional circuit realisation schemes for high fan in.

- c. Design of improved D-PFSCL architectures.

- d. Investigation into the use of PFSCL in sub threshold region.

In order to achieve the objectives, the following are the highlights of the work carried out:

- a. Two different architectures are proposed with the introduction of multithreshold technique in PFSCL based implementation leading to reduction in area and reduction in minimum power supply voltage respectively.

- b. PFSCL fundamental cell architecture is extended for higher fan-in such that three input complex logic circuits can be implemented in a single stage with advantage in delay and power consumption.

- c. D-PFSCL architecture is modified so that any two input logic function can be implemented in a single stage giving reduction in power consumption and speed.

d. Operation of PFSCL circuits in subthreshold region and its advantages compared to performance of CMOS circuits in subthreshold region is investigated.

### **1.4 Thesis Organization**

This thesis examines the proposed PFSCL based architectures so as to be able to implement complex logic with optimised delay, power and area. It also explores the PFSCL based architectures that can support higher fan-in and work as a dynamic logic. It further explores the PFSCL in subthreshold region of operation and details how the performance in subthreshold region may be improved. Chapter 2 investigates basic PFSCL operation and provides an overview of the logic style and includes an examination of performance characteristics of basic PFSCL gates. It also discusses in detail the PFSCL fundamental cell and dynamic PFSCL.

Chapter 3 discusses two new PFSCL based architectures based on multithreshold technique that introduce the low threshold voltage transistor— i) in pull down network and ii) in constant current source. The two new architectures are analysed and it is seen that the first architecture leads to reduction in area while the second leads to reduction in power consumption.

Chapter 4 discusses a new PFSCL architecture that increases the fan-in and thus enables the implementation of complex logic in reduced number of cascaded stages leading to reduction in delay and power dissipation.

Chapter 5 builds upon the work done in D-PFSCL and presents ways to implement complex logic circuits in PFSCL style using dynamic current source and requiring lesser number of stages for implementation with improvement in delay and power consumption.

Chapter 6 examines the behaviour of circuit implemented using PFSCL style operating in subthreshold region. This region of operation is suitable for ultra low power applications, used for biomedical, implantable devices and devices used in sensor networks. The circuits implemented using PFSCL style in subthreshold region offers benefits compared to CMOS in subthreshold region and these results are presented.

Chapter 7 provides a final summary of the work throughout the thesis and summarizes avenues of potential future work where many projects or theses could build upon the base line principles established here.

Chapter 2 Existing PFSCL architectures

### 2.1 Introduction

In the previous chapter, the PFSCL literature survey is discussed followed by the observations on research gaps for further work in this thesis. The existing structures that have been picked are therefore discussed to better understand their working principle, design and their benefits. The architectures that are discussed in this chapter include basic PFSCL style with NOR based architecture, PFSCL fundamental cell architecture, D-PFSCL architecture.

### 2.2 PFSCL Style Fundamentals

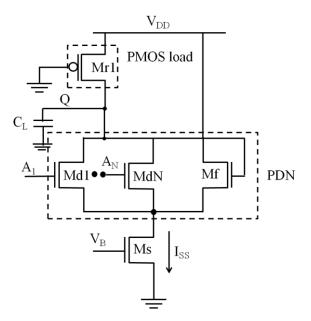

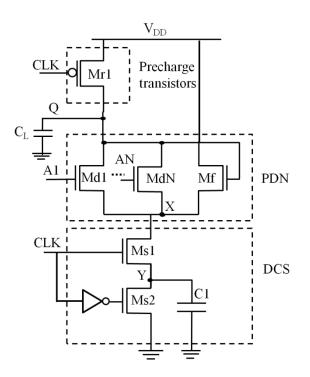

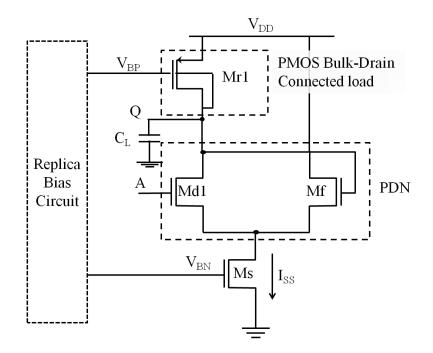

The Positive Feedback Source Coupled Logic (PFSCL) [37] is a modified form of singleended SCL style. This logic style introduces a positive feedback into the conventional singleended SCL style to improve the switching speed of the gates and is targeted towards high speed and low power dissipation. Basic architecture of a generic PFSCL gate is given in Fig. 2.1.

Fig. 2.1 Basic architecture of a generic PFSCL gate

It consists of three major parts: a pull-down network (PDN) comprising of transistors Md1-MdN along with feedback transistor Mf, a constant current source realized by transistor (Ms) and a load transistor (Mr1). The circuit works on the principle of current steering.

Based on the logic level of the inputs  $A_1$ - $A_N$ , the bias current  $I_{SS}$  flows through either Md1-MdN or Mf. If any of the inputs  $A_1$ - $A_N$  is/are high,  $I_{SS}$  flows through left side branch and is converted into equivalent output voltage by the PMOS Mr1 presenting equivalent resistance  $R_P$ . This is the output low voltage  $V_{OL}$ , given by  $V_{DD}$ - $I_{SS}R_P$ . For the case where logic inputs  $A_1$ - $A_N$  are low, the output remains high, given by  $V_{DD}$ , as no current is drained from the left side branch and consequently there is no voltage drop across the resistance  $R_P$ . This is the output high voltage  $V_{OH}$ , given by  $V_{DD}$ . The difference between  $V_{OH}$  and  $V_{OL}$  is called the voltage swing,  $V_{SWING}$ . From Fig. 2.1, it can be observed that output Q generates the NOR of all the inputs  $A_1$ - $A_N$ . For the case where the inputs are  $\overline{A_1}$ - $\overline{A_N}$ , the output Q is the AND of all the inputs. Correspondingly, the OR and NAND output can be taken from the drain of Mf, with help of De Morgan's law. Thus, the architecture of the conventional PFSCL based gate leads to direct implementation of NOR/OR functions. However, from the architecture, it is observed that for implementation of logic functions that are sum-of-minterms expression, multiple gates are needed, each gate implementing either a AND/NAND or an OR/NOR function.

#### 2.2.1 **PFSCL** operation and analysis

To analyze its behaviour, a PFSCL inverter as shown in Fig. 2.2 is considered. The operation of the PFCSL inverter is explained as follows: Based on the logic level of the input A, the bias current  $I_{SS}$  flows through either Md1 or Mf. For the case when input A is high,  $I_{SS}$  flows through Md1 and is converted into equivalent output voltage by the load transistor Mr1 presenting equivalent resistance  $R_P$ . This is the output low voltage  $V_{OL}$ , given by  $V_{DD}$ - $I_{SS}R_P$ .

For the case where logic inputs A is low, the output remains high, given by  $V_{DD}$ , as no current is drained from the left side branch and consequently there is no voltage drop across the resistance  $R_P$ . This is the output high voltage  $V_{OH}$ , given by  $V_{DD}$ . The difference between  $V_{OH}$  and  $V_{OL}$  is called the voltage swing,  $V_{SWING}$ .

Fig. 2.2 PFSCL inverter [37]

The analysis of the PFSCL inverter is done with approximations such that designing of any PFSCL circuit can be done through hand calculations as described in [37]. The analysis is presented in two parts: static model and delay model. The quantities such as voltage swing  $(V_{SWING})$ , small-signal voltage gain  $(A_v)$  and the noise margin (NM) are constituents of static model and are mathematical represented.

The values of high, low output voltages ( $V_{OH}$  and  $V_{OL}$ ) and  $V_{SWING}$  are respectively given as

$V_{OL} = V_{DD} - I_{SS} R_P \tag{2.1b}$

$$V_{SWING} = I_{SS}R_{P}$$

(2.2)

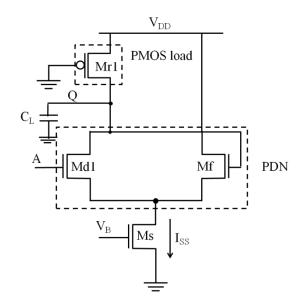

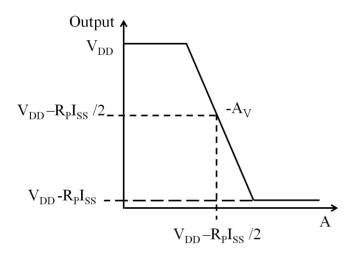

Fig. 2.3 Voltage transfer characteristics of the PFSCL inverter

The voltage transfer characteristics (VTC) of the PFSCL inverter is shown in Fig. 2.3. It may be noted that VTC is symmetrical around the logic threshold voltage ( $V_{LT}$ ). The small-signal voltage gain ( $A_V$ ) is evaluated around  $V_{LT}$ . The value of  $A_V$  is computed around the  $V_{LT}$  by using superposition of the input voltages at the gate of the transistors Md1 and Mf, and is given as

$$A_{\rm V} = \frac{\frac{g_{\rm mn}R_{\rm P}}{2}}{1 - \frac{g_{\rm mn}R_{\rm P}}{2}}$$

(2.3)

Where  $g_{mn}$  corresponds to the transconductance of the NMOS transistor and its value around the V<sub>LT</sub> is  $\sqrt{\mu_n C_{ox} \frac{W_N}{L_N} I_{SS}}$ .

The NM of a PFSCL inverter [61] is given by (2.4).

$$NM = \frac{V_{SWING}}{2} f \left( \frac{g_{mn} R_P}{2} \right)$$

(2.4)

where function f is expressed as

$$2\sqrt{\frac{1}{2}\left(1-\frac{1}{16x^{2}}\right)\left(1-\sqrt{1-\frac{1-\frac{1}{4x^{2}}}{\left(1-\frac{1}{16x^{2}}\right)^{2}}}\right)\left\{2\sqrt{1-\frac{1}{2}\left(1-\frac{1}{16x^{2}}\right)\left(1-\sqrt{1-\frac{1-\frac{1}{4x^{2}}}{\left(1-\frac{1}{16x^{2}}\right)^{2}}\right)-\frac{1}{x}}\right\}}$$

(2.5)

For  $x = \frac{g_{mn}R_P}{2} < 1$ , the function of (2.5) can be approximated by (2.6)

$$f(x) = 1.4x - 0.65$$

(2.6)

The function exhibits hysteresis for x greater than unity. The above relation is valid for  $x = \frac{g_{mn}R_P}{2} < 1$ , whereas it 1. Alternatively, by using the piecewise-linear approximation of the VTC [61], the NM can also be computed as

$$NM = \frac{V_{SWING}}{2} \left( 1 - \frac{1}{A_V} \right)$$

(2.7)

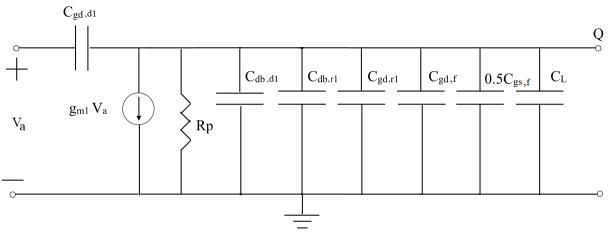

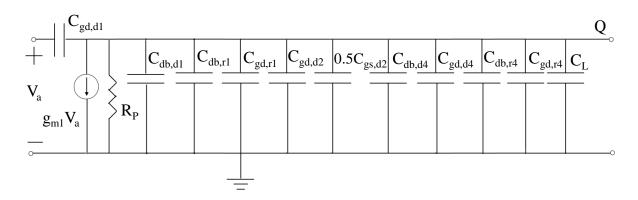

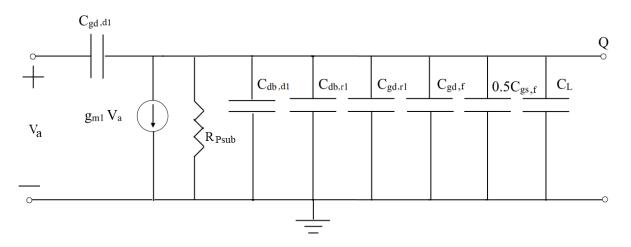

Fig. 2.4 Linear half circuit

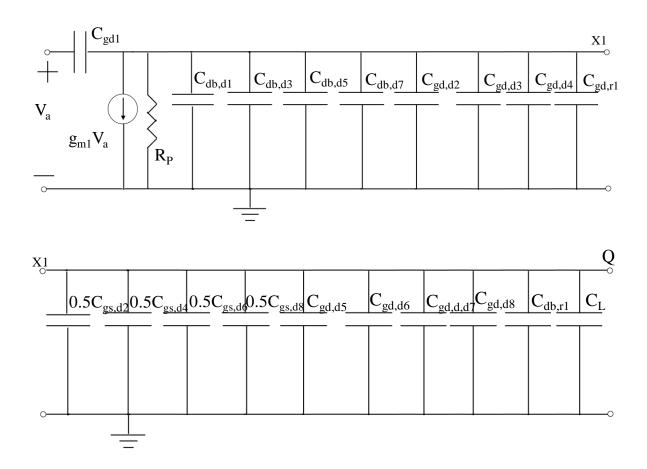

To evaluate the propagation delay, the circuit may be linearised around the logic threshold. The presence of feedback, however, makes the analysis complex and an alternate approach is given in [62] which suggests the use of half circuit model depicted in Fig. 2.4. The propagation delay is computed as

$$\tau_{PD} = R_P C_{out} = R_P (C_{db,d1} + C_{gd,d1} + C_{db,r1} + C_{gd,r1} + C_{gd,f1} + \frac{1}{2} C_{gs,f} + C_L)$$

(2.8)

Here,  $C_{out}$  represents overall capacitance at the output node and includes capacitive contribution of the transistors and the external load capacitance  $C_L$ . The drain-bulk junction capacitance ( $C_{db}$ ), the gate-to-source capacitance ( $C_{gs}$ ) and the gate-to-drain capacitance ( $C_{gd}$ ) are capacitive contribution from transistors in PDN (Md1-Mf) and load section (Mr1). For the transistors operating in saturation region, only overlap capacitance need be considered. Therefore, the  $C_{gst}$  contribution from NMOS transistors will be equal to  $C_{gst}W_N$  where  $W_N$  represents width of NMOS transistor in PDN [62]. As the PMOS transistor in load section operates in linear region, so both overlap capacitance and the intrinsic contribution associated with its channel charge [62] are taken into account. The contribution of junction capacitance for the transistors is adopted from [62]. The Miller effect associated with the gain from the gate-to-source makes capacitance contribution of transistor Mf into  $\frac{1}{2}C_{gs}$  [62]. Further,  $R_P$  in Fig. 2.4 is the equivalent resistance of the PMOS Mr1, given as in (2.11).

Based on the expressions for small signal voltage gain, voltage swing etc. the design approach of a PFSCL inverter for a given value of the bias current  $I_{ss}$  and the noise margin is presented in [62]. Considering saturation region operation of NMOS transistors in the PDN and  $g_{mn}R_P/2=1$ , the value of voltage swing for a specified value of NM is computed using (2.4) as

$$V_{SWING} = \frac{2NM}{f(1)} = 2.7NM$$

(2.9)

Once the voltage swing is obtained, the next step is to size load transistor with equivalent resistance  $R_P$  (=V<sub>SWING</sub>/I<sub>SS</sub>). The equivalent resistance, of minimum sized PMOS transistor ( $R_{Pmin}$ ), is assessed first which is followed by determining the bias current I<sub>HIGH</sub> using (2.10)

$$I_{\text{HIGH}} = \frac{V_{\text{SWING}}}{R_{\text{Pmin}}}$$

(2.10)

If the computed value of bias current is higher than  $I_{HIGH}$ , then  $R_P < R_{Pmin}$ . To achieved this, LP is set to its minimum value (LMIN) and the required WP is computed using the standard BSIM3v3 MOSFET model [80] given by (2.11) as

$$R_{\rm P} = \frac{R_{\rm int}}{1 - \frac{R_{\rm DS}}{R_{\rm int}}}$$

(2.11)

where  $R_{DS} = \frac{(R_{DSW}^{*1E-6)}}{W_P}$  models the source/drain parasitic resistance with  $R_{DSW}$  as the empirical model parameter,  $W_P$  as the width of the PMOS load transistors and  $R_{int}$  as the intrinsic resistance of the load transistor in the linear region given as

$$R_{int} = \left[\mu_{effp} C_{ox} \frac{W_{P}}{L_{P}} (V_{DD} - |V_{TP}|)\right]^{-1}$$

(2.12a)

$$W_{P} = \frac{I_{SS}}{V_{SWING}} \frac{L_{Pmin}}{\mu_{effp} C_{ox} (V_{DD} - |V_{TP}|) \left( 1 - \frac{R_{DSW} 10^{-6} \mu_{effp} C_{ox} (V_{DD} - |V_{TP}|)}{L_{Pmin}} \right)}$$

(2.12b)

Similarly, if  $I_{SS} < I_{HIGH}$ , then the value of  $R_P > R_{Pmin}$ . In such case minimum value is taken for  $W_P$  and the values of WMIN and LP are calculated from (2.11) as

$$L_{P} = \mu_{effp} C_{ox} W_{Pmin} \left( V_{DD} - |V_{TP}| \right) \left[ \frac{V_{SWING}}{I_{SS}} - \frac{R_{DSW} 10^{-6}}{W_{Pmin}} \right]$$

(2.13)

After this, the dimensions of transistors in the PDN (Md1, Mf1) are derived by substituting  $\frac{g_{mn}R_{p}}{2} = \sqrt{\mu_{n}C_{ox}\frac{W_{N}}{L_{N}}\frac{1}{I_{ss}}} * \frac{V_{SWING}}{2}$ in the derived equation of A<sub>V</sub> in (2.3). The width W<sub>N</sub> of the PDN

transistors is calculated as.

$$W_{N} = \left(\frac{A_{v}}{1 - A_{v}}\right)^{2} \frac{L_{Nmin}I_{SS}}{2\mu_{n}C_{ox}V_{SWING}^{2}}$$

(2.14)

If bias current is taken lower than supported by minimum sized NMOS transistor, ( $I_{LOW}$ ) then (2.14) yields in a value smaller than the minimum channel width. The  $W_N$  is also set to minimum value  $W_{Nmin}$  in such cases. Using (2.14),  $I_{LOW}$  is given by (2.15).

$$I_{LOW} = \frac{1}{4} \frac{W_{Nmin}}{L_{min}} \mu_n C_{ox} V_{SWING}^2$$

(2.15)

Further to the discussion on the design of the gates, the minimum power supply,  $V_{DDmin}$  under which the PFSCL inverter can function correctly is also calculated. This is an important parameter as knowing the minimum power supply can provide scope in reducing the static power dissipation, which is directly proportional to the power supply and is given by  $V_{DD}$ .I<sub>SS</sub>. For any source coupled logic gate with N levels of source coupled transistor pair, the  $V_{DDmin}$ can be expressed as:

$$V_{DDmin} = (N+1)V_{B} - (N-1)V_{TN} - V_{Tcurr}$$

(2.16)

Where  $V_{TN}$ ,  $V_B$ , and  $V_{Tcurr}$  represent the typical threshold voltage, bias voltage and threshold voltage for current source respectively. With the PFSCL inverter having single level of source coupled transistor pair i.e. N=1, the minimum power supply ( $V_{DDmin}$ ) given by (2.16) changes to:

$$V_{\text{DDmin}} = 2V_{\text{B}} - V_{\text{Tcurr}}$$

(2.17)

## 2.2.2 Realisation of Conventional PFSCL gates

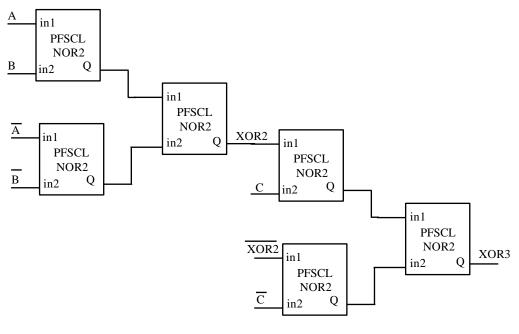

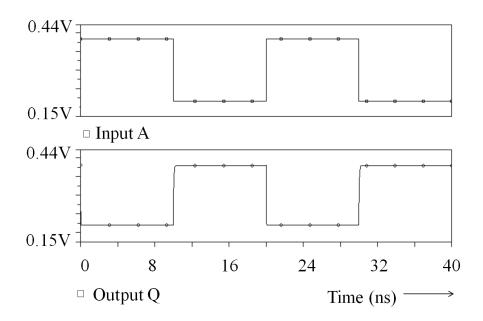

The PFSCL realisation of generic N input NOR and NAND gates are discussed in section 2.2 and shown in Fig. 2.5a and Fig. 2.5b respectively. Based on this, the 2 input XOR (XOR2) PFSCL gate requires two levels as shown in Fig. 2.5c. Other complex gates can also be implemented in similar way.

(a)

(b)

Fig. 2.5 PFSCL style a) NOR2 b) NAND2 c) XOR2

## 2.3 PFSCL fundamental cell architecture

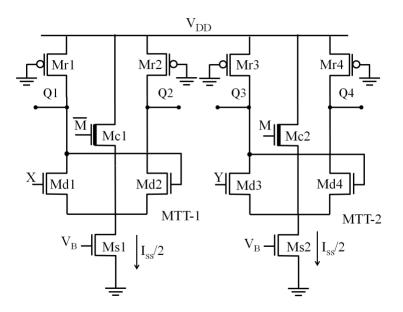

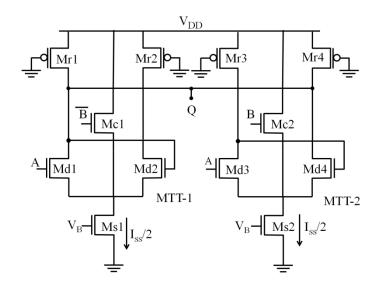

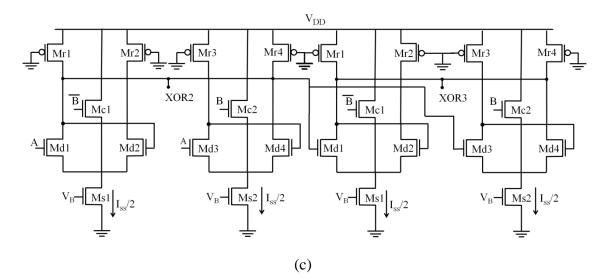

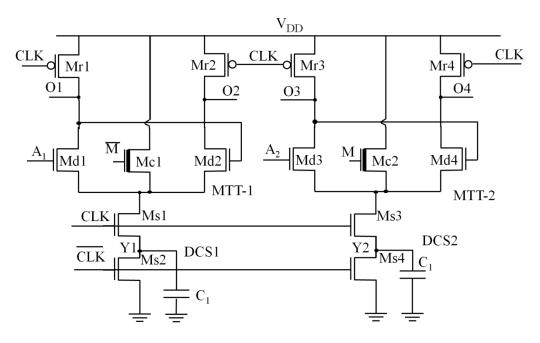

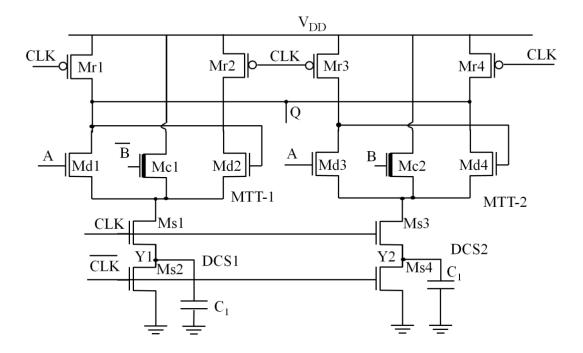

In the previous section, we discussed conventional PFSCL style, where the gates are implemented using NOR based architecture [37]. As we saw for the case of XOR2 gate and similarly for other complex logic, conventional PFSCL based implementation leads to multiple cascaded PFSCL gates with corresponding increase in its delay and power. This issue is mitigated in [65], which proposes a new architecture, called fundamental cell, that can implement any 2-input complex logic function in a single stage, thus reducing the number of cascaded stages needed for function implementation.

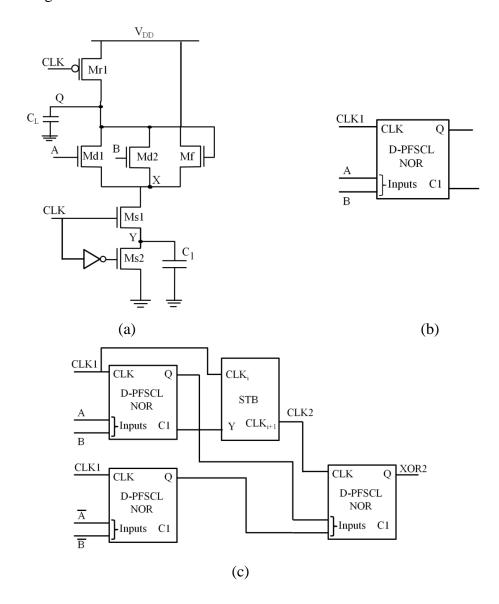

A D-latch based on PFSCL fundamental cell architecture (PFSCL FC) is shown in Fig. 2.6a [66], with the associated block diagram in Fig. 2.6b. The fundamental cell is based on the triple-tail cell concept, consisting of two triple-tail cells TT-1:(Md3, Mc1, Md4) and TT-2: (Md5, Mc2, Md6) biased by separate current sources of  $I_{SS}/2$  value such that the new cell draws the same current as that of the single traditional PFSCL gate. The said D-latch also uses a PFSCL inverter in the first stage to generate complement of the CLK input. Comparing

this implementation with a NOR based implementation that needs 6 NOR gates and 3 stages, it is observed that the PFSCL FC offers advantages in terms of delay and power dissipation.

Fig. 2.6 a) PFSCL FC based D-Latch [66] b) Block representation

The transistors Ms1 and Ms2 operate in saturation in order to maintain a constant bias current of  $I_{SS}/2$  value. The four PMOS transistors (Mr1, Mr2, Mr3 and Mr4) work as load. To realize a D-latch, the transistors Mc2 and Mc1 are driven by the input clock (CLK) and its complement. The complement of the CLK is generated by the PFSCL inverter in the first stage. Mc1 and Mc2 are connected between the supply terminal and the common source terminal of transistor pairs Md3–Md4 and Md5–Md6 respectively, as shown in Fig. 2.6. A high voltage on CLK turns ON the transistor Mc2, and deactivates the transistor pair Md5–

Md6. At the same time, the transistor Mc1 turns OFF so that the transistor pair Md3–Md4 generates the output according to the input D. For the case when CLK is low, the transistor pair Md3–Md4 gets activated and preserves the previous output. Thus, the PFSCL FC based D-latch models the positive level sensitive D-latch.

Proper operation demands that when either Mc1 or Mc2 is ON, the side transistors Md3-Md4 or Md5-Md6 should be OFF. However, if all transistors are of the same dimension, then this would not be possible. When a triple-tail cell is inactive i.e. Mc1 or Mc2 is ON, it has to be ensured that all of the bias current flows through the central branch and not through the side branches. If the dimensions of all the transistors in the PDN are the same, then the current would get equally divided between the side branch and the central branch for the case where side branch is also ON along with the central branch. To avoid such a situation, the central branch in the triple-tail cell is designed to have a dimension which is N times the dimensions of the side branch, ensuring the majority of the bias current flows through the central branch deactivating the cell properly. Further, at any given time, either of the two cells (TT-1/TT-2) gets activated and determines the output of the gate.

## 2.3.1 Fundamental cell operation and analysis

To analyse the operation of the fundamental cell, a OR2 gate is considered, as in Fig. 2.7.

Fig. 2.7 Fundamental cell based OR2 gate

In the OR2 gate, for the case when B is asserted high, TT-1 is activated while TT-2 gets deactivated. In this case, since for OR2 gate the output should be logic high irrespective of the value of input A, and the TT-1 is driven by  $V_{DD}$ . The other TT-2 does not contribute to the output since whole of the bias current  $I_{SS}/2$  flows through Mc2. Further, for the case where input B is low, TT-1 is deactivated and TT-2 contributes to the output, which in this case depends on the input A. The general expression for the current flowing through the central branch (Mci) and side branch (Mdi), keeping in mind that the ratio of dimensions of central branch to side branch is N, is as in (2.18). The value of N is generally taken from 5-20.

$$I_{Mdi} = \frac{I_{SS}}{2} \frac{1}{N+1}$$

$$I_{Mci} = \frac{I_{SS}}{2} \frac{N}{N+1}$$

(2.18)

Considering all the input combinations for the OR2 gate, the currents through the central branch and the side branches were derived using which the output high voltage and output

low voltage were derived. The output voltage is decided by the currents flowing through Md2 and Md4. Table 2.1 gives the output voltages for various combinations of inputs.

| S.No. | b. Inputs |      | Output voltage V <sub>Q</sub>                                            |  |

|-------|-----------|------|--------------------------------------------------------------------------|--|

|       | A         | В    |                                                                          |  |

| 1.    | High      | High | $V_{OH} = V_{DD}$                                                        |  |

| 2.    | Low       | Low  | $V_{OL1} = V_{DD} - \frac{R_P I_{SS}}{2} \left(1 + \frac{1}{N+1}\right)$ |  |

| 3.    | High      | Low  | $V_{OL2} = V_{DD} - \frac{R_P I_{SS}}{2}$                                |  |

| 4.    | Low       | High | $V_{OL2} = V_{DD} - \frac{R_P I_{SS}}{2}$                                |  |

Table 2.1 Output voltages for various combinations of inputs

Since there are two values of output low voltage  $V_{OL1}$  and  $V_{OL2}$ , there are two values of voltage swing, as given in (2.19).

$$V_{SWING1} = \frac{R_{P}I_{SS}}{2} \left( 1 + \frac{1}{N+1} \right)$$

(2.19a)

$$V_{SWING2} = \frac{R_P I_{SS}}{2}$$

(2.19b)

For large values of N, the voltage swing V<sub>SWING</sub> can be approximated as:

$$V_{SWING} = \frac{R_P I_{SS}}{2}$$

(2.20)

where  $R_P$  is the equivalent PMOS resistance given in [37].

The small signal voltage gain,  $A_V$  and the noise margin, NM for the new fundamental cell are computed by the method outlined in [37] and are given in (2.21) and (2.22) respectively.

$$A_{V} = \frac{g_{mn}R_{P}/2}{1-g_{mn}R_{P}/2}$$

(2.21)

30

$$NM = \frac{V_{SWING}}{2} \left( 1 - \frac{1}{A_V} \right)$$

(2.22)

Where  $g_{mn} = \sqrt{\mu_n C_{ox} \frac{W_N}{L_N} \frac{I_{ss}}{2}}$ , is the transconductance of the transistors Md1-Md4,  $\mu_n$ ,  $W_N$  and  $L_N$  are the effective electron mobility, the effective channel width and length of the said transistors, respectively.

The use of fundamental cell offers high performance circuits but there exists a limitation in terms of area requirement. The proper operation of fundamental cell requires that the complete bias current  $I_{SS}/2$  should flow through the centre transistor in a deactivated triple-tail cell. But in practice it is difficult to achieve since the bias current  $I_{SS}/2$  divides between the centre branch and one of the two outer branches as both of them are driven by high inputs. To address this limitation and facilitate proper activation/ deactivation, the aspect ratio of centre transistors is made N times of the outer transistors [66]. However, it is obvious that while realizing complex function this approach leads to significant area overhead due to larger aspect ratio of centre transistors.

#### 2.3.2 Implementation of gates

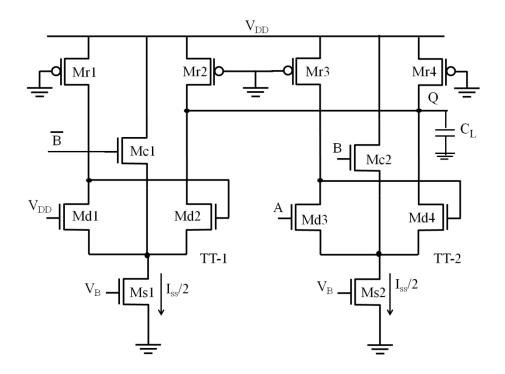

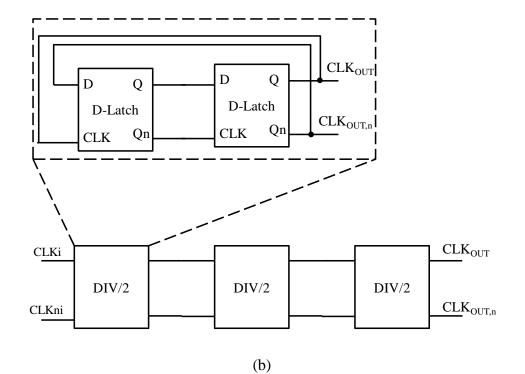

The concept of fundamental cell is generalized by defining a configurable logic block (CLB) [69], as shown in Fig. 2.8. It consists of a PFSCL inverter to generate complement of input M and two triple-tail cells (TT-1, TT-2) and can be configured to realise various two input logic functions. Its usage has also been extended to efficiently realize complex circuits such as comparators, adders, multipliers, LFSR etc. [70-74].

Fig. 2.8 CLB [71]

The mapping of various inputs to X, Y and  $\overline{M}$  and interconnection of the outputs Q1-Q4 for the implementation of various two input logic functions like XOR2, MUX2 etc. is given in the following Table 2.2.

| Logic    | Actual    | Mapping with the CLB inputs |    |    | Output nodes |

|----------|-----------|-----------------------------|----|----|--------------|

| Function | Inputs    | М                           | X  | Y  |              |

| OR       | A, B      | В                           | В  | А  | Q2, Q4       |

| NOR      | A, B      | В                           | В  | А  | Q1, Q3       |

| NAND     | A, B      | В                           | А  | В  | Q1, Q3       |

| AND      | A ,B      | В                           | А  | В  | Q2, Q4       |

| XOR      | A, B      | В                           | А  | А  | Q1, Q4       |

| XNOR     | A, B      | В                           | А  | А  | Q2, Q3       |

| MUX      | SEL,I0,I1 | SEL                         | I1 | IO | Q2, Q4       |

Table 2.2 Realisation of different logic functions using CLB

From the architecture, it is further observed that any two input complex function can be easily implemented using fundamental cell, however, three input complex logic functions would require cascading of two fundamental cell based gates.

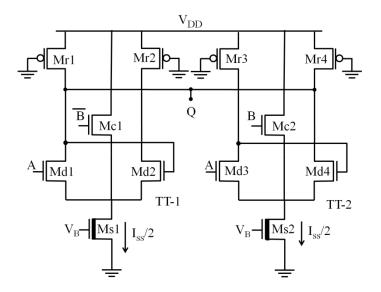

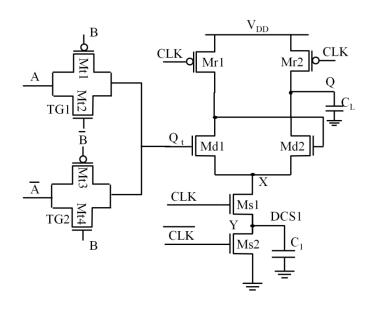

## 2.4 Dynamic PFSCL (D-PFSCL)

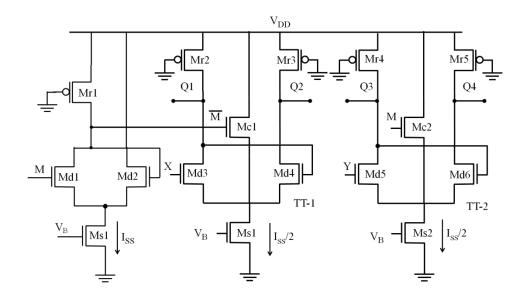

The Dynamic Positive Feedback Source Coupled Logic (D-PFSCL) gates [67] are designed by adapting the method suggested for differential dynamic gates in [52, 56] and they show an improvement in speed and power consumption over the static PFSCL counterpart. Like static PFSCL, the D-PFSCL supports only NOR/OR operation and the structure of a D-PFSCL inverter is shown in Fig. 2.9. It comprises of three main parts namely a pull down network (PDN), precharge transistors and a dynamic current source (DCS).

Fig. 2.9 D-PFSCL inverter [67]

The PMOS transistor  $M_{r1}$  is the precharge transistor while the transistors  $M_{s1}$ ,  $M_{s2}$  and the capacitor  $C_1$  form the DCS. Both of these are driven by a clock (CLK) input. The PDN consists of transistor Md1-Mf, with Md1-driven by input A. The transistor  $M_f$  is driven by a feedback connection from the output node Q voltage to provide a feedback connection. The output node, Q provides the inverted output. However, in cases, where buffer output is required, then it is obtained by placing an additional precharge transistor Mr2 in Fig 2.9 and

then taking the output from its drain terminal (drain of  $M_f$ ). At any given instance, output from only one node is obtained as these gates belong to single-ended SCL gates.

A D-PFSCL gate operates in two phases known as precharge phase and the evaluation phase, depending on the CLK signal. For low value of CLK, the circuit works in precharge phase wherein the output node is charged to  $V_{DD}$  since the precharge transistor is ON. Simultaneously, the capacitor C<sub>1</sub> gets discharged to ground potential via the conducting M<sub>s2</sub> transistor. Further, any changes in the applied input A does not influence the output as M<sub>s1</sub> is OFF such that no conductive path can be established between the output nodes and ground. Alternatively, for high value of CLK, the logic function is evaluated since M<sub>s1</sub> is ON and the transistors M<sub>s2</sub>, M<sub>r1</sub> are OFF. In this evaluation phase, either the output remains at logic high i.e. V<sub>DD</sub> or discharges to logic low i.e. V<sub>DD</sub>-V<sub>SWING</sub>. The mechanism for fixing the voltage swing is discussed in the next section.

### 2.4.1 D-PFSCL operation and analysis

To achieve the required voltage swing  $V_{SWING}$  during the evaluation, the capacitor  $C_1$  is sized such that the output is discharged to the low level i.e.  $V_{DD}$ - $V_{SWING}$ . Using the charge conservation principle, we can write:

$$V_{DD}C_{OUT} = (C_{OUT} + C_1)(V_{DD} - V_{SWING})$$

$$(2.23)$$

where  $C_{OUT}$  is the total load capacitance at the output node which include the parasitic capacitances of the transistors and the external load capacitance  $C_L$ .

$$C_1 = \frac{(V_{SWING}C_{OUT})}{(V_{DD}-V_{SWING})}$$

(2.24)

In practice, the capacitor  $C_1$  is realized by a dummy transistor with its source and drain terminals connected together. Considering the width and length of dummy transistor to be  $W_{C1}$  and  $L_{C1}$ , the size of dummy transistor can be calculated as:

$$W_{C1}L_{C1} = \frac{(V_{SWING}C_{OUT})}{C_{ox}(V_{DD}-V_{SWING})}$$

(2.25)

where  $C_{\text{ox}}$ , is the gate oxide capacitance per unit area.

The D-PFSCL gates do not consume static power. This is due to the fact that there is no constant current path from the power supply to the ground because the transistor pairs  $M_{s1}$  and  $M_{s2}$  (Fig. 2.9) in the dynamic current source would never turn ON simultaneously. The D-PFSCL gates, however, consume dynamic power which is

$$P_{dyn} = C_{OUT} V_{DD} V_{SWING} f_{CLK}$$

(2.26)

where  $f_{CLK}$  is frequency of the clock signal.

The dynamic power consumption of the logic gates depends on the switching activity of the output node [1]. It is already known that for uniformly distributed inputs, the low-to-high transition probability for an N input gate is

$$\alpha_{L \to H} = \frac{N_0}{2^N} \tag{2.27}$$

where  $N_0$  is the number of zero entries in the truth table of the logic function. Thus, the power consumption of an N-input D-PFSCL gate with transition probability  $\alpha_{L \to H}$  is given as:

$$P_{dyn} = \alpha_{L \to H} C_{OUT} V_{DD} V_{SWING} f_{CLK}$$

(2.28)

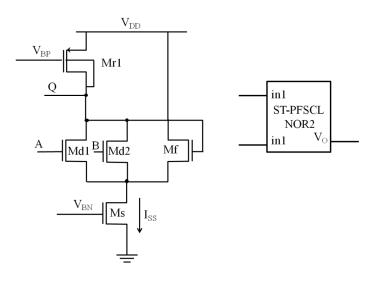

### 2.4.2 Realisation of gates

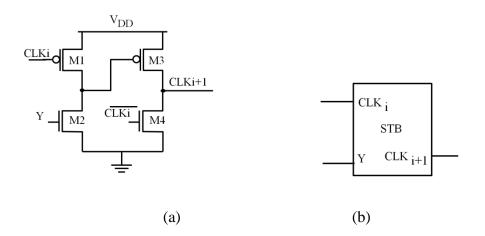

To implement complex logic, multiple D-PFSCL gates need to be cascaded and D-PFSCL gates are cascaded by two methods: one by inserting a PFSCL inverter in between each stage so that only a low to high transition at the output will occur and will avoid erroneous outputs of the subsequent stages. However, insertion of PFSCL inverter leads to static power consumption that contradicts the basic aim of the proposed logic style. Second method involves inserting a self-timed buffer (STB) to avoid malfunction because of the succeeding stage, after the preceding stage output has stabilized ensuring that the evaluation of a succeeding stage starts only after the completion of evaluation in its preceding stage [56]. The STB uses two clocked cascaded inverters as shown in Fig. 2.10a, with its symbol shown in Fig.2.10b. The CLK signal (CLK<sub>i</sub>) and the node Y voltage in dynamic current source of the preceding state (stage i) drives the first inverter. The output of STB (CLK<sub>i+1</sub>) is now given as the CLK signal to the subsequent stage (stage i+1).

Fig. 2.10 STB a) MOS schematic b) symbol

The overall power consumption for multi-stage D-PFSCL gate based on use of STB between the stages with K D-PFSCL identical gates and M identical STBs can be approximated as Where  $C_{STB}$  is the capacitance at drain of M1-M2 of STB (and consequently of M3-M4 of STB) and the factor of 2 is due to the two transistor pairs M1-M2, M3-M4.

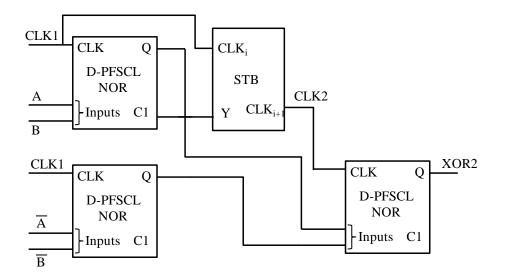

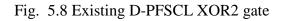

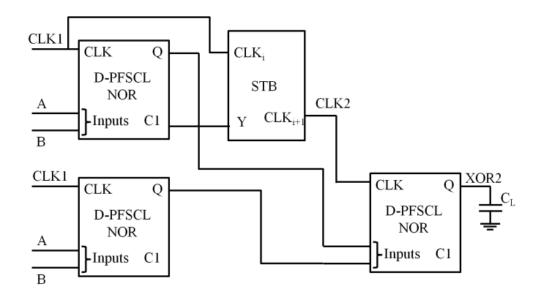

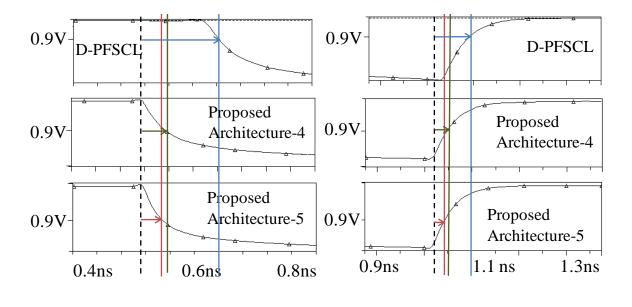

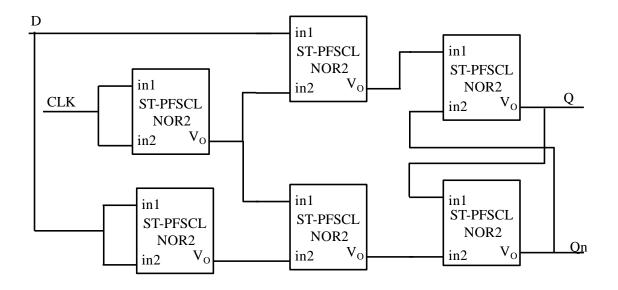

An implementation of 2-input D-PFSCL XOR gate is shown in Fig. 2.11c using 2-input D-PFSCL NOR gates (Fig. 2.11a) with symbol as in Fig.2.11b using an intermittent STB (Fig. 2.10b). Similarly, the 3-input D-PFSCL XOR gate can be implemented by connecting two identical XOR gates.

Fig. 2.11 a) D-PFSCL NOR2 b) D-PFSCL NOR2 symbol c) D-PFSCL XOR2 gate [66]

# 2.5 Conclusion

In this chapter, the analysis and design of the existing PFSCL architectures are presented. The modelling of static parameters and delay is discussed under fundamentals of PFSCL style which is followed by design considerations. PFSCL FC is also described and its advantages in realizing XOR2 gate are also elucidated. The D-PFSCL, a dynamic variant of PFSCL which helps in avoiding static power consumption is next discussed. The operation, design and methods for cascading D-PFSCL gates are also elaborated.

Chapter 3 Multithreshold PFSCL Architecture

## 3.1 Introduction

Multithreshold technique is widely used for achieving higher speed in active mode of operation and lowering power in sleep mode [49]. The use of lower threshold transistor provides higher current drive and this fact may be exploited in reducing device dimensions. It is also seen that the minimum power supply for the operation for SCL and its variants depends on threshold voltage of the current source,  $V_{Tcurr}$ . Thus, the introduction of lower threshold transistor may help in reducing footprint as well as power supply.

This chapter focuses on two aspects of using low threshold transistor in PFSCL fundamental cell. It is introduced in central branch transistor to reduce the footprint, and in current source transistor to lower minimum power supply. Both their behaviours are analysed and supported by mathematical formulations followed by simulations.

### **3.2 Proposed architecture-1**

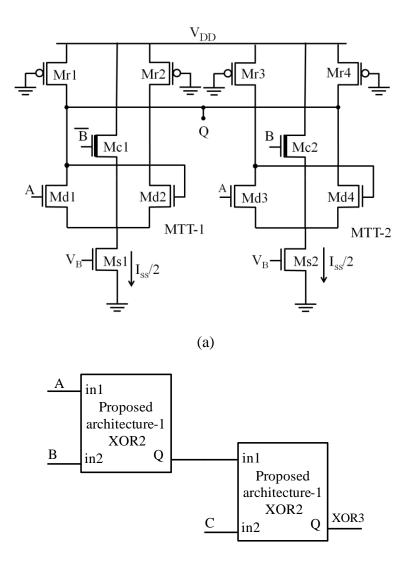

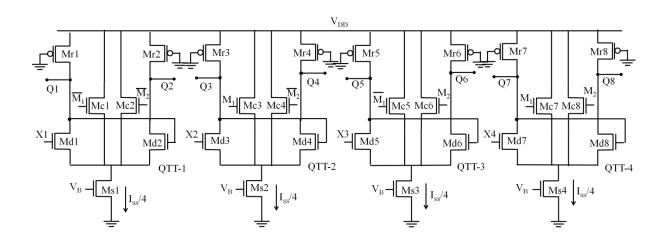

The existing PFSCL fundamental cell (PFSCL FC) [66] requires that for proper operation, the dimension of the centre transistor be N times the dimension of the outer transistors and this approach leads to significant area overhead due to larger aspect ratio of centre transistors. Proposed architecture-1 modifies the existing PFSCL FC [66] to include a low threshold voltage transistor as the centre transistor, instead of normal threshold voltage transistor.

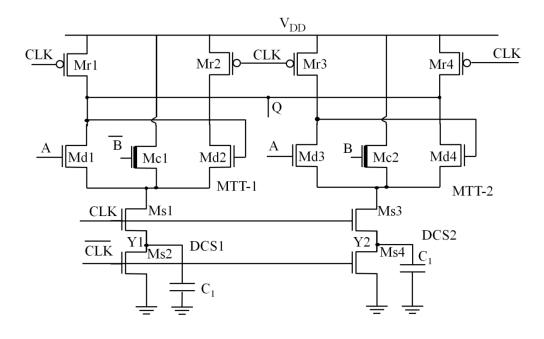

The proposed architecture-1 achieves activation/deactivation by lowering the threshold voltage of the centre transistor by a factor  $\alpha$  in comparison to the outer transistors. For understanding the working, consider the proposed architecture-1 based XOR2 gate given in Fig. 3.1a, with symbol as in Fig. 3.1b. The PDN has two modified triple-tail cells MTT-1 (Md1, Mc1, Md2) and MTT-2 (Md3, Mc2, Md4) each biased by I<sub>SS</sub>/2 with the inputs A, B and  $\overline{B}$ . In the schematic, the low threshold voltage centre transistors Mc1- Mc2 are made bold

to differentiate from others having typical threshold voltage. The transistors Mr1-Mr4 act as loads and generate the output voltage Q.

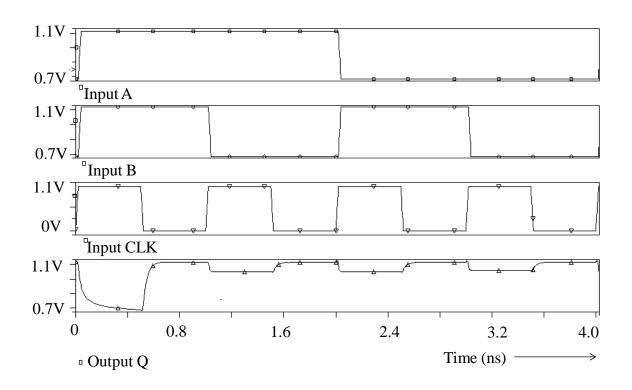

Fig. 3.1 Proposed architecture-1 a) XOR2 gate b) Symbol

From the schematic, the working of the proposed architecture-1 based XOR2 gate is as follows: As in the case of existing PFSCL FC, for proper operation of the gate, only one of the modified triple-tail cells MTT-1 or MTT2 is active, that is one of the central branches (Mc1-Mc2) is OFF (active) and the other is ON (inactive). Going further, for the case where input B is high, MTT-2 is inactive as Mc2 drains the bias current  $I_{SS}/2$  from  $V_{DD}$  and does not affect the output. This happens because Mc2 is low threshold voltage transistor compared to Md3-Md4 and conducts majority of the current even when Md3 or Md4 is ON. Thus, low 42

threshold voltage for Mc1-Mc2 enables correct operation. Correspondingly, MTT-1 is active for input B at high level, and the output Q is high if A is low else it is high. Similarly for the case when input B is low, MTT-1 is inactive and MTT-2 is active. In this case, if A is high, output Q is high else it is low. Thus, the functionality of the gate can be modeled as:

$$Q = \begin{cases} A & \text{if } B = 0 \\ \\ \overline{A} & \text{if } B = 1 \end{cases}$$

(3.1)