## Thesis

on

# Study and Modeling of Single and Multi Layer Graphene Field Effect Transistor Structures with Various Dielectric

submitted in the partial fulfilment of the requirements for the Degree of

# **DOCTOR OF PHILOSOPHY**

by

Mr. MUNINDRA Roll No. 2k17/Ph.D./EC/03

under the Supervision of Dr. Deva Nand Assistant Professor

# Department of Electronics and Communication Engineering Delhi Technological University, Delhi-India-110042 2021

#### ACKNOWLEDGMENT

I owe my debt and would like to express deep feelings of gratitude to accomplish the research program with the support and direction of several persons. This challenging and rewarding experience definitely helped me to grow in character as well as academically. It is a pleasant aspect that I have now the opportunity to express my gratitude for all of them.

First and foremost, I would like to thank my professor (Prof. Om Prakash Verma, Emeritus Prof. Data Ram Bhaskar, and Prof. Deva Nand) for their support and trust throughout the course of my PhD studies. Their substantial and thorough approach, together with his genuine interest in the research subject, turned my research work into a great experience. Words cannot express my gratitude to him for his patience and support.

My deepest thanks go to my parents for their unconditional love and support. Also, my heartiest thanks go to my family, my wife whose proximity, love & affection, and whose everyday early start day efforts made it possible to complete this research work. I admire her sincere efforts in providing support at various stages.

Finally, I would like to express my thanks to my friends (Tej Singh, Rahul Bansal, Rehan Mohd. Gazi, Rohit Kumar and Rahul Meena), my family, brothers (Jogender Singh, Ravinder, Vijender, Mintu, Sulender, Pankaj and Rajat Kumar) and sister-in lows Deeksha, my students and all those who supported me directly or indirectly.

Date: -

Place: -

Sign.: - MUNINDRA

DEPARTMENT OF ELECTRONICS AND COMMUNICATION DELHI TECHNOLOGICAL UNIVERSITY (Govt. of National Capital Territory of Delhi) BAWANA ROAD, DELHI, INDIA - 110042

Date:

#### CERTIFICATE

This is to certify that the work which is being presented in this thesis **"Study and Modeling of Single and Multi Layer Graphene Field Effect Transistor Structures with Various Dielectric"**, in partial fulfilment of the requirement for the Doctor of Philosophy in the Department of Electronics and Communication Engineering at Delhi Technological University, Delhi is an authentic record of my own work carried under the supervision of <u>Dr. Deva Nand, Assistant Professor</u>, Department of Electronics and Communication Engineering, Delhi Technological University. The matter presented in this research plan has not been submitted by me for the award of any other degree of this or any other Institute/University. If there is any copyright with this matter, then I will be responsible for any legal dispute.

Signature of Student Munindra, Roll no. 2K17/Ph.D./EC/03

This is to certify that the above statement made by the candidate is correct and true to the best of my knowledge and belief.

Dr. Deva Nand Supervisor Assistant Professor ECE Department Delhi Technological University

# Index

| List of Figures       | vi  |

|-----------------------|-----|

| List of Tables        | X   |

| List of Abbreviations | xi  |

| List of Publications  | xii |

|                       |     |

# Chapter one

| Introduction and Motivation                                                            | 01 |

|----------------------------------------------------------------------------------------|----|

| 1.1 Introduction                                                                       | 01 |

| 1.2 Motivation Graphene Flagship                                                       | 02 |

| 1.3 Limitless possibilities of the limitless layers of graphene and graphene composite | 03 |

| 1.4 Graphene Electronics and its wafer-scale integration                               | 06 |

| 1.5 Research objectives and findings of the thesis                                     | 07 |

# Chapter two

| Lite | erature | e survey                                                                    | 10   |

|------|---------|-----------------------------------------------------------------------------|------|

| 2.1  | Introdu | action                                                                      | 10   |

| 2.2  | Literat | ure survey                                                                  | 11   |

|      | 2.2.1   | Rise of Graphene                                                            | 11   |

|      | 2.2.2   | Limitations of GFET structure towards device logics, while have scope for h | nigh |

|      |         | frequency transistors                                                       | 13   |

|      | 2.2.3   | Graphene electronic properties and its limit on SiO <sub>2</sub> platform   | 15   |

| 2.3  | Prepara | ation Methods and Specific Properties of Graphene and other 2D materials    | 15   |

| 2.4  | Modell  | ling of GFETs                                                               | 20   |

| 2.5  | GFETs   | Structures                                                                  | 27   |

| 2.6  | Resear  | ch gaps                                                                     | 29   |

| 2.7  | Resear  | ch Objectives                                                               | 29   |

# Chapter three

| Study of Electronic Properties of Single and Bilayer Graphene gr/hBN Heterostructure |    |  |

|--------------------------------------------------------------------------------------|----|--|

| 3.1 Introduction and motivation                                                      | 30 |  |

| 3.2 Result and discussion                                                            | 32 |  |

| 3.3 Comparison                                                                       | 35 |  |

| 3.4 Chapter Summary                                                                  | 36 |  |

# Chapter four

| Nonlinear   | rity Analysis of Quantum Capacitance and its Effect on Nat            | no-GFET's   |

|-------------|-----------------------------------------------------------------------|-------------|

| character   | istics                                                                | 37          |

| 4.1 Introdu | uction and motivation                                                 | 37          |

| 4.2 Analyt  | tical model                                                           | 40          |

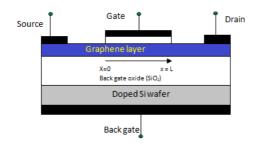

| 4.2.1       | Device structure of GFETs                                             | 40          |

| 4.2.2       | Formulation of charge carrier sheet density $(\rho_{gr})$ and quantum | capacitance |

|             | calculation $(C_q)$                                                   | 40          |

| 4.3 Drain   | current calculation                                                   | 45          |

| 4.4 Result  | and discussion                                                        | 46          |

| 4.5 Chapte  | er Summary                                                            | 53          |

|             |                                                                       |             |

# Chapter five

| Nonlinearity, Scaling Trends of Quasi-Ballistic GFETs Targeting RF Applications | 54 |

|---------------------------------------------------------------------------------|----|

| 5.1 Introduction and motivation                                                 | 54 |

| 5.2 Device structure and simulation setup                                       | 56 |

| 5.3 Static nonlinearity model of GETs model                                     | 58 |

| 5.4 Result and discussion                                                       | 61 |

| 5.5 Chapter Summary                                                             | 66 |

# Chapter six

| Conclusion and Future scope                                                            | 67    |

|----------------------------------------------------------------------------------------|-------|

| 6.1 Conclusion                                                                         | 67    |

| 6.2 Future scope                                                                       | 68    |

| 6.3 Modelling and simulation and realization of the GFETs devices with help of Euler's | s and |

| LaGrange's for Calculus of variable (COV) and Integral Equations (IE).                 | 69    |

| 6.4 Design and development of Graphene based sports hand rackets for game              | 70    |

| 6.5 Chapter summary                                                                    | 70    |

|                                                                                        |       |

| Appendix                                                                               | 71    |

|                                                                                        |       |

| References | 72 |

|------------|----|

|            |    |

#### **List of Figures**

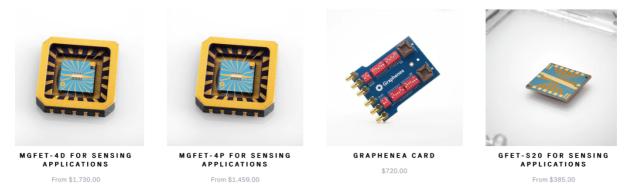

- Figure 1.1 The MGFET-4D, MGFET-4P GFET-S20, chip from Graphenea provides 36 graphene devices distributed in four quadrants with the devices in the centre of the chip and the probe pads located near the periphery of the chip [65].

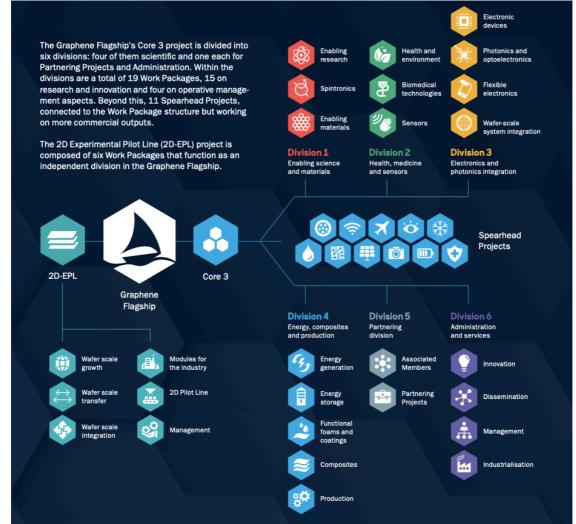

- Figure 1.2 Plan of action for the year 2022 and functional summary of development in the year 2021Of Graphene Flagship [2].

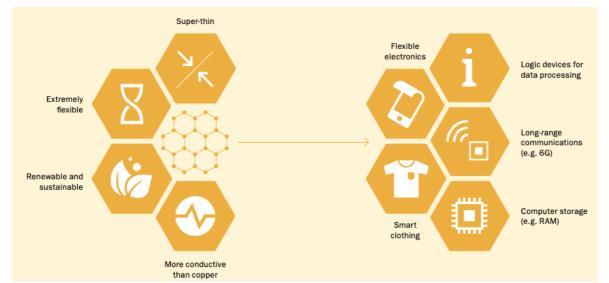

- Figure 1.3 Extraordinary properties of graphene towards its electronic applications with wafer-scale integration [2].

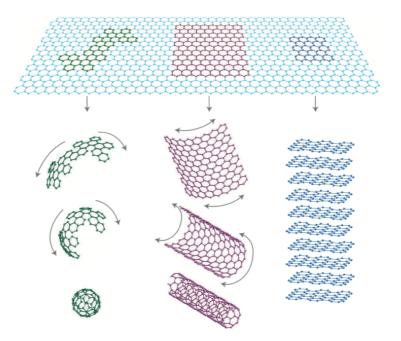

- Figure 2.1 Graphene the mother of all carbon forms graphite, graphene is a fundamental 2D building material for all (0D, 1D,3D) dimensions carbon 0D Buckyballs, 1D nanotube and 3D graphite stack [3].

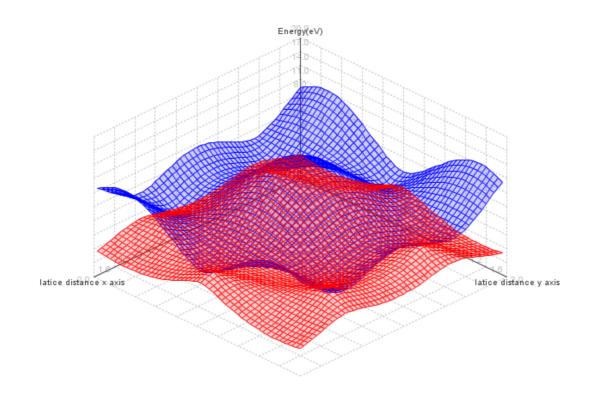

- Figure 2.2 Energy momentum graph shows six contact points of valance and conduction band called Dirac point.

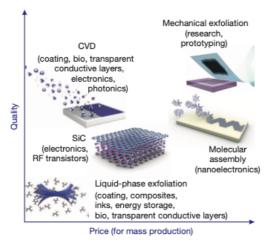

- Figure 2.3 Method of graphene preparation with applications of the particular graphene sheet [6].

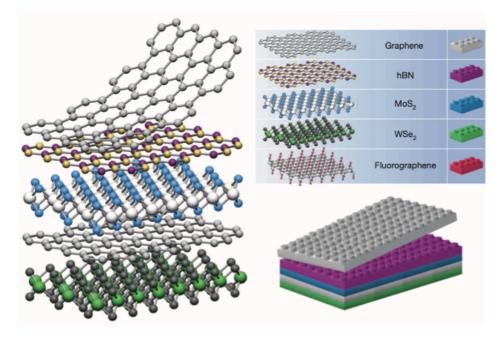

- Figure 2.4 layered structure of graphene other 2D layered materials [09]

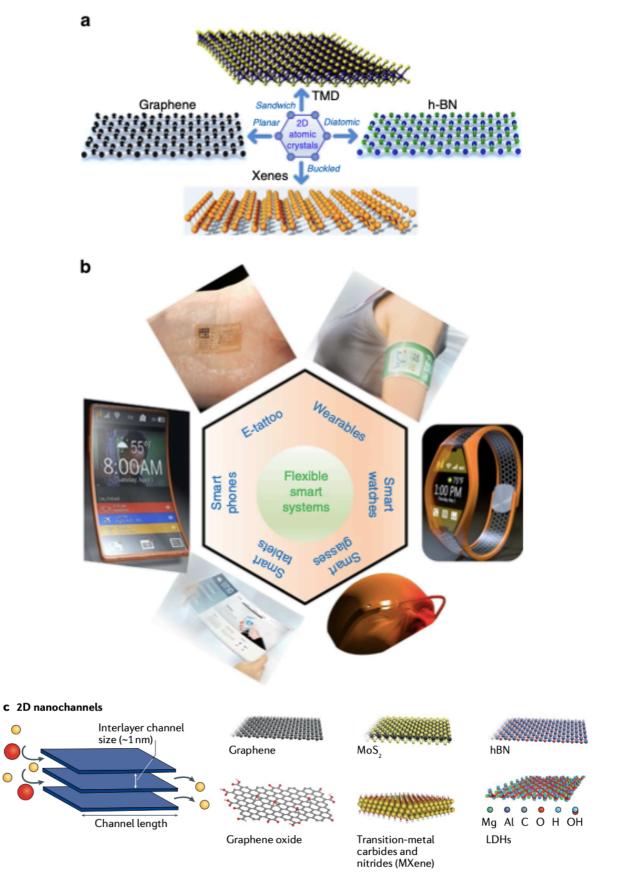

- Figure 2.5 a) Graphene and other 2d materials with their b) flexible electronic applications [12] c) sub-Nano channels [21].

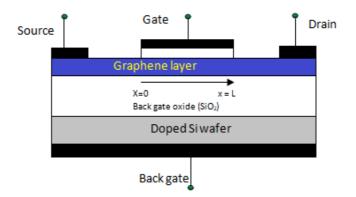

- Figure 2.6 Two-dimensional Cross-sectional view of the basic Graphene Field Effect Transistors

- Figure 2.7 Two-dimensional Cross-sectional view of the heterostructure Graphene Field Effect Transistors

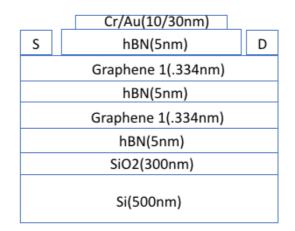

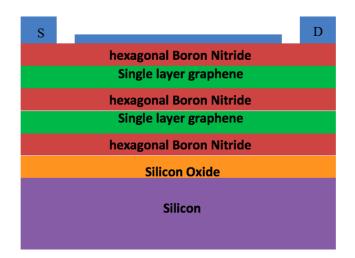

- Figure 3.1 Single layer Gr/hBN Heterostructure Fits for GFETs, with source, drain at top ends and gate in top middle with Ag/Cu metal.

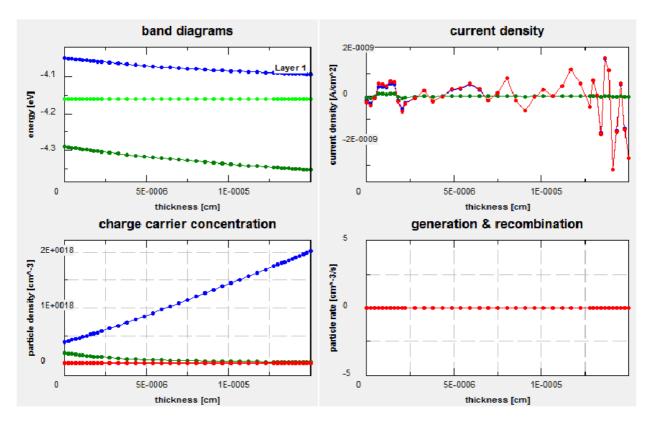

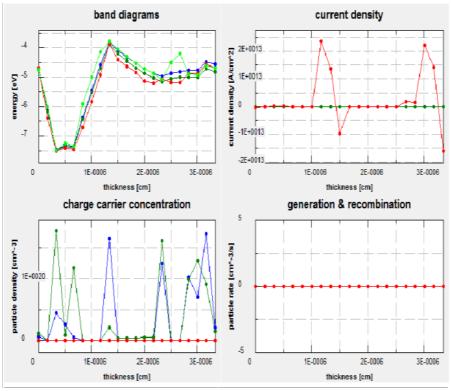

- Figure 3.2 Single layer graphene electronics property with band diagram, current density and charge carrier concentration along with zero rate of generation and recombination of charge carriers versus thickness of the particular layer.

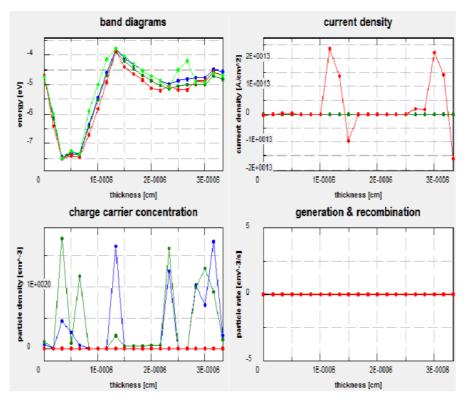

- Figure 3.3 Bilayer graphene electronics properties with band diagram, current density and charge carrier concentration along with zero rate of generation and recombination of charge carriers versus thickness of the particular layer.

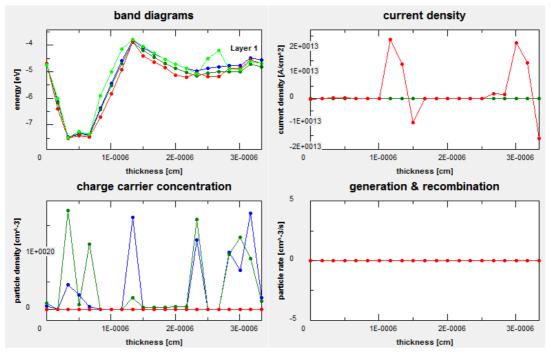

- Figure 3.4 Single layer graphene encapsulated by single hBN layers on top and bottom, electronic properties with band diagram, current density and charge carrier concentration along with zero rate of generation and recombination of charge carriers versus thickness of the particular layer.

- Figure 3.5 bilayer graphene encapsulated by single hBN layers on top and bottom graphene, electronic properties with band diagram, current density and charge carrier concentration along with zero rate of generation and recombination of charge carriers.

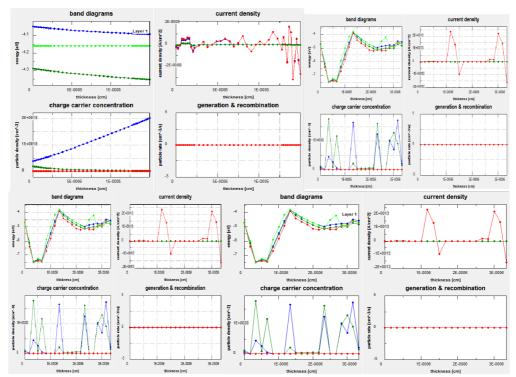

- Figure 3.6. Comparison of a single layer, bilayer, single layer encapsulated, and bilayer encapsulated graphene sheet bandgap, current density, carrier concentration and interaction rate of the carrier in the graphene layer.

- Figure 4.1 2-D Cross-sectional view of the proposed GFETs.

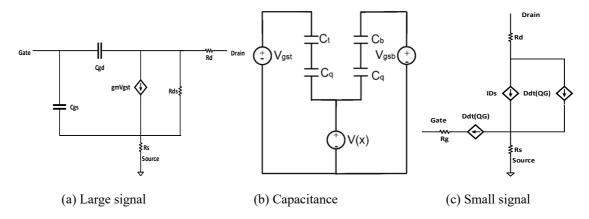

- (a) Large signal (b) Capacitance (c) Small signal.

Figure 4.2 (a), (b), (c) Equivalent circuit of the proposed GFETs (all h-parameter symbols have their usual meaning).

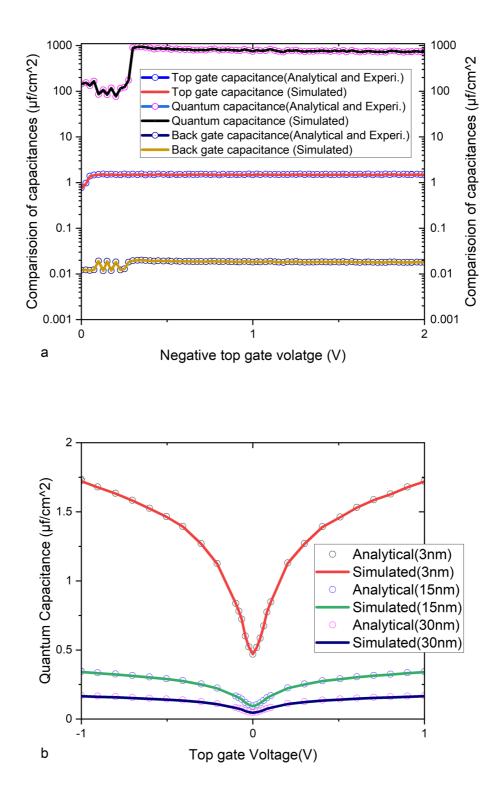

- Figure 4.3 Quantum capacitance effect on overall gate capacitance vs gate voltage. Fig.

3.a presents the comparative results of the capacitance, comparison of analytical model results is done with simulation results and with the experimental results [78]. Fig. 3. b the quantum capacitance investigated at different top gate oxide thicknesses (3nm, 15nm, and 30nm).

- Figure 4.3 (c, d) Quantum capacitance effect on overall gate capacitance vs gate voltage. Fig. 4.3.c top gate capacitance of the proposed model is investigated with respect to the top gate oxide thickness (3nm, 15m, and 30nm). Fig 4.3.d quantum capacitance is compared with different GFET structures at 1000nm channel length.

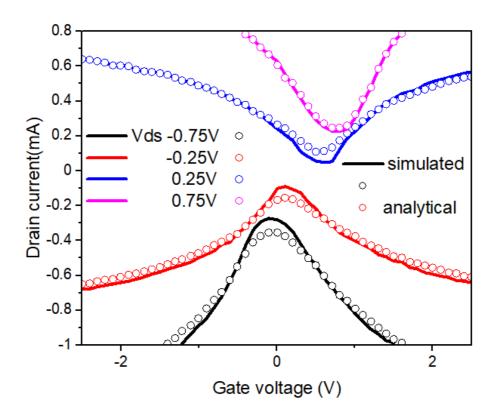

- Figure 4.4 Transfer characteristic of the proposed model i.e. drain current vs top-gate voltage for the proposed GFETs model.

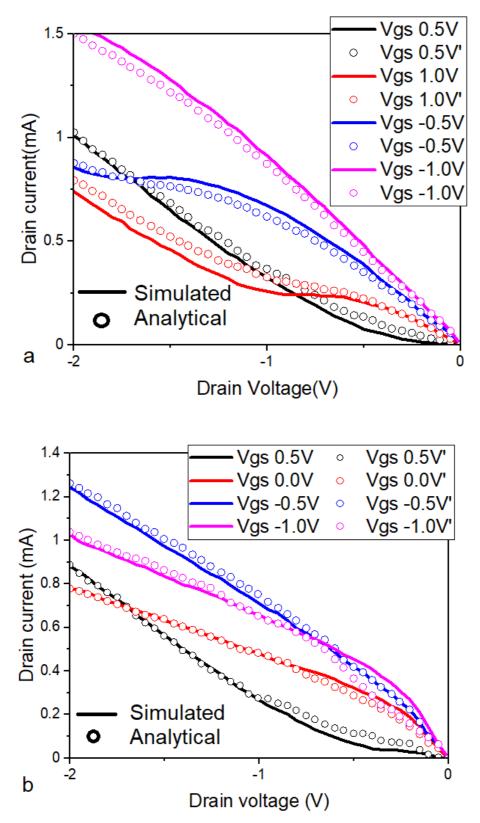

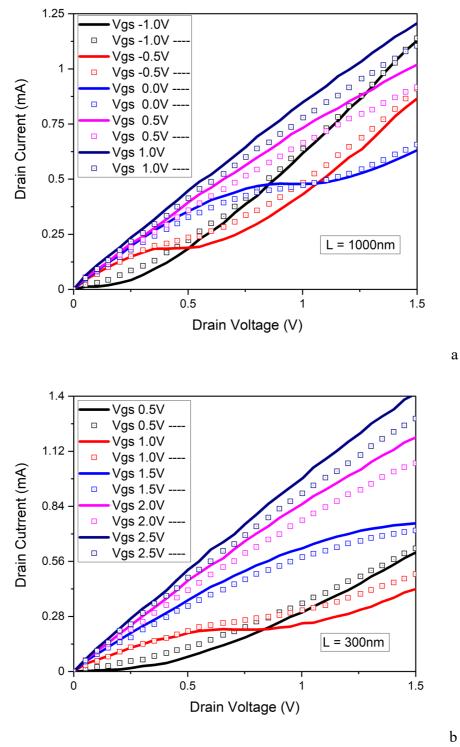

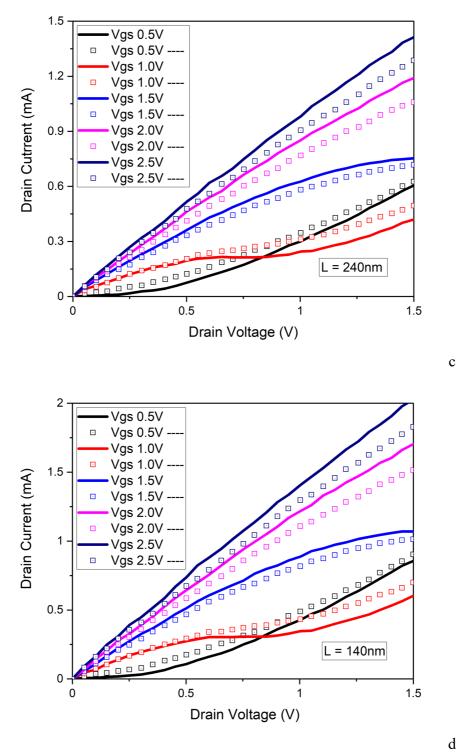

- Figures 4.5. a and 4.5.b: Output characteristic of the proposed model i.e. drain current vs drain to source voltage for the GFETs model at 1000nm in 4.5. a and 300nm in 4.5.

b.

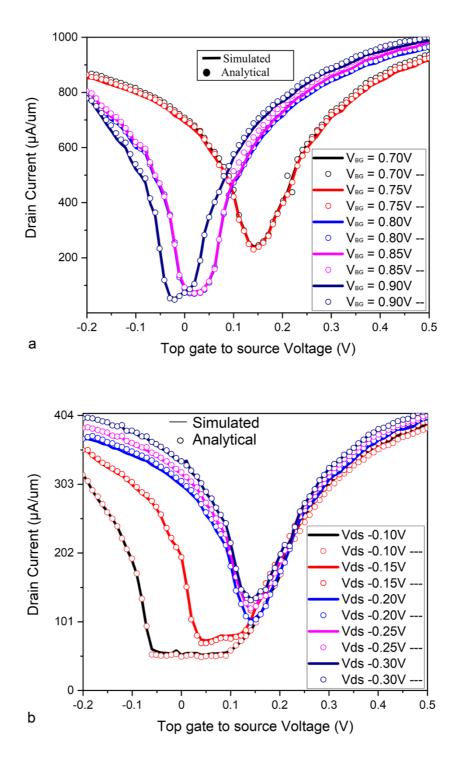

- Figure 4.6.a and 4.6.b: Transfer characteristic of the proposed model i.e. drain current vs drain to source voltage for the GFETs model. Top gate control by V<sub>ds</sub> and back gate control by V<sub>BG</sub> over drain current are presented in this graph (while for this dual gate control an exception is considered that the graphene sheet is not a large area sheet). V<sub>ds</sub> and V<sub>BG</sub> are the externally applied drain to source and back gate voltage.

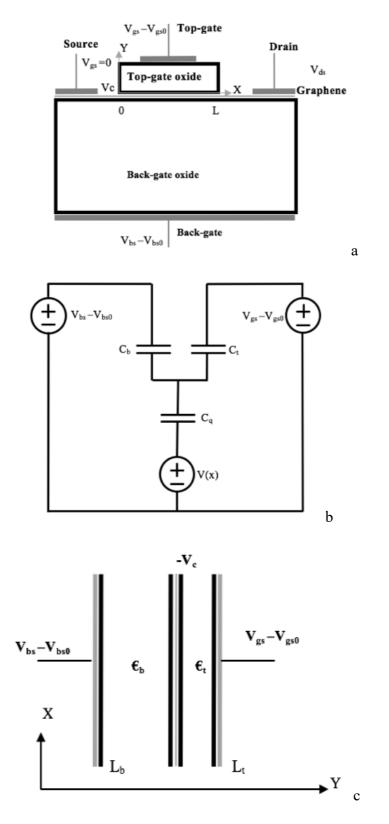

- Figure 5.1.a cross-sectional view of the proposed GFET device with the basic electrostatic parametric details, in figure 5.1. b equivalent capacitance of the GFET model, in figure 5.1.c view of the proposed model GFET with the equivalent capacitance of the GFET model of GFET.

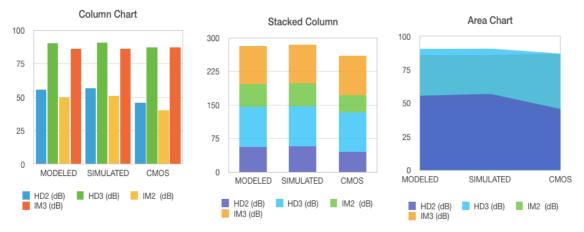

- Figure 5.2: Non-linear behaviour of the bilayer graphene field effect transistors (GFET) shown with bar graph as the static nonlinearity by the column, stacked and area chart for the proposed modelled, and CMOS field effect devices.

- Figure 5.3(a,b): Non-linear characteristic behavior of the quasi-ballistic GFETs. figure 5.3. a I<sub>ds</sub> vs V<sub>ds</sub> output characteristic curve is showing highly nonlinear behavior of curve at 1000nm. Figure. 3. b at 300nm also shows nonlinearity at low (0 to 1V) drain voltage and shows linear shape after 1V drain voltage value.

• Figure 5.3.c shows the almost linear curve of current and voltage at 240nm, while a kink is present at 1.25V at a low gate voltage value. Figure 5.3.d is shown the linear curve of output drain current and voltage at all (0 to 2V) drain voltage at 140nm. All the simulated results shown in figure 3 are drawn by lines while all the analytical outcome values are drawn by squares (symbols).

#### List of Tables

- Table 2.1 Comparison of recent transistor technology by fabricating semiconductor foundries

- Table 2.2 ITRS-International Roadmap for Semiconductor devices trends for MOS devices

- Table 2.3| Summary of properties of application-specific graphene prepared by different Methodology

- Table 2.4 | solid-state properties of 2D layered crystalline materials at 300k [12].

- Table 2.5 | Summary of the promising sub-nanometre-scale channel [21]

- Table 2.6 List of graphene-based product that travels out of laboratories [27].

- Table 4.1 Dimensions and parameters of the modelled GFETs devices

- Table 5.1 listed the nonlinearity characteristics of the high-frequency operation of GFETs.

### List of abbreviations used

| Gr-Graphene                                  |

|----------------------------------------------|

| hBN-hexagonal boron nitride                  |

| <b>2D-</b> Two dimensional                   |

| nm-Nanometer                                 |

| GFETs-Graphene field effect transistors      |

| QC- Quantum capacitance                      |

| MFT-McKelvey's flux theory                   |

| CMOS-Complementary Metal Oxide Semiconductor |

| HDs-harmonic distortions                     |

| IMs-Intermodulation distortions              |

| NEMS-Nano Electronics Mechanical System      |

| MEMS-Micro Electronics Mechanical System     |

#### LIST OF PUBLICATIONS

#### Journals

#### Published

- Munindra, Deva Nand, "Nonlinearity, Scaling Trends of Quasi-Ballistic Graphene Field Effect Transistors Targeting RF Applications" Journal of Computational Electronics, vol. 20, pp. 2379- 2386, 2021. https://doi.org/10.1007/s10825-021-01772x (SCIE) Impact factor 1.730.

- Munindra, Deva Nand, "Nonlinearity Analysis of Quantum Capacitance and its Effect on Nano- Graphene Field Effect Transistor characteristics" Journal of Electronic Materials, vol. 51, issue 7, 2022. htt[s://doi.org/10.1007/s11664-002-09639-y, (SCI & SCIE), Impact factor 1.746.

- Munindra, Deva Nand, "Study of Electronic Properties of Single and Few Layer Graphene gr/hBN Heterostructure" IJRECE, vol. 7, issue no. 2, pp. 1515-1554, 2019. (Scopus).

#### **Conferences:**

- Munindra, Deva Nand, "Non-linearity of the Single Layer Graphene Field Effect Transistors" an oral contribution in11th International Conference on RECENT PROGRESS IN GRAPHENE AND TWO-DIMENSIONAL MATERIALS RESEARCH CONFERENCE (RPGR-2019), 2019, Matsue, JAPAN.

- Munindra, Deva Nand, "Study of Non-linearity of Bilayer Graphene Field Effect Transistors" an oral contribution in IEEE 14th International Conference on Nanotechnology Materials and Devices Conference (IEEE-NMDC-2019), 2019, Stockholm, SWEDEN.

- Munindra, Deva Nand, A.K. Upadhaya, "Evaluation of Graphene FET Model in Quasi-Ballistic Regime for Frequency Doubler Circuit" a poster contribution 5th International

Conference on Emerging Electronics (ICEE-2020), 2020, IIT-Delhi.

4. Munindra, Om Prakash Verma, "Analysis of Quantum Capacitance Effect and Velocity Saturation in Graphene- Metal-Oxide-Semiconductor Field Effect Transistor with Large Area Graphene Channels" an oral contribution in 10th International Conference on RECENT PROGRESS IN GRAPHENE AND TWO-DIMENSIONAL MATERIALS RESEARCH CONFERENCE (RPGR-2018), October 22-25, 2018 in Guilin (China).

#### **Chapter one**

#### **Introduction and Motivation**

#### **1.1 INTRODUCTION**

A transistor is the most important component of computer and electronic devices, which is facing the problem of performance limitations of conventional Integrated circuits, as it is the biggest challenge for the electronics, semiconductor industry and information technology. The reduction of dimensions in silicon-based transistors faces great challenges as dimensions approach atomic sizes and physical limits will be eventually reached. A great deal of research has been centred on new 2-D material graphene that can overcome these limitations. Thus, to make our computers smart and fast we have to replace the silicon material with graphene, it has enormous electrical conductivity and many research's almost in every space of life has proved graphene as the material of the future. The Discovery of graphene raises the prospect of a new class of nanoelectronics devices based on the extraordinary physical properties of this one-atom-thick layer of carbon. Unlike other two-dimensional electron layers in semiconductors, where the charge carriers become immobile at low densities, the carrier mobility in graphene can remain high, even when their density vanishes at the Dirac point.

The high electron mobility of graphene (200000 cm<sup>2</sup>V<sup>-1</sup>S<sup>-1</sup>) [1] makes graphene-based field effect transistors (GFETs) excellent candidates for replacing silicon-based nanometer Complementary Metal Oxide Semiconductor (CMOS). High transconductance gain ( $g_m$ ) and saturation region for GFETs drain current facilitates the use of GFETs as a voltage-controlled current source and the design of analog circuits. Until now, drain current saturation has been observed in long gate GFET devices, but now short gate also presents unsatisfying current saturation behavior, Bilayer graphene comes out as an alternate and improves the current saturation behavior for GFET Devices. Lateral graphene heterostructure is another solution for current saturation improvement for high-frequency GFETs. Some of the physical models have been developed by the researcher, which does not have closed expressions and so need numerical methods and expressions which avail us of simple mathematical models for different parameters for GFETs. Since Graphene is a miracle material which has extraordinary properties: like high mobility, very high thermal conductivity, optically transparent, and stability at the atomic level. It is the two-dimensional single atomic layer of 0.342 nm thickness. It is stronger than steel and even lighter in weight. This material is of importance and integrating ICs at the industrial level named by 2D-Experimental Plot line (EPL). Figure 1.1 graphene electronics product from the fabrication lab to market MGFET-4D, MGFET-4P, and GFET-S20 chip from Graphenea. GFET-S20 contains 36 GFETs applicable for sensing applications.

Figure 1.1 The MGFET-4D, MGFET-4P GFET-S20, chip from Graphenea provides 36 graphene devices distributed in four quadrants with the devices in the centre of the chip and the probe pads located near the periphery of the chip [65].

#### **1.2 MOTIVATION GRAPHENE FLAGSHIP**

Graphene flagship is the world's biggest platform for graphene and 2D materials research, innovation, production, industrialization and collaboration. The Graphene Flagship was launched in 2013 by the European Commission with a budget of one billion Euros. Graphene flagship is the collaboration of 22 countries, 167 Core partners, 1200 members and 100 associate members. Funded by the European Commission graphene flagship is the home for

the 19 research centres including industry (48%), Academia (34%) with 4500 publications and 333 patents. For the innovation, the graphene flagship is associated with the 11 spearhead projects of 16 companies. In 2022 graphene flagship starts its 2D materials Semiconductor foundry named by 2D-Experimental Plot line (EPL). Figure 1.2 Plan of action for the year 2022 and functional summary of development in the year 2022. Figure 1.3 Extraordinary properties of graphene towards its electronic applications with wafer-scale integration [2].

Figure 1.2 Plan of action for 2022 and functional summary of development in 2021Of Graphene Flagship [2].

# **1.3** Limitless possibilities of the limitless layers of graphene and graphene composite

The birth of limitless layers in 2004 is the outcome of years of research by the chunk of graphite and sticky tape. Now just 17 years later we have a vast family of layered materials and vast opportunities for solo layered materials or the composite of the layer materials. Graphene is a single atomic thin/thick layer of carbon atom in a hexagonal structure with extraordinary thermal and electrical conductivity, stronger than steel and harder than diamond even though highly flexible. Graphene layers with twisted orientation are highly researchable layered materials of semiconductor industries and digital device applications. Graphene composite is highly recommended in electronic industries for RF electronic applications and its spintronic applications. Graphene composite with lithium is highly recommended for optoelectronics applications and photovoltaic industries' solar panels. Graphene's extraordinary thermal conductivity found its application in electro mechanics, microelectronic mechanical systems (MEMS) and nanoelectronics mechanical systems (NEMS). Graphene is also versatile in aviation and automation industries, many of them foundries like Lufthansa and Mercedes are aiming for a fully automotive battery module. Graphene heterostructure and twistronics are also two new filed to understand the behaviour of layered materials. A small angle twist in the two-graphene layer stack could change electrical conductivity unimaginably from superconductive to insulator. Wearable and communicable electronic device applications are also aiming the high flexibility just because of graphene properties. The extremely thin layer of graphene could also pave the way for the printable, wearable and flexible internet of things (IoT) ideals. Graphene and layered materials are also promising to design and develop sensor and sensor-based products for biomedical, health and safe environments for the habitat in an urban area. Graphene technology like compact NO2 is efficient to clean and save urban city air with help of graphene photocatalyst. Pure water is the best and primary food integrant for human health graphene is also helpful to produce compact and cost-effective water filters. The strong spin-orbit coupling and magnetic properties of graphene are encouraging for spintronic devices. The theoretical investigation of graphene spin devices has extended the conventional approach of quantum simulation by developing brute force for making the simulation realistic. The experimental study of graphene heterostructure, and encapsulation of graphene layer into

two 2D materials layers demonstrate the charge particle interaction swapped by gate potential and exchange of spin-orbit coupling. Self-lubricating property of graphene-metal composites could replace the lubricating grease in the low-voltage circuit breakers. The grease-free and maintenance-free low circuit voltage breakers could be monumental as well as sustainable for fault detection in electrical grids. The self-lubricating technology of graphene composite is developed at graphene flagship initially for electrical contacts and now is scaled up for the circuit breaker application. Thin film technology perovskite would have increased the power efficiency of solar panels with reduced the cost since silicon solar cells have reached their theoretical upper power conversion efficiency. The estimated cost of solar power based on thin film perovskite is \$0.3 per watt with 25% power conversion efficiency. Graphene flagship's GRAPES project aims to revolutionize the Photovoltaic industries as it combines two different technology new thin-film perovskite solar cells and silicon tandem cells on graphene and layered materials. GRAPES project is aiming to design, fabricate characterize and install 20 m<sup>2</sup> solar panels with 23 % power conversion by 2023 [2].

Graphene transducer-enabled image sensor-based broadband super pixel camera would be capable to detect visible infra-red rays ranges (400 nm to 700nm wavelength corresponds to 450 THz to 750 THz) using a single focal plane array [2]. The broadband camera would have a resolution of 80 x 60 super pixels. The graphene flagship project used three different materials with a graphene transducer (colloidal quantum dots, pyroelectric thin film and nanoparticle oxides with narrow band gap) to a developed absorber material solution to read full spectral visible infra-red band. The functionality of this camera is tested successfully at CMOS wafer integrated with graphene patterns named readout integrated circuit (ROIC) for its first version 80 x 60 super pixel. This ROIC makes it possible to integrate graphene and photosensitive materials. The fabrication of silicon/graphene composite electrodes in lithium-ion batteries used as anode has been done in 2020 through the GrEEnBat project. The advantage of silicon/graphene electrode is increased cyclability of the batteries by 60% along with the efficient energy density of silicon batteries [2]. Graphene flagship aims to develop a fully functional silicon/graphene battery module for an automotive application like an electric car by the end of the year 2025. The ultimate goal of sustainable development will be fulfilled by using green technology lithium-ion battery material which helps us to reduce the release of greenhouse gases. The high electrothermal conductivity property of graphene helps GICE teams to characterize and develop the graphene heater element to resolve the ice accumulation on aeroplane wings, rudders and propellers. Ice accumulation on aircraft surfaces is very dangerous and could be solved by graphene's lightweight, highly efficient, and flexible properties. GICE project team hosted by graphene flagship has developed the Ice detector and also tested it in laboratories. Lufthansa technique and graphene also host an AEROGraFT project, which is aiming to produce and replace aircraft state of art HEPA filters with graphene-based self-clean filters.

#### **1.4 GRAPHENE ELECTRONICS AND ITS WAFER-SCALE INTEGRATION**

The extraordinary electrical conductivity of the graphene layer is highly versatile in the electronics world and its wafer scale integration is highly motivational for the limited silicon electronics industry. Extremely flexible, super thin, supper conductive and sustainable development supportive properties of graphene prove it ideal layer material for RF electronics.

Figure 1.3 Extraordinary properties of graphene towards its electronic applications with wafer-scale integration [2].

#### **1.5 RESEARCH OBJECTIVES AND FINDINGS OF THE THESIS**

**1.5.1** To explore and implement a closed form model of GFET, using effective mobility.

- A quasi-analytic model for single-layer GFETs with large area graphene is presented. Drain current formulation with velocity saturation effect and role of quantum capacitance over the total capacitance is explained with the precise output and transfer characteristics of the proposed GFET model.

- The effect of enhanced quantum capacitance value at nanometre technology adds nonlinearity to the transfer and output drain characteristics of the proposed GFETs model.

- The fitting parameter addition in velocity saturation has improved the drain current characteristic by avoiding the early saturation stage. Modelling and simulation of the GFETs model have provided a high drain current when compared with the results of the well-established experimental work.

- Dual gate control along with the nonlinearity study of single-layer large area graphene field effect transistor is done.

- **1.5.2** To study and formulate the non-linearity and linearity characteristic behaviour of the quasi-ballistic GFETs model.

- An explicit nonlinearity characteristic behaviour of the ballistic transport approach GFET presented in this work has significant importance Since the nonlinearity of the particular devices is a great source of noise in the nanoelectronics device application based on GFETs.

- This work is a Comparison of GFETs at various scaling channel lengths for the proposed model and simulation results with better drain current values. Better drain current at nanometre technology is a big achievement of this modelling and simulation work.

- The higher frequency response of the GFETs model in comparison to conventional MOSFETs technology at the same channel length is the paramount potential of this work.

- The explicit quantum capacitance drives the drain current formulation and also presents the nonlinearity of characteristic curves of the GFETs at nanometre technology. Since noise is always a key element to disturb the performance of the FETs and GFETs in real-world electronic devices and circuits, the study of nonlinearity to the transfer as well as output characteristics is our contribution to the modelling and simulation of the quasi-ballistic GFETs.

- **1.5.3** To drive and formulate scalable closed form quasi-ballistic GFETs model.

- TCAD simulation setup and device structure setup of ballistic and quasi-ballistic GFETs at four different channel lengths (140, 240, 300 and 1000 nm) are done from quasi-ballistic to ballistic transport nature of charge carrier in graphene channel.

- The entire simulation process is done in four independent steps device structure for 1000nm, 300nm 240nm and 140nm, which follows similar basic device structure formation fundamentals like all of them are four terminal devices. 500nm thick silicon base with 22nm/10nm back gate contact, 285nm (300-15) thick back gate oxide hBN, atomically thick single-layer graphene, 15nm thick top gate oxide hBN and the source, drain and gate contacts similar to the back-gate thickness. Graphene has been modified with the established poly-silicon properties like electron mobility MUN, hole mobility MUP, energy band gap EG at room temperature and work function.

- 1.5.4 To explore and simulate the electronic properties of graphene on various 2D dielectric beds.

- The electronic properties of single layer and bilayer graphene, along with graphene over the hBN layer (gr/hBN heterostructure) are studied and well demonstrated.

- The electronic band diagram, current density and charge carrier density concerning the thickness of graphene layer over gr/hBN heterostructure have been find.

- An energy band gap widening is observed from the single and bilayer graphene encapsulated in the hBN dielectric sheet.

#### 1.5.5 Scope and applications of this thesis work

- RF frequency response of this work is very much comparable to the graphene FET RF mixer and subharmonic mixer, high voltage gain Amplifier, and frequency doubler circuits.

- Modelling and simulation done for the nonlinearity of single layer large area GFET and quasi-ballistic GFET are very much applicable for the quantum computation of the RF electronics circuits based on these devices.

- Modelling and simulation done for the nonlinearity of single layer large area GFET and quasi-ballistic GFET are very much applicable for the VLSI and circuit design module for the latest nanoelectronics applications.

- Modelling and simulation of the devices we have modelled can be modelled on various CAD tools COGENDA TCAD, SILVACO and SENTAURUS TCAD, and COMSOL.

- The GFETs model we have studied is technically similar to the GFETs used in the GFET-S20, MGFET-4D, and MGFET-4P graphene chips available in the market for sensing applications.

#### Chapter two

#### Literature survey

#### **2.1 INTRODUCTION**

The transistors of the recent internet of things amenities like mobile, computers and laptops are 5nm across (M2 chip of MacBook air 2021). The atomic size of silicon is 0.21nm, which means 24 to 25 atoms are present in today's transistors. This simply indicates the atomistic limitations of the silicon transistors. Silicon technology advancement in future years in table 2.1 is compared by the semiconductor foundries with different technologies. The advancement of silicon transistors beyond 1nm is not possible even after 2026 because of short channel effects at 1nm or 10Aungstrom and if possible, only and only in industry and academic partnerships. Academics always suggest 2D material graphene as a semimetal for electronics applications. Table 2.2 Comparison of the physical parameter of these transistors by ITRS.

| Name\Years | 2018 | 2019 | 2020 | 2021 | 2022   | 2023   | 2024 | 2025 |

|------------|------|------|------|------|--------|--------|------|------|

| TSMC       | 7nm  |      | 5nm  | 5nm  | 3nm    | 3nm+   |      | 2nm  |

|            |      |      |      |      | FinFET | FinFET |      | GAA  |

| SAMSUNG    | 8nm  |      | 5nm  |      | 3nm    | 3nm+   |      | 2nm  |

|            |      |      |      |      | GAA    | GAA    |      |      |

| INTEL      |      | 10nm |      | 7nm  | 4nm    | 3nm    | 20A  | 18A  |

Table 2.1 Comparison of recent transistor technology by fabricating semiconductor foundries.

Based on the official data published by INTEL, SAMSUNG AND TSMC [102-104]

| Table 2.2 ITRS-International Ro | admap for Semiconduc | tor devices trend | s for MOS devices |

|---------------------------------|----------------------|-------------------|-------------------|

|---------------------------------|----------------------|-------------------|-------------------|

| Year                                      | 2009 | 2012 | 2015 | 2018 | 2021 |

|-------------------------------------------|------|------|------|------|------|

| physical size length (nm)                 | 34   | 24   | 17   | 12   | 8.4  |

| MPU physical gate length (nm) (Lg)        | 20   | 14   | 10   | 7    | 5    |

| Supply voltage V <sub>dd</sub> (V)        | 1.0  | 0.9  | 0.8  | 0.7  | 0.65 |

| Number of transistors per chip (Millions) | 878  | 1106 | 2212 | 4424 | 8848 |

| Oxide thickness (nm) (0.02Lg)             | 1.4  | 1.3  | 0.9  | 0.64 | 0.44 |

| Max power dissipation with heat sink(W)   | 180  | 190  | 218  | 215  | 288  |

#### **2.2 LITERATURE SURVEY**

#### 2.2.1 **RISE OF GRAPHENE**

The rise of graphene presents the electric field behaviour of a few atomically thick or thin carbon layers. Heart of the modern world electronics is all about a particular material's behaviour in the presence of another's electric field and so, we called it as electric field effect. since the semiconductor world is just reached the limits of performance improvement and scaling of parameters for the conventional silicon technology, so after the researcher's hard work and continuous efforts. we land with organic conductors and carbon nanotubes at the same time electronics are also being exposed to the transition metal, and tend to use it for all-metallic transistors, for very long. however electronic field screening through metal is only less than one nm (<1nm) so, this article reports a mechanical exfoliation produced monocrystalline graphite films, which was just a few atomic thick and even under some ambient condition thermally stable. Figure 2.1 Graphene the mother of all carbon forms graphite, graphene is a fundamental 2D building material for all (0D, 1D,3D) dimensions carbon 0D Buckyballs, 1D nanotube and 3D graphite stack [3].

Figure 2.1 Graphene the mother of all carbon forms graphite, graphene is a fundamental 2D building material for all (0D, 1D,3D) dimensions carbon 0D Buckyballs, 1D nanotube and 3D graphite stack [3].

This report presents the electric field effect in a naturally exfoliated occurring few layers of graphene [1-2], as the first novel 2D material. Before this, it was unbelievable that planner graphene (carbon form) could be found in the free form at the nanometer (atomic) level. Above all these myths and beliefs they have been done this and able to produce a graphene sheet of one atomic thick, even developed electronic devices based on this and study their electronic properties. This graphene sheet shows superb high-quality 2D electronic ballistic transport at submicron lengths. This is highly remarkable to get such an efficient conducting atomically thick semi-metallic layer. A metallic field effect transistor has been prepared by using the conducting channel as 2D electron gas and hole gases switched by the voltage tuning. To explore more about the electronic properties of these mechanically exfoliated (from highly oriented pyrolytic graphite) sheets from a single layer (SLG) to few-layer graphene (FLG) ranges from less than one nm to hundreds of nm respectively, has been processed in multiterminal Hall bar devices and put on top of oxidized Si at the base so that gate can be controlled by applying gate voltage (Vg). All the FLG (1, 2, 3 layers) devices exhibited identical electronic properties for 2D semimetal, unlike the multilayer graphene to the properties of 3D graphite.

# 2.2.2 LIMITATIONS OF GFET STRUCTURE TOWARDS DEVICE LOGICS, WHILE HAVING SCOPE FOR HIGH FREQUENCY TRANSISTORS

The absence of bandgap in pure graphene Flack is the main concern of graphene-based device logic application, which also limits its scope in digital electronics [4-6]. So, it is unlikely to see that graphene will be able to make it into high–performance ICs for logic application as a planer channel 2D material. However, the CVD-grown graphene layer and graphene growth over SiC could be a possible option for high-frequency and analog electronic devices and circuits [5].

#### 2.2.3 GRAPHENE ELECTRONIC PROPERTIES AND ITS LIMIT ON THE SIO<sub>2</sub> PLATFORM

The intrinsic and extrinsic performance limits and expectations of graphene on SiO<sub>2</sub> devices have been shown by numerous articles. An unexpected/surprising prediction has been come out with the fact of linear dispersion relation in wave vector k and 2D energy, is that we may have resistivity (due to isotropic scattered-phonons) independent of charge density n. This has been predicted and lightens up [7] that the acoustic phonon scattering and an intrinsic limit of 30  $\Omega$  resistivity in graphene, which is also found independent of n, at room temperature. With the technology relevancy fit carrier density is  $10^{12}$  cm<sup>-2</sup>, very high intrinsic carrier mobility 2 x  $10^5$  cm<sup>2</sup>/Vs [5-6] (which is more than ever known inorganic semiconductor as InSb of value approx. 7.7 x  $10^4$  cm<sup>2</sup>/Vs, CNTs of value approx. 1 x  $10^5$  cm<sup>2</sup>/Vs) and electron acoustically scattered mean free path is > 2µm.

While the extrinsic scattering due to surface phonons of the SiO<sub>2</sub> substrate shows resistivity strongly dependent on temperature above ~ 200K and it limits the mobility value to 4 x  $10^4$  cm<sup>2</sup>/Vs approx. at room temperature. So, to develop quality graphene-based electronics, a quality graphene sample is not enough one also needs a surface scattering and roughness-free, impurity-free and surface optical-free substrate for the graphene layer [7]. Furthermore, near charge neutrality and substrate-induced disorder creates inhomogeneous patterns of electron and hole puddles. Because of these many surface interface problems of graphene with the substrate, it exhibited characteristics far inferior to the expected intrinsic properties. A novel approach for substrate engineering is developed is graphene-based vertical heterostructures [9]. Figure 2.2 Energy momentum graph shows six contact points of valance and conduction band called Dirac point.

Figure 2.2 Energy momentum graph shows six contact points of valance and conduction band called Dirac point.

Graphene-based FETs on conventional oxide (SiO<sub>2</sub>) beds show highly disordered and degraded properties that are very menial as compared to the pristine graphene layer [8]. Although GFETs electronics quality is being upgraded by suspending the graphene channel on the above substrate and by hydrogenating the graphene channel to the nanopore and nanomesh FETs. These geometry arrangements have also imposed limitations on device architecture and functionality. So, the very needed and technology-matched 2D dielectric material Hexagonal boron nitride (hBN) [6-8] is an appealing substrate to the GFETs. It has an atomic size dangling bond-free smooth surface and has a must-needed bandgap (5.97) [10] along with large enough surface optical phonon modes. Graphene and the graphene-based device show appealing high-frequency gain and other characteristics for RF and analog circuits design [11].

# 2.3 PREPARATION METHODS AND SPECIFIC PROPERTIES OF GRAPHENE AND OTHER 2D MATERIALS

First and foremost, the preparation method by the birth of graphene in Manchester university 2004 is the scotch tape method. The impossible task of isolation of single-layer graphene ever is done and the finding of electric field effect in the graphene layer bless K.S. Novoselov and A.K. Geim sir with the noble prize in 2010. Scotch tape method or mechanical exfoliation of graphene was initially very promising with exceptional electronic property for graphene electronic applications but after researching a decade liquid phase exfoliation (or chemical exfoliation), graphene production on SiC and CVD growth of graphene are providing highly productive graphene layer. The separation of graphite crystal using the surface tension of non-aqueous liquid into graphene platelets or we can say graphene sheets is liquid phase exfoliation. Liquid phase or chemical exfoliation also uses graphene oxide by oxidizing the graphite crystal to produce very low conductive graphene for battery electrodes to develop fully automobile applications. CVD-grown graphene or graphene transferred on dielectric layers like hBN and HfO<sub>2</sub> is the best production method of graphene, this method leads to provide the intrinsic mobility of the graphene layer.

| Method of      | Crystal Size | Sample Size        | Mobility                                           | Applications   |

|----------------|--------------|--------------------|----------------------------------------------------|----------------|

| Preparation    | (um)         | (nm)               | (cm <sup>2</sup> V <sup>-1</sup> S <sup>-1</sup> ) |                |

| Mechanical [1] | >1000        | >1                 | $>2x10^{5}$ m                                      | Research       |

| exfoliation    |              |                    |                                                    |                |

| Chemical       | <= 0.1       | Infinite as layers | 100 (overlaps                                      | Coating        |

| exfoliation    |              | overlaps           | layers)                                            | Biomedical     |

| Chem. Ex. Via. | ~100         | Infinite as layers | 1(overlaps                                         | Energy storage |

| Graph. oxide   |              | overlaps           | layers)                                            | Bat. electrode |

| CVD [3]        | 1000         | ~1000              | 10000                                              | Nano-          |

|                |              |                    |                                                    | electronics    |

| Graphene on    | 50           | 100                | 10000                                              | High frequency |

| SiC/hBN/HfO2   |              |                    |                                                    | transistor     |

Table 2.3| Summary of properties of application-specific graphene prepared by different Methodology

Figure 2.3 Method of graphene preparation with applications of the particular graphene sheet [6].

The summary of the preparation method of graphene given in table 2.3 is application specific. Figure 2.3 Method of graphene preparation with applications of the particular graphene sheet [6]. Chemical vapour deposition grew graphene sheet and transfer technology of graphene on dielectric/silicon base surface is highly conduct electrically and thermally. Both of these properties are highly commendable for graphene-based RF electronic devices. Exemplary high voltage gain amplifiers or frequency doubler circuits are the graphene RF electronics available in the market. Finding bandgap in graphene and the required magnitude of on/off ratio for digital electronics is still a challenge for graphene electronics, however graphene heterostructure with hBN, MoS<sub>2</sub> and HfO<sub>2</sub> is under research. Graphene heterostructure has published marvellous results supporting graphene optoelectronics, and flexible electronic applications. A comparison of graphene properties with other 2D materials is given in table 2.4. Graphene channel length and their compatibility according to rigidity, tunability and density are summarized in table 2.5. The supremacy of graphene over all the 2D layer materials conductivity-wise and tenability-wise can be found in the tables. Figure 2.4 molecular layered structure of graphene other 2D layered materials [09].

| 2D material        | Electrical propertiesMobility andVsat(cm²/V sec) &(cm²/sec) | Optical<br>Band gap and<br>Band type | RF Applications                             |

|--------------------|-------------------------------------------------------------|--------------------------------------|---------------------------------------------|

| Graphene 1, 4, 11  | $3-5 \ge 10^4$ and $1-5 \ge 10^7$                           | 0 and D                              | High Voltage Gain<br>Amplifier              |

| 1L MoS2 13, 16,    | 10-130 and 4 x 10 <sup>6</sup>                              | 1.8 and D                            | Flexible nanoelectronics<br>display devices |

| Bulk MoS2 13, 14   | 30-500 and 3 x 10 <sup>6</sup>                              | 1.2 and I                            | Flexible nanoelectronics<br>display devices |

| 1L WSe2 13, 15     | 140-250 and 4 x 10 <sup>6</sup>                             | 1.7 and D                            | TFET as frequency<br>multiplier             |

| Bulk WSe2 13,93    | 500 and NA                                                  | 1.2 and I                            | Frequency multiplier                        |

| h-BN 17, 18        | NA and NA                                                   | 5.9 and D                            | 2D dielectric                               |

| Phosphorene 19, 20 | 50-1000 and NA                                              | 0.3-2 and D                          | Flexible electronics                        |

Table 2.4 | solid-state properties of 2D layered crystalline materials at 300k [12].

Figure 2.4 molecular layered structure of graphene other 2D layered materials [09]

Graphene channel length, graphene channels in different configurations and their comparison with other 2D materials channel is given in table 2.5. Graphene products from lab to market can be found in table 2.6. Figure 2.5 a) Graphene and other 2d materials with their b) flexible electronic applications [12] c) sub-Nano channels [21]. The heat sink capacity of graphene because of its high thermal conductivity has been utilized in Huawei 20X model smartphone for its supercool vapour chamber technology. TeamGroup and Momodesign also have developed a product using graphene's high thermal conductivity is now in the market. Graphenea produced mGFET-4D, mGFET-4P, and GFET-S20 graphene chip and card for the sensor application like biosensor with great readout capabilities. Chongqing Graphene Technology has processed CVD grew graphene sheets for touch panels with remarkable flexibility. The versatile sports manufacturing company has designed highly strong tennis and squash rackets.

| 2D Materials     | Nanometer channel       | Structural tunability, channel rigidness     |

|------------------|-------------------------|----------------------------------------------|

|                  | lengths                 | and density for nanoelectronics devices      |

| Graphene         | Graphene fluidic        | Low in tunability, which is depends on       |

|                  | channels 22, 23         | channel size, highly rigid and moderate      |

|                  | 34 to 1000nm            | channel density                              |

| Graphene oxide   | a ~ 46 to 66nm (dry) 24 | Moderate tunability, tuned by oxidation      |

|                  | a ~ 86 to 104 nm (wet)  | degree, lowly rigid and moderate channel     |

|                  |                         | density                                      |

| WSe <sub>2</sub> | NA                      | Moderate tunability, tuned by sheet size and |

|                  |                         | layer by layer functionality, moderate rigid |

|                  |                         | and moderate channel density                 |

| hBN              | a ~ 19nm (dry) 25       | Moderate tunability, tuned by sheet size and |

|                  | a ~ 80 to 183 nm (wet)  | layer by layer functionality, moderate rigid |

|                  |                         | and moderate channel density                 |

| MoS <sub>2</sub> | a ~ 30 nm (dry) 26      | Moderate tunability, tuned by sheet size and |

|                  | a ~ 90 nm (wet)         | layer by layer functionality, moderate rigid |

|                  |                         | and moderate channel density                 |

| Table 2.5 | Summary                                 | v of the | promising  | sub-nanometre-sca | ale channel | [21] |

|-----------|-----------------------------------------|----------|------------|-------------------|-------------|------|

| 10010 200 | ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ ~ |          | promoning. |                   |             |      |

Figure 2.5 a) Graphene and other 2d materials with their b) flexible electronic applications [12] c) sub-Nano channels [21].

| Company       | Product (model)            | Graphene properties utilized and Features     |

|---------------|----------------------------|-----------------------------------------------|

| 1.Huawei      | Smartphone (Mate 20 X)     | Thermal, Graphene film as a heat sink for     |

|               |                            | cooling 28                                    |

| 2.TeamGroup   | Solid-state drives (Cardea | Thermal, Graphene heat spreader for efficient |

|               | Zero M.2 PCIe SSD)         | SSD cooling 29                                |

| 3.Momodesign  | Helmet (FGTR Graphene      | Thermal, mechanical, and Graphene film for    |

|               | 1.0)                       | efficient heat dissipation 30                 |

| 4.HEAD        | Tennis racquet, Ski        | Mechanical, Graphene for light weight,        |

|               | (GrapheneXT)               | flexibility and robustness 31                 |

| 5.Nanomedical | Biosensor (Agile)          | Electrical, Graphene FET as a biochemical     |

| diagnostics   |                            | sensor 32                                     |

| 6.Graphenea   | Transistor array (GFET-    | Electrical, FETs on SiO2 with CVD graphene    |

|               | S10)                       | and 1,000 cm2 V s-1 mobility 33               |

|               |                            | ( <u>https://www.Graphenea.com</u> )          |

| 7.Chongqing   | Smartphone                 | Electrical, Optical and Mechanical, Flexible  |

| Graphene      |                            | touch screen for mobile phone 34              |

| Tech.         |                            |                                               |

| 8.Graphene    | Communication link         | Electrical, Optical, and All-graphene optical |

| Flagship      | (modulator and detector)   | communication link at 25 Gb s–1 35            |

| 9.CalBattery  | Lithium battery electrode  | Silicon-graphene composite anode 36           |

Table 2.6 List of graphene-based product travels out of laboratories [27].

#### **2.4 MODELLING OF GFETS**

The very first Graphene based FET [37] is comes in 2007, and technological advancement is very fast. In a few next years, interesting GFET models are reported with the intrinsic transit frequency comparable to higher than similar size CMOS nanometer technology [38-42]. Few other compacts and fundamental physics-based quasi-analytic modelling for graphene heterostructure field effect transistor (GFETs) with large area graphene are described with time as well as research technology advancement [43]. GFETs modelling based on basic physics exploring drain current, capacitance and charge parameters for graphene channel are reported in [44-47].

In electronics applied amplifier, a small signal is amplified and operated in ON state and RF signals are to be superimposed onto DC gate-source voltage but what is more important to improve is the figure of merit (FoM) like cut-off frequency or intrinsic gain with high transconductance. The compact model is benchmarked with measured current-voltage characteristics with accuracy for prototype devices and predictive behavior. The explicit compact model of drain current [44] has been extended in [45] to explore the AC and transient behavior of the GFET. Both of these physical frameworks are field effect models based on the drift-diffusion charge carrier transport mechanism. The Ward-Dutton charge partition scheme is implemented to model the source-drain charge together with transconductance and selfcapacitance.

Furthermore, scalable large signal Graphene based Field effect model has been implemented on the SPICE, Cadence or ADS and Verilog-A platforms [48-55]. A comprehensive simple and compact mathematical model provides graphene field effect transistor's physical parameters [49] and their closed form formulas like g<sub>m</sub>, r<sub>0</sub>, C<sub>gs</sub> and C<sub>gd</sub>. While [48] presents a scalable and compact graphene FET model analyzing its electrical properties. An accurate hardware descriptive language programmable GFET is modelled in [50]. Unlike other GFETs models [51] formulate an accurate drain current with effective carrier mobility calculation, which differentiates in electron and hole considering mobility variations against carrier density. A series of two large signal graphene FETs model intrinsic capacitance [52] and benchmark performance analysis [53] provide Verilog implementable graphene transistor modelling. In 2017, a year later model of a large-signal compact monolayer Graphene FET targeting RF circuits is reported [54]. Some unique and conventional or obsolete but always important structure (BJT) technology has been modelled for DC and RF performance analysis of Graphene Base Transistor [55] with an ideal limit of unity common base current gain. Graphene-based transistors (GBTs) are quite different from GFETs. Two insulating layers sandwiched graphene to form a vertical stack that separates the emitter from the collector. GBTs operates similarly to conventional hot electron transistor electrons travel from the emitter towards the collector by tunneling through the emitter-base insulator (EBI) and the base-collector insulator (CBI), hence the charge travels through a high mobile graphene sheet. Although in GBTs base is very thin but the high mobility of the graphene is expected to reduce the base resistance.

The DC functionality of the GBTs has been proven experimentally by the "A Graphenebased hot electron transistor" and others. But no RF measurements are available and the potential for RF operations has been done by simulation only. "Modeling, simulation, and design of vertical graphene base transistor," suggested that the intrinsic device may be capable of reaching cutoff frequencies ( $f_T$ ) in the terahertz range. Whereas observed output resistance and intrinsic gain are larger than for GFETs which are confirmed in "DC and small signal numerical simulation of a graphene-base transistor for terahertz operation. Therefore, it is expected that GBTs can overcome the typical limitation of GFETs. Continuous research efforts and search for a favorable graphene transistor configuration exploring resistance, Negative differential resistance and conductance have been modelled [56-59].

A short-channel contact-induced negative differential resistance GFETs model using non-equilibrium green's function (NEGF) to explore ballistic transport nature in the channel [56]. A boron nitride substrates GFET model explains pseudosaturation and negative differential conductance (NDC) behavior using NEGF to solve a tight binding Hamiltonian for graphene [57]. Targeting high voltage gain negative differential resistance (NDR) monolayer Graphene based FETs model investigates numerical feasibility itself [58]. Dual gate GFETs model introducing Debye length to calculate drain current-voltage heuristically [59]. Since graphene has exceptional carrier mobility so it must travel ballistically through the channel but due to the lack of suitable substrate interface scattering and substrate surface roughness does not allow ballistic transport in earlier models. Even though some hard work is done, produce ballistic and quasi-ballistic transport models explain backscattering using Mekelvey's flux theory approach [60-63].

A short-channel ballistic regime GFETs model analysis and optimize device model for analog and RF applications [60]. An explicit quasi-ballistic transport model for graphene with only a few fitting parameters to calculate drain-to-source current is reported in [61]. A less than 9% normalized root mean square error and electronic design tool development supportive quasi-ballistic model for graphene-based FET is presented in [62]. The latest Quasi-ballistic GFETs model to determine the backscattering coefficient for a charge, capacitance and current is reported in [63]. A GFET model to investigate graphene transistors' electrostatic discharge (ESD) behavior is published recently [64].

#### 2.4.1 FUNDAMENTAL PHYSICS BASED MODELLING

The modelling of graphene field effect transistors (GFETs) is categorized majorly into four types 1) fundamental physics-based model 2) explicit drain current and capacitance model 3) drift-diffusion model 4) Quasi-ballistic or flux-based model. The fundamental physics-based model starts with the properties graphene layer which is used as the channel in the GFETs and formulates the energy levels present in graphene material, no. of energy states, the density of states, electron and hole density of graphene channel. Quantum mechanics theory also constitutes density of states, kinetic energy, mean free path length, and electron density of charged particles in solid-state semiconductors.

• The density of electrons (N, E (kinetic energy) is given) [93]

$$\frac{\mathrm{dN}}{4\pi(\mathrm{p}\sim)2\mathrm{dp}\sim} = \frac{N}{(2\pi m_o kT)^{3/2}} + \exp\left[\frac{(\mathrm{p}\sim)2}{(2m_o kT)}\right]$$

Kinetic energy

$$E = \frac{\hbar^2 \psi^2}{2m_o} = \frac{\hbar^2 k^2}{2m_o}$$

• Mean free path ( $\lambda$ ) length

$$\lambda = \frac{\hbar^2}{2m_o} \psi$$

• Electron density of the Conduction band (C.B.) [93]

$$n = \left(\frac{2\pi m *_n K_B T}{h}\right)^{3/2} \int_0^\infty \left[\frac{|E|}{\exp\left\{|E| - \frac{(E_F - E_c)}{K_B T}\right\} + 1}\right] dE$$

$n = NC \left[ \exp \frac{(E_F - E_C)}{K_B T} \right]$  Boltzmann's approx. of FDI only when the distance between Fermilevel and C.B is more than the 3KT(quantum limit). Lorentz model (Lorentz assumed that electron velocities and momenta varied in accordance with the classical Maxwell-Boltzmann distribution law.) a brief introduction of classical theory to present electrical versus thermal conductivity model of semiconductor to reformulate the electron density in an energy band.

• Classical momentum (scattering not given)

$$p \sim = (3m_o kT)^{1/2}$$

• Ratio of thermal to electrical conductivity

$$\frac{k}{\sigma} = 3(\frac{k}{e})^2 T$$

(Wiedemann and Franz exp model 1853)

• Reformulated mean free path ( $\lambda$ ) length

$$\tau = m/\rho ne^2$$

,  $\lambda = V_0 \tau$

• Lorentz model (Lorentz assumed that electron velocities and momenta varied in accordance with the classical Maxwell-Boltzmann distribution law) [93].

$$dN = \frac{4\pi N(p\sim)2}{(2\pi m_o kT)^{3/2}} + \exp\left[\frac{(p\sim)2}{(2m_o kT)}\right]$$

Use of these classical and quantum mechanics theories to formulate the density of states, charge carrier concentration, quantum capacitance and drain current for graphene FETs. Fermi Dirac integral (FDI) is also very handful to calculate the fundamental physics for the graphene channel and GFETs.

• DOS (density of states) of graphene layer [81].

$$N(E) = g_s g_v \frac{Ak^2}{4\pi (\hbar v_f)^2}$$

• Now use charge carrier density and Fermi level to find carrier concentration i.e. no. of holes and electron [81].

$$p = \int_{-Ecv}^{\infty} \frac{2}{\pi} \frac{|E|}{(\hbar v_{\rm f})^2} \left[ \frac{1}{exp \frac{(E+E_F)}{K_B T} + 1} \right] dE$$

• Thus, total charge density can be found.

$$Q_{gr} = \frac{2}{\pi} \frac{q|E|}{(\hbar v_{\rm f})^2} \int_0^\infty \left[ \frac{1}{exp \frac{(E-E_F)}{K_B T} + 1} - \frac{1}{exp \frac{(E+E_F)}{K_B T} + 1} \right] dE$$

• Now use total charge carrier density to calculate quantum capacitance.

$$C_{q} = -\frac{dQ_{gr}}{dV_{gr}}$$

• Drain current [43, 44]

$$I_{d} = q\mu W \frac{\mu \int_{0}^{V_{ds}} \rho_{gr} dV}{L - \mu \int_{0}^{V_{ds}} \frac{1}{v_{sat}} dV}$$

• Quantum capacitance [42]

$$C_{q} = -\frac{2q}{\pi} \frac{qV_{CH}K_{B}T}{(\hbar v f)^{2}} \ln \left[ 2\left(1 + \cosh \frac{qV_{CH}}{K_{B}T}\right) \right]$$

• Channel potential

$$V_{CH} = \frac{C_{box}}{C_{t} + C_{b} + 0.5 C_{q}} [(V_{gs} - V(x)/2) - (V_{gs} - V(x)/2)]$$

#### 2.4.2 EXPLICIT DRAIN CURRENT BASED MODEL

2) Explicit drain current model keeps it compact and concentrates to formulate drain current and quantum capacitance using the electric potential of the graphene channel. Drain current is here simple product of charge carrier mobility, width/length ratio, and channel potential term. While the integration of charge density over drain voltage and integration of inverse velocity of saturation of charge particle is interestingly complex. Integration of charge density is also including the puddle charge which means electron to electron and hole to hole and electron to hole interaction is also an active part to generate charge particles in the graphene channel of GFETs other than thermal agitation.

• Drain current [61,62]

$$I_{DS} = \mu_{(n,p)} W \frac{\int_{0}^{V_{ds}} (|Q_{(n,p)}| + q n_{(puddle)}/2) dV}{L + \mu \int_{0}^{V_{ds}} \frac{1}{v_{sat}} dV}$$

• Quantum capacitance [42]

$$C_{q} = -\frac{2q^{2}}{\pi} \frac{q|V_{CH}|}{\left(\hbar v_{f}\right)^{2}}$$

• Channel potential [44]

$$V_{CH} = \frac{-(C_t + C_b) + \sqrt{(C_t + C_b)^2 \pm kC_q \{ (V_{gs} - V_{gs0} - V(x))C_t + (V_{bs} - V_{bs0} - V(x))C_b \}}}{\pm kC_q}$$

Where the positive and negative sign is depends on that if,  $\{(V_{gs} - V_{gs0} - V(x))C_t + (V_{bs} - V_{bs0} - V(x))C_b\}$  is > (<) 0.

#### 2.4.3 QUASI-BALLISTIC TRANSPORT(FLUX) BASED MODEL

Fundamental physics-based model Considered charge carrier and explicit drain current model considered electric potential a basic element to modelled the solid-state physics of GFETs. While quasi-ballistic model considered electric flux a basic element for modelling solid state physics of the ballistically and quasi-ballistically transported charge carrier in the ]graphene

channel of GFETs. The complexity of the integration of saturation velocity is solved in this modelling, however, backscattering coefficients ( $r_{bs}$ ) add complexity to this modelling. A modified FDI is applied to integration and to calculate the flux of the graphene channel in quasi-ballistic GFETs. 4) Drift and diffusion modelling are very conventional means basically deals with resistance at the input and at the output of FETs, due to very high electrical and thermal conductivity of graphene we do not concern too much for input and output resistance of GFET models. Drift-diffusion is also not our scope of GFETs modelling and simulation, so the drift and diffusion modelling in detail can be found [43-44]. Contact resistance and quantum capacitance is big deal for graphene devices, so in this thesis, we focus on fundamental physics-based and quasi-ballistic flux-based modelling. Quantum capacitance is the parameter of big concern for our models. The Quantum capacitance model leads modelling of the drain current and to the nonlinearity of the GFET models.

• Drain current [63,64]

$$I_{DS} = \frac{Wn(0)V_{Th}(1-r_{bs})[1-I_1(\omega_F - \omega_{DS})/I_1(\omega_F)]}{[(1+r_{bs} + (1-r_{bs})I_1(\omega_F - \omega_{DS})/I_1(\omega_F)]}$$

• Flux (or potential) to drive drain current

$$I_{DS} = Wq[F^+(0) - F^-(0)]$$

• Where flux can be written as

$$F^+(0) = N_{2D} V_{th} \mathfrak{I}_1(\omega_F)$$

• When  $I_1(\omega_F)$  is the Fermi-Dirac integral of order one defined by Blakemore.

#### **2.5 GFETs STRUCTURES**

A single-layer graphene flack is being used as the transport channel in GFETs. The 2D crosssectional View of the GFET structure is shown above in Fig. 2.6, in which gate length is extended from x (0 to L) source end to drain end, which is approx. 1000nm. This model contains a top gate and a back gate, so one can use it as a single and double gate. This modelled structure also has top gate oxide (t<sub>ox</sub>) of 15 nm thickness of hexagonal boron nitride (hBN) shown below the gate and back gate oxide (SiO<sub>2</sub>) thickness of approx. 300nm above on the Ptype silicon (100) base of thickness 500nm. Top gate, source and a drain electrode on top single layer graphene flack made of a stack of Ti/Au of thickness 70/50nm respectively. Fig. 2.7 is showing a graphene heterostructure with a few layers of hBN on a silicon body.

Figure 2.6 Two-dimensional Cross-sectional view of the basic Graphene Field Effect Transistors

Figure 2.7 Two-dimensional Cross-sectional view of the heterostructure Graphene Field Effect Transistors.

#### 2.6 RESEARCH GAPS

Based on the literature survey following research gaps are identified.

- **2.6.1** Unexplored important parameters of the GFETs modelling.

- **2.6.2** Linearity and non-linearity of GFET models have not developed enough for all regions and transport approaches.

- **2.6.3** Unavailability of a high-performance ballistic/quasi-ballistic transport model for GFETs.

- **2.6.4** Limitations of Graphene-SiO2 and scope for the other 2D dielectric materials.

#### **2.7 RESEARCH OBJECTIVES**

Based on the literature survey and research gaps following research objectives are identified.

- **2.7.1** To explore and implement a closed-form model of GFET, using effective mobility.

- **2.7.2** To study and formulate the non-linearity and linearity characteristic behaviour of the quasi-ballistic GFETs model.

- **2.7.3** To drive and formulate scalable closed form quasi-ballistic GFETs model.

- 2.7.4 To explore and simulate the electronic properties of graphene on various 2D dielectric beds.

#### **Chapter three**

# Study of Electronic Properties of Single and Bilayer Graphene gr/hBN Heterostructure

#### **3.1 INTRODUCTION**

Graphene is of high-interest 2D material for electronics applications [1-2], because of its very high electron mobility [3-5] of 200000cm<sup>2</sup>V<sup>-1</sup>S<sup>-1</sup> in its pure suspended state. It is just out of imagination thoughts that an atomically thick/thin material could be thermally stable. Although graphene shows marvellous electronic qualities in its pristine thin film form these properties are being deteriorated by the supporting semiconductor material and oxides [6-7]. The mean free path greater than 2 microns at high carrier density 10<sup>12</sup> cm<sup>-2</sup> with a big low down in intrinsic mobility to extrinsic mobility from  $2 \times 10^5$  to  $4 \times 10^4$  cm<sup>2</sup>/Vsec for graphene at room temperature seeks to find a new substrate choice for graphene-based electronics [6]. Graphene electronic devices exhibit many inferior characteristics on SiO<sub>2</sub> as expected of intrinsic graphene properties [7]. Thus, the Research advancements come in terms of various 2D Dielectric materials like BN, BCN, etc. Specially hBN (hexagonal Boron Nitride) is found best suitable 2D material that supports graphene flack and provides a wonderful Gr/hBN interface along with keeping graphene's superb electronic qualities [8-10]. A dangling bond-free smooth surface and atomically matched structure of hBN is an appealing substrate for graphene electronic applications [8]. Even after solving substrate issues graphene-based field effect devices lagging regularly for bandgap, which is very useful to graphene device logic applications. Bilayer graphene gr/hBN heterostructure i.e. graphene layers stacked with hBN layer as insulating isomorph of graphite produce a bandgap along with a good current ON/OFF ratio [11, 18]. Gr/hBN heterostructure in its lateral tunnelling structure is compared with gr/MoS<sub>2</sub> heterostructure and shows an approximate current ON/OFF ratio of 50 [11]. Another

different structure named encapsulated means a graphene layer captured by an hBN oxide at both top and bottom end also explores the scope and possibility of gr/hBN heterostructure and provides great results for graphene electronics [66-67]. A comparison of gr/hBN heterostructure with (graphene nanoribbon) GNR/hBN heterostructure suggests that gr/hBN heterostructure are better graphene structure option for graphene-based electronics devices [68].

Figure 3.1 Single layer Gr/hBN Heterostructure Fits for GFETs, with source, drain at top ends and gate in top middle with Ag/Cu metal.

Literature [69-74] has explored gr/hBN heterostructure electronically such as electronic highways (transports) in bilayer graphene [69], the study of gr/hBN Van der Walls heterostructure [70-71] interlayer or layer by layer Dirac fermions formation, cross-sectional images and buried interface properties [72], Scanning Tunnelling Microscopy (STM) based locale electronic properties [73] and interlayer tunnelling insight [74-77] of gr/hBN heterostructure. Figure 3.1 shows a gr/hBN i. e. graphene layer of atomic thickness is encapsulated by the hexagonal Boron Nitride layer of the almost same thickness, and so provides a stable structure with appropriate band gap and much needed and improved current on-off ratio.

This paper is organized into three sections, Section one introduces graphene (2D material) properties and the pros and cons of substrates for graphene-like hBN. Section two discusses and explains the band diagram electronically, current density and charge carrier density concerning the thickness of graphene layer stacked over hBN, gr/hBN heterostructure followed by simulation results. Section-III concludes the paper that gr/hBN heterostructure is the appealing graphene electronic device structure.

#### **3.2 RESULT AND DISCUSSION**

This section discusses and demonstrates single-layer graphene, bilayer and graphene heterostructure (encapsulated by top and bottom of hBN layers) electronic properties developed by the AFORS-HET CAD tool. Electronic properties of a single layer of a thickness (.342nm) [2] and bilayer graphene of a thickness (.684nm), with a bandgap of approx. 0.24 eV and encapsulation of them with the single layer hBN layer at the top and bottom end (gr/hBN) heterostructure is being explained graphically. Bandgap and other basic properties such as Nv, Nc, electron affinity and permittivity of the single layer and bilayer graphene are given [1]. Bandgap, thickness and other basic properties of the hBN layer are accounted for on behalf of [7] where thickness is almost the same as (0.334nm) as of the graphene layer, but with the band gap of 5.97 eV [9].

Figures 3.2 and 3.4 graphically explore the bandgap, current density of am-bipolar nature graphene and the change in concentration of the graphene single layer and encapsulated graphene layer by the hBN layer top and down respectively, over the thickness of material layers. Figure 3.3 Bilayer graphene electronic properties with band diagram, current density and charge carrier concentration along with zero rate of generation and recombination of charge carriers versus thickness of the particular layer demonstrated.

Figure 3. 2 Single layer graphene electronics property with band diagram, current density and charge carrier concentration along with zero rate of generation and recombination of charge carriers versus thickness of the particular layer.

The electronic band diagram, current density and charge carrier density concerning the thickness of graphene layer over gr/hBN heterostructure have been presented. Figure 3.4 Single layer graphene encapsulated by single hBN layers on top and bottom, electronic properties with band diagram, current density and charge carrier concentration along with zero rate of generation and recombination of charge carriers versus thickness of the particular layer. Figure 3.5 bilayer graphene encapsulated by single hBN layers on top and bottom graphene, electronic properties with band diagram, current density and charge carrier concentration along with zero rate of generation and recombination of charge carriers. Similarly, 3.3 and 3.5 explain results, like bandgap, current density carrier concentration and recombination during the transport with the layer for bilayer graphene and encapsulated bilayer graphene by the hBN layer top and down respectively, over the variation of thickness of the material layer.

Figure 3.3 Bilayer graphene electronic properties with band diagram, current density and charge carrier concentration along with zero rate of generation and recombination of charge carriers versus thickness of the particular layer.

Figure 3.4 Single layer graphene encapsulated by single hBN layers on top and bottom, electronic properties with band diagram, current density and charge carrier concentration along with zero rate of generation and recombination of charge carriers versus thickness of the particular layer.

Figure 3.5 bilayer graphene encapsulated by single hBN layers on top and bottom graphene, electronic properties with band diagram, current density and charge carrier concentration along with zero rate of generation and recombination of charge carriers.

#### **3.3 COMPRESSION**

Figure 3.6. Comparison of a single layer, bilayer, single layer encapsulated, and bilayer encapsulated graphene sheet bandgap, current density, carrier concentration and interaction rate of the carrier in the graphene layer.

#### **3.4 CHAPTER SUMMARY**

The electronic properties of single layer and bilayer graphene, along with graphene over the hBN layer (gr/hBN heterostructure) are studied and well demonstrated. The electronic band diagram, current density and charge carrier density concerning the thickness of graphene layer over gr/hBN heterostructure have been presented. An energy band gap widening is observed from the single and bilayer graphene encapsulated in the hBN dielectric sheet.

#### **Chapter four**

# Nonlinearity Analysis of Quantum Capacitance and its Effect on Nano-GFET characteristics

#### **4.1 INTRODUCTION**