## SRAM DESIGNS FOR NANOMETER TECHNOLOGIES

Thesis Submitted to the Delhi Technological University

for the Award of Degree of

### **Doctor of Philosophy**

in

#### **Electronics and Communication Engineering**

by

Monica Gupta

(Enrollment No.: 2K17/PhD/EC/11)

Under the Supervision of

**Prof. Neeta Pandey**

&

## Prof. Kirti Gupta

## **Department of Electronics & Communication Engineering**

Delhi Technological University

Delhi-110042, India. December 2021 © Delhi Technological University-2021

All Rights Reserved

Delhi Technological University Formerly Delhi College of engineering Shahbad Daulatpur, Bawana Road, Delhi-110042

## CERTIFICATE

This is to certify that the thesis entitled — **SRAM DESIGNS FOR NANOMETER TECHNOLOGIES** submitted by **Monica Gupta** (2K17/PhD/EC/11) to the Department of Electronics and Communication Engineering, Delhi Technological University for the award of the degree of Doctor of Philosophy is based on the original research work carried out by her under our guidance and supervision. In our opinion, the thesis has reached the standards fulfilling the requirements of the regulations relating to the degree. It is further certified that the work presented in this thesis is not submitted to any other university or institution for the award of any degree or diploma.

Kuldupt

**Prof. Neeta Pandey** Supervisor, Department of ECE Delhi Technological University Delhi-110042 India **Prof. Kirti Gupta** Co-Supervisor, Department of ECE Bharati Vidyapeeth's College of Engg. Delhi-110063 India

**Prof. N.S. Raghava** Head of Department, Department of ECE Delhi Technological University Delhi-110042 India I hereby certify that the research work, which is being presented in the thesis, titled,

— "SRAM DESIGNS FOR NANOMETER TECHNOLOGIES" in fulfillment of requirements of the award of the degree of Doctor of Philosophy is an authentic record of my research work carried under the supervision of Prof. Neeta Pandey and Prof. Kirti Gupta. The matter presented in this thesis has not been submitted elsewhere in part or fully to any other University or Institute for the award of any degree.

Monica

Monica Gupta

(2K17/PhD/EC/11)

The support and expert advice of my supervisor, Prof. Neeta Pandey, Department of Electronics and Communication Engineering, Delhi Technological University (DTU), are greatly acknowledged with gratitude. I would like to express my deep gratitude towards my co-supervisor, Prof. Kirti Gupta, Department of Electronics and Communication Engineering, Bharati Vidyapeeth's College of Engineering. I always availed of their priceless supervision, continuous motivation and ever-unforgettable humanitarian considerations.

My sincere thanks to Prof. N.S. Raghava, Head, ECE Dept., DTU, Delhi for providing me all the necessary facilities for the completion of my work. I am thankful to all the faculty members of the department for their time-to-time advice, support and help on various occasions.

I am also grateful to Prof. Jai Prakash Saini, Vice-Chancellor, DTU, Delhi, for providing the research environment in the institute.

I am also thankful to all non-teaching staff at DTU, and who have helped me directly or indirectly in completion of the Ph.D. work.

Monica

**Monica Gupta**

## ABSTRACT

High performance applications, such as biomedical and wireless sensor networks, require low power circuits for extended time operation. Supply voltage scaling in such systems is an effective way to lower the power consumption. Although voltage scaling has benefits, it has brought serious challenges for designing reliable digital circuits including Static Random Access Memories (SRAMs). Further, as SRAM occupies a significant area on SoC, the memory failures may lead to complete collapse of the system.

The conventional 6T SRAM cell has been the industry standard for a long time. However, it has limitation in operating reliably at lower voltages due to reduced margins and other performance related issues. Therefore, conventional 8T SRAM cell with improved margins has emerged as the potential substitute for its 6T counterpart. In nanometer regime, the leakages and PVT-variations become significant culminating into degraded performance and restricting its usage in sub-threshold region in small-geometry devices.

As sub-threshold leakage dominates the total leakages in SRAM cell in nanoscale devices, the classification of sub-threshold leakage reduction techniques and their impact on performance parameters under various operating conditions need extensive analysis. The available techniques are classified as those addressing leakage current component at the level of latch, bitline and read port levels; and their impact on major performance parameters is evaluated. Since the performance of a technique is also susceptible to PVT-variations, this aspect is also considered for suggesting the best suitable operating conditions for a technique falling under each classification. A low leakage SRAM cell based on the use of leakage reduction techniques is also presented. The latch and bitline leakages are respectively addressed through Multi threshold CMOS and Negative

wordline techniques in the cell. Further, Multi threshold CMOS technique is applied to non-critical transistors in the latch core to avoid its degrading effect.

There are issues in read and write operation of nanometer SRAMs and isolated read port is popular technique used to address this. The trade-off existing between the read current and read bitline leakages needs examination. To address this issue, two new SRAM cells with an isolated read port are proposed in this work. In the first proposed cell, the write performance is improved by incorporating write assist transistor with single ended write to reduce power consumption. An attempt is made to achieve high read current values by removing the stacking of MOS transistors in the read port. The second proposed cell addresses yet another issue of nanometer SRAM cells i.e. read bitline leakages. It uses compensation transistor which suppresses and equalizes read bitline leakages in unaccessed cells irrespective of the stored data resulting in low and data-independent leakages in SRAM cell. Additionally, it provides the reverse current in accessed cell to maintain high read bitline voltage while compensating read bitline leakages in unaccessed cell. The reduced stacking effect of transistors further helps in maintaining reasonable values of read current resulting in significant improvement in all the read performance parameters. For improvement in write mode, the proposed cell employs faster differential write.

With reduced supply voltage and device scaling, the issue of PVT-variations has also emerged as a serious design challenge for nanometer SRAMs. This issue is addressed in the literature by incorporating Schmitt-trigger inverters for latch core in SRAM cells. However, a Schmitt-trigger based SRAM cell that can address the major performance parameters in all the three operating modes is not available in literature. In this regard, a new Schmitt-trigger based SRAM cell is presented that provides data-independent

vii

tolerance against PVT-variations in all the three modes. The proposed cell provides better write performance due to the presence of novel combination of Negative bitline write assist technique with modified Schmitt-trigger action. Further, fully-gated grounded scheme is used in isolated read port to reduce read bitline leakages.

FinFET is emerging as an alternative to CMOS technology due to its good scaling ability, high ON current, reduced  $V_{th}$  variations, better sub-threshold slope and short-channel effect. Therefore, an attempt is made to propose a FinFET based SRAM cell with an isolated read port that can address the issues of existing cells such as reduced stability of stored data, increased bitline load capacitance, increased leakages etc. The proposed cell achieve better data stability due to the isolation of internal storage nodes from external bitlines. The read bitline leakages are also reduced in un-accessed cells by maintaining similar operating conditions in the read port, independent of stored data values. Further, the increased driving strength of FinFET based cell results in high read current values providing significant improvement in read performance parameters. Additionally, the use of write assist transistor helps in quick charging of internal storage nodes resulting in faster write operation.

In the thesis, the performance of all the proposed SRAM cells is analyzed and compared based on various standard cell metrics. The functionality of proposed cells is verified in all the three operating modes and performance simulations are done using 32 nm bulk CMOS PTM model parameters. Further, the performance of FinFET based cell is verified using 22 nm FinFET PTM model parameters.

| CERTIFICATE        |                                                    | iii |

|--------------------|----------------------------------------------------|-----|

| CANDIDATE'S DECLAR | ATION                                              | iv  |

| ACKNOWLEDGEMENT    | ·S                                                 | v   |

| ABSTRACT           |                                                    | vi  |

| TABLE OF CONTENTS  |                                                    | ix  |

| LIST OF FIGURES    |                                                    | xii |

| LIST OF TABLES     |                                                    | xv  |

| ABBREVIATIONS      |                                                    | xvi |

| Chapter 1          | INTRODUCTION                                       | 1   |

|                    | 1.1 Background                                     | 2   |

|                    | 1.1.1 SRAM architecture                            | 2   |

|                    | 1.1.2 Conventional 6T SRAM cell                    | 5   |

|                    | 1.1.3 SRAM cell metrics                            | 7   |

|                    | 1.1.4 Issues with conventional 6T SRAM cell        | 12  |

|                    | 1.2 Literature Review and Scope of Work            | 13  |

|                    | 1.2.1 Challenges in SRAM cell design with scaling  | 13  |

|                    | 1.2.2 State-of-the-art SRAM cell designs           | 15  |

|                    | 1.2.3 Performance improvement                      | 16  |

|                    | 1.2.3.1 Approaches to improve read                 | 16  |

|                    | performance                                        |     |

|                    | 1.2.3.2 Approaches to improve write                | 18  |

|                    | performance                                        |     |

|                    | 1.2.3.3 Approaches to reduce leakages              | 19  |

|                    | 1.2.3.4 Approaches to improve PVT-variation        | 20  |

|                    | tolerance                                          |     |

|                    | 1.2.4 What is next at 28 nm and beyond?            | 21  |

|                    | 1.3 Objectives                                     | 22  |

|                    | 1.4 Organization of the Thesis                     | 23  |

|                    |                                                    |     |

| Chapter 2          | SRAM CELL DESIGN WITH LOW LEAKAGE IN SUB-THRESHOLD | 25  |

|                    | REGION                                             |     |

|                    | 2.1 Introduction                                   | 26  |

2.2 Leakage current components in conventional SRAM cells 27

|           | 2.3 Classification of leakage reduction techniques    | 28  |

|-----------|-------------------------------------------------------|-----|

|           | 2.3.1 Latch leakage reduction techniques              | 28  |

|           | 2.3.1.1 Multi-threshold CMOS technique                | 29  |

|           | 2.3.1.2 Substrate-bias technique                      | 30  |

|           | 2.3.1.3 Drowsy mode technique                         | 30  |

|           | 2.3.1.4 Comparative analysis                          | 31  |

|           | 2.3.2 Bitline leakage reduction techniques            | 41  |

|           | 2.3.2.1 Negative wordline technique                   | 44  |

|           | 2.3.2.2 Leakage biased bitline technique              | 44  |

|           | 2.3.2.3 Comparative analysis                          | 45  |

|           | 2.3.3 Read port leakage reduction techniques          | 52  |

|           | 2.3.3.1 Stack effect technique                        | 52  |

|           | 2.3.3.2 Dynamic control of power rail technique       | 53  |

|           | 2.3.3.3 Virtual cell ground technique                 | 53  |

|           | 2.3.3.4 Comparative analysis                          | 55  |

|           | 2.4 Design of SRAM cell with low leakage              | 67  |

|           | 2.4.1 Proposed cell I                                 | 67  |

|           | 2.4.1.1 Operation                                     | 68  |

|           | 2.4.1.2 Simulation results                            | 69  |

|           | 2.5 Conclusions                                       | 79  |

| Chapter 3 | SRAM CELL DESIGN WITH IMPROVED READ AND WRITE         | 82  |

|           | PERFORMANCE                                           |     |

|           | 3.1 Introduction                                      | 83  |

|           | 3.2 Existing SRAM cell designs with improved read and | 84  |

|           | write performance                                     |     |

|           | 3.3 Design of SRAM cell with improved read and write  | 87  |

|           | performance                                           |     |

|           | 3.3.1 Proposed cell II                                | 88  |

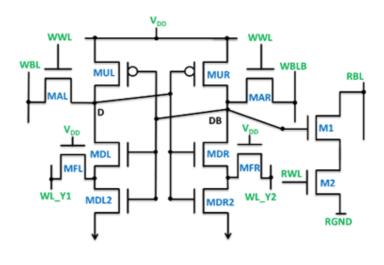

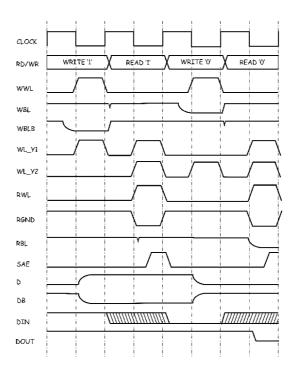

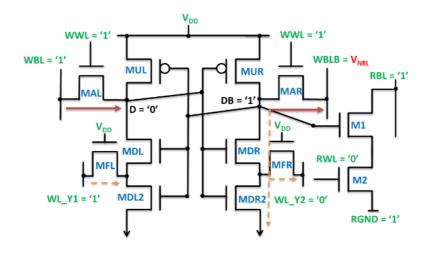

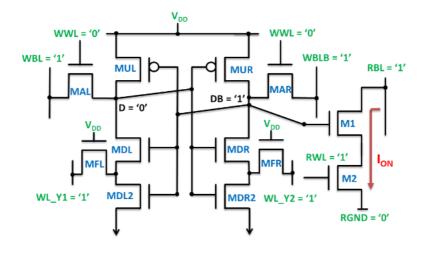

|           | 3.3.1.1 Operation                                     | 89  |

|           | 3.3.1.2 Simulation results                            | 91  |

|           | 3.3.2 Proposed cell III                               | 99  |

|           | 3.3.2.1 Operation                                     | 100 |

|           | 3.3.2.2 Simulation results                            | 107 |

|           | 3.4 Conclusions                                       | 117 |

| Chapter 4 | SRAM CELL DESIGN WITH PVT-VARIATION TOLERANCE         | 119 |

|           | 4.1 Introduction                                      | 120 |

|           |                                                       |     |

х

|              | 4.2 Existing SRAM cell designs with PVT-variation tolerance | 120 |

|--------------|-------------------------------------------------------------|-----|

|              | 4.3 Design of SRAM cell with PVT-variation tolerance        | 124 |

|              | 4.3.1 Proposed cell IV                                      | 124 |

|              | 4.3.1.1 Operation                                           | 125 |

|              | 4.3.1.2 Simulation results                                  | 128 |

|              | 4.4 Conclusions                                             | 145 |

| Chapter 5    | SRAM CELL DESIGN WITH IMPROVED TRANSISTOR TECHNOLOGY        | 146 |

|              | 5.1 Introduction                                            | 147 |

|              | 5.2 Existing SRAM cell designs with improved transistor     | 147 |

|              | technology                                                  |     |

|              | 5.3 Design of SRAM cell with improved transistor            | 148 |

|              | technology                                                  |     |

|              | 5.3.1 Proposed cell V                                       | 148 |

|              | 5.3.1.1 Operation                                           | 149 |

|              | 5.3.1.2 Simulation results                                  | 151 |

|              | 5.4 Conclusions                                             | 159 |

| Chapter 6    | CONCLUSION AND FUTURE SCOPE                                 | 160 |

|              | 6.1 Summary of work done in the Thesis                      | 161 |

|              | 6.2 Future Scope                                            | 163 |

| REFERENCES   |                                                             | 165 |

| PUBLICATIONS |                                                             | 184 |

## LIST OF FIGURES

| Fig. 1.1  | Memory hierarchy of modern computer system                                             | 2  |

|-----------|----------------------------------------------------------------------------------------|----|

| Fig. 1.2  | SRAM architecture                                                                      | 3  |

| Fig. 1.3  | Pre-charge circuit for SRAM                                                            | 4  |

| Fig. 1.4  | Schematic of Conventional 6T SRAM cell                                                 | 5  |

| Fig. 2.1  | Leakage currents in conventional SRAM cells (a) 6T (b) 8T SRAM cells                   | 28 |

| Fig. 2.2  | Schematic of 6T SRAM cell with (a) MTCMOS (b) SB (c) DM techniques                     | 30 |

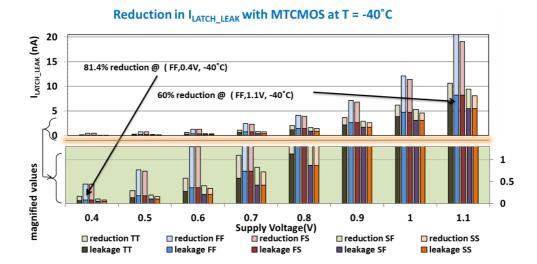

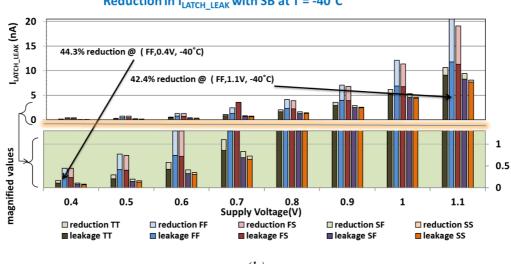

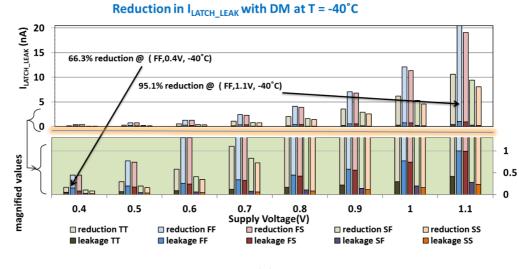

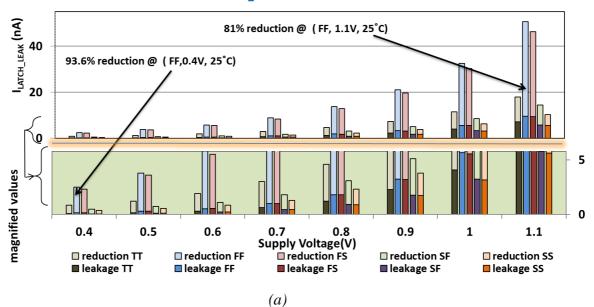

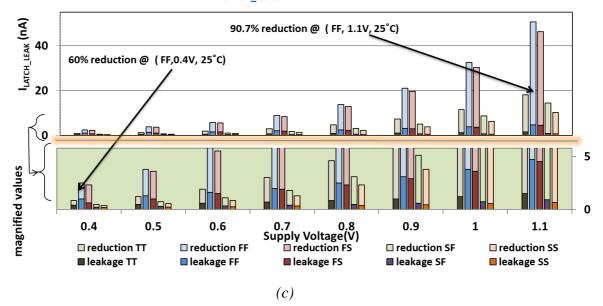

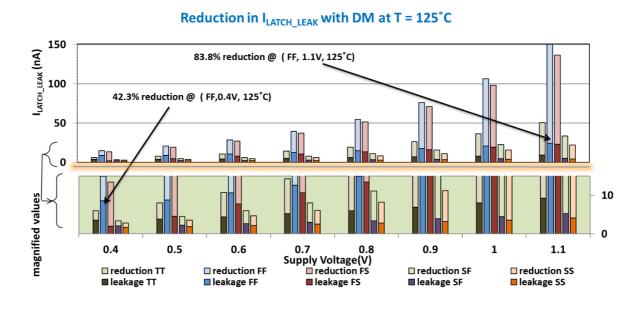

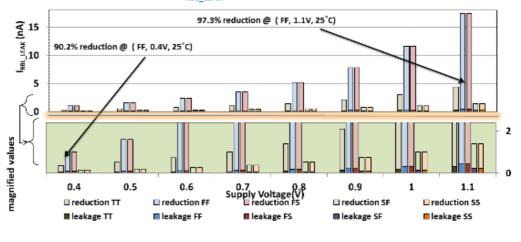

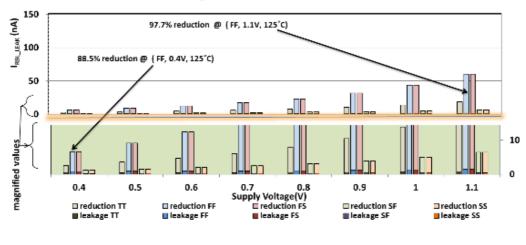

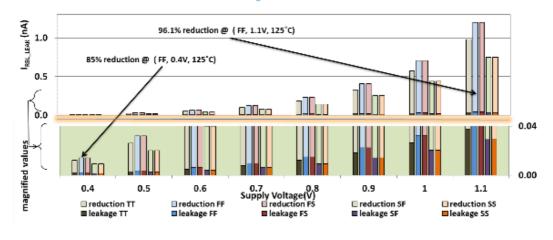

| Fig. 2.3  | Effect on $I_{LATCH\_LEAK}$ at $T = -40$ °C                                            | 33 |

| Fig. 2.4  | Effect on $I_{LATCH\_LEAK}$ at $T = 25$ °C                                             | 35 |

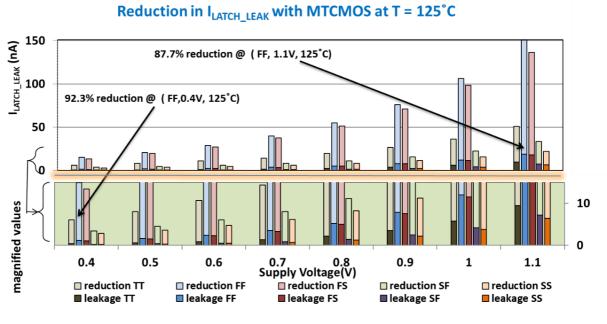

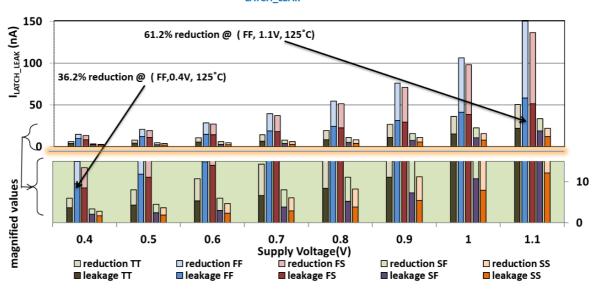

| Fig. 2.5  | Effect on $I_{LATCH\_LEAK}$ at $T = 125$ °C                                            | 36 |

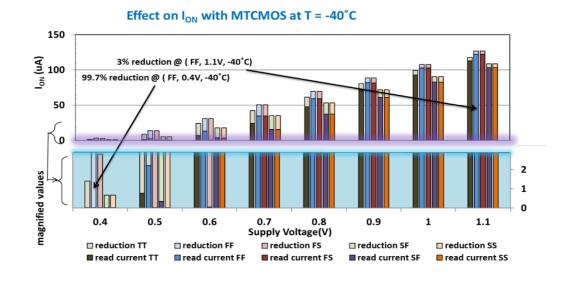

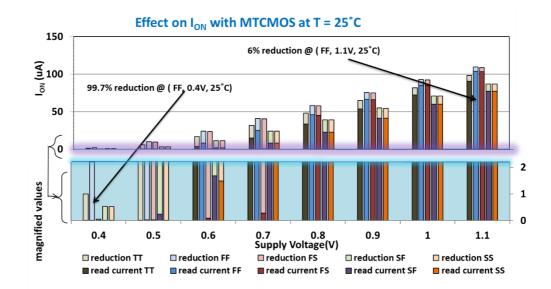

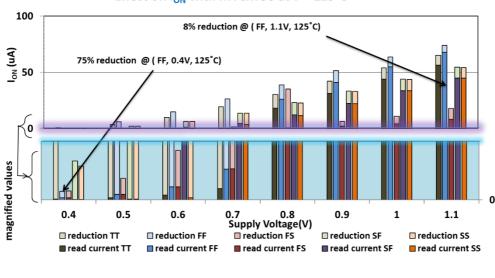

| Fig. 2.6  | Effect on $I_{ON}$ using MTCMOS technique at (a) -40 °C (b) 25 °C (c) 125 °C           | 38 |

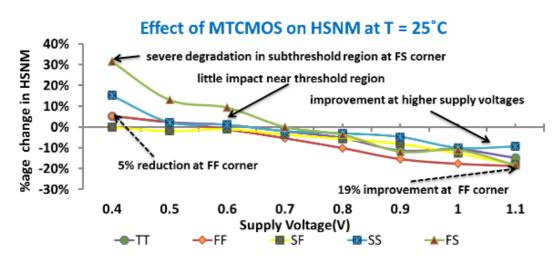

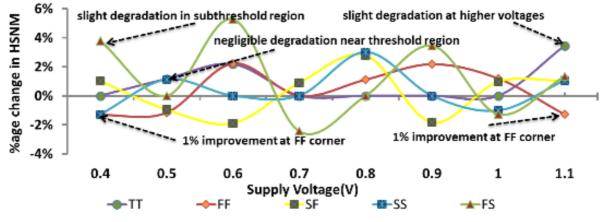

| Fig. 2.7  | Effect on HSNM at 25 °C                                                                | 39 |

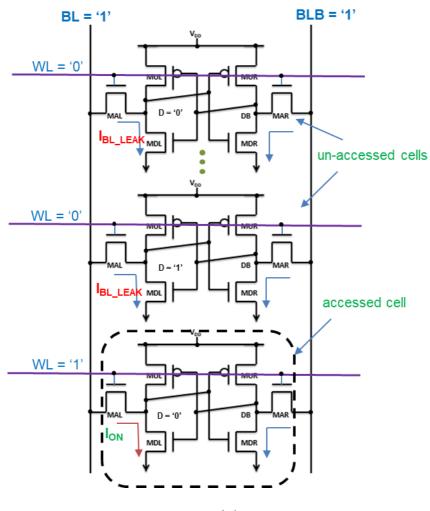

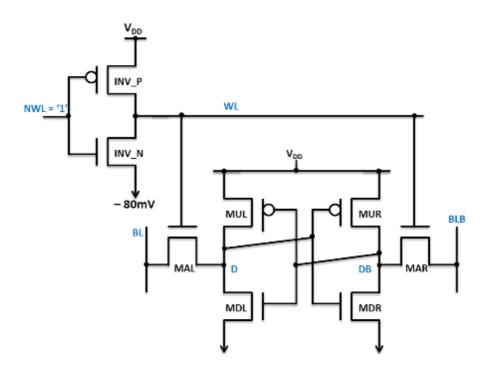

| Fig. 2.8  | (a) Flow of current in accessed and un-accessed cells (b) Schematic of 6T SRAM         | 43 |

|           | cell with NWL technique (c) Sub-banks with LBB technique in Hierarchical bit line      |    |

|           | architecture                                                                           |    |

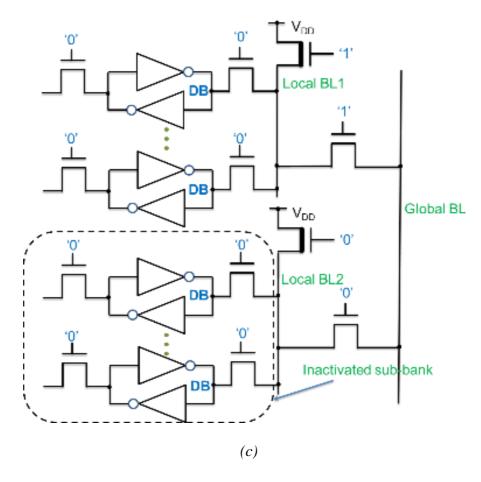

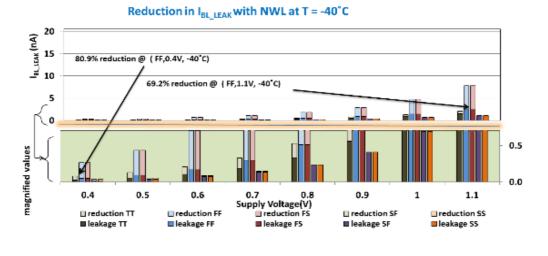

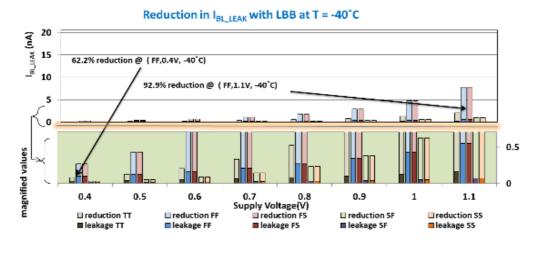

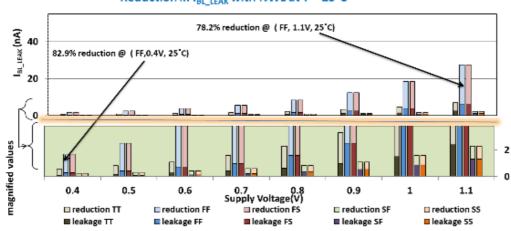

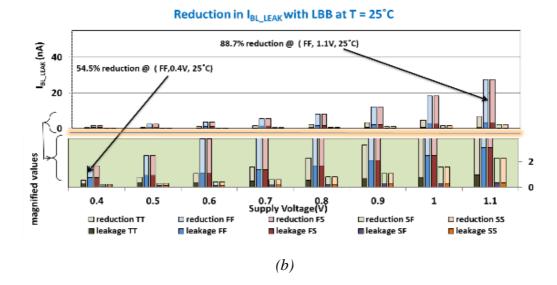

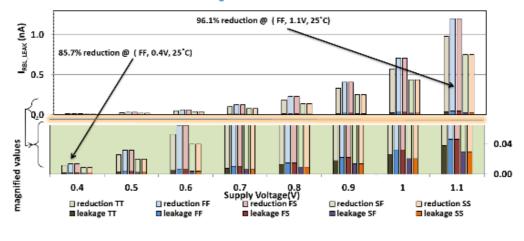

| Fig. 2.9  | Effect on $I_{BL\_LEAK}$ at $T = -40$ °C                                               | 46 |

| Fig. 2.10 | Effect on $I_{BL\_LEAK}$ at $T = 25$ °C                                                | 47 |

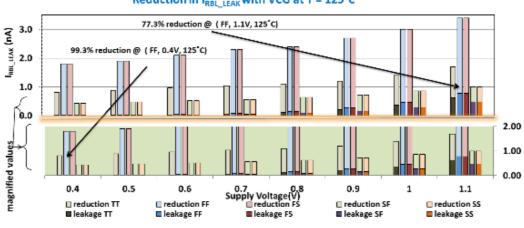

| Fig. 2.11 | Effect on $I_{BL\_LEAK}$ at $T = 125$ °C                                               | 47 |

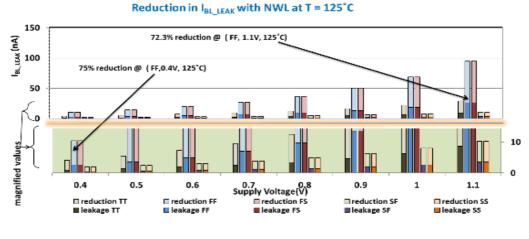

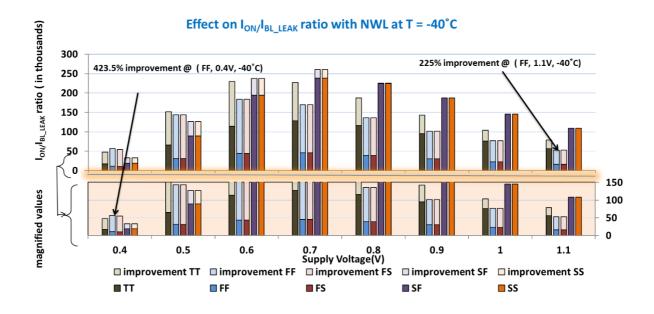

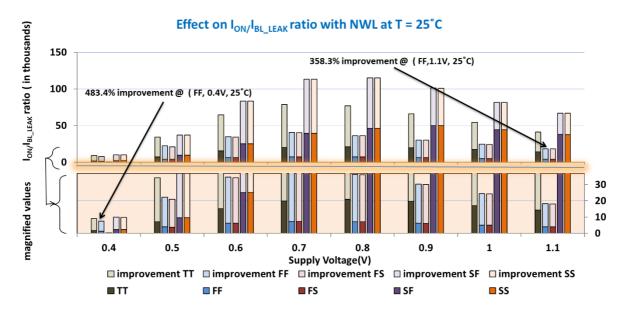

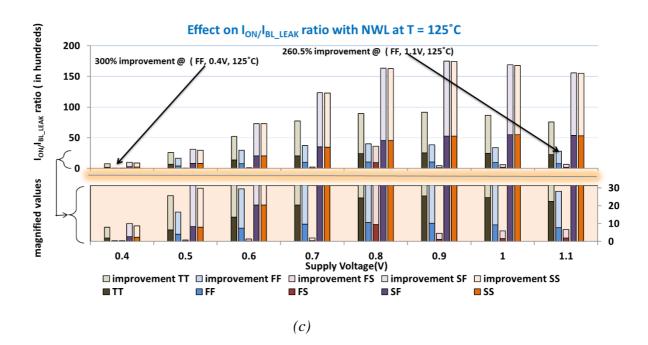

| Fig. 2.12 | Effect on ION/IBL_LEAK ratio using NWL technique                                       | 49 |

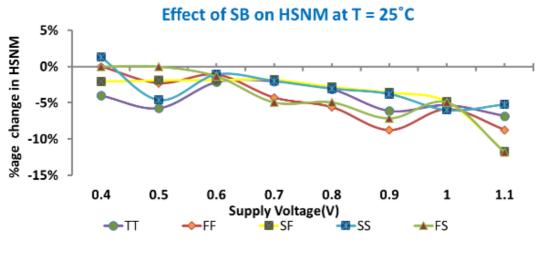

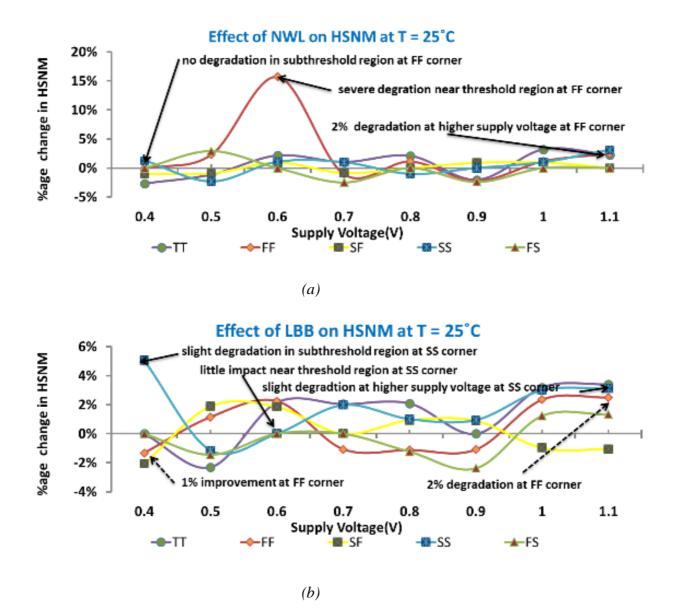

| Fig. 2.13 | Effect on HSNM at 25 °C                                                                | 50 |

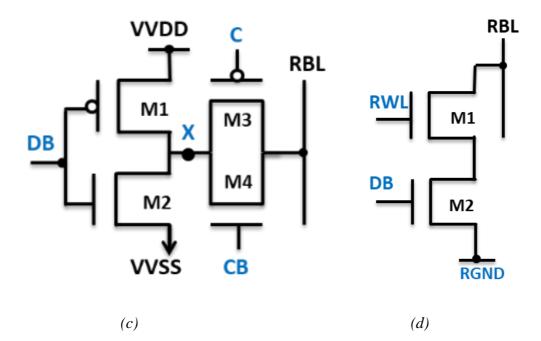

| Fig. 2.14 | Read ports using (a, b) Stack effect (c) DCPR (d) VCG techniques                       | 54 |

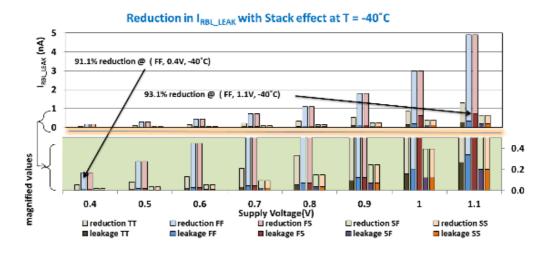

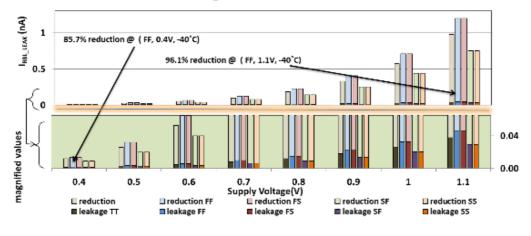

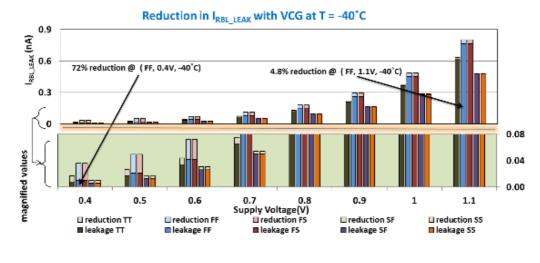

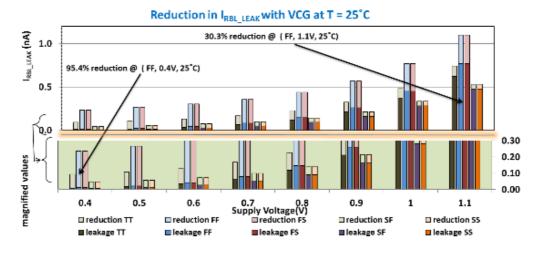

| Fig. 2.15 | Effect on $I_{RBL\_LEAK}$ at $T = -40$ °C                                              | 56 |

| Fig. 2.16 | Effect on $I_{RBL\_LEAK}$ at $T = 25$ °C                                               | 57 |

| Fig. 2.17 | Effect on $I_{RBL\_LEAK}$ at $T = 125$ °C                                              | 58 |

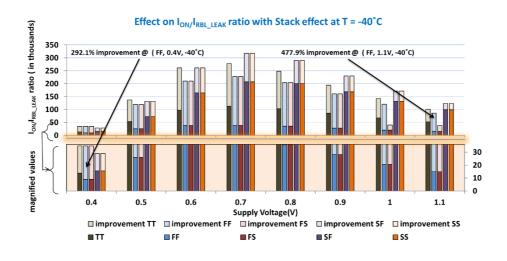

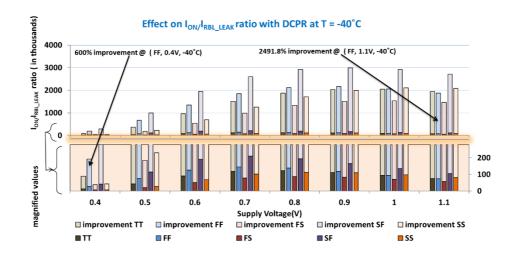

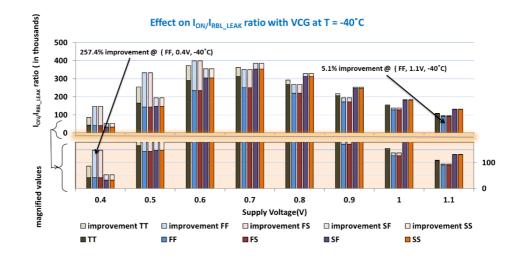

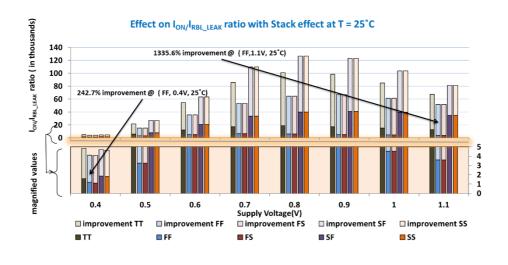

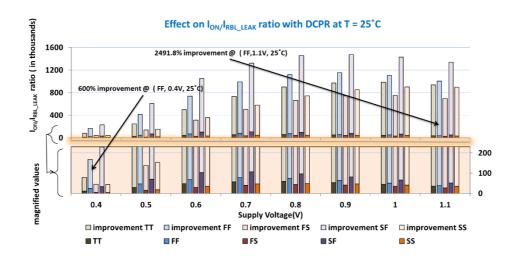

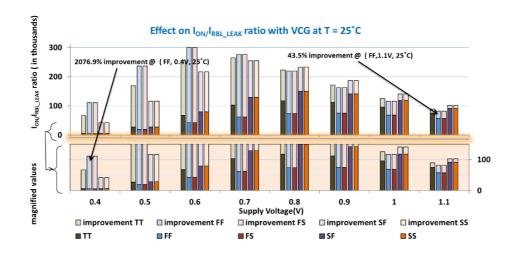

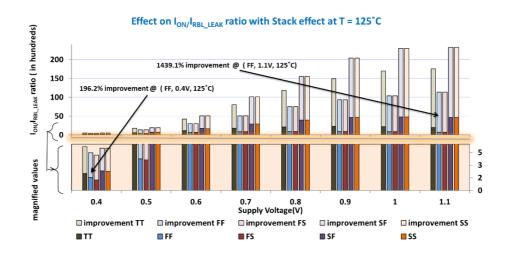

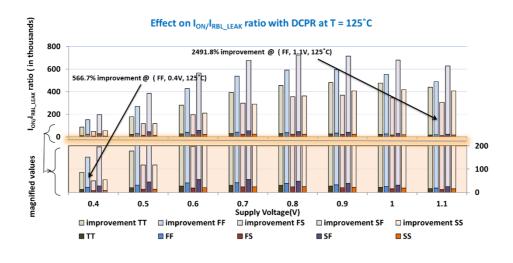

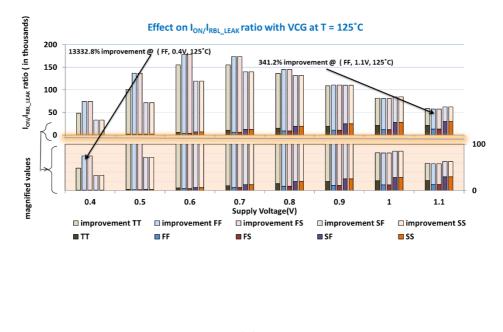

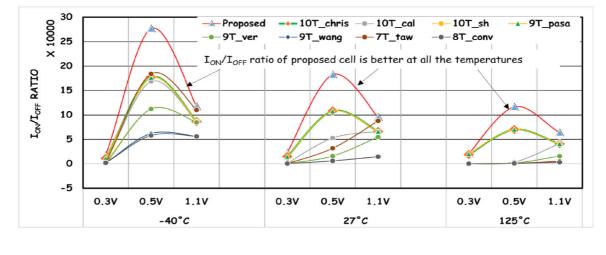

| Fig. 2.18 | Effect on $I_{ON}/I_{RBL\_LEAK}$ ratio at $T = -40$ °C                                 | 61 |

| Fig. 2.19 | Effect on $I_{ON}/I_{RBL\_LEAK}$ ratio at $T = 25$ °C                                  | 63 |

| Fig. 2.20 | Effect on $I_{ON}/I_{RBL\_LEAK}$ ratio at $T = 125$ °C                                 | 64 |

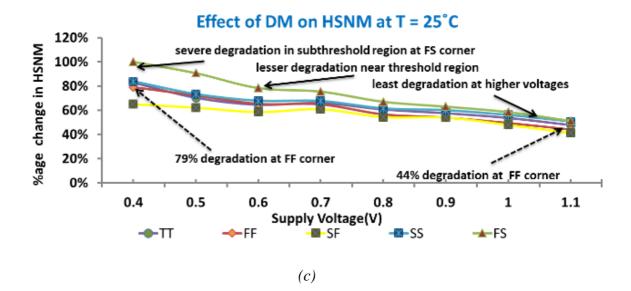

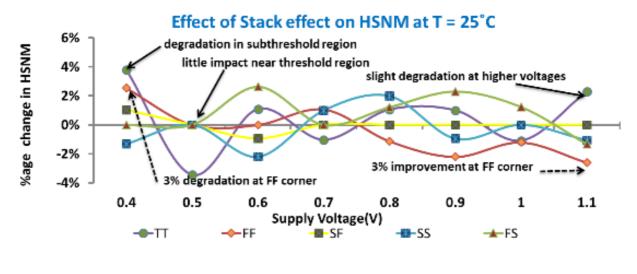

| Fig. 2.21 | Effect on HSNM at 25 °C                                                                | 65 |

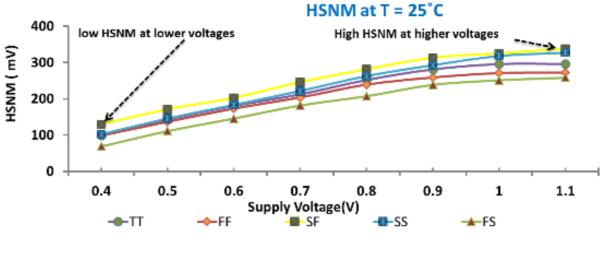

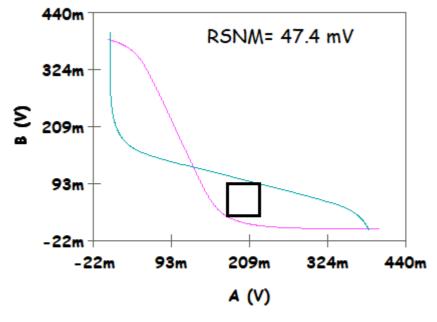

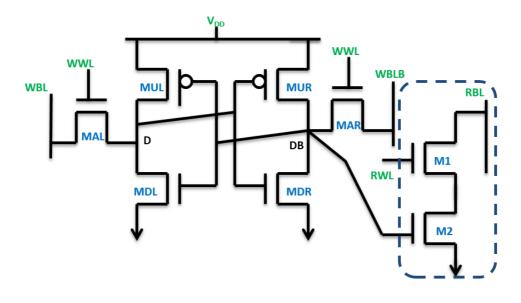

| Fig. 2.22 | Proposed cell I (a) Schematic (b) Operating conditions                                 | 68 |

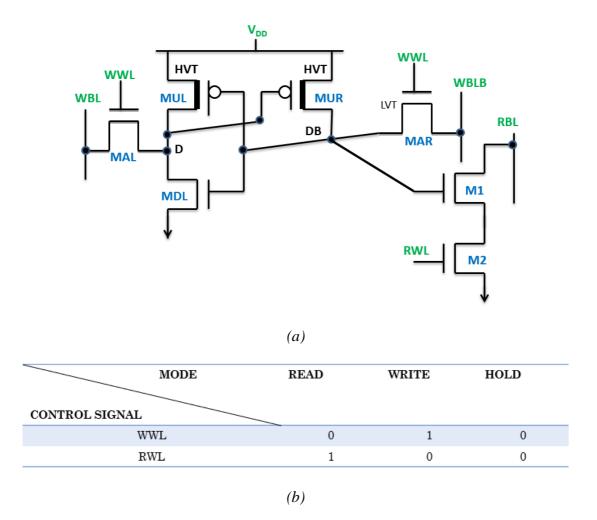

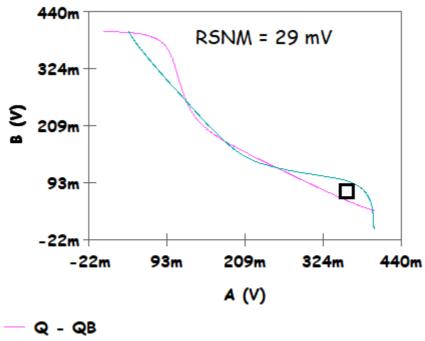

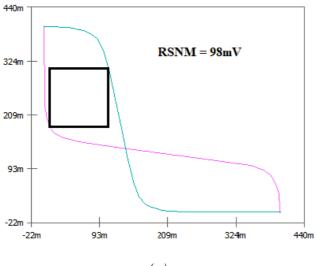

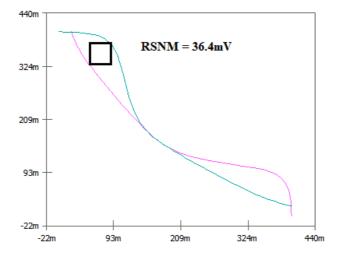

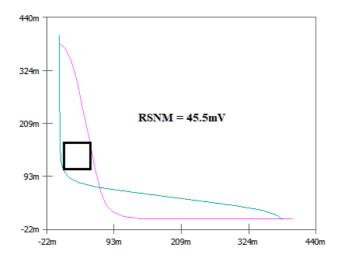

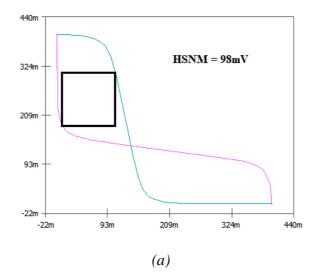

| Fig. 2.23 | RSNM at $V_{DD} = 0.4 V$ for (a) Proposed cell I (b) Conventional 6T (c) 7T_taw SRAM   | 72 |

|           | cells                                                                                  |    |

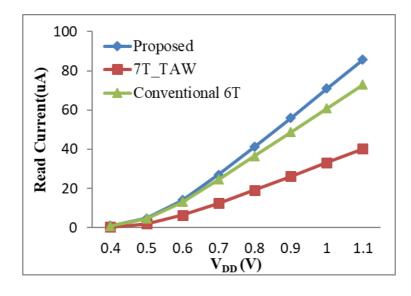

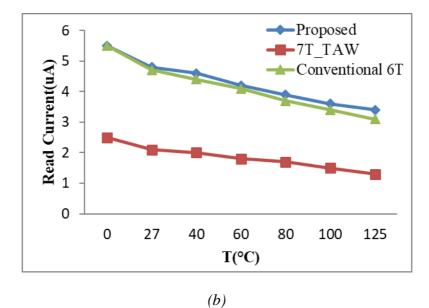

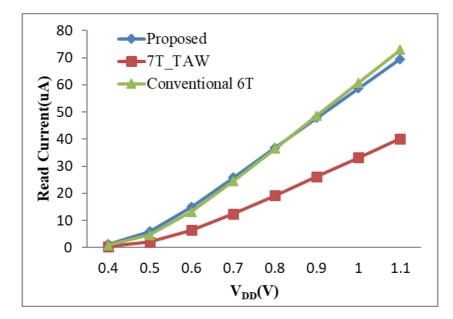

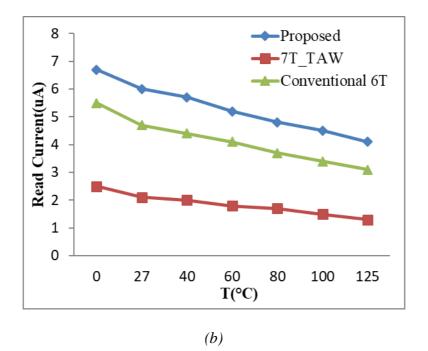

| Fig. 2.24 | $I_{ON}$ of Proposed cell I, Conventional 6T and 7T_taw cells under (a) Supply voltage | 73 |

|           | variations at 27 °C and (b) Temperature variations at $V_{DD} = 0.4 V$                 |    |

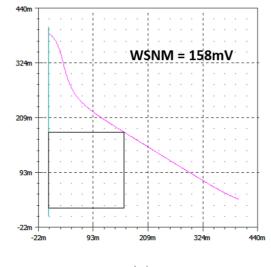

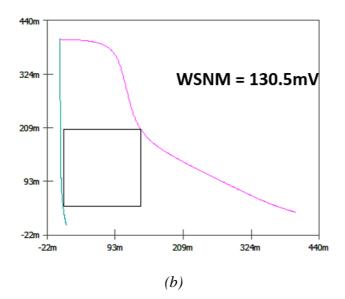

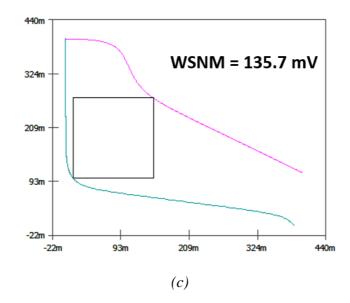

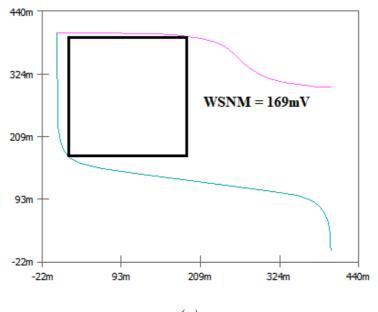

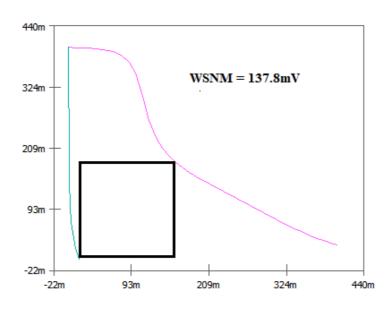

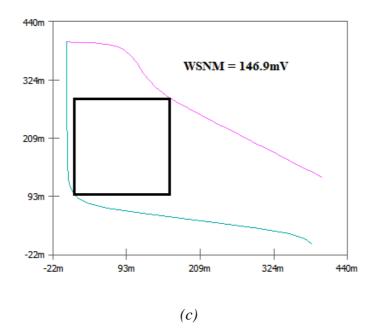

| Fig. 2.25 | WSNM at $V_{DD} = 0.4$ V for (a) Proposed cell I (b) Conventional 6T (c) 7T_taw SRAM   | 75 |

|           | cells                                                                                  |    |

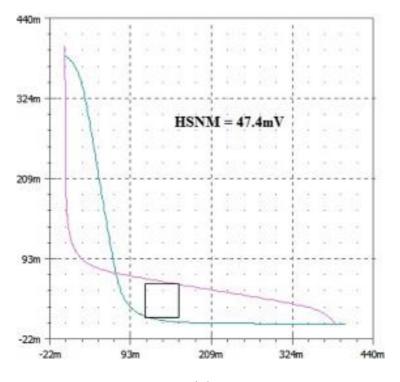

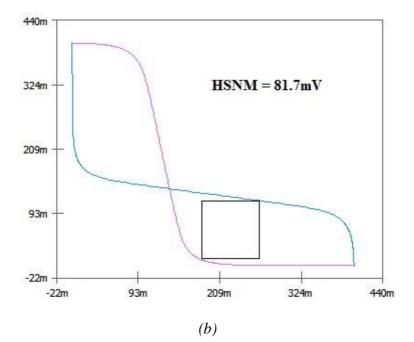

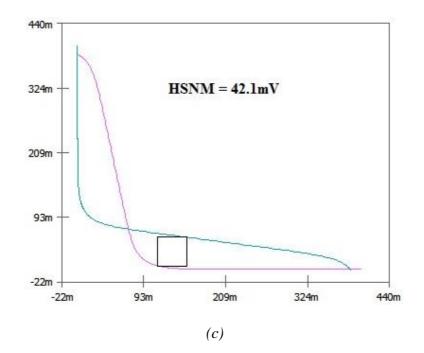

| Fig. 2.26 | HSNM at $V_{DD} = 0.4 V$ for (a) Proposed cell I (b) Conventional 6T (c) 7T_taw SRAM   | 77 |

|           | cells                                                                                  |    |

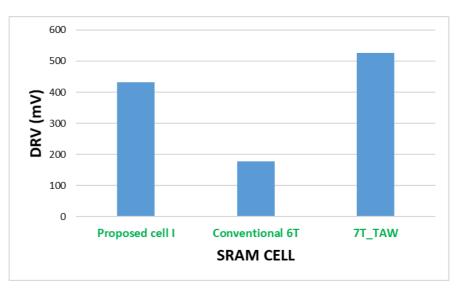

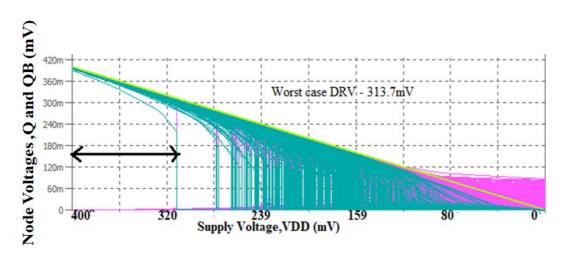

| Fig. 2.27 | DRV for Proposed cell I, Conventional 6T and 7T_taw SRAM cells                                                                   | 77  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|-----|

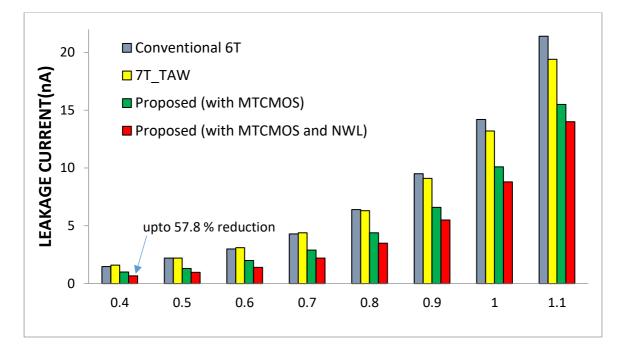

| Fig. 2.28 | ILEAK for Proposed cell I (with MTCMOS only and with both MTCMOS and NWL),                                                       | 78  |

|           | Conventional 6T and 7T_taw SRAM cells                                                                                            |     |

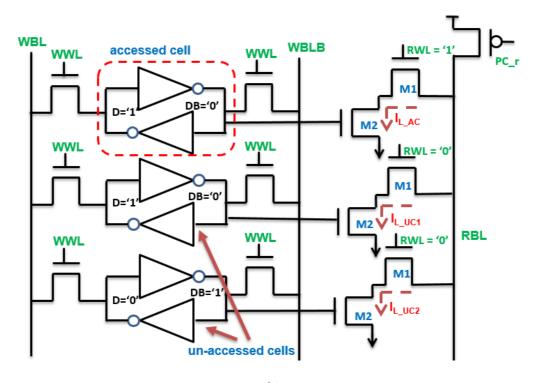

| Fig. 3.1  | Conventional 8T SRAM cell (a) Read operation (b) Leakage current components in                                                   | 86  |

|           | accessed and un-accessed cells (c) Impact of leakage currents on $\Delta V_{RBL}$                                                |     |

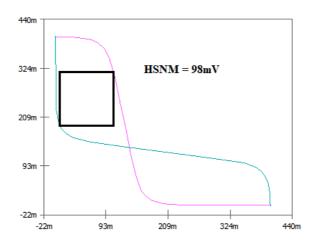

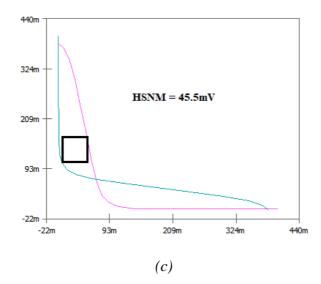

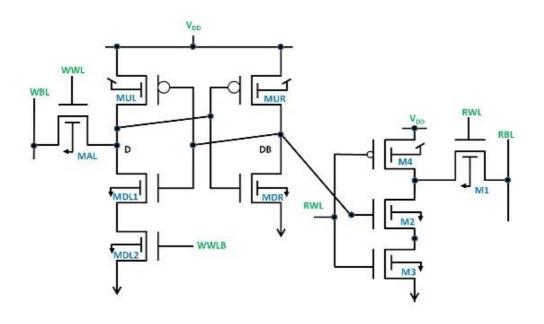

| Fig. 3.2  | Proposed cell II (a) Schematic (b) Operating conditions                                                                          | 89  |

| Fig. 3.3  | <i>RSNM at</i> $V_{DD} = 0.4$ <i>V and</i> $T = 27$ ° <i>C for (a) Proposed cell II (b) Conventional</i> 6 <i>T</i> ( <i>c</i> ) | 93  |

|           | 7T_taw SRAM cells                                                                                                                |     |

| Fig. 3.4  | Ion for Proposed cell II, Conventional 6T and 7T_taw cells under (a) Supply                                                      | 94  |

|           | voltage variations and (b) Temperature variations                                                                                |     |

| Fig. 3.5  | WSNM at $V_{DD} = 0.4$ V and T=27 °C for (a) Proposed cell II (b) Conventional 6T (c)                                            | 96  |

|           | 7T_taw SRAM cells                                                                                                                |     |

| Fig. 3.6  | HSNM at $V_{DD} = 0.4$ V and $T = 27$ °C for (a) Proposed cell II (b) Conventional 6T                                            | 97  |

|           | (c) 7T_taw SRAM cells                                                                                                            |     |

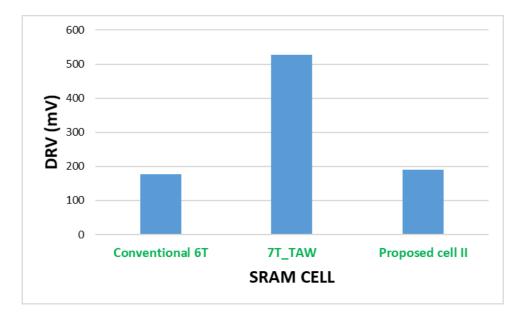

| Fig. 3.7  | DRV for Proposed cell II, Conventional 6T and 7T_taw SRAM cells                                                                  | 98  |

| Fig. 3.8  | Worst-case DRV of the Proposed cell II at $T = 27 \text{ °C}$ under $6\sigma$ global process and                                 | 98  |

|           | $1\sigma$ local mismatch variations                                                                                              |     |

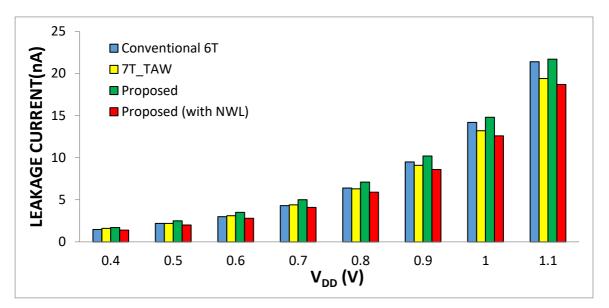

| Fig. 3.9  | ILEAK for Proposed cell II (with and without NWL), Conventional 6T and 7T_taw                                                    | 99  |

|           | SRAM cells                                                                                                                       |     |

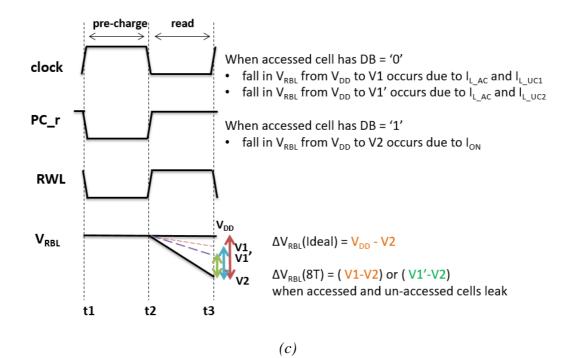

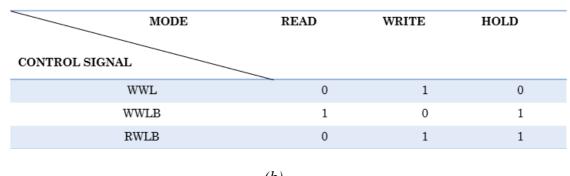

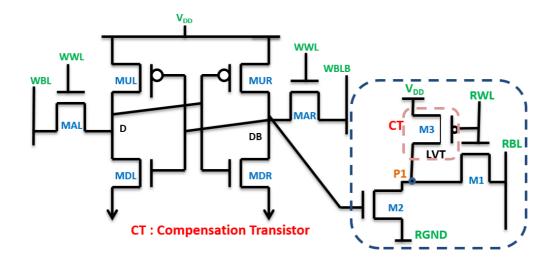

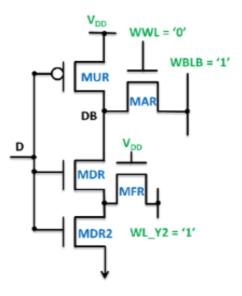

| Fig. 3.10 | Proposed cell III (a) Schematic (b) Operating conditions                                                                         | 100 |

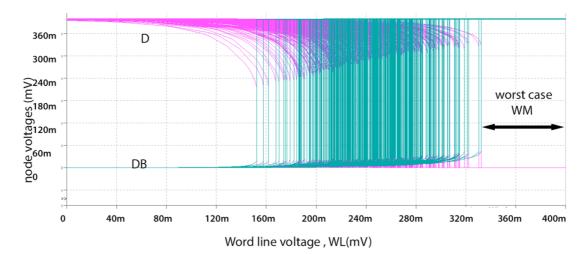

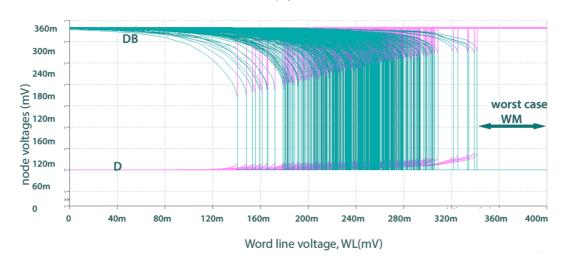

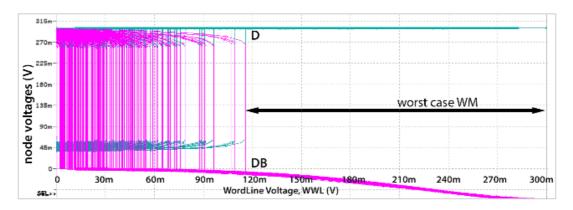

| Fig. 3.11 | WM (a) Worst-case WM ('0') (b) Worst-case WM ('1') for the Proposed cell III at                                                  | 101 |

|           | $V_{DD} = 0.4 V$ under 6 $\sigma$ global process and 1 $\sigma$ local mismatch variations (500 points)                           |     |

| Fig. 3.12 | P1 node voltage distribution in un-accessed cell for (a) $DB = 0^{\circ}$ and (b) $DB = 1^{\circ}$                               | 103 |

|           | at $V_{DD} = 0.4 V$ under 6 $\sigma$ global process and 1 $\sigma$ local mismatch variations (500                                |     |

|           | points)                                                                                                                          |     |

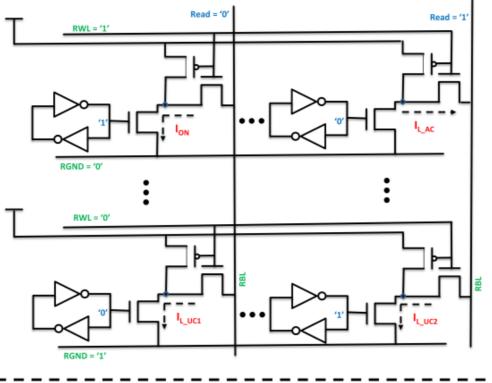

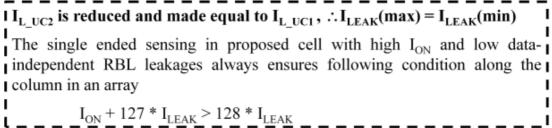

| Fig. 3.13 | RBL leakages in (a) Proposed cell III (b) 8T_conv SRAM cells                                                                     | 105 |

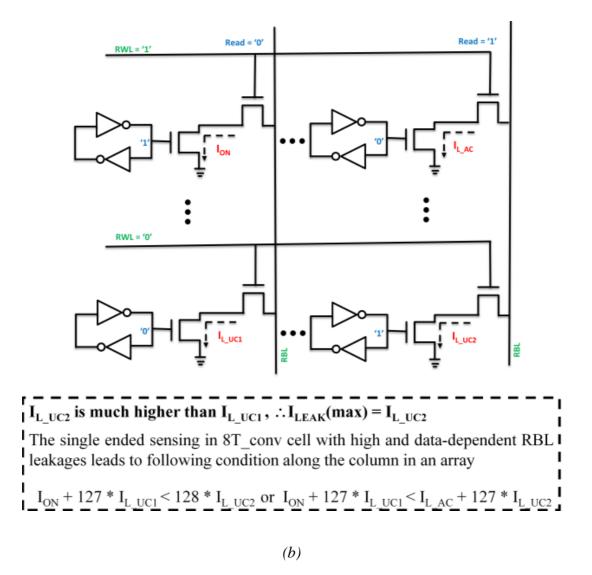

| Fig. 3.14 | (a) Impact of leakage currents on $\Delta V_{RBL}$ (b) Worst-case Hold '0' margin and Hold                                       | 106 |

|           | '1' margin for the Proposed cell III at $V_{DD}$ = 0.4 V under 6 $\sigma$ global process and 1 $\sigma$                          |     |

|           | local mismatch variations (500 points)                                                                                           |     |

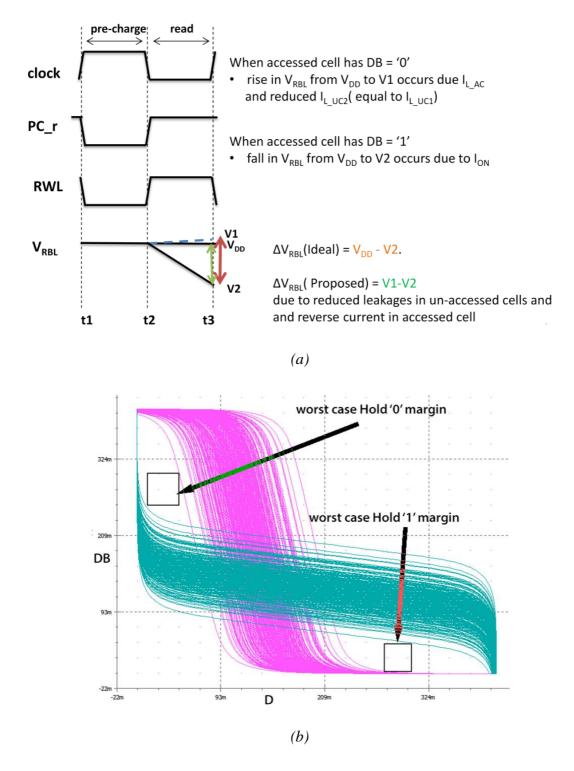

| Fig. 3.15 | Effect of (a) process corners (at $T = 27$ °C) and (b) temperature (at TT corner) on                                             | 110 |

|           | I <sub>ON</sub> /I <sub>OFF</sub> ratio                                                                                          |     |

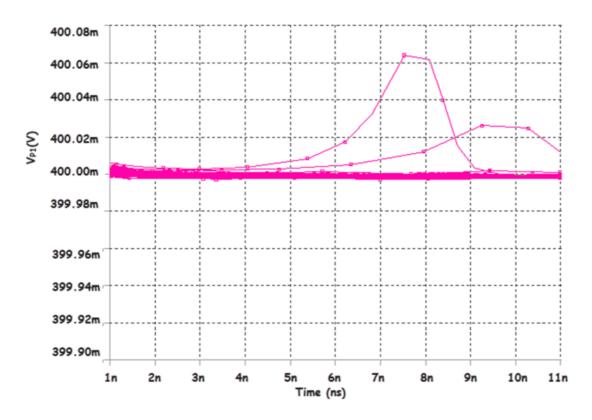

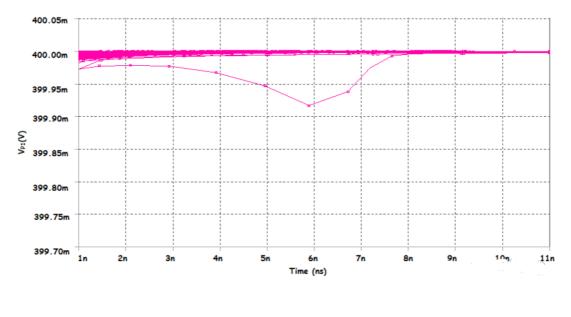

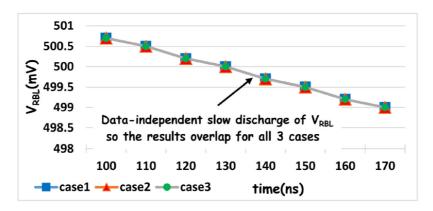

| Fig. 3.16 | RBL voltage of the Proposed cell III for three different data patterns in un-accessed                                            | 112 |

|           | cells                                                                                                                            |     |

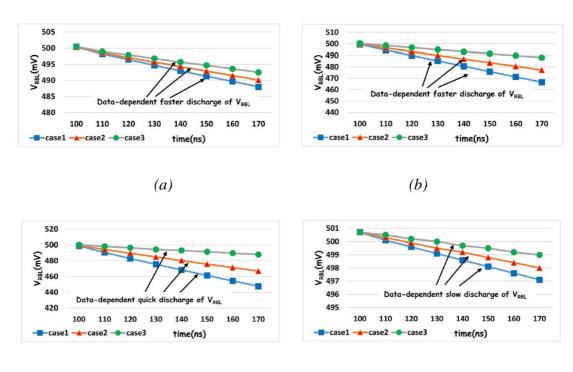

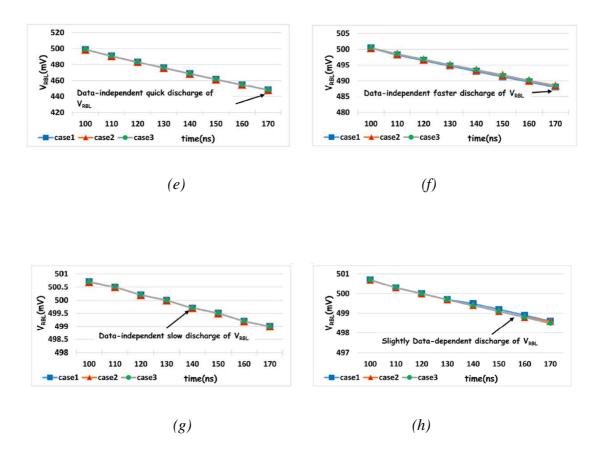

| Fig. 3.17 | RBL voltage of existing cells for three different data patterns in un-accessed cells                                             | 113 |

|           | (a) 9T_ver, (b) 7T_taw, (c) 8T_conv, (d) 10T_cal, (e) 9T_wang, (f) 10T_sh, (g)                                                   |     |

|           | 10T_chris, and (h) 9T_pasa SRAM cells                                                                                            |     |

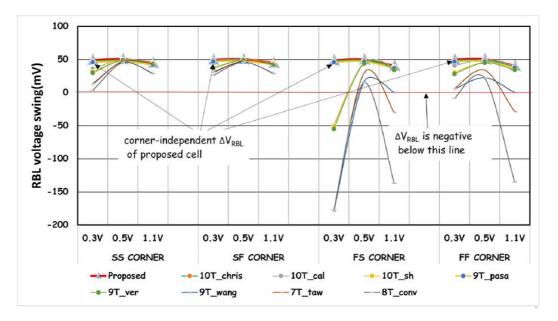

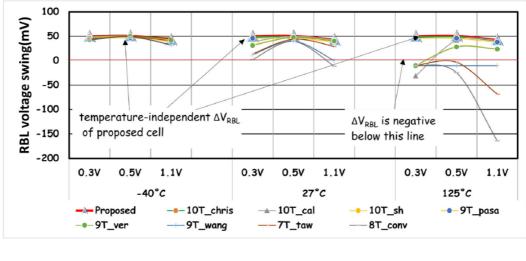

| Fig. 3.18 | Effect of (a) process corners (at $T = 27$ °C) and (b) temperature (at TT corner) on                                             | 115 |

|           | $\Delta V_{RBL}$                                                                                                                 |     |

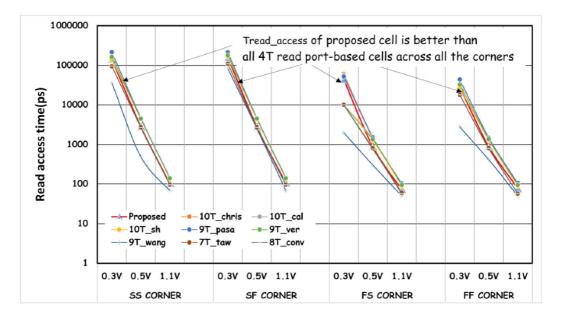

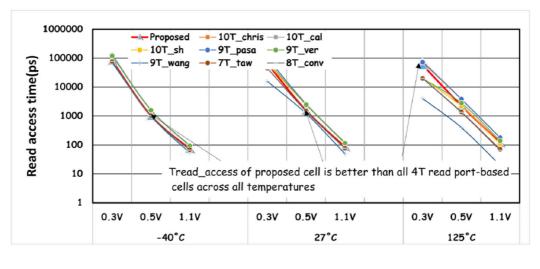

| Fig. 3.19 | Effect of (a) process corners (at $T = 27$ °C) and (b) temperature (at TT corner) on                                             | 117 |

|           | T <sub>READ_ACCESS</sub>                                                                                                         |     |

|           |                                                                                                                                  |     |

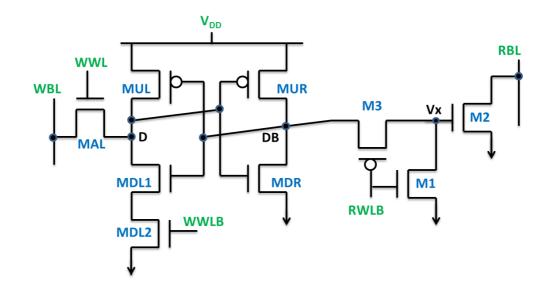

| Fig. 4.1  | Proposed cell IV (a) Schematic (b) Operating conditions                                              | 125 |

|-----------|------------------------------------------------------------------------------------------------------|-----|

| Fig. 4.2  | Proposed cell IV (a) Timing diagram (b) Write operation (c) Read operation                           | 128 |

| Fig. 4.3  | (a) Schematic of ST inverter (b) VTC of Proposed cell IV (c) VTC of 8T_conv cell                     | 131 |

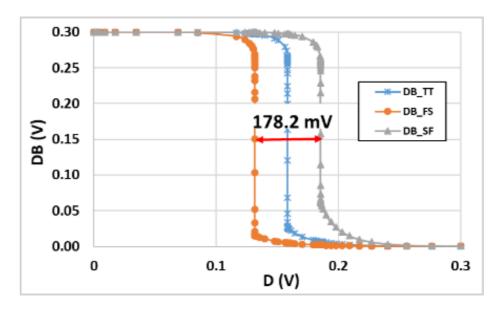

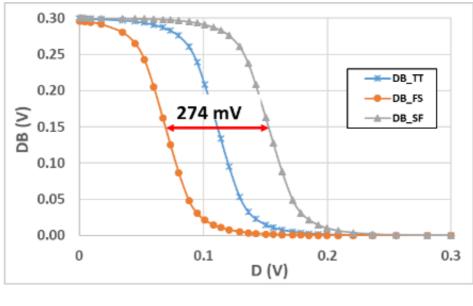

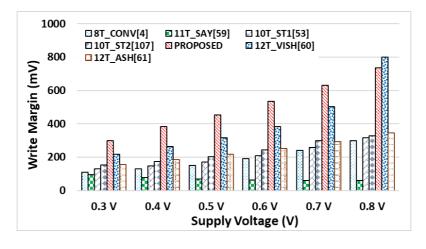

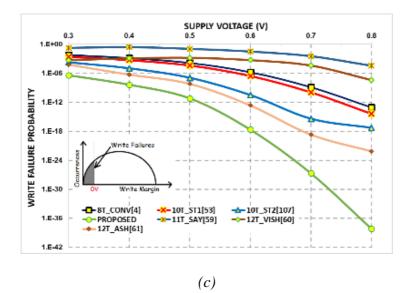

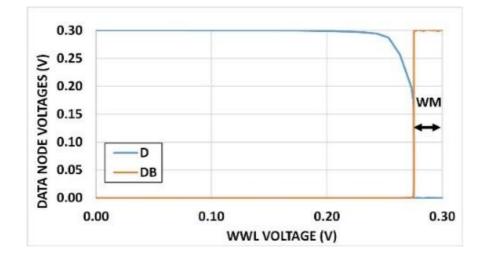

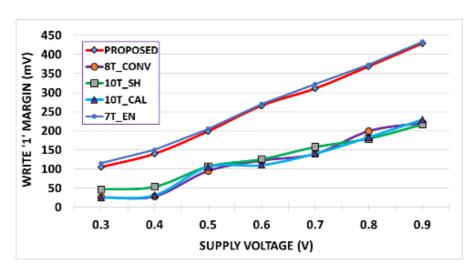

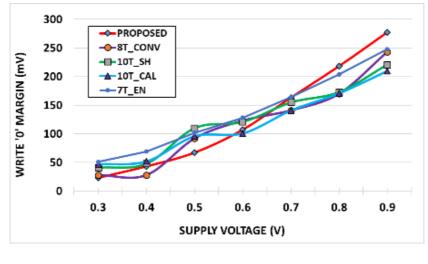

| Fig. 4.4  | WM (a) Effect of supply voltage on WM (27 $^{\circ}$ C, TT corner) (b) Worst-case WM for             | 132 |

|           | the Proposed cell IV under 6 $\sigma$ global process and 1 $\sigma$ local mismatch variations        |     |

|           | (1000 points) (c) Effect of PVT-variations on WM in terms of write failure                           |     |

|           | probability                                                                                          |     |

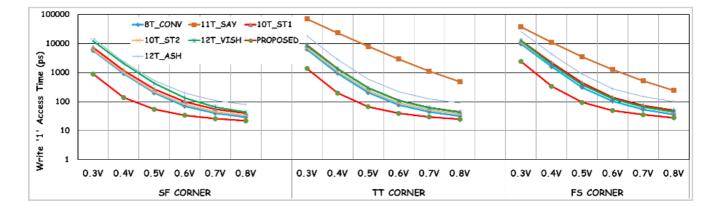

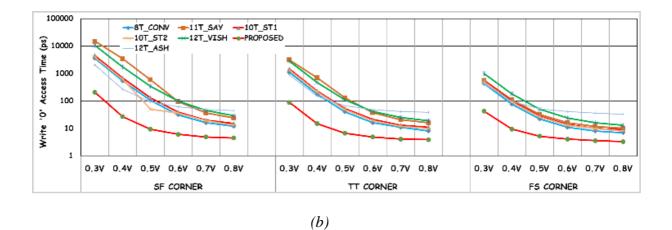

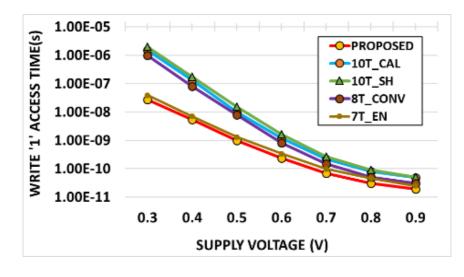

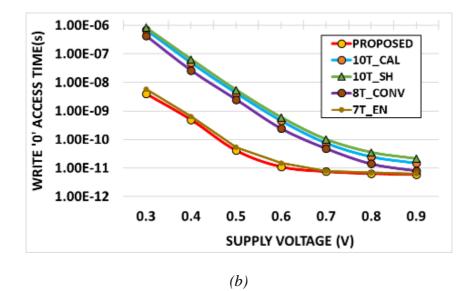

| Fig. 4.5  | $T_{WRITE\_ACCESS}(a) T_{WRITE\_ACCESS}('1')(b) T_{WRITE\_ACCESS}('0')$ at different supply voltages | 135 |

|           | and corners                                                                                          |     |

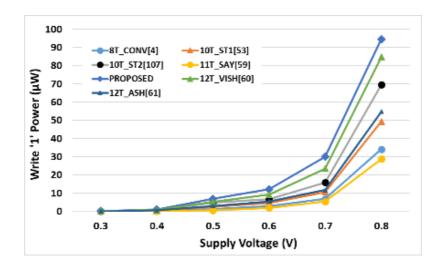

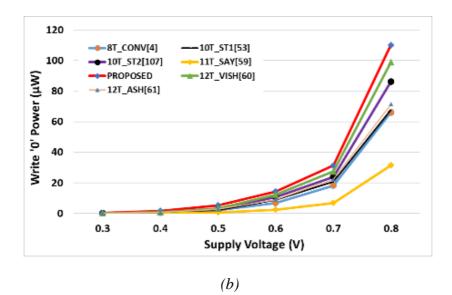

| Fig. 4.6  | $P_{WRITE}(a) P_{WRITE}('1')$ (b) $P_{WRITE}('0')$ at different supply voltages (27 °C, TT corner)   | 136 |

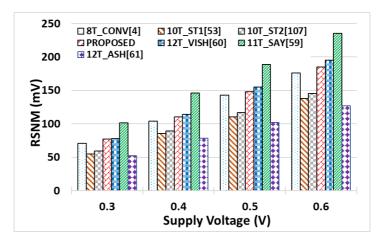

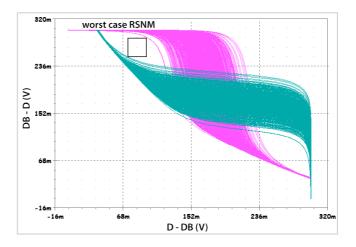

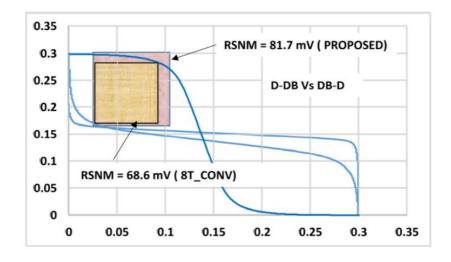

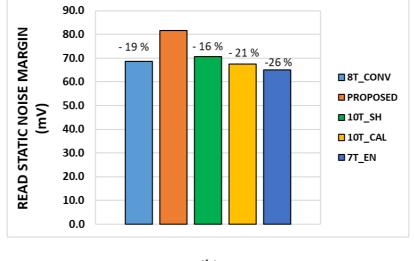

| Fig. 4.7  | RSNM (a) Effect of supply voltage on RSNM (27 °C, TT corner) (b) Worst-case                          | 137 |

|           | RSNM for the Proposed cell IV under 6 $\sigma$ global process and 1 $\sigma$ local mismatch          |     |

|           | variations (1000 points) (c) Effect of PVT-variations on RSNM in terms of read                       |     |

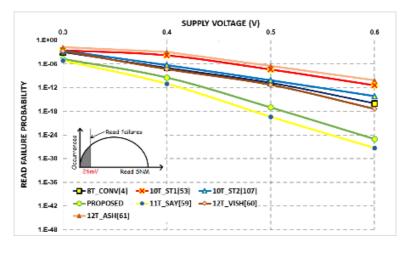

|           | failure probability                                                                                  |     |

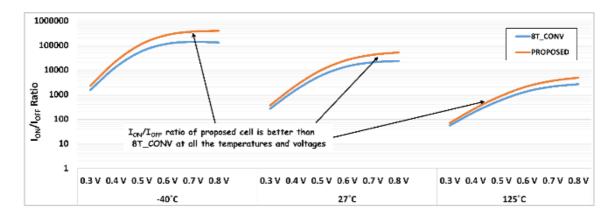

| Fig. 4.8  | Effect of supply voltage and temperature on $I_{ON}/I_{OFF}$ ratio for Proposed cell IV and          | 139 |

|           | 8T_conv SRAM cells                                                                                   |     |

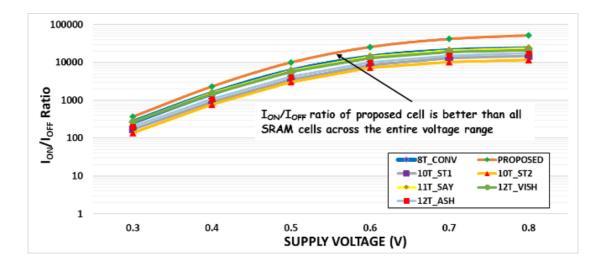

| Fig. 4.9  | $I_{ON}/I_{OFF}$ ratio at different supply voltages (27 °C, TT corner)                               | 139 |

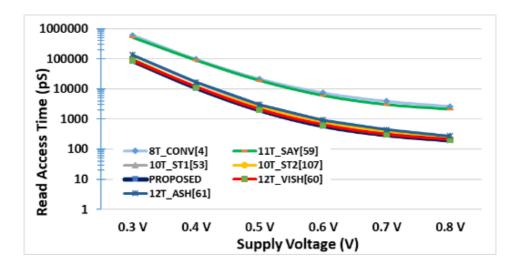

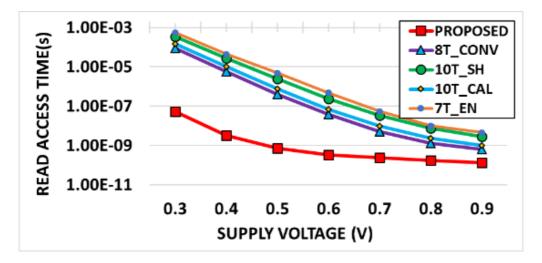

| Fig. 4.10 | $T_{READ\_ACCESS}$ at different supply voltages (27 °C, TT corner)                                   | 140 |

| Fig. 4.11 | $P_{READ}$ at different supply voltages (27 °C, TT corner)                                           | 141 |

| Fig. 4.12 | HSNM (a) Effect of supply voltage on HSNM (27 $^{\circ}$ C, TT corner) (b) Effect of PVT-            | 142 |

|           | variations on HSNM in terms of hold failure probability                                              |     |

| Fig. 4.13 | $P_{LEAK}$ at different supply voltages (27 °C, TT corner)                                           | 143 |

| Fig. 5.1  | Proposed cell V (a) Schematic (b) Operating conditions                                               | 149 |

| Fig. 5.2  | WM at 27 °C (a) Simulated plot for Proposed cell V (b) WM ('1') (c) WM ('0')                         | 153 |

| Fig. 5.3  | $T_{WRITE\_ACCESS}$ at 27 °C (a) $T_{WRITE\_ACCESS}$ ('1') (b) $T_{WRITE\_ACCESS}$ ('0')             | 154 |

| Fig. 5.4  | RSNM (a) Simulated butterfly curves (b) RSNM values at 0.3 V and 27 $^{\circ}C$                      | 155 |

| Fig. 5.5  | $T_{READ\_ACCESS}$ at 27 °C                                                                          | 156 |

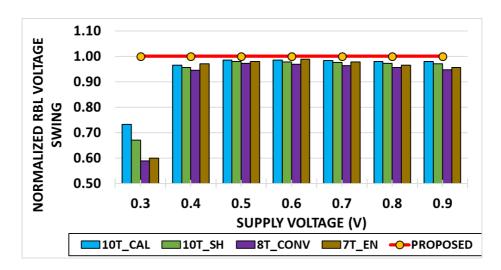

| Fig. 5.6  | <i>Normalized</i> $\Delta V_{RBL}$ <i>at</i> 27 ° <i>C</i>                                           | 156 |

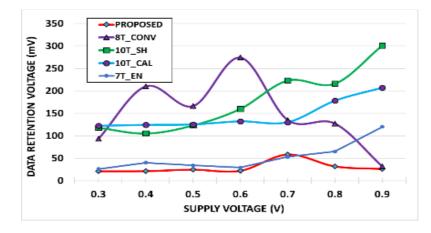

| Fig. 5.7  | HSNM at 0.3 V and 27 °C                                                                              | 157 |

| Fig. 5.8  | DRV at 27 °C                                                                                         | 157 |

| Fig. 5.9  | $P_{LEAK}$ at 27 °C                                                                                  | 158 |

|           |                                                                                                      |     |

# LIST OF TABLES

| Table 2.1 | Performance comparison of latch leakage reduction techniques                       | 40  |

|-----------|------------------------------------------------------------------------------------|-----|

| Table 2.2 | Comparison of latch leakage reduction techniques at different technology nodes     | 41  |

| Table 2.3 | Performance comparison of bitline leakage reduction techniques                     | 51  |

| Table 2.4 | Comparison of bitline leakage reduction techniques at different technology nodes   | 52  |

| Table 2.5 | Performance comparison of read port leakage reduction techniques                   | 66  |

| Table 2.6 | Comparison of read port leakage reduction techniques at different technology nodes | 67  |

| Table 2.7 | Aspect ratio of transistors                                                        | 70  |

| Table 2.8 | <i>Performance comparison at</i> $V_{DD} = 0.4 V$ <i>and</i> $T = 27 °C$           | 79  |

| Table 3.1 | Aspect ratio of transistors                                                        | 91  |

| Table 3.2 | Aspect ratio of transistors                                                        | 107 |

| Table 3.3 | Typical values of performance parameter at TT corner, 27 $^\circ C$                | 108 |

| Table 4.1 | Aspect ratio of transistors                                                        | 129 |

| Table 4.2 | <i>Performance comparison at</i> $V_{DD} = 0.3$ <i>V and</i> $T = 27$ ° <i>C</i>   | 144 |

| Table 5.1 | FinFET and CMOS parameters                                                         | 151 |

| Table 5.2 | Performance comparison at $V_{DD} = 0.3 V$ and $T = 27 $ °C                        | 159 |

## ABBREVIATIONS

| SRAM   | Static Random Access Memory                         |

|--------|-----------------------------------------------------|

| WL     | Word line                                           |

| WWL    | Write wordline                                      |

| RWL    | Read wordline                                       |

| BL     | Bitline                                             |

| BLB    | Bitline bar                                         |

| RBL    | Read bitline                                        |

| SNM    | Static noise margin                                 |

| HSNM   | Hold static noise margin                            |

| RSNM   | Read static noise margin                            |

| WSNM   | Write static noise margin                           |

| WM     | Write margin                                        |

| DRV    | Data retention voltage                              |

| MTCMOS | Multi-threshold CMOS                                |

| SB     | Substrate-bias                                      |

| DM     | Drowsy mode                                         |

| NWL    | Negative wordline                                   |

| LBB    | Leakage biased bitline                              |

| SE     | Stack-effect                                        |

| DCPR   | Dynamic control of power rails                      |

| VCG    | Virtual cell ground                                 |

| PVT    | Process-voltage-temperature                         |

| SCE    | Short channel effect                                |

| RDF    | Random dopant fluctuations                          |

| ITRS   | International Technology Roadmap for Semiconductors |

| HVT    | High threshold voltage                              |

| MVT    | Multiple threshold voltage                          |

| LVT    | Low threshold voltage                               |

|        |                                                     |

# CHAPTER 1

# INTRODUCTION

#### 1.1 Background

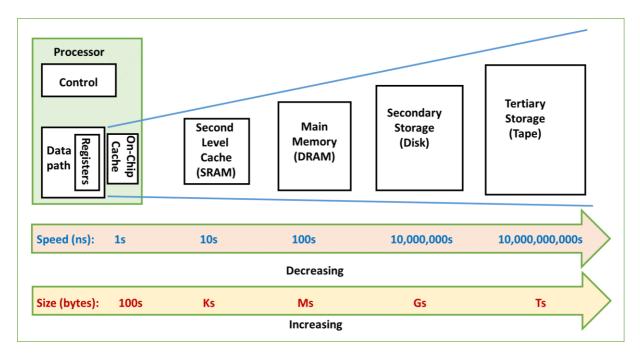

SRAM plays a key role in memory organization of a computer system as shown in Fig. 1.1. It occupies a significant chip area and thus is considered as a critical component on system-onchip such as in portable devices, microelectronic applications, sensor networks, biomedical implants etc. [1-11]. Thus, there is a need of fast, robust, high density SRAMs [12-13].

Fig. 1.1 Memory hierarchy of modern computer system [1]

## 1.1.1 SRAM architecture [1][10]

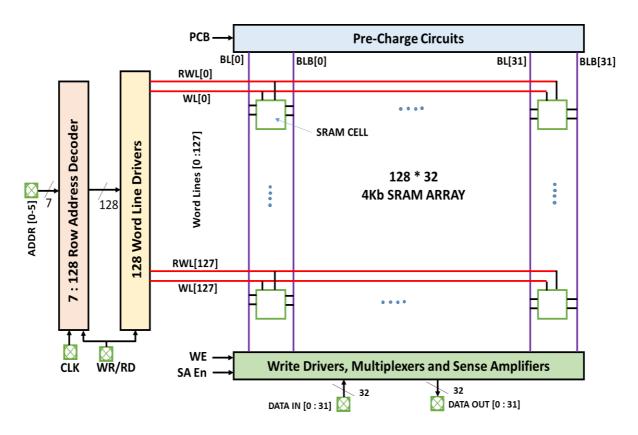

A typical SRAM architecture for 4 Kb SRAM (Fig. 1.2) consists of an SRAM array, in which the SRAM cells are arranged over multiple rows and columns, along with the decoders, readwrite column circuitry and control logic. A brief description on different blocks is as under:

**SRAM array**: It consists of a regular arrangement of SRAM cells organized in various rows and columns (N rows and M columns) where each cell can store one bit of data. For example, a 4 Kb SRAM consists of 4096 SRAM cells arranged over 128 rows and 32 columns. Now, to access these cells for read and write operations, different types of peripheral circuitry such as a row address decoder, pre-charge circuit, sense amplifier, write driver circuit and multiplexers are needed.

**Row address decoder:** The data in the SRAM array is usually stored in non-interleaved and interleaved ways [1]. In non-interleaved arrangement, one word is stored per row whereas in an interleaved arrangement one bit of multiple words are stored per row. So, to read/write data in a specific SRAM cell, initially a row is selected out of the given N rows using a row address decoder. The row address decoder pulls the corresponding wordline (WL) high using a word line driver circuitry. After this, the multiplexers select a specific column using a complementary pair of bitlines, BL and BLB. The bitlines are then driven by write driver circuit or sense amplifier through various control signals depending upon the type of memory operation to be performed.

Fig. 1.2 SRAM architecture [10]

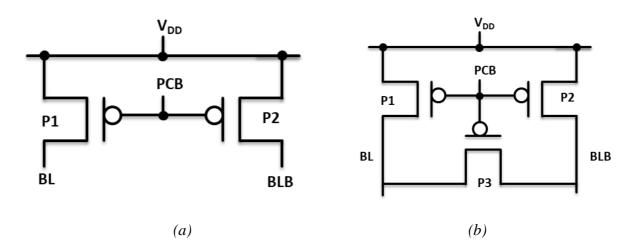

**Pre-charge circuit**: The pre-charge circuit is used to pull the bitline pair (BL and BLB) towards supply voltage ( $V_{DD}$ ) using an active low control signal PCB prior to read/write operation on the SRAM cell. Two such implementation are shown in Fig. 1.3. The circuit in Fig. 1.3(a) shows the basic implementation using two pMOS transistors P1 and P2. The circuit in Fig. 1.3(b) that helps in maintaining equalized voltages on the bitlines uses an extra pMOS transistor (P3) and improves voltage swing between the bitlines during read operation.

Fig. 1.3 Pre-charge circuit for SRAM [1]

**Sense amplifier**: A sense amplifier is considered as a key peripheral component while designing large memories as it has a strong impact on the read access time of the SRAM cell. The main function of the sense amplifier is to convert the small differential voltage developed on the bitlines during read operation to full swing output voltage. The sense amplifier enable signal, SA En (shown in Fig. 1.2) activates the sense amplifier for sensing the stored data in SRAM cell and completes the read operation. The large bitline capacitance, process variations, device mismatch, timing and layout constraints are some of the challenges that need to be dealt with while designing SRAM memories. Various types of sense amplifiers such as current-mirror based differential, latch-type, transmission-gate based sense amplifiers are available in the literature [1].

Write drivers: A write driver is used to pull down the voltage of internal storage node holding '1' below the WM of SRAM cell. This is done using write enable signal, WE (Fig. 1.2) which activates the driver circuit and provides the discharging path for the storage node of the accessed cell. Due to the large bitline capacitance, the write drivers are always designed with non-minimal width and length. Pass-gate and AND-gate based circuits are some of the most commonly used write drivers [1].

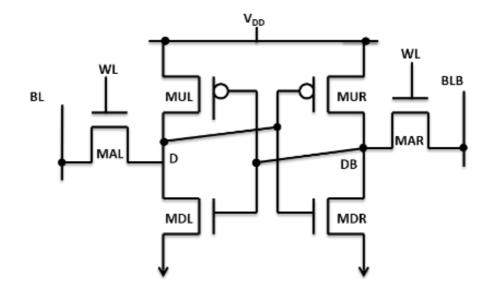

#### 1.1.2 Conventional 6T SRAM cell

There are numerous circuit realizations for the SRAM cell. The cells are classified according to the number of transistors used in their implementation. The structure of conventional 6T SRAM cell is shown in Fig. 1.4.

Fig. 1.4 Schematic of Conventional 6T SRAM cell

The conventional cell consists of six transistors and hence the name is given as 6T SRAM cell. The four transistors form the cross-coupled latch (MUL-MDL, MUR-MDR) to store the complementary data at internal storage nodes D and DB. The other two transistors (MAL, MAR) are used to access the internal storage nodes D and DB using wordline (WL) for performing read and write operation on the SRAM cell. The transistor pairs: MAL-MAR, MDL-MDR and MUL-MUR are respectively called access, pull-down and pull-up transistors. The cell can be operated in three different modes: hold, write and read.

#### Hold mode

In the hold mode, the SRAM cell maintains the voltage levels on internal storage nodes, D and DB. The wordline WL is pulled low using write driver while the bitlines are pre-charged to  $V_{DD}$  using pre-charge circuit. It is assumed that the cell is currently storing '1' at node D and '0' at node DB. This turns the transistors MDL and MUR OFF. The transistors MAR and MAL are already OFF as the wordline is low. This isolates the internal storage nodes from the external circuit. In this state, the noise immunity of the latch is maximum.

#### Write mode

In this mode, the new data values are written into the cell. To perform the write operation, initially the data to be written is applied on the bitlines through the write driver circuit and then the wordline WL is pulled high. This turns both the access transistors, MAL and MAR, ON. The write operation always starts at the node storing '1'. The voltage at this node is pulled-down below the WM of the cell. The feedback action of the cross-coupled inverter structure then helps in flipping the stored values quickly. However, this can happen only if the charging current flowing through the pull-up transistor towards the node storing '1' is smaller than the discharging current through the access transistor. Therefore, for write operation to be completed successfully, access transistors must be stronger than the pull-up transistors. This is estimated by means of the pull-up ratio which is usually set between 1 and 1.5.

- - - -

#### <u>Read Mode</u>

The read operation begins by pulling the wordline WL high. This connects the pre-charged bitlines to the internal storage nodes, D and DB. A read path is set up through the access transistor and pull-down transistor through the internal node storing value '0'. This read current (I<sub>ON</sub>) helps in discharging the pre-charged bitline towards low level. The sense amplifier then senses this fall in voltage at the corresponding bitline for reading the stored data. However, for this to happen the charging current through the access transistor towards the node storing '0' should be smaller than the discharging current flowing through the corresponding pull-down transistor. This requires that the strength of the pull-down transistor should be more than the strength of access transistor, which is defined by means of a cell ratio and it is usually set equal to 2.

#### 1.1.3 SRAM cell metrics [2-126]

The following standard cell metrics are used in the literature to compare the performance of various SRAM cells:

#### **1.1.3.1 Data stability**

Maintaining the stability of stored data at internal storage nodes in the presence of disturbance is a major concern in nanometer regime during hold and read modes. The static immunity to disturbances like process and mismatch variations, bulk static noise, supply ring offset, quasi static temperature changes are well characterized by means of the Static Noise Margin (SNM). The noise margin is calculated as the amount of noise voltage required at the input of a long chain of inverters such that it has the maximum tendency to upset the logic levels. Such a setup is equivalent to two cross-coupled inverters connected back-to-back as in a SRAM cell.

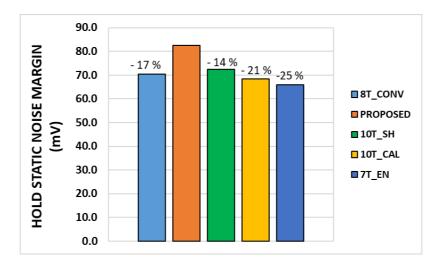

#### Hold static noise margin (HSNM)

It is calculated by superimposing the characteristics of one inverter on the characteristics of other inverter of the cross-coupled inverter structure of SRAM cell by sweeping either one of the internal nodes (D or DB) from GND to  $V_{DD}$  in the hold mode [18]. The side length of the largest square that can be embedded into the smaller lobe (in case of asymmetric cell structure) or any of the lobe (in case of symmetric cell structure) of the butterfly curve gives the estimate of HSNM.

#### Read static noise margin (RSNM)

The butterfly curve obtained by plotting the characteristics of one inverter superimposed on the mirror image of the characteristics of the other inverter in the read mode is used to calculate the RSNM. The butterfly curve in this case usually has smaller lobes compared to that in hold mode. The side length of biggest square in smallest lobe gives us the RSNM.

#### Data retention voltage (DRV)

The data stored in the cell becomes unstable as the cell supply reduces below particular value. The supply voltage at which the latch attains metastability and can maintain just sufficient voltages at its internal storage nodes is called DRV [27]. Usually, the cells are operated well above this value to compensate for the effect of Process-Supply voltage-temperature (PVT)-variations.

#### 1.1.3.2 Write ability

The write ability of the SRAM cell is determined by its ability to overwrite the stored value at the given supply voltage.

#### Write static noise margin (WSNM)

To calculate this parameter, the feedback loop is disconnected and the SRAM cell is put in write mode. The characteristics of one inverter is then superimposed on the other. It is to be noted that the butterfly curve in this case has only one lobe.

#### Write margin (WM)

It is used to get an idea about the ease with which the new data value can be written into the cell. The smaller is the value of this parameter, the harder it will be to write into the cell. The larger its value, more easy it would be to overwrite the value stored in the cell. Therefore, the moderate value of this parameter is desirable. The write margin is measured using combined wordline margin method as suggested by Makino et al. [8]. To estimate this parameter, the wordline WL is swept from GND to  $V_{DD}$ . The voltage difference between  $V_{DD}$  and the value of WL at which the stored values cross each other gives the estimate of this parameter.

#### **1.1.3.3 Minimum supply voltage (Vmin)**

It is defined as the minimum supply voltage level required for the cell to perform all the three basic operations - read, write and hold operations. The supply voltage at which the area under the butterfly curve becomes zero during read and hold modes is respectively referred to as read  $V_{min}$  and hold  $V_{min}$ . Similarly, the supply voltage at which the WM becomes negligible in write mode is known as write  $V_{min}$ . The maximum value out of these determines the  $V_{min}$  of the cell.

### 1.1.3.4 Delay performance

The delay is measured as the time required to complete the specified operation in SRAM cell.

#### Read access time (TREAD\_ACCESS)

The time required to perform read operation is evaluated in terms of  $T_{READ_ACCESS}$ . The  $T_{READ_ACCESS}$  for SRAM cells performing differential sensing, is defined as the time required for the bitlines to develop 50 mV or 100 mV of differential voltage after the wordline is activated along a row [59]. A current-mirror based differential sense amplifier is used for sensing the data [1]. For SRAM cells employing single ended sensing,  $T_{READ_ACCESS}$  is estimated as the time required for RBL to discharge from V<sub>DD</sub> to GND after the activation of wordline. For such SRAM cells, a hierarchical bitline-sensing design is used [126].

#### Write access time (Twrite\_Access)

The  $T_{WRITE\_ACCESS}$  is analyzed by considering both  $T_{WRITE\_ACCESS}$  ('1') and  $T_{WRITE\_ACCESS}$  ('0'). The  $T_{WRITE\_ACCESS}$  ('1') is estimated as the time required by internal storage node to charge to 90 % of supply voltage value when wordline is pulled high during write operation. Similarly,  $T_{WRITE\_ACCESS}$  ('0') is defined as the time required by the internal node to discharge to 10 % of the supply voltage value after the activation of wordline [59].

#### 1.1.3.5 Power consumption

The total power consumption comprises of dynamic power consumption and leakage power consumption of the cell.

#### Dynamic power consumption (P<sub>DYN</sub>)

Dynamic power consumption includes read power and write power consumptions.

#### **Read power consumption** (PREAD)

It is defined as the power consumption of the switching nodes/ transistors when the cell performs the read operation.

#### Write power consumption (P<sub>WRITE</sub>)

It is defined as the power consumption of the switching nodes/ transistors when the cell is performing the write operation.

#### Leakage power consumption (PLEAK)

It is the power consumption of the cell in hold mode. It consists of the sub-threshold leakage current ( $I_{SUB}$ ), gate direct tunnelling current ( $I_{GATE}$ ) and junction tunnelling current ( $I_{JUNC}$ ) of all the MOS transistors. Out of all leakage components,  $I_{SUB}$  is the largest contributor of the total leakage current in the sub-threshold region.

#### 1.1.3.6 Miscellaneous

Besides the metrics described above, the following metrics are equally important:

#### **ION/OFF** ratio

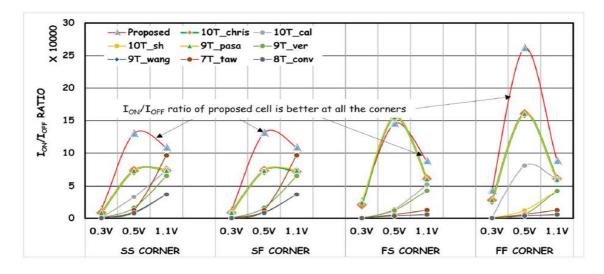

This parameter determines the number of SRAM cells that can share the peripheral circuitry along the column and thus, plays a major role in determining the peripheral requirements for implementing a larger array. The read bitline (RBL) leakages pull down the bitline and cause a false read resulting in read failures. Therefore, it is necessary to maintain a reasonable value of this parameter under all operating conditions.

#### **RBL** voltage swing ( $\Delta V_{RBL}$ )

The  $\Delta V_{RBL}$  is defined as the worst-case difference in RBL voltage for read '1' and read '0' operation [57]. For successful read operation, RBL voltage for read '1' should be greater than RBL voltage for read '0'; otherwise, a read failure occurs due to negative  $\Delta V_{RBL}$  [50].

#### Area

The smaller area is desirable to reduce the cost. However, there exists a trade-off between the area and cell performance particularly at lower technology nodes and sub-threshold region.

#### 1.1.4 Issues with conventional 6T SRAM cell [1-120]:

The conventional 6T SRAM cell is an industry standard since long time due to faster differential read and write operations and compact area [14]. For successful operation of the cell in read and write modes it needs stronger nMOS pull-down (MDL, MDR), medium strength nMOS access (MAL, MAR) and weaker pMOS pull-up (MUL, MUR) transistors (Fig. 1.4). However, at lower supply voltages the cell sizing becomes less effective resulting in deteriorated read and write performance. The increased PVT-variations exaggerate the situation and may lead to increased memory failures.

**Destructive read operation:** During read operation, the read current flows through the access and pull-down transistors connected to internal node storing '0'. Due to the voltage divider action between the access and pull-down transistors, the voltage at this node increases slightly. If the increased voltage is greater than the switching threshold voltage of the other inverter then the regenerative action of the cross-coupled inverter structure is triggered resulting in flipping of stored values. This is known as **destructive read operation**.

**Read-write conflict issue:** In the conventional 6T SRAM cell, the write performance can be improved by increasing the strength of access transistors. However, this deteriorates the read performance of the cell. Similarly, when an attempt is made to improve the read performance of the cell, write performance degrades. This is known as **read-write conflict issue**.

To overcome these issues, the alternate approaches are used that include use of different assist techniques or assist circuits for performance improvemen [62-120]. Alternatively, the new SRAM cell topologies [2-6][10-15][32-61] are introduced by adding one or more transistors to the existing SRAM cell designs.

#### **1.2 Literature Review and Scope of Work**

The growing need for high density SRAMs has motivated the designers to reduce the MOS channel length from submicron to nanometer scale to increase the number of SRAM cells per unit chip area. The presence of huge number of SRAM cells on a limited chip area in turn causes problem of high power consumption and excessive leakages in small geometry devices. To curb these problems, voltage scaling on smaller devices is applied. However, it leads to degraded read and write performance in SRAM cell that further exaggerates under PVT-variations.

#### 1.2.1 Challenges in SRAM cell design with scaling [2][52][68-74]

The device scaling on SRAMs reduces the parasitic capacitances and provides faster operation. As per Moore's law, scaling of the minimum MOS length by about 30 %, doubles the number of transistors on a given chip area and decreases the parasitics by 30 %. Further, the scaling of supply voltage results in significant reduction of dynamic power consumption due to its quadratic relationship with supply voltage. In addition, it reduces the tendency of ultra-thin

oxides to breakdown in small geometry devices. However, this imposes some serious design challenges for SRAM designers as described below:

#### **Data stability**

In the SRAM cell, direct access of internal nodes during read operation makes it vulnerable to external noise, causing degraded RSNM and may even result in destructive read operation. The conventional 6T SRAM cell fails due to read margin deterioration below 800 mV at 65 nm [52].

#### Write ability

Similarly, to perform a successful write operation, the access transistors must be made wider than the pull-up transistors to enhance their current conducting capability. This was not a concern for cell operating in strong inversion but in sub-threshold region the impact of process variations becomes much more prominent specifically at slow-nMOS and fast-pMOS (SF) corner. At SF corner, the pMOS transistor becomes stronger than nMOS transistor resulting in increased write failures. This problem is further exaggerated at lower temperature due to increased subthreshold-slope of pMOS transistor than nMOS transistor resulting in increased driving strength of pMOS transistor. Due to this, the 6T SRAM cell loses write ability below 700 mV at 65 nm and 600 mV at 32 nm [2][52].

#### Leakage power consumption

Dynamic power consumption dominates at high supply voltages whereas leakage power shows dominance in sub-threshold region and causes increased total power consumption. If the leakages of the entire column pulls down the bitline below the offset voltage of sense amplifier during read operation then there may be false read operation.

#### **PVT-variations**

Due to the exponential dependence of the sub-threshold leakage current on the threshold voltage of the transistors, even a small variation in threshold voltage causes large changes in the sub-threshold leakage current. This leads to increased read and write failure probabilities in SRAM cell.

#### **1.2.2 State-of-the-art SRAM cell designs** [2-6][10-15][32-61][116-120]

The various SRAM cell topologies are introduced in the literature to address the performance issues of conventional 6T SRAM cell [2-6][10-15][32-61][116-120]. These topologies use extra transistors to provide improved performance at lower supply voltages in nanometer regime. Some of the most popular SRAM cell designs are discussed next.

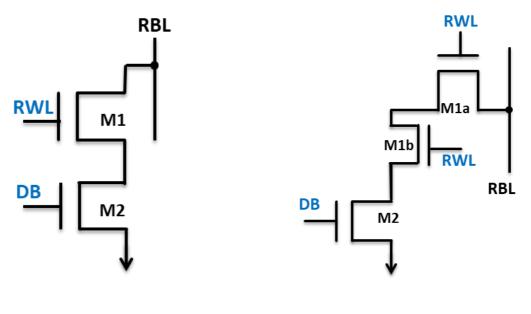

The 7T SRAM cells [33][116] and 9T SRAM cell [117] provide faster write by cutting the feedback loop using extra nMOS transistors during write operation. In addition, in [33] use of low-threshold voltage pull-down transistor is suggested to further ease the writing process. The strong feedback mechanism of the cross-coupled latch is retained during read and hold modes to maintain the stability of stored data. The conventional 8T SRAM cell [4] performs differential write in the same manner as is done in 6T SRAM cell. However, it isolates the internal nodes from external bitlines using a decoupled read port, thus, providing improved read stability. The 9T SRAM cell [38] provides an alternate way to isolate the internal nodes from the external bitlines. The disadvantage is the doubling of the number of transistors connected per bitline resulting in increased bitline load capacitance and longer discharge times. The 10T SRAM cell [51] uses a novel isolated read port design to improve the read stability and reduce the RBL leakages. However, the read current is reduced due to the increased stacking effect of the transistors. The 11T SRAM cell [59] and 10T SRAM cells [118][119][120] use an isolated read port and a Schmitt-trigger action to provide improved

read stability and inverter characteristics. The Schmitt-trigger action helps in modifying the switching voltage of the latch inverters depending upon the direction in which the node voltages change due to PVT-variations. The result is improved noise immunity of the cell under PVT-variations. In addition, the Schmitt-trigger action is disabled [59] or feedback loop is weakened [118] or disabled [119][120] during write operation for easing the writing process. The 12T SRAM cell [60] uses an innovative write-assist technique to improve the write performance in sub-threshold region. It uses data-dependent feedback-path cutting technique by disabling one of the pull-down paths to GND during write operation. The fully-gated ground scheme is used to reduce the RBL leakages. However, the increased bitline load capacitance due to connection of more transistors per SRAM cell to bitlines deteriorates the time required to complete the write operation. The presence of multiple leakage paths also has a degrading effect on the cell performance.

#### 1.2.3 Performance improvement [2-115]

In the literature, the research on SRAM is mainly focused towards improving read and write performance, leakage reduction and PVT-variation tolerance. The chances of achieving lower failure probability and higher yield are becoming thin with increasing process variation. Thus, novel designs and techniques are developed and adopted at the cost of area, power dissipation, or speed to improve SRAM cell performance.

#### **1.2.3.1** Approaches to improve read performance

The read performance of the SRAM cell can be improved by using either read assist techniques or read assist circuits.

#### **Read assist techniques**

This includes techniques like World line underdrive (WLUD) [6][37], Suppressed bitline (SBL) [37][43][84], Negative  $V_{SS}$  (NV<sub>SS</sub>) [37][43] and Asymmetrical cell sizing [2][14]. These

techniques are aimed towards enhancing the cell ratio by strengthening the pull-down transistor compared to access transistors. The WLUD technique improves the RSNM but decreases the read current and degrades the WM. In the SBL technique, the bitlines are pre-charged to voltages lower than the full  $V_{DD}$ . It incurs overhead of voltage generator circuit and hence increased power consumption and area. The NVss approach reduces the read disturbance but decreases the stability of stored data in other cells sharing the same row. An asymmetrical cell sizing increases the area drastically with subsequent increase in leakages.

#### **Read assist circuits**

When the improvement through assist techniques is less than the target value it is clear that SRAM topologies with read assist circuits are required [4][12][47-49][51][57][86]. The read operation in conventional 6T SRAM cell shows degraded RSNM values as the internal node lies directly in the read current path that affects the voltage level at storage node resulting in reduced data stability. The read assist circuits provide separate discharge path for the read current as is done in conventional 8T SRAM cell [4]. However, the read port transistors need to be up-sized to maintain low  $T_{READ\_ACCESS}$  resulting in increased RBL leakage current. The circuit in [47] uses a stacking effect of three transistors to reduce the RBL leakages but suffers from degraded read current values and high access time. The next circuit [48], provides a low resistance read current path in the accessed cell and alternatively keeps the RBL voltage at  $V_{DD}$  by providing the leakage current path to RBL through un-accessed cells in the same column. However, the drawback is the significant increase in static power consumption.

It can be deduced that SRAM cell designed with available read assist techniques/circuits in nanometer regime maintains lower values of read current, with higher read access times. So, the design of read port with enhanced read current values to improve the read performance of the cell is explored in this work.

#### 1.2.3.2 Approaches to improve write performance

The write performance of the SRAM cell can be improved by using either write assist techniques or write assist circuits.

#### Write assist techniques

It includes the techniques such as Negative bitline (NBL) [6], Boosted bitline (BBL) [77], Boosted negative bitline (BNBL) [77], Transient voltage collapse (TVC) [36], Wordline over drive (WLOD) [9], Raising global  $V_{DD}$  (RGV) [43] and Cell ground boosting (CGB) [77]. These approaches are aimed towards enhancing the pull-up ratio of the cell thereby making the access transistors stronger than pull-up transistors. The techniques like WLOD, NBL, RBV, BBL, BNBL make the access transistor stronger compared to the pull-up transistor. The remaining techniques such as TVC and CGB weaken the latch compared to the access transistor. Most of these techniques either degrades the HSNM of other cells on same row or require elaborate control of global or local  $V_{DD}$  except those that work on bitlines such as NBL, BBL and BNBL techniques. The techniques that work on bitlines either incorporate negative charge pumps or apply optimum value of charge to boost capacitor for implementation.

#### Write assist circuits

When the improvement through assist techniques is less than the target value, the new SRAM topologies are introduced to improve the write performance [2][12-13][35][52]. The circuit in [2] removes the pull down transistor from one of the latch inverter to provide faster write '0' operation whereas an extra transistor is used in [13] to weaken the feedback loop of cross coupled latch structure during write operation to ease out the writing process. The circuit in [35] interrupts the supply to one of the inverters thereby decreasing the resistance of the positive feedback loop and hence easing the writing process. The other circuit in [52] interrupts the cell supply during write operation and connects it to weak source through pMOS transistor

instead of floating the supply voltage completely through a power switch. The advantage is that the other cells in the same row are saved from the retention problem of stored data.

It is observed that the existing designs for SRAM cell improve the write performance with either no change or degradation of read performance. Therefore, a design that can provide improvement in both read as well as write performance needs to be explored.

#### 1.2.3.3 Approaches to reduce leakages

As per ITRS roadmap, power consumption is a major concern in portable devices [72]. It is addressed by reducing either dynamic or leakage power consumption. It is worth mentioning that at high supply voltages, dynamic power consumption is dominant, however, as the technology scales the leakage power consumption becomes critical specifically in subthreshold region. To address this issue, the leakage current in SRAM cell can be classified as latch, bitline and RBL (in cell with isolated read port) leakage currents and correspondingly, the leakage reduction techniques can be classified as latch, bitline and read port leakage reduction techniques. The techniques in each category can be used to target a particular leakage component within the cell.

#### Latch leakage reduction techniques

As latch is the integral part of a cell, therefore these techniques can be applied to different SRAM cells to achieve the purpose. This category includes techniques such as Multi-threshold CMOS (MTCMOS) [12][32][92-93], Substrate-bias (SB) [9][94-96] and Drowsy mode (DM) [27][49][73][78][88][97-98] techniques. The MTCMOS technique suggests the use of high-threshold voltage MOS transistors in latch to lower the latch leakages of the cell. The SB technique provides the alternate way to accomplish the same objective. The DM technique lowers the cell supply in order to reduce the drain to source voltage across the transistors resulting in reduction of leakages.

#### **Bitline leakage reduction techniques**

The negative wordline (NWL) [38][74][81][99][102] and leakage biased bitline (LBB) [103-105] techniques fall under this category. In the NWL technique, the access transistors are biased in super cut-off region by applying a negative gate voltage instead of GND during hold mode whereas in LBB technique, the bitlines of inactivated sub-banks in hierarchical bitline architecture are left in floating state. This biases the bitlines at random voltage levels depending on the leakage from the un-accessed cells connected to the same column and helps in reducing the overall leakage in the column.

#### Read port leakage reduction techniques

This category includes the stack-effect (SE) [4][20][47][59][107-108], dynamic control of power rails (DCPR) [50] and virtual cell ground (VCG) [4][34][56] techniques to reduce the RBL leakages of an isolated read port. The SE technique uses reverse-biasing effect whereas DCPR and VCG techniques adjust the voltage supply ( $V_{DD}$ ) and ground level (GND) respectively to reduce the drain to source voltage across the read port resulting in reduced leakages [114].

Further, in nanometer regime there exist a substantial increase in the power consumption due to leakages which is of small magnitude otherwise [71][89]. It is pertinent to mention here that the above techniques are applied at higher technology nodes therefore their suitability at lower node in the presence of PVT-variations is explored in this work. Further, a novel SRAM cell with reduced leakage current values is designed in the thesis.

#### 1.2.3.4 Approaches to improve PVT-variation tolerance

Process variation is the naturally occurring variation in the attributes of transistors when it is fabricated [28]. The sources of variations are gate oxide thickness, device geometry and random dopant fluctuations. The Process-Voltage-Temperature (PVT) induced variations in the MOS behavior are addressed through changes in threshold voltage of the MOS transistors. Pelgrom's law states that the threshold (or other process related) mismatch between two adjacent identically drawn transistors increases inversely with the gate area [28]. The effect of process variation becomes more prominent at smaller technology nodes (< 65 nm). This causes the performance of a particular metric of SRAM cell to degrade and hence reduces the overall yield. To address this issue, various PVT-variation tolerant SRAM topologies are available in literature [10][53][59][61].

It is observed that the existing Schmitt-trigger based SRAM cells have degraded write ability, low read stability and poor  $I_{ON}/I_{OFF}$  ratio and reflect data-dependent tolerance against PVT-variations. Thus, the design of Schmitt-trigger based SRAM cell with enhanced performance is addressed in this thesis.

# 1.2.4 What is next at 28 nm and beyond? [121-134]

With on-going device and supply voltage scaling, conventional planar CMOS technology suffers from increased susceptibility to process variation, random dopant fluctuation (RDF), short channel effects, leakages, inability to write at ultra-low voltages etc. In a bulk CMOS transistor, current flows from the source to the drain through a channel. As chip designers scale transistors at each node, the channel length becomes shorter. As a result, the transistor may suffer from **short-channel effects** (SCE) which degrades the sub-threshold slope or turn-off characteristics in a device. Another issue is **transistor variability** due to which a given bulk CMOS transistor may perform differently from its nominal behavior. It may produce random differences in threshold voltage of devices, a phenomenon popularly known as **random dopant fluctuation** (RDF). To overcome the issues associated with bulk CMOS technology, several alternatives like the use of modified topologies and high permittivity gate dielectric are

being explored [10][53][59][61][125-127]. The other option is to use improved transistor technology for designing SRAM cell at lower technology nodes such as SOI FET [121-122] and FinFET [123-134]. The novel transistor structure such as FinFET, which promise better transistor aspect ratio, better scalability, low power consumption, better control on channel and higher channel mobility, has emerged as the leading candidate for next generation electronic devices.

The FinFET based SRAM designs in [133][134] use common port for performing read and write operations. Due to this, the designs suffer from read-write conflict issue resulting in degradation of performance of the cell in read and write modes. Thus, a novel FinFET based SRAM design with improved read as well as write performance is explored in this thesis.

# **1.3 Objectives**

Based on the literature review and the research gaps identified thereafter, the following objectives are set for the research work:

- Design of SRAM with improved read and write performance for nanometer regime.

- Design of low leakage SRAM in sub-threshold region.

- A process variation tolerant SRAM design for nanometer regime.

- Use of improved transistor technology for performance improvement in SRAM.

# 1.4 Organization of the Thesis

The research work is structured in six chapters including this introductory chapter. Following is the brief description of chapters:

## Chapter 1:

This chapter gives a background, literature review of existing SRAM cell designs, and objectives set for exploring new SRAM cell designs for nanometer technologies.

# Chapter 2:

This chapter presents a comprehensive review of leakage reduction techniques prevailing in SRAM by classifying them in three categories namely latch, bitline and read port. The performance of the techniques are evaluated in terms of leakage reduction capability along with the impact on major performance parameters in three operating modes through extensive simulative investigations. The performance at different PVT corners and technology nodes is captured to demonstrate the efficacy of each technique with PVT-variations and technology scaling. A low-leakage SRAM cell that implements leakage reduction techniques for leakage reduction at different levels in SRAM cell is presented. In addition, it aims for improved read and write performance.

# Chapter 3:

This chapter is devoted to the design of two SRAM cells, which successfully overcomes the read-write conflict issue, and provide improved read and write performance. The first design, achieves high read current values, improved RSNM and WSNM. The second design aims for low and data-independent RBL leakages, high I<sub>ON</sub>/I<sub>OFF</sub> ratio, low read access time, large RBL voltage swing and faster write in near threshold and sub-threshold regions.

# Chapter 4:

This chapter extends into the designing of a PVT-variation tolerant Schmitt-trigger based SRAM cell. The idea is to enhance the performance of SRAM cell in all the operating modes. The cell uses techniques for improving the write ability and read performance in the sub-threshold region of operation. The reduced write, read and hold failure probabilities translates into reduction in minimum supply voltage required for accomplishing the memory operations.

# Chapter 5:

This chapter exploits the possibility of designing SRAM under 28 nm technology node. In the nanometer regime, maintaining the performance under 28 nm is becoming difficult with bulk CMOS technology. FinFET is emerging as the most promising substitute for planar CMOS technology due to good scaling ability, high ON current, reduced  $V_{th}$  variations, better subthreshold-slope and SCE. A SRAM cell design below 28 nm node is worked upon in this chapter.

# Chapter 6:

This chapter summarizes the work presented in the thesis and the future scope of the work.

# **CHAPTER 2**

# SRAM CELL DESIGN WITH LOW LEAKAGE IN SUB-THRESHOLD REGION

The content and results of the following papers have been reported in this chapter:

Gupta M, Gupta K, Pandey N, "Comparative Analysis of the Design Techniques for Low Leakage SRAMs at 32nm", Journal of Microprocessors and Microsystems, Elsevier, 85, 1-19, 2021. (SCI Journal with Impact Factor: 1.526)

2. Gupta M, Gupta K, Pandey N, "A Design of Low Leakage Cache Memory Cell for High Performance Processors", *Journal of Information and Optimization Sciences*, 40(2), Taylor and Francis, 279-290, 2019.

## 2.1 Introduction

In nanometer regime, when many SRAM cells are integrated over a smaller chip area, there is substantial increase in power consumption due to leakages which is of small magnitude otherwise [71][89]. It is pertinent to mention here that sub-threshold leakage current is one of the major contributors in leakage power and needs consideration [50][90].

The sub-threshold leakages present in conventional SRAM cells are classified in section 2.2 of this chapter based on their origin within the cell. Further, a comprehensive review of the existing techniques that address sub-threshold leakage current at different levels in the conventional design of SRAM cell is done in section 2.3 [9][12][24][27][32][34][38][47-49][53][56][59][73-74][76][78][81][84][88][92-108]. The objective of this review is to quantify the impact of available leakage reduction techniques on SRAM cell performance under PVT-variations so that a suitable technique may be used in nanometer regime. This is done by classifying the existing techniques as latch, bitline and read port leakage reduction techniques, based on the leakage current component addressed through them within the cell. The impact of techniques in each category is then evaluated on major performance parameters. Since the performance of a technique is also susceptible to PVTvariations and technology scaling at lower technology nodes [91], therefore, this aspect is also considered for determining the best suitable operating conditions for their usage. In addition, a Proposed cell I with low leakage is presented in section 2.4. It is based on the use of NWL and MTCMOS techniques for reducing bitline and latch leakages respectively. The structure, functional verification and the performance comparison of the proposed cell with existing cells are also discussed in the same section. The conclusions are drawn in section 2.5.

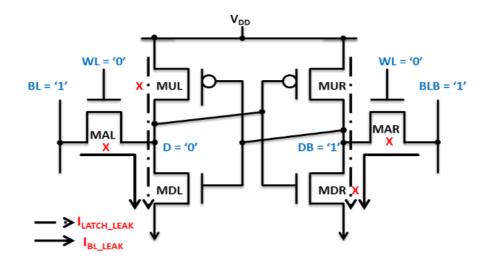

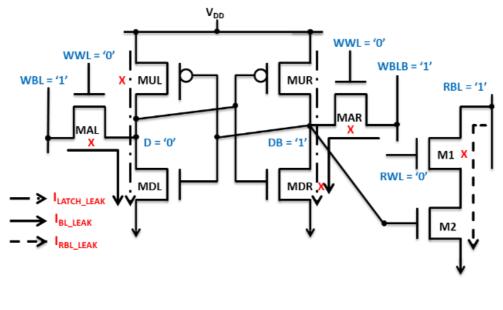

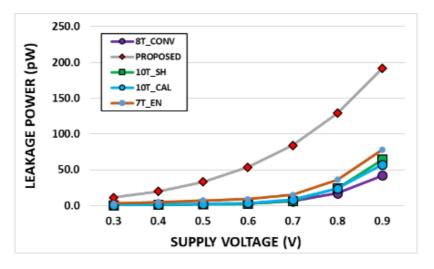

# 2.2 Leakage current components in conventional SRAM cells

In this section, a brief review of various leakage current components existing in conventional SRAM cells is presented. In the 6T SRAM cell, two components of leakage current are identified based on their origin within the cell. The first component is the latch leakage current (ILATCH\_LEAK) that flows from cell supply to GND through non-conducting latch transistors. The bitline leakage current  $(I_{BL\_LEAK})$  is the second component that flows from BL/BLB to GND through non-conducting access transistors. One more leakage current component is defined for cells with decoupled read port, such as conventional 8T SRAM cell, and is named as read port leakage current (I<sub>RBL LEAK</sub>). A pictorial representation for leakage currents in conventional 6T and 8T SRAM cells storing logic '0' at D during hold mode is shown in Fig. 2.1(a) and Fig. 2.1(b) respectively. In nanometer regime, the leakage current becomes a critical performance parameter as the diffusion of the charge carriers in the source and drain regions is increased which results in a current flow in non-conducting transistors [93]. This leakage current affects the overall performance of the memory (such as number of SRAM cells connected to sense amplifiers, speed of operation etc.) and makes the cell more sensitive to variations [91]. Therefore, various techniques are used to suppress the leakage current.

Fig. 2.1 Leakage currents in conventional SRAM cells (a) 6T (b) 8T SRAM cells [4]

# 2.3 Classification of leakage reduction techniques

The existing techniques are classified in three categories namely latch leakage reduction techniques, bitline leakage reduction techniques and read port leakage reduction techniques based on leakage current origin. The techniques suggest either a circuit level modification in cell topology/multiple supply rails or at device level by using improved MOS transistors.

# 2.3.1 Latch leakage reduction techniques [9][12][24][27][32][34][38][47-

# 49][53][56][59][73-74][76][78][81][84][88][92-108]

The techniques in this category aim at reducing the leakage current generated within the latch in a SRAM cell. As latch is the integral part of a cell, therefore these techniques can be applied to different SRAM cells to achieve the purpose. A detailed description on the techniques is presented below.

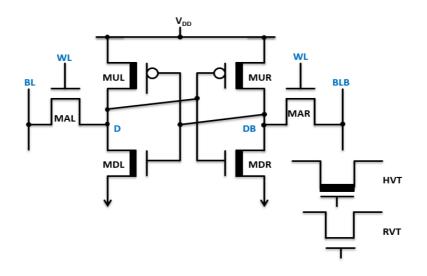

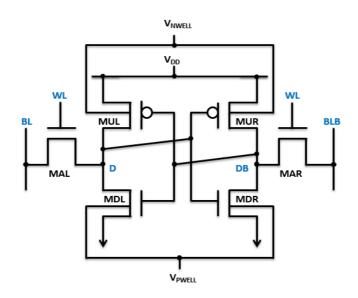

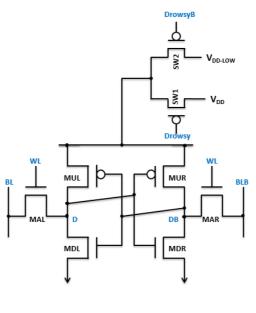

# 2.3.1.1 Multi-threshold CMOS technique (MTCMOS) [12][32][92-93]

This technique suggests the use of high-threshold voltage (HVT) MOS transistors in latch while typical-threshold voltage transistors to be used in the remaining cell. The presence of HVT MOS transistors lowers the  $I_{LATCH\_LEAK}$  of the cell. A schematic of 6T SRAM cell using MTCMOS technique is depicted in Fig. 2.2(a) where the transistors with bold lines denote HVT MOS transistors. The modification of the threshold voltages is done at fabrication level by changing the doping profiles of the selected transistors yielding a lowleakage SRAM cell.

*(a)*

*(b)*

*(c)*

Fig. 2.2 Schematic of 6T SRAM cell with (a) MTCMOS (b) SB (c) DM techniques

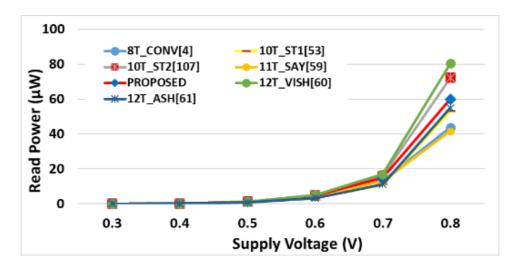

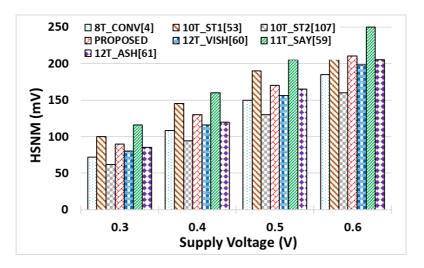

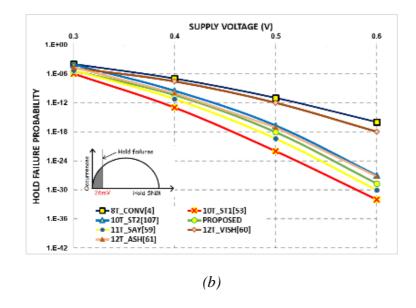

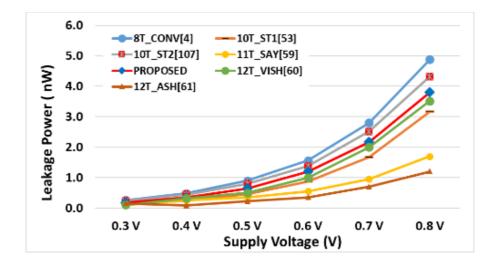

# 2.3.1.2 Substrate-bias technique (SB) [9][94-96]