## SIMULATION AND ANALYSIS OF OPTICAL LOGIC GATES

#### A DISSERTATION

## SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE

OF

# MASTER OF TECHNOLOGY IN MICROWAVE AND OPTICAL COMMUNICATION

Submitted by:

## BHAVNA PRASAD 2K20/MOC/02

Under the supervision of

Dr. YASHNA SHARMA

#### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

MAY, 2022

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CANDIDATE'S DECLARATION**

I, Bhavna Prasad (2K20/MOC/02) student of M. Tech (Microwave and Optical

Communication Engineering), hereby declare that the Major Project-II dissertation titled

"SIMULATION AND ANALYSIS OF OPTICAL LOGIC GATES" which is submitted by me to the

Department of Electronics and Communication Engineering, Delhi Technological University,

Delhi in partial fulfillment of the requirement for the award of the degree of Master of

Technology is original and not copied from any source without proper citation. This work

has not previously formed the basis for the award of any Degree, Diploma Associateship,

Fellowship, or other similar title or recognition.

Place: Delhi

Date: 30/05/2022

**Bhavna Prasad**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**CERTIFICATE**

I hereby certify that the Major Project-II dissertation titled "SIMULATION AND ANALYSIS

OF OPTICAL LOGIC GATES" which is submitted by Bhavna Prasad (2K20/MOC/02) in the

Department of Electronics and Communication Engineering, Delhi Technological University,

Delhi in partial fulfilment of the requirement for the award of the degree of Master of

Technology is a record of project work carried out by the student under my supervision. To

the best of my knowledge this work has not been submitted in part or full for any Degree or

Diploma to this University or elsewhere.

Place: Delhi

Date: 30/05/2022

Dr. YASHNA SHARMA

**SUPERVISOR**

#### <u>ACKNOWLEDGEMENT</u>

The success and outcome of this project required a lot of guidance and assistance from many people, and I am extremely fortunate to get this all along with the completion of my project work. Whatever I have done is only due to such guidance and assistance and I would not forget to thank them.

I owe my profound gratitude to my project guide Dr. Yashna Sharma for giving me the opportunity to do this work. Dr. Yashna Sharma to ok keen interest in my project work and guided me throughout, till the completion of the project work by providing all the necessary information, constant encouragement, sincere criticism, and a sympathetic attitude.

**BHAVNA PRASAD**

#### **ABSTRACT**

Optical logic gates are designed to perform same functions in optical domain as Boolean logic gates performs in digital domain. The basic gates are OR, NOT and AND. NAND and NOR are universal gates and XOR and XNOR are derived Gates. Here, these gates are implemented in LUMERICAL by using finite difference time domain. The structure consist of a Y shaped cavity in silver film layer which is on the top of silicon dioxide substrate. There are two input ports to provide different input according to amplitude requirement and a single output to obtain the output according to logic function. Here the substrate is made up of SiO2 layer and the signal path has no element the signal is transmitting in Air. The air gap is created in the Ag metal. The range of the simulation is 400 to 700 nm.

## **CONTENTS**

| Can         | didate's Dec | claration                               | ii   |

|-------------|--------------|-----------------------------------------|------|

| Cert        | tificate     |                                         | iii  |

| Ack         | nowledgeme   | ent                                     | iv   |

| Abs         | tract        |                                         | V    |

| Con         | tents        |                                         | vii  |

| List        | of Figures   |                                         | viii |

| List        | of Tables    |                                         | X    |

| CHA         | APTER 1      | INTRODUCTION                            | 1    |

| 1.1         | Overview     |                                         | 1    |

| 1.2         | Designing    | and methodology of Gates                | 3    |

| CHA         | APTER 2      | LITERATURE OVERVIEW                     | 5    |

| 2.1         | Optical log  | gic gates                               | 5    |

| 2.2         | Derivation   | of all gates from Universal logic gates | 14   |

| СНА         | APTER 3      | SIMULATION                              | 19   |

| 3.1         | Inputs       |                                         | 19   |

| 3.2         | Simulation   |                                         | 20   |

| <b>CH</b> A | APTER 4      | RESULT AND OBSERVATION                  | 22   |

| 4.1         | Result       |                                         |      |

| CHAPTER 5  | CONCLUSION AND FUTURE SCOPE | 28 |

|------------|-----------------------------|----|

| REFERENCES |                             | 29 |

## LIST OF FIGURES

| Figure No. | Name                                            | Page No. |

|------------|-------------------------------------------------|----------|

| 1          | Description of all logic gates                  | 2        |

| 2          | Front view structure of gate based on slot film | 3        |

| 3          | Side view structure of gate based on slot film  | 4        |

| 4          | Designing using different amplifiers            | 6        |

| 5          | Symbol of AND Gate                              | 6        |

| 6          | Symbol of OR Gate                               | 7        |

| 7          | Symbol of NOT Gate                              | 8        |

| 8          | Symbol of NAND Gate                             | 9        |

| 9          | Symbol of NOR Gate                              | 10       |

| 10         | Symbol of XOR Gate                              | 12       |

| 11         | Symbol of XNOR Gate                             | 13       |

| 12         | NOT Gate using NAND Gate                        | 14       |

| 13         | AND Gate using NAND Gate                        | 14       |

| 14         | NAND Gate using NAND Gate                       | 14       |

| 15         | OR Gate using NAND Gate                         | 15       |

| 16         | NOR Gate using NAND Gate                        | 15       |

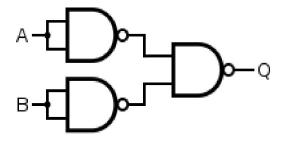

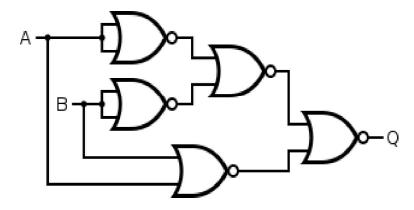

| 17         | XOR Gate using NAND Gate                        | 15       |

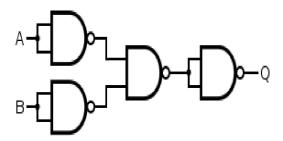

| 18         | XNOR Gate using NAND Gate                       | 16       |

| 19         | NOT Gate using NOR Gate                         | 16       |

| 20 | AND Gate using NOR Gate         | 16 |

|----|---------------------------------|----|

| 21 | NAND Gate using NOR Gate        | 17 |

| 22 | OR Gate using NOR Gate          | 17 |

| 23 | NOR Gate using NOR Gate         | 17 |

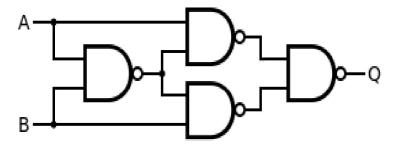

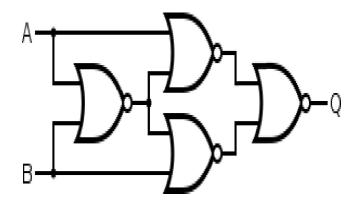

| 24 | XOR Gate using NOR Gate         | 18 |

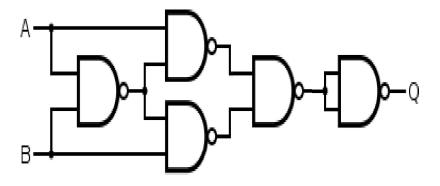

| 25 | XNOR Gate using NOR Gate        | 18 |

| 26 | Time domain monitor for input 1 | 19 |

| 27 | XY VIEW                         | 20 |

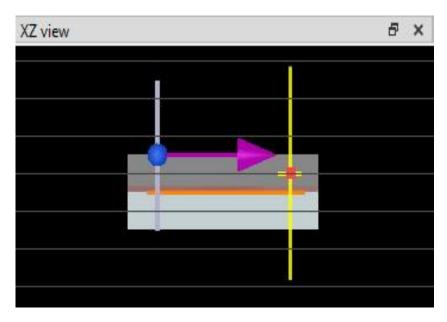

| 28 | XZ VIEW                         | 20 |

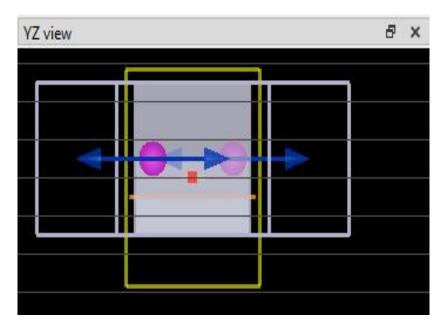

| 29 | YZ VIEW                         | 21 |

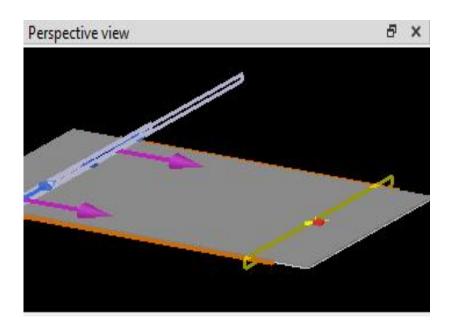

| 30 | Perspective VIEW                | 21 |

| 31 | OR Gate output                  | 22 |

| 32 | OR Gate output                  | 23 |

| 33 | OR Gate output                  | 23 |

| 34 | OR Gate output                  | 24 |

| 35 | AND Gate output                 | 24 |

| 36 | AND Gate output                 | 25 |

| 37 | AND Gate output                 | 25 |

| 38 | AND Gate output                 | 26 |

| 39 | NOT Gate output                 | 26 |

| 40 | NOT Gate output                 |    |

## LIST OF TABLES

| Table No. | Name                      | Page No. |

|-----------|---------------------------|----------|

| 1         | Truth table for AND Gate  | 7        |

| 2         | Truth table for OR Gate   | 8        |

| 3         | Truth table for NOT Gate  | 9        |

| 4         | Truth table for NAND Gate | 10       |

| 5         | Truth table for NOR Gate  | 11       |

| 6         | Truth table for XOR Gate  | 12       |

| 7         | Truth table for XNOR Gate | 13       |

## **CHAPTER 1**

#### INTRODUCTION

#### 1.1 OVERVIEW

There is always a question striking that how and in what way are computers able to send data between its components? The computers earlier uses switches which were programmed for "on" and "off" so that it can control transmission of data. The switches are easy understandable, now they are not used because they were slow. There are many technologies to replace switches, which are vacuum tubes, different generations of microchips and transistors. Now a days switches are not in use still there are function are still in use to send data. Different functions are used by the set of different name and symbols and these are basically known as Logic gates. Logic Gate represents the relationship between various classical logical and the gate name in the logic part represents that the logic gates can transfer the signal to the different part of the large circuit which is basically similar to a stoplight directing the traffic.

The following are the examples of the logical situations:

- 1. For example a gumball machine in this machine there can be two inputs. Input A will be we have to insert a coin and input B will be to click the button. So, in the outcome if we want a ball we have to do both which means we have to insert a coin and push the button (AND)

- 2. If there is a common bulb which has two switches in different rooms. These switches will be input of the bulb. And the bulb is on when either of the two switches are on. (OR)

- 3. Magnets are very good example of XOR gate. The two poles north and South Pole can be considered as two inputs. In magnet when there is same pole they repel each other and when there are different poles they attract each other (Exclusive or, XOR, in this when both conditions are true then output is false).

The system which shows above logical conditions are Logic Gates like AND, OR, XOR and many others. Logic gates are drawn with functionality of gate which is represented by AND, OR, XOR gates.

The input ports are generally represented on the left hand side and output ports are represented on right hand side.

The logical function is represented through logical table where logic 0 represents the false condition while 1 represents the true condition.

| Logic Gate | Symbol     | Description                                                                                                                                   | Boolean                |

|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| AND        | 10-        | Output is at logic 1 when, and only when all its inputs are at logic 1,otherwise the output is at logic 0.                                    | X = A•B                |

| OR         | <b>→</b>   | Output is at logic 1 when one or more are at logic 1.lf all inputs are at logic 0,output is at logic 0.                                       | X = A+B                |

| NAND       |            | Output is at logic 0 when,and only when all its inputs are at logic 1,otherwise the output is at logic 1                                      | X = A•B                |

| NOR        | <b>⊅</b> ~ | Output is at logic 0 when one or more of its inputs are at logic 1.If all the inputs are at logic 0,the output is at logic 1.                 | X = A+B                |

| XOR        |            | Output is at logic 1 when one and Only one of its inputs is at logic 1. Otherwise is it logic 0.                                              | X = A⊕ B               |

| XNOR       |            | Output is at logic 0 when one and only one of its inputs is at logic1.Otherwise it is logic 1. Similar to XOR but inverted.                   | X = A ⊕ B              |

| NOT        | <b>→</b> > | Output is at logic 0 when its only input is at logic 1, and at logic 1 when its only input is at logic 0.That's why it is called and INVERTER | X = \( \overline{A} \) |

Fig 1. Description of all logic gates

#### 1.2 DESIGNING OF GATES

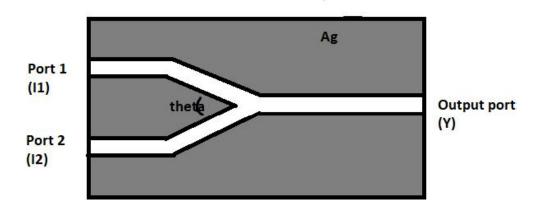

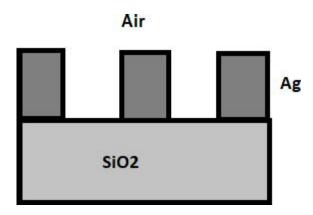

The optical logic gates are designed using a SiO2 substrate and a Y coupler on it as shown in the figure below. There are two input ports to provide different input according to amplitude requirement and a single output to obtain the output according to logic function. Here the substrate is made up pf SiO2 layer and the signal path has no element the signal is transmitting in Air. The air gap is created in the Ag metal.

Fig 2. Front view structure of gate based on slot film

The thickness of the Ag metal and SiO2 layer is taken as 100nm and the angle of the coupler is 30 degree. The path for the transmission is 60nm wide. The permittivity of SiO2 is 2.13.

For, FDTD simulation the boundary conditions are taken to be periodic for all the boundaries.

The frequency range is 400 to 700 nm.

DFT monitors and Time monitors are used to view the results and spectrum.

Fig 3. Side view structure of gate based on slot film

## CHAPTER 2 LITERATURE OVERVIEW

#### 2.1 OPTICAL LOGIC GATES

Optical Logic gates are the device used for transmission of light form input to output based on the different logic gates functions. For example – if we talk about AND logic gate the output of the gate will be according to AND function i.e. until we get all the input as high we will not get output.

Logical Gates works at two different levels of voltages one is the positive level and other one is the zero Level since Logic gates are digital components. These works on two states on and off. In the voltage zero, it is off state while for the voltage 1 it is on state. The range of the on state varies from 3.5 to 5 Volts and the range can be lower for some of the applications.

The state at the inputs of Logic Gates compares the state at the inputs and it decides what should be the output according to the input. A Logic Gate is either active or on according to the rules if they are correctly met. At the On state of the logic gates dictates the electricity which is flowing through the logic gate.

Truth tables indicates the state of the output depending upon the input and the Boolean Logic are the electronic versions of Logic Gates.

And optical logical gate are the optical version of digital logic gate and these gates are used to perform logical functions in photonics domain.

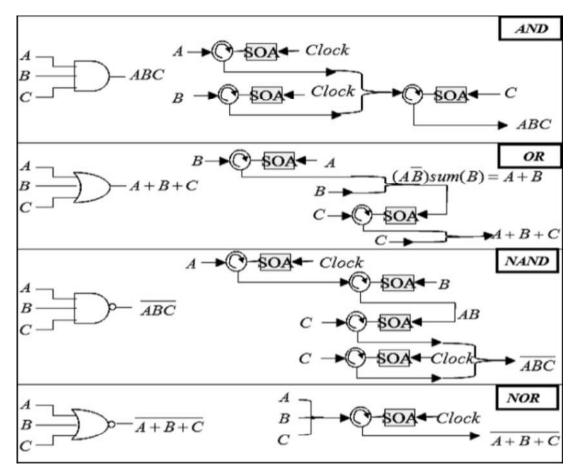

Fig 4. Designing using different amplifiers

#### **2.1.1 BASIC LOGIC GATES**:

#### AND GATE

The optical AND gate is a digital logic gate which is used to function same as logical AND in optical domain. The symbol, expression and truth table of the gate is mentioned below. The output is high when the both the inputs are high is one input is low then the output is low.

Symbol-

Fig 5. Symbol of AND Gate

Expression-

Y = A.B

Truth table-

Table 1. Truth table of AND Gate

| INPUT |   | OUTPUT |

|-------|---|--------|

| A     | В | Y      |

| 0     | 0 | 0      |

| 0     | 1 | 0      |

| 1     | 0 | 0      |

| 1     | 1 | 1      |

#### OR GATE

The optical OR gate is a digital logic gate which is used to function same as logical OR in optical domain. The symbol, expression and truth table of the gate is mentioned below. The output is high when any of the inputs is high is both input arw low then the output is low.

#### Symbol-

Fig 6. Symbol of OR Gate

Expression-

$$Y = A + B$$

Truth table-

Table 2. Truth table of OR Gate

| INPUT |   | OUTPUT |

|-------|---|--------|

| A     | В | Y      |

| 0     | 0 | 0      |

| 0     | 1 | 1      |

| 1     | 0 | 1      |

| 1     | 1 | 1      |

#### NOT GATE

The optical NOT gate is a inverter which means if we give any input it will give inverted output.

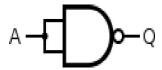

Symbol-

Fig 7. Symbol of NOT Gate

Expression-

$$Y = A$$

Truth table-

Table 3. Truth table of NOT Gate

| INPUT (A) | OUTPUT<br>(Y) |

|-----------|---------------|

| 0         | 1             |

| 1         | 0             |

#### **2.1.2 UNIVERSAL LOGIC GATES:**

#### NAND GATE

In electronics, a NAND gate is a combination of NOT and AND gate. The output is first AND then it is inverted. This means when both inputs are high we will get a low output.

Symbol-

Fig 8. Symbol of NAND Gate

Expression-

$$Y = \overline{AB}$$

Truth table-

Table 4. Truth table of NAND Gate

| INPUT |   | OUTPUT |

|-------|---|--------|

| A     | В | Y      |

| 0     | 0 | 1      |

| 0     | 1 | 1      |

| 1     | 0 | 1      |

| 1     | 1 | 0      |

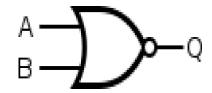

#### NOR GATE

In electronics, a NOR gate is a combination of NOT and OR gate. The output is first added then it is inverted. This means when both inputs are low we will get a high output.

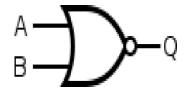

Symbol-

Fig 9. Symbol of NOR Gate

Expression-

$$Y = \overline{AB}$$

Truth table-

**Table 5**. Truth table of NOR Gate

| INPUT |   | OUTPUT |

|-------|---|--------|

| A     | В | Y      |

| 0     | 0 | 1      |

| 0     | 1 | 0      |

| 1     | 0 | 0      |

| 1     | 1 | 0      |

#### 2.1.3 DERIVED GATES

#### **XOR GATE**

This are called derived gates because they are derived from the basic AND, OR and NOT gates. They can be made from universal gates also. Then function of this gate if any one input is high we get high output and if there are same input at both the places we get a low input. Symbol,, expression and truth table are shown below.

Symbol-

Fig 10. Symbol of XOR Gate

Expression-

$$Y = \Theta = A.\overline{B} + \overline{A}.B = A \text{ xor } B$$

Table 6. Truth table of XOR Gate

| INPUT |   | OUTPUT |

|-------|---|--------|

| A     | В | Y      |

| 0     | 0 | 0      |

| 0     | 1 | 1      |

| 1     | 0 | 1      |

| 1     | 1 | 0      |

#### **XNOR GATE**

This are called derived gates because they are derived from the basic AND, OR and NOT gates. They can be made from universal gates also. Then function of this gate if any one input is high we get low output and if there are same input at both the places we get a high input. Symbol, expression and truth table are shown below.

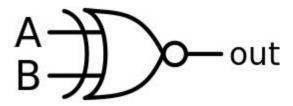

#### Symbol-

Fig 11. Symbol of XNOR Gate

Expression-

$$Y = A \odot B = A.B + \overline{A.B} = \overline{x} - \overline{y}$$

Truth table-

Table 7. Truth table of XNOR Gate

| INPUT |   | OUTPUT |

|-------|---|--------|

| A     | В | Y      |

| 0     | 0 | 1      |

| 0     | 1 | 0      |

| 1     | 0 | 0      |

| 1     | 1 | 1      |

## 2.2 Derivation of all gates from Universal logic gates

Using NAND Gate-

**NOT Gate**

Fig 12. NOT Gate using NAND Gate

Fig 13. AND Gate using NAND Gate

NAND Gate

Fig 14. NAND Gate using NAND Gate

OR Gate

Fig 15. OR Gate using NAND Gate

NOR Gate

Fig 16. NOR Gate using NAND Gate

#### XOR Gate

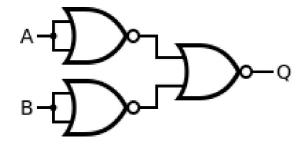

Fig 17. XOR Gate using NAND Gate

#### XNOR Gate

Fig 18. XNOR Gate using NAND Gate

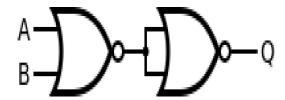

Using NOR Gate-NOT Gate

Fig 19. NOT Gate using NOR Gate

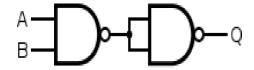

#### AND Gate

Fig 20. AND Gate using NOR Gate

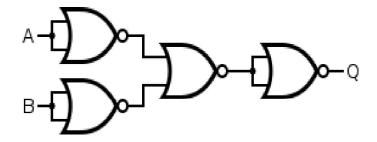

### NAND Gate

Fig 21. NAND Gate using NOR Gate

### OR Gate

Fig 22. OR Gate using NOR Gate

NOR Gate

Fig 23. NOR Gate using NOR Gate

## XOR Gate

Fig 24. XOR Gate using NOR Gate

## XNOR Gate

Fig 25. XNOR Gate using NOR Gate

Here, we are using LUMERICAL as a simulation tool to study these gates in optics and check we are getting the desired result or not.

Results given by the student are not correct, and need major corrections before the date of viva. Even after multiple reminders, she has failed to incorporate these changes.

## CHAPTER 3 SIMULATIONS

#### 3.1 INPUTS-

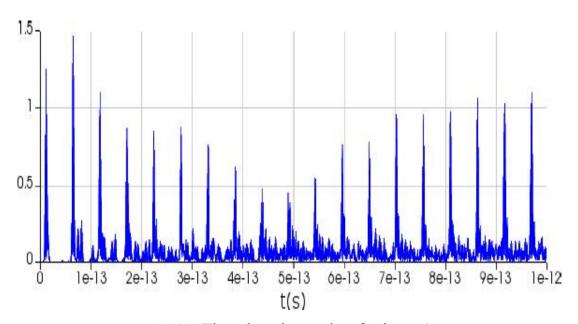

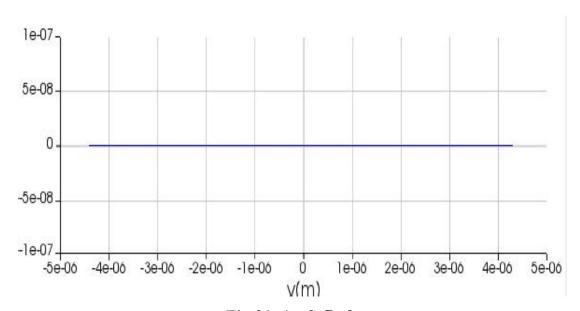

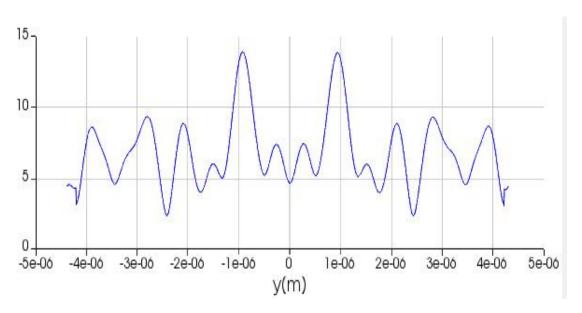

In the fig shown below, the spectrum which is represented it is in time domain. The following spectrum represent the high input given at input port. For low input the spectrum will be of straight line at y = 0 axis.

Fig 26. Time domain monitor for input 1

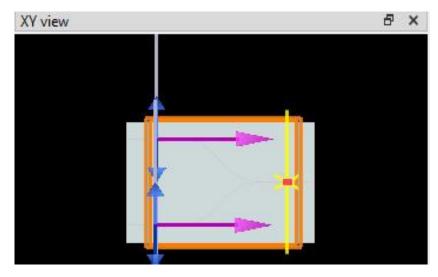

#### 3.2 DESIGN OF GATE-

The following figures represent the different simulation views of our design.

Fig 27. XY VIEW

Fig 28. XZ VIEW

Fig 29. YZ VIEW

Fig 30. PERSPECTIVE VIEW

## CHAPTER 4 RESULT AND OBSERVATIONS

#### **4.1 RESULT**

#### OR GATE-

So, for OR Gate we create a constructive inputs i.e. the input in electrical part can be said to be as between 0V to 5V. For low input we have taken amplitude equals to 0 and for high input we have taken input equals to 1.

So, output of the OR Gate for different combinations are,

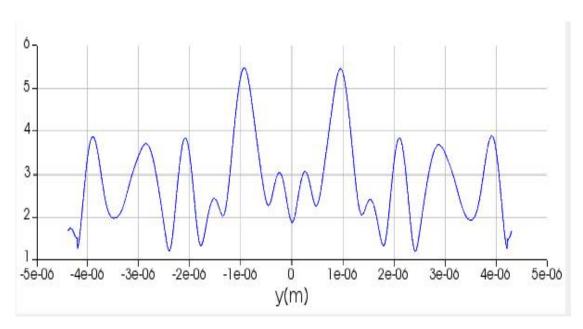

**Fig 31.** A =0, B=0

For (0,1) input fig 32 represents the electric field of the OR Gate. As the there is one input high we have got some result. The spectrum is not symmetry because there are some errors also. The similar result is for (1,0) and (1,1) inputs also.

**Fig 32.** A =0, B=1

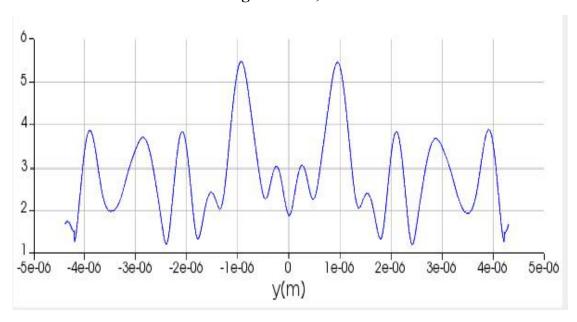

**Fig 33.** A =1, B=0

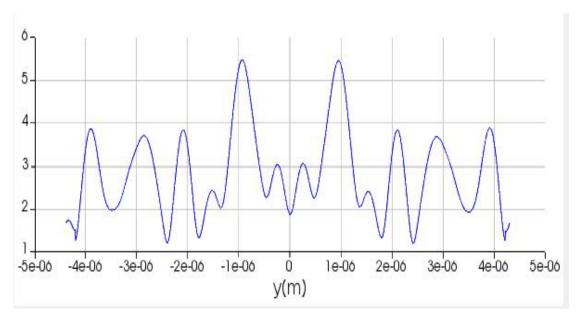

**Fig 34.** A =1, B=1

#### AND GATE-

So, for AND Gate we create a constructive inputs i.e. the input in electrical part can be said to be as between 0V to 5V. For low input we have taken amplitude equals to 0 and for high input we have taken input equals to 5. Here the inputs should be more than the threshold value and less than maximum input.

So, output of the AND Gate for different combinations are,

**Fig 35.** A =1, B=1

As the above Gate is AND Gate, so in fig 35. It is showing some result. And we can see that compared to AND gate the output of electric field has higher amplitude. This is because we have taken high amplitude in input side also to make it work as AND gate.

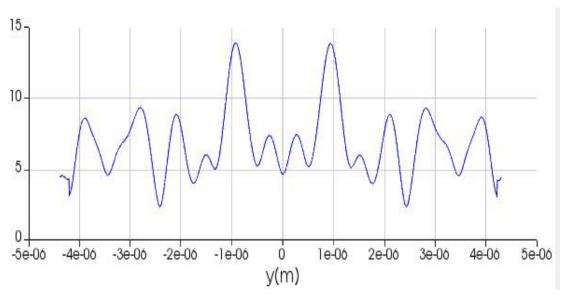

And below are the output is any of the input is low. This means we haven't got any output for (0,0),(0,1) and (1,0).

**Fig 36.** A =0, B=1

Fig 37. A =1, B=0

**Fig 38.** A =0, B=0

#### NOT GATE

NOT Gate gives output opposite to the input provided. So, the input port 2 is used as a control signal and only 1 input is sending signals.

**Fig 39.** A =0

**Fig 40.** A = 1

## **CONCLUSION**

After studying the gates above we are confident that the rest of the gates like NAND, NOR, XOR and XNOR can be also implemented using same method. In the future there is many more researches on this topic. By changing the value of input we have seen changes in our output also. The change in output is recorded. The result can be little different from the real result and as its in optical domain we can use it in various optical networks where we have to perform the logical operations. Further these logic gates can be fabricated and tested and the result can be compared to the simulation results.

#### REFERENCES

- [1] Simulation of varied Si Waveguides to study FCA effect in TPA based Optical Logic Gates Rudra Vaswata Roy Choudhury Department of Electrical Engineering Indian Institute of Technology Madras Chennai, India <a href="mailto:ee14s047@ee.iitm.ac.in">ee14s047@ee.iitm.ac.in</a>

- [2] Energy Efficiency of Microring Resonator (MRR)- Based Binary Decision Diagram (BDD) Circuits Ozan Yakar, Yuqi Nie, Kazumi Wada, Anuradha Agarwal and Ilke Ercan, Junior Member, IEEE

- [3] Implementing Inverse Design Tools for Plasmonic Digital Logic Devices Krishna Narayan Mark C. Harrison

- [4] Propose, Analysis and Simulation of an All Optical Full Adder Based on Plasmonic Waves using Metal-Insulator-Metal Waveguide Structure Mohsen Olyaee\*,1, Mohammad Bagher Tavakoli1, Abbas Mokhtari11 Department of Electronic Engineering, Arak Branch, Islamic Azad University, Arak, IranDTD based Plasmonic light trapping analysis in thin film hydrogenated amorphous silicon solar cells Article in International Journal of Renewable Energy Research January 2018

- [5] Optical interferometric logic gates based on metal slot waveguide network realizing whole fundamental logic operations Deng Pan,1 Hong Wei,1 and Hongxing Xu1,2,3,\* 1Beijing National Laboratory for Condensed Matter Physics and Institute of Physics, Chinese Academy of Sciences, Box 603-146, Beijing 100190, China 2School of Physics and Technology, Wuhan University, Wuhan 430072, China 3Division of Solid State Physics/The Nanometer Structure Consortium, Lund University, Box 118, SE-22100 Lund, <a href="mailto:Sweden\*hxxu@iphy.ac.cn">Sweden\*hxxu@iphy.ac.cn</a>

- [6] Design of all- optical XOR and XNOR logic gates based on Fano resonance in plasmonic ring resonators Marziyeh Moradi1 · Mohammad Danaie1 · Ali Asghar Orouji1 Received: 22 December 2018 / Accepted: 30 April 2019 © Springer Science+Business Media, LLC, part of Springer Nature 2019

- [7] All-optical logic gates using a plasmonic MIM waveguide and elliptical ring resonator Rida El Haffar Abdelmalek Essaadi University: Universite Abdelmalek Essaadi oussama mahboub ( omahboub@uae.ac.ma ) National school of Applied sciences of Tetouan <a href="https://orcid.org/0000-0001-7437-2761">https://orcid.org/0000-0001-7437-2761</a> Abdelkrim Farkhsi Abdelmalek Essaadi University: Universite Abdelmalek Essaadi Mustapha Figuigue Abdelmalek Essaadi University: Universite Abdelmalek Essaadi

- [8] Silicon photonic NAND gate Conference Paper · July 2017 DOI: 10.1109/CLEOPR.2017.8118621

- [9] Topological all-optical logic gates based on two-dimensional photonic crystals L. HE, W. X. ZHANG, AND X. D. ZHANG\* China Beijing Key Laboratory of Nanophotonics & Ultrafine Optoelectronic Systems, School of Physics, Beijing Institute of Technology, 100081, Beijing, China \*zhangxd@bit.edu.cn