# ANALYSIS OF VDDDA BASED VOLTAGE-MODE MISO AND SIMO UNIVERSAL FILTER

A DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE

OF

## MASTER OF TECHONOLOGY IN VLSI DESIGN & EMBEDDED SYSTEM

Submitted by:

DHRUV GOEL

2K18/VLS/02

Under the supervision of

Dr. DEVA NAND

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

**AUGUST, 2020**

#### **DELHI TECHNOLOGICAL UNIVERSITY**

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **CANDIDATE'S DECLARATION**

I, DHRUV GOEL, Roll No. 2K18/VLS/02 student of MTech (VLSI Design and Embedded System), hereby declare that the project titled **"Analysis of VDDDA based Voltage-Mode MISO and SIMO Universal Filter"** which is submitted by me to the Department of Electronics And Communication Engineering, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associate ship, Fellowship or other similar title or recognition.

Sherry God

Place: Delhi Date: 31/08/2020 **DHRUV GOEL**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

# **CERTIFICATE**

I hereby certify that the Project Dissertation titled "Analysis of VDDDA based Voltage-Mode MISO and SIMO Universal Filter" which is submitted by DHRUV GOEL, Roll No. 2K18/VLS/02, Electronics and Communication Engineering, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date: 31/08/2020 Dr. DEVANAND SUPERVISOR To My Parents,

## Mrs. Asha Goel & Mr. Shiv Kumar Goel

And

All My Teachers

## **ACKNOWLEDGEMENT**

I would like to articulate my deep gratitude to my supervisor **DR. DEVA NAND** (Assistant Professor, ECE), for continuous support, patience, moral support, motivation and immense knowledge during my MTech research project. Furthermore, I would like to thank him for introducing me to the topic as well as for the support on the way for the completion of this project report under the guidance of professional like him. I could not have imagined having a better guide and advisor for my MTech study.

I am also grateful to **Prof. N.S. RAGHAVA**, HOD, Department of Electronics and Communication Engineering, DTU for providing the right academic resources & environment for this work to be carried out. I would also acknowledge **Prof. NEETA PANDEY**, for her immense support. Last but not the least, my whole-heartedly thanks to all my friends who have patiently extended all sorts of help for accomplishing this undertaking.

Sherry God

**DHRUV GOEL**

## ABSTRACT

Research on analog signal processing has been heavily explored in the analysis and applications of various active building blocks (ABBs), which are expected to perform better than traditional op amps. Voltage Differencing Differential Difference Amplifier (VDDDA) is one such new versatile 'voltage differencing' active building block (ABB). It is a universal block to realize various amplifiers with less transistor count. Device's internal structure consists of operational transconductance amplifier (OTA) followed by differential difference amplifier (DDA).

In this project, two second order voltage-mode filters are proposed using the VDDDA as an active block. The first proposed filter is sort of MISO multifunction filter having three input nodes and single output node. It consists of one VDDDA, one resistor and two identical capacitors. The proposed filter can provide five standard functions: Low-Pass (LP), High-Pass (HP), Band-Pass (BP), Band-Stop (BS) and All-Pass (AP) responses for the same circuit topology. The natural frequency and quality factor both can be electronically controllable and tuneable.

The second proposed filter is universal voltage-mode SIMO filter. It comprises of three VDDDAs, two grounded capacitors and single grounded resistor. The input voltage node exhibits high impedance. The proposed filter simultaneously provides Low-Pass (LP), High-Pass (HP), Band-Pass (BP), Band-Reject (BR) and All-Pass (AP) responses with same circuit topology. The natural frequency and quality factor can be tuned electronically and orthogonally by dc bias current. The impedance at output nodes HP, AP and BR has low impedance which can connect to other circuit without the use of voltage buffer. This makes the proposed filter suitable for IC development.

The theoretical results are verified by SYMICA DE simulations using TSMC 0.18 $\mu$ m SCN018 CMOS process parameters with  $\pm 0.9$ V supply voltages.

# TABLE OF CONTENTS

| Candidate's Declaration                             | ii  |

|-----------------------------------------------------|-----|

| Certificate                                         | iii |

| Acknowledgement                                     | v   |

| Abstract                                            | vi  |

| Table of Contents                                   | vii |

| List of Figures                                     | ix  |

| List of Tables                                      | xi  |

| CHAPTER 1 INTRODUCTION                              | 1   |

| 1.1 Background                                      | 1   |

| 1.2 Current-mode and Voltage-mode Signal Processing | 2   |

| 1.3 Analog Filter Design                            | 3   |

| 1.4 Motivation                                      | 7   |

| 1.5 Objective                                       | 8   |

| 1.6 Organization of Report                          | 8   |

| CHAPTER 2 LITERATURE REVIEW                         | 9   |

| 2.1 Comparison of various voltage-mode SIMO filters | 9   |

| 2.2 Comparison of various voltage-mode MISO filters | 11  |

| CHAPTER 3 CIRCUIT DESIGN                                           | 13 |

|--------------------------------------------------------------------|----|

| 3.1 VDDDA (Voltage Differencing Differential Difference Amplifier) | 13 |

| 3.2 Proposed MISO filter description                               | 16 |

| 3.3 Proposed High input impedance SIMO filter description          | 19 |

| 3.3.1 Analysis of non-ideal case                                   | 21 |

| CHAPTER 4 SIMULATIONS RESULTS                                      | 23 |

| 4.1 Analyses of VDDDA                                              | 24 |

| 4.2 Analyses of proposed VM MISO filter                            | 27 |

| 4.3 Analyses of proposed VM SIMO Universal filter                  | 32 |

| CHAPTER 5 CONCLUSION AND FUTURE SCOPE                              | 38 |

| REFERENCES                                                         | 39 |

# LIST OF FIGURES

| Fig. No. | Title                                                    | Page No. |

|----------|----------------------------------------------------------|----------|

| Fig. 1   | Ideal responses of different filters                     | 5        |

| Fig. 2   | (a) VDDDA Circuit Symbol, (b) its Equivalent circuit     | 14       |

| Fig. 3   | VDDDA implemented by CMOS technology                     | 15       |

| Fig. 4   | VDDDA based voltage-mode MISO filter                     | 17       |

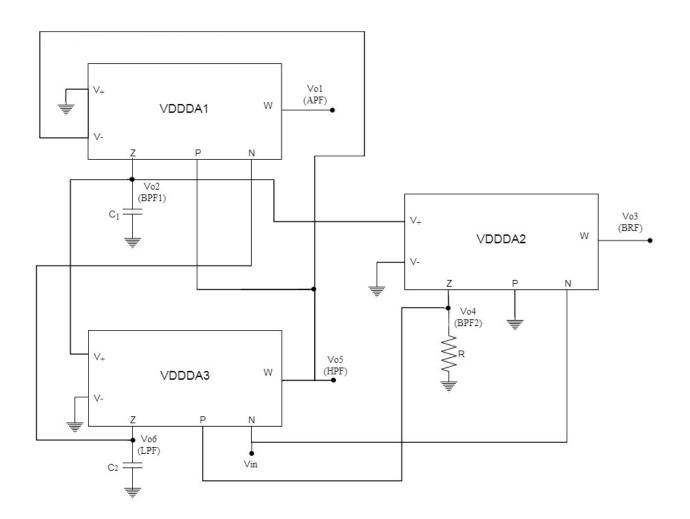

| Fig. 5   | VDDDA based voltage-mode SIMO filter                     | 19       |

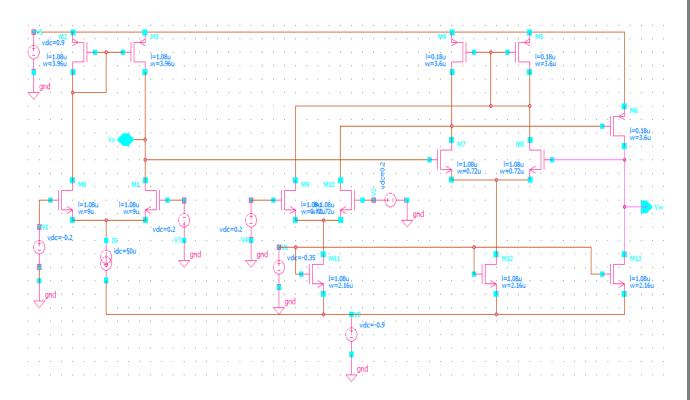

| Fig. 6   | Schematic of CMOS implemented VDDDA                      | 23       |

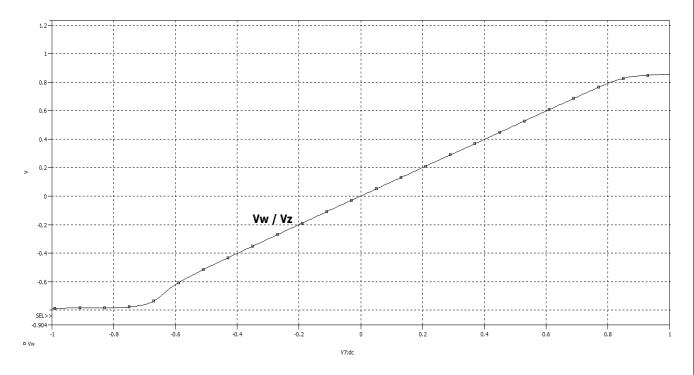

| Fig. 7   | DC analysis of VDDDA (V <sub>w</sub> vs V <sub>z</sub> ) | 24       |

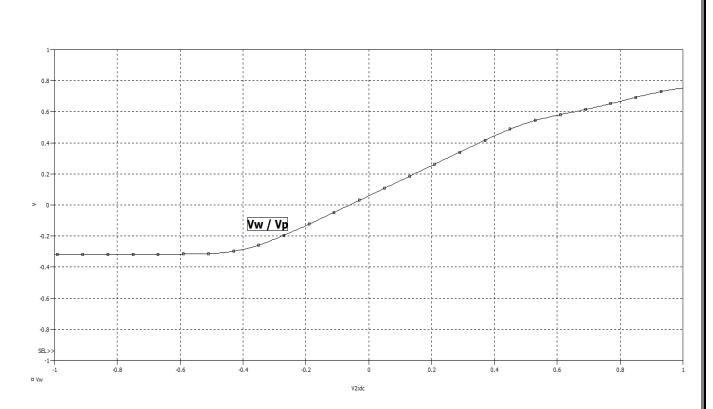

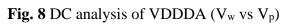

| Fig. 8   | DC analysis of VDDDA (V <sub>w</sub> vs V <sub>p</sub> ) | 25       |

| Fig. 9   | DC analysis of VDDDA (V <sub>w</sub> vs V <sub>n</sub> ) | 25       |

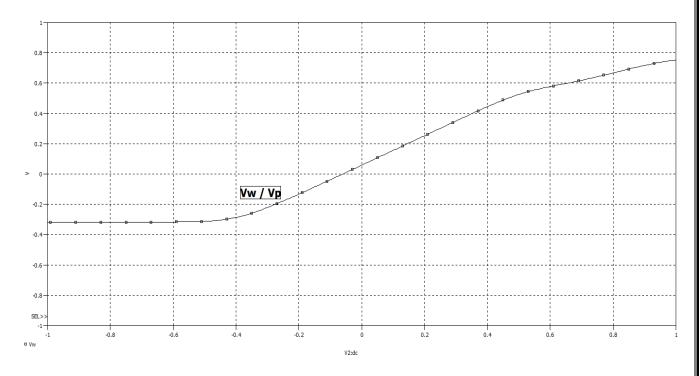

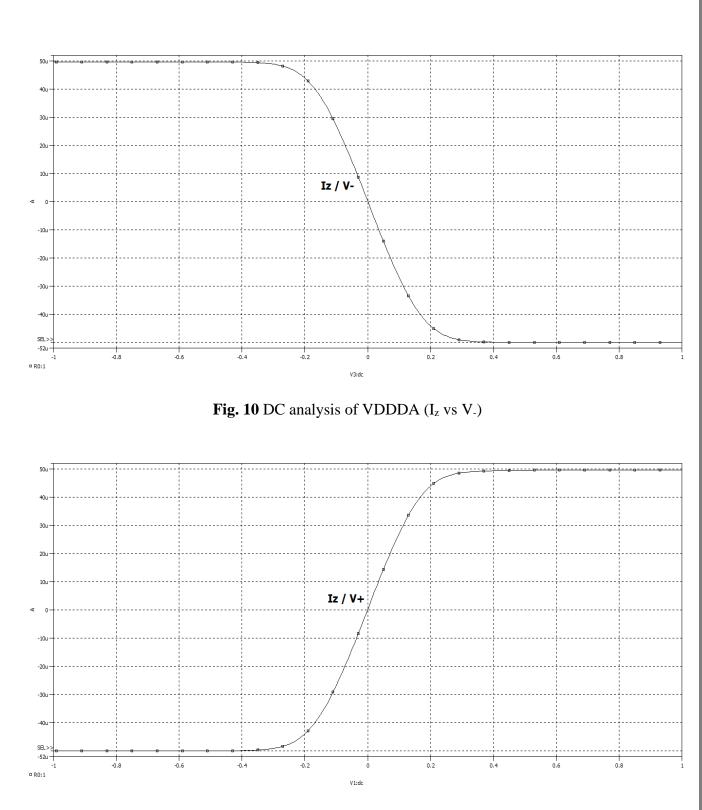

| Fig. 10  | DC analysis of VDDDA (Iz vs V.)                          | 26       |

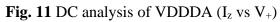

| Fig. 11  | DC analysis of VDDDA (Iz vs V <sub>+</sub> )             | 26       |

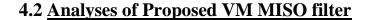

| Fig. 12  | Schematic of proposed MISO filter using VDDDA            | 27       |

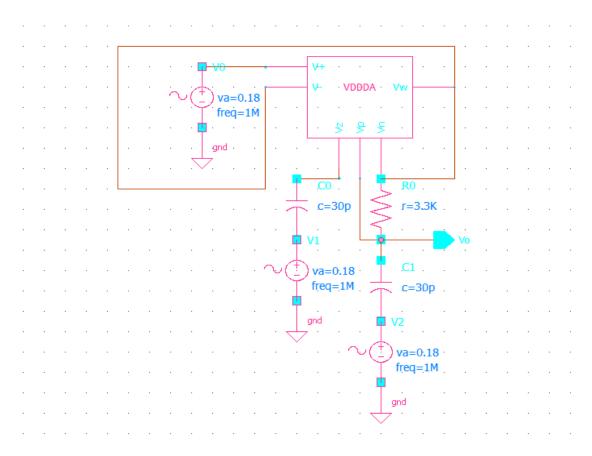

| Fig. 13  | Gain response of LP                                      | 28       |

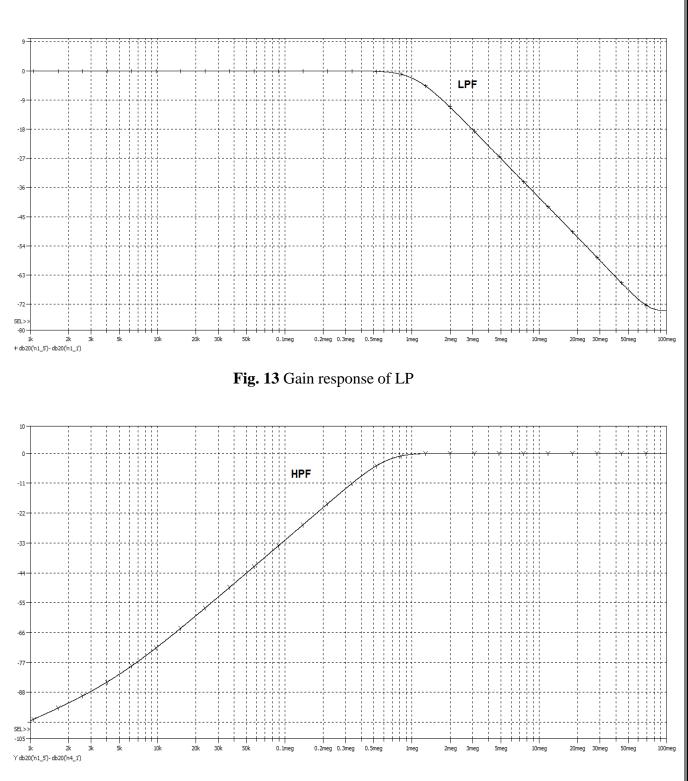

| Fig. 14  | Gain response of HP                                      | 28       |

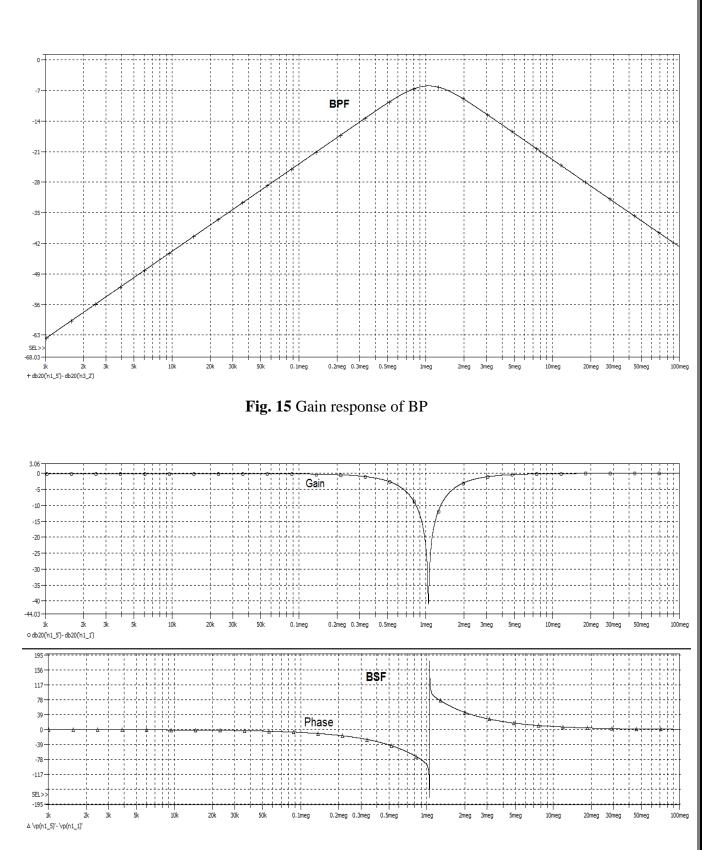

| Fig. 15  | Gain response of BP                                      | 29       |

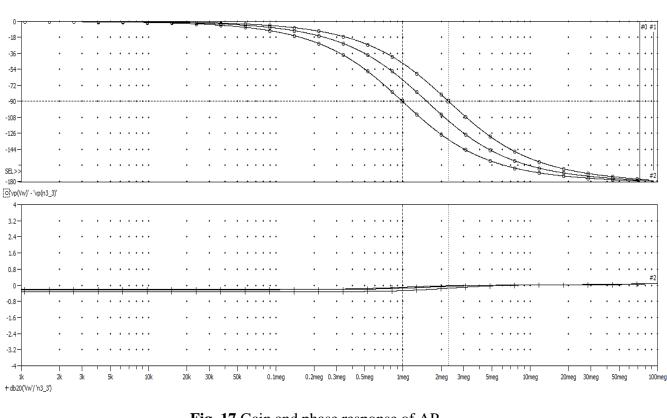

| Fig. 16  | Gain and phase response of BS                            | 29       |

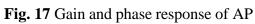

| Fig. 17 | Gain and phase response of AP                                                     | 30 |

|---------|-----------------------------------------------------------------------------------|----|

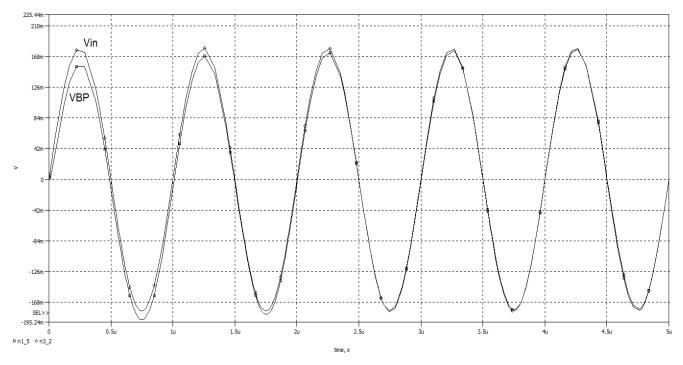

| Fig. 18 | Transient response of BP function                                                 | 30 |

| Fig. 19 | BP responses for different values of $I_B$                                        | 31 |

| Fig. 20 | Schematic of proposed SIMO filter using VDDDA                                     | 32 |

| Fig. 21 | Gain response of LP                                                               | 33 |

| Fig. 22 | Gain response of HP                                                               | 33 |

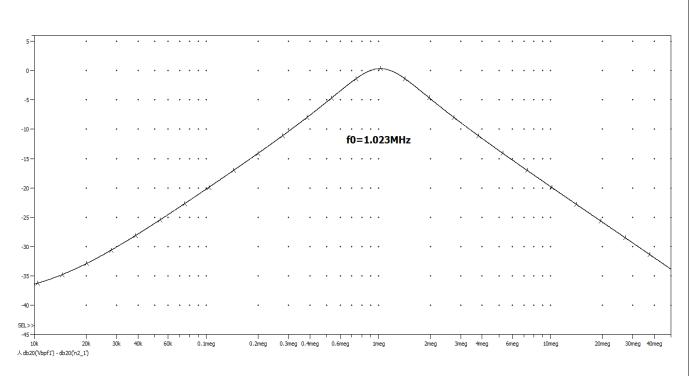

| Fig. 23 | Gain response of BP <sub>1</sub>                                                  | 34 |

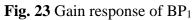

| Fig. 24 | Gain response of BP <sub>2</sub>                                                  | 34 |

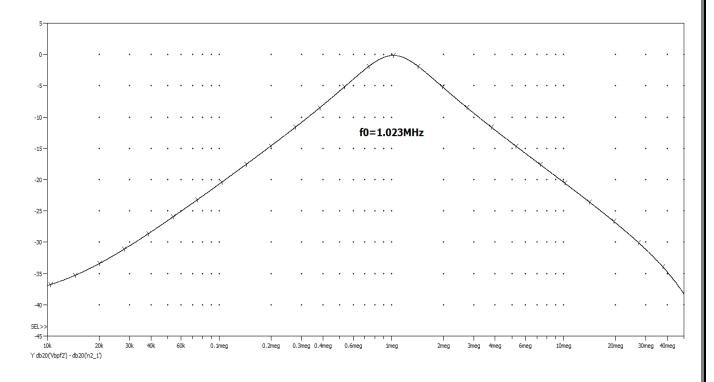

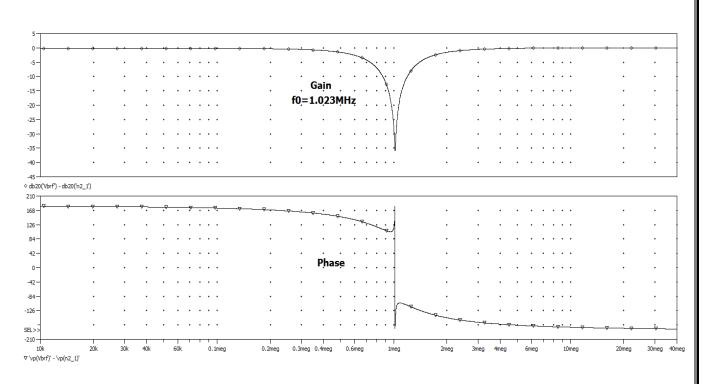

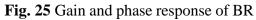

| Fig. 25 | Gain and phase response of BR                                                     | 35 |

| Fig. 26 | Gain and phase response of AP                                                     | 35 |

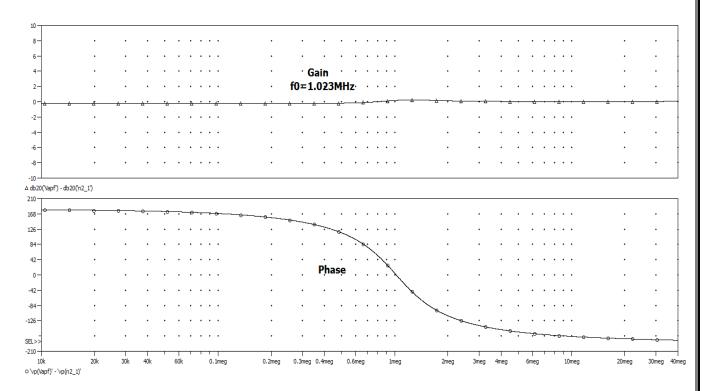

| Fig. 27 | $BP_2$ responses for different values of $I_{B2}$                                 | 36 |

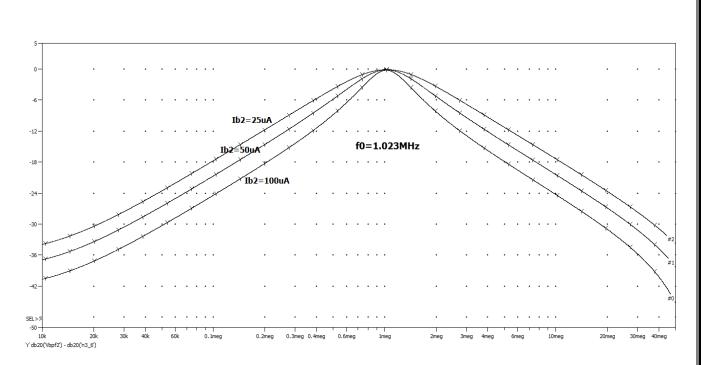

| Fig. 28 | BP <sub>2</sub> responses for different values of C <sub>1</sub> , C <sub>2</sub> | 36 |

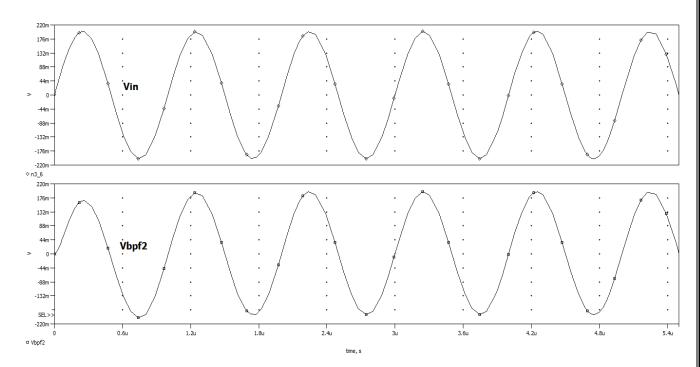

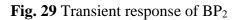

| Fig. 29 | Transient response of BP <sub>2</sub>                                             | 37 |

# LIST OF TABLES

| Table No. | Title                                   | Page No. |  |  |

|-----------|-----------------------------------------|----------|--|--|

| Table 1   | Biquads transfer functions              | 7        |  |  |

| Table 2   | Comparison of different VM SIMO filters | 10       |  |  |

| Table 3   | Comparison of different VM MISO filters | 12       |  |  |

| Table 4   | Aspect ratios of MOS transistors        | 24       |  |  |

## CHAPTER 1

## **INTRODUCTION**

#### 1.1 Background

The demand for analog and digital circuits with extremely low supply voltages and low power consumption has become a topic of great significance for long term prospects which influence the improvement of microelectronic industry [1]. In numerous applications, extra necessities show up, especially the extraordinary speed or the accuracy of signal processing. There is a problem in meeting the above requirements at the same time and the trade-off arrangements ought to be utilized in real time applications [2].

Over the last 20 years, the evolution of modern analog signal processing applications has followed the trend of so-called current-modes [3], where the signal representing the information being processed is in the form of a current. In contrast to traditional voltage- mode, which utilizes voltage, current-mode circuits can exhibit, among other things, higher bandwidth and better signal linearity under certain conditions. They are designed for low voltage swings, so smaller supply voltages can be used. Simultaneously with the development of current-mode applications, mixed mode circuits are also analyzed because the interface between sub-blocks operating in different modes needs to be optimized. There is even another justification for mixed-mode operation and return to traditional voltage-mode. Some generally accepted statements about the benefits of current-mode [4] seem to have no real rationale.

Voltage Differencing Differential Difference Amplifier (VDDDA) [5] is a new versatile 'voltage differencing' active building block (ABB). It is a six-terminal universal block to realize various amplifiers with less transistor count and constitute dynamic properties required for any real-time applications. Device's internal structure consists of operational transconductance amplifier (OTA) followed by differential difference amplifier (DDA). This building block consists of three addition/subtraction input voltage terminals where the transconductance ( $g_m$ ) of the block can be tuned electronically. In analog signal processing, we use VDDDA as an active building block which offers various advance features, for example,

1

electronic controllability, avoiding the need of external voltage summing circuit in circuit design, quick circuit synthesization with least number of external passive components, etc. Especially, in the design of voltage-mode active filter which is an important requirement for application in electrical and electronic system [1], the voltage summing is required in filter thus; VDDDA is a good choice for designers. Moreover, the output impedance of VDDDA is low which allows the cascadability of devices without the need of voltage buffer.

The universal filters are considered as the versatile circuit because they can offer multiple filter response in the same circuit without altering the circuit topology. If we consider the input and output terminals as a parameter, there are four types of universal filter. The first one is simple and not being used frequently i.e., single input single output (SISO) filter. The second one is single input multiple outputs (SIMO) filter. This filter topology simultaneously provides several output responses. The third filter is called as the multiple inputs multiple outputs (MIMO) universal filter. The last one is the multiple inputs single output (MISO) filter. In this MISO filter, there is only single output port, but we can select multiple output filter responses by applying the suitable input signal. The attractive way to select the input signal to obtain the desired output response is to use the digital switch which is easy to control by microcontrollers. Therefore, in this project report, we have proposed one MISO multifunction filter and one SIMO universal filter using VDDDA block.

### 1.2 Current-mode and Voltage-mode signal processing

The signal processing performed on electrical or electronic circuits is carried out through organized charge motion, where currents and voltages are usually variables and time, resistance, inductance and capacitance are the circuit parameters that define the characteristics of signal processing. The reason for the use of voltage and current in analog signal processing is that the active devices used in analog electronics primarily use resistance (conductance) as the parameters for control signal processing. The signal is then processed through a variety of voltage-current and current-voltage conversion, amplification, weighted addition, and multiplication. In the past, voltage was used as the primary variable for signal processing because designers thought voltage processing was easier and simpler than current. In the early years of analog electrons, only voltage mode processing was practical, and most of the building blocks used in analog electrons, such as op amps, were typical voltage processing circuits.

Over the time, for analog signal processing there is need to increase the speed of circuits and also to reduce the supply voltages of integrated circuits and so what the designers do, they began to dedicate themselves to the so-called current mode. In current mode, the individual circuit elements should be controlled by current and not by voltage.

There is a difference one can study between voltage and current mode circuits is that a single output terminal of a current processing block is able to supply only a single input terminal, because it is not possible to arrange the inputs of the current processing blocks into a serial connection [4]. Therefore, to supply the same input signal to multiple input terminals of the block, it is necessary to design current processing building blocks with multiple outputs giving the same output signal while in voltage processing circuits a single voltage-output terminal can supply more voltage-input terminals connected in parallel.

As more and more advances in the field of analog system and circuits were made, need for some application specific modes also aroused. In certain circuits, the input was current and the output was needed to be voltage, these circuits were called trans-impedance mode circuits. Similarly, in some other circuits the input was voltage and the output was needed as current, such circuits are called trans-admittance mode circuits. These modes are however very application specific.

#### 1.3 Analog Filter Design

Basically, Digital circuits can operate only with two voltage values, while analog circuits can process the signals with continuous variation of voltages. But we know the fact that no macroscopic signal can truly quantized, so the digital circuit designers must have some familiarity or knowledge of analog electronics also to work with signals. Therefore, analog circuit design plays a pivotal role in the today's integrated circuit technology. The most common used analog electronic circuits are filters, active filters, oscillators, active oscillators, multi-vibrators, rectifiers, mixers, etc. A simple analog filters or passive filters consist of either

all three or any two out of resistors, capacitors and inductors. And accordingly, we have, RC, RL, LC and RLC circuits. Using these passive circuits, a filter can be designed by blocking certain frequencies and passing another signal frequency [1].

The active filters are those filters which uses active components like amplifiers in their circuit along with some passive elements. Inclusion of active components, like amplifiers, it improves the performance and expectedness of a filter, while the requirement for inductors is also avoided as inductors are typically expensive and bulky. An amplifier inhibits the load impedance of the succeeding stage from upsetting the characteristics of the filter. But on the other hand, active devices also bring some limitations to the circuits like finite bandwidth, noise injection, and more power consumption into the circuit, etc.

Filters are analog electronic circuits that process signals depending on the frequency. The fundamental filter concept can be explained by examining the frequency dependence of the impedance of the inductor and capacitor. Consider a voltage divider whose shunt leg has a reactive impedance. As the frequency changes, the reactive impedance value and the voltage division ratio changes. This mechanism is called as the frequency response because it causes the input/output transfer function to change in a frequency-dependent manner.

Filters are used for numerous practical purposes. A Lowpass filters are often used to roll off the gain and stabilize the amplifier at higher frequencies, as excessive phase shift can cause oscillations. High pass filters can be used to block the DC offset of high gain amplifiers or single supply circuits. Filter circuits are commonly used to isolate or separate signals, pass signals of interest, and attenuate the undesirable/unwanted frequencies.

A radio receiver is one such example, where the signal, with desired gain that you wanted to process is passed through the filter and the rest of the signal is attenuated. Filters are also used for data conversion, eliminating the effects of aliasing on A/D systems. They are also used to reconstruct the output signal of a digital-analog system, removing high frequency components such as the sampling frequency and its harmonics, and also unwanted noise mixed in the filtering signal to get desired waveform.

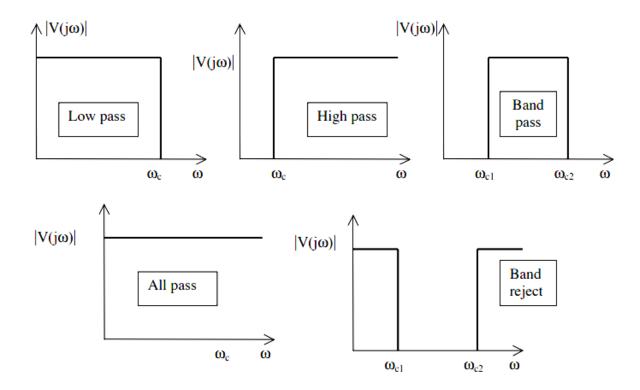

The ideal filter magnitude response has unity or some definite gain over the desired frequencies known as the pass band region and zero elsewhere known as the stop band region. Cut-off frequency is the frequency at which the filter response curve changes from passband to stopband or vice-versa depending upon the filter configuration. Fig.1 shows an ideal filter response of all filters i.e., low-pass (LP), high-pass (HP), band-pass (BP), band-reject (BR) and all-pass (AP) filters. In LP filter, passband is the region of low frequencies and stopband is the region of higher frequencies [2].

Fig. 1 Ideal responses of different filters [2]

The filter that complements the low-pass functionality is high-pass filter. Here, the passband allows high range of frequencies and stopband has low range of frequencies. A band-pass filter is created by cascading two filters i.e., HP and LP filter. The band-pass filter passes the range of frequencies i.e., a frequency band between a lower cut-off frequency,  $\omega_{c1}$  and an upper cut-off frequency,  $\omega_{c2}$ . Frequencies below  $\omega_{c1}$  and above  $\omega_{c2}$  come under the region of stopband.

Band-pass filter is the function that complements the band-reject, or notch filter. Here, the pass bands include frequencies below  $\omega_{c1}$  and above  $\omega_{c2}$ . The frequency band from  $\omega_{c1}$  to  $\omega_{c2}$  fall under the stopband region. The all-pass filter has constant amplitude, so it passes all frequencies equally, as shown in Fig.1. If it is desired to shift the phase as needed without changing the magnitude portion of the frequency response, it is usually placed in a cascade. Unfortunately, the ideal filter defined above is not easy to build. There is a transition region from pass band to stop band in all-pass filter rather not instantaneous transition. Stop band attenuation is not infinite.

### **Standard Biquadratic Filters or Biquads**

The transfer function for the second-order filter is in the form of,

$$H(s) = \frac{N(s)}{D(s)} = \frac{b_2 s_2 + b_1 s + b_0}{s_2 + a_1 s + a_0} \tag{1}$$

is called as biquadratic function. The problem here is that if the poles and zeros of the filtering function lie on the negative real x-axis then those poles and zeros can be realized using a passive RC network [2]. For those cases, we can define the transfer function as

$$H(s) = \frac{N(s)}{D(s)} = H_0 \frac{s^2 + (\omega_z/Q_z)s + \omega_z^2}{s^2 + (\omega_p/Q_p)s + \omega_p^2}$$

(2)

"where,  $H_o$  is the maximum gain or midband frequency gain which could be positive or negative. Here,  $\omega_p$  and  $Q_p$  are the pole-frequency and pole Q-factor respectively; sometimes  $\omega_p$  is also known as undamped natural frequency or cut-off frequency since there will be resonance at  $s = j\omega_p$  in Eq. (2)." [2]

| Types of filter     | N(s)                                      |

|---------------------|-------------------------------------------|

| Low pass            | $H_0\omega_0^2$                           |

| High pass           | $H_0 s^2$                                 |

| Band pass           | $H_0(\omega_0/Q_0)s$                      |

| All pass            | $H_0(s^2 - (\omega_0/Q_0)s + \omega_0^2)$ |

| Band reject / Notch | $H_0(s^2 + \omega_0^2)$                   |

Table 1 Biquads transfer functions [9]

Note: For all filters,

$$H(s) = \frac{N(s)}{D(s)}$$

, with  $D(s) = s^2 + (\omega_0/Q_0)s + \omega_0^2$

From table 1, it is observed that by selecting the appropriate values of the coefficients  $b_0$ ,  $b_1$  and  $b_2$ , we can get various types of biquads transfer functions.

### 1.4 Motivation

The VDDDA based circuits for analog signal processing can be found in the literature surveys where many applications are designed such as first-order voltage-mode filter, inductance simulator, oscillator, SIMO & MISO voltage-mode multifunction biquad filter, etc. In general, following are the desired features of VDDDA, which motivates one to use this building block for the filter designing:

- 1) It can provide inverting as well as non-inverting voltage-mode outputs simultaneously from the same circuit topology.

- Voltage input terminals are of high impedance and voltage-mode output terminals are of low impedance, thus easing the device cascadability.

- 3) Use of grounded passive elements in filter circuit is advantageous for monolithic integration.

- 4) It consists of three addition/subtraction input voltage terminals where the transconductance  $(g_m)$  of the block can be tuned electronically.

- 5) Realization of different filter transfer function for proposed MISO and SIMO filter with same circuit topology depending upon the terminals used.

#### 1.5 <u>Objective</u>

The main objective of this report is to describe the proposed design of second-order multifunction voltage-mode filter using VDDDA as an active building block. The proposed MISO and SIMO filters provide all five filtering functions namely, low-pass, high-pass, band-pass, band-reject and all-pass responses for the same circuit configuration. Also, the natural frequency and the Q-factor of filter can be electronically tuneable and controllable.

#### 1.6 Organization of Report

This report has been organized into five chapters. In Chapter 1, it starts with the introduction of analog filter design and its standard filter equations. It also includes the motivation and objective behind the report. Chapter 2 deals with the literature study of various voltage- mode MISO and SIMO filters. Chapter 3 deals with the description of circuit design of VDDDA block and detailed analysis of the proposed MISO filter and SIMO filter. In chapter 4, all the simulation results with schematic and waveforms of the proposed filter are presented. Chapter 5 deals with the conclusion and future scope of the proposed filter.

## CHAPTER 2

## LITERATURE REVIEW

Despite the significant development in digital signal processing and its real time applications, one can never replace the analog signal processing due to its particular advantages. Amplification, rectification, modulation, etc, processed on the message signals can only be performed by the analog processing. Various devices that can process the analog electrical signals have been designed and further modifications in circuits are done according to their characteristics. These modified devices could now further be used for applications such as amplifiers, summers, filters, oscillators, wave generators etc. One of the key applications of analog signal processing is electronic filter. A filter can be designed by allowing the electrical signals of certain frequencies to pass through it depending upon their type and blocking the unwanted or undesired frequencies, which can be "low pass", "high pass", "band pass", "band reject" and "all pass" filter. "Current-mode", "voltage-mode", "trans-conductancemode" and "trans-resistance-mode filters" are various available modes of the filter operation [9]. Multifunction filter is the one that is capable of performing two or more types of filtering functions whereas universal filter is the one that can perform all five types of filtering functions. Further according to number of input and output terminals, filters are classified into four types which are "Single-Input-Single-Output" (SISO), "Single-Input-Multiple-Output" "Multiple-Input-Single-Output" (MISO) or "Multiple-Input-Multiple-Output" (SIMO), (MIMO) type.

#### 2.1 Comparison of various voltage-modes SIMO filters

Many literature surveys have been conducted for voltage-mode universal filters using active building block. A comparison has been done between the proposed SIMO filter and the other referenced VM SIMO filter as shown in Table 2. This table tabulates the advantages and disadvantages of the previously filters as well as the proposed filter. From the table it is noted that for second-order filtering function; we require at least two capacitors for quadratic equation. Filters in [21, 22, 24, 27, 31, 33, 35, 36, 39, 40, and 43] consist of floating passive elements in their circuit. Electronic tunability between natural frequency ( $\omega_0$ ) and Q-factor ( $Q_0$ )

9

can be achieved in filters [25, 26, 28-32, 36-39, 41, and 42]. All standard five filter responses can't be realized in these filters: [23, 25-27, 29, 31, 34, 35, 37-40, and 42].

| Refs.     | ABB           | No. of<br>ABB | No. of<br>R+C | All<br>grounded<br>passive<br>elements | Electronic<br>Tune | Orthogonal tune of Q and $\omega_0$ | input | Low<br>output<br>impedance | Five<br>filter<br>responses | Technology    |

|-----------|---------------|---------------|---------------|----------------------------------------|--------------------|-------------------------------------|-------|----------------------------|-----------------------------|---------------|

| 20        | DVCC          | 3             | 3+2           | Yes                                    | No                 | No                                  | Yes   | No                         | Yes                         | CMOS          |

| 21        | DVCC          | 3             | 3+2           | No                                     | No                 | Yes                                 | Yes   | No                         | Yes                         | CMOS          |

| 22        | DVCC          | 2             | 3+2           | No                                     | No                 | Yes                                 | No    | No                         | Yes                         | CMOS          |

| 23        | FDCCII        | 1             | 2+2           | Yes                                    | No                 | No                                  | Yes   | No                         | No                          | CMOS          |

| 24        | DDCC          | 3             | 2+2           | No                                     | No                 | No                                  | No    | No                         | Yes                         | CMOS          |

| 25        | DDCC &<br>OTA | 2             | 1+2           | Yes                                    | Yes                | No                                  | Yes   | No                         | No                          | CMOS          |

| 26        | OTA           | 8             | 0+2           | Yes                                    | Yes                | Yes                                 | Yes   | No                         | No                          | CMOS          |

| 27        | CFOA          | 1             | 3+2           | No                                     | No                 | Yes                                 | No    | LP                         | No                          | Commercial IC |

| 28        | DDCCTA        | 2             | 2+2           | Yes                                    | Yes                | No                                  | Yes   | No                         | Yes                         | CMOS          |

| 29        | OTA           | 8             | 0+2           | Yes                                    | Yes                | Yes                                 | Yes   | No                         | No                          | CMOS          |

| 30        | DDCCTA        | 3             | 0+2           | Yes                                    | Yes                | No                                  | Yes   | AP                         | Yes                         | CMOS          |

| 31        | CCCCTA        | 1             | 1+3           | No                                     | Yes                | Yes                                 | No    | No                         | No                          | BJT           |

| 32        | DDCCTA        | 2             | 2+2           | Yes                                    | Yes                | No                                  | Yes   | AP                         | Yes                         | CMOS          |

| 33        | FDCCII        | 1             | 3+2           | No                                     | No                 | No                                  | No    | No                         | Yes                         | CMOS          |

| 34        | DVCC          | 4             | 5+2           | Yes                                    | No                 | Yes                                 | Yes   | No                         | No                          | CMOS          |

| 35        | DVCC          | 2             | 2+3           | No                                     | No                 | No                                  | No    | No                         | No                          | CMOS          |

| 36        | DDCCTA        | 2             | 2+2           | No                                     | Yes                | Yes                                 | Yes   | No                         | Yes                         | CMOS          |

| 37        | VD-DIBA       | 2             | 0+2           | Yes                                    | Yes                | No                                  | Yes   | HP                         | No                          | Commercial IC |

| 38        | VDCC          | 1             | 2+2           | Yes                                    | Yes                | Yes                                 | No    | No                         | No                          | CMOS          |

| 39        | VDCC          | 1             | 2+2           | No                                     | Yes                | Yes                                 | No    | No                         | No                          | BJT           |

| 40        | CCII          | 2             | 3+2           | No                                     | No                 | No                                  | Yes   | No                         | No                          | CMOS          |

| 41        | DDCCTA        | 2             | 3+2           | Yes                                    | Yes                | Yes                                 | Yes   | AP                         | Yes                         | CMOS          |

| 42        | VDTA          | 1             | 0+2           | Yes                                    | Yes                | No                                  | Yes   | No                         | No                          | CMOS          |

| 43        | CCII          | 4             | 5+2           | No                                     | No                 | Yes                                 | Yes   | No                         | Yes                         | Commercial IC |

| This work | VDDDA         | 3             | 1+2           | Yes                                    | Yes                | Yes                                 | Yes   | HP,AP,<br>BS               | Yes                         | CMOS          |

Table 2 Comparison of different VM SIMO filters

Those circuits that can't provide high input impedance are [22, 24, 27, 31, 33, 35, 38, and 39]. The proposed SIMO filter can provide low output impedance for HP, BS and AP filter. The natural frequency and Q-factor can be orthogonally tuneable in filters [21, 22, 26, 27, 29, 31, 34, 36, 38, 39, 41, and 43]. The circuits which have commercialised IC are [27, 37, and 43].

#### 2.2 Comparison of various voltage-mode MISO filters

Many literature surveys have been conducted and numerous designing techniques have been developed for voltage-mode universal filters using active building block. A comparison has been done between the proposed MISO filter and the other referenced voltage-mode MISO filter as shown in Table 3. This table tabulates the advantages and disadvantages of the previously filters as well as the proposed filter.

From the table 3, it is noted that for second-order filtering function; we require at least two capacitors for a quadratic equation. Filters in [44-46, 48, 50, 52, 53, 56-58] consist of floating passive elements in their circuit. Electronic tunability between natural frequency ( $\omega_0$ ) and Q-factor ( $Q_0$ ) can be achieved in filters [46, 48, 51-53, 55, 57-59]. All standard five filter responses can be realized in all surveyed filters. Those circuits that can't provide high input impedance are [45, 47, 48, 50, 52, 53, 55-58]. The filters that can provide low output impedance are [47, 49, 50, 56, and 59]. The mentioned voltage-mode MISO filters in [44, 45, 50, 53-55] require matching condition between passive elements. Also the circuits in [44-46, 48, 53, and 58] need inverting input signals for filter responses.

| Refere<br>nce | ABB           | No. of<br>ABB | No. of<br>R+C | All<br>grounded<br>passive<br>elements | Electronic<br>Tune | Matching<br>condition | High<br>input<br>impedanc<br>e | Low<br>output<br>impedance | Inverting<br>input |

|---------------|---------------|---------------|---------------|----------------------------------------|--------------------|-----------------------|--------------------------------|----------------------------|--------------------|

| 44            | CCII          | 3             | 2+2           | No                                     | No                 | Yes                   | Yes                            | No                         | Yes                |

| 45            | CFA           | 1             | 3+2           | No                                     | No                 | Yes                   | No                             | No                         | Yes                |

| 46            | OTA &<br>CCII | 3             | 0+2           | No                                     | Yes                | No                    | Yes                            | No                         | Yes                |

| 47            | DDCC          | 2             | 2+2           | Yes                                    | No                 | No                    | No                             | Yes                        | No                 |

| 48            | OTA           | 2             | 0+2           | No                                     | Yes                | No                    | No                             | No                         | Yes                |

| 49            | DDCC          | 3             | 2+2           | Yes                                    | No                 | No                    | Yes                            | Yes                        | No                 |

| 50            | OTRA          | 1             | 4+4           | No                                     | No                 | Yes                   | No                             | Yes                        | No                 |

| 51            | OTA           | 6             | 0+2           | Yes                                    | Yes                | No                    | Yes                            | No                         | No                 |

| 52            | CCTA          | 1             | 2+2           | No                                     | Yes                | No                    | No                             | No                         | No                 |

| 53            | DVCC          | 1             | 2+2           | No                                     | Yes                | Yes                   | No                             | No                         | Yes                |

| 54            | DVCC          | 3             | 4+2           | Yes                                    | No                 | Yes                   | Yes                            | No                         | No                 |

| 55            | VDTA          | 1             | 0+2           | Yes                                    | Yes                | Yes                   | No                             | No                         | No                 |

| 56            | CDBA          | 2             | 4+2           | No                                     | No                 | No                    | No                             | Yes                        | No                 |

| 57            | VD-DIBA       | 1             | 1+2           | No                                     | Yes                | No                    | No                             | No                         | No                 |

| 58            | VDDDA         | 1             | 2+2           | No                                     | Yes                | No                    | No                             | No                         | Yes                |

| 59            | VDDDA         | 2             | 0+2           | Yes                                    | Yes                | No                    | Yes                            | Yes                        | No                 |

| This<br>work  | VDDDA         | 1             | 1+2           | No                                     | Yes                | Yes                   | LP                             | No                         | Yes                |

## Table 3 Comparison of different VM MISO filters

## CHAPTER 3

## **CIRCUIT DESIGN**

Usually designers use the tactics of designing the electronic circuits and filters with active building block for design flexibility. The circuit realized by the active building block requires a minimum number of external passive elements which can be either grounded or floating components to get desired functionality. The VDDDA is one of such interesting active building block [5].

#### 3.1 VDDDA (Voltage Differencing Differential Difference Amplifier)

Voltage Differencing Differential Difference Amplifier (VDDDA) is one of the new versatile 'voltage differencing' active building block (ABB). It is a six terminal universal block to realize various amplifiers with less transistor count and constitute dynamic properties required for any real-time applications. Device's internal structure consists of operational transconductance amplifier (OTA) [11] followed by differential difference amplifier unit (DDA) [12], [13].

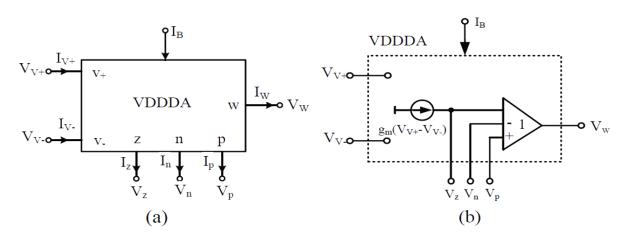

This building block consists of three addition/subtraction input voltage terminals where the transconductance ( $g_m$ ) of the block can be tuned electronically. The circuit symbol and its equivalent circuit are shown in Fig. 2. It has five input voltage ports, named as V<sub>+</sub>, V<sub>-</sub>, Z, P and N. The Z port is also the output current terminal and the W port is the output voltage terminal. Ideally, the input impedance at V<sub>+</sub>, V<sub>-</sub>, Z, P and N ports are high and the output impedance at W port is low. The voltage difference between V<sub>+</sub> and V<sub>-</sub> is transmitted as an output current I<sub>z</sub> via the transconductance ( $g_m$ ) which is tuneable too. The differential input voltages of V<sub>z</sub>, V<sub>n</sub> and V<sub>p</sub> constitutes output voltage V<sub>w</sub>.

Fig. 2 (a) VDDDA Circuit Symbol, (b) its Equivalent circuit [5]

The terminal characteristic equation for an ideal VDDDA can be modelled in form of matrix equation which is as follows:

Following are the equations derived from matrix equation,

$$I_{\nu+} = I_{\nu-} = I_n = I_p \tag{4}$$

$$I_{z} = g_{m} \left( V_{\nu_{+}} - V_{\nu_{-}} \right)$$

(5)

$$V_w = \beta_1 V_z - \beta_2 V_n + \beta_3 V_p \tag{6}$$

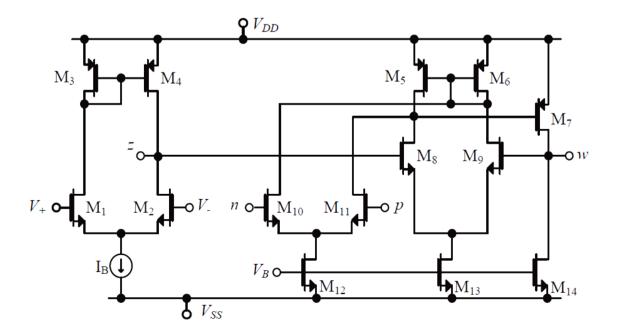

"where in ideal scenario, the currents at terminals  $v_+$ ,  $v_-$ , n and p are equal to zero from Eq. (4). In Eq. (5) and (6),  $g_m$  and  $\beta_i = 1 - \varepsilon_{vi}$  for i = 1, 2, 3 and so on, represent the transconductance and the non-ideal voltage gain of VDDDA respectively, and  $\varepsilon_{vi}$  which is less than one in magnitude denotes the voltage tracking error of block VDDDA. For ideal case,  $\beta_i$  is taken as unity gain." [5] The internal structure of VDDDA is implemented through CMOS which is shown in Fig. 3, where transistors  $M_1$ – $M_4$  realize the OTA unit and  $M_5$ – $M_{14}$  realizes the DDA unit. Note, we can utilize the same CMOS circuit structure effectively for implementation of VDBA [6] and VD-DIBA [7], if  $V_n$  and  $V_p$  or only  $V_p$  terminals of VDDDA are grounded.

Fig. 3 VDDDA implemented by CMOS technology [3]

The transconductance,  $g_m$  of the CMOS implemented VDDDA depends on both bias current (I<sub>B</sub>) and physical parameter of CMOS transistor, which is given by,

$$g_m = \sqrt{\mu C_{ox} \left(\frac{W}{L}\right)_{1,2} I_B} \tag{7}$$

"where,  $\mu$  is the mobility of the charge carrier for NMOS transistors i.e., M<sub>1</sub> and M<sub>2</sub> transistors, C<sub>ox</sub> is the gate oxide capacitance per unit area and W/L is the aspect ratio where W is channel width and L is channel length of transistor." [8]

#### 3.2 Proposed MISO Filter Description

Filter plays a pivotal role in analog signal processing. They are two major classifications of filter i.e., analog and digital filters. Compared to digital one, analog filters are quite faster, less expensive and have dynamic range in both frequency and amplitude. In numerous applications, analog filters are generally used such as noise reduction, graphic equalizers, videos signal enhancement for advanced systems. There are two major categories of analog filter circuits: Voltage-mode and current-mode. Voltage mode analog filter can be further classified into multi input single output (MISO) type and single input multi output (SIMO) type voltage filter. For the designing of MISO type voltage-mode universal filters in signal processing, designers are giving major importance due to following key features: (i) Realization of all standard five filter responses with same circuit topology on the basis of input ports used. (ii) Minimum use of active and passive components in circuit design (iii) Design simplicity and versatility that bring cost reduction to IC manufacturer [19].

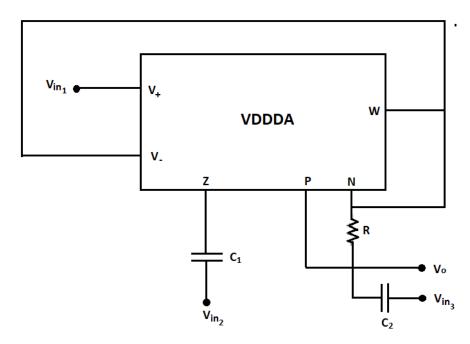

Fig. 4 shows the proposed second order voltage-mode MISO filter. The filter consists of single VDDDA, two capacitors and one resistor. It is noted that the proposed filter uses minimum number of active elements which is an attractive feature for integration. In future study circuit can further be modified by replacing the resistor with CMOS implemented electronic resistor. In this filter design, there are three input voltage signals, namely  $V_{in1}$ ,  $V_{in2}$ ,  $V_{in3}$  and  $V_0$  is the only output voltage. Considering an ideal VDDDA block, mathematical analysis of the MISO filter provides the output voltage, which is given as,

$$V_0 = \frac{s^2 V_{in3} + s \frac{(C_1 V_{in2} + C_2 Rgm V_{in3})}{2C_1 C_2 R} + \frac{gm V_{in1}}{2C_1 C_2 R}}{D(s)}$$

(8)

where,

$$D(s) = s^{2} + s \frac{(C_{1} + C_{2}Rg_{m})}{2C_{1}C_{2}R} + \frac{g_{m}}{2C_{1}C_{2}R}$$

(9)

16

Fig. 4 VDDDA based voltage-mode MISO filter

It is found from Eq. (8) that the proposed MISO filter has unity gain and if we want to achieve desired gain from the active filter, designers need to add voltage amplifies to get additional gain. From Eq. (8), we can get all standard five output filter responses by selecting the input voltage terminals ( $V_{in}$ ) accordingly and selection can be done digitally through below conditions,

- The second order LP response can be obtained if  $V_{in1} = V_{in}$  and  $V_{in2} = V_{in3} = 0$ .

- The second order HP response can be obtained if  $-V_{in2} = V_{in3} = V_{in}$  and  $V_{in1} = 0$ .

- The second order BP response can be obtained if  $V_{in2} = V_{in}$  and  $V_{in1} = V_{in3} = 0$ .

- The second order BS response can be obtained if  $V_{in1} = -V_{in2} = V_{in3} = V_{in}$ .

- The second order AP response can be obtained if  $V_{in1} = \frac{-V_{in2}}{3} = V_{in3} = V_{in3}$ .

17

For hardware implementation of HP and BS filter response, there is need of inverting unity gain amplifier and for AP filter implementation, inverting triple gain amplifier is required. From the characteristic equation Eq. (9), we can find the natural frequency and quality factor given by:

$$\omega_0 = \sqrt{\frac{g_m}{2C_1 C_2 R}} \tag{10}$$

$$Q_0 = \frac{\sqrt{2C_1 C_2 Rg_m}}{C_1 + C_2 Rg_m}$$

(11)

It is observed from Eqs (10) and (11) that the natural frequency ( $\omega_0$ ) and quality factor ( $Q_0$ ) both are tuned electronically through transconductance,  $g_m$ . And, for realizing HP, BS and AP filter responses; there is need of component matching condition ( $C_1 = C_2 R g_m$ ). The relative sensitivities of natural frequency and quality factor for the proposed filter can be calculated in Eq. (12),

$$S_{g_m}^{\omega_0} = \frac{1}{2}; \quad S_{C_1}^{\omega_0} = S_{C_2}^{\omega_0} = S_R^{\omega_0} = -\frac{1}{2};$$

$$S_{C_1}^{Q_0} = \frac{1}{2} - \frac{C_1}{C_1 + C_2 R g_m}; \quad S_{g_m}^{Q_0} = S_{C_2}^{Q_0} = S_R^{Q_0} = \frac{1}{2} - \frac{C_2 R g_m}{C_1 + C_2 R g_m}$$

(12)

It is observed that the magnitude of relative sensitivities is either equal to one or less than one.

## 3.3 Proposed high input impedance SIMO Filter Description

Fig. 5 VDDDA based voltage-mode SIMO filter

The benefits of SIMO filters are (i) we can apprehend low-pass, high-pass, band-pass, band-stop, and all-pass filter responses simultaneously without changing the circuit topology and input signal values, (ii) it plays an important role in the fields of electronic measurement, communication, auto control, and neural network, and (iii) it only requires single input supply voltage for all five filter responses. Fig. 5 shows the proposed voltage-mode universal SIMO filter. The filter consists of three VDDDAs, two grounded capacitors and one grounded resistor. It is noting that the proposed filter uses grounded and minimum number of active elements makes this an attractive feature for monolithic integration. It exhibits low output impedance for HP, BR and AP terminals. This proposed universal filter can provide six

filter responses simultaneously which are LP, HP, BR, AP and BP (BP<sub>1</sub> and BP<sub>2</sub>) with high input impedance. Considering an ideal VDDDA block, mathematical analysis of the SIMO filter provides the following output responses:

$$HP(s) = \frac{V_{05}}{V_{in}} = -\frac{s^2}{D(s)}$$

(13)

$$LP(s) = \frac{V_{06}}{V_{in}} = \frac{\frac{gm_1gm_3}{C_1C_2}}{D(s)}$$

(14)

$$BS(s) = \frac{V_{03}}{V_{in}} = -\frac{s^2 + \frac{g_{m_1}g_{m_3}}{c_1c_2}}{D(s)}$$

(15)

$$AP(s) = \frac{V_{01}}{V_{in}} = -\frac{\left[s^2 - s\frac{gm_1}{C_1} + \frac{gm_1gm_3}{C_1C_2}\right]}{D(s)}$$

(16)

$$BP_1(s) = \frac{V_{02}}{V_{in}} = \frac{s\frac{gm_1}{C_1}}{D(s)}$$

(17)

$$BP_2(s) = \frac{V_{04}}{V_{in}} = \frac{s\frac{gm_1gm_2R}{C_1}}{D(s)}$$

(18)

where,

$$D(s) = s^{2} + s \frac{g_{m_{1}}g_{m_{2}}R}{c_{1}} + \frac{g_{m_{1}}g_{m_{3}}}{c_{1}c_{2}}$$

(19)

From Eqs (13-19), it is found that all the filter responses have unity gain; it means that if a designer wants to use the filter for a real-time application, there is need of additional voltage amplifier to get some extra gain. Also, the characteristics equation provides the natural frequency and quality factor which are given as below:

$$\omega_0 = \sqrt{\frac{g_{m_1}g_{m_3}}{c_1 c_2}} \tag{20}$$

$$Q_0 = \frac{1}{g_{m_2}R} \sqrt{\frac{c_1 g_{m_3}}{c_2 g_{m_1}}}$$

(21)

20

It should be noted from Eqs (20) and (21) that the natural frequency  $(\omega_0)$  can be electronically tuned if  $g_{m_1}$  is equal to  $g_{m_3}$ , without affecting the quality factor. Also, the quality factor  $(Q_0)$  can be electronically tuned independently via  $g_{m_2}$ . Thus, both natural frequency and quality factor are orthogonal to each other. However, for realizing AP response, the proposed circuit needs component matching condition  $(g_{m_2}=1/R)$ .

The relative sensitivities of natural frequency and quality factor for the proposed filter can be calculated in Eq. (22),

$$S_{g_{m_1}}^{\omega_0} = S_{g_{m_3}}^{\omega_0} = \frac{1}{2}; \quad S_{C_1}^{\omega_0} = S_{C_2}^{\omega_0} = -\frac{1}{2};$$

$$S_{g_{m_2}}^{Q_0} = S_R^{Q_0} = -1; \quad S_{C_1}^{Q_0} = S_{g_{m_3}}^{Q_0} = \frac{1}{2}; \quad S_{C_2}^{Q_0} = S_{g_{m_1}}^{Q_0} = -\frac{1}{2}$$

(22)

#### 3.3.1 Analysis of non-ideal behaviour

Practically, the overall performances of the proposed SIMO filter are affected by the influences of voltage tracking error of VDDDA block. In this section, we will study and analyse these non-ideal characteristics of VDDDA which can be represented as following:

$$V_w = \beta_z V_z - \beta_n V_n + \beta_p V_p \tag{23}$$

"where in Eq. (23),  $\beta_z$ ,  $\beta_n$  and  $\beta_p$  represent the non-ideal voltage gain (or, voltage tracking error) of VDDDA from Z, N and P ports to W port, respectively and it is less than one in magnitude. For ideal case,  $\beta$  is taken as unity gain." The voltage filter responses for the non-ideal case are represented in Eqs (24-29):

$$LP^{*}(s) = \frac{V_{06}}{V_{in}} = \frac{\frac{g_{m_1}g_{m_3}\beta_{n_3}}{c_1c_2}}{D(s)}$$

(24)

$$HP^*(s) = \frac{V_{05}}{V_{in}} = -\frac{s^2 \beta_{n3}}{D(s)}$$

(25)

21

$$BS^{*}(s) = \frac{V_{03}}{V_{in}} = \frac{-\left[s^{2}\beta_{n2} + s\frac{gm_{1}gm_{2}R}{C_{1}}(\beta_{n2}\beta_{p3} - \beta_{z2}\beta_{n3}) + \frac{gm_{1}gm_{3}\beta_{n2}\beta_{z3}}{C_{1}C_{2}}\right]}{D(s)}$$

(26)

$$AP^{*}(s) = \frac{V_{01}}{V_{in}} = -\frac{\left(s^{2}\beta_{p1}\beta_{n3} - s\frac{gm_{1}\beta_{z1}\beta_{n3}}{C_{1}} + \frac{gm_{1}gm_{3}\beta_{n1}\beta_{n3}}{C_{1}C_{2}}\right)}{D(s)}$$

(27)

$$BP_1^*(s) = \frac{V_{02}}{V_{in}} = \frac{s\frac{gm_1\beta_{n3}}{c_1}}{D(s)}$$

(28)

$$BP_2^{*}(s) = \frac{V_{04}}{V_{in}} = \frac{s \frac{g m_1 g m_2 R \beta_{n3}}{C_1}}{D(s)}$$

(29)

where,

$$D^{*}(s) = s^{2} + s \frac{g_{m_{1}}g_{m_{2}}R\beta_{p_{3}}}{c_{1}} + \frac{g_{m_{1}}g_{m_{3}}\beta_{z_{3}}}{c_{1}c_{2}}$$

(30)

From Eq. (30), it is noted that the tracking error will also affect the natural frequency and the quality factor of the proposed filter. The non-ideal values of  $\omega_0$  and  $Q_0$  are given below,

$$\omega_0^* = \sqrt{\frac{g_{m_1}g_{m_3}\beta_{n_3}}{c_1 c_2}} \tag{31}$$

$$Q_0^* = \frac{1}{g_{m_2} R \beta_{p_3}} \sqrt{\frac{C_1 g_{m_3} \beta_{n_3}}{C_2 g_{m_1}}}$$

(32)

## **CHAPTER 4**

## SIMULATION RESULTS

The theoretical study of CMOS implemented VDDDA structure in Fig. 3 and the proposed filters as shown in Fig. 4 and 5, have been verified by SYMICA DE simulations. The transistors in the circuit design are modelled by the TSMC 0.18 µm level-7 CMOS process parameters ( $V_{\text{THn}} = 0.3725 \text{ V}$ ,  $\mu_n = 259.5304 \text{ cm}^2/(\text{V} \cdot \text{s})$ ,  $V_{\text{THp}} = -0.3948 \text{ V}$ ,  $\mu_p = 109.9762 \text{ cm}^2/(\text{V} \cdot \text{s})$ ,  $T_{\text{ox}} = 4.1 \text{ nm}$ ) [60] with ±0.9 V supply voltages and  $V_B = -0.35 \text{ V}$ . From Table 4, aspect ratio of MOS transistors are listed.

The functionality of CMOS implemented VDDDA is shown in Fig. 6 which is verified through SYMICA DE simulation using  $0.18 \,\mu m$  TSMC CMOS parameter.

Fig. 6 Schematic of CMOS implemented VDDDA

| NMOS transistors                                                                   | W(μm) / L(μm)                    |

|------------------------------------------------------------------------------------|----------------------------------|

| $ \begin{array}{c} M_{1}, M_{2} \\ M_{8} - M_{11} \\ M_{12} - M_{14} \end{array} $ | 9/1.08<br>0.72/1.08<br>2.16/1.08 |

| PMOS transistors                                                                   | W(μm) / L(μm)                    |

| M <sub>3</sub> , M <sub>4</sub><br>M <sub>5</sub> – M <sub>7</sub>                 | 3.96/1.08<br>3.6/0.18            |

**Table 4** Aspect ratios of MOS transistors [5]

## 4.1 Analyses of VDDDA

The performance of the VDDDA was tested and depicted in Figs. 7 to 11 in which relations between the output and input terminals are verified. From the DC analyses, it is noted that the input voltage terminals have maximum voltage equal to  $\pm 200$  mV. The bias current is selected as I<sub>B</sub> = 50 µA, which results in  $g_m$  approximately equal to 300 µA/V. Subsequently, the obtained gains  $\beta_i$  of voltage transfers V<sub>w</sub>/ {V<sub>z</sub>, V<sub>n</sub>, V<sub>p</sub>} are equal to 0.997.

Fig. 7 DC analysis of VDDDA (V<sub>w</sub> vs V<sub>z</sub>)

Fig. 9 DC analysis of VDDDA ( $V_w vs V_n$ )

From Eq. (6) we can see that  $V_w$  is proportional to  $V_p$  and  $V_n$  for an ideal VDDDA, i.e.  $\beta_i = 1$  and above graphs show their dependence on input voltages.

Fig. 12 Schematic of proposed MISO filter using VDDDA

The functionality of CMOS implemented proposed multifunction MISO filter as shown in Fig. 12, is verified through SYMICA DE simulations with model library of 0.18  $\mu$ m TSMC CMOS parameter file [60] at ±0.9V supply voltages. The aspect ratio of the transistors is tabulated in Table 4. The component's values used in filter are as follows:  $C_1 = C_2 = 30 \text{ pF}$  and  $R = 3.3k\Omega$  and the bias current I<sub>B</sub> is set to 50  $\mu$ A. Figs. (13-15) provide the gain responses of LP, HP and BP functions and Fig. 16 and 17 provide the gain and phase responses of BS and AP functions of the proposed MISO filter. The simulated natural frequency is 1.106 MHz and the quality factor is 0.707. But the theoretical natural frequency in Eq. (10) is 1.131 MHz with the same value of passive components and bias current. This deviation is due to voltage tracking error or non-ideal nature of VDDDA. The transient response of BP function is shown in Fig. 18. In this experiment, the input is a sinusoidal signal with 180 mV and 1 MHz frequency was fed into the proposed filter.

Fig. 16 Gain and phase response of BS

Fig. 18 Transient response of BP function

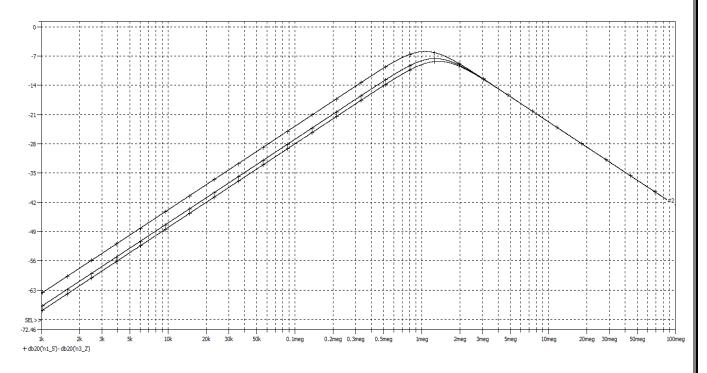

The gain responses of BP function for different  $I_B$  are shown in Fig. 19, where  $C_1 = C_2 = 30 \text{ pF}$  and  $I_B$  is equal to 50  $\mu$ A, 100  $\mu$ A & 150  $\mu$ A and the corresponding simulated natural frequencies are 1.106 MHz, 1.272 MHz and 1.355 MHz respectively. This is confirmed from Eq. (10) and (11) that the natural frequency can be electronically tuned via  $I_B$ .

Fig. 19 BP responses for different values of  $I_B$

## 4.3 Analyses of Proposed VM SIMO Universal filter

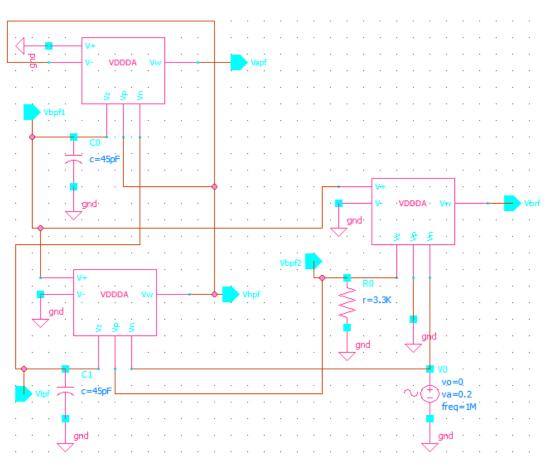

Fig. 20 Schematic of proposed SIMO filter using VDDDA

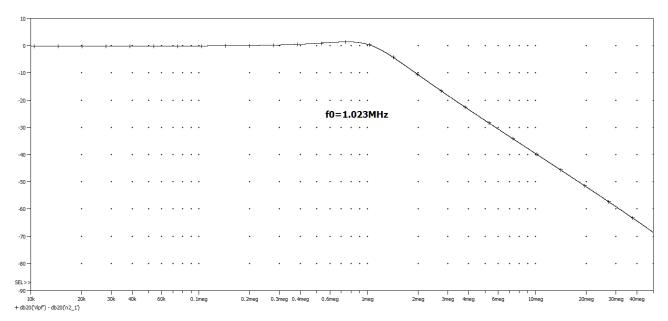

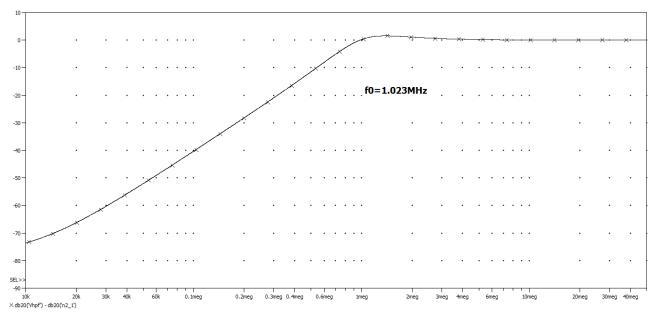

The functionality of CMOS implemented proposed universal SIMO filter as shown in Fig. 20, is verified through SYMICA DE simulations with model library of 0.18  $\mu$ m TSMC CMOS parameter file [60] at ±0.9V supply voltages. The aspect ratios of MOS transistors are listed in Table 4. The values of the components used in filter are as follows: C<sub>1</sub> = C<sub>2</sub> = 45 pF, R = 3.3k $\Omega$  and I<sub>B1</sub> = I<sub>B2</sub> = I<sub>B3</sub> = 50  $\mu$ A. Figs. (21-24) provide the gain responses of LP, HP, BP<sub>1</sub> and BP<sub>2</sub> functions and Fig. 25 and 26 provide the gain and phase responses of BR and AP functions of the proposed SIMO filter respectively. The simulated natural frequency is 1.023 MHz and the quality factor is unity. But the theoretical natural frequency in Eq. (20) is 1.061 MHz with the same value of passive components and bias current. This deviation is due to the voltage tracking error or non-ideal nature of VDDDA. The proposed circuit is a universal filter means that it can simultaneously provide low-pass, high-pass, band-pass, band-reject/notch and

all-pass functions without switching the circuit topology. The gain responses of BP<sub>2</sub> function for different I<sub>B2</sub> are shown in Fig. 27, where  $C_1 = C_2 = 45$  pF and I<sub>B2</sub> is equal to 25 µA, 50 µA & 100 µA and the corresponding values of quality factor ( $Q_0$ ) are 1.414, 1 and 0.707 respectively. It is confirmed from Eq. (21) that the quality factor can be electronically tuned via  $g_{m2}$  by changing I<sub>B2</sub> without altering natural frequency. To get high  $Q_0$ , we can set the value of I<sub>B2</sub> as low as possible.

Fig. 21 Gain response of LP

Fig. 22 Gain response of HP

Fig. 24 Gain response of BP<sub>2</sub>

34

Fig. 26 Gain and phase response of AP

Fig. 27 BP<sub>2</sub> responses for different values of  $I_{B2}$

In order to control the natural frequency ( $\omega_0$ ) without affecting the *Qo*, we can adjust C<sub>1</sub> and C<sub>2</sub> simultaneously. The BP<sub>2</sub> gain responses in Fig.28, by varying C<sub>1</sub> = C<sub>2</sub> with different values of capacitance 35 pF, 45 pF and 55 pF. The simulated natural frequencies are 0.825 MHz, 1.023 MHz and 1.289 MHz, respectively.

**Fig. 28** BP<sub>2</sub> responses for different values of C<sub>1</sub>, C2

The transient response of  $BP_2$  function is shown in Fig. 29. In this experiment, the input is a sinusoidal signal with amplitude of 180 mV and 1 MHz frequency was fed into the proposed filter.

## CHAPTER 5

## **CONCLUSION AND FUTURE SCOPE**

In this report, two voltage-mode second order filters using VDDDA as an active building block have been proposed along with the study of the VDDDA block. First is a voltage-mode multifunction filter with MISO configuration and the other is voltage-mode Universal filter with SIMO type circuit topology. Following are the advantages of proposed MISO filter: (i) The proposed filter can provide all five standard functions: Low-Pass (LP), High-Pass (HP), Band-Pass (BP), Band-Stop (BS) and All-Pass (AP) responses with digitally terminal switching of input ports, (ii) the natural frequency and the quality factor both can be electronically controllable and tuneable, (iii) it consists of single VDDDA, two capacitors and one resistor and (iv) the input voltage terminal for V<sub>in1</sub> is high impedance.

The advantages of proposed SIMO filter are as follows: Firstly, the filter circuit consists of three VDDDAs, two grounded capacitors and one grounded resistor which is an attractive feature for IC implementation. Secondly, it can realize low-pass, high-pass, band-pass, band-stop, and all-pass filter responses simultaneously without changing circuit topology. Thirdly, it has high input impedance and exhibits low output impedance for HP, BR and AP terminals. Finally, the natural frequency and the quality factor both are electronically and orthogonally controllable and tuneable. Simulation results verified the theoretical concepts and validity of synthesis. However, with slight modification in future, both MISO and SIMO filter can be used for the implementation of the voltage-mode quadrature oscillator, VDDDA based voltage-mode shadow filter and many more applications.

## **REFERENCES**

- A. S. Sedra and K. C. Smith, "Microelectronic circuits", Florida: Holt, Rinehart and Winston, 1991.

- [2] M. E. Van Valkenburg, "Analog Filter Design", Holt, Rinehart & Winston, 1982.

- [3] G. Ferri, N.C. Guerrini, "Low-Voltage Low-Power CMOS Current Conveyors", Cluwer Academic Publishers, 2003.

- [4] C. Toumazou, F.J. Lidgey, D.G. Haigh, "Analogue IC Design: The current mode approach". IEE Circuits and Systems Series 2. Peter Peregrinus Ltd., 1990.

- [5] N. Herensar, R. Sotner, B. Metin, J. Koton and K. Vrba, "VDDDA New 'voltage differencing' device for analog signal processing," Proceeding of the 8th International Conference on Electrical and Electronics Engineering, pp. 17-20, 2013.

- [6] D. Biolek, R. Senani, V. Biolkova, and Z. Kolka, "Active elements for analog signal processing: classification, review, and new proposals", Radioengineering, vol. 17, no. 4, pp. 15–32, 2008.

- [7] D. Biolek and V. Biolkova, "First-order voltage-mode all pass filter employing one active element and one grounded capacitor", Analog Integr. Circ. Sig. Process., vol. 65, pp. 123–129, 2010.

- [8] S. Tuntrakool, M. Kumgern, "A voltage-mode quadrature sinusoidal oscillator using VDDDAs," 2015 International Symposium on Multimedia and Communication Technology, September 23 – 25, 2015, Classic Kameo Hotel, Ayutthaya, Thailand, pp. 134-137.

- [9] R. Raut and M. N. S. Swamy, "Modern Analog Filter Analysis and Design: A Practical Approach", Copyright © 2010 WILEY-VCH Verlag GmbH & Co. KGaA, Weinheim.

- [10] K. L. Pushkar, D. R. Bhaskar, and D. Prasad, "Single resistance-controlled sinusoidal

oscillator using single VD-DIBA", Active and Passive Electronic Components, vol. 2013, Article ID 971936, 5 pages, 2013.

- [11] R. L. Geiger and E. Sanchez-Sinencio, "Active filter design using operational transconductance amplifiers: A tutorial", IEEE Circuits Devices Mag., vol. 1, pp. 20– 32, 1985.

- [12] E. Sackinger and W. Guggenbiihl, "A versatile building block: CMOS differential difference amplifier", IEEE J. Solid-State Circuits, vol. 22, pp. 287–294, 1987.

- [13] W. Chiu, S.-I. Liu, H.-W. Tsao, and J.-J. Chen, "CMOS differential difference current conveyors and their applications", IEE Proc. Circuits Devices Syst., vol. 143, pp. 91– 96, 1996.

- [14] J. Koton, N. Herensar, K. Vrba and B. Metin," The VDDDA in multifunction filter with mutually independent Q and  $\omega_0$  control feature," 2013, 8th International Conference on Electrical and Electronics Engineering (ELECO), 2013, pp. 53-56.

- [15] P. Supavarasuwat, M. Kumngern, S. Sangyaem, W. Jaikla, and F. Khateb, "Cascadable independently and electronically tunable voltage-mode universal filter with grounded passive components," AEU - International Journal of Electronics and Communications, vol. 84, pp. 290-299, 2018.

- [16] S. Minaei and E. Yuce, "Novel voltage-mode all-pass filter based on using DVCCs", Circuits System Signal Process, vol. 29, pp. 391–402, 2010.

- [17] N. Herencsar, A. Lahiri, K. Vrba, and J. Koton, "An electronically tunable currentmode quadrature oscillator using PCAs", Int. J. Electron., vol. 99, no. 5, pp. 609–621, 2012.

- [18] F. Kacar, A. Yesil, and A. Noori, "New CMOS realization of voltage differencing buffered amplifier and its biquad filter applications", Radio engineering, vol. 21, no. 1, pp. 333–339, 2012.

- [19] A. Ranjan and S. K. Paul, "Voltage Mode Universal Biquad Using CCCII," Active

and Passive Electronic Components, vol. 2011, Article ID 439052, 2011.

- [20] S. Minaei & E. Yuce, Circuits System Signal Process, 29 (2010) 295.

- [21] W. Y. Chiu, J. W. Horng, H. Lee & C. C. Huang, IEEE International Symposium on Electronic Design, Test and Applications, Ho Chi Minh City, Vietnam, 2010.

- [22] J. W. Horng, Analog Integr Circuits Signal Process, 62 (2010) 407.

- [23] W. Y. Chiu & J. W. Horng, Indian J Eng Mater Sci, 18 (2011) 97.

- [24] W. Y. Chiu, J. W. Horng, Y. S. Guo & C. Y. Tseng, DDCCs based voltage-mode one input five outputs biquadratic filter with high input impedance, International Symposium on Integrated Circuits, Singapore, 2011.

- [25] N. Udorn, D. Duangmalai & A. Noppakarn, High input impedance current controlled voltage-mode universal filter using DDCC and OTA, IEEE International Conference on Vehicular Electronics and Safety (ICVES), 2011.

- [26] M. Kumngern, P. Suwanjan & K. Dejhan, Electronically tunable voltage-mode SIMO OTA-C universal biquad filter, Asia-Pacific Conference on Communications (APCC2011), 2011.

- [27] J. W. Horng, C. L. Hou, W. S. Huang & D. Y. Yang, Circuits System, 2 (2011) 60.

- [28] O. Channumsin, T. Pukkalanun & W. Tangsrirat, Microelectron J, 43 (2012) 555.

- [29] M. Kumngern, P. Suwanjan & K. Dejhan, Int J Electron, 100 (2013) 1118.

- [30] W. Tangsrirat, O. Channumsim & T. Pukkalanun, Microelectron J, 44 (2013) 210.

- [31] S. V. Singh, S. Maheshwari, R. S. Tomar & D. S. Chauhan, Single input four output voltage-mode biquad filter with electronic tuning, International Conference on Multimedia Signal Processing and Communication Technologies, 2013.

- [32] H. P. Chen, IET Circuits Dev System, 8 (2014) 280.

[33] J. Mohan, B. Chaturvedi & S. Maheshwari, Adv Electr Eng, (2014) Article ID 514019.

- [34] M. U. Ismail & B. Arif, Single input multi output digitally reconfigurable biquadratic analog filter, International Conference on Systems Informatics, Modelling and Simulation, 2014.

- [35] H. P. Chen, Y. L. Chiu, C. K. Chung & C. C. Chou, Voltage-mode multifunction filter with single input and three outputs based on single plus-type DVCC, International Conference on Information Science, Electronics and Electrical Engineering, (2014) 1838-1841.

- [36] H. P. Chen, S. F. Wang, W. Y. Huang & M. Y. Hsieh, IEICE Electron Express, 11 (2014) 20140234.

- [37] W. Jaikla, D. Biolek, S. Siripongdee & J. Bajer, Radioengineering, 14(3) (2014) 914.

- [38] F. Kacar, A. Yesil & K. Gurkan, Indian J Pure Appl Phys, 53 (2015) 341.

- [39] M. Sagbas, U. E. Ayten, M. Koksal & N. Herencsar, Electronically tunable universal biquad using a single active component, International Conference on Telecommunications and Signal Processing (TSP), 2015.

- [40] F. Yucel & E. Yuce, J Circuits Syst Comput, 24(4) (2015), 1550047.

- [41] H. P. Chen & S. P. Wang, AEU Int J Electron Commun, 70 (2016) 491.

- [42] E. Alaybeyoglu & H. Kuntman, Analog Integr Circuits Signal Process, 89 (2016) 675.

- [43] J. W. Horng & W. Y. Chiu, Indian J Pure Appl Phys, 54 (2016) 557.

- [44] J. W. Horng. High-input impedance voltage-mode universal biquadratic filter using three plus-type CCIIs. IEEE Trans Circuits Syst II 2001; 48(10):996–7.

- [45] J. W. Horng, C. K. Chang, J. M. Chu. Voltage-mode universal biquadratic filter using single current-feedback amplifier. IEICE Trans Fundam 2002; 85:1970–3.

- [46] J. W. Horng. High input impedance voltage-mode universal biquadratic filter using two OTAs and one CCII. Int J Electron 2003; 90(3):153–7.

- [47] C. M. Chang, H. P. Chen. Universal capacitor-grounded voltage-mode filter with three inputs and a single output. Int J Electron 2003; 90(6):401–6.

- [48] J. W. Horng. Voltage-mode universal biquadratic filter using two OTAs and two capacitors. IEICE Trans Fundam 2003; 86A (2):411–3.

- [49] J. W. Horng. High-input and low-output impedance voltage-mode universal biquadratic filter using DDCCs. IEEE Trans Circuits Syst II 2007; 54(8):649–52.

- [50] S. Kılınc, A. Ü. Keskin, U. Cam. Cascadable voltage-mode multifunction biquad employing single OTRA. Frequenz 2007; 61:84–6.

- [51] M. Kumngern, M. Somdunyakanok, P. Prommee. High-input impedance voltagemode multifunction filter with three-Input single-output based on simple CMOS OTAs. Int Symp Commun Inf Technol 2008:426–31.

- [52] N. Herencsar, J. Koton, K. Vrba. Single CCTA-based universal biquadratic filters employing minimum components. Int J Comput Electr Eng 2009;1(3):309–12.

- [53] W. Tangsrirat, O. Channumsin. Voltage-mode multifunctional biquadratic filter using single DVCC and minimum number of passive elements. Indian J Pure Appl Phys 2011; 49:703–7.

- [54] J. W. Horng, C. H. Hsu, C. Y. Tseng. High input impedance voltage-mode universal biquadratic filters with three inputs using three CCs and grounding capacitors. Radioengineering 2012; 21(1):290–6.

- [55] J. Satansup, W. Tangsrirat. Single VDTA-based voltage-mode electronically tunable universal filter. In: The 27th International Technical Conference on Circuits Systems, Computers and Communications. 2012.

- [56] J. K. Pathak, A. K. Singh, R. Senani. New voltage mode universal filters using only

two CDBAs. ISRN Electron 2013 [Article ID 987867].

- [57] K. L. Pushkar, D. R. Bhaskar, D. Prasad. A new MISO-type voltage-mode universal biquad using single VD-DIBA. ISRN Electron 2013 [Article ID 478213].

- [58] A. Chaichana, S. Sangyaem, W. Jaikla. Multifunction voltage-mode filter using single voltage differencing differential difference amplifier. In: 3rd international conference on mechatronics and mechanical engineering; 2016.

- [59] S. Sangyaem, S. Siripongdee, W. Jaikla, F. Khateb. Five-inputs single-output voltage mode universal filter with high input and low output impedance using VDDDAs. Optik 2017; 128:14–25.

- [60] TSMC 0.18 μm level-7 SCN018 CMOS technology parameters [online]: <u>ftp://ftp.isi.edu/pub/mosis/</u> vendors/tsmc-018/t44e lo epi-params.txt.