### POWER FACTOR CORRECTION OF VARIOUS CONVERTERS FOR EV CHARGING APPLICATIONS

### DISSERTATION/THESIS

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

### MASTER OF TECHNOLOGY IN POWER ELECTRONICS AND SYSTEMS

Submitted by:

# **RISHITA SHUKLA**

# 2K20/PES/17

Under the supervision of

Mr. KRISHNA DUTT (Assistant Professor, EED, DTU)

## DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

2022

# DECLARATION

I, **Rishita Shukla**, Roll No. 2K20/PES/17 student of M.Tech (Power Electronics and Systems), hereby declare that the project Dissertation titled **"Power Factor Correction of DC-DC Converters for EV Charging Applications"** which is submitted by me to the Department of Electrical Engineering Department, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is original and not copied from any source without proper citation. This work has not previously submitted for the award of any Degree, Diploma.

The matter presented in this report has not been submitted by me for the award of any other degree of this or any other Institute/University. The work has been accepted and presented in peer reviewed Scopus indexed conference with the following details:

|    | Title of the Paper:                     | PFC of SI-SEPIC and Flyback                                   |  |  |  |  |

|----|-----------------------------------------|---------------------------------------------------------------|--|--|--|--|

|    |                                         | Converter for EV Applications                                 |  |  |  |  |

|    | Author names:                           | <sup>1</sup> Rishita Shukla and <sup>2</sup> Mr. Krishna Dutt |  |  |  |  |

|    | Name of Conference:                     | 7 <sup>th</sup> International Conference for                  |  |  |  |  |

|    |                                         | Convergence in Technology (I2CT)                              |  |  |  |  |

|    | Name of Organizer:                      | Global Institute of Business Management                       |  |  |  |  |

|    |                                         | & Decision Sciences (GIBDS), Pune,                            |  |  |  |  |

| 1. |                                         | India and IEEE Bombay Section                                 |  |  |  |  |

|    | Conference Date with Venue:             | April 7 <sup>th</sup> – April 9 <sup>th,</sup> 2022           |  |  |  |  |

|    |                                         | Virtual Mode                                                  |  |  |  |  |

|    | Have you registered for the Conference? | Yes                                                           |  |  |  |  |

|    | Status of the paper:                    | Accepted and Presented                                        |  |  |  |  |

|    | Date of Communication:                  | 23 <sup>rd</sup> November, 2021                               |  |  |  |  |

|    | Date of Acceptance:                     | 6 <sup>th</sup> December, 2021                                |  |  |  |  |

|    | IEEE Xplore                             |                                                               |  |  |  |  |

|    | Title of the Paper:                                                      | A Modified Zeta Converter Fed with                  |  |  |  |  |

|----|--------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|

|    |                                                                          | HB-LLC Resonant Converter for                       |  |  |  |  |

|    |                                                                          | Power Factor Correction                             |  |  |  |  |

|    | Author names: <sup>1</sup> Rishita Shukla and <sup>2</sup> Mr. Krishna I |                                                     |  |  |  |  |

|    | Name of Conference:                                                      | IEEE Region 10 Symposium                            |  |  |  |  |

|    |                                                                          | (TENSYMP)                                           |  |  |  |  |

|    | Name of Organizer:                                                       | IIT Bombay and IEEE Bombay Section                  |  |  |  |  |

| 2. | Conference Date with Venue:                                              | July 01 <sup>st</sup> – July 03 <sup>rd,</sup> 2022 |  |  |  |  |

|    |                                                                          | Virtual Mode                                        |  |  |  |  |

|    | Have you registered for the Conference?                                  | Yes                                                 |  |  |  |  |

|    |                                                                          |                                                     |  |  |  |  |

|    | Status of the paper:                                                     | Accepted                                            |  |  |  |  |

|    | Date of Communication:                                                   | 27 <sup>th</sup> February, 2020                     |  |  |  |  |

|    | Date of Acceptance:                                                      | 12 <sup>th</sup> April, 2022                        |  |  |  |  |

|    | Publication Platform:                                                    | IEEE Xplore                                         |  |  |  |  |

*Place: Delhi Technological University, Delhi Date:* 31/05/2022

( Rishita Shukla)

2K20/PES/17

DEPARTMENT OF ELECTRICAL ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

## **SUPERVISOR'S CERTIFICATE**

This is to certify that the work presented in this dissertation "**Power Factor Correction of Various Converter for EV Battery Charging Applications**" by Rishita Shukla, Roll No. 2K20/PES/17, is a record of original research carried out by her under my supervision and guidance in partial fulfilment of the requirements for the degree of Master of Technology (Power Electronics and Systems Engineering). Neither this dissertation nor any part of it has been submitted earlier for any degree or diploma to any institute or university in India or abroad.

Supervisor's Signature

Mr. Krishna Dutt Assistant Professor Electrical Engineering Department Delhi Technological University (Formerly known as Delhi College of Engineering)

Date: 31-05-2022 Place: Delhi

# DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY

## ACKNOWLEDGEMENT

I take this opportunity to express my deepest gratitude and appreciation to my project supervisor **Mr. Krishna Dutt**, Assistant Professor, Delhi Technological university and Head of Department **Prof. (Dr.) Uma Nangia**, Delhi Technological university for their everlasting support.

I am thankful to him for suggesting the various aspects of the problem and project, rendering help during fabrication of work and rendering encouragement during the various phases of work.

I would like to thank my friends and all those who have helped me and encouraged me in completion of my dissertation in time.

Finally, I thank my parents for their moral support and confidence which they showed in me to pursue M. Tech at the advanced stage of my academic career.

Rishita Shukla 2K20/PES/17 M.Tech (Power Electronics and Systems) Department of Electrical Engineering, D.T.U, DELHI (2020-22)

**Place: DELHI**

Date: 31/05/2022

### ABSTRACT

This work presents the modelling and design of two different EV Chargers. The proposed EV chargers consists of two-stage power conversion. Initially, DBR (Diode Bridge Rectifier) is connected for AC-DC Conversion which is followed by LC Filter to damp out the third order harmonics. The first stage consists of Power factor correction circuit using various DC-DC converters like boost, buck and buck-boost derived converter and the second stage consist of DC-DC stage for providing isolation of the grid and the charging port. Total research is done into two sections as mentioned below.

The first section consists of power factor correction using SI-SEPIC Converter cascaded with Flyback converter. It comprises of two stage EV Charger where initial stage consists of SI-SEPIC converter, which inherently provides the power factor correction of the EV charger at the source, and the later consists of Flyback converter. Collective combination of these two converters for the EV charger results for the operation of converter at reduced duty ratio resulting which efficiency of the converter is increased. This work mainly focuses on designing the components of the converter and power factor correction using PWM and SPWM controller techniques in MATLAB environment. The SEPIC Converter has a disadvantage of having more ripple in the output current so, modified Zeta converter is used which provides better dynamic response in DCM and it also provides less ripple in the output current.

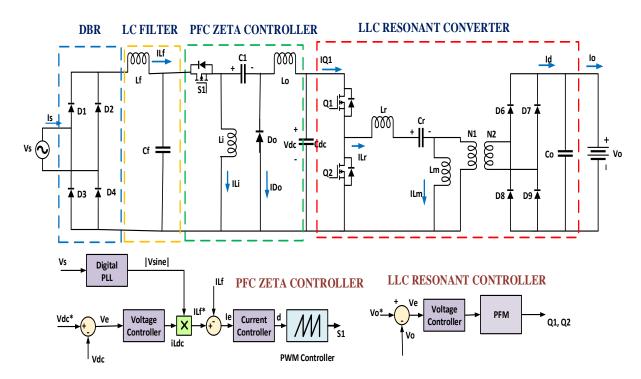

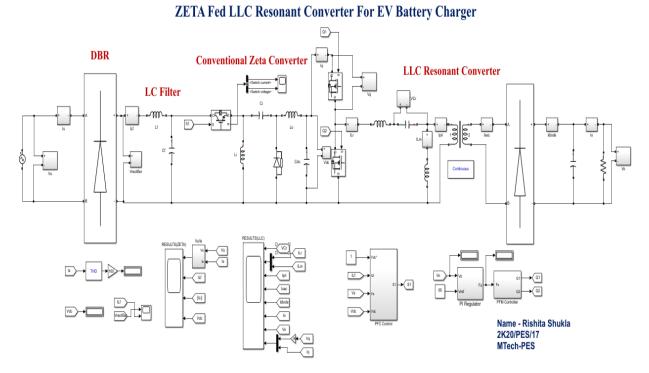

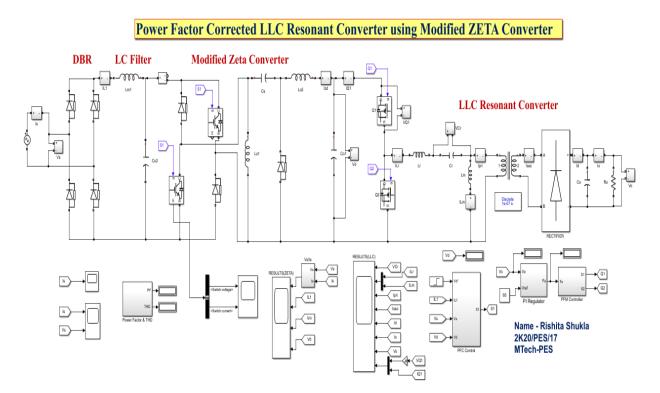

The second section comprises of power factor correction using modified zeta converter cascaded with HB-LLC Resonant Converter. The Modified Zeta Converter operates in Discontinuous Conduction mode (DCM) and LLC Resonant Converter is used to transfer the DC-Link power to the battery. Collective combination of these two converters for the EV charger results in smooth operation, reduced voltage stress across the PFC devices and Modified efficiency of the converters. This work mainly focuses on designing the components of the converter and comparison of the Modified and Conventional Zeta Converter fed HB-LLC Resonant Converter in MATLAB/Simulink environment.

# CONTENTS

| DECLARATION     | i    |

|-----------------|------|

| CERTIFICATE     | iii  |

| ACKNOWLEDGEMENT |      |

| ABSTRACT        |      |

| CONTENTS        | vi   |

| LIST OF FIGURES | ix   |

| LIST OF TABLES  |      |

| NOMENCLATURE    | xiii |

|                 |      |

| 1. | INTRODUCTION                                               | 1  |

|----|------------------------------------------------------------|----|

|    | 1.1 Background of Project                                  | 1  |

|    | 1.2 Importance of Power Factor                             | 3  |

|    | 1.3 Disadvantage due to harmonic current in the power grid | 4  |

|    | 1.4 Power Factor Correction of two stage EV Charger        | 4  |

|    | 1.5 Main Objective of Research                             | 5  |

|    | 1.6 Outline of dissertation                                | 6  |

| 2. | LITERATURE REVIEW                                          | 8  |

|    | 2.1 Introduction                                           | 8  |

|    | 2.2 Overview of Various DC-DC Converters                   | 8  |

|    | 2.3 Overview of Power Factor Corrected DC-DC Converter     |    |

|    | In Literature                                              | 11 |

|    | 2.4 Active Power Factor Correction                         | 12 |

|    | 2.5 Conclusion                                             | 14 |

| 3. | DESIGN AND SIMULATION OF SI-SEPIC CONVERTER                |    |

|    | CASCADED WITH FLYBACK CONVERTER                            | 15 |

|    | 3.1 Introduction                                           | 15 |

|    | 3.2 Modeling of SI-SEPIC Converter cascaded with Flyback   |    |

|    | Converter                                                  | 15 |

|    | 3.3 Modes of operations of Proposed SI-SEPIC             |    |

|----|----------------------------------------------------------|----|

|    | Converter                                                | 18 |

|    | 3.4 Design considerations of SI-SEPIC converter.         | 21 |

|    | 3.5 Control of EV charger                                | 24 |

|    | 3.5.1 Control of SI-SEPIC Converter                      | 24 |

|    | 3.5.2 Control of Flyback Converter                       | 25 |

|    | 3.6 Conclusion                                           | 26 |

| 4. | DESIGN AND SIMULATION OF MODIFIED ZETA                   |    |

|    | CONVERTER FED WITH LLC RESONANT CONVERTER                | 27 |

|    | 4.1 Introduction                                         | 27 |

|    | 4.2 Modeling of Modified Zeta Converter cascaded         |    |

|    | with HB-LLC Resonant Converter                           | 27 |

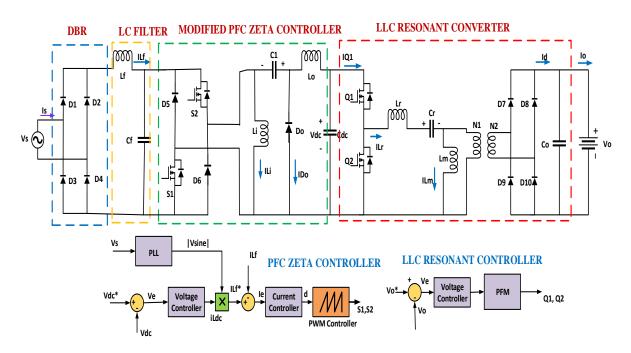

|    | 4.3 Modes of operations of Modified Zeta Converter       | 30 |

|    | 4.4 Design considerations of Modified ZETA converter.    | 32 |

|    | 4.4.1 Design of Modified Zeta Converter                  | 32 |

|    | 4.4.2 Design of HB-LLC Resonant Converter                | 33 |

|    | 4.5 Control of EV charger.                               | 35 |

|    | 4.5.1 Control of Modified Zeta Converter                 | 35 |

|    | 4.5.2 Control of HB-LLC Resonant Converter               | 36 |

|    | 4.6 Conclusion                                           | 37 |

| 5. | RESULTS AND DISCUSSION                                   | 39 |

|    | 5.1 Introduction                                         | 39 |

|    | 5.2 MATLAB Simulation Results of SI-SEPIC Converter      |    |

|    | Cascaded with Fly back Converter                         | 39 |

|    | 5.2.1 LC Filter Bode Plot                                | 40 |

|    | 5.2.2 PWM Controller                                     | 41 |

|    | 5.2.3 SPWM Controller                                    | 44 |

|    | 5.3 MATLAB Simulation Results of Modified Zeta Converter |    |

|    | Fed with Half Bridge LLC Resonant Converter              | 47 |

|    | 5.3.1 Steady State performance of the charger            | 50 |

|    | 5.3.1.1 Output Waveforms of modified Zeta                |    |

|    | Converter                                                | 50 |

|   |                  | 5.3.1.2 Output Waveforms of HB-LLC         |    |

|---|------------------|--------------------------------------------|----|

|   |                  | Resonant Converter                         | 51 |

|   | 5.3.2            | Performance of the charger over different  |    |

|   |                  | supply voltage                             | 54 |

|   | 5.3.3            | Comparison of Modified Zeta Converter with |    |

|   |                  | Conventional Zeta Converter                | 55 |

|   | 5.4 Conclusion   |                                            | 57 |

|   |                  |                                            |    |

| 6 | CONCLUSION A     | ND FUTURE SCOPE                            | 58 |

|   | 6.1 Conclusion   |                                            | 58 |

|   | 6.2 Future Scope |                                            | 60 |

| 7 | REFERENCES       |                                            | 61 |

| 8 | PUBLICATIONS     |                                            | 66 |

9 APPENDIX 67

# LIST OF FIGURES

| Figure No.     | Figure Name                                                                                                                                                       | Page No. |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|

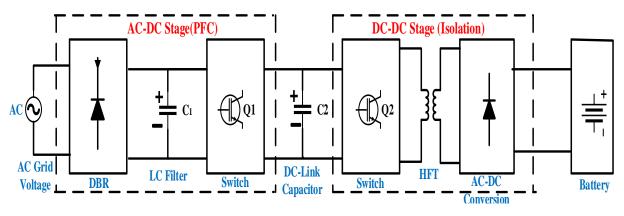

| Fig 1.1        | A General Structure of two stage on-board EV Charger                                                                                                              | 2        |  |  |

| Fig 1.2        | Structure of two-stage on-board EV Charger                                                                                                                        | 5        |  |  |

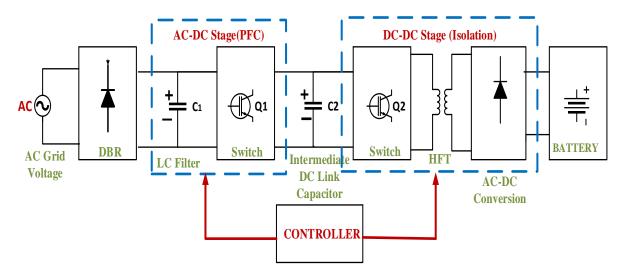

| Fig 2.1        | Rectifier Circuit for AC-DC Conversion and its Input Voltage<br>and Current waveforms                                                                             | 12       |  |  |

| Fig 2.2        | <b>g 2.2</b> Waveforms of input voltage $(V_i)$ and fundamental component of current $(I_1)$                                                                      |          |  |  |

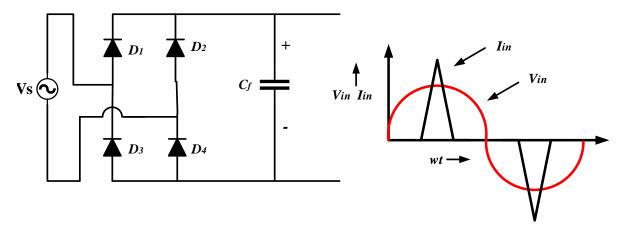

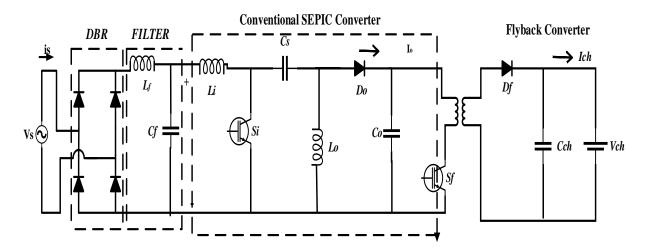

| Fig 3.1        | EV battery charger with conventional SEPIC Converter cascaded with Flyback converter                                                                              | 16       |  |  |

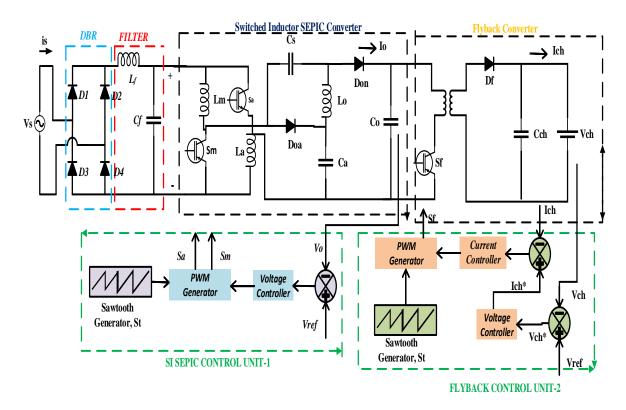

| Fig 3.2        | Proposed EV battery charger with SI-SEPIC Converter cascaded with flyback converter                                                                               | 17       |  |  |

| Fig 3.3        | Modes of Operation of SI-SEPIC converter cascaded with<br>Flyback converter. (a) Mode-1, (b) Mode-2, (c) Mode-3                                                   | 19       |  |  |

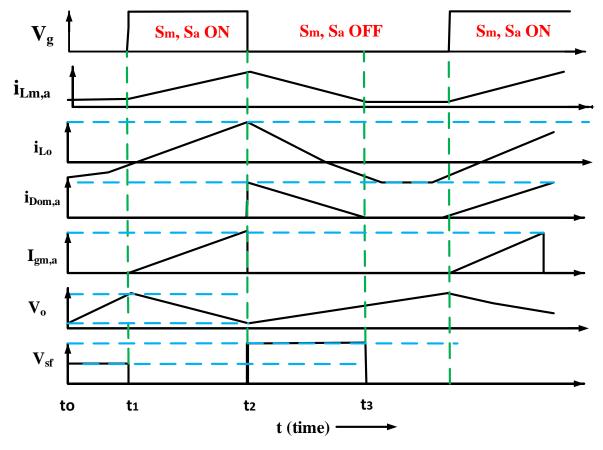

| Fig 3.4        | Switching waveforms of SI-SEPIC Converter cascaded with<br>Flyback converter                                                                                      | 20       |  |  |

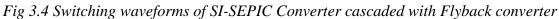

| Fig 3.5        | Controller design of SI-SEPIC converter                                                                                                                           | 24       |  |  |

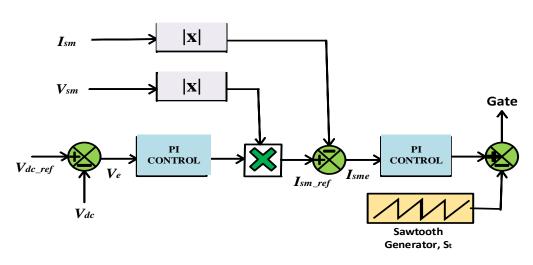

| Fig 3.6        | Controller design of flyback converter                                                                                                                            | 25       |  |  |

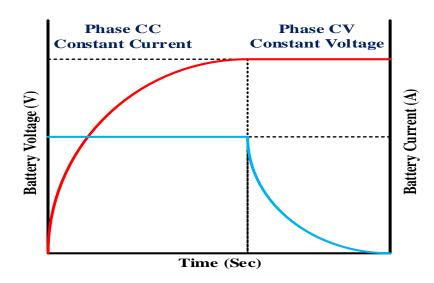

| <b>Fig 3.7</b> | Battery Charger profile in CC-CV mode                                                                                                                             | 25       |  |  |

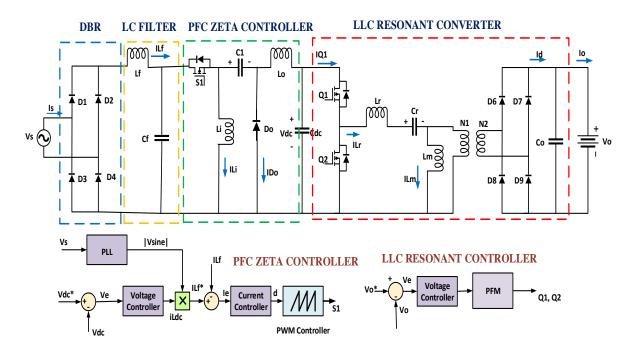

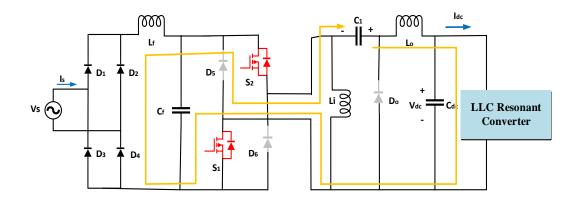

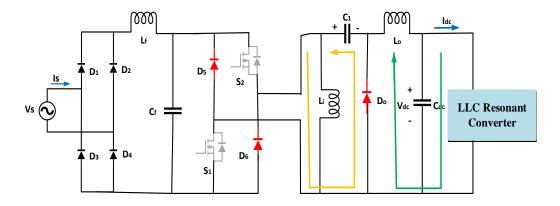

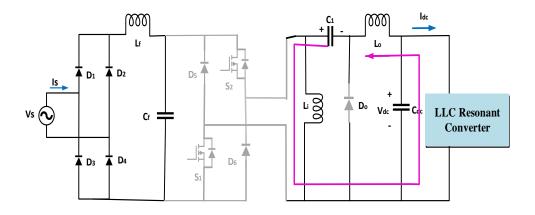

| Fig 4.1        | Battery Charger with Conventional Zeta Converter fed LLC<br>Resonant Converter                                                                                    | 29       |  |  |

| Fig 4.2        | Battery Charger with Modified non-isolated Zeta Converter fed<br>LLC Resonant Converter                                                                           | 29       |  |  |

| Fig 4.3        | Operating waveforms of Modified Zeta Converter fed half bridge<br>LLC Resonant Converter                                                                          | 30       |  |  |

| Fig 4.4        | Modes of Operations of Modified Zeta Converter fed half bridge<br>LLC Resonant Converter, (a) Mode-I Operation, (b) Mode-II<br>Operation, (c) Mode-III Operation. | 31       |  |  |

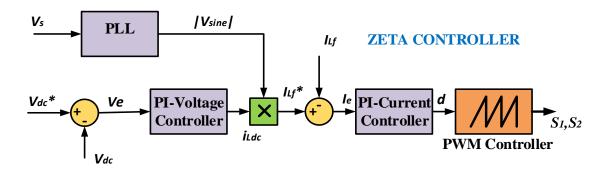

| Fig 4.5        | Controller of Modified Zeta Converter                                                                                                                             | 35       |  |  |

| Fig 4.6        | Controller of HB-LLC Resonant Converter                                                                                                                           | 36       |  |  |

| Fig 4.7        | Block Diagram of PFM                                                                                                                                              | 37       |  |  |

| Fig 5.1         Proposed EV battery charger with SI-SEPIC Converter cascaded                   |                                                                                  |    |  |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----|--|

|                                                                                                | with flyback converter                                                           |    |  |

| <b>Fig 5.2</b>                                                                                 | MATLAB Simulation Model of SI-SEPIC Converter cascaded                           | 40 |  |

| 8                                                                                              | with Flyback Converter                                                           |    |  |

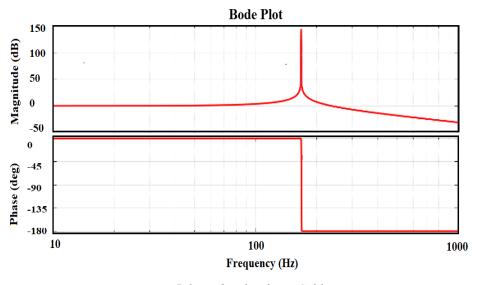

| Fig 5.3                                                                                        | Bode plot for LC filter                                                          | 41 |  |

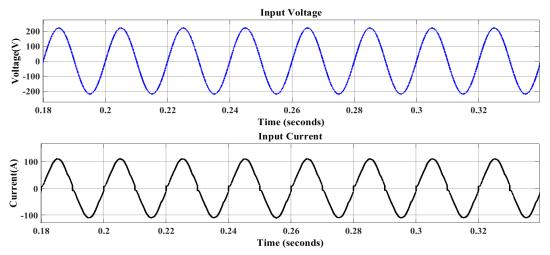

| Fig 5.4                                                                                        | Input Voltage and Current for SI-SEPIC converter                                 | 41 |  |

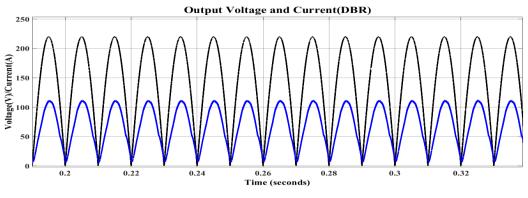

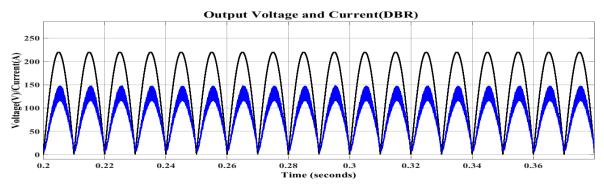

| Fig 5.5                                                                                        | Output Voltage and Current (across DBR)                                          | 42 |  |

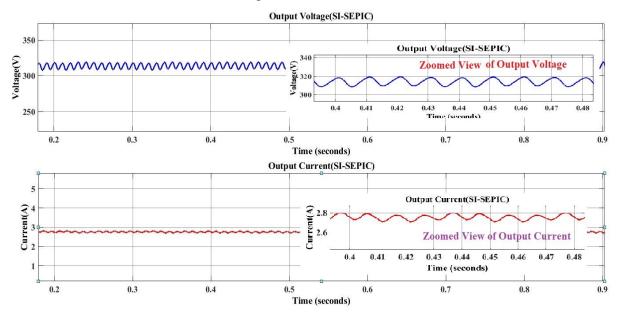

| Fig 5.6                                                                                        | Output Voltage and Current (across SI-SEPIC converter)                           | 42 |  |

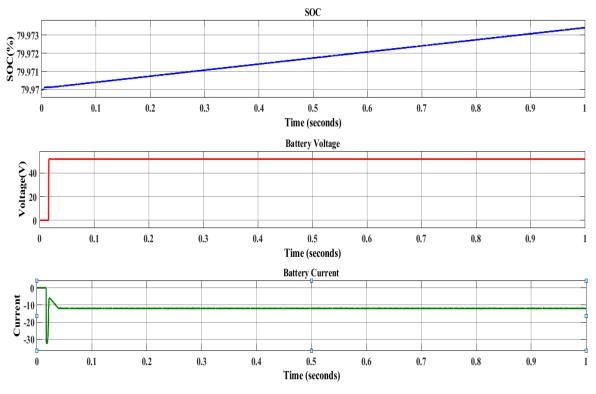

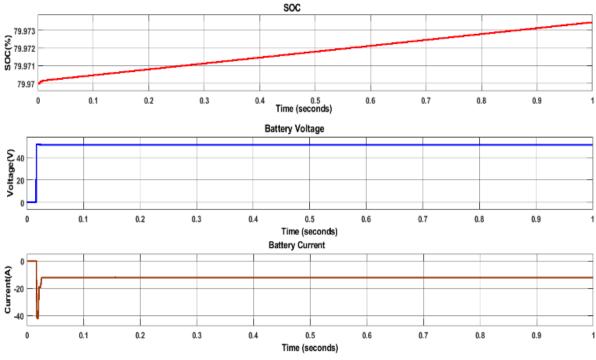

| Fig 5.7                                                                                        | Battery SOC, Battery Voltage and Battery Current                                 | 43 |  |

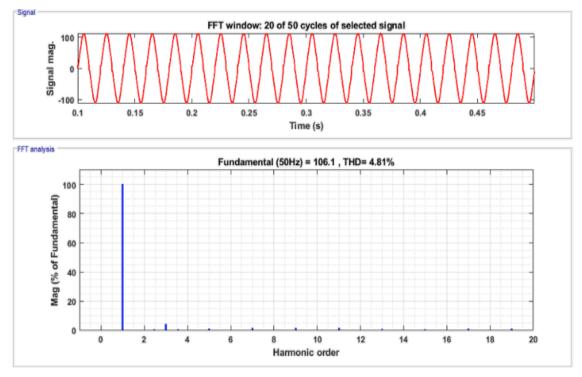

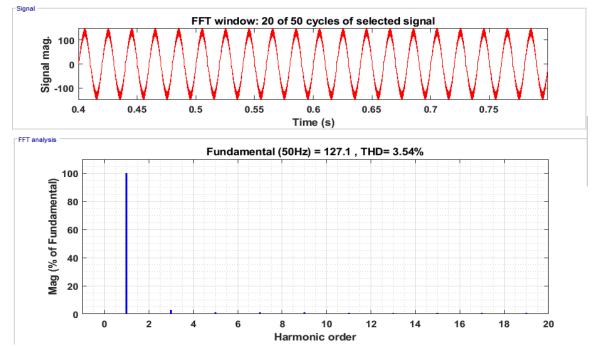

| Fig 5.8                                                                                        | THD (%) in input current using PWM controller                                    | 43 |  |

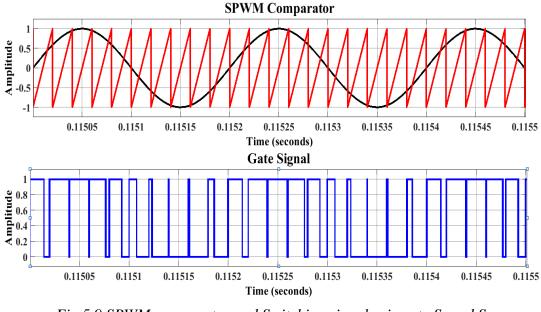

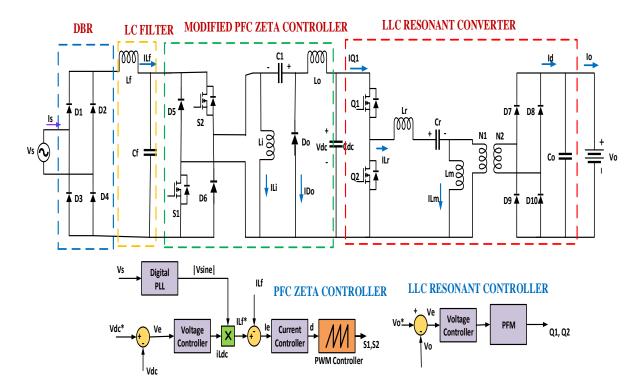

| Fig 5.9                                                                                        | SPWM comparator and Switching signals given to S <sub>a</sub> and S <sub>m</sub> | 44 |  |

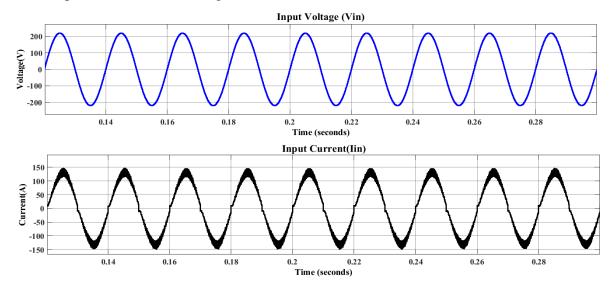

| Fig 5.10                                                                                       | V <sub>in</sub> and I <sub>in</sub> of SI-SEPIC converter                        | 44 |  |

| Fig 5.11                                                                                       | Output Voltage and Current (across DBR)                                          | 45 |  |

| Fig 5.12                                                                                       | Battery SOC, Battery Voltage and Battery Current                                 | 45 |  |

| Fig 5.13                                                                                       | THD (%) in input current using SPWM controller                                   | 46 |  |

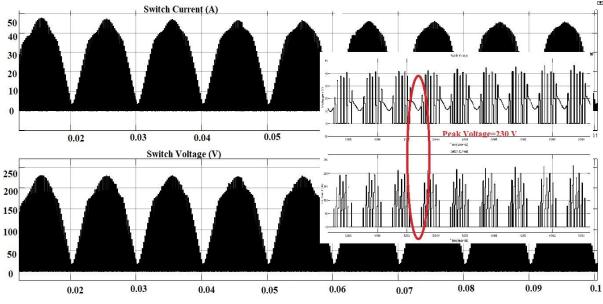

| Fig 5.14       Voltage and Current across auxiliary switches S <sub>a</sub> and S <sub>m</sub> |                                                                                  | 46 |  |

| Fig 5.15                                                                                       | Battery Charger with Conventional Zeta Converter fed LLC                         | 48 |  |

| 11g 3.13                                                                                       | Resonant Converter                                                               | 40 |  |

| Fig 5.16                                                                                       | MATLAB Simulink model of Conventional Zeta Converter fed                         | 48 |  |

| Fig 5.10                                                                                       | with HB-LLC Resonant Converter                                                   | 40 |  |

| Fig 5 17                                                                                       | Battery Charger with Modified non-isolated Zeta Converter fed                    | 49 |  |

| Fig 5.17                                                                                       | LLC Resonant Converter                                                           | 49 |  |

| Fig 5 18                                                                                       | MATLAB Simulink model of Modified Zeta Converter fed with                        | 49 |  |

| Fig 5.18                                                                                       | HB-LLC Resonant Converter                                                        | 47 |  |

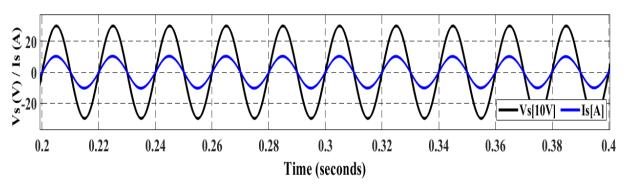

| Fig 5.19                                                                                       | Input Voltage and Current of Modified Zeta Converter                             | 50 |  |

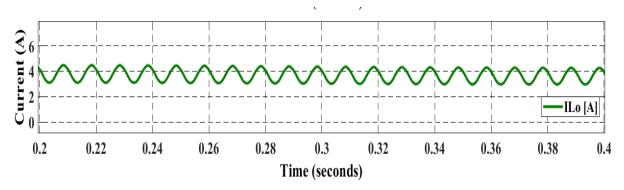

| Fig 5.20                                                                                       | Output Inductor Current of Modified Zeta Converter                               | 50 |  |

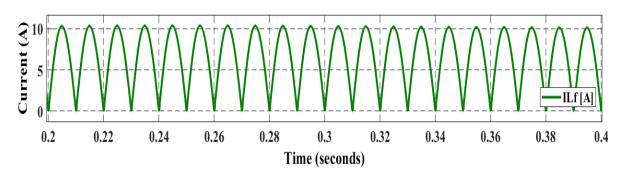

| Fig 5.21                                                                                       | Input Inductor Current of Modified Zeta Converter                                | 51 |  |

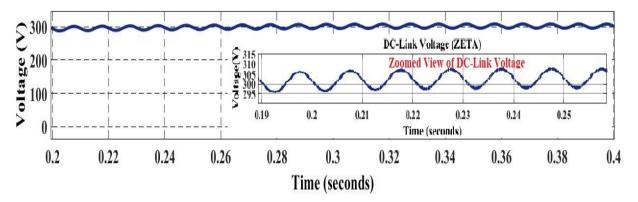

| Fig 5.22                                                                                       | DC-Link Voltage of Modified Zeta Converter                                       | 51 |  |

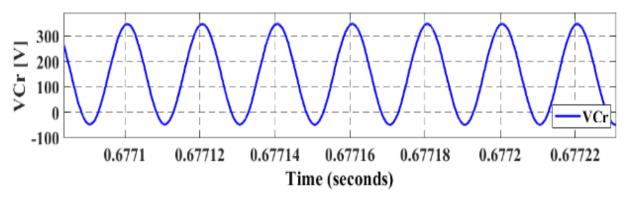

| Fig 5.23                                                                                       | Voltage across resonant capacitance (V <sub>Cr</sub> )                           | 51 |  |

| Fig 5 24                                                                                       | Magnetizing inductance and resonant inductance Current                           | 50 |  |

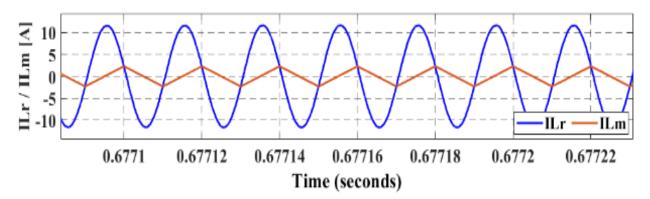

| Fig 5.24                                                                                       | waveform ( $I_{Lr}$ and $I_{Lm}$ )                                               | 52 |  |

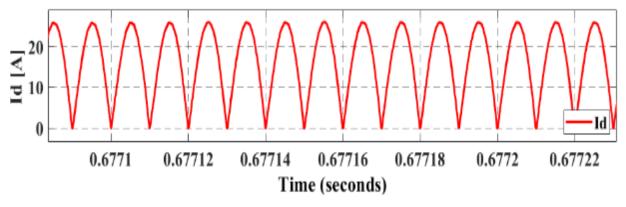

| Fig 5.25                                                                                       | Diode Current (I <sub>d</sub> ) of LLC Resonant Converter                        | 52 |  |

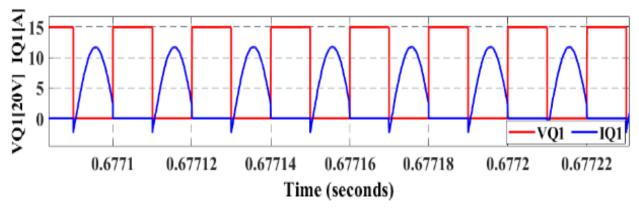

| Fig 5.26                                                                                       | Voltage and Current across the MOSFET Q1                                         | 52 |  |

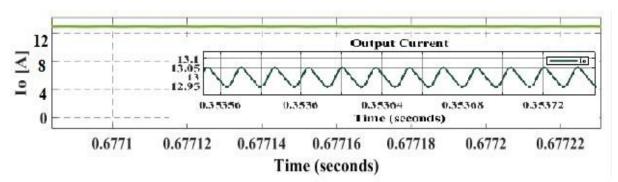

| Fig 5.27                                                           | Output Current (A) waveform of HB-LLC Resonant Converter                | 53 |  |  |

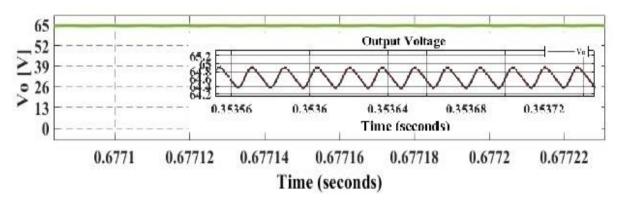

|--------------------------------------------------------------------|-------------------------------------------------------------------------|----|--|--|

| Fig 5.28                                                           | Output Voltage (V) waveform of HB-LLC Resonant Converter                | 53 |  |  |

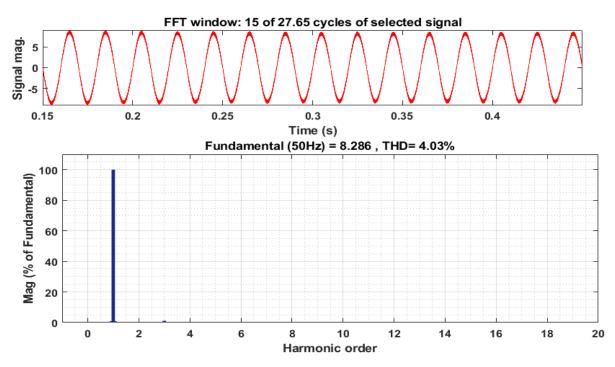

| Fig 5.29                                                           | Fig 5.29Total Harmonic Distortion (THD) of Conventional Zeta Converter  |    |  |  |

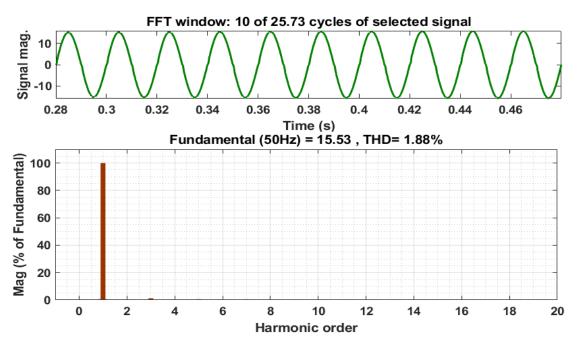

| Fig 5.30Total Harmonic Distortion (THD) of Modified Zeta Converter |                                                                         | 54 |  |  |

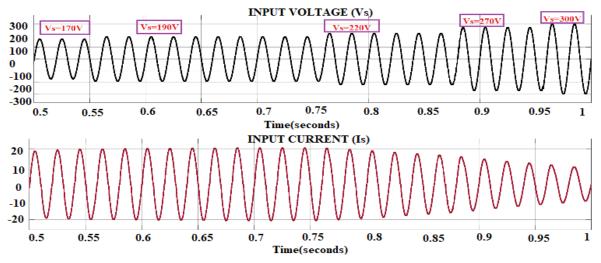

| Fig 5.31                                                           | Waveform of voltage (V) and current (I) over different supply           | 54 |  |  |

| Fig 5.51                                                           | voltage (V <sub>s</sub> )                                               | 54 |  |  |

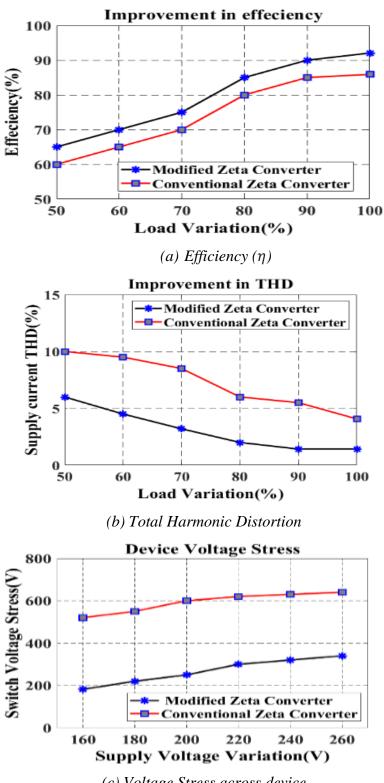

|                                                                    | Comparison in (a) Efficiency ( $\eta$ ), (b) Total Harmonic Distortion, |    |  |  |

| Fig 5.32                                                           | (c) Voltage Stress across device of Modified Zeta Converter and         | 55 |  |  |

|                                                                    | Conventional Zeta Converter                                             |    |  |  |

# LIST OF TABLES

| S. No.    | Table Name                                             | Page No. |

|-----------|--------------------------------------------------------|----------|

| TABLE I   | IEC 61000-3-2 maximum permissible harmonic current for | 1        |

|           | Class D equipment                                      |          |

| TABLE II  | Comparison of Various DC-DC Converters                 | 9        |

| TABLE III | Specifications of Proposed Converter                   | 23       |

| TABLE IV  | Specifications of Modified Zeta Converter              | 34       |

| TABLE V   | Design Parameters of Modified Zeta Converter           | 35       |

| TABLE VI  | Comparison of Controller                               | 47       |

| TABLE VII | Comparison of Conventional and Modified Zeta Converter | 56       |

|           | based EV Charger                                       |          |

### NOMENCLATURE

| PQ       | Power Quality                                               |

|----------|-------------------------------------------------------------|

| THD      | Total Harmonic Distortion                                   |

| EV       | Electric Vehicle                                            |

| PFC      | Power Factor Correction                                     |

| DBR      | Diode Bridge Rectifier                                      |

| UPS      | Uninterrupted Power Supply                                  |

| PF       | Power Factor                                                |

| CC-CV    | Constant Current-Constant Voltage                           |

| DCM      | Discontinuous Conduction Mode                               |

| SI-SEPIC | Switched Inductor-Single Ended Primary Inductance Converter |

| PWM      | Pulse Width Modulation                                      |

| SPWM     | Sinusoidal Pulse Width Modulation                           |

| HB-LLC   | Half Bridge-Inductor-Inductor-Capacitance                   |

| EMI      | Electromagnetic Interference                                |

| DPF      | Displacement Power Factor                                   |

| CF       | Crest Factor                                                |

| BEV      | Battery Electric Vehicle                                    |

| PFM      | Pulse Frequency Modulation                                  |

| SOC      | State of Charge                                             |

| HFT      | High Frequency Transformer                                  |

### **CHAPTER 1**

### **INTRODUCTION**

#### **1.1 Background of Project**

In current scenario, electric vehicle is gaining more popularity as they do not produce hazardous carbon emission [1]. In addition, the price of fuel is increasing every day, which lead people to adopt Electric Vehicle. EVs have several advantages over conventional vehicles as fuel is reserved which causes the reduction in air pollution [2]. There are three levels of EV Charging which includes Level 1, Level 2 and Level 3 Charging respectively. The final Level of charging which is the Level 3 is further classified into Supercharging and DC Fast Charging. Each level is characterised by its speed of charging the electric vehicle which is different at each level. So, at higher charging levels speed of charging increases and the provided power is also increased [3].

Battery charger is an important component of the electric vehicle, which not only affects the life of the battery but it also affects the performance of all the electrical apparatus which are connected to the grid which may result a polluted electrical supply at the grid. For this reason, a reliable EV charger must be constructed which should operate at unity power factor and low input current distortion [4]. Line current should exactly follow line voltage, line power factor should be unity, and line current THD should be less than 5%, according to IEC 61000-3-2 which is shown in Table I and IEEE 519 standards. [5].

TABLE I. IEC 61000-3-2 MAXIMUM PERMISSIBLE HARMONIC CURRENTS FOR CLASS D

EQUIPMENT [6]

| n (harmonics order) | 3   | 5    | 7    | 9    | 11   | 13   | 15 to 19      |

|---------------------|-----|------|------|------|------|------|---------------|

| Max In (harmonics   | 2.3 | 1.14 | 0.77 | 0.40 | 0.33 | 0.21 | 0.15 - 0.15/n |

| Current in Amp)     |     |      |      |      |      |      |               |

An off-board EV charger must have better Power Quality (PQ) characteristics in addition to a small form factor and high-power density, so that energy utilisation density is maximised during charging. However, the line THD (Total Harmonic Distortion) of traditional EV chargers is in the range of 50-70% having Full Bridge Rectifiers at the front end [7]. In this type of EV charging, highly distorted current is drawn from the AC mains. As a result, losses

in traditional EV chargers are quite high, and different Power Quality indices such as power factor (PF), displacement power factor (DPF), and total harmonic distortion (THD) are extremely low. Also, the requirement of reactive power rises significantly, low power factor results in depreciation for the availability of active power from the utility grid whereas a rise in harmonic content is the outcome. High harmonic distortion in the line produces EMI issues and cross-interferences across all the different components connected to the same grid via the line impedance. [8].

The conventional EV charger without power factor correction increases the content of harmonic into the supply current which results in poor input power quality (PQ) indices such as PF (Power Factor), DPF (displacement power factor) and CF (crest factor). The power factor value lies between 0 and 1 for lagging load, but to have significant PQ indices it should be near to unity i.e. 0.95-0.99 or 1. For lagging load, When the load power demand is reactive (for inductive load) the value of true PF is 0 as active power demand becomes zero.

Displacement Power Factor represents the power factor which occurs because of phase difference between input current and input voltage at fundamental line frequency. The value of true PF is considered with respect to harmonic current whereas DPF is taken into account at fundamental frequency. The value of PF and DPF is same for sinusoidal current having less distortion in its waveform and the value becomes unity. Therefore, to overcome the problem of PQ indices and to improve the converter efficiency, a front-end Power Factor Correction converter is designed to meet the requirements of EV charger for this reason, single stage and double stage EV charger comes into literature.

Fig.1.1 A General Structure of two-stage on-board EV Charger

The conventional Electric Vehicle charger consists of Diode Bridge Rectifier (DBR) for AC-DC conversion. Due to the presence of DBR, these chargers suffer from several Power Quality issues i.e. it draws non-sinusoidal and peaky current from the mains, resulting in a very

large amount of THD which badly affects the life of distributed transformer and various other elements, that are present in the charger [9]. Due to the bad effects of harmonics and large amount of THD present in the line, the addition of UPF (Unity Power Factor) based converter is required between the DBR and the DC-Link Capacitor. The charger added can be either a single-stage or double-stage EV charger based on the requirements.

As Diode Bridge Rectifier (DBR) is present at the input stage for AC-DC conversion, several problems are observed such as,

- a. It draws peak input current from the mains

- b. Produces high level of harmonics

- c. Poor Input power factor

- d. High THD

- e. Increase in harmonic content into the supply

To mitigate these problems, PFC is essential for every AC-DC Converter. A General structure for PFC in an onboard EV Charger is shown in Fig 1.1 where for PFC different converters are used such as boost converter, buck converter, buck-boost converter, SEPIC converter, Cuk converter, Zeta converter etc. PFC is necessary to reduce the harmonics, improve the THD and power factor of the converter, effective utilization of active power which makes the grid more stable [10]

#### **1.2 Importance of Power Factor**

Nowadays, due to the modernization and electrification in the industries, the power quality requirements have been increased drastically among people. All the electronic gadgets such as computers, mobile phones, laptops etc have basic requirement of power quality. If the power quality is bad, then these electronic devices will not work adequately. Power factor is one of the most significant factors for power quality which directly impacts the PQ (Power Quality) [11] and effective utilization of active power.

When the power factor is poor, it has various negative impacts on the grid such as waveform distortion, large phase distortion between current and voltage and increased losses on the line which in turn reduces the service time of the power devices. AC-DC conversion circuit is also known as rectifier circuit which is used to convert alternating current to direct current and these circuits are widely used in the industries nowadays in various stages of power conversion. One of the applications of rectifier circuit is UPS (Uninterrupted Power Supply) [12]. Rectifier circuit acts as an interface between grid and power electronics devices, by providing regulated DC power supply, it supplies good quality power for power electronics devices in the subsequent stages for power conversion.

Switching devices are widely used in different power conversion devices due to the large application of power electronic devices into the power industry. Because of the presence of switching devices, the device efficiency can be improved effectively but several problems like harmonics and low power factor are subsequently introduced which are considered as PQ issues. To mitigate such PQ issues i.e. elimination of harmonics and improvement in the power factor, power factor correction is being utilised effectively [13].

#### 1.3 Disadvantage due to the presence of harmonic current in the grid

Due to the presence of harmonic component of current phase shift between current and voltage increases, thus power factor becomes poor. The impulse shaped waveform of input current contains a numerous number of odd ordered harmonic components of current which pollutes the grid [14]. Harmonics in the electric power system are present because of the presence of non-linear electric loads such as rectifiers. The current will be produced at different frequency levels rather from its original, i.e. fundamental frequency. Following are the disadvantages due to the presence of harmonic current component into the power grid:

- 1. When the harmonic current passes through the load, the phase difference between voltage and current is increased resulting which it distorts the effective voltage of the power grid, causing overvoltage and overcurrent into the grid. This is also known as "secondary effect" of the harmonic current.

- 2. Due to the presence of harmonic current components, losses will be more in the circuit and thereby decreasing the efficiency of equipment.

- Abnormal operation of Power devices such as capacitors, transformers and electric motors, relay protection, automatic devices and computer system will be observed due to the presence of harmonic current component.

- 4. Improper calibration and measurement of quantities from the measuring instruments will be observed.

#### **1.4 Power Factor Correction of two stage EV Charger**

To overcome above disadvantages and to minimize the presence of harmonic components, also to improve the PQ indices present on AC mains, an additional Power Factor Correction stage is added in conventional EV charger. The addition of PFC stage improves the efficiency of charger on the cost of increase in the cost and size of the charger.

A single stage and double stage charger are used for the power factor correction. Generally, a double-staged AC-DC converter is chosen for improved Power Quality-based EV chargers as it offers the advantage for the low value of DC-Link capacitor, high reliability and reduced voltage stress across PFC device.

Single-stage PFC converter have high value of voltage stress and current stress across the PFC device, due to this reason it is generally not used [15]. A general configuration of twostage EV charger is shown in Fig 1.2.

Fig. 1.2 A General Structure of two-stage on-board EV Charger

The high-performance BEV (Battery Electric Vehicle) charger circuit includes, DBR for AC-DC Conversion, but it injects a huge amount of harmonic current into the circuit which affects the efficiency and the performance of the charger. To mitigate the adverse effects of DBR, LC filter is connected which reduces the amount of third order harmonics in the charger. The LC Filter is followed by a Power Factor Correction (PFC) circuit at the front end.

The PFC circuit at the front end is used to obtain high power factor and reduce the harmonic current injected into the grid. Then it is cascaded with DC-DC converter with isolation from the main grid. It will provide higher efficiency, high power density and economical PFC based AC-DC Converter [16]. HFT (High Frequency Transformer) is used to provide isolation between the grid and the charging port.

Various DC-DC converters that are used for providing isolation are Flyback Converter, Forward Converter, Push-Pull Converter, Half-Bridge LLC Resonant Converter and Full-Bridge LLC Resonant Converter [17]. Then Battery is connected for charging the electric vehicle. Various ratings of battery can be connected for charging the EV, in this work 48 V and 100 Ah battery is used for charging the BEV.

#### **1.5 Main Objective of Research**

The main objective of this work includes:

- Design and Modelling of the EV Charger. The EV Charger consists of two stages. First stage consists of DC-DC converter used for power factor correction and the later stage consist of DC-DC converter for providing isolation between main grid and charging port. Initially, we learn to compute various converter parameters and implement the model of EV charger.

- 2. *Modes of Operation of EV Charger*. In this work we will see the operation of converter in three different modes of operation with its applicability.

- 3. *Control of EV Charger*. After designing various components, we will learn about the control methods of EV charger with different controller techniques for controlling various parameters and increasing the efficiency of the chargers which will be discussed in the later chapters.

- MATLAB-Simulink Implementation. With the help of design parameters that are calculated using the design equations and the control strategy of the EV Charger, the implementation of converter is done on MATLAB-Simulink environment and results obtained are discussed.

#### **1.6 Outline of dissertation**

The dissertation consists of the following chapters:

**Chapter 1:** In this chapter the importance of power factor correction for electric vehicle along with the problems arises due to the presence of DBR in the charger is discussed. Also, various methods are observed to mitigate the PQ issues present in the grid.

**Chapter 2:** This chapter includes the literature survey of the project "Power Factor Correction of DC-DC Converter for EV Battery Charging Applications". This chapter gives the basic understanding of various DC-DC Converters which are used for power factor correction along with their advantages and disadvantages.

**Chapter 3:** This chapter presents the first work which includes "Power Factor Correction of SI-SEPIC converter cascaded with Fly back Converter for EV Battery Charging Application". It includes the modelling and design of the proposed EV charger along with the control of EV charger using PWM and SPWM controller techniques.

**Chapter 4:** This chapter presents second work which includes "Power Factor Correction of Modified Zeta Converter Fed with Half Bridge-LLC Resonant Converter for EV Charging Applications". In this chapter a comparison between conventional and modified Zeta converter is also discussed along with the design and modelling of Modified Zeta Converter and its control using dual loop controller technique.

**Chapter 5:** In this chapter, the MATLAB-Simulink Model of both the EV Chargers are presented and the results are discussed.

**Chapter 6:** This chapter summarizes the results obtained through the MATLAB-Simulink Model of the Proposed Converter and also acknowledge the future work that can be done.

### **CHAPTER 2**

### LITERATURE REVIEW

#### **2.1 Introduction**

In this chapter, various DC-DC Converters that are being used for providing PFC (Power Factor Correction) are reviewed along with a comparison table which shows the advantages and disadvantages of various DC-DC converter present in literature. Also, Research papers related to Power Factor Correction of DC-DC converter for Electric Vehicle charging applications are discussed.

#### 2.2 Overview of Various DC-DC Converters

Various DC-DC converters can be used for PFC converters like buck converter, boost converter, buck-boost converter, Cuk converter, zeta converter etc and DC-DC converter for isolation stage like Flyback converter, Forward converter, Push-Pull converter, half and full bridge converter etc. Every converter has its own advantage and disadvantages like buck and boost converter have discontinuous input and output current respectively, high input voltage ripple and high electric stress across the device but it requires lesser number of components so the cost of converter is reduced [18]-[19]. In Buck-Boost configuration [20], output voltage is negative and input voltage ripple is more.

Another converter is Cuk converter [21], the output voltage is inverting but continuous and reduced current flows at input and output terminals. Some demerits of this topology include increased number of passive components, large size of inductors and higher electrical stress across the PFC device. In SEPIC converter [22], the polarity of output voltage is same as input voltage and the voltage stress is less as compared to Cuk converter, but the input inductor and output capacitor are large in size and also the output current is discontinuous. Among all these configurations, Zeta converter provides good voltage regulations, better dynamic response in DCM, positive output voltage and less ripple in output voltage [23].

The DC-DC converter for isolation stage includes Flyback converter which is used for isolated conversion. It is simple to design with lesser cost. In flyback converter [24], high voltage can be obtained at the output but voltage stress across the devices is high and has lower efficiency.

Another one is Forward converter [25], where one of the switches is replaced by a diode which causes the reduction in cost of the converter. Push-Pull converter is used in high power application but it has a demerit that its duty ratio cannot be exceeded more than 50% [26].

The demerits of conventional buck-boost PFC converters include [27]:

- a) Increased size of magnetic components due to higher current and voltage ratings.

- b) Increased voltage stress across switch during operations.

- c) high parasitic losses due to operation of conventional converter at higher duty ratio.

To overcome these disadvantages high gain PFC converters are used. Table II shows various DC-DC converters with the relation between the output and input voltage along with advantages and disadvantages.

| CONVERTER  | OUTPUT                      | ADVANTAGE                                                                                          | DIS-ADVANTAGES                                                                                                            |

|------------|-----------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Buck       | Vo = Vs * D                 | Lesser number of components                                                                        | Discontinuous input<br>current, high input<br>voltage ripple, high stress<br>across device.                               |

| Boost      | $Vo = \frac{Vs}{1-D}$       | Lesser number of components                                                                        | Discontinuous output<br>current, high ripple in<br>input voltage, high stress<br>across device.                           |

| Buck-Boost | $Vo = \frac{Vs * D}{1 - D}$ | Lesser number of components                                                                        | High ripple in input<br>voltage, high stress<br>across device, negative<br>output voltage                                 |

| Cuk        | $Vo = \frac{Vs * D}{1 - D}$ | Continuous current<br>present at input and<br>output, reduction in<br>input and output<br>current. | Large number of passive<br>components, large<br>inductor size, high stress<br>across device, inverting<br>output voltage. |

TABLE II. COMPARISION OF VARIOUS DC-DC CONVERTERS [28]

|             |                                                    |                        | Large input inductor and |

|-------------|----------------------------------------------------|------------------------|--------------------------|

| SEPIC       | $Vo = \frac{Vs * D}{1 - D}$                        | Voltage stress is less | large output capacitor,  |

|             | V = 1 - D                                          | than cuk converter     | discontinuous output     |

|             |                                                    |                        | current.                 |

|             |                                                    |                        | Large input inductor and |

| Zeta        | Vs * D                                             | Output current ripple  | large output capacitor,  |

| Leta        | $Vo = \frac{Vs * D}{1 - D}$                        | is less                | output current is        |

|             |                                                    |                        | discontinuous.           |

|             |                                                    |                        | Large input inductor and |

| Luo         | $Vo = \frac{Vs * D}{1 - D}$                        | Output current ripple  | large output capacitor,  |

| Luo         | $V D = \frac{1}{1-D}$                              | is less                | output current is        |

|             |                                                    |                        | discontinuous.           |

|             |                                                    | Simple and             |                          |

| Flyback     | $Vo = Vs \frac{D}{1-D} \left(\frac{Ns}{Np}\right)$ | inexpensive, high      | High voltage stress and  |

|             |                                                    | voltage can be         | lower efficiency         |

|             |                                                    | obtained easily.       |                          |

| Forward     | $Vo = VsD(\frac{Ns}{Np})$                          | Cost is less           |                          |

| Push-Pull   | $Vo = 2VsD(\frac{Ns}{Nn})$                         | Used in high power     | Duty ratio cannot be     |

| Pusn-Pull   | $V O = 2V SD(\frac{Np}{Np})$                       | application            | more than 50%            |

|             | Ma                                                 | Fewer component,       | High electric stress,    |

| Half-Bridge | $Vo = VsD(\frac{Ns}{Np})$                          | lower cost, simple     | discontinuous output     |

|             |                                                    | control                | current                  |

|             |                                                    | Lower electrical       | More components are      |

| Full-Bridge | $Vo = 2VsD(\frac{Ns}{Np})$                         | stress, high           | present, control is      |

| i un Druge  | , 0 = 2, 3D (Np)                                   | conversion ratio and   | complex, higher cost.    |

|             |                                                    | power level.           | complex, inglici cost.   |

\* V<sub>o</sub> = Output Voltage

\* V<sub>s</sub> = Input Voltage

\* D = Duty Ratio

$* N_s$  and  $N_p$  = Secondary and Primary turns ratio of high frequency transformer for providing isolation respectively

#### 2.3 Overview of Power Factor Corrected DC-DC Converter in Literature

A survey of comparison of various topologies which are used for front-end PFC Converter are reported in [29]. All the EV Chargers are designed based on on-board and offboard charger configurations. Various on-board EV charger configurations with single-stage are discussed in [30]-[31]. But on-board EV Chargers have the disadvantage of heavy vehicle weight and charging at high power ratings is not possible, which makes off-board EV charger configurations to be more promising.

For providing built in PFC in EV Chargers, the conventional boost converter fed with DBR is the foremost choice but it has various disadvantage like, at high power ratings, boost converter involves some severe problems like degradation in efficiency, increased bridge losses, increased size of inductor [32]. For buck converter, discontinuous input current, high input voltage ripple, high electric stress across the device are present. So, buck and boost converters are not preferred for providing good power factor correction as the duty cycle is restricted and the quality of wave shaping becomes poor.

The buck-boost configuration provides the advantage of stepping up and stepping down the wide range of input voltage. For providing high efficiency and increased power density, the full bridge LLC (Inductor-Inductor-Capacitor) Resonant converter appears to be a good solution. But due to the presence of four driver circuit, the cost of the converter is increased and the complexity of the topology also increases. An LLC Resonant converter-based EV Charger also provides the additional advantage of low EMI (Electromagnetic Interference) noise along with improved efficiency and increased power density over wide range of input voltage. Hence, EV Chargers need some specific topology of converters for providing reliable charging applications [33].

All the buck-boost derived topologies such as Cuk, Zeta, SEPIC etc are more attractive solution for providing power factor correction due to the availability of wide range of duty cycle, with or without the presence of isolating transformer. SEPIC converter has the ability to improve thermal utilization of switches as the conduction losses are less. It also has less input current ripple and provides better efficiency at low level of input voltage. Also, the switch voltage stress is less in SEPIC converters. Zeta converter provides better dynamic response in discontinuous conduction mode (DCM) [34]. It also provides good voltage regulation, less ripple in output current and positive output voltage. Also, the voltage stress across the devices is quiet low in case of Zeta converter as compared to SEPIC converter.

In this research, a detailed discussion is done on power factor correction using SI (Switched Inductor)-SEPIC converter cascaded with flyback converter which works on lower duty ratio, provides better efficiency, reduces the THD, reduce the third order harmonics and reduces the voltage stress across the power factor correction devices. Also, power factor correction using Modified Zeta converter fed with HB-LLC (Half Bridge-Inductor Inductor Capacitor) Resonant Converter is discussed in detail, which improves the efficiency of EV charger, reduces the third order harmonics, reduces the Total Harmonic Distortion (THD), improves the power factor and reduces the voltage stress across the devices. Also, the modified Zeta converter is compared with the conventional Zeta converter and the obtained results are discussed in detail.

#### **2.4 Active Power Factor Correction**

For a linear circuit,  $cos\varphi$  is used to express the power factor, where  $\varphi$  is the phase difference between the sinusoidal voltage and sinusoidal current. In rectifier circuit diode is non-linear, despite the fact that the input voltage is sinusoidal, the rectified current has a non-sinusoidal shape to it. So, finally it was found that power factor calculation is invalid for AC-DC converter.

The ratio of active power to perceived power is known as the power factor. So, its formula can be written as:

$$PF = \frac{P}{V * I} \tag{2.1}$$

were, PF=Power Factor, P= Active Power

Fig 2.1 Rectifier Circuit for AC-DC Conversion and its Input Voltage and Current waveforms

The rms voltage and current are represented by V and I respectively in the above motioned equation. If the input voltage Vi (where the rms value is V) is sinusoidal but the input current is not, the rms of current is as follows:

$$I = \sqrt{I_1^2 + I_2^2 + \dots + I_N^2 + \dots}$$

(2.2)

In this equation,  $I_1$ ,  $I_2$ , ...,  $I_n$  are respectively the fundamental component, second harmonic, ..., and N<sup>th</sup> harmonic.

The power factor definition used in linear systems is no longer available in switching power systems due to the input current's severe distortion and phase change. We suppose that  $I_1$  is behind  $V_i$  in terms of phase angle  $\alpha$ , as indicated in the diagram below:

Fig 2.2 Waveforms of Input Voltage  $(V_i)$  and Fundamental Component of Current  $(I_1)$

$$P = VI \cos \alpha \tag{2.3}$$

where, the angle between input voltage  $V_i$  and fundamental component of current  $I_1$  is the phase difference and is denoted by  $\alpha$ . The power factor is calculated as,

$$PF = \frac{VI_1 \cos \alpha}{VI} = \frac{I_1 \cos \alpha}{I}$$

(2.4)

The ratio of fundamental component of current to the rms current is calculated as,

$$\frac{I_1}{I} = \frac{I_1}{\sqrt{I_1^2 + I_2^2 + \dots + I_N^2 + \dots}}$$

(2.5)

where,  $I_1$ ,  $I_2$ , ...,  $I_n$  are rms value of the fundamental component, second harmonic, ..., and N<sup>th</sup> harmonic. The equation above describes the relative magnitude of the fundamental current, which is called distortion factor. And  $\cos \alpha$  is called displacement factor, and the power factor equals the distortion factor times the displacement factor.

When  $\alpha=0$ , then power factor is given as:

$$PF = \frac{I_1}{I} \tag{2.6}$$

Total harmonic distortion (THD) is defined as the measure of harmonic content in the signal [34]. The amplitude of harmonic content in a current signal is characterized as THD and is calculated as,

$$THD = \frac{I_h}{I_1} = \sqrt{\frac{(I_1^2 + I_2^2 + \dots + I_N^2 + \dots)}{I_1^2}}$$

(2.7)

where,  $I_h$  is the rms value of all the harmonic component of current. THD considers all the fundamental frequency present on the line. It can be related to either current harmonic or voltage harmonics.

The equation of distortion factor is calculated as:

$$\frac{l_1}{l} = \frac{1}{\sqrt{1 + THD^2}}$$

(2.8)

And when  $\alpha = 0$ ,

$$PF = \frac{I_1}{I} = \frac{1}{\sqrt{1 + THD^2}}$$

(2.9)

Equation 2.9 gives the relationship between the power factor (PF) and Total Harmonic Distortion (THD), it will help us to find the THD and PF of proposed DC-DC Converter. From the equation it is clear that THD and PF are inversely proportional to each other which means lower THD, results in improved power factor, which leads to lower peak currents and increasing the efficiency.

#### **2.5 Conclusion**

The literature review is done for the power factor correction stage in EV Charger is presented in this chapter in the relevant area for work presented in "Power Factor Correction of DC-DC Converter for EV Battery Charging Applications" in detail. The literature review is carried out to analyse all the different DC-DC converters topologies which are used for providing power factor correction along with their advantages and disadvantages. Among all the converters, SEPIC converter provides the advantage of less input current ripple and provide better efficiency at low level of input voltage. Also, the switch voltage stress is less in SEPIC converters. In discontinuous conduction mode (DCM), the ZETA converter provides a better dynamic response. It also improves the voltage regulation and lowers the ripple in output current. In the next chapters, design for the power factor correction using SEPIC and Zeta Converters are discussed.

### CHAPTER 3

### DESIGN AND SIMULATION OF SI-SEPIC CONVERTER CASCADED WITH FLYBACK CONVERTER

#### **3.1 Introduction**

In this chapter, Power Factor Correction of SI-SEPIC Converter cascaded with Flyback converter for EV Battery charging applications is presented. Initially, there will be a comparison between the traditional SEPIC converters and SI-SEPIC converters. Along with this the modeling and the three modes of operations of the proposed SI-SEPIC converter cascaded with Flyback converter will be discussed. The charger operates is Discontinuous Conduction Mode. Also, various parameters of the converter are calculated and the controller of the charger is designed using PWM and SPWM controller techniques.

#### 3.2 Modeling of SI-SEPIC Converter cascaded with Flyback Converter

Due to the addition of an intermediate capacitor, the SEPIC converter does not have inrush current issues, and the regulated DC link voltage is not affected by the AC voltage peak, unlike boost converters. In discontinuous conduction mode (DCM), the control algorithm of the SEPIC converter and bridgeless SEPIC converter for inductor current is completed. Although it simplifies the PFC control technique, it has large input current peaks, which leads to overdesigned input filters. [35-36]. As a result, these converters can only be used for low-power applications. [37-38] investigates several variants of SEPIC converters and digital control of such converters; nevertheless, the component count is larger, resulting in increased cost and complexity.

The traditional SEPIC converter has step-up and step-down capabilities with positive voltage polarity [39]. A lower current ripple is obtained at the converter's input, as a high current ripple will distort the supply current, affecting the converter's performance. The sum of the input voltage and the DC-link voltage is the voltage across the device in the SEPIC converter [40]-[42]. Fig 3.1 represents the EV battery charger with conventional SEPIC converter. This configuration suffers from high voltage stress and less efficiency as compared

to high gain SEPIC converters [43]. To reduce the voltage stress across the device, the PFC converter is operated at lower input voltage with same DC-Link voltage and same power rating.

As a result, to reduce voltage stress across the devices, the standard SEPIC converter is substituted with a high step-up gain converter. We may be able to get the same DC-Link voltage with a lower input voltage due to the decreased duty cycle of these high step-up gain converters. [44]. Using a connected inductor is another technique to reduce voltage stress across the device. However, despite the inductor's simple design, voltage spikes develop across the devices when employing linked inductors.

A number of single stage single switch topologies based on integrated SEPIC with LLC converter, flyback converter, and valley fill circuit that are useful for EV chargers are discussed in the literature [45–46]. However, through the PFC device, all of these single-stage solutions are subjected to significant voltage and current stress. As a result, two-stage EV chargers are becoming increasingly common in order to ensure high dependability and low switch voltage stress on front-end PFC converter devices using high gain PFC converters.

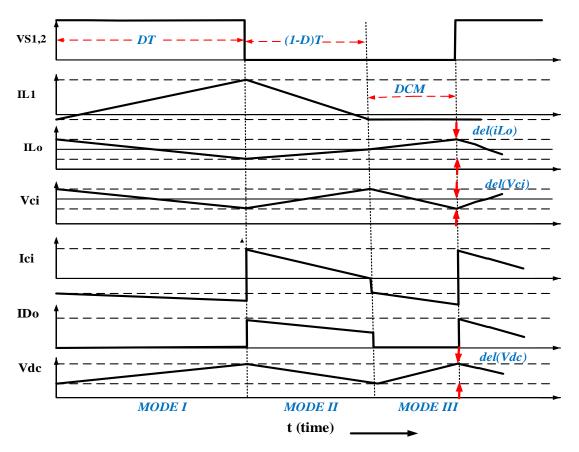

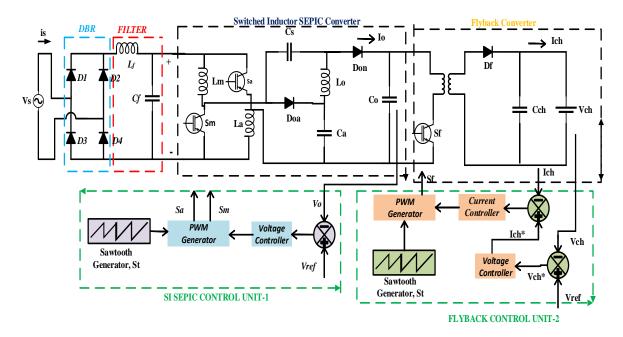

Fig 3.1 EV battery charger with conventional SEPIC Converter cascaded with Flyback converter

This work presents a two-stage EV charger with Switched Inductor (SI)-SEPIC converter cascaded with Flyback Converter for providing high-frequency isolation as shown in Fig 3.2, with reduced Duty Ratio (D) operation, providing lesser voltage stress across the switch. The converter consists of switched inductors  $L_m$  and  $L_a$  at stage-I along with two switches  $S_m$  and  $S_a$  with auxiliary components like  $C_a$  and  $D_{oa}$ , used to provide high gain to the converter. The main advantage of operating at reduced duty ratio is that efficiency of the

converter is improved as compared to conventional battery charger [47]-[48]; also, it provides the viability to increase the range of EV charger.

The advantages of the proposed converter over conventional SEPIC converter are:

1. The gain in voltage of SI-SEPIC converter is calculated as,

$$Gain = \frac{(3D+1)}{(1-D)}$$

where, D is the duty ratio of the proposed converter.

- 2. Reduced voltage stress across the PFC device.

- 3. Lower voltage stress leads to increase in voltage blocking capability of the switch, also reduces the on-state resistance.

- 4. High gain converter.

- 5. Efficiency of converter is improved.

- 6. Simple control topology.

Fig 3.2 Proposed EV battery charger with SI-SEPIC Converter cascaded with flyback converter

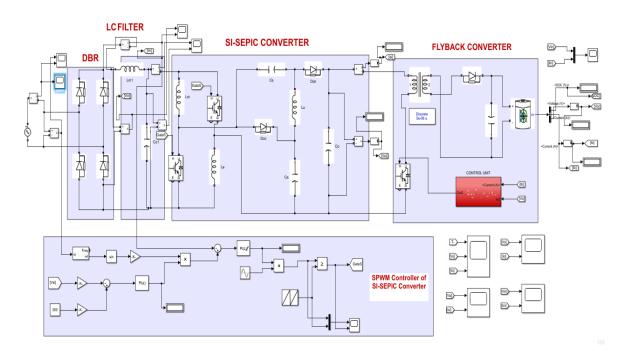

Both the converters are designed to operate in Discontinuous Conduction Mode (DCM), to achieve zero voltage and zero current switching. A 220V AC is used at the source voltage then this AC voltage is converted to DC by connecting a DBR. A constant DC voltage

of 300V is achieved at the output of SI-SEPIC converter, this voltage is provided as the input of flyback converter and a voltage of 65V and 11A current is achieved across the battery at a power rating of 700W. The flyback converter is operated in CC-CV regions. The SI-SEPIC converter is operated using PWM and SPWM voltage control techniques individually; results of both of the controllers are compared. Simultaneously voltage stress across the devices is reduced and power factor is corrected.

#### 3.3 Modes of Operations of Proposed SI-SEPIC Converter

The converter consists of switched inductors  $L_m$  and  $L_a$  at stage-I along with two switches  $S_m$  and  $S_a$  with auxiliary components like  $C_a$  and  $D_{oa}$ , used to provide high gain to the converter. The inductance  $L_o$  is designed for DCM operation. Different modes of this converter are explained below:

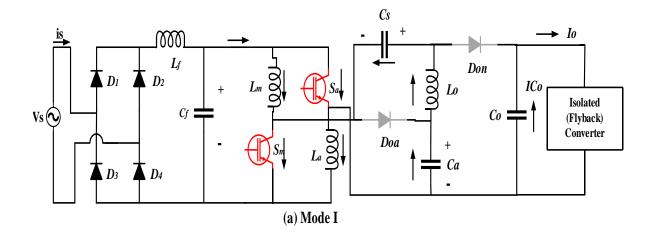

**MODE 1**: Both the switches  $S_m$  and  $S_a$  are turned on simultaneously, Fig 3.3(a). The current through the inductance  $L_m$  and  $L_a$  starts increasing linearly as in Fig 3.4. Both of the diodes i.e.  $D_{oa}$  and  $D_{on}$  remains reverse bias in this mode. Capacitors  $C_a$  and  $C_s$  starts to discharge in this mode through  $S_m$  and  $S_a$ .

In this topology we are considering  $L_m = L_a = L$ , using this expression we can calculate the expressions of voltage across switched inductors ( $V_{Lm}$ ,  $V_{La}$ ) and inductor voltage ( $V_{Lo}$ ):

$$V_{Lm} = V_{La} = V_{sm} = L \frac{di_L}{dt}$$

(3.1)

$$V_{Lo} = L_o \frac{di_{Lo}}{dt} = V_{ca} + V_{sm} - V_{cs}$$

(3.2)

where,  $V_{sm}$  is the peak input voltage and  $i_L$  is current through inductor  $L_m$  and  $L_a$ .

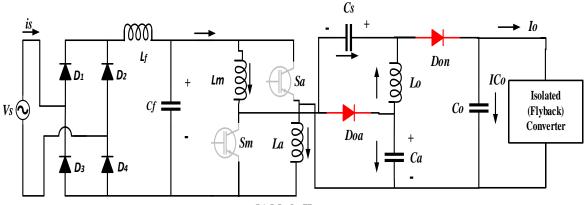

**MODE 2:** Both the switches  $S_m$  and  $S_a$  are turned off simultaneously, Fig 3.3(b). The stored energy in inductor  $L_m$  and  $L_a$  is given to load via diode  $D_{on}$  and capacitor Cs. The auxiliary diode  $D_a$  is used to transfer the energy to the auxiliary capacitor  $C_a$ . The energy, which was present in  $L_0$ , is released through the diode  $D_{on}$ . The expressions of voltage across  $L_m$ ,  $L_a$  and  $L_0$  is:

$$V_{Lm} = V_{La} = \frac{V_{sm} + V_{cs} - V_0}{2} = L \frac{di_L}{dt}$$

(3.3)

$$V_o = L_o \frac{d_{iLo}}{dt} = -V_{cs} \tag{3.4}$$

where, V<sub>o</sub> is the output voltage of SI-SEPIC converter across the C<sub>o</sub> DC-link capacitor.

(b) Mode II

Fig 3.3 Modes of Operation of SI-SEPIC converter cascaded with Flyback converter. (a) Mode-1, (b) Mode-2, (c) Mode-3

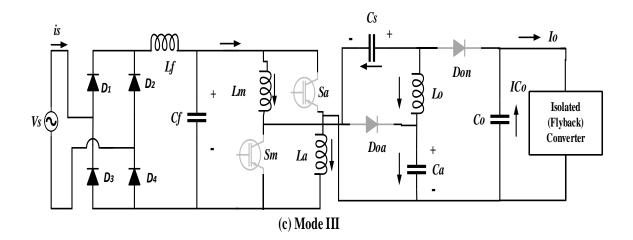

**MODE 3:** Both the diodes  $D_{on}$  and  $D_{oa}$  and the switches  $S_m$  and  $S_a$  remains turned off, thus this mode is called freewheeling period or DCM period, Fig 3.3(c). The current through the diodes  $D_{oa}$  and  $D_{on}$  is zero since both of them are non-conducting in this region, therefore

current  $i_{Lm}$ ,  $i_{La}$  and  $i_{Lo}$  freewheels through the path shown. Using KVL in the closed path, the expressions of voltage is:

$$V_{Lm} + V_{La} + V_{ca} = V_{sm} + V_{cs} + V_{Lo}$$

(3.5)

Voltages  $V_{Lm}$ ,  $V_{La}$  and  $V_{Lo}$  are considered zero during the steady state. Therefore, equation (3.5) becomes,

$$V_{ca} = V_{sm} + V_{cs} \tag{3.6}$$

The input and output voltage over one switching cycle is:

$$\frac{1}{T_s} \left( \int_0^{DT_s} V_{sm} dt + \int_{DT_s}^{T_s} \frac{V_{sm} - V_o + V_{cs}}{2} dt \right) = 0$$

(3.7)

$$\frac{1}{T_s} \left( \int_0^{DT_s} (V_{sm} + V_{ca} - V_{cs}) dt + \int_{DT_s}^{T_s} - V_{cs} dt \right) = 0$$

(3.8)

The voltage across capacitors  $C_a$  and  $C_s$  can be calculated by using the equations (3.5), (3.6), (3.7) and (3.8)

$$V_{cs} = \frac{2D}{1-D} V_{sm} \tag{3.9}$$

$$V_{ca} = \frac{3D+1}{1-D} V_{sm} \tag{3.10}$$

Using above equations, the voltage gain across the SI-SEPIC converter is given as:

$$M_H = \frac{V_O}{V_{sm}} = \frac{3D+1}{1-D}$$

(3.11)

From equation (3.11) shows that the voltage gain of the proposed SI-SEPIC converter is greater than the conventional SEPIC converter.

The flyback converter operates in constant current and constant voltage regions to facilitate the battery current. The magnetizing inductance is designed for DCM operation. The output current is provided to the battery by the capacitor  $C_{ch}$ . The operation of flyback converter can be explained as follows:

*In Mode 1*, the switch  $S_f$  is turned ON. During this mode the energy is stored in the inductance  $L_f$ , as the magnetizing current rises linearly. The diode  $D_f$  is in OFF state which means there is no transfer of energy between primary and secondary.

*In Mode 2*, S<sub>f</sub> is turned OFF. The voltage across the primary reduces and positive voltage is applied to diode D<sub>f</sub>, making it forward biased.

*In Mode 3*, both the switch and the diode are in OFF state and the converter operates in DCM. During this instant, the energy stored in  $L_m$  is completely reduced and the battery current is facilitated through the output capacitor  $C_{ch}$ .

#### **3.4 Design Considerations of SI-SEPIC Converter**

The instantaneous source voltage is,

$$V_s(t) = V_s \sqrt{2} \sin(2\pi f t)$$

(3.12)

where,  $V_s$  is the source voltage which is taken to be 220V and f is the supply frequency. Using equation (3.11), the relation between DC Voltage  $V_o$  and peak input voltage  $V_{sm}$  can be given as,

$$V_o = \frac{3D+1}{1-D} V_{sm}$$

(3.13)

The Duty Ratio of the proposed converter is,

$$D = \frac{V_o - V_{sm}}{V_o + 3V_{sm}}$$

(3.14)

The above equation shows that the value of D (duty ratio) of this converter is less as compared to the conventional SEPIC converter

$$D = \frac{V_o - V_{sm}}{V_o + V_{sm}}$$

(3.15)

which reduces the conduction losses of the converter and improves the efficiency. The switching inductances  $L_m$  and  $L_a$  can be calculated using the equation,

$$L_m = L_a = \frac{V_{sm}D}{\sigma i L_m f_s} \tag{3.16}$$

where,  $\sigma$  is the permissible ripple in input current and  $f_s$  is the switching frequency SI-SEPIC converter.

The value of transfer capacitor  $C_s$  and auxiliary capacitor  $C_a$  are considered same and can be calculated from the equation given below,

$$C_s = C_a = \frac{P_i}{\rho \sqrt{2} V_{sm} f s (\sqrt{2} V_{sm} + V_o)}$$

(3.17)

where,  $P_i$  is the input Power and  $\rho$  is the permissible ripple in voltage. The inductance  $L_o$  in DCM can be expressed as,

$$L_{o} = \left(\frac{V_{sm}^{2}}{P_{i}}\right) \frac{1}{fs} \frac{V_{o} - V_{sm}}{V_{o} + 3V_{sm}}$$

(3.18)

The value of output capacitor  $C_o$  is designed in such a way that the battery current remains uniform at the output. The expression of  $C_o$  is,

$$C_o = \frac{I_o}{2\omega\Delta V_o} \tag{3.19}$$

where,  $\Delta$  is the permissible voltage ripple in output and  $\omega$  is angular frequency of supply voltage. The rating of the battery is taken to be 48V, 100 Ah and to provide CC-CV charging the output of the flyback converter is controlled at 65V. The transformation ratio of the Flyback converter is taken to be 1:3. The relation between  $V_o$ , Duty cycle  $C_o$  and  $V_{ch}$  can be given as,

$$V_{ch} = \frac{nD_o}{1 - D_o} V_o \tag{3.20}$$

where,  $V_{ch}$  is the output voltage of charger and  $V_o$  is the output voltage of SI-SEPIC converter, acts as the input of Flyback converter. The capacitor  $C_{ch}$  is used to provide rated output voltage in CC-CV mode and value of this capacitor is given as,

$$C_{ch} = \frac{D_o V_{ch}}{f_{sw} \left(\frac{V_{ch}^2}{P_i}\right) \Delta \varepsilon V_{ch}}$$

(3.21)

The magnetising inductance is given as,

$$L_{mg} \le \frac{(V_o D_o)^2}{2V_{ch} I_{ch} f_{sw}} \tag{3.22}$$

LC filter is used after DBR to limit the reflection of high frequency harmonics and thereby reducing the THD of input current. The design equation of filter capacitance is,

$$C_{fmax} = \frac{I_m}{\omega V_m} \tan \theta \tag{3.23}$$

where,  $\theta$  is the angle of displacement between the measured source current and fundamental component of supply voltage.  $f_c$  is defined as filter cut off frequency which chosen to be  $1/10^{\text{th}}$  of switching frequency for eliminating higher order switching harmonics. The expression of filter inductance is given as,

$$L_f = \frac{1}{4\pi^2 f_c^2 C_f}$$

(3.24)

Table III shows the parameters of the proposed converter used for the design of converter.

| S.No. | SPECIFICATIONS                                      | VALUES     |

|-------|-----------------------------------------------------|------------|

| 1.    | Supply Voltage (V <sub>s</sub> )                    | 220V       |

| 2.    | Output Voltage (SI-SEPIC)                           | 300V       |

| 3.    | Output Current (SI-SEPIC)                           | 2A         |

| 4.    | Switching Frequency (SI-SEPIC)                      | 20kHz      |

| 5.    | Output Power (SI-SEPIC)                             | 600W       |

| 6.    | Input Voltage (Flyback)                             | 300V       |

| 7.    | Output Voltage (Flyback)                            | 65V        |

| 8.    | Output Current (Flyback)                            | 11A        |

| 9.    | Switching Frequency (Flyback)                       | 50kHz      |

| 10.   | Battery Rating                                      | 48V, 100Ah |

| 11.   | Ripple Current in $L_m(\sigma)$                     | 10%        |

| 12.   | Ripple Voltage across $C_s(\rho)$                   | 10%        |

| 13.   | Ripple Voltage across $C_o(\Delta)$                 | 3%         |

| 14.   | Ripple Voltage across $C_{ch}(\varepsilon)$         | 0.1%       |

| 15.   | Input Inductance (L <sub>m</sub> , L <sub>a</sub> ) | 0.16mH     |

| 16.   | Transfer Capacitance (Cs)                           | 5μF        |

| 17.   | Auxiliary Capacitance (Ca)                          | 5μF        |

| 18    | Output Inductance (L <sub>o</sub> )                 | 3.57µH     |

| 19.   | Filter Capacitance (C <sub>f</sub> )                | 900µF      |

| 20.   | Filter Inductance (L <sub>f</sub> )                 | 1mH        |

| 21.   | DC-Link Capacitance (C <sub>o</sub> )               | 250µF      |

| 22.   | Magnetic Inductance (L <sub>mg</sub> )              | 240µH      |

| 23.   | Output Capacitance (C <sub>ch</sub> )               | 1000µF     |

# TABLE III. SPECIFICATIONS OF PROPOSED CONVERTER

### **3.5 CONTROL OF EV CHARGER**

The control methodology of proposed EV charger can be explained in two stages:

- (a) Control of SI-SEPIC converter

- (b) Control of Flyback converter.

#### **3.5.1 Control of SI-SEPIC converter**

The multi-loop control is used for the control of SI-SEPIC converter. For the generation of reference source current and switching signals ( $G_s$ ) the outer and inner PI controller is used respectively. Initially, Voltage error signal is generated on comparing  $V_{dc}$  with  $V_{dc_ref}$  as,

$$V_{oe}(k) = V_{dc_{ref}}(k) - V_{dc}(k)$$

(3.25)

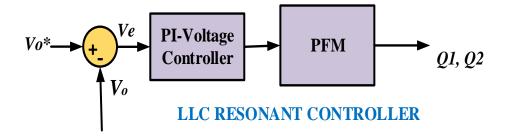

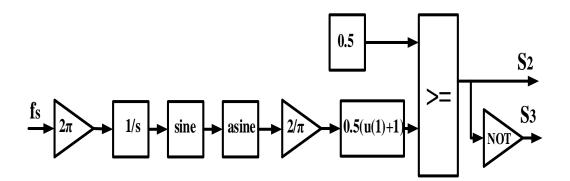

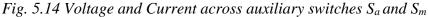

Fig 3.5 Controller design of SI-SEPIC converter

The outer voltage loop is used to control DC Link voltage of SI-SEPIC converter and the inner current loop control is used to control the output current of SI-SEPIC Converter. The DC-Link voltage ( $V_{dc}$ ) is compared with the reference voltage ( $V_{dc\_ref}$ ) to generate error in voltage ( $V_e$ ) and is provided to PI-Voltage Controller.

This voltage error signal is multiplied with the source voltage,  $V_{sm}$  to generate the reference source current. Both, reference source current and source current are then compared and the generated current error is given to PI controller. The PI Controller is used to control the current. The output of PI based current controller is compared with saw-tooth carrier waveform to generate the switching pulsed which are given to switches  $S_m$ ,  $S_a$  of the SI-SEPIC Converter. Fig 3.5 represents the control methodology of SI-SEPIC converter by the help of dual loop controller technique.

#### 3.5.2 Control of Flyback converter

Fig 3.6 Controller design of flyback converter