# RELIABILITY IMPROVEMENT OF PV MODULE THROUGH MODIFIED BYPASS ARRANGEMENT

#### A DISSERTATION

#### SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

## MASTER OF TECHNOLOGY IN POWER ELECTRONICS SYSTEM

Submitted By

## ASHWANI SRIVASTAV

### 2K20/PES/06

Under the supervision of

## Prof. VINOD KUMAR YADAV &

Prof. M. RIZWAN

## DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

### DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

#### **CANDIDATE'S DECLARATION**

I, ASHWANI SRIVASTAV, Roll No. 2K20/PES/06 student of M.Tech (POWER ELECTRONICS SYSTEM), hereby declare that the project Dissertation titled "TO IMPROVE THE RELIABILITY OF PV MODULE UNDER DIFFERENT PARTIAL SHADING CONDITIONS BY MODIFIED BYPASS CIRCUIT" which is submitted by me to the Department of Electrical Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship or other similar title or recognition."

Place: Delhi Date: ASHWANI SRIVASTAV M.Tech (Power Electronics System) (2K20/PES/06)

### DEPARTMENT OF ELECTRICAL ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

#### CERTIFICATE

I hereby certify that the Project Dissertation titled "TO IMPROVE THE RELIABILITY OF PV MODULE UNDER DIFFERENT PARTIAL SHADING CONDITIONS BY MODIFIED BYPASS CIRCUIT" which is submitted by ASHWANI SRIVASTAV, whose Roll No. is 2K20/PES/06, Electrical Engineering Department, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the students under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date: 26/06/22 Prof. VINOD KUMAR YADAV (SUPERVISOR) Department of Electrical Engineering Delhi Technological University Prof. M. RIZWAN (SUPERVISOR) Department of Electrical Engineering Delhi Technological University

#### **ABSTRACT**

Photovoltaic (PV) generation systems are being developed in response to the rapidly depleting conventional energy sources and the growing demand for alternative energy sources. PV technology is the most widely chosen alternative source among the various options because it is the most abundant. But one of the major problems associated with this technique is the generation of Hotspot in PV panel and this long standing problem is still present even after so much advancement in the technique. However, it does not affect the performance but seriously affect the safety and reliability of the system.

In this paper, solution to this problem is proposed which is cost effective and also does not increase the complexity of the circuit. A hotspot mitigation circuit is proposed in which a Mosfet is used, as a switch, which will cut off the entire panel which is under the partial shading condition and the rest of the connection can continue to work smoothly at reduced voltage but at very minute power loss as compared to the prior design.

The performance of the modified bypass circuit is demonstrated using a simulation model of a  $3\times3$  Photovoltaic (PV) panel system, and the results are then compared in terms of current-voltage and power-voltage characteristics under various partial shading conditions, with and without modified bypass circuit. The results are then validate through hardware experimentation on a  $3\times3$  PV panel using EXIDE INDIA LIMITED (EIL-40) modules each have capacity of 40 W.. The results reveal that the proposed modified bypass arrangement effectively reduced the temperature of the affected cell hence the reliability is improved.

#### ACKNOWLEDGEMENT

First and foremost, I express my deep sense of gratitude to my supervisor, counselor and advisor **Prof. Vinod Kumar Yadav** and **Prof. M. Rizwan**, department of Electrical Engineering for their constant guidance, support, motivation and encouragement throughout the period this work was carried out. Their readiness for consultation at all times, educative comments, concern and assistance have been invaluable.

I want to thank **Prof. Uma Nangia**, Head of Electrical Department for building this platform and creating such an energetic environment for research work.

I want to thank for support from all the staff of the Internet of Things Lab (E1), Electrical Engineering Department for their fullest cooperation.

I would like to thank my friends and all those who have directly or indirectly helped me in completion of the thesis well in time.

Finally, I wish to thank my parents for their moral support and confidence showed in me to pursue M. Tech at an advanced stage of my academic career.

#### ASHWANI SRIVASTAV

M.Tech (Power Electronics System)

(2K20/PES/06)

## CONTENTS

| Candidate's  | s Dec | laration                                    | ii   |

|--------------|-------|---------------------------------------------|------|

| Certificate  |       |                                             | iii  |

| Abstract     |       |                                             | iv   |

| Acknowledg   | geme  | ent                                         | v    |

| Contents     |       |                                             | vi   |

| List Of Figu | ures  |                                             | viii |

| List Of Tab  | les   |                                             | xi   |

| List Of Sym  | ıbols | And Abbreviations                           | xii  |

| Chapter 1 I  | ntro  | duction                                     | 1    |

| 1            | .1    | Introduction                                | 1    |

| 1            | .2    | Renewable Energy Resources                  | 4    |

| 1            | .3    | Global Initiatives                          | 5    |

| 1            | .4    | Problem Statement                           | б    |

| Chapter 2 T  | Гһеоі | retical Background                          | 8    |

| 2            | 2.1   | Modeling Of PV Cell                         | 8    |

| 2            | 2.2   | Power Dissipation Across Shaded Solar Cells | 9    |

| 2            | 2.3   | Proposed Hot Spot Mitigation Circuit        | 11   |

| 2            | 2.4   | Circuit Topologies                          | 13   |

| 2            | 2.4.1 | Series-Parallel (SP)                        | 14   |

| 2            | 2.4.2 | Bridge Link (BL)                            | 14   |

| 2            | 2.4.3 | Total Cross-Tied (TCT)                      | 15   |

| 2            | 2.5   | Scheme Of Experiment                        | 16   |

| Chapter 3 S  | Simul | ation Modeling And Results                  | 18   |

| 3            | 8.1   | Ratings Of PV Module                        | 18   |

| 3            | 8.2   | Simulation Modeling                         | 19   |

| 3            | 3.3   | Results                                     | 22   |

| 3.3            | .1 Series Parallel (SP)                 | 22 |

|----------------|-----------------------------------------|----|

| 3.3            | .2 Bridge Link (BL)                     | 23 |

| 3.3            | .3 Total Cross-Tied (TCT)               | 25 |

| Chapter 4 Ha   | ardware Implementation And Results      | 29 |

| 4.1            | Hotspot Mitigation Circuit              | 30 |

| 4.2            | Experimental Setup                      | 30 |

| 4.3            | Graphs                                  | 36 |

| 4.4            | Thermographic Pictures                  | 38 |

| Chapter 5 Co   | nclusion And Observations Of Experiment | 42 |

| 4.1            | Summary                                 | 42 |

| 4.2            | Observation                             | 43 |

| 4.3            | Future Scope                            | 43 |

| List of Public | ations                                  | 44 |

| References     |                                         | 45 |

## LIST OF FIGURES

| Figure No. | Description                                                                                                                                                                          | Page No. |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1        | A Typical Solar Powered System                                                                                                                                                       | 2        |

| 1.2        | PV Module Structure                                                                                                                                                                  | 3        |

| 1.3        | Changes in share of power generation in India in the Stated<br>Policies Scenario, 2010-2040                                                                                          | 6        |

| 2.1        | Equivalent circuit diagram of Photovoltaic cell                                                                                                                                      | 8        |

| 2.2        | Reverse voltage across shaded cell with BPD                                                                                                                                          | 10       |

| 2.3        | I-V characteristic of PV module under the partial shading condition                                                                                                                  | 11       |

| 2.4        | <ul><li>(a) schematic diagram of proposed bypass circuit with mosfet</li><li>(b) panel under fully illuminated condition (c) panel under</li><li>partial shading condition</li></ul> | 13       |

| 2.5        | Scheme of series-parallel topology                                                                                                                                                   | 14       |

| 2.6        | Scheme of Bridge link topology                                                                                                                                                       | 15       |

| 2.7        | Scheme of TCT topology                                                                                                                                                               | 15       |

| 2.8        | Flowchart of Work done                                                                                                                                                               | 16       |

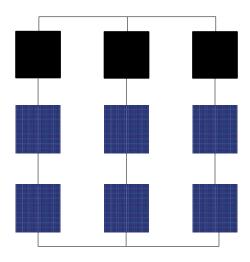

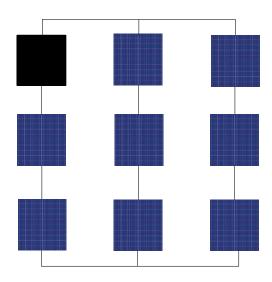

| 3.1        | 3×3 PV array in (a) SP configuration, (b) Bridge link configuration (c) TCT configuration                                                                                            | 19       |

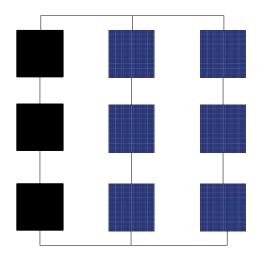

| 3.2  | Representation of Row shading                                                   | 20 |

|------|---------------------------------------------------------------------------------|----|

| 3.3  | Representation of Column shading                                                | 20 |

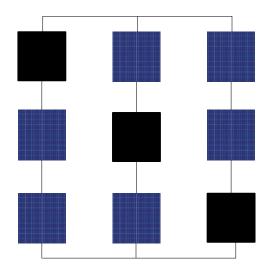

| 3.4  | Representation of Diagonal shading                                              | 21 |

| 3.5  | Representation of Random shading                                                | 21 |

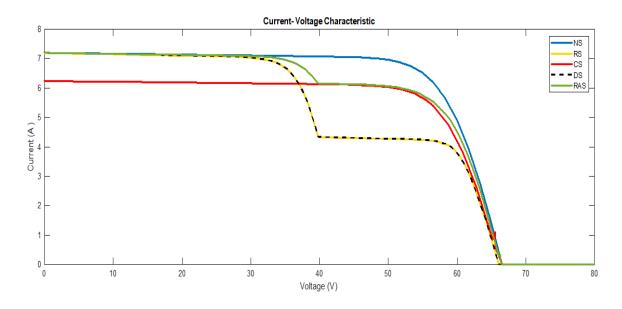

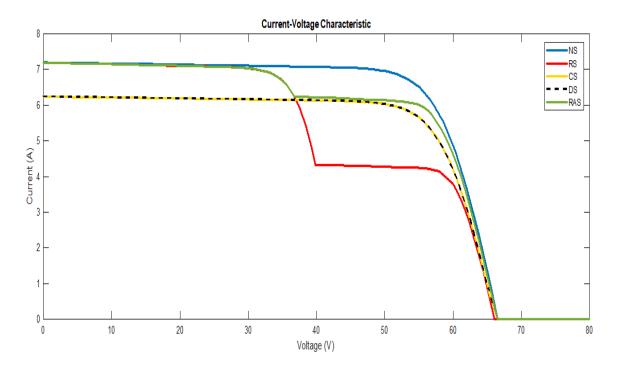

| 3.6  | I-V plot for series-parallel configuration under different PSC for 1000 watt/m2 | 23 |

| 3.7  | P-V plot for series-parallel configuration under different PSC for 1000 watt/m2 | 23 |

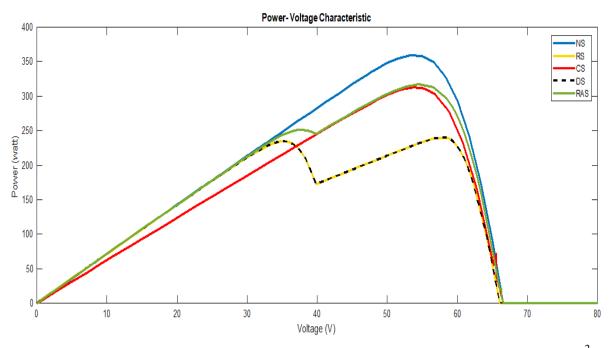

| 3.8  | I-V plot for bridge link configuration under different PSC for 1000 watt/m2     | 24 |

| 3.9  | P-V plot for bridge link configuration under different PSC for 1000 watt/m2     | 24 |

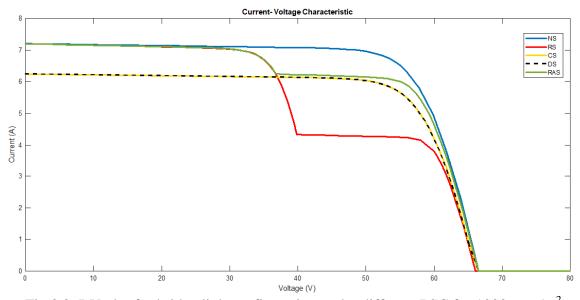

| 3.10 | I-V plot for TCT configuration under different PSC for 1000 watt/m2             | 25 |

| 3.11 | P-V plot for TCT configuration under different PSC for 1000 watt/m2             | 26 |

| 4.1  | Schematic diagram of hardware implantation                                      | 31 |

| 4.2  | Flowchart of working of proposed HSMC                                           | 32 |

| 4.3  | Lab testing of proposed mitigation circuit                                      | 33 |

| 4.4  | Controller testing circuit                                                      | 34 |

| 4.5  | Experimental setup for one cell shading without Bypass Diode                    | 34 |

| 4.6  | Experimental setup for four cell shading with Conventional Bypass Diode                                                  | 35 |

|------|--------------------------------------------------------------------------------------------------------------------------|----|

| 4.7  | Experimental setup for four cell shading with Hotspot<br>Mitigation circuit                                              | 35 |

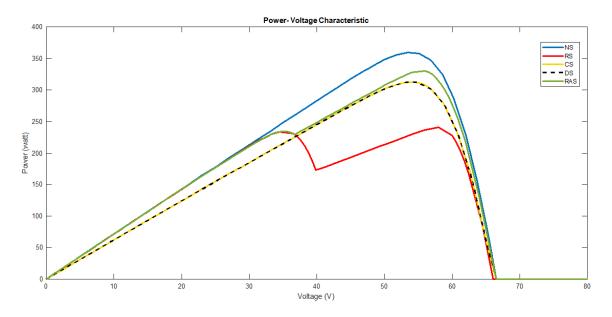

| 4.8  | I-V Plot for Hardware implementation of TCT configuration for four different conditions for radiation 650 to 850 watt/m2 | 37 |

| 4.9  | P-V plot for Hardware implementation of TCT configuration for four different conditions for radiation 650 to 850 watt/m2 | 37 |

| 4.10 | Thermal images of panel under one cell shading without Bypass Diode                                                      | 40 |

| 4.11 | Thermal images of panel under four cell shading with Bypass Diode                                                        | 40 |

| 4.12 | Thermal images of panel under four cell shading with Mosfet                                                              | 41 |

## LIST OF TABLES

| Table No. | Description                                                      | Page No. |  |

|-----------|------------------------------------------------------------------|----------|--|

|           |                                                                  |          |  |

| 1.1       | Different types of renewable energy sources                      | 5        |  |

| 3.1       | Ratings for the PV Module used for Simulation                    | 18       |  |

| 3.2       | GMPP and LMPP during various partial shading conditions          | 27       |  |

| 4.1       | Ratings for the PV Module-EIL40 used for Hardware implementation | 29       |  |

| 4.2       | GMPP and LMPP during various Condition considered                | 38       |  |

| 4.3       | Temperature of the panel under various Conditions considered     | 39       |  |

## LIST OF SYMBOLS AND ABBREVIATIONS

## List of Symbols

| $I_P$            | Photo Current generated by PV Cell (A)              |  |

|------------------|-----------------------------------------------------|--|

| $I_D$            | Diode Current (A)                                   |  |

| $I_{Sh}$         | Shunt Current (A)                                   |  |

| $I_{pv}$         | PV Module Current (A)                               |  |

| Ι                | PV cell terminal Current (A)                        |  |

| V                | PV cell terminal Voltage (V)                        |  |

| $V_d$            | Diode Voltage (V)                                   |  |

| $V_{pv}$         | PV Module Voltage(V)                                |  |

| $V_R$            | Reverse voltage across shaded cell (V)              |  |

| $V_{\mathrm{F}}$ | Voltage supplied by illuminated cells (V)           |  |

| Ν                | Number of serially connected cells in a sub-panel   |  |

| $R_{Se}$         | Series resistance of Photovoltaic cell ( $\Omega$ ) |  |

|                  |                                                     |  |

$R_{Sh}$  Shunt resistance of Photovoltaic cell ( $\Omega$ )

## List of Abbreviations

| BPD    | Bypass Diode                                        |

|--------|-----------------------------------------------------|

| CS     | Column shading                                      |

| DS     | Diagonal shading                                    |

| GMPP   | Global maximum power point                          |

| HSMC   | Hotspot mitigation circuit                          |

| LMPP   | Local maximum power point                           |

| MOSFET | Metal- Oxide- Semiconductor Field Effect Transistor |

| NS     | Non shading                                         |

| PSC    | Partial shading condition                           |

| RAS | Random shading   |  |

|-----|------------------|--|

| RS  | Row shading      |  |

| SP  | Series- parallel |  |

| TCT | Total cross tied |  |

#### **CHAPTER 1**

#### **INTRODUCTION**

#### **1.1 INTRODUCTION**

Continual increase in demand, due to growth in population, technology development, manufacturing advancement and industrial expansion, has led to the expansion of the alternative source of the energy generation system. Due to Environmental issues concern with greenhouse effect and diminution of natural reserves of conventional energy source, globally researchers and investors are trying to develop technologies to harvest energy from renewable source like solar, wind, nuclear etc. Out of them, solar energy is most abundant and easier to convert in required electrical energy.

Photovoltaic (PV) generation systems are being developed in response to the rapidly depleting conventional energy sources and the growing demand for alternative energy sources. PV technology is the most widely chosen alternative source among the various options because it is the most abundant. Its first application in satellites [1] brings it into focus in 1958. PV was only used in a techno-commercial application for a few terrestrial applications for another three decades after that, but the situation has changed with the dawn of the twenty-first century. It is currently more appealing than any other power generation technology ever devised by mankind. As a result, PV technology is currently generates 821 TWh of energy [2].

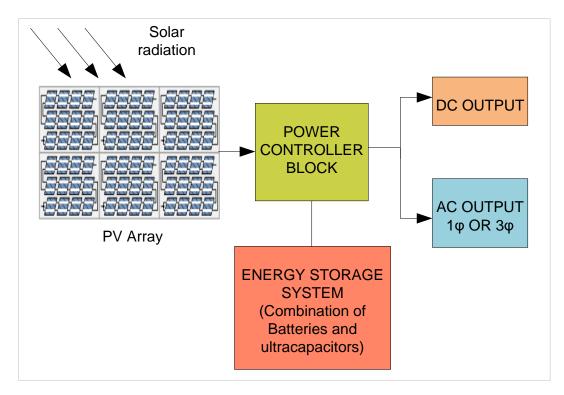

Fig.1.1 shows the typical PV system, which comprises of solar panels, power converter modules, energy storage systems and then connected to the distribution utilities. The number of modules or array used in a PV system depends upon the total output current and voltage requirement of the system it is feeding. A battery storage system (BMS) is required for the stand-alone system to maintain the supply in night and bad weather conditions.

Fig 1.1: A Typical Solar Powered System

Apart from all the advantages it posses, there are some issues which are still needed to be taken care of such as, PSCs, deposition of aerosol and the most important among them is generation of hotspot and this long standing problem is still present even after so much advancement in the technique. However, it does not affect the performance but seriously affect the safety and reliability of the system. Also such problems restrict the system against its full utilization. Depending upon current and voltage level PV systems are basically combination of the PV cells in different configuration. These combinations make the PV systems highly sensitive towards mismatch of PV cells [3].

Practically, cell properties differ greatly from each another because of the prevalence of parametric drifts, surface flaws, lack of homogeneity micro cracks, and caused by potential induced degradation (PID), light induced degradation (LID), and non-uniform ageing of PV cells [4]. Also there are some issues that act as a barrier against the full utilization of the PV technologies such as partial shading condition and aerosol deposition [5].

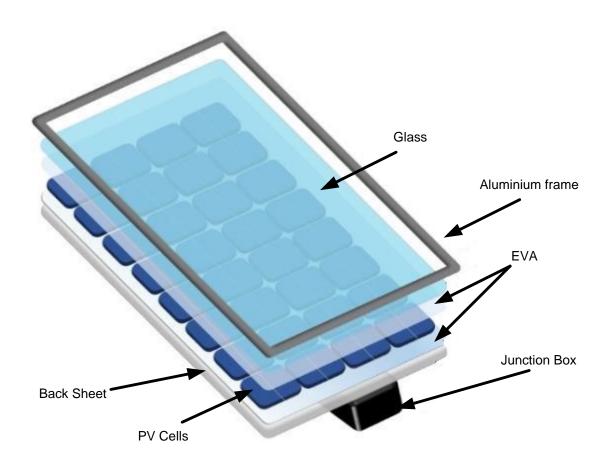

Fig 1.2: PV Module Structure

Thermal runaway or secondary breakdown may occur as a result of elevated temperature, resulting in the flow of reverse current. The PV cells could be irreversibly damaged if the temperature rises to 400°C [6-7]. Under controlled environmental condition, different Experimental investigation shows that PV cell may get damage permanently at 4.6 A of reverse current [8].

Due to the generation of extremely high temperatures, the electrical joints become fragile with time, causing electrical arcing and, in certain cases, shattering of protective glass. Furthermore, the material used in solar modules is highly flammable and can catch fire at high temperature when exposed to oxygen [9]. As a result, adverse climatic variables and mismatch situations have a negative impact on PV module efficiency and performance ratios, as well as posing serious safety and reliability concerns for PV systems [10-13].

Combination of multiple PV cells serially and parallelly makes one PV array which are then connected in different configuration to maximize the output generated. To enhance the terminal voltage photovoltaic cells are connected serially, similarly to enhance the output current photovoltaic cells are connected parallelly. The solar energy is the most popular form of renewable energy as it is available most abundantly, lower cost of generation, produce clean and green energy but along with all the advantages it possess , it also has certain serious issues associated with it like deposition of aerosol, partial shading condition (PSCs) and generation of hotspot. Researches and study are being done to resolve these issues in order to produce a PV system with high efficiency, low cost and high reliability [14]. Some of the methods are differential converters and innovative array topologies [15], proposing a new innovative hotspot mitigation technique, module level dcdc converters [16] and inverters [15].

In the present work a hotspot mitigation circuit is proposed which enable the panel to be completely cutoff from the string which is under the condition of PSCs such that the partially shaded cell will no longer experience the reverse voltage across itself hence there will be no generation of hotspot will . This prevents the possibility of thermal runaway, increase the life of the PV cell and also the reliability of the system will be increased. The modified circuit is simulated in MATLAB/Simulink platform and the corresponding results are observed. Then later the results are validated through hardware implementation.

#### **1.2 RENEWABLE ENERGY RESOURCES**

From different researches and articles it is clearly established that energy producing from fossil fuels is polluting the environment and become one of the major source of greenhouse gases like oxides of nitrogen and sulphur, carbon monoxide, PM4 and PM10 which results in occurrence of major issue like respiratory diseases [17-19]. So for the betterment of both environment and the health of the people, steps are taken to shift the power generation more towards renewable energy sources. Certain issues related to renewable energy generation, such as improving efficiencies, reliability, and related technical issues, are the subject of research and development.

Different types of renewable energy sources are mentioned in Table 1.1.

| RENEWABLE<br>RESOURCES | SOURCES                                  | OUTPUT               |

|------------------------|------------------------------------------|----------------------|

| Solar energy           | Storing heat from sun                    | Electricity and heat |

| Hydro power            | Water flowing through dams               | Electric Energy      |

| Hydrogen Fuels         | Burning hydrogen gas                     | Motion power         |

| Wind energy            | Collection of winds by<br>turbines       | Electric energy      |

| Geothermal             | Extracting steam, hot water from earth   | Electricity and heat |

| Biological materials   | Burns of animal waste and plant material | Heat energy and fuel |

| Nanotechnology         | Using unique property of material        | Electric energy      |

Table 1.1: Different types of renewable energy sources

#### **1.3 GLOBAL INITIATIVES**

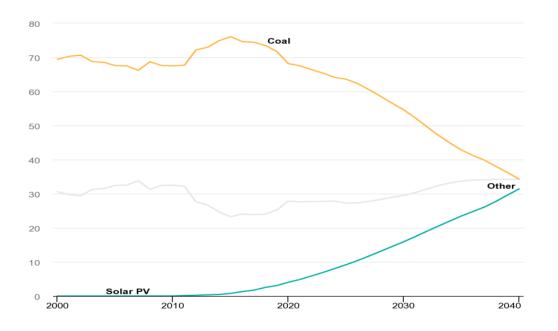

India has set more ambitious targets for 2030 in order to achieve net zero emissions by 2070, including installing 500 Giga watts of renewable energy capacity, lowering its economy's emissions intensity by 45 percent, and reducing a billion tones of  $CO_2$ . These goals are ambitious, however the best part is that India is well on its way to becoming a clean energy powerhouse. It has already met 40% of its power capacity from non-fossil fuels, nearly nine years ahead of commitment made at COP 21- Paris Summit, and the share of solar and wind in India's energy mix has increased dramatically [14].

India is gaining more renewable electricity capacity as compared to other major economy, with new capacity expected to double by 2026. The country is also one of the largest producers of modern bio energy in the world, with big plans to expand its use throughout the economy. After the United States and Brazil, the IEA predicts that India will surpass Canada and China in the coming years to become the world's third largest ethanol market.

Fig 1.3: Changes in share of power generation in India in the Stated Policies Scenario, 2010-2040 [17]

#### **1.4 PROBLEM STATEMENT**

Renewable energy source is the future of electrical energy generation as they are environmental friendly and also because conventional energy sources are not enough to meet the demand. But with current technologies and practices we are not able to generate its full potential. Among different renewable sources available, solar energy is the most promising method due to its widespread availability, relatively lower cost of generation, produces clean and green energy. But despite of all of its advantages it is not efficient and reliable and largely depends on the Partial shading conditions. The generation of hotspot is the main drawback of the PV system. Under partial shading condition, the shaded cell experience the reverse biased voltage which causes generation of hotspot and lead to sudden rise in temperature which in turn can permanently damage the PV cell, can cause fire, joints may become fragile or shattering of protective glass. To overcome the problem of hotspot generation we need to research and study the methods which can make the photovoltaic system more reliable and hence improve its performance. So in this work, a new mitigation circuit is proposed whose objective is to improvise the photovoltaic system such that effect of partial shading over it can be reduced.

#### **CHAPTER 2**

#### THEORETICAL BACKGROUND

#### 2.1 MODELLING OF PV CELL

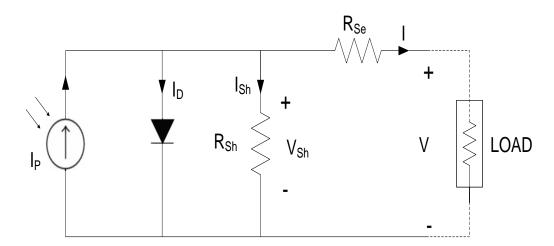

A PV panel contains number of photovoltaic cell which are interconnected serially or parallelly as per the output voltage and output current requirements. Fig. 2.1 shows the circuit diagram of a photovoltaic cell. In the Fig. 2.1,  $I_p$  is photocurrent,  $I_d$  is photodiode current,  $R_{sh}$  is shunt resistance depicting leakage current and  $R_{se}$  is series resistance depicting internal resistance of the cell, I is cell current and V is voltage produce by one cell [20].

Fig 2.1: Equivalent circuit diagram of Photovoltaic cell

Current and voltage equations of a photovoltaic cell are as follows [21]:

$$I = I_p - I_d - I_{sh} \tag{2.1}$$

$$I_{d} = I_{o} \left[ e^{\frac{V + IR_{se}}{V^{\alpha}}} - 1 \right]$$

(2.2)

$$I = \frac{V + IR_{se}}{R_{sh}}$$

(2.3)

From equations (2.1), (2.2), (2.3) we get:

$$I = I_p - I_o \left[ e^{\frac{V + IR_{se}}{V_t}} - 1 \right] - \frac{V + IR_{se}}{R_{sh}}$$

(2.4)

Where I<sub>o</sub> is saturation current of the photodiode,  $V_t = \frac{AkT}{q}$  in which A is ideality factor, k is Boltzmann constant, T is temperature of the cell (Kelvin) and q is elementary charge[22,23]. From above equations it can be inferred that photocurrent is dependent upon the temperature of the cell. Generated photocurrent rise slightly with rise in temperature but the saturation current reduces exponentially with rise in temperature hence decreasing cell voltage hence the efficiency and reliability of PV system decreases [24].

If  $N_S$  numbers of cells are connected serially and  $N_P$  numbers of cells are connected parallelly in the photovoltaic array than array current  $I_A$  is:

$$I_{A} = N_{P}I_{P} - N_{P}I_{O} \left[ e^{\frac{V + IR_{se}}{V_{t}}} - 1 \right] - \frac{N_{P}V + IN_{S}R_{se}}{N_{S}R_{sh}}$$

(2.5)

#### 2.2 POWER DISSIPATION ACROSS SHADED SOLAR CELLS

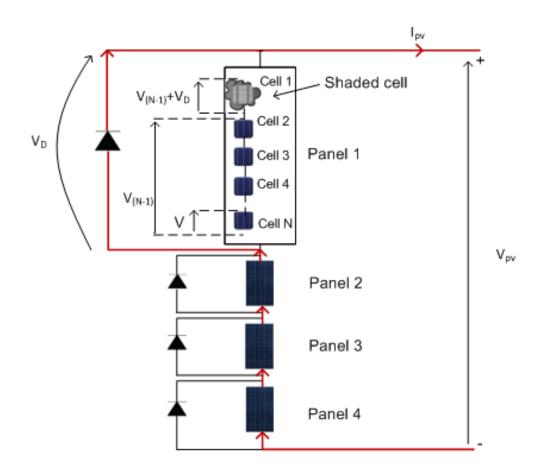

To decrease the effects of the partial shading condition, bypass diode is use which is connected in antiparallel manner across a panel. Under full illumination, the Bypass diode is reversed biased and the entire output current is passed through panel itself but under the condition of partial shading the bypass diode get forward biased due to the reversal of voltage across the shaded cell and bypass the entire PV panel across which it is connected [25-28].

To understand the mechanism, consider a sub panel in which N solar cells are connected serially with a bypass diode, if a cell experienced partial shading than its photo generated current is significantly degrade which in turns limit the serial current. A bypass diode is used across the panel to rectify this problem, which gets forward biased during shading condition and provide an alternate path for series current which reverse bias the shaded cell.

Fig 2.2: Reverse voltage across shaded cell with BPD

For the close loop created by the BPD, we can use Kirchhoff's voltage law to quantify reverse voltage across shaded cells as in (2.6).

$$-V_{R(max)} = \sum_{N=1}^{m-1} V_{OC,N} + V_D$$

(2.6)

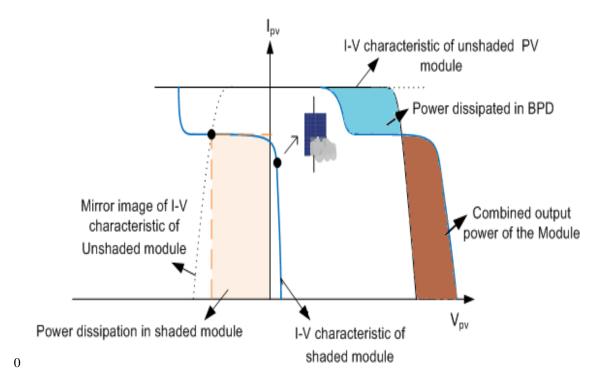

The current-voltage characteristic corresponding to the effected cell is explained in Fig. 2.3, in which slope is determined by the shunt resistance. The electrical power dissipated by the shaded cell which is under reverse bias condition can be determined by

means of geometrical approach [29]. In Fig. 2.3, the point represents the point of operation of a solar cell that is partially shaded and product of the current-voltage gives the corresponding dissipated power. It should be observed that partially shaded region causes the maximum amount of power produced by the illuminated cells to be absorbed by the shaded cell, which results in a larger temperature rise [30].

Fig 2.3: I-V characteristic of PV module under the partial shading condition

Maximum reverse voltage for 0.5V forward voltage drop of BPD and 0.6V open circuit voltage of PV cells is calculated as 19.1V, 14.3V and 11.9V for 96, 72.60 cell module respectively [31]. This much voltage level should be under safe limits and there effects could be neglected but by different Reverse breakdown characteristics of PV cells changes due to different manufacturing processes as micro defects get generated.

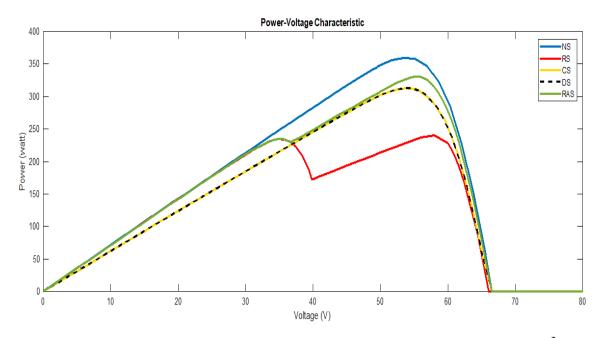

#### 2.3 PROPOSED HOT SPOT MITIGATION CIRCUIT

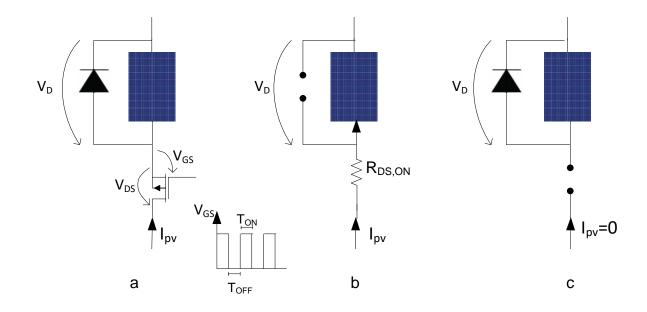

The circuit connection for proposed topology is shown in Fig. 2.4. Here MOSFET is used as a voltage controlled switch which offers very low on state resistance to serial

current [32]. When the panel is under the condition of full illumination, the voltage at the output terminal is high, which coincides with the MOSFET's input voltage, causing it to turn on and offer extremely low resistance. However, when the panel is under partial shading condition, the voltage at the input terminal is low, reducing the input of the MOSFET and thus its current capability. In this case, the MOSFET will turn off and the serial current would flow through bypass diode, resulting in an overall voltage across the MOSFET and the panel equal to  $V_D$ . As a result of the MOSFET, the peak reverse voltage across the shaded cell gets reduced. This condition is formulated as follows:

$$V_{\rm R} = (N - 1)V_{\rm F} + V_{\rm D} - V_{\rm DS}$$

(2.7)

By this arrangement it was found that reverse voltage across shaded cell is decreased significantly. This is shown in the next section through simulation results and the various results are then compared for different shading condition. The reduced voltage across the shaded cell also implies that corresponding power dissipated by the shaded cell is also decreased which in turn results in negligible temperature rise hence the problem of hotspot mitigation is largely reduced. The presence of MOSFET reduces the possibility of solar panel to reach the unsafe temperature which could damage the possibility of the rupturing of module. It should be noted that rest of the power which earlier dissipated by the shaded cell is now dissipated by the MOSFET so care should be taken during the selection of the MOSFET and other components. Also the overall cost of the design is also negligible with respect to the advantage it generates.

A gate triggering circuit would be needed to automatically generate the gate pulse for the MOSFET by monitoring the hot spot condition, halting the tracking of the maximum power point, and frequently measuring the module's impedance, all of which would make the circuit more complex. The switch activation circuit's reliability, as well as its reliance on site conditions and non-significant cost concerns, has all prevented the widespread use of various similar active bypass switches reported by researchers over the years [33-34].

Fig 2.4: (a) schematic diagram of proposed bypass circuit with MOSFET (b) panel under fully illuminated condition (c) panel under partial shading condition

#### 2.4 CIRCUIT TOPOLOGIES

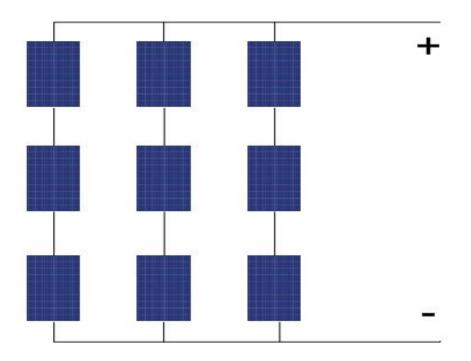

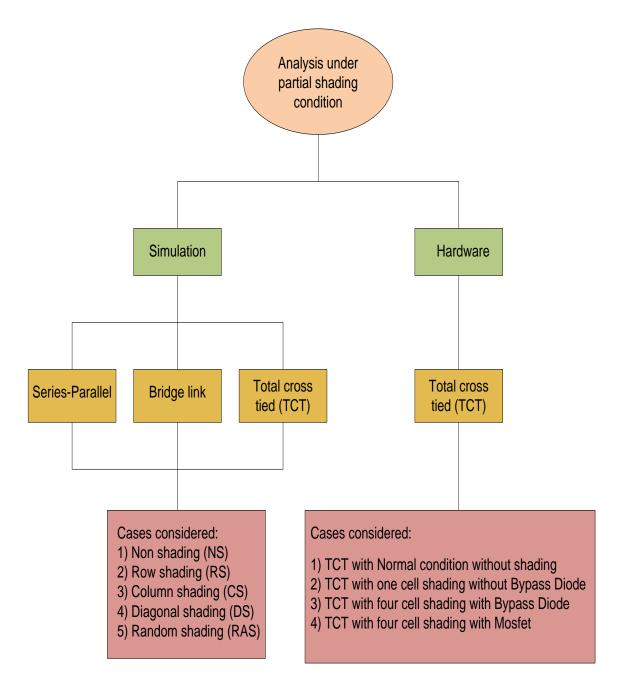

PV panels may be rearranged in a variety of methods to minimize the effects of partial shading and maximize power generation. The ratings of the PV system to be developed will influence the number of PV panels to be linked in series or parallel. Photovoltaic cells are linked serially to increase terminal voltage, while photovoltaic cells are connected parallelly to increase output current. Series-connected PV systems are the most common arrangement. On this basic design, the reconfiguration entails extra connections. The interconnection technique lowers power mismatch losses and partial shading effects [25,35,36]. Different topologies are suggested by many scholars having different advantages over each other. In this work,  $3 \times 3$  PV array is used for the analysis so total 3 topologies are possible which are as follows:

1) Series-parallel (SP)

2) Bridge link (BL)

3) Total cross-tied (TCT)

#### 2.4.1 SERIES-PARALLEL (SP)

In this configuration certain number PV panels are connected serially to form a string than numbers of strings are connected parallel. This configuration is widely use in industrial application because of its simplest connection. Many authors recommended that this topology generates maximum power output in the absence of partial shading. It has less number of wires so easy to connect and price is least among all the topologies.

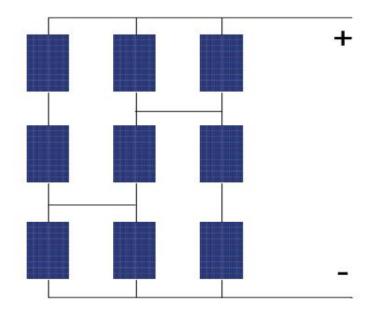

Fig 2.5: Scheme of series-parallel topology

#### 2.4.2 BRIDGE LINK (BL)

Bridge link configuration is modified version of series-parallel configuration in which alternate panels are connected together. It is a bridge like structure between two parallel strings. The impact of partial shading is lesser compared to the series parallel configuration.

Fig 2.6: Scheme of Bridge link topology

### 2.4.3 TOTAL CROSS-TIED (TCT)

This topology is most supported by the scholars through different studies. In this configuration, all the panels are interconnected providing alternate path for current in case of partial shading hence the effect of partial shading is least in this case proved later in this work.

Fig 2.7: Scheme of TCT topology

#### 2.5 SCHEME OF EXPERIMENT

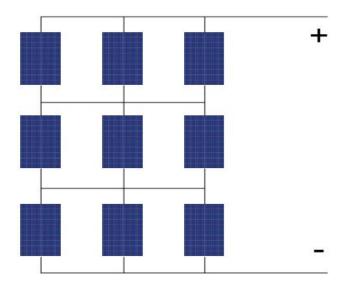

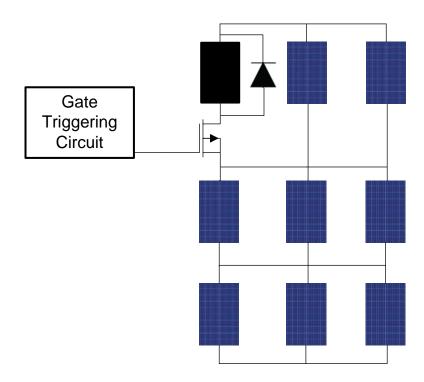

Scheme of experiment is demonstrated through flow chart as shown in Fig. 2.8.

Fig 2.8: Flowchart of Work done

First all the topologies are studied and simulated along with hotspot mitigation circuit (HSMC) under different partial shading condition through MATLAB/SIMULINK

software. The results are then formulated and compared in terms of maximum power generated and the effect of partial shading conditions. From the results, it is inferred that TCT is best configuration and generate maximum power during partial shading hence latter only TCT is performed on the Hardware setup of  $3\times3$  PV array. Again P-V and I-V characteristics are plotted and the corresponding results are analyzed. Also Thermographic images are taken for four different cases and are then compared to judge the temperature difference. Then finally on the basis of the results generated the study is concluded.

#### **CHAPTER 3**

## SIMULATION MODELING AND RESULTS

In this chapter simulation results of the experiment under different partial shading conditions and the corresponding inference are included.

#### 3.1 RATINGS OF PV MODULE

For simulation the Panels are designed for the ratings same as taken for the hardware analysis. The panel's specifications are listed in Table 3.1 below.

| Electrical parameters                       | Ratings                 |

|---------------------------------------------|-------------------------|

| Number of cells                             | 36                      |

| Maximum Power (P <sub>max</sub> )           | 40W                     |

| Voltage at Maximum Power (V <sub>mp</sub> ) | 18.00V                  |

| Current at Maximum Power (I <sub>mp</sub> ) | 2.22A                   |

| Open Circuit Voltage(V <sub>oc</sub> )      | 22.18V                  |

| Short Circuit Current (I <sub>sc</sub> )    | 2.40A                   |

| Temperature at STC                          | 25 °C                   |

| Irradiance at STC                           | $1000 \text{ watt/m}^2$ |

Table 3.1: Ratings for the PV Module used for Simulation

For better comparison between hardware and software results, it is better to use the equipments of similar ratings.

#### 3.2 Simulation Modeling

In this section, the simulation modeling of a  $3\times3$  PV array is discussed, and the associated findings are provided for two distinct topologies, namely series-parallel and TCT, at a constant temperature of  $25^{\circ}$  C, as well as under various solar irradiances measured in watt/m<sup>2</sup> [37]. The design voltage level of the plant and the nominal voltage of the modules dictate the number of modules that should be linked serially. The number of strings (serially linked modules) that can be connected parallelly is determined by plant capacity and land availability. [21, 38] explains the linkages and comparative study of the various topologies in detail.

Fig 3.1: 3×3 PV array in (a) SP configuration, (b) Bridge link configuration (c) TCT configuration

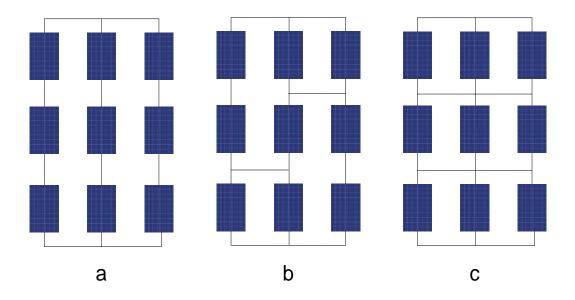

For understanding the behavior of PV array during various partial shading conditions (PSC), we have taken 4 different condition of partial shading. Those are: non shading (NS), row shading (RS), column shading (CS), diagonal shading (DS) and random shading (RAS).

Non-shaded Condition (NS): In this case all the panels are fully and uniformly illuminated.

**Row Shading Condition (RS):** In this case, first panel of each string which are connected parallelly are shaded i.e. one row is shaded

Fig 3.2: Representation of Row shading

**Column Shading Condition (CS):** In this case, one entire string i.e. serially connected panels are shaded.

Fig 3.3: Representation of Column shading

**Diagonal Shading Condition (DS):** In this case, diagonal panels of PV array matrix are shaded.

Fig 3.4: Representation of Diagonal shading

**Random Shading Condition (RAS):** In this case, panels are shaded randomly i.e. they do not form any specific pattern.

Fig 3.5: Representation of Random shading

All the cases of shading are taken for the analysis of PV system. For fully illuminated condition, Irradiance is taken 1000watt/m<sup>2</sup>. For the shading condition the, 600 watt/m<sup>2</sup> irradiance is taken. For all the test condition, 25°C temperature is taken.

The MOSFET in the proposed mitigation circuit is in the conduction state in full illumination and should be switched off in partial shade (PSC). The terminal voltage of each panel is monitored and compared in a logic circuit for regulating gate pulses, and no gate pulse is generated for the panel with the lowest voltage. As a result, when the panel is partially shaded, it is completely shut off from the remainder of the connection, and the serial current passes through the bypass diode. Although the total power and current output will be lowered, when the panel is cutoff, the temperature will not rise and will remain within the safety limit, resolving the problem of hotspot generation.

#### 3.3 RESULTS

Current-Voltage and Power-Voltage characteristics for various topologies, as well as variable configuration and shading irradiance, are included in the simulation results. In [39,40] the current-voltage and power-voltage characteristics without a mitigating circuit are explained. The Fig. 3.6 to Fig. 3.11 indicates the results of the proposed mitigation circuit:

#### 3.3.1 Series parallel (SP)

Due to the ease of connection and implementation, this topology is widely accepted and used for project implementation by various power producers. According to the voltage and current handling requirements of inverters, topology consists of some series paths and some parallel paths.

Series Parallel configuration is subjected to different partial shading conditions and current-voltage and power-voltage characteristics are plotted.

From current-voltage and power-voltage characteristics, it can be observed that maximum power output is 359.7 watt at 53.33 V under uniform irradiance at 1000 watt/m<sup>2</sup>.

Fig 3.6: I-V plot for series-parallel configuration under different PSC for 1000 watt/m<sup>2</sup>

Fig 3.7: P-V plot for series-parallel configuration under different PSC for 1000 watt/m<sup>2</sup>

#### 3.3.2 Bridge link (BL)

When compared to series parallel, BL has a higher number of parallel paths, which helps to reduce voltage mismatch loss and improve performance ratio. A connecting lead connects two parallelly connecting paths in the same way that a bridge connects two nearby roads.

Fig 3.8: I-V plot for bridge link configuration under different PSC for 1000 watt/m<sup>2</sup>

Fig 3.9: P-V plot for bridge link configuration under different PSC for 1000 watt/m<sup>2</sup>

Bridge link configuration is subjected to different partial shading conditions and current-voltage and power-voltage characteristics are plotted.

From current-voltage and power-voltage characteristics, it can be observed that maximum power output is 359.7 watt at 53.42 V under uniform irradiance at 1000 watt/m<sup>2</sup>.

#### **3.3.3** Total cross-Tied (TCT)

In comparison to series parallel and bridge links, the structure has a greater number of interconnecting paths, which helps to reduce voltage mismatch losses and provide an alternate path for current in the event of partial shading. It improves the efficiency and performance ratio.

Total cross-Tied configuration is subjected to different partial shading conditions and current-voltage and power-voltage characteristics are plotted.

Fig 3.10: I-V plot for TCT configuration under different PSC for 1000 watt/m<sup>2</sup>

Fig 3.11: P-V plot for TCT configuration under different PSC for 1000 watt/m<sup>2</sup>

From current-voltage and power-voltage characteristics, it can be observed that maximum power output is 359.7 watt at 53.44 V under uniform irradiance at 1000 watt/m<sup>2</sup>.

The current-voltage and power-voltage characteristics of various configurations are illustrated in Fig. 3.6 to Fig. 3.11, indicating that the panel's performance may be enhanced by employing a modified bypass design. By analyzing several attributes, it can be deduced that the TCT configuration produces the best outcomes and has the smallest drop. As a result, we picked TCT setup for the experiment, and the resulting findings are reported in the next section.

From Table 3.2 it can be observed that there are different power points, also we get global maximum and local maximum power points which cause problem for conventional power tracing algorithms.

| Topology            | PSCs | GMPP           |             |                 | LMPP           |                |                 |

|---------------------|------|----------------|-------------|-----------------|----------------|----------------|-----------------|

|                     |      | Voltage<br>(V) | Current (A) | Power<br>(watt) | Voltage<br>(V) | Current<br>(A) | Power<br>(watt) |

| Series-<br>Parallel | NS   | 53.33          | 6.743       | 359.7           | -              | -              | -               |

|                     | RS   | 58.6           | 4.091       | 239.7           | 35.41          | 6.62           | 234.4           |

|                     | CS   | 54.55          | 5.742       | 312.4           | -              | -              | -               |

|                     | DS   | 58.6           | 4.091       | 239.7           | 35.41          | 6.62           | 234.4           |

|                     | RAS  | 54.55          | 5.809       | 31 6.9          | 37.92          | 6.628          | 251.3           |

| Bridge-<br>Link     | NS   | 53.42          | 6.725       | 359.7           | -              | -              | -               |

|                     | RS   | 58             | 4.151       | 240.8           | 34.15          | 6.707          | 233.9           |

|                     | CS   | 53.79          | 5.808       | 312.5           | -              | -              | -               |

|                     | DS   | 53.79          | 5.808       | 312.5           | -              | -              | -               |

|                     | RAS  | 54             | 6.123       | 326.1           | 35.56          | 6.707          | 234.3           |

| TCT                 | NS   | 53.44          | 6.732       | 359.7           | -              | -              | -               |

|                     | RS   | 58             | 5.376       | 240.8           | 35.76          | 6.589          | 233.9           |

|                     | CS   | 54.17          | 5.77        | 312.5           | -              | -              | -               |

|                     | DS   | 54.17          | 5.77        | 312.5           | -              | -              | -               |

|                     | RAS  | 55.17          | 4.28        | 330.9           | 34.96          | 6.707          | 234.4           |

Table 3.2: GMPP and LMPP during various partial shading conditions

The current-voltage and power-voltage characteristics of various configurations are illustrated in Fig. 3.6 to Fig. 3.11, indicating that the panel's performance may be enhanced by employing a modified bypass design. By analyzing several attributes, it can be deduced that the TCT configuration produces the best outcomes and has the smallest drop. As a result, we picked TCT setup for the experiment, and the resulting findings are reported in the next section.

# **CHAPTER 4**

# HARDWARE IMPLEMENTATION AND RESULTS

In the previous section, simulation results has been analyzed and studied extensively and among different topologies it was observed that TCT configuration generates best results under partial shading conditions. TCT has maximal connectivity, which gives it the benefit of improved efficiency since the interconnection would provide an alternate channel to the current that was altered owing to partial shade [41]. TCT configuration is utilized for hardware validation of the proposed mitigation circuit

The panel's specifications are listed in Table 4.1 below.

| Electrical parameters                       | Ratings                 |

|---------------------------------------------|-------------------------|

| Number of cells                             | 36                      |

| Maximum Power (P <sub>max</sub> )           | 40W                     |

| Voltage at Maximum Power (V <sub>mp</sub> ) | 18.00V                  |

| Current at Maximum Power (I <sub>mp</sub> ) | 2.22A                   |

| Open Circuit Voltage(Voc)                   | 22.18V                  |

| Short Circuit Current (I <sub>sc</sub> )    | 2.40A                   |

| Tolerance                                   | 0 to 5 W                |

| Temperature at STC                          | 25 °C                   |

| Irradiance at STC                           | $1000 \text{ watt/m}^2$ |

Table 4.1: Ratings for the PV Module-EIL40 used for Hardware implementation

#### 4.1 Hotspot Mitigation Circuit

The conventional Bypass diode has the disadvantage of not completely cutting off a panel that is partially shaded, allowing some current to pass through. Although it would be lesser than the load current, it is sufficient to generate hotspot in the panel. As a result, we need a circuit that will completely turn off the panel, allowing the panel's temperature to be maintained even when partially shaded. The hotspot mitigation circuit is designed to solve this problem by acting as a switch to turn off the panel when it is partially shaded.

The mitigation circuit employs a MOSFET, which is a bidirectional device, necessitating the usage of an external triggering circuit to generate the gate pulse. The triggering circuit measures the voltage and current of each panel constantly, calculates the average value, and deducts the voltage and current values of each panel from the average value. Because the panel that is shaded has the greatest difference, an external triggering circuit is used to switch off the MOSFET attached to that panel. This will disconnect the whole panel from the rest of the system. The terminal voltage will stay same as the configuration is TCT, and the reduction in power is insignificant in comparison to the increased reliability.

# 4.2 Experimental setup

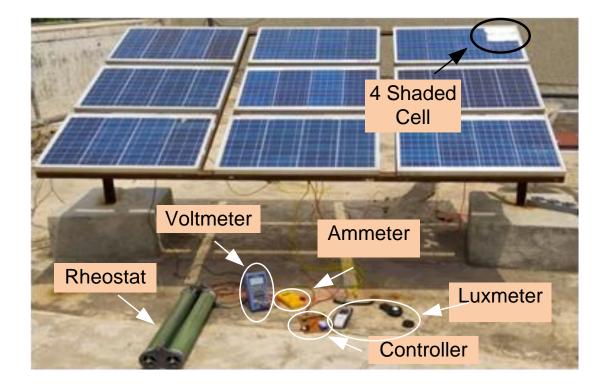

In the experimental setup following devices are utilized:

- 3×3 PV module

- Luxmeter

- Rheostat

- Ammeter

- Connecting leads

#### Hotspot Mitigation Circuit

The Experiment is being performed on the  $3\times3$  PV module connected in TCT configuration. Variable rheostat of  $100\Omega/5A$  is used to vary load and hence trace the power-voltage and current-voltage characteristics. Luxmeter is a device which measures the amount of light falling on an area and is used for observing irradiance which helps in calculation of efficiency. Ammeter and voltmeter are used to measure voltage and current at particular load point. Connecting leads are used to connect modules as per requirement or topology. Hotspot mitigation circuit is connected in series with the panel which is under the affect of partial shading.

Fig 4.1: Schematic diagram of hardware implementation

Fig. 4.1 depicts the schematic circuit design for the Hardware implementation set up. For hardware experimentation, shading over one panel is chosen for legibility and clarity, and the associated results are observed.

Fig.4.2 Flowchart of working of proposed HSMC

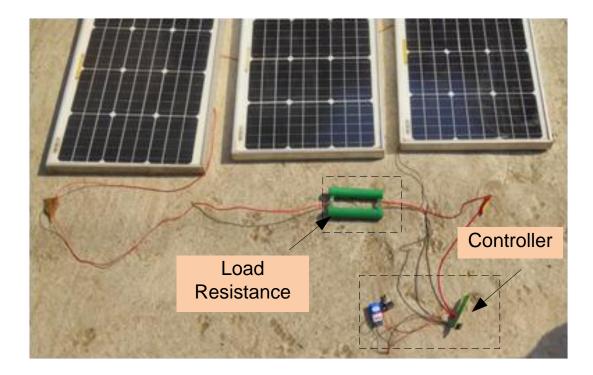

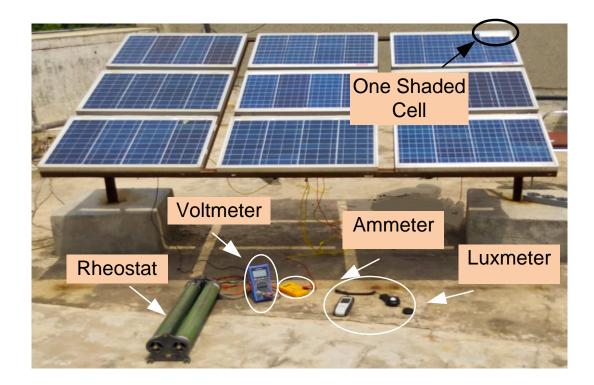

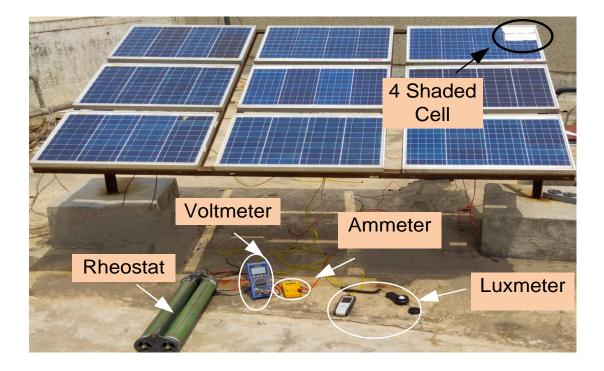

Following Figs shows the experimental setup. A total of  $3\times3$  panels, each rated at 40 watts, are used. To create the requisite V-I and P-V characteristics, a rheostat of  $100\Omega/5$  A is utilized as a load. Natural irradiance ranges from 650 watt/m<sup>2</sup> to 800 watt/m<sup>2</sup>. The experiment uses IRFP 260 since its R<sub>DS(ON)</sub> is exceptionally low, at 0.055 $\Omega$ . So each MOSFET's on-state power loss is 0.266 watt, and the overall set power loss is 2.394 watt, which is quite low and thus acceptable. It can be seen from the characteristic that when four cells are shaded and a MOSFET is employed, the produced power is lower than when simply BPD has been used. However, this loss is sparse and may be overlooked if the accompanying increase in reliability is large.

All four cases were photographed in the same environment and under the same operational conditions.

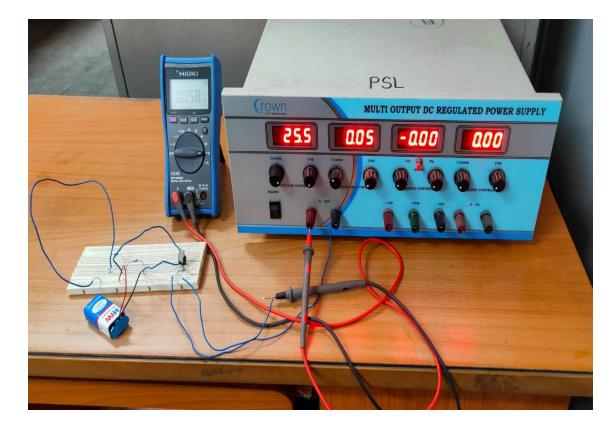

Fig 4.3: Lab testing of proposed mitigation circuit

Fig 4.4: Controller testing circuit

Fig 4.5: Experimental setup for one cell shading without Bypass Diode

Fig 4.6: Experimental setup for four cell shading with Conventional Bypass Diode

Fig 4.7: Experimental setup for four cell shading with Hotspot Mitigation circuit

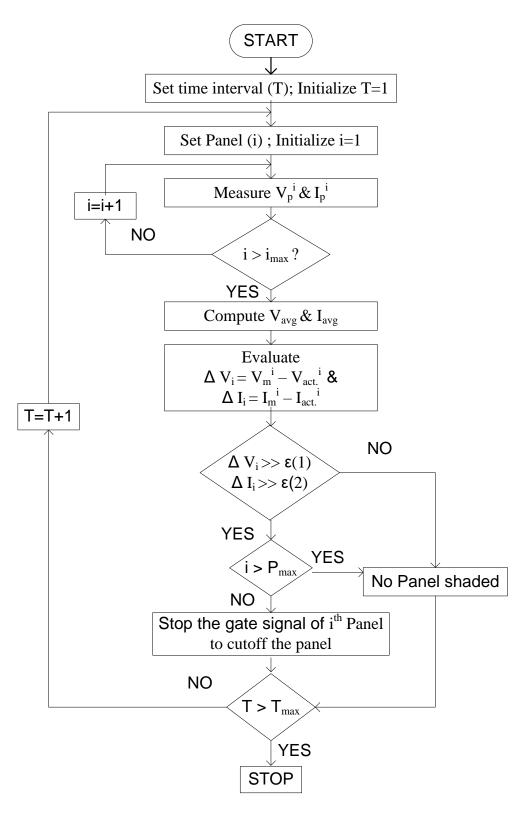

#### 4.3 Graphs

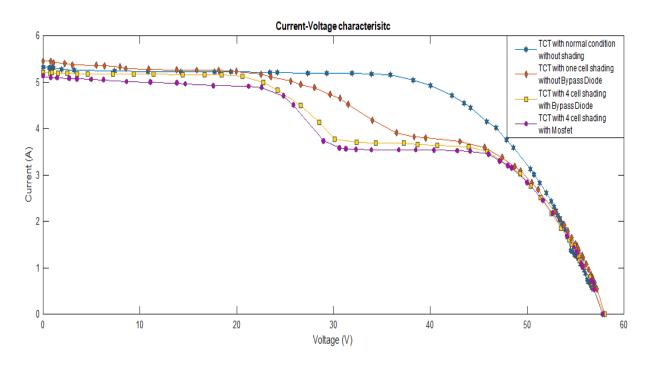

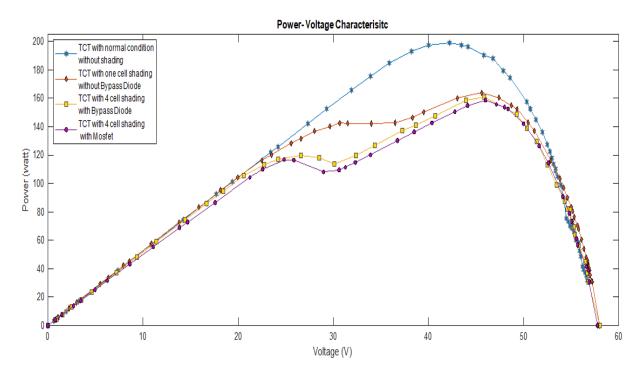

The first case is TCT with no shading, while the second case has one shaded cell. In the second scenario, it was discovered that when up to two cells are shaded, the bypass diode does not become forward biased. In the third case, four cells are shaded at the same time, and BPD gets forward biased. Four cells are shaded in the fourth case, along with the proposed mitigation circuit.

Characteristic of current-voltage are exhibit in Fig. 4.8 and Fig. 4.9 demonstrate the power-voltage characteristics obtained by altering the load from open circuit to short circuit. It can be seen from the characteristic that when four cells are shaded and a MOSFET is employed, the produced power is lower than when simply BPD has been used. However, this loss is sparse and may be overlooked if the accompanying increase in reliability is large.

As shown in the Table 4.2, there is a high chance of multiple maximum power points arising due to partial shading, which causes a problem for traditional power point tracing algorithms. Rather than reaching global maximum power, they become stuck at local maximum power.

From Table 4.2 it can be observed that due to controller the global maximum power generated is 158.7 watt and the local maximum power generated is 117.7 watt while with bypass diode the global maximum power generated is 161 watt and the local maximum power generated is 119.7 watt. The power difference between the global maximum power generated and the local maximum power generated in two cases are 2.3 watt and 2 watt respectively. The power drop due to Controller is negligible which can be ignored if the reliability is significantly improved.

Fig 4.8: I-V Plot for Hardware implementation of TCT configuration for four different conditions for radiation 650 to 850 watt/m<sup>2</sup>

Fig 4.9: P-V plot for Hardware implementation of TCT configuration for four different conditions for radiation 650 to 850 watt/m<sup>2</sup>

|                                                         | GMPP           |                |                 | LMPP           |                |                 |

|---------------------------------------------------------|----------------|----------------|-----------------|----------------|----------------|-----------------|

| Condition                                               | Voltage<br>(V) | Current<br>(A) | Power<br>(watt) | Voltage<br>(V) | Current<br>(A) | Power<br>(watt) |

| TCT with<br>normal<br>condition<br>without shading      | 42.22          | 4.71           | 198.9           | -              | -              | -               |

| TCT with one<br>cell shading<br>without Bypass<br>Diode | 45.62          | 3.59           | 163.8           | 30.67          | 4.65           | 142.6           |

| TCT with 4 cell<br>shading<br>with Bypass<br>Diode      | 45.86          | 3.51           | 161             | 26.59          | 4.5            | 119.7           |

| TCT with 4 cell<br>shading<br>with MOSFET               | 46             | 3.4            | 158.7           | 28.96          | 4.02           | 117.7           |

Table 4.2: GMPP and LMPP during various conditions considered

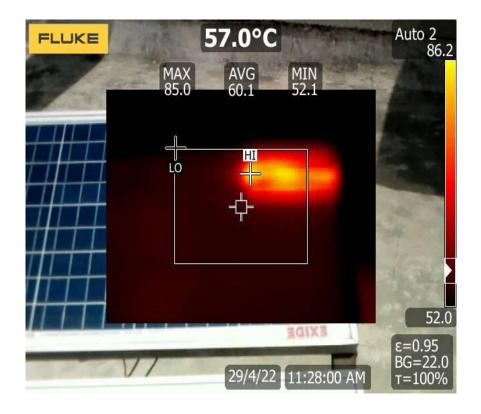

## 4.4 Thermographic pictures

Thermographic pictures are captured for all three conditions, as shown in Fig. 4.9 to Fig. 4.11, because it is the most effective way for identifying the position of a hotspot as well as its temperature, which may be used to estimate the mismatch condition and remark on reliability improvement [42].

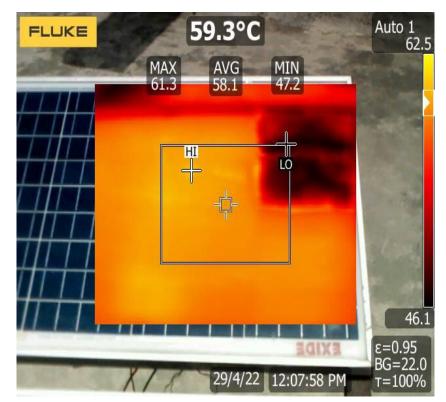

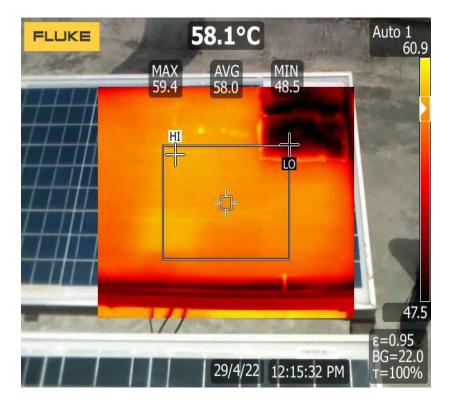

Fig. 4.10 shows that when only one cell is shaded for 10 minutes, the temperature of the hotspot formed rises to 85°C, while the balance of the panel remains at 52.1°C. The temperature has risen by 32.9 °C or 63.14 percent. Fig. 4.11 and Fig. 4.12 show that when the temperature of the shaded cell is 47.2°C and the panel temperature is 61.3°C, the temperature differential is 14.1°C or 23 percent of the panel temperature. The temperature of the shaded cell is reduced to 48.5 degrees Celsius using HSMC, while the remainder of the panel is 59.4 degrees Celsius, resulting in a temperature differential of 10.9 degrees Celsius, or 18.35 percent of the panel temperature. With HSMC, the temperature drops by 4.65 percent more than without it. As a result, the reliability has greatly improved. The above results are tabularized in Table 4.3.

| Condition                                            | Temperature of<br>Non Shaded area<br>of the panel | Temperature of<br>the Shaded area of<br>the panel | Temperature<br>Difference |

|------------------------------------------------------|---------------------------------------------------|---------------------------------------------------|---------------------------|

| TCT with one cell<br>shading<br>without Bypass Diode | 52.1°C                                            | 85°C                                              | 32.9°C                    |

| TCT with 4 cell<br>shading<br>with Bypass Diode      | 61.3°C                                            | 47.2°C                                            | 14.1°C                    |

| TCT with 4 cell<br>shading<br>with MOSFET            | 59.4°C                                            | 48.5°C                                            | 10.9°C                    |

Table 4.3: Temperature of the panel under various Conditions considered

Fig 4.10: Thermal images of panel under one cell shading without Bypass Diode

Fig 4.11: Thermal images of panel under four cell shading with Bypass Diode

Fig 4.12: Thermal images of panel under four cell shading with MOSFET

# **CHAPTER 5**

## **CONCLUSION AND OBSERVATIONS OF EXPERIMENT**

#### 5.1 SUMMARY

In this study controller is designed and tested successfully to improve the reliability of the PV panel under partial shading condition. Following actions have been performed to get the desired results.

• Firstly, advantage of the Photovoltaic system is studied the problem associated with the hotspot generation is analyzed and the level of problem it could create is understood in details

• Secondly, the hotspot mitigation circuit is proposed and designed and then tested in laboratory with regulated DC supply under all favorable and secured conditions.

• Thirdly, a MATLAB/Simulink model is simulated for different configuration under different PSCs. Then corresponding results are being investigated in chapter3 and it was observed that under full irradiance all the topologies generated same maximum power but under partial shading condition, TCT configuration generates maximum power also the effect of the partial shading is minimum on the PV panel in this configuration. Hence TCT is opted for further analysis.

• Fourthly, Hardware setup is accomplished for TCT configuration with and without controller and different observation are taken explained in detail in chapter 4. The current voltage and power voltage characteristics are plotted with the help of varying load under different conditions and then the results are tabulated for GMPP and LMPP.

• Lastly, Thermographic images are taken for analyzing the temperature of the shaded and unshaded area of the PV panels in chapter 4. It was observed that the temperature difference in the two areas is lesser in case when proposed hotspot mitigation circuit is connected compared to that when conventional BPD is connected.

#### 5.2 **OBSERVATION**

A Hotpot mitigation circuit is proposed in this paper, and the temperature of the hotspot is monitored. The simulation results indicate that the TCT arrangement generates more power than the Series parallel configuration. Partial shading has a smaller effect on PV panels when linked in TCT arrangement. When one panel with HSMC is shaded, simulation results show that the global maximum power for TCT is 348.3 watt, whereas the global maximum power for Series parallel is only 335.2 watt with 1000 watt/m2 irradiance. As a consequence, it can be inferred that the TCT arrangement produces the best outcomes. As a result, panels are joined in a TCT arrangement for hardware validation. For irradiance ranging from 750 watt/m2 to 850 watt/m2, the worldwide maximum power is 161 watt with BPD and 160.8 watt with HSMC, according to current voltage and power voltage characteristics. As a result, the power loss caused by HSMC is not large. Furthermore, the MOSFET is chosen with the lowest feasible R<sub>DS(ON)</sub> to minimize conduction loss. As a result, efficiency is effectively maintained. Thermal pictures show that while using HSMC, the temperature drops by 4.65% more than just using BPD alone. As a result, it can be inferred that HSMC is enhancing reliability.

#### 5.3 FUTURE SCOPE

In this study, the hotspot mitigation circuit is proposed and implemented successfully. But this is the new topic of research area where methods are being proposed for increasing the reliability of the system so this area demand more research in terms of designing a more suitable controller or a method. Also, a new triggering circuit can be proposed which can reduce the complexity of the controller further using voltages and current of each of the panel of PV array.

# **List of Publications**

#### **List of SCI Journals:**

• Ashwani Srivastav, Vinod Kumar Yadav, M. Rizwan, "Improving Reliability of PV Module through Modified Bypass Arrangement using MOSFET," *IEEE Transactions on Device and Materials Reliability, 2022. Impact Factor: 1.761. (Communicated).*

#### **List of Conferences:**

- Ashwani Srivastav, Vinod Kumar Yadav, M. Rizwan, "Comparative Analysis of Conventional and Intelligent Methods for Speed Control of Induction Motor," *3rd Electric Power and Renewable Energy Conference (EPREC-2022). (Accepted).*

- Ashwani Srivastav, Vinod Kumar Yadav, M. Rizwan, "Comparative Analysis of Series Parallel and Bridge link Configurations Under Various Partial Shading Conditions," *SIGMA-2022: 2nd International Conference on Signals, Machine, and Automation-2022. (Accepted).*

# References

- [1] V. Smil, "March 1958: The first PVS in orbit [Numbers Don't Lie]," IEEE Spectrum, vol. 55, no. 3, pp. 26-26, March 2018.

- [2] Frankfurt School-UNEP Centre/BNEF, (2020), Global Trends in Renewable Energy Investment [Online]. Available: <u>https://www.fs-unep\_centre.org</u>.

- [3] R. G. Ross, "Photovoltaic array reliability optimization," IEEE Trans. Rel., vol. R-31, no. 3, pp. 246–251, August 1982.

- [4] Y. Hu, J. Zhang, P. Li, D. Yu and L. Jiang, "Non-Uniform Aged Modules Reconfiguration for Large-Scale PV Array," IEEE Transactions on Device and Materials Reliability, vol. 17, no. 3, pp. 560-569, September 2017.

- [5] S. Kawai, T. Tanahashi, Y. Fukumoto, F. Tamai, A. Masuda and M. Kondo, "Causes of degradation identified by the extended thermalcycling test on commercially available crystalline silicon photovoltaic modules," IEEE J. Photovolt, vol. 7, no. 6, pp. 1511–1518, November 2017.

- [6] S. E. De León-Aldaco, H. Calleja and J. A. Alquicira, "Reliability and mission profiles of photovoltaic systems: A FIDES approach," IEEE Transactions Power Electron., vol. 30, no. 5, pp. 2578–2586, May 2015.

- [7] J. Oh et al., "Reduction of PV module temperature using thermally conductive backsheets," IEEE J. Photovolt, vol. 8, no. 5, pp. 1160–1167, September 2018.

- [8] M. Barbato, M. Meneghini, A. Cester, G. Mura, E. Zanoni, and G. Meneghesso, "Influence of shunt resistance on the performance of an illuminated string of solar

cells: Theory, simulation, and experimental analysis," IEEE Transactions Device Mater. Rel., vol. 14, no. 4, pp. 942–950, December 2014.

- [9] C. Barreiro, P. M. Jansson, A. Thompson and J. L. Schmalzel, "PV by-pass diode performance in landscape and portrait modalities," 37th IEEE Photovoltaic Specialists Conference, Seattle, WA, USA, pp. 003097-003102, June 2011.

- [10] Mohamed A. Mohamed, Ahmed A. Zaki Diab, Hegazy Rezk, "Partial shading mitigation of PV systems via different meta-heuristic techniques," Renewable Energy, Vol.130:1159-1175, 2019.

- [11] H. S. Sahu, S. K. Nayak and S. Mishra, "Maximizing the Power Generation of a Partially Shaded PV Array," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 4, no. 2, pp. 626-637, June 2016.

- [12] Bingöl, O. and Özkaya B., "Analysis and comparison of different PV array configurations under partial shading conditions," Solar Energy, 160, 336-343, January 2018.

- [13] S. Hamdi, D. Saigaa, and M. Drif, "Modeling and simulation of photovoltaic array with different interconnection configurations under partial shading conditions for fill factor evaluation," Proc. 2014 International Renewable Sustainable Energy Conference, IRSEC 2014, pp. 25–31, 2014.

- [14] A. S. Joshi, I. Dincer, and B. V. Reddy, "Performance analysis of photovoltaic systems: A review," Renewable Sustainable Energy Revolution, vol. 13, no. 8, pp. 1884–1897, 2009.

- [15] N. Mishra, A.S. Yadav, R. Pachauri, Y.K. Chauhan, V.K. Yadav, "Performance enhancement of PV system using proposed array topologies under various shadow patterns," Solar Energy, 157, pp.641–656, 2017.

- [16] G. Adinolfi, G. Graditi, P. Siano, A. Piccolo, "Multiobjective Optimal Design of Photovoltaic Synchronous Boost Converters Assessing Efficiency, Reliability and Cost Savings," IEEE Transactions Industrial Informatics, 11, pp.1038–1048, 2015.

- [17] IEA (2022), India's clean energy transition is rapidly underway, benefiting the entire world, IEA, Paris https://www.iea.org/commentaries/india-s-clean-energy-transitionis-rapidly-underway-benefiting-the-entire-world.

- [18] T. Boningari, P.G. Smirniotis, "Impact of nitrogen oxides on the environment and human health : Mn-based materials for the NO<sub>x</sub> abatement", ScienceDirect Curr. Opin. Chem. Eng. 13, pp.133–141, 2016.

- [19] IEA, Changes in share of power generation in India in the Stated Policies Scenario, 2010-2040, IEA, Paris https://www.iea.org/data-and-statistics/charts/changes-in-shareof-power-generation-in-india-in-the-stated-policies-scenario-2010-2040.

- [20] O.Bingöl, B. Ozkaya, "Analysis and comparison of different PV array configurations under partial shading conditions," Solar Energy, 160, 336–343, 2018.

- [21] S. Ghosh, V.K. Yadav and V. Mukherjee, "Improvement of partial shading resilience of PV array though modified bypass arrangement," Renewable Energy 143, pp. 079-1093, 2019.

- [22] Z. Zhao, R. Cheng, B. Yan, J. Zhang, Z. Zhang, M. Zhang, L.L. Lai, "A dynamic particles MPPT method for photovoltaic systems under partial shading conditions," Energy Conversation Management,113070, 2020.

- [23] G. Walker, "Evaluating MPPT converter topologies using a matlab PV model," J. Electrical Electronics Engineering, pp.49–55, 2001.

- [24] F.A. Touati, M.A. Al-Hitmi, H.J. Bouchech, "Study of the effects of dust, relative humidity, and temperature on solar PV performance in Doha: comparison between

monocrystalline and amorphous" PVS, International Journal Green Energy 10, pp.680-689, 2013.

- [25] O. Kunz, R.J. Evans, M.K. Juhl, T. Trupke, "Understanding partial shading effects in shingled PV modules," Solar Energy 202, pp. 420–428, 2020.

- [26] P. Guerriero and S. Daliento, "Toward a Hot Spot Free PV Module," IEEE Journal of Photovoltaic, vol. 9, no. 3, pp. 796-802, May 2019,

- [27] P. Guerriero, F. Di Napoli, M. Coppola and S. Daliento, "A new bypass circuit for hot spot mitigation," International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM), pp. 1067-1072, 2016.

- [28] L. hui, C. Yunmei and L. Xiangwei, "Study of bypass diodes configuration on PV modules with partial shaded," Chinese Control And Decision Conference (CCDC), pp. 511-515, 2019.

- [29] V. d'Alessandro, P. Guerriero and S. Daliento, "A simple bipolar transistor-based bypass approach for photovoltaic modules," IEEE Journal Photovoltaic, vol. 4, no. 1, pp. 405–413, January 2014

- [30] G. Acciari, D. Graci, and A. L. Scala, "Higher PV module efficiency by a novel CBS bypass," IEEE Transaction Power Electronics, vol. 26, no. 5, pp. 1333–1336, May 2011.

- [31] S. Ghosh, V.K. Yadav and V. Mukherjee, "Impact of environmental factors on photovoltaic performance and their mitigation strategies–A holistic review," Renewable Energy Focus, pp.153–172, 2019.

- [32] S. Ghosh, V.K. Yadav and V. Mukherjee, "A Novel Hot Spot Mitigation Circuit for Improved Reliability of PV Module," IEEE Transaction Device Material Reliability pp.191–198. 2020

- [33] A. Amerasekera, M.-C. Chang, J. Saatchi, A. Chatterjee, K. Mayaram and J.-H. Chern, "Self-heating effects in basic semiconductor structures," IEEE Transaction Electronics Devices, vol. 40, no. 10, pp. 1836–1844, October 1993.

- [34] S.V. Oprea, A. Bara, D. Preotescu and L. Elefterescu ,"Photovoltaic power plants (PV-PP) reliability indicators for improving operation and maintenance activities. A case study of PV-PP Agigea located in Romania," IEEE Access, vol. 7, pp. 39142– 39157, 2019.

- [35] S.R. Pendem, S. Mikkili, "Modelling and performance assessment of PV array topologies under partial shading conditions to mitigate the mismatching power losses," Solar Energy. 160, pp.303–321, 2018.

- [36] N.K. Gautam, N.D. Kaushika, "Reliability evaluation of solar photovoltaic arrays," Solar Energy, 72 (2002) 129–141.

- [37] M. G. Villalva, J. R. Gazoli and E. R. Filho, "Comprehensive Approach to Modeling and Simulation of Photovoltaic Arrays," IEEE Transactions on Power Electronics, vol. 24, no. 5, pp. 1198-1208, May 2009.

- [38] KP Palawat, VK Yadav, RL Meena and S. Ghosh, "Comparative performance of different PV array topologies under partial shading condition," Innovations in Electrical and Electronic Engineering, pp. 367-380, Springer, Singapore, 2021.

- [39] Shah, Nilesh and Chudamani Rajagopalan "Experimental investigation of a multifunctional grid interactive photovoltaic system operating in partial shading conditions," IET Renewable Power Generation 10, no. 9 1382-1392, 2016.

- [40] KP Palawat, VK Yadav, RL Meena, S. Ghosh, "Experimental investigation of performance of PV array topologies under simulated PSCs," Applied Soft Computing and Embedded System Applications in Solar Energy, pp. 47-64, CRC Press, 2021.

- [41]S. Mohammadnejad, A. Khalafi, S.M. Ahmadi, "ScienceDirect Mathematical analysis of total-cross-tied photovoltaic array under partial shading condition and its comparison with other configurations," Solar Energy. 133, pp.501–511, 2016.

- [42] Y. Hu, W. Cao, J. Ma, S. J. Finney, and D. Li, "Identifying PV module mismatch faults by a thermography-based temperature distribution analysis," IEEE Transaction Device Mater. Rel., vol. 14, no. 4, pp. 951–960, December 2014.