# DESIGN AND IMPLEMENTATION OF UART USING VERILOG

### PROJECT REPORT

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

# MASTER OF TECHNOLOGY IN VLSI DESIGN AND EMBEDDED SYSYEMS

Submitted by: Manisha Mishra 2K20/VLS/10

Under the supervision of

Mr Akshay Mann

(Assistant Professor, ECE Department)

DEPARTMENT OF ELECTRONICS AND COMMUNICATION

ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

# **CANDIDATE'S DECLARATION**

I, Manisha Mishra (2K20/VLS/10) student of M.Tech(VLSI Design and Embedded System), hereby declare that the project Dissertation titled "Design and Implementation of UART using Verilog" which is submitted by me to Department of Electronics and Communication Engineering, Delhi Technological University (Delhi). In the Requirement Of partial fulfillment of the award of the degree of Master of Technology. It is original and do not copied from any source and without any paper citation. This work does not previously form the basis for the award of any Degree Diploma or any other recognition.

Manisha Mishra

69884855

Mishua

Place: DTU

# **CERTIFICATE**

I hereby certify that the project report titled "Design and Implementation of UART Using Verilog" which is submitted by Manisha Mishra (2K20/Vls/10) of Electronics and Communication Department (Delhi Technological University), in theRequirement of partial fulfillment of the award of the degree of Master of Technology.

This is the record work carried out by the student under my supervision. This work has Not been submitted in part or full for any degree or diploma to this University or Anywhere else.

Place: DTU

**SUPERVISOR**

Alpax 30/6/22

**Department of Electronics and Communication**

Delhi Technological University

# **ACKNOWLEDGEMENT**

A successful project can never be prepared by effort of the person to whom the project is assigned, but it is also depends and demands for the help and guardianship of people who helped in the completion of the project. With sincere sense of gratitude, I thank to Mr Akshay Mann my project Supervisor who gave me encouragement ,support , patience and proper guidance in this project work . I take gigantic gladden in extending my acknowledgement to my family and friends who have helped me throughout in this project.

# **ABSTRACT**

Designing of a chip or we can say system on a chip in contact with Field Programmable Gate Array (FPGA) is now a days trend in the design or digital design industry. It is because of it has lots of advantages as compare to discrete electronics hinge products. It has lots of or many Advantages some of the are higher speed, Power consumption is low, Size is small and Cost is low and-soforth. Universal Asynchronous Receiver and Transmitter(UART) is a protocol which is categorized as serial communication protocol. Predominantly, these type of protocols are use to allows short distance, reduces cost and well founded for the full duplex communication. These are basically it swaps the data between the peripherals to processors of the well founded transmission of data. Throughout opposed versus parallel communication, serial communication is substantially more cost-effective although the system's complexity increases. For something like the design of either a UART that is performed in Verilog HDL, it may be quickly racially segregated upon an FPGA to achieve the highest level of data reliability as well as blunder data.

# **CONTENTS**

| TITLE                      |                      | 1  |

|----------------------------|----------------------|----|

| Candidate's Declaration    |                      | 2  |

| Certificate                |                      | 3  |

| Acknowledgement            |                      | 4  |

| Abstract                   |                      | 5  |

| Contents                   |                      | 6  |

| List of Figures and Tables |                      | 7  |

| CHAPTER 1                  | INTRODUCTION         | 8  |

| CHAPTER 2                  | LITERATURE REVIEW    | 17 |

| CHAPTER 3                  | ARCHITECTURE OF UART | 29 |

| CHAPTER 4                  | VERILOG CODE         | 34 |

| CHAPTER 5                  | SIMULATION RESULTS   | 46 |

| CHAPTER 6                  | CONCLUSION           | 49 |

| REFERENCES                 |                      | 50 |

# **List of Figures**:

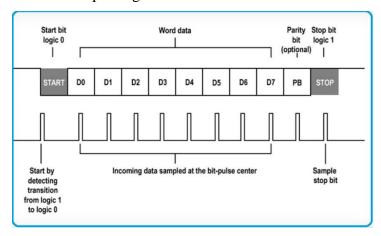

- Figure 1 Asynchronous Code Format.

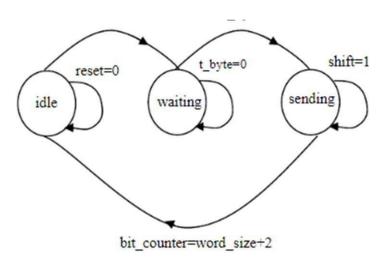

- Figure 2 State diagram of UART transmitter

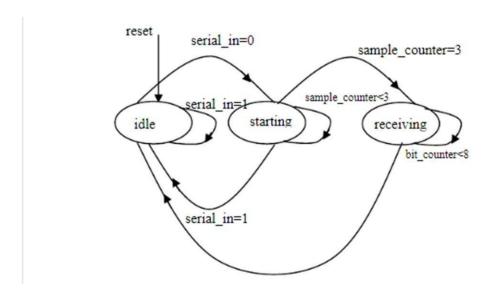

- Figure 3 State diagram of UART receiver

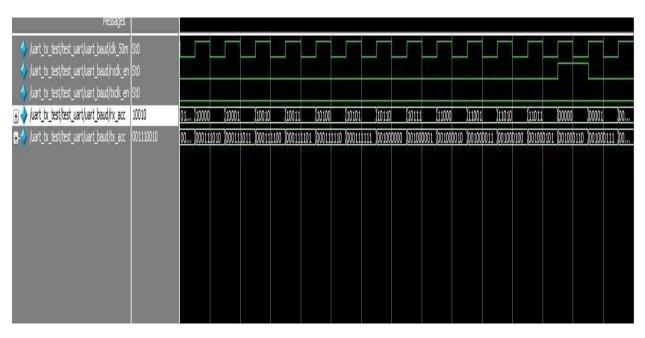

- Figure 4 Simulation result of baud rate generator

- Figure 5 Simulation result of transmitter

- Figure 6 Simulation result of receiver

# **CHAPTER 1- INTRODUCTION**

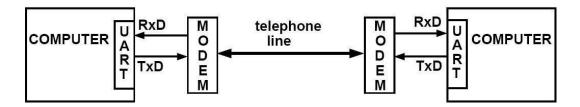

# 1.a The UART – Introduction And Working of UART

A Universal Asynchronous Receiver Transmitter (UART) is a semiconductor chip that governs a computer's functionality to something like a serial computer connected to that though. Particularly, it come up with the computer Data terminal Equipment (DTE) RS-232C interface in order to avoid to Serial devices and modems may "speak" to each other and transmit information. While pieces of those interface, the UART is also called:

- It refashion the bytes which that receiving since Pc by the side of parallel circuits in the direction of a 1 serially bit stream for departing transmission.

- For inflowing Transmitting it refashion steams of the serial bit into the bytes which handles the system.

- It Appends the parity bit (whenever it will be selected ) to departing transmissions and it also the parity checked by incoming bytes (in case it selected ) the parity bits also discards.

- Starting with inflowing transmission it appends and stops delineators on inflowing and strips.

- Mouse and Keyboard will also be handles the interrupts (those are specials ports in serial devices ).

- The operation speed of computer and the speed of device will be coordinating and manageable and handled other type of interrupts.

- For modems and other devices there is serial communication will be used and also for computers as well

#### Serial Data Transmission

( It could have been an encoding of certain bits in some kind of a sequence of blocks) by the side of numerous channels (such as wires ,printed circuits tracks, optical fibers so on) ; a single stream of data will be transmitted by a serial link.

As compare to parallel link serial one would be lesser at the first time, The reason behind it is the it will transmits inferior data on the every clock tick. In spite of that, they will frequently parallel links clocked less faster than the case of serial link, or it will also achieve a higher data rate. At the greater rate of clocks for serial is a number of factors of a number of factors allow serial;

- There is no issues between the different channels and Clock skew (for unclocked seriallinks)

- There is less interconnecting cables will requires for the serial connections (such as fibers and wires) so it consumes very minimum space. For the better isolation of the channels and its surroundings the extra spaces will be allowed.

- In view of the fact that there is minimum conductors inproximity so Crosstalk is minimum.

There is in the maximum of the situations serial communication is better option since its implementation is Cheaper. Most of Integrated circuits have serial interfaces, and not suitable for the parallel one because they have pins and they are cheaper. In computer science and telecommunication, the blocks of the data bits may be sending single bit at a one time is mostly the process of serial communication.

Succession above a computer bus channels. As we all know in parallel communications, every bits and symbols are sent together. In most computer networks and all long- haul communications serial communications will be used, because of serial communication is cheaper and it has less synchronizations. Because of the higher speed of data transfer and improved technology serial communication technology becomes more common and improved.

# 1.b Parallel versus serial

The Parallel port is slower to interface than the Serial port. In maximum cases, if we want to connect to the serial port of any device we will need to convert serial transmission to the parallel then it will be used .The whole process can be used by UART. Upon this software side, you'll ought to deal with hundreds fewer registers than you could ever on something like a standard parallel port (SPP).

Consequently, what are the benefits of serial data transfer vs parallel data transfer?

- Serial cables may be longer than parallel cables. The serial port sends "1" at three to twenty-five volts, "0" at +three to +25 volts, and the parallel port sends "0" at 0V and "1" at 5V. Therefore, the most amplitude of a serial port is 50V in comparison to a parallel port with a most amplitude of five volts. Therefore, cable loss is not as complex with serial cables as it's far with parallel cables.

- You don't want as many wires as parallel transmission. If you want to mount your tool some distance out of your computer, a three-twine cable (null modem configuration) is a good deal less expensive than a 19- or 25-twin cable. However, you want to don't forget the price of the interfaces at each ends.

- Infrared gadgets have lately established to be very famous. You can also additionally have visible many digital journals and palmtop computer systems with integrated infrared capabilities. But are you able to believe sending eight bits of records at a time throughout area and deciphering which bit is which (from a tool's factor of view)? Therefore, serial transmission is used, wherein one bit is transmitted at a time. IrDA1 (first infrared spec) became capable of ship 115.2 kbaud and became linked to a UART. However, thinking about that those gadgets are specially used for diaries, laptops, and palmtops, the heartbeat period has been decreased to three/sixteen of the RS232 bit period to store power.

- Microcontrollers have additionally established to be very famous those days.

Many of them have a integrated SCI (Serial Communication Interface) that may be used to talk with the outdoor world. Serial conversation reduces the range of pins on those MPUs. Normally, best pins, transmit records (TXD) and acquire records (RXD), are used, however while the use of the eight-bit parallel method, at the least 8 pins are used (a strobe can also be required). ).

There are essential styles of serial transmission: synchronous and asynchronous. Depending at the mode supported through the hardware, the conversation subsystem call typically consists of A if it helps asynchronous conversation and S if it helps synchronous conversation. Both codecs are defined below.

#### 1.c : Synchronous Serial Transmission

Synchronous serial transmission necessitates that perhaps the transmitter and recipient have been using the same clock, but rather that the sender sends a flashing and perhaps other timing signal to both the receiver such that it understands when to "read" that this next piece of knowledge. Unless there is no information available to transmit at a given time throughout most forms of serial Synchronous communication, a fill character should have been sent once again to ensure that the information is always transferred. When only data bits are exchanged between the sender and receiver, synchronous communication is normally economically efficient. However, synchronous communication might be a little more expensive if supplementary wiring additional circuits seem to be essential to exchange a clock signal between the sender and receiver. Printers and Although most fixed disc connector standards transfer the whole word of material with each clock as well as strobe signal while using a separate wire on every bit of the word, devices aren't really ordinarily serial devices. These would be referred to those as Parallel devices throughout the Personal computer industry. Synchronous operations are not supported by the Computers and laptops conventional serial communications hardware. The above approach is mentioned solely for the purpose of comparison.

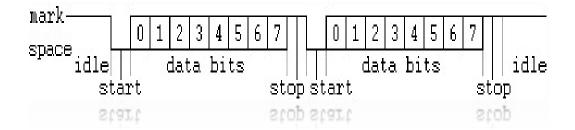

# 1.d: Asynchronous serial transmission

Asynchronous serial communication delivers a start signal before each byte, character,

or keyphrase as well as a stop signal after each codeword in an asynchronous transmission protocol. The start signal prepares the receiving mechanism for receiving and registering the symbol, whereas the stop command soothes the receiving mechanism before acquiring that this next metaphor. ASCII through RS232 is a widespread sort of start-stop transmission, which is used in teleprinter operations, for example

The commencement bit gets transmitted initially, accompanied by eight transmitted data (without parity bits) and indeed the stop bit throughout this example for something like a 10-bit graphic frame. The quantity of knowledge, maximum frequency of format bits, and the transmission speed must all be agreed upon in advance with the communication partner. This string can continue indefinitely after the stop bit, but it can also immediately start a fresh character.

# 1.e: Bit Baud and symbol

Transfer rate of asynchronous communication is measured by Baud. Communication technology Have recent advances data rates for the devices is often misused while discribing. Baud rate is Defines by the numbers of bits actually transmitted over the media, In DTE devices the data amount is not transmitted actual data from one devices to another devices. The baud count contains parity, stop, and start cleared by the receive UART and overhead bits generated by the transmit UART and. So. We can say that if we want to transmitted 7-bits dataword we actually needs 10 bits to be transmitted. As a consequence, modems that can transfer 300 bits per second from one location to another typically use parity and can transfer 30 7-bit words only if the begning and End bits are contempory. If Eight-bit datawords are utilised, as well as parity bits are also used, the data rate will be reduced. 27.27 words / 2nd, 8-bit words require 11 bits to

send, and the modem is still sending only 300 bits / second, so until the advent of error-correcting modems, the number of bytes / second will be baud rate. These modems take a serial bitstream from the host computer's UART (an internal modem is used, but the data is often episodic) and convert bits to bytes. The amalgamate bytes are then a packet as well as forwarded information telephone synchronous transmission technology on something like a connection As little more than a result, the stop, start, and processing elements appended mostly by the DTE (computer) This same modem had already deleted the UART.

it was transmitted beside transmitting modem. Because when router receives these bytes, it adds start, stop, and parity bits toward the sentence, transforms everything to recidivist format, as well as sends those to the receive UART somewhat on distant computer. Then install something and deactivate it. Includes parity bit and indeed the stop bit. What's the use of all these extra bits

The system usually handled mostly by connections, and indeed the DTE equipment generally oblivious that it would be actually happening. Additional packets of data information records which that two modems ought to distribute upon themselves to perform expensive error-correction are generally hidden from the powerful transmission price apparent through the use of the transmitting and receiving DTE equipment by stripping the Start, Stop, and Parity bits. For example, if an internet service starts sending ten 7-bit buzzwords to another broadband connection and including the Start, Stop, and Parity bits, the trying to send internet service may indeed be prepared to email 30 bits of its own facts and figures to the receiving broadband connection, which the eligible to receive modem could have used to perform debugging without slowing down the transmission speed of the historical documents

On opposite ends of the discourse, the and DCE. Due to the use of compression via modems, the rate between DTE and DCE is usually faster than the rate between DCE and DCE. Because the variety of bits had to describe a byte numerous for the duration of the experience among the 2 machines plus the differing bits-according to-seconds speeds which are used gift at the DTE-DCE and DCE-DCE links, the use of the time period Baud to explain the general verbal exchange pace reasons issues and may the genuine falsify transmission pace. So, Bits Per Second (bps) is the proper time period to apply to explain the transmission price visible on the DCE to DCE interface to Baud as a substitute Bits / Second are desirable phrases to apply while a interrelation is made among structures with a stressed out association, if a modem is the process of that isn't appearing demnification. Latter-day high-pace modems (2400, 9600,

14,400, and 19,200bps) in fact nevertheless function beneath 2400 baud, or extra accurately, 2400 emblem according to 2d. High pace modem are Capable of encoding extra bits of record sin the direction of every Symbol the usage of method known as stuffing of Constellation, that is what the powerful bits according to 2d price modem on the is better, however the modem keeps function in phone machine as long as is confined audio bandwidth. Modems running at 28,800 and better speeding has been rate of variable Symbol rates, methods are changed.

# 1.f: Asynchronous serial reception

The multichannel information transmission wave could only exist in another one of different states, each with its own set of names. This same pulsing seems to be in the "vacant" condition when the circuit is closed, low voltage, current is flowing, or logic is zero. If the pulse is off, the circuit is open, and the voltage is high,

That's in the "marked" condition, which means it's open circuit or logical. Each character code begins with a 0 (zero).

Fig 1: Code format for the Asynchronous.

Invariably send the least relevant bit initially. The parity bit comes after the data bit and before the stop bit if parity is present. The start bit, often known as a space, is always "0" (logical row). Ironically, the data line's high voltage corresponds to the logic row "0."

The start bit alerts the receiving DTE to the arrival of the character code. Depending on the coding set, the next 5-8 bits indicate characters. The parity bit in the ASCII coding set can be the 8th data bit. The stop bit is the following bit, which is always in the marked state (logic high, or "1"). These offer a "calm" period

for the receiving DTE to prepare for the next transmission.

Each character must be decoded. The engine took time at the end of each character to hit the yoke (print the character) and reset the camshaft. In order to receive a serial character code in a parallel register, there are six main steps. To begin, the recipient uses a clock to keep track of time. A "tick" sound is produced. The receiver will sample the line 16 times if it is in a room condition.the data transfer rate To put it another way, one data interval is 16 clocks long. This permits the receiver to figure out what the message is about. "Step over" to the centre of the data sampling bit time at the start of the start bit. After then, when the Declare a "find start bit" condition and wait half a bit after the line is marked(The data should have been there for the previous 8 clocks and should continue to be there for another 8 clocks.) The sample is then shifted to the shift register. Steps 4 and 5 should be repeated seven times more. The start bit "moves" to the flip-flop signifying the received character after the ninth shift. Go to step 1 now. Before the test, the five parameters must all have the same values. UARTs can be used as transmitters and receivers. First, both parties must agree on the amount of people who will be involved the number of bits per character Second, on both sides, the line speed, or baud, must be the same. Finally, both Parties must agree whether or not to employ parity. Fourth, you must agree to use parity if you use it. On both sides, there is an odd or even parity. Finally, we must agree on the number of stop bits to be used. Apart from that, most DTEs employ 8 data bits, 1 stop bit, and no parity nowadays. As a rule of thumb, the baud rate of a normal RS232 or RS423 port is equal to the number of letters per second. 10 times the data line

# **Other Features of UART**

Aside from transferring data between parallel to serial for transmission and from serial to parallel for receipt, the UART generally indicates overall state of both the transmission media as well as being a signal that can be used to govern transmission of data. Additional circuitry is provided for. If somehow the remote device is not capable of receiving any additional data. If the device linked to the UART is a modem, for illustration, the connection might transmit this same appearance of something like the bearer toward the telephone line, allowing the computer to reconfigure this wifi router or order it to raise or lower the phone so it does not answer. There might be some instances where this would be true. That most of these changes devote more resources. The intention of a few of each The EIARS232C specification describes several new signals.

# CHAPTER 2 – LITERARY WORK OR REVIEW

FANG Yiyuan, CHEN Xuejun [1] presented a paper on the design and simulation of UART module. The work was similar to what we wanted to accomplish through our project so their paper guided us about how to achieve our desired results. Universal Asynchronous Receiver Transmitter is a sort of sequential correspondence convention; generally utilized for brief distance, low speed, minimal expense information trade among PC and peripherals. During the genuine modern creation, once in a while we needn't bother with the full usefulness of URAT, however basically coordinate its center part. The transmitter, baud rate generator and receivers are includes by URAT which are known as three kernel. For achieving the reliable ,compact and stable transmission data the UART implemented with the help of VHDL which could be integrating in which FPGA so there is a significance of the design of SOC chip. The UART protocol in every way consistent the simulation results with Quartus II . In the given paper, there is the method of design used is down to top (top to bottom)

The submodules are used or devided in the URAT serial communication three module is: These are known as the module transmitter baud rate generator and transmitter .So we can saw that the URAT communication module is actually implemented and realized in the three submodules. The transmission and reception of the UART is used to control from baud generator generating a a rate baud which is local clock signal and higher. These receiver module of UART is used by RXD to receiving the serial signals and converting to proper parallel data. This transmitter module of URAT is used to converts serial to info bits same as the frame format for the basic and sends these bits over the TXD. These designing used VHDL as the designing language to implement the URAT module. Whole testing and the simulation with Altera Cyclone Series, Quartus II software EP2C5F256C6 FGPA chips. Abov resuls are reliable and stable. The complete design have the very good elasticity, a maximum degree reference, specific integration values. For the most part.

If we can talk in the electronic design feild the above design is very important, Emplacement SOC technology has matured not long ago. We can also saw and indicated how we can use the state model to clarify the design of the module receiver. Those are used whenever UART is designing. The paper was very useful for our project. The basic understanding which is we needed for the project the paper gave us. He talked about the design of the UART module and its

simulation and was an excellent source of information for the project.

UART transmitter and receiver has been designed by the Miss.M.A. choudhari et.al[2]. We will take or learn profound cognizance about UART module from the given paper. The paper elucidate us the importance UART module. - Uiversal Asynchronous Receiver Transmitter (UART) supports the full duplex serial communication which is frequently or nearly new used for serial data transmission protocol. The paramount device for transmission of data and Receiver is for receiving the data in the transmitter is UART. Accordingly, the asynchronous de transmitter and receiver are used for UART. So, innumerable UART is proportional to number of channels so that we proposed to design UART using master slave configuration. There are lots of advantages of UART which we know are given as simple resources, unfailing performance, strong anti-jamming capability, easy to control and understand and many more. The above advantages are flatters one of standard integrated peripherals of various processors, which is given as chips 8250, 8251, 16550. Which accommodate a parallel-to-serial converter which transmits the data from the computer and a serial to parallel converter for data coming in by way of the serial line. Serial Communication Protocols cheaper in cost so it is used than Parallel communication. For the immediate transmission of temporarily storing data a buffer is being used which UART already have. Master slave configuration has been used proposed to the design UART. In the past few years the researchers have proposed various UART designs like automatic baud rate synchronizing capability, predictable timing behavior to allow the integration of nodes with imprecise clocks in time triggered. The UART module which acronyms of Universal Asynchronous Receiver Transmitter (UART) is serial data transmission protocols supports full duplex and used serial data transmission protocols. UART contains receiver and transmitter which receives and transmits the data. The design of UART explains the asynchronous transmitter and receiver. For that reason, the number of channels is proportional to the number of UARTs. That being the case, The design put forward to the UART is with a master-slave configuration.

The UART has many advantages, including: B. Simple resources, perfect performance, strong anti-interference capability, easy control and comprehension, etc. It will be the standard integrated peripheral for various processors such as the 8250, 8251 and 16550 chips. It includes a parallel-to-serial converter for data sent from a computer and a serial-to-parallel converter for data arriving over a serial line. Since parallel communication is costly, we will use the serial communication protocol here. The UART also has a buffer to temporarily store data from immediate transmissions. Proposed to design the UART in a master-slave configuration. In recent years, researchers have proposed various UART designs such as automatic baud rate synchronization and predictable timing behavior, allowing nodes to be integrated with inaccurate clocks at time-triggered times.

To remove clattering samples and iterative running and thumb cleaning Real-time system is being used, integrated core functionality into one FPGA chip to avoid wasting resources and reduce costs, compressed and stable DSP with reliable data transmission, programming logic and synchronous serial port to enable interface between asynchronous communication protocols. Different requirements and different designs of UARTs have discribed in the literature for different systems that require data communication between functional units. A UART have normal design, in the proposed paper there is a master -slave configuration adds an innovative element are used. For sending and receiving the date there is only one port is used in the UART. Because of that in master – slave configuration the number of ports increases here. The above frame has been received on the deflated receiver input and only the data bits are available in parallel format on the output receiver. The LCR, baud rate generator (BRG), transmitter and receiver as functional units are includes in the receiver output.

The details design of the UART are given by Ananya Chakraborty[3]. UART (Universal Asynchronous Receivers Transmitters) are generally used to improve serial data transmission. For sending and receiving data serially to send and receive date serially shift register is used. The UART consists of a frame format which gives a start bit (usually low), 58 data bits, an optional parity bit, and a stop bit (the opposite polarity of the start bit). Asynchronous means that by using the start and stop bits as the transmit data, To

receiving, synchronizing and transmitting ASCII(SYN) not required or transmit (PAD). It Sends 9600-38400 bps data to transfer data bits. The shift register principle is being used for the entire serial transmitting procedure. In this paper working UART is explained and tells how it works. For the serial communication an integrated circuit is used which is called UART which includes a receiving (serial to parallel converter) and the transmitting (parallel to serial converter), every and every separated clock. Computer bus is being usually added to the parallel side to the UART. Whenever the computer tells or sends any bytes towards the UART transmit data register (TDR). The UART would start transmitting towards the serial line. If the UART is ready to transfer another bytes the computer can be read to see the status register contains a flag or not . the UART received bytes from the serial lines whenever status register bit indicates. By that means, the Received Data Register (RDR) is being read by the computer. The UART will give signal "invade" error via other status bit in case any other byte is being receiving previously the initial byte will be read. When maximum number of data is to be ready to send the UART could be configured to interrupt the computer whenever data is being received. The UART serial connection typically goes through an integrated receiver line and separate driver line circuit that provides the voltage and powering needed to flowing the one by one line serially and provides and the noise on the line will be protected. The data on the serially line is formatting by the help of UART according to the settings in the UART will controls the register. It can also be determining, receiving and transmitting the baud rates whenever the UART have its their self-clocked circuit or the "baud rate generator". If a mis formatted data will be received, the UART can notify you of a "framing error" or a "parity error". Clocks often operate at sixteen times the bits per second that is the baud rate, allowing the receiver for center of the sample. H. You can read any middle of the bit in the allotted time. The whole process makes the UART higher tolerant of fluctuations to the jitter or clock rate of incoming data.

The UART would start transmitting towards the serial line. If the UART is ready to transfer another bytes the computer can be read to see the status register contains a flag or not . the UART received bytes from the serial lines whenever status register bit indicates. By that means, the Received Data Register (RDR) is being read by the computer. The UART will give signal "invade" error via other status bit in case any other byte is being receiving previously the initial byte will be read. When maximum number of data is to be ready to send the UART could be configured to interrupt the computer whenever data is being received. The UART serial connection typically goes through an integrated receiver line and separate driver line circuit that provides the voltage and powering needed to flowing the one by one line serially and provides and the noise on the line will be protected. The data on the serially line is formatting by the help of UART according to the settings in the UART will controls the register. It can also be determining, receiving and transmitting the baud rates whenever the UART have its their self-clocked circuit or the "baud rate generator". If a mis formatted data will be received, the UART can notify you of a "framing error" or a "parity error". Clocks often operate at sixteen times the bits per second that is the baud rate, allowing the receiver for center of the sample. H. You can read any middle of the bit in the allotted time. The whole process makes the UART higher tolerant of fluctuations to the jitter or clock rate of incoming data.

He Chunzhi et al. [4] A UART designed has been proposing. This design features self-adjusting generators the baud rate. Asynchronous FIFO is required as a buffer to realize in order to achieve speed matching between the processor and the UART interface. would begin to transmitting the serially. UART is ready to transmit different bytes then the status register of UART is suppress flag bits which the computer can read to see. One more status of register bits indicates if the URAT have obtained a byte from either the serial connection, where such case the Receive Data Register should be read by the computer (RDR). Whenevr one more byte will be received from the preceding one bit will be read, UART would send another status bit to indicate a "overrun" problem. Whenever the data will be received or whenever new data is start to be transmitted, the UARTs can be the computer will be setting up to interrupt. The serial connections on the UART are normally made through separate line operator as well as receiving line integrating circuit, which will be providing the necessary powering and voltaged to driving serially and

provide minimum noise protectected. The UART formats data will be serially according to settings of the URAT. If UARAT has their self clocked circuits or "baud rate generators," these might be decide the baud rate will be received and the transmits. Whenever data is wrongly formatted, the UART "Framed fault" or "parity glitch." The clock is usually set to sixteen measure to the baud rate to enabling the receiving to execute middle sampled, essentially usually entails every bits in the center to given period (bits per second). As a byproduct, the UART is more forgiving of packet header clock rate. He additionally discussed that UART's existing developments and how it has changed over time. In the late 1980s, the Intel 8450 was an example of a UART. A new UART with an integrated data buffer memory was designed in the 1990s. This enables for quicker data transfer rates without data loss or the computer's constant attention. The Intel 16550, for comparison, does indeed have a 16-byte FIFO.

A UART design is implemented by He Chun-zhi et al. [4]. An auto-tuning baud rate generator will be included in the design. Asynchronous FIFOs will be used as buffers to achieve processor and UART interface speed matching.

UART-to-external-device communication ModelSim SE 6.0 is being used to functionally verify the design, and Synplicity's Synplify Premier 9.6.2 is used to synthesise and enhance it.[5] Biswajit Roy Dakua et al. Sending and receiving information using asynchronous serial communication is a popular, simple, efficient strategy. UART is usually the company that implements this innovation. The Universal Asynchronous Receiver Transmitter (UART) is a programming-controlled microprocessor that manages a computer's serial device interface. The UART is mostly used to communicate amongst slow and rapid passive components, such as a computer and a printer, or a controller and an LCD. The essential functionalities of UART are developed and combined onto an FPGA chip through this whole study. To make the UART system more stable and trustworthy, they used an FSM (finite state machine) in their design. The UART's 3 premier componenting are the baud rate generator ,transmitter & receiver. This study specified the UART architecture, which was then gadge on the FPGA on the gadge using the Hardware description language to enable reliabling serially data transfer. UART's capability was shown using the Quartus II emulator, Altera's Cyclone II series, the FPGA

chip EP2C20F484C7. Thus according ourselves, the result of simulation are usually reliabled and robust. The designed appears to be extremely adaptable, as it can detect and correct numerous forms of communication faults utilising error checking techniques. It also supports a wide range of baud rates. A UART execution in FPGA. To develop a Verilog HDL-implemented UART that would be integrating into an FGPA for maximum reliablde and faultless data will be transmitting. These work shows the hardware gadge of UART used Verilog HDL FPGA: EP2C20F484C7, Altera cyclone II family. For simulatioting, the Quartus II simulator is utilised, which is completely compatible with UART. Despite the fact that it was written in Verilog rather than VHDL, it taught us a lot. The Universal Asynchronous Receiver Transmitter (UART) will be often using to better transfer serially, that is, to send and receiving the data, as Amanpreet Kaur and Amandeep Kaur [6] mentioned in their article. It is a frequently used data communications channel inside this telecommunications industry. In the industry, there have been increasingly salient of the UART. A UART seems to be an integrated circuit with a separate clocked transmitter (parallel to serial converter) as well as receiver (serial to parallel converter). Transfers data bits at a rate of 9600 bits per second. The shift register principle underpins the entire serial transmission mechanism. Serial transmission is divided into two types: synchronous and asynchronous. To enable the receiver to understand when and how to receive the very next set of data, synchronous serial transmission necessitates the transmitter and receiver to maintain a clocking or offer a strobe or other timing signal. Yes, there is. If you can't deliver data at a specific moment in mostly of the serial synchronous communication, you must provide the padding character to ensure that the data is always sent. The sender can deliver data without sending the clock signal to the recipient using asynchronous transmission. Furthermore, the transmitter and receiver must agree on timing settings ahead of time, but each sentence incorporates a special bit that synchronises the transmit and receive units.

Asynchronous serial communication is commonly used for sending information between computers and passive components because it has the advantages of fewer transmission lines, improved reliability, as well as extended transmission distances. UART is commonly used to implement asynchronous serial communication. The stop bit, parity bit, data bit, start bit & state idle are usually included in the UART transmission protocol. Data frame format for UART A bit termed the "begin bit" is inserted to the begined of every word conveyed when a word for asynchronous transmission is given to the UART. The start bit serves as a warning to the receiver that a data word is going to have been sent, as well as forcing up receiver's clock. The constituent bits will be data word are transferred with the LSB after the begin bit there will be LSB signal would indeed be forwarded towards the clock transmitter during synchronization.

The sender can add the parity bits that the sender generates because after complete data word has been delivered. The recipient can utilise parity bits to do a simple error check. The sender then we will flow at least 1 end bit. The UART may inform you of a framed fault whenever data is received in an inappropriately formatted format. The UART will report an overflow fault if another byte is received before the previous byte is read.

Because the whole data word will be sent, the sender would add the parity bits that the sender generating. The recipient can do a simple error check using parity bits. After then, the sender sends at least one stop bit. If data is received in an incorrectly formatted format, the UART may notify you of a framing mistake. Whenever other byte is receiving before the previously byte will be read, the UART would be indicate an overflow fault

These are advantages using VHDL to implement UART:

- 1. Then instead of focusing mostly on transmitter's implementation stage somewhere at gate level, VHDL helps us to determine the transmitter's operation in a somewhat more behavioural approach.

- 2. VHDL makes it so much easier to comprehend as well as comprehend the design implementation. The issue of timing characteristics of something like a typical UART is addressed by Wilfried Elmenreich and Martin Delvai [7]. The Internal Capabilities Network (LIN) and indeed TimeTriggered Protocol for SAE class A applications (TTP/A), both unique fieldbus protocol for realtime systems, utilise similar simple UART (Universal Asynchronous Receiver and Transmitter) encoding. Due accomplish predictable time, many protocols have been using a scheduled communication schedule. Off-the-shelf hardware like conventional UARTs save money, and yet you still have to deal with issues like clock drift, transmit jitter.

I look at some of the most common and common timing challenges that are directly related to UARTs and imprecise oscillators, as well as a calculation of upper bounds for the timeliness of UART-driven communications, in this paper. In addition, we discuss methods for overcoming timing difficulties caused by erroneous on-chip oscillators. In time-triggered fieldbus protocols, a customizable UART with no transmission jitter is typically utilised to assist synchronisation. With typical hardware UARTs, this isn't always the case. It is possible to construct a software UART, albeit at the sacrifice of node performance. We invented a different UART architecture that is better equipped to time-triggered systems over traditional UARTs. When provided with conventional protocol synchronisation compliance, the above approach makes it possible to integrate networks with faulty clocks within time-triggered real-time applications. Despite the fact that UARTs weren't really developed for with this classifier, it's indeed important to ensure that perhaps the UART communication of a microcontroller with an on-chip oscillator can encounter this same communication protocol's timing requirements in order to

attain the desired purpose of formulaic communication.

Despite UARTs weren't really designed for all of this application domain, it can only be established that perhaps the UART communication of something like a microcontroller and an on oscillator should withstand overall time requirements defined by that of the communication protocol. This paper's goal is to look into the timing aspects of a UART transmission and analyse the implications regarding protocol as well as hardware design. They researched upon how commonplace UARTs could be used in time-triggered systems and devised mathematical methods to ensure that a UART frame stays inside its own designated time slot (Inter-Slot condition) and therefore all supplied bits are accurately acknowledged (Intra-Slot condition).

This same Inter-Slot as well as Intra-Slot characteristics, when combined, create a necessary criterion regarding proper communication scheduling. Using these settings, two typical UARTs were tested, and it was discovered that some parameters limit the application of conventional UARTs, particularly when combined alongside erroneous on-chiposcillators.

Following aspect of the study [8], which would have been published in 2015, discusses something like a UART to decrease overall complexity of hardware requirements for something like the BIST testing technique.

Built-in Self-Test is among the most frequently utilized analytical techniques (BIST). Primary purposes of a BIST Universal Asynchronous Receive/Transmit (UART) include therefore to meet stated testability standards, and then to implement at the lowest cost with the maximum performance. For decades, the UART has been a key I/O tool, and it has been frequently used today. While BIST technology is becoming more frequently used throughout the industry, increased BIST circuits which it add hardware overhead elongate development time, and poor performance would be frequently mentioned as nothing more than a cause to minimize BIST utilisation. Through use of BIST technology provides aided in the computerized implementation of the application.

Built-in Self-Test is among the most frequently applied analytical techniques (BIST).

Primary goals of either a BIST Universal Asynchronous Receive/Transmit (UART) include always to authorization testability standards, and then to construct at the cheapest price well with enhanced efficiency. For decades, the UART seems to have been a fundamental I/O tool, and it has been frequently deployed today. Although BIST technology is becoming more widely used in the industry, new BIST circuits that add hardware overhead lengthen development time, and poor performance is frequently cited as a cause to limit BIST utilization.

The use of BIST technology has aided in the automated testing of the system. Universal Asynchronous Receive / Transmit (UART) seeks to first meet the required testability constraints prior to actually developing the cheapest price with both the maximum performance implementation. For decades, the UART has been a significant I/O tool. Additional BIST circuits can increase chip design time, size, and performance by increasing hardware overhead.

These white paper focuses on utilising the VHDL language to develop a UART device that integrates the BIST architecture. The above paper goes into the (VLSI) test issue as well as how the UART works, including the transmitter and receiver components. That serial port is used to send serial data. Your computer's serial port is the most universal component.

# **Applications of UART:**

Specifies another synchronisation mechanism which thus simplifies software as well as renders regular frequent synchronisation necessitated by that of the real-time communication protocols discussed above easier. When an event occurs, the UART can also developed and produced. As a result, the UART module could handle the majority of the communication process on its own. Transmission jitter has really been totally destroyed, and calculation mistakes in baud rate setting have been greatly reduced. As a result, the UART module can work with a low-cost RC oscillator or an imprecise clock source with a high drift rate

These research certainly sparked new ideas for additional studies. B. Enable interesting applications with the UART. Various components are just being integrated within system-on-chips because as low-cost microcontroller market segment continues to rise (SoC). Integration of a microcontroller, sensors/actuators, communication units, and a complete network node consisting of one can result in significant cost reductions. On a single silicon chip, there is an oscillator. However, because current technology does not allow for the incorporation of a crystal oscillator, SoCs are often outfitted with RC oscillators.

Because RC oscillators' frequency seems to be particularly robust to differences in voltage and temperature, a conventional RC oscillator does indeed have a nominal frequency of 1MHz 50 percent and then a frequency and phase drift of 10% per second. TTP / A [1] and LIN [2], two new wired or wireless communication protocols, establish a common UART as the network communication connection to give a premium alternative. Two protocols are core master UART protocols enabling permit time-predictable communication for low-cost single-chip smart sensors and actuator nodes.

Research papers have also shown that COTS (commercial) hardware implementations are possible. Nonetheless, a thorough examination of either the objects involved UART's behaviour indicated that it had been unsuitable for real-time communication. Furthermore, both LIN and TTP / A define synchronisation messages which thus enables slave nodes with low-cost on-chip oscillators to synchronise with both the operational network.

Zhaojin Wen, Lili Yi, Shouqian Yu Weihai Chen, Shouqian Yu [10] This paper is a non-linear and non URAT controller centered on first in, first out FIFO & FPGA to meet the communication requirements of something like the latest complicated control systems (field programmable gate array).

This same asynchronous FIFO optimization algorithm and controller configuration are introduced. Inside that FPGA, the assembly manages a FIFO circuit block as well as Universal Asynchronous Receiver Transmitter (UART) circuit block to accurately and thoroughly establish communication in today's complicated control systems. This controller could be using to gadge communication when the master and slave devices are configured to different baud rates, as shown in the communication sequence diagram. It could be used to eliminate synchronisation issues between subsystems that are important for sustainable development. The controller is extendable as well as programmable.

You may now simply construct complex control algorithms to achieve your desired system performance through using newest microcontrollers and digital signal processors (DSPs). Unfortunately, obtaining these intended outcomes in some kind of a real-world control system is challenging due to a variety of elements affecting the control system, including that of the optimization technique mechanism, the controller's function, the function of the device, and indeed the condition of the control status. Aside from either of these considerations, control system communication parameters like BER (bit error rate), Baud Rate and subsystem synchronisation are also highly useful.

In the given page to increase the accuracy of the control system and make efficient use of the latest control algorithms, more attention must be devoted to communication in the control system. The UART, a form of serial communication circuit, is widely employed in control systems. UART stands for Universal Asynchronous Receive/Transmit and is the most important component in serial communication. Converts data between serial and parallel formats.

As a result, data transfer amongst two systems being far apart and it's achievable. Communication between the master controller and slave controller is accomplished through serial or parallel ports in some complicated systems. Parallel communication would be only practical because it productivity of the organisation use of multi-bit address buses and data buses.

According to M.S. Michael [11], this same built-in self-testable UART first achieves the required testability requirements, and then the major purpose is to build the cheapest implementation with the best performance. I published an article. The VHISC Hardware Description Language is used in the design process (VHDL). Then evaluate and synthesise your design with the Xilinx Foundation Series software.

FPGA (Field Programmable Gate Array) circuits, thus according Hazim Kamal Ansari and Asad Suhail Farooqi [12], were among the most recent innovations that were already changing the electronics industry. They've grown larger, better and faster, and cheaper, following the same integrated circuit production curves as processors and memory, and who are now widespread in small and medium-sized embedded systems. Many engineers can now work with midscale digital designs because among advancements in FPGA technology. They're used in surveillance radar, satellite communications, automotive, manufacturing, and a variety of these other industries. With both the intervention of the Universal Asynchronous Receiver Transmitter, time-triggered communication within the FPGA has been improved (UART). Works by converting binary information across sequentially and simultaneous. This machine is switched digital signals into serial data when it is received. The information can be accessed using the secondary UART. The UART manages everything including communication to synchronization to parity verification and more. VHDL is used to create the UART. Your specifications are transformed into a structure that depicts the digital capabilities you desire during the design phase.

# **CHAPTER 3 - ARCHITECTURE OF UART**

# Transmitter Design of UART OPERATION

The transmitter will transform this same serial bit stream toward a parallel bit stream. To count individual bits transferred, the transmitter's architecture would have a data register (trans data reg), controller, a data shift register (trans shift reg) and then a register status (bits contr). This presenter CPU provides the input signals, while the output signals govern data transfer in the UART. The trying to follow seem to be the inputs toward the controller.

The controller has the following inputs.

- ready: assert by the host machine to indicate that data bus has valid data.

- t\_byte: transition of state to sending.

- bit\_counter: counts the bit during transmission. Controlled forming the given o/p to control the code word of transmitted.

- Load\_shiftreg: Assertioning of load\_shiftreg loads the contents of tx\_datareg to tx\_shiftreg.

- clear: clears bit\_counter.

A finite state machine was used in the transmitter design. These three states transmitter state machine..

#### A. idle

The equipment enters the above state because when reset is asserted. It's also the default condition. Two activities can take place throughout this state.

- The information of transmitter data reg being imported in and out of transmitter shiftreg, which seems to have ten bits; the begin bit is LSB, the end bit is MSB, and the middle eight bits are data bits.

- State transition from state idle to state waiting.

#### B. waiting

The machine remains in waiting state until the external processor asserts t\_byte.

#### C. sending

The LSB tx shiftreg will really be communicated throughout the transmitting state. The first transmitted bit seems to be a zero, which informs wireless receiver that transmission had already begun. The elements of tx shiftreg are moved toward LSB at around the same time. 1s are replenish in tx shiftreg & bit counter is incrementing the data shifting occurs. Whenever bit counter is fewer than [word size+2], the state remains in transmitting. Clear is setting to one whenever the bit counter reaches [word size+2], indicating that all bits will be enhanced words will be moved to serially o/p. The equipment returns to idle at the vergesclock. The design of the system of a UART transmitter is depicted in Fig.

Fig. 2. State diagram of UART transmitter

#### 3.2 Baud Rate Generator

These quantity to characters transferred per sec is characterized as baud rate of a high bandwidth system. A character can represent more than one binary bit if it has more than two states. A frequency divider is similar to something like a baud rate generator. Hang on the given system clock frequency and indeed the necessary baud rate, this same baud rate frequency factor can sometimes be determined. Because counting things of the baud rate generator's frequency coefficient (M) is.

The operating system in their architecture is 50 MHz, and indeed the baud rate will be 9600 bits per second. The baud rate generator's output clock frequency is 19600Hz.

So,

The frequency coefficient M should not be in a round figure throughout this case. We count on the assumption that perhaps the serial interface would tolerate a few percentages more baud rate generation inaccuracy to achieve efficiency in FPGA.,

# 3.3 <u>UART Receiver Design</u>

The serial bit quantity of information is received by that of the UART receiver. The information is then converted to parallel format by removing the start and stop bits. Data will be taken into account while selecting set by baud rate generator, which would be generated somewhere at receiver's host, in with us architecture. Counter will sampled the cycle of clock will be verify that perhaps data is shown throughout the midst of a bit time interval. The sampled algo might be verified:

- The bit will be received and start properly.

- produce sample.

- Load the data into local bus.

Only after input data goes low, subsequent samples containing value 0 will establish this same start bit will be arrived. Afterwards to , three further specimens were taken to guarantee that a valid start bit has already been received. Going to follow that, 8 bits will be represents at roughly the middle of corresponding bit times. The receiver state machine in our design comprises three states: stop, starting, and the idle. Sample clock synchronises transitioned throughout states. The clock representative will be synchronized in the middle states by Transition.

#### A. idle

A The machine was switched into standby mode because when asynchronous active low reset was asserted. That's also the default condition. It should be there unless data in is turned off. The machine switches to state commencing whenever data in is extremely sufficient, the machine makes a transition to state starting.

#### B. starting

In order to determining whether the first bit is a legitimate start bit accept but rather reject, this same computer system recordings data including its prior level. Unless the bit is zero, it is indeed an acceptable start bit; otherwise, it's really meaningless.

Predicated somewhat on statistical features, an Inc specimen counter will indeed be asserted, gradually increasing the counter's maximum. Everything just acknowledges clear different sampling counter just before clearing this same counter.

### c.Receiving

For every 8 data bits, 8 samples are taken in the receiving state. Throughout this case, inc sample counter will indeed be asserted. After that, bit counter is incremented. Increase bit counter and shifts are asserted if the sample bit is not the last bit. The representative value should be freight in the shift register's the Most Significant Bit recipient, which is the recipient shift register, when the shift assertion is being. It will also shifting the reg 7 leftmost bits to the LSB. Load and ready out are set to 1 once all the bits have been sampled. The contents of receiver shift reg will load onto the data bus as a parallel word when load is asserted with logic high. The handshake output signal to the CPU is the assertion of ready out. In Fig. The UART receiver's status diagram being provided-

Fig. 3. State diagram of UART receiver

### **CHAPTER 4 – VERILOG CODE**

uart.v `timescale 1ps/1ps module for asynchronous communication, for expample, The serial port of PC 8/N/1 Eight bits data, There is no parity check, One bit stop module UART( //\*\*\*\*\* Reset signal and global clk \*\*\*\*\* ip clock, // clk of system i Reset M, // reset's the system //\*\*\*\*\*\*\*consucutive lines\*\*\*\*\*\*\*\* i\_rec, //receiving line o\_trans, //sending line //\*\*\*\*\*\* controal's the signals \*\*\*\*\*\*\*\*\*\* //receiving finish. this signal is in low level during receiving processing, it turn to high o Receiver, level after receiving finish. o\_Transmitter,//sending finish. this signal is in low level during sending processing, it turn to high level after sending finish. i trans,//seding request has been sent from high level to low level whenever process will start. iT SENDDATA. //It will send the data. oR RECEIVEDATA //it will received the data. ); input ip\_clock; input i\_Reset\_M; input i\_rec; output o\_trans; output o\_Receiver; output o\_Transmitter; input iT; input [7:0] iT\_SENDDATA; output [7:0] oR\_RECEIVEDATA; reg o\_trans; reg o\_Receiver; reg o Transmitter; reg [7:0] o\_RrceiverDATA; parameter clock frequency=100000; //It shows system's clock frequency BAUD\_RATE=9600; //the baud rate localparam BAUD\_COUNT=clock\_frequency/BAUD\_RATE; //counts the baud rate localparam BAUD 1=BAUD COUNT/4; //the first sampling point localparam BAUD 2=BAUD COUNT/2; //the sencond sampling point localparam //the thirt sampling point BAUD\_3=(3\*BAUD\_COUNT)/4; reg [15:0] r ReceiverBaudCount; //sents the baud rate count reg [15:0] r TransmitterBaudCount;//receives the baud rate reg [7:0] r ReceiveData; //received data reg [7:0] r\_TransmitterData; //seding data reg [2:0] recSample\_1; //It counts the high level sampling point //Receives the bits count reg [2:0] r ReceiverBitCount;

```

reg [2:0] r_TransmitterBitCount;

//sends the count

reg rReceiver syn,rReceiver syn 0; //i Receiver syn always@(posedge ip clock or negedge

i Reset M)

begin if(!i Reset M){rReceiver syn,rReceiver syn 0}<=2'b11;

else {rReceiver_syn,rReceiver_syn_0}<={rReceiver_syn_0,iReceiver};

end

reg [2:0] rStateM; //receiving state machine

localparam rStateM 0=3'b000;

localparam rStateM 1=3'b001; localparam rStareM 2=3'b010; localparam rStateM 3=3'b100;

always@(posedge ip_clock or negedge i_Reset_M)begin if(!i_Reset_M) rStateM<=rStateM_0;

else begin

case(rStateM)

rStateM 0:if(!rReceiver syn) rStateM<=rStateM 1;

rStateM 1:begin

// start bit will be receiving if(r_ReceiverBaudCount==BAUD_COUNT)begin

if(rSample 1[1]) rStateM<=rStateM 0;

//starting signal will wait

else rStateM<=rStateM 2; //date bits will be received

end

end

rStateM 2:begin //data received if(r ReceiverBitCount==3'd7)

if(r ReceiverBaudCount==BAUD COUNT) rStateM<=rStateM 3;

//end bit will received

end

end

rStateM_3:begin //stop bit will be receving if(r_ReceiverBaudCount==BAUD_COUNT)

begin if(!rReceiver_syn) rStateM<=rStateM_1;</pre>

else rStateM<=rStateM 0;

end

end

default: rStateM<=rStateM_0; endcase</pre>

end

end

wire wEnableSamp=(r_ReceiverBaudCount==BAUD_1) | (r_ReceiverBaudCount==BAUD_2) |

(r_ReceiverBaudCount==BAUD_3);

//r_Samp_1 high level sampling point will add

//r Samp 1

always@(posedge ip clock or negedge i Reset M)begin if(!i Reset M) r Samp 1<=3'b0;

else begin if(r_ReceiverBaudCount<BAUD_1)r_Samp_1<=3'b0; else if(wEnableSample)begin

if(rReceiver_syn) r_Samp_1<={r_Samp_1[1:0],1'b1};

end

end

end

//Receiving bits for count

//r ReceiverBitCount

```

```

always@(posedge ip_clock or negedge i_Reset_M)begin if(!i_Reset_M) r_ReceiverBitCount<=3'd0;

else if(rstateM==rStateM 2)begin

if(r_ReceiverBaudCount==BAUD_COUNT) r_ReceiverBitCount<=r_ReceiverBitCount+3'd1;

end

else r ReceiverBitCount<=3'd0;

end

//r ReceiverBaudCount

//data receive's for baud rate count

always@(posedge ip_clock or negedge i Reset_M)begin if(!i Reset_M) r ReceiverBaudCount<=0;

else if(rStateM==rStateMta 0)

begin if(!rReceiver_syn) r_ReceiverBaudCount<=1; else r_ReceiverBaudCont<=0;</pre>

end

else begin

if(r_ReceiverBaudCount==BAUD_COUNT) r_ReceiverBaudCount<=1;

r ReceiverBaudCount<=r ReceiverBaudCount+1;

end end

//received data

//r RvdDat

always@(posedge ip_clock or negedge i_Reset_M)begin if(!i_Reset_M)r_RvdDat<=8'd0;

else if(rStateM==rStateM_2)begin if(r_ReceiverBaudCount==BAUD_COUNT)

begin if(r_samp_1[1]) r_rvdDat <= \{1b1, r_rvdDat[7:1]\};

else

r_RvdDat <= \{1'b0, r_RvdDat[7:1]\};

end end end

//receiving finish

//o Receiver

always@(posedge ip_Clock or negedge i_Reset_M)begin if(!i_Reset_M o_Receiver<=1'b1;

else

begin

case(rStateM)

rStateM 0:

o_Receiver<=o_Receiver; rStateM_1:o_Receiver<=1'b0; rStateM_2:o_Receiver<=1'b0;

rStateM 3:

if(r ReceiverBaudCount==BAUD COUNT)begin if(r Samp 1[1]) o Receiver<=1'b1;

else o Receiver<=1'b0; end

end endcase end

end

//received data

//out DATAReceived

always@(posedge ip_clock or negedge i_Reset_M)begin if(!i_Reset_M) out_DATAReceived<=8'd0;

else if(rStateM==rStateM 3)begin if(r ReceiverBaudCount==BAUD Samp 1[1])

```

```

out_DATAReceived<=r_RvdDat; end

end end

reg synReq,synReq 1,synReq 0; //sending request always@(posedge ip clock or negedge

i_Reset_M)begin if(!i_Reset_M) {synReq_synReq_1,synReq_0}<=3'b111;

else {synReq.synReq 1.synReq 0}<={synReq 1.synReq 0.ipT};

end

//sending state machine reg[2:0] T_stateM;

localparam T stateM 0=3'b000; localparam T stateM 1=3'b001; localparam T stateM 2=3'b010;

localparam T_stateM_3=3'b100;

always@(posedge ip clock or negedge i Reset M)begin if(!i Reset M) T stateM 0

else begin

case(T stateM)

T_stateM_0:if({synReq,synReq_1}==2'b01) T_stateM<=T_stateM_1;

T_stateM_1:if(r_TrmtrBaudCont==BAUD_CONT)T_stateM<=T_stateM_2;

//sending start bit

T_stateM_2:begin //data sends

if(r_TrmtrBitCount==3'd7)begin if(r_TrmtrBaudCont==BAUD_CONT) T_stateM<=T_stateM_3;

end

end

//stop bit sent if(r_TrmtrBaudCount==BAUD_COUNT)

T_stateM_3:begin

begin if({synReq,synReq 1}==2'b01) T stateM<=T stateM 1; else T stateM<=T stateM 0;

end end

default:T stateM<=T stateM 0; endcase

end end

//sending bit count

//r TransmitterBitCount

always@(posedge ip_clock or negedge i_Reset_M)begin if(!i_Reset_M) r_TransmitterBitCount<=3'd0;

else if(T stateM==T stateM 2)begin

if(r_TransmitterBaudCount==BAUD_CONT)r_TransmitterBitCount<=r_TransmitterBitCount+3'd1; end

else r TransmitterBitCount<=3'd0; end

//sends the baud rate count

//r TransmitterBaudCount

always@(posedge ip_clock or negedge i_Reset_M)begin if(!i_Reset_M) r_TransmitterBaudCount<=0;

else if(T_stateM==T_stateM_0)begin if({synReq,synReq_1}==2'b01) r_TransmitterBaudCount<=1;

else r TransmitterBaudCount<=0; end

else begin

if(r_TransmitterBaudCount==BAUD_COUNT) r_TransmitterBaudCount<=1; else

r TransmitterBaudCount<=r TransmitterBaudCount+1;

end end

//sending data

//r TransDat

always@(posedge ip clock or negedge i Reset M)begin if(!i Reset M) r TransDat<=8'd0;

```

```

else if(T_stateM==T_stateM_0)begin if({synReq,synReq_1}==2'b01)begin r_TransDat<=ip_TDATA;

//$display("%d",ip TDATA); //only debug end

else if(T stateM==T stateM 2)begin if(r TransmitterBaudCount==BAUD COUNT)begin

r_{\text{TransDat}} = \{1'b0, r_{\text{TransDat}}[7:1]\};

end end end

//the sending line

//o Transmitter

always@(posedge ip clock or negedge i Rrset M)begin if(!i Reset M) o Transmitter<=1'b1;

else begin case(T_stateM)

T stateM 0:o Transmitter<=1'b1;

T_stateM_1:o_Transmitter<=1'b0; //sending first bit T_stateM_2:begin //data sent

if(r TransmitterBaudCount==1) o Transmitter<=r TransDat[0];

end

T_stateM_3:o_Transmitter<=1'b1; //end bit send b endcase

end end

//sending finish

//o Trans

always@(posedge ip_clock or negedge i_Reset_M)begin if(!i_Reset_M) o_Trans<=1'b1;

else if(T stateM==T stateM o Trans<=1'b1;

else o_Trans<=1'b0; end

endmodule

baud rate generator.v

/*

It is divided in a 50MHz clock into a 115200 baud

receiver/transmitter pair where the receiver clock enable over samples by 16x.

*/

module baudrate generator(input wire clock 50m,

output wire recclock_enable, output wire transclock_enable);

parameter REC_ACCMAXMUM = 50000000 / (115200 * 16);

parameter TRANS_ACCMAXMUM = 50000000 / 115200;

parameter REC_ACCWID =$clog2(REC_ACCMAXMUM); parameter TX_ACC_WIDTH =

$clog2(TRANS_ACCMAXMUM); reg [REC_ACCWID - 1:0] rx_acc = 0;

reg [TRANS ACCWID - 1:0] trans acc = 0;

assign recclock_enable = (rec_acc == 5'd0); assign transclock_enable = (trans_acc == 9'd0);

always @(posedge clock_50m) begin

if (rec_acc == REC_ACCMAXMUM[REC_ACCWID - 1:0]) rec_acc <= 0;

end

else

```

```

rec_acc \le rec_acc + 5'b1;

always @(posedge clk 50m) begin

if (trans_acc == TRANS_ACC_MAXMUM[TRANS_ACCWID - 1:0]) trans_acc <= 0;

end

else

trans_acc <= trans_acc + 9'b1;

endmodule

transmitter.v

module trans(input wire [7:0] dinpt,

input wire wr enable,

input wire clock_50m,

input wire clockenable,

output reg transmitter,

output wire transmitter_by);

initial begin

transmitter = 1'b1;

end

parameter STA_IDLE = 2'b00; parameter STA_STRT = 2'b01; parameter STA_DATA = 2'b10;

parameter STA\_STP = 2'b11;

reg [7:0] data = 8'h00; reg [2:0] bit_position = 3'h0;

reg [1:0] state = STA_IDLE;

always @(posedge clock_50m) begin case (state)

STA_IDLE: begin

if (wr enable) begin

state <= STA_STRT;

data <= dinpt;

bit_position <= 3'h0;

end

end

STA_STRT: begin

if (clockenable) begin

transmitter <= 1'b0;

state <= STA_DATA;

end

end

STA_DATA: begin

if (clockenable) begin

if (bit_position == 3'h7)

```

```

else

state <= STA STP;

bit_position <= bit_position + 3'h1;</pre>

end

end

transmitter <= data[bit_position];</pre>

STA_STP: begin

if (clockenable) begin

transmitter <= 1'b1;

state <= STA_IDLE;

end

end

default: begin

transmitter <= 1'b1;

state <= STA_IDLE;</pre>

end

end

endcase

assign transmitter_by = (state != STA_IDLE);

endmodule

receiver.v

module recver(input wire rec,

output reg r_dey, input wire r_dey_clr,

input wire clock_50m, input wire clockenable,

output reg [7:0] data);

initial begin

r_{dey} = 0; data = 8'b0;

end

parameter REC_STA_SRT= 2'b00;

parameter REC_STA_DATA= 2'b01;

parameter REC_STA_STP= 2'b10;

reg [1:0] state = REC_STA_SRT;

reg [3:0] samp = 0;

reg [3:0] bit_position = 0;

reg [7:0] scrtch = 8'b0;

always @(posedge clock_50m) begin if (r_dey_clr)

r_{dey} <= 0;

```

```

if (clockenable) begin

case (state) REC STA SRT: begin

/*

*

Data bits will be collected when full bit will be sampled and low samples starts be counting.

*/

if (!receiver || samp != 0)

samp \le samp + 4'b1;

if (samp == 15) begin

state <= REC_STA_DATA; bit_position <= 0;

samp \le 0;

sertch \le 0;

end

end

REC_STA_DATA:

begin

samp \le samp + 4'b1;

if (samp== 4'h8) begin

scrtch[bit_position[2:0]] <= receiver; bit_position <= bit_position + 4'b1;</pre>

end

if (bit position == 8 && sample == 15) state <= REC STA STP;

REC_STA_STP: begin

if (samp == 15 || (samp >= 8 && !receiver)) begin state <= REC_STA_SRT;

data \le scrtch; r_dey \le 1'b1; samp \le 0;

end else begin

samp \le samp + 4'b1;

end

end

default: begin

state <= REC_STA_SRT;</pre>

end

end

end

end

end

endcase

endmodule

uart tx test.v

Sends the bits and data in the loop fashion from transmitter and receiver pins is the UART

testbench

Increases the bytes, we will receive the result, which we want.

*/

`include "uart.v"

module uart_trans_tst();

reg [7:0] data = 0;

```

```

reg clock = 0; reg en = 0;

wire transmitter_by;

wire r dey;

wire [7:0] rec_data;

wire loopback; reg r_dey_clr = 0;

uart tst_uart(.dinpt(data),

.wr_enable(en),

.clock_50m(clock),

.transmitter(loopback),

.teansmitter_by(transmitter_by),

.receiver(loopback),

.r_dey(r_dey),

.r_dey_clr(r_dey_clr),

.dout(receiverdata));

initial begin

$dumpfile("uart.vcd");

$dumpvars(0, uart_trans_tst);

enable <= 1'b1;

#2 enable <= 1'b0;

end

always begin

#1 \operatorname{clock} = \sim \operatorname{clock};

end

always @(posedge r_dey) begin #2 r_dey_clr <= 1;

#2 r_dey_clr <= 0;

if (receiverdata != data) begin

$display("FAIL: receiverdata %x does not match transmitter %x", receiverdata, data);

$finish; end else begin

if (receiverdata == 8'hff) begin

$display("SUCCESS: verified");

$finish;

end

end

end

data \le data + 1'b1; enable \le 1'b1;

#2 enable <= 1'b0;

endmodule

```

## <u>CHAPTER 5 – SIMULATION RESULTS</u>

### SIMULATION OF BAUD RATE GENERATOR

Fig. 4 baud rate generator

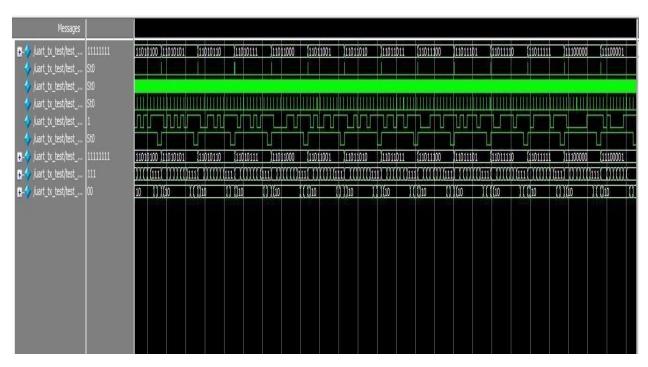

### TRANSMITTER SIMULATION

Fig. 5. Transmitter's simulation

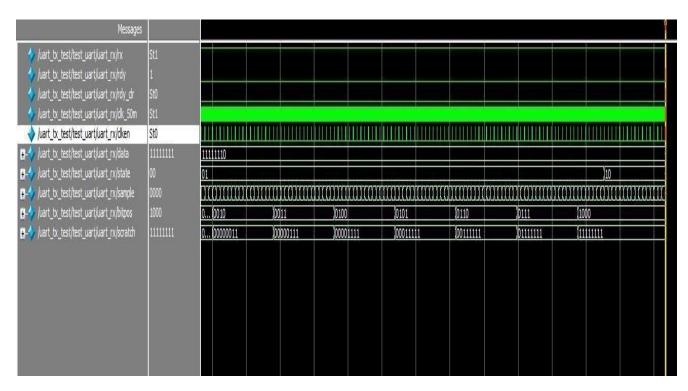

### **RECEIVER SIMULTION**

Fig. 6. Receiver simulation result

# CHAPTER 6 CONCLUSION

Throughout this project, I demonstrate how and where to design modern UART architecture on either an FPGA leveraging Verilog (hardware description language), that also encourages and promotes dependable serial data connection. The UART, Altera's clone II series, and FPGA chip EP2C20F484C7 are indeed being tested through using Modelsim simulator. The simulation findings have demonstrated to somehow be stable as well as dependable. The architecture seems to be quite flexible, even though it can detect as well as rectify numerous types of mistakes which it occurred through communication employing erroneous having checked techniques. It is therefore compatible with a wide range baud rates. As nothing more than a result, such design really does have the potential to play a significant influence within SoC technology inside this following year.

#### **REFERENCES**

- [1] Yi-yuan Fang, Xue-jun Chen "Design and Simulation of UART Serial Communication Module Based on VHDL" 2011 3rd International Workshop on Intelligent Systems and Applications.

- [2] Miss. M. A. Choudhari, Mr. S. B. Pawar, Prof. S. M. Sakhare-" Design of Transmitter & Receiver of UART in VHDL", International Journal on Recent and Innovation Trends in Computing and Communication ISSN: 2321-8169 Volume: 4 Issue: 5 146

- [3] Ananya Chakraborty, Surbhi, Sukanya Gupta, Swati Deshkar, Pradeep Kumar Jaisal "Design of UART (Universal Asynchr onous Receiver Transmitter) using VHDL". IJCST Vol. 3, Issue 1, Jan. March 2012

- [4] He Chun-zhi; Xia Yin-shui; Wang Lun-yao "A universal asynchronous receiver transmitter design" International Conference on Electronics, Communications and Control (ICECC) 2011 INSPEC Accession Number: Accession Number: 12436049 12436049

- [5] Biswajit Roy Dakua, Md. Ismail Hossain and Foisal Ahmed "Design and Implementation of UART Serial Communication Module Based on FPGA." International Conference on Materials, Electronics & International Conference on Materials, Electronics & Information Engineering, ICMEIE-2015 05-06 June, 2015 Information Engineering, ICMEIE-2015 05-06 June, 2015

- [6] Amanpreet Kaur, Amandeep Kaur, "An approach for designing a universal asynchronous receiver transmitter (UART)", International Journal of Engineering Research and Applications (IJERA) ISSN: Engineering Research and Applications (IJERA) ISSN: 2248-9622 www.ijera.com Vol. 2, Issue 3, May-Jun 2012, pp.2305-2311 2248-9622 www.ijera.com Vol. 2, Issue 3, May-Jun 2012, pp.2305-2311

- [7] Elmenreich, Wilfried and Martin Delvai. "Time Elmenreich, Wilfried and Martin Delvai. "Time--Triggered Communication with UARTs." (2001). Triggered Communication with UARTs." (2001).

- [8] M. Mamatha, IIVijaykumar R. Urkude "BIST Enabled UART for Real Time Interface Applications using FPGA" International Journal of Research in Electronics and Communication Technology (IJRECT 2015)

- [9] Martin Delvai1, Ulrike Eisenmann1, Wilfried Elmenreich1 "Intelligent UART Module for Real- Time Applications" Time Applications" Published 2003 in WISES Published 2003 in WISES

- [10] Shouqian Yu,Lili Yi ,Weihai Chen,Zhaojin Wen," Implementation of a Multi-channel UART -channel UART Controller Based on FIFO Te Controller Based on FIFO Technique and FPGA" 2007 IEEE chnique and FPGA" 2007 IEEE Sakshi S. Kedar, Dr. S. D. Chede, 2014, VHDL Implementation of Universal Asynchronous Transmitter, INTERNATIONAL JOURNAL OF ENGINEERING RESEARCH & TECHNOLOGY (IJERT) Volume 03, Issue 06 (June 2014),

- [11] M. S. Michael,"A Comparison of the INS8250, NS16450 and NS16550AF Series of UARTs", National Semiconductor Application Note 493, 1989 National Semiconductor Application Note 493, 1989

- [12] Hazim Kamal Ansari, Asad Suhail Farooqi," Design Of High Speed UART For

- Programming FPGA" International Journal Of Engineering And Computer Science Volume 1 Issue 1 Oct 2012. International Journal Of Engineering And Computer Science Volume 1 Issue 1 Oct 2012.

- [13] C. H. Roth, "Digital System Design Using VHDL", PWS Publishing Company, 1998.

- [14] Sakshi S. Kedar, Dr. S. D. Chede, 2014, VHDL Implementation of Universal Asynchronous Transmitter, INTERNATIONAL JOURNAL OF ENGINEERING RESEARCH & TECHNOLOGY (IJERT) Volume 03, Issue 06 (June 2014).

- [15] M. A. Choudhari, S. B. Pawar and S. M. Sakhare (2016) "Design of Transmitter & Receiver of UART in VHDL", International Journal on Recent and Innovation Trends in Computing and Communication ISSN: 2321-8169 Volume: 4 Issue: 5 146 149

- [16] Chakraborty, A., Gupta, S., Deshkar, S., & Jaisal, P.K. (2012). Design of UART (Universal Asynchronous Receiver Transmitter) using VHDL.

- [17] Kaur, Amanpreet and Amandeep Kaur. "An Approach For Designing A Universal Asynchronous Receiver Transmitter (UART)." (2012).

- [18] Dakua, Biswajit Roy et al. "Design and Implementation of UART Serial Communication Module Based on FPGA." (2015).

- [19] Jaiswal, Durgesh. (2015). Synthesis and Implementation of UART using VHDL Code.

- [20] Dhanadravye, Ashwini D. and Samrat S. Thorat. "A Review on Implementation of UART using Different Techniques." (2014).

- [21] Benodkar, Mangesh V. and Umesh W. Hore. "Design and Simulation of Universal Asynchronous Receiver Transmitter on Field Programmable Gate Array Using VHDL." International Journal of Scientific Research in Education 2 (2014): n. pag.

- [22] M. Mamatha, IIVijaykumar R. Urkude. "BIST Enabled UART for Real Time Interface Applications using FPGA." International Journal of Research in Electronics and Communication Technology (IJRECT 2015) 2014, IJRECT All Rights Reserved 10 Vol. 2, Issue 4 Oct. Dec. 2015

- [23] Wong, Ching-Chang, Lin, Yu-Han. "A Reusable UART IP Design and its Application in Mobile Robots". Mobile Robotics, Moving Intelligence, edited by Jonas Buchli, IntechOpen, 2006. 10.5772/4719.