# STUDY AND SIMULATION OF SECOND GENERATION VOLTAGE CONVEYOR AND ITS APPLICATION

## A DISSERTATION

# SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE

OF

## MASTER OF TECHNOLOGY

IN

## **VLSI DESIGN & EMBEDDED SYSTEMS**

Submitted By:

## SUMIT GANGWAR (2K20/VLS/21)

Under The Supervision Of:

## **DR. RAJESHWARI PANDEY**

# (PROFESSOR)

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY, DELHI

(Formerly Delhi College Of Engineering)

Bawana Road, Delhi- 110042

MAY 2022

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi- 110042

#### UNDERTAKING

I Sumit Gangwar, Roll No. 2K20/VLS/21 student of M.Tech (VLSI Design & Embedded Systems), hereby declare that the project Dissertation titled "Study and Simulation of Second Generation Voltage Conveyor and Its Application", which is submitted by me to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi in the partial fulfillment of the requirement for the award of the degree of Master of Technology is my original work. I have not plagiarized or submitted the same work for the award of any other degree. In case this undertaking is found incorrect, I accept that my degree may be unconditionally withdrawn.

Buit

Sumit Gangwar(2K20/VLS/21) Place:

Date: 30/05/2022 Delhi

# DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

Delhi Technological University, Delhi (Formerly Delhi College of Engineering) Delhi- 110042

#### CERTIFICATE

I hereby certify that the work contained in the project Dissertation titled "Study and Simulation of Second Generation Voltage Conveyor and Its Application", submitted by Sumit Gangwar, Roll No. 2K20/VLS/21 in the partial fulfilment of the requirement for the award of degree of Master of Technology in VLSI Design & Embedded Systems to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi, is a record of the project work carried out by the student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree of Diploma to this university or elsewhere.

Date: 30/05/2022 Place: Delhi

Dr. Rajeshwari Pandey (Professor) ECE Department DTU, Delhi

## ABSTRACT

Low-power design for portable devices is becoming increasingly crucial in today's environment. This entices researchers to seek for the best solution while minimising compromises with other characteristics like as speed and area. Power consumption is becoming a critical aspect in chip design as the density of transistors on a chip rises in order to meet high performance requirements. Power dissipation is becoming a serious challenge as transistors are being scaled down.

In this project I am working upon "Second Generation Voltage Conveyor (VCII)". VCII is based upon dual concept of CCII block. VCII is a three terminal device. It provides voltage realization atouput port. I am simulating a VCII Block using LTspice.We have used TSMC level 8, 180nm node parameter in our simulation. This block comprises of 2 stages 1<sup>st</sup> one is current buffer stage and 2<sup>nd</sup> one is voltage buffer stage. I have performed its DC analysis as current buffer and as a voltage buffer. I have calculated its impedance at all three ports. In this report I will discuss its functionality and and advantage over Op-Amp. and CCII block in detail.

In this report I will present the changes I have made, in current buffer stage, and in voltage buffer stage. In the previous simulation I used the current buffer stage with single output, this time I will use the differential current buffer stage and voltage buffer stage. These stage promises much better bandwidth, stability, and low power results in comparision to previous one. I will also implement application using this voltage conveyor. We will simulate the 1<sup>st</sup> order Low pass, High pass and Band pass active filters, current to voltage converter, voltage to current converter, voltage differentiator, voltage integrator, voltage buffer, current buffer, and perform AC analysis, DC and transient analysis.

## ACKNOWLEDGEMENT

It gives me immense pleasure to present this Dissertation work for the partial fulfillment for the award of degree of Master of Technology in VLSI Design & Embedded Systems. I owe special debt of gratitude to my supervisor **Dr. Rajeshwari Pandey**, Professor in Department of Electronics and Communication Engineering, Delhi Technological University, Delhi for their constant support and guidance throughout the course of my work. Their sincerity, thoroughness and perseverance have been a constant source of inspiration for me.

I would also like to thank all other faculty members of Electronics and Communication Engineering Department, DTU for their valuable suggestions and co-operation at every step in this project. I would also like to thank my parents and batchmates for their constant motivation throughout this work. Last but not the least I would like to thank Almighty for His invisible presence and constant support.

Buit Sumit Gangwar (2K20/VLS/21)

Date: 30/05/2022

Place: Delhi

# TABLE OF CONTENT

| UNDERTAKINGi              |

|---------------------------|

| CERTIFICATEii             |

| ABSTRACTiii               |

| ACKNOWLEDGEMENTiv         |

| LIST OF TABLESx           |

| LIST OF FIGURESxi-xvii    |

| ABBREVIATIONS USEDxviii   |

| CHAPTER 1: INTRODUCTION1  |

| 1.1 INTRODUCTION          |

| 1.2 MOTIVATION1           |

| 1.3 BUFFER2               |

| 1.4 IMPEDANCE MATCHING2   |

| 1.5 HIGH INPUT IMPEDANCE2 |

| 1.6 LOW OUTPUT IMPEDANCE                                           |

|--------------------------------------------------------------------|

| CHAPTER 2: REVIEW OF DIFFERENT TYPES OF VOLTAGE AND CURRENT BUFFER |

| CIRCUITS4                                                          |

| 2.1 VOLTAGE BUFFER4-5                                              |

| 2.1.1 HIGH VOLTAGE UNITY GAIN VOLTAGE FOLLOWER                     |

| 2.1.2 FULLY DIFFERENTIAL LOW VOLTAGE WIDE SWING VOLTAGE            |

| FOLLOWER                                                           |

| 2.1.3 CLASS AB TYPE FLIPPED VOLTAGE FOLLOWER7-9                    |

| 2.1.4 HIGH INPUT IMPEDANCE HIGH VOLTAGE UNITY GAIN VOLTAGE         |

| FOLLOWER9-10                                                       |

| 2.1.5 VOLTAGE BUFFER STAGE, USED IN PROPOSED VCII SIMULATED        |

| CIRCUIT10-12                                                       |

| 2.1.6 FLIPPED VOLTAGE FOLLOWER 12-13                               |

| 2.1.7 DIFFERENTIAL VOLTAGE BUFFER STAGE 13-14                      |

| 2.1.8 SIMULATION OF USED VOLTAGE BUFFER STAGE                      |

| 2.2 CURRENT BUFFER19                                            |  |

|-----------------------------------------------------------------|--|

| 2.2.1 DIFFERENTIAL CURRENT FOLLOWER                             |  |

| 2.2.2 DIFFERENTIAL CURRENT BUFFER USING COMMON FEED FORWARD     |  |

| TECHNIQUE21                                                     |  |

| 2.2.3FULLY DIFFERENTIAL CURRENT FOLLOWER HAVING LOW INPUT       |  |

| IMPEDANCE AND LOW POWER CAPABILITY                              |  |

| 2.2.4 HIGH CMRR AND LOW POWER FULLY DIFFERENTIAL CURRENT        |  |

| FOLLOWER23-24                                                   |  |

| 2.2.5 COMMON MODE SEPRATION TECHNIUQE BASED CURRENT             |  |

| BUFFER                                                          |  |

| 2.2.6 CURRENT BUFFER STAGE USED IN PROPOSED VCCII CIRCUIT 25-29 |  |

| 2.2.7 SIMULATION OF USED CURRENT BUFFER STAGE                   |  |

| CHAPTER 3: REVIEW OF DIFFERENT TECHNIQUES CURRENT AND VOLTAGE   |  |

| CONVEYOR                                                        |  |

| 3.1 CURRENT MODE OPERATION                                      |  |

| 3.2 CURRENT CONVEYORS                                             |  |  |

|-------------------------------------------------------------------|--|--|

| 3.2.1 CURRENT CONVEYOR'S TRANSISTOR LEVEL IMPLEMENTATION36-37     |  |  |

| 3.2.2 QUASI FLOATING TYPE CURRENT CONVEYOR                        |  |  |

| 3.2.3 FULLY DIFFERENTIAL TYPE CURRENT CONVEYOR                    |  |  |

| 3.2.4 CURRENT CONVEYOR APPLICATION                                |  |  |

| 3.3 VOLTAGE MODE OPERATION40                                      |  |  |

| 3.4 VOLTAGE CONVEYOR40-42                                         |  |  |

| 3.4.1 RAIL TO RAIL VCII42-43                                      |  |  |

| 3.4.2 SECOND GENERATION VOLTAGE CONVEYOR44                        |  |  |

| CHAPTER 4: PREVIOUSLY IMPLEMENTED VCII SIMULATION RESULTS45       |  |  |

| 4.1 SIMULATION RESULTS45-49                                       |  |  |

| 4.1.1 SIMULATION RESULTS OF FULLY DIFFERENTIAL CURRENT BUFFER     |  |  |

| STAGE                                                             |  |  |

| CHAPTER 5: SIMULATION RESULTS OF PROPOSED VCCII STRUCTURE AND ITS |  |  |

| APPLICATION56                                                     |  |  |

| R | REFRENCES                                   | 73-77  |

|---|---------------------------------------------|--------|

| C | CHAPTER 6: LEARNINGS FROM PROJECT           | .71-72 |

|   | 5.2 SIMULATION OF APPLICATION OF VCII BLOCK | .59-70 |

|   | 5.1 SIMULATION OF PROPOSED VOLTAGE CONVEYOR | .56-59 |

# LIST OF TABLES

| Table 2.1: Aspect ratio used in simulation of buffer stage                          | 14-15 |

|-------------------------------------------------------------------------------------|-------|

| Table 2.2: Aspect ratio used in simulation of current buffer stage                  | 29    |

| Table 4.1: Transistor sizing used in simulation of the Voltage Conveyor II circuit  | 45    |

| Table 4.2: Transistor sizing used in circuit given in refrence paper[3]             | 46    |

| Table 4.3: Aspect ratio and biasing parameters used in simulation of current buffer | 50    |

| Table 4.4: Aspect ratio used in voltage conveyor circuit                            | 51-52 |

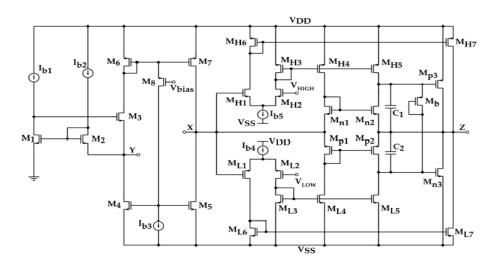

| Table 5.1: Table of aspect ratio used in proposed voltage conveyor circuit          | 56-57 |

# LIST OF FIGURES

| Figure 1.1: Voltage buffer circuit designed using Op-Amp                                                         | 2             |

|------------------------------------------------------------------------------------------------------------------|---------------|

| Figure 2.1: Small signal model of Ideal Voltage buffer circuit                                                   | 4             |

| Figure 2.2: Pictorial representation of high voltage unity gain voltage follower circuit [1]                     | 5             |

| Figure 2.3: Circuit diagram of FDDA based voltage buffer [2]                                                     | 7             |

| Figure 2.4: Circuit diagram of class AB type flipped voltage follower circuit a). without b b). with biasing [3] | oiasing<br>8  |

| Figure 2.5: Circuit diagram of high input impedance and high voltage unity gain voltage fol circuit [4]          | llower<br>9   |

| Figure 2.6: Circuit diagram of conventional voltage follower [5]                                                 | 10            |

| Figure 2.7: Circuit diagram of Voltage follower with rai to rail capability [5]                                  | 11            |

| Figure 2.8: Circuit diagram of common drain voltage buffer and flipped voltage buffer [6]                        | 12            |

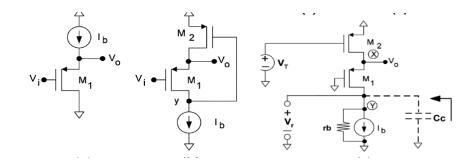

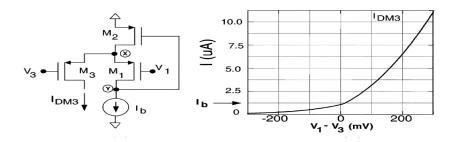

| Figure 2.9: Circuit diagram of Differential flipped voltage buffer and corresponding output c plot[6]            | eurrent<br>14 |

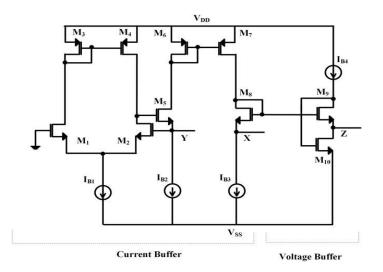

| Figure 2.10: Circuit diagram of voltage follower circuit used in proposed VCII block                             | 15            |

| Figure 2.11: Plot of AC analysis of voltage follower circuit used in proposed VCII block                         | 16            |

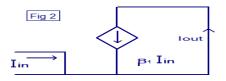

| Figure 2.13: Plot of transient analysis of voltage follower circuit used in proposed VCII block       17         Figure 2.14: Plot of transient analysis using step response of voltage follower circuit used i proposed VCII block       18         Figure 2.15: Plot of power consumption of voltage follower circuit used in proposed VCII block       18         Figure 2.16: Small signal model of ideal current buffer circuit       19         Figure 2.17: Circuit diagram of differential current follower [22]       20         Figure 2.18: Circuit diagram of current buffer using common feed forward technique [7]       21         Figure 2.19: Circuit diagram of fully differential current follower having low input impedanc capability [26]       22         Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]       24         Figure 2.21: Circuit diagram of common mode separation technique based current buffer       25         Figure 2.22: Circuit diagram of current buffer stage used in proposed VCII block [8]       27         Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]       27         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]       28 | Figure 2.12: Plot of DC analysis of voltage follower circuit used in proposed VCII block    | 17      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------|

| Figure 2.14: Plot of transient analysis using step response of voltage follower circuit used in proposed VCII block       18         Figure 2.15: Plot of power consumption of voltage follower circuit used in proposed VCII block       18         Figure 2.16: Small signal model of ideal current buffer circuit       19         Figure 2.17: Circuit diagram of differential current follower [22]       20         Figure 2.18: Circuit diagram of current buffer using common feed forward technique [7]       21         Figure 2.19: Circuit diagram of fully differential current follower having low input impedanc capability [26]       22         Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]       24         Figure 2.21: Circuit diagram of common mode separation technique based current buffer       25         Figure 2.22: Circuit diagram of current buffer stage used in proposed VCII block [8]       27         Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]       28                                                                                                                                                                                                                                | Figure 2.13: Plot of transient analysis of voltage follower circuit used in proposed VCII b | lock    |

| proposed VCII block18Figure 2.15: Plot of power consumption of voltage follower circuit used in proposed VCII block18Figure 2.16: Small signal model of ideal current buffer circuit19Figure 2.16: Small signal model of ideal current buffer circuit19Figure 2.17: Circuit diagram of differential current follower [22]20Figure 2.18: Circuit diagram of current buffer using common feed forward technique [7]21Figure 2.19: Circuit diagram of fully differential current follower having low input impedanc<br>capability [26]22Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]24Figure 2.21: Circuit diagram of common mode separation technique based current buffer25Figure 2.22: Circuit diagram of current buffer stage used in proposed VCII block [8]27Figure 2.23: Circuit diagram of current buffer in differential mode used in proposed VCII block18Figure 2.24: Circuit diagram of current buffer in common mode used in proposed VCII block28Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block28                                                                                                                                                                                                                                                                                                                                                |                                                                                             | 17      |

| Figure 2.15: Plot of power consumption of voltage follower circuit used in proposed VCII block       18         Figure 2.16: Small signal model of ideal current buffer circuit       19         Figure 2.16: Circuit diagram of differential current follower [22]       20         Figure 2.17: Circuit diagram of current buffer using common feed forward technique [7]       21         Figure 2.18: Circuit diagram of fully differential current follower having low input impedanc capability [26]       22         Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]       24         Figure 2.21: Circuit diagram of common mode separation technique based current buffer       25         Figure 2.22: Circuit diagram of common gate based current buffer [8]       26         Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]       27         Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]       28                                                                                                                                                                                                                                                                               |                                                                                             | used in |

| 18Figure 2.16: Small signal model of ideal current buffer circuit19Figure 2.17: Circuit diagram of differential current follower [22]20Figure 2.18: Circuit diagram of current buffer using common feed forward technique [7]21Figure 2.19: Circuit diagram of fully differential current follower having low input impedance capability [26]22Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]24Figure 2.21: Circuit diagram of common mode separation technique based current buffer25Figure 2.22: Circuit diagram of current buffer stage used in proposed VCII block [8]27Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]28Figure 2.25: Circuit diagram of current buffer in common mode sed used in proposed VCII block [8]28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | proposed VCII block                                                                         | 18      |

| Figure 2.16: Small signal model of ideal current buffer circuit19Figure 2.17: Circuit diagram of differential current follower [22]20Figure 2.18: Circuit diagram of current buffer using common feed forward technique [7]21Figure 2.19: Circuit diagram of fully differential current follower having low input imperation<br>capability [26]24Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]24Figure 2.21: Circuit diagram of common gate based current buffer [8]26Figure 2.22: Circuit diagram of current buffer stage used in proposed VCII block [8]27Figure 2.23: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]28Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Figure 2.15: Plot of power consumption of voltage follower circuit used in proposed VCII    | block   |

| Figure 2.17: Circuit diagram of differential current follower [22]       20         Figure 2.18: Circuit diagram of current buffer using common feed forward technique [7]       21         Figure 2.19: Circuit diagram of fully differential current follower having low input impedance capability [26]       22         Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]       24         Figure 2.21: Circuit diagram of common mode separation technique based current buffer       25         Figure 2.22: Circuit diagram of common gate based current buffer [8]       26         Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]       27         Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             | 18      |

| Figure 2.18: Circuit diagram of current buffer using common feed forward technique [7]       21         Figure 2.19: Circuit diagram of fully differential current follower having low input impedance capability [26]       22         Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]       24         Figure 2.21: Circuit diagram of common mode separation technique based current buffer       25         Figure 2.22: Circuit diagram of common gate based current buffer [8]       26         Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]       27         Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 2.16: Small signal model of ideal current buffer circuit                             | 19      |

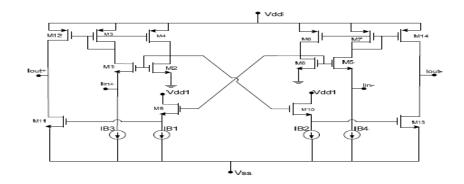

| Figure 2.18: Circuit diagram of current buffer using common feed forward technique [7]       21         Figure 2.19: Circuit diagram of fully differential current follower having low input impedance capability [26]       22         Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]       24         Figure 2.21: Circuit diagram of common mode separation technique based current buffer       25         Figure 2.22: Circuit diagram of common gate based current buffer [8]       26         Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]       27         Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 2.17: Circuit diagram of differential current follower [22]                          | 20      |

| Figure 2.19: Circuit diagram of fully differential current follower having low input impedance<br>capability [26]22Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]24Figure 2.21: Circuit diagram of common mode separation technique based current buffer25Figure 2.22: Circuit diagram of common gate based current buffer [8]26Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]27Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block28Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 2.17. Circuit diagram of differential current follower [22]                          | 20      |

| capability [26]22Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]24Figure 2.21: Circuit diagram of common mode separation technique based current buffer25Figure 2.22: Circuit diagram of common gate based current buffer [8]26Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]27Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]28Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 2.18: Circuit diagram of current buffer using common feed forward technique [7]      | 21      |

| capability [26]22Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]24Figure 2.21: Circuit diagram of common mode separation technique based current buffer25Figure 2.22: Circuit diagram of common gate based current buffer [8]26Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]27Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]28Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 2.19: Circuit diagram of fully differential current follower having low input imp    | edance  |

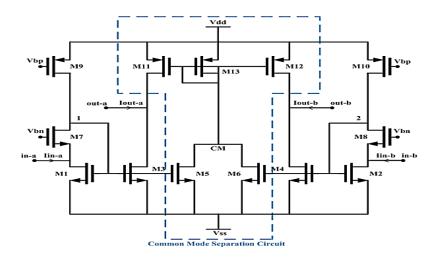

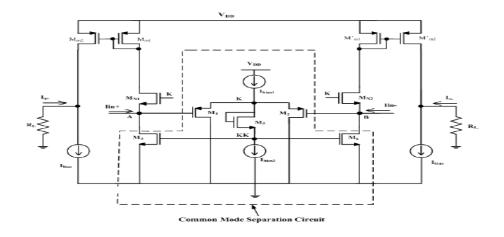

| Figure 2.21: Circuit diagram of common mode separation technique based current buffer       25         Figure 2.22: Circuit diagram of common gate based current buffer [8]       26         Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]       27         Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |         |

| Figure 2.21: Circuit diagram of common mode separation technique based current buffer       25         Figure 2.22: Circuit diagram of common gate based current buffer [8]       26         Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]       27         Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |         |

| Figure 2.22: Circuit diagram of common gate based current buffer [8]       26         Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]       27         Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 2.20: Circuit diagram of high CMRR and Low power current follower [9]                | 24      |

| Figure 2.22: Circuit diagram of common gate based current buffer [8]       26         Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]       27         Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]       28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 2.21: Circuit diagram of common mode congration technique based current buffer       | 25      |

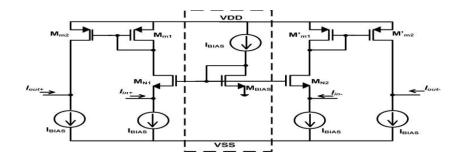

| Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]       27         Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII block [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 2.21. Circuit diagram of common mode separation technique based current burier       | 23      |

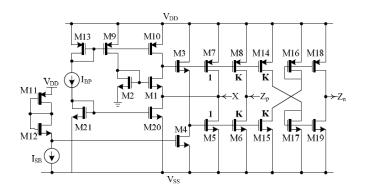

| Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII bloc<br>[8] 28<br>Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 2.22: Circuit diagram of common gate based current buffer [8]                        | 26      |

| Figure 2.24: Circuit diagram of current buffer in differential mode used in proposed VCII bloc<br>[8] 28<br>Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                             |         |

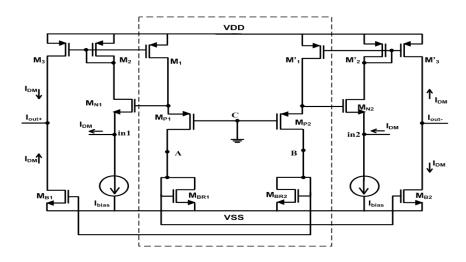

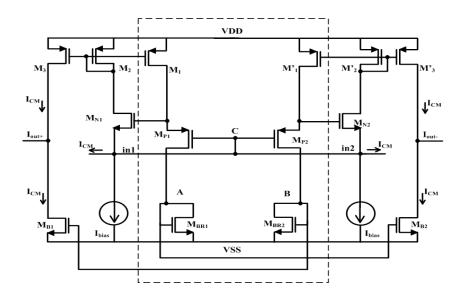

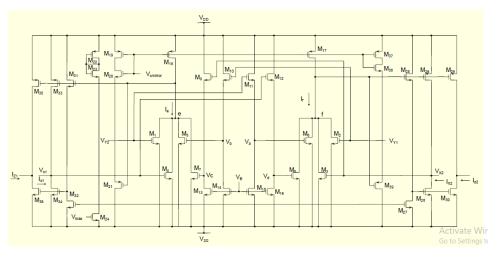

| [8]   28     Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Figure 2.23: Circuit diagram of current buffer stage used in proposed VCII block [8]        | 27      |

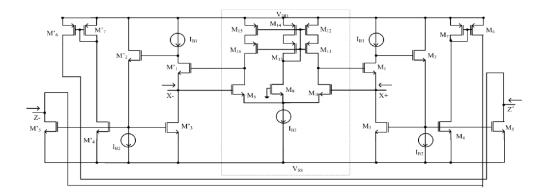

| [8]       28         Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 2.24. Circuit diagram of current buffer in differential mode used in proposed VCI    | T block |

| Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII block [8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                             |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                             |         |

| 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 2.25: Circuit diagram of current buffer in common mode used in proposed VCII blo     | ock [8] |

| 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                             | 28      |

xii

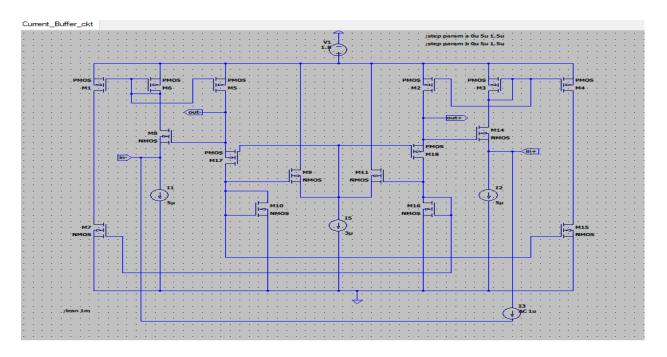

| Figure 2.26: Circuit diagram of current buffer stage used in proposed VCII block         | 30 |

|------------------------------------------------------------------------------------------|----|

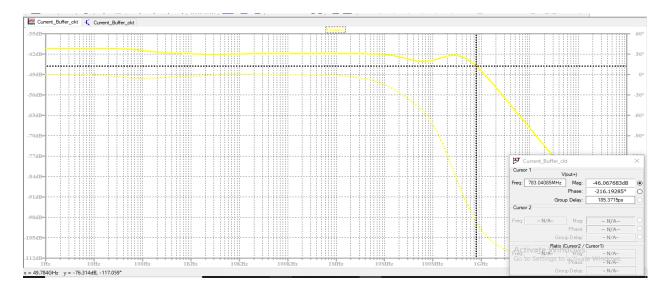

| Figure 2.27: Plot of AC analysis of used current buffer stage                            | 31 |

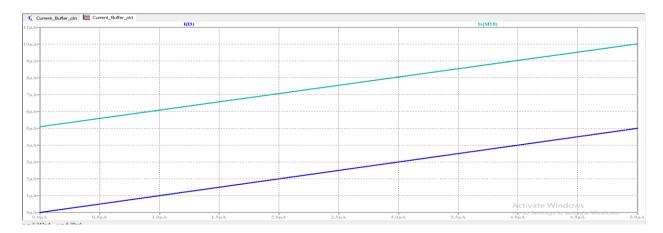

| Figure 2.28: Plot of DC analysis of used current buffer stage                            | 31 |

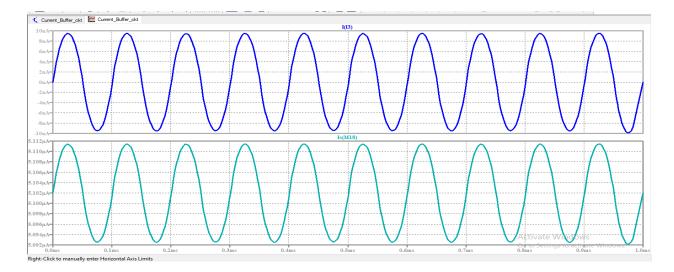

| Figure 2.29: Plot of transient analysis of used current buffer stage                     | 32 |

| Figure 2.30: Plot of transient analysis using step response of used current buffer stage | 32 |

| Figure 2.31: Plot of power consumption of current buffer stage                           | 33 |

| Figure 3.1: Block diagram of Current Conveyor [11]                                       | 36 |

| Figure 3.2: Transistor level implementation of CCII+ block [12]                          | 37 |

| Figure 3.3: Circuit diagram of quasi floating type current conveyor [13]                 | 38 |

| Figure 3.4: Block diagram of FD current conveyor [14]                                    | 39 |

| Figure 3.5: Circuit diagram of FD current conveyor [14]                                  | 39 |

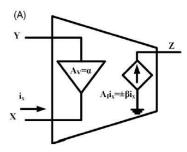

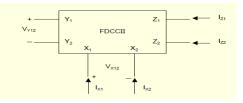

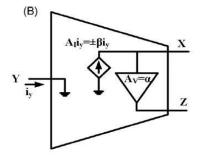

| Figure 3.6: Block diagram of Second Generation Voltage Conveyor[11]                      | 41 |

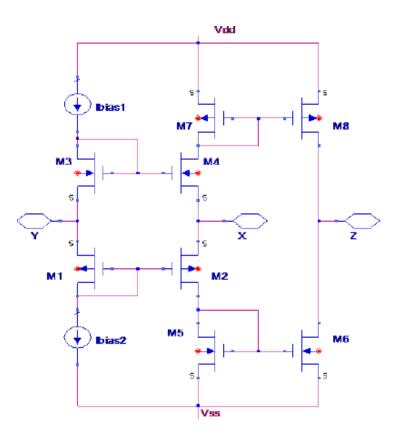

| Figure 3.7: Transistor level implementation of VCII block[11]                            | 42 |

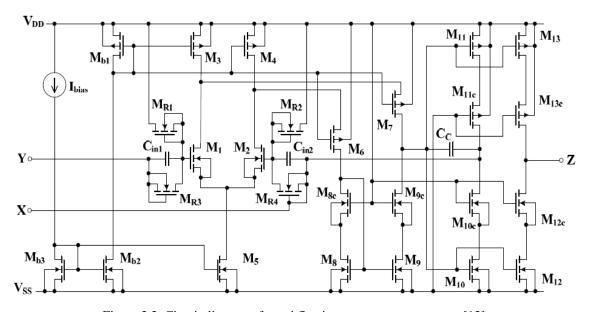

| Figure 3.8: Circuit diagram of rail to rail VCII [15]                                    | 43 |

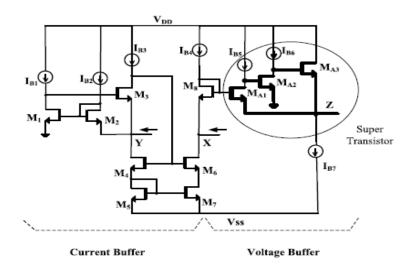

| Figure 3.9: Circuit diagram of VCII using super transistor concept[16]                        | 44 |

|-----------------------------------------------------------------------------------------------|----|

| Figure 4.1: Circuit diagram of Voltage Conveyor II [11]                                       | 45 |

| Figure 4.2: Circuit diagram of voltage conveyor II                                            | 46 |

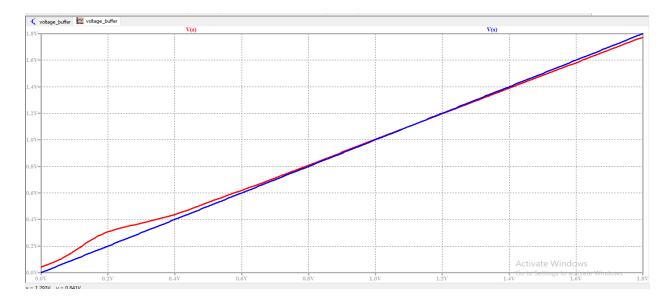

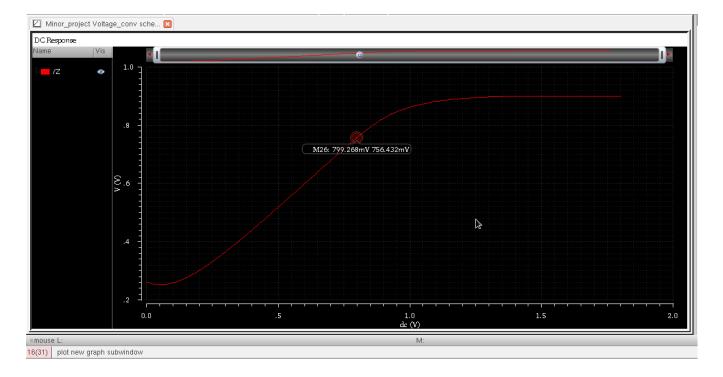

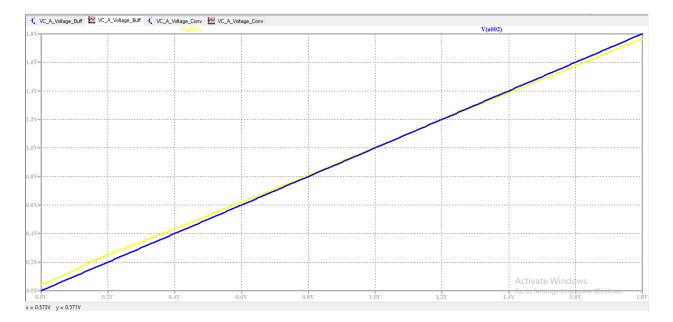

| Figure 4.3: Graph plotted between current at y port and at x-port (Current DC analysis)       | 47 |

| Figure 4.4: Graph plotted between Voltage at x port and z port (Voltage DC analysis)          | 47 |

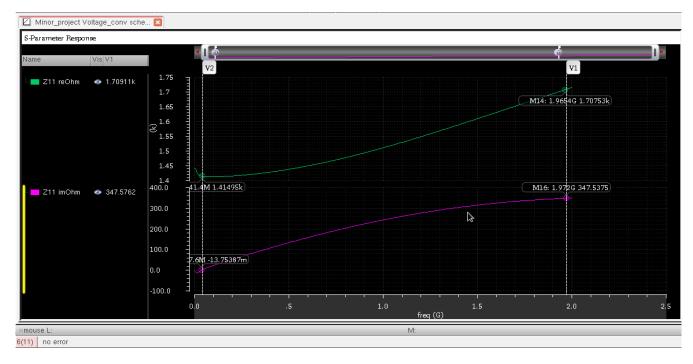

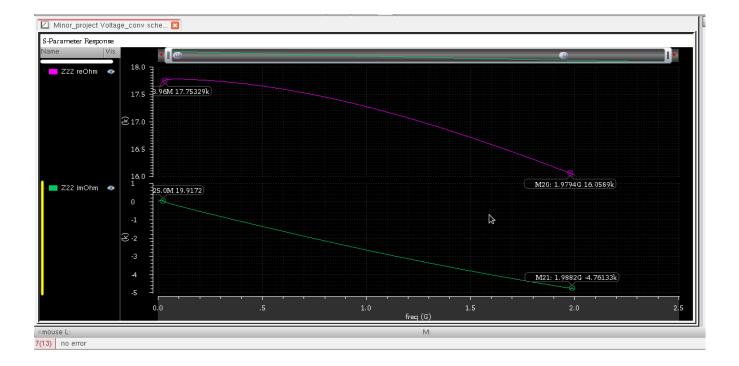

| Figure 4.5: Graph plotted for impedance at y port (real & imaginary)                          | 48 |

| Figure 4.6: Graph plotted for impedance at x port (real & imaginary)                          | 48 |

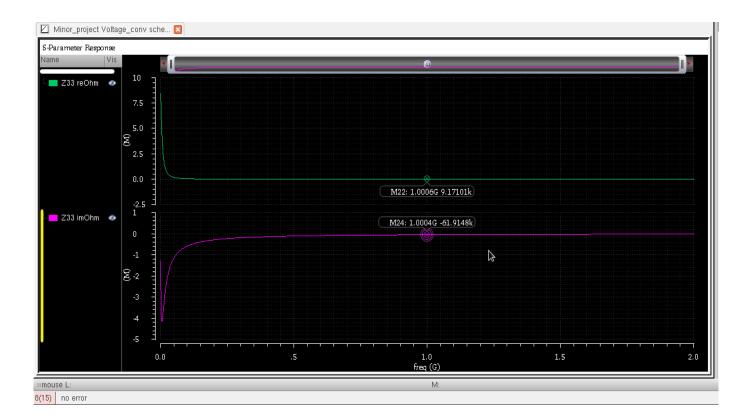

| Figure 4.7: Graph plotted for impedance at z port (real & imaginary)                          | 49 |

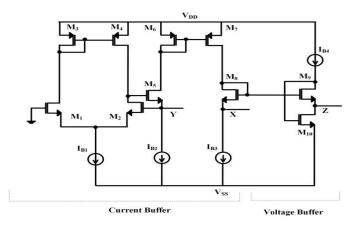

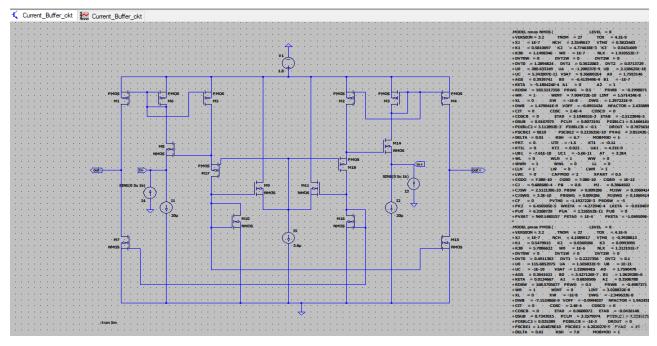

| Figure 4.8: Circuit diagram of fully differential current buffer source                       | 50 |

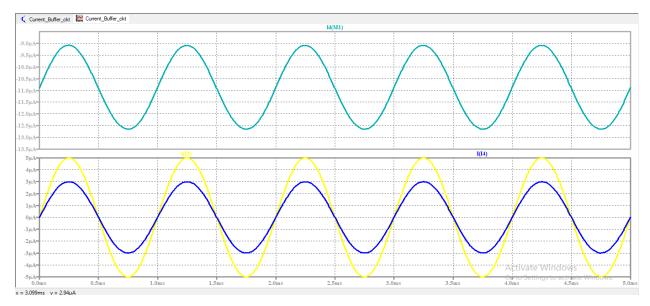

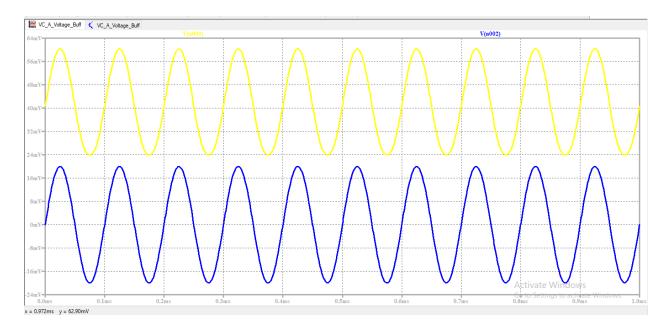

| Figure 4.9: Transient response of fully differential current buffer                           | 51 |

| Figure 4.10: Circuit diagram of second generation voltage conveyor                            | 52 |

| Figure 4.11: Hierarchical symbol of voltage conveyor block                                    | 52 |

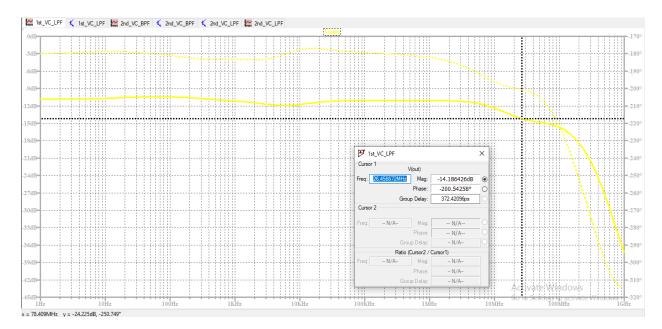

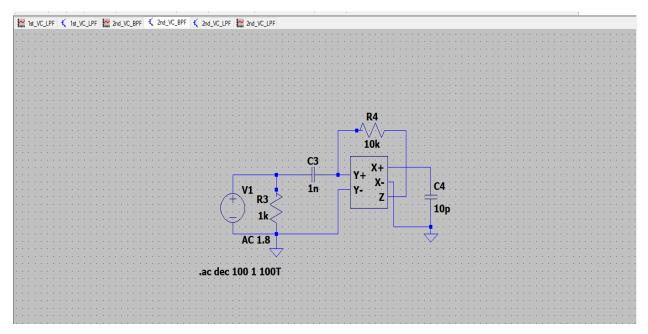

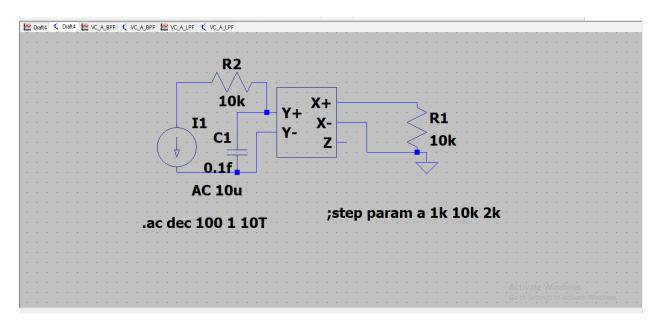

| Figure 4.12: Circuit diagram of 1 <sup>st</sup> order active low pass filter using VCII block | 53 |

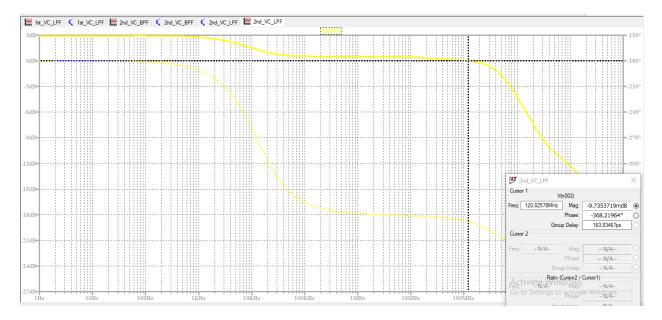

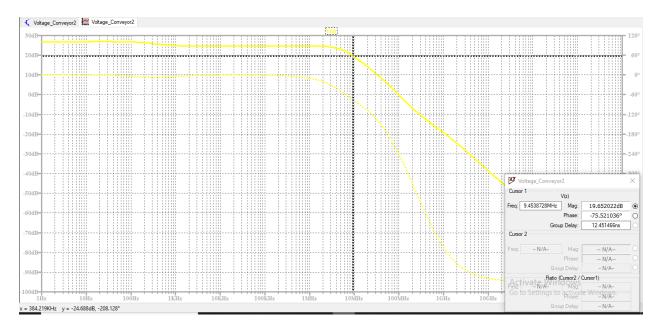

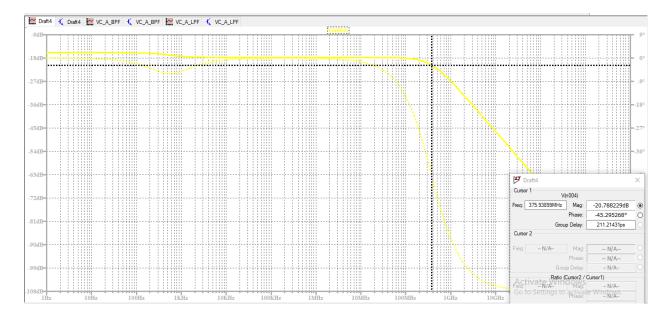

| Figure 4.13: Frequency response plot of 1 <sup>st</sup> order active low pass filter          | 53 |

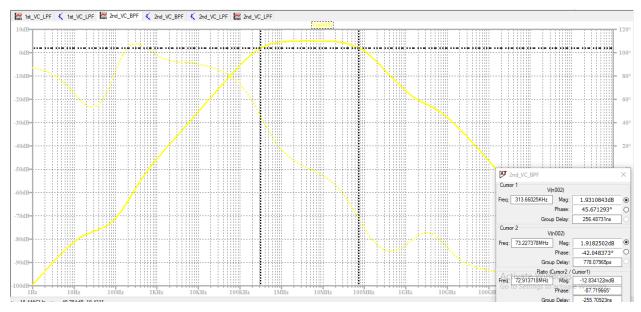

| Figure 4.14: Circuit diagram of band pass filter using VCII block                                                                                                                                             | 54                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Figure 4.15: Frequency response of active band pass filter                                                                                                                                                    | 54                   |

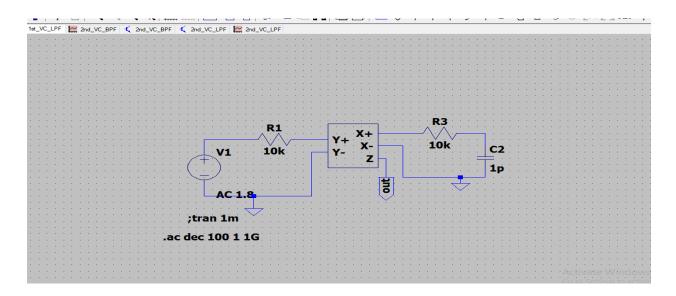

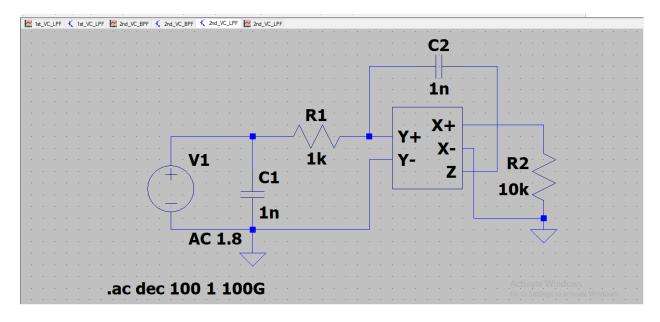

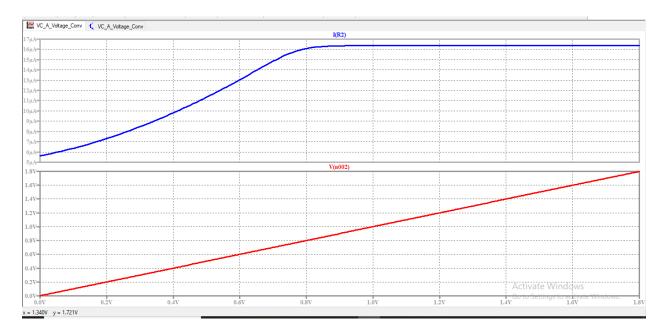

| Figure 5.16: Circuit diagram of 2 <sup>nd</sup> order active low pass filter using VCII block                                                                                                                 | 55                   |

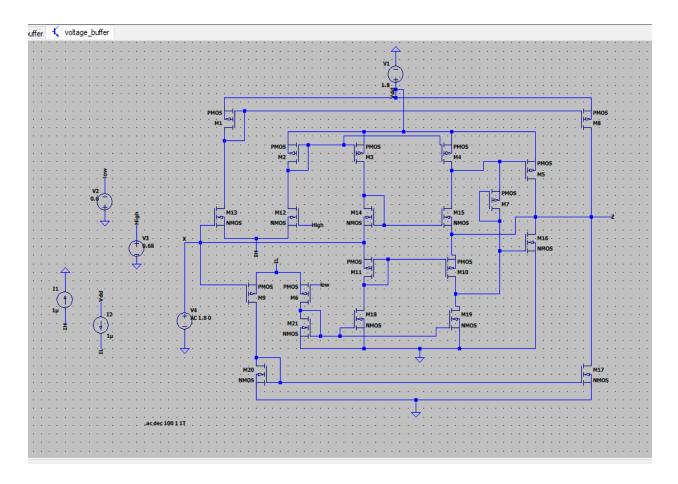

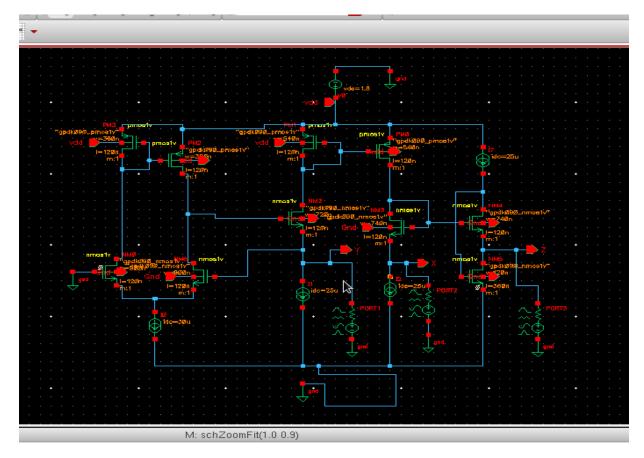

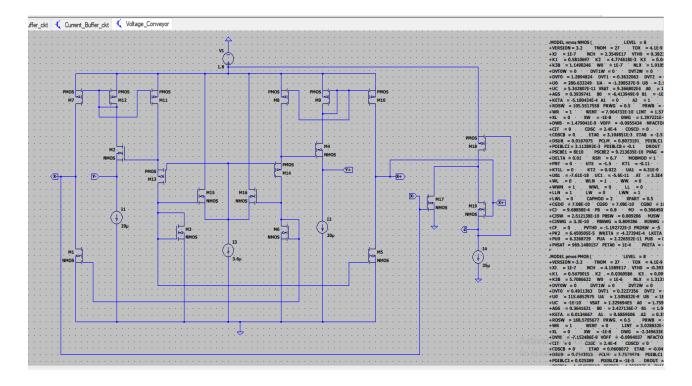

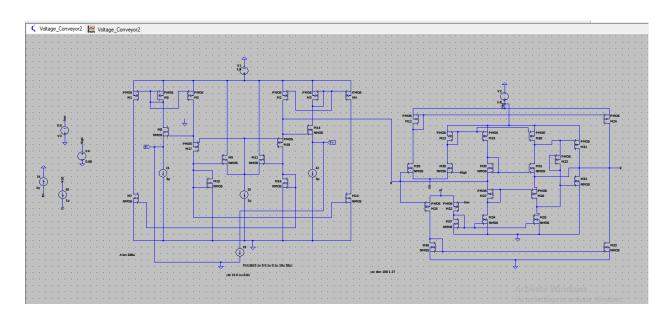

| Figure 5.1: Circuit diagram of Proposed second generation voltage conveyor                                                                                                                                    | 57                   |

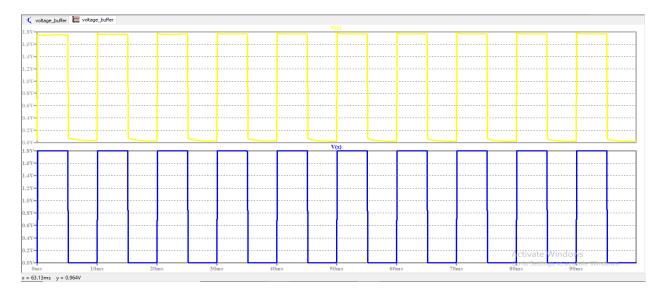

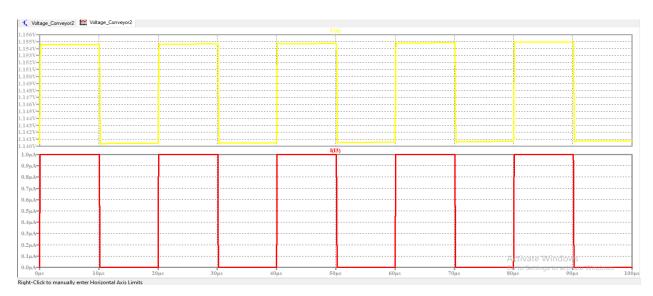

| Figure 5.2: Transient step response of proposed VCII circuit                                                                                                                                                  | 57                   |

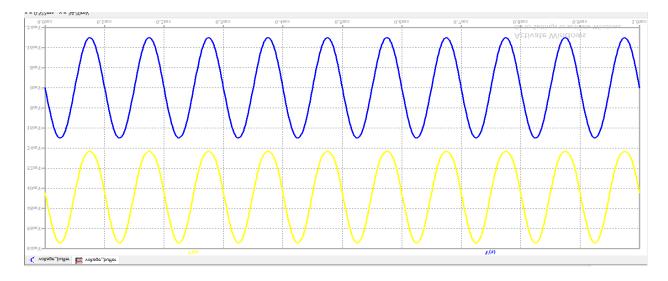

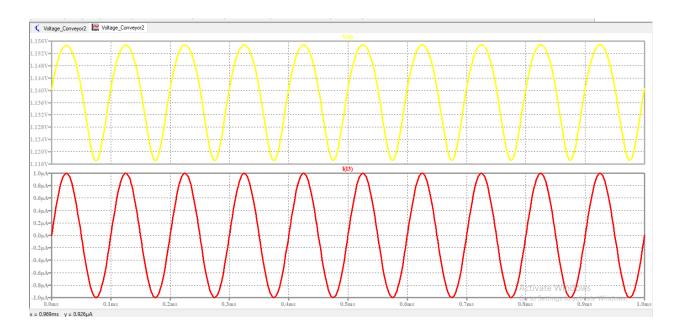

| Figure 5.3: Transient response of proposed VCII circuit                                                                                                                                                       | 58                   |

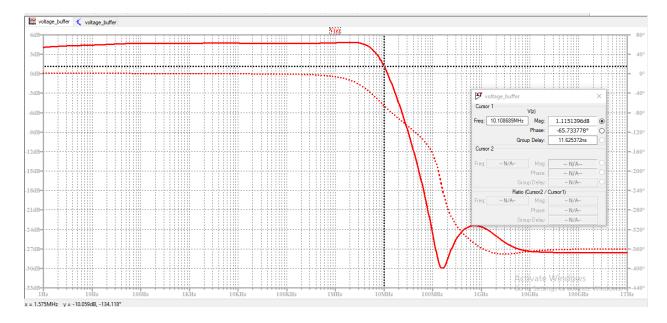

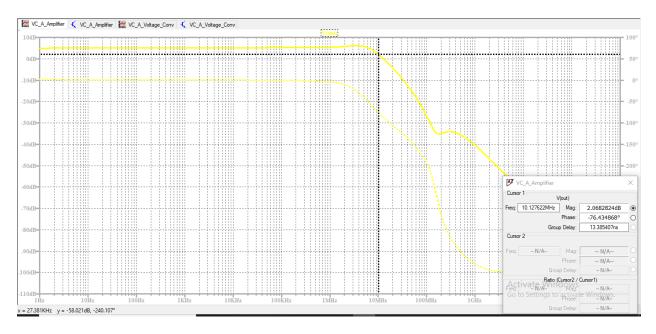

| Figure 5.4: AC analysis of proposed VCII circuit                                                                                                                                                              | 58                   |

|                                                                                                                                                                                                               |                      |

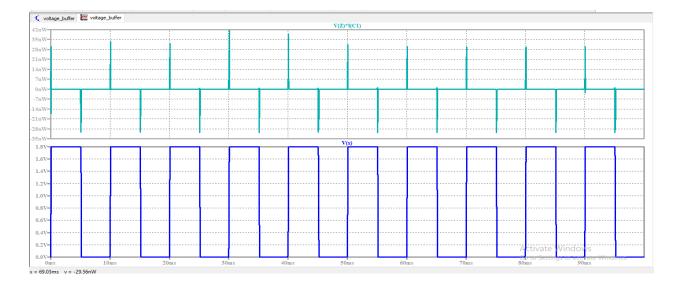

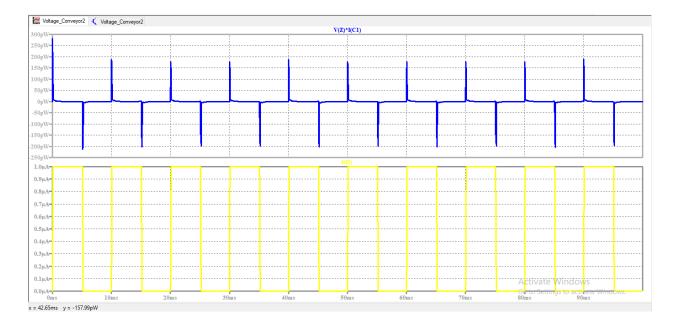

| Figure 5.5: Plot of Power consumption across the load capacitor with respect to waveform at the input                                                                                                         | the square 59        |

|                                                                                                                                                                                                               | -                    |

| waveform at the input                                                                                                                                                                                         | 59<br>59             |

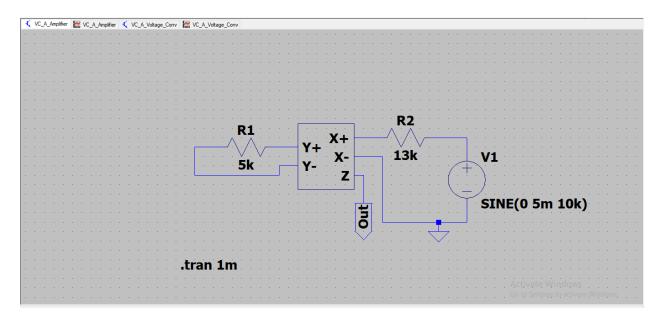

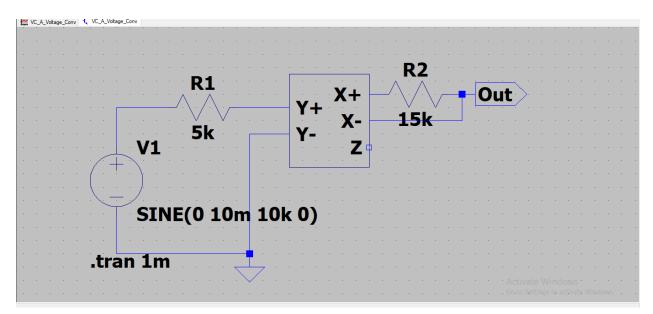

| waveform at the input<br>Figure 5.6: Circuit diagram of Voltage Amplifier using VCII block                                                                                                                    | 59<br>59             |

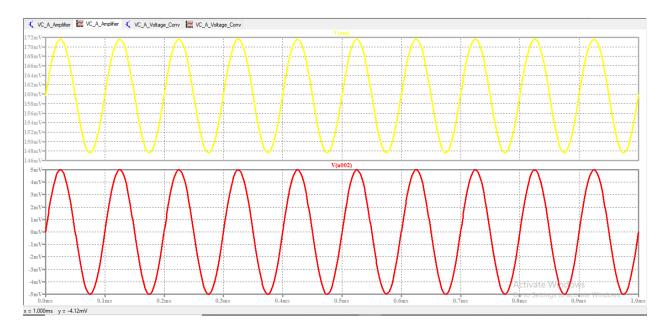

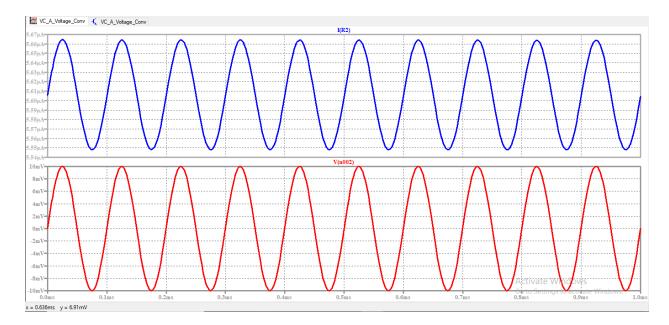

| <ul><li>waveform at the input</li><li>Figure 5.6: Circuit diagram of Voltage Amplifier using VCII block</li><li>Figure 5.7: Transient response of voltage amplifier implemented using proposed VCII</li></ul> | 59<br>59<br>block 60 |

| Figure 5.11: Plot of Transient analysis of current buffer circuit using VCII block | 62 |

|------------------------------------------------------------------------------------|----|

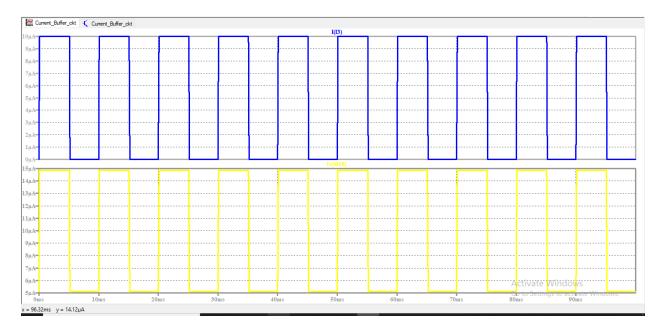

| Figure 5.11: Plot of Transient analysis of current buffer circuit using VCII block | 62 |

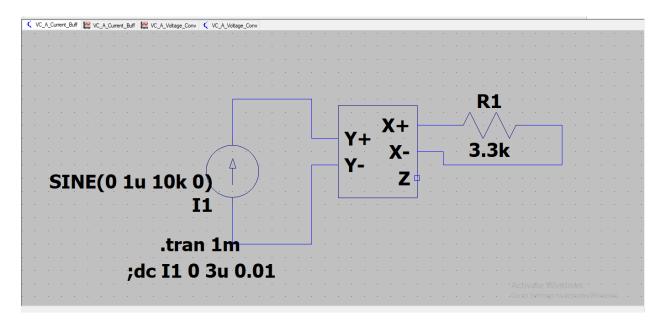

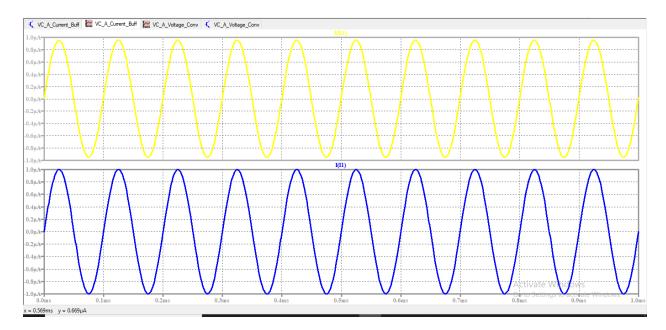

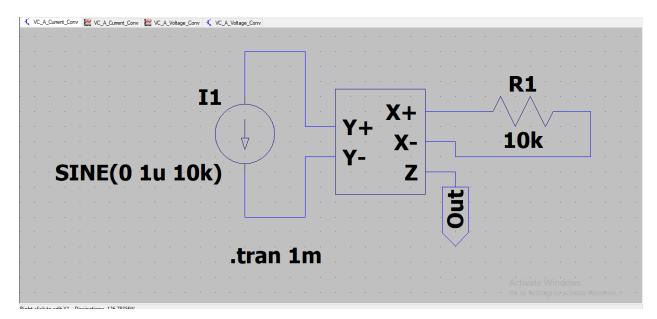

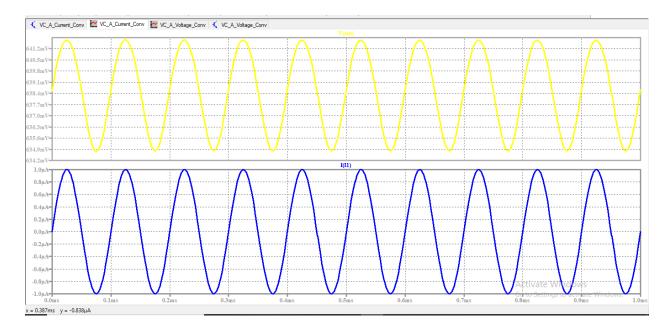

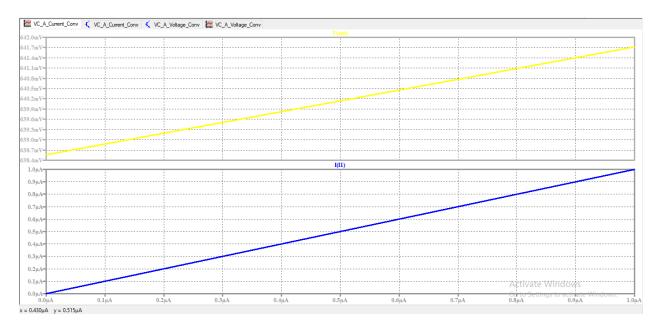

| Figure 5.13: Plot of transient analysis of current to voltage converter            | 63 |

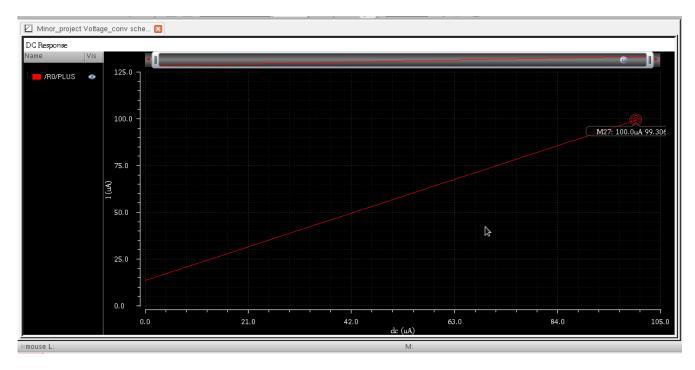

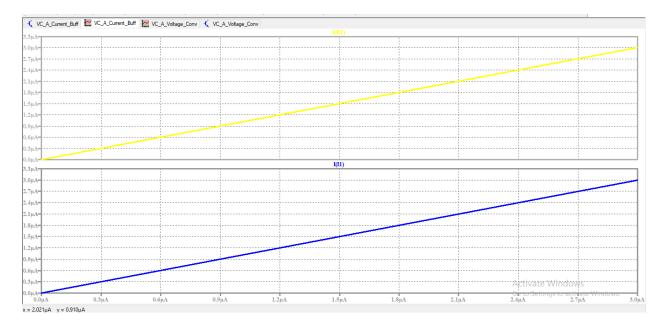

| Figure 5.14: Plot of DC analysis of current to voltage converter                   | 63 |

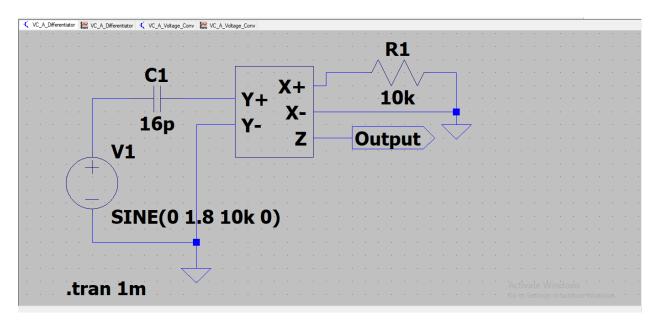

| Figure 5.15: Circuit diagram of voltage differentiator using VCII block            | 64 |

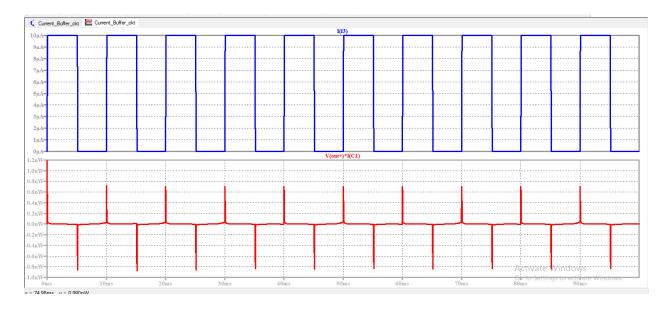

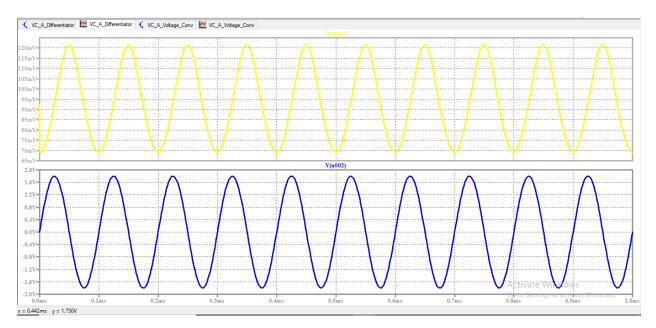

| Figure 5.16: Transient analysis of voltage differentiator circuit using VCII block | 64 |

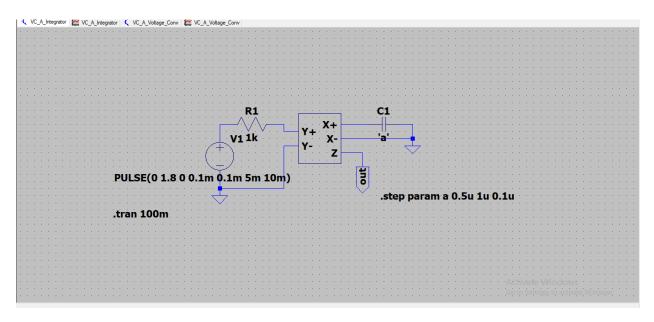

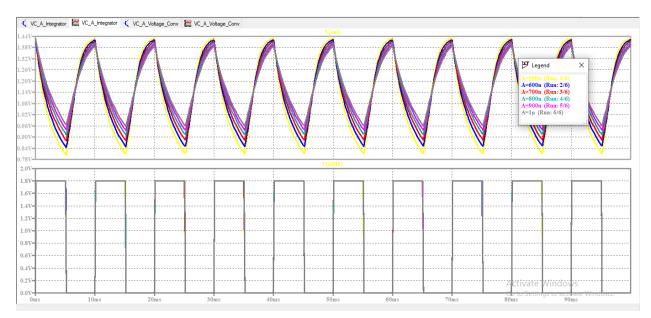

| Figure 5.17: Circuit diagram of voltage integrator using proposed VCII block       | 65 |

| Figure 5.18: Transient analysis of voltage integrator implemented using VCII block | 65 |

| Figure 5.19: Circuit diagram of voltage buffer using proposed VCII block           | 66 |

| Figure 5.20: Plot of DC analysis performed for voltage buffer circuit              | 66 |

| Figure 5.21: Plot of transient analysis performed for voltage buffer circuit       | 67 |

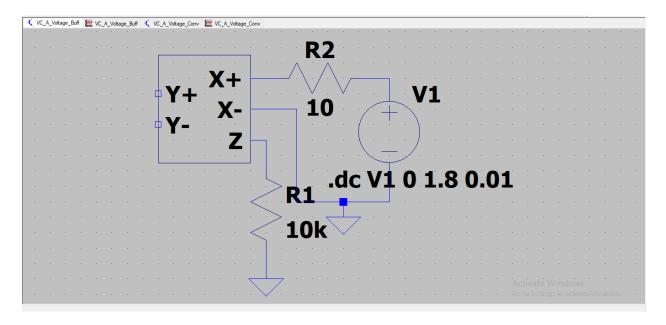

| Figure 5.22: Circuit diagram of voltage to current converter using proposed VCII bloc | ck 67 |

|---------------------------------------------------------------------------------------|-------|

| Figure 5.23: Plot of transient analysis of voltage to current converter               | 68    |

| Figure 5.24: Plot of DC analysis of voltage to current converter                      | 68    |

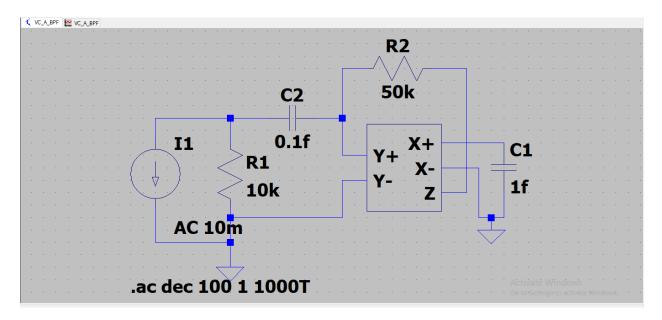

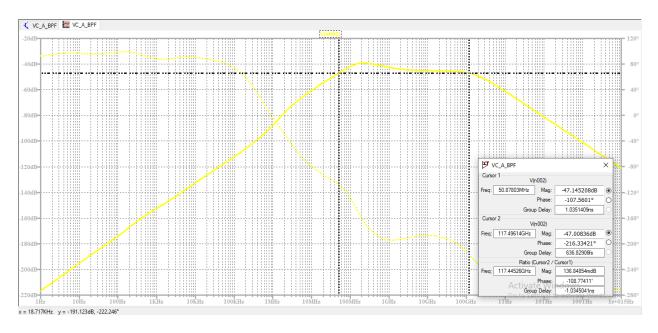

| Figure 5.25: Circuit diagram of band pass filter using proposed VCII block            | 69    |

| Figure 5.26: Plot of AC analysis of band pass filter                                  | 69    |

| Figure 5.27: Circuit diagram of low pass filter using proposed VCII block             | 70    |

| Figure 5.28: Plot of AC analysis of low pass filter                                   | 70    |

# LIST OF ABBREVIATIONS USED

VLSI: Very Large Scale Integration

CCII: Second Generation Current Conveyor

VCII: Second Generation Voltage Conveyor

**Op-Amp: Operational Amplifier**

Ckt : Circuit

IC: Integrated Circuit

NMOS: n-Type Metal Oxide Semiconductor

PMOS: p-Type Metal Oxide Semiconductor

DC: Direct Current

CD: Common Drain

CG: Common Gate

### **CHAPTER 1**

### **INTRODUCTION**

This chapter sets the stage for Second generation voltage conveyor (VCII). In section 1.1 we have discussed about basic property of VCII block. In section 1.2 we have discussed about the motivation behind doing this project. In section 1.3 we have discussed the property of a buffer circuits. In section 1. 4, 1.5, 1.6 we discussed general properties of a buffer and amplifier circuits. We have discussed about the concept of impedance matching and impedance requirement for a voltage amplifier.

#### **1.1 INTRODUCTION:-**

In today's environment, power, area, and speed are becoming increasingly significant variables in virtually every electronic business. These three variables are intertwined and trade-offs exist. The Second Generation Voltage Conveyor (VCII) is based on the duality idea of the CCII block. The VCII block has the finest Power, Area, and Speed ratio. It has a larger frequency range than an Op-Amp, uses less power, and takes up less space. The VCII block allows for cascading, which is a particularly valuable feature in higher-level architecture.

#### **1.2MOTIVATION**

Because of the inadequacies of the CCII block, researchers moved their focus to VCII. When voltage is required at the output port in a design application, we need to use the CCII block to provide a voltage buffer to the output side. As a result, the circuitry required increases, resulting in higher power and area requirements. Some CCII-based applications have significant limitations, for example, when examining the transfer function of a voltage differentiator, voltage integrator, current to voltage converter, and voltage amplifier, two CCII blocks are required instead of one that necessitates more power and space [1]. Other

circuits produced by the CCII block, such as the current amplifier, current differentiator, and current integrator, also have issues, such as their reliance on input or output impedance or gain issues.

All of these issues drew researchers in, who set out to find the best solution for all of them. For all of these issues, the VCII block produces excellent performance. Because only a single VCII block is required, it has a minimal power and area demand.

#### 1.3 BUFFER:-

A voltage or current buffer is a circuit that processes an input signal with a gain of one. Buffer circuitry is commonly utilised when a transition in high input impedance to low input impedance or low to high input impedance is required. When impedance matching is necessary, a buffer can be employed.

Figure 1.1: Voltage buffer circuit designed using Op-Amp

#### **1.4 IMPEDANCE MATCHING:-**

Impedance matching is a power transfer optimization approach. The signal reflection from the load circuit is minimised using this technique. For minimum signal reflection, the input and output impedances should be matched in this procedure.

#### **1.5 HIGH INPUT IMPEDANCE:-**

A high input impedance is a characteristic of a good voltage amplifier (ideally infinite). A voltage amplifier has a greater input impedance to ensure that the signal applied to the input stage is almost ready for further processing, or to avoid loading effect at the input port.

### **1.6 LOW OUTPUT IMPEDANCE:-**

The output impedance of a good voltage amplifier should be low (ideally zero). Low output impedance is necessary for greater fanout, allowing the output stage to drive the largest number of devices possible. It aids in cascading and higher-level design. On the other hand for current buffer circuit output impedance should be high.

### **CHAPTER 2**

# REVIEW OF DIFFERENT TYPES OF VOLTAGE AND CURRENT BUFFER CIRCUITS

In this chapter we will discuss about the various method of current and voltage follower circuit design. We will review functionality of those buffer circuits, advantage of using these circuits and shortcomings associated with them. In section 2.1 we will discuss about the different type of voltage buffer circuits like circuits which are operating in differential mode, which are suitable for high voltage operation, which provide high slew rates, high value of input impedance and low value of output impedance. We will also discuss and simulate the voltage follower circuit which we are using in our proposed design. In section 2.2 we will discuss about the current buffer stages. In current buffer circuits we have reviewed circuits on the basis of the functionality they promised like low value of input impedance, high value of output impedance, differential nature, ability of high current buffer stage which we are going to use in our proposed design. We performed AC, DC, transient and power consumption analysis.

#### **2.1 VOLATAGE BUFFER:-**

The voltage is passed from the 1st circuit to the 2nd circuit without any modification in amplitude in a voltage follower, also known as a voltage buffer or unity gain voltage buffer. The output voltage is simply a reflection of the input voltage. The voltage follower's voltage gain is one (Av = 1). Although there will be no voltage gain, there will be significant current gain. When a voltage follower is linked in between two circuits, it transfers voltage from one to the other without changing the amplitude and drives the 2nd circuit without overloading the 1st.

Figure 2.1: Small signal model of Ideal Voltage buffer circuit

The voltage buffer is a type of analogue cell that is utilised in the construction of analogue circuits. Large capacitive loads are driven with it at maximum speed and low power consumption. This means that symmetrical slew rate and minimal static power consumption are required. The negative slew rate in a standard voltage buffer (=Ibias/CL,where CL The bias current limits the load capacitance). (Ibias), The positive slew rate, on the other hand, has a rather high rate value. Because the speed of a large-signal is limited by the minimal value of positive, symmetrical slew rate is usually necessary. Slew rates are both positive and negative. Both the negative slew rate and the bandwidth can be increased at the cost of higher latency, Ibias and, consequently, the static power consumption will increased.

#### 2.1.1 HIGH VOLTAGE UNITY GAIN VOLTAGE FOLLOWER:-

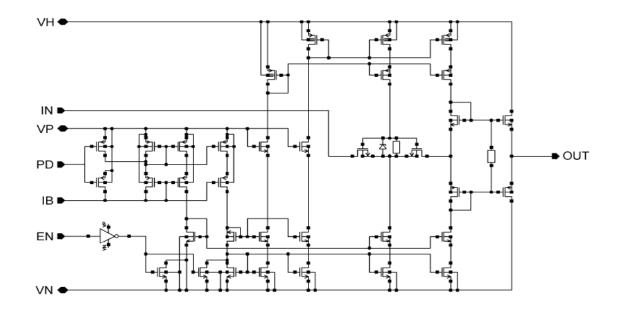

This circuit have EN and PD enable signal inputs. The EN and PD signals must be set to the correct value in order to power off the buffer. However, the When EN is used, high-impedance functionality is enabled. only a signal Changes in control application methods are possible. In this circuit customised control logic is used. In this instance, the logic circuitry I buffered and considered as an external circuitry Consequently, not included.

Figure 2.2: Circuit diagram of high voltage unity gain voltage follower [1]

The EN/PD signal-induced power in down mode disables complete circuit functions by cutting off all bias currents. The EN signal in Fig.2.2 is employed to drive numerous aspects of high-Z functioning, both at input and output and nodes for output. The bias current mirrors feed when the EN signal is high with the externally defined HV current-controlled switches. There are numerous current constructions, controlled switching devices [1].

These switches are each powered by two high-voltage currents. sources. This solution, in combination with a resistor-driven switch, The use of transistors ensures a smooth transition towards the cut-off situation. Both are transistor switches.

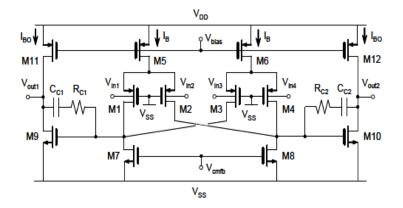

# 2.1.2 FULLY DIFFERENTIAL LOW VOLTAGE WIDE SWING VOLTAGE FOLLOWER:-

The voltage follower is based on the FD DA [2], which posses of a bulk-driven input stage which drives a gate-driven class-A output stage. A PMOS Since there are n differential pairings, implementation is chosen. Technology is taken into account. There are four input terminals required. in order to produce a noninverting FD unity Configuration of gain feedback The FD DA was indeed linked. As a result of the feedback system presented in Fig. 2.3, a voltage buffer with FD. Bulk-driven MOS transistors are used in The FDDA input stage enables a large input voltage range. The mid supply voltage area is included in this range. The The two-stage scheme's frequency response is corrected by A Miller network with a zero-nulling resistor is used. The The input capacitively loads the FD amplifier outputs. The CM detector's bulk-driven MOS transistors. However this capacitance is connected in parallel with the, *C*L, and it has a minor effect in most cases. The response of the FD voltage buffer's DM loop is determined by the signal path of the FD-DA in Fig. 2.3. As previously stated, this path contains of consisting of a gate-driven output stage and a bulk-driven input stage It's worth noting that the input-related

Figure 2.3: Circuit diagram of FDDA based voltage buffer [2]

noise contribution is significant. Because of the existence of the, the FDDA in Fig. 2.3 is increased. MOS transistors in the input stage that are bulk-driven In fact, the An MOS transistor generates the same intrinsic noise. Regardless of their link, there is a distinction when the The device's input terminal is chosen.

#### 2.1.3 CLASS AB FLIPPED TYPE VOLTAGE FOLLOWER :-

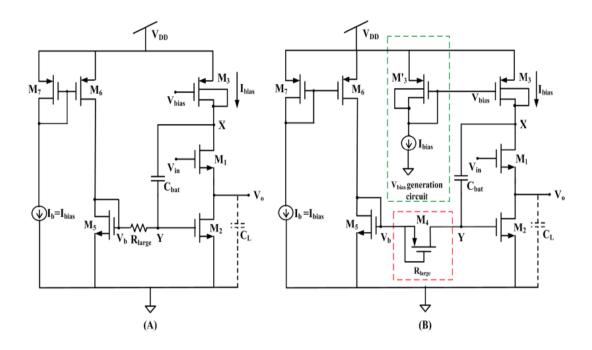

The suggested class-AB FVF cell, based on bulk-driven and quasi-floating gate approaches, is shown in Figure 2.4. M6-type PMOS transistors to clone the current state, create a current mirror. Ib (= Ibias), and an NMOS transistor with a diode M5 7 gives the necessary voltage Vb. The capacitor is a device that stores electricity. Cbat between nodes "Y" and "X," as well as a high-valued resistance Rlarge is linked between NMOS transistor gate terminals M2 and M5. The opposition Rlarge PMOS transistor has been implemented. Transistor M4 operating in the cutoff zone. There is no voltage decrease in this area. Rlarge As a result, it creates well-defined quiescent voltage Vb at the transistor's gate M2 that keeps the bias current flowing through the transistor M2. As a result, the gate of

Figure 2.4: Circuit diagram of class AB type flipped voltage follower circuit a). without biasing b). with biasing [3]

Under dynamic situations, transistor M2 acts as a quasi-floating gate. The voltages are higher in DC operation. VY and VX "Y" and "X" are independent of each other at nodes "Y" and "X," however they are coupled under dynamic conditions. " The capacitor is a device that stores electricity. Cbat and opposition Rlarge operate as a cutoff frequency HPF fo( 1/ 2pRlargeCbat) for passing signals ing between nodes "X" and "Y." "A bulk-driven PMOS transistor replaces the standard FVF cell's biassing current source (Ibias). M3. In bulk 1, 2 A fixed DC voltage source is applied to the gate ends of a driven transistor, and input is applied to the bulk ends. As a result, the suggested class-AB FVF cell uses a constant DC voltage (Vbias) voltage is applied to the gate ends VX, which The bulk terminal of the transistor is used as an input. M3. To provide a constant DC voltage (Vbias), the gate station M'3 (clone of transistor) is a diode-connected transistor. M3) is used. Transistor M'3's bulk and drain connections are 3 '3 also interconnected, as well as a sinking current source Ibias where the drain terminal is linked as demonstrated in The gate voltage (Figure 1B). Vbias fixes the transistor's gate-source voltage M3 As a result, the current bias in the branch M3 to M1. The transistor is a small electronic device. M3 works as a flexible current source and improves current sourcing capability suggested FVF cell of class AB The positive output current becomes larger than the bias current as a result of this. (Ibias). The

current at Transistors are controlled by node "X." M2 and M3 to maintain the branch's bias current M1 to M3. The current VX at node Transient fluctuations in input voltage produce "X." Vin.

# 2.1.4 HIGH INPUT IMPEDANCE HIGH VOLTAGE UNITY GAIN VOLTAGE FOLLOWER:-

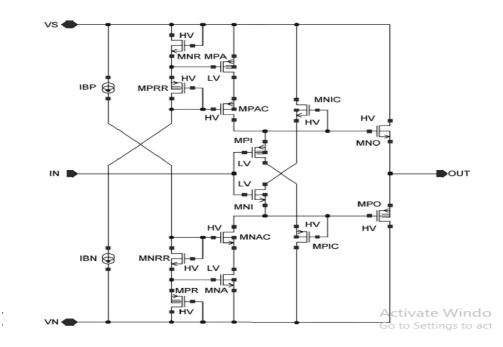

There have been attempts to develop voltage buffers that use gate as input architectures, however they lack control over gain and DC voltage offset [10] For precision, some techniques employ complicated adaptive biassing structures. suggested buffer structures are under control [11]. Unfortunately, the majority of The structures are made for low-voltage applications. The structure is intricate in order to maintain excellent quality. This is similar to a source-input voltage buffer. This is accomplished by modifying the gate-source voltage drops of the input stage transistor, which may be near to the gate-source voltage drops of the output stage transistor. The voltage falls. Alternatively, to make the input stage GS voltages are provided by transistors in the gate-input buffer. similar to gate-source voltage drop on the It is necessary to obtain transistors for the input stage. polarised properly This is accomplished by altering the input. current sources stage bias gate input impedance voltage buffer and gain value

Figure 2.5: Circuit diagram of high input impedance and high voltage unity gain voltage follower circuit [4]

The idea is to create enough current to make the voltage drop at the input transistor gate-source equal to the voltage drop at the source-input voltage buffer's input-stage transistors. The principle of Fig. 2.5 is illustrated with a simple picture. The transistors' names. In the introductory form of the proposed solutions, a complimentary version of the buffers demonstrates how those employed in gate-and-source-follower are used. Figure 2.5 shows The introduction buffer structure has been supplemented. There are two current sources, and their currents are equivalent to the source-input voltage buffer's input bias current. Each securrent biassed one of the reference transistors (MPR, MNR), which is identical to one of the source-input buffer's input-stage transistors..

# 2.1.5 VOLTAGE BUFFER STAGE, USED IN PROPOSED VCII SIMULATED CIRCUIT:-

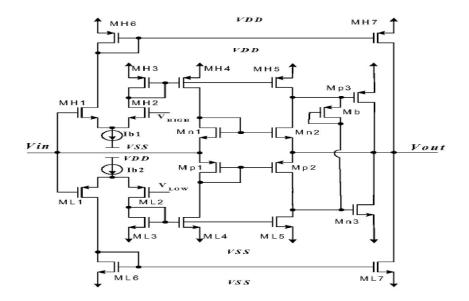

A source follower with pseudo functionality has a low output impedance and, is fast. Same time, can cope with When compared to a simple CD type, there is a substantial output swing. source observer. However, this strategy has a flaw. Controlling the quiescent is challenging. as a consequence of a random high transconductance and threshold voltage Parts that pull up and

down. Consequently, any a working circuit Taking this strategy necessitates incorporate additionally mechanism to govern the dormant current. Also, capacitors for compensation are required to enhance the transient responsiveness and stability leading in a substantial chip area.

Figure 2.6: Circuit diagram of conventional voltage follower [5]

Figure 2.6 depicts a standard voltage follower. Four transistors make up the circuit. (M,11, MP1, MK2 and Mp2) which are connecting in a straightforward complimentary manner This circuit provides excellent control and efficiency in the workplace application of the quiescent current because of its simplicity, the The characteristic of frequency is excellent and is determined by The input and output nodes have a time constant linked with them. In Furthermore, the follower has a low voltage offset, which is primarily decided by transistor mismatch. There are three major disadvantages to becoming a follower: 1) The linearity is low and highly reliant on the data. 2) a high ratio between biassing and output current output impedance as a result of lower transconductance 3) a restriction of the MOS transistor

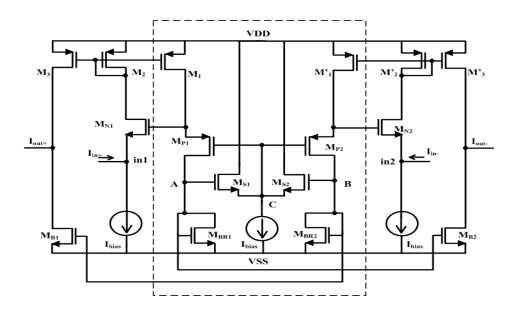

Figure 2.7: Circuit diagram of Voltage follower with rai to rail capability [5]

The symmetrical voltage buffer described in Fig. 2.6 is the basis for the proposed circuit in Fig. 2.7 Four (M,11, Mn2, Mp1, Mp2)transistor work as a traditional follower of voltage MH1, Mp2 and MH2 x are intertwined in the differential amplifier arrangement, which is in charge of sensing the amplitude of the input Mp3 and Mn3 consisting of be a second cs output stage running parallel with the traditional follower linked to negative feedback the output impedance should be reduced. The process of following diagram depicts the circuit. The circuit behaves like a traditional voltage follower when the input voltage is between VHIGH and VLOW. The input signal is amplified with the help of Mp2 and Mn2 after which it was passed to gates of Mp3 And Mn3 Respectively.Mp3 And Mn3, that are suit the purpose when coupled in a cs configuration depending on the load, to sink to source and current an incoming input signal's polarity.

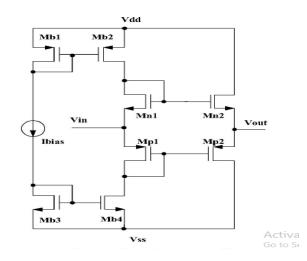

#### 2.1.6 FLIPED VOLTAGE FOLLOWER:-

Property of voltage buffer circuit is that it has high ideally infinite impedance at the input and a low ideally zero output impedance, with ideal values of infinite and zero, but in practice, the output and intput impedances are few hundreds of ohms and a several hundreds of ohms, respectively. It has unity gain, which means that the output voltage is proportional to the input voltage. The common drain amplifier is the most widely used voltage buffer circuit. Let's take a look at the typical drain amplifier, which is frequently employed as a voltage buffer. The Circuit follows the input voltage with a dc level shift, if the body effect is ignored, as Vo = VSGM1 + Vi, where VSGM1 is the transistor's source-to-gate voltage.

Figure 2.8: Circuit diagram of common drain voltage buffer and flipped voltage buffer [6]

In terms of large-signal behaviour, this circuit can sink a lot of current from the load, but the biassing current source limits its sourcing ability. The current through M1 transistor is dependent on the output current, hence VSGM1 is not constant and, as a result, the voltage gain for resistive loads is less than unity. At high frequencies, capacitive loads have a similar difficulty. The circuit also functions as a source follower, with the current flowing through transistor M1 being constant regardless of the output current. It's a voltage follower with shunt feedback, in a sense. Neglecting the body's effect and the short-term effects Influence of a channel The voltage gain is unity, and VSGM1 is kept constant. The circuit may generate a huge amount of current, unlike a traditional voltage follower, however its sinking capability is limited by the biassing current source Ib. The low impedance at the output node, which is about ro = 1/(gm1gm2ro1), explains the high sourcing capability, gmi and roi are the transconductance and output resistance of transistor Mi, respectively. This number is somewhere between 20 and 100. M2 gives shunt feedback, while M1 and M2 create a negative feedback loop with two poles. The identical circuit as before, but with the feedback loop open at M2's gate and a test voltage source Vt. There is an open-loop gain in this circuit. AOL = Vr / Vt = -gm2 AOL = Vr / Vt = -gm2 Roly (where the open-loop resistance at node Y is given by ROLY rb||gmro1ro2), Wpy= 1/CyROLY, a dominating pole at node Y, WPX= 1/ROLYCx (where the open-loop resistance at node X is given by ROLX((1+rb/ro1)/gm1||ro2), and a high-frequency pole at no The parasitic