# LOW POWER LOW NOISE PLL DESIGN

MAJOR PROJECT

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

# MASTER OF TECHNOLOGY IN VLSI DESIGN AND EMBEDDED SYSTEMS

Submitted by:

# VISHAL AGRAHARI

# 2K20/VLS/23

Under the supervision of

Prof. J.Panda

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

### **CANDIDATE'S DECLARATION**

I Vishal Agrahari student of M.Tech (VLSI Design and Embedded Systems), hereby declare that the project Dissertation titled "Low Power Low Noise PLL Design" which is submitted by me to the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship or other similar title or recognition.

Place: Delhi Date: Vishal Agrahari

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

### CERTIFICATE

I hereby certify that the Project Report titled "Low Power Low Noise PLL Design" which is submitted by Vishal Agrahari, 2K20/VLS/23 of Electronics and Communication Department, Delhi Technological University, Delhi in partial fulfillment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by the students under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date: Prof. J. Panda SUPERVISOR

# ACKNOWLEDGEMENT

A successful project can never be prepared by the efforts of the person to whom the project is assigned, but it also demands the help and guardianship of people who helped in completion of the project. I would like to thank all those people who have helped me in this research and inspired me during my study.

With profound sense of gratitude, I thank Prof. J Panda, my Research Supervisor, for his encouragement, support, patience and his guidance in this thesis work. Their kind comments and guidance let me complete this study in an improved manner.

I take immense delight in extending my acknowledgement to my family and friends who have been supporting me morally to keep going with this study and inspired me to come up with the expected results throughout this research work.

Vishal Agrahari

# ABSTRACT

Traditionally, the PLL has been a linear circuit. While the first PLLs were built with discrete components, they were made available in discrete ICs across 1965. Each of these was linear devices (LPLLs), which were constructed through semiconductor technologies similar to the operational amplifiers of the time. A few years later (around 1970s), the first digital PLLs (DPLLs) became available, however when we look at their schematics, we could see that only the phase detector was built from logic, while the VCO and loop filter remained analog. As a consequence, PLL can be considered of as a hybrid system. Furthermore, we integrate LPLLs and DPLLs into a single class known as mixed signal PLLs.

A PLL is a very versatile device that can be found in most of the devices we use every day. Since its inception, it has been constantly evolving and implemented in various technologies a, whereas the basic phase look loop circuit hasn't changed.. The PLL circuit is broadly utilized communication systems, including, mobile phones, radio, telephone personal computers and electronic devices.

PLLs oftenly finds its uses in mobile or wireless communications for synchronization, clock synthesis, and jitter reduction. A PLL used in a microprocessor to generate clocks appears to be very similar to a frequency synthesizer used in a cell phone, but the actual circuits are designed very different manner.

This report describes the design and the basic concepts of the PLL, along with its operation principle and block diagram, have indeed been explained first. This is based on a detailed explanation and stability analysis of individual blocks in the PLL, which uses negative feedback to achieve phase/frequency lock.

Ltspice is used for the design and implementation, and 90nm technology was used. Simulations of each individual block were described to further explain the function of each individual block, such as the Phase Frequency Detector (PFD), charge pump, Low pass filter (LPF), and Current Starved Voltage controlled Oscillator (CSVCO), as well as the calculation of performance measures such as capture range, lock range, and settling time. Finally the simulation for the complete PLL has been presented along with the calculation of its performance metrics like capture range, lock range and settling time.

# **CONTENTS**

| Candidate's Declaration |                                                            | i   |

|-------------------------|------------------------------------------------------------|-----|

| Certificate             |                                                            | ii  |

| Acknowledgement         |                                                            | iii |

| Abstract                |                                                            | iv  |

| List of Figures         | List of Figures                                            |     |

| List of Tables          | List of Tables                                             |     |

| Chapter 1:-             | Introduction to Phase Locked Loops                         | 1   |

| 1.1                     | Why to choose PLLs?                                        | 1   |

| 1.2                     | What is PLL?                                               | 2   |

| 1.2.1                   | Phase / Frequency Detector                                 | 3   |

| 1.2.2                   | Charge Pump                                                | 8   |

| 1.2.3                   | Loop Filter                                                | 9   |

| 1.2.4                   | Voltage Controlled Oscillator                              | 11  |

| Chapter 2:-             | Study of PLL behavior under Phase and Frequency Transience | 13  |

| 2.1                     | Frequency Transience                                       | 13  |

| 2.2                     | Phase Transience                                           | 16  |

| Chapter 3:-             | Dynamics of type-I PLLs and CP-PLLs                        | 20  |

| 3.1                     | Dynamics of type-I PLLs                                    | 20  |

| 3.2                     | Dynamics of Charge Pump PLLs                               | 23  |

| Chapter 4:-             | Non-ideal Effects in PLL                                   | 29  |

| 4.1                     | PFD/CP Non-idealities                                      | 29  |

| 4.1.1                   | Reset Delay of PFD                                         | 29  |

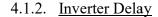

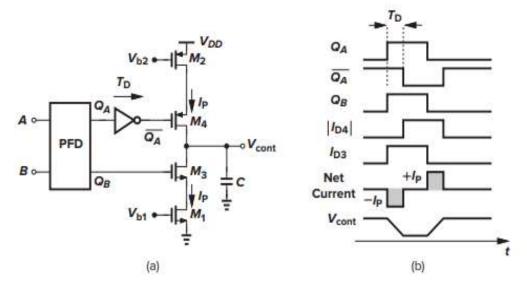

| 4.1.2                   | Inverter Delay                                             | 31  |

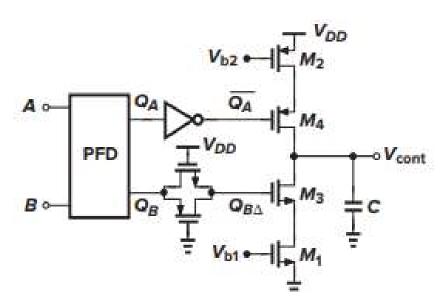

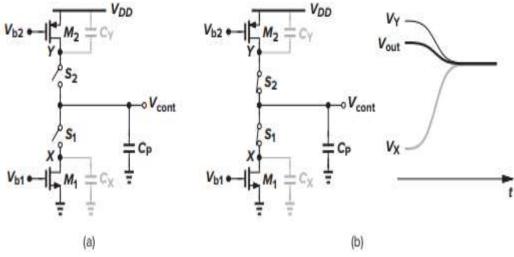

| 4.1.3                   | Charge Sharing at drain of the current sources             | 32  |

| 4.2                     | PLL's Jitter                                               | 34  |

| Chapter 5:-             | Applications of PLL                                        | 37  |

| 5.1          | Frequency Multiplier and Synthesizer                              | 37 |

|--------------|-------------------------------------------------------------------|----|

| 5.1.1        | Frequency Multiplier                                              | 37 |

| 5.1.2        | Frequency Synthesizer                                             | 38 |

| 5.2          | Clock Skew Suppression                                            | 38 |

| 5.3          | Jitter Reduction                                                  | 39 |

| Chapter 6:-  | Current Starved VCO                                               | 41 |

| 6.1          | 7-Stage Current Starved Inverter Circuit based Ring<br>Oscillator | 41 |

| 6.2          | 5-Stage Current Starved Inverter Circuit based Ring<br>Oscillator | 46 |

| Chapter 7:-  | Phase Frequency Detector                                          | 49 |

| 7.1          | Gate Based Phase Frequency Detector                               | 49 |

| 7.2          | Modified TSPC Master-Slave edge triggered D-FF based PFD          | 51 |

| 7.3          | 5T TSPC edge triggered master slave D-FF based PFD                | 55 |

| 7.4          | Fast Frequency Acquisition with Minimum Dead Zone PFD             | 58 |

| Chapter 8:-  | Charge Pump Designs                                               | 63 |

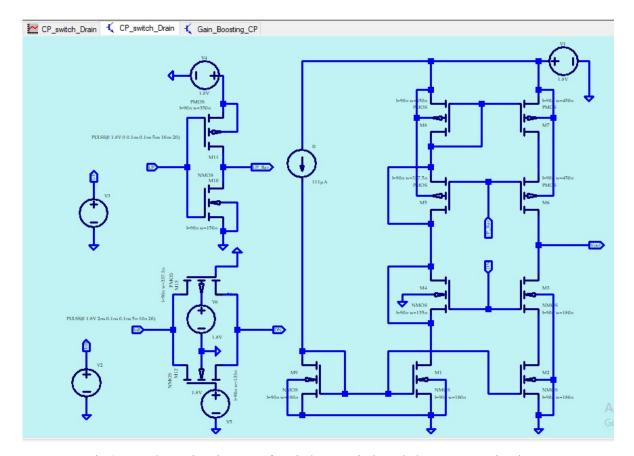

| 8.1          | Switch at Drain Charge Pump                                       | 63 |

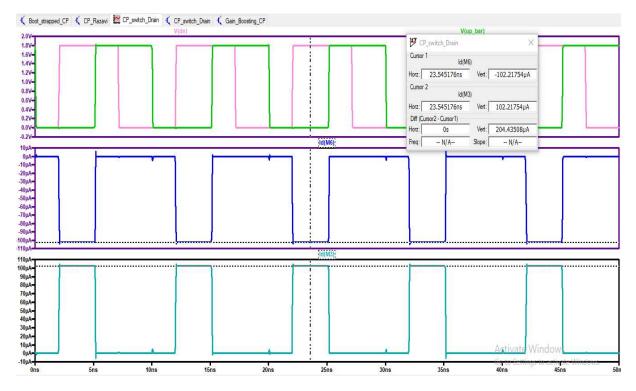

| 8.2          | Boot Strapped Charge Pump Design                                  | 64 |

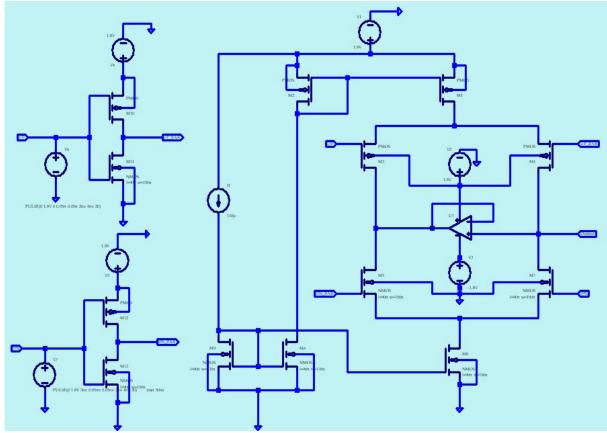

| 8.3          | Gain Boosting Charge Pump Design                                  | 66 |

| Chapter 9:-  | PLL Implementation and Simulation Results                         | 71 |

| 9.1          | Schematic and Simulation Results of the Frequency Divider circuit | 72 |

| 9.1          | Schematic and Simulation Results of the PLL circuit               | 73 |

| Chapter 10:- | Conclusion and Future Scope                                       | 81 |

|              | References                                                        | 82 |

# **List of Figures**

| S.No. | DESCRIPTION                                                                                                | Page<br>No. |

|-------|------------------------------------------------------------------------------------------------------------|-------------|

| 1     | PLL Block Diagram                                                                                          | 3           |

| 2     | EXOR gate as a Phase Detector                                                                              | 4           |

| 3     | $V_{out}(t)$ vs. $\Delta \Phi$ plot for a phase detector                                                   | 4           |

| 4     | $V_{out}(t)$ vs. $\Delta \Phi$ plot with respect to different phase relation between $V_1(t)$ and $V_2(t)$ | 5           |

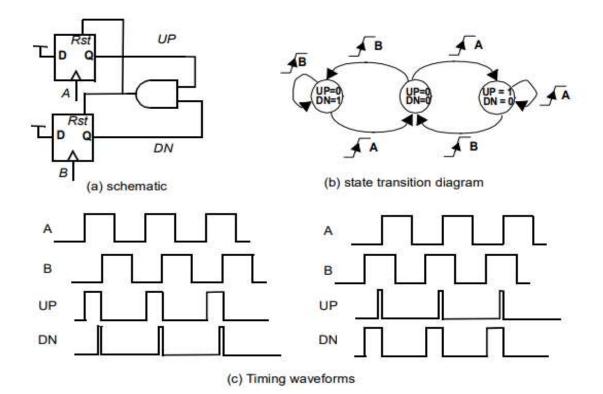

| 5     | Frequency Detector (a) Schematic (b) Transition Diagram (c) Timing Waveform                                | 7           |

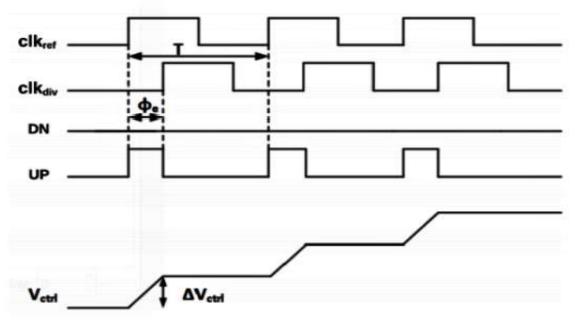

| 6     | Timing of PFD measuring frequency error                                                                    | 8           |

| 7     | Basic Charge Pump schematic                                                                                | 8           |

| 8     | Charge Pump Waveform                                                                                       | 9           |

| 9     | Loop Filter Circuit                                                                                        | 10          |

| 10    | Frequency vs. Voltage plot of an Ideal VCO                                                                 | 11          |

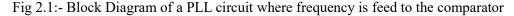

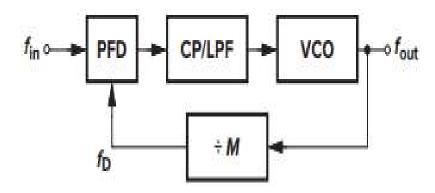

| 11    | Block Diagram of a PLL circuit where frequency is feed to the comparator                                   | 13          |

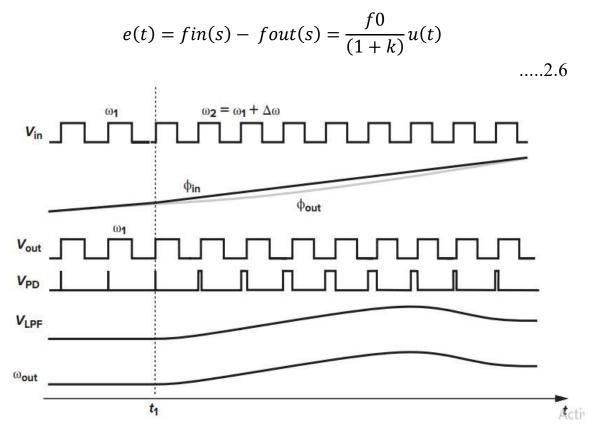

| 12    | Response of PLL for small frequency step                                                                   | 15          |

| 13    | Block Diagram of a PLL circuit where phase is fed to the comparator                                        | 11          |

| 14    | Response of a PLL for phase step                                                                           | 18          |

| 15    | Block Diagram of a PLL circuit                                                                             | 20          |

| 16    | Variation in $\omega_{out}$ with time because of transience in $\omega_{in}$                               | 32          |

| 17    | PFD circuit along with charge pump and low pass filter                                                     | 23          |

| 18    | (a) Linearity test of combine block (b) Response approximation                                             | 24          |

| 19    | Behavior of PFD+CP+LPF combination under step input                                                        | 24          |

| 20    | Frequency domain modelling of chrge punp PLL                                                               | 25          |

| 21    | Chage-punp PLL circuit with an added capacitor for the zero addition.                                      | 28          |

| 22    | Capacitor C2 is added to reduce ripple on the control line                                                 | 28          |

| 23    | PFD-generated collinear pulses with zero phase shift                                                       | 29          |

| 24    | (a) Zero input phase shift output wave (b) Output wave with minor phase shift                              | 30          |

in the input.

|    | 1                                                                                                                                                              |    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 25 | Figure showing dead zone in the charge pump current                                                                                                            | 30 |

| 26 | Real Response of a Phase Detector to a small input phase shift                                                                                                 | 31 |

| 27 | (a) Charge pump implementation (b) Skew effects between $Q_{\rm A}$ and $Q_{\rm B}$                                                                            | 31 |

| 28 | Pass gate logic used to thwart skew.                                                                                                                           | 32 |

| 29 | (a) Charge pump integration (b) Skew influence between QA and QB                                                                                               | 33 |

| 30 | X and Y are being bootstrapped to minimise charge sharing.                                                                                                     | 33 |

| 31 | Ideal and jittery waveforms                                                                                                                                    | 34 |

| 32 | Figure illustrating of slow and fast jitter                                                                                                                    | 35 |

| 33 | Effect of jitter because of VCO                                                                                                                                | 35 |

| 34 | Block diagram to showing frequency multiplication using PLL and $\div M$ circuit                                                                               | 37 |

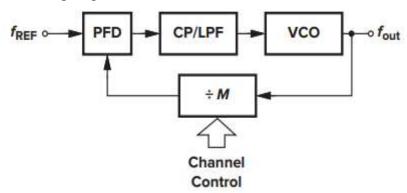

| 35 | Block diagram to showing frequency synthesizer using PLL and $\div M$ circuit                                                                                  | 38 |

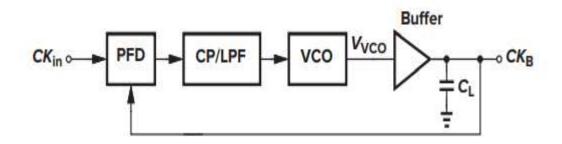

| 36 | Block diagram to showing use of PLL to eliminate clock skew                                                                                                    | 39 |

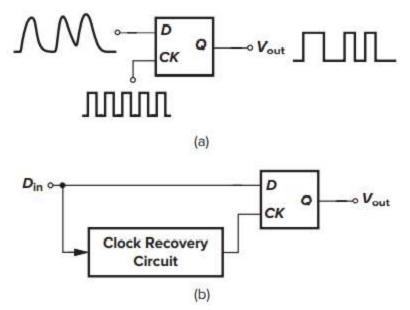

| 37 | Block diagram to showing (a) Retiming data with a D flip-flop steered by a low-noise clock; (b) creating the clock with a phase-locked clock recovery circuit. | 40 |

| 38 | Architecture of Current Starved VCO                                                                                                                            | 42 |

| 39 | Implementation of 7-stage CSVCO using Ltspice at 90nm technology node                                                                                          | 42 |

| 40 | Figure showing the output wave form of the Oscillator at different inverter stages                                                                             | 43 |

| 41 | Figure showing the measurement of the oscillation frequency for Vctrl = 1.6 V using Ltspice                                                                    | 43 |

| 42 | Figure showing Fvco (GHz) plot with varying Vctrl (Volts) for 7-stage VCO                                                                                      | 45 |

| 43 | Figure showing Fvco (GHz) plot with varying Vctrl (Volts) for 5-stage VCO                                                                                      | 47 |

| 44 | Figure showing the measurement of the oscillation frequency for Vctrl = 0.9 V using Ltspice for 5-stage VCO                                                    | 47 |

| 45 | Block Diagram of a Gate Level Phase Frequency Detector                                                                                                         | 49 |

| 46 | Schematic Diagram of a Gate Level Phase Frequency Detector                                                                                                     | 50 |

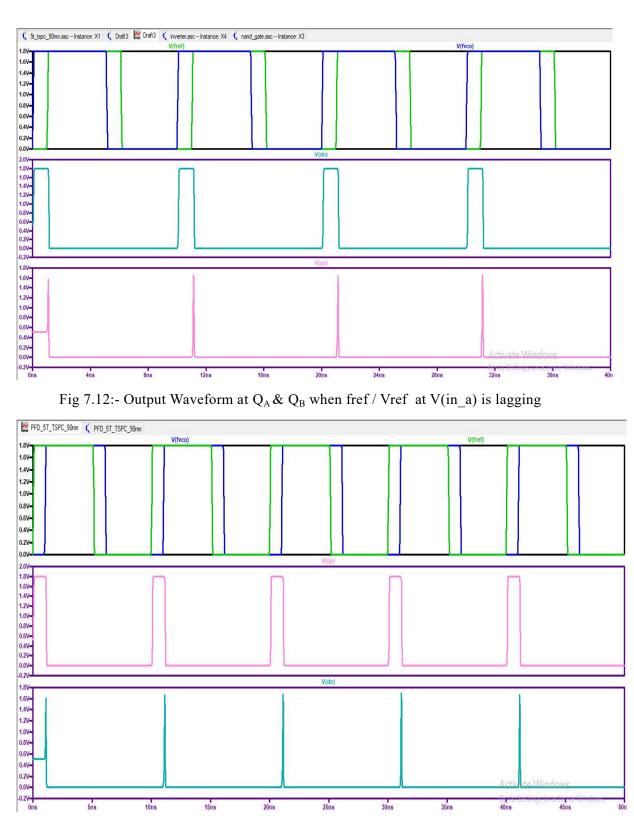

| 47 | Output Waveform at $Q_A \& Q_B$ when fref / Vref at V(in_a) is lagging                                                                                         | 50 |

|    |                                                                                                                                                                |    |

| 48 | Output Waveform at Q <sub>A</sub> when fref / Vref at V(in_a) is leading                                  | 51 |

|----|-----------------------------------------------------------------------------------------------------------|----|

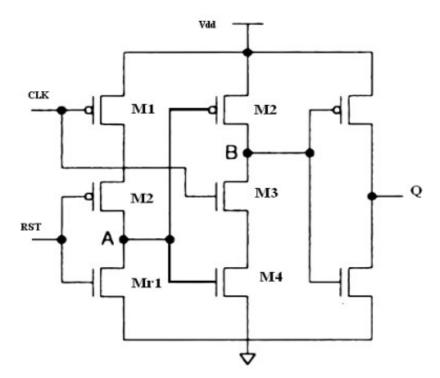

| 49 | Transistor level circuit diagram of a modified TSPC Positive edge triggered D-FF                          | 52 |

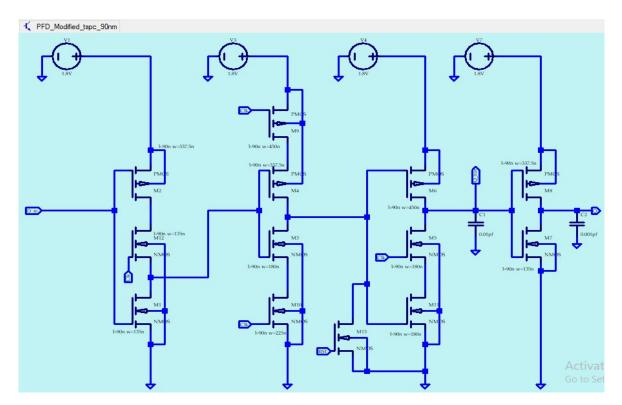

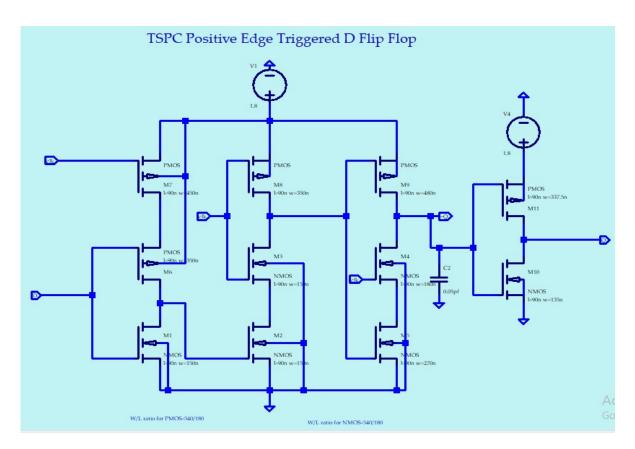

| 50 | Schematic diagram of a modified TSPC Positive edge triggered D-FF using LTspice at 90nm technology node   | 53 |

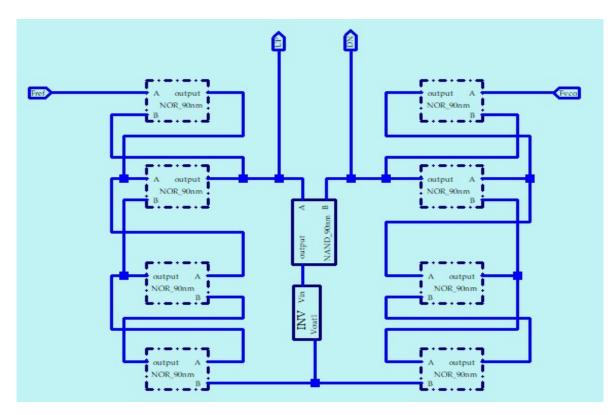

| 51 | Schematic diagram of D-FF based Phas/Frquency Detector implemented with modified TSPC.                    | 53 |

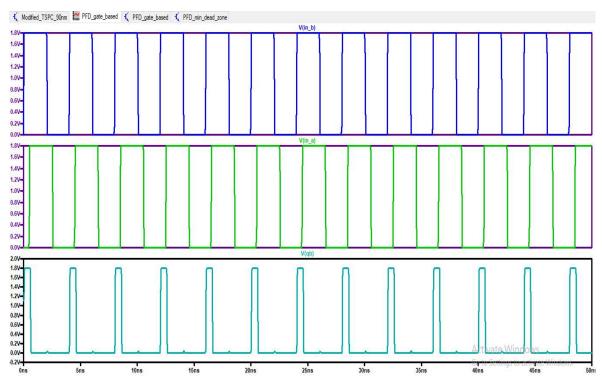

| 52 | Output Waveform at $Q_A$ when fref / Vref at V(in_a) is leading                                           | 54 |

| 53 | Output Waveform at $Q_A \& Q_B$ when fref / Vref at V(in_a) is lagging                                    | 54 |

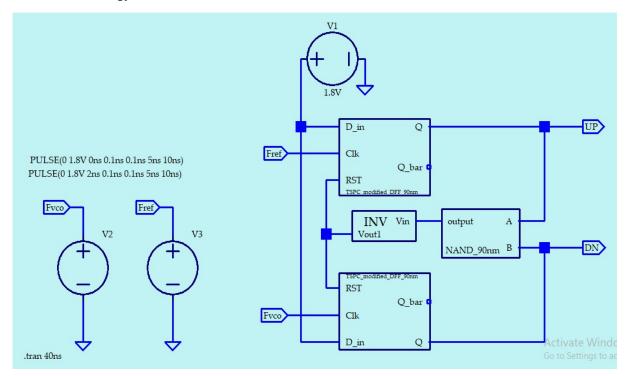

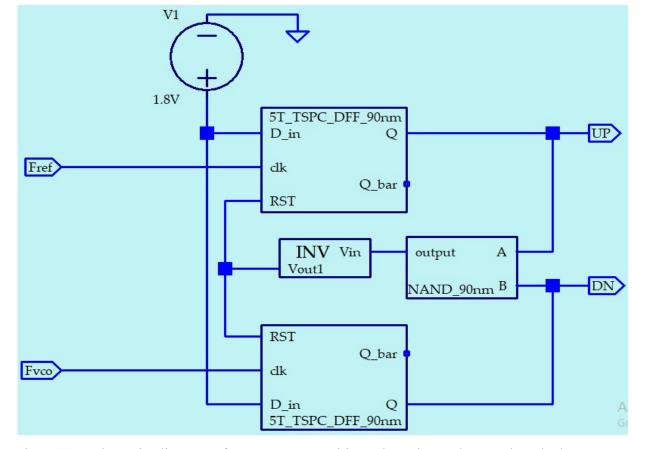

| 54 | Schematic diagram of a 5T TSPC Positive edge triggered Master-Slave D-FF.                                 | 55 |

| 55 | Schematic diagram of a 5T TSPC Positive edge triggered D-FF based Phase Frequency Detector.               | 56 |

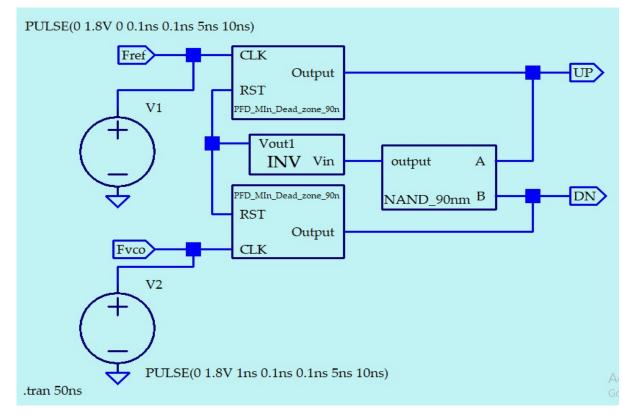

| 56 | Output Waveform at $Q_A \& Q_B$ when fref / Vref at V(in_a) is lagging                                    | 57 |

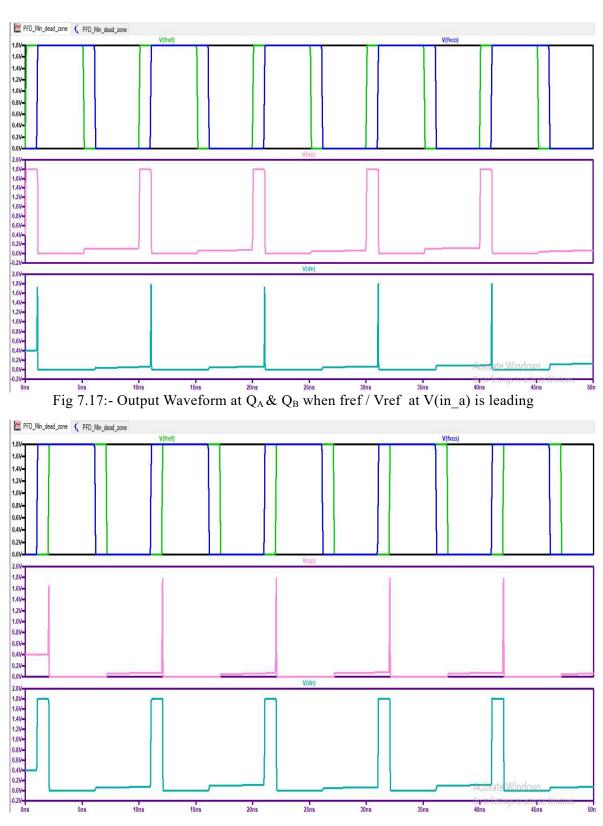

| 57 | Output Waveform at $Q_A \& Q_B$ when fref / Vref at V(in_a) is leading                                    | 57 |

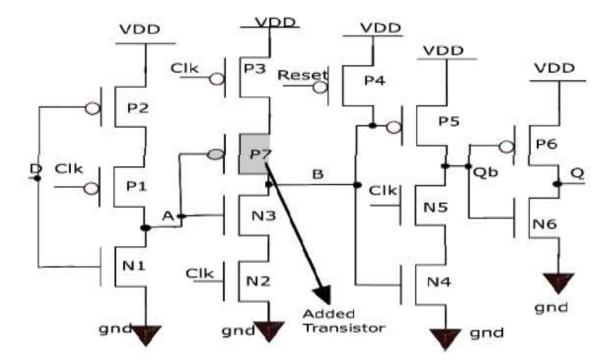

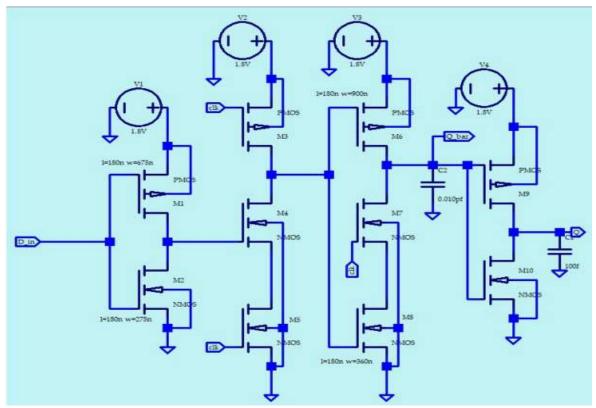

| 58 | Transistor level circuit diagram of a modified D-FF for Minimum Dead Zone                                 | 59 |

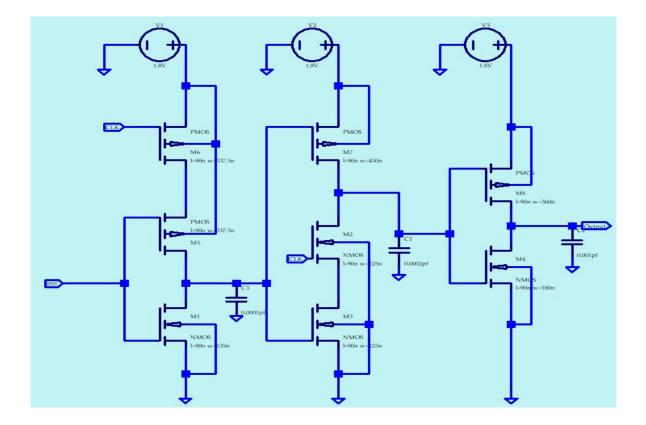

| 59 | Schematic diagram of a modified D-FF for Minimum Dead Zone                                                | 59 |

| 60 | Schematic diagram of a Positive edge triggered D-FF with minimum dead zone based Phase Frequency Detector | 60 |

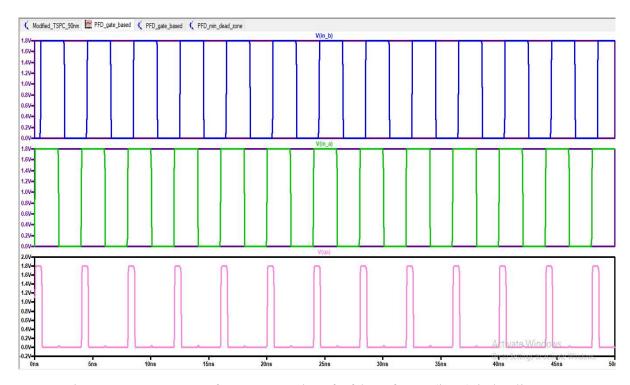

| 61 | Output Waveform at $Q_A \& Q_B$ when fref / Vref at V(in_a) is leading                                    | 61 |

| 62 | Output Waveform at $Q_A \& Q_B$ when fref / Vref at V(in_a) is lagging                                    | 61 |

| 63 | Schematic Diagram of Switch at Drain based charge pump circuit                                            | 63 |

| 64 | Current Waveform plot at the output node of the Switch at Drain based CP circuit                          | 64 |

| 65 | Schematic Diagram of Boot Strapped Charge pump circuit                                                    | 65 |

| 66 | Current Waveform plot of the Bootstrap circuit                                                            | 66 |

| 67 | (a) Gain boosting circuit principle (b) Gain boosting circuit condensed                                   | 67 |

| 68 | Transistor level circuit diagram of a gain boosting circuit                                               | 68 |

| 69 | Schematic Diagram of Gain Boosting Charge pump circuit                                                    | 68 |

| 70 | Current Waveform plot at the output node of the Gain Boosting CP circuit                                  | 69 |

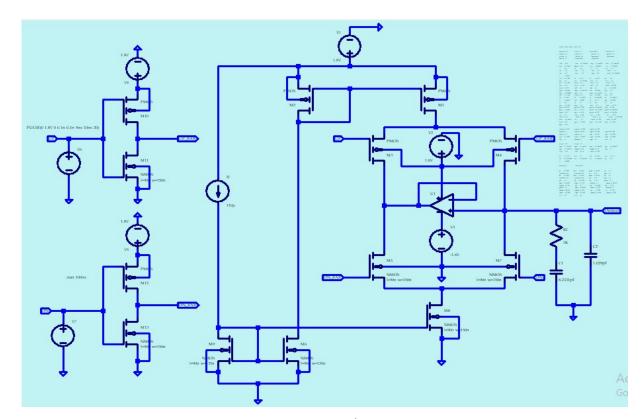

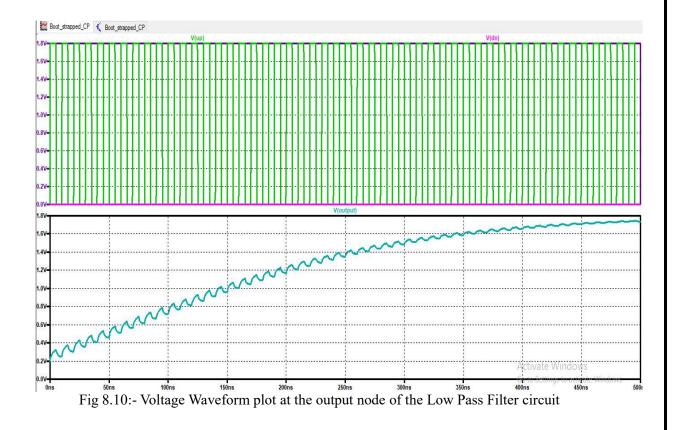

| 71 | Schematic of the Boot strapped circuit with 2 <sup>nd</sup> order LPF implemented using Ltspice            | 70 |

|----|------------------------------------------------------------------------------------------------------------|----|

| 72 | Voltage Waveform plot at the output node of the Low Pass Filter circuit                                    | 70 |

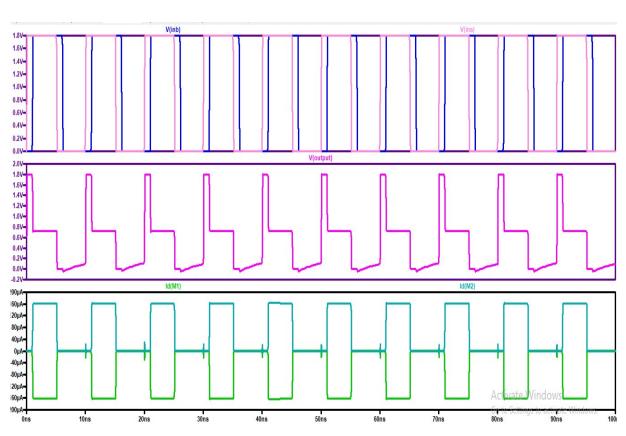

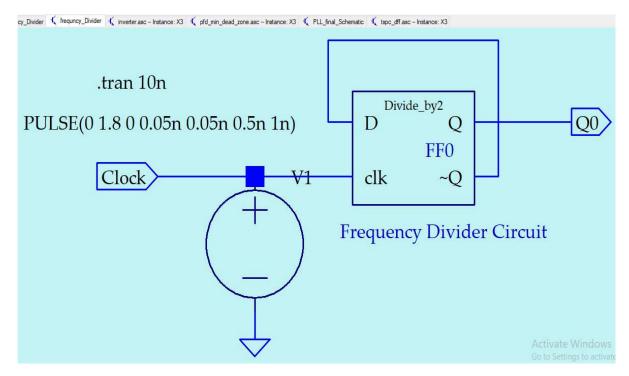

| 73 | Schematic diagram of the Frequency Divider Circuit                                                         | 71 |

| 74 | Schematic diagram of the TSPC Master-Slave edge triggered D-FF                                             | 72 |

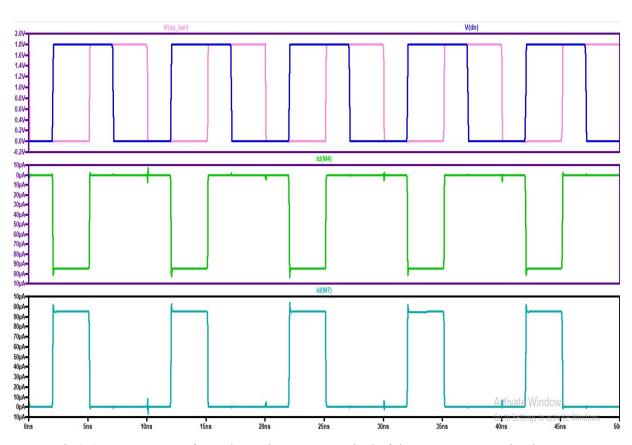

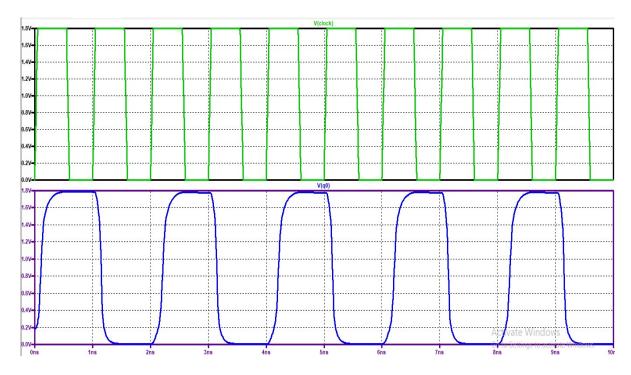

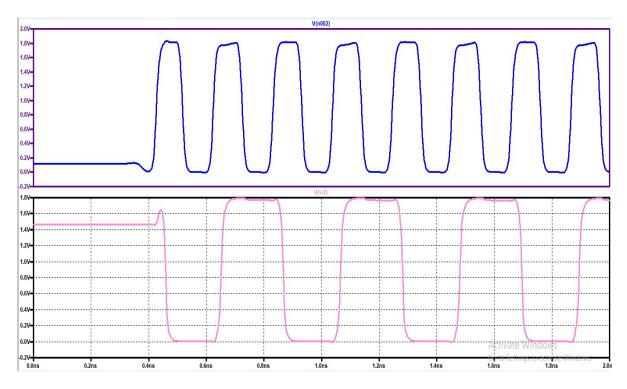

| 75 | Output Waveform of the frequency divider circuit simulated using Ltspice                                   | 72 |

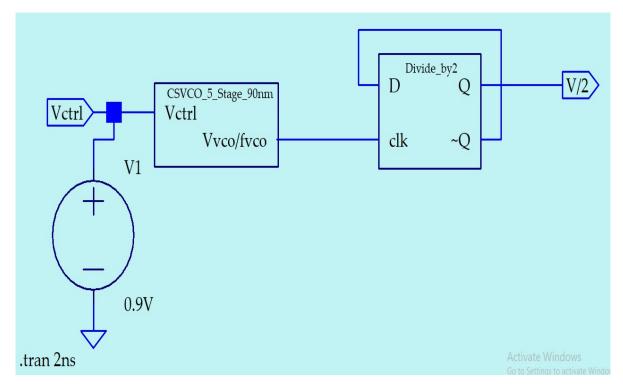

| 76 | Schematic diagram of the interconnection of CSVCO and TSPC DFF for $\operatorname{Fvco}/2$                 | 73 |

| 77 | Output wave form of the Fvco and Fvco/2 signal                                                             | 73 |

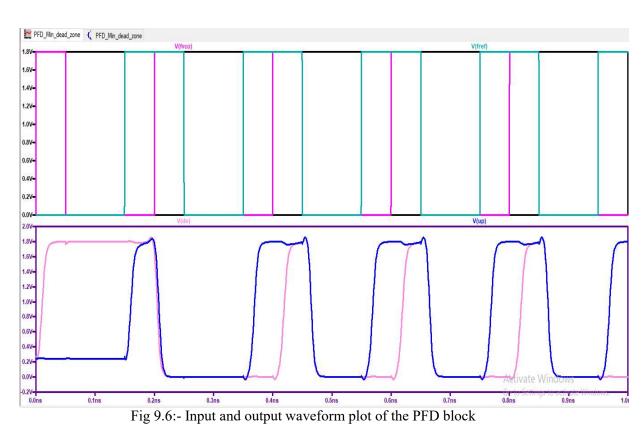

| 78 | Input and output waveform plot of the PFD block                                                            | 74 |

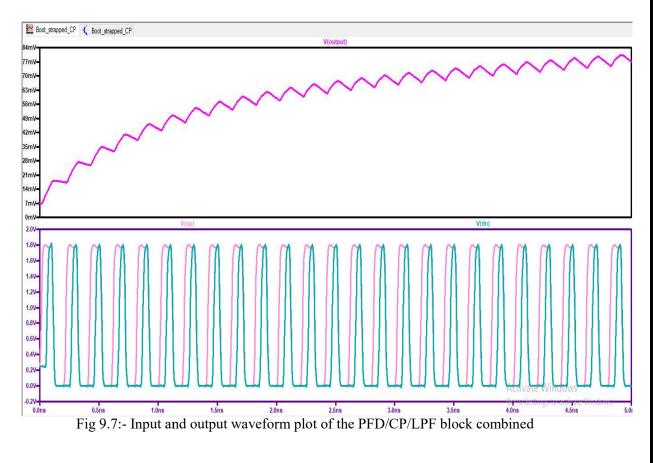

| 79 | Input and output waveform plot of the PFD+CP+LPF block combined                                            | 74 |

| 80 | Schematic Diagram of the PLL with no input for the calculation of Free Running Frequency                   | 75 |

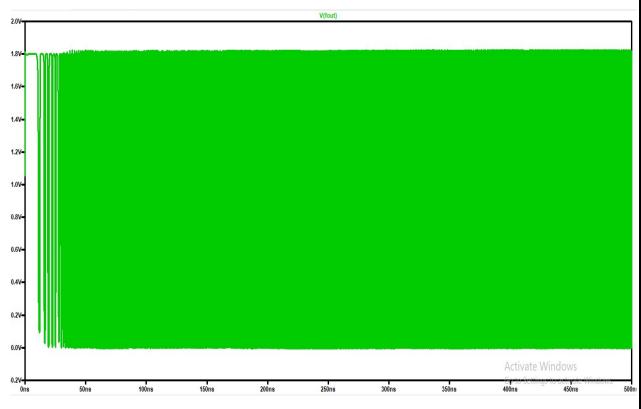

| 81 | Output waveform of the PLL for the calculation with no input signal                                        | 75 |

| 82 | Expended view of output waveform of the PLL for the calculation with no input signal                       | 76 |

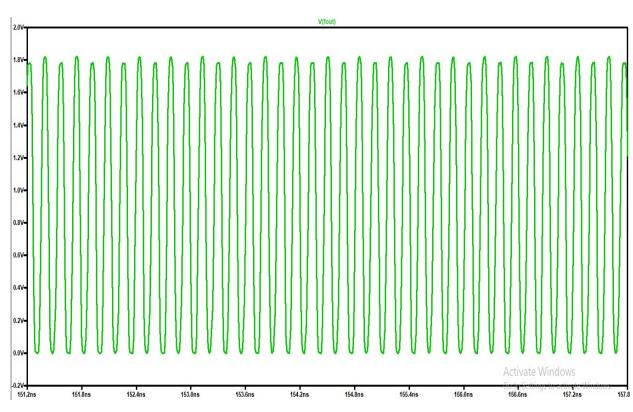

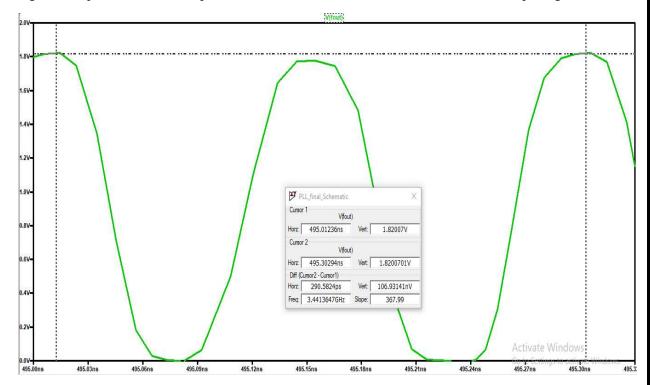

| 83 | Expended view of output waveform of the PLL for the calculation with free Running frequency of the PLL     | 76 |

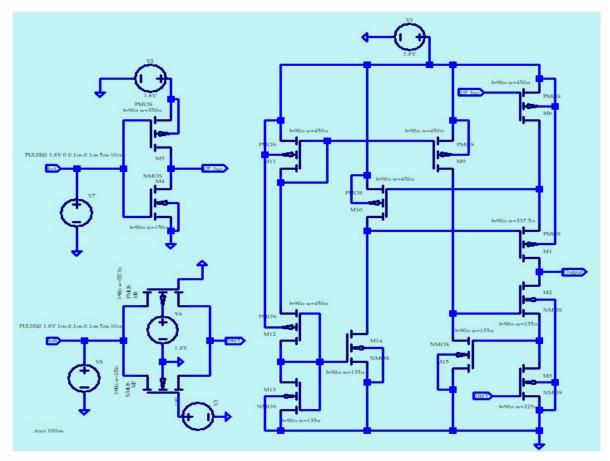

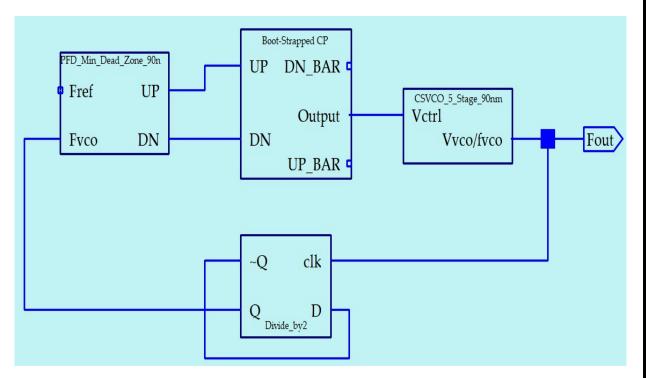

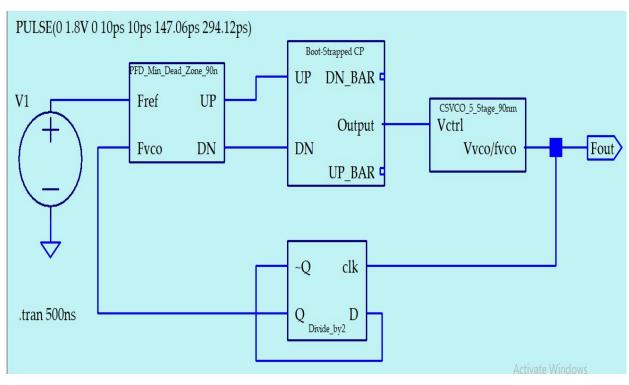

| 84 | Schematic Diagram of the implemented PLL circuit                                                           | 77 |

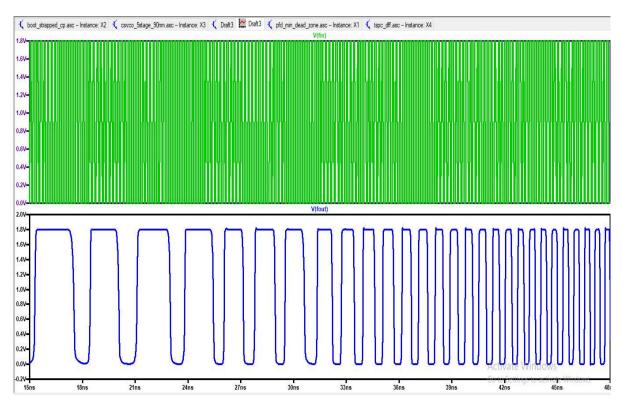

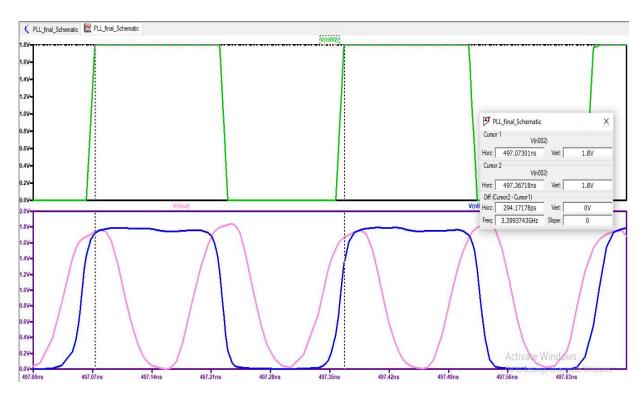

| 85 | Zoom in view of the Input and output waveform plot of the PLL                                              | 77 |

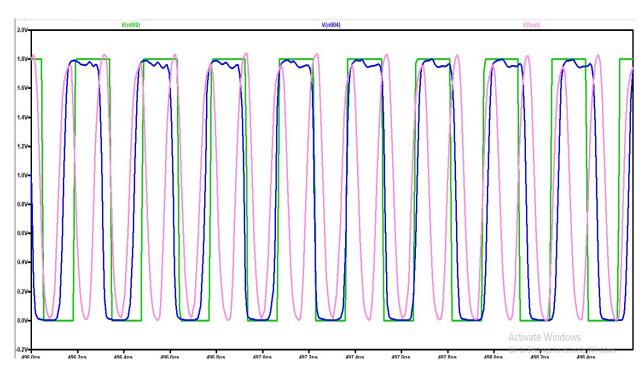

| 86 | Zoom in view of the Input waveform (V(n002)), Divider waveform (V(n004)) and VCO output waveform (V(fout)) | 78 |

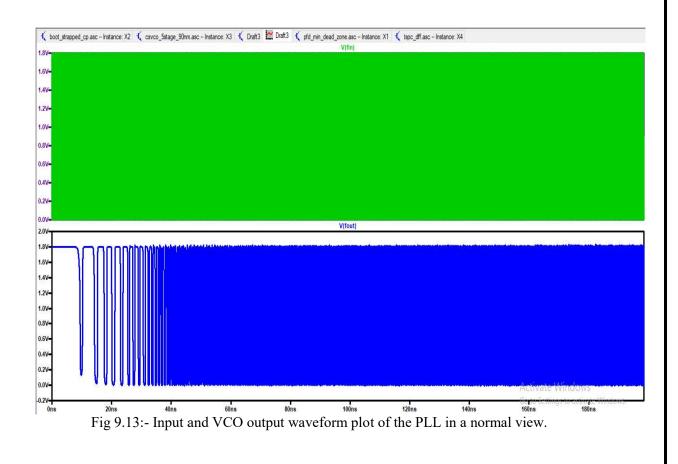

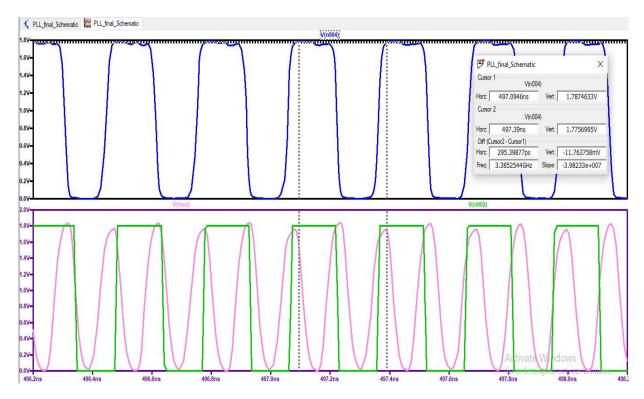

| 87 | Input and VCO output waveform plot of the PLL in a normal view                                             | 78 |

| 88 | Frequency measurement of the input signal from the output waveform                                         | 79 |

| 90 | Frequency measurement of the frequency divider output signal from the waveform                             | 79 |

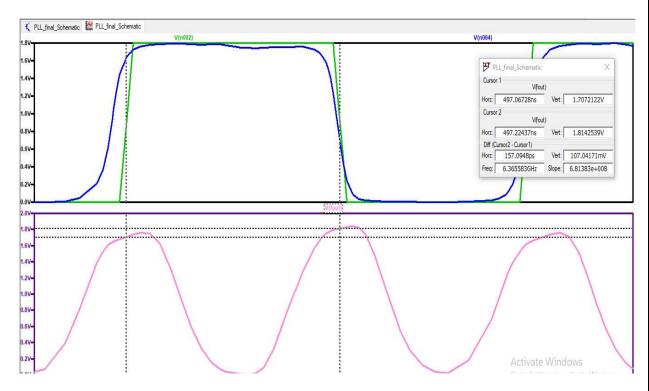

| 91 | Frequency measurement of the VCO output signal for given input                                             | 80 |

# LIST OF TABLES

| S.No. | Description                                                                                                                             | Page No. |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1     | Specifications of the implemented CSVCO                                                                                                 | 44       |

| 2     | Vctrl vs. Fvco from the implemented CSVCO                                                                                               | 44       |

| 3     | Specifications of the implemented CSVCO                                                                                                 | 46       |

| 4     | Vctrl vs. Fvco from the implemented CSVCO                                                                                               | 46       |

| 5     | Specifications of the implemented Gate Level PFD                                                                                        | 49       |

| 6     | Specifications of the implemented Modified TSPC based PDF                                                                               | 55       |

| 7     | Truth Table a 5T TSPC Positive edge triggered Master-Slave D-FF                                                                         | 56       |

| 8     | Specifications of the implemented 5T TSPC M-S based PDF                                                                                 | 58       |

| 9     | Specifications of the implemented Fast Frequency Acquisition with Minimum Dead Zone PDF                                                 | 60       |

| 10    | Comparative Study of Implemented PFDs                                                                                                   | 62       |

| 11    | Calculations for Rp, Cp and C2 of Low Pass Filter using equations as<br>mentioned in section 3.2 under Dynamics of Charge Pump Circuits | 71       |

| 12    | Calculated values and Measured Values of PLL parameters.                                                                                | 80       |

## **CHAPTER-1** Introduction to Phase Locked Loops

#### 1.1 Need of PLL

A very simple question arises here that can we have a reference clock generate it on a chip and distribute it across the entire chip. Is it possible?

Answer is Very easy - No, In general it is not possible.

Essentially, the objective is having a reference clock and the frequency of this clock cannot be very high. We already know that we can have a Quartz crystal and crystals have a very high Q (which is called Quality Factor and for the crystals it ranges of 20000 to 100000 and can be above it) thus by virtue they produces a very stable clock signal Q is inversely proportional to bandwidth ( $W_H - W_L$ ).

Thus we may have a crystal, generate the reference clock and the problem is solved. Actually this is not that easy as it said.

Why not we do this and Why Phase locking is required?

Reasons can be multiple but essential gist of it is:-

Range of frequency cannot be achieved and also crystal cannot produce a very high frequency.

We cannot generate a square wave using a crystal oscillator.

See Crystal is a piezoelectric material which works on the principle of piezoelectricity where the mechanical energy being constantly converted to electric energy and by nature the **mechanical** systems are very slow but they are very perfect. We can emulate a mechanical system to an electrical system or vice-versa but there will be significant difference between speed of operation and size of the system.

Now, if we want to have a high frequency then we essentially needs to multiply the frequencies and to perform a frequency multiplication we need a frequency multiplier which is very accurate on its own. There cannot be skew in output.

For example - if we need to multiply the frequency 10 times than it cannot be 9.8 or 10.2. It should precisely be 10 and the phase of signal should not change quite a lot.

First thing I do need a very perfect frequency multiplier. Second thing is suppose I need to distribute this signal over a large area and off course the periodic nature needs to be maintained.

So the most prominent advantage of a PLL in CMOS technology is it helps to control jitter, the phase of the clock and also it helps to control the frequency. Yes we can control the phase and frequency both. This provides a significant advantage of distributing a low frequency signal easily across the chip.

So the whole idea is - We put a crystal for the reference clock outside the chip, put a PLL with whatever module you want to implement which multiplies the input frequency by N (fixed number) and thus enables us to locally generate those frequencies which are in sync with the main frequency and there is no phase shift or very negligible phase shift which can be ignored hence getting our job done.

#### 1.2 What is a PLL?

A PLL is a circuit that enables one system to track with another. A PLL is a circuit which synchronizes an output signal (generated by the reference oscillator) in both frequency and phase with a reference signal. The phase deviation between the oscillator's output signal and the reference signal is negligible or remains consistent in the synchronized-also known as locked-state.

If the phase error rises, a control mechanism acts on the oscillator to minimize the phase shift to a minimum value. The phase of the control signal is completely locked to the phase of the input/reference signal in such a system. This is why it's called a phase-locked loop.

A Phase-locked loop is a mixed-signal electronic circuit that generates a high frequency output clock. It is a feedback control system that constantly works on the input and the output clock phase relationship to get the desired output frequency. It has wide variety of application in analog, digital and RF communication systems where clocks with high spectral purity are needed.

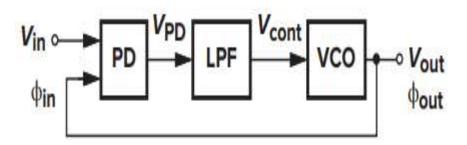

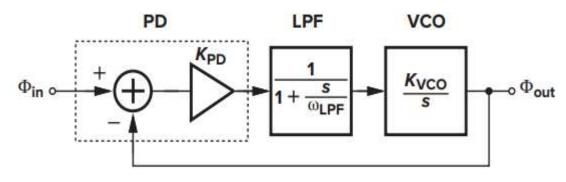

Fig.1.1:- PLL Block Diagram

The Phase Locked Loop (PLL) circuit is composed of three major components:-

- 1. Phase Frequency Detector (PFD)

- 2. Charger (CP)

- 3. The Low Pass Filter (LPF)

- 4. Oscillator with Voltage Control (VCO)

The PLL circuit is composed of all of these components. PLL layout has undergone numerous changes as a result of its applications. Some blocks are introduced into the loop while others are excluded depending on the circumstances. PLL design is rapidly advancing as they are useful in implementing greater frequencies ranging GHz to instantly latch them. To achieve the desired results, the VCO, which is at the soul of the PLL circuit, has advanced dramatically. To minimize Phase Noise and increase the locking range of the VCO, a resistor is added.

We simply cannot proceed further without knowing the details of these blocks. So the following subsections will have a detailed study of these blocks.

#### **1.2.1 PHASE / FREQUENCY DETECTOR**

By Definition: - A phase detector is a circuit whose average output  $V_{out}(t)$  is linearly proportional to the phase difference  $\Delta \Phi$  between two inputs.Starting from a simple XOR, we want to make a feedback loop which receives the reference frequency and let this be clear that the *amplitude of the reference signal doesn't matter*. So loop receives a frequency then this loop provides a feedback, this frequency is integrated therefore we have phase information, the feedback will give information about the phase of the signal which is available for the system then these two phases are compared at the input of loop and accordingly the loop will adjust itself. The only difference is the variable is not a voltage, variable is frequency here.

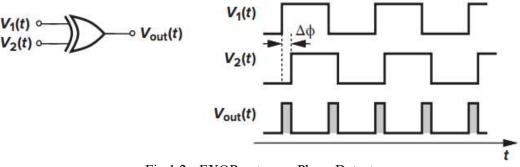

Fig 1.2:- EXOR gate as a Phase Detector

How an XOR can be used a simple phase detector?

XOR as a "Differential Phase Amplifier or Digital Phase Detector".

$V_1$  (t) and  $V_2$  (t) are two square wave signals with same amplitude and having a small phase shift denoted by  $\Delta \Phi$ . Based on the phase shift of the two input signals it generates the timing information which is the  $V_{out}$  (t) or  $V_{avg}$  (t) pulse.

So what will XOR do .If there exists a phase shift in between two signals the duty cycle at the XOR output will change as shown in the output in Fig 1.2 and that  $V_{out}(t)$  pulse will have different average output value associated with it. Therefore, I am able to convert phase shift into voltages. Then this voltage information is used to control the phase for the signal.

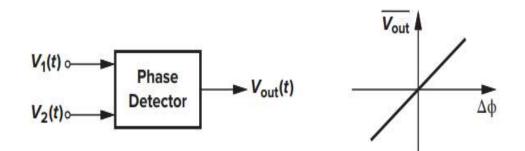

Fig 1.3:-  $V_{out}(t)$  vs.  $\Delta \Phi$  plot for a phase detector

In ideal scenarios as shown in Fig 1.3, the relationship between  $V_{out}(t)$  and  $\Delta \Phi$  is linear across the origin for  $\Delta \Phi = 0$ . The slope of the  $V_{out}(t)$  vs.  $\Delta \Phi$  is called the gain of the PD and the slope is expressed in V/rad.

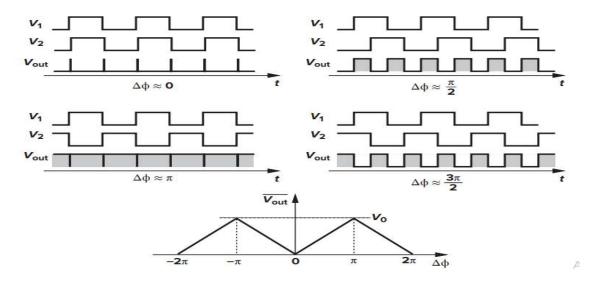

If  $V_1$  (*t*) leading is the phase difference between  $V_1$  (*t*) and  $V_2$  (*t*) is positive and similarly when  $V_1$  (*t*) is lagging phase difference between  $V_1$  (*t*) and  $V_2$  (*t*) is negative as shown in Fig 1.4.

However, the behavior of XOR is not monotonic meaning whether it is lagging or leading XOR cannot judge this. Also if we just have a look over the variation of  $V_{avg}$  (t) with the  $\Delta \Phi$  considering the amplification of the circuit, the gain is coming out to be sometimes positive and sometimes negative. This will create stability issues in the circuit like if I design my circuit for a positive gain we cannot switch it into negative gain region.

So we could end-up in a situation where the system working for the phase lead might not work for the phase lag or vice-versa.

But we need to remind that - Even though we may consider unstable systems being unworthy but we still use is in our designs because of its regenerative feedback action and also gain of a practical system cannot reach to an infinite value, it saturates over a certain value. And that's how we utilize the behavior of the unstable systems for our purpose.

Fig 1 4:-  $V_{out}(t)$  vs.  $\Delta \Phi$  plot with respect to different phase relation between  $V_1(t)$  and  $V_2(t)$ .

Another possibility seems to be that the loop locks to harmonics of the input signal when a multiplier is used as the phase detector. The PLL code, for example, can lock twice the frequency of the input signal, three times the frequency of the input signal, or just about any multiple. It might get latched to a sub-product of the input signal frequency. This *false lock* will occur whenever the VCO's free running frequency is comparable to a multiple or some multiple of the frequency of the input signal than the real frequency. *False lock* can only be prevented by ensuring that the oscillator's free running frequency is closer to the real input frequency than to some multiple or submultiples.

The dilemma of lock accretion in type-1 PLLs has already intensively investigated, but we affirm without evidence that the "acquisition range" is on the order of  $\omega_{LPF}$  i.e., the loop latches only if the separation among  $\omega_{in}$  and  $\omega_{out}$  is close to  $\omega_{LPF}$ . The issue of lock accretion further complicates the quid pro quo in type-1 PLLs. When the LPF is minimized, the acquisition range is scaled down to reduce the control voltage ripple.

To overcome this drawback, PFDs are used in PLLs. PLLs based on such phase comparator have a lot of beneficial characteristics. Firstly, they do not exhibit a false lock. Second, whenever the system is locked, the input signal and the oscillator output waveforms are accurately in phase, even if the input frequency is not the same as oscillator's free running frequency. Eventually, the PLL achieves lock rapidly even when the input frequency is considerably different from the oscillator's free running frequency.

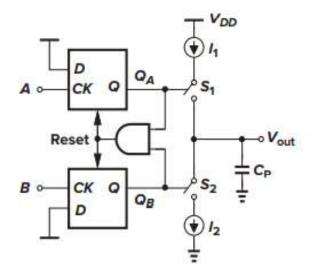

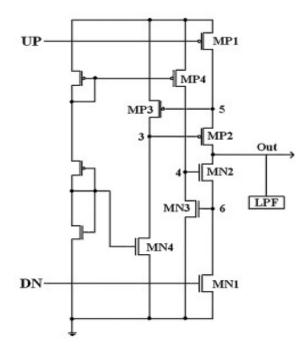

The PFD block, Fig 1.5, tracks the phase and frequency of the reference clock and the divided clock. It generates two pulses, UP and DN, based on the phase difference between the two incoming signal (error signal). When the frequencies of the two inputs become the same and the error signal acquires a small constant value over time, the PLL accomplishes a lock.

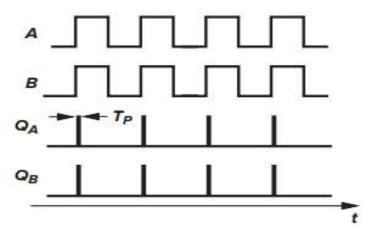

Fig 1.5:- Phase Frequency Detector (a) Schematic (b) Transition Diagram (c) Timing Waveform

The PFD is a three-state state machine. Suppose that the UP and DN outputs are both low initially. Once input A precedes input B, the UP output is asserted on input A's positive edge. The UP signal will continue to stay in this state unless there is a low-tohigh transition on input B. The DN output is asserted at around that time, causing both flip-flops to reset through the asynchronous reset signal. On the DN signal, a relatively brief pulse proportional to the phase difference is generated, and there is a narrow pulse on the DN output with a duration equal to the delay through the AND gate and register reset delay.

On the DN signal, a short pulse proportional to the phase difference is produced, and there is a limited pulse on the DN output with just a duration equal to the delay through the AND gate and register reset delay. The UP pulse's pulse width equals the phase difference between the two signals. When input B lags behind input A, the situation is reversed, and a pulse proportional to the phase difference is produced on the DN output. Short pulses will be obtained on the UP and DN outputs if the loop is locked.

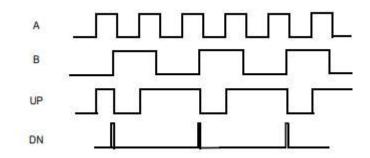

Fig 1.6:- Timing of PFD measuring frequency error

#### **1.2.2 CHARGE PUMP**

To mitigate the bounded phase inaccuracy encountered in type-I Locked Loops, we really would like to increase the gain of the loop to almost infinity, probably using an integrator. As our first step, we interpose a "*charge pump*" (CP) between the PFD and the loop filter. A charge pump is comprised of two switched current sources that pump charge into or out of a loop filter based on two logical inputs i.e., UP and DN signals. Fig 1.7 depicts a Charge Pump circuit powered by a Phase Frequency Detector and driving a capacitor.

The charge pump converts the *UP and* DN input pulses coming from PFD into current pulses that charge/discharge the Loop Filter to give the desired control voltage (*Vctrl*).

Fig 1.7:- Basic Charge Pump schematic

The operation can be understood in detail with the help of the following waveforms

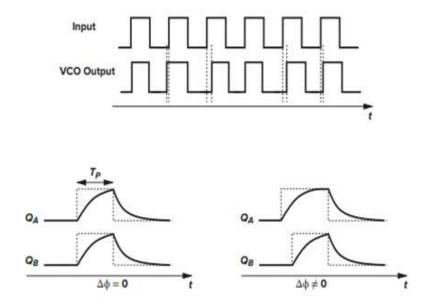

Fig 1.8:- Charge Pump Waveform

Due to a phase difference between *clkref* and *clkdiv* signals, PFD produces UP and DN pulses as shown in the waveforms. Since *clkref* leads *clkdiv*, UP pulse goes high. This causes the UP current to dump charge into the Loop Filter capacitor and hence increase *Vctrl(t)*. Thus *Vctrl(t)* increases as long as *clkref* leads *clkdiv*.

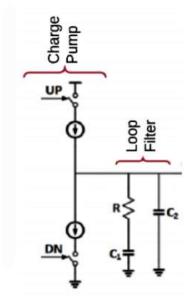

#### **1.2.3 LOOP FILTER**

The loop filter is very important for lock acquisition, phase/frequency tracking and noise filtering. The Low Pass Filter is used to remove out the PFD's high frequency components, allowing only lower frequency components to pass through. It produces a direct current voltage that controls the output. The output frequency of the voltage controlled oscillator is determined by this DC voltage. The LPF output is fed into the VCO as an input.

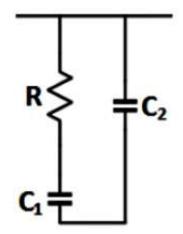

The loop filter circuit discussed in thesis is a low-pass filter consisting of two capacitors and a resistor as shown in Fig 1.9 shown below.

Resistor, R, introduces a zero and capacitor,  $C_1$ , adds a pole to system function such that it is stable in the desired frequency realm. Capacitor,  $C_2$ , reduces  $\nabla ctrl$  (t) ripple but works against ensuring the stability of the system. The values of R, C1 and C2 are

9

chosen to have optimum stability and good high frequency noise rejection. Ideal the value of  $C_2$  capacitor should be  $1/5^{\text{th}}$  to  $1/10^{\text{th}}$  of the  $C_1$  capacitor.

Working of the loop filter: -

It transforms digital error pulses from the PFD's output to analog error currents. The charge pump is composed of switched a current source which charges the capacitor and generate the corresponding voltage. The current sources and switches are accomplished using PMOS and NMOS transistors. PMOS and NMOS serve as current sources and therefore are biased to function in the saturation mode. PM0 and NM0 are used to implement the switches. The *UP* output is forwarded through the inverter, which is linked to the PMOS switch (PM0). The output *DN* is forwarded through a transmission gate to reimburse for the gate delay caused by the inverter before even being fed into the NMOS switch (NM0). The charge pump input variables can be in one of three states. If *UP* and *DN* are both zero, both PM0 and NM0 are turned off, but the control voltage across the capacitor remains unchanged. If *UP* is high and *DN* is low then PM0 is one and PM1 charges the capacitor increasing the control voltage. If *DN* are on for such a short period of time, any imbalance in current flow through PM0 and NM0 during this time produces ripple effects in the control voltage.

Fig 1.9:- Loop Filter Circuit

The transfer function for this filter is given by-

..... 1.1

#### **1.2.4 VOLTAGE CONTROLLED OSCILLATOR**

The very first step in constructing a voltage controlled oscillator is to realize an oscillator and then add a means for trying to control its frequency of oscillation through the use of input voltage, but in some cases the control signal could be a current. Oscillators are categorized into two categories: those that produce pure sine wave outputs explicitly and those that produce square wave outputs. Sinusoidal output oscillators are typically realized using a feedback frequency selective or tuning circuit, whereas square wave output oscillators are typically realized using a nonlinear circuit such as a relaxation oscillator or ring counter.

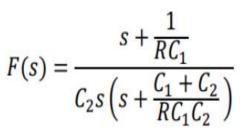

An ideal VCO block generates a periodic output whose frequency out is a linear function of input control voltage  $V_{ctrl}(t)$ . The plot below shows the linear relationship-

Fig 1.10:- Frequency vs. Voltage plot of an Ideal VCO

The linear relationship can be described by the equation:-

$$\omega_{\rm out} = \omega_0 + K_{\rm VCO} \ge V_{\rm cont} \qquad \dots 1.2$$

Here,  $\omega_0$  represents the intercept corresponding to  $V_{cont} = 0$  also called the "Free running frequency" and  $K_{VCO}$  denotes the "gain" or "sensitivity" of the circuit (expressed in rad/s/V). The achievable range,  $\omega_2 - \omega_1$ , is called the "tuning range." As the phase is the time integral of the frequency, the phase output of the VCO block is given by:-

$$\phi_{out} = \omega_0 t + K_{vco} \cdot \int_{-\infty}^t v_{cont} dt$$

.....1.3

The VCO is one of the main contributors to jitter in the output clock, so the topology needs to be chosen carefully according to specification. The two broad categories of VCOs are Ring oscillators and LC tank oscillators. LC oscillators offer lower jitter than ring oscillators but occupy more on-chip area.

## **CHAPTER-2**

## Study of PLL behavior under Phase and Frequency Transience

Basic PLL has a *phase detector* to generate the phase difference information to an equivalent voltage levels. An LPF (Low Pass Filter) to deduce the average value of the output voltage and we also need some module to convert this voltage to an equivalent frequency value which is performed by non-other than a VCO (Voltage Control Oscillator).

Output of a VCO can actually be  $\omega$  i.e. frequency or  $\omega xt$  i.e. phase anyway both of these are interrelated hence both are correct. Therefore, I have a VCO whose output will have a phase which is changing with time and input signal is also variable with time.

Suppose I have a periodic signal with frequency  $\omega_{\theta}$  hence its phase is  $\omega_{\theta} t$  therefore the phase is changing linearly with time.

Suppose my loop is locked the VCO will generate the frequency  $\omega_0$  and the static phase of  $V_1$  (*t*) is also zero, making the phase difference between  $V_1$  (*t*) and  $V_2$  (*t*) to be zero. 'Or' I can have two linearly varying phase such that there phase difference is also zero.

See we can't say that we have phase information but don't have frequency information. This sounds illogical. Phase and frequency are two sides of a coin.

Question may arise here, why I need to compare two phases? Can't we simply perform the frequency comparison?

Off course yes frequency comparisons can also be performed, the loop will have go to a locking position if those two frequencies are close to each other and there exists a constant phase difference between them. Let's just prove it mathematically,

2.1 Frequency Transience:-

$$\frac{e(s)}{fin(s)} = \frac{1}{1 + \beta(s)G(s)}$$

.....2.1

where, e(s) = fin(s) - fout(s), that is the error between input and output frequency G(s) is the forward path loop gain;  $\beta(s)$  is the feedback factor. From the block diagram shown in the Fig 2.1,

$$\frac{e(s)}{fin(s)} = \frac{1}{1 + \frac{K}{1 + \frac{S}{P}}}$$

.....2.2

$K = K_{vco} \times K_{PD}$ , is the D.C. gain and P is the pole of the system. Now suppose, there occur a step change in the input frequency  $\Delta f_e$ . Taking its Laplace transforms;

$$fin(s) = \frac{\Delta f0}{s} \qquad \dots 2.3$$

Now,

$$e(s) = \frac{\Delta f0}{s} \times \frac{1}{1 + \frac{K}{1 + \frac{S}{P}}}$$

.....2.4

Solving this equation, we will get;

$$e(t) = \frac{f0}{(1+k)}u(t) + \frac{K}{P(1+K)^2}e^{-t (t+1)}u(t)$$

....2.5

At steady state, the exponential component will vanish; we will be still left with,

14

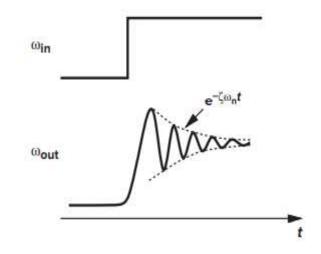

Fig 2.2:- Response of PLL for small frequency step

PLL response to a small frequency step input at  $t = t_I$ . Still, the VCO persists to oscillate at  $\omega_I$  instantly after  $t_I$  because the voltage across the capacitor cannot be changed at an instant. As a result, the PD produces extremely broad pulses as well as  $V_{LPF}(t)$  increases over time. As  $\omega_{out}$  approaches  $\omega_1 + \Delta \omega$ , the width of the PD pulses reduces, finally settle

downs to a level which generates a DC offset equivalent to  $\frac{(\omega 1 + \Delta \omega - \omega 0)}{KVCO}$ . In comparison to a phase step, a PLL's answer to a step frequency involves a radical shift in both the voltage and the phase steps.

Hence, it can be concluded from the above derivation that while performing the frequency comparison rather than phase there always occurs an error at the steady state which is inversely proportional to the loop gain.

#### 2.2 Phase Transience:-

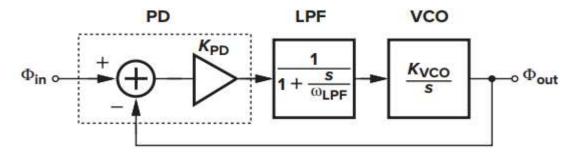

Fig 2.3:- Block Diagram of a PLL circuit where phase is fed to the comparator

$$\frac{e(s)}{\phi in(s)} = \frac{1}{1 + \beta(s)G(s)}$$

.....2.7

Now, let's just do all of this for the phase detector in spite of frequency detector. where,  $e(s) = \Phi in(s) - \Phi out(s)$ , that is the error between input and output phase. G(s) is the forward path loop gain;  $\beta(s)$  is the feedback factor. From the block diagram shown in the Fig 2.3,

$$\frac{e(s)}{fin(s)} = \frac{1}{1 + \frac{1}{S} \times \frac{K}{1 + \frac{S}{P}}}$$

.....2.8

$K = K_{vco} \times K_{PD}$ , is the D.C. gain and P is the pole of the system. Now suppose, there occur a step change in the input frequency  $\Delta \Phi_e$ . Taking its Laplace transforms;

$$\Phi in(s) = \frac{\Delta \Phi 0}{s}$$

.....2.9

Now,

$$e(s) = \frac{\Delta \Phi 0}{s} \times \frac{1}{1 + \frac{1}{S} \times \frac{K}{1 + \frac{S}{P}}}$$

.....2.10

Even without solving this equation, we can deduce that the steady state error of the above described system is zero because it is a type-1 system, because of the open loop pole at origin, *error of a type-1 system for step input at steady state is zero*.

Therefore, at steady state,  $e(s) = \Phi in(s) - \Phi out(s) = 0$ Since,

$$\omega = \frac{d\Phi}{dt}$$

.....2.11

$$\frac{d\Phi in(t)}{dt} - \frac{d\Phi out(t)}{dt} = 0$$

....2.12

$$\omega in(t) - \omega out(t) = 0$$

.....2.13

$$\omega in(t) = \omega out(t)$$

.....2.14

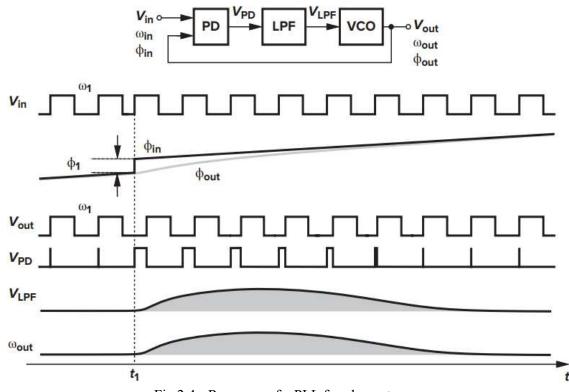

Fig 2.4:- Response of a PLL for phase step

As shown in Fig 2.4, suppose the input has a phase step of  $\Phi_1$  at  $t = t_1$ , i.e.,  $\Phi_{in} = \Phi_1(t) + \Phi_1 u(t-t_1)$ . The phase step does seem to be a positive edge in *Vin* (t) that occurs earlier (or later) than the periodicity suggests. The phase step, on the other hand, causes a contraction (or lengthening) of the duration well before t1. The VCO initially oscillates at  $\omega_1$  because the LPF output does not change immediately. The increasing phase shift between input and output generates broad pulses at the PD's output, causing VLPF to gradually increase. As a result, the VCO frequency starts to vary in an effort to minimize phase shift. Because the phase error varies over time, the loop does not get locked during the transient.

In case the loop comes back to lock state,  $\omega_{out}$  must eventually returns to  $\omega_I$ , which needs  $V_{LPF}$  and therefore  $\Phi out - \Phi in$  also return to their actual values. The disparity in the output frequency of VCO is such that the area under  $\omega_{out}$  provides an access phase of  $\Phi I$  in  $\Phi$ out because  $\Phi$  in has changed by  $\Phi 1$ . As

$$\int_{t1}^{\infty} woutdt = \mathbf{\Phi}1$$

.....2.15

All variables (except the total input and output phases) revert to their initial values when the loop returns to the lock state. That is, the  $\Phi_{in}$ - $\Phi_{out}$ , VCO, and  $V_{LPF}$  frequencies stay intact expected result considering that all these three variables have a one-to-one correlation and the input frequency stays constant.

Two observations highlight the significance of this property. In certain applications, even a really small (deterministic) frequency inaccuracy may be unacceptable. For example, if a digital signal is to be processed simultaneously by a clocked system, a subtle change in data rate and operating frequency may end up causing "drift," which causes errors. Aside from that, if the PLL tried to compare input and output frequencies instead of phases, the equality would simply not exist. A loop using a frequency detector (FD) would have a finite difference between in and out due to mismatches and other non-idealities.

# **CHAPTER-3** Dynamics of type-I PLLs and CP-PLLs

The only justification for including this chapter is to provide an in-depth examination of the PLL's behaviour and attitude. In this chapter, we will look at the mathematical model between input phase and output phase for the open-loop and closed-loop systems, as well as the behaviour of the system in time domain.

Why  $\Phi_{out}(s) / \Phi_{in}(s)$  hold so much significance?

Reason being, it reveals whether the output phase tracks the input phase slowly or rapidly.

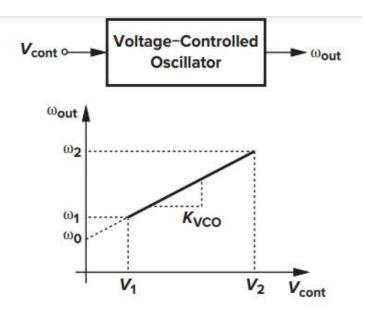

#### 3.1 Dynamics of type-I PLLs

Fig 3.1:- Block Diagram of a PLL circuit

Let's just consider a model of a PLL which is linear, consider a 1<sup>st</sup> order low pass filter for the sake of simplicity in the analysis.

The Phase Detector output contains a dc component equal to  $K_{PD}(\Phi_{in} - \Phi_{out})$  as well as the higher frequency components. This output is fed to the next block which is an LPF. The LPF will eliminate the high frequency component and allows only the DC components to pass. This simple looks like both the PD and the LPF in a combine way works like an "subtractor" circuit.

Before starting the whole analysis it must be made clear that in following cases  $\Phi_{in}$  &  $\Phi_{out}$  are the excess phase in the input and output respectively because anyway we will be getting the  $V_{PD}(t)$  which will be proportional to the phase difference only.

For the block diagram shown in Fig 3.1, the open loop transfer function can be given as:-

The equation (1) reveals that, the open loop system has two poles one at s=0 and other at  $s=\omega_{LPF}$ . Since at the origin for the open loop system there exist a pole, such systems also called type-I system.

The equation (1) reveals that, the open loop system has two poles one at s=0 and other at  $s=\omega_{LPF}$ . Since at the origin for the open loop system there exist a pole, such systems also called type-I system.

In the above equation, it can be seen at as  $s \rightarrow 0$ , the gain of the system moves to infinity. This can be interpreted as if the excess phase of the input varies slowly, the loop will ensure that the input phase change  $\Phi_{in}$  will exactly matches with output phase change  $\Phi_{out}$ .

In a similar way, closed loop equation can be derived as:-

Since,

$$\omega = \frac{d\Phi}{dt}$$

.....3.3

Equation (3.2) can also be interpreted as :-

$$\frac{\omega out(s)}{\omega in(s)} | closed = \frac{Kpd.Kvco}{\frac{S^2}{\omega LPF} + S + Kpd.Kvco}$$

.....3.4

This outcome indicates that only if  $\omega in$  changes very slowly  $(s \rightarrow 0)$ , then  $\omega out$  tracks  $\omega in$ , that is another expected outcome because the loop is believed to be locked. Also itindicates that if  $\omega in$  varies sharply and the system is provided sufficient time to relax i.e.  $(s \rightarrow 0)$ , the variation in  $\omega out$  equalise the variation in  $\omega in$ .

Comparing the equation (4) with the standard second order system equation shown below:-

$$F(s) = \frac{\omega n^2}{s^2 + 2\Sigma\omega ns + \omega n^2}$$

.....3.5

Let's assume that, K = Kpd. *Kvco*. We have

$$\omega n = \sqrt{\omega LPF \times K}$$

.....3.6

$$\sum = \frac{1}{2} \sqrt{\frac{\omega LPF}{K}}$$

.....3.7

Also, the damping factor, from above relations,

$$a = \Sigma \omega_n = \frac{1}{2} \omega LPF$$

.....3.8

a is a critical parameter to define the speed of the closed loop system i.e. settling time of the closed loop system is inversely proportional to a.Lower the value of  $\omega_{LPF}$ , lesser will be the high frequency components however the system will gets slower and require more time to settle down.

Fig 3.2:- Variation in  $\omega_{\text{out}}$  with time because of transience in  $\omega in$

Also, to avoid excessive ringing in the output waveform,  $\Sigma$  is chosen between  $\frac{1}{\sqrt{2}}$  and 1.

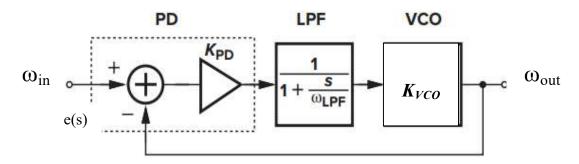

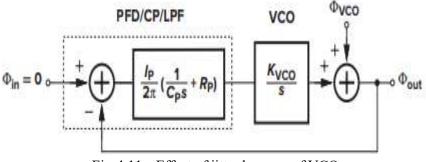

#### 3.2. Dynamics of Charge Pump PLLs:-

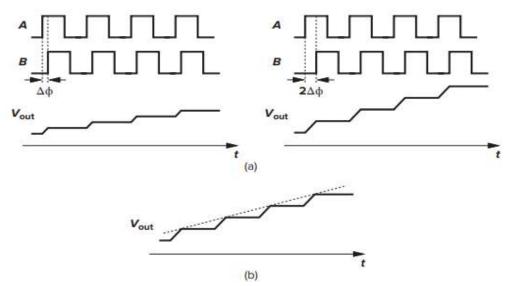

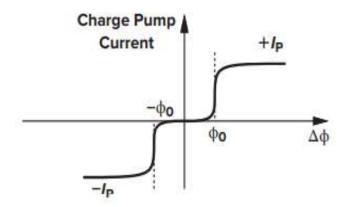

To estimate the behaviour of chage-punp PLLs, we generate a liner model that incorporates PFD, charge pump, and the low-pass filter, yielding the transfer function.

Fig 3.3:- PFD circuit along with charge pump and low pass filter

Question arise here is - Does the combined PFD+CP+LPF circuit shown in Fig 3.3 a linear system?

23

Fig 3.4:- (a) linearity test of the combine block (b) Response approximation

To put it in simple terms, we run the system through a linearity test. As shown in Fig 3.4, We have doubled the input phase shift and will see if Vout as well doubles. Surprisingly, Vout's flat sections get double but the ramp segment remains the same. This is because of the current charging or discharging capacitor  $C_P$  is stable, the ramp has a constant slope. As a consequence, the system is not strictly linear.

To solve this dilemma, we will be using a ramp to estimate the output waveform a ramp signal shown in Fig 3.4 (b), resulting in a direct interdependence between *Vout* and phase  $\boldsymbol{\Phi}$ .

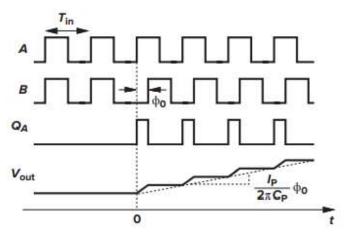

Fig 3.5:- Behaviour of PFD+CP+LPF combination under step input

Let's suppose the input period is Tin and the charge pump circuit delivers an  $\pm Ip$  current to the capacitor. As illustrated in Fig 3.5, we starts with a phase shift of zero radian and, at t = 0, the phase of step signal B by  $\Phi 0$ , i.e., =  $\Phi 0u$  (t). As a consequence, Q<sub>A</sub> or QB

continues to generate pulses of  $\Phi$ 0Tin/(2x  $\pi$ ) seconds width, raising the output voltage by (IP/CP) x  $\Phi$ 0Tin/(2 $\pi$ ) for each period.

Thus, *Vout(t)* can be expressed as

$$Vout(t) = (I_P/C_P) \times \Phi_0 Tin/(2\pi)$$

The impulse response is therefore given by:-

$$h(t) = \frac{lp}{2\pi Cp} u(t)$$

.....3.10

.....3.9

Yielding the transfer function,

$$\frac{Vout(s)}{\Delta \Phi} = \frac{Ip}{2\pi Cp} \cdot \frac{1}{S}$$

.....3.11

Consequently, the PFD/CP/LPF combination contains a pole at the origin, a point of contrast to the PD/LPF circuit used in the type-I PLL. In analogy with the expression  $K_{VCO}$  /s, we call I<sub>P</sub> /(2 $\pi$ C<sub>P</sub>) the "gain" of the PFD and denote it by K<sub>PFD</sub>.

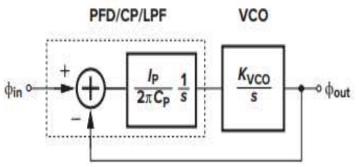

Fig 3.6:- Frequency domain modelling of charge pump PLL

Let's build a linear model of charge-pump PLLs now. The prototype, as shown in Fig 3.6, provides an open-loop transfer function.

$$\frac{\Phi out(s)}{\Phi in(s)} | open = \frac{Ip}{2\pi Cp} \cdot \frac{Kvco}{S^2}$$

....3.12

This topology is referred to as a "type II" PLL because the loop gain has two poles at the origin. The closed-loop transfer function, abbreviated H(s), is thus equal to

$$\frac{\Phi out(s)}{\Phi in(s)}|closed = \frac{\frac{Ip.Kvco}{2\pi Cp}}{S^2 + \frac{Ip.Kvco}{2\pi Cp}}$$

....3.13

This outcome is concerning reason being the closed-loop system has two non-real poles. at  $s_{1,2} = \pm j \sqrt[2]{Ip \text{ Kvco }/(2\pi\text{Cp})}$  and is therefore unstable.

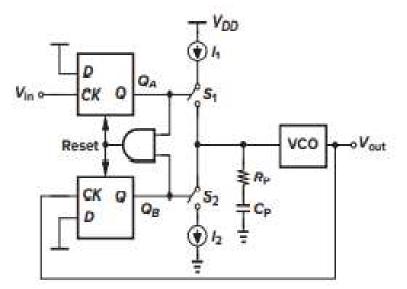

To improve the stability, we must modify the phase aspect such that the phase shift at the gain crossover is less than 180. This would be accomplished, as shown in Fig 3.7, by incorporating a zero in the loop function, i.e., by integrating a resistor in series with the loop filter's capacitor.

The combined PFD+CP+LPF circuit now has a transfer function,

$$\frac{Vout(s)}{\Delta \Phi} = \frac{Ip}{2\pi} \cdot (Rp + \frac{1}{SCp})$$

.....3.14

Open-loop transfer function for the PLL design is equal to,

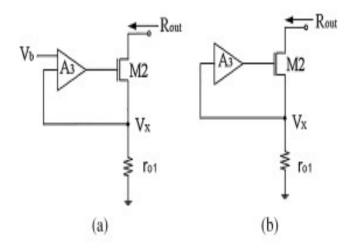

Fig 3.7:- Charge-pump PLL circuit with an added resistor for the zero addition

And hence,

$$F(s) = \frac{\Phi out(s)}{\Phi in(s)} | closed = \frac{\frac{Ip}{2\pi} \cdot \frac{Kvco}{Cp} (SCpRp + 1)}{S^2 + \frac{Ip}{2\pi} Kvco. RpS + \frac{Ip}{2\pi} \cdot \frac{Kvco}{Cp}}$$

....3.16

$$\omega n = \sqrt[2]{\frac{Ip}{2\pi} \cdot \frac{Kvco}{Cp}}$$

....3.17

$$\Sigma = \frac{Rp}{2} \sqrt{\frac{Ip}{2\pi}} Kvco. Cp$$

....3.18

If Rp = 0, then, as expected,  $\Sigma = 0$ . The decay time constant for complex poles is given by  $1/(\zeta \omega n) = 4\pi/(Rp \ Ip \ Kvco)$ .

If Rp = 0, then, as expected,  $\Sigma = 0$ . The decay time constant for complex poles is given by  $1/(\zeta \omega n) = 4\pi/(Rp \ Ip \ Kvco)$ .

Fig 3.7 shows a critical flaw in the compensated type-II PLL. When a current is injected into the loop filter, the control voltage jumps dramatically because the charge pump drives the series combination of Rp and Cp.Even when the circuit is locked, voltage jumps in Vcont are caused by the imbalance between  $I_1$  and  $I_2$ , as well as the charge injection and clock feed through of S1 and S2. The resulting ripple heavily perturbs the VCO, exacerbating the corrupted output phase.

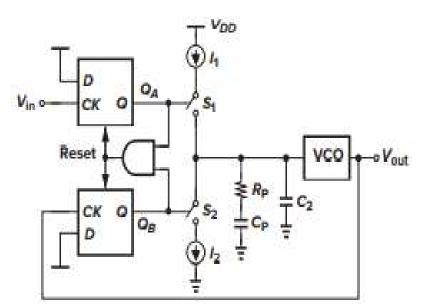

Fig 3.8:- Capacitor C2 is added to reduce ripple on the control line.

To tackle this question, a second capacitor is normally connected in parallel with Rp and Cp in Fig 3.8, curbing the initial step. The loop filter is now of second order, resulting in a third-order PLL and instability issues. Even if C2 is chose between one-fifth to one-tenth of Cp, the closed-loop time and frequency responses remain constant.

# **CHAPTER-4** Non-ideal Effects in PLL

### 4.1. PFD/CP Non-idealities

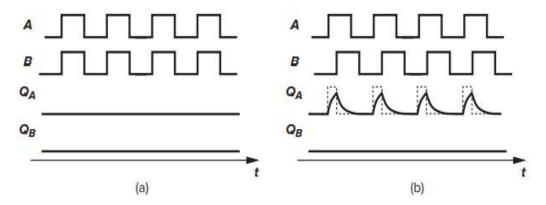

#### 4.1.1 <u>Reset Delay of PFD:-</u>

Even when the phase difference between the inputs is zero, the PFD implementation in Fig 1.5 generates narrow, coincident pulses on both QA and QB. As shown in Fig 4.1, if A and B start rising at the very same time, so do QA and QB, triggering the reset. That is, even when the PLL is locked, QA and QB turn on the charge pump synchronously for a predefined timeframe TP  $\approx$  5TD, where TD signifies the gate delay.

Fig.4.1- PFD-generated collinear pulses with zero phase shift.

What impact do the reset pulses have on QA and QB? Consider a purely theoretical Fig 4.2 (a) shows a PFD that creates no pulses for a zero input phase shift. What is the PFD's response to a small phase error? Fig 4.2(b) shows how the circuit generates very narrow pulses on QA or QB.

Nevertheless, due to the finite rise and fall times prompted by capacitance at these nodes, the pulse wouldn't have enough time to achieve a logical high level and thus will fail to turn on the charge pump switches. In other words, if the input phase shift exceeds the threshold value of, the output voltage of  $\Phi$ , the PFD/CP/LPF combination circuit is no longer a function of  $\Phi 0$ . Because the charge pump injects no current for  $|\Delta \Phi| < \Phi 0$ , as shown in Fig 4.3, the loop gain falls to zero as well as the output phase is not locked. The PFD/CP circuit appears to have a dead zone equal to  $\pm \Phi 0$  around  $\Delta \Phi = 0$ .

Nevertheless, due to the finite rise and fall times prompted by capacitance at these nodes, the pulse wouldn't have enough time to achieve a logical high level and thus will fail to turn on the charge pump switches. In other words, if the input phase shift exceeds the threshold value of, the output voltage of  $\Phi$ , the PFD/CP/LPF combination circuit is no longer a function of  $\Phi 0$ . Because the charge pump injects no current for  $|\Delta \Phi| < \Phi 0$ , as shown in Fig 4.3, the loop gain falls to zero as well as the output phase is not locked. The PFD/CP circuit appears to have a dead zone equal to  $\pm \Phi 0$  around  $\Delta \Phi = 0$ .

Fig 4.2:- (a) Zero input phase shift output wave (b) Output wave with minor phase shift in the input.

Fig 4.3:- Fig showing dead zone in the charge pump current

Astonishingly, concurrent pulses on QA and QB can totally eradicate the dead zone. This is because, for  $\Delta \Phi = 0$ , the pulses always power up the charge pump once they are sufficiently wide. As a result, as illustrated in Fig 4.4, even a slight rise in the phase shift causes an approximately equal increase in the net current of the charge pump. In other words, if TP lasts long enough for QA and QB to reach a logically valid level and turn on the charge pump switches, the dead zone disappears.

Fig 4.4:- Real Response of a Phase Detector to a small input phase shift.

Fig 4.5 (a) Charge pump implementation (b) Skew effects between  $Q_A$  and  $Q_B$

The first issue in the circuit shown in Fig 4.5 is caused by the delay between QA and QB in turning on their respective switches (a). The total current injected into the loop filter by the charge pump jumps between +Ip and Ip, causing the oscillator control voltage to rise or fall even though the loop is locked, as shown in Fig 4.5. (b).To counterbalance this effect, a complementary pass gate can also be placed between QB and the gate of M3, resulting in the delays shown in Fig 4.6 being compensated.

Fig 4.6:- Pass gate logic used to thwart skew.

It is worth noting:-

(1) The control voltage's periodic ripple continues.

(2) The terminal voltage affects the current mismatch.

(3) The phase shift & ripple are amplified by the clock feed through and charge injection mismatch between M3 and M4.

4.1.3. Charge sharing at the drain of the current sources

The third problem in the PFD circuit of is caused by the finite capacitance seen at the current source drains. As shown in Fig 4.7 (a), assume  $S_1$  and  $S_2$  both are turned off, allowing  $M_1$  to discharge X to ground and  $M_2$  to charge Y to VDD. If indeed the voltage drop across S1 and S2 is neglected, both S1 and S2 turn on at the next phase comparison moment,  $V_X$  rises,  $V_Y$  falls, and  $V_X \approx V_Y \approx$  V cont at the next phase comparison instant as shown in Fig 4.7 (b). Does V cont stay constant after the switches are turned on if the phase error is zero and  $ID_1 = |ID_2|$ ? Even if  $C_X$  equals  $C_Y$ , the change in  $V_X$  is not the same as the change in  $V_Y$ . The difference between the two changes must therefore be supplied by  $C_P$ , leading to a jump in V cont.

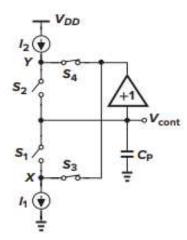

The aforementioned charge-sharing phenomenon can be suppressed by "bootstrapping." The idea, as shown in Fig 4.8, is to "pin"  $V_X$  and  $V_Y$  to Vcont once the phase correlation is complete. Once  $S_1$  and  $S_2$  are turned off,  $S_3$  and  $S_4$  are turned on, permitting the unity-gain amplifier to hold nodes X and Y at a potential equal to Vcont.

Fig 4.7 (a) Charge pump integration (b) Skew influence between QA and QB.

It really should be noted that the amplifier does not have to to provide a lot of current because  $I1\approx I2$ .

Fig 4.8:- X and Y are being bootstrapped to minimise charge sharing.

### 4.2 PLLs Jitter

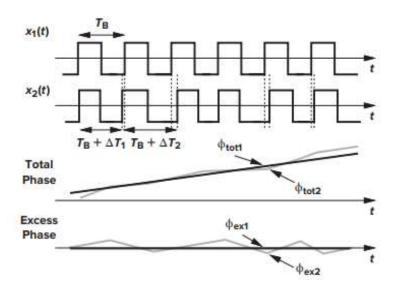

A strictly periodic wave function, x1(t), has crossovers that are equally separated in time, as shown in Fig 4.9. Consider the nearly periodic signal x2(t), the period of that which varies slightly, going to cause the zero crossings to differ from their ideal points. Jitter is a term used to describe the latter waveform. By plotting the overall phase,  $\Phi$ tot, excess phase,  $\Phi$ ex, we can see that jitter introduces itself as a randomness of the surplus phae with time.

Take a look at the jittery waveforms in Fig 4.10. Because its instantaneous frequency changes gradually through one period to another, the first signal, y1(t), showcases "slow jitter." y2, the second signal, has "fast jitter" (t). The excess phase plots of the two waveforms also show the rate of change.

Fig 4.9:- Ideal and jittery waveforms.

Fig 4.10:- Figure illustrating slow & fast jitter

There are two particularly interesting jitter phenomena in phase-locked loops namely:-

(1) Jitter in the input.

(2) Jitter produced by the VCO

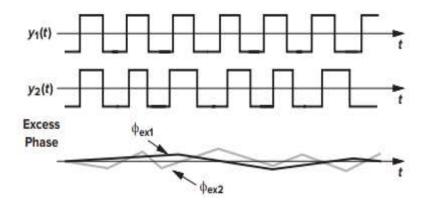

The obtained transfer functons for type-1 and type-2 PLLs have low-pass qualities, implying that if  $\Phi$ in(t) tends to vary quickly,  $\Phi$ out(t) somehow doesn't fully record the variations. In other words, slow jitter doesn't quite affect output but fast jitter does. PLL low-pass filters are known as  $\Phi$ in (t). Suppose that the input is purely periodic but the VCO does have jitter. We design the system shown in Fig 4.11, wherein the input

additional phase is reduced to 0 and an erratic part VCO is introduced to the VCO's output to depict its jitter.

Fig 4.11:- Effect of jitter because of VCO

Surprisingly, the defining feature is high-pass, denoting that the VCO's slow jitter constituents but not its fast jitter constituents are suppressed. If  $\Phi$ VCO (t) varies gradually (for example, drifts in oscillation with temperature), the similarity with  $\Phi$ in = 0 produces a time varying error, which proliferates the LPF and revises VCO's frequency to compensate for the transition in  $\Phi$ VCO (t). When VCO differs quickly (for example, when high-frequency noise modulates the oscillation period), the phase detector inaccuracy is hugely damped by the loop poles, and the transformation is not rectified.

## CHAPTER-5 Applications of PLL

After nearly a century of development, phase locking is still finding new applications in electronics, communication, and instrumentation. Memory, microprocessors, hard disc drive electronics, RF and wireless transceivers, and optical fibre receivers are some examples. In this chapter, we will see a variety of applications that exhibits phase locking versatility.

### 5.1. Frequency Multiplier and Synthesiser

### 5.1.1. Frequency Multiplier:-

The input frequency of a PLL can be multiplied by a M factor. Once we divide the generated frequncy signal of a PLL by Multiple (M) and apply it to a phase detector circuit, we get fout equals M times fin. In another context, because fD equals to fout/M and fD and fin must equal in the latched state, the PLL amplifies fin by M. The M circuit is designed as a counter, producing single pulse for each M input. The frequency-multiplying loop in Fig 5.1 has two attractive features. First, unlike the voltage amplifier, the PLL has a multiplication factor that is exactly identical to M, which is a unique property of phase locking Second, by varying the divide ratio M, the output frequency can be varied, which is a very useful property when synthesising frequencies.

Fig 5.1:- Block diagram to showing frequency multiplication using PLL and ÷M circuit

#### 5.1.2. Frequency Synthesiser:-

Some devices necessitate a periodic waveform with such a frequency that is (a) incredibly precise (e.g., below 10 ppm) and (b) variable in ultra delicate step (example, 30 kHz steps from 0.9 GHz to 0.925 GHz). PLL frequency multiplication can always meet these requirements, which are common in wireless transmitters and receivers.

The design of a phase-locked frequency synthesiser has been depicted in Fig 5.2. A digital word defining the value of M is used as the channel control input. Given that  $f_{out}$  equals to M times  $f_{REF}$ , the comparative accuracy of  $f_{out}$  is the same as that of  $f_{REF}$ . As a result,  $f_{REF}$  is obtained from a low-noise, stable crystal oscillator. If M shifts by one each time, fout varies in steps equal to  $f_{REF}$ .

Fig 5.2:- Block diagram to showing frequency synthesiser using PLL and +M circuit

### 5.2. Clock Skew Suppression

Phase locking was first used in digital systems to reduce skew. Suppose a synchronous set of clock and data paths reaches a huge digital chip, as illustrated in Fig 5.3. Because the clock is typically used to drive many tranistors and lengthy interconnects, it is first provided to a huge buffer. As a result, the clock distributed on the chip may exhibit significant skew, T, in relation to data, which is an unwanted effect as it minimises the timing closers for on-chip functions. The skew is eliminated because the PLL maintains a nominally zero phase shift between CKin and CKB. In another way, the feedback system's infinite loop gain is divided by the buffer's constant phase shift.

Fig 5.3:- Block diagram to showing use of PLL to eliminate clock skew

#### **5.3 Jitter Reduction**

At the input, PLLs inhibit fast jitter components. When a GHz signal along with the jitter is put as an input to a PLL with the bandwith of 1 MHz, jittery components of the input that vary faster than 1 MHz are suppressed. The phase-locked-loop, in some ways, functions as a narrowband filter with an overall bandwidth of 20 MHz, concentrated around 1 GHz. PLLs have yet another important and useful property.

The suggestion would be to use a D flip-flop guided by the clock to resample the halfway point of each bit, as shown in Fig 5.4. (a). However, the clock may not be available individually in many applications. Because an optical fibre, for example, only conveys an arbitrarily defined data stream, it lacks a distinct clock waveform at the receiver end. Fig 5.4 (b) depicts a circuit in which a "clock recovery circuit" generates the timming from data.. The circuit reduces the impact of input jitter on the retrieved clock by using phase locking with a pretty narrow loop bandwidth.

Fig 5.4:- Block diagram to showing (a) Retiming data with a D flip-flop steered by a low-noise clock; (b) creating the clock with a phase-locked clock recovery circuit.

# CHAPTER-6 Current Starved VCO

### 6.1. 7-Stage Current Starved Inverter Circuit based Ring Oscillator

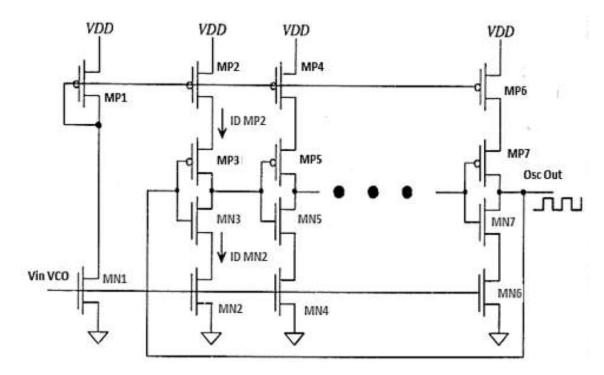

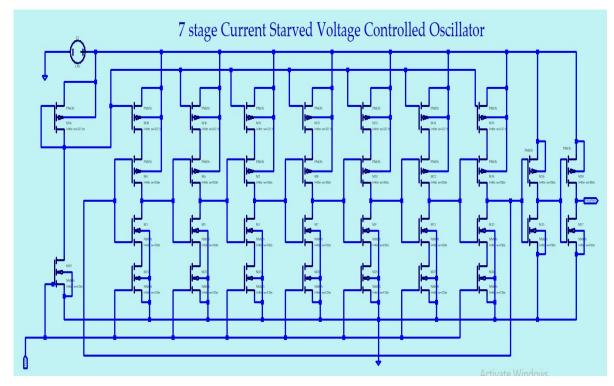

The supply voltage, VDD, of a ring oscillator circuit varies in real time, and the voltage imbalance causes an output frequency variation. As a result, current must be delivered to each inverter to make sure that the output frequency remains stable. This can be accomplished by using a current-starved inverter, as illustrated in Fig 6.1, which controls the amount of current used to charge and discharge the capacitive load at each stage. M1 and M2 act as current sources, limiting the current flowing through M3 and M4. M3 and M4 are inverters that are currently said to be current starved. The current of M5 and M6 is controlled by the input control voltage, and the values are mirrored in each inverter or current source voltage.

MOS MP1 and MN1 drain currents are identical and are controlled by the input control voltage. Currents in MOS MN1 and MP1 are reflected in every inverter. The frequency of the N stages CS-VCO oscillation is given by eq. (6.1), ID can be calculated using eq. (6.2), and thus the total drain capacitance of MOS MN3 and MP3 is fixed by eq. (6.3) Fig 6.2 depicts the control voltage versus output frequency of a three and seven stage current starved VCO.

$$Fosc = \frac{Id}{NCtotVdd}$$

.....6.1

$$Id = \frac{\beta}{2} (Vgs - Vth)^2$$

.....6.2

$$Ctot = Cox(WpLp + WnLn) + \frac{3}{2}Cox(WpLp + WnLn)$$

Fig 6.1:- Architecture of Current Starved VCO

Fig 6.2:- Implementation of 7-stage CSVCO using Ltspice at 90nm technology node

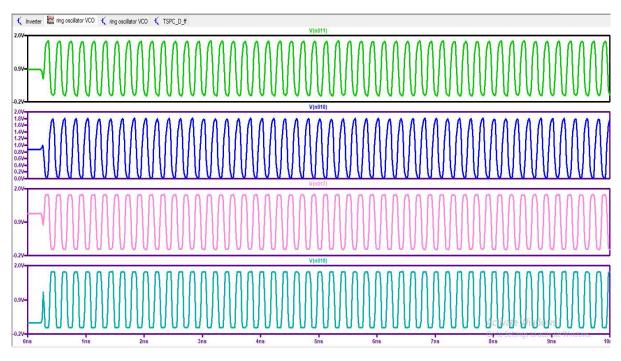

Fig 6.3: Fig showing the output wave form of the Oscillator at different inverter stages

Fig 6.4:- Fig showing the measurement of the oscillation frequency for Vctrl = 1.6 V using Ltspice

| Technology node                       | 90nm                                    |

|---------------------------------------|-----------------------------------------|

| Biasing Voltage                       | 1.8V                                    |

| Number of Current Starve stages       | 7                                       |

| Total Number of transistors used      | 30 + 4 (inverter used for wave shaping) |

| Variation in Vctrl                    | 0.4V - 3.6V                             |

| Frequency Range                       | 0.5771 – 5.4033 GHz                     |

| Centre Frequency                      | 3.5135GHz                               |

| Tuning Range                          | 1.3187                                  |

| Average Power Dissipation per cycle   | 142.29nW                                |

| Operation Frequency for linear output | 0.5771 - 5.0906 GHz                     |

| VCO gain                              | 23.633 rad/ns/V                         |

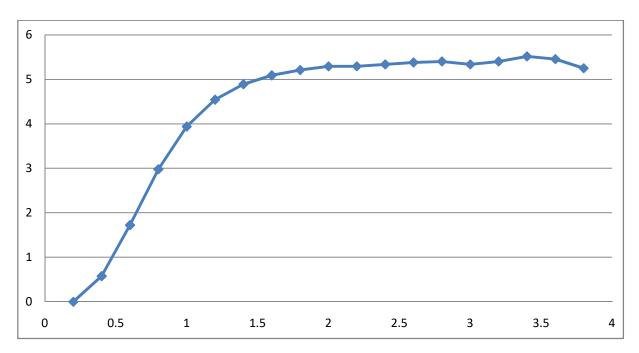

Table 6.1 – Specifications of the implemented CSVCO

Table 6.2: Vctrl vs. Fvco from the implemented CSVCO

| Vctrl(V) | Fvco(GHz) |  |  |  |  |

|----------|-----------|--|--|--|--|

| 0.2      | 0         |  |  |  |  |

| 0.4      | 0.5771    |  |  |  |  |

| 0.6      | 1.724     |  |  |  |  |

| 0.8      | 2.9795    |  |  |  |  |

| 0.9      | 3.5135    |  |  |  |  |

| 1        | 3.9398    |  |  |  |  |

| 1.2      | 4.5437    |  |  |  |  |

| 1.4      | 4.8919    |  |  |  |  |

| 1.6      | 5.0906    |  |  |  |  |

| 1.8      | 5.2103    |  |  |  |  |

| 2        | 5.2944    |  |  |  |  |

| 2.2      | 5.2944    |  |  |  |  |

| 2.4      | 5.3374    |  |  |  |  |

| 2.6      | 5.3812    |  |  |  |  |

| 2.8      | 5.4033    |  |  |  |  |

| 3        | 5.3374    |  |  |  |  |

| 3.2      | 5.4033    |  |  |  |  |

| 3.4      | 5.5168    |  |  |  |  |

Fig 6.5: Fig showing Fvco (GHz) plot with varying Vctrl (Volts) for 7-stage VCO

The Tuning Range graph is a voltage vs. frequency graph. It can be viewed as proportional region obtained by drawing a voltage and frequency plot. A mathematical formula can also be used to calculate it. –

*Tuning* Range = (*High* frequency – low frequency) / (*Central* frequency)

## 6.2. 5-Stage Current Starved Inverter Circuit based Ring Oscillator

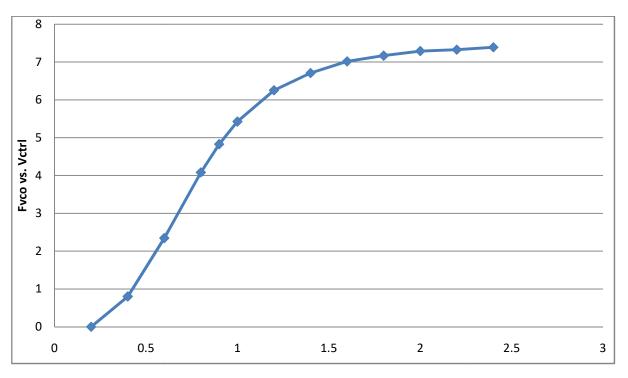

| Technology node                            | 90nm                                    |

|--------------------------------------------|-----------------------------------------|

| Biasing Voltage                            | 1.8V                                    |

| Number of Current Starve stages            | 5                                       |

| Total Number of transistors used           | 22 + 4 (inverter used for wave shaping) |

| Variation in Vctrl                         | 0.4V - 2.4V                             |

| Frequency Range                            | 0.8006 - 7.3886GHz                      |

| Centre Frequency                           | 4.8272 GHz                              |

| Tuning Range                               | 1.3187                                  |

| Average Power Dissipation per cycle        | 130.44 nW                               |

| Operational Frequency for linear operation | 2.3446 - 6.7076 GHz                     |

| VCO gain                                   | 34.2669 rad/ns/V                        |

## Table 6.3 – Specifications of the implemented CSVCO

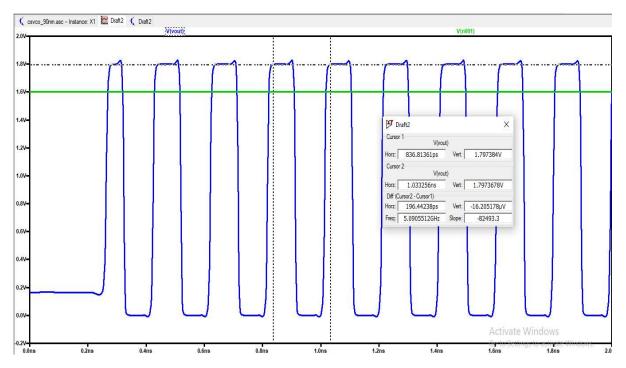

Table 6.4: Vctrl vs. Fvco from the implemented CSVCO

| Vctrl(V) | Fvco(GHz) |  |

|----------|-----------|--|

| 0.2      | 0         |  |

| 0.4      | 0.8006    |  |

| 0.6      | 2.3446    |  |

| 0.8      | 4.081     |  |

| 0.9      | 4.8272    |  |

| 1        | 5.4256    |  |

| 1.2      | 6.2524    |  |

| 1.4      | 6.7076    |  |

| 1.6      | 7.0159    |  |

| 1.8      | 7.1667    |  |

| 2        | 7.2889    |  |

| 2.2      | 7.3263    |  |

| 2.4      | 7.3886    |  |

Fig 6.6: Fig showing Fvco (GHz) plot with varying Vctrl (Volts) for 5-stage VCO

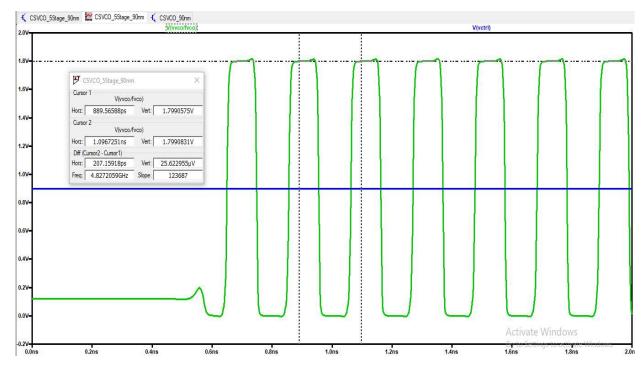

Fig 6.7: Fig showing the measurement of the oscillation frequency for Vctrl = 0.9 V using Ltspice for 5-stage VCO

**Conclusion**:- The CSVCO used here is a five-stage CSVCO. The linearity range of a three-stage CSVCO deteriorated, and the output frequency of operation was drastically reduced for a seven-stage VCO. As a result, a 5 stage VCO was used, which provided a good linearity range as well as a higher output frequency. To achieve optimal PLL performance, it is important to ensure that the output voltage range of the PFD CP-LPF block is within the dynamic linearity range of the VCO when designing the PLL.

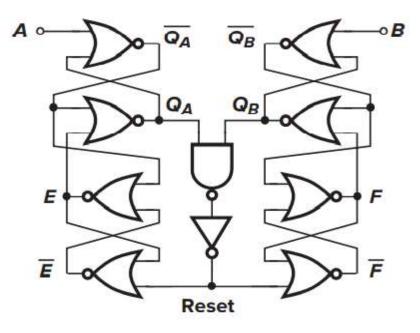

# **CHAPTER-7** Phase Frequency Detector

### 7.1. Gate Based Phase Frequency Detector