# Analysis of ASIC Design Flow by performing Design and Verification of ALU Block and Lint using Spyglass

A

Dissertation Submitted in the fulfilment of the requirements For the award of degree

# Of

MASTER OF TECHNOLOGY In VLSI Design and Embedded System

# By SHUBHAM GOYAL (2K19/VLS/18)

Under the Guidance of

# **Dr. SONAL SINGH**

## ELECTRONICS AND COMMUNICATION DEPARTMENT DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042 SESSION 2019-2021

# ELECTRONICS AND COMMUNICATION DEPARTMENT DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042 SESSION 2019-2021

# **CANDIDATE'S DECLARATION**

I hereby declare that the work being presented in this dissertation entitled "Analysis of ASIC Design Flow by performing Design and Verification of ALU Block and Lint using Spyglass" submitted towards the fulfilment of the Major project requirements for the award of degree, Master of Technology in VLSI Design and Embedded System to the Electronics and Communication Dept., Delhi Technological University, is an authentic record of my work carried out from January 2021 to June 2021, under the guidance of Dr. Sonal Singh, Electronics and Communication Dept., Delhi Technological University, Delhi Technol

I have not submitted the matter embodied in the dissertation for the award of any other degree.

Shulehamo

**Shubham Goyal** 2K19/VLS/18 Electronics and Communication Department

Date: 24<sup>th</sup> June, 2021

## ELECTRONICS AND COMMUNICATION DEPARTMENT DELHI TECHNOLOGICAL UNIVERSITY DELHI-110042 SESSION 2019-2021

# CERTIFICATE

This is to certify that the dissertation entitled "Analysis of ASIC Design Flow by performing Design and Verification of ALU Block and Lint using Spyglass" is the authentic record of work done by Shubham Goyal under my guidance and supervision. This dissertation is being submitted to the Delhi Technological University, Delhi towards the fulfilment of the requirements for the award of degree of Master of Technology in VLSI Design and Embedded System.

Dr. Sonal Singh SUPERVISOR Assistant Professor Electronics and Communication Department Delhi Technological University, Delhi

Date: 24<sup>th</sup> June, 2021

# ACKNOWLEDGEMENT

I would like to express my deep gratitude and appreciation to all the people who have helped and supported me in the process of dissertation. Without their help and support, 1 would not have been able to reach this level of satisfaction with what 1 have learnt and accomplished during my Master's dissertation. First and foremost, I would like to express my deep sense of respect and gratitude towards my supervisor Dr. Sonal Singh, Assistant Professor, Electronics and Communication Dept., DTU, for giving me opportunity to do my Major project of master's dissertation under her guidance. I am very thankful for her for giving me the opportunity to choose such an interesting topic by my own. I would also like to thanks the NPTEL Lectures for their valuable thoughts and knowledge, which motivated me to do better. Finally, none of this would have been possible without incredible support of my friends. They were always supporting me and encouraging me with their best wishes.

#### **Shubham Goyal**

Roll No. 2K19/VLS/18 Electronics and Communication Dept.

# ABSTRACT

We are living in the era of artificial intelligence where everything which we can imagine is in our hands with the help and emergence of the ongoing technology. There is a need for the semiconductor industries, as well, to make themselves comfortable with the growing pace of the world of technology. With the increase demand of the technologies and the evolution of the products, the big giants of semiconductor industries like Qualcomm, Intel, NXP Semiconductors and Western Digital are finding their way in a best appropriate manner to design the product which is user friendly.

There are various constraints which are implemented, which are imposed by these industries like functionality of the electronic device, power dissipation by the product, area occupied and also the reliability of the product. All these constraints, require some special attention and the measurements, which needs to be fulfilled by the design engineers, so that the reputation of the industry, and the competition in the products will be sustained.

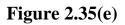

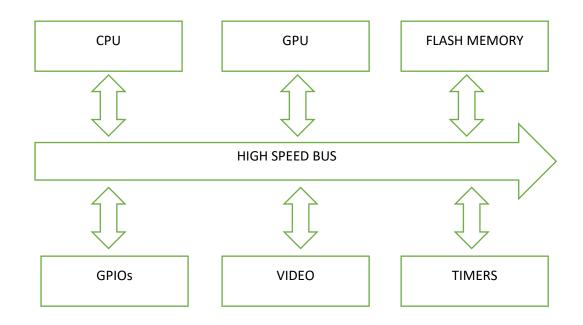

There are various steps, followed by every Semiconductor industry to make their products the best one. Some of the basic VLSI design flow steps are described in this thesis, and a special focus has been done on the frontend part of the design flow, which includes the designing of the RTL code, and then the Lint process, which generally verifies the syntax and the functionality of the coding so that it can be synthesized properly. And then, verification environment has been created with the help of system Verilog, so that the verification of the RTL code could be done, along with a brief introduction of UPF unified power format is also been studied in this thesis, so that the power aware estimations can be done, along with the functionality checks of the RTL design.

The last set of these thesis is a study of the clock domain crossing as clock is one of the crucial nets in the design of complex SOCs, and there are many clock domains running from one part of the SOC to another. So, there must be the proper data transfer between the two clock domains.

To understand the basic concept of design and verification of the SOC, the thesis contains one example of ALU, the design part of which is written in the Verilog language, it contains all the proper syntax of the language and the code

is synthesizable. And to verify the functionality of this, a new environment is created with the help of system Verilog which includes the concepts of objectoriented programming and functional coverage measures. After the verification part of the design process, lint is done to verify the functional checks on the RTL design so that it can be synthesized properly to the gate level netlist.

# TABLE OF CONTENT

| DECLARATION                 |                                                                                                                                                                             |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DECLARATION                 | i                                                                                                                                                                           |

| CERTIFICATE                 | ii                                                                                                                                                                          |

| ACKNOWLEDGEMENT             | iii                                                                                                                                                                         |

| ABSTRACT                    | iv                                                                                                                                                                          |

| LIST OF FIGURES             | vii                                                                                                                                                                         |

| LIST OF ABBREVIATIONS       | xi                                                                                                                                                                          |

| INTRODUCTION                | 1                                                                                                                                                                           |

| LITERATURE REVIEW           | 15                                                                                                                                                                          |

| 3 LINT, CDC AND UPF         |                                                                                                                                                                             |

| 4 RESULT AND DISCUSSION     |                                                                                                                                                                             |

| CONCLUSION AND FUTURE SCOPE | 67                                                                                                                                                                          |

| REFERENCES                  | 68                                                                                                                                                                          |

| APPENDIX                    | 70                                                                                                                                                                          |

|                             | ACKNOWLEDGEMENTABSTRACTABSTRACTLIST OF FIGURESLIST OF ABBREVIATIONSINTRODUCTIONLITERATURE REVIEWLINT, CDC AND UPFRESULT AND DISCUSSIONCONCLUSION AND FUTURE SCOPEREFERENCES |

# **LIST OF FIGURES**

| FIGURE NO. | TITLE                                           | PAGE NO. |

|------------|-------------------------------------------------|----------|

| 1.1        | Memory Specification Chart                      | 3        |

| 1.2        | NAND Controller Architecture                    | 4        |

| 1.3        | RTL of function and showing data flow           | 5        |

| 1.4        | Basic Architecture of the Testbench Environment | 5        |

| 1.5        | Conversion of RTL to Gate Level Netlist         | 6        |

| 1.6        | DFT Insertion                                   | 7        |

| 1.7        | Functional Verification of the logic            | 7        |

| 1.8        | Data path for Timing Analysis                   | 8        |

| 1.9        | Conversion of Netlist to Layout is PD           | 8        |

| 1.10       | Partitioning and Floor-Planning                 | 9        |

| 1.11       | Placement of the Blocks                         | 10       |

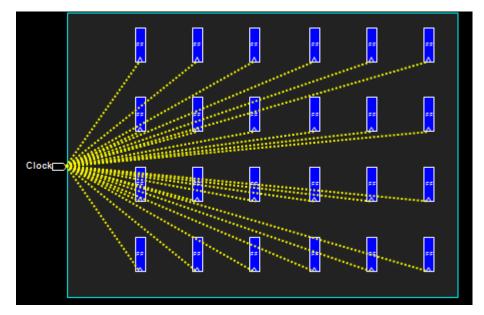

| 1.12       | Clock Nets connected to F/Fs                    | 11       |

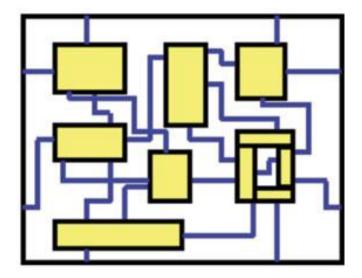

| 1.13       | Routing                                         | 11       |

| 1.14       | Design Rule Check and Layout Versus Schematic   | 12       |

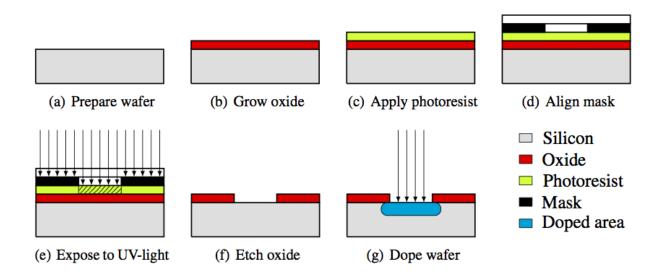

| 1.15       | CMOS Fabrication Process                        | 13       |

|                                      | <del>ر ا</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chip after Floor-planning            | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chip after Placement                 | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chip after Clock Tree Synthesis      | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chip after Clock Net Shielding       | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chip after Routing                   | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chip after Parasitic Extraction      | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Width and Height of the core         | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Effective area calculation           | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Finding the utilization factor       | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| interconnection of IPs               | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Black-Boxing the logic               | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Commonly used Macros                 | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

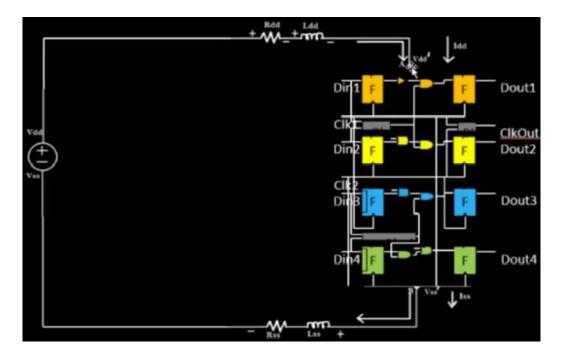

| Cells without Decoupling Capacitor   | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

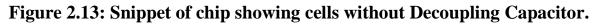

| Cells with Decoupling Capacitor      | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

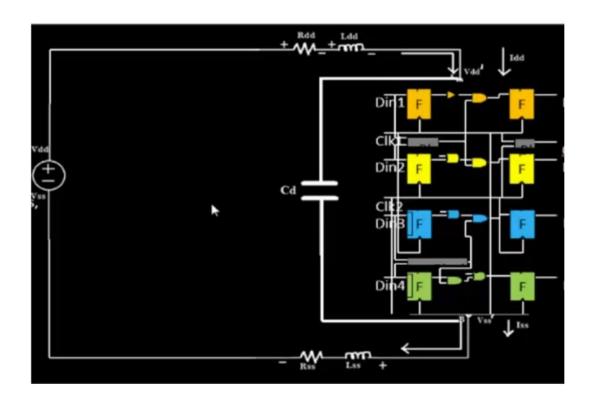

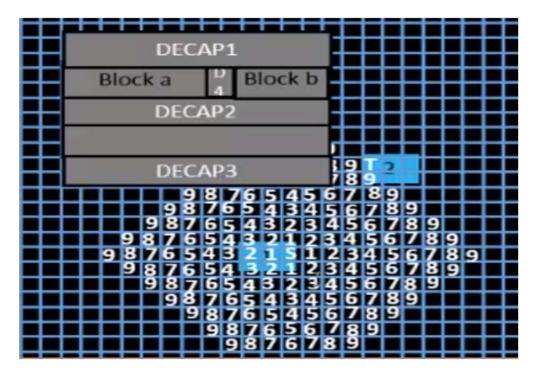

| Placement of Decoupling capacitances | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Power Planning                       | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Mesh arrangement of Power Rails      | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pin Placement                        | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

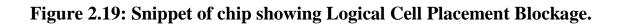

| Logical Cell Placement Blockage      | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Mapping of Library cells             | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Placement of Logical Cells           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                      | Chip after Clock Tree Synthesis<br>Chip after Clock Net Shielding<br>Chip after Routing<br>Chip after Parasitic Extraction<br>Width and Height of the core<br>Effective area calculation<br>Finding the utilization factor<br>interconnection of IPs<br>Black-Boxing the logic<br>Commonly used Macros<br>Cells without Decoupling Capacitor<br>Cells with Decoupling Capacitor<br>Placement of Decoupling capacitances<br>Power Planning<br>Mesh arrangement of Power Rails<br>Pin Placement<br>Logical Cell Placement Blockage<br>Mapping of Library cells |

| Optimised placement with inserting Buffers | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Setup time analysis for ideal clocks       | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Hold time analysis for ideal clocks        | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Clock available at CLK1                    | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Clock Tree Synthesis                       | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Clock path using H-tree                    | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Clock net shielding                        | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Setup time analysis for Real clocks        | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Hold time analysis for real clocks         | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

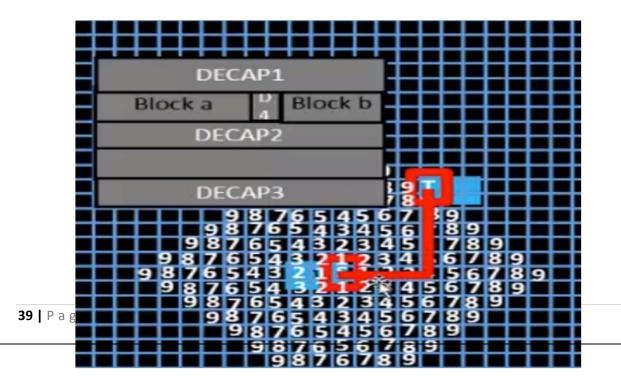

| Maze Algorithm for Routing                 | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Routing                                    | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Routing the data path                      | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

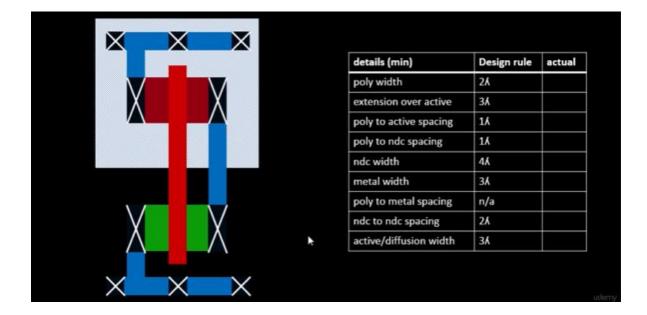

| Lambda rules                               | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Steps of Physical Design Flow              | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

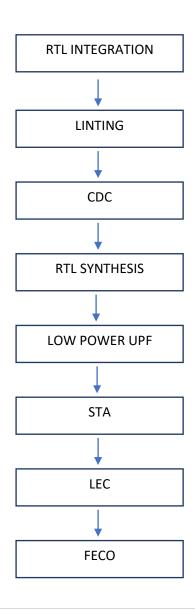

| Showing Synchronous Clocks                 | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

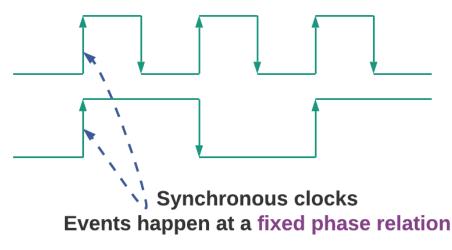

| Asynchronous clock                         | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

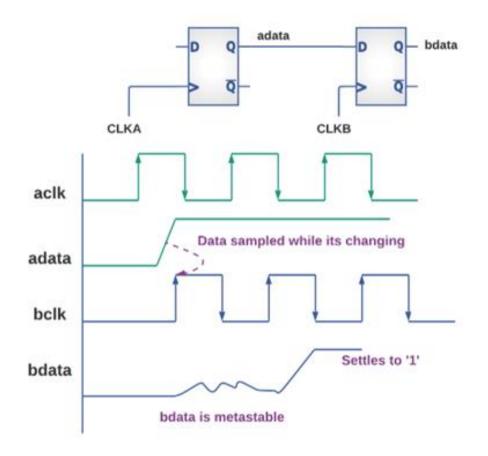

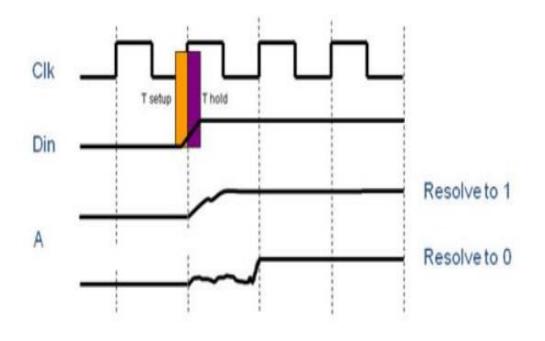

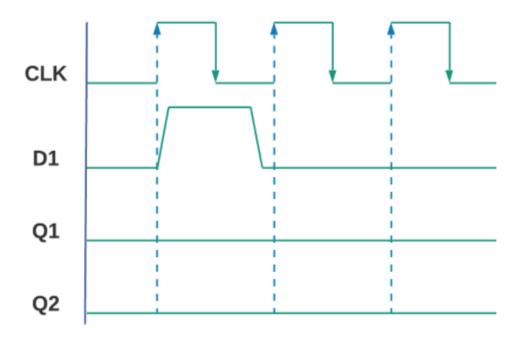

| Concept of Metastability                   | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

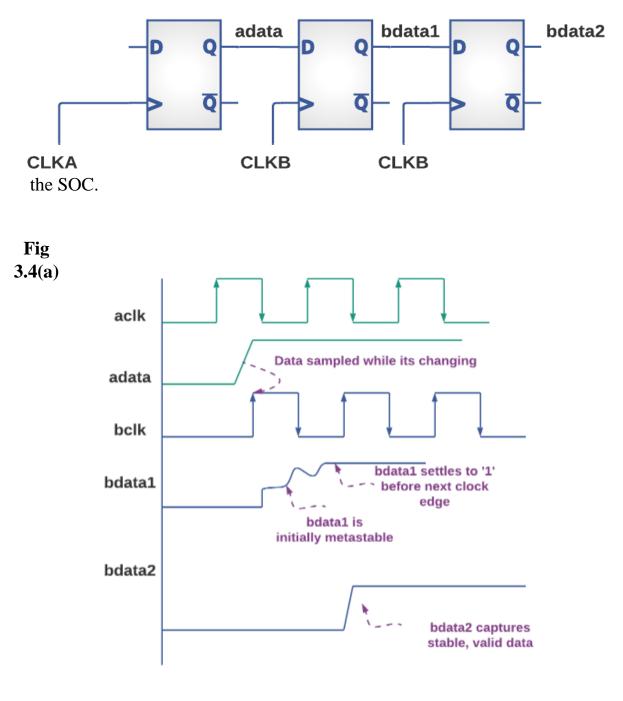

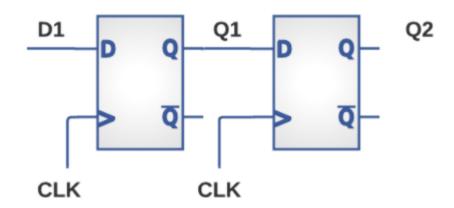

| Advantages of 2 F/F Synchronizers          | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

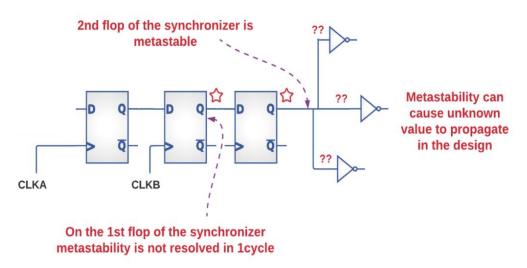

| Data Copying Problem due to Metastability  | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

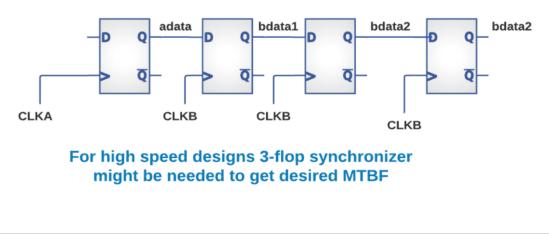

| 3 F/F Synchronizer                         | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.7 Explaining Effect of Metastability     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                            | Setup time analysis for ideal clocks         Hold time analysis for ideal clocks         Clock available at CLK1         Clock Tree Synthesis         Clock path using H-tree         Clock net shielding         Setup time analysis for Real clocks         Hold time analysis for real clocks         Hold time analysis for real clocks         Maze Algorithm for Routing         Routing         Routing the data path         Lambda rules         Steps of Physical Design Flow         Showing Synchronous Clocks         Asynchronous clock         Concept of Metastability         Advantages of 2 F/F Synchronizers         Data Copying Problem due to Metastability |

| 2.0  | Matastability on Dulsa dalay                                               | 51 |

|------|----------------------------------------------------------------------------|----|

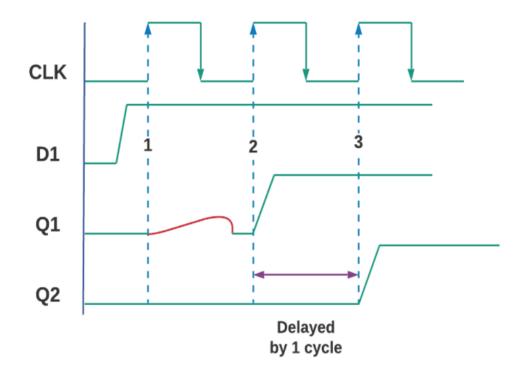

| 3.8  | Metastability on Pulse delay                                               | 51 |

| 3.9  | Metastability on Pulse Missed                                              | 52 |

| 3.10 | Metastability on Glitch Captured                                           | 52 |

| 4.1  | Spyglass error W18                                                         | 55 |

| 4.2  | Spyglass error W19                                                         | 55 |

| 4.3  | Spyglass error W69                                                         | 56 |

| 4.4  | Spyglass error W111                                                        | 57 |

| 4.5  | Spyglass error W123                                                        | 57 |

| 4.6  | Spyglass error W336                                                        | 58 |

| 4.7  | Spyglass error W391                                                        | 59 |

| 4.8  | Spyglass error W392                                                        | 59 |

| 4.9  | Spyglass error W414                                                        | 60 |

| 4.10 | Spyglass error W448                                                        | 60 |

| 4.11 | Error information in Spyglass                                              | 61 |

| 4.12 | Report generation in Spyglass                                              | 61 |

| 4.13 | Error reduction in Spyglass                                                | 62 |

| 4.14 | Functional Coverage in QuastaSim with 25 test<br>cases                     | 62 |

| 4.15 | Functional Coverage in QuastaSim with 25 test cases for particular inputs. | 63 |

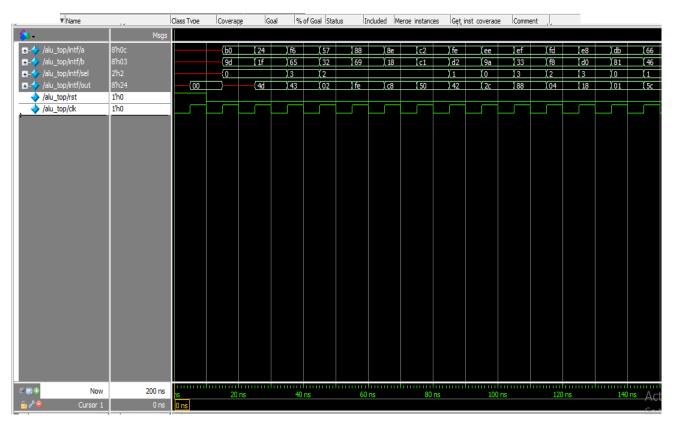

| 4.16 | Waveform showing of the functionality of ALU with 25 testcases.            | 64 |

| 4.17 | Functional coverage of ALU with 50 testcases.                              | 64 |

| 4.18 | Functional coverage of ALU with 150 testcases.                              | 65 |

|------|-----------------------------------------------------------------------------|----|

| 4.19 | Functional coverage of ALU with 250 testcases.                              | 65 |

| 4.20 | Functional Coverage in QuastaSim with 250 test cases for particular inputs. | 66 |

# LIST OF ABBREVIATIONS

| RTL   | Register transfer level                 |  |

|-------|-----------------------------------------|--|

| VLSI  | Vert Large Scale Integration            |  |

| GDSII | Graphic design system                   |  |

| ASIC  | Application specific integrated circuit |  |

| GPU   | Graphical processing unit               |  |

| SOC   | System on chip                          |  |

| FPGA  | Field programmable gate array           |  |

| HDL   | Hardware description language           |  |

| DFT   | Design for testability                  |  |

| STA   | Static timing analysis                  |  |

| CTS   | Clock tree synthesis                    |  |

| UF    | Utilization factor                      |  |

| PnR   | Placement and Routing                   |  |

| DRC   | Design rule checks                      |  |

| IP    | Intellectual property                   |  |

| IC   | Integrated circuit           |

|------|------------------------------|

| EDA  | Electronic design automation |

| CLK  | Clock                        |

| DUT  | Design Under Test            |

| DUV  | Design Under Verification    |

| CDC  | Clock Domain Crossing        |

| UPF  | Unified Power Format         |

| ALU  | Arithmetic and Logical Unit  |

| MTBF | Mean Time Before Failure     |

| F/Fs | Flip Flop                    |

| Ι/Ο  | Input or Output              |

| SDs  | Standard Devices             |

| PD   | Physical Design              |

# Chapter 1

# **INTRODUCTION**

## **1.1 VLSI DESIGN FLOW**

With the increase of the semiconductor industry and with the emergence of the VLSI, there is a lot of contribution of the big giants like Intel, Qualcomm, Western digital to produce millions of chips within a small amount of time. And the experience we are getting to the evolution of these Products and the IPs impact the world of artificial intelligence up to great extent.

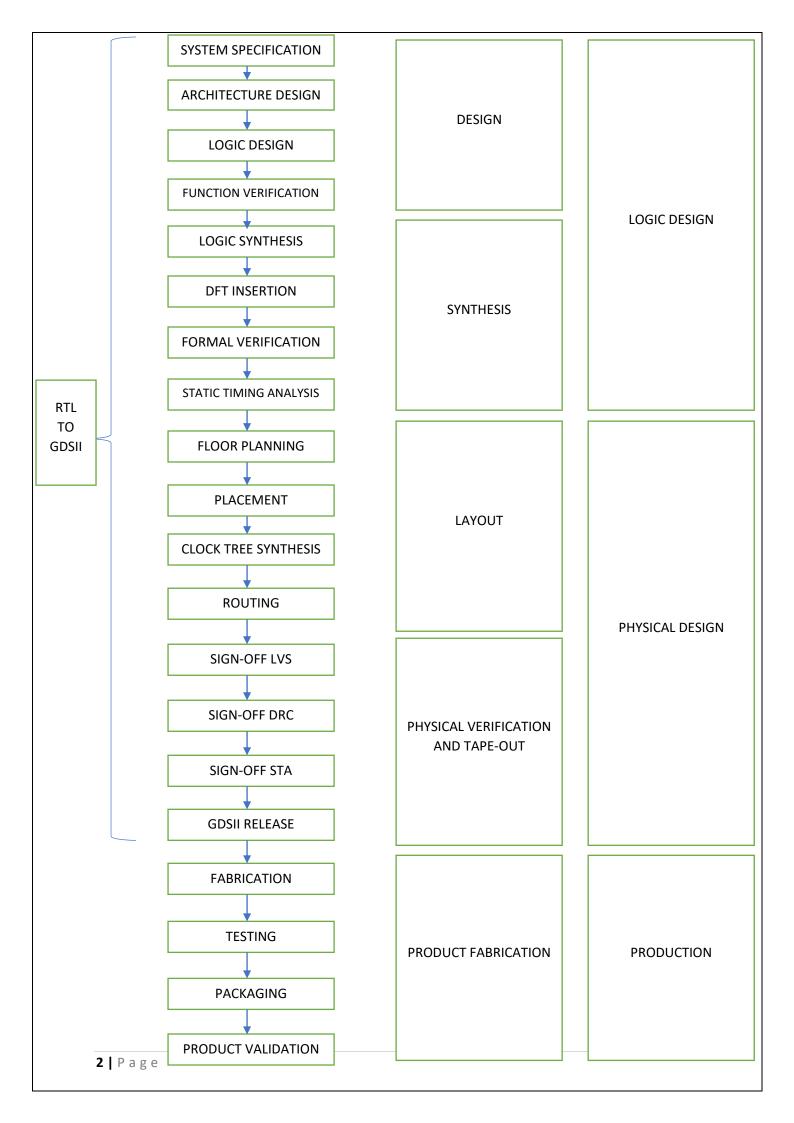

The ongoing process of making the chips by the semiconductor industries requires the particular flow for the correct functioning of the chip and the good yield which further leads to the marketing strategy of the big giants like Western Digital, Qualcomm, Intel and many more. The VLSI Design Flow is depicted below which is followed by almost all the industries in the world to make their products a better one.

Here in this session, the VLSI design flow is explained thoroughly so that a brief idea could get, how the industry follows the basic steps from the design specification, up to the final silicon, which we are using in our PCs, in our mobile phones and in our day to day life.

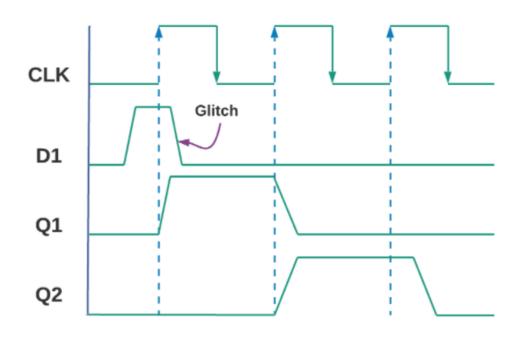

There are many steps, which mainly include the front end of the VLSI design flow and the backend design flow and also the packaging part. Each industry has its different names given to be intermediate steps but generally, the major ones are as follows. There is a difference between the ASIC design flow and FPGA design flow.

The front end of the basic design for an FPGA design flow is common for the ASIC as well. It has input as the design specification and goes to the gate level netlist, which is nothing but the synthesizable RTL code. The difference between the ASIC and FPGA design flow comes in the backend part, as in FPGA we already have the hardware, so we don't need the floor planning and placement steps of the physical design. These steps have been eliminated in the FPGA part since FPGA design flow basically eliminates, and we don't get the entire flow of the backend part. So here, the VLSI design flow is basically depicted in terms of the ASIC design flow.

#### **1.1.1 LOGIC DESIGN**

Starting with the first part of the ASIC design flow is the logical design. This is also known as the front end of VLSI, where we have the specifications of the product which we needed for the designing part. Then we had the architectural design, logical design, functional verification, logical synthesis, DFT, formal verification and static timing analysis and this is basically what the logical design do. The input of the logical design part of the ASIC Design Flow is the specifications provided by the marketing team, or by the directors and the managers of the industry, which are having their look to the ongoing production which they have launched in the market, till the gate level netlist which can be synthesizable and which should be given as an input to the physical design engineers of the ASIC design flow.

### **1.1.2 SYSTEM SPECIFICATION**

Starting with the VLSI Design Flow, the first step is a system specification. System Specification basically includes all the things which industry have as the ongoing customer demand, which the marketing team have analyzed in the market phenomena. It contains all the specifications of the blocks which the organization wants to design in terms of functionality, speed, power and area, or whether in terms of the research done by the marketing team. The one such kind of specification is shown in Figure 1.1.

| edd tsop            | SD - up to<br>UHS50 | SD UHS104                                         | SD-UHS-II                                                                                           | SD-UHS-III                                                                                          | SD Express                                                               |

|---------------------|---------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| SD - up to<br>UHS50 | Up to<br>50MB/s     | Up to 50MB/s                                      | Up to 50MB/s<br>(basic SD interface)                                                                | Up to <b>50MB</b> /s (basic SD interface)                                                           | Up to 50MB/s<br>(basic SD interface)                                     |

| SD - UHS104         | Up to<br>50MB/s     | Up to 104MB/s                                     | Up to <b>104MB/s</b><br>(basic SD interface and if<br>host supports it)                             | Up to 104 <b>MB</b> /s<br>(basic SD interface and if<br>host supports it)                           | Up to <b>104MB</b> /s<br>(basic SD interface<br>and if host supports it) |

| SD-UHS-II           | Up to<br>50MB/s     | Up to <b>104MB/s</b><br>(if supported<br>by card) | Up to 156MB/s<br>(Full Duplex)<br>Up to 312MB/s<br>(Half Duplex)                                    | Up to <b>156MB/s</b><br>(Full Duplex)<br>Up to <b>312MB/s</b><br>(Half Duplex if supported by host) | Up to 104MB/s<br>(basic SD interface<br>and if host supports it)         |

| SD-UHS-III          | Up to<br>50MB/s     | Up to 104MB/s<br>(if supported<br>by card)        | Up to <b>156MB/s</b><br>(Full Duplex)<br>Up to <b>312MB/s</b><br>(Half Duplex if supported by card) | Up to 624MB/s<br>(Full Duplex)                                                                      | Up to <b>104MB/s</b><br>(basic SD interface<br>and if host supports it)  |

| SD Express          | Up to<br>50MB/s     | Up to <b>104MB/s</b><br>(if supported<br>by card) | Up to 104MB/s<br>(basic SD interface and if<br>host and card support it)                            | Up to <b>104MB</b> /s<br>(basic SD interface and if<br>host and card support it)                    | Up to 985MB/s<br>(PCIe Interface)                                        |

**Fig 1.1: Memory Specification Chart**

### **1.1.3 ARCHITECTURE DESIGN**

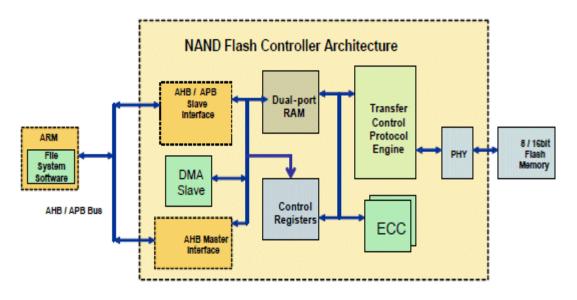

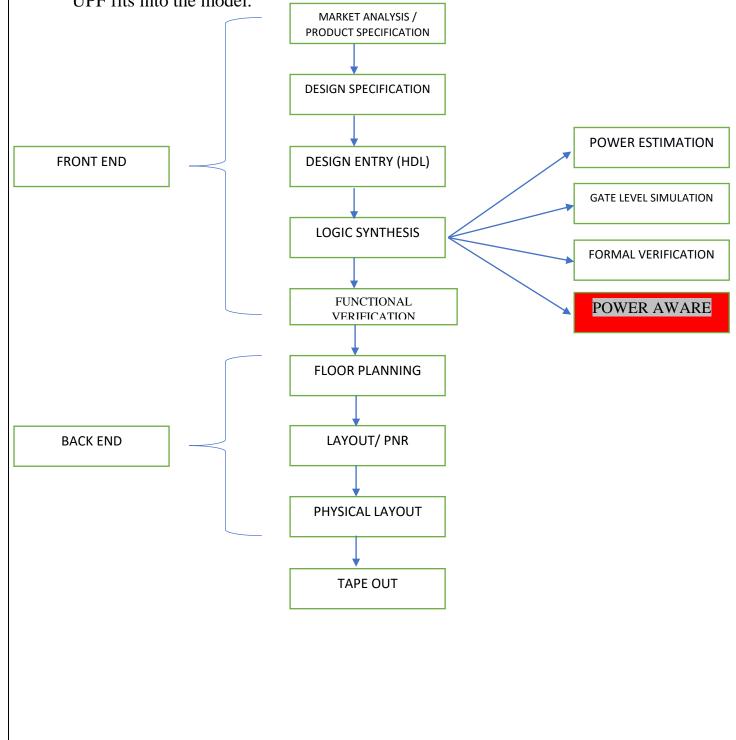

Next step after the design and Market Specification is Architecture Design. Now in architecture design the organization generally have the broad idea of the architecture or the higher level of abstraction where engineers know all the components and all the SOCs needed to be integrated for the designing part. One SOC contains millions of IPs and the interconnections between them so it's the part of the high level of engineers to implement such an architecture like for example, some SoC then it's a part of the architectural design, which designers have to implement this, either by using the ripple carry adder or by the carry Look ahead adder or skip carry adder or many other topologies. This is the type of architecture design the industry generally have. Figure 1.2 shows one such type of Architecture of the NAND Memory.

Fig 1.2: NAND Controller Architecture.

### **1.1.4 LOGIC DESIGN**

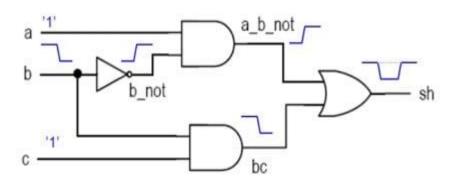

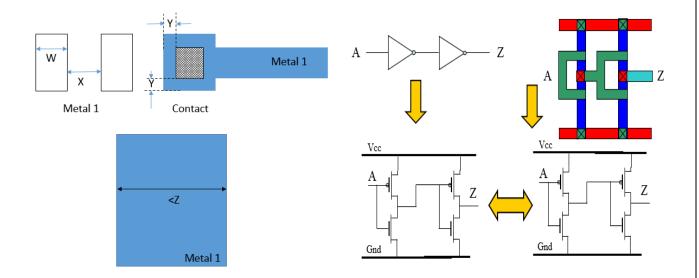

The next step after the architectural design is the logical design, where designers are actually designing the logic of the Product based on the specification. For all the specification and for all the product, designer want to design for the requirement of the industry logic design, like for example if the requirement is to design the and gate then, let's suppose there is a four input NAND gate using two input AND gate. Then there are two ways to design it, the logic one is this and the logic, two is shown in the figure. The design can be implemented with the help of HDLs (Hardware Descriptive Language), as shown in Figure 1.3.

Fig 1.3: RTL of function and showing data flow.

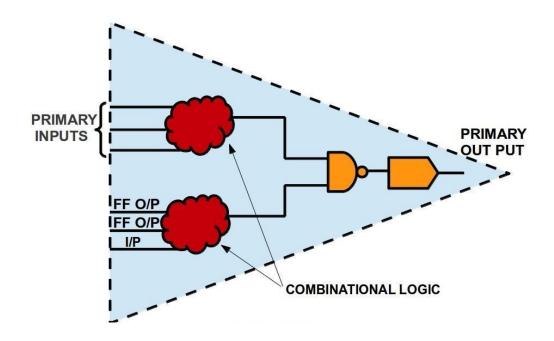

#### **1.1.5 FUNCTIONAL VERIFICATION**

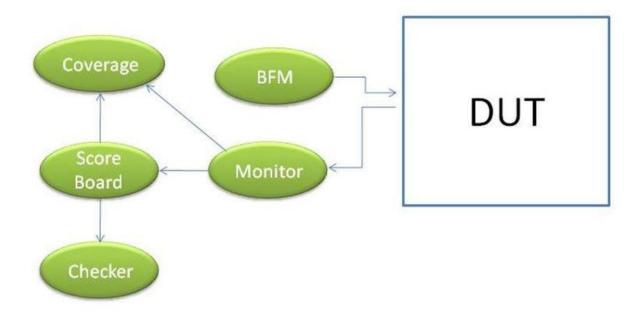

After that we'll go for the functional verification. Functional verification is the major step for defining the yield of the VSI design flow as to check the functionality of the logic design which we have implemented so that in the later part of this flow, the industry can get the correct yield, and the correct output so that we should not go to the entire flow process which is time consuming and expensive as well. This can be done with the help of high-level verification environment made with the help of system Verilog and UVM (Universal Verification Methodologies). The components of Environment are shown in the Figure 1.4.

Fig 1.4: Showing the Basic Architecture of the Testbench Environment.

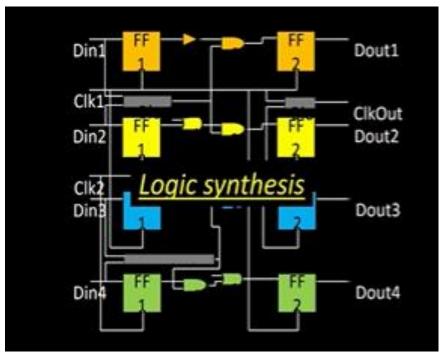

#### **1.1.6 LOGIC SYNTHESIS**

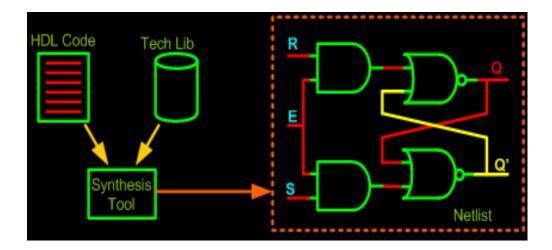

After the verification. After the functional verification of the above design which we have implemented using these specifications given by the marketing team or by the customers, we want to design it for the hardware purpose so the next step comes is the logical synthesis. Synthesis is basically the step where we need to convert the RTL into the gate level netlist, so that it can be synthesizable. And it can be implemented in the actual hardware. This step, eliminates all the unwanted and unnecessary coding styles which we have made by mistake in RTL Design part while writing the Verilog and System Verilog code, it contains the elimination of unwanted Latches, width mismatch, unintentional loops, and many other errors. So, this part is basically the actual synthesis part of this design process where we are getting the Actual Hardware, as shown in Figure 1.5.

Fig 1.5: Conversion of RTL to Gate Level Netlist

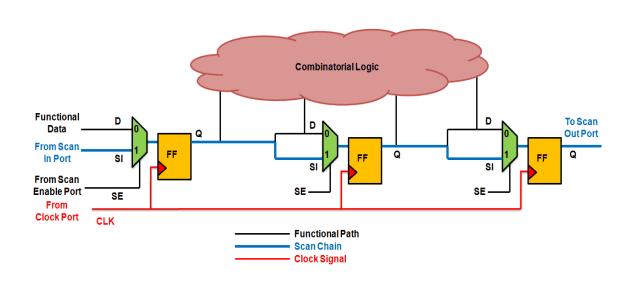

### **1.1.7 DFT INSERTION**

After the synthesis, where we get the gate level netlist of the design, we move to the DFT insertion In this step we are just inserting the DFT that is design for testability block into the design, so that the block can test itself in the simulation flow, and it will create test vectors for functional analysis, we have random generator block, which will create error patters and test patterns to test the circuitry of design which we have implemented so that it can be verified properly. The Scan and MBIST topologies are shown in Figure 1.6.

Fig 1.6: Showing the DFT Insertion.

### **1.1.8 FORMAL VERIFICATION**

After the insertion DFT insertion, next is the formal verification, where the tool verifies the logic and the DFT part which it has implemented, and verify all the things in a broad aspect. The concept of emulation is used by the verification engineers where, the bits patterns are given to the DUT in terms of C Codes and the log file is maintained for all the mis-matches based on the golden response. The following image is shown below for the formal verification.

**Fig 1.7: Showing the Functional Verification of the logic.**

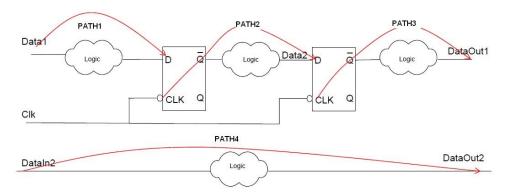

#### **1.1.9 STATIC TIMING ANALYSIS**

After the formal verification done by the verification engineers, next is to move to the static timing analysis. The analysis done till now is for the functionality of the design. Now it comes to the timing part of the design, where industries are using static timing analysis, static timing analysis is also the timing analysis, which contains many constraints and many parameters like setup constraints, hold constraints, clock frequency, skew rate, effect of jitter on the timing, effect of delta delay on the timing. There are many questions in a static timing analysis where STA engineer checks all the parameters, and then verify, and then rolls the ball to the layout team. So here ends the logical design of the ASIC design flow, which is generally refers to the FRONT END of ASIC design Flow.

Fig 1.8: Showing Data path for Timing Analysis

#### **1.1.10 PHYSICAL DESIGN FLOW**

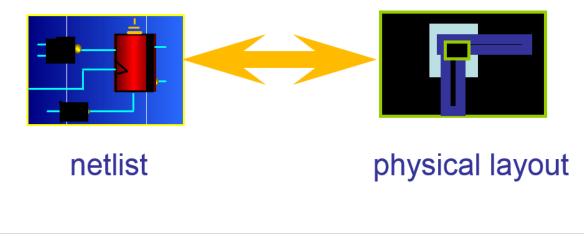

After completing the logical design of the ASIC design flow, we move to the physical design. Physical design is the other angle of the flow where we have the gate level netlist generated by the step of synthesis, and then we move to the layout part. There are various steps which include from floor planning to the Layout part, which comes under the physical design.

#### Fig 1.9: Conversion of Netlist to Layout is PD

#### **1.1.11 PARTITIONING AND FLOOR PLANNING**

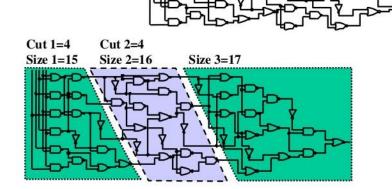

This is the first step of the Physical Design where the big SoC is divided into small sub groups and generally this step is referred to as Partitioning which is based on some constraints like interfaces must be minimum, each partition much get almost equal amount to gates and complexity. After that, the next step is Floor-planning. Like for example, when we make the house we have the blueprint of the house we have the bathrooms, we have the location of the kitchen, all the blueprints which we have for the house similar Blueprint we have for the chip as well, where we have the location of the pre-placement cells, where we have the pin placement, power planning Input size: 48 and

information.

other

#### Fig 1.10 (b)

# Fig 1.10 (a) Showing the Partitioning (b) Showing the Floor-Planning 1.1.12 PLACEMENT

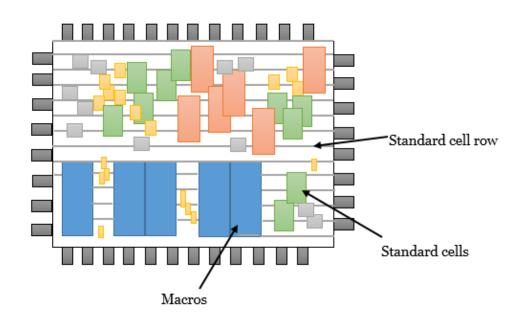

After the Floor-planning, we have the placement of the logical blocks, how they are placed on the basis of the flow of the data. So, there are many constraints of the placements like whether we have to include buffers in the parts, whether we have to replace IOs, technology cells, S/Ds, IPs. So, in this step we roughly placed all these cells, and we just measure the locations inside the core.

As mentioned in the floor-planning step, we generally measured the width and the height of the core, and in the placement, we take the blocks of the cells from the libraries, and we just fit it inside the core so that it can be placed according.

#### Fig 1.11 Placement of the Blocks

#### **1.1.13 CLOCK TREE SYNTHESIS**

After the placement is done, the most important step is to fix the clock nets, as we know that clock is a major source of concern in the field of VLSI, it is the most switching signal, and the product efficiency depends majorly on the clock frequency. It decides the overall frequency of this system. So, this step includes the synthesis of the clock tree, what are the measures which are taken for the implementing clock in this circuit, it contains many constraints like we have to check the pulse width of the clock, pulse duration, we have to check skew, we have to check slew rate, we have to check the latency. So, these things are covered in the clock the synthesis part.

Fig 1.12 Showing the Clock Nets connected to F/Fs

#### 1.1.14 ROUTING

The next part after synthesizing the clock, we generally synthesize the data paths, since we have just placed the cells we haven't connected, or we haven't routed it yet. So now in the routing part we can only connect the data path in an efficient manner. So here we generally use the algorithms of the shortest path, of which we generally covered in the data structure subject.

Fig 1.13 Showing the Net connection between the Blocks.

# 1.1.15 SIGN-OFF DRC, LVS, STA

After the routing part we have the sign-off things, Layout v/s Schematic, DRC and STA. These are the three tasks, we complete with the help of tool so that it measures all the timing requirements of the product, of the placement and clock tree synthesis and the routing which we have developed. If there is any error or if there any mismatch in the timing, which we found in these checks, then we'll go above the flow and we'll do the changes in the placement, in the clock tree and in the routing part, we generally avoid changes in the clock path as the clock net is the most critical net and we have to take care of it, so we generally change in the data path that is in Routing.

#### Fig 1.14: Showing the Design Rule Check and Layout Versus Schematic

#### **1.1.16 PRODUCTION**

After the functional checks which we have done, like Layout versus schematic, DRC checks and STA checks, we are ready for our GDSII log file which we have the information of all the layout kind of thing that is layout and systematic, which is the input to the foundry. So, many VLSI industries have their foundries, which take the GDSII file from the engineers from the software patch, and they do the necessary steps of lithography and etching so that they can fabricate the Silicon chips.

The next step is to fabricate the chip based on the GDSII and the machines present in foundry. Now, after the fabrication of the chips, there are many chips inside. Inside the silicon wafers which are not functionality correct, which should be checked so that so to maintain the functionality of the products which we have implemented, so the next step is Testing. This is the post Silicon testing. In the above verification part, we have used pre-silicon testing where we have tested we have verified through simulation. Now this is we are verifying with the help of hardware we have in the hands. We have many test vectors, we generally use C codes and the Python codes for testing. We verified these results with the golden results and verify the functional coverage. After the testing, the product which we are desired, is allowed to done with validation part, where we do the last function checks of the product which we have created.

In this way the entire basic flow goes from the specification to the product validation, which includes several steps and there are many intermediate steps between these major steps, so the necessary parts are covered in the following sections.

# Fig 1.15: Showing the CMOS Fabrication Process

# **1.2 OBJECTIVES**

The main objectives of this thesis are as follows:

- To understand the ASIC design Flow in great extent by analysing its various stages from Design Specification till the Production of the Product.

- To understand the various stages in the Physical Design Flow.

- The functional checks in the Verilog like: Lint, Clock Domain Crossing and UPF.

- To Design and Verify the ALU with the help of Quartus Prime and calculate its functional coverage.

### **1.3 THESIS ORGANIZATION**

The Thesis is organized in 5 chapters which are as follows:

- **Chapter 1** introduces the overall aspect of the ASIC Design Flow, which starts with the specification till the Production of the product. And the objective of the thesis which is showing the motivation while taking this title.

- **Chapter 2** helps in understanding the Physical Design Flow in detail, which includes the Floor-Planning step and then the placement and Routing till the Sign-off STA.

- **Chapter 3** includes 3 major steps of Linting, Clock Domain Crossing and UPF. These are the functional checks which helps in the synthesis of the gate level netlist from the Verilog code.

- **Chapter 4** shows the results which includes the ALU Design and Verification of ALU depending on the code coverage. And the various cases in the Lint using Spyglass which helps in understanding the Functional Checks easily.

- **Chapter 5** results in the conclusion and the future scope of the thesis and also what can be done next and the improvement in the design flow which helps in the industry to improvise.

# Chapter 2

# LITERATURE REVIEW

### **2.1 INTRODUCTION**

As discussed earlier in the first chapter that the VLSI design flow comprises of the physical design flow. Here is a quick overview of the physical design flow, where the input is the gate level netlist, and we have to design till the GDSII which contains the layout files of the gates for all the SOCs or the IPs which are needed to be implemented. There are many steps in the physical design flow, which contains many further steps depending on the topologies used by the particular industry.

The physical design steps comprise of:

- 1) Floor Planning

- 2) Placement and Optimize Placement

- 3) Clock Tree Synthesis

- 4) Clock Shielding

- 5) Routing

- 6) DRC check.

- 7) Parasitic Extraction

# 2.2 OVERVIEW OF PHYSICAL DESIGN FLOW

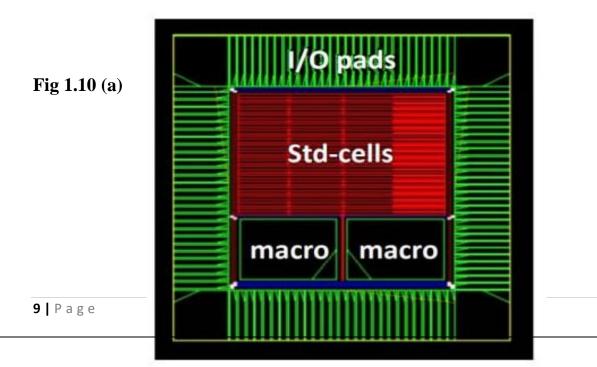

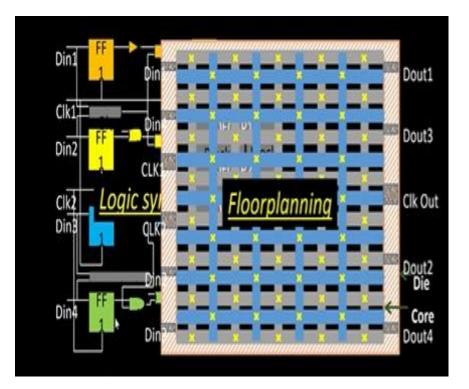

### **2.2.1 Floor Planning**

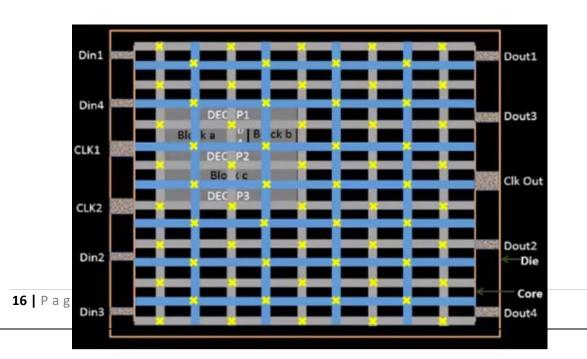

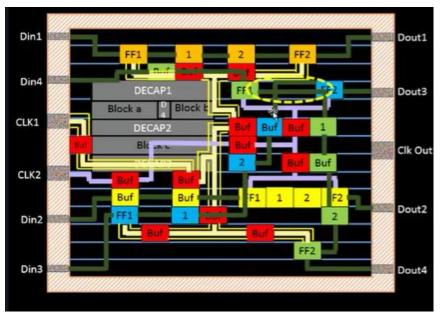

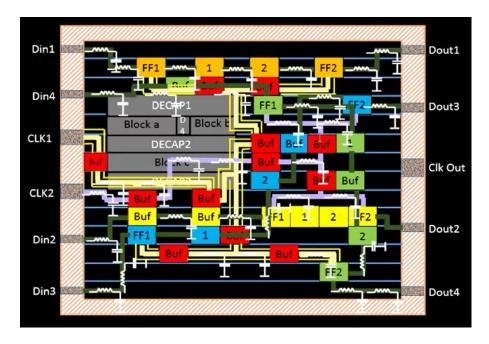

Starting with the floor-planning, where we have the constraints on width and height of the core, and to integrated many pre-placed cells. Power planning and Pin placement is also done in this step of Physical Design Flow. Figure 2.1 is showing the snippet of Floor Planning where there are many components like, core and die, decoupling capacitance, power grids and pins connections.

# Figure 2.1: Snippet of the chip after Floor-planning

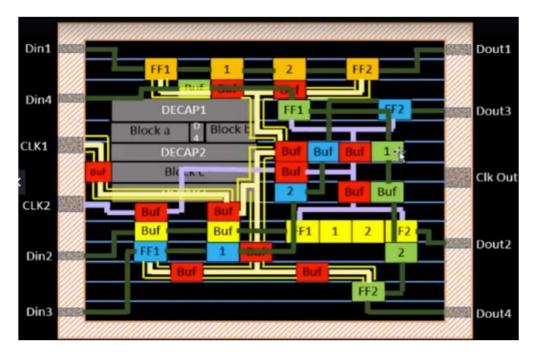

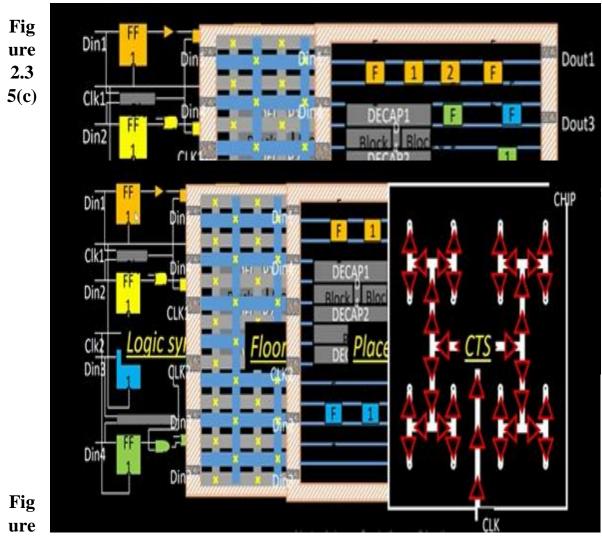

### 2.2.2 Placement and Optimised Placement

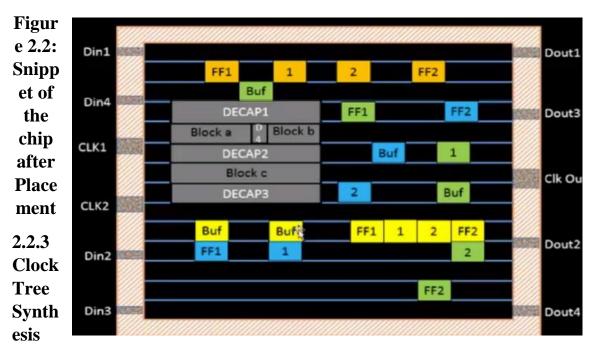

Then we have the netlist binding and placement optimization, where we are just finding the netlist and we have the placements, which get optimized, including the buffers and all the necessary things. Figure 2.2 is showing the chip where the blocks are placed according to the defined regions based on the placement optimisation tool.

Then we have the timing issues and the clock and data path in the physical design flow, we have to generally study, the static timing analysis, and the clock synthesis. Figure 2.3 depicts the chip have the clock path connected with the flip-flops using the H-Tree algorithm.

Figure 2.3: Snippet of chip after Clock Tree Synthesis

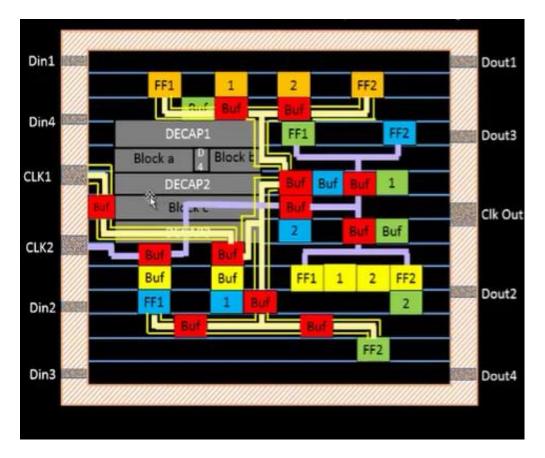

## 2.2.4 Clock Net Shielding

Then we have the shielding of the clock nets as clock is the most critical net so we shield them so that it can be glitch free. So here we study the signal integrity issue, which is generally a crosstalk, which is a combination of glitch and the data delays, which will affect the timing. Figure 2.4 shows that the clock nets have been shielded by the lines which are not fluctuating, to reduce the effect of glitch in clock signal.

Figure 2.4: Snippet of chip after Clock Net Shielding

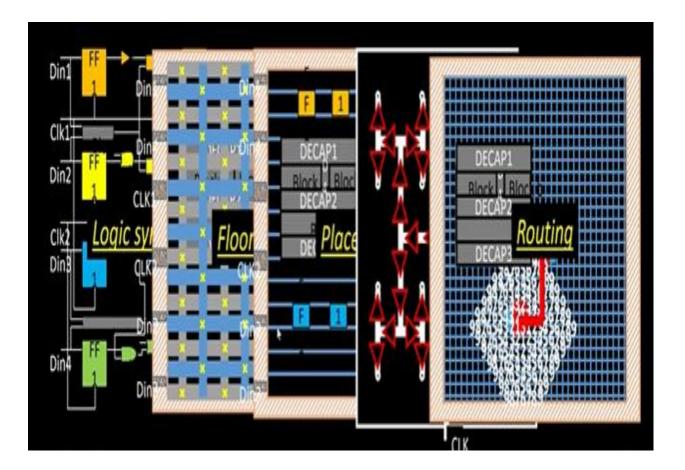

# 2.2.5 Routing

After the shielding of the clock net, we have to route the data for the proper functioning of the SOC. The routing of the data path can be done by various ways using the shortest path algorithms where we have the source point and the destination point and the connection between them is generally, the L shape. Figure 2.5 depicts the routing of the data path, and if some data paths are critical, which means that if data path is crucial for the timing and performance point of view, then it can also be shielded as like the clock nets.

Figure 2.5: Snippet of chip after Routing

## 2.2.6 DRC and Parasitic Extraction

Then the last step of the physical design flow is the violation checks of the data wires, which contains the DRC checks and parasitic extraction, and then after the final step we have the static timing analysis for all the real clock path and the data path. Figure 2.6 shows the parasitic resistances and capacitances which are present in the SOC because of the interconnection of the wires and the nets running very close to each other.

Figure 2.6: Snippet of chip after Parasitic Extraction.

# 2.3 FLOOR PLANNING

There are series of steps that are followed in floor planning. The sequence of steps that are followed are:

- 1) Define width and height of core and die.

- 2) Define the location of preplaced cells.

- 3) Surround the preplaced cells with a decoupling capacitor.

- 4) Power Planning

- 5) Pin placement

- 6) Logical Cell Placement Blockage

#### 2.3.1 Width and Height of core and die

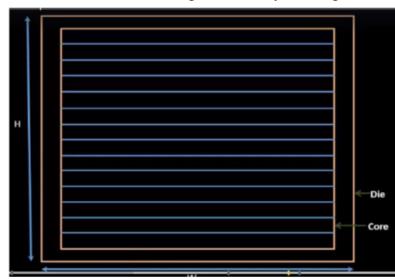

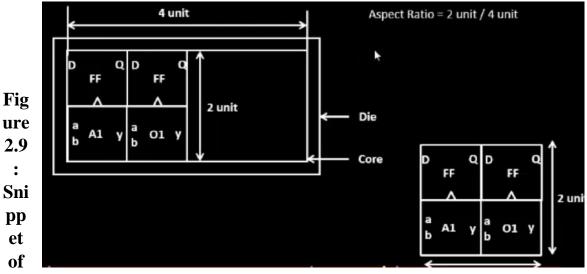

The first step of the physical design flow is floor-planning which includes many small steps, the initial one is the utilization factor and the aspect ratio of the core and the die. The first step is to measure the width and the height of the core and die so that the designer can get the overall area where he can do the placement of the blocks.

Here, the utilization factor is calculated and the aspect ratio is calculated in terms of the gates and in terms of the area of the core and the type of the technology node used, which is effectively used by the core and by the interfaces. Utilization factor can never be 100% since we want space between the cells, so that there can be an interconnection amongst the blocks on the same layer. Figure 2.7 is showing the core and die of the chip, where the actual logic of the chip will be placed in further steps. Figure 2.8 is showing the calculation of the effective area of the logic which is used inside the chip for the desired functionality. Figure 2.9 depicts the utilization factor, which means the amount of area of the core being utilized by the logic to the total amount of the area of

core.

Figure 2.7: Snippet of chip showing the width and Height of the core.

Figure 2.8: Snippet of chip showing the effective area calculation.

chip for finding the utilization factor.

### 2.3.2 Pre-placed cells

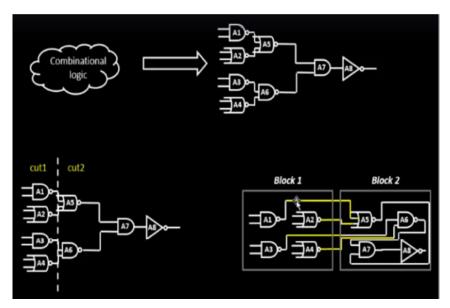

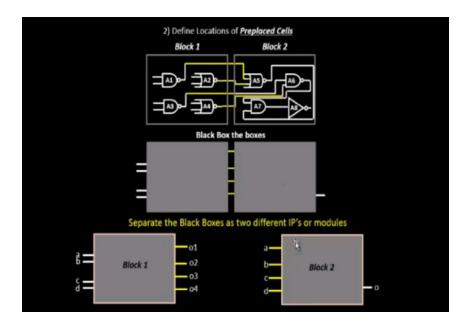

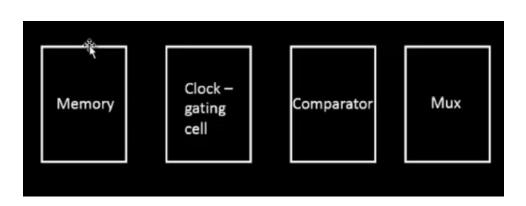

After the calculation of the width and the height of the core and utilization factor, pre-placement cells are included in the core. These pre-placement cells are basically the IPs/ IOs used frequently into the design and in the big SOCs, so that they can be available in each and every session in which they are required. For example, some of the common IPs, which we generally used are

some Digital IPs, like adders, multiplexers, some Analog IPs like regulators, crystal oscillators, so these are some of the examples of IPs which frequently use, so these are considered under the pre-placement cells. Figure 2.10 shows the logic which is commonly used in the SOC. Figure 2.11 shows, how the common logic can be converted into black box and can be used as the IP. Figure 2.12 shows the commonly used macros in the SOC Design which contains both Analog and Digital IPs, IOs and Macros.

Figure 2.10: Snippet of chip making interconnection of IPs.

Figure 2.11: Snippet of chip for Black-Boxing the logic.

Figure 2.12: Snippet of chip for commonly used Macros.

## 2.3.3 Use of Decoupling Capacitance

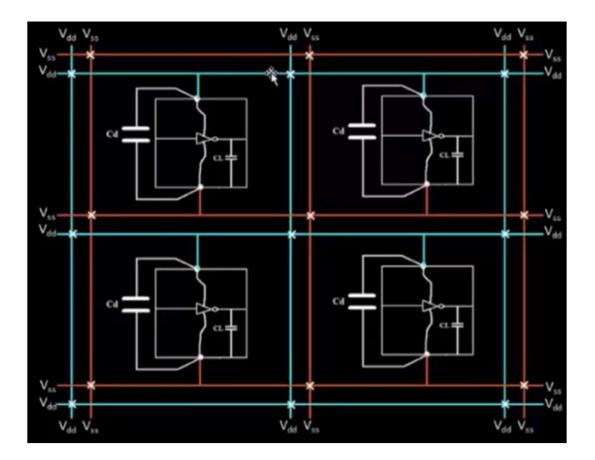

Then the next step is to include the decoupling capacitors. The decoupling capacitors are used in this circuit so that there can be a measure for the unwanted saturations in the power supply. As some of the common problem of Voltage drawn and ground bounce occurs in the SOC, so these decoupling capacitors provide a backup supply to the cells, when there is a need of power. Figure 2.13 shows the logic which is not having the Decoupling capacitance. Figure 2.14 shows the logic which is having the capacitance for resolving the issue of voltage drop and ground bounce. Figure 2.15 shows the placements of Macros and Decoupling capacitances.

Figure 2.14: Snippet of chip showing cells with Decoupling Capacitor.

Figure 2.15: Snippet of chip showing placement of Decoupling capacitances.

#### **2.3.4 Power Planning**

The next step after the Decoupling capacitance is the Power-Planning, where generally, the names of the powers are made, the layer above the blocks, so that each and every block can get the continuous supply of the VDD and the VSS for the correct operation. And there would be the minimum delay amongst the power nets and the wires so that they are within the noise margins, and the effect due to parasitic delays can be avoided. Figure 2.16 depicts the logic high line and logic low line supply, which is connected to each logic, so that there will be no problem of supply rails while the particular block is not active mode, or in power save mode. This is basically the local power connection technique. Figure 2.17 depicts the global power grid for the entire SOC, so that the appropriate power rails is available within the short distance to each and every block of the IP or SOC.

Figure 2.16: Snippet of chip showing Power Planning

Figure 2.17: Snippet of chip showing Mesh arrangement of Power Rails.

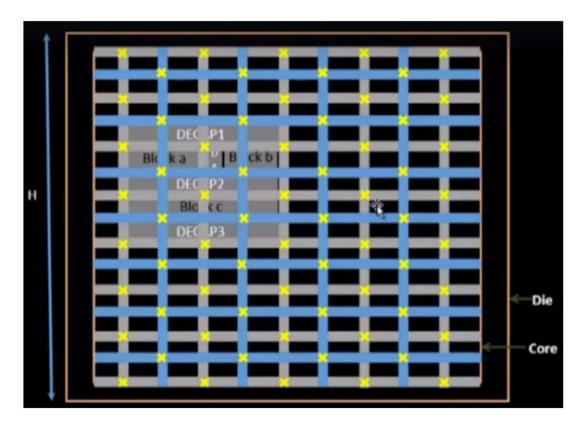

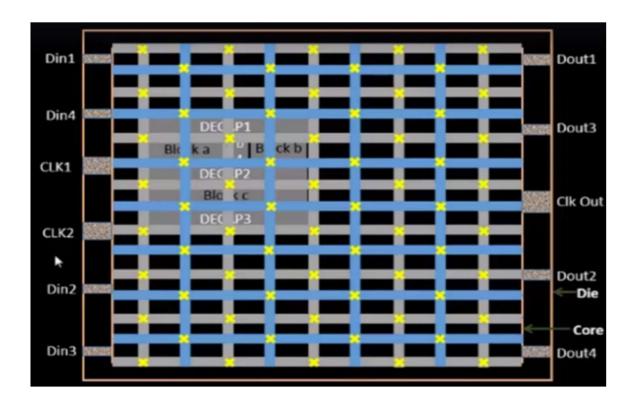

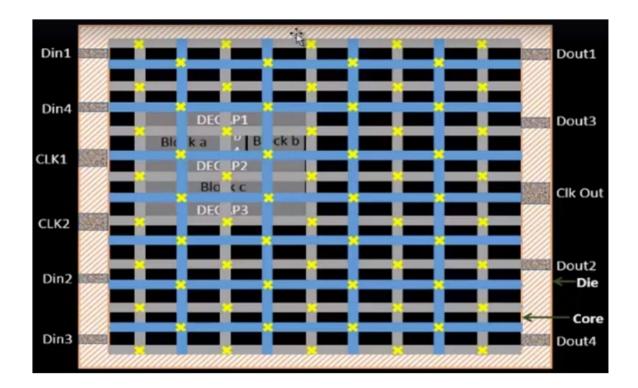

## 2.3.5 Pin Placement and Logical Cell Placement Blockage

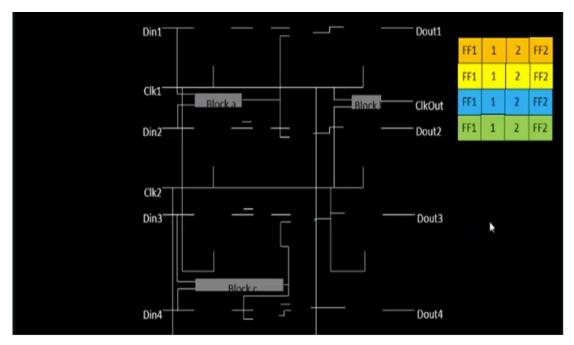

And the final step is logical cell placement blockage, where the pins are placed according to the need of the SOC design, the pins are placed according to their interfaces inside the code and logical cell placement blockage is done to block the area of the core where we don't have to place any cells, these areas can be blocked due to the other block which is inherently present there, or avoid to run the placement optimization tool. Figure 2.18 shows the arrangement of the pins in the die location which depends on the requirement given by the design team for the timing constraints. Figure 2.19 depicts the Blockage of the placement tool, so that no logical cell could be allowed to get placed onto that specific region where it should not be.

Figure 2.18: Snippet of chip showing Pin Placement

## **2.4 PLACEMENT**

The next step after the Floor Planning is the placement process, it carries various steps starting with binding the netlist into the physical cells with the help of technology node present in the library of the particular dataset of the organization which is generated after the synthesis part in the design flow.

Following steps are performed in Placement

- 1. Bind the netlist with Physical Cells.

- 2. Placement

- 3. Optimize Placement

## 2.4.1 Physical cells in the netlist

Netlist contains many IPs, IOs, S/Ds that are technology dependent so we have to link those blocks or cells to some technology node. There are the libraries present which contains different technology in the database, so the optimized gate with respect to time period, power and area is taken from the library and are integrated and placed into that core region. Figure 2.20 shows many logical cells which are present in the library and are needed to be integrated in the netlist.

Figure 2.20: Snippet of chip showing Mapping of Library cells.

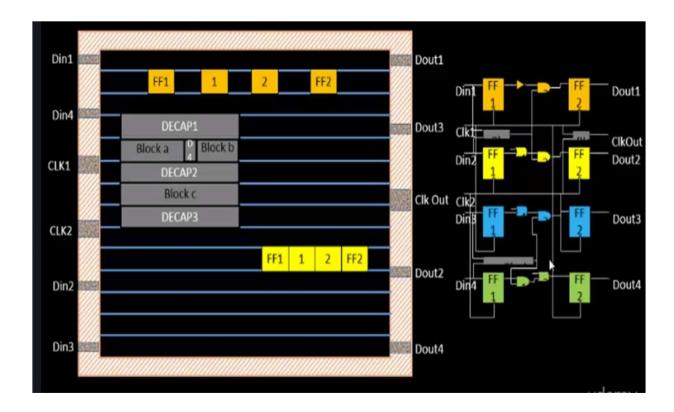

## 2.4.2 Placement of the logical Blocks

The placement of the blocks is done based on the requirement of the design of the IP or SOC. All the blocks which have common path of data are placed to each other. Placement is done with the help of automatic tools which exclude the region of pins and location of pre-placement cells. Figure 2.21 shows the placement of the blocks based on the EDA tool.

Figure 2.21: Snippet of chip showing Placement of Logical Cells.

## 2.4.3 Optimised Placement

Optimised placement is done to ensure the correct functionality of the data path, while transferring the data from one logic gate to another. There are many parasitic resistances and capacitances present in the SOC, due to which there can be the effect of signal integrity issues and the most common is of crosstalk which can disturb the original signal. Thus, to eliminate or to minimise the effect of glitches and crosstalk, buffers are added in the path to maintain the signal strength of the data. Optimize placement is done using the estimated wire delay and lumped capacitances to measure the delays, which can change the

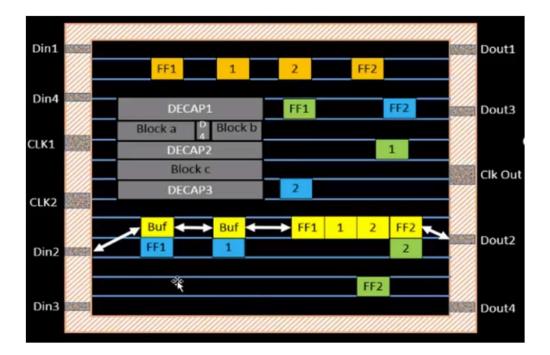

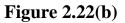

strength of the signal. So, accordingly optimized placement is done. Figure 2.22 shows the introduction of the buffers inside the Core, so as to improve the quality of the signal being transferred from one logic gate to another, depending on the relative connectivity of the logical blocks.

**Figure 2.22(a)**

Figure 2.22(c)

# Figure 2.22: Snippet of chip showing Optimised placement with inserting Buffers.

## 2.5 Static Timing Analysis with Ideal Clocks

Now since for the connection of the clock, for the proper functioning of the SOC, there are some measures like the data delays, and the slew rate, latency, should be studied so that the signal integrity should be maintained.

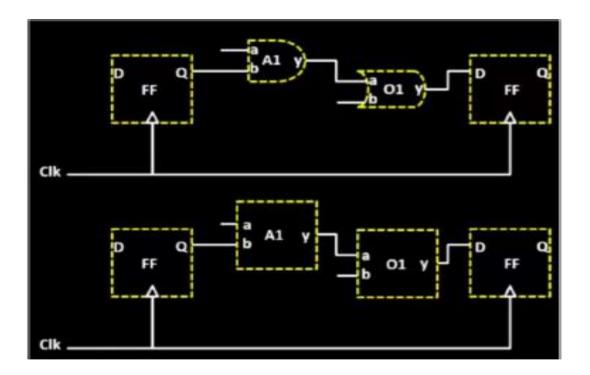

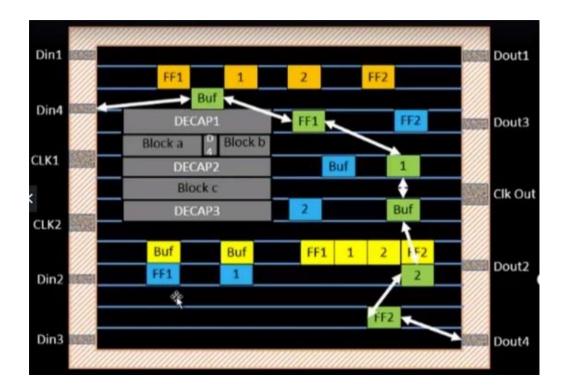

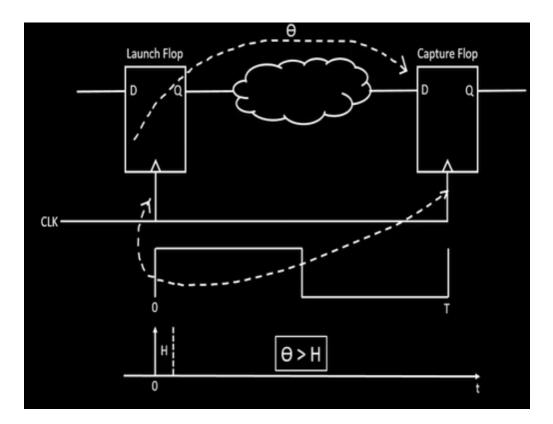

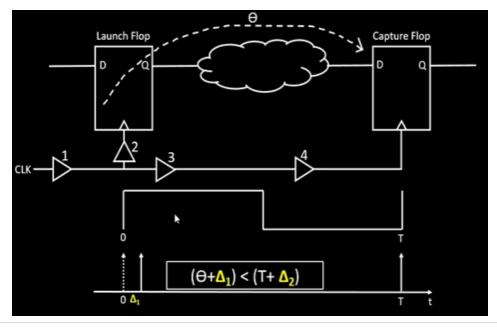

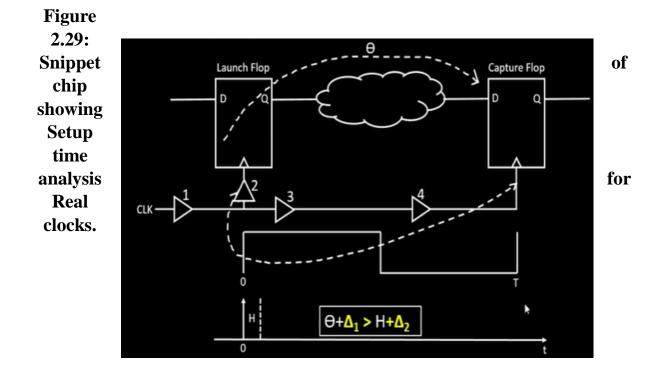

The next step after the placement is to perform the timing analysis with the estimated clock nets and the estimated data wire delays. Here the timing analysis performed on the basis of the setup and hold constraints, and the introduction of the clock jitter and uncertainty is also engaged so to perform the clock domains in a more efficient manner. After the static timing analysis, with a single clock. the STA is performed with the help of multiple clocks. Multiple clocks are introduced in this method and the multifrequency clocks, multi-level clocks are introduced. Figure 2.23 shows one of the stages of pipelined architecture where there are two F/Fs, one is Launch (Left) and the other is Capture (Right) and Setup timing constraints have been verified with real clock. Figure 2.24 shows the calculation of Hold time constraints with real clock.

Figure 2.23: Snippet of chip showing Setup time analysis for ideal clocks.

Figure 2.24: Snippet of chip showing Hold time analysis for ideal clocks.

## **2.6 CLOCK TREE SYNTHESIS**

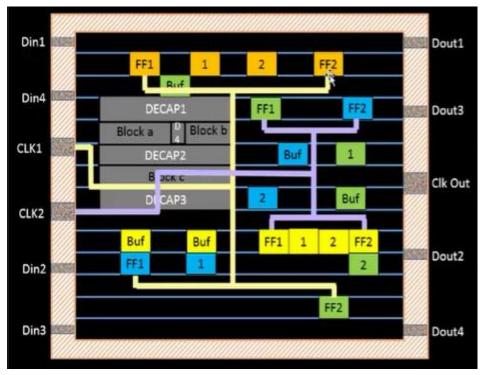

Now, after the static timing analysis status check is done. To maintain the clock net and the data net of the SOC functional correct, the next step is clock synthesis, where the clock path is analysed and synthesis is done in between the clock signals so that the signal integrity can be matched accordingly.

The general algorithm which is used in the clock tree is the tree algorithm, where the main objective is to minimize the latency, and to reduce the skew for launch and capture F/Fs. Figure 2.25 shows the clock pin CLK1, which is needed to make the connection to the desirable F/Fs.

Figure 2.25: Snippet of chip showing Clock available at CLK1.

For Clock there are various quality parameters check that are needed to be verified. The six quality parameters checks are:

- 1. SKEW

- 2. PULSE WIDTH

- 3. DUTY CYCLE

- 4. LATENCY

- 5. CLOCK TREE POWER

- 6. SIGNAL INTEGRITY AND CROSS TALK

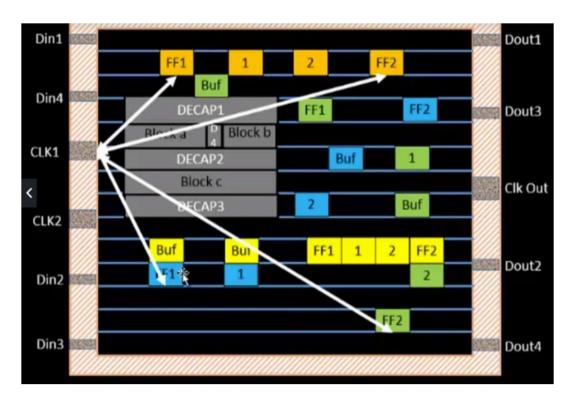

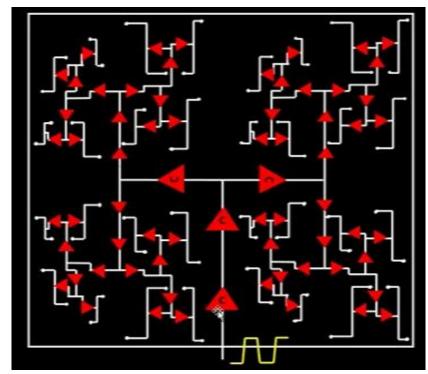

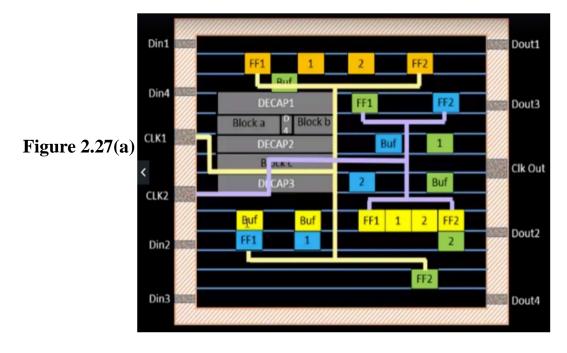

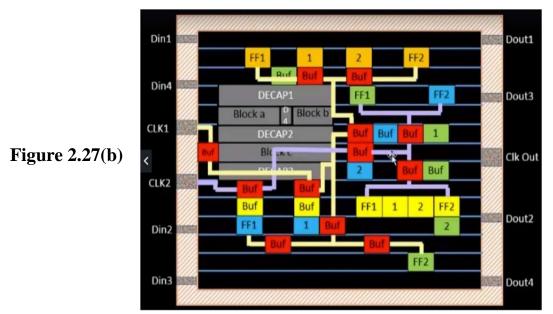

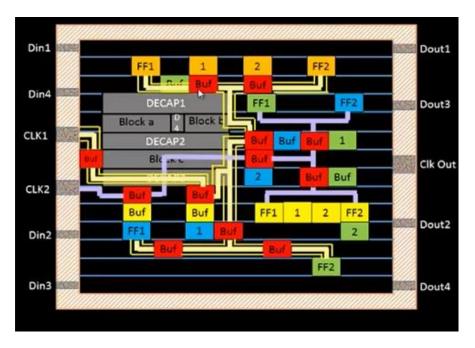

Figure 2.26 shows the typical implementation of the H tree, which is used to make the skew as low as possible by eliminating the latency difference between the Launch F/F and Capture F/F which will be working and transferring the data from the same clock pin. Figure 2.27 depicts the H-tree implementation into the SOC, where the shape of 'H' can easily be visible through the clock path.

Figure 2.26: Snippet of chip showing Clock Tree Synthesis

Figure 2.27: Snippet of chip showing Clock path using H-tree.