# Comparative Power Analysis of RISC Processor using Machine Learning Algorithms

#### A DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

#### MASTER OF TECHNOLOGY

in

#### VLSI DESIGN AND EMBEDDED SYSTEMS

Submitted by:

PRIYA

### 2K19/VLS/11

Under the guidance of

Dr. MALTI BANSAL Dept. of Electronics & Communication Engineering, Delhi Technological University (DTU)

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Delhi-110042

**JUNE 2021**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Delhi-110042

# **CANDIDATE'S DECLARATION**

I Priya, Roll No. 2K19/VLS/11, student of M.Tech (VLSI and Embedded Systems), hereby declare that the Project Dissertation titled **"Comparative Power Analysis of RISC Processor using Machine Learning Algorithms"** which is submitted by me to the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, in the partial fulfillment of the requirement for the award of the degree of Master of Technology, has been done under the guidance of my project mentor **Dr. Malti Bansal**, Assistant Professor, Department of Electronics & Communication Engineering, Delhi Technological University (DTU), is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associateship, Fellowship or other similar title or recognition.

Place: Delhi Date:25.04.2021 **PRIYA** (2K19/VLS/11)

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering),Delhi-110042

## **CERTIFICATE**

I hereby certify that the Project Dissertation titled "**Comparative Power Analysis of RISC Processor using Machine Learning Algorithms**" which is submitted by **PRIYA**, **2K19/VLS/11** of Electronics and Communication Department, Delhi Technological University, Delhi, in the partial fulfillment of the requirement for the award of the degree of Master of Technology, is a record of the project work carried out by student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date: 25.04.2021 **Dr. MALTI BANSAL** Assistant Professor Department of ECE

## **ACKNOWLEDGEMENT**

A successful project can never be prepared by the efforts of the person to whom the project is assigned, but it also demands the help and guardianship of people who helped in completion of the project. I would like to thank all those people who have helped me in this research and inspired me during my study.

With profound sense of gratitude, I thank my Research Supervisor **Dr. Malti Bansal**, Assistant Professor, Department of Electronics & Communication Engineering, Delhi Technological University (DTU), for her encouragement, support, patience and her guidance in this project work. I heartily appreciate the guidance given by her in the project presentation that has improved my presentation skills with her comments and advices.

I take immense delight in extending my acknowledgement to my family and friends who have helped me throughout this project work.

> PRIYA 2K19/VLS/11

### **ABSTRACT**

The exigency of automation and advancements ushers machine learning and artificial intelligence to expand it dimensionality into numerous domains like Internet of Things (IoT), Military, product and market analytics, language and sentiment analysis and Very Large Scale Integration of chips is also one of them. ML has started transuding as an significant application in the development and evolution of the Computer Aided tools and technologies that are involved in VLSI domain in the design of ASICs or FPGAs. The SoCs, Macros, IPs and Processors etc. otherwise would take large turnaround time to spin off as a final chip. As RISC Processors are being extensively used due to their less flexibility and high performance as compared to CISC Processors. We focused on the study, design and imposition of a RISC Processor on the Register Transfer Level (RTL) and apply machine learning algorithm to predict and analyze its power consumption. And also we compare which machine learning algorithm fits the power dataset of RISC Processor in the best possible manner in terms of the performance metrics.

In the thesis, a 32-bit, MIPS based RISC Processor is implemented which supports basic Instruction Set Architecture (ISA) to perform few simple arithmetic computations like ADD, SUB, MUL etc. This processor is simulated using Xilinx VIVADO and its power is calculated and stored as a dataset under various input conditions often called as dataset features or attributes. The obtained power dataset is analyzed graphically to know on which factor different types of power majorly depends. Furthermore, machine learning algorithms are applied to obtain the classification report stating the accuracy, precision and recall on the power dataset of the RISC Processor to state which Machine learning algorithm is best fit for the Power dataset generated. In a nutshell, the thesis focuses on the application and relative analysis on performance metrics of machine learning algorithms on the power dataset of RISC Processor.

##

| CONTENTS                                                    |    |

|-------------------------------------------------------------|----|

| Candidate's                                                 | 1  |

| Declaration                                                 | 2  |

| Certificate                                                 | 3  |

| Acknowledgement                                             | 4  |

| Abstract                                                    | 5  |

| Contents                                                    | 6  |

| List of Figures                                             | 8  |

| List of Abbreviations                                       | 9  |

| Tables                                                      |    |

| CHAPTER 1 INTRODUCTION                                      |    |

| 1.1 Introduction to RISC Processors                         | 12 |

| 1.2 RISC Processor Architecture                             | 13 |

| 1.3 Pipelining and its hazards                              | 15 |

| 1.4 Instruction Set format                                  | 17 |

| 1.5 Advantages of Processor                                 | 22 |

| 1.6 Application of Processor                                | 23 |

| CHAPTER 2 MACHINE LEARNING PERSPECTIVES                     | 25 |

| 2.1 Introduction to Machine Learning in VLSI                | 25 |

| 2.2 The basic paradigm of Machine Learning                  | 26 |

| 2.3 Areas of Machine Learning                               | 27 |

| 2.4 Machine Learning Algorithms                             | 27 |

| 2.5 Drawbacks of Machine Learning                           | 31 |

| CHAPTER 3 LITERATURE SURVEY– MACHINE LEARNING<br>ALGORITHMS | 32 |

| 3.1 Support Vector Machine (SVM)                            | 32 |

| 3.2 Isolation Forest (IF) Algorithm                         | 34 |

| 3.3 Local Outlier Factor (LOF) Algorithm                    | 36 |

| 3.4 K-Nearest Neighbor (KNN) Algorithm                      | 36 |

| 3.5 Naïve Bayes (NB) Algorithm                              | 37 |

| CHAPTER 4 TOOLS USED                  | 40 |

|---------------------------------------|----|

| 4.1 Introduction to Verilog HDL       | 40 |

| 4.2 Features of Verilog               | 42 |

| 4.3 Simulation                        | 42 |

| 4.4 Advantages of Verilog             | 43 |

| 4.5 Xilinx VIVADO                     | 43 |

| CHAPTER 5 SIMULATION RESULTS          | 44 |

| 5.1 Experimental Setup                | 44 |

| 5.2 Experimental Results              | 48 |

| CHAPTER 6 CONCLUSION AND FUTURE SCOPE | 66 |

| REFERENCES                            | 69 |

| APPENDIX A                            | 71 |

| APPENDIX B                            | 79 |

# **LIST OF FIGURES**

Figure 1.1 Basic Architectural block diagram of RISC Processor.

Figure 1.2 Instruction execution in pipelined processor.

Figure 1.3 Instruction execution in non-pipelined processor.

Figure 1.4 Distribution of the bits in the Instruction Frame.

Figure 1.5 Opcode and Funct assignment in Instruction Frame.

Figure 1.6 Distribution of Instruction bits in the Datapath.

Figure 2.1 Basic model of Machine Learning with Process Steps

Figure 2.2 Classification of Machine Learning Algorithm

Figure 3.1 Types of SVM Classification

Figure 3.2 (i) Representation of a tree in a forest and as a radial line,

Figure 3.2 (ii) Working of LOF algorithms.

Figure 3.3 Algorithm representation for Naïve Bayes classifier

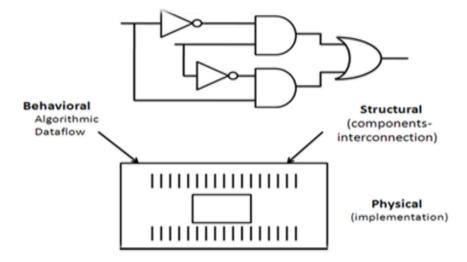

Figure 4.1: Level of Representation and Abstraction

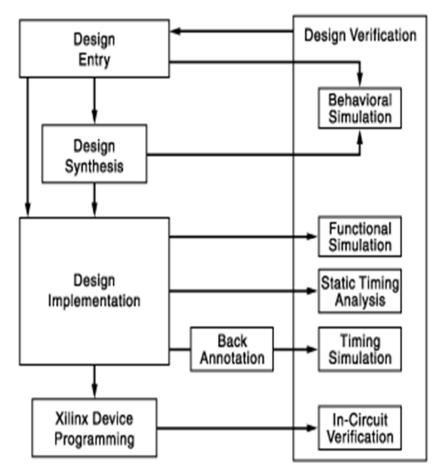

Figure 4.2: FPGA Design Flow Overview

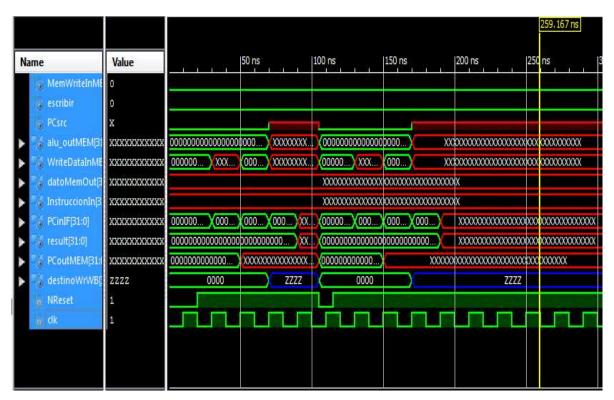

Figure 5.1 Simulation Result of 32 bit RISC Processor

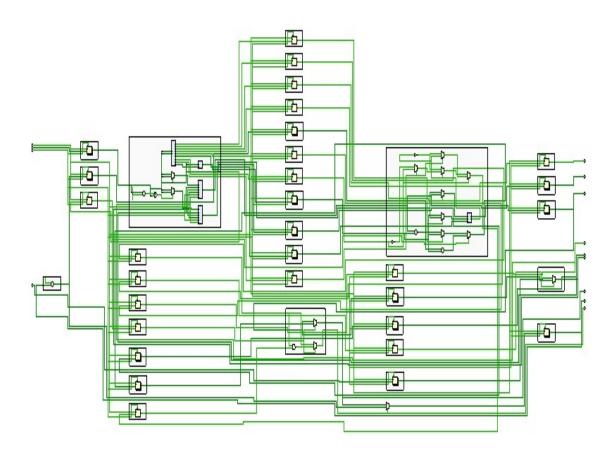

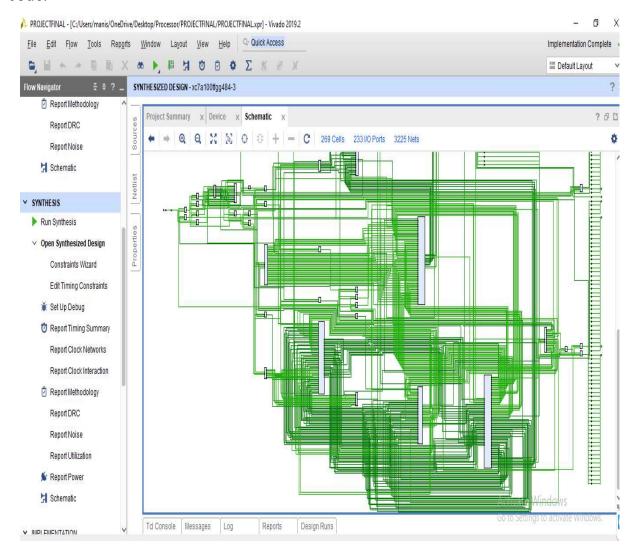

**Figure 5.2** Register Transfer Level schematic of RISC Processor after implementation stage.

Figure 5.3 Power Report and required Input features.

Figure 5.4 Data Information of Power samples of RISC Processor

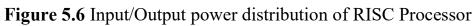

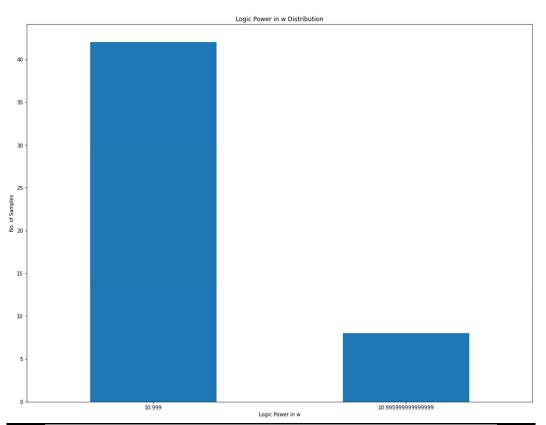

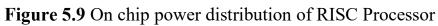

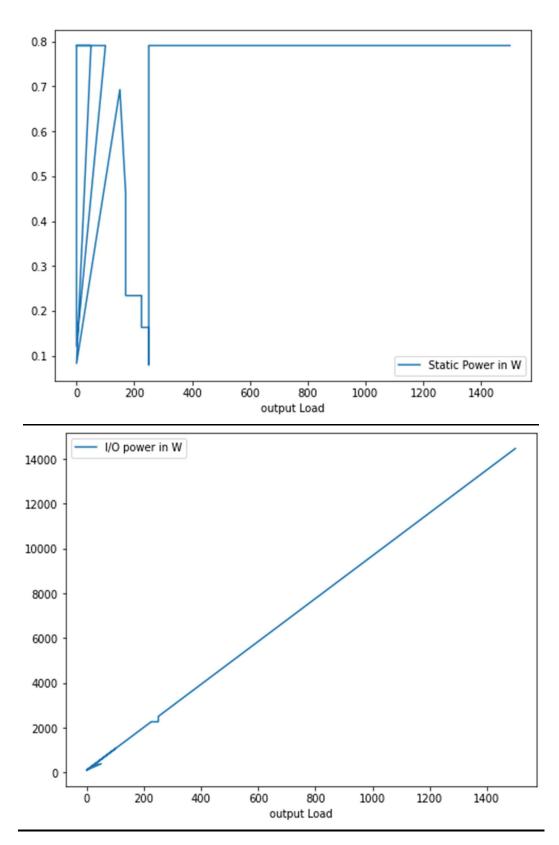

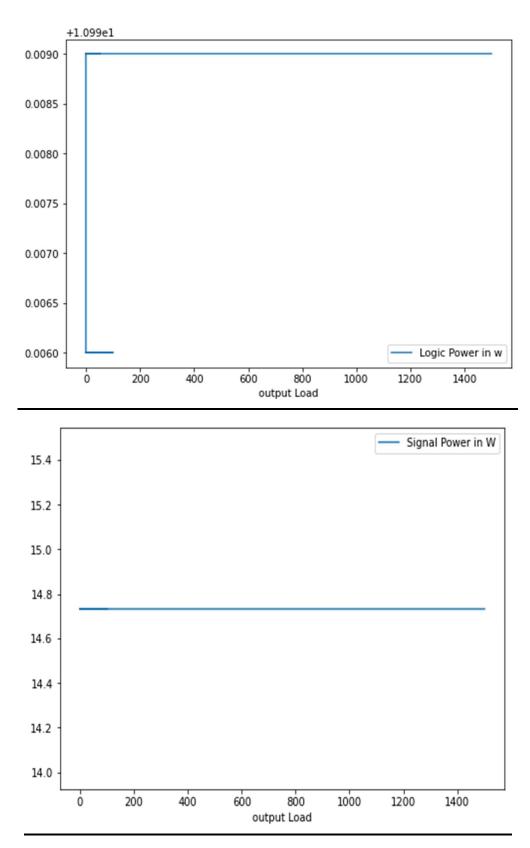

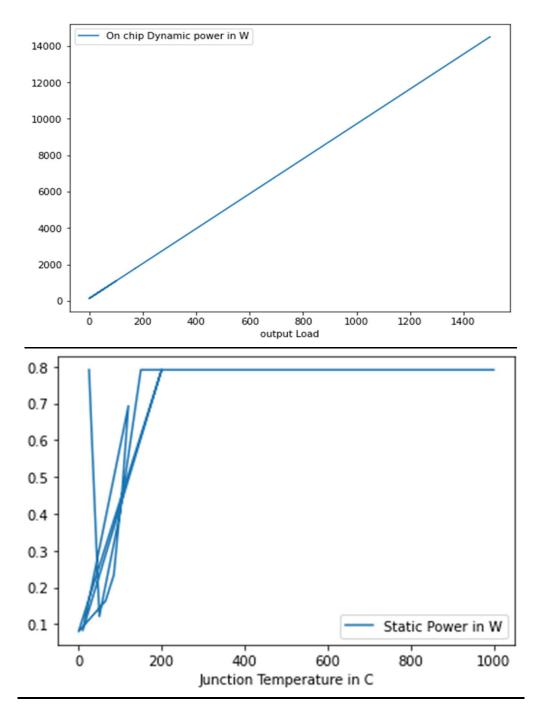

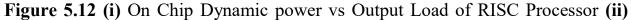

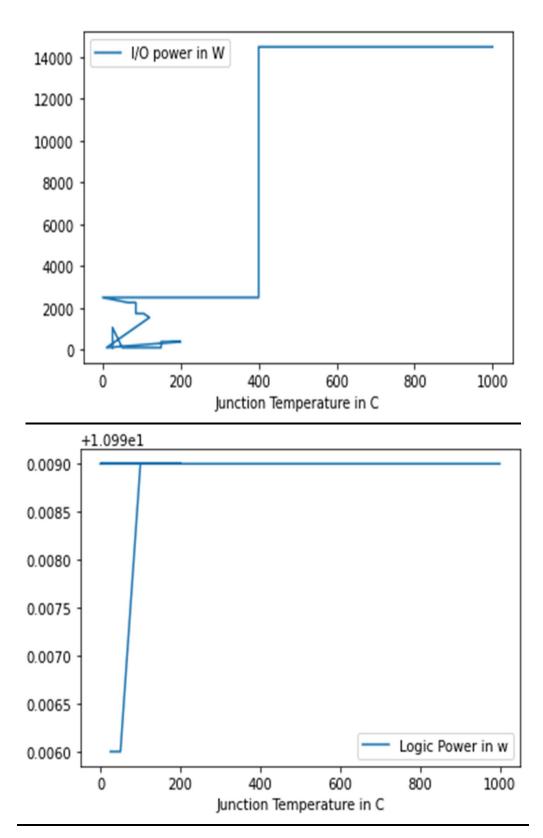

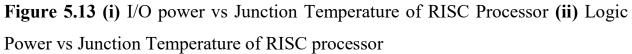

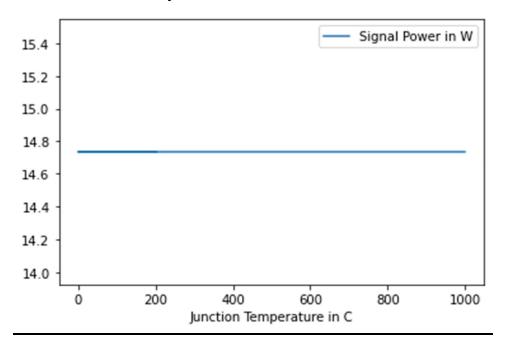

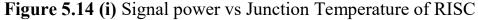

Figure 5.5 Static power distribution of RISC Processor Figure 5.6 Input/Output power distribution of RISC Processor Figure 5.7 Logic power distribution of RISC Processor Figure 5.8 Signal power distribution of RISC Processor Figure 5.9 On chip power distribution of RISC Processor Figure 5.10 (i) Static power vs Output Load of RISC Processor Figure 5.10 (ii) I/O power vs Output Load of RISC Processor Figure 5.11 (i) Logic power vs Output Load of RISC Processor Figure 5.11 (ii) Signal power vs Output Load of RISC Processor Figure 5.12 (i) On Chip Dynamic power vs Output Load of RISC Processor Figure 5.12 (ii) Static Power vs Junction Temperature of RISC processor Figure 5.13 (i) I/O power vs Junction Temperature of RISC Processor Figure 5.13 (ii) Logic Power vs Junction Temperature of RISC processor Figure 5.14 (i) Signal power vs Junction Temperature of RISC Processor Figure 5.14 (ii) On chip Dynamic Power vs Junction Temperature of RISC processor

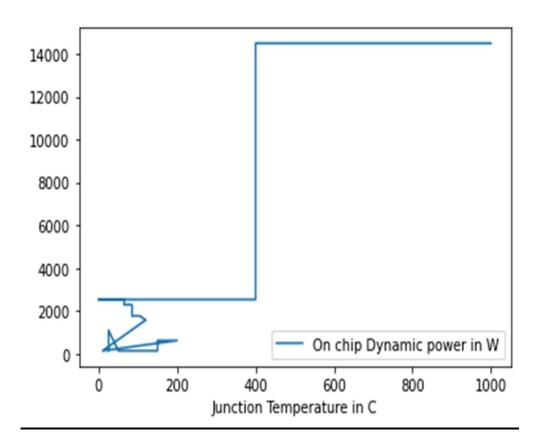

Figure 15 Correlation of each features in dataset

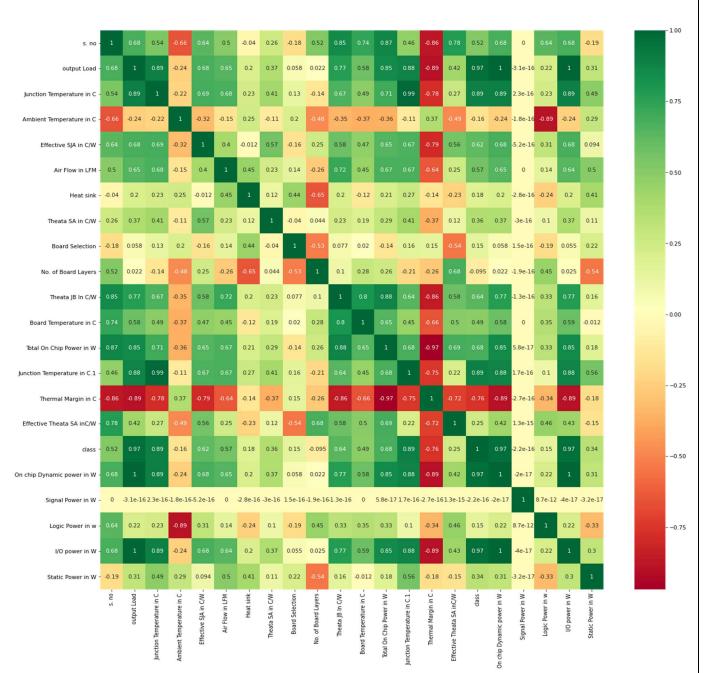

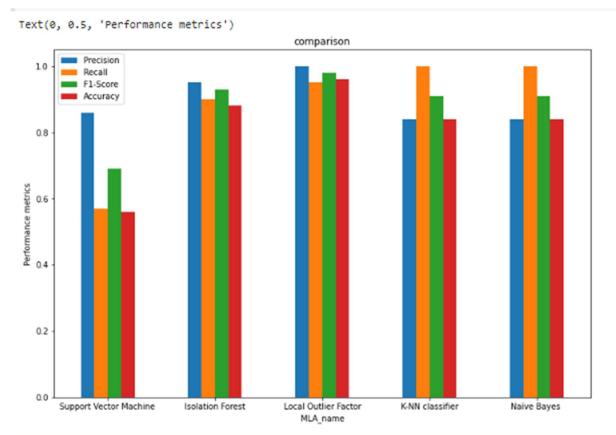

**Figure 16** Comparative graphical analysis showing performance metric of Machine Learning algorithms.

# LIST OF ABBREVIATIONS

| RISC  | Reduced Instruction Set Computer |

|-------|----------------------------------|

| CISC  | Complex Instruction Set Computer |

| IR    | Instruction Register             |

| ID    | Instruction Decode               |

| PC    | Program Counter                  |

| NPC   | Next Program Counter             |

| IF    | Instruction Fetch                |

| EX    | Execution                        |

| MEM   | Memory Access                    |

| WB    | Write Back                       |

| IM/DM | Instruction Memory/Data Memory   |

| ML    | Machine Learning                 |

| AI    | Artificial Intelligence          |

| SVM   | Support Vector Machine           |

| IF    | Isolation Forest                 |

| LOF   | Local Outlier Factor             |

| KNN   | K-Nearest Neighbor               |

| NB    | Naïve Bayes                      |

| HDL   | Hardware Description Language    |

| RTL   | Register Transfer Level          |

| FPGA  | Field Programmable Gate Array    |

| IP    | Intellectual Property            |

# LIST OF TABLES

**Table 2.1** Machine Learning algorithms and their Uses, Advantages and its Drawbacks**Table 5.1** Comparative classification report showing performance metric of MachineLearning algorithms.

# **CHAPTER 1**

### **INTRODUCTION**

#### **1.1 INTRODUCTION TO RISC PROCESSOR**

In the late 1970s, Researcher who worked with IBM, John Coke and his team developed the first processor prototype that deployed Reduced Instruction Set Computer (RISC) architecture [1]. This architecture has reduced number of instructions which are simpler to implement. Also, RISC architecture has fixed and same bits of instructions, register file and memory which allows the fetch, decode, execute, access to the memory and write back to register file, each operation to be performed in exactly 1 clock cycle. Due to this reason, RISC architecture is less flexible but delivers high performance by increasing the speed of operations.

It only has two operations to be performed with the memory i.e. LOAD and STORE. All the other operations and arithmetic computations are done with the register files. Since interactions with the memory takes more time or more number of clock cycles than what is taken by the registers present in the architecture, and RISC processors mainly performs operations on registers only, makes RISC Processors faster and efficient enough to implement pipelining in the best way possible [2]. LD(load) directive allows to access the data/instructions from the memory and ST(store) directive allows the processor to store the data /results back into the memory.

However, there is other type of processors also based on Complex Instruction Set Computer (CISC) Architecture. The main difference is that they support variable sizes of instructions for example a CISC Processor of 32 bit can support instructions of 8 bit, 16 bit or 32 bit which means that one instruction may or may not get fetched, decoded and executed in one clock cycle. This adds to the complex nature of CISC processor. Although CISC processors are flexible in terms of executing any type of instructions but, performance is greatly affected since many instructions in this processor might take more cycles or more memories to be processed. Speeds of such processors are very slow comparative to the RISC processors.

Most of the operations in the CISC Processor involve the interactions with the memory which adds to more number and types of instructions. Since interaction with the memory is slower process than the interaction with register, this is one more reason that why CISC Processors are slower. CISC Processors have lesser numbers of Registers but definitely have more number of instructions and more number of modes to address those instructions. The major disadvantage of CISC processor is that the pipelining implementation is never effectively done in CISC Processor which adds to the fact that CISC Processors although being too flexible but compromises in the performance part.

### **1.2 RISC PROCESSOR ARCHITECTURE**

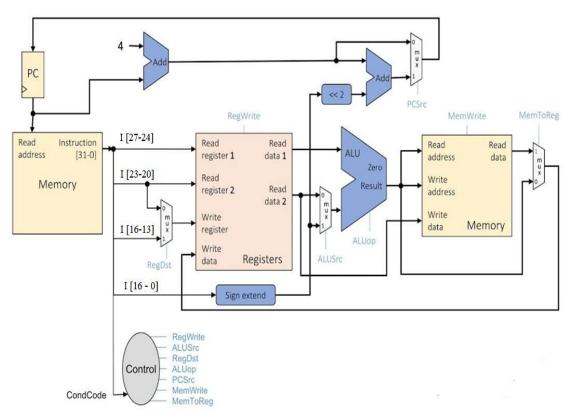

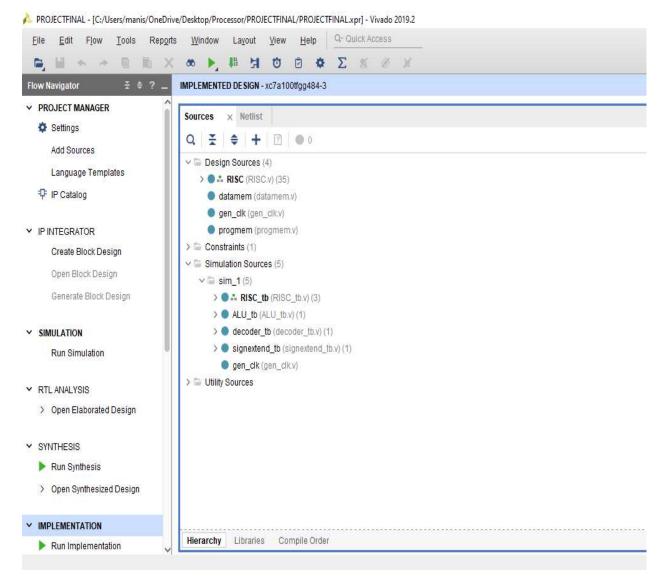

The RISC processor that has been implemented has 32-bit core with separate data and instruction memory (Harvard architecture) where instruction memory is generally read only memory and data memory is both read-write memory. The register transfer level code is written in Verilog language and named as RISC.v. It is instantiated in the test bench named RISC\_TB.v file. The code also has a double bank of 16 registers (Register File) to allow two simultaneous reads in addition to one write operations from the register file. Also, it has a set of instructions of fixed size but different structure depending on the addressing modes and the specific instructions.

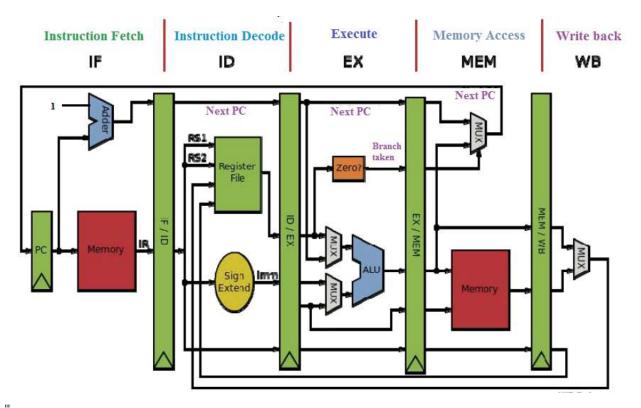

There are five stages incorporated in executing a instruction in 32 bit RISC i.e. IF, ID, EX, MEM and WB as shown in Figure below. Figure 1 shows the basic

Architecture which shows the pipelining stages in the RISC Processor.

Figure 1.1 Basic Architectural block diagram of RISC Processor [3].

There are five stages in a processor pipeline to perform a specific operation. This is coded in hexadecimal instruction format. The IF stage allows fetching of succeeding instruction by accessing the address of IM stored in program counter and stores the fetched instruction into the Instruction Register (IR). Next stage is the Instruction Decode (ID) which calculates the next PC (NPC), decodes the Instruction stored in IR and performs read operations from the register file (reading rs and rd registers). In the Execution stage, based on the opcode and funct decoded in the previous stage, ALU performs the operations on the operands and stores the value in intermediate register called ALUOut. Memory Access stage allows operations on data to be performed to and from the memory such as load and store(LD/ST). Final stage is the Write Back Stage which perform the Write operation on the register file [3].

#### **1.3 PIPELINING AND ITS HAZARDS**

Pipelining is one of the prominent attribute of RISC Processors which when incorporated to the architecture helps in improving the throughput and performance of the processors[3]. Pipelining divides the entire execution of a Instruction (particularly a task like arithmetic computations) into multiple stages, often the operations executing at these stages are called micro-operations. These stages help the processors to work on multiple numbers of instructions at a time.

For example: In the RISC processor designed, there are five stages as we discussed in the previous section. Suppose we have our Instructions say,  $I_0$ ,  $I_1$ ,  $I_2$ ,  $I_3$ ...so on. In first cycle of clock,  $I_0$  will be fetched. In the second clock cycle,  $I_0$  will move to second stage i.e.  $I_0$  will be decoded. And by the time  $I_0$  is decoded, processor can fetch I<sub>1</sub>. Processor handles two instructions simultaneously in different stages. In the third clock cycle,  $I_0$  moves to third stage i.e. execution,  $I_1$  moves to decode stage and I<sub>2</sub> moves fetch stage. Here, Processor handles three instructions simultaneously in different stages. In the fourth clock cycle, I<sub>0</sub> moves to fourth stage i.e. memory access,  $I_1$  moves to execution stage and  $I_2$  moves decode stage and I<sub>3</sub> moves to fetch stage. So now, Processor handles four instructions simultaneously in different stages. In the fifth clock cycle, I<sub>0</sub> moves to fifth stage i.e. write back,  $I_1$  moves to memory access stage and  $I_2$  moves execution stage and I<sub>3</sub> moves to decode stage, I<sub>4</sub> moves to fetch stage. So now, Processor handles five instructions simultaneously in different stages. In the coming next cycles, new instruction enters fetch stage and one Instruction completes the entire execution and gets out of the pipeline.

This simultaneous execution of multiple instructions at a time increases the efficiency of the processor. The processor does sit idle waiting for the next instruction.

|                  | νć | I. |    | Num | nber of | clock c | ycles |     |     | v   | 2   |    |

|------------------|----|----|----|-----|---------|---------|-------|-----|-----|-----|-----|----|

| Instruction      | 1  | 2  | 3  | 4   | 5       | 6       | 7     | 8   | 9   | 10  | 11  | 12 |

| Load instruction | IF | ID | EX | MEM | WB      |         |       |     |     |     |     |    |

| Instruction I+1  |    | IF | ID | EX  | MEM     | WB      |       |     |     |     |     |    |

| Instruction I+2  |    |    | IF | ID  | EX      | MEM     | WB    |     |     |     |     |    |

| Instruction I+3  |    |    |    | IF  | ID      | EX      | MEM   | WB  |     |     |     |    |

| Instruction I+4  |    |    |    |     | IF      | ID      | EX    | MEM | WB  |     |     |    |

| Instruction I+5  |    |    |    |     |         | IF      | ID    | EX  | MEM | WB  |     |    |

| Instruction I+6  |    |    |    |     |         |         | IF    | ID  | EX  | MEM | WB  |    |

| Instruction I+7  |    |    |    |     |         |         |       | IF  | ID  | EX  | MEM | WB |

Figure 1.2 Instruction execution in pipelined processor

| Number of clock cycles |    |    |    |     |    |    |    |    |     |    |    |    |

|------------------------|----|----|----|-----|----|----|----|----|-----|----|----|----|

| Instruction            | 1  | 2  | 3  | 4   | 5  | 6  | 7  | 8  | 9   | 10 | 11 | 12 |

| Load instruction       | IF | ID | EX | MEM | WB |    |    |    |     |    |    |    |

| Instruction I+1        |    |    |    |     |    | IF | ID | EX | MEM | WB |    |    |

| Instruction I+2        |    |    |    |     |    |    |    |    |     |    | IF | ID |

Figure 1.3 Instruction execution in non-pipelined processor

If we have k number of stages and n number of instructions, then the overall execution of all the instructions will take  $(n+(k-1) \operatorname{clock} \operatorname{cycles} \operatorname{which} \operatorname{very} \operatorname{less}$  than the non-pipelined execution where number of clock cycles for the same is (n\*k). For example 50 instructions in 5 stages of pipeline takes 54 cycles in a pipelined processor where as non-pipelined processor would take 250 clock cycles. Here, non-pipelined processor is 5 times slower and time consuming than the pipelined one. This is the reason why performance of pipelined processors like RISC is very high. As far as throughput is concerned, pipelined processor automatically has higher throughput since throughput is number of instructions per

clock cycle. Pipelined processor after first instruction completes its entire execution; the every next clock cycle will then complete one instruction means its nearly one instruction per clock cycle. In case of non-pipelined processor, in every 5 clock cycle, one instruction is executed. So, the throughput is very less in non-pipelined processor.

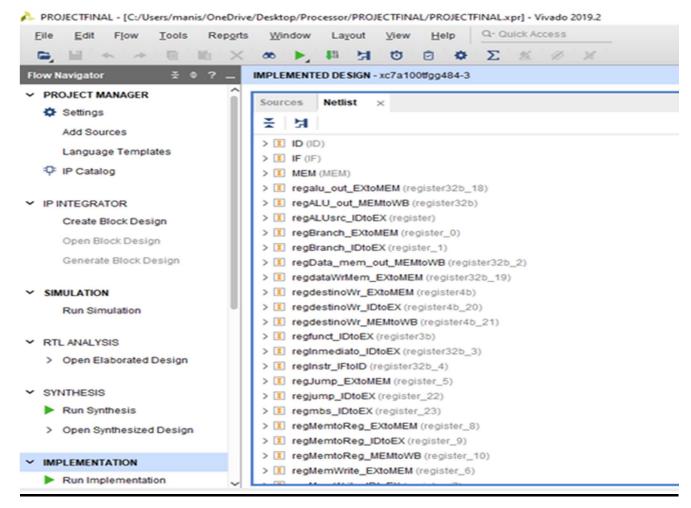

Also, the most important requirement while implementation of pipelining is the storing the results of the micro-operations because if each stage is connected to next one directly, there is possibility that data may change before it is used in the next stage while the current stage is working on new data changes the input to next stage which needs to work on previous data. So, to store the results of each stage such that it does not change, we need to use latches or registers in between two stages so that the output of a particular stage is not changing in between the micro-operations and this result in the successful functioning of pipeline. These latches/registers are the part of register file of Processor used to store the data. They are named as ID\_IF\_IR, IF\_EX\_IR, IF\_EX\_A, IF\_EX\_B, IF\_EX\_NPC etc.

Hazards in pipelining: There are some challenges faced during the proper implementation of pipelining. 100% implementation of pipelining of Processors is not possible due to some reasons such as data hazards, structural hazards and control hazards.

1) Data hazards: This can be understood with the help of the following example.  $I_0$ : ADD R5 R3 R4;  $I_1$  : ADD R6 R5 R7. In this example,  $I_0$  instruction executing first, writes the final result in 5<sup>th</sup> stage and  $I_1$  instruction reads the data stored in R5 in the second stage. So,  $I_1$  accesses the data before the final result gets written in register R5. In such a case,  $I_1$  accesses the wrong data present in the R5. Hence, it leads to the incorrect result. This hazard can be removed by introducing the dummy instruction. For example:  $I_0$  : ADD R5 R3 R4;  $I_1$  : ADD R5 R5 R0;  $I_2$  : ADD R6 R5 R7. Here,  $I_1$  is dummy instruction. Another solution can be renaming the registers or using different registers. Latter solution needs more memory and clock cycle and former one only need extra clock cycle.

2) Structural hazards: This hazard occurs when there is conflict at different stages for different instruction to use the same resource such as memory or a register simultaneously. If both the instructions are trying to access the memory, let's say one for reading the instruction and another for reading the data from memory. In such case, one instruction gets the resource but other one waits for it thereby killing the pipelining. Solution for this hazard is that to use different memory for the instruction such as Instruction memory and different memory to store and access the data.

3) Branch hazards: This hazard occurs when there are some branch instructions in the program. Whenever branch is encountered the execution of upcoming instruction has to be stopped and the execution has to be carried out from the address indicated by the branch instruction. It is generally not the next instruction indicated by the Program Counter. It has the address other than the next instruction. Hence, the next instruction has to be stopped from changing or writing the value in the memory. Also, we cannot stop the entire processor at a time after encountering a branch instruction because previous instructions are also in the ahead stages and they should be allowed to complete their write operations to the memory. Solution to above hazard is the use of two flag registers such as Halted and Branch Taken. Whenever branch instruction is decoded, these flag registers should be set to 1. Next instructions that are already fetched should write in the memory only when Branch Taken register is set to 0. If Branch Taken register is set to 1, write operations for those instructions should be disabled. And instruction fetching should start again when Halted register is set to 0 after the execution of

the branch instruction.

Due to presence of these three hazards during the pipelining of the instruction, the pipelining is never implemented in the excellent manner but it does gives us advantages over CISC processor where the implementation of pipelining is even poorer.

### **1.4 INSTRUCTION SET FORMAT**

A designer can control the distribution of bits in the instruction frame depending upon the applications to be performed and operations to be performed. Also, it can be designed in a way so that processor can run in various addressing modes. So, while deciding the position and number of the fields in each type of Instruction Frame, it was taken into account which bits were going to be used and which ones were not in each case, mainly so that there is no need to change their position in other configurations/ modes that shared that field (rd , rs , funct and rt). The following Figure 2 depicts the distribution of the bits in the instruction frame.

| N bits   | 3      | 1 | 4  | 4                        | 3                     |      | 4        | 13         |

|----------|--------|---|----|--------------------------|-----------------------|------|----------|------------|

| Type-R   | opcode | 1 | rd | rs                       | fund                  | ct   | rt       | Unused     |

|          |        |   |    |                          |                       |      |          |            |

| N bits   | 3      | 1 | 4  | 4                        | 3                     |      | 17       |            |

| Type-I   | opcode | 1 | rd | rs                       | funct                 | Dire | ct/immed | diate mode |

|          |        |   |    |                          |                       |      |          |            |

| N bits   | 3      | 1 | 4  | 4                        | 20                    |      |          |            |

| Type - X | opcode | 1 | rd | rs                       | Direct/immediate mode |      |          | e mode     |

|          |        |   |    |                          |                       |      |          |            |

| N bits   | 3      | 1 | 4  |                          |                       | 2    | 4        |            |

| Туре-Ү   | opcode | 1 | rd | rd Direct/Immediate mode |                       |      |          |            |

|          |        |   |    |                          |                       |      |          |            |

| N bits   | 3      | 1 | 28 |                          |                       |      |          |            |

| Type-J   | opcode | 1 |    | Direct/Immediate mode    |                       |      |          |            |

Figure 1.4 Distribution of the bits in the Instruction Frame.

| Opcode a | assignment | Funct assignment |     |  |  |  |

|----------|------------|------------------|-----|--|--|--|

| bgt      | 000        | Zero             | 000 |  |  |  |

| blt      | 001        | add              | 001 |  |  |  |

| bne      | 010        | sub              | 010 |  |  |  |

| beq      | 011        | and              | 011 |  |  |  |

| log      | 100        | or               | 100 |  |  |  |

| lw/sw    | 101        | not              | 101 |  |  |  |

| nop      | 110        | xor              | 110 |  |  |  |

| jmp      | 111        | hlt              | 111 |  |  |  |

Figure 1.5 Opcode and Funct assignment in Instruction Frame.

Each of the four immediate type distributions corresponds to a specific type with 2 bits that are used to identify them in the Processor: I = 00, X = 01, Y = 10, J = 11. When deciding the encoding of the opcode and the arithmetic and logical functions (funct field), this frame had to be re-used throughout the design as conditional jump share a bit that differentiates them from the rest of the instructions to use it directly in the control signals. And to save program bits, arithmetic-logical functions share opcode and use a funct field.

For Example, If the functions are to be 8 and fit in 3 bits, the load and store commands took advantage of the fact that they did not need to use the bit that differentiated immediate from non-immediate functions, and were joined in the same opcode, differentiating them precisely with that bit. It was also necessary to make a change in the encoding of the opcode because it was chosen for the address 000 for the beq function, which when resetting the microcontroller caused that the equal operands (they were 0 due to the reset), it always executed the jump command and did not it never worked. To decide the code of the "funct" field, it is only necessary to comment that when required only 6 functions, there were two valid codes that had no implementation. So it was decided to make those codes

give an output with the 32 bits at the logic level low to take advantage of this function in the ALU to generate a one in the zero output and thus implement by means of "funct" = 000 or "funct" = 111 the unconditional jumps. All instructions have an associated "funct" function, but only arithmetic operations indicate this function in a field of its plot, the rest are generated by the decoder according to the opcode it receives.

Bit "I" (4th bit) differentiates if it is immediate operation from non-immediate except for lw / sw which identifies precisely whether it is lw or sw. The default value for "I" bit is 0 which is non-immediate or lw where as I = 1 is immediate or sw.

The decoder generates the following control signals : RegWrite: which helps in activating the write input of the register bank. MemtoReg: which helps in indicating whether the command output comes from the ALU (0) or from memory.

(i) MemWrite: helps in activating the write input of the data memory.

(ii) Branch: helps in indicating if the order is a jump (1) or not (0).

(iii)Funct: will tell which ALU operation to be performed (it only generates it if opcode is not 100). Type : iindicates the type immediately, if it is 17 bits (00), 20 bits (01), 24 bits (10) or 28 bits (11).

(iv) ALUsrc: iindicates if the operation is on a register (0) or an immediate (1) [in the case of jump indicates if it is addressed to imm + reg (1) or only to imm (0)].

(v) mbs: by default it is always low level, except for conditional jump bgt and blt, since it indicates that the output that is evaluated at the output of the ALU to jump is the heavier bit instead of zero.

(vi) Output: by default it is always at a low level, except for the conditional jumps bne and bgt, since it inverts the signal that indicates whether the jump occurs, since for bne and bgt it would be 0 instead of 1.

Figure 1.6 Distribution of Instruction bits in the Datapath

### **1.5 ADVANTAGES OF RISC PROCESSORS**

1. Power Consumption: RISC processors consume and dissipate lesser power due to execution of simpler operation and dealing with the simpler hardware. The lesser the hardware, the lesser will be power consumption at device level. It has two advantages. Longer use of battery. No need form cooling of device. Smaller device design without noise.

2. Simpler hardware: All the components of processor are fabricated on a same chip. Smaller chips allow a semiconductor manufacturer to place more parts on a single silicon wafer, which can lower the per-chip cost dramatically.

3. Less area: The chip area used in the design of control unit is considerably reduced. More area is available for additional features.

4. Excellent performance: since in RISC processor, pipelining can be implemented in the excellent way. Number of cycle to execute a program drastically reduces leading to the excellent performance. Also, as no. of bit processing per second is increasing, the operations are performed at faster rate which increases the performance.

5. Addressing modes: RISC processors use less number of addressing modes since majority of the read and write operations are performed on the registers. Very few operations such as only load and store are the operations are done with memory. This is the main reason lesser ways of accessing the instructions are available since lesser operation are on memory.

6. Memory: These processors have lesser use of memory hence memory consumption to store the data is less. Only results of the computation and data on which computation is done are stored in memory. Instead large numbers of on-chip registers are used to store intermediate results. This is one of the reasons that these processors are faster since we know that interactions with memory can take multiple cycles.

#### **1.6 APPLICATIONS OF PROCESSOR**

1. Single board Microcomputers: simplest, cheapest general purpose processor based device with the minimum possible hardware and software attached. Used for universities and educational institutional for delivering training to the student and in industries for evaluation of the processor or for building prototype systems.

2. Terminals: Used for communication between a device and its user. Instructions and data to be fed into the computer are given by the help of keyboard and mouse, and the output of the computer is displayed on the monitor screen.

3. Personal computers: Used for playing games and learning simple programming and 16-bit processors are used for word processing, payroll, business accounts, medical record keeping and inventory control.

4. CAD Machines: execute powerful functions, with their increased word length and memory size. Used to make powerful microcomputer. Used as an engineering workstation and computer aided design (CAD) machines.

5. Communication: Used in a wide range of communication equipment. Used in digital telephone sets, telephone exchanges and modems. Widespread use of processors in radio, telephone, television and satellite communication, teleconferencing, railway reservation systems at the national level and air reservation systems at the international level.

6. Instrumentation: Processor based frequency meters, frequency synthesizers, function generator, spectrum analyzer and controllers are used in medical instrumentation, e.g. patient monitoring in intensive care unit, pathological analysis and the measurements of parameters like blood pressure and temperature.

7. Control: Controllers are used in home appliances such as microwave oven, washing machine. Used in controlling various PVT parameters such as speed, temperature and pressure.

8. Automation and Publication: Instead of typing, drafting and fling, processor based systems are applied in word processing, excel sheet operation, storing and retrieving the information from secondary devices. In publishing houses, used for automating phototypesetting directly from the output of the word process or system.

9. Consumers: Used in toys, entertainment equipment and home appliances with novel features.

### **CHAPTER 2**

# **MACHINE LEARNING PERSPECTIVES**

#### **2.1 INTRODUCTION TO MACHINE LEARNING IN VLSI**

Machine learning is a field growing rapidly which has brought up a revolution in the world by combining the advancements in Artificial Intelligence(AI) and data science that comes up with the systems and solutions which can learn from the prior experiences or preexisting information or data and improve without being implicitly and comprehensively programmed for the same i.e. evolving the methods or solutions without help of human intelligence which is more of developing its own intelligence to deal with a problem. In a nutshell, Machine Learning is the enabling the computers with human intelligence[4]. Machine learning revolves around finding and creating effective and efficient learning algorithms that assists the machines to analyze the available data and train itself to accurately predict for the unknown data samples.

In 1950's, a computer program for playing checkers was created by Arthur Samuel who worked with IBM in the AI domain. In this program, Samuel used a scoring mechanism using the locations of the pieces on board and tried calculating the probability of each side winning. Using a minimax technique, the program selects its next move and this technique eventually got developed into Minimax algorithm. A variety of mechanisms were also developed by Samuel to allow his program become better. His program remembered all the locations on the board that was valued for the reward function. His program had learned from the available data samples and predicted the reward function. Arthur Samuel was the first who coined the term Machine Learning [5]. ML is progressively developing in numerous spheres like Quantum computing, Robotics, Data Mining, VLSI, Automation, Signal Processing, Artificial Intelligence, Internet of Things (IoT), Medical,

Military etc. As ML is majorly working on neural networks and logical & computational algorithms, it makes a system both smartly accurate and highly beneficial. Due its accuracy, reliability, efficiency and ability to improve, ML is excessively effective over the human biological intelligence [6].

### **2.2 THE BASIC PARADIGM OF MACHINE LEARNING**

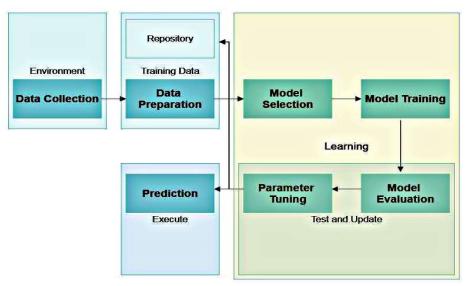

The basic model of Machine Learning consists of few steps starting from the Collection of data samples from the experiences. This is the preexisting data samples that help the machine to learn a given task. Data is conditioned by removing errors, missing values, repeated values etc. Next step chooses an algorithm model according to aptness with different tasks/problems /data.. Now, the model is trained iteratively followed by the evaluation in which the model is tested against unknown data samples. Further, tuning of the model parameter is done to increase the performance of the model proceeded with the final step of making the predictions in the real scenario. The performance in the tasks improves as the machines gains experience while executing the tasks and updating the model each time [5]. The basic model and its process has been represented in the block diagram Figure2.1.

Figure 2.1 Basic model of Machine Learning with Process Steps

### **2.3 AREAS OF MACHINE LEARNING**

ML has uncountable number of applications and it offers solutions to many real time issues. Some of the areas where machine learning is being progressively applied are mentioned below[5]: i)Face Detection and Recognition ii) Visual Perception iii)Classification iv)Adaptive Systems v) Modeling vi) Speech and Image processing vi)Automation vii) Problem Solving viii) Genetics ix)Anomalies Detection x)Games xi)Internet of Things (IoT) xii) Quantum computing xiii) Medical Diagnosis xiv) VLSI xv) Stock Market Trading xvi) Virtual Personal Assistant xvii) Online Fraud Detection xviii) Speech Recognition

### 2.4 MACHINE LEARNING ALGORITHMS

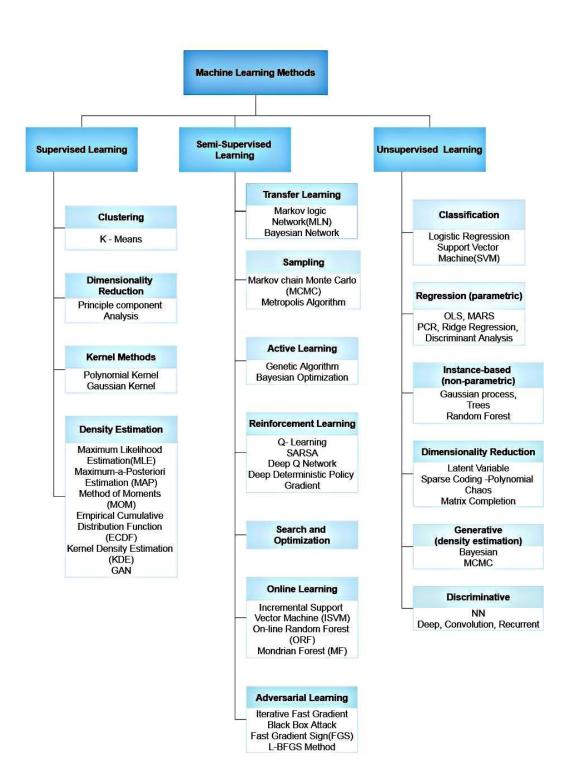

The highest level of abstraction in machine learning methods is based on the source of data/information that directs into the learning[7]. It is broadly classified into three categories. These are:

- i) Unsupervised Learning

- ii) Supervised Learning

- iii) Semi-Supervised.

In unsupervised learning, only input data is available and some structure or label needs to be developed to distinguish between the input data samples. In supervised learning, input and corresponding output data samples are available along with the structure/ labels. In semi-supervised learning, only some fraction of input data samples have corresponding output pairs i.e. few of them are labeled or structured[8]. Figure 2.2 represents the basic classification of machine learning methods and the algorithms used for learning in different methods.

Figure 2.2 Classification of Machine Learning Algorithms

A brief summary of different Machine Learning algorithms has been represented in the form of table that briefly lists the Uses, Advantages and its Drawbacks which can be useful in the appropriate selection of algorithm is given below.

| •  | Name of<br>Algorithm                     | Uses                                                                             | Advantages                                                                                                                                                                                           | Drawbacks                                                                                                                                                                            |

|----|------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | Gradient Descent                         | To minimize cost<br>function                                                     | Efficient , Stable<br>error gradient                                                                                                                                                                 | Never converges for too<br>high and too low learning<br>rate                                                                                                                         |

| 2. | Linear Regression                        | Models<br>continuous<br>variables,<br>prediction,<br>Data analysis<br>process    | Easier to<br>understand,<br>Easy to avoid<br>Over fitting                                                                                                                                            | Not a good fit for nonlinear<br>relationships, cannot handlo<br>complex pattern, over<br>simplifies real word issues                                                                 |

| 3  | Multi –Variate<br>Regression<br>Analysis | Used on number<br>of independent<br>variable and<br>single dependent<br>variable | Deeper insight to<br>relationship<br>between variables<br>Models complex<br>real time issues,<br>Realistic and<br>practical                                                                          | Complex, High knowledge<br>is required for modeling,<br>sample size needs to be<br>high, difficult to analyze                                                                        |

| 4  | Logistic<br>Regression                   | Used on<br>classification<br>problem                                             | Simple to<br>implement,<br>Ease of<br>regularization,<br>Efficient in<br>computation and<br>training, no<br>scaling required,<br>reliable                                                            | Unable to solve nonlinear<br>problem, prone to over<br>fitting, does not work well<br>unless all the variables are<br>identified.                                                    |

| 5  | Descion<br>Tree                          | Used on<br>regression and<br>classification<br>problem                           | suitable for<br>regression<br>Classification<br>problem, easy to<br>interpret and<br>handle, capability<br>to fill missing<br>values, high<br>performance due<br>to efficiency of<br>tree traversal. | unstable, difficult to contro<br>size of tree, it may be pror<br>to sampling error and it<br>gives a locally optimal<br>solution- not optimal<br>solution. Prone to Over-<br>fitting |

**Table 2.1** Machine Learning algorithms and their Uses, Advantages and its Drawbacks.

| s. | Machine Learning Algorithms |                                                                 |                                                                                                                                                                                                                                            |                                                                                                                                                                                                                              |  |  |  |  |  |  |

|----|-----------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| no | Name of<br>Algorithm        | Uses                                                            | Advantages                                                                                                                                                                                                                                 | Drawbacks                                                                                                                                                                                                                    |  |  |  |  |  |  |

| 6  | Support<br>Vector Machine   | Used on<br>regression and<br>classification<br>problem          | Handles both<br>semi structured<br>and structured<br>data, can handle<br>complex<br>function, less<br>probability of<br>over fitting,<br>scales up the high<br>dimensional data.<br>does not get stuck<br>in local optima.                 | Low performance in large<br>data sets, difficult to find<br>appropriate kernel function<br>Does not work in noisy<br>dataset. No probability<br>estimates. Difficult to<br>understand                                        |  |  |  |  |  |  |

| 7  | Bayesian<br>Learning        | To handle<br>incomplete<br>data sets.                           | Prevents over-<br>fitting, no<br>removal of<br>contradictions<br>required.                                                                                                                                                                 | Prior selection is not easy.<br>distribution can be<br>influenced by prior, wrong<br>predictions possible,<br>complex computation                                                                                            |  |  |  |  |  |  |

| 8. | Naïve Bayes                 | Used on binary<br>and multi-class<br>classification<br>problems | easy to<br>implement, gives<br>good performance<br>,<br>less training data<br>required, scales<br>linearly with<br>predictors and<br>data samples,<br>handles<br>continuous,<br>discrete data.<br>insensitive to<br>irrelevant<br>features | Model often outperforms,<br>too simple, cannot be<br>applied directly, requires<br>retraining, stops scaling<br>when data points are high,<br>more runtime memory<br>required, complex<br>computation for more<br>variables. |  |  |  |  |  |  |

| 9. | K Nearest<br>Neighbour      | Used on<br>classification<br>problems                           | Simple and easy<br>to implement,<br>cheap and<br>flexible<br>classification,<br>suitable for multi<br>modal classes                                                                                                                        | Expensive, computation is<br>distant and intense, less<br>accuracy, no<br>generalization, data large<br>sets                                                                                                                 |  |  |  |  |  |  |

### 2.5 DRAWBACKS OF MACHINE LEARNING

Despite Machine learning being very effective and offering a technical advancement in various domains, it has numerous drawbacks related to a specific problem or a particular machine learning algorithm. The drawbacks of ML are mentioned as following.

(i) **Volume of Data** : When the training and learning process is carried out, a large volume of data is required and used. The data used in this process should be non-partisan and unbiased consistency and high quality which might need the generation of more data and hence, more time, space and power is required for better quality of results.

(ii) Authentic and Dependable Resources: are required in case learning algorithms show time consuming errors and complexity. It is very important to check that the algorithms that has been assisted in the process is producing the desired output or not because to get the desired output we need an accurate learning algorithm with high performance.

(iii) Selection and availability of accurate algorithm : is also a challenge.Machine learning still needs a lot of improvements in algorithms and the software that performs the analysis on datasets.

(iv) Moreover, due to large volume of data, **Error susceptibility** is also high which needs to be taken care of while using a particular dataset and learning algorithms.

(v) **Drawbacks related to a specific machine learning algorithm** such as nonlinearity, sampling errors, overfitting, noisy datasets, incomprehensible datasets, low performance, complex and expensive computation, insufficient runtime memory etc.

### **CHAPTER 3**

# LITERATURE SURVEY - MACHINE LEARNING ALGORITHMS

The power dataset of RISC Processor is used in the implementation of five different Machine Learning Algorithms to find the Accuracy, precision and Recall. These Five algorithms are studied and summarized as follows.

### **3.1 SUPPORT VECTOR MACHINE**

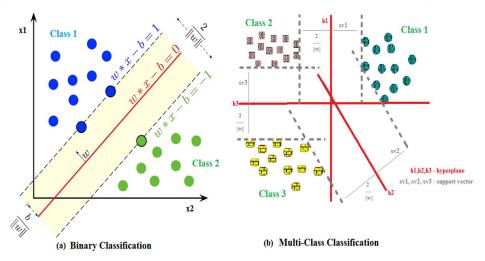

For the statistical analysis of classification based power dataset, an appropriate ML algorithm can be Support Vector Machine (SVM) [9]. It is applicable to both binary and multi class dataset. To define a Binary classification problem using SVM, a hyper-plane is constructed and optimized. The optimization of this hyper-plane involves the maximization of margin separating the two different classes [9]. SVM dealing with multiple classes combines many binary classifiers. Figure 5 shows the two types of classification where support vector machine is applicable.

Let us assume that a set of n number of data vectors are available which can be written in a form (Xi,Yi) where i=1,2,...,n given that Yi belongs to the range between -1 to 1 and Xi belongs to R<sup>N</sup>. Here, X denotes the data vector, Y denotes the binary class and i denote the i<sup>th</sup> number of data vector or binary class.

### Figure 3.1 Types of SVM Classification

This type of SVM classification aims at constructing the following optimization function for the hyper plane that accurately distinguishes the difference between the class label/tag of input data sample to be tested X[10].

$$Y(X) = sgn[w. \varphi(X) + b]$$

(1)

such that  $\varphi(X)$  is a mapped function of input data X. It is nonlinear in nature and maps to high dimensional characteristics space of available data. The difference between two support vectors is 2/||w||.We obtain the optimization by maximizing the difference between the support vectors.

The general separating hyper-plane equation where input data is lying on the hyper plane itself, is written as  $w \cdot \varphi(X) + b = 0$ . When two classes are linearly separable, the expression for two separating hyper plane are written as w.Xi + b is greater than or equal to +1 given that Yi is +1 and w .Xi + b is less than or equal to -1 given that Yi is -1[11]. On combining both the conditions, we get the following expression.

$$Yi(w \cdot Xi + b) - l \ge 0 \tag{2}$$

and its optimization is obtained by  $\min\{(1/2)||w||^2\}$ . But, when the classes cannot be separated by linear expression, we need to modify the hyper plane expression as well as its optimization by using slack variable which helps in penalizing the nonlinearity problem in separating the two classes. The modified hyper plane expression is given as

$$Y(w \cdot Xi + b) > 1 - \xi i. \tag{3}$$

The optimization obtained from modified expression is given as :  $\min[\{(1/2)||w||^2\}+P\sum \xi_i]$ , where  $P\sum \xi_i$  is the penalty term [11] and  $\xi_i$  is the slack variable in which value of i=1,2,...,n. these parameters are selected by the user depending on their requirements. The more the value of C, the higher is the penalty for wrongly classifying the data [10].

#### **3.2 ISOLATION FOREST (IF) ALGORITHM**

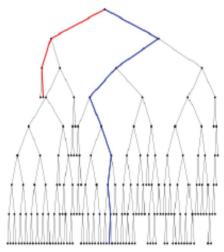

The Isolation Forest (IF) algorithm is applied when at least one class is an anomaly i.e. one class is very small in proportion to the other class in terms of numbers of samples or size and there is notable difference between the two classes[12]. While constructing a random tree, the instances or attributes of the entire dataset is partitioned in a repetitive manner until all the attributes/instances are completely separated from each other. In such a case when tree is generated by partitioning, the anomalies will have distinguishable shortest path among the entire dataset because anomalies will be detected in smaller number of partitions only. So, they are the fastest one to be detected when a large number of random trees are produced together, also called Random Forest Trees [14].

Consider an initial node T, which is called to be a parent node or root node in an Isolation Tree. The node T can be an exterior-node possessing no sub nodes or an interior-node having performed 1 test and 2 sub nodes, say  $(T_1, T_r)$ . An assessment is carried where the attribute value of an instance (m) and attribute value of a randomly chosen instance often called split value(s) are compared. Depending on the condition- m < s, it will segregate the data into two data points' i.e  $T_1$  and  $T_r$ . This, building up of isolation tree is performed with repetitive segregation of entire data sample X by randomly choosing an instance and respective split value considering a data sample X where X has n number of instances/ attribute. The process is repeated till the tree attains a certain height or the data sample left = 1. An isolation tree can simply be called a binary tree in which every node has either zero or two sub nodes. If all instance/attributes are mutually exclusive and separable, then instance/attribute are isolated as root node and the total count of root node is equal to the total number of instances in the dataset X i.e.  $n_r$  and  $n_r - 1$ is the no. of sub nodes.  $2n_r - 1$  is the total number of nodes of an isolation Tree. Memory required for isolation forest algorithm grows in a linear fashion with n<sub>r</sub>.

[14].Path Length of isolation tree is the number of branches covered while moving from root/main node of the tree to the last terminating node of the tree[12].

(a) Representation of a single

(b) Representation of a full forest where each radial line corresponds to a tree.

**Figure 3.2** (i) Representation of a tree in a forest and as a radial line [13], (ii) Working of LOF algorithms [16].

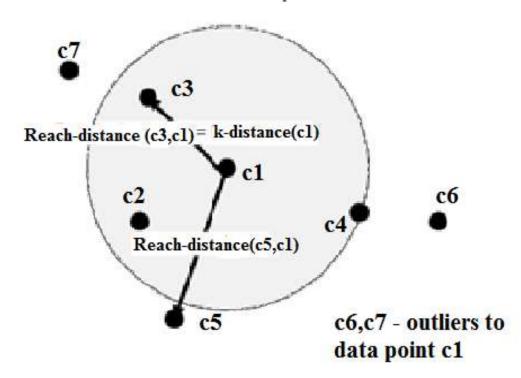

### **3.3 LOCAL OUTLIER FACTOR (LOF) ALGORITHM**

Local Outlier Factor (LOF) algorithm is used to demarcate the outlier samples from the usual or ordinary samples in the dataset which is done with the help of comparison of dataset points. To ascertain whether a given sample point is outliers or not, we calculate the deviation of data points from the other and the data point with less density is labeled as outlier. Normal data is given the output as '1' and outlier as '0' [15]. For example- noise detection in pixels, fraud detection in ATM transaction [17]. The distance between the data points are measured by term kdistance (k-dis(c5))of a sample point c5 which is stated as the Euclidean distance between data points c5 & c1 i.e. d(c1.c5) such that at least k data points have d(c1,ci) less than d(c1,c5) where i ={2,3,4,..n} and k should be greater than one[18].

K-distance neighborhood of a sample/data point say c1 is the k-distance neighborhood of c1 consists of every data point in the sample space which are less than k-distance (d (c1, c5)) distant apart from c1 as represented all the data points in a circle in figure 3.2(ii). k reach-distance (c1, c5). Local Outlier Factor (LOF) of a sample/data point say c1. is can be defined as the mean of the ratio of c1's local reachability density and data points in k nearest neighbors e.g. c2, c3, c4, where local reachability density of c1 is {mean(k-reach-distance of data points)}<sup>-1</sup> which are in the k-distance neighborhood of the data point c1 i.e. c2, c3, c4 etc. to the data point c1 itself and k-reach-distance (c1,c5) is defined as real distance from c5 to c1[18].

### 3.4 K-NEAREST NEIGHBOR(KNN) CLASSIFIER

The most commonly applied machine learning algorithm is K-Nearest-Neighbor classifier for the classification based problems. This algorithm is very simple, efficient and has high accuracy [19]. In KNN, the classification is done on the basis Euclidean distance. The data points close to the Kth nearest neighbor are given the label of Kth neighbors group. The only disadvantage of KNN classifier is that when the dataset volume is huge, it consumes more time to find out the K-nearest neighbors [20][21].

The working of K-Nearest Neighbor classifier is elucidated in accordance with the following steps: first step is to pick minimum number of neighbors say K. Second step is to determine the Euclidean distance of those K no. of neighbor data points. Third step is to consider only the K nearest neighbors. Next step is that out of these K neighbors, segregate the data points categorizing them according to proximity and for each new category, set new data points considering the fact of keeping neighbor as maximum as possible. Last step makes the KNN classifier ready for a use as a model. While choosing the value of K, following points should be considered: If value of K is very small, the model becomes sensitive to outliers and If value of K is large, classifier may include in the neighborhood, those data points which are part of other categories. KNN Classifier can be improved on accuracy by adding weights to the sample features and adjusting the value of K[21].

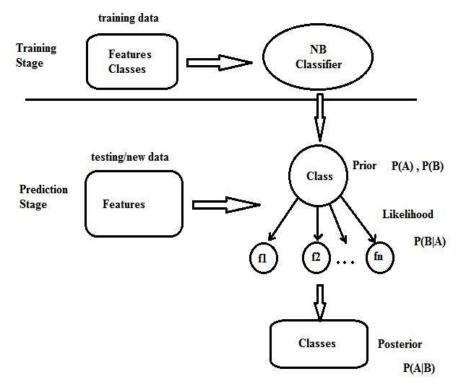

### 3.5 NAÏVE BAYES(NB) ALGORITHM

NB is a plain classification machine learning algorithm which uses mathematical Bayes theorem [23] and has higher accuracy [22]. Naïve Bayes theorem is of mainly three types. i)Multinomial ii)Gaussian iii)Bernoulli[24].

It detects and predicts the internet traffic while assuming that that the sample features/attributes are mutually exclusive to each other i.e. independent of one another [26]. Every machine learning algorithm has two main stages i.e. training the model and testing/predicting the unknown sample using the trained model. This trained model here works on Naïve Bayes algorithm [25]. In the initial training process, data set comprising of input features/attributes and selected output is fed

to the model implementing NB classifier algorithm. From this training data, NB Classifier calculates the independent probabilities e.g. P(A), P(B) of the data whose output class has to be predicted i.e. target data. In the next step, dependent probabilities of input attributes of data set is calculated with the help of already calculated target data probabilities e.g.(A|B) or P(B|A) etc. Next is the testing phase where data to be tested i.e. test data's new input attributes are fed to the NB classifier model. Finally, the probability of output class of test data given that probability of input attribute of test data is already known; P(A|B), is calculated. The expression for the posteriori probability is P(A|B) given as

$$P(A|B) = [P(B|A)*P(A)]/P(B)$$

(4)

Such that P(B|A) is the likelihood probability; P(A) and P(B) are the independent probabilities in the expression 4[24].

Figure 3.3 Algorithm representation for Naïve Bayes classifier[24]

Naive Bayes(NB) Classifier have good speed and performance since they take lesser starting up time and are accurate in producing results.

### **Performance Metrics**

Every machine learning algorithm is evaluated on the basis of some parameters also called performance metrics that measures how a machine learning algorithm is performing on particular problem or dataset. These parameters are named as Precision, Recall, F1-Score and support. Let us briefly understand their meaning.

With respect to the power dataset we have used, power consumption more than 3000W is beyond tolerable limits and it is unacceptable.

We have divided the power dataset as class '0' when power is under tolerable limit and class '1' when beyond the tolerable limit. When data is predicted as class'0' when it was actually class '0', it is called True Positive (TP). When data is predicted as class'1' when it was actually class '0', it is called False Negative(FN). When data is predicted as class'0' when it was actually class '1', it is called False Positive(FP). When data is predicted as class'1' when it was actually class '1', it is called True Negative(TN).

i) **Precision (P)**: It is the ratio of True Positive to the sum of True Positive and False Negative.

ii) **Recall (R):** It is the ratio of True Negative to the sum of True Negative and False Positive.

iii) **Support (S):** Number of samples in Class '0' i.e. Total number of power data samples which are under tolerable limit in Target.

iv) F1-Score: It is the harmonic mean of the precision and recall. i.e.  $\{2^*(P^*R)\}(P+R)$

### CHAPTER 4 TOOLS USED

### **4.1 INTRODUCTION TO VERILOG HDL**

Verilog HDL is widely used as design description language for field programmable gate arrays and application specific integrated circuits in the automation of electronic design circuits. Verilog HDL is a generic language which needs a simulator to run the design code. Due to its generic nature, it is quite possible to code a test bench which verifies and checks whether the design code written is working correctly or not.

### **4.2 FEATURES OF VERILOG**

Following are the major features and capabilities that Verilog provides which makes itself different from other hardware languages.

- Exchange medium between chip vendors and CAD Tool users.

- Open Source, comprehensible, readable to machine.

- Flexible design methodologies: top to down, bottom to up, mixed.

- Supports hierarchy.

- Not technology specific, but supports the technology related features.

- Support various hardware technologies.

- Synchronous and asynchronous timing models supported.

- An IEEE and ANSI standard; hence models are portable.

- Three different description styles: structural, behavioral, data flow supported.

- Test benches allowed to be written to test other Verilog models.

- A wide range of abstraction level is supported.

- It does not, support modeling at or below the transistor level.

- Propagation delays, min max delays, setup and hold timing, timing constraints, spike detection can be described.

There are several abstraction levels in which a digital circuit can be designed which are shown in Fig.4.1. The lowest level from where we start designing a digital circuit is the transistor level; it deals with the discrete transistors. The transistors are connected with each other to make a circuit. Gate level is higher level in the abstraction where we combine logic gates to form the circuit. With the use of logic gates, standard combinational as well as sequential circuits can be made.

These combinational and sequential circuits are put together to form the larger circuits such as processor. It becomes an easier to solve a digital problem when we solve it from lower level to higher abstraction level. The RTL consists of data path and control circuit along with their connections that makes the data flow within these functional units. Behavioral level is the highest level of abstraction which describes the operation of the larger circuits.

#### Levels of representation and abstraction:

Figure 4.1: Level of Representation and Abstraction [28]

### **4.3 SIMULATION**

The stimulation is done with the help of test benches. They check and tell whether the output generated is correct or not. The block representation of stimulation is shown in Figure 4.2.

### 4.4 ADVANTAGES OF VERILOG

The main advantages of Verilog can be listed as following:

- Description of a concurrent system which is not possible in other programming languages like Pascal, BASIC, C, low level assembly language.

- Translates the gates and wires of CPLD or FPGA which no other language can do.

- It is just like an actual hardware being configured.

Figure 4.2: FPGA Design Flow Overview[27]

### 4.5 XILINX VIVADO

#### 4.5.1 INTRODUCTION TO XILINX VIVADO SOFTWARE

XILINX VIVADO is a software tool mainly used for the synthesis, simulation, analysis and implementation of digital circuit design. It helps the designers to simulate and synthesize the digital designs, performing the analysis on timing constraint and examining the RTL schematics. It also helps simulating a design's response to various stimulus, and also configure the targeted device. It supersedes the Xilinx ISE with added feature SoC development and High Level synthesis. Vivado came up in April 2012[29] and is an integrated design environment with system to IC level tools which is built on a shared data paradigm and a common debug environment. Vivado incorporates ESL design tools for synthesis and verification of C based IP; standard packaging of RTL IP for reuse; standard IP integration of all kinds of system blocks; and their verification[30].

- Vivado HLS helps C, C++ and SystemC programs to be directly targeted into Xilinx devices without the need to manually create RTL. Vivado HLS increases designer's productivity, and supports C++ classes, templates, functions and operators[31].

- Vivado Simulator bolsters mixed language like Tcl scripts, IP and its verification.

- The Vivado IP Integrator combines and configure IP from the large Xilinx IP library.

- Vivado Tcl Store develops add on to Vivado, and used to add and change Vivado's capabilities. Vivado is based on Tcl scripting language. Internal functions can be called and controlled using Tcl scripts[32].

## <u>CHAPTER 5</u> SIMULATION RESULTS

### **5.1 EXRIMENTAL SETUP**

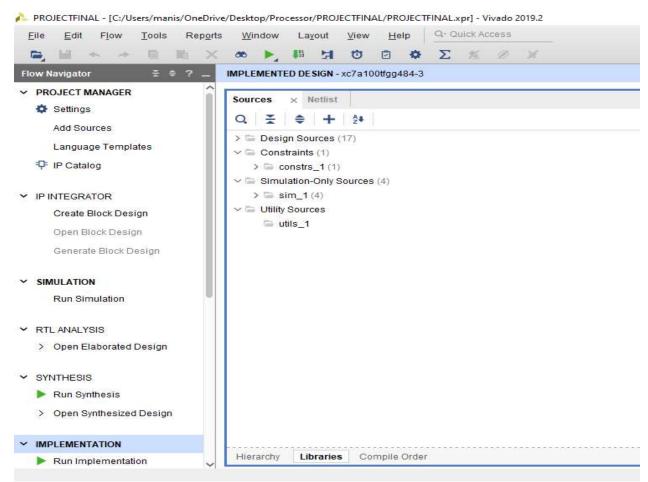

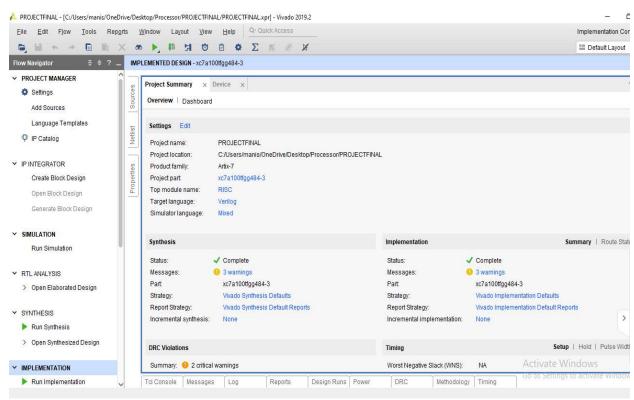

The RTL code for the RISC Processor is written in Verilog Hardware Description Language and the software used for its behavioral simulation, RTL analysis, RTL synthesis and schematic generation and design implementation is XILINX VIVADO 2019.1 version.

Figure 5.1 Simulation Result of 32 bit RISC Processor

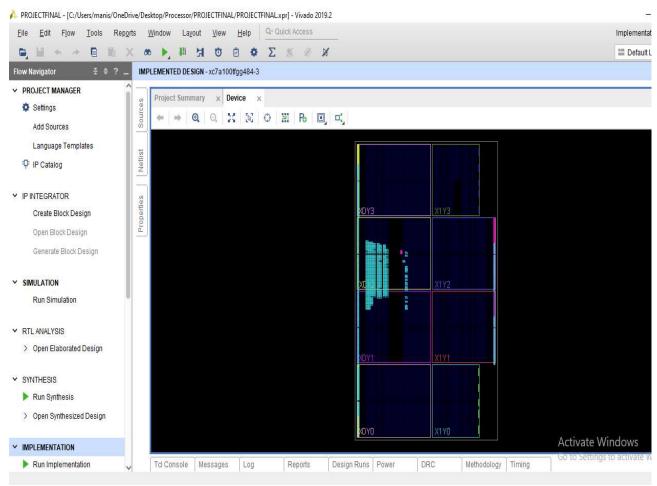

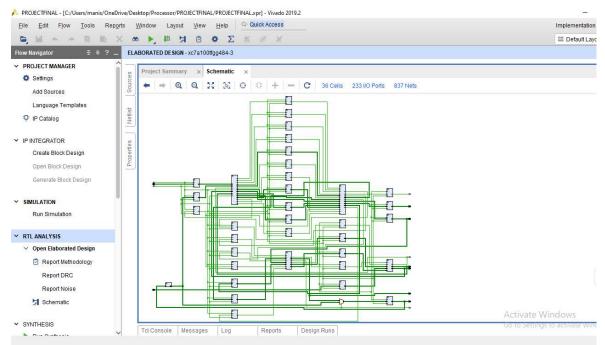

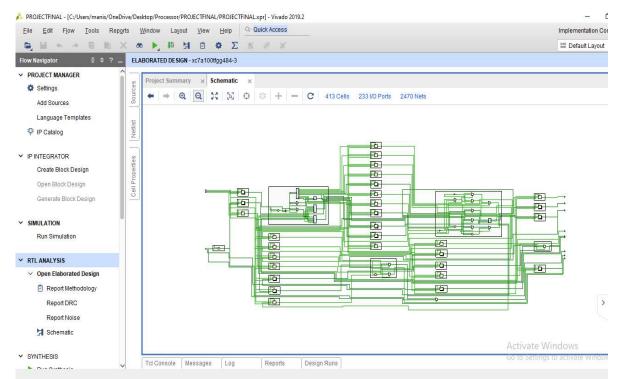

Figure 5.1 shows that 32 bit RISC processor so designed is working correctly and the simulation results are generated. It is just to show that this RTL code is the basic model of RISC Processor and its simulation results showing that the RTL code is bug/error free. On the analysis of RTL code, the elaborated design of the RTL schematic is shown as in the figure 5.2. The RTL code synthesizes to a circuit as shown in the figure depending upon constraint files and design code files

depicting number of logic cells and their interconnections when implemented on a FPGA.

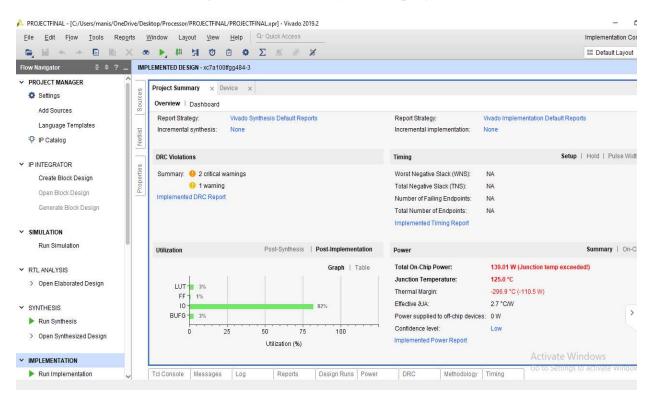

**Figure 5.2** Register Transfer Level schematic of RISC Processor after implementation stage.

After the design and simulation of 32 bit RISC Processor, its power reports has been generated giving variety of inputs such as Output Load, Junction Temperature, Ambient Temperature,Effective SJA, Airflow, Heat Sink, Theata, Board Selection, No. of board layers, Board Temperature , Thermal Margin etc. The output report consisted of Logic power, On chip dynamic power, Static power and I/O power, Total on chip power, signal power, class etc. All the inputs and outputs given here are the features/attributes of a data sample. Approximately 50 data samples has been recorded and maintained in .csv file.

| nalyze power co<br>c7a100tfqq484-3               | nsumption based | on the implem | ented desig | in and part    | 2  |

|--------------------------------------------------|-----------------|---------------|-------------|----------------|----|

|                                                  | ~               |               |             |                |    |

| Res <u>u</u> lts name:                           | power_1         |               |             |                | 0  |

| Environment                                      | Power Supply    | Switching     | Output      |                | CI |

| Device Setting                                   | IS              |               |             |                | î  |

| Temp <u>g</u> rad                                | le:             | extended      | ~           |                |    |

| Pro <u>c</u> ess:                                |                 | typical       | ~           |                |    |

| Environment S                                    | Settings        |               |             |                |    |

| Output Loa                                       | id:             |               | 25 🌲        | pF [0 - 10000] |    |

| Junctio                                          | n temperature:  |               | 50 🌲        | °C             |    |

| Ambient temperature:                             |                 |               | 49.57 🌲     | °C             |    |

| Effective &JA:<br>Airflow:<br>Heat sink:<br>&SA: |                 |               | 3.768       | °C/W [0 - 100] |    |

|                                                  |                 | 250           | ~           | LFM            |    |

|                                                  |                 | custom        | ~           |                |    |

|                                                  |                 |               | 4.6 🌲       | *C/W [0 - 100] |    |

| <u>B</u> oard sele                               | ection:         | Custom        | ~           |                |    |

| Number of                                        | board layers:   | 4to7 (4 to 7  | Layer: 🗸    |                |    |

| JB:                                              |                 |               | 6.8 🔔       | °C/W [0 - 100] |    |

Figure 5.3 Power Report and required Input features.

These data samples are used as training sample for the analysis of power dataset and implementation of ML Algorithms to obtain their comparative performance measuring parameters such as macro average and weighted average of Precision, Recall, F1-Score and Accuracy.

Implementation of Machine Learning :

The first step is the collection of data samples. Here, the collection of different types of power consumption is the data on which the machine learning algorithm will be applied. A comma separated file is created from the different input of power samples. This data is analyzed first hence is called power analysis of RISC

Processor. Figure 5.4 represents the data information mainly the input features or attributes and their related power outcomes included in the dataset created from various power samples of RISC Processor.

|     | data.info() |  |

|-----|-------------|--|

| F 1 | uata.Into() |  |

| #  | columns (total 21 columns):<br>Column | Non- | Null Count | Dtype  |

|----|---------------------------------------|------|------------|--------|

|    |                                       |      |            |        |

| 0  | s. no                                 | 50 r | non-null   | int64  |

| 1  | output Load                           | 50 r | non-null   | int64  |

| 2  | Junction Temperature in C             | 50 r | non-null   | float6 |

| 3  | Ambient Temperature in C              | 50 r | non-null   | float6 |

| 4  | Effective SJA in C/W                  | 50 r | non-null   | float6 |

| 5  | Air Flow in LFM                       | 50 r | non-null   | int64  |

| 6  | Heat sink                             | 50 r | non-null   | int64  |

| 7  | Theata SA in C/W                      | 50 r | non-null   | float6 |

| 8  | Board Selection                       | 50 r | non-null   | int64  |

| 9  | No. of Board Layers                   | 50 r | non-null   | int64  |

| 10 | Theata JB In C/W                      | 50 r | non-null   | float6 |

| 11 | Board Temperature in C                | 50 r | non-null   | int64  |

| 12 | Total On Chip Power in W              | 50 r | non-null   | float6 |

| 13 | Junction Temperature in C.1           | 50 r | non-null   | int64  |

| 14 | Thermal Margin in C                   | 50 r | non-null   | float6 |

| 15 | Effective Theata SA inC/W             | 50 r | non-null   | float6 |

| 16 | On chip Dynamic power in W            | 50 r | non-null   | float6 |

| 17 | Signal Power in W                     | 50 r | non-null   | float6 |

| 18 | Logic Power in w                      | 50 r | non-null   | float6 |

| 19 | I/O power in W                        | 50 r | non-null   | float6 |

| 20 | Static Power in W                     | 50 r | non-null   | float6 |

Figure 5.4 Data Information of Power samples of RISC Processor

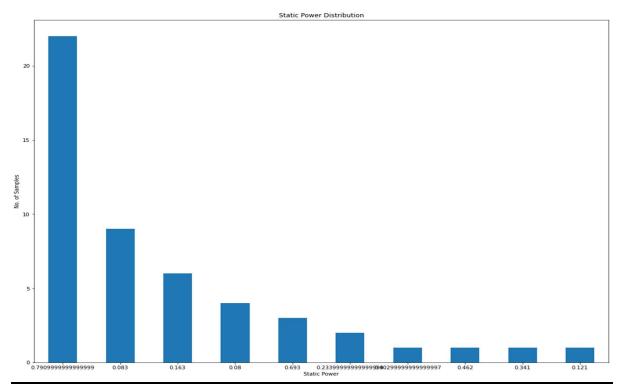

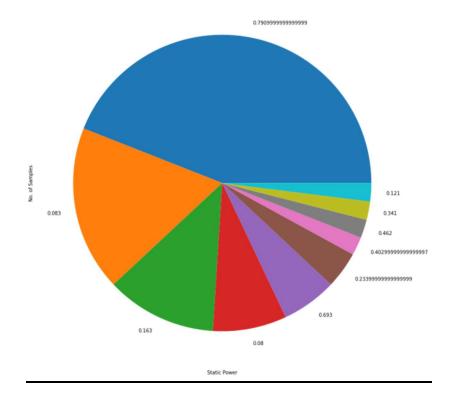

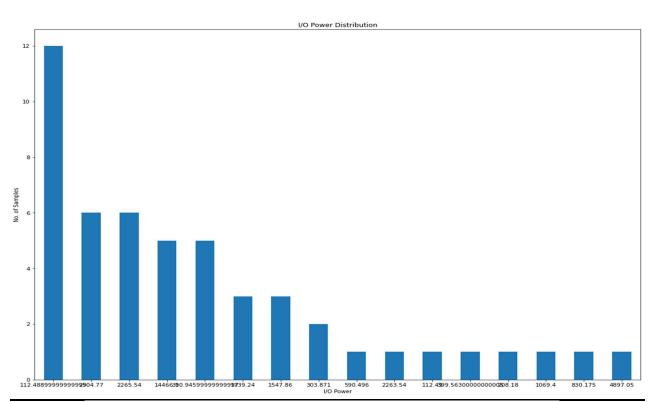

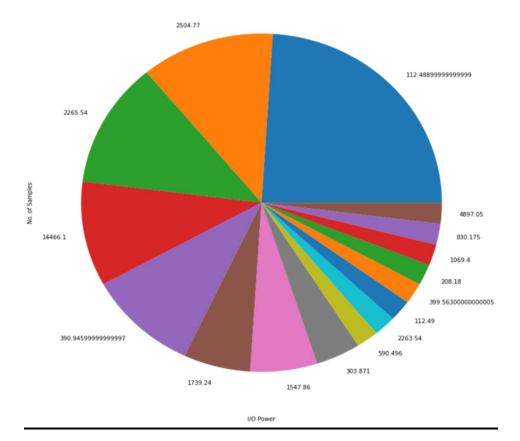

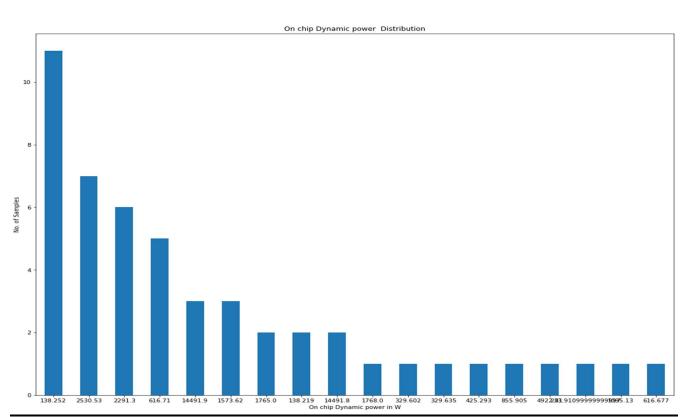

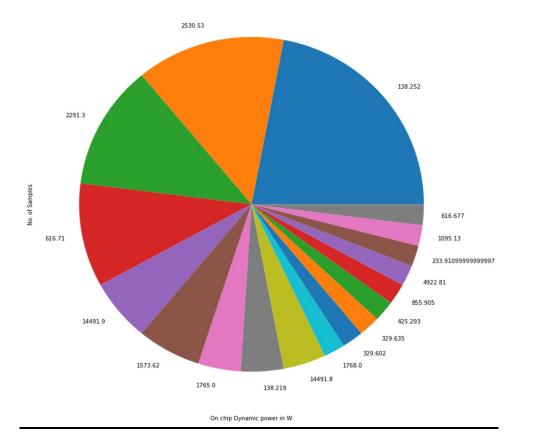

There are five types of power dissipation calculated and recorded from VIVADO which can enumerated as static power dissipation, I/O power dissipation, Signal Power dissipation, Logic Power dissipation and On chip power dissipation. Further Figure 5.5 to Figure 5.9 all the types of power are represented in the form of bar and pie. They represent what is the power consumption in majority of the samples.

### **5.2 EXPERIMENTAL RESULTS**

Static Power Distribution

Figure 5.5 Static power distribution of RISC Processor

I/O Power Distribution

Logic Power in w Distribution

The three main type of powers out total five power are discussed below.

(i) Static Power (ii) Input/Output Power (iii) Logic Power

Figure 5.5 shows the distribution of static power consumed by the RISC Processor. Static power consumption by RISC processor is the power consumed by Processor when there are no switching activities taking place. This power is mainly due to the leaky current when the processor is in OFF state. Maximum number of samples consuming static power equal to 0.790 W, rest of the samples consuming 0.043 W, 0.143W, 0.08W, 0.693W and so on. There are various input features on which static power depends. This variation in Static power consumption depends on what input was given to generate the power report of RISC Processor.

Similarly, for the Input/Output power distribution among the samples is shown in Figure 5.6. I/O power is power consumed by the inputs and output ports of the processor while transitioning the signal from high to low or low to high. Maximum number of samples consuming 112.489W and rest of the samples consuming 2504.77W, 2265.54W, 14466.1W, 390.95W, 1739.24W and so on. Maximum I/O power reaches 14466.1W under some input conditions.

Figure 5.7 shows Logic Power distribution of the RISC Processor. Logic power consumed by the processor is the power consumed by the logic implementation present inside the processor. Here, all the samples consume nearly same amount of power i.e 10.990W and 10.995W treated as differently but not much difference in the logic power consumption can be inferred that it does not much depend upon the variation of input features in the power report of the processor. This processor consumes same logic power i.e. it depends on processor internal implementation rather than outside application of the various inputs.

Signal Power

On chip Dynamic power Distribution

Two more power out of total five powers are described below.

(iv) Signal Power (v) On chip Dynamic Power

Figure 5.8 shows the distribution of signal power of RISC processor that what amount of power is consumed by the signals in the processor. Here, all the samples consume fixed amount of signal power i.e. 14.735W which can also infer that signal power of the processor does not vary with the variation in the input features. It is fixed under all conditions.

Figure 5.9 shows On chip dynamic power distribution of RISC processor. It is the power consumed by the processor during the switching activities caused to the transistors used in the implementation of the processor circuit. Maximum numbers of samples consume 138.252W On chip dynamic power. Rest of the samples consumes 2530.53W, 2291.3W, 616.71W, 14491.9W, 1573.62W, 1765W and so on. The maximum and unacceptable on chip dynamic power consumed is 14491.9W. The variation in the on chip dynamic power consumption depends upon the variation in the values of Input features.

### Factors affecting various power of the processor:

There are two factors on which power of the processor depends and have been listed as (i) Output Load Capacitance (ii) PVT conditions – Junction Temperature (i) Output Load Capacitance (fF):