# STUDY AND IMPLEMENTATION OF THRESHOLD TYPE BINARY MEMRISTOR EMULATOR

#### A DISSERTATION

### SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

## MASTER OF TECHNOLOGY IN VLSI DESIGN & EMBEDDED SYSTEMS

Submitted by:

## JULI KUMARI ROY

## 2K19/VLS/07

Under the supervision of

## PROF. NEETA PANDEY

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

**JUNE, 2021**

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **CANDIDATE'S DECLARATION**

I, Juli Kumari Roy, Roll No. 2K19/VLS/07 student of MTech (VLSI & Embedded systems), hereby declare that the work presented in this thesis designated "**Study and implementation of Threshold Type binary memristor emulator**" is done by me and submitted to the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi in fractional fulfillment of the prerequisite for the award of the degree of Master of Technology.

This is an original research work and not copied from any source without acknowledge them with proper citation and has not previously published anywhere for the award of any Degree, Diploma Associate ship, Fellowship or other similar title or recognition.

Juli Kumali Roy

Place: Delhi Date: 25-08-2021 (Juli Kumari Roy)

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

## **CERTIFICATE**

I hereby certify that the Project Dissertation titled "**Study and implementation of Threshold Type binary memristor emulator**" which is submitted by **Juli Kumari Roy, 2K19/VLS/07**, to the Department of Electronics & Communication Engineering, Delhi Technological University, Delhi in partial fulfillment of the prerequisite for the award of the degree of Master of Technology, is a record of the project work carried out by the student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date: PROF. NEETA PANDEY Department of ECE Delhi Technological University

## **ACKNOWLDEMENTS**

It gives me immeasurable pleasure to express my deepest sense of gratitude and sincere appreciation to my supervisor, Professor Neeta Pandey, who has the substance of a intellect. She persuasively encouraged and guided me to be professional and do the work in a proper manner. The objective of this project would not have been completed without her persistent help. Her useful suggestions during this whole work and supportive behavior are sincerely acknowledged.

I would like to acknowledge the support of my family and friends. They helped me a lot directly and indirectly during this project work.

Juli Kumeri Roy

Date: 25-08-2021

JULI KUMARI ROY

2K19/VLS/07

#### **ABSTRACT**

Memristor is a fourth basic circuit element which depicts the relationship between charge (q) and flux ( $\phi$ ). There is a lean presence of fabricated memristors in the market due to complexities involved in its processing. Therefore, significant research efforts are made towards presenting emulators that mimic memristor behaviour.

In this project, new memristor emulator circuit has been designed based on DVCC and CFOA. The emulator consists of subtractor, inverting amplifier, integrator, bistable circuit, inverting summing amplifier, multiplier and voltage into current to ensures floating characteristic of the emulator. The subtractor senses the memristor voltage. The diodes in anti-parallel configuration provides threshold sensitive behaviour of the emulator which may be adjusted by resistor ratio. The integrator ensures the dependence of memductance on history state. The bistable circuit provides non-volatility and bistable properties of the emulator. The proposed circuit uses lesser number of resistor than the available binary memristor circuit. The proposal has been verified through Pspice simulations.

## **TABLE OF CONTENTS**

| Candio | late's D               | eclaration                     | i   |

|--------|------------------------|--------------------------------|-----|

| Certif | ficate                 |                                | ii  |

| Ackn   | owledge                | ement                          | iii |

| Abstr  | act                    |                                | iv  |

| Table  | of Con                 | tents                          | v   |

| List o | f Figure               | es                             | vii |

| List o | f Tables               | 8                              | ix  |

| List o | f abbre                | viations                       | X   |

| Chap   | ter 1                  | Introduction                   | 1-3 |

| 1.1 Ba | ackgrour               | nd                             | 1   |

| 1.2 O  | bjective               |                                | 3   |

| 1.3 Oı | ganizati               | on of Thesis                   | 3   |

|        |                        |                                |     |

| Chapt  | Organization of Thesis |                                |     |

| 2.1    | The C                  | CFOA                           | 4   |

| 2.2    | Basic                  | circuit applications of CFOA   | 4   |

|        | 2.2.1                  | Inverting Voltage Amplifier    | 5   |

|        | 2.2.2                  | Noninverting Voltage Amplifier | 5   |

|        | 2.2.3                  | The Summing Amplifier          | 6   |

|        | 2.2.4                  | The Subtractor Amplifier       | 6   |

|        | 2.2.5                  | Integrator                     | 7   |

|        | 2.2.6                  | The bistable circuit           | 8   |

| 2.3    | Simul                  | ation Results                  | 9   |

| Chap      | oter 3      | Differential Voltage Current Conveyor            | 13-16 |

|-----------|-------------|--------------------------------------------------|-------|

| 3.1       | The DVC     | С                                                | 13    |

| 3.2 B     | istable cir | cuit based on DVCC                               | 13    |

| 3.3 S     | imulation   | Results                                          | 15    |

| Chapt     | er 4        | Proposed Memristor Emulator Circuits             | 17-28 |

| 4.1       | Mathen      | natical model                                    | 17    |

| 4.2       | CFOA b      | pased Threshold Type Binary Memristor Emulator   | 18    |

|           | 4.2.1       | Simulation Results                               | 20    |

| 4.3       | Thresho     | old Type Binary Memristor Emulator based on DVCC | 23    |

|           | 4.3.1Si     | mulation Results                                 | 26    |

| Chapte    | er 5        | <b>Conclusion and Future Scope</b>               | 29    |

| Refere    | nces        |                                                  | 30-33 |

| List of [ | Publicati   | ons                                              | 34    |

## **LIST OF FIGURES**

| Fig No.   | Title Pa                                                                                                                                   | age No                     |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Fig. 2.1  | Symbolic diagram of AD844 [39]                                                                                                             | 4                          |

| Fig. 2.2  | Inverting Voltage Amplifier [40]                                                                                                           | 5                          |

| Fig. 2.3  | Non-Inverting Amplifier [40]                                                                                                               | 6                          |

| Fig. 2.4  | Summing amplifier                                                                                                                          | 6                          |

| Fig. 2.5  | Subtractor Amplifier                                                                                                                       | 7                          |

| Fig. 2.6  | The inverting integrator                                                                                                                   | 8                          |

| Fig. 2.7  | Bistable Circuit                                                                                                                           | 9                          |

| Fig. 2.8  | Transient waveforms of summing amplifier for (a) $R_1=R_2=R_3=1k\Omega$ , (                                                                | b) R <sub>1</sub> =        |

|           | 1k $\Omega$ , R <sub>2</sub> =R <sub>3</sub> =2k $\Omega$ and (c)R <sub>1</sub> =1k $\Omega$ , R <sub>2</sub> =R <sub>3</sub> =4k $\Omega$ | 10                         |

| Fig. 2.9  | Transient waveforms of subtractor amplifier for (a) $R_1=R_2=1k\Omega$ , (b) $R_1=R_2=2k\Omega$ and (c) $R_1=1k\Omega$ , $R_2=1.5k\Omega$  | <sub>-1</sub> = 1kΩ,<br>11 |

| Fig. 2.10 | Transient waveform of inverting integrator                                                                                                 | 12                         |

| Fig. 2.11 | Transient waveform of bistable circuit                                                                                                     | 12                         |

| Fig. 3.1  | Symbolic diagram of DVCC [46]                                                                                                              | 13                         |

| Fig. 3.2  | DVCC based Bistable circuit [47]                                                                                                           | 14                         |

| Fig. 3. 3 | Time domain waveform a) $V_X$ and $V_{Y2}$ and b) $I_Z$ and $I_X$                                                                          | 15                         |

| Fig. 3.4  | Transient waveform of bistable circuit                                                                                                     | 16                         |

| Fig. 4.1  | CFOA based proposed threshold binary type emulator                                                                                         | 19                         |

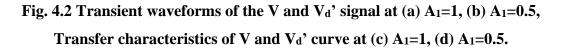

| Fig. 4.2  | Transient waveforms of the V and V <sub>d</sub> ' signal at (a) $A_1=1$ , (b) $A_1=0.5$ , T                                                | Fransfer                   |

|           | characteristics of V and V <sub>d</sub> ' curve at (c) $A_1=1$ , (d) $A_1=0.5$                                                             | 21                         |

| Fig. 4.3  | Time domain waveform (a) V, (b) $V_d$ ', (c) $V_b$ , (d) $V_w$                                                                             | 22                         |

| Fig. 4.4  | V versus $V_w$ characteristics of the emulator (a) at $A_1$ =1 (b) at $A_1$ =0.5                                                           | 23                         |

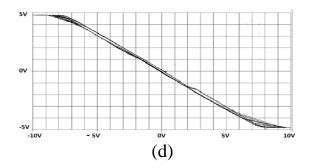

Fig. 4.5DVCC based proposed threshold binary type memristor emulator24Fig. 4.6V versus  $V_W$  characteristics of the emulator (a) at f=7kHz, (b) at f=9kHz, (c) at<br/>f=10kHz, (d) at f=15kHz28

## LIST OF TABLES

| Table No. | Title                                           | Page No. |

|-----------|-------------------------------------------------|----------|

| Table 4.1 | Component Setting CFOA Based Memristor Emulator | 21       |

| Table 4.2 | Component Setting DVCC Based Memristor Emulator | 26       |

#### **LIST OF ABBREVIATIONS**

- CCII Second-generation Current Conveyor

- OTA Operational Transconductance Amplifier

- VDCC Voltage Differencing Current Conveyor

- VDTA Voltage Differencing Transconductance Amplifier

- CBTA Current Backward Transconductance Amplifier

- CFOA Current Feedback Operational Amplifier

- DVCCTA Differential Voltage Current Conveyor Transconductance Amplifier

- DVCC Differential Voltage Current Conveyor

# <u>CHAPTER -1</u> INTRODUCTION

#### **1.1 Background**

MEMRISTOR is a circuit element with excellent features memory and neuromorphic application characteristics. It is non-volatile and has a very small size of just a few nanometres, making it suitable for memory applications. It also has pulse-based operation and adjustable resistance, which are required for regulating the synaptic weights of neuromorphic cells for neuromorphic applications. Chua proposed the memristor (memristor+ resistor) as a new passive circuit element in 1971, which offers the needed fundamental relationship between charge and flux linkage [1]. Due to their particular behaviour and properties, the memristors created by Hewlett-Packard (HP) Laboratories in 2008 by Strukov et al. [2] with TiO2 are well known. The pinched hysteresis loop in the current versus voltage plane under sinusoidal excitations is a common property of both the memristor and the memristive device. As a result of these occurrences, the devices resistance is dependent on the input current or voltage history, and it can therefore act neural network synapses. Despite the high level of interest in the memristor among scientists, commercially available memristors are unlikely to appear in the near future due to the high cost and technical challenges of fabricating nano-scale devices. To develop real world application circuits that use memristors properties, various circuit substitutes that behave like memristors are required. SPICE macro models [3-6] have been presented by numerous research groups and are suitable for simulating memristor. Macro models, on the other hand, are not hardware and cannot be utilised to create physically implementable memristor application circuits. As a result, emulators that can emulate the behaviour of real memristors are required. The processing difficulties in the production at memristor at nanoscale has directed research in making memristor emulators based on active blocks. Floating and grounded memristor emulators are the two forms of memristor emulators, based on their architectures. The analogue active blocks of floating-type memristors are identical to a second-generation current conveyor (CCII), a multiplier, and an Op-amp [7-8]. CCII and operational transconductance amplifiers (OTAs) [9] can be used to create a memristor emulator that is electronically controllable but has a restricted frequency response. A charged controlled memristor emulator based on DVCCTA has been presented in [10]. [11] describes a memristor emulator utilizing the IC AD844AN

and an analogue multiplier, however the number of active and passive parts necessary to create this type of emulator circuit is greater. In [12] proposes a memristor emulator with four CCIIs and one multiplier, as well as various passive components, in an incremental design. One DDCC and one multiplier were utilized as active elements in the construction of a memristor emulator in [13], and the circuit performed well up to 1 MHz. Using CCTA as an active element and a few passive components, a floating/grounded type memristor [14] has been presented. In [15] employed two CFOAs as active elements and one diode as a nonlinear element to build an emulator circuit, and it was updated again in [16], however this time an OTA was used instead of a diode. The emulator circuit illustrated in [17] is made up of two AD844ANs with an analogue multiplier and can operate at a frequency of up to 160 kHz. [18] describes a modification of this emulator that can operate at up to 860 kHz. A grounded memristor emulator has been built in [19] that can be programmed in both incremental and decremental modes utilising one VDTA and one capacitor. In [20], describes a flux-controlled grounded/floating-type memristor emulator with two OTAs and one capacitor that can function at up to 8 MHz. One CCTA and one CCII were used as active elements in [21] to create a floating-type memristor emulator that can work at up to 5 MHz.

Memristor, a passive circuit element, featuring relationship between Charge and Flux [2], having applications in circuit designs like memory [22], digital circuits [23-24], neuro network [25], chaotic systems [26-27] and analog circuits [28-29]. Memristor is still not available as a commercial component due cost and technical difficulties in fabricating nanoscale devices. However, memristor emulators are cost-efficient and easy to implement. Analog building blocks are used to emulate memristor behavior in [7,13,14,30,31,32,33] while microcontroller-based emulator circuits are presented in [34-36]. Recently there is an interest in design binary memristor. These are based on low pass filter [37] and thresholding concept [38]. Thus, there is limited literature available for threshold type memristor emulator.

#### **1.2 Objective**

The main objective of this project is to present new structures for threshold-type binary memristor emulator based on CFOA and DVCC.

## **1.3 Organization of Thesis**

In Chapter 1, there is a basic introduction of Project

In Chapter 2, current feedback operational amplifier and its basic circuits application are given.

The Chapter 3 presents an overview of DVCC.

In Chapter 4, the proposed memristor emulator circuit based on DVCC and CFOA are detailed and verified through simulations. All simulation results for evaluating the properties of the proposed memristor emulators circuit are included.

Chapter 5 describes Conclusion & Future Scope of this project.

### **CHAPTER-2**

### **CURRENT FEEDBACK OPERATIONAL AMPLIFIER**

This chapter describes current feedback operational amplifier. Some of the CFOA based applications such as inverting voltage amplifier, non-inverting amplifier, summing amplifier, subtractor amplifier, integrator and bistable circuit are explained. Their characteristics have been simulated and verified by Pspice.

#### 2.1 The CFOA

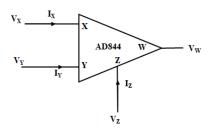

The CFOA uses a second-generation current conveyor followed by a voltage buffer. A simplified symbolic diagram is shown in Fig. 2.1[39] and its characteristics equations are given by (2.1).

Fig. 2.1 Symbolic diagram of AD844 [39]

$I_{Y} = 0$   $V_{X} = V_{Y}$   $I_{Z} = I_{X}$   $V_{W} = V_{Z}$ (2.1)

## 2.2 Basic Circuit Applications of CFOA

This section describes the basic circuit applications of CFOA which have been used in this project.

### 2.2.1 Inverting Voltage Amplifier

The inverting voltage amplifier shown in Fig. 2.2. it consists of an CFOA and two resistances  $R_1$  and  $R_2$ , has a finite input impedance given by  $R_1$  which must be taken much larger than the input resistance of the CFOA which is typically of the order of 650hm.

Fig. 2.2 Inverting Voltage Amplifier [40]

the transfer function can be computed as

$$\frac{V_O}{V_i} = \frac{-R_2}{R_1} \tag{2.2}$$

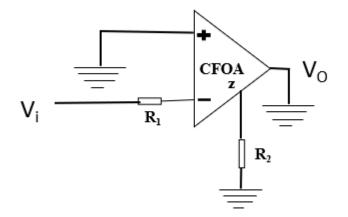

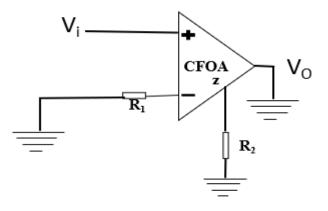

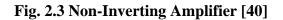

## 2.2.2 Non-Inverting Amplifier

A non-inverting amplifier consist of a CFOA and two resistances  $R_1$  and  $R_2$  as shown in Fig.3.3.

The resulting transfer function as

$$\frac{V_O}{V_i} = \frac{R_2}{R_1}$$

(2.3)

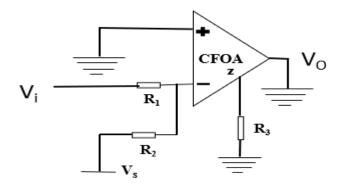

## 2.2.3 Summing Amplifier

An CFOA based summer is shown in Fig. 2.4 and this circuit makes use of a single CFOA.

The output voltage Vo can be written as:

$$V_{0} = -\left(\frac{R_{3}}{R_{1}} V_{i} + \frac{R_{3}}{R_{2}} V_{s}\right)$$

(2.4)

Fig. 2.4 Summing amplifier

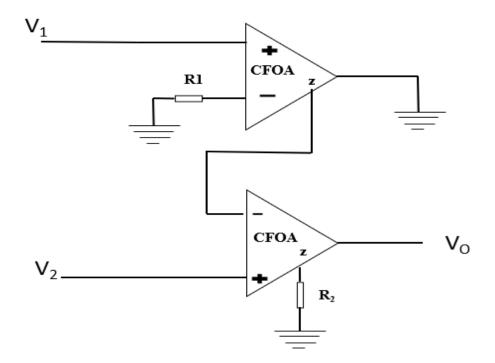

## 2.2.4 Subtractor Amplifier

Considering the CFOA to be ideal the output voltage for the circuit shown in Fig. 2.5 can be expressed

$$V_0 = -\frac{R_2}{R_1}(V_1 - V_2) \tag{2.5}$$

The circuit of Fig. 2.5 can also be used as a subtractor if  $R_1 = R_2 = R$  and the voltage at the output can be written as

$$V_0 = -(V_1 - V_2) \tag{2.6}$$

Fig. 2.5 Subtractor Amplifier

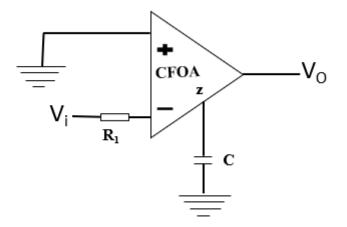

## 2.2.5 Integrator

The circuit shown in Fig. 2.6 represents an inverting integrator. Assuming the CFOA to be ideal.

The output voltage  $V_0$  is calculated as follows:

$$V_0 = -\frac{\omega_0}{s} V_i \tag{2.7}$$

Where  $\omega_0 = \frac{1}{CR_1}$

Fig. 2.6 The inverting integrator

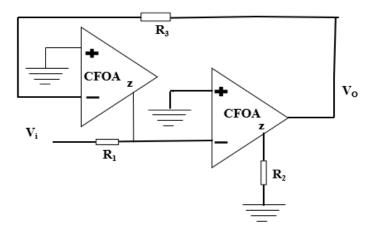

## 2.2.6 Bistable Circuit

A bistable circuit Fig 2.7 is needed next to add non volatility and bistable properties to the emulator. Its output is given by (2.8).

$$Vsc = \begin{cases} V_{ss} & V_{TH} < V_{int} \\ hold & V_{TL} \le V_{int} \le V_{TH} \\ V_{DD} & V_{int} < V_{TL} \end{cases}$$

(2.8)

Fig. 2.7 Bistable Circuit

where  $V_{TH}$  and  $V_{TL}$  correspond to upper and lower threshold voltages of bistable circuit and are related by (2.9)

$$V_{\rm TH} = -V_{\rm TL} = \frac{R_1}{R_3} V_{\rm DD}$$

(2.9)

Other symbols in (2.8) have their usual meaning.

#### 2.3 Simulation Results

The CFOA based applications such as summing amplifier, subtractor amplifier, integrator and bistable circuit are simulated and verified by Pspice. The power supply of  $V_{DD} = -V_{SS}=10V$  is taken.

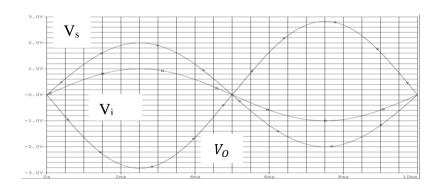

An input Voltage  $V_i = 1\sin(2000\pi t)$  and  $V_s = 2\sin(2000\pi t)$  is applied to the summing amplifier. The performance of summing amplifier is verified for (a) R<sub>1</sub>=R<sub>2</sub>=R<sub>3</sub>=1k $\Omega$ , (b)R<sub>1</sub>= 1k $\Omega$ , R<sub>2</sub>=R<sub>3</sub>=2k $\Omega$  and (c)R<sub>1</sub>=1k $\Omega$ , R<sub>2</sub>=R<sub>3</sub>=4k $\Omega$ , its transient waveform shown in Fig. 2.8.

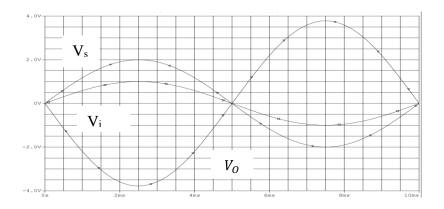

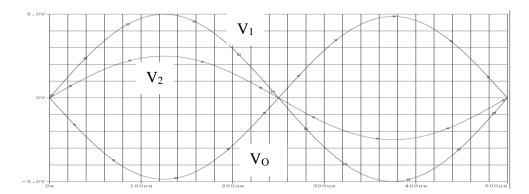

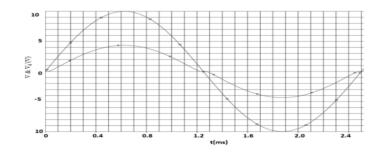

An input Voltage  $V_1 = 5\sin(2000\pi t)$  and  $V_2 = 2.5\sin(2000\pi t)$  is applied to the subtractor amplifier. Functionality of subtractor can be verified from the Transient response presented in Fig. 2.9 for (a)  $R_1=R_2=1k\Omega$  (b)  $R_1=1k\Omega$ ,  $R_2=2k\Omega$  (c)  $R_1=1k\Omega$ ,  $R_2=1.5k\Omega$ .

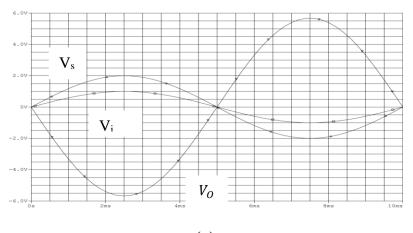

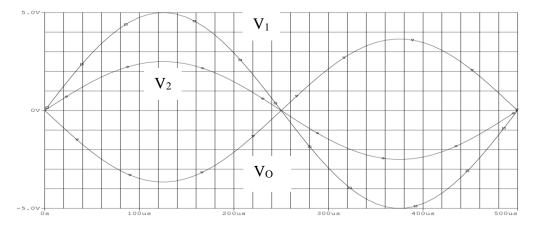

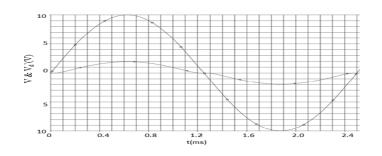

The simulation waveform is depicted in Fig. 2.9 verify the functionality of inverting integrator for  $R_1 = 100 \text{ k}\Omega$  and C = 10nF and input Voltage V= 5 sin(1000 $\pi$ t) is applied to the integrator circuits.

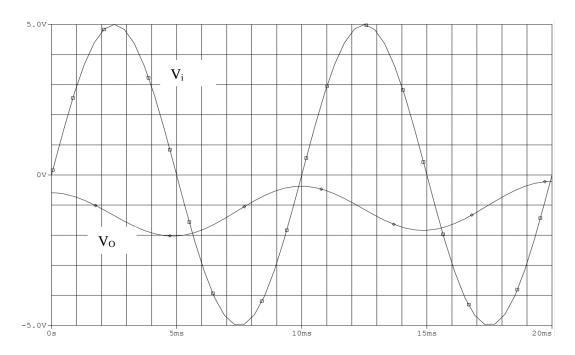

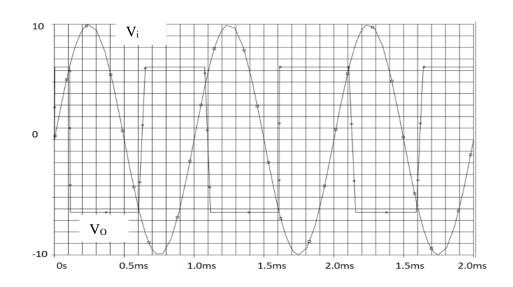

An input Voltage V= 8 sin(1000 $\pi$ t) is applied to the bistable circuit. The characteristic of bistable circuit is verified for R<sub>1</sub>=5 k $\Omega$ , R<sub>2</sub>=500k $\Omega$  and R<sub>3</sub>=10k $\Omega$ . The simulation waveform is depicted in Fig. 2.10 which is in tune with theoretical prediction.

**(a)**

**(b)**

(c)

Fig. 2.8 Transient waveforms of summing amplifier for (a)  $R_1=R_2=R_3=1k\Omega$ , (b)  $R_1=1k\Omega$ ,  $R_2=R_3=2k\Omega$  and (c) $R_1=1k\Omega$ ,  $R_2=R_3=4k\Omega$

(a)

(c)

Fig. 2.9 Transient waveforms of subtractor amplifier for (a)  $R_1=R_2=1k\Omega$ , (b)  $R_1=1k\Omega$ ,  $R_2=2k\Omega$  and (c) $R_1=1k\Omega$ ,  $R_2=1.5k\Omega$

Fig. 2.10 Transient waveform of inverting integrator

Fig. 2.11 Transient waveform of bistable circuit

According to the above Simulation results the characteristics of CFOA and its applications have been simulated and verified using Pspice.

#### **CHAPTER-3**

#### **DIFFERENTIAL VOLTAGE CURRENT CONVEYOR**

Having seen the circuit and applications of CFOA in previous chapter, this chapter explains another block Differential Voltage Current Conveyor (DVCC) which is designed to work with differential signals.

#### **3.1 The DVCC**

The Differential Voltage Current Conveyor is capable of processing difference of voltages and also possesses current conveying capability. The DVCC finds wide applications in analog signal processing circuits namely filters [41-42], oscillator [43-44], multivibrator [45] etc.

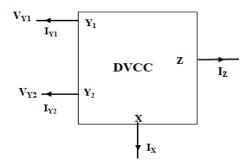

Fig. 3.1 shows a symbolic representation of DVCC. It has four terminals namely  $Y_1$ ,  $Y_2$ , X and Z. Its principle of operation can be explained by the set of characteristics equations as given in equation (3.1)

Fig. 3.1 Symbolic diagram of DVCC [46]

$$I_{Y1}=0 I_{Y2}=0 V_X = V_{Y1} - V_{Y2} I_Z = I_X$$

(3.1)

From equations (3.1), it can be concluded that the difference of voltages applied at  $Y_1$ &  $Y_2$  terminals is conveyed to voltage at *X* terminal while the injected current at *X* terminal is the conveyed to terminal Z. Since input terminals  $Y_1$  &  $Y_2$ , have high input impedances, hence no current flows through these terminals.

#### 3.2 Bistable Circuit based on DVCC

The bistable circuit depicted in Fig. 3.2 uses a single DVCC and two resistors. The connection  $Y_1$  to Z provides the positive feedback of bistable circuit. Loop gain of the positive feedback is greater than unity.

The voltage at output node of the bistable circuit varies from high to low and low to high. When the input voltage given by equation (3.2).

$$V_{in} = V_{Y1} - V_X$$

(3.2)

Fig. 3.2 DVCC based Bistable circuit [47]

Where  $V_{TH}$  and  $V_{TL}$  related to upper and lower threshold voltage of bistable circuit given by (3.3) and (3.4) respectively.

$$V_{TH} = V_{DD} - V_{XDD} \tag{3.3}$$

$$V_{TL} = V_{SS} - V_{XSS} \tag{3.4}$$

Where  $V_{XDD}$  and  $V_{XSS}$  saturated voltage at X terminal.

#### **3.2 Simulation Results**

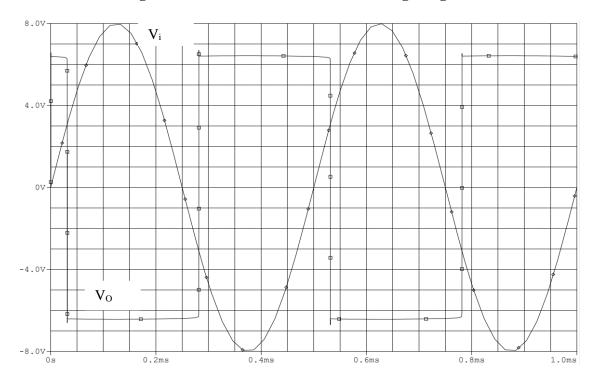

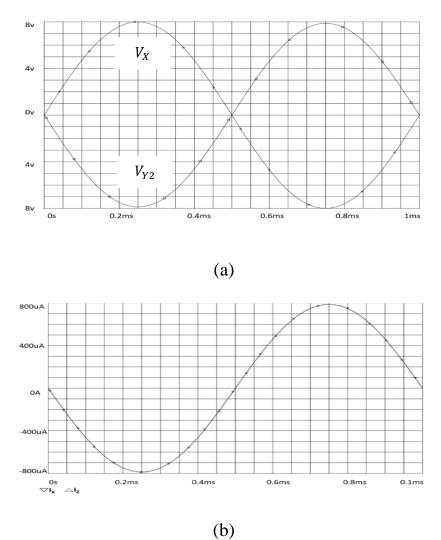

The operation of the DVCC is examined through Pspice simulations. The realization of DVCC based on IC AD844. The power supply of  $V_{DD} = -V_{SS} = 10$ V and R = 10k $\Omega$  are used. An input Voltage V= 8 sin(2000 $\pi$ t) is applied at  $Y_2$  terminal and  $Y_1$  is connected to ground in the circuit shown in Fig. 3.1. The output was taken at the Z and X terminal of DVCC. The simulation waveforms are depicted in Fig. 3.3 which are in tune with basic characteristics of DVCC and fig 3.4 verified the functionality of bistable circuit which is based on DVCC.

Fig. 3. 3 Time domain waveform a)  $V_X$  and  $V_{Y2}$  and b)  $I_Z$  and  $I_X$

Fig. 3.4 Transient waveform of bistable circuit

The Characteristics of DVCC and its applications have been simulated and verified using PSpice.

### **CHAPTER-4**

#### **PROPOSED MEMRISTOR EMULATOR CIRCUITS**

This chapter presents CFOA and DVCC based binary memristor emulator. The proposed threshold type memristor emulator has the ability of threshold type switching which ensure the basic logic operations essential for non-volatile storage property, on which all its applications are based.

#### 4.1 Mathematical Model

The behaviour of threshold type memristor [47] is briefly reviewed in this section. The current i through voltage controlled memristor is product of memconductance G and voltage v where G is function of time (t), state variable x and voltage v and is given by (4.1).

$$\mathbf{i} = \mathbf{G} \left( \mathbf{x}, \mathbf{v}, \mathbf{t} \right) \mathbf{v} \tag{4.1}$$

Additionally, the following equation for derivative of state variable x also needs be satisfied

$$\frac{\mathrm{dx}}{\mathrm{dt}} = \mathbf{f} \left( \mathbf{x}, \mathbf{v}, \mathbf{t} \right) \tag{4.2}$$

The threshold phenomenon [48] is modelled by (4.3)

$$\frac{\mathrm{dx}}{\mathrm{dt}} = \beta \mathbf{v} + 0.5(\alpha - \beta) \left[ |\mathbf{v} + \mathbf{v}_{\mathrm{th}}| - |\mathbf{v} - \mathbf{v}_{\mathrm{th}}| \right]$$

$$\tag{4.3}$$

Here coefficients  $\alpha$  and  $\beta$  characterize the rate of change in state variable and v<sub>th</sub> corresponds to threshold voltage.

Further, the binary memristor has low resistance and high resistance states which are abbreviated as LRS and HRS. Assuming threshold voltages as Y1 and Y2 the value of resistance is LRS if state variable is less than Y1 and HRS if state variable is greater than Y2. In case the state variable lies in between Y1 and Y2, the memristor holds the state.

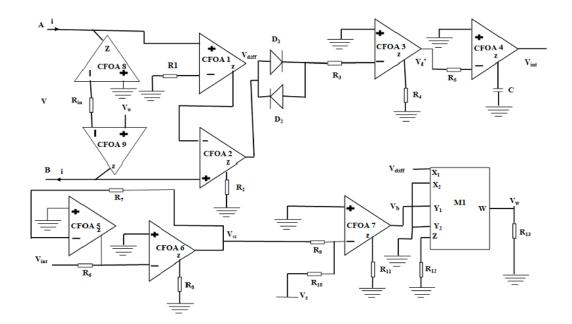

#### 4.2 CFOA based Threshold Type Binary Memristor Emulator

The proposed emulator uses 9 CFOAs, one multiplier, two diodes, 14 resistors and one capacitor against 2 CFOAs, 7 opamps, one multiplier, two diodes, 17 resistors and one capacitor. Thus, proposed circuit use lesser number of resistors.

The proposed emulator corresponds to floating memristor, therefore a voltage subtractor circuit is required CFOA 1 and CFOA 2 serve this purpose the output  $V_{diff}$  is given by

$$V_{diff} = -\frac{R_2}{R_1} (V_A - V_B), V = V_A - V_B = -A_1 (V_A - V_B)$$

(4.4)

where  $A_1 = \frac{R_2}{R_1}$

with the selection  $R_2 = R_1$ ,  $V_{diff}$  reduces to

$$V_{\rm diff} = -(V_{\rm A} - V_{\rm B}) \tag{4.5}$$

The diode  $D_1$  and  $D_2$  are used to model threshold voltages. Assuming cut in voltage of both the diodes as  $v_{\gamma}$ , ( $v_{\gamma}$  may be interpreted as  $v_{th}$ ) in equation (4.3) to the next stage (comprising of diodes and CFOA 3) is

$$V_{d}' = A_{1}V - 0.5[|A_{1}V + A_{2}v_{y}| - |A_{1}V - A_{2}v_{y}|]$$

(4.6)

where

$$A_2 = \frac{R_4}{R_3}$$

with  $A_2 = 1$ , (4.6) reduces to (4.7)

$$V'_{d} = V - 0.5[|V + v_{\chi}| - |V - v_{\chi}|]$$

(4.7)

It may be noted that for input voltage  $\leq |v_{y}|$  the output is zero. Further the threshold voltage may be varied by changing the value of A<sub>1</sub>. The threshold increases with A<sub>1</sub> < 1, remains same as diode cut in voltage for A<sub>1</sub> = 1 and decreases with A<sub>1</sub> > 1.

To satisfy (4.1), an integrator is to be placed next. The CFOA 4 performs this function. Its output is given by

$$V_{\rm int} = -\frac{1}{R_5 C} \int V_{\rm d}' \, dt$$

(4.8)

The operating frequency of memristor is decided by the product  $R_5C$  i.e., a higher value will yield lower frequency and a lower value result in higher frequency.

A bistable circuit is needed next to add non volatility and bistable properties to the emulator. The CFOA 5 and CFOA 6 provide the functionality of bistable circuit. Its output is given by (4.9).

$$Vsc = \begin{cases} V_{ss} & V_{TH} < V_{int} \\ hold & V_{TL} \le V_{int} \le V_{TH} \\ V_{DD} & V_{int} < V_{TL} \end{cases}$$

(4.9)

Fig. 4.1 CFOA based proposed threshold binary type emulator

where  $V_{TH}$  and  $V_{TL}$  correspond to upper and lower threshold voltages of bistable circuit and are related by (4.10)

$$V_{\rm TH} = -V_{\rm TL} = \frac{R_6}{R_7} V_{\rm DD}$$

(4.10)

Other symbols in (4.9) have their usual meaning.

The output of bistable circuit passes through an inverting summing amplifier formed by CFOA 7 so that output voltage  $V_b$  has single polarity ( $V_s$  is used for shifting the voltage level).

A multiplier is necessary to provide voltage proportional to memristor current. AD633 is used for this purpose. It multiplies signals  $V_{diff}$  and  $V_b$  and uses resistors  $R_{12}$  and  $R_{13}$  to adjust multiplication coefficient.

$$V_{\rm w} = R_{\rm in} \, i \tag{4.11}$$

The CFOA 8 and CFOA 9 are used to convert the voltage  $V_w$  to memristor current i. The current flowing through  $R_{in}$  is given by

$$i = \frac{V_w}{R_{in}}$$

(4.12)

According to the above analysis the proposed circuit emulates threshold type memristor.

#### **4.2.1 Simulation Results**

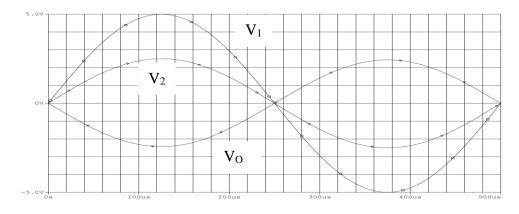

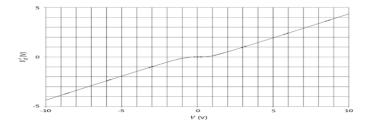

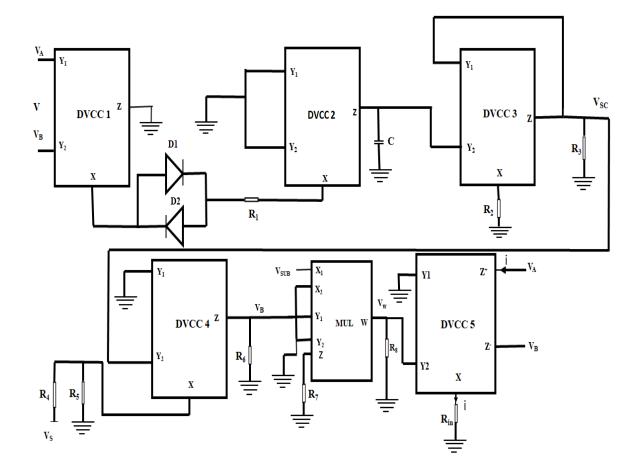

The operation of the proposed emulator is examined through PSPICE simulations. The power supply of  $V_{DD} = -V_{SS}=10V$  is taken. An input Voltage V= 10 sin(1000 $\pi$ t) is applied to the circuit Fig. 4.2 depicts the time domain waveforms for V and V<sub>d</sub>' for A<sub>1</sub>=1 (R<sub>1</sub>=R<sub>2</sub>=R<sub>3</sub>=R<sub>4</sub>=10k $\Omega$ ) and A<sub>1</sub>=0.5 (R<sub>1</sub>=5k $\Omega$ , R<sub>2</sub>=2.5k $\Omega$ , R<sub>3</sub>=10k $\Omega$ , R<sub>4</sub>=20k $\Omega$ ). A decrease in threshold voltage is observed which corroborates with theoretical prediction.

(a)

Table 4.1 Component Setting CFOA Based Memristor Emulator

| Component                                       | Value |

|-------------------------------------------------|-------|

| $R_3 = R_4 = R_5 = R_6 = R_7 = R_{13} = R_{in}$ | 10kΩ  |

| R <sub>8</sub>                                  | 500kΩ |

| R9                                              | 20kΩ  |

| R <sub>10</sub>                                 | 2.1kΩ |

| R <sub>11</sub>                                 | 7kΩ   |

| R <sub>12</sub>                                 | 5.6kΩ |

| С                                               | 10nF  |

The functionality of complete circuit is verified for  $A_1=1$  ( $R_1=R_2=R_3=R_4=10k\Omega$ ) and  $V_s$  =2.1V. The component settings are listed in Table 1 and for diode  $D_1$  and  $D_2$  D1N4148 is used. The simulation waveforms are depicted in Fig. 4.3 which are in tune with theoretical prediction.

(d)

Fig. 4.3 Time domain waveform (a) V, (b) Vd', (c) Vb, (d) Vw.

Fig. 4.4 V versus V<sub>w</sub> characteristics of the emulator (a) at A<sub>1</sub>=1 (b) at A<sub>1</sub>=0.5

The plot of V versus V<sub>w</sub> are shown in Fig. 5.4 for A<sub>1</sub>=1 (R<sub>1</sub>=R<sub>2</sub>=R<sub>3</sub>=R<sub>4</sub>=10k $\Omega$ ) and A<sub>1</sub>=0.5 (R<sub>1</sub>=5k $\Omega$ , R<sub>2</sub>=2.5 k $\Omega$ , R<sub>3</sub>=10 k $\Omega$ , R<sub>4</sub>=20k $\Omega$ ) while keeping another component setting same as given in Table 4.1. The plots correspond to pinched hysteresis loop confirming the functionality of memristor.

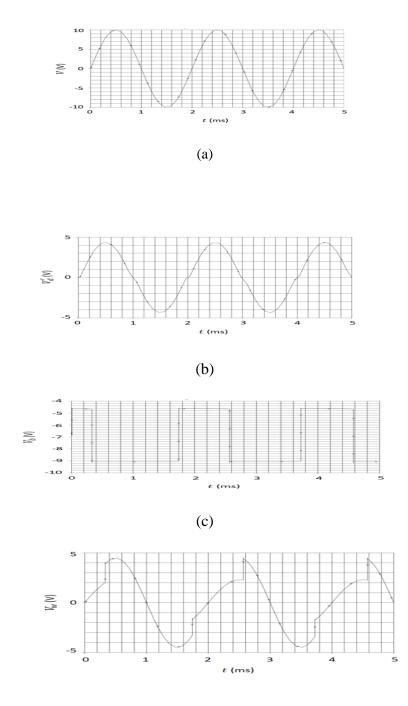

#### 4.3 Threshold Type Binary Memristor Emulator based on DVCC

The proposed emulator uses 5 DVCC, two diodes, 9 resistors, one capacitor, and one multiplier against 2 CFOAs, two diodes 7 opamps, 17 resistors, one capacitor and one multiplier. Thus, proposed emulator circuits use lesser number of resistors.

The proposed floating emulator circuits consists of subtractor, integrator, bistable circuit, inverting summing amplifier, multiplier and voltage into current to ensures floating characteristic of the emulator. The subtractor senses the memristor voltage, therefore a voltage subtractor circuit is required DVCC 1 serve this purpose the output  $V_{SUB}$  is given by (4.13)

$$V_{SUB} = (V_A - V_B)$$

$$V = V_A - V_B$$

(4.13)

Fig. 4.5 DVCC based proposed threshold binary type memristor emulator

The diode D1 and D2 in anti-parallel configuration provide threshold sensitive behaviour of the emulator which may be adjusted by resistor ratio of DVCC. Assuming cut in voltage of both the diodes as  $v_{th}$ , in equation (4.14).

$$V'_{d} = V - 0.5[|V + v_{th}| - |V - v_{th}|]$$

(4.14)

It may be noted that for input voltage  $\leq$  |vth| the output is zero. The threshold voltage remains same as diode cut in voltage, however, by introducing block with gain ( $G_1$ ) before integrator formed by DVCC2. In presence of gain, (4.14) modifies to

$$V'_{d} = V - 0.5[|V + G_{1}v_{th}| - |V - G_{1}v_{th}|]$$

(4.15)

It may be noted that the threshold voltage increases when  $G_1$  is less than unity while a decreasing trend is observed for  $G_1$  is greater than unity.

An integrator circuit is needed next to add the dependence of memductance on history state. The DVCC 2 provides the functionality of integrator circuit.

The product of *RC* performs the operating frequency of memristor emulator, for higher value will produce lower frequency and a lower value result in higher frequency. For bistable and non- volatility properties to the memristor emulator, a bistable circuit is needed. The DVCC 3 deliver the functionality of bistable circuit. Its output is given by (4.16)

$$Vsc = \begin{cases} V_{ss} & V_{TH} < V_{int} \\ hold & V_{TL} \le V_{int} \le V_{TH} \\ V_{DD} & V_{int} < V_{TL} \end{cases}$$

(4.16)

Other symbols in (4.15) have their usual meaning

The bistable circuit employing a single DVCC and two resistors which shown in Fig. 4.5. The connection  $Y_1$  to Z provides the positive feedback of bistable circuit. Loop gain of the positive feedback is greater than unity.

The voltage at output node of the bistable circuit varies from high to low and low to high. When the input voltage given by equation (4.17).

$$V_{in} = V_{Y1} - V_X \tag{4.17}$$

Where  $V_{TH}$  and  $V_{TL}$  related to upper and lower threshold voltage of bistable circuit given by (4.18) and (4.19) respectively.

$$V_{TH} = V_{DD} - V_{XDD}$$

(4.18)

$V_{TL} = V_{SS} - V_{XSS}$  (4.19)

The output of bistable circuit passes through an inverting summing amplifier formed by DVCC 4 so that output voltage  $V_S$  ( $V_S$  is used for shifting the voltage level).

A multiplier is necessary to provide voltage proportional to memristor current. AD633

is used for this purpose. It multiplies signals  $V_{SUB}$  and  $V_S$  and uses resistors  $R_7$  and  $R_8$  to adjust multiplication coefficient.

$$V_W = R_{in} i \tag{4.20}$$

The DVCC 5 is used to convert the voltage  $V_W$  to memristor current i. The current flowing through  $R_{in}$  is given by

$$i = \frac{V_w}{R_{in}} \tag{4.21}$$

The proposed circuits, according to above analysis, emulates a threshold type memristor.

The proposed emulator uses 5 DVCC, two diodes, 9 resistors, one capacitor, and one multiplier whereas the existing counterpart [47] uses 2 CFOAs, two diodes 7 opamps, 17 resistors, one capacitor and one multiplier.

#### **4.3.1 Simulation Results**

Pspice simulations are used to verify the proposed emulator circuit functionality. The power supply of  $V_{DD} = -V_{SS} = 10$ V is taken. An input Voltage V=  $10 \sin(2000\pi t)$  is applied to the circuit shown in Fig. 4.5.

Table 4.2 Component Setting DVCC Based Memristor Emulator

| component                                   | value  |

|---------------------------------------------|--------|

| $R_1 = R_2 = R_4 = R_5 = R_6 = R_7 = R_8 =$ | 10 kΩ  |

| R <sub>in</sub>                             |        |

| С                                           | 10nF   |

| R <sub>3</sub>                              | 100 kΩ |

The functionality of complete circuit is verified for  $G_1=1$  and  $V_S=2.1$ V. The component settings are listed in Table II and for diode D1 and D2 D1N4001 is used.

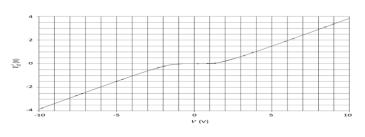

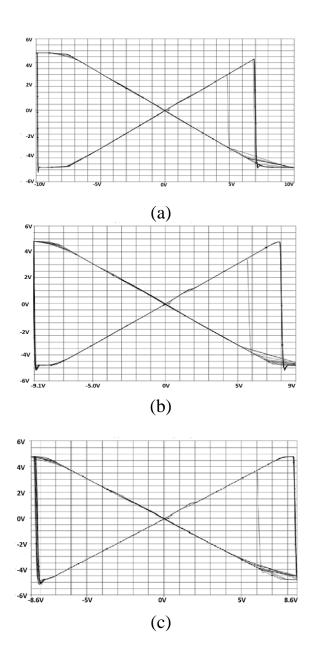

The plot of *V* versus  $V_W$  are shown in Fig. 4.6 for  $G_1=1$  and while keeping another component setting same as given in Table 4.2. The plots correspond to pinched hysteresis loop confirming the functionality of memristor.

Simulations are done to examine the frequency-dependent pinched hysteresis loop of the proposed design for different frequencies. The input voltage (V) versus  $V_W$  characteristics of the proposed emulator at different input frequencies, i.e.,7kHz, 9kHz, 10kHz and 15kHz are observed and are shown in Fig. 4.7. It is noted that the area of the hysteresis loop is dependent on the frequency of the input signal. The enclosed area of the pinched hysteresis loop decreases monotonically with the increase in frequency of the input.

Fig.4.6 V versus  $V_W$  characteristics of the emulator (a) at f=7kHz (b) at f=9kHz (c)at f=10kHz (d) at f= 15kHz

Memristor emulator based on both CFOA and DVCC have been presented in this chapter. The Characteristics of memristor emulator have been simulated and verified.

## CHAPTER-5

#### **CONCLUSION AND FUTURE SCOPE**

In this thesis, new threshold type binary memristor emulator circuit based on DVCC and CFOA has been proposed. The proposed emulator consists of subtractor, diode, inverting amplifier, integrator, bistable circuit, inverting summing amplifier, multiplier and voltage into current to ensures floating characteristic of the emulator. The diodes in anti-parallel configuration provides threshold sensitive behaviour of the emulator which may be adjusted by resistor ratio. The proposed circuit uses lesser number of resistor than the available binary memristor circuit.

The emulator circuits in this thesis, implemented by using of CFOA and DVCC. The CFOA uses a second-generation current conveyor followed by a voltage buffer and DVCC which is capable of processing difference of voltages. The proposed circuit consists of subtractor, inverting amplifier, integrator, bistable circuit and inverting summing amplifier can be implemented by DVCC as well as CFOA, which reduces number of resistors.

Simulations are done to examine the frequency-dependent pinched hysteresis loop of the proposed design for different frequencies. It was noted that the area of the hysteresis loop is dependent on the frequency of the input signal. The enclosed area of the pinched hysteresis loop decreases monotonically with the increase in frequency of the input. The threshold voltage can be varied by changing the value of gain of the subtractor.

Memristor having applications in circuit designs like memory, digital circuits, neuro network, chaotic systems and analog circuits. The proposed circuit possess adjustable thresholds. Hence, this circuit can be used in multiple applications requiring logical based operations. With these features and components, the proposed circuit can be helpful in further study, simulations and design of memristor.

#### References

[1] L. O. Chua, "Memristor—The Missing Circuit Element," IEEE Trans. Circuit Theory, vol. 18, no. 5, pp. 507–519, 1971.

[2] B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," Nature, vol. 453, no. 7191, pp. 80–83, May 2008.

[3] D. B. Strukov, G. S. Snider, D. R. Stewart, R. S.Williams, "The missing memristor found", Nature (London) 453 (2008) 80–83.

[4] Z. Biolek, D. Biolek, and V. Biolková, "SPICE model of memristor with nonlinear dopant drift," Radio Eng., vol. 18, no. 2, pp. 210–214, Jun. 2009.

[5] D. Batas and H. Fiedler, "A memristor SPICE implementation and a new approach for magnetic flux-controlled memristor modeling," IEEE Trans. Nanotechnol., vol. 10, no. 2, pp. 250–255, Mar. 2011.

[6] S. Benderli and T. A. Wey, "On SPICE macromodelling of TiO memristors," Electron. Lett., vol. 45, no. 7, pp. 377–379, Mar. 2009.

[7] D. Yu, H. H.-C. Iu, A. L. Fitch, and Y. Liang, "A floating memristor emulator based relaxation oscillator," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 61, no. 10, pp. 2888–2896, Oct. 2014.

[8] H. Kim, M. P. Sah, C. Yang, S. Cho, and L. O. Chua, "Memristor emulator for memristor circuit applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 59, no. 10, pp. 2422–2431, Oct. 2012.

[9] H. Sözen and U. Çam, "Electronically tunable memristor emulator circuit," Analog Integr. Circuits Signal Process., vol. 89, no. 3, pp. 655–663, Dec. 2016.

[10] R. K. Ranjan, N. Raj, N. Bhuwal, and F. Khateb, "Single DVCCTA based high frequency incremental/decremental memristor emulator and its application," AEU-Int. J. Electron. Commun., vol. 82, pp. 177–190, Feb. 2017.

[11] C. Sánchez-López, J. Mendoza-López, C. Muñiz-Montero, and M. A. Carrasco-Aguilar, "A floating analog memristor emulator circuit," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 61, no. 5, pp. 309–313, May 2014.

[12] Z. G. Cam and H. Sedef, "A new floating memristance simulator circuit based on second generation current conveyor," J. Circuits, Syst. Comput., vol. 26, no. 2, pp. 29–43, 2017.

[13] A. Ye,sil, Y. Babacan, and F. Kaçar, "A new DDCC based memristor emulator circuit and its applications," Microelectron. J., vol. 45, no. 3, pp. 282–287, Mar. 2014.

[14] R. K. Ranjan, N. Rani, R. Pal, S. K. Paul, and G. Kanyal, "Single CCTA based high frequency floating and grounded type of incremental/decremental memristor emulator and its application," Microelectron. J., vol. 60, pp. 119–128, Feb. 2017.

[15] M. T. Abuelma'atti and Z. J. Khalifa, "A new memristor emulator and its application in digital modulation," Analog Integr. Circuits Signal Process., vol. 80, no. 3, pp. 577–584, Sep. 2014

[16] M. T. Abuelma'atti and Z. J. Khalifa, "A continuous-level memristor emulator and its application in a multivibrator circuit," AEU-Int. J. Electron. Commun., vol. 69, no. 4, pp. 771–775, Apr. 2015.

[17] C. Sánchez-López, M. A. Carrasco-Aguilar, and C. Muñiz-Montero, "A 16 Hz–

160 kHz memristor emulator circuit," Int. J. Electron. Commun., vol. 69, no. 9, pp. 1208–

1219, 2015.

[18] C. Sánchez-López and L. E. Aguila-Cuapio, "A 860 kHz grounded memristor emulator circuit," AEU-Int. J. Electron. Commun., vol. 73, pp. 23–33, Mar. 2017.

[19] A. Yesil, Y. Babacan, and F. Kacar, "Design and experimental evolution of memristor with only one VDTA and one capacitor," IEEE Trans. Comput. -Aided Design Integr. Circuits Syst., vol. 38, no. 6, pp. 1123–1132, Jun. 2019.

[20] G. Kanyal, P. Kumar, S. K. Paul, and A. Kumar, "OTA based high frequency tunable resistorless grounded and floating memristor emulators," AEU-Int. J. Electron. Commun., vol. 92, pp. 124–145, Aug. 2018.

[21] R. K. Ranjan, S. Sagar, S. Roushan, B. Kumari, N. Rani, and F. Khateb, "High-frequency floating memristor emulator and its experimental results," IET Circuits, Devices Syst., vol. 13, no. 3, pp. 292–302, May 2019.

[22] Y. Seok, S. J. Song, J. H. Yoon, et al., "A review of three-dimensional resistive switching cross-bar array memories from the integration and materials property points of view," Advanced Functional Materials, vol. 24, pp. 5316-5339, 2014.

[23] Y. Guo, X. Wang, and Z. Zeng, "A compact memristor-CMOS hybrid look-uptable design and potential application in FPGA," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 36, no. 12, pp. 2144-2148, Dec.2017.

[24] I. Vourkas and G. C. Sirakoulis, "Emerging memristor-based logic circuit design approaches: a review," IEEE Circuits and Systems Magazine, vol. 16, no. 3, pp. 15-30, Aug. 2016.

[25] W. Yi, K. K. Tsang, S. K. Lam, et al., "Biological plausibility and stochasticity in scalable VO2 active memristor neurons," Nature Communications, vol. 9, pp. 4661, Nov.

2018.

[26] J. Sun, X. Zhao, J. Fang, et al., "Autonomous memristor chaotic systems of infinite chaotic attractors and circuitry realization," Nonlinear Dynamics, vol. 94, no. 4, pp. 2879-2887, 2018.

[27] J. Sun, Y. Wu, G. Cui, et al., "Finite-time real combination synchronization of three complex-variable chaotic systems with unknown parameters via sliding mode control," Nonlinear Dynamics, vol. 88, no. 3, pp. 1677-1690, 2017.

[28] P. Mazumder, S. M. Kang, and R. Waser, "Memristors: devices, models, and applications," Proceedings of the IEEE, vol. 100, no. 6, pp. 1911-1919, June 2012.

[29] P. Maffezzoni, L. Daniel, N. Shukla, et al., "Modeling and simulation of vanadium dioxide relaxation oscillators," IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 62, no. 9, pp. 2207-2215, 2015.

[30] C. Yang, H. Choi, S. Park, et al., "A memristor emulator as a replacement of a real memristor," Semiconductor Science and Technology, vol. 30, pp. 015007, Jan. 2015.

[31] Singh D, Pandey N. Realization of Single CCCDTA based incremental/decremental type Memconductance Emulator. In2019 International Symposium on Advanced Electrical and Communication Technologies (ISAECT) 2019 Nov 27 (pp. 1-4).

[32] Ayten UE, Minaei S, Sağbaş M. Memristor emulator circuits using single CBTA. AEU-International Journal of Electronics and Communications. 2017 Dec 1;82:109-18.

[33] Petrović PB. Floating incremental/decremental flux-controlled memristor emulator circuit based on single VDTA. Analog Integrated Circuits and Signal Processing. 2018 Sep;96(3):417-33.

[34] V. Ntinas, I. Vourkas, A. Abusleme, et al., "Experimental study of artificial neural networks using a digital memristor simulator," IEEE transactions on neural networks and learning systems, vol. 29, no. 10, pp. 5098-5110, Oct. 2018.

[35] M. F. Tolba, M. E. Fouda, H. G. Hezayyin, et al., "Memristor FPGA IP Core Implementation For Analog and Digital Applications," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 66, no. 8, pp. 1381-1385, Aug. 2019.

[36] Tolba MF, Halawani Y, Saleh H, Mohammad B, Al-Qutayri M. FPGA-Based Memristor Emulator Circuit for Binary Convolutional Neural Networks. IEEE Access. 2020 Jun 23; 8:117736-45.

[37] Li D, Zhang J, Yu D, Xu R, Iu HH, Fernando T, Wang X. A Family of Binary Memristor-Based Low-Pass Filters With Controllable Cut-Off Frequency. IEEE Access. 2020 Mar 24;8:60199-209. [38] Liang Y, Lu Z, Wang G, Yu D, Iu HH. Threshold-Type Binary Memristor Emulator Circuit. IEEE Access. 2019 Dec 3;7:180181-93.

[39] SENANI, R., BHASKAR, D.R., SINGH, A.K., SINGH, V.K. Current Feedback Operational Amplifiers and Their Applications. Springer Science and Business Media New York 2013.

[40] Soliman AM. Applications of the current feedback operational amplifiers. Analog Integrated Circuits and Signal Processing. 1996 Nov;11(3):265-302.

[41] S. Minaei, E. Yuce, Novel voltage-mode all-pass filter based on using DVCCs. Circuits Syst. Signal Process. 29(3), 391–402 (2010).

[42] Mishra SK, Gupta M, Upadhyay DK. Active realization of fractional order Butterworth lowpass filter using DVCC. Journal of King Saud University-Engineering Sciences. 2020 Feb 1;32(2):158-65.

[43] Daoud H, Bensalem S, Lahiani S, Bensalem C, Loulou M. NanoCMOS optimized DVCC-based quadrature voltage controlled oscillator performances prediction through bisquare-weights method. Analog Integrated Circuits and Signal Processing. 2019 Sep;100(3):547-63.

[44] Yesil A, Babacan Y, Kacar F. An electronically controllable, fully floating memristor based on active elements: DO-OTA and DVCC. AEU-International Journal of Electronics and Communications. 2020 Aug 1;123:153315.

[45] Chien, Y.-K. Lo, Design and implementation of monostable multivibrators employing differential voltage current conveyors. Microelectron. J. 42(10), 1107–1115 (2011).

[46] Vista J, Pheiroijam NM, Pamu H, Tarunkumar H, Ranjan A. A Novel Differential Voltage Current Conveyor (DVCC) Based Instrumentation Amplifier. IETE Journal of Research. 2019 Apr 13:1-2.

[47] Minaei S, Yuce E. A simple Schmitt trigger circuit with grounded passive elements and its application to square/triangular wave generator. Circuits, Systems, and Signal Processing. 2012 Jun;31(3):877-88.

[48] I. Vourkas, A. Batsos, G. C. Sirakoulis, "SPICE modeling of nonlinear memristive behavior," International Journal of Circuit Theory and Applications, vol. 43, no. 5, pp. 553-565, May 2015.

# List of publications

| Paper | Author list. Title. Conference                        | Status   |

|-------|-------------------------------------------------------|----------|

| [1]   | Juli Kumari Roy, Neeta Pandey, "CFOA based Threshold  | Accepted |

|       | Type Binary Memristor Emulator"                       |          |

|       | First International Conference on Emerging Trends in  |          |

|       | Industry 4.0 (2021 ETI 4.0)                           |          |

| [2]   | Juli Kumari Roy, Neeta Pandey, "Threshold Type Binary | Accepted |

|       | Memristor Emulator based on DVCC"                     |          |

|       | 8th International Conference on Signal Processing &   |          |

|       | Integrated Networks (SPIN 2021)                       |          |