### Functional Coverage and Assertion Based Verification of Communication Protocol Using System Verilog

A DISSERTATION

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE AWARD OF THE DEGREE OF

MASTER OF TECHNOLOGY IN SIGNAL PROCESSING AND DIGITAL DESIGN

Submitted by:

### Mahesh Sai Chaganti

### 2K19/SPD/09

Under the supervision of

## Mr. Rajesh Birok (Associate Professor)

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY (Formerly Delhi College of Engineering)

Bawana Road, Delhi-110042

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

#### **CANDIDATE'S DECLARATION**

I, Mahesh Sai Chaganti, Roll No. 2K19/SPD/09 student of M.Tech. (Signal Processing and Digital Design), hereby declare that the project Dissertation titled "<u>FUNCTIONAL</u> <u>COVERAGE AND ASSERTION BASED VERIFICATION OF</u> <u>COMMUNICATION PROTOCOL USING SYSTEM VERILOG</u>" which is submitted by me to the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology is original and not copied from any source without proper citation. This work has not previously formed the basis for the award of any Degree, Diploma Associate ship, Fellowship or other similar title or recognition.

Mahesh Sai Chaganti

Place: Delhi Date: 17-08-2021

#### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

#### CERTIFICATE

I hereby certify that the M. Tech.[SPDD], Major Project-II [SPD602] Report titled "FUNCTIONAL COVERAGE AND ASSERTION BASED VEIFICATION OF COMMUNICATION PROTOCOL USING SYSTEM VERILOG" which is submitted by SH. MAHESH SAI CHAGANTI, [ROLL NO: 2K19/SPD/09] of Electronics and Communication Engineering Department, Delhi Technological University, Delhi in partial fulfilment of the requirement for the award of the degree of Master of Technology, is a record of the dissertation work carried out by the student under my supervision. To the best of my knowledge this work has not been submitted in part or full for any Degree or Diploma to this University or elsewhere.

Place: Delhi Date: 22-08-2021

Base que RAJESH BIROK) Supervisor x

Associate Professor Department of ECE, DTU

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

DELHI TECHNOLOGICAL UNIVERSITY

(Formerly Delhi College of Engineering) Bawana Road, Delhi-110042

#### ACKNOWLEDGEMENT

A successful project can never be prepared by the efforts of the person to whom the project is assigned, but it also demands the help and guardianship of people who helped in completion of the project. With profound sense of gratitude, I thank MR. Rajesh Birok(Associate Professor) my Project Supervisor, for his encouragement, support, patience and his guidance in this project work. I take immense delight in extending my acknowledgement to my family and friends who have helped me throughout this project work.

Date: 17-08-2021

Mahesh Sai Chaganti M.Tech. (SPDD) Roll No: 2K19/SPD/09

### CONTENTS

| Title           |                                                                                          |                                                                |                                    | Page No |

|-----------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------|---------|

| Candidate's l   | Declarati                                                                                | n                                                              |                                    | i       |

| Certificate     |                                                                                          |                                                                | ii                                 |         |

| Acknowledgement |                                                                                          |                                                                | iii                                |         |

| Contents        |                                                                                          |                                                                |                                    | iv      |

| List of Figure  | es                                                                                       |                                                                |                                    | vii     |

| List of Tables  |                                                                                          |                                                                |                                    | viii    |

| Abstract        |                                                                                          |                                                                |                                    | ix      |

|                 |                                                                                          |                                                                |                                    |         |

| Chapter 1       | Intro                                                                                    | uction                                                         |                                    | 1-4     |

| 1.1             | On-Chi                                                                                   | Communication Protocol                                         |                                    | 1       |

| 1.2             | Embed                                                                                    | ed System Protocol                                             |                                    | 2       |

|                 | 1.2.1                                                                                    | Protocol Communication be                                      | etween two systems                 | 2       |

|                 |                                                                                          |                                                                | nronous Receiver Transmitter       | 2       |

|                 |                                                                                          |                                                                | ronous Asynchronous Receiver       | 2       |

|                 |                                                                                          | Transmitter                                                    | -                                  | 2       |

|                 |                                                                                          | 1.2.1.3 Universal Serial                                       | Bus                                | 2       |

|                 | 1.2.2                                                                                    | Protocol Communication in                                      | side the system                    | 3       |

|                 |                                                                                          | 1.2.2.1 Inter Integrated C                                     | Circuit                            | 3       |

|                 |                                                                                          | 1.2.2.2 Serial Peripheral                                      | Interface                          | 3       |

|                 |                                                                                          | 1.2.2.3 Controller Area M                                      |                                    | 4       |

| 1.3             | Interfac                                                                                 | Protocols                                                      |                                    | 4       |

| 1.4             | Memor                                                                                    | Management Protocols                                           |                                    | 4       |

| Chapter 2       |                                                                                          | Literature review                                              |                                    | 5-9     |

| 2.1             |                                                                                          | erature Survey on communication protocol designs               |                                    | 5       |

| 2.2             |                                                                                          | Literature Survey on designs involving physical implementation |                                    | 5       |

| 2.3             | Literature survey on IP Core designs involving two protocols                             |                                                                |                                    | 6       |

| 2.4             |                                                                                          | e Survey on Verification of                                    |                                    | 7       |

| 2.5             |                                                                                          | ion contribution                                               | Free and See                       | 8       |

|                 |                                                                                          | Brief about APB and SPI                                        |                                    | 8       |

|                 |                                                                                          | Design specification invol                                     | ving APB Slave/SPI Master IP       | 8       |

|                 | Core           2.5.3         Functional Coverage and Assertion based Verification of the |                                                                | esertion based Varification of the |         |

|                 | 2.5.3                                                                                    | design:                                                        | assertion based vernication of the | 9       |

| Chapter 3       | Adva                                                                                     | 0                                                              | us Architecture(AMBA)              | 10-13   |

| 3.1             |                                                                                          | Background                                                     |                                    | 10      |

| 3.2             | AMBA Protocol Specifications                                                             |                                                                | 10                                 |         |

|                 | 3.2.1                                                                                    | Advanced High Performance                                      | ce Bus                             | 11      |

|                 | 3.2.2                                                                                    | Advanced System Bus                                            |                                    | 11      |

|                 | 3.2.2                                                                                    | Advanced Peripheral Bus                                        |                                    | 12      |

| 3.3             |                                                                                          | A general purpose AMBA built microcontroller                   |                                    | 13      |

| 3.3             | AMBA Release Versions                                                                    |                                                                | 13                                 |         |

| Chapter 4       |                                                                                          | ced Peripheral Bus(AP                                          | <b>PB</b> )                        | 15-18   |

| 4.1             | Introduction                                                                             |                                                                |                                    | 15      |

| 4.2             | APB Signal List                                                                          |                                                                |                                    | 17      |

| 4.3       | APB State Machine                                           | 18    |

|-----------|-------------------------------------------------------------|-------|

| Chapter 5 | Serial Peripheral Interface(SPI)                            | 19-38 |

| 5.1       | Introduction                                                | 19    |

|           | 5.1.1 Features of SPI                                       | 19    |

|           | 5.1.2 Configurable features of SPI                          | 19    |

| 5.2       | Signal List                                                 | 20    |

| 5.3       | Pin Modes                                                   | 21    |

|           | 5.3.1 3-pin mode                                            | 21    |

|           | 5.3.2 4-pin mode                                            | 22    |

| 5.4       | Data Formats                                                | 22    |

|           | 5.4.1 Character Length                                      | 23    |

|           | 5.4.2 Shift Direction                                       | 23    |

|           | 5.4.3 CPOL and CPHA                                         | 23    |

| 5.5       | Master Mode                                                 | 25    |

|           | 5.5.1 Chip Select Setup time                                | 26    |

|           | 5.5.2 Chip Select Hold time                                 | 26    |

|           | 5.5.3 Delay between transmissons                            | 27    |

|           | 5.5.4 Chip select hold option                               | 27    |

| 5.6       | Registers                                                   | 28    |

|           | 5.6.1 Global Control Register 0                             | 29    |

|           | 5.6.2 Global Control Register 1                             | 29    |

|           | 5.6.3 Interrupt Register                                    | 30    |

|           | 5.6.4 Interrupt Level Register                              | 31    |

|           | 5.6.5 Flag Register                                         | 32    |

|           | 5.6.6 Pin Control Register 0 (Function)                     | 33    |

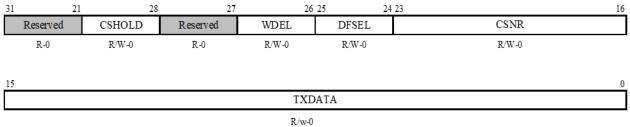

|           | 5.6.7 Data Transmit Register 0                              | 33    |

|           | 5.6.8 Data Transmit Register 1                              | 34    |

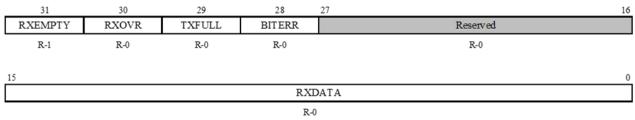

|           | 5.6.9 Receive Buffer Register                               | 35    |

|           | 5.6.10 Receive Emulation Register                           | 35    |

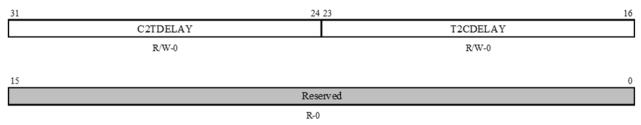

|           | 5.6.11 Delay Register                                       | 36    |

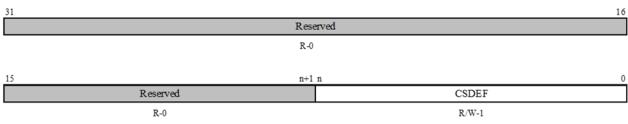

|           | 5.6.12 Default Chip Select Register                         | 36    |

|           | 5.6.13 Data Format Register                                 | 37    |

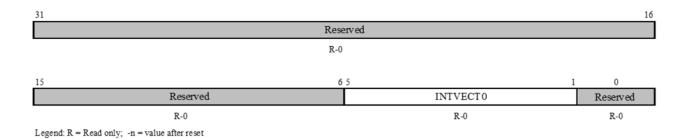

|           | 5.6.14 Interrupt Vector Register 0                          | 38    |

|           | 5.6.15 Interrupt Vector Register 1                          | 38    |

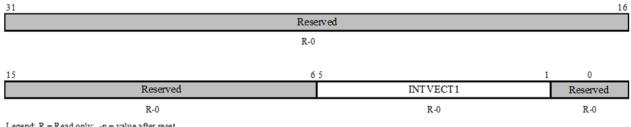

| Chapter 6 | Design Specification                                        | 39-47 |

| 6.1       | Introduction                                                | 39    |

| 6.2       | APB Slave                                                   | 40    |

| 6.3       | SPI Master                                                  | 41    |

| 6.4       | APB to SPI Interface                                        | 41    |

| 6.5       | Registers                                                   | 42    |

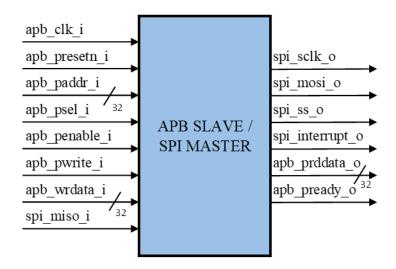

| 6.6       | FIFO                                                        | 42    |

| 5.0       | 6.6.1 Clock domain crossing                                 | 43    |

|           | 6.6.2 Binary to gray converter and Gray to binary converter | 43    |

|           | 6.6.3 Comparator                                            | 43    |

| 6.7       | Data pipeline                                               | 44    |

| 6.8       | Data transfer                                               | 45    |

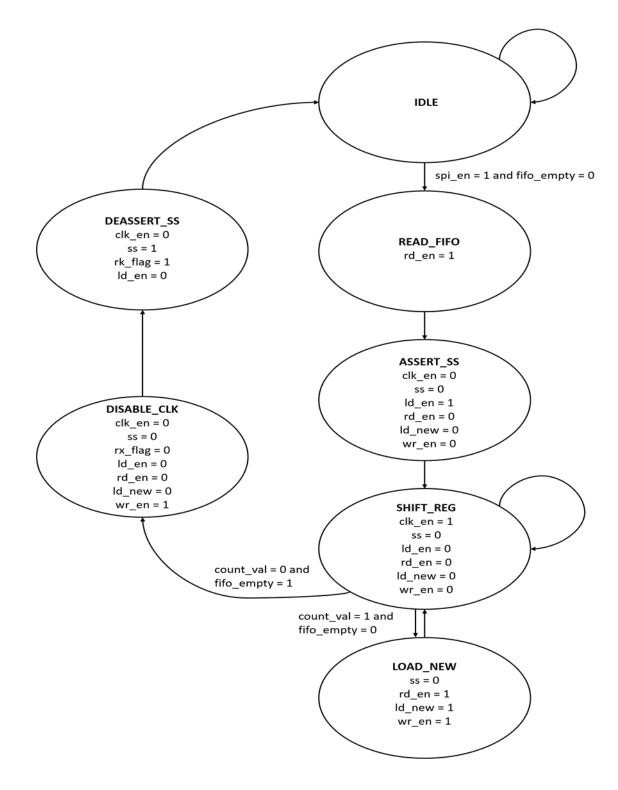

| 6.9       | Finite State Machine                                        | 46    |

| Chapter 7  | Verification               | 48    |

|------------|----------------------------|-------|

| 7.1        | Introduction               | 48-51 |

| 7.2        | Testbench Design           | 49    |

|            | 7.2.1 Functional Coverage  | 49    |

|            | 7.2.2 Assertions           | 50    |

| Chapter 8  | Simulation Results         | 52-54 |

| Chapter 9  | Conclusion and future work | 55-56 |

| 9.1        | Conclusion                 | 55    |

| 9.2        | Future Work                | 56    |

| References |                            | 57-60 |

| List of Figures |                                              |         |  |

|-----------------|----------------------------------------------|---------|--|

| Fig.No          | Name of the Figure                           | Page No |  |

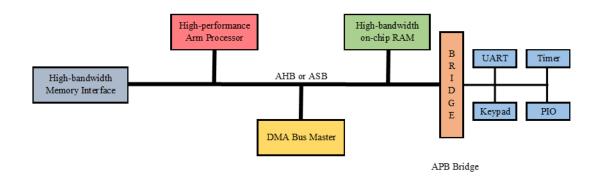

| 3.1             | AMBA Functional Block Diagram                | 12      |  |

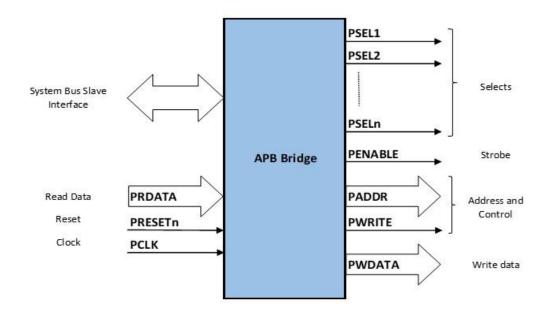

| 4.1             | APB Bridge between ASB and APB slave         | 16      |  |

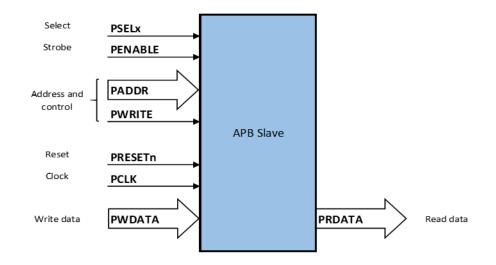

| 4.2             | APB Slave                                    | 16      |  |

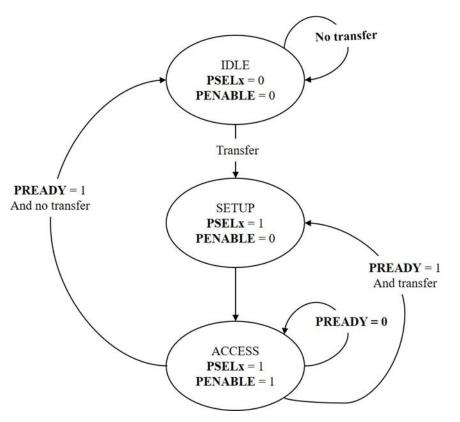

| 4.3             | APB State Diagram                            | 18      |  |

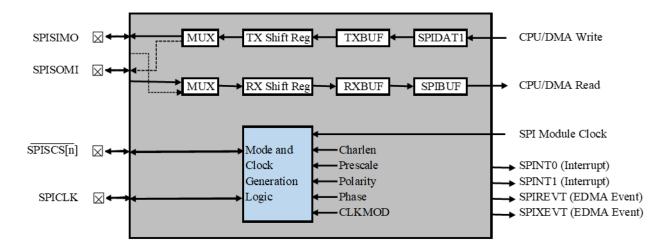

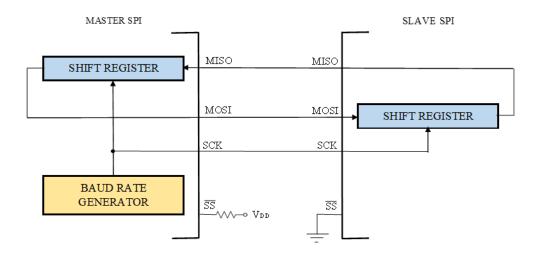

| 5.1             | Functional Block diagram of SPI protocol     | 20      |  |

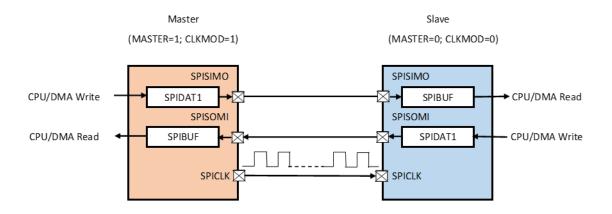

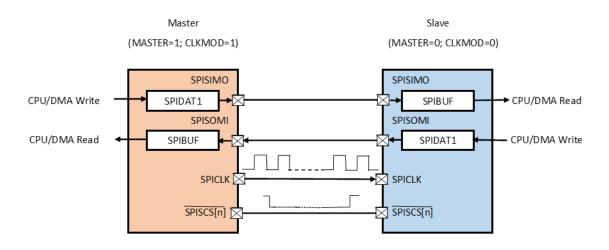

| 5.2             | 3-pin mode                                   | 21      |  |

| 5.3             | 4-pin mode                                   | 22      |  |

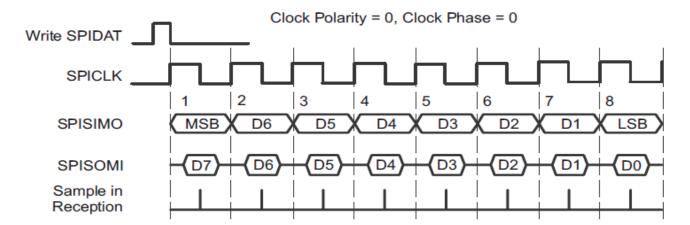

| 5.4             | Timing diagram for CPOL=0, CPHA=0            | 24      |  |

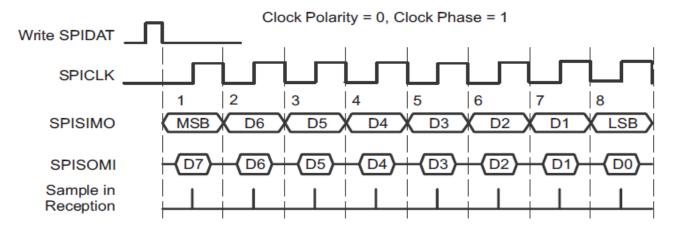

| 5.5             | Timing diagram for CPOL=0, CPHA=1            | 24      |  |

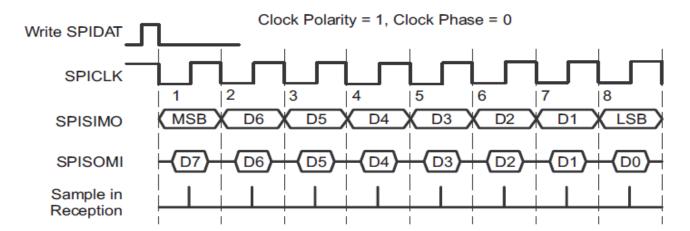

| 5.6             | Timing diagram for CPOL=1, CPHA=0            | 25      |  |

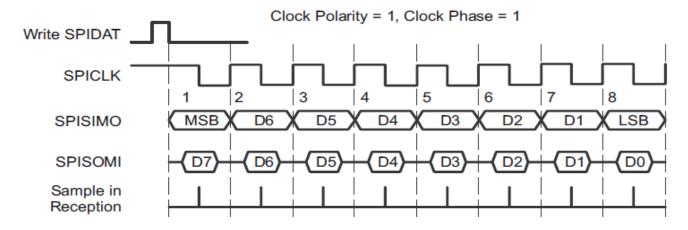

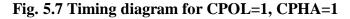

| 5.7             | Timing diagram for CPOL=1, CPHA=1            | 25      |  |

| 5.8             | GCR0 Register                                | 29      |  |

| 5.9             | GCR1 Register                                | 29      |  |

| 5.10            | INTO Register                                | 30      |  |

| 5.11            | INTLVL Register                              | 31      |  |

| 5.12            | FLG Register                                 | 32      |  |

| 5.13            | PC0 Register                                 | 33      |  |

| 5.14            | DAT0 Register                                | 34      |  |

| 5.15            | DAT1 Register                                | 34      |  |

| 5.16            | RXBUF Register                               | 35      |  |

| 5.17            | RXEMU Register                               | 35      |  |

| 5.18            | DELAY Register                               | 36      |  |

| 5.19            | DEFCS Register                               | 36      |  |

| 5.20            | FORMATn Register                             | 37      |  |

| 5.21            | INTVEC0 Register                             | 38      |  |

| 5.22            | INTVEC1 Register                             | 38      |  |

| 6.1             | Main Block diagram of the design             | 40      |  |

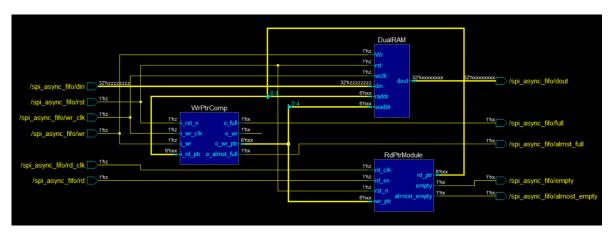

| 6.2             | Asynchronous FIFO block diagram              | 44      |  |

| 6.3             | Asynchronous FIFO Schematic                  | 44      |  |

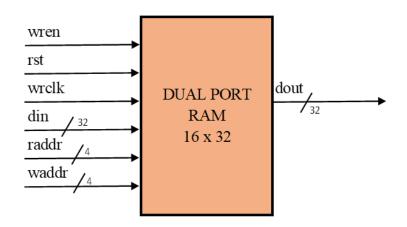

| 6.4             | Dual port RAM module                         | 45      |  |

| 6.5             | Data transfer between SPI master and slave   | 46      |  |

| 6.6             | Design State Diagram                         | 47      |  |

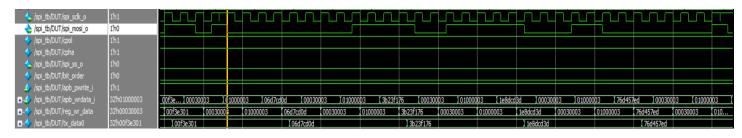

| 8.1             | Data transfer on MOSI line with clock mode-4 | 52      |  |

| 8.2             | Data transfer on MOSI line with clock mode-1 | 53      |  |

| 8.3             | Covergroup statistics                        | 53      |  |

| 8.4             | Assertions status                            | 54      |  |

| 8.5             | Overall Coverage report                      | 54      |  |

| List of Tables |                                 |         |  |

|----------------|---------------------------------|---------|--|

| Table No       | Name of the Table               | Page No |  |

| 4.1            | APB Signal List                 | 17      |  |

| 4.2            | Different states in APB         | 18      |  |

| 5.1            | Clock Transmission modes        | 23      |  |

| 5.2            | Master mode configurable pins   | 26      |  |

| 5.3            | Offset addresses for registers  | 28      |  |

| 5.4            | Description of GCR0 register    | 29      |  |

| 5.5            | Description of GCR1 register    | 29      |  |

| 5.6            | Description of INT0 register    | 30      |  |

| 5.7            | Description of INTLVL register  | 31      |  |

| 5.8            | Description of PC0 register     | 32      |  |

| 5.9            | Description of DAT0 register    | 33      |  |

| 5.10           | Description of DAT1 register    | 34      |  |

| 5.11           | Description of RXBUF register   | 35      |  |

| 5.12           | Description of RXEMU register   | 35      |  |

| 5.13           | Description of DELAY register   | 36      |  |

| 5.14           | Description of DEFCS register   | 36      |  |

| 5.15           | Description of FORMATn register | 37      |  |

| 5.16           | Description of INTVEC0 register | 38      |  |

| 5.17           | Description of INTVEC1 register | 38      |  |

## ABSTRACT

#### ABSTRACT

There are different types of protocols formulated for specific needs in the Very Large Scale Integrated circuit design. Some of those include On-chip Communication protocols, Interface protocols, Memory management protocols, I/O protocols. A protocol helps devices connect to each other and acts a mediator which carries data, addresses and other information required for the communication. There are different types of protocols which define a set of rules for the communication to happen. Each protocol is uniquely defined for the needs. Generally a protocol needs to be functionally verified in the design stage itself. Suppose at a later stage a bug is encountered it takes huge amount of money, time and work to be put in to fix that. Hence it is recommended to fix any errors or bugs in the early stages. These days Verification engineers are at high demand for this reason. Generally for a design with more complexity, the verification environment is developed using System Verilog. As the title of project suggests, the Functional Verification and Assertion based verification is performed for a communication protocol using System Verilog. The project aims on creating a testbench environment using the most common Hardware Verification Language(HVL).

The design involves an interfacing block which can be employed in between an APB Master and an SPI Slave. So it acts fairly as both APB slave and SPI Master. Advanced peripheral bus(APB) is a low power peripheral protocol under Advanced Microcontroller Bus Architecture(AMBA) bus. AMBA is an enrolled brand name of ARM Ltd. Serial Peripheral Interface(SPI) is a full duplex serial communication protocol developed by Motorola. APB is in a way considered to be a parallel bus. It is capable of upto 32 bit wide data transfer between the master and the slave. In the project, the focus is on the

- Design of the APB slave

- Deisgn of SPI Master

- Creating a verification environment to verify if the read and write operations are done successfully without any mismatches.

Since AMBA is a very vast protocol and has many components like AHB, AXI. The APB bridge here acts as a communication bridge between the AXI and the APB bus. Here the APB bus is designed to communicate with the peripherals.

AMBA is generally considered as the basic interconnect specification. Since it has the bus architecture, it enables the assembly and organization of the functional blocks in an SoC design. AMBA helps in even multiprocessor designs where many components and peripherals are involved. These days, every other ASIC or SoC is in a way incorporating AMBA bus architecture. On a variety of processors, which are a part of cellphones and gadgets use AMBA protocol. So, APB interface is picked up as an input.

One of the most used serial communication protocols is Serial Peripheral Interface. It is used for communication with the external peripherals serially. It acts as one of the high speed and highly reliable seral data stream supporting protocol. So the design this work emphasises, is about connecting these two protocols. The input comes from an SoC device which employs a high end communication and the output obtained will be a serial data stream driving a peripheral device like a Flash memory or a display driver.

# CHAPTER 1 INTRODUCTION

### CHAPTER 1 INTRODUCTION

The communication between electronic devices has been a challenging task over the years. So protocols have been devised by different companies for different levels. Each protocol has a set of rules by which the data transfer can be done between the devices. Some protocols can handle large amount of data which have more hardware complexities, some are small enough to handle minor data transfers. Some of the protocols include System-On-Chip communication protocols, Embedded system Interface Protocols, Memory Management Protocols, I/O protocols.

#### **1.1 On-Chip Communication Protocols:**

Such a protocol is used to define the inter connect specification inside an SoC. It defines the management of connections between the functional blocks inside the chip. SoC is an Integrated circuit chip which requires a busing system to connect to various components it is comprised of. Usually SoC consists of one or more microprocessors, memory, peripherals, and other special logic but not limited to these. So a shared bus is required for those components to connect to each other. Many SoC designs are implemented by the bus architectures defined by the leading manufacturers like IBM, ARM[1]. Those are listed as below:

- 1. CoreConnect by IBM

- 2. AMBA designed by ARM

- 3. SiliconBackPlane from Sonics

- 4. Avalon made by Altera

- 5. Wishbone by OpenCores

- 6. STBus by STMicroElectronics

- 7. Open Core Protocol(OCP) made by Accellera

Some of the architectures are compared by researchers [3][4].However AMBA specification is the most popular and most used among the SoC bus specifications for high performance devices including modern day Mobile devices.

#### **1.2 Embedded System Protocol:**

A set of rules that define a way to connect two devices to each other is called a protocol. Embedded system is group of components like microprocessor, memory, and external peripheral devices which has a specific function.

The two types of protocols used in the embedded designs are:

- 1. Protocol Communication between two systems

- 2. Protocol Communication inside the system

#### **1.2.1 Protocol Communication between two systems:**

This type of protocol is used for the data transfer between a CPU and some micro controller kit. It is often referred as Inter system Protocol.

This type of communication includes the following protocols:

#### **1.2.1.1 Universal Asynchronous Receiver Transmitter Protocol:**

The protocol serves as one of the serial protocols for the data transfer. Therese mainly two signals each for transmission(Tx) and reception(Rx). It sends and receives the data stream serially without any clock which makes it asynchronous. It is only half duplex communication which means only one data line is active at a time. UART needs a start bit and a stop as a validation signal to avoid data errors. It's data format generally used is 8 bit data stream. Usually microcontroller kits have UART signals on board.

#### **1.2.1.2 Universal Synchronous Asynchronous receiver Transmitter Protocol :**

This protocol serves both as an Asynchronous and synchronous mode. It facilitates the use of clock for the data transfer. In asynchronous mode the data is sent indefinitely without a particular data transfer rate. Unlike that Synchronous mode helps to send the data with respect to clock. Even this mode has two signals each for transmission and reception. In addition to the data clock pulses are also sent in this protocol when used in synchronous mode. It supports full duplex serial communication which allows the data transfer simultaneously on both the lines..

#### 1.2.1.3 Universal Serial Bus Protocol:

It is again a 2-wire serial communication protocol. The data signals are known as D+ and D-. This is mainly used for the system to communicate with its peripherals. So here the host can transmit or receive data to or from the peripherals without any request on the host system. But it needs a driver software according to the specification of the system and the peripheral. Almost every peripheral like mouse and keyboard are connected to the present day PCs using the USB protocol. There are different speed with which a USB can operate till 400mbps.

#### **1.2.2 Protocol Communication inside the system Protocol:**

Such a protocol is used for the data transfer between the two devices which are accommodated on the same circuit board. The circuit might become complex because the protocol is also employed inside the main circuit. But such a design is cost effective and is secure to access the data since no data is going out.

Such protocols include the following:

#### **1.2.2.1 Inter Integrated Circuit Protocol:**

The Inter Integrated circuit is often referred as I2C protocol. It has two wires which stand for SDA(serial data) and SCLK(serial clock). Since it is a 2-wire serial communication protocol only, one each for data and clock. It has a data word format which has a start and stop bits. It can support 8 bit data transfer but in a half-duplex mode. Since it has only one data line it can only send data to or receive data from a slave at a time. Each slave has a unique address. The start and stop bits are the deciding factors the serial data transfer. The Master first sends the target slave address on the address after the start bit and when the slave address matches it responds with an acknowledgement signal. After it is received the master starts sending the data serially. Even after the data transfer slave sends an ack signal which indicates the master to issue a stop bit. I2C is used in embedded systems where there is a need for a microcontroller to communicate with peripheral devices serially[17].

#### **1.2.2.2 Serial Peripheral Interface Protocol:**

The SPI is the one of the most commonly used serial protocols developed by Motorola . There are 4 signals under SPI called clk, mosi, miso, cs making it a 4-wire protocol [6]. It is full duplex communication protocol which is described in detail in the coming chapters. The SPI can operate in 3-pin mode which is even without chip select pin accomodating only one slave. The data rates and clock frequencies can be configured according to the needs.

#### **1.2.2.3** Controller Area Network Protocol:

It can be abbreviated as CAN. This is also a serial communication protocol developed by Robert Bosch. It consists of two signals CAN high and CAN low(H+ and H-). This protocol often finds use in the vehicular applications where we need airbag, antilock braking system.

#### **1.3 Interface Protocols:**

The protocols designed to act as interface between devices may be between multi device box or a single device box. These are commonly used as computer interface bus protocols where data between devices, Hard Disk Drives, RAM can be achieved. Some of the interface protocols defined are:

- 1. SATA(Serial Advanced Technology Attachment)

- 2. PCIe(Peripheral Component Interconnect Express)

PCIe is the most common Interface used in motherboard architecture through which HDD, SSD, Ethernet, WiFi, Graphic Cards, Host Adapters connections happen.

#### **1.4 Memory Management Protocols:**

A bus protocol which helps in communication from an IC such as microprocessor to an external memory on another circuit. The external main memory interface protocols are:

- 1. DDR

- 2. DDR2

- 3. DDR3

- 4. DDR4 etc.

DDR refers to Double Data Rate which means it is capable of two data reads and two data writes per clock cycles. Among these DDR4 has more speeds compared to DDR3 and so on. So each new version replaces the older memory interface protocols. Some of the memory interface protocols which are used for low power devices are:

- 1. LPDDR

- 2. Wide I/O

- 3. Memory MCP

## CHAPTER 2 LITERATURE REVIEW

#### **CHAPTER-2**

#### **Literature Review**

#### 2.1. Literature Survey on communication protocol designs

Communication protocol designs have evolved in a fast pace in the recent years. When it comes to On-Chip communications protocols many companies have left their footsteps in this field like AMBA developed by ARM [1] is by far the most popular communication protocol. After ARM becoming a giant in this field, companies like IBM, Altera, STMicro, Accellera have developed SoC communication through their interconnect structures which have been briefly discussed in [3]. Jovanovic et al. in [4] discussed about the three interconnect specifications. A. Shrivastav et al. took up the comparative study of various AMBA releases over the years in [5]. Each year ARM released newer and advanced versions of high performance system buses which added to the present day performance of the SoC. Under the AMBA specification , a low bandwidth interface is present which is used to drive the peripherals. The APB version used in this work is presented in [10].

Leens et.al. discussed the overview and a brief comparison study of most used serial communication protocols which are I2C and SPI in [6]. These are used as a connections from the microcontrollers to the external peripherals. The I2C and SPI need 2 wires and 4 wires respectively. Basic SPI was first developed by Motorola, which is then carried forward by Freescale semiconductor [7] which is now NXP Semiconductors. The thesis work is related to the guide published by the Texas Instruments [8]. Many companies came up with different specifications formulated for their own controllers. So SPI has multiple specifications unlike its 2-wire competitor I2C which is given by firstly developed by Philips but then developed later by NXP [9]. These are the most common peripheral interfaces used for the serial communication with microcontrollers.

#### 2.2. Literature Survey on designs involving physical implementation

Anand N et al. discusses the design approaches which explore the flexibility of the transmission modes of SPI and capability of driving multiple slaves with chip select lines. They verified the model using an FPGA where the results showed a very high clock frequency in [16]. Oudjida et al. discussed physical implementation aspects of the two serial communication protocols as a comparative study in [17]. A. K. Oudjida in [18] proposed general purpose Master/Slave Ips which are mapped on to FPGA for verification. The model proposed runs on OPB bus(On-chip Peripheral Bus) which is an interconnect specification developed by IBM. M. B. Aykenar et al. proposed a less logic resourced SPI Master design which helps in making cost effective FPGAs in [19]. Ge Zhiwei et al. proposed an image processing technique based on APB bus with CMOS sensor in [35]. It shows that can enhance the image quality using the auto white balance method.

N. b. Mohd Noor et al. proposed a new concept of utilizing the SPI design and achieving a different data transfer mode in contrast to continuous data stream in [20]. The design can incorporate burst, continuous, interleave data streams. S. Saha in [21] formulated a self-testing capability in SPI interface which eliminates the need of two devices to verify the communication. This method which mainly reduces the testing cost is run over an FPGA Recently, Internet of Things has seen a boom in the electronics industry. L. Huihui in [34] designed a SPI master controller driver which is based on VxWorks, a Real time operating system developed by WindRiver. VxWorks is an RTOS developed for IoT applications. R. R. Pahlevi et al. in [22] designed a faster SPI slave for scalable IoT platform which needed change in control register. P. S. Mutha in [23] proposed a design where the reconfiguration of FPGA can be done through UART lines and an SPI Flash. Since FPGAs are reusable they are reconfigured using SPI flash which in turn reduces time.

#### 2.3. Literature survey on IP Core designs involving two protocols

Since the communication on a chip happens with a high performance interconnect specification, there needs to be a low bandwidth peripheral driving protocol. APB happens to be the low bandwidth bus that is used to communicate with the peripherals. APB being a parallel sometimes cannot be integrated with a serial data slave device. So, to eliminate this problem serial communication protocols should be accompanied. One such protocol is Serial Peripheral Interface which is serial full duplex 4-wire communication protocol.

One more popular 2-wire protocol used for this purpose is I2C. Implementing a bridge between I2C and APB bus is proposed by J. Chhikara et al. in [11]. D. Trivedi et al. proposed a communication between two widely accepted protocols which are I2C and SPI. In [33] they proposed a design where SPI as 4-wire protocol is the sender and is received by a receiver which runs on I2C. Using the high speed of SPI and less hardware of I2C the design is proposed. L. Bacciarelli et al. proposed an architecture to interface the serial protocols for the APB bus in [12]. M. Hafeez et al. in [13] showed up an IP Core design which takes input as APB signals and giving out SPI signals. They designed a SPI Master controller which is controlled by the different registers to configure. Cadence developed an IP core for production into the market which acts as an interface between the APB bus and the SPI peripherals. It [14] involves a 32 bit APB parallel bus as an input which ultimately produces a serial full duplex output. J. Yang et al. proposed a configurable SPI interface for the AMBA APB bus in [15]. They gave a model which is convenient and flexible to use. The design works with a programmable transmission mode, data transfer rate, clock frequency, direction of bit transfer. Using a FPGA toolkit they verified the working with slave devices for communication. The high performance system bus ASB needs a bridge to communicate with the peripheral bus APB which is discussed in [10].

#### 2.4. Literature Survey on Verification of protocol designs

If the verification is about reusability the testbench methodology called Universal Verification Methodology is used. Dipti Girdhar Shankar et al. developed a UVM module for verification of APB protocol in [31]. Even R.K Vaishnavi et al. developed a design of APB module and verified it through the reusable methodology in [32]. Jaideep Varier E.V. et al. discussed about the Verification of the IIC protocol using UVM in [24]. Here, the interface used is an APB interface. Z. Zhou et al. in [25] developed a verification environment for SPI with an APB driver where coverage, assertions were used with checker and scoreboard for reusability. Constrained random vectors are driven into the DUT for higher functional coverage.

In [26] Y P. Jain et al. formulated a design which acts as APB Slave and a verification environment using random values driven onto the design. P. Dwivedi et al. in [27] proposed an assertion and coverage based verification model for the APB bus. It covers all the internal transactions in the APB cycle using the constrained random checks and assertions. Y. Guo et al. in [28] formulated constrained random coverage along with self-check verification module with SPI interface using UVM. P. Gurha et al. in [29] modulated an SVA based approach to verify the AHB to APB bridge. B. Vineeth et al.

in [30] proposed a UVM based verification plan where coverage based verification is performed. At the same time scoreboards are included to check automatically if the functions are met correctly.

#### 2.5. Dissertation Contribution

Following are the detailed contributions of this dissertation:

#### 2.5.1 Brief about APB and SPI:

We first review the design specs developed by the major tech companies. Each company have its own interconnect specifications for On-chip communication. But, needless to say AMBA is the most used SoC protocols in the market today. Every mobile phone accommodates an SoC which uses high performance AMBA bus. Out of all the high performance system buses APB is the one bus which is used for the communication with the external peripheral devices.

It is one of the important aspects for a microcontroller to communicate with peripherals such as keypad, timer etc. When it comes to streaming data serially two most used protocols are I2C and SPI. Since SPI is the faster protocol and a full duplex communication supported one, it is chosen by most. Even though it has 4 wires it is used extensively till date. So these protocols are briefly discussed in the early chapters of this work.

#### 2.5.2 Design specification involving APB Slave/SPI Master IP Core:

Here, the major design specification is proposed. In the hierarchy of AMBA buses, a system bus like AHB or ASB is mandatory for an SoC. When the data stream is to be transported inside a major bus like AXI, AHB, ASB is needed but when it comes to low bandwidth peripheral operations those higher end protocols are not needed. That's where the use of Advanced Peripheral Bus comes in. Even to convert an AHB transaction into an APB transaction, a bridge is needed. As an output from the bridge we obtain APB bus which is distributed on to every peripheral device.

The APB bus is however a complex bus for a simple serial data driven peripheral. So that's where an SPI bus finds a need. In devices like sensors, ADC, Flash memory, video game controllers SPI is used. So to communicate with these we need an SPI Master to stream the data outwards. The design proposed in this work acts both as an APB Slave which takes input as APB bus and an SPI Master which drives SPI Slaves. So in a way this IP Core acts as a parallel to serial communication protocol where at the output end, we achieve a high speed, serial, full duplex communication protocol.

## **2.5.3** Functional Coverage and Assertion based Verification of the design:

This design is verified functionally using coverage metrics. Assertions are used to check if the condition is met, if not the assertion fails. The assertions are written using System Verilog Assertions(SVA). The coverage done in this thesis involves code coverage also which basically gives an idea about how much of our code is used and not wasted. This type of verification is growing popular because all the test cases are checked in the simulation stage itself which drastically reduces costs.

# CHAPTER 3 AMBA

## CHAPTER 3 AMBA

#### 3.1 Background:

Advanced RISC Machine(ARM) Limited first introduced AMBA(Advanced Microcontroller Bus Architecture) in the year 1996. In the beginning, APB and ASB protocols were introduced. In 1999, as its second release the Advance High performance bus was added. In the coming years, they were succeeded by the third generation AMBA.

AMBA 3 contained Advanced extensible Interface which focused on higher interconnect performance and also the Advanced Trace Bus. AMBA 4 that was released recently in 2011 had AXI4 along with the coherency extensions. In the following years AMBA released Coherent Hub Interface with a redesigned layers and features that reduced overcrowding.

The SOC building not only depends on the components it contains, even the connections it possesses. AMBA helps interconnection of the components inside a System on chip.

The aim of the AMBA protocol is to:

- 1. It enables development of a processor unit with either single or multiple processors

- 2. It allows reuse of intellectual property cores and other macrocells

- 3. It encourages system design module-by-module where peripheral and system libraries can be reused.

- 4. Helps in reducing silicon while enabling high performance and less power consuming designs

#### **3.2 AMBA protocol specifications:**

The AMBA specification provides a SoC standard that enables designing high performance microcontrollers. Even though it was developed by ARM Limited, it enjoys wide participation throughout the industry which makes it easy for the designers to develop a processor or microcontroller.

The AMBA release facilitates a SoC standard that enables us in designing a high performance micro-controller. The three buses that are widely used in the bus protocol specification are:

#### 3.2.1 Advanced High-performance Bus:

It is mainly designed for high performance and which involves high frequencies. It supports the effective connection of processors, memory blocks that are present on-chip and off-chip with all the low-power peripherals. Its main advantages include: high performance, pipelined process, multiple bus transactions, burst transfers.

#### 3.2.2 Advanced System Bus:

It is the one stop alternate solution if high performance system bus modules are needed, but all the AHB features are not required. It also supports all other functionalities such as efficient connection of processors, on and off-chip memory and the peripherals. Its main advantages include: high performance, pipelined process, multiple bus transactions

#### **3.2.3 Advanced Peripheral Bus:**

The APB protocol is basically designed for the peripheral that consume low power. Over the years APB is improved so that it is comfortably used with devices consuming low power and those which involve reduced interface complexity. It is generally adaptable to any release of the system bus. Its main advantages include: less power consumption, quite simple interface, latched address, appropriate for a large number of peripherals.

#### **3.3 A general purpose AMBA built microcontroller:**

A microcontroller built on AMBA generally comprises of a high level system bus which is able to transact with the on-chip residing memory, external memory devices and direct memory access controllers. This bus provides a high-bandwidth interface between the components concerned within the most of the transfers. Conjointly situated on the AHB may be a bridge that connects to APB bus where all the peripheral devices are connected (see Fig. 3.1).

#### Fig. 3.1 AMBA Functional Block Diagram

APB helps in providing the peripheral transactions as the minor bus whereas the high performance system bus(AMBA AHB and AMBA APB) acts as the main system. The peripherals under this generally:

- May have interfaces with memory map

- Has low-bandwidth interface

- They are under manageable level when coded accordingly

Generally the external memory interface is specific to the desired application. In this case we use SPI data bus as the peripheral interface. It supports a test access mode which allows the internal AMBA AHB, ASB and APB modules to be tested.

#### **3.4 AMBA Release Versions:**

The ARM till now released 5 versions of AMBA bus. In each version, it has added some new protocols or released a new edition of the same protocol. Highlights of each release is listed below:

AMBA v5 release involves the buses:

- AXI v5.0, AXI5Lite and ACE v5.0

- AHB5, AHBLite

- CHI interface

AMBA 4 release involves following main buses:

- ACE, ACELite, AXI4, AXI4Lite

- APB4 v2

AMBA 3.0 release involves following buses:

- AXI4

- AHBLite v1

- APB3 v1

- ATB v1.0

AMBA 2.0 release involves 3 buses:

- AHB2

- ASB2

- APB2

AMBA 1 release involves 2 buses:

- ASB

- APB

Advanced System Bus(ASB) is the one of the first generation buses developed under AMBA. ASB sits on top of the peripheral bus for the high performance system operations such as pipelining, burst transfers, and supporting multiple bus master modes. Bus masters could be a high performance processor, high bandwidth memory interface or even a DMA or DSP processor. An APB bridge or internal memory are the most common slaves. Any peripheral connected to the system might also serve as an ASB slave

ASB Master initialises the read and write operations providing the address and control information. The ASB arbiter takes care that only one bus master initiates the data transfers at a time. ASB decoder decodes the transfer addresses and selects the slave appropriately. ASB slave responds about the read and write to the master if it's a success or failure.

Another High performance bus that is most used is Advanced High Performance Bus(AHB). The features required for high bandwidth and high performance operations include Wider data bus configurations(64 or 128 bits), Burst transfers, Split transactions among others. All other components are similar to the system bus. These higher performance buses need a bridge to implement the connection to peripheral bus like APB and should be done efficiently to integrate it to other existing designs.

# CHAPTER 4 ADVANCED PERIPHERAL BUS

## CHAPTER 4 ADVANCE PERIPHERAL BUS

#### 4.1 Introduction:

APB as a part of AMBA has been far more power efficient and has been effective in terms of interfacing. The APB is a component of the AMBA buses and is far more effective for reduced power consumption and less interface complexness[2]. It is generally not regarded as a primary bus. But when accompanied by a high performance bus they both bind together in a very good way. It is known for providing a low power bus protocol to a performance oriented system bus. This protocol is mainly used when there is no use of high performance and the peripherals just need a low bandwidth operation. The APB specification specifies, signal change is all dependent on the rising clock edge.

The above changes made possible the below listed advantages:

- It is easy to attain a large frequency for process

- Output is regardless of the clock's mark space ratio

- STA is simplified by the usage of one clock edge

- No special consideration are necessary for automatic insertion of the control

- Several ASIC libraries have an improved choice of rising edge registers

APB bus mainly contains a bridge that is responsible to convert the high performance transactions into the peripheral understandable language. The bridge enables latching of all types of signals, and also provides a deciphering mechanism that generates the slave select signals. Sometimes the main system bus might change for the SoC. In [10] he system bus involved was ASB. The authors managed to design a bridge which could convert the transactions into peripheral bus transaction. Generally for high performance systems, AHB is the higher level bus that would be involved. The same AHB-APB bridge is discusses in [36]. Similarly bridge between I2C and APB is designed because both need to share resources but the protocols are different. The AHB/ASB to APB bridge is shown in the Fig. 4.1. The signals on the right indicate the APB interface signals used to drive an APB Slave.

#### Fig. 4.1 APB Bridge between ASB and APB slave

All the other modules are typically slaves. A typical APB Slave is as shown in the Fig.4.2 The APB peripherals have the below listed features:

- The address and control can be valid throughout the access

- zero-power interface throughout non-peripheral bus activity (peripheral bus is static once not in use)

- Timing can be analyzed by means of decode with the unclocked interface.

- Write information valid for the total access (allowing glitch-free clear latch implementations).

Fig. 4.2 APB slave

#### 4.2 APB signal list:

All APB signals have the letter P as prefix. The below table shows the list of APB signals

#### AMBA APB signals

| APB Bus Signal        | Description                                                    |

|-----------------------|----------------------------------------------------------------|

| PCLK(Bus Clock)       | The rising edge of this signal times all signals on the bus    |

|                       | The active low signal that is generally connected to system    |

| PRESETn(APB reset)    | bus                                                            |

| PADDR[0:31]           | Address bus which comes from the APB Interface                 |

|                       | Each bus slave has this and it indicates that particular slave |

| PSELx(APB Select)     | is selected and needs a transfer                               |

| PENABLE(APB strobe)   | This indicates 2nd cycle on the transfer.                      |

| PWRITE(APB transfer   |                                                                |

| direction)            | Low is read and high is write                                  |

| PRDATA(APB read data  | Driven by the selected slave for a read operation which is 32  |

| bus)                  | bit wide                                                       |

| PWDATA(APB write data |                                                                |

| bus)                  | Driven by APB bus and is 32 bit wide when pwrite is high       |

|                       | Table 4.1 ADD Signal List                                      |

#### Table 4.1 APB Signal List

**4.3 APB specifications:** The table above represents the signals of an APB bus. Since APB is a parallel bus the address and data are 32 bit wide.

#### State Diagram:

APB state machine jumps to three states:

**IDLE:** This is the default state.

**SETUP**: When a transfer is needed, the bus moves into the SETUP state **PSELx**, is asserted. The bus remains for only one cycle then jumps to enable after a rising clock edge.

**ENABLE**: Here enable signal, **PENABLE** is asserted. All signals stay stable during the jump. This state only lasts for one cycle if no other transfers then returns to IDLE if there then jumps to SETUP state. Every signal can be subjected to a change during the jump to SETUP. The jump from the ACCESS state depends on the state of the PREADY signal.

If PREADY is held low by the peripheral the state remains unchanged. When that is held High the state jumps to SETUP if transfer is needed. If not, state jumps to IDLE state.

Fig. 4.3 APB State Diagram

There are 3 states in the state diagram of a APB transaction:

- 1. Setup

- 2. Write Enable

- 3. Read Enable

| APB signals | Setup | Read Enable | Write enable |

|-------------|-------|-------------|--------------|

| Psel        | 1     | 1           | 1            |

| Penable     | 0     | 1           | 1            |

| Pwrite      | -     | 0           | 1            |

**Table 4.2 Different States of APB**

Whenever there is a positive edge of clock, the above values are checked for every cycle. According to these values, the state changes and the read, write operations are performed

# CHAPTER 5 SPI PROTOCOL

### CHAPTER 5 SPI PROTOCOL

#### 5.1 Introduction:

Serial Peripheral Interface is abbreviated as SPI. It works as a high speed synchronous serial communication protocol[16] which lets you program a convenient bit transfer rate to be transmitted and received. Since it supports full duplex mode it can be simultaneously at a time[6]. The SPI is generally used with a micro controller device and a peripheral. Since it acts a high speed serial port it assumes use in applications like memory devices(FLASH), LCD display drivers, sensors and some converters(ADCs,DACs).

#### 5.1.1 Features of SPI include:

- 1. Programmable master or slave mode

- 2. Chip select signal

- 3. Registers used to transmit data

- 4. Buffer register for reception

- 5. Registers to select Data Format

- 6. Capability to be driven by Interrupts

#### 5.1.2 Basic configurable features of SPI:

- 1. The clock frequency of SPI

- 2. Number of pins(3-pin or 4-pin)

- 3. The data word length can also be modified with the shift direction.

- 4. 4 clock transmission modes

- 5. Any type of delay(b/w the transfers, setup, hold)

- 6. The setup and hold times of chip select signal

- 7. The chip select can also be held

The protocol supports change of number of pins. If it's a bus master every pins is driven by itself. Additionally chip select pin is added to the list if it operates in a 4 pin mode. It means it can operate multiple slaves, but SPI supports only a single master. The Fig. 5.1 shows a functional block diagram of SPI protocol[8]. The four external pins or signals are:

Fig. 5.1 Functional Block diagram of SPI protocol

#### 5.2 Signal List:

**MOSI**: This pin is used to transmit data out of the SPI Master and receive data into SPI Slave.

**MISO**: This pin is used to transmit data out of the SPI Slave and receive data into the SPI Master.

**SS:** This pin is used to select the peripheral device(slave) when it is configured as Master and used to receive the signal when configured as Slave. This enables to drive multiple slaves by the same single SPI bus

**SCK**: This pin is used to generate the clock when it is configured as SPI Master according to which the data transfer happens. When the module is configured as Slave pin is used to receive the clock.

SPI supports reset mode when the RESET bit is set in the Global control register. SPI supports power conservation using a POWERDOWN mode. When set, the module enters into power saving mode which means all operations are inactive.

**Clock**: The clock is obtained from the module clock provided. The maximum achievable frequency is half of the module clock frequency. The clock frequency for the SPI is determined by the PRESCALE bit in the format registers(FORMATn). The clock is obtained from the module clock through the below formula:

Frequency of clock = (Module clock) /(PRESCALE + 1)

When the prescale is cleared, the clock frequency is set to the default value of half of module clock.

### 5.3 Pin modes:

### 5.3.1 3-pin mode:

This mode uses the clock and both the data pins for data transfer between the master and slave devices. The below Fig. 5.2 shows the mode with only 3 pins.

### Fig. 5.2 3-pin mode

To run the SPI in 3-pin mode, the CLK, SOMI, and SIMO pins should be made as functional pins by setting the bits high in pin control register 0 (PC0).

To make SPI as master, the bits in global control register should be set high. The master is the device decides whether to generate clock and to initiate data transfer. The necessary bits in the Global Control register should be set high. In master generally the master in slave out pin is in high impedance state and output buffer of the other data pin is enabled.

The master mode SPI device takes in the data through the two data transmission registers which initiates the data transfer. A series of clock pulses help the data to be transferred simultaneously in and out of the master and slave devices. Either of the two data transmission registers can used on both master and slave.

### 5.3.2 4-pin mode:

This mode has an additional chip select pin along with the data and clock pins[14]. Fig. 5.3 shows the 4-pin mode of the SPI.

Fig. 5.3 4-pin mode

In addition to MOSI, MISO, CLK, the chip select pin(SPISCS[n]) is also configured as functional pin using the pin control register bits.

When SPI is configured as master the chip select pin works as output pin and is activated when a slave is selected. Only one slave chip select pin can be incorporated in the SPI. However, multiple general I/O pins are needed to support multiple slave chip selects.

The advantage of using the chip select as a functional pin is set the timing parameters using the delay register's SPIDELAY pin. To meet the slave timing requirements the such a delay can be used to automatically add the delays. Another advantage is to have the error detection capability.

### 5.4 Data formats:

The protocol offers an option to configure with format of the data used[15]. The data formats are configured by varying the bits in the data format registers(FORMATn). The following characteristics change in each data format:

- Character length: It is represented by CHARLEN field in the data format register. It can vary from 2 to 16 bits.

- Shift direction: The data transferred can be even configured for the direction. SHIFTDIR represents if the LSB or MSB is to be shifted first.

- Clock polarity: It can be configured by the CPOL bit.

- Clock phase: It is configured by the CPHA bit.

On each transaction, the data format is chosen. The data format can change for every transaction or can be configured once for every transaction that follows until it is changed.

### Shift direction:

The protocol automatically right aligns the data even if its transmitted or received data.

### **Character Length:**

The character length of the data can have values from 2 bits (2h) to 16 bits (10h). It should be programmed in the master mode. It is independently configured for each of the four data formats.

### **CPOL and CPHA:**

The protocol gives a flexibility to choose between the options of four different clock modes. These 4 combinations are defined upon the clock phase and the clock polarity. These modes help to connect easily to the other serial peripheral devices.

| CPOL | СРНА | Action                                                                                                               |

|------|------|----------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | Output data is obtained at posedge of clk. Input data is latched on the negedge of clk                               |

| 0    | 1    | Output data is obtained one half clock prior to the first posedge of clk.<br>Input data is latched on the negedge.   |

| 1    | 0    | Output data is obtained on the negedge of the clk. Input data is latched<br>on the posedge of the clk.               |

| 1    | 1    | Output data is obtained one half clock cycle prior to the first negedge of clk. Input data is latched on the negedge |

### Table 5.1 Clock transmission modes

- 1. Clock Phase=0 which means clock without delay:

- Data is outputted on the positive edge of clock

- Input data is latched on the negative edge of the SPICLK

- The clock starts with the data coming at the data register

### Fig. 5.4 Timing diagram for CPOL=0, CPHA=0

- 2. Clock Phase=1 which means clock with delay:

- Data is outputted a half cycle before a the first positive edge of the clock and subsequently falls on every negative edge of the clock

- Input data is latched on the positive edge of the SPICLK

### Fig. 5.5 Timing diagram for CPOL=0, CPHA=1

- 3. Clock Phase=0 which means clock without delay:

- Data is outputted on every negative edge of clock

- Input data is latched on every positive edge of the SPICLK

- The clock starts with the data coming at the data register

### Fig. 5.6 Timing diagram for CPOL=1, CPHA=0

- 4. Clock Phase=1 which means clock with delay:

- Data is outputted a half cycle before the first negative edge of the clock and subsequently falls on every positive edge of the clock

- Input data is latched on the negative edge of the SPICLK

- The clock starts with the data coming at the data register

### 5.5 Master mode:

If the Master bit in Global control register is set high the SPI operates in Master mode ready to drive the signals to slave devices. In addition to that for the SPI module to function as Master, it needs to be set with the following configuration bits in 3-pin and 4pin modes respectively

| Name of the register | Bit      | 3-pin | 4-pin |

|----------------------|----------|-------|-------|

| GCR0                 | RESET    | 1     | 1     |

| GCR1                 | ENABLE   | 1     | 1     |

| GCR1                 | LOOPBACK | 0     | 0     |

| GCR1                 | CLKMOD   | 1     | 1     |

| GCR1                 | MASTER   | 1     | 1     |

| PC0                  | SOMIFUN  | 1     | 1     |

| PC0                  | SIMOFUN  | 1     | 1     |

| PC0                  | CLKFUN   | 1     | 1     |

| PC0                  | ENAFUN   | 0     | 0     |

| PC0                  | SCS0FUN  | 0     | 1     |

Table 5.2 Master mode configurable pins

### **Timing Options in SPI Master mode:**

The SPI operating in master mode gives multiple options to supports several options to alter the timing for generating the chip select pin (CS[n]). This allows to add additional timing delays automatically according to the requirement to synchronize the multiple slave devices.

# 5.5.1 Chip Select setup time:

The master can be made to provide a slower slave, a slave select setup time before the first edge of clock. This setup time can only be enabled while the master is in 4-pin mode. The setup time can be configured using C2TDELAY in the delay register of the SPI registers. The C2TDELAY values range from 2 to 257 SPI module clock cycles. The C2TDELAY begins after the chip select pin is asserted.

The C2T delay period is specified by:

Max C2TDELAY period = C2TDELAY + 2 clock cycles(2 to 257 clocks)

The prior value of the chip select hold bit in the transmit data register must be cleared for this delay to be enabled.

### 5.5.2 Chip Select Hold time:

The master device can be made to provide a slower slave, a chip select setup time after the last edge of clock. This setup time can only be enabled while the master is in 4-pin mode. The setup time can be configured using T2CDELAY in the delay register of the SPI registers. The T2CDELAY values range from 1 to 256 SPI module clock cycles. The T2CDELAY begins after the end of shift period.

The T2CDELAY delay period is specified by:

Max T2CDELAY period = T2CDELAY + 1 clock cycles(1 to 256 clocks)

The present value of the chip select hold bit in the transmit data register must be cleared for this delay to be enabled

### 5.5.3 Delay between transmission:

The Master device can automatically put a delay of 2 to 65 clock cycles in between the transmissions. This delay is set by the WDELAY and can be enabled by the delay counter bit. This delay period begins when the T2CDELAY or T2EDELAY terminates or when the master deasserts the chip select when both are disabled.

The WDELAY delay period is specified by:

Max WDELAY period = WDELAY + 2 clock cycles(2 to 65 clocks)

### 5.5.4 Chip Select Hold option:

There can be slaves which require the chip select to be active for continuous data transmission. There might be slave devices which need the chip selects to be deactivated during successive word transfers. The CSHOLD in data transmit register determines if the chip select is to be held or not. If this hold option is enabled, then both the above delays will not applied before the second transfer and after the first transfer. However the WDELAY period can be applied if it is enabled.

When this bit is disabled while the data transfer is happening, the values of chip select number field in the data transmit register is written to slave chip select pins. All the chip select default pattern values(CSDEF[n:0]) are put on to the slave chip select pins

### 5.6 SPI Registers:

The SPI module is often considered to be a configurable serial interface. It can be usually configured using the registers. Three types of registers are used mainly: Control, Data and pin registers. The offset is relative to the base address of the module.

| Offset Address | Acronym | Register Description         |

|----------------|---------|------------------------------|

| Oh             | GCR0    | Global Control Register 0    |

| 4h             | GCR1    | Global Control Register 1    |

| 8h             | INT0    | Int Register                 |

| Ch             | INTLVL  | Int Level Register           |

| 10h            | FLG     | Flag Register                |

| 14h            | PC0     | Pin Control Register 0       |

| 38h            | DAT0    | Data Tx Register 0           |

| 3Ch            | DAT1    | Data Tx Register 1           |

| 40h            | RXBUF   | Rx Buffer Register           |

| 44h            | RXEMU   | Rx Emulation Register        |

| 48h            | DELAY   | Delay Register               |

| 4Ch            | DEFCS   | Default Chip Select Register |

| 50h            | FORMAT0 | Data Format Register 0       |

| 54h            | FORMAT1 | Data Format Register 1       |

| 58h            | FORMAT2 | Data Format Register 2       |

| 5Ch            | FORMAT3 | Data Format Register 3       |

| 60h            | INTVEC0 | Int Vector Register 0        |

| 64h            | INTVEC1 | Int Vector Register 1        |

Table 5.3 Offset addresses for registers

# 5.6.1 Global Control Register 0:

| 31 |          | 10    |

|----|----------|-------|

|    | Reserved |       |

|    | R-0      |       |

| 15 |          | 1 0   |

|    | Reserved | RESET |

|    | R-0      | R/W-0 |

Legend: R = Re ad only; R/W = Re ad/Write; -n = value after reset

# Fig. 5.8 GCR0 Register

| Bit | Bit Field Description |                          |  |  |  |

|-----|-----------------------|--------------------------|--|--|--|

|     |                       | If 0 it is in Reset mode |  |  |  |

| 0   | RESET                 | If 1 it's not in reset   |  |  |  |

|     |                       | mode                     |  |  |  |

Table 5.4 Description of GCR0 Register

# 5.6.2 Global Control Register 1:

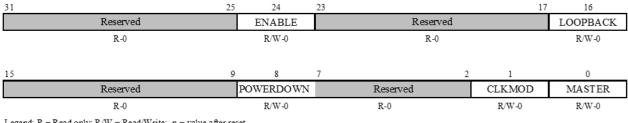

Legend: R = Read only; R/W = Read/Write; -n = value after reset

# Fig. 5.9 GCR1 Register

| Bit | Field    | Description                                                       |  |  |

|-----|----------|-------------------------------------------------------------------|--|--|

|     |          | This bit when set high enables the SPI transfers                  |  |  |

|     |          | When cleared to 0, some of the SPI registers go to their          |  |  |

| 24  | ENABLE   | default states                                                    |  |  |

|     |          | 0= Disabled for transfers.                                        |  |  |

|     |          | 1 = SPI is activated.                                             |  |  |

|     | LOOPBACK | The internal loopback testing can be done through this bit.       |  |  |

| 16  |          | Both the data bits are internally connected and the transmit      |  |  |

| 10  |          | data is stored in the receive field. Externally the data pins are |  |  |

|     |          | in high impedance state and clock gives an inactive value. SPI    |  |  |

|     |                   | should be in master mode to select loopback<br>0 = Disabled loopback mode<br>1 = Loopback mode enabled                                                                    |  |  |  |

|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 8   | POWERDOWN         | When set high, the SPI enters an inactive state.<br>0 = Active state.<br>1 = Inactive mode                                                                                |  |  |  |

| 1-0 | CLKMOD,<br>MASTER | These bits when configured as 3h, represent Master mode. All<br>other modes are retained for compatibility. All the 4 pins act<br>functional when SPI operates as Master. |  |  |  |

# Table 5.5 Description of GCR1 Register

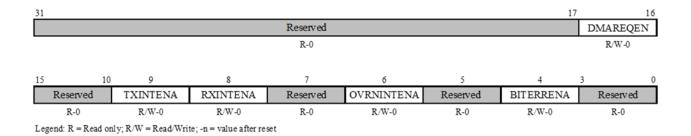

# 5.6.3 Interrupt Register:

# Fig. 5.10 INTO Register

| Bit | Field    | Description                                                |  |  |  |  |

|-----|----------|------------------------------------------------------------|--|--|--|--|

|     |          | Direct Memory Access Request Enable This bit should be set |  |  |  |  |

| 16  | DMAREQEN | high only after setting the Enable bit.                    |  |  |  |  |

| 10  |          | 0 = Direct Memory Access is not used.                      |  |  |  |  |

|     |          | 1 = Requests are generated.                                |  |  |  |  |

|     |          | Tx int enable.                                             |  |  |  |  |

| 9   | TXINTENA | 0 = No int even if flag is high                            |  |  |  |  |

|     |          | 1 = Int will be generated if the flag is set high          |  |  |  |  |

| 8   | RXINTENA | Rx int enable.                                             |  |  |  |  |

| 0   |          | 0 = No int even if flag is high                            |  |  |  |  |

|   |            | 1 = Int will be generated if the flag is set high |  |  |  |

|---|------------|---------------------------------------------------|--|--|--|

|   |            | Overrun int enable                                |  |  |  |

| 6 | OVRNINTENA | 0 = Not enabled.                                  |  |  |  |

|   |            | 1 = It will be enabled.                           |  |  |  |

|   |            | when bit error occurs this interrupt is enabled.  |  |  |  |

| 4 | BITERRENA  | 0 = No Int enabled on bit error.                  |  |  |  |

|   |            | 1 = Enables an int on a bit error                 |  |  |  |

# Table 5.6 Description of INT0 Register

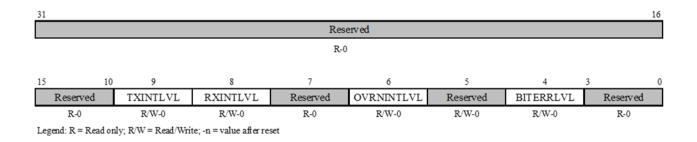

# 5.6.4 Interrupt Level Register:

# Fig. 5.11 INTLVL Register

| Bit | Field      | Description           |  |  |  |

|-----|------------|-----------------------|--|--|--|

|     |            | Tx int level.         |  |  |  |

| 9   | TXINTLVL   | 0 = mapped to INT0.   |  |  |  |

|     |            | 1 = mapped to INT1.   |  |  |  |

|     |            | Rx int level.         |  |  |  |

| 8   | RXINTLVL   | 0 = mapped to INT0.   |  |  |  |

|     |            | 1 = mapped to INT1.   |  |  |  |

|     |            | Rx overrun int level. |  |  |  |

| 6   | OVRNINTLVL | 0 = mapped to INT0.   |  |  |  |

|     |            | 1 =mapped to INT1.    |  |  |  |

|   |           | Bit error int level. |

|---|-----------|----------------------|

| 4 | BITERRLVL | 0 = mapped to INT0.  |

|   |           | 1 = mapped to INT1.  |

# 5.6.5 Flag Register:

| 31 |          |          |          |          |            |          |           | 16       |

|----|----------|----------|----------|----------|------------|----------|-----------|----------|

|    | Reserved |          |          |          |            |          |           |          |

|    |          |          |          | R-0      | )          |          |           |          |

|    |          |          |          |          |            |          |           |          |

| 15 | 10       | 9        | 8        | 7        | б          | 5        | 4         | 3 0      |

|    | Reserved | TXINTFLG | RXINTFLX | Reserved | OVRNINTFLG | Reserved | BITERRFLG | Reserved |

|    | R-0      | R-0      | R/WC-0   | R-0      | R/WC-0     | R-0      | R/WC-0    | R-0      |

|    |          |          |          |          |            |          |           |          |

Legend: R = Read only; W = Write only; WC = Write/Clear; -n = value after reset

# Fig. 5.12 FLG Register

| Bit | Field       | Description                                                  |

|-----|-------------|--------------------------------------------------------------|

|     |             | Transmitter empty interrupt flag.                            |

| 9   | TXINTFLG    | 0 = It indicates transmitter is full.                        |

|     |             | 1 = It indicates transmit buffer is empty.                   |

|     |             | Receiver full interrupt flag.                                |