### DESIGN OF ENERGY EFFICIENT TRANSCEIVER BLOCKS FOR WIRELESS SENSOR NODES

SAJI M ANTONY

### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY, NEW DELHI

May 2020

## DESIGN OF ENERGY EFFICIENT TRANSCEIVER BLOCKS FOR WIRELESS SENSOR NODES

A thesis submitted in fulfilment of the requirements for the degree of

**Doctor of Philosophy**

in

**Electronics and Communication Engineering**

by

SAJI M ANTONY

### (2K14/PHDEC/01)

under the Guidance of

Prof. S. Indu Department of Electronics and Communication Engineering, Delhi Technological University, Delhi

and

Prof. Rajeshwari Pandey Department of Electronics and Communication Engineering, Delhi Technological University, Delhi

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING DELHI TECHNOLOGICAL UNIVERSITY, NEW DELHI

May, 2020

### **CERTIFICATE**

This is to certify that the thesis titled "**Design of Energy Efficient Transceiver Blocks for Wireless Sensor Nodes**" being submitted by Saji M Antony to the Department of Electronics and Communication Engineering, Delhi Technological University, Delhi, for fulfilment of requirements for award of degree of Doctor of Philosophy, is a record of bonafide research work carried out by her under our guidance and supervision. In our opinion, the thesis has reached the standards fulfilling the requirements of the regulations relating to the degree.

It is also certified that this thesis has not been submitted to any other university or institute for the award of any degree or diploma.

#### **Prof. S. Indu**

Professor Department of Electronics and -Communication Engineering, Delhi Technological University, Delhi - 110042

#### **Prof. Rajeshwari Pandey**

Professor Department of Electronics and -Communication Engineering, Delhi Technological University, Delhi - 110042

# Acknowledgments

First, I would like to express my deep gratitude to my supervisors, **Prof. S. Indu and Prof Rajeshwari Pandey** (Department of Electronics and Communication Engineering, Delhi Technological University) for their guidance, encouragement, patient & positive attitude and for their thorough insight into the problems and the ideas which have formed the core of this thesis. I owe them immense gratitude for allowing me to work at my own pace, and for carefully reviewing and giving valuable feedback for all my papers so that they have been accepted promptly. Their superior mentoring skills and clear thinking have played a great role, without which, this thesis could not have been accomplished.

I would also like to express my sincere gratitude to **Prof. N S Raghava**, Head of Department and the faculty of Electronics and Communication Engineering Department, Delhi Technological University, for their relentless guidance and support.

I am also grateful to **Prof. Anuradha Basu** and my colleagues at the Department of Electronics and Communication Engineering, Bharati Vidyapeeth's College of Engineering, New Delhi for their continuous support and encouragement for completing the work

Last but not the least; I am thankful to my husband, Col Stephan K J and my two sons, Sebin Duke Stephan and Sachin Duke Stephan and all my relatives and friends, for their love, encouragement and support.

Saji. M. Antony

May 2020.

## Contents

| C  | tificate                                                                                  | i    |

|----|-------------------------------------------------------------------------------------------|------|

| A  | nowledgements                                                                             | ii   |

| Li | of Figures                                                                                | vi   |

| Li | of Tables                                                                                 | viii |

| A  | tract                                                                                     | ix   |

|    |                                                                                           |      |

| 1. | ntroduction                                                                               | 1    |

|    | .1. Importance of the design of energy efficient wireless sensor nodes                    | 2    |

|    | .2. Problem definition                                                                    | 3    |

|    | .3. Overview of the research work                                                         | 5    |

|    | 1.3.1. Design of high speed low power vedic multipliers for wireless sensor nodes.        | 5    |

|    | 1.3.2. Design of energy efficient ALU using Vedic multipliers                             | 6    |

|    | 1.3.3. Design of improved power amplifiers for making energy efficient transceiver blocks | 6    |

|    | 1.3.4. Design of an efficient solar energy harvesting system for wireless sensor nodes    | 7    |

|    | .4. Thesis layout                                                                         | 7    |

| 2. | Energy efficient wireless sensor nodes: a review                                          | 10   |

|    | 2.1. Low power wireless sensor nodes                                                      | 11   |

|    | 2.2. Multipliers for sensor nodes                                                         | 14   |

|    | 2.3. Design of ALU for sensor nodes                                                       | 18   |

|    | 2.4. Power Amplifiers for energy efficient Transceiver Blocks                             | 20   |

|    | 2.5. Energy harvesting systems for wireless sensor nodes                                  | 22   |

|    | 2.6. The thesis in perspective: Motivation and Contributions                              | 25   |

| 3. | 3. High speed low power Vedic multipliers for wireless se | ensor nodes 30 |

|----|-----------------------------------------------------------|----------------|

|    | 3.1. Introduction                                         | 30             |

|    | 3.2. State of the art                                     | 31             |

|    | 3.3. Problem formulation                                  | 34             |

|    | 3.4. Methodology                                          |                |

|    | 3.4.1. Vedic mathematics                                  | 35             |

|    | 3.4.1.1. Urdhva Triyakbhyam Sutra.                        | 36             |

|    | 3.4.2. Multiplexer based adders                           | 39             |

|    | 3.5. Simulation Results                                   |                |

|    | 3.5.1. Simulation of proposed 8-bit Urdhva Multiplie      | er 41          |

|    | 3.5.2. Simulation of 8-bit conventional Urdhva Multi      | plier 42       |

|    | 3.5.3. Simulation of 16-bit Multipliers                   | 43             |

|    | 3.5.4. Synthesis                                          |                |

|    | 3.5.5. Results                                            | 45             |

|    | 3.6. Conclusion                                           | 49             |

| 4. | 4. Energy efficient ALU using Vedic multipliers           |                |

|    | 4.1. Introduction                                         | 51             |

|    | 4.2. State of the Art                                     | 52             |

|    | 4.3. Problem formulation                                  | 56             |

|    | 4.4. Methodology                                          |                |

|    | 4.4.1. Artificial Neural Networks (ANN)                   | 57             |

|    | 4.4.2. Components of ANN                                  | 59             |

|    | 4.4.3. Advantages of ANN                                  | 61             |

|    | 4.4.4. Design of Vedic neuron                             | 61             |

|    | 4.4.5. Design of ALU using Vedic neurons                  | 62             |

|    | 4.5. Simulation results                                   | 65             |

|    | 4.5.1. Simulation of Vedic neuron                         | 65             |

|    | 4.5.2. Simulation of proposed ALU                         | 67             |

|    | 4.5.3. Results                                            | 73             |

|    | 4.6. Conclusion                                           | 75             |

| 5. |      | ign of improved power-amplifiers for making energy efficient       | 76  |

|----|------|--------------------------------------------------------------------|-----|

|    | 5.1. | Introduction                                                       | 76  |

|    | 5.2. | State of the Art                                                   | 77  |

|    | 5.3. | Problem formulation                                                | 80  |

|    | 5.4. | Methodology                                                        | 80  |

|    |      | 5.4.1. Power Amplifier                                             | 81  |

|    |      | 5.4.1.1. Amplification Methods                                     | 81  |

|    |      | 5.4.2. Class E Power Amplifier                                     | 82  |

|    |      | 5.4.2.1. The Cascode Amplifier                                     | 84  |

|    |      | 5.4.2.2. Common drain common source (CD-CS) configuration          | 85  |

|    | 5.5. | Simulation results                                                 | 85  |

|    | 5.6. | Conclusion                                                         | 92  |

| 6. |      | efficient solar energy harvesting system for wireless sensor<br>es | 93  |

|    | 6.1. | Introduction                                                       | 93  |

|    | 6.2. | State of the Art                                                   | 94  |

|    | 6.3. | Problem formulation                                                | 96  |

|    | 6.4. | Methodology                                                        | 96  |

|    |      | 6.4.1. Solar Energy Harvesting (SEH) system                        | 98  |

|    |      | 6.4.2. Modified Solar Energy harvesting System for WSN Nodes       | 100 |

|    | 6.5. | Results                                                            | 103 |

|    | 6.6. | Conclusion                                                         | 105 |

| 7. | Cor  | nclusion                                                           | 108 |

|    | 7.1. | Summary of Work Done                                               | 109 |

|    | 7.2. | Future Work                                                        | 111 |

| A  | nnex | ure                                                                | 113 |

|    | Ref  | erences                                                            | 113 |

|    | Pub  | lished works                                                       | 138 |

### **List of Figures**

| 2.1  | Block diagram of a Sensor Node                                         | 12 |

|------|------------------------------------------------------------------------|----|

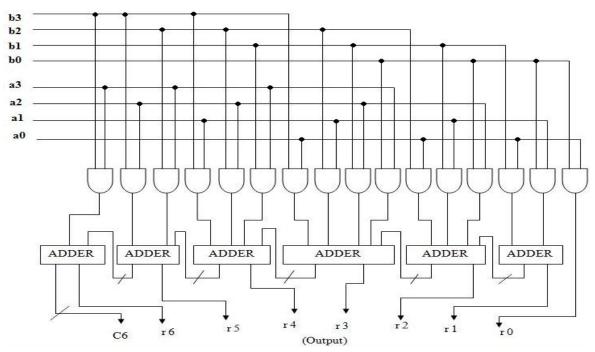

| 3.1  | Urdhva multiplication method for 2 bit binary numbers                  | 37 |

| 3.2  | Block diagram of 2x2 bit Urdhva multiplier                             | 37 |

| 3.3  | Line diagram for 4 bit Urdhva multiplication                           | 38 |

| 3.4  | Hardware architecture for 4-bit Urdhva multiplier                      | 38 |

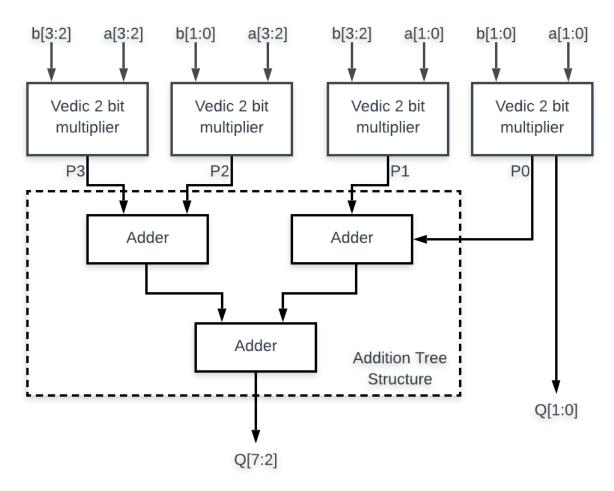

| 3.5  | Block diagram for 4x4 Vedic multiplier using 2x2 multipliers           | 39 |

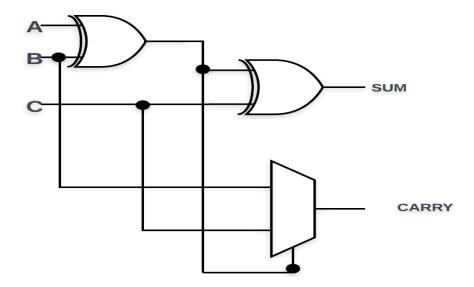

| 3.6  | Full adder with XOR gates and MUX                                      | 40 |

| 3.7  | Simulation result of proposed 8-bit Urdhva multiplier                  | 42 |

| 3.8  | Simulation Result of conventional 8-bit Urdhva multiplier              | 42 |

| 3.9  | Simulation result of proposed 16-bit Urdhva multiplier                 | 43 |

| 3.10 | Simulation result of 16-bit conventional Urdhva multiplier             | 43 |

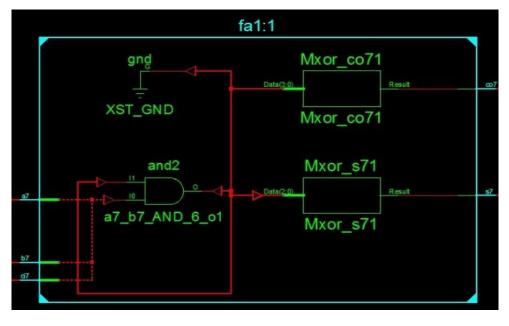

|      | RTL view of full adder of (a) Proposed (b) Conventional Urdhva ipliers | 44 |

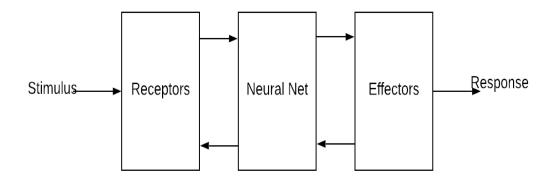

| 4.1  | Block diagram of nervous system                                        | 58 |

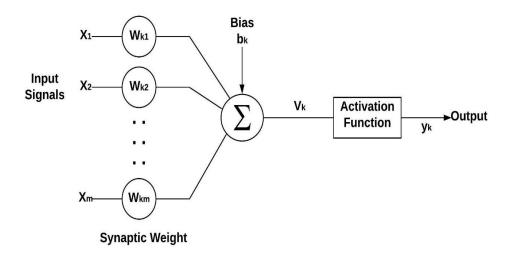

| 4.2  | Basic artificial Neuron model                                          | 59 |

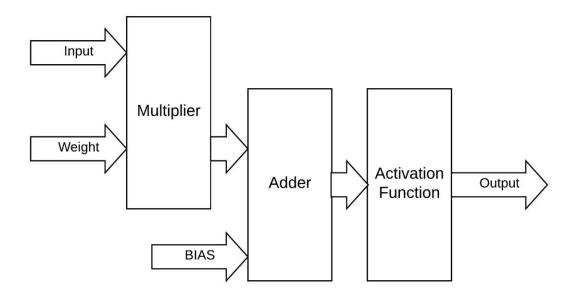

| 4.3  | Hardware implementation of single neuron                               | 60 |

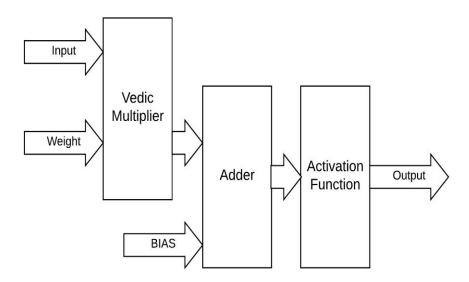

| 4.4  | Hardware implementation of Vedic neuron                                | 62 |

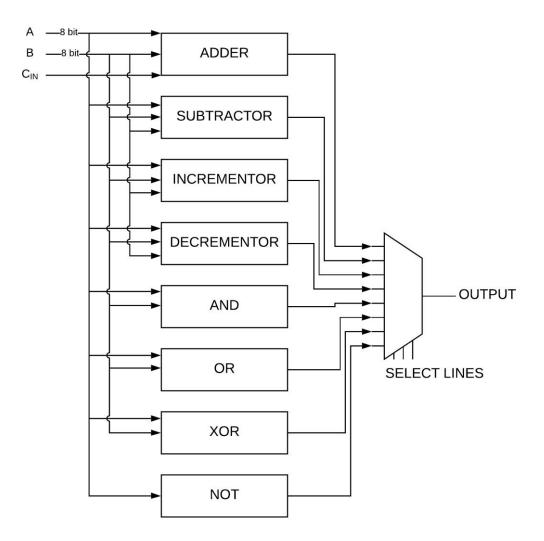

| 4.5  | Block diagram of ALU circuit                                           | 64 |

| 4.6  | Simulation results of 8-bit Vedic multiplier                           | 66 |

| 4.7  | Simulation result of activation function                               | 66 |

| 4.8  | Simulation result of Vedic Neuron                                      | 67 |

| 4.9  | Simulation results of 8-bit Adder                                      | 69 |

| 4.10 | Simulation results of 8-bit Subtractor                                 | 69 |

| 4.11 | Simulation results of 8-bit Incrementor                                | 70 |

| 4.12 | Simulation results of 8-bit decrementor                                | 70 |

| 4.13 | Simulation results of 8-bit AND gate                          | 71  |

|------|---------------------------------------------------------------|-----|

| 4.14 | Simulation results of 8-bit OR gate                           | 71  |

| 4.15 | Simulation results of 8-bit NOT gate                          | 72  |

| 4.16 | Simulation results of 8-bit XOR gate                          | 72  |

| 4.17 | Simulation results of Vedic ALU                               | 73  |

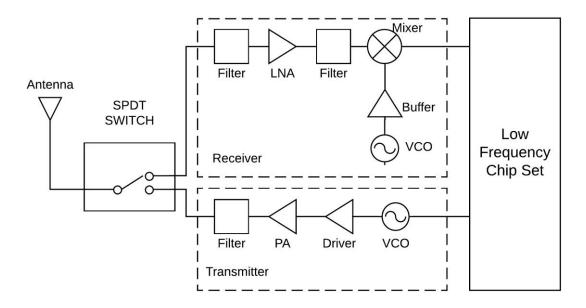

| 5.1  | Block diagram of transceiver in a sensor node                 | 77  |

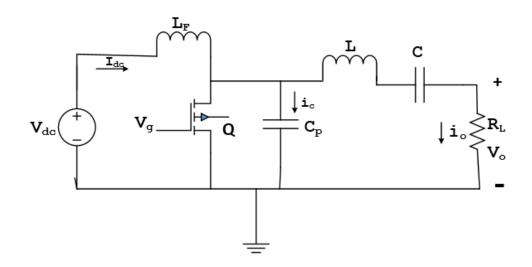

| 5.2  | Circuit of class E power amplifier                            | 83  |

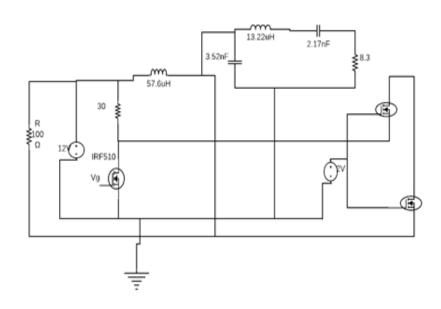

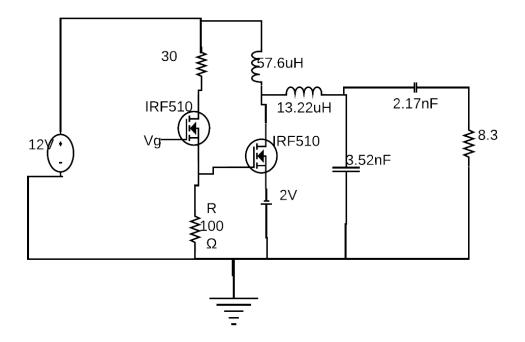

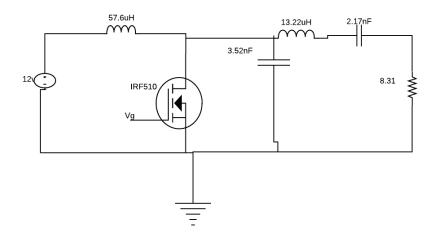

| 5.3  | Class E amplifier with double cascading                       | 86  |

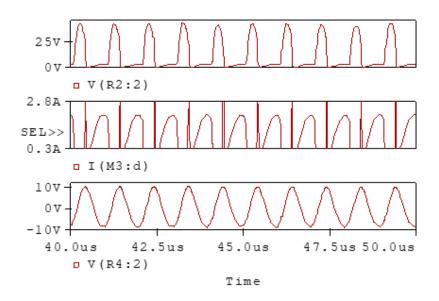

| 5.4  | Simulation results of class E amplifier with double cascoding | 86  |

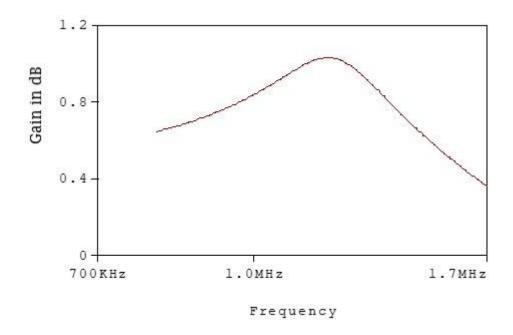

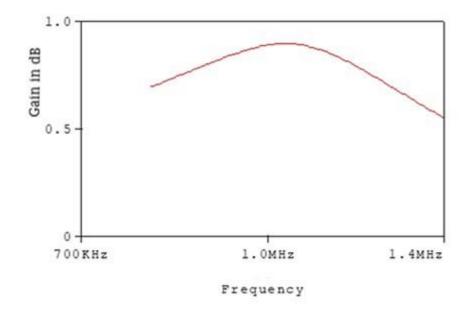

| 5.5  | Frequency response of double cascode amplifier                | 87  |

| 5.6  | Class E amplifier with CD-CS cascading                        | 88  |

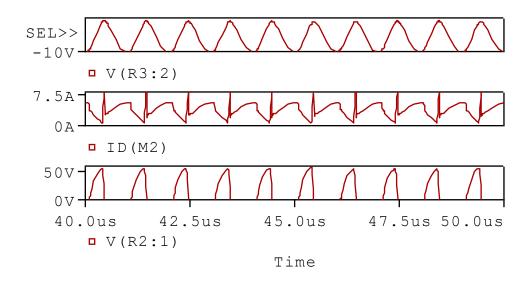

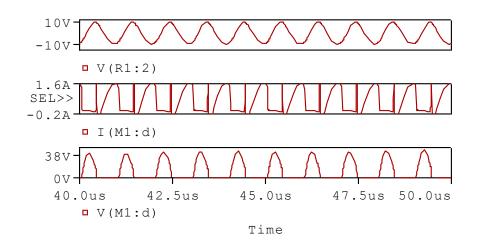

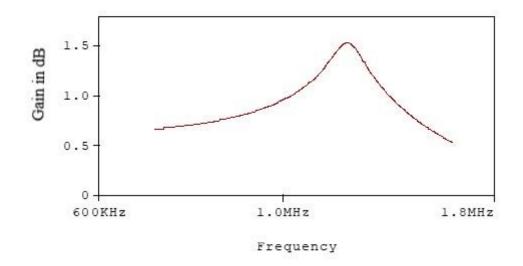

| 5.7  | Simulation results of Class E amplifier with CD-CS cascading. | 88  |

| 5.8  | Frequency response of CD-CS cascading                         | 89  |

| 5.9  | Simple class E amplifier circuit                              | 90  |

| 5.10 | Simulation results of simple class E amplifier circuit        | 90  |

| 5.11 | Frequency response of class E Amplifier                       | 91  |

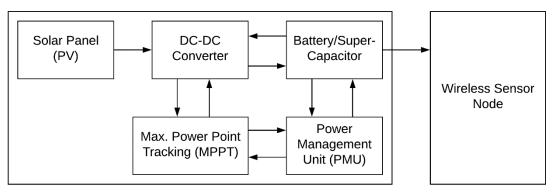

| 6.1  | Components of SEH system                                      | 99  |

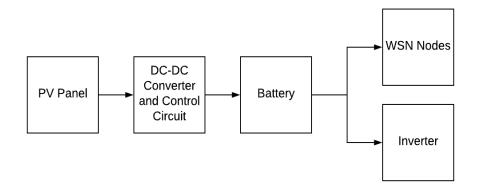

| 6.2  | Block diagram of proposed SEH system                          | 100 |

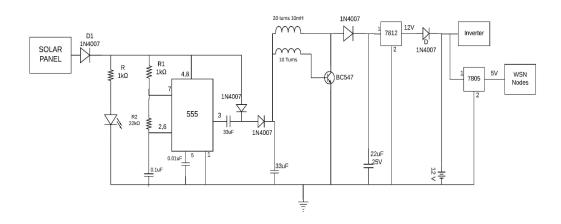

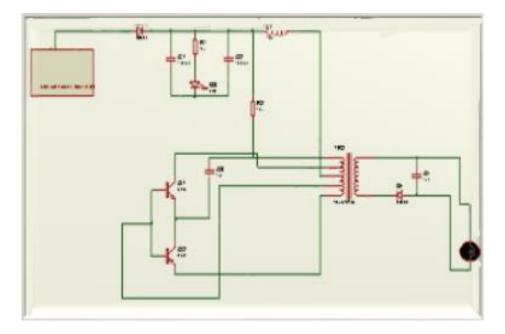

| 6.3  | Circuit diagram of solar harvesting for wireless sensor node  | 102 |

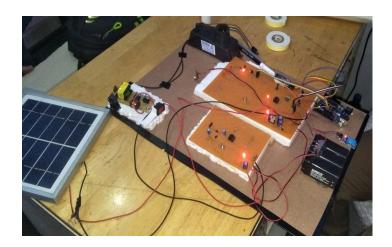

| 6.4  | Photo of design implementation in lab                         | 102 |

| 6.5  | Circuit diagram of inverter                                   | 103 |

### List of Tables

| 3.1 | Logical effort for different inputs of CMOS gates                              | 41      |

|-----|--------------------------------------------------------------------------------|---------|

| 3.2 | Synthesis results of logic utilization for 4-bit multipliers                   | 46      |

| 3.3 | Synthesis results of logic utilization for 8-bit multipliers                   | 46      |

| 3.4 | Synthesis results of logic utilization for 16-bit multipliers                  | 47      |

| 3.5 | Synthesis results on delay                                                     | 47      |

| 3.6 | Summary of synthesis results                                                   | 48      |

| 3.7 | Delay comparisons reported by previous approaches                              | 48      |

| 3.8 | Area comparisons reported by previous approaches                               | 49      |

| 3.3 | Performance analysis                                                           | 49      |

| 4.1 | Delay comparison                                                               | 74      |

|     | Device utilization summary for Vedic logic Vs. Conventional c of eight bit ALU | -<br>74 |

|     | Performance analysis                                                           | 75      |

|     | Performance comparison table                                                   | 91      |

| 6.1 | Experimental results                                                           | 104     |

| 6.2 | Performance comparison with existing system                                    | 104     |

|     |                                                                                |         |

### ABSTRACT

Sensor networks have been recognised as one of the most advanced technologies of the 21st century with vast practical applications. The life of a sensor network is mainly determined by its energy consumption. Commercially available sensor nodes are battery driven devices. As most sensor nodes are deployed widely scattered and in isolated areas, replacing battery is not an option. This dissertation focuses on extending the lifespan of sensor networks by reducing energy consumption in design and operation of sensor nodes.

The study goes in depth to analyse the state of art technology to achieve energy efficiency in sensor nodes and identify scope for further research in this field. In the architecture of sensor nodes, multipliers are the main blocks for designing an energy efficient processor. Vedic Mathematics provides principles of high speed multiplication. The main reason for power dissipation in multiplier circuit is due to power dissipation of full adder circuit. Low power multipliers have been designed by using low power adders. Motivated by this, a high speed Vedic multiplier has been designed using multiplexer based adder. When compared with existing Vedic multipliers, proposed designs showed significant improvement in reduction of delay and energy consumption.

Sensor nodes consume maximum power during data communication. So processing data locally at each node in a sensor network is important for minimizing power consumption. High processing speed and low area designs are in ever growing demand. In order to predict outcomes, based on previous inputs, ALU can be designed with neurons. Processing speed of ALU can be improved by replacing conventional multipliers with Vedic multipliers. This research work suggests implementation of high speed ALU using Vedic neurons. The analysis of the results shows that the proposed design leads to

ix

reduction in the delay and reduction in LUT count (an indicator of area) of the ALU.

Use of energy efficient power amplifiers is an essential requirement for sensor nodes, as power amplifiers are responsible for the main power consumption in the transceivers of sensor nodes. Again, wider band width is another important requirement for power amplifiers used in sensor transceivers especially in wireless visual sensor networks and wireless multimedia sensor networks. Reliability of a power amplifier can be increased by designing it at smaller supply voltage. This thesis suggests improvements in design of power amplifier in class E configuration, for transceivers in wireless sensor nodes. In order to achieve wider band width, cascade of common drain followed by common source in class E configuration has been designed; and for more reliable operation with higher efficiency, class E in double cascoded has been implemented. The proposed designs, when simulated in SPICE, higher efficiencies and band widths have been achieved.

This research also explored to design a robust solar energy harvesting system to enhance life time of sensor nodes. Proposed solar energy supply system mainly consists of a solar panel, rechargeable battery and a control circuit. To obtain sufficient voltage to charge battery, electrical energy generated through panel is boosted by boost converter. Different sensor nodes are supplied with energy from this system. An inverter is also designed for AC applications. Experimental results show that this compact, self-sufficient system enables outdoor based wireless sensor network nodes to operate successfully for longer periods.

### **CHAPTER 1.**

## **INTRODUCTION**

A wireless sensor network (WSN) comprises of spatially distributed devices employing sensors to cooperatively monitor autonomous environmental or physical conditions, like sound, temperature, vibration, light, humidity, motion, pollutants or nature of biological organisms at varying locations [1]-[4]. Wireless sensor networks were originally developed for defence applications like battle field surveillance. Now a days WSNs are used in many non-military applications such as precision agriculture, transportation, environment and habitat monitoring, structural health monitoring, medical monitoring, home automation, traffic control, Sensor networks are basically different from standard etc [5]-[8]. communication networks as the aim of sensor network is to monitor a phenomenon over space and time and not to just send data from one node to another. So, the underlying communication infrastructure is used to achieve a larger objective of geo-temporal sampling and the subsequent detection and classification of events of interest [9], [10].

Sensor networks have been recognised as one of the most advanced technologies of the 21st century. Current developments in micro-electromechanical systems (MEMS), advances in the fabrication and integration of sensing and communication technologies have simplified the design of multifunctional sensor nodes and have enabled the development of smaller size sensor nodes that are low-cost and low power consuming. They can sense various information from the surroundings, and they have capabilities of data processing, communication, storage etc. The sensor nodes are therefore capable of collecting, processing, storing and communicating data to other nodes in the network and even to outside the network.

# 1.1 Importance of the Design of Energy Efficient Wireless Sensor Nodes

A wireless sensor network consists of large number of sensor nodes, densely deployed in region, either inside a phenomenon or very close to it. It gives significant improvement over the traditional sensors. When compared to the deployment of a few very accurate and high expensive sensors, using a large number of inexpensive sensors has many advantages, like achieving more spatial resolution, reduced total system cost, easy to deploy, robustness against failures from distributed operations, less obtrusiveness and uniform coverage [11], [12].

The life of a sensor network is mainly determined by its energy consumption. Commercially available sensor nodes are driven by batteries. As most sensor nodes are deployed widely scattered and in isolated and inaccessible areas, replacing battery is not an option. Hence, low energy consumption requirement is the most crucial constraint of sensor nodes, as life of a sensor network mainly depends on energy consumption of sensor nodes. In many applications large number of networked sensors require

unattended operations. Also, applications such as health monitoring of animals or humans, require the sensor nodes to be unobtrusive in the normal functioning of the individual. Another factor that highlights the importance of low energy consumption requirement is the fact that battery technology itself hasn't advanced as much as the computer technology in the last few decades. So, energy utilized by each part of individual nodes precisely affects the life of the complete network. This leads energy optimization more complicated, as it involves increasing life of sensor network by reducing energy consumption. This can be achieved with energy awareness in each and every step of design and operation [13]-[16].

### **1.2 Problem Definition**

Like any other technology, sensor networks also have some key issues that need to be understood in order to completely appreciate the contributions of this work. This dissertation focuses on extending the lifespan of sensor networks by reducing energy consumption in design and operation of sensor nodes. The study goes in depth to analyse the state of art technology to achieve energy efficiency in sensor nodes and identifies scope for further research in this field.

Due to diverse application domains of sensor networks, a variety of data types are included from temperature, pressure, magnetic field, acceleration etc. The data collected by these sensors is rarely forwarded in raw form. It is subject to some form of signal processing mainly to reduce communication costs. The size of sensors and actuators have made down to the millimetre scale due to advancement in MEMS. Also advances in VLSI technology have made very small button sized computers a reality. However, such devices, are designed with low cost in mind and it results limited computational resources, like CPU speed and memory. Based on these observations, we address the following problems in this thesis.

a) In the architecture of sensor nodes, multipliers are the main structure for designing an energy efficient processor. Many research works have been focused on design of low power multiplier algorithms, but it is not explored for real time applications, using efficient adder circuits with more power savings and speed.

**b**) Similarly, for application-oriented processors, not much has been explored in the design of ALU. A conventional ALU is less capable of intelligently predicting outcomes based on previous inputs. Its neural counterpart, on the other hand, aims at improving its prediction capabilities by employing an activation function and making it an intelligent ALU.

c) In a sensor node, most of the power is consumed in transceivers; and in transceivers the most significant power consumption is contributed by power amplifiers. Requirement of high efficiency power amplifiers without reducing bandwidth and sensitivity demands new design strategies. Adequate work has not been found in the design of power amplifiers for higher efficiency of the transceiver blocks.

d) Various harvesting techniques are available such as solar energy, wind energy, piezo electric energy, etc. Among these, currently most matured technology is based on solar cells and it gives high power density. But efficient solar energy harvesting technology for small systems have not been explored much.

### **1.3** Overview of the Research Work

This dissertation focuses on extending the lifespan of sensor networks by reducing energy consumption in design and operation of sensor nodes. The study goes in depth to analyse the state of art technology to achieve energy efficiency in sensor nodes and identified scope for further research in this field.

# **1.3.1** Design of high speed low power Vedic multipliers for wireless sensor nodes.

In the architecture of sensor nodes, design of multipliers plays a major role in making an energy efficient processor. The speed of multiplier is limited by the speed of adders used in partial product addition [17]. Fast multiplication can be achieved by using the principles of Vedic mathematics [18]-[21]. From the performance analysis on delay, power dissipation, transistor count etc, it is observed that full adder with XOR and multiplexer (MUX) gives best performance [22]. Motivated by this, a high speed Vedic multiplier based on Urdhva Triyakbhyam Sutra is proposed in this research. Summation of partial products is done with high speed MUX based full adders. The proposed design gives much less delay and power dissipation as compared to other conventional Vedic multipliers.

#### 1.3.2. Design of energy efficient ALU using Vedic multipliers.

This thesis also focuses on designing a high speed ALU using Vedic neurons. A conventional ALU is incapable of intelligently predicting outcomes based on previous inputs [23]-[25]. Its neural counterpart, on the other hand, aims at improving its prediction capabilities by employing an activation function and making it an intelligent ALU. But ALU designed with neurons suffers from bulky and slow architecture. This can be solved by implementing the Vedic logic in all arithmetic and logical operations performed. The Vedic logic helps in performing faster calculations by utilizing simple techniques to solve complex problems. This provides a faster and a smarter ALU design. This work is intended for laying a foundation for the intelligent sensor nodes by implementing Vedic logic on neural platforms.

# **1.3.3 Design of improved power amplifiers for making energy efficient transceiver blocks.**

The essential quality required for a power amplifier in wireless sensor nodes is its efficiency. Power amplifier with low power supply gives more reliable operation. But overall gain and efficiency are decreased due to reduced power supply [26], [27]. In class E power amplifiers, these combinations do not exist. So our study focuses on modifications for basic class E amplifier to achieve efficiency without reducing bandwidth and sensitivity at lower power supply. Two different configurations using basic class E amplifier are proposed in this work. The first configuration is class E amplifier with double cascoding and second design is class E amplifier designed using common drain followed by common source (CDCS) cascading. The proposed designs give better efficiency, and more reliable operation with higher bandwidth.

# **1.3.4** Design of an efficient solar energy harvesting system for wireless sensor nodes.

Nowadays various harvesting techniques from the renewable energy sources are available to design self-powered wireless sensor nodes. Solar energy, wind energy and piezo electric energy are some of the available ambient energy sources [28]. Among these, currently most matured technology is based on solar cells and it gives high power density [29]. Requirement of small sized sensor nodes demands small solar panels in the harvesting system which leads to design a compact and simple solar energy harvesting system (SEH) for sensor nodes. This research also designed a solar harvester for WSN nodes with compact models of solar panel and harvesting circuits to increase the life span of battery. Proposed design combines energy harvesting system with a compact energy storage device. It gives stable operation with high reliability, efficiency and less power loss.

### 1.4 Thesis Layout

#### 1. Introduction

This chapter broadly covers the motivation and purpose of the outlined research topic. It contains the main idea for the development of the thesis along with different issues associated with energy efficiency of wireless sensor nodes.

#### 2. Energy efficient wireless sensor nodes: A review

This chapter discusses the state of art techniques developed in existing research work in the field of "Design of Energy efficient Wireless

Sensor Nodes". It also highlights the inadequacies and deficiencies in the existing work that has stimulated the development of research objectives of the dissertation.

# 3. High speed low power Vedic multipliers for wireless sensor nodes

This chapter presents use of multiplexer based adder in designing a high-speed Vedic multiplier. It gives a brief introduction to Vedic mathematics and also cover multiplication techniques used in Vedic mathematics. This chapter concludes with results and comparative analysis with the related work.

#### 4. Energy efficient ALU using Vedic multipliers.

This chapter introduces a high speed ALU, using Vedic neurons. It covers the problems encountered with implementation of ALU using neurons. Design of ALU using Vedic neurons is explained in this chapter, followed by results and comparisons with the existing methods in the literature.

# 5. Design of improved power amplifiers for making energy efficient transceiver blocks.

In this chapter, we propose improvements in the design of class E power amplifier for transceivers in wireless sensor nodes. Two different configurations using basic class E amplifier are discussed in this section. The first configuration is class E amplifier with double cascoding and second design is class E amplifier designed using common drain followed by common source (CDCS) cascading. Finally, analysis of results is done with various state of art techniques.

# 6. An efficient solar energy harvesting system for wireless sensor nodes

This chapter presents a solar energy harvester for wireless sensor nodes with compact models of solar panel and harvesting circuit. It introduces a suitable method for effective utilization of solar energy for small wireless sensor nodes and concludes with the analysis of obtained results.

### 7. Conclusion

This chapter contains the brief summary of the work done. We also outline the future scope of this work.

### **CHAPTER 2**

# ENERGY EFFICIENT WIRELESS SENSOR NODES: A REVIEW

Sensor networks are self-sustaining systems of nodes that coordinate amongst themselves autonomously but, their enhancement is restricted by the limitations of the devices used. First, they are restricted by power consumption, which leads to eventual device failure and in turn makes energy efficient communications an essential requirement. Their computing power is also limited, which prevents running of sophisticated network protocols. They also have limited bandwidth which constraints the amount of communication to be transmitted. Human intervention to keep the network up and running, in such conditions, is at the least a tedious job and mostly infeasible. It is for this reason that there is a continued effort to make sensor networks as autonomous as possible. Many research efforts are being focused towards overcoming the common issues that are peculiar to sensor networks.

Objective of the present study is to increase the life of sensor nodes by reducing the energy consumption of sensor nodes with suitable energy conserving designs. In this literature survey, the discussion is divided under the categories of multiplier and ALU design for sensor nodes, power amplifier configurations for transceivers of sensor nodes, and energy harvesting systems for sensor nodes. Recently many research efforts have been directed towards overcoming the energy constrained nature of WSN nodes. Such efforts are mainly focused in improving energy efficient, intelligent software rather than in improving hardware. Due to the demand of low power sensor nodes in wide range of applications, recent research has been focused on every block of sensor nodes.

### 2.1 Low Power Wireless Sensor Nodes.

Wireless sensor networks consist of large number of sensor nodes deployed in target region or very close to it randomly. These nodes collect information from the surrounding and send through wireless transmission. Like any embedded system, sensor nodes also face the challenge of reducing energy consumption, as much as possible to maximize its operational life span without changing batteries. Therefore, one of the key objectives while designing sensor nodes is to minimize the power consumption. To reduce the power consumption of a sensor node, researchers preferred to employ both unique structural solutions and progressive power saving techniques. I F Akyildiz et al. focus on the importance of power management and power consumption in sensor networks [30]. A detailed analysis on wireless sensor networks has been discussed in this paper. The potential tasks and applications of WSN are explained and a survey has been conducted on the factors effecting the design of sensor network and on the communication architecture for sensor Protocols and algorithms suitable for various layers are networks. discussed in this paper. Reference [3] provides a detailed investigation of embedded sensor networks. Authors explore challenges in three major Energy consumption, signal processing algorithms and selfareas. configuration. Figure 2.1 shows block diagram of a sensor node [31].

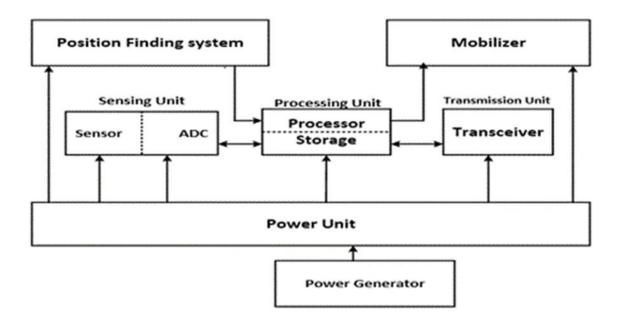

Figure 2.1. Block diagram of a Sensor Node [7].

As shown in Figure 2.1, sensor node consists of sensor unit, processor unit, power unit and transmission unit. Sensor unit consists of a sensor along with an analog-to-digital converter (ADC). Sensor unit converts physical inputs into electrical signals. These analog signals produced by sensors are converted to digital signals by ADC. Processor unit comprises of microcontrollers or microprocessors, which control sensors, execute communication protocol and signal processing algorithms on collected data. Transmission unit collects information from processor unit for transmitting to the outside world. Power unit monitors the battery power to sensor node. The main characteristics sensor nodes required to implement sensor networks are low cost, small size and low power [5]. Recent advances in micro-electro-mechanical systems (MEMS) have made it possible to bring the size of sensors and actuators down to the milli meter scale. Similarly, progresses in VLSI technology have made button sized

computers a reality. Such devices, however, are designed with low cost in mind and as a result the computational resources, such as CPU speed and memory are limited [32].

Characteristics of sensor networks are as under:

- a) Self-organizing abilities,

- b) Multi-hop routing and broadcast & short range communication,

- c) Close deployment and collaborative efforts of sensor nodes,

- d) Capability to change topology due to node failure and fading

- e) Constraints on computing power, memory and transmission power.

These characteristics distinguish sensor networks from traditional ad hoc wireless networks [11]. Even though implementation of sensor networks and their applications uses ad hoc wireless networking techniques, most algorithms and protocols of wireless networks are not suited for sensor networks because of their unique features. Sensor nodes are based on broadcast communication standards, but many ad hoc networks use point to point communications. Due to the need for large quantity of sensors and high overhead (operating cost), sensors may not Instead global identification. of traditional single have hop communication, multi-hop communication gives less power consumption as neighbour nodes may be very close to each other due to dense deployment of large number of sensor nodes. Signal propagation effects in long distance wireless communication can be reduced in multi hop communication [30].

One of the most important constraints on sensor node is low power consumption requirements. Sensor nodes carry limited, irreplaceable power source. Therefore, traditional networks design to achieve high

quality while sensor network design focuses on power conservation. Many researchers are presently focused on developing designs to achieve these requirements [33]-[37].

### 2.2 Multipliers for Sensor Nodes.

The performance of a processor is mainly determined by its speed. In arithmetic operations, multiplication is an important fundamental function. Compared to other arithmetic operations like addition and subtraction, multiplication has large delay and complex algorithm. In many applications like digital signal processing (DSP) applications such as filtering, convolution, Fast Fourier Transform (FFT) etc. and arithmetic functions such as inner products, multiply and accumulate (MAC) unit, frequently use operations based on multiplication [38], [39].

In digital image processing systems multiplier is an important unit. In many signal processing applications such as weather forecasting, analysis of satellite data involve large amount of data and multiplier should be capable of handling this huge data quickly and efficiently so that entire operation is completed in minimum time. In addition to ALU, multipliers are used in other parts of processor design such as various data path units. For processing acquired signal in real time applications, high speed processing is an essential requirement [40], [41]. So demand for high speed multiplier circuit with reduced power consumption has been continuously increasing. Multiplication operations are complex and require more power consumption. Due to the demand of high speed processing and wide range of applications, many research efforts have been made on various multiplication algorithm to decrease the delay and power consumption [42]-[45].

A unique system of mathematics prevalent in ancient India is known as Vedic mathematics. Mathematics is known as mother of all other It is full of numbers and its mysteries. The ancient Indians sciences. understood these numbers and developed easy techniques to solve these mysteries. In ancient times, Indians employed these techniques in varying fields such as astrology, construction of temples, medical science etc., which may be the reason for India's rise as one of the richest countries in the world. This ancient Indian system of calculations were known as "Vedic Mathematics". The word 'Vedic' is derived from the word 'Veda' which means the store-house of all knowledge. Vedic mathematics is primarily consists of sixteen Sutras or techniques dealing with different branches of mathematics like algebra, arithmetics, geometry etc. Vedic Mathematics unveils the outstanding applications to algebraic equations, factorisations, complex multiplications, arithmetical calculations, quadratic and higher order equations, theory of numbers, partial fractions, squaring, cubing, square rooting, cube rooting, coordinate geometry and calculus etc [46].

In this ancient method, basic arithmetic problems were solved by simple, logical and powerful methods. Added advantage is its Consistency. Vedic Mathematics has emerged as a major topic for research due to these advantages. Among sixteen Sutras of Vedic approach, Urdhva Triyakbhyam and Nikhilam are used for multiplication. Vedic multipliers are the best compared to conventional ones and Urdhva Triyakbhyam Sutra architecture is more efficient compared to Nikhilam Sutra [47], [48]. It is well known from literature [49] that Nikhilam Sutra based multipliers expected to work for larger inputs, that is, inputs near to base (20% from the nearest base). Regularity and simplicity of Vedic Mathematics leads to easy implementation in FPGA [50]. Another advantage of this approach is that all partial products required for multiplication are calculated much before actual multiplication begins. Based on the Vedic Mathematics algorithm, these partial products are added to obtain final product which leads to a very high speed approach [51], [52]. In addition, high speed multiplier designs based on Vedic mathematics consume low power too [53].

In reference [54], a high speed Vedic multiplier based on Urdhva Triyakhbyam Sutra is proposed. In this paper, multipliers with four, eight, sixteen and thirty two bits are implemented using Vedic technique and its performance has been compared with conventional method based multiplier which evidently shows that Vedic multipliers are much faster. For Vedic multipliers with large number of bits, design complexity reduces due to their hierarchical nature. Reference [55] presents a similar method for hierarchical multiplier design for Urdhva multiplier wherein 4x4 and 8x8 multipliers are designed using 2x2 multipliers. Comparison of Urdhva and Nikhilam multipliers is drawn in [56] for various bit multiplications starting from 8x8 bits to 64x64 bits.

For small inputs Urdhva multiplier performs better than Nikhilam multiplier and when size of multiplicand increases, Nikhilam multiplier performs much faster than Urdhva multiplier. So integrated Vedic multiplier architecture is proposed in [49], which is capable of selecting appropriate multiplier based on the given inputs. The work presented in [47] focuses on implementation and comparison of array, Urdhva and Nikhilam multiplier for 8bits, 16bits and 32 bits. It is observed that the Urdhva multiplier is best among the three. A high performance multiplier with low energy utilisation and small critical path is proposed in reference [57] especially for DSP applications. This paper designs a highperformance low power consuming partial product accumulation tree for a multiplier using approximate adder. Approximate adder ignores the carry propagation by generating an approximate sum and an error signal. To overcome main limitations like power utilization, performance delay, and to achieve greater performance for real time applications various multiplier architectures have been explored and analysed in references [58] - [62].

The speed of multiplier is limited by the speed of adders used in partial product addition. Performance comparison of various adders is done in [63]. It is observed that carry save adder is having minimum delay, but among seven adder topologies carry increment adder has best balance between area and delay. Logic optimization of adders through technology independent mapping was proposed by R. Uma and P. Dhavachelvan in reference [22]. Concept of logical effort has been used to bring out the differences in performance of the various full adder configurations. The work presents 20 different logical constructions to implement one bit full adder circuit. From the performance analysis on delay, power dissipation, transistor count etc., it is observed that full adder with XOR and MUX gives best performance. Full adder with XNOR, NOT and MUX is the second optimized adder. The basic unit of the multiplier is an adder, so delay of multiplier can be reduced by reducing the delay of adder. So adders have a critical role, in the design of an efficient multiplier. То overcome crucial constraints like power utilization, speed, and to achieve greater performance, configurations of several adders have been discussed and reviewed in [64]-[69].

### 2.3 Design of ALU for Sensor Nodes.

Due to the wide range of applications, a lot of research has been focused on power dissipation, physical size and processor design of sensor nodes. The main difference of sensor networks from standard wireless communication networks is, sensor networks are used to detect some events, and not for just sending data from one node to another. Currently, sensor networks are mostly used to sense phenomena and act as information sources. On the occurrence of certain events they have to perform related actions; such as mobilizing robots in case a target is detected or activating water sprinklers in case of a fire. In such real time applications, quick responses should be automatically generated without any human intervention. To achieve fast acting and fault tolerant responses, it is desirable to design network as distributed as possible [70], [71].

The exact position of sensor nodes may not be predetermined or engineered. This permits random deployment in isolated regions or for disaster relief operations. These regions may include: in the atmosphere, inside buildings, in vehicles, under water and on bodies. So algorithms and protocols used in the sensor networks should have self-organizing abilities. Self-organization means that the network should acquire and retain the essential organizational structures for survival without depending upon human intervention [72]. So, sensor network should be able to execute functional operations through individual nodes. Another distinct characteristic of sensor networks is the coordinated attempt of sensor nodes in collecting the data. Instead of sending the raw data, sensor nodes use their computing abilities to locally carry out simple computations and transmit only partially processed, required data [73], [74]. Necessity of prediction based monitoring in large sensor networks to increase energy efficiency and life time, is explained in [75].

In WSN, primary functions of sensor nodes are to detect events, process and transmit data. Therefore, major domains of power consumption are during Sensing, Communicating and data processing. Among these three domains, maximum energy consumption takes place during data communication. Energy consumption for processing data is very little compared to communicating data. So instead of transmitting raw data, sensor nodes carry out simple computations locally, then transmit partially processed required data. Hence, local data processing is very important for low power consumption in a WSN [76]. For many real time applications like monitoring battle field, controlling of environmental conditions, sensor nodes require fast processors for processing the detected signals. High speed processing and low area design are essential requirements for sensor nodes in an efficient WSN [77].

In reference [76], authors emphasized the necessity of local data processing at each sensor node. Data processing consumes much less energy compared to communication. So sensor nodes carry out data computation and transmit partially processed required data in place of entire raw data. A Munir et al. explain compromise between communication and data processing for many applications and permits transmission of event driven data to conserve energy [78]. So design of high speed low area processors, are essential for various applications in wireless sensor networks [79], [80].

Structure of biological neuron and its basic behaviour are explained in [81]. This behaviour is emulated in an artificial neuron in references

[82], [83]. Implementation of network model for neurons and synapses are demonstrated in these papers. In reference [84], complicated models of biological systems are accurately simulated. Neuron model VHDL library has been established which empowers a wide variety of complex neuron systems. Availability of standard library allows to implement complex neuron system on field programmable gate array (FPGA).

A conventional ALU is incapable of intelligently predicting outcomes based on previous inputs. Using artificial neural network (ANN), as basic building block, digital logic circuits are realized, and verified in [85]. Using ANN, a 5-bit ALU has been designed in this paper. Major disadvantages of designed ALU are slow and complex architecture. By using Vedic algorithm, computation speed of single neuron is increased in [86]. Using Vedic Mathematics, Anshika et al. implemented high performance neuronal logic gates in [87]. High speed neural network has wide range of applications like medical applications, image compression and many more.

# 2.4 Design of Power Amplifiers for Energy fficient Transceiver Blocks.

Due to plenty of sensor nodes installed in isolated area and long lifespan requirement, replacing battery is not an option. So, energy optimization in sensor network is more complicated as it involves reducing the energy utilization and increasing the lifespan of sensor network. In sensor nodes, power is consumed mainly in transceivers and in transceivers, the most significant power consumption is contributed by power amplifiers [88], [89]. In reference [90], N O Sokal has introduced class-E amplifier with parallel capacitor which was a famous technological breakthrough obtaining ideal power efficiency value as 100%.

To achieve low power and long life time, circuit-level design procedures are focused in [91]-[93]. Importance of low power transceiver design is explained in [94]. This paper focuses on the design parameters which significantly influence energy consumption of transceiver unit. D G Rahn et al. have designed a transceiver for multiple input / multiple output wireless LAN applications in [95]. In RF transceivers, the major power consumption unit is power amplifier. Class AB operation is suitable for improved linearity and higher power added efficiency. Adaptive biasing schemes can be implemented for low power applications. Low power amplifier with adaptive biasing is designed in reference [96]. In reference [97], Daniela D Vento and Jan Rabaey designed a high resolution transceiver using class E power amplifier for smart and implantable microprobes that were capable of transmitting neural data to outside world through RFID.

High linearity, greater average output power, wider operating bandwidths and reduced energy consumption are the key design aspects for power amplifiers. In power amplifiers working in switch-mode configuration, the transistor operates in saturation, and either voltage or current, is switched on and off, depending on class of amplifier. A switch can be used in place of transistor. Only voltage is present across an open switch and current flows through the closed switch. So class E power amplifier has zero overlap of time between voltage and current. It gives 100% theoretical efficiency. Class-E power amplifier is a compromise between switched configuration and linear class AB configuration [98], [99]. M P Gopalrao et al. have done a comparative study of switch-mode

power amplifiers with different classes of operation and technologies for radio frequencies in [100]. Use of CMOS technology gives compactness and better results. Different techniques such as feedback, feed forward, and distortion to improve linearity of amplifier are discussed in [101]. Analysis of basic class E amplifier and design procedures are given in [102]-[106]. Reference [107] suggests improvements in design of basic class E power amplifier using self-biasing to improve efficiency. To minimise power loss and reduction in delay the active device is turned off by charging acceleration technique in reference [108].

To obtain higher output power and efficiency, mixed mode switching power amplifiers are discussed in reference [109]. The main mixed mode switching power amplifiers consist of class EF and class EM. Authors focused on the analytical study of duty ratio effects and nonlinearity effects of the gate to drain and drain to source parasitic capacitances on the performance of class EM power amplifiers. Authors also focused on the design procedures of class EM power amplifiers at any duty ratio. A single ended parallel circuit class E/F power amplifier is proposed by Chang Liu and Qian-Fu Cheng in [110]. Compared with other class E power amplifiers, proposed structure has same theoretical efficiency with improved performance in peak drain voltage, maximum operating frequency and power output capacity without much complexity in circuit. Reference [111] presents a two-stage class E linear power amplifier with greater power added efficiency.

### 2.5 Energy Harvesting Systems for Wireless Sensor Nodes.

Limited and irreplaceable battery energy is the most important constraint for wireless sensor nodes in sensor networks. Adapting more advanced technologies, sensor nodes can be powered even without batteries by employing energy harvesting systems. The most suitable approach is to combine energy harvesting system with a compact energy storage device. In parallel with existing energy management approaches, which generally focused on power saving architecture and power saving network design at each communication layer, active research has also been taken place in the field of renewable energy harvesting techniques [112], [113]. Many research efforts are focused on energy harvesting from the renewable energy sources in order to design self-powered WSNs. Nowadays various harvesting techniques are available. Solar energy, wind energy, piezo electric energy are some of the ambient energy sources available for harvesting [114], [115]. Among these, currently most matured technology is based on solar cells and it gives high power density [116]-[119]. M Rahim et al. have carried out studies to extend life span of wireless sensor network by allowing a small percentage of network nodes to move in search of energy. These autonomously mobile nodes recharge and supply energy to immobile energy drained nodes [120].

Zheng et al. proposed a new piezo electric energy harvesting technology for WSN nodes in [121]. In order to achieve the impedance matching between energy supply system and vibration source, proposed circuit applies an optimum control voltage to piezo electric element and efficiency has been improved four times. In reference [122], energy is harvested from load power cables using a single split core toroidal coil transformer (SCCT) current to supply power WSN to node. Simultaneously, same SCCT estimates the main current in the power line. Thus, in this research work, a system which is capable of supplying power

to a WSN node and at the same time estimating current consumption has been discussed.

A solar harvester with self-powered WSN nodes with maximum power point tracking (MPPT) is proposed in [123]. Their design enhanced the efficiency of solar harvester working under varying light irradiance Instead of using microcontrollers and DSP processors for conditions. control action in MPPT algorithm, a comparator is used in the design. A high speed comparator is used in maximum light irradiance conditions and an ultra-low power comparator is suggested in poor light irradiance. The potential of solar cell to supply energy for one node is studied in detail in In this paper, characteristics of solar cell and design of control [124]. circuit to control the voltage for battery are described in detail. A detailed survey has been conducted on solar energy harvesting for WSN nodes by H Authors conducted survey at four basic levels; solar Sharma et al. [125]. level, sensing level, computation level energy harvesting and communication level. An in depth survey of solar cell efficiency, DC-DC converter, MPPT and energy prediction algorithms have been discussed. Design challenges and their practical solutions are explained in detail.

An efficient solar energy harvesting system has been proposed in [126] with pulse width modulation (PWM) and MPPT for WSN nodes. Modelling, simulation, optimization and hardware implementation are performed in this research work. PWM and MPPT control techniques for solar harvesting system have been analysed and compared. Efficiency of MPPT controlled systems were found to be better than PWM controlled systems. Design and development of efficient wind energy harvesting system is discussed in references [127]-[129]. An optimised wind energy harvesting system for WSN nodes using specially designed ultra-low power

management circuit is discussed in [130]. Instead of using conventional MPPT algorithm boost converter with MPPT techniques based on the impedance matching is implemented in this research paper. Another effective approach to harvest wind energy to keep self-powered low power WSN nodes running independently for years is proposed in [131]. This paper focuses on an optimized wind energy harvesting system with specially designed DC-DC Converter - aware Optimal Power Management (DCOPM) technique. Micro-scale wind energy harvesting system and power management units are discussed in detail in this paper.

#### 2.6 The Thesis in Perspective: Motivation and Contributions.

In previous sections, we discussed different approaches to increase the life span of wireless sensor nodes. Few challenges are addressed in recent works. However, there are still many challenges unattended. A brief of issues to be addressed are given in succeeding paragraphs.

After conducting a detailed literature review, it is found that most of the research works have been directed towards software techniques for power savings in WSN applications. But very few efforts have been done for improving the hardware to reduce the power consumption. Many research works have focused on design of low power multiplier algorithms, but it is not explored for real time applications, using efficient adder circuits in order to achieve more power savings and speed.

Similarly, for application-oriented processors, not much has been explored in the design of ALU. Works have been concentrated in the modification of general transceiver architecture to save power. Adequate work has not been found in the design of power amplifiers for energy

efficient transceivers. Even though, lots of literature are available for solar energy harvesting, efficient energy harvesting technology for small systems have not been explored much.

Motivated by these observations we present in this thesis novel methods to reduce the energy consumption of sensor nodes and to increase the life time of sensor network. Our contributions are under:

(a) We have developed a high speed, low power Vedic multiplier for sensor nodes. To make multiplier suitable for all types of inputs, Urdhva Triyakbhyam Sutra is selected for multiplier architecture. Summation of partial products is done with high speed multiplexer based full adders. When compared with other conventional Vedic multipliers, proposed design gives much less delay and area utilisation.

The proposed design of Urdhva Vedic multiplier is coded in Verilog HDL and functionally verified through simulation using Modelsim SE 6.4. First a basic 2x2 Urdhva Vedic multiplier is designed, using half adders. This basic 2x2 multiplier is further used to implement 4x4 bits to 16x16 bits multipliers and are then simulated. The performance of proposed design is also compared with conventional Urdhva Multiplier.

(b) An energy efficient ALU using Vedic multipliers has been designed for energy efficient sensor nodes. A conventional ALU is incapable of intelligently predicting outcomes based on previous inputs. Its neural counterpart, on the other hand, aims at improving its prediction capabilities by employing an activation function and making it an intelligent ALU. But ALU designed with neurons suffers from bulky and slow architecture. This can be solved by implementing the Vedic logic in all arithmetic and logical operations performed. The Vedic logic helps in

performing faster calculations by utilizing simple techniques to solve complex problems. This provides a faster and a smarter ALU design. This work is intended for laying a foundation for the intelligent sensor nodes by implementing Vedic logic on neural platforms.

Proposed design of ALU has been coded in Active HDL and verified through simulation using ModelSim SE 6.4. The Active HDL codes of the ALU were synthesized using Xilinx ISE 14.7.

(c) Improved power amplifier configurations for making energy efficient transceiver blocks of sensor nodes have designed in this thesis work. The efficiency and bandwidth are the most important characteristics of power amplifier in sensor nodes. Low power sensor nodes must communicate with their neighbours at hundreds of kilobytes per second and have to operate at higher volumetric densities especially in wireless visual sensor networks and wireless multimedia sensor networks [132]-[135]. High data rate requires wider band width. But wider bandwidth limits the sensitivity and range. Requirement of wider bandwidth and higher efficiency without reducing sensitivity demands new design strategies.

Power amplifier with low power supply gives more reliable operation. But overall gain and efficiency are decreased due to reduced power supply. In class E power amplifiers, these combinations do not exist. So our study focuses on modifications for basic class E amplifier to achieve improved band width and efficiency at lower power supply.

Two different configurations using basic class E amplifier are proposed in this work. The first configuration is class E amplifier with double cascoding and second design is class E amplifier designed using common drain followed by common source (CDCS) cascading.

The transceivers should operate at high data rate for better efficiency which allows many nodes to share same channel through time division multiplexing. Thus, wider band width is another important requirement for power amplifiers used in sensor transceivers. In order to achieve wider band width, cascade of common drain followed by common source in class E configuration has been designed.

Power amplifier can be designed at smaller supply voltage for enhanced reliability. For more reliable operation with higher efficiency, class E in double cascoded has been implemented.

(d) We have designed an efficient and compact energy harvesting system to increase life of wireless sensor nodes. Using more advanced technologies, sensor nodes can be powered even without batteries by employing energy harvesting systems. The most suitable approach is to combine energy harvesting system with a compact energy storage device. More research efforts are focused on energy harvesting from the renewable energy sources to design self-powered WSNs.

Nowadays various harvesting techniques are available. Solar energy, wind energy, piezo electric energy are some of the available ambient energy sources. Among these, currently most matured technology is based on solar cells and it gives high power density. Requirement of small sized sensor nodes demands small solar panels in the harvesting system which leads to design a compact and simple solar energy harvesting system (SEH) for sensor nodes. We have designed a solar harvester for WSN nodes with compact models of solar panel and harvesting circuits. This design performed stable with high reliability and efficiency and without much power loss. In order to achieve long lasting power for the system, proposed design focused energy saving principles by using low power consumption devices in each module.

# **CHAPTER 3**

# HIGH SPEED LOW POWER VEDIC MULTIPLIERS FOR WIRELESS SENSOR NODES

## 3.1 Introduction

In real time applications like measuring various environmental conditions, fast response of the processor is required to process the measured signals. In arithmetic operations, multiplication is a fundamental function. Operations based on multiplication are frequently used in critical applications of digital signal processing (DSP) like convolution, Fast Fourier Transform (FFT), filtering etc. These are also used in arithmetic functions like inner products, MAC (multiply and accumulate) units etc. Multiplier is an important unit in digital image processing systems. Multipliers are used not only in ALU but also in other components of processor implementations, like various data path units.

Currently, with large number of applications in consumer and industrial sectors, internet of things (IOT) is a widely accepted reality. For IOT to continue growing, many intelligent devices and WSN are required [136] – [139]. Hence, in order to develop efficient and reliable sensor networks for real time and IOT applications, high speed processing is essential, to process acquired signals. So demand for low power consuming multiplier circuit with high speed for small sensor nodes has been continuously increasing.

#### **3.2** State of the Art

Recently, many efforts have been directed towards increasing the speed of multiplier with reduction in power consumption. As the efficiency of basic building block determines the performance of the system, multiplier plays an essential role in the performance of wireless sensor nodes. As the demand for high performance multipliers is highly increasing, many research efforts have been focusing on multiplication algorithms and various types of adders.

Generally, multipliers with different algorithm require large area, more power consumption and long latency. Multiplier architecture based on Vedic mathematics achieve high speed, low area and low power consumption.

Using Vedic mathematics, complex calculations can be executed with simpler steps. Due to this, recent research has focused on implementation of Vedic multiplier. Vedic algorithms for multiplication are used with different approaches as existing multiplier architectures have their own limitations.

G Ganesh Kumar et al. [54] proposed the design of high-speed Vedic multiplier and established the efficiency of Urdhva Triyakbhyam Sutra in Vedic mathematics for multiplication and explained the difference from the conventional method of multiplication. Vedic multiplier can be efficiently used for parallel generation of partial products and for eliminating steps for multiplication with zeroes. Proposed design used Karatsuba algorithm for higher bit levels. 32\*32 bit multiplier using Urdhva Triyakbhyam Sutra and its FPGA has been implemented using Verilog HDL coding and Xilinx synthesis tool on Spartan 3E kit. They have implemented proposed multiplier and conventional multiplier with shift and add techniques for 4,8,16 and 32 bits. It is observed that Vedic architecture provides least delay.

C Sheshavali et al. [50] has designed a Vedic multiplier based on ROM approach on a cyclone IIIFPGA. Their proposed multiplier is compared with Array multiplier and conventional Urdhva multiplier for 8bit and 16 bit input data. Proposed 16\*16 bit multiplier is 150% faster and consumes 42% area.

Harish Kumar [47] presented different architectures for multipliers. He focused generally on array multiplier and Vedic multipliers based on Urdhva Triyakbhyam Sutra and Nikhilam Sutra. To find out best architecture for multiplication, comparison of these architectures is carried out for 8, 16, 32 bits inputs, in terms of power and delay. The designs are done in Verilog and simulated using Xilinx10.1 ISE. From the results of power, delay and memory he proved that multiplier architecture using Urdhva Triyakbhyam Sutra gives best results compared with Array and Nikhilam architecture.

Poornima M et al. [55] have carried out an in depth study of Vedic mathematics and Urdhva Triyakbhyam Sutra for multiplication. Their paper presents study on 8\*8 Vedic multiplier architecture using Urdhva Triyakbhyam Sutra. Authors concluded that proposed Vedic multiplier is faster than Array Booth multipliers.

Surbhi Bhardwaj et al. [19] presents a Vedic multiplier using Urdhva Triyakbhyam Sutra. Authors have synthesized their proposed design in 4\*4, 8\*8 and 16\*16 using Xilinx ISE tool and speed is compared with existing multiplier architectures. Comparison results show that proposed architecture has achieved more speed.

S R Panigrahi et al. [42] also developed a Vedic multiplier using Urdhva Triyakbhyam Sutra. Their proposed architecture is designed using VHDL and simulated using Xilinx ISE. The results has shown that their design required lesser amount of hardware with reduced delay. Their proposed design is, thus, suitable for many real time signal and image processing applications.

Ramachandran S et al. [49] focused on Vedic multiplier algorithms based on Urdhva Triyakbhyam Sutra and Nikhilam Sutra. Authors have designed 8x8 bits, 16x16 bits, 32x32 bits and 64x64 bits Urdhva and Nikhilam multipliers on Xilinx ISE 11 and concluded that Urdhva multipliers work faster and better for smaller inputs; and multipliers based on Nikhilam Sutra are suitable for larger inputs. So authors designed an integrated Vedic multiplier architecture that can select better multiplier Sutra on the basis of incoming inputs. In their model, for larger inputs, ie upto 20% from the nearest base, Nikhilam multiplier has been selected; otherwise Urdhva multiplier has been selected.

M Uma Maheswara Sainath et al. [56] developed a Vedic multiplier using Urdhva Triyakbhyam Sutra. But a high speed approach using 4 : 2 compressor for addition has been included in their architecture. On the basis of comparing speed and area occupied with existing multiplier architectures, authors concluded that Vedic multiplier based on compressor is more efficient.

Premananda B S et al. [39] designed an eight bit Vedic multiplier with the help of Urdhva Triyakbhyam Sutra. Addition of partial products in Vedic multiplier has been implemented employing carry skip technique. Simulation of architecture is carried out using Xilinx and results have shown 13.65% increase in the speed of their proposed design compared with conventional multipliers.

From the literature, we can conclude that multiplier architecture using Vedic mathematics found to be a better option compared with other conventional multipliers. Among 16 Sutras of Vedic mathematics, Urdhva Triyakbhyam Sutra and Nikhilam Sutra are for multiplication. Among these two, Nikilam Sutra is suitable only for larger inputs. Hence, Urdhva Triyakbhyam Sutra is suitable for all other types of data. Further speed of multiplier speed is limited by speed of adders used for partial product addition. So the performance of Vedic multiplier can be improved if we select proper adder circuit in the multiplier architecture.

#### **3.3 Problem Formulation**

The main aim of the present work is to design a high speed low power Vedic multiplier. The proposed design integrates high speed multiplication features of Urdhva Triyakbhyam Sutra and MUX based adders for minimizing delay and power dissipation. Urdhva Triyakbhyam Sutra is used for generating partial products and MUX based adders for adding partial products.

## 3.4 Methodology

The research objective is to design high speed, low power Vedic multiplier. In order to make multiplier suitable for all types of inputs, Urdhva Sutra is selected for multiplier architecture. To enhance the speed of multiplier operation, instead of traditional adders, full adder with MUX is used. The proposed architecture reduces the propagation delay significantly. The proposed design integrates the high speed multiplication features of Urdhva Triyakbhyam Sutra and MUX based adders for minimizing delay. Urdhva Triyakbhyam Sutra is used for generating partial products and MUX based adders for adding partial products.

The proposed design of Urdhva Vedic multiplier is coded in Verilog HDL and is functionally verified through simulation using ModelSim SE 6.4. First a basic 2x2 Urdhva Vedic multiplier is designed, using half adders. This basic 2x2 multiplier is further used to implement 4x4 bits to 16x16 bits multipliers and are then simulated. The performance of proposed design is also compared with conventional Urdhva multiplier.

## **3.4.1 Vedic mathematics**

Vedic mathematics is an ancient system of mathematics existed in India. In this eminent approach, methods of basic arithmetic are simple, powerful and logical. Another advantage is its regularity. Because of these advantages, Vedic mathematics has become an important topic for research. The techniques in Vedic mathematics are mainly based on sixteen Sutras. Among sixteen Sutras, Urdhva Triyakbhyam and Nikhilam are used for multiplication [46]. Vedic multipliers have proved to be more efficient when compared to conventional ones. Urdhva Triyakbhyam Sutra architecture is more efficient compared to Nikhilam Sutra [47]. It is well known from literature [49] that Nikhilam Sutra based multipliers are expected to work better for larger inputs, that is, inputs near to base (20% from the nearest base).

Regularity and simplicity of Vedic mathematics leads to easy implementation in FPGA [50]. Another advantage of this approach is that all partial products required for multiplication are calculated much before actual multiplication begins. Based on the Vedic mathematics algorithm, these partial products are added to obtain final product which leads to a very high speed approach [56]. In addition, high speed multiplier designs based on Vedic mathematics consume low power too [54]. Therefore, in this research, a high speed multiplier using Vedic mathematics has been designed. The speed of multiplier is determined by the speed of adders used for partial product addition. Hence, in this part, we use multiplexer based full adders to increase the speed of multiplier.

#### 3.4.1.1 Urdhva Triyakbhyam Sutra.

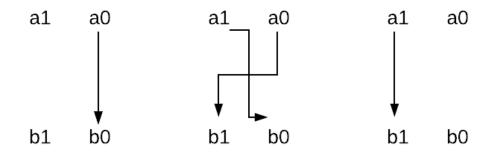

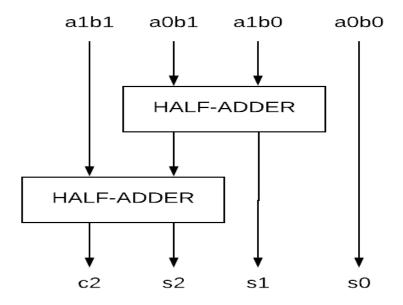

'Urdhva' literally conveys "vertical and cross-wise" and suggests that vertical and crosswise multiplication is done for obtaining the partial products and their concurrent addition. Because of the parallel processes of partial product calculation and their addition, Vedic multiplier does not depend on clock frequency. Implementation of a 2x2 Urdhva multiplier is shown in Figure 3.1 and Figure 3.2. Vedic multiplier architecture can be easily extended to higher inputs due to its regular structure. Figure 3.3 shows generation of partial products using "vertical and crosswise" logic for a 4x4 multiplier. Parallel addition of these partial products is done along with their generation [47]. Implementation of 4x4 Vedic multiplier is shown in Figure 3.4 [136]. The 4x4 multiplier can also be constructed using four, 2x2 multiplier blocks which is shown in Figure 3.5 [47].

Figure 3.1. Urdhva multiplication method for 2 bit binary numbers [47]

Figure 3.2. Block diagram of 2x2 bit Urdhva multiplier [47]

Figure 3.3. Line diagram for 4 bit Urdhva multiplication [49]

Figure 3.4. Hardware architecture for 4-bit Urdhva multiplier [140].

Figure 3.5 Block diagram for 4x4 Vedic multiplier using 2x2 multipliers [47].

## 3.4.2 Multiplexer Based Adders

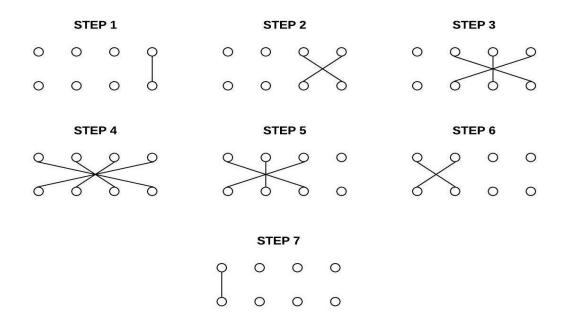

Adders become a critical hardware unit for efficient implementation of multiplier unit. Reducing the delay of full adder ultimately increases the speed of multiplier. From the literature [22], [44] and [63], it is observed that full adder with multiplexer and XOR gate gives best performance, especially in terms of delay and power dissipation. It consists of two XOR gates and one 2x1 MUX as shown in Figure 3.6.

Instead of using simulation tools, we can calculate delay mathematically using logical effort method. It gives a simple method to select best logical construct (topology) [22]. Equation (3.1) gives delay (d) for a single stage network in terms of logical effort (g), electrical effort (h) parasitic delay (p).

$$d = g^*h + p;$$

(3.1)

where 'g' represents logic gate's ability to produce output current (compared to inverter, how much worse it is in producing output current), 'h' gives ratio of output capacitance to input capacitance and 'p' gives delay of gate due to internal capacitance. As ascertained from the Table 3.1, the logical effort of 2X1 multiplexer is constant for any number of inputs, where 'n' represents number of inputs. But the logical effort for XOR, NOR and NAND gate is higher, which were the components of conventional full adder circuits. Therefore, the above full adder circuit gives minimum delay compared to other full adder circuits.

Figure 3.6 Full adder with XOR gates and MUX [22].

| Gate        | Number of Inputs (n) |     |     |     |      |          |  |